(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3564455号

(P3564455)

(45) 発行日 平成16年9月8日(2004.9.8)

(24) 登録日 平成16年6月11日(2004.6.11)

(51) Int.CI.<sup>7</sup>

F 1

**H01L 29/786**

**G02F 1/1368**

**H01L 21/336**

**H01L 21/8238**

**H01L 27/08**

H01L 29/78 613A

G02F 1/1368

H01L 27/08 331E

H01L 29/78 616A

H01L 29/78 617A

請求項の数 9 (全 18 頁) 最終頁に続く

|              |                                                |

|--------------|------------------------------------------------|

| (21) 出願番号    | 特願2001-384463 (P2001-384463)                   |

| (22) 出願日     | 平成13年12月18日 (2001.12.18)                       |

| (62) 分割の表示   | 特願平11-151840の分割<br>原出願日 平成11年5月31日 (1999.5.31) |

| (65) 公開番号    | 特開2002-252231 (P2002-252231A)                  |

| (43) 公開日     | 平成14年9月6日 (2002.9.6)                           |

| 審査請求日        | 平成13年12月18日 (2001.12.18)                       |

| (31) 優先権主張番号 | 1998P19760                                     |

| (32) 優先日     | 平成10年5月29日 (1998.5.29)                         |

| (33) 優先権主張国  | 韓国 (KR)                                        |

| (31) 優先権主張番号 | 1998P48365                                     |

| (32) 優先日     | 平成10年11月12日 (1998.11.12)                       |

| (33) 優先権主張国  | 韓国 (KR)                                        |

| (31) 優先権主張番号 | 1998P53796                                     |

| (32) 優先日     | 平成10年12月8日 (1998.12.8)                         |

| (33) 優先権主張国  | 韓国 (KR)                                        |

|           |                                                             |

|-----------|-------------------------------------------------------------|

| (73) 特許権者 | 390019839<br>三星電子株式会社<br>大韓民国京畿道水原市靈通区梅灘洞 416               |

| (74) 代理人  | 100095957<br>弁理士 龟谷 美明                                      |

| (72) 発明者  | 季 柱亨<br>大韓民国ソウル市江南区大峙洞 (番地なし)<br>住公アパート 311-1102            |

| (72) 発明者  | ホン ムンジャク<br>大韓民国京畿道城南市盆唐区亭子洞 (番地なし) ジョンドンマウル宇成アパート 609-1705 |

| (72) 発明者  | 尹 燦宙<br>大韓民国ソウル市冠岳区奉天6洞 100-556                             |

最終頁に続く

(54) 【発明の名称】 液晶表示装置用薄膜トランジスタ形成方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ガラス基板にポリシリコンでアクティブ領域をパターニングして形成する段階と；前記アクティブ領域の上側にゲート絶縁膜を形成する段階と；前記ゲート絶縁膜上に下部ゲート膜及び上部ゲート膜を順次形成する段階と；NチャンネルTFTを形成する部分ではゲート部分にのみ，PチャンネルTFTを形成する部分では全体にフォトレジストからなるエッチング保護膜を形成する段階と；前記フォトレジストをマスクとして，前記下部ゲート膜からなる下部ゲートパターンが，前記上部ゲート膜からなる上部ゲートパターンに比べ幅が狭くなるようにアンダーカットエッチングする段階と；前記フォトレジストを除去した後に，前記上部ゲートパターンをイオン注入マスクとして高濃度N型不純物イオンをイオン注入する段階と；前記上部ゲートパターンを除去した後に，NチャンネルTFTが形成された部分全体とPチャンネルTFTが形成される部分中のゲート部分にフォトレジストパターンを形成し，PチャンネルTFT領域の下部ゲートパターンを形成するエッチングをする段階と，P型不純物イオンをイオン注入する段階を有することを特徴とする，TFT形成方法。

10

## 【請求項 2】

前記上部ゲートを除去した後に，低濃度N型不純物イオンを注入する段階をさらに有することを特徴とする，請求項1に記載のTFT形成方法。

## 【請求項 3】

前記アンダーカットエッチングする段階は，下部ゲート膜に対する選択性が大きいエッチ 20

ング液を用いて，上部ゲート膜及び下部ゲート膜をエッチングすることを特徴とする，請求項1または2のいずれかに記載のTFT形成方法。

**【請求項4】**

前記P型不純物イオンをイオン注入する段階の前に，前記PチャンネルTFTの前記下部ゲートパターン上のフォトレジストパターンが前記PチャンネルTFTの前記下部ゲートパターンに比べ幅を狭くする段階をさらに有することを特徴とする，請求項1，2または3のいずれかに記載のTFT形成方法。

**【請求項5】**

前記P型不純物イオンをイオン注入する段階の後に，前記PチャンネルTFTとNチャンネルTFTの下部ゲートパターン上に，前記下部ゲートパターンより狭い幅で補助フォトレジストパターンを形成して，前記補助フォトレジストパターンをエッチングマスクとして前記下部ゲートパターンをエッチングして，幅が狭くなった下部ゲートパターンを形成する段階と，レーザアニーリングを行ってイオン注入が行なわれたアクティブ領域を活性化させる段階をさらに有することを特徴とする，請求項2または3のいずれかに記載のTFT形成方法。10

**【請求項6】**

ガラス基板上にポリシリコンでアクティブ領域をパターニングして形成する段階と；前記アクティブ領域の上側にゲート絶縁膜を形成する段階と；前記ゲート絶縁膜上に下部ゲート膜及び上部ゲート膜を順次形成する段階と；前記下部ゲート膜からなる下部ゲートパターンが前記上部ゲート膜からなる上部ゲートパターンに比べて幅が狭くなるようにアンダーカットエッチングする段階と；前記上部ゲートパターンをイオン注入マスクとして低濃度イオンをイオン注入する段階と；前記下部ゲートパターン及び上部ゲートパターンを覆うようにフォトレジストパターンを形成する段階と；前記フォトレジストパターンをイオン注入マスクとして高濃度イオンをイオン注入してソース及びドレーン領域とLDD領域及びチャンネル領域とが区分されるように形成する段階と；前記フォトレジストパターン及び前記上部ゲートパターンを順次除去する段階と；イオン注入が行なわれた前記アクティブ領域の部分をレーザアニーリングして活性化させる段階とを有することを特徴とする，TFT形成方法。20

**【請求項7】**

ガラス基板上にポリシリコンでアクティブ領域をパターニングして形成する段階と；前記アクティブ領域の上側にゲート絶縁膜を形成する段階と；前記ゲート絶縁膜上に下部ゲート膜を形成し，NチャンネルTFT領域全体とPチャンネルTFTのゲート部分を残す下部ゲートパターン形成段階と；前記下部ゲートパターンをイオン注入マスクとして用いてアクティブ領域にP型不純物イオンをイオン注入する段階と；上部ゲート膜を形成し，PチャンネルTFT領域全体とNチャンネルTFTのゲート部分を残す上部ゲートパターン形成段階と；前記上部ゲートパターンをエッチングマスクとして，下部ゲートパターンに対する等方性エッチングを行い，NチャンネルTFT領域に上部ゲートパターンに比べて幅が狭くなるようにアンダーカットエッチングをして下部ゲートパターンを形成する段階と；前記上部ゲートパターンをマスクとしてN型不純物イオンをイオン注入する段階と；前記上部ゲートパターンを選択的に除去する段階と；を有することを特徴とする，TFT形成方法。30

**【請求項8】**

前記上部ゲートパターンを除去した後に，低濃度N型不純物イオン注入する段階をさらに有することを特徴とする，請求項7に記載のTFT形成方法。

**【請求項9】**

前記アクティブ領域中でイオン注入が行なわれた部分に対するレーザアニーリングを行う段階をさらに有することを特徴とする，請求項7または8のいずれかに記載のTFT形成方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、液晶表示装置（LCD：Liquid Crystal Display）のためのTFT（Thin Film Transistor）を形成する方法に係り、より詳しくはトップゲート（TOP GATE）方式の多結晶シリコン型TFTを形成しながらオフセットあるいはLDD（Lightly Doped Drain）構造を形成する方法に関する。

**【0002】****【従来の技術】**

近年、表示装置に関連して最も活発に発展している分野はLCD分野であり、特にアクティブマトリックタイプのTFT LCD分野の発展は著しい。 10

**【0003】**

LCDは、概略的に言えば、二枚の基板間に液晶を注入し、基板の内側に形成された二つの電極に電圧を印加して、間に存在する液晶の配列を調節することによって、基板に付着される偏光板との関係で光を透過させたり遮断させる原理を利用したものである。

**【0004】**

このような基本原理下で表示装置としての機能と活用範囲を拡大するために、位相差板、反射板、バックライト、カラーフィルタなどの要素を導入して、偏光板、背向膜とラビング（rubbing）技法、電極の構成、ガラス基板等要素の変更と改善を模索する様々な試みが続いている。

**【0005】**

TFT LCDは、表示装置の画面を形成する個々画素の電極を非線形素子であるトランジスタを利用して制御する構成を有しており、トランジスタは半導体薄膜を利用してガラス基板上に形成される。そしてTFT LCDは、用いられる半導体薄膜の特性によってアモルファスシリコントイプとポリシリコントイプに大別することができる。 20

**【0006】**

アモルファスシリコンの場合、低い温度でCVDを利用して形成することができるので、ガラス基板を利用するLCDの特性上有利な点がある。しかし、アモルファスシリコンの場合には、キャリアの移動度が低いため、速い動作特性を要する駆動回路のトランジスタ素子を形成する用途としては適合せず、アモルファスシリコンは、ガラス基板上の画素電極内に形成されるスイッチング用トランジスタ素子の用途に主に使われる。そのため、LCDの駆動のためのICは別途に製作して、LCDパネル周辺部に付着して使用しなければならず、したがって、駆動モジュールのための付加的な工程が必要であり、LCD製作コストが上昇してしまう。 30

**【0007】**

一方、ポリシリコンはアモルファスシリコンに比べてキャリアの移動度が遙かに大きいため、駆動回路用ICを製作するためにも用いることができる。それゆえ、ポリシリコンをLCDのTFT形成のための半導体薄膜に用いる場合には、一連の工程を通して同一ガラス基板に画素電極のためのTFT素子と駆動回路用TFT素子と一緒に形成することができる。これはLCD製作におけるモジュール工程のコストを節減する効果をもたらすと同時にLCDの消費電力を低めることができる利点もある。 40

**【0008】**

しかし、ポリシリコンを用いようとする場合、ガラス基板にポリシリコン薄膜を形成するためには、まずアモルファスシリコン薄膜を低温CVD工程を通して形成し、ここにレーザ光線を照射する等の結晶化のための付加工程が必要であり、キャリア移動度が高いほど形成されたトランジスタでゲート電圧がオフされる瞬間漏洩電流（off Current）が過度に流れるため、画素部で十分な電界を維持できないという問題がある。以下漏洩電流（off Current）の問題を図面を参照しながらさらに説明する。

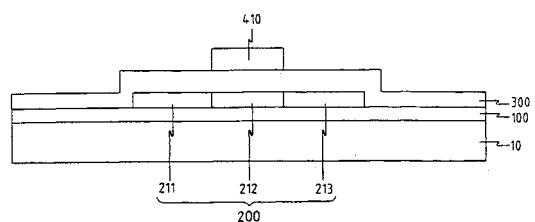

**【0009】**

図32は従来の薄膜トランジスタの構成を示す断面図である。基板100上にバッファ層である絶縁膜100が形成されており、その上にシリコンのような半導体膜からなるアクテ 50

イブ領域 200(211, 212, 213)が形成されており、その上をゲート絶縁膜 300が被覆している。ゲート絶縁膜 300上にはアクティブ領域 200のほぼ中間部分にゲート電極 410が形成されている。アクティブ領域 200内で左右部分にはゲート電極 410をマスクとしてイオン注入された結果ソース及びドレーン領域 211, 213が形成されている。

#### 【0010】

このような構成でゲート電極 410にスレショルド電圧(threshold voltage)以上の電圧が印加されると、薄膜トランジスタがオン状態になって、ドレーン領域 213に印加された画像信号により、電流がソース領域 211とドレーン領域 213間に形成されたチャンネル 212を通してソース領域 211に流れるようになる。この電流はソース領域 211と連結された画素電極に画像信号を印加するようになる。ゲート電極 410にオフ電圧(off voltage)が印加されると、トランジスタはオフ状態になるが、この際ポリシリコンで、特にNチャンネルトランジスタの場合には、キャリアである電子の移動度が大きいため多量の電流が瞬間に流れるようになる。したがって、次のオン(on)電圧が印加される時まで画素電極で維持されなければならない電界が十分に維持できなくなり、必要な画素状態を維持できないという問題を引き起こす。

#### 【0011】

このようなオフ電流(off current)発生を抑制する方法としては、薄膜トランジスタのソース及びドレーン領域とチャンネルとの接合部に、不純物濃度が低くなるようにイオン注入したLDD領域または不純物イオン注入がされていないオフセット領域を形成し、オフ電流に対するバリヤ(barrier)として作用させる方法を一般的に用いている。

#### 【0012】

以上で述べた点を考慮すると、LCDパネルを製作する過程において、画素部と駆動回路を同一ガラス基板に形成することを前提として、ポリシリコンタイプのTFTを形成する時に問題になることは、「如何にNチャンネルTFTでバリヤ領域を形成するか?」、「如何にP型やN型不純物(dopant)をイオン注入をする時に他の領域、すなわちN型やP型不純物がドーピングされる領域を遮るか?」、また「どのようにすると工程数、すなわちマスク作業の数を減じることができるか?」等である。

#### 【0013】

その中で電流バリヤ領域を形成する問題を検討すると、従来のオフセットやLDDのような電流バリヤ領域を形成する方法には、イオン注入マスクとして別途のフォトレジストパターンを形成して用いる方法、ゲート電極側壁にスペーサを形成してこのスペーサをイオン注入マスクとして用いる方法、ゲートメタルを一部酸化させて酸化された部分を利用する方法などがある。

#### 【0014】

しかし、別途のフォトレジストパターンを形成する方法は、フォトレジストパターンの位置を正確に形成することが難しく、別途パターン形成のための工程が追加されなければならない。さらにイオン注入エネルギーによる熱が生じるため、高エネルギーで多量のイオン注入を行うという条件ではフォトレジストの使用が制限されるという問題点がある。

#### 【0015】

スペーサを形成する方法の場合、スペーサを形成する別途のCVD膜を形成する工程とエッチバック工程が必要であり、エッチバックのための異方性ドライエッチングでは、エッチングの選択性が低く素子の部分的損傷が生じる場合がある。

#### 【0016】

また、ゲートメタルを酸化させる方法は、ゲートラインと他の層との電気的接触部分で酸化膜の形成を防止しなければならぬので1段階以上のマスク工程すなわち、露光、現像、エッチングのような一連の通常の工程が追加され、陽極酸化のための別途の工程が追加されなければならない。

#### 【0017】

10

20

30

40

50

**【発明が解決しようとする課題】**

本発明は、従来の方法が有する上記問題点に鑑みてなされたものであり、液晶表示装置の製作において、最小限の工程数で正確な位置にオフ電流の抑制のための LDD あるいはオフセット構造を有するポリシリコンタイプの TFT を形成するための、新規かつ改良された方法を提供することを目的としている。

**【0018】**

**【課題を解決するための手段】**

本発明のある観点による液晶表示装置用 TFT 形成方法は、ガラス基板にシリコン層を形成する段階と；前記シリコン層をパターニングしてアクティブ領域を形成する段階と；前記アクティブ領域の上側にゲート絶縁膜を形成する段階と；前記ゲート絶縁膜上に、エッチングの選択比が大きいメタルの組み合わせから成る下部ゲート膜及び上部ゲート膜を順次形成する段階と；前記上部ゲート膜上にフォトレジストを塗布し、フォトレジストパターンを形成する段階と；前記フォトレジストパターンをマスクとして、前記上部ゲート膜に対する選択性を有する第 1 エッチャントを用いたウェットエッチングにより、前記上部ゲート膜から成る上部ゲートパターンを形成する段階と；前記下部ゲート膜に対する選択性を有する第 2 エッチャントを用いたウェットエッチングにより、前記上部ゲートパターンをエッチングマスクとして利用し、前記下部ゲート膜からなる下部ゲートパターンが、前記上部ゲートパターンに比べ幅が狭くなるようにアンダーカットエッチングして、下部ゲートパターンを形成する段階と；前記上部ゲートパターンをイオン注入マスクとして高濃度イオンをイオン注入する段階と；前記上部ゲートパターンを除去する段階と；を有することを特徴とする。10

**【0019】**

本発明の別の観点による液晶表示装置用 TFT 形成方法は、ガラス基板にシリコン層を形成する段階と；前記シリコン層をパターニングしてアクティブ領域を形成する段階と；前記アクティブ領域の上側にゲート絶縁膜を形成する段階と；前記ゲート絶縁膜上に、上部ゲート膜よりイオン化傾向が大きい下部ゲート膜と、前記上部ゲート膜とを順次形成する段階と；前記上部ゲート膜上にフォトレジストを塗布し、フォトレジストパターンを形成する段階と；前記下部ゲート膜及び前記上部ゲート膜に対してエッチング性を示すエッチング液を用いたウェットエッチングにより、電気移動力の発生現象により、前記下部ゲート膜からなる下部ゲートパターンが、前記上部ゲート膜からなる上部ゲートパターンに比べ幅が狭くなるようにアンダーカットエッチングして、上部ゲートパターン及び下部ゲートパターンを形成する段階と；前記上部ゲートパターンをイオン注入マスクとして高濃度イオンをイオン注入する段階と；前記上部ゲートパターンを除去する段階と；を有することを特徴とする。20

**【0020】**

このような過程を経てポリシリコンからなるアクティブ領域にはイオン注入過程でソース及びドレーン領域が形成され、上部ゲートパターンと下部ゲートパターンの幅のゆがみ (skew) によりオフセット領域が形成され、オフ電流に対するバリヤを形成するようになる。但し、オフセット領域があまりにも長くなると駆動電流自体が減少する現像が現れる場合があることを考慮しなければならない。30

**【0021】**

本発明において、上部ゲートパターンを除去した後に低濃度イオン注入を実施する場合には、上部ゲートパターンによっては保護されるが下部ゲートパターンによっては保護されないゆがみ (skew) 領域に、低濃度でのみイオン注入が行われ、LDD 構造を形成することもできる。この構造はオフセット構造のようにオフ電流に対するバリヤの役割をしながら同時にオフセット構造で問題になることがある駆動電流の減少を防ぐ効果がある。40

**【0022】**

本発明において、他の種で 2 段階にわたりゲート膜を形成してゲート膜の材質の差を利用してアンダーカットを形成する方法には、二つのゲート膜に対する選択比が大きく、選択性が異なる 2 種のエッチャントを利用して上部ゲート膜と下部ゲート膜を各々エッチング50

する方法と、電気化学的な原理を利用して同一エッチャントで連続して二つのゲート膜をエッティングする方法が挙げられる。LCD工程では概してウェット式等方性エッティングが行われるが、特に第2エッチャントは等方性エッティングにより適正なアンダーカット構造を形成できるように調節が容易なものを選択することが重要である。この際、アンダーカットの程度はエッティング時オーバーエッティング量によって決定される。

#### 【0023】

##### 【発明の実施の形態】

以下、添付図面を参照しながら本発明の第1構成及び第2構成の望ましい実施形態を通して本発明をより詳細に説明する。添付図面の中で、図1～図8は本願発明を直接的に説明するものである。

10

された

#### 【0024】

まず、第1構成に対する第1実施形態としてポリシリコンタイプ TFT でオフ電流バリヤ領域が含まれたトランジスタを形成する方法を調べる。

#### 【0025】

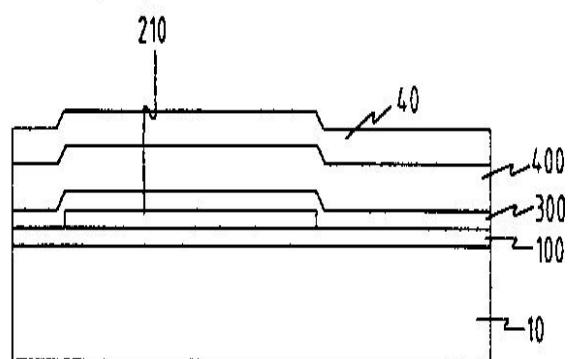

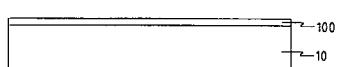

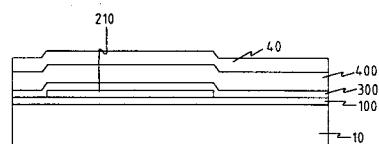

まず、透明なガラス基板10にシリコン酸化物のような物質を3000程度の厚さで形成して絶縁膜バッファ層100を形成し(図1参照)，アモルファスシリコン膜200を500ないし800厚さで蒸着する(図2参照)。

#### 【0026】

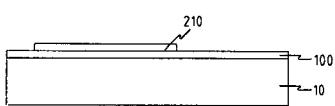

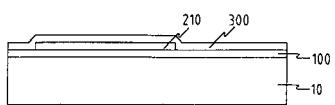

次いで、レーザアニーリングでアモルファスシリコン膜200を多結晶化し、パターニングしてアクティブ領域210を形成する(図3参照)。その上にシリコン酸化膜などの絶縁膜を1000程度の厚さで蒸着してゲート絶縁膜300を形成した次に(図4参照)，ゲート電極を形成するための下部及び上部ゲート膜400，40を各々2000ないし3000程度の厚さで蒸着する。この金属膜は一般的に相互に大きい選択比を有するAl/Cr, Cr/AlまたはCr/ITOの二重膜で形成することも可能であり、アルミニウムエッティング液またはITOエッティング液に対して選択比がほぼないAl/Mo, Mo/AlまたはMo/ITOの二重膜で形成することもできる(図5参照)。

20

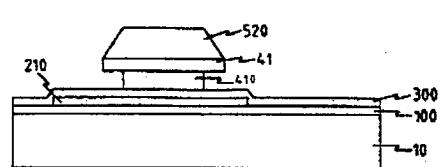

#### 【0027】

下部及び上部ゲート膜400，40上にフォトレジストを塗布してゲート電極形成のためのフォトレジストパターン520を形成した次に、フォトレジストパターン520をマスクとして下部及び上部ゲート膜400，40をウェットエッティングして上部ゲートパターンが下部ゲートパターンより外側の方向に突き出た二重構造のゲート電極410，41を形成する。

30

#### 【0028】

ここで、第一に、下部及び上部ゲート膜が選択比が大きいメタルの組み合わせから成る場合には、ゲート膜上に形成されたフォトレジストパターン520をエッティングマスクとして上部ゲート膜に対する選択性を有する第1エッチャントを用いてまず上部ゲートパターン41を形成する。そして上部ゲート膜に対してはエッティング力がなかったり少なくて下部ゲート膜に対して大きい選択性を有する第2エッチャントを用いて上部ゲートパターンを一種のエッティングマスクとして利用しながら下部ゲートパターン410を形成する。

40

#### 【0029】

第二に、例えば磷酸-硝酸-酢酸の混合液であるアルミニウムエッティング液に対して選択比が大きくないMo/Al金属の組み合わせで二重膜を形成した場合、スプレー方式または浸漬(dip)方式を利用して、二種類のゲート物質に対して、すべてエッティング性を示すこのエッティング液を用いてエッティングを進める。この場合、フォトレジストパターンをエッティングマスクとして、Moから成る上部ゲート膜のパターンがほぼ形成された状態で、Alから成る下部ゲート膜が露出すると、下部ゲート膜に対するエッティングが主に行なわれる。すなわち、下部ゲート膜が、イオン化傾向が大きいAlであり、Moから成る上層膜が接触した状態でエッティング液が作用とすると、化学電池と同様の電気移動力(electro motive force)が発生し、Alがエッティング液に溶解し、M

50

○はほとんどエッチングされない状態となる。したがって、M○から成る上部ゲート膜の下方にA1から成る下部ゲート膜がアンダーカット状態にエッチングされる。アンダーカットの程度はオーバーエッチング量、エッチング溶液の組成、エッチングモードの程度によって調節できる。（図6参照）。

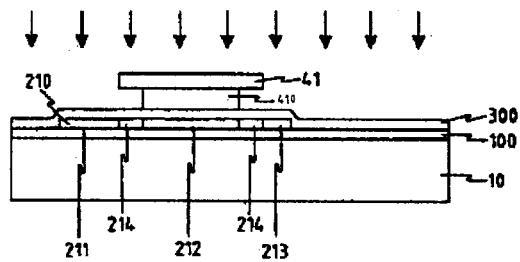

#### 【0030】

次に、フォトレジストパターン520を除去した後、全面に不純物イオン注入をする。この際、上部ゲート電極がイオン注入時マスクの役割をするのでアクティブ領域中央上部ゲートパターン41と対応する領域の外側の方向に位置したアクティブ領域がドーピングされる。このドーピングされた領域がソース及びドレーン領域211、213の間に位置し、下部ゲートパターン410と重畠されずに同時にドーピングもされない領域がオフセット領域214になる（図7参照）。 10

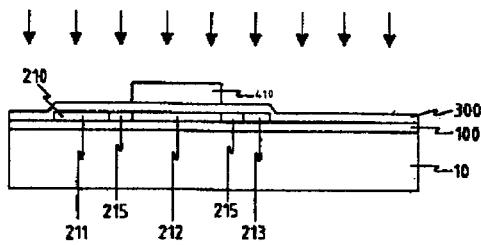

#### 【0031】

必要に応じて、上部ゲートパターン41をエッチングで除去し、下部ゲートパターン410をマスクとして低濃度でイオン注入すると、ソース及びドレーン領域の内側にLDD領域215を形成することができる（図8参照）。

#### 【0032】

以後は一般的なTFT形成方法によって絶縁膜、コンタクト、保護膜、画素電極などを形成してTFT電極構造が完成する。

#### 【0033】

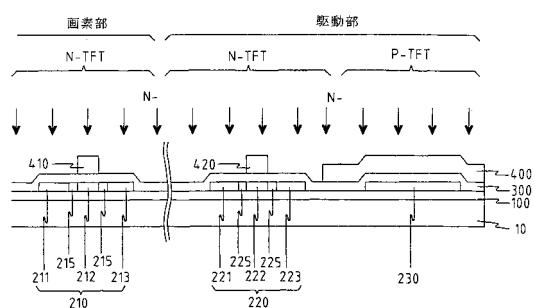

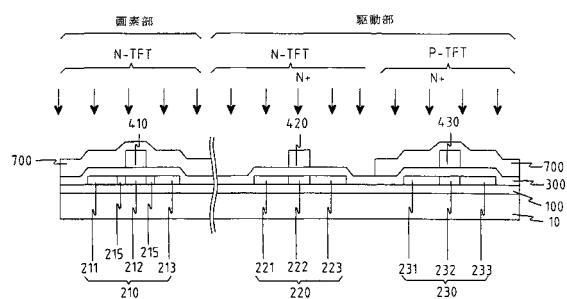

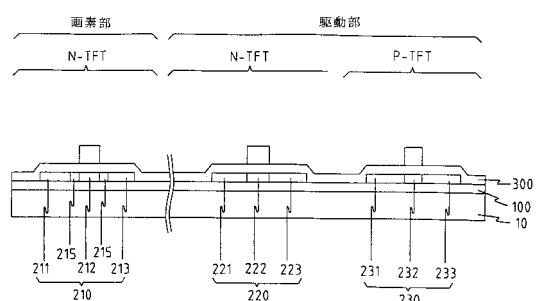

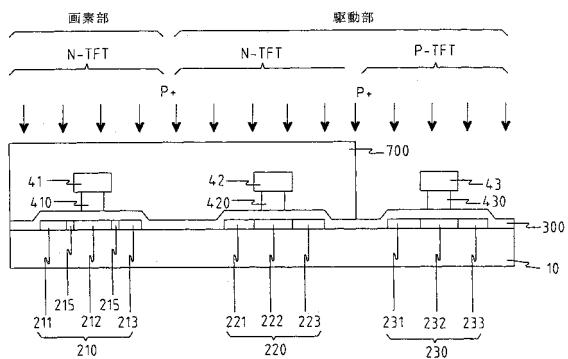

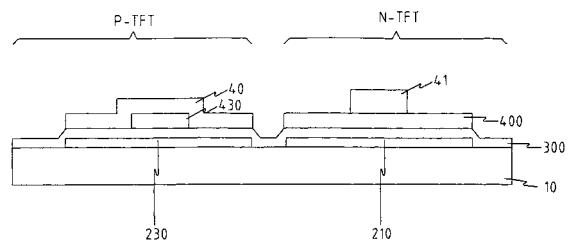

次に、本発明の第2実施形態にかかる、ガラス基板に画素部のNチャンネルと駆動回路部のNチャンネル及びPチャンネルのポリシリコンタイプTFTを同時に形成する方法について説明する。図9ないし図18は、第2の実施形態にかかるTFT形成方法を工程順序に従って示した断面図である。 20

#### 【0034】

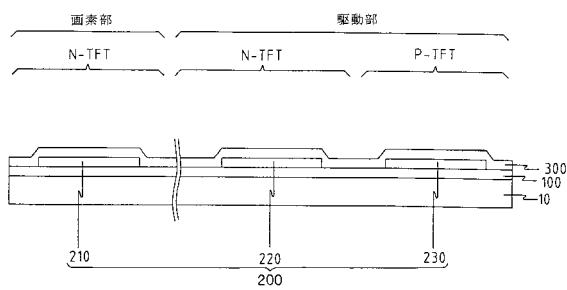

まず、ガラス基板10上にシリコン酸化膜などの物質を蒸着してバッファ層100を形成し、その上にピクセル部のNチャンネルTFTになる部分と駆動回路部のNチャンネルTFT及びPチャンネルTFTになる部分にポリシリコンアクティブ領域200（210、220、230）を形成する。このアクティブ領域200はバッファ層100上にアモルファスシリコン層を低温CVDで形成した後に、レーザアニーリングにより多結晶化し、さらにマスク技法を利用してパターニングすることにより形成することができる。 30

#### 【0035】

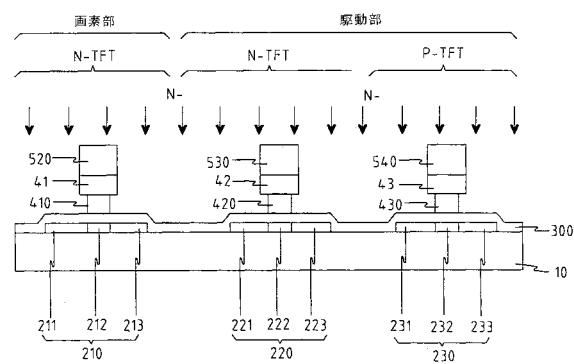

次に、シリコン酸化膜などの材料でゲート絶縁膜300を形成して（図9参照）再びその上に下部及び上部ゲート膜400、40を順次に積層する（図10参照）。この際、下部ゲート膜400を形成する金属膜は上部ゲート膜40を形成する金属膜に比べて用いられるエッチャントに対するエッチング比が大きい物質を用いる。

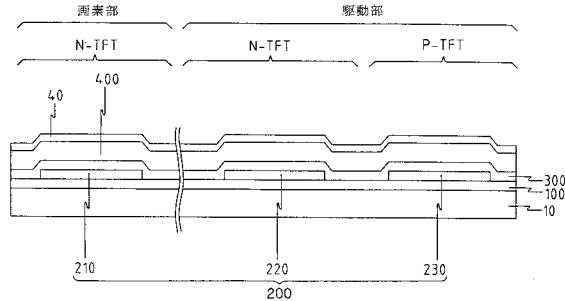

#### 【0036】

そして上部ゲート40膜上にフォトレジストを塗布してマスク技法を利用して、PチャンネルTFTになる部分ではフォトレジストパターン500を全体的に残し、NチャンネルTFTになる部分ではゲート部分にのみフォトレジストパターン520、530を残し、エッチングマスクとして用いてエッチングを進めることによって、上部ゲート膜層にNチャンネル領域の上部ゲートパターン41、42を形成する（図11）。この際、フォトレジストもゲート膜層上に存在して上部ゲートパターン41、42はフォトレジストパターン520、530下にアンダーカット部を形成する。 40

#### 【0037】

エッチングを続けると下部ゲート膜層もエッチングが行なわれるが、下部ゲート膜400を構成する物質がエッチャントに対する選択比が大きいため、下部ゲートパターン410、420は上部ゲートパターン41、42の下にアンダーカット部を有しより狭い幅で形成される。この過程で電気化学的な作用により上部ゲートパターン対下部ゲートパターンのエッチング率を高めることができ、場合によっては選択性が異なる2種のエッチング物質を利用することにより、上部ゲート膜と下部ゲート膜を順次エッチングすることができ 50

る。

**【 0 0 3 8 】**

実質的にトランジスタのゲートになる部分は下部ゲートパターン 410, 420 であり、上部ゲートパターン 41, 42 は後続工程で N チャンネルトランジスタのソース領域とドレーン領域を形成するためのイオン注入工程で、マスクの役割をし、特に下部ゲートパターンより横に突き出たゆがみ (skew) の長さは最終的に形成されるオフセットあるいは LDD 領域の幅となる。

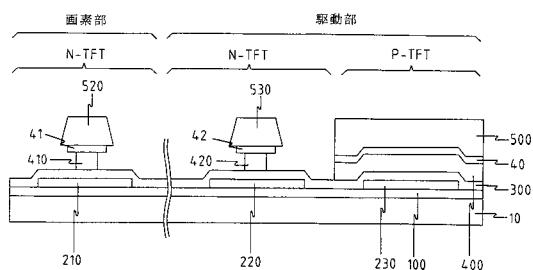

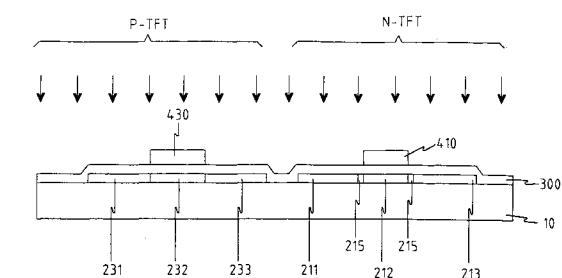

**【 0 0 3 9 】**

N チャンネル TFT 部分のゲートを形成するエッチングが完了した後に、上部ゲート層上に残存するフォトレジスト 500 及びフォトレジストパターン 520, 530 をすべて除去して、ガラス基板全面に N 型不純物のイオン注入を実施する。この際、上部ゲートパターン 41, 42 及び P チャンネル部分の上部ゲート膜 40 がイオン注入マスクとして機能する。したがって、P チャンネル TFT 部分のための別途のイオン注入マスクは必要がない。イオン注入が行なわれた N チャンネル TFT のポリシリコン層アクティブ領域 210, 220 は、ソース領域及びドレーン領域 211; 221, 213; 223 とチャンネル領域 212, 222 を形成するようになる（図 12）。

**【 0 0 4 0 】**

次に、ガラス基板全体において上部ゲート膜 40, 上部ゲートパターン 41, 42 を除去して、N 型不純物を低い濃度でイオン注入する。この際、下部ゲートパターン 410, 420 がイオン注入マスクとして機能するので、N チャンネル TFT が形成される領域で上部ゲートパターンのゆがみ (skew) に該当するアクティブ領域は LDD 領域 215, 225 を形成するようになる。（図 13 参照）。この LDD 領域は、完成されるトランジスタにおいて、オフ電流を減少させながらも駆動電流が過度に減少することを防ぐように機能する。低濃度のイオン注入工程が省略される場合には、LDD 領域でないオフセット領域が形成される。P 型 TFT が形成される部分は、全体が下部ゲート膜 400 で包まれているので、イオン注入は行われない。

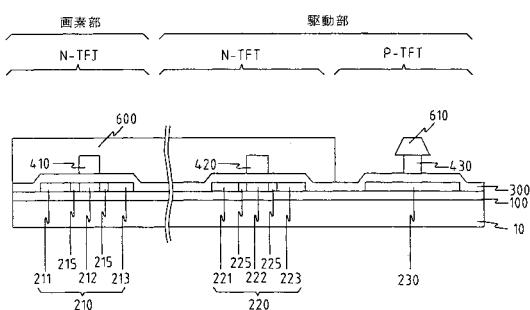

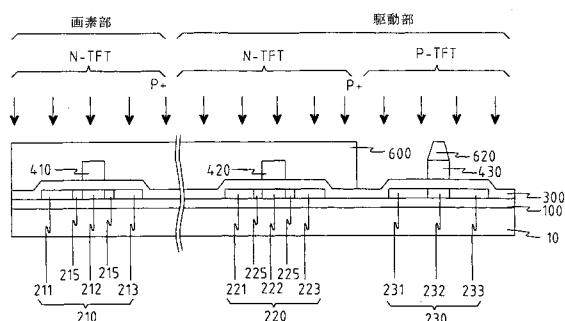

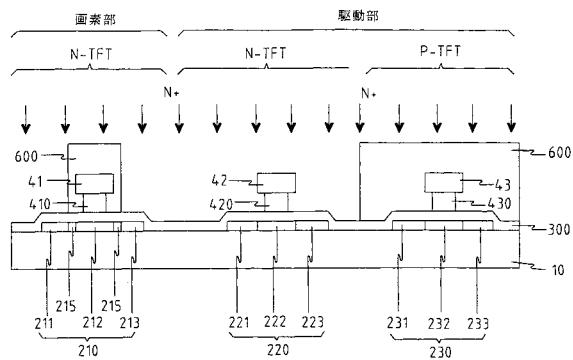

**【 0 0 4 1 】**

そして P チャンネル TFT を形成するために再びフォトレジストを塗布し、マスク工程を通して、N チャンネルトランジスタ領域には全体にフォトレジスト 600 を残し、P チャンネルトランジスタ領域にはゲートに該当する部分にフォトレジストパターン 610 を残す（図 14）。

**【 0 0 4 2 】**

フォトレジスト 600 とフォトレジストパターン 610 をエッチングマスクとしてエッチングを実施すると、P チャンネルトランジスタ部分の下部ゲート膜にゲートパターン 430 が形成される。エッチング過程でフォトレジストパターン 610 下にアンダーカット部が形成されるので、このパターンはフォトレジストパターンより幅が縮まった状態で形成される。

**【 0 0 4 3 】**

P チャンネルトランジスタでは、無理やりに LDD やオフセット領域を形成しなくても問題がないので、アッシングやベーキングでフォトレジストパターンを一部除去したりして縮少パターン 620 を形成し、さらに下部ゲートパターン 430 をイオン注入マスクとして P 型イオン注入を実施することによって P チャンネルトランジスタのソース領域及びドレーン領域 231, 233 とチャンネル領域 232 を形成する。この際、N チャンネルトランジスタ領域ではフォトレジストがイオン注入マスクの役割をする。

**【 0 0 4 4 】**

そして N チャンネルトランジスタ領域と P チャンネルゲート上部の残余フォトレジストを除去し、層間絶縁膜を形成し、ソースドレーン電極を形成し、保護膜及び画素電極を形成して、TFT を含む下部電極構造を完成する。

**【 0 0 4 5 】**

もし駆動回路部の N チャンネルで電流バリヤ領域、すなわち LDD やオフセット構造が必

10

20

30

40

50

要でない場合には、P型不純物のイオン注入を終えた時点で再び金属膜700やフォトレジスト膜を積層し、マスク技法で駆動回路部のNチャンネルトランジスタ領域のみを露出させて、高濃度N型イオン注入をもう一度さらに実施する（図16、図17参照）。この際はLDDあるいはオフセット領域のマスクがないので、この領域にも高濃度のN型不純物イオン注入が行なわれて、単純構造のソース／チャンネル／ドレーン221、222、223を構成するようになる（図18参照）。

#### 【0046】

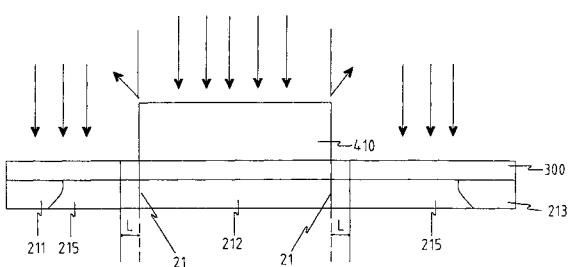

一方、本実施の形態において層間絶縁膜を形成する前に、イオン注入が行なわれたアクティブ領域に、レーザアニーリングを実施して領域を活性化させる過程を一般的に実施する。この際、ゲートパターンとすぐ隣接したアクティブ領域では、ゲートパターンによる散乱現像でイオン注入された領域の活性化が生じない問題がある。オフセットの場合には、隣接したアクティブ領域にイオン注入がよくできないために大きな問題にならないが、LDD構造の場合には領域活性化が生じない場合、その機能を実現することに問題がある場合がある。

#### 【0047】

図19はゲートパターンによる散乱によりゲート隣接部LDD領域に活性化が生じない現像を示している。ソース領域及びドレーン領域211、213とLDD領域215にレーザを照射する時、ゲートパターン410の角部でレーザの散乱が起きてゲート下部と隣接した領域、すなわちチャンネルと隣接したLDD領域では境界面21から一定幅（L）ほど活性化あるいは結晶化が生じなくなる。このような現像はトランジスタの特性低下をもたらすことがあるので問題になる。

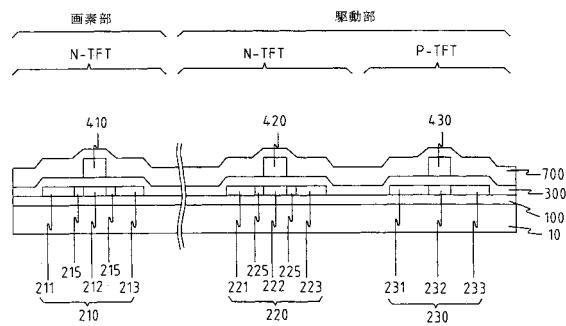

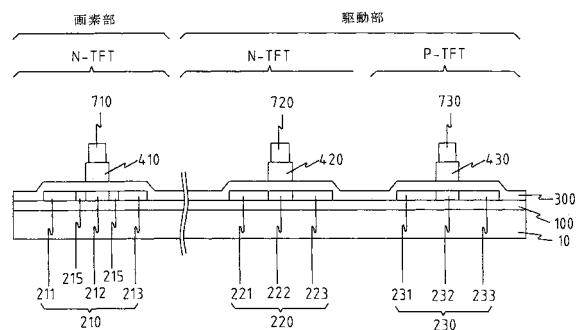

#### 【0048】

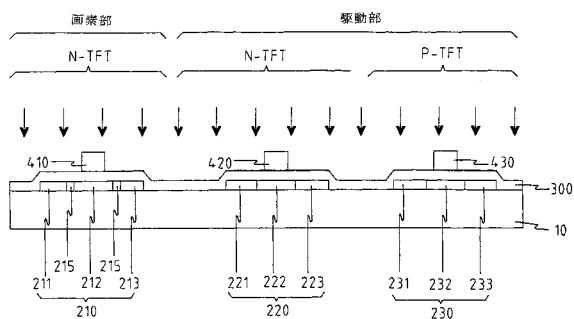

このような問題を解決するために、以上の実施形態を行う段階に付加してソース、ドレン、ゲート及びLDD領域を形成した状態で、ゲートパターン410、420、430上にフォトレジストや金属膜で幅が縮まったパターン710、720、730を形成し（図20参照）、このパターンをエッチングマスクとしてゲートパターンの側壁をさらにエッチングして除去してレーザアニーリングを実施することにより（図21参照）、ゲートパターン側壁に隣接した部分にレーザアニーリングがよく行われない場合にも、LDD部分におけるイオン注入された不純物の活性化はできるようにする方法を用いることができる。

#### 【0049】

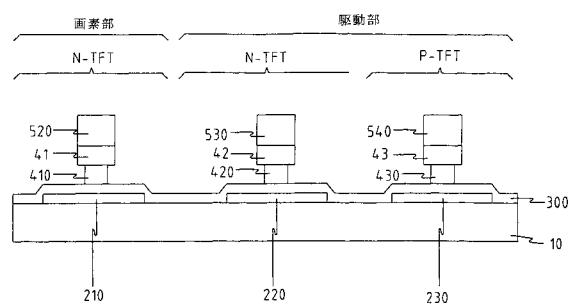

図22ないし図26は、本発明の他の実施形態にかかる構成による工程順序を示す断面図である。この構成はオフ電流バリヤ領域の形成とレーザアニーリングを考慮して、アンダーカットの形態を有する二重のゲートパターン状態で、低濃度イオン注入をまず実施してゲートパターンより幅が広い新しいフォトレジストパターンを形成するが、ゲートパターンを包むように形成してこれをイオン注入マスクとして利用して高濃度イオン注入する方法を利用したことである。

#### 【0050】

図1および図2に示されたような方法で、ガラス基板上にバッファ層とポリシリコンアクティブ領域、下部及び上部ゲート膜を形成した後に、図22に示すように、フォトレジストを蒸着して露光、現像してTFT領域のアクティブ領域に各々ゲートパターンを形成するためのフォトレジストパターン520、530、540を形成する。そしてフォトレジストパターンをエッチングマスクとして上下部ゲート膜にゲートパターン41；42；43、410；420；430を形成する。この際、下部ゲートパターンは上部に置かれたメタルマスクパターンより幅が狭く形成されるアンダーカット部が形成される。

#### 【0051】

次に、図23のようにN型不純物を低濃度でイオン注入する。この際、上部ゲートパターンがイオン注入マスクの役割をして、アンダーカットによるゆがみ（skew）が形成された部分に対応してアクティブ領域を含むマスク下部地域212、222、232にはイオン注入が行われず、そのマスクを外れた地域には低濃度イオン注入領域211、213

10

20

20

30

40

50

, 221, 223, 231, 233が形成される。

**【0052】**

そしてフォトレジストパターンを除去した後に、図24のように新しいフォトレジストを塗布し露光して、駆動回路部のP型TFT上部と画素部のN型TFTのゲート電極41, 410を覆うフォトレジストパターン600が残るようにする。この際、画素部内のゲート電極41, 410上部に置かれるフォトレジストパターン600は、その縁部がアクティブ領域200のチャンネル領域212のへりに対して一定幅外側の方向に位置するよう形成すべきであるが、これはフォトレジストパターン600をLDD領域215を形成するためのマスクとして用いるためである。

**【0053】**

フォトレジストパターン600をマスクとしてN型不純物を高濃度イオン注入して、チャンネル領域212, 222の外側の方向に薄くドーピングされている部分を高濃度イオン注入領域としてソース及びドレーン領域211; 221, 213; 223を形成する。この際、画素部のN型TFTの場合には、フォトレジストパターンの縁部がチャンネル領域212のへりから一定幅外側に位置するようゲートパターン41, 410を覆っているので、チャンネル領域212とソース及びドレーン領域211, 213間に薄くドーピングされたLDD領域215が存在するようになる。

**【0054】**

次いで、フォトレジストパターンを除去した後、新しいフォトレジストパターン700を、図25のように形成する。この際は、上記と反対に駆動回路部のP型TFT部分のみが露出するようにフォトレジストパターンが形成される。そしてホウ素のようなP型不純物イオン注入を実施してアクティブ領域230にソース及びドレーン領域231, 233を形成する。したがって、その間はイオン注入が行われないチャンネル領域232になる。

**【0055】**

そして図26に示されたようにフォトレジストパターンを除去した後に、上部ゲートパターン41, 42, 43を除去してレーザアニーリングを実施し、アクティブ領域に注入された不純物イオンを活性化させる。次に通常通り、層間絶縁膜、ソース及びドレーン電極、保護膜及び画素電極などを形成してLCDの下部基板の電極構造を完成させる。

**【0056】**

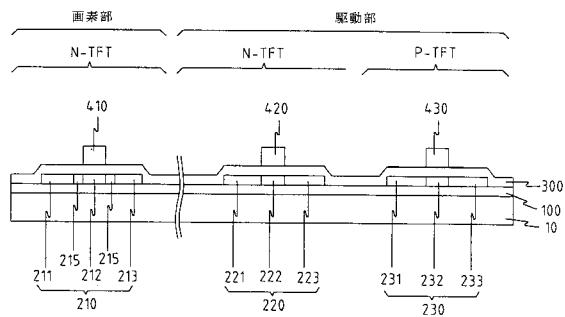

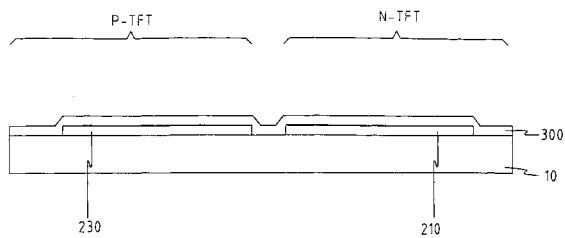

図27ないし図31は、本発明の第2の実施形態にかかる構成の工程順序図である。

**【0057】**

まず、図27のようにガラス基板10に多結晶シリコンでアクティブ領域210, 230を形成してゲート絶縁膜を形成する。このパターンを形成するためにはガラス基板に低温CVD工程を通してアモルファスシリコン膜を形成してレーザアニーリングを通してポリシリコン化した後、マスク技法を利用してTFTのアクティブ領域をパターニングすればよい。シリコン膜を形成する前にガラス基板にまずバッファ層を絶縁材質で形成することもできる。

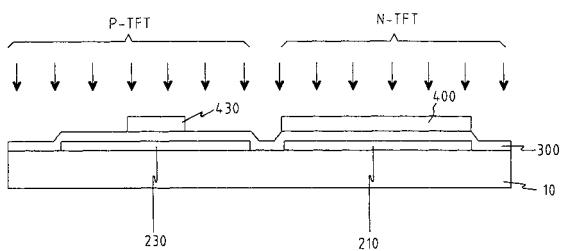

**【0058】**

次に、図28のように下部ゲート膜を形成してマスク技法を利用して、ゲート膜をNチャンネルTFT領域上部とPチャンネルTFT領域のゲート位置にのみ残して下部ゲートパターン400, 430を形成し、さらにP型不純物を基板全域にドーピングする。この過程でPチャンネルTFTが形成されNチャンネルTFT領域は下部ゲート膜がイオン注入マスクの役割をするので別途のイオン注入マスクを形成するための工程段階を省くことができる。

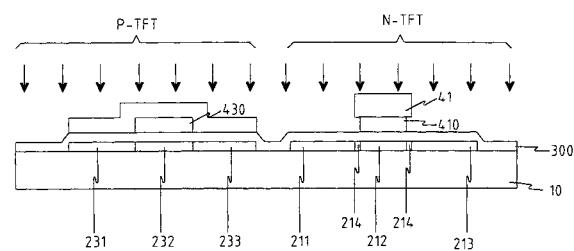

**【0059】**

そして図29のようにガラス基板全面に上部ゲート膜を形成し、マスク技法を利用してPチャンネルTFT領域上部とNチャンネルTFT領域のゲート部にのみ膜を残して、上部ゲートパターン40, 41を作る。その結果、PチャンネルTFT領域上部は、下部ゲートパターン430を上部ゲートパターン40が覆う状態となり、NチャンネルTFT領域は、領域全体を広く覆う下部ゲートパターン400上のゲート部分に上部ゲートパターン

10

20

30

40

50

41が形成される。

**【0060】**

図30は次の段階で、上部ゲートパターン41をエッティングマスクとして下部ゲートパターン400をエッティングしてゲート410を形成し、続いてN型不純物でイオン注入を実施する様子を示している。

**【0061】**

結果的にこの過程でNチャンネルTFTにおけるソース領域213、ドレーン領域211、チャンネル領域212及びゲート410が構成される。ゲート下部であるチャンネル領域とイオン注入が行なわれたソース及びドレーン領域との間には、イオン注入が行われずオフセット領域214を構成する。

10

**【0062】**

この際、PチャンネルTFT領域では、上部ゲート膜に包まれた下部ゲートパターンはエッティング過程で保護されて維持され、アクティブ領域ではP型不純物がイオン注入された状態でN型イオン注入から保護される。そしてNチャンネルTFT部分ではエッティング段階で等方性エッティングが行なわれ、上部ゲートパターンの下も一定幅にわたり下部ゲート膜がエッティングされ、アンダーカット現像を示しながら下部ゲートパターンが形成される。エッティングは等方性で行なわれ、膜質が均一であれば、下部ゲートパターンが上部ゲートパターン周辺部からアンダーカットされる幅はほぼ一定であるから、オフセット領域形成のための別途の露光工程が不要となり、露光時のミスアライメントといった工程上の困難さが軽減される。

20

**【0063】**

図31は、次の段階で上部ゲートパターンを全部除去して必要に応じて低濃度でN型不純物をイオン注入することを示している。図30におけるオフセット領域214は低濃度イオン注入によってLDD領域215になる。

**【0064】**

本実施の形態によれば、注入イオンの活性化のためのレーザアニーリングや、不要部分におけるNチャンネルTFTのLDD領域やオフセット領域の除去方法については、特に言及していないが、これらについてはすでに説明した実施形態と同様の方法により実施することが可能である。

**【0065】**

30

以上、添付図面を参照しながら、本発明にかかる液晶表示装置用薄膜トランジスタ形成方法の好適な実施形態について説明したが、本発明はかかる例に限定されない。当業者であれば特許請求の範囲に記載された技術的思想の範疇内において各種の変更例または修正例に想到することは明らかであり、それらについても当然に本発明の技術的範囲に属するものと了解される。

**【0066】**

**【発明の効果】**

本発明によるとガラス基板に画素部と駆動回路部を同時に形成するためにポリシリコンタイプのTFTを形成する場合に、NチャンネルTFTの形成時にポリシリコンにおけるキャリアの移動度が大きいために生じるオフ電流問題を解決できるように、電流バリヤ領域であるオフセット領域やLDD領域を、補助膜役割をする上部ゲート膜を利用した二重ゲート膜工程と等方性エッティングの特質であるアンダーカットの形状を利用して簡便に形成することができるようとする。

40

**【0067】**

特に本発明の第2構成によると別途のイオン注入マスクが必要としないために工程段階を省くことができ、イオン注入マスクを形成するための工程で生じる付随的な問題を予防できる。

**【図面の簡単な説明】**

**【図1】**本発明の第1構成にかかる実施の一形態を示す工程順序図である。

**【図2】**本発明の第1構成にかかる実施の一形態を示す工程順序図である。

50

【図 3】本発明の第 1 構成にかかる実施の一形態を示す工程順序図である。

【図 4】本発明の第 1 構成にかかる実施の一形態を示す工程順序図である。

【図 5】本発明の第 1 構成にかかる実施の一形態を示す工程順序図である。

【図 6】本発明の第 1 構成にかかる実施の一形態を示す工程順序図である。

【図 7】本発明の第 1 構成にかかる実施の一形態を示す工程順序図である。

【図 8】本発明の第 1 構成にかかる実施の一形態を示す工程順序図である。

【図 9】本発明の第 1 構成にかかる実施の別形態による TFT 形成方法を工程順序で示す図面である。

【図 10】本発明の第 1 構成にかかる実施の別形態による TFT 形成方法を工程順序で示す図面である。 10

【図 11】本発明の第 1 構成にかかる実施の別形態による TFT 形成方法を工程順序で示す図面である。

【図 12】本発明の第 1 構成にかかる実施の別形態による TFT 形成方法を工程順序で示す図面である。

【図 13】本発明の第 1 構成にかかる実施の別形態による TFT 形成方法を工程順序で示す図面である。

【図 14】本発明の第 1 構成にかかる実施の別形態による TFT 形成方法を工程順序で示す図面である。 20

【図 15】本発明の第 1 構成にかかる実施の別形態による TFT 形成方法を工程順序で示す図面である。

【図 16】本発明の第 1 構成にかかる実施の別形態による TFT 形成方法を工程順序で示す図面である。

【図 17】本発明の第 1 構成にかかる実施の別形態による TFT 形成方法を工程順序で示す図面である。

【図 18】本発明の第 1 構成にかかる実施の別形態による TFT 形成方法を工程順序で示す図面である。

【図 19】ゲートパターンによる散乱で、ゲート隣接部の LDD 領域に活性化が生じない現像を示す説明図である。

【図 20】図 16 に示す問題を解決するための付加工程の一例を示す説明図である。

【図 21】図 16 に示す問題を解決するための付加工程の一例を示す説明図である。 30

【図 22】本発明の他の構成にかかる実施の一形態による工程順序を示す断面図である。

【図 23】本発明の他の構成にかかる実施の一形態による工程順序を示す断面図である。

【図 24】本発明の他の構成にかかる実施の一形態による工程順序を示す断面図である。

【図 25】本発明の他の構成にかかる実施の一形態による工程順序を示す断面図である。

【図 26】本発明の他の構成にかかる実施の一形態による工程順序を示す断面図である。

【図 27】本発明の第 2 構成にかかる実施の一形態を示す工程順序図である。

【図 28】本発明の第 2 構成にかかる実施の一形態を示す工程順序図である。

【図 29】本発明の第 2 構成にかかる実施の一形態を示す工程順序図である。

【図 30】本発明の第 2 構成にかかる実施の一形態を示す工程順序図である。

【図 31】本発明の第 2 構成にかかる実施の一形態を示す工程順序図である。 40

【図 32】従来の薄膜トランジスタの構成を示す断面図である。

#### 【符号の説明】

|               |           |

|---------------|-----------|

| 1 0           | 基板        |

| 4 1           | 上部ゲートパターン |

| 2 1 1 , 2 3 3 | ドレーン領域    |

| 2 1 2 , 2 3 2 | チャンネル領域   |

| 2 1 3 , 2 3 1 | ソース領域     |

| 2 1 4         | オフセット領域   |

| 3 0 0         | ゲート絶縁膜    |

| 4 1 0         | ゲート       |

4 3 0

## 下部ゲートパターン

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図14】

【図13】

【図15】

【図16】

【図18】

【図17】

【図19】

【図20】

【図22】

【図21】

【図23】

【図24】

【図26】

【図25】

【図27】

【図28】

【図30】

【図29】

【図31】

【図32】

---

フロントページの続き

(51)Int.Cl.<sup>7</sup>

H 0 1 L 27/092

F I

H 0 1 L 27/08 3 2 1 E

## 前置審査

(72)発明者 鄭 柄厚

大韓民国京畿道安養市東安区虎溪洞(番地なし) 木蓮マウル宇成アパート501-708

(72)発明者 黃 長元

大韓民国京畿道城南市盆唐区數内洞29 陽地マウル漢陽アパート603-908

審査官 宮崎 園子

(56)参考文献 特開平07-321329(JP,A)

特開平06-104241(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H01L 21/336

H01L 29/786

H01L 21/306

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 形成液晶显示装置用薄膜晶体管的方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP3564455B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2004-09-08 |

| 申请号            | JP2001384463                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2001-12-18 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 李柱亨<br>ホンムンジヤク<br>尹燦宙<br>鄭柄厚<br>黃長元                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 李柱亨<br>ホンムンジヤク<br>尹燦宙<br>▲鄭柄厚<br>▲黃長元                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/1368 G02F1/136 H01L21/20 H01L21/336 H01L21/8238 H01L27/08 H01L27/092 H01L29/423 H01L29/49 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| CPC分类号         | H01L27/127 H01L27/1214 H01L29/42384 H01L29/4908 H01L29/66757 H01L29/78621                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | H01L29/78.613.A G02F1/1368 H01L27/08.331.E H01L29/78.616.A H01L29/78.617.A H01L27/08.321.E H01L21/20 H01L27/088.331.E H01L27/092.E H01L29/78.617.M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H092/GA59 2H092/JA25 2H092/JA33 2H092/JA34 2H092/JA35 2H092/JA40 2H092/KA04 2H092/KA05 2H092/KA12 2H092/KA18 2H092/MA15 2H092/MA17 2H092/MA27 2H092/MA30 2H092/NA22 2H092/NA27 2H192/AA24 2H192/CB02 2H192/CB34 2H192/CB53 2H192/CB83 2H192/CC32 2H192/EA76 2H192/FB02 2H192/HA64 5F048/AC04 5F048/BA16 5F048/BB09 5F048/BB12 5F048/BC06 5F048/BE08 5F052/AA02 5F052/DA02 5F052/DB01 5F052/DB04 5F052/JA01 5F110/AA16 5F110/BB02 5F110/BB04 5F110/CC02 5F110/DD02 5F110/DD13 5F110/EE03 5F110/EE04 5F110/EE07 5F110/EE14 5F110/EE22 5F110/EE43 5F110/EE50 5F110/FF02 5F110/FF27 5F110/FF29 5F110/GG02 5F110/GG13 5F110/GG25 5F110/GG42 5F110/GG44 5F110/HJ01 5F110/HJ13 5F110/HJ23 5F110/HM14 5F110/HM15 5F110/NN02 5F110/PP03 5F110/QQ02 5F110/QQ05 5F110/QQ11 5F152/BB02 5F152/CC02 5F152/CD13 5F152/CE05 5F152/CE12 5F152/CE16 5F152/CE24 5F152/FF01 |         |            |

| 优先权            | 1998P19760 1998-05-29 KR<br>1998P48365 1998-11-12 KR<br>1998P53796 1998-12-08 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 其他公开文献         | JP2002252231A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

## 摘要(译)

提供一种形成能够抑制截止电流的LDD的TFT的方法。该方法包括图案化形成在玻璃基板上的硅层以形成有源区，在有源区上形成栅极绝缘膜，在栅极绝缘膜上依次形成下栅极膜和上栅极膜，形成，以形成上和下栅极图案进行削弱作为由下部栅极层的下部栅极图案蚀刻比由上层侧栅层，高浓度离子上栅极图案作为离子注入掩模的上栅极图案更窄植入和移除上部门图案。利用这样的配置，通过利用用作辅助膜的上栅极膜和作为各向同性蚀刻的特征的底切形状的双栅极膜工艺，可以方便地形成偏移区域和LDD区域。

【 5 】