(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4104639号

(P4104639)

(45) 発行日 平成20年6月18日(2008.6.18)

(24) 登録日 平成20年4月4日(2008.4.4)

(51) Int.Cl.

F 1

**G09G 3/36 (2006.01)**

**G09G 3/20 (2006.01)**

**G02F 1/133 (2006.01)**

GO9G 3/36

GO9G 3/20 6 1 1 A

GO9G 3/20 6 2 1 B

GO9G 3/20 6 2 4 C

GO9G 3/20 6 4 1 C

請求項の数 22 (全 88 頁) 最終頁に続く

(21) 出願番号 特願2006-550817 (P2006-550817)

(86) (22) 出願日 平成17年12月27日 (2005.12.27)

(86) 国際出願番号 PCT/JP2005/023951

(87) 国際公開番号 WO2006/070829

(87) 国際公開日 平成18年7月6日 (2006.7.6)

審査請求日 平成19年6月11日 (2007.6.11)

(31) 優先権主張番号 特願2004-382003 (P2004-382003)

(32) 優先日 平成16年12月28日 (2004.12.28)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100101683

弁理士 奥田 誠司

(72) 発明者 北山 雅江

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(72) 発明者 下敷領 文一

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

審査官 西島 篤宏

最終頁に続く

(54) 【発明の名称】 液晶表示装置およびその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

それが液晶層と前記液晶層に電圧を印加する複数の電極とを有し、行および列を有するマトリクス状に配列された複数の画素を備え、

前記複数の画素のそれぞれは、それぞれの前記液晶層に互いに異なる電圧を印加することができる第1副画素および第2副画素であって、ある階調において前記第1副画素が前記第2副画素よりも高い輝度を呈する第1副画素および第2副画素を有し、

前記第1副画素および前記第2副画素のそれぞれは、

対向電極と、前記液晶層を介して前記対向電極に対向する副画素電極とによって形成された液晶容量と、

前記副画素電極に電気的に接続された補助容量電極と、絶縁層と、前記絶縁層を介して前記補助容量電極と対向する補助容量対向電極とによって形成された補助容量と、を有し、

前記対向電極は、前記第1副画素および前記第2副画素に対して共通の单一の電極であり、前記補助容量対向電極は、前記第1副画素と前記第2副画素とで電気的に独立であつて、かつ、

前記複数の画素の内の任意の画素の前記第1副画素の前記補助容量対向電極と、前記任意の画素に列方向に隣接する画素の前記第2副画素の前記補助容量対向電極とは、電気的に独立である液晶表示装置であつて、

互いに電気的に独立な複数の補助容量幹線を有し、

10

20

前記補助容量幹線のそれぞれは、前記複数の画素の前記第1副画素および前記第2副画素が有する前記補助容量対向電極のいずれかに補助容量配線を介して電気的に接続されており、

前記複数の補助容量幹線のそれぞれが供給する補助容量対向電圧は、入力映像信号の1垂直走査期間( $V - Total$ )内に、第1波形を有する第1期間(A)と、第2波形を有する第2期間(B)とを有し、前記第1期間と前記第2期間との和が垂直走査期間と等しく( $V - Total = A + B$ )、

前記第1波形は、第1電圧レベルと第2電圧レベルとの間を水平走査期間(H)の2以上の整数倍の第1周期( $P_A$ )で振動する波形であり、

前記第2波形は、連続する20以下の所定数の垂直走査期間毎に前記補助容量対向電圧の実効値が、所定の一定値をとるように設定されている、液晶表示装置。 10

#### 【請求項2】

前記所定数の垂直走査期間は、4以下の垂直走査期間である、請求項1に記載の液晶表示装置。

#### 【請求項3】

前記所定の一定値は、前記第1波形の前記第1電圧レベルと前記第2電圧レベルとの平均値と等しい、請求項1または2に記載の液晶表示装置。

#### 【請求項4】

前記複数の補助容量幹線の中で電気的に独立な補助容量幹線はL本(Lは偶数)の補助容量幹線であって、

前記第1周期( $P_A$ )は、水平走査期間のL倍( $L \cdot H$ )または $2 \cdot K \cdot L$ 倍(Kは正の整数)であり、かつ、前記第1周期における前記第1電圧レベルにある期間と前記第2電圧レベルにある期間とは互いに等しい、請求項1から3のいずれかに記載の液晶表示装置。 20

#### 【請求項5】

前記第2波形は、1垂直走査期間における前記第2波形の実効値が、前記第1電圧レベルと前記第2電圧レベルとの平均値と一致する波形である、請求項1から4のいずれかに記載の液晶表示装置。

#### 【請求項6】

前記第2波形は、第3電圧レベルと第4電圧レベルとの間を水平走査期間の正の整数倍の第2周期で振動する波形である、請求項5に記載の液晶表示装置。 30

#### 【請求項7】

前記第3電圧レベルは前記第1電圧レベルと等しく、前記第4電圧レベルは前記第2電圧レベルと等しい、請求項6に記載の液晶表示装置。

#### 【請求項8】

前記第2期間は、水平走査期間の偶数倍であって、

前記第2期間において、前記第3電圧レベルにある期間と前記第4電圧レベルにある期間とは互いに等しい、請求項6または7に記載の液晶表示装置。

#### 【請求項9】

前記第2期間は、水平走査期間の奇数倍であって、

ある垂直走査期間の前記第2期間において、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短く、当該垂直走査期間の次の垂直走査期間の前記第2期間においても、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短い、請求項6または7に記載の液晶表示装置。 40

#### 【請求項10】

前記第1期間は、前記第1周期の半整数(整数+1/2)倍である、請求項1から9のいずれかに記載の液晶表示装置。

#### 【請求項11】

前記複数の画素がN行の画素行を構成し、有効表示期間( $V - Disp$ )が水平走査期間のN倍( $N \cdot H$ )であるとき、前記第1周期を $P_A$ とすると、 50

前記第1期間( A )は、 $A = [ \text{Int} \{ (N \cdot H - P_A / 2) / P_A \} + 1 / 2 ] \cdot P_A + M \cdot P_A$  の関係(但し、Int( x )は任意の実数 x の整数部分を意味するものとし、Mは0以上の整数)を満足する、請求項10に記載の液晶表示装置。

**【請求項12】**

垂直走査期間( V - Total )が水平走査期間の Q 倍( Q · H )であるとき( Q は正の整数)、前記第1周期を  $P_A$  とすると、

前記第1期間( A )は、 $A = [ \text{Int} \{ (Q \cdot H - P_A) / P_A \} + 1 / 2 ] \cdot P_A$  の関係(但し、Int( x )は任意の実数 x の整数部分を意味するものとする)を満足する、請求項10に記載の液晶表示装置。

**【請求項13】**

垂直走査期間( V - Total )が水平走査期間の Q 倍( Q · H )であるとき( Q は正の整数)、前記第1周期を  $P_A$  とすると、

前記第1期間( A )は、 $A = [ \text{Int} \{ (Q \cdot H - 3 \cdot P_A / 2) / P_A \} + 1 / 2 ] \cdot P_A$  の関係(但し、Int( x )は任意の実数 x の整数部分を意味するものとする)を満足する、請求項10に記載の液晶表示装置。

**【請求項14】**

前記補助容量対向電圧は、垂直走査期間ごとに位相が 180° ずれる、請求項10から13のいずれかに記載の液晶表示装置。

**【請求項15】**

前記複数の補助容量幹線は偶数本の補助容量幹線であって、互いに振動の位相が 180° 異なる補助容量対向電圧を供給する補助容量幹線の対で構成されている、請求項1から14のいずれかに記載の液晶表示装置。

**【請求項16】**

請求項1から15のいずれかに記載の液晶表示装置を備えるテレビ受像機。

**【請求項17】**

それぞれが液晶層と前記液晶層に電圧を印加する複数の電極とを有し、行および列を有するマトリクス状に配列された複数の画素を備え、

前記複数の画素のそれぞれは、それぞれの前記液晶層に互いに異なる電圧を印加することができる第1副画素および第2副画素であって、ある階調において前記第1副画素が前記第2副画素よりも高い輝度を呈する第1副画素および第2副画素を有し、

前記第1副画素および前記第2副画素のそれぞれは、

対向電極と、前記液晶層を介して前記対向電極に対向する副画素電極とによって形成された液晶容量と、

前記副画素電極に電気的に接続された補助容量電極と、絶縁層と、前記絶縁層を介して前記補助容量電極と対向する補助容量対向電極とによって形成された補助容量と、を有し、

前記対向電極は、前記第1副画素および前記第2副画素に対して共通の单一の電極であり、前記補助容量対向電極は、前記第1副画素と前記第2副画素とで電気的に独立であつて、かつ、

前記複数の画素の内の任意の画素の前記第1副画素の前記補助容量対向電極と、前記任意の画素に列方向に隣接する画素の前記第2副画素の前記補助容量対向電極とは、電気的に独立であり、

互いに電気的に独立な複数の補助容量幹線を有し、

前記補助容量幹線のそれぞれは、前記複数の画素の前記第1副画素および前記第2副画素が有する前記補助容量対向電極のいずれかに補助容量配線を介して電気的に接続されている液晶表示装置の駆動方法であって、

前記複数の前記補助容量幹線のそれぞれに対応する補助容量対向電圧を用意する工程を含み、前記補助容量対向電圧を用意する工程が、

入力映像信号の1垂直走査期間( V - Total )内に、第1波形を有する第1期間( A )と、第2波形を有する第2期間( B )とを有し、前記第1期間と前記第2期間との和

10

20

30

40

50

が垂直走査期間と等しく ( $V - T_{total} = A + B$ )、

前記第1波形は、第1電圧レベルと第2電圧レベルとの間を水平走査期間 ( $H$ ) の2以上の整数倍の第1周期 ( $P_A$ ) で振動する波形であり、

前記第2波形は、連続する20以下の垂直走査期間における前記補助容量対向電圧の実効値が、所定の一定値をとるように設定された補助容量対向電圧を用意する工程である、液晶表示装置の駆動方法。

#### 【請求項18】

前記互いに電気的に独立な複数の補助容量幹線は、 $L$ 本 ( $L$ は偶数) の補助容量幹線であって、

前記補助容量対向電圧を用意する工程が、

入力映像信号の垂直走査期間 ( $V - T_{total}$ ) を、水平走査期間を  $H$  として、 $Q \cdot H$  となる整数  $Q$  を求める工程と、

前記複数の画素が  $N$  行の画素行を構成し、水平走査期間を  $H$  とし、有効表示期間 ( $V - Disp$ ) を  $N \cdot H$  とし、 $A = [ \text{Int}\{ (N - L / 2) / L \} + 1 / 2 ] \cdot L \cdot H + M \cdot L \cdot H$  の関係または  $A = [ \text{Int}\{ (N - K \cdot L) / (2 \cdot K \cdot L) \} + 1 / 2 ] \cdot 2 \cdot K \cdot L \cdot H + 2 \cdot M \cdot K \cdot L \cdot H$  (但し、 $\text{Int}(x)$  は任意の実数  $x$  の整数部分を意味し、 $K$  は正の整数であり、 $M$  は0以上の整数である) を満足する  $A$  を求める工程と、

$Q \cdot H - A = B$  となる  $B$  を求める工程と、

長さ  $A$  を有する第1期間において第1波形を有し、長さ  $B$  を有する第2期間において第2波形を有する補助容量対向電圧を生成する工程であって、

前記第1波形は第1電圧レベルと第2電圧レベルとの間を  $L \cdot H$  または  $2 \cdot K \cdot L \cdot H$  の第1周期 ( $P_A$ ) で振動する波形であり、

前記第2波形は第3電圧レベルと第4電圧レベルとの間を振動する波形であって、前記第3電圧レベルと前記第4電圧レベルとの平均値は前記第1電圧レベルと前記第2電圧レベルとの平均値と等しく、

$B / H$  が偶数の場合には、前記第3電圧レベルにある期間と、前記第4電圧レベルにある期間とが互いに等しく、

$B / H$  が奇数の場合には、ある垂直走査期間においては、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短く、当該垂直走査期間の次の垂直走査期間の前記第2期間においても、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短い、

補助容量対向電圧を生成する工程と

を包含する、請求項17に記載の液晶表示装置の駆動方法。

#### 【請求項19】

前記互いに電気的に独立な複数の補助容量幹線は、 $L$ 本 ( $L$ は偶数) の補助容量幹線であって、

前記補助容量対向電圧を用意する工程が、

入力映像信号の垂直走査期間 ( $V - T_{total}$ ) を水平走査期間を  $H$  として、 $Q \cdot H$  となる整数  $Q$  を求める工程と、

$A = [ \text{Int}\{ (Q - L) / L \} + 1 / 2 ] \cdot L \cdot H$  の関係または  $A = [ \text{Int}\{ (Q - 2 \cdot K \cdot L) / (2 \cdot K \cdot L) \} + 1 / 2 ] \cdot 2 \cdot K \cdot L \cdot H$  の関係 (但し、 $\text{Int}(x)$  は任意の実数  $x$  の整数部分を意味し、 $K$  は正の整数である) を満足する  $A$  を求める工程と、

$Q \cdot H - A = B$  となる  $B$  を求める工程と、

長さ  $A$  を有する第1期間において第1波形を有し、長さ  $B$  を有する第2期間において第2波形を有する補助容量対向電圧を生成する工程であって、

前記第1波形は第1電圧レベルと第2電圧レベルとの間を  $L \cdot H$  または  $2 \cdot K \cdot L \cdot H$  の第1周期 ( $P_A$ ) で振動する波形であり、

前記第2波形は第3電圧レベルと第4電圧レベルとの間を振動する波形であって、前記第3電圧レベルと前記第4電圧レベルとの平均値は前記第1電圧レベルと前記第2電圧レ

10

20

30

40

50

ベルとの平均値と等しく、

B / H が偶数の場合には、前記第3電圧レベルにある期間と、前記第4電圧レベルにある期間とが互いに等しく、

B / H が奇数の場合には、ある垂直走査期間においては、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短く、当該垂直走査期間の次の垂直走査期間の前記第2期間においても、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短い、

補助容量対向電圧を生成する工程と

を包含する、請求項17に記載の液晶表示装置の駆動方法。

**【請求項20】**

10

前記互いに電気的に独立な複数の補助容量幹線は、L本（Lは偶数）の補助容量幹線であって、

前記補助容量対向電圧を用意する工程が、

入力映像信号の垂直走査期間（V-Total）を水平走査期間をHとして、Q・Hとなる整数Qを求める工程と、

$A = [ \text{Int} \{ (Q - 3 \cdot L / 2) / L \} + 1 / 2 ] \cdot L$  の関係または  $A = [ \text{Int} \{ (Q - 3 \cdot K \cdot L) / (2 \cdot K \cdot L) \} + 1 / 2 ] \cdot 2 \cdot K \cdot L \cdot H$  の関係（但し、Int（x）は任意の実数xの整数部分を意味し、Kは正の整数である）を満足するAを求める工程と、

$Q \cdot H - A = B$  となるBを求める工程と、

20

長さAを有する第1期間において第1波形を有し、長さBを有する第2期間において第2波形を有する補助容量対向電圧を生成する工程であって、

前記第1波形は第1電圧レベルと第2電圧レベルとの間をL・Hまたは $2 \cdot K \cdot L \cdot H$ の第1周期（P<sub>A</sub>）で振動する波形であり、

前記第2波形は第3電圧レベルと第4電圧レベルとの間を振動する波形であって、前記第3電圧レベルと前記第4電圧レベルとの平均値は前記第1電圧レベルと前記第2電圧レベルとの平均値と等しく、

B / H が偶数の場合には、前記第3電圧レベルにある期間と、前記第4電圧レベルにある期間とが互いに等しく、

B / H が奇数の場合には、ある垂直走査期間においては、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短く、当該垂直走査期間の次の垂直走査期間の前記第2期間においても、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短い、

30

補助容量対向電圧を生成する工程と

を包含する、請求項17に記載の液晶表示装置の駆動方法。

**【請求項21】**

前記補助容量対向電圧は垂直走査期間ごとに位相が180°ずれる、請求項17から20のいずれかに記載の液晶表示装置の駆動方法。

**【請求項22】**

40

入力映像信号の垂直走査期間（V-Total）を水平走査期間をHとして、Q・Hとなる整数Qを求める工程は、当該垂直走査期間の2つ前の垂直走査期間に対して行う、請求項18から21のいずれかに記載の液晶表示装置の駆動方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は液晶表示装置およびその駆動方法に関し、特に、液晶表示装置の特性の視野角依存性を改善できる構造および駆動方法に関する。

**【背景技術】**

**【0002】**

液晶表示装置は、高精細、薄型、軽量および低消費電力等の優れた特長を有する平面表

50

示装置であり、近年、表示性能の向上、生産能力の向上および他の表示装置に対する価格競争力の向上に伴い、市場規模が急速に拡大している。

#### 【0003】

従来一般的であったツイステッド・ネマティク・モード（TNモード）の液晶表示装置は、正の誘電率異方性を持つ液晶分子の長軸を基板表面に対して略平行に配向させ、かつ、液晶分子の長軸が液晶層の厚さ方向に沿って上下の基板間で約90度捻れるように配向処理が施されている。この液晶層に電圧を印加すると、液晶分子が電界に平行に立ち上がり、捻れ配向（ツイスト配向）が解消される。TNモードの液晶表示装置は、電圧による液晶分子の配向変化に伴う旋光性の変化を利用することによって、透過光量を制御するものである。

10

#### 【0004】

TNモードの液晶表示装置は、生産マージンが広く生産性に優れている。一方、表示性能とりわけ視野角特性の点で問題があった。具体的には、TNモードの液晶表示装置の表示面を斜め方向から観測すると、表示のコントラスト比が著しく低下し、正面からの観測で黒から白までの複数の階調が明瞭に観測される画像を斜め方向から観測すると階調間の輝度差が著しく不明瞭となる点が問題であった。さらに、表示の階調特性が反転し、正面からの観測でより暗い部分が斜め方向からの観測ではより明るく観測される現象（いわゆる、階調反転現象）も問題であった。

#### 【0005】

近年、これらTNモードの液晶表示装置における視野角特性を改善した液晶表示装置として、特許文献1に記載のインプレイン・スイッチング・モード（IPSモード）、特許文献2に記載のマルチドメイン・パーティカル・アラインド・モード（MVAモード）、特許文献3に記載の軸対称配向モード（ASMモード）および、特許文献4に記載の液晶表示装置等が開発された。

20

#### 【0006】

これらの新規なモード（広視野角モード）の液晶表示装置は、いずれも視野角特性に関する上記の具体的な問題点を解決している。すなわち、表示面を斜め方向から観測した場合に表示コントラスト比が著しく低下したり、表示階調が反転するなどの問題は起こらない。

#### 【0007】

液晶表示装置の表示品位の改善が進む状況下において、今日では視野角特性の問題点として、正面観測時の特性と斜め観測時の特性が異なる点、すなわち特性の視角依存性の問題が新たに顕在化してきた。ここで、特性とは表示輝度の階調依存性であり、特性が正面方向と斜め方向で異なるということは、階調表示状態が観測方向によって異なることとなるため、写真等の画像を表示する場合や、またTV放送等を表示する場合に特に問題となる。

30

#### 【0008】

特性の視野角依存性の問題は、IPSモードよりも、MVAモードやASMモードにおいて顕著である。一方、IPSモードは、MVAモードやASMモードに比べて正面観測時のコントラスト比の高いパネルを生産性良く製造することが難しい。これらの点から、特にMVAモードやASMモードの液晶表示装置における特性の視角依存性を改善することが望まれる。

40

#### 【0009】

そこで本出願人は、特許文献5に、1つの画素を明るさの異なる複数の副画素に分割することにより特性の視角依存性、とりわけ白浮特性を改善することができる液晶表示装置および駆動方法を開示している。本明細書においてこのような表示あるいは駆動を面積階調表示、面積階調駆動、マルチ画素表示またはマルチ画素駆動などと呼ぶことがある。

#### 【0010】

特許文献5には、1つの画素（P）内の複数の副画素（SP）ごとに補助容量（Cs）を設け、補助容量を構成する補助容量対向電極（CSバスラインに接続されている）を副

50

画素ごとに電気的に独立とし、補助容量対向電極に供給する電圧（補助容量対向電圧という。）を変化させることによって、容量分割を利用して、複数の副画素の液晶層に印加される実効電圧を異ならせる液晶表示装置が開示されている。

#### 【0011】

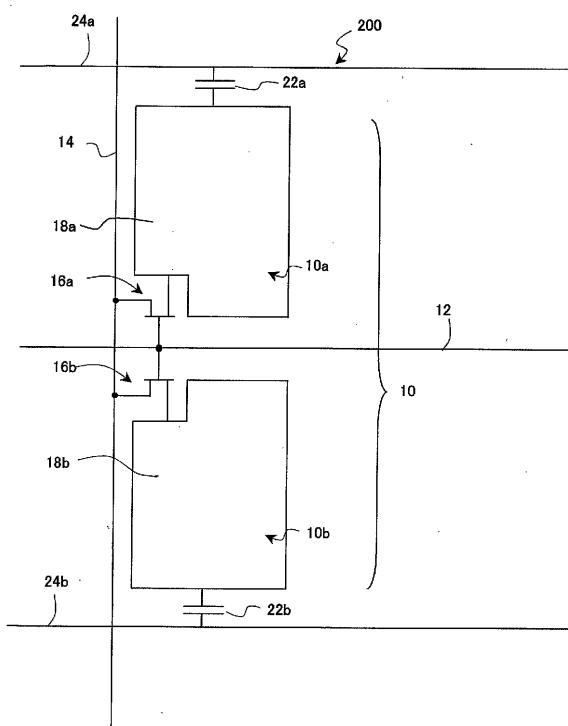

図55を参照しながら、特許文献5に記載されている液晶表示装置200の画素分割構造を説明する。

#### 【0012】

画素10は、副画素10a、10bに分割されており、副画素10a、10bは、それぞれTFT16a、TFT16b、および補助容量(CS)22a、22bが接続されている。TFT16aおよびTFT16bのゲート電極は走査線12に接続され、ソース電極は共通の（同一の）信号線14に接続されている。補助容量22a、22bは、それぞれ補助容量配線(CSバスライン)24aおよび補助容量配線24bに接続されている。補助容量22aおよび22bは、それぞれ副画素電極18aおよび18bに電気的に接続された補助容量電極と、補助容量配線24aおよび24bに電気的に接続された補助容量対向電極と、これらの間に設けられた絶縁層(不図示)によって形成されている。補助容量22aおよび22bの補助容量対向電極は互いに独立しており、それぞれ補助容量配線24aおよび24bから互いに異なる補助容量対向電圧が供給され得る構造を有している。

#### 【0013】

次に、液晶表示装置200の2つの副画素10aおよび10bの液晶層に互いに異なる実効電圧を印加することができる原理について図を用いて説明する。

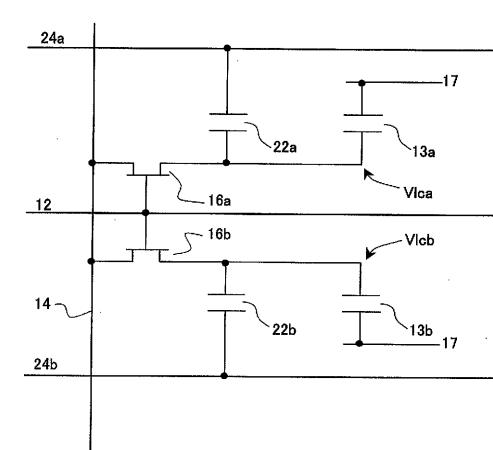

#### 【0014】

図56に、液晶表示装置200の1画素分の等価回路を模式的に示す。電気的な等価回路において、それぞれの副画素10aおよび10bの液晶層を液晶層13aおよび13bとして表している。また、副画素電極18aおよび18bと、液晶層13aおよび13bと、対向電極17(副画素10aおよび10bに対して共通)によって形成される液晶容量をC1ca、C1cbとする。

#### 【0015】

液晶容量C1caおよびC1cbの静電容量値は同一の値CLC(V)とする。CLC(V)の値は、副画素10a、10bの液晶層に印加される実効電圧(V)に依存する。また、各副画素10aおよび10bの液晶容量にそれぞれ独立に接続されている補助容量22aおよび22bをCcsa、Ccsbとし、この静電容量値は同一の値CCSとする。

#### 【0016】

副画素10aの液晶容量C1caと補助容量Ccsaの一方の電極は副画素10aを駆動するために設けたTFT16aのドレイン電極に接続されており、液晶容量C1caの他方の電極は対向電極に接続され、補助容量Ccsaの他方の電極は補助容量配線24aに接続されている。副画素10bの液晶容量C1cbと補助容量Ccsbの一方の電極は副画素10bを駆動するために設けたTFT16bのドレイン電極に接続されており、液晶容量C1cbの他方の電極は対向電極に接続され、補助容量Ccsbの他方の電極は補助容量配線24bに接続されている。TFT16aおよびTFT16bのゲート電極はいずれも走査線12に接続されており、ソース電極はいずれも信号線14に接続されている。

#### 【0017】

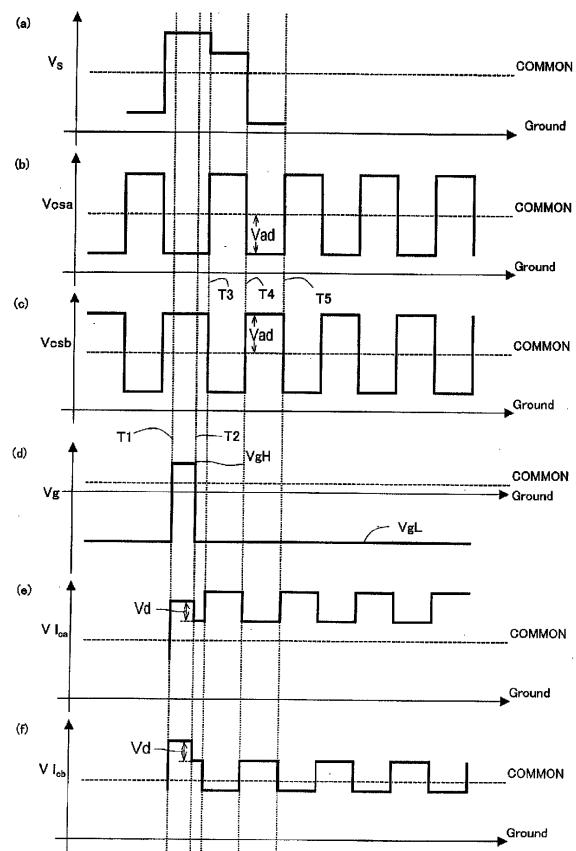

図57(a)～(f)に液晶表示装置200を駆動する際の各電圧のタイミングを模式的に示す。

#### 【0018】

図57(a)は、信号線14の電圧波形Vs、図57(b)は補助容量配線24aの電圧波形Vcса、図57(c)は補助容量配線24bの電圧波形Vc sb、図57(d)は走査線12の電圧波形Vg、図57(e)は副画素10aの画素電極18aの電圧波形

10

20

30

40

50

V1c a、図57(f)は、副画素10bの画素電極18bの電圧波形V1c bをそれぞれ示している。また、図中の破線は、対向電極17の電圧波形COMMON(Vcom)を示している。

#### 【0019】

以下、図57(a)~(f)を用いて図56の等価回路の動作を説明する。

#### 【0020】

時刻T1のときVgの電圧がVgLからVgHに変化することにより、TFT16aとTFT16bが同時に導通状態(オン状態)となり、副画素10a、10bの副画素電極18a、18bに信号線14の電圧Vsが伝達され、副画素10a、10bに充電される。同様にそれぞれの副画素の補助容量Cs a、Cs bにも信号線からの充電がなされる。

10

#### 【0021】

次に、時刻T2のとき走査線12の電圧VgがVgHからVgLに変化することにより、TFT16aとTFT16bが同時に非導通状態(OFF状態)となり、副画素10a、10b、補助容量Cs a、Cs bはすべて信号線14と電気的に絶縁される。なお、この直後TFT16a、TFT16bの有する寄生容量等の影響による引き込み現象のために、それぞれの副画素電極の電圧V1c a、V1c bは概ね同一の電圧Vdだけ低下し、

$$V1c a = Vs - Vd$$

$$V1c b = Vs - Vd$$

となる。また、このとき、それぞれの補助容量配線の電圧Vcs a、Vcs bは

$$Vcs a = Vcom - Vad$$

$$Vcs b = Vcom + Vad$$

20

である。

#### 【0022】

時刻T3で、補助容量Cs aに接続された補助容量配線24aの電圧Vcs aがVcom - VadからVcom + Vadに変化し、補助容量Cs bに接続された補助容量配線24bの電圧Vcs bがVcom + VadからVcom - Vadに2倍のVadだけ変化する。補助容量配線24aおよび24bのこの電圧変化に伴い、それぞれの副画素電極の電圧V1c a、V1c bは

$$V1c a = Vs - Vd + 2 \times Kc \times Vad$$

$$V1c b = Vs - Vd - 2 \times Kc \times Vad$$

30

へ変化する。但し、 $Kc = CCS / (CLC(V) + CCS)$ である。

#### 【0023】

時刻T4では、Vcs aがVcom + VadからVcom - Vadへ、Vcs bがVcom - VadからVcom + Vadへ、2倍のVadだけ変化し、V1c a、V1c bもまた、

$$V1c a = Vs - Vd + 2 \times Kc \times Vad$$

$$V1c b = Vs - Vd - 2 \times Kc \times Vad$$

から、

$$V1c a = Vs - Vd$$

$$V1c b = Vs - Vd$$

40

へ変化する。

#### 【0024】

時刻T5では、Vcs aがVcom - VadからVcom + Vadへ、Vcs bがVcom + VadからVcom - Vadへ、2倍のVadだけ変化し、V1c a、V1c bもまた、

$$V1c a = Vs - Vd$$

$$V1c b = Vs - Vd$$

から、

$$V1c a = Vs - Vd + 2 \times Kc \times Vad$$

$$V1c b = Vs - Vd - 2 \times Kc \times Vad$$

50

へ変化する。

**【0025】**

$V_{csa}$ 、 $V_{csb}$ 、 $V_{lca}$ 、 $V_{lcb}$ は、水平走査期間（水平書き込み時間）1Hの整数倍の間隔毎に上記T4、T5における変化を交互に繰り返す。従って、それぞれの副画素電極の電圧 $V_{lca}$ 、 $V_{lcb}$ の実効的な値は、

$$V_{lca} = V_s - V_d + K_c \times V_{ad}$$

$$V_{lcb} = V_s - V_d - K_c \times V_{ad}$$

となる。

**【0026】**

よって、副画素10a、10bの液晶層13aおよび13bに印加される実効電圧 $V_1$ 、 $V_2$ は、

$$V_1 = V_{lca} - V_{com}$$

$$V_2 = V_{lcb} - V_{com}$$

すなわち、

$$V_1 = V_s - V_d + K_c \times V_{ad} - V_{com}$$

$$V_2 = V_s - V_d - K_c \times V_{ad} - V_{com}$$

となる。

**【0027】**

従って、副画素10aおよび10bのそれぞれの液晶層13aおよび13bに印加される実効電圧の差 $V_{12}$ (=  $V_1 - V_2$ )は、 $V_{12} = 2 \times K_c \times V_{ad}$  (但し、 $K_c = CCS / (CLC(V) + CCS)$ )となり、互いに異なる電圧を印加することができる。

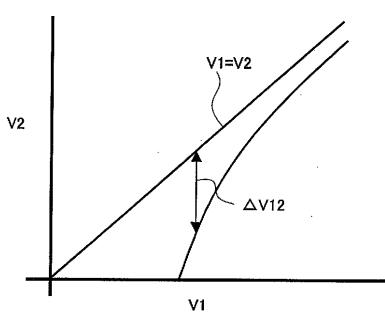

**【0028】**

図58に $V_1$ と $V_2$ の関係を模式的に示す。図58からわかるように、液晶表示装置200では、 $V_1$ の値が小さいほど $V_{12}$ の値が大きい。このように、 $V_1$ の値が小さいほど $V_{12}$ の値が大きくなるので、とりわけ白浮特性を改善することができる。

**【特許文献1】**特公昭63-21907号公報

**【特許文献2】**特開平11-242225号公報

**【特許文献3】**特開平10-186330号公報

**【特許文献4】**特開2002-55343号公報

**【特許文献5】**特開2004-62146号公報 (米国特許第6958791号明細書)

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0029】**

しかしながら、本発明者が検討した結果、特許文献5に記載されているマルチ画素構造を高精細または大型の液晶テレビに適用すると、特性の視角依存性は改善されるものの、下記の問題が発生することがわかった。米国特許第6958791号の開示内容を参考のために本明細書に援用する。

**【0030】**

補助容量対向電極(CSバスライン)に印加する振動電圧の振動の周期が短いと、表示パネルの高精細化あるいは大型化に伴って、振動電圧の振動の周期も短くなるため、振動電圧発生のための回路の作製が困難になる(高価になる)、消費電力が増加する、あるいはCSバスラインの電気的な負荷インピーダンスによる波形鈍りの影響が大きくなるという問題がある。さらに、この問題を解決するために、複数の電気的に独立なCS幹線を設けて、補助容量対向電極に印加する振動電圧の振動の周期を長くする構成とすると、後に詳述するように、表示品位が低下することがある。

**【0031】**

本発明は、上記諸点に鑑みてなされたものであり、その主な目的は、特に大型あるいは高精細の液晶表示パネルに上記面積階調表示技術を適用する際に、CSバスラインに印加する振動電圧の振動周期を長くしても、表示品位が低下しない液晶表示装置およびその駆

10

20

30

40

50

動方法を提供することにある。

【課題を解決するための手段】

【0032】

本発明の液晶表示装置は、それぞれが液晶層と前記液晶層に電圧を印加する複数の電極とを有し、行および列を有するマトリクス状に配列された複数の画素を備え、前記複数の画素のそれぞれは、それぞれの前記液晶層に互いに異なる電圧を印加することができる第1副画素および第2副画素であって、ある階調において前記第1副画素が前記第2副画素よりも高い輝度を呈する第1副画素および第2副画素を有し、前記第1副画素および前記第2副画素のそれぞれは、対向電極と、前記液晶層を介して前記対向電極に対向する副画素電極とによって形成された液晶容量と、前記副画素電極に電気的に接続された補助容量電極と、絶縁層と、前記絶縁層を介して前記補助容量電極と対向する補助容量対向電極とによって形成された補助容量とを有し、前記対向電極は、前記第1副画素および前記第2副画素に対して共通の单一の電極であり、前記補助容量対向電極は、前記第1副画素と前記第2副画素とで電気的に独立であって、かつ、前記複数の画素の内の任意の画素の前記第1副画素の前記補助容量対向電極と、前記任意の画素に列方向に隣接する画素の前記第2副画素の前記補助容量対向電極とは、電気的に独立である液晶表示装置であって、互いに電気的に独立な複数の補助容量幹線を有し、前記補助容量幹線のそれぞれは、前記複数の画素の前記第1副画素および前記第2副画素が有する前記補助容量対向電極のいずれかに補助容量配線を介して電気的に接続されており、前記複数の補助容量幹線のそれぞれが供給する補助容量対向電圧は、入力映像信号の1垂直走査期間( $V-T_{total}$ )内に、第1波形を有する第1期間(A)と、第2波形を有する第2期間(B)とを有し、前記第1期間と前記第2期間との和が垂直走査期間と等しく( $V-T_{total} = A + B$ )、前記第1波形は、第1電圧レベルと第2電圧レベルとの間を水平走査期間(H)の2以上の整数倍の第1周期( $P_A$ )で振動する波形であり、前記第2波形は、連続する20以下の所定数の垂直走査期間毎に前記補助容量対向電圧の実効値が、所定の一定値をとるように設定されていることを特徴とする。

【0033】

ある実施形態において、前記所定数の垂直走査期間は4以下の垂直走査期間である。

【0034】

ある実施形態において、前記所定の一定値は、前記第1波形の前記第1電圧レベルと前記第2電圧レベルとの平均値と等しい。

【0035】

ある実施形態において、前記複数の補助容量幹線の内で電気的に独立な補助容量幹線はL本(Lは偶数)の補助容量幹線であって、前記第1周期( $P_A$ )は、水平走査期間のL倍( $L \cdot H$ )または $2 \cdot K \cdot L$ 倍(Kは正の整数)であり、かつ、前記第1周期における前記第1電圧レベルにある期間と前記第2電圧レベルにある期間とは互いに等しい。

【0036】

ある実施形態において、前記第2波形は、1垂直走査期間における前記第2波形の実効値が、前記第1電圧レベルと前記第2電圧レベルとの平均値と一致する波形である。

【0037】

ある実施形態において、前記第2波形は、第3電圧レベルと第4電圧レベルとの間を水平走査期間の正の整数倍の第2周期で振動する波形である。

【0038】

ある実施形態において、前記第3電圧レベルは前記第1電圧レベルと等しく、前記第4電圧レベルは前記第2電圧レベルと等しい。

【0039】

ある実施形態において、前記第2期間は、水平走査期間の偶数倍であって、前記第2期間において、前記第3電圧レベルにある期間と前記第4電圧レベルにある期間とは互いに等しい。

【0040】

10

20

30

40

50

ある実施形態において、前記第2期間は、水平走査期間の奇数倍であって、ある垂直走査期間の前記第2期間において、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短く、当該垂直走査期間の次の垂直走査期間の前記第2期間においても、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短い。

#### 【0041】

ある実施形態において、前記第1期間は、前記第1周期の半整数(整数+1/2)倍である。

#### 【0042】

ある実施形態において、前記複数の画素がN行の画素行を構成し、有効表示期間(V-Disp)が水平走査期間のN倍(N·H)であるとき、前記第1周期をP<sub>A</sub>とすると、前記第1期間(A)は、 $A = [\text{Int}\{(N \cdot H - P_A / 2) / P_A\} + 1 / 2] \cdot P_A + M \cdot P_A$ の関係(但し、Int(x)は任意の実数xの整数部分を意味するものとし、Mは0以上の整数)を満足する。

10

#### 【0043】

ある実施形態において、垂直走査期間(V-Total)が水平走査期間のQ倍(Q·H)であるとき(Qは正の整数)、前記第1周期をP<sub>A</sub>とすると、前記第1期間(A)は、 $A = [\text{Int}\{(Q \cdot H - P_A) / P_A\} + 1 / 2] \cdot P_A$ の関係(但し、Int(x)は任意の実数xの整数部分を意味するものとする)を満足する。

20

#### 【0044】

ある実施形態において、垂直走査期間(V-Total)が水平走査期間のQ倍(Q·H)であるとき(Qは正の整数)、前記第1周期をP<sub>A</sub>とすると、前記第1期間(A)は、 $A = [\text{Int}\{(Q \cdot H - 3 \cdot P_A / 2) / P_A\} + 1 / 2] \cdot P_A$ の関係(但し、Int(x)は任意の実数xの整数部分を意味するものとする)を満足する。

#### 【0045】

ある実施形態において、前記補助容量対向電圧は、垂直走査期間ごとに位相が180°ずれる。

#### 【0046】

ある実施形態において、前記複数の補助容量幹線は偶数本の補助容量幹線であって、互いに振動の位相が180°異なる補助容量対向電圧を供給する補助容量幹線の対で構成されている。

30

#### 【0047】

本発明のテレビ受像機は、上記のいずれかの液晶表示装置を備えることを特徴とする。

#### 【0048】

本発明の液晶表示装置の駆動方法は、それぞれが液晶層と前記液晶層に電圧を印加する複数の電極とを有し、行および列を有するマトリクス状に配列された複数の画素を備え、前記複数の画素のそれぞれは、それぞれの前記液晶層に互いに異なる電圧を印加することができる第1副画素および第2副画素であって、ある階調において前記第1副画素が前記第2副画素よりも高い輝度を呈する第1副画素および第2副画素を有し、前記第1副画素および前記第2副画素のそれぞれは、対向電極と、前記液晶層を介して前記対向電極に対向する副画素電極とによって形成された液晶容量と、前記副画素電極に電気的に接続された補助容量電極と、絶縁層と、前記絶縁層を介して前記補助容量電極と対向する補助容量対向電極とによって形成された補助容量とを有し、前記対向電極は、前記第1副画素および前記第2副画素に対して共通の单一の電極であり、前記補助容量対向電極は、前記第1副画素と前記第2副画素とで電気的に独立であって、かつ、前記複数の画素の内の任意の画素の前記第1副画素の前記補助容量対向電極と、前記任意の画素に列方向に隣接する画素の前記第2副画素の前記補助容量対向電極とは、電気的に独立であり、互いに電気的に独立な複数の補助容量幹線を有し、前記補助容量幹線のそれぞれは、前記複数の画素の前記第1副画素および前記第2副画素が有する前記補助容量対向電極のいずれかに補助容量配線を介して電気的に接続されている液晶表示装置の駆動方法であって、前記複数の前記

40

50

補助容量幹線のそれぞれに対応する補助容量対向電圧を用意する工程を含み、前記補助容量対向電圧を用意する工程が、入力映像信号の1垂直走査期間（V-Total）内に、第1波形を有する第1期間（A）と、第2波形を有する第2期間（B）とを有し、前記第1期間と前記第2期間との和が垂直走査期間と等しく（V-Total = A + B）、前記第1波形は、第1電圧レベルと第2電圧レベルとの間を水平走査期間（H）の2以上の整数倍の第1周期（P<sub>A</sub>）で振動する波形であり、前記第2波形は、連続する20以下の垂直走査期間における前記補助容量対向電圧の実効値が、所定の一定値をとるように設定された補助容量対向電圧を用意する工程であることを特徴とする。

#### 【0049】

ある実施形態において、前記互いに電気的に独立な複数の補助容量幹線は、L本（Lは偶数）の補助容量幹線であって、前記補助容量対向電圧を用意する工程が、入力映像信号の垂直走査期間（V-Total）を水平走査期間をHとして、Q・Hとなる整数Qを求める工程と、前記複数の画素がN行の画素行を構成し、水平走査期間をHとし、有効表示期間（V-Disp）をN・Hとし、 $A = [\text{Int}\{(N - L / 2) / L\} + 1 / 2] \cdot L \cdot H + M \cdot L \cdot H$ の関係または $A = [\text{Int}\{(N - K \cdot L) / (2 \cdot K \cdot L)\} + 1 / 2] \cdot 2 \cdot K \cdot L \cdot H + 2 \cdot M \cdot K \cdot L \cdot H$ （但し、Int（x）は任意の実数xの整数部分を意味し、Kは正の整数であり、Mは0以上の整数である）を満足するAを求める工程と、Q・H - A = BとなるBを求める工程と、長さAを有する第1期間において第1波形を有し、長さBを有する第2期間において第2波形を有する補助容量対向電圧を生成する工程であって、前記第1波形は第1電圧レベルと第2電圧レベルとの間をL・Hまたは $2 \cdot K \cdot L \cdot H$ の第1周期（P<sub>A</sub>）で振動する波形であり、前記第2波形は第3電圧レベルと第4電圧レベルとの間を振動する波形であって、前記第3電圧レベルと前記第4電圧レベルとの平均値は前記第1電圧レベルと前記第2電圧レベルとの平均値と等しく、B/Hが偶数の場合には、前記第3電圧レベルにある期間と、前記第4電圧レベルにある期間とが互いに等しく、B/Hが奇数の場合には、ある垂直走査期間においては、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短く、当該垂直走査期間の次の垂直走査期間の前記第2期間においても、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短い、補助容量対向電圧を生成する工程とを包含する。

#### 【0050】

ある実施形態において、前記互いに電気的に独立な複数の補助容量幹線は、L本（Lは偶数）の補助容量幹線であって、前記補助容量対向電圧を用意する工程が、入力映像信号の垂直走査期間（V-Total）を水平走査期間をHとして、Q・Hとなる整数Qを求める工程と、 $A = [\text{Int}\{(Q - L) / L\} + 1 / 2] \cdot L \cdot H$ の関係または $A = [\text{Int}\{(Q - 2 \cdot K \cdot L) / (2 \cdot K \cdot L)\} + 1 / 2] \cdot 2 \cdot K \cdot L \cdot H$ の関係（但し、Int（x）は任意の実数xの整数部分を意味し、Kは正の整数である）を満足するAを求める工程と、Q・H - A = BとなるBを求める工程と、長さAを有する第1期間において第1波形を有し、長さBを有する第2期間において第2波形を有する補助容量対向電圧を生成する工程であって、前記第1波形は第1電圧レベルと第2電圧レベルとの間をL・Hまたは $2 \cdot K \cdot L \cdot H$ の第1周期（P<sub>A</sub>）で振動する波形であり、前記第2波形は第3電圧レベルと第4電圧レベルとの間を振動する波形であって、前記第3電圧レベルと前記第4電圧レベルとの平均値は前記第1電圧レベルと前記第2電圧レベルとの平均値と等しく、B/Hが偶数の場合には、前記第3電圧レベルにある期間と、前記第4電圧レベルにある期間とが互いに等しく、B/Hが奇数の場合には、ある垂直走査期間においては、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短く、当該垂直走査期間の次の垂直走査期間の前記第2期間においても、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短い、補助容量対向電圧を生成する工程とを包含する。

#### 【0051】

ある実施形態において、前記互いに電気的に独立な複数の補助容量幹線は、L本（Lは

10

20

30

40

50

偶数)の補助容量幹線であって、前記補助容量対向電圧を用意する工程が、入力映像信号の垂直走査期間( $V - Total$ )を水平走査期間を $H$ として、 $Q \cdot H$ となる整数 $Q$ を求める工程と、 $A = [Int\{(Q - 3 \cdot L / 2) / L\} + 1 / 2] \cdot L$ の関係または $A = [Int\{(Q - 3 \cdot K \cdot L) / (2 \cdot K \cdot L)\} + 1 / 2] \cdot 2 \cdot K \cdot L \cdot H$ の関係(但し、 $Int(x)$ は任意の実数 $x$ の整数部分を意味し、 $K$ は正の整数である)を満足する $A$ を求める工程と、 $Q \cdot H - A = B$ となる $B$ を求める工程と、長さ $A$ を有する第1期間において第1波形を有し、長さ $B$ を有する第2期間において第2波形を有する補助容量対向電圧を生成する工程であって、前記第1波形は第1電圧レベルと第2電圧レベルとの間を $L \cdot H$ または $2 \cdot K \cdot L \cdot H$ の第1周期( $P_A$ )で振動する波形であり、前記第2波形は第3電圧レベルと第4電圧レベルとの間を振動する波形であって、前記第3電圧レベルと前記第4電圧レベルとの平均値は前記第1電圧レベルと前記第2電圧レベルとの平均値と等しく、 $B / H$ が偶数の場合には、前記第3電圧レベルにある期間と、前記第4電圧レベルにある期間とが互いに等しく、 $B / H$ が奇数の場合には、ある垂直走査期間においては、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短く、当該垂直走査期間の次の垂直走査期間の前記第2期間においても、前記第3電圧レベルにある期間は前記第4電圧レベルにある期間よりも1水平走査期間分だけ短い、補助容量対向電圧を生成する工程とを包含する。

## 【0052】

ある実施形態において、前記補助容量対向電圧は垂直走査期間ごとに位相が $180^\circ$ ずれる。

10

## 【0053】

ある実施形態において、入力映像信号の垂直走査期間( $V - Total$ )を水平走査期間を $H$ として、 $Q \cdot H$ となる整数 $Q$ を求める工程は、当該垂直走査期間の2つ前の垂直走査期間に対して行う。

20

## 【発明の効果】

## 【0054】

本発明によると、特に大型あるいは高精細の液晶表示パネルに上記面積階調表示技術を適用する際に、CSバスラインに印加する振動電圧の振動周期を長くしても、表示品位が低下しない液晶表示装置およびその駆動方法を提供することができる。

30

## 【図面の簡単な説明】

## 【0055】

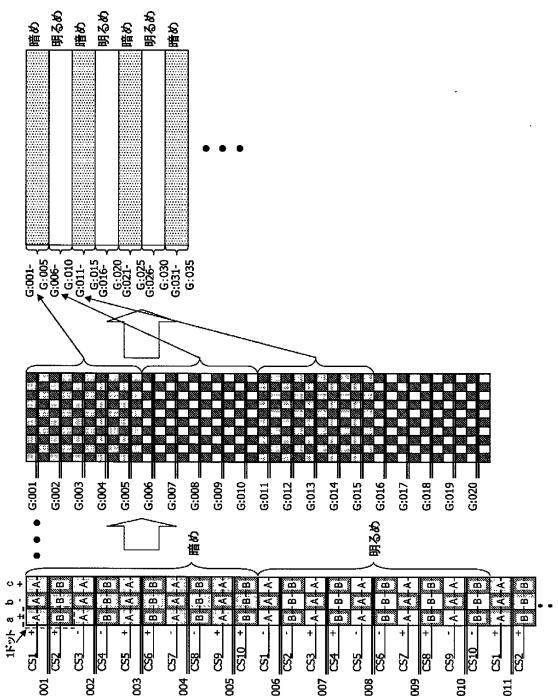

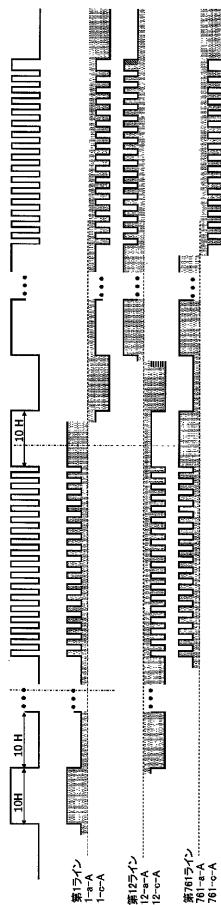

【図1】本発明による実施形態の液晶表示装置の画素配列を模式的に示す図である。

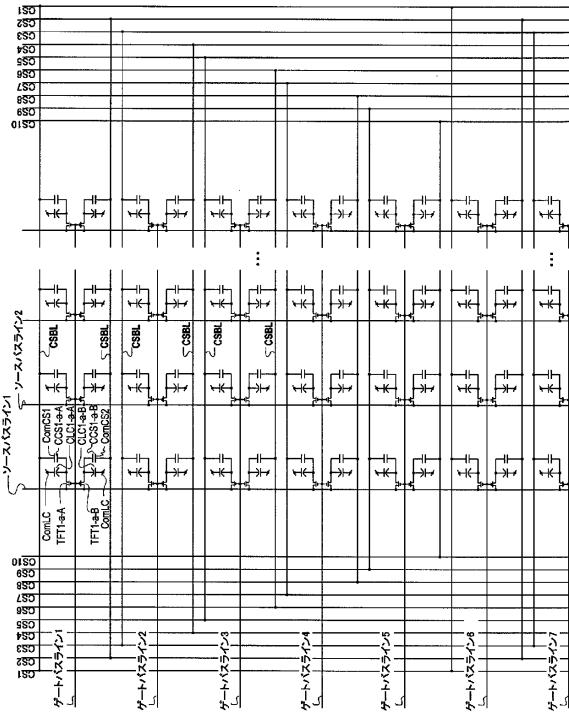

【図2】本発明による実施形態の液晶表示装置のある領域の等価回路図である。

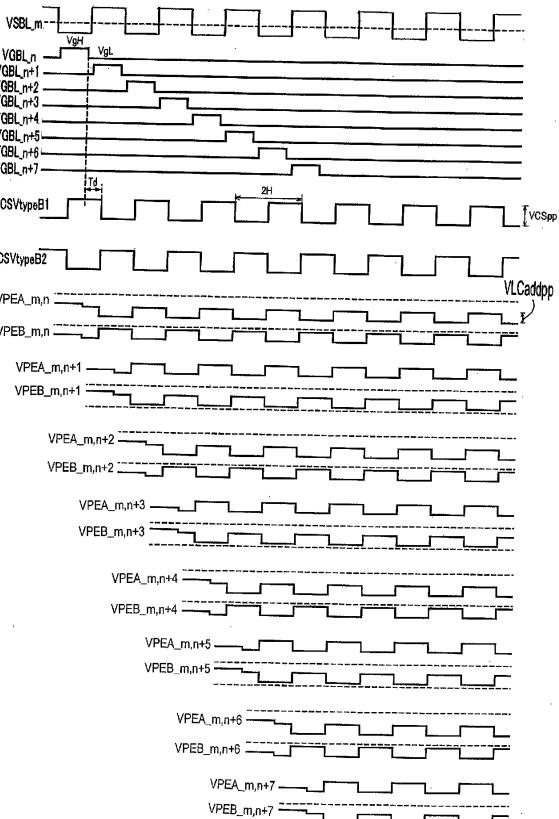

【図3A】図2に示した液晶表示装置におけるゲートバスラインの電圧波形を基準としたCSバスラインに供給される振動電圧の振動の周期および位相および各副画素電極の電圧を示す図である。

【図3B】図2に示した液晶表示装置におけるゲートバスラインの電圧波形を基準としたCSバスラインに供給される振動電圧の振動の周期および位相および各副画素電極の電圧を示す図である(液晶層に印加される電圧の極性が図3Aの場合と反転)。

【図4A】図2に示した液晶表示装置の駆動状態(図3Aの電圧を用いた場合)を示す模式図である。

40

【図4B】図2に示した液晶表示装置の駆動状態(図3Bの電圧を用いた場合)を示す模式図である。

【図5】(a)は、本発明の第2の局面による実施形態の液晶表示装置におけるCSバスラインに振動電圧を供給するための構成を模式的に示す図であり、(b)はその電気的な負荷インピーダンスを近似した等価回路を模式的に示す図である。

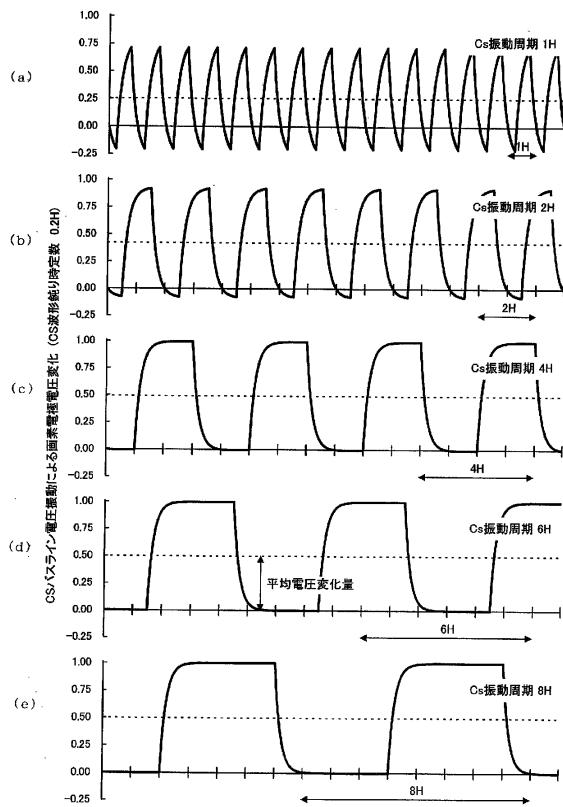

【図6】(a)から(e)は、CS電圧波形鈍りが無い場合の副画素電極の振動電圧波形を模式的に示す図である。

【図7】(a)から(e)は、CR時定数が「0.2H」の場合に相当する波形鈍りが発生した場合の副画素電極の振動電圧波形を模式的に示す図である。

50

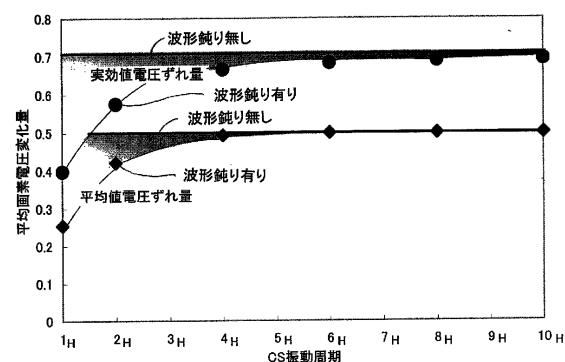

【図8】図6、図7の波形を基に算出した振動電圧の平均値および実効値とCSバスライン電圧の振動周期の関係を示すグラフである。

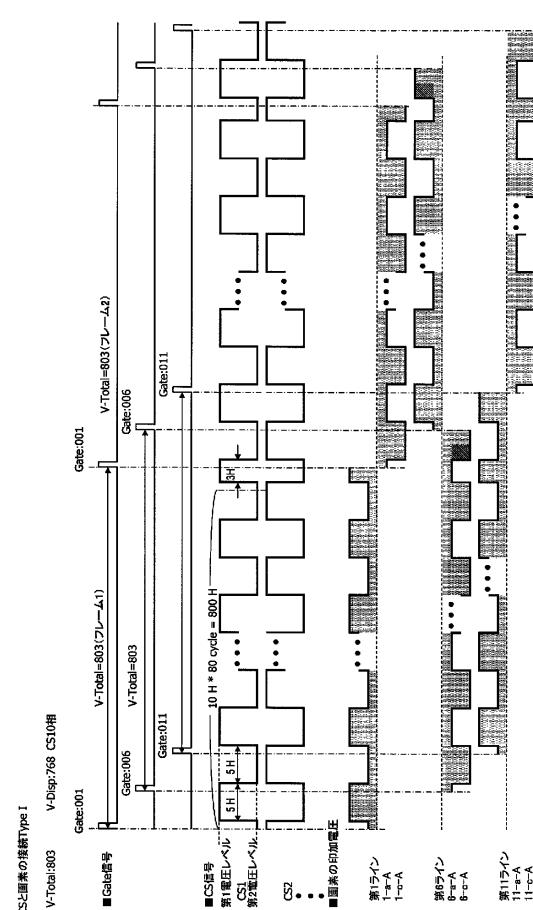

【図9】本発明のType Iの構成を有する実施形態の液晶表示装置の等価回路を模式的に示す図である。

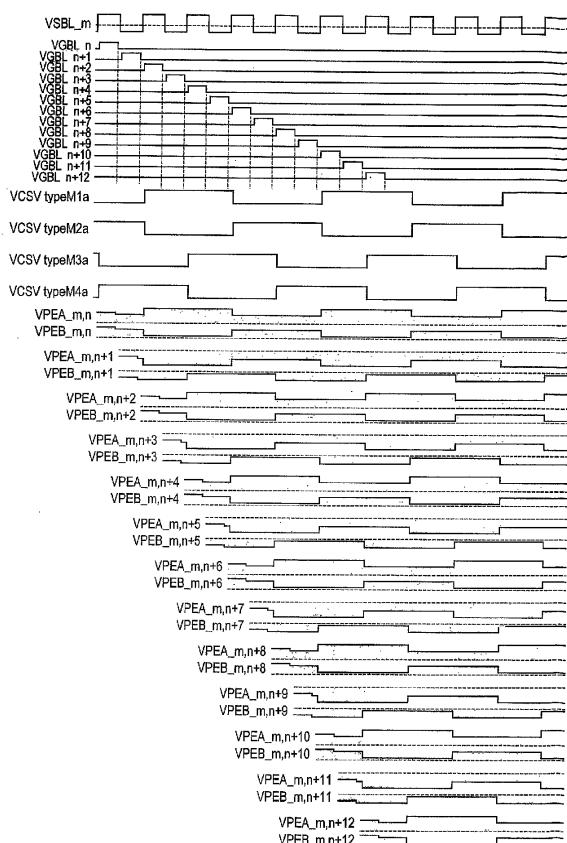

【図10A】図9に示した液晶表示装置におけるゲートバスラインの電圧波形を基準としたCSバスラインに供給される振動電圧の振動の周期および位相および各副画素電極の電圧を示す図である。

【図10B】図9に示した液晶表示装置におけるゲートバスラインの電圧波形を基準としたCSバスラインに供給される振動電圧の振動の周期および位相および各副画素電極の電圧を示す図である(液晶層に印加される電圧の極性が図10Aの場合と反転)。 10

【図11A】図9に示した液晶表示装置の駆動状態(図10Aの電圧を用いた場合)を示す模式図である。

【図11B】図9に示した液晶表示装置の駆動状態(図10Bの電圧を用いた場合)を示す模式図である。

【図12】本発明のType Iの構成を有する他の実施形態の液晶表示装置の等価回路を模式的に示す図である。

【図13A】図12に示した液晶表示装置におけるゲートバスラインの電圧波形を基準としたCSバスラインに供給される振動電圧の振動の周期および位相および各副画素電極の電圧を示す図である。

【図13B】図12に示した液晶表示装置におけるゲートバスラインの電圧波形を基準としたCSバスラインに供給される振動電圧の振動の周期および位相および各副画素電極の電圧を示す図である(液晶層に印加される電圧の極性が図13Aの場合と反転)。 20

【図14A】図12に示した液晶表示装置の駆動状態(図13Aの電圧を用いた場合)を示す模式図である。

【図14B】図12に示した液晶表示装置の駆動状態(図13Bの電圧を用いた場合)を示す模式図である。

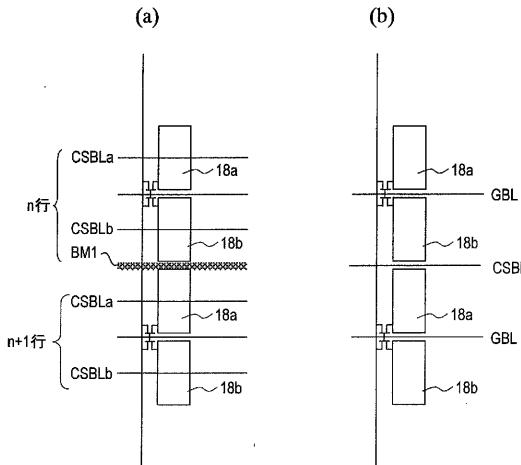

【図15】(a)は本発明のType Iの構成を有する実施形態の液晶表示装置におけるCSバスラインおよび画素間遮光層の配置例を示す模式図であり、(b)は本発明のType IIの構成を有する実施形態の液晶表示装置における画素間遮光層を兼ねるCSバスラインの配置例を模試的に示す図である。 30

【図16A】本発明のType IIの構成を有する実施形態の液晶表示装置の駆動状態を示す模式図である。

【図16B】本発明のType IIの構成を有する実施形態の液晶表示装置の駆動状態を示す模式図であり、図16Aの駆動状態と液晶層に印加される電界の向きが逆の場合を示している。

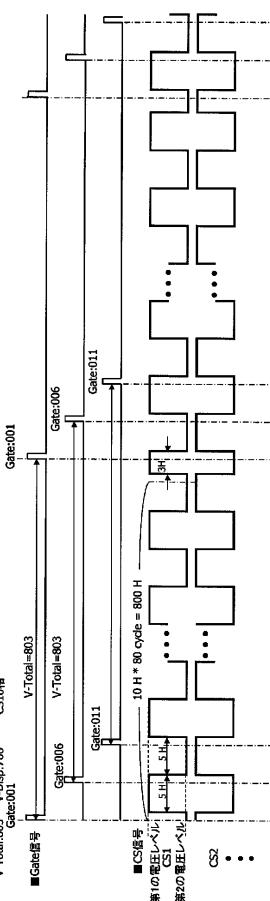

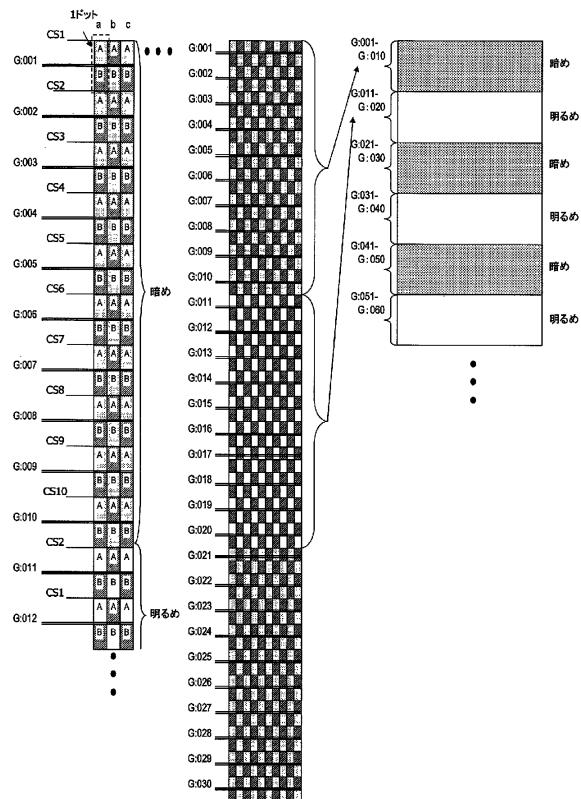

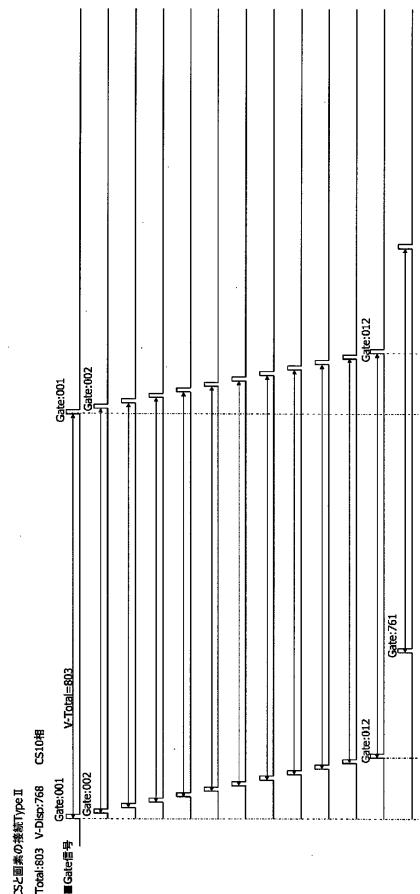

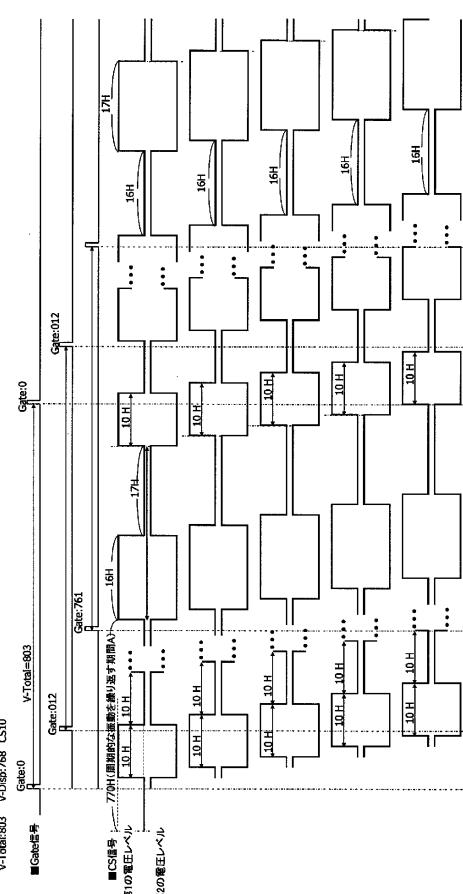

【図17】本発明のType IIの構成を有する実施形態の液晶表示装置のマトリックス構成(CSバスラインの接続形態)示す模式図である。

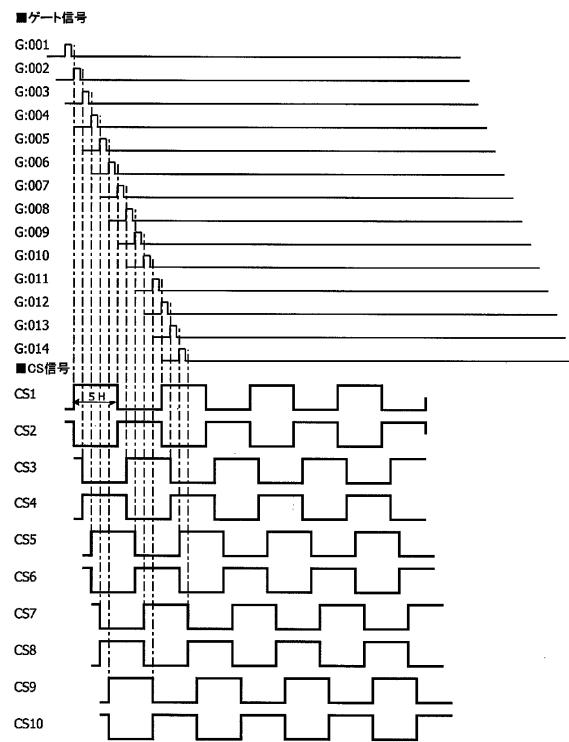

【図18】図17に示した液晶表示装置の駆動信号波形を示す模式図である。

【図19】本発明のType IIの構成を有する他の実施形態の液晶表示装置のマトリックス構成(CSバスラインの接続形態)示す模式図である。 40

【図20】図19に示した液晶表示装置の駆動信号波形を示す模式図である。

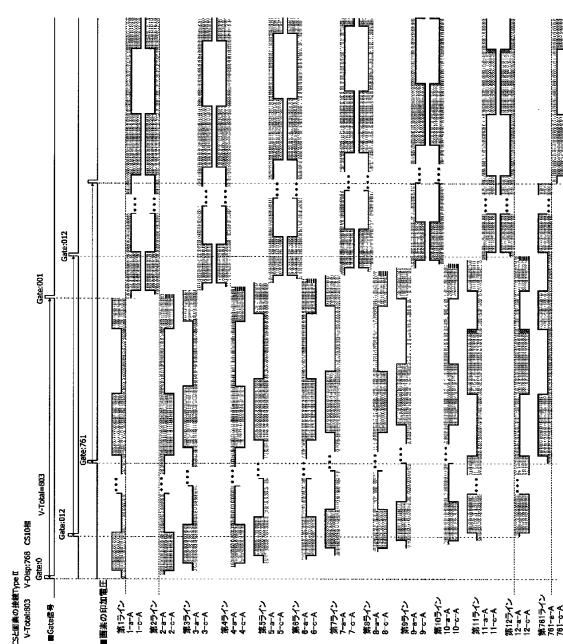

【図21】本発明のType IIの構成を有するさらに他の実施形態の液晶表示装置のマトリックス構成(CSバスラインの接続形態)示す模式図である。

【図22】図21に示した液晶表示装置の駆動信号波形を示す模式図である。

【図23】本発明のType IIの構成を有するさらに他の実施形態の液晶表示装置のマトリックス構成(CSバスラインの接続形態)示す模式図である。

【図24】図23に示した液晶表示装置の駆動信号波形を示す模式図である。

【図25】本発明のType IIの構成を有するさらに他の実施形態の液晶表示装置のマトリックス構成(CSバスラインの接続形態)示す模式図である。

【図26】図25に示した液晶表示装置の駆動信号波形を示す模式図である。 50

【図27】本発明のType IIの構成を有するさらに他の実施形態の液晶表示装置のマトリックス構成(CSバスラインの接続形態)示す模式図である。

【図28】図27に示した液晶表示装置の駆動信号波形を示す模式図である。

【図29】本発明のType IIの構成を有するさらに他の実施形態の液晶表示装置のマトリックス構成(CSバスラインの接続形態)示す模式図である。

【図30】図29に示した液晶表示装置の駆動信号波形を示す模式図である。

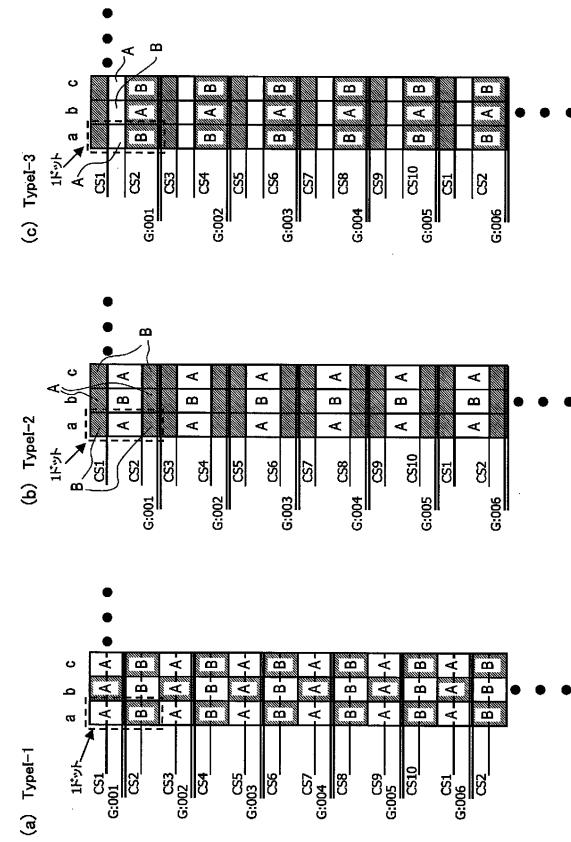

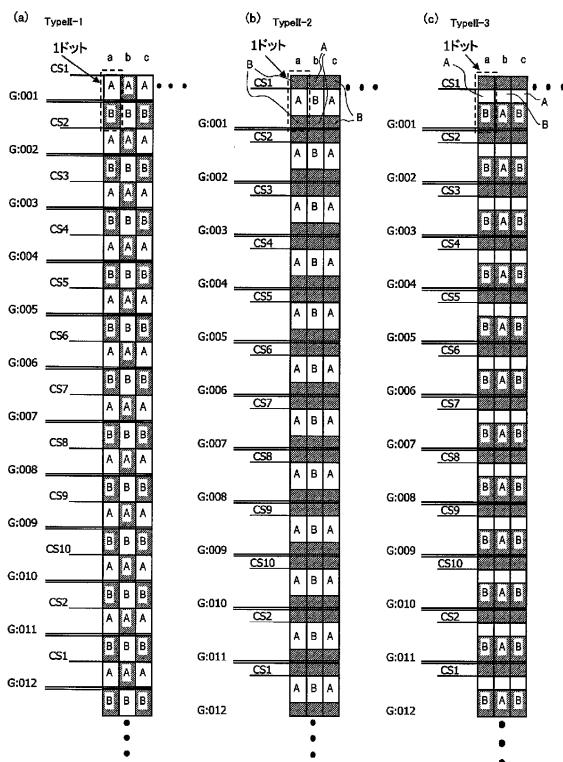

【図31】(a)～(c)は、本発明による実施形態のType Iの液晶表示装置の3つの代表的な構成を模式的に示す図である。

【図32】(a)～(c)は、本発明による実施形態のType IIの液晶表示装置の3つの代表的な構成を模式的に示す図である。 10

【図33A】Type Iの液晶表示装置においてスジが発生する原因を説明するためのゲート電圧およびCS電圧の波形図である。

【図33B】Type IIの液晶表示装置においてスジが発生する原因を説明するためのゲート電圧およびCS電圧の波形図である。

【図34】Type Iの液晶表示装置におけるスジを模式的に示す図である。

【図35A】Type Iの液晶表示装置の等価回路とCS幹線との接続形態を示す図である。

【図35B】Type Iの液晶表示装置の等価回路とCS幹線との接続形態を示す図である(図35Aの続き)。

【図36】図35Aおよび図35Bに示した液晶表示装置におけるCS電圧とゲート電圧とのタイミングの関係を示す図である。 20

【図37】図35Aおよび図35Bに示した液晶表示装置においてスジが発生する原因を説明するためのゲート電圧およびCS電圧の波形図である。

【図38】Type IIの液晶表示装置におけるスジを模式的に示す図である。

【図39A】Type IIの液晶表示装置の等価回路とCS幹線との接続形態を示す図である。

【図39B】Type IIの液晶表示装置の等価回路とCS幹線との接続形態を示す図である(図39Aの続き)。

【図39C】Type IIの液晶表示装置の等価回路とCS幹線との接続形態を示す図である(図39Bの続き)。 30

【図40】図39A～図39Cに示した液晶表示装置におけるCS電圧とゲート電圧とのタイミングの関係を示す図である。

【図41A】図39A～図39Cに示した液晶表示装置においてスジが発生する原因を説明するための図であり、ゲート電圧の波形図である。

【図41B】図39A～図39Cに示した液晶表示装置においてスジが発生する原因を説明するための図であり、CS電圧の波形図である。

【図41C】図39A～図39Cに示した液晶表示装置においてスジが発生する原因を説明するための図であり、画素の印加電圧の波形図である。

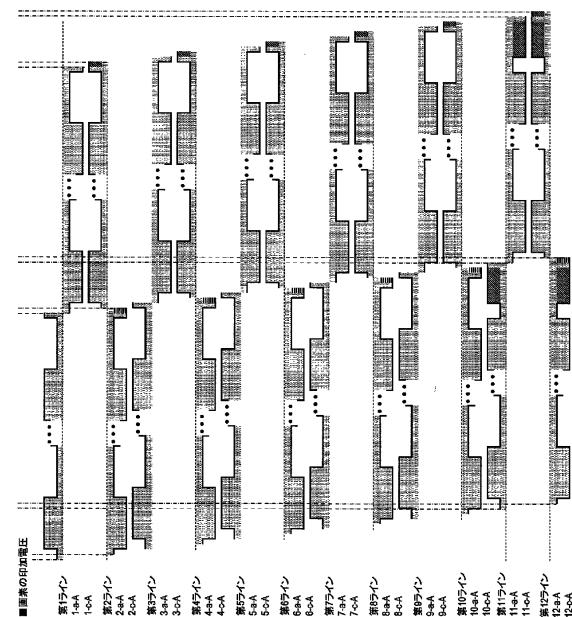

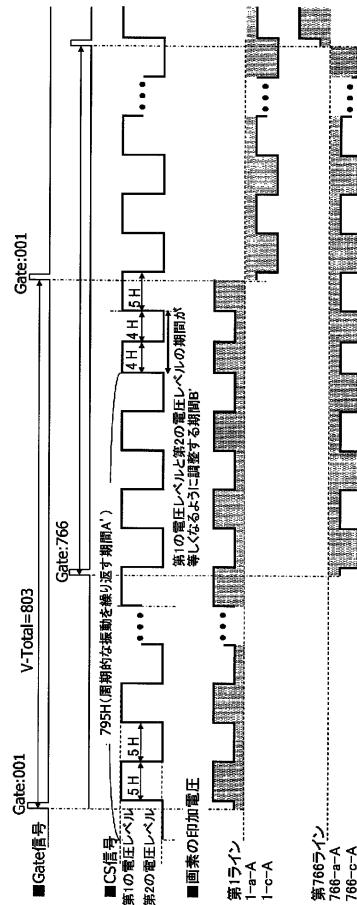

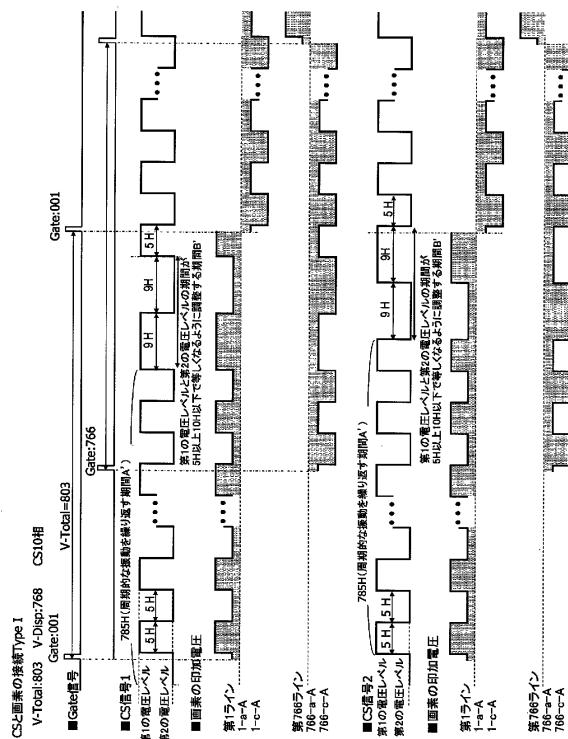

【図42A】本発明による実施形態1の液晶表示装置(Type I)を駆動する方法を説明するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である(例1)。 40

【図42B】本発明による実施形態1の液晶表示装置(Type I)を駆動する方法を説明するための図であり、CS電圧および画素の印加電圧の波形図である(例2)。

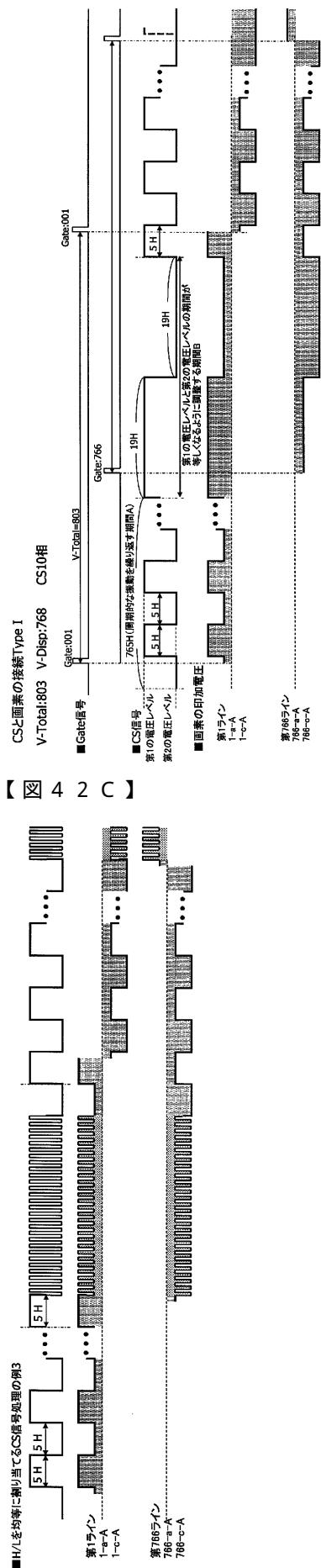

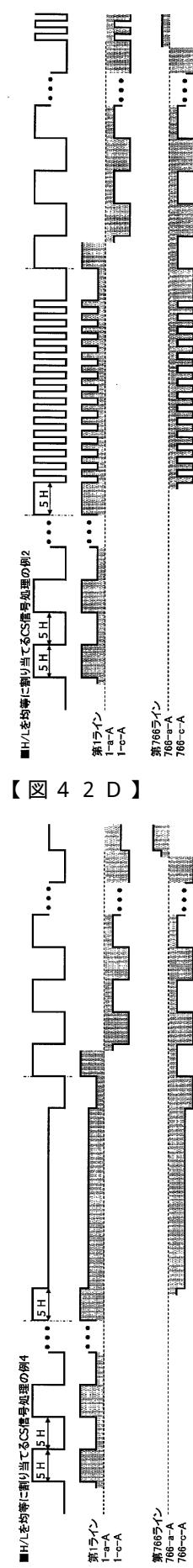

【図42C】本発明による実施形態1の液晶表示装置(Type I)を駆動する方法を説明するための図であり、CS電圧および画素の印加電圧の波形図である(例3)。

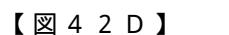

【図42D】本発明による実施形態1の液晶表示装置(Type I)を駆動する方法を説明するための図であり、CS電圧および画素の印加電圧の波形図である(例4)。

【図43】Type Iの他の液晶表示装置においてスジが発生する原因を説明するためのゲート電圧、CS電圧および画素の印加電圧の波形図である。

【図44】本発明による実施形態2の液晶表示装置(Type I)を駆動する方法を説明 50

するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である。

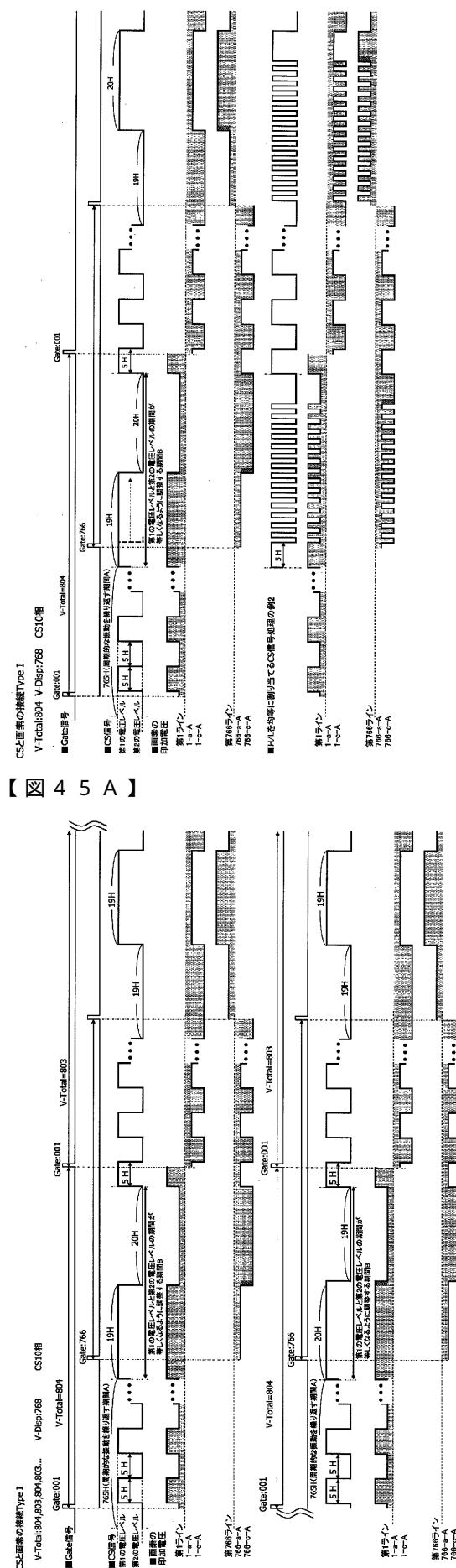

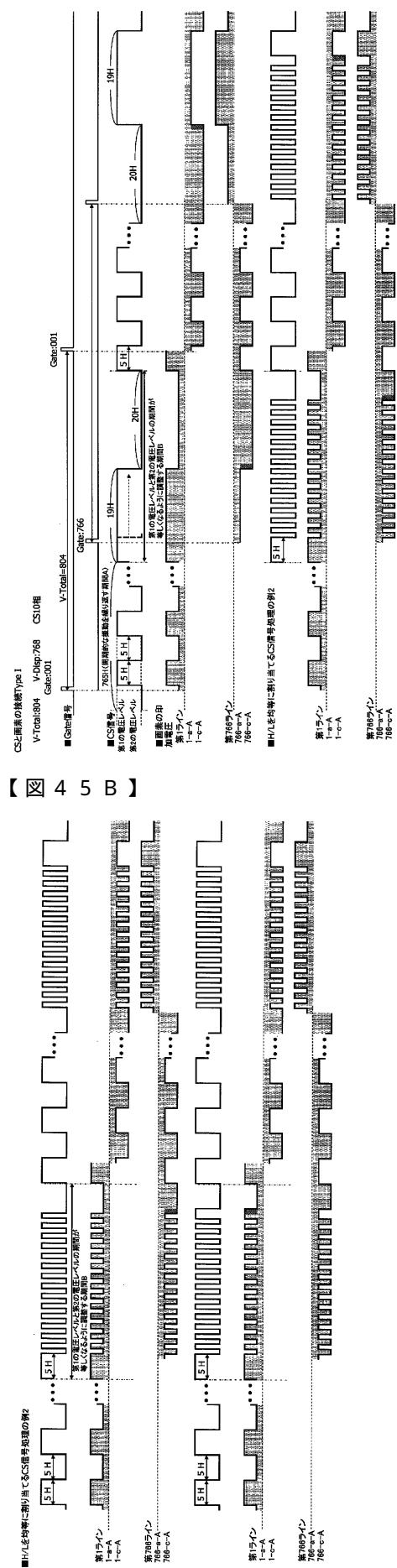

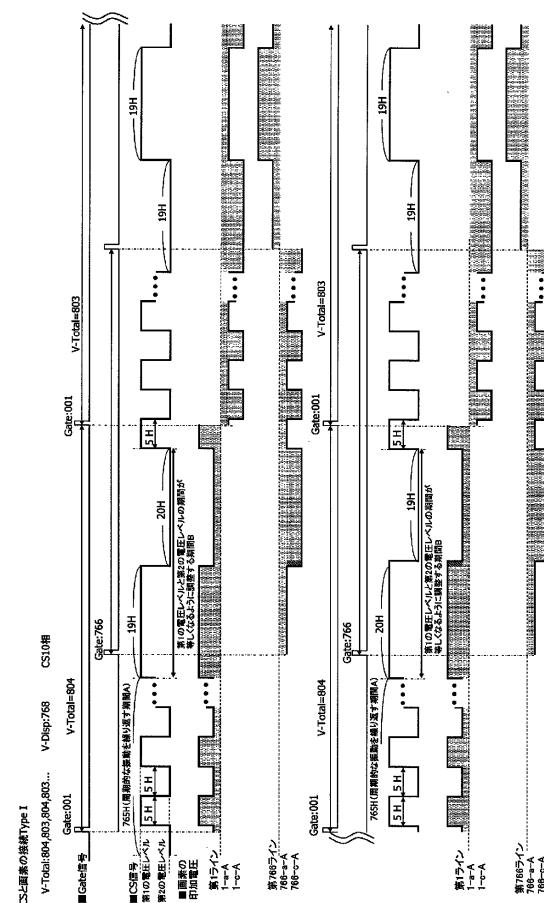

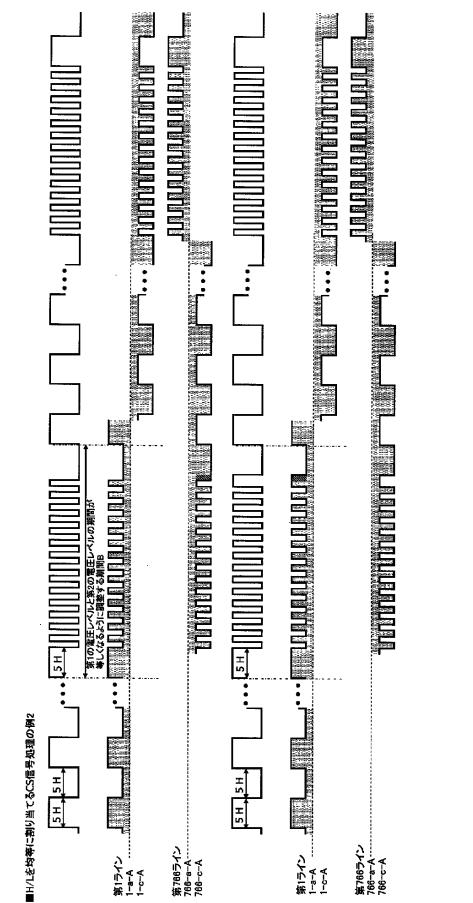

【図45A】本発明による実施形態3の液晶表示装置（Type I）を駆動する方法を説明するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である（例1）。

【図45B】本発明による実施形態3の液晶表示装置（Type I）を駆動する方法を説明するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である（例2）。

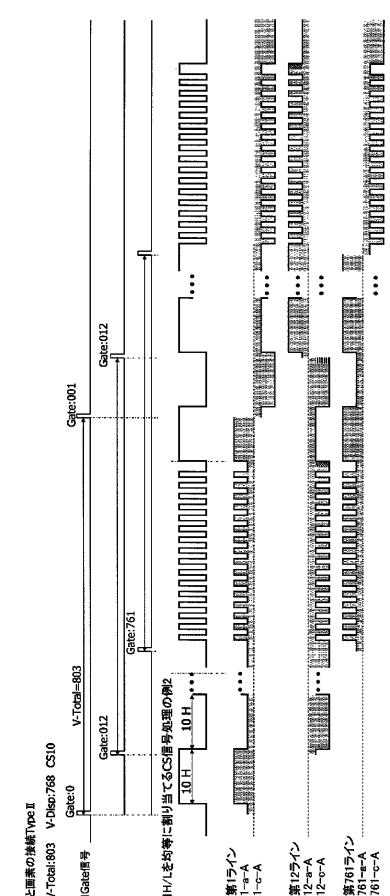

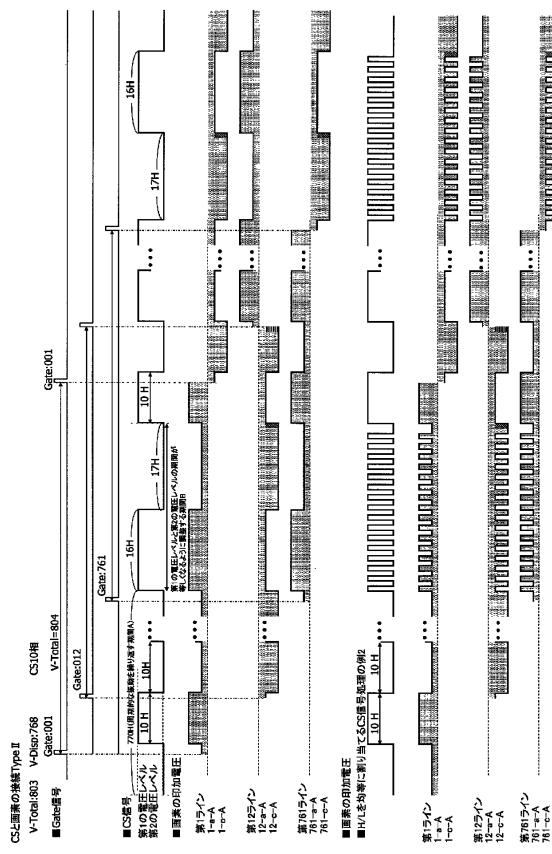

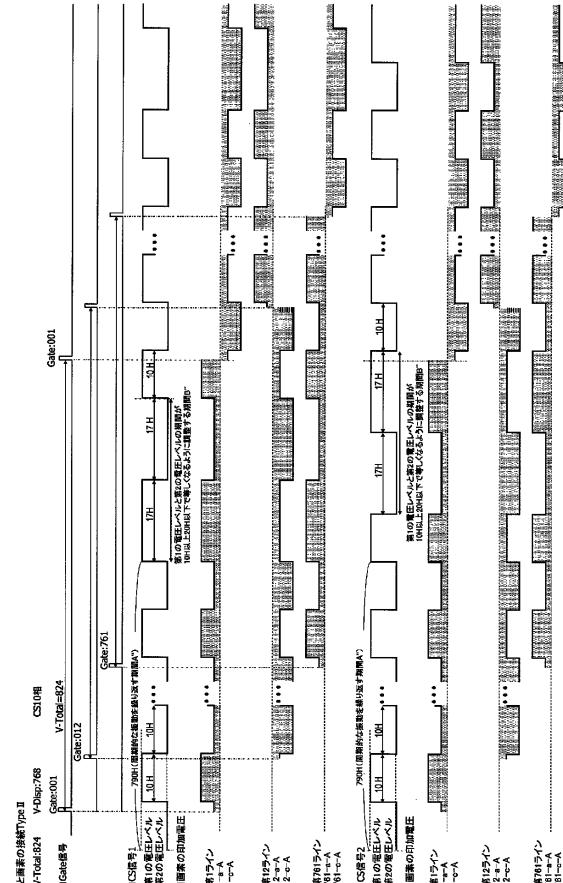

【図46A】本発明による実施形態4の液晶表示装置（Type II）を駆動する方法を説明するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である（例1）。 10

【図46B】本発明による実施形態4の液晶表示装置（Type II）を駆動する方法を説明するための図であり、CS電圧および画素の印加電圧の波形図である（例2）。

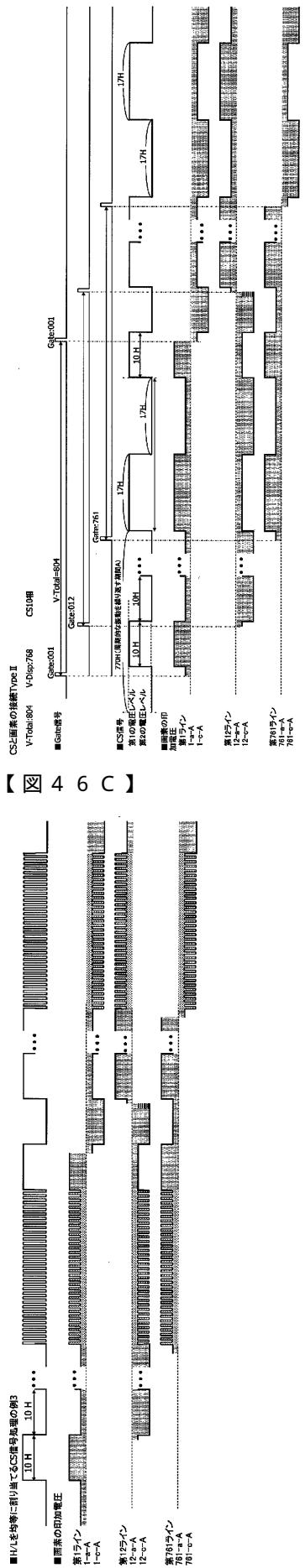

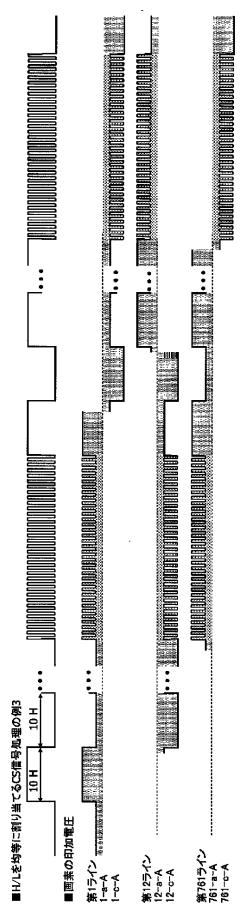

【図46C】本発明による実施形態4の液晶表示装置（Type II）を駆動する方法を説明するための図であり、CS電圧および画素の印加電圧の波形図である（例3）。

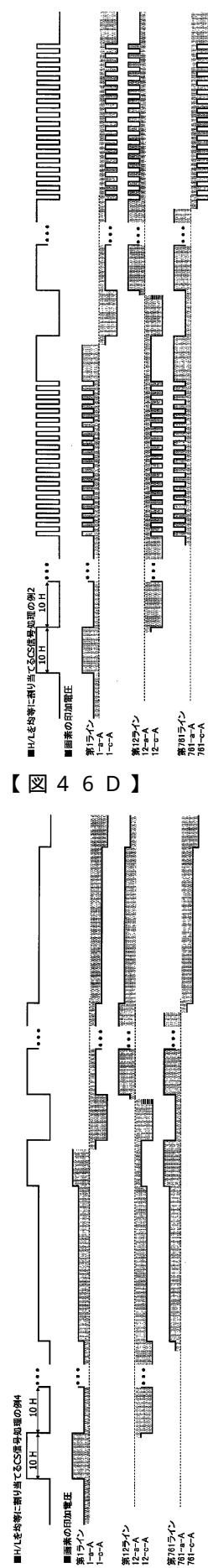

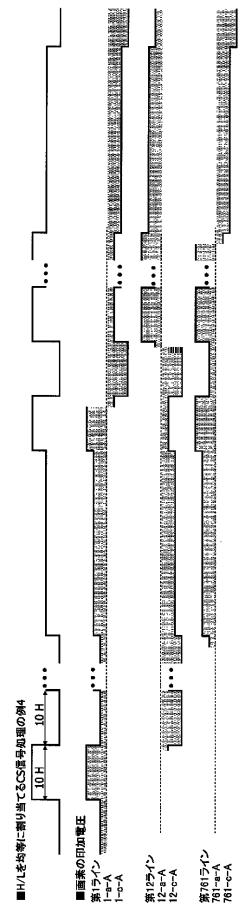

【図46D】本発明による実施形態4の液晶表示装置（Type II）を駆動する方法を説明するための図であり、CS電圧および画素の印加電圧の波形図である（例4）。

【図47A】Type IIの他の液晶表示装置においてスジが発生する原因を説明するためのゲート電圧の波形図である。

【図47B】Type IIの他の液晶表示装置においてスジが発生する原因を説明するためのゲート電圧およびCS電圧の波形図である。 20

【図47C】Type IIの他の液晶表示装置においてスジが発生する原因を説明するためのゲート電圧および画素の印加電圧の波形図である。

【図47D】Type IIの他の液晶表示装置においてスジが発生する原因を説明するためのゲート電圧、CS電圧および画素の印加電圧の波形図である（例2）。

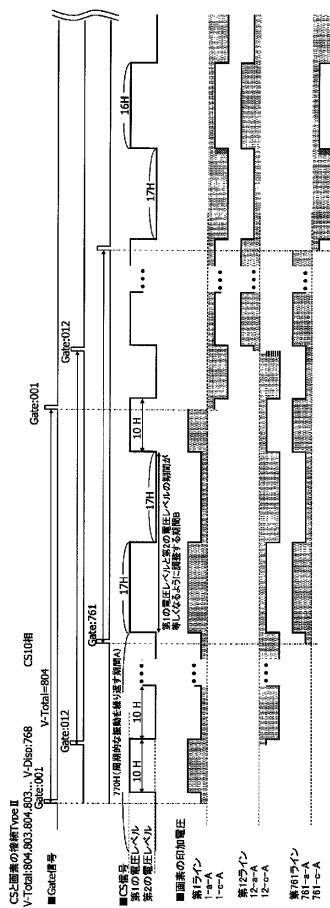

【図48】本発明による実施形態5の液晶表示装置（Type II）を駆動する方法を説明するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である。

【図49A】本発明による実施形態6の液晶表示装置（Type II）を駆動する方法を説明するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である（例1）。

【図49B】本発明による実施形態6の液晶表示装置（Type II）を駆動する方法を説明するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である（例1）。 30

【図49C】本発明による実施形態6の液晶表示装置（Type II）を駆動する方法を説明するための図であり、CS電圧および画素の印加電圧の波形図である（例2）。

【図49D】本発明による実施形態6の液晶表示装置（Type II）を駆動する方法を説明するための図であり、CS電圧および画素の印加電圧の波形図である（例2）。

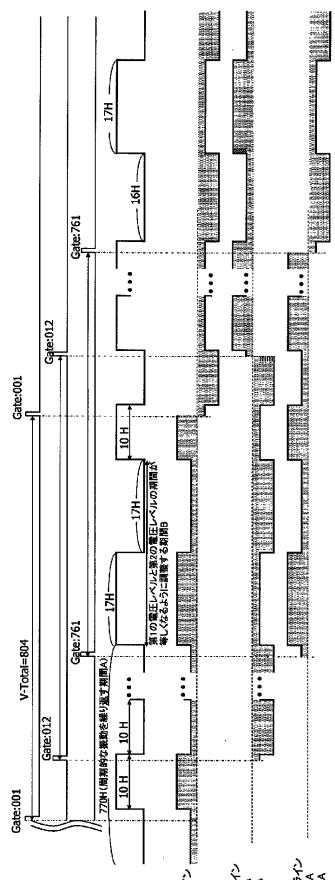

【図50】本発明による実施形態7の液晶表示装置（Type I）を駆動する方法を説明するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である。

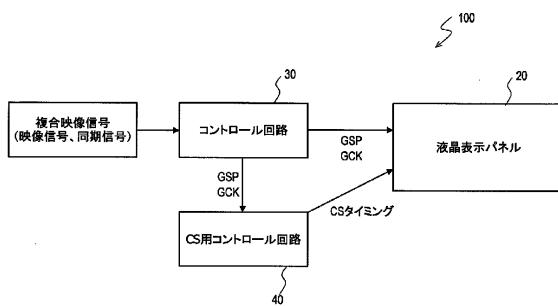

【図51】本発明による実施形態7の液晶表示装置100においてCS電圧を発生させる回路の構成を模式的に示す図である。 40

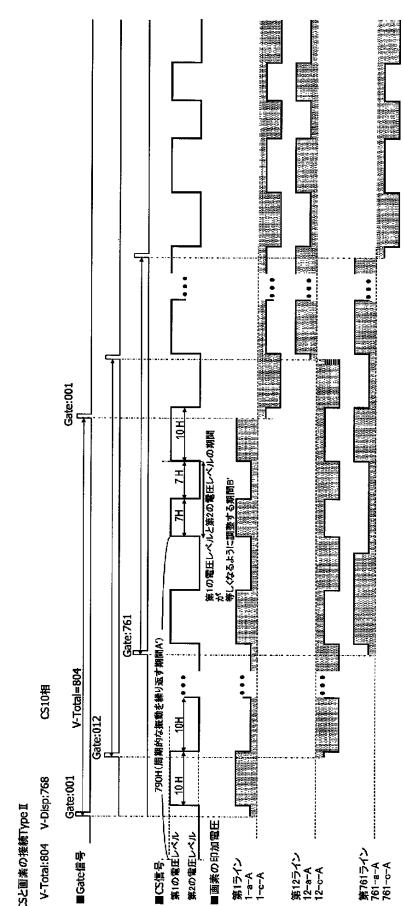

【図52】本発明による実施形態8の液晶表示装置（Type II）を駆動する方法を説明するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である。

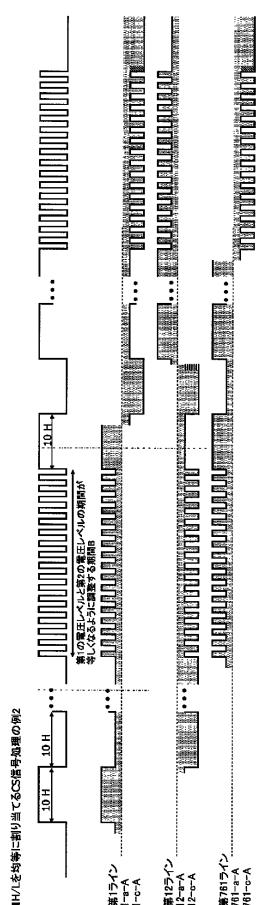

【図53】本発明による実施形態9の液晶表示装置（Type I）を駆動する方法を説明するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である。

【図54】本発明による実施形態10の液晶表示装置（Type II）を駆動する方法を説明するための図であり、ゲート電圧、CS電圧および画素の印加電圧の波形図である。

【図55】特許文献5に記載されている液晶表示装置200の画素分割構造を模式的に示す図である。

【図56】液晶表示装置200の画素構造に対応した電気的な等価回路を示す図である。

【図57】(a)～(f)は、液晶表示装置200の駆動に用いられる各種の電圧波形を 50

示す図である。

【図58】液晶表示装置200における副画素間の液晶層への印加電圧の関係を示す図である。

【符号の説明】

【0056】

10 画素

10a、10b 副画素

12 走査線（ゲートバスライン）

14a、14b 信号線（ソースバスライン）

16a、16b TFT

10

18a、18b 副画素電極

100、200 液晶表示装置

【発明を実施するための最良の形態】

【0057】

以下、図面を参照しながら本発明による実施形態の液晶表示装置およびその駆動方法を説明する。なお、本発明による実施形態の液晶表示装置の画素は上述した特許文献5に記載されている画素と同様の構造を有しており、補助容量配線（CSバスライン）の接続形態および補助容量対向電圧（CS電圧）の波形が特許文献5に記載されているものと異なっている。まず、CSバスラインに印加する振動電圧（CS電圧）の振動周期が短い場合に生じる問題を説明する。

20

【0058】

以下では、図1に示すような1H1ドット反転駆動に適した画素配列を備える液晶表示装置を例示する。1H1ドット反転駆動は、画素電極と対向電極との電位の大小関係が一定時間毎に反転し、液晶層に印加される電界の向き（電気力線の向き）が垂直走査期間毎に反転する。その結果、表示のちらつきを抑制することができる。表示のちらつきを防止するためには、積極的に輝度を異ならせた副画素の輝度順位（輝度の大小関係の順位）を可能な限りランダムに配置することが好ましく、輝度順位の等しい副画素が互いに列方向、および行方向に隣接しない配置が最も好ましい。言い換えれば、輝度順位の等しい副画素を市松状に配置することが表示上最も好ましい。

30

【0059】

なお、「垂直走査期間」とは、ある走査線が選択され、次にその走査線が選択されるまでの期間と定義することにする。液晶表示装置における1垂直走査期間は、ノンインターレース駆動用の信号の場合には1フレーム期間であり、インターレース駆動用の信号の場合に1フィールド期間に対応する。

【0060】

また、各垂直走査期間内において、ある走査線を選択する時刻と、その次の走査線を選択する時刻との差（期間）を1水平走査期間（1H）という。

【0061】

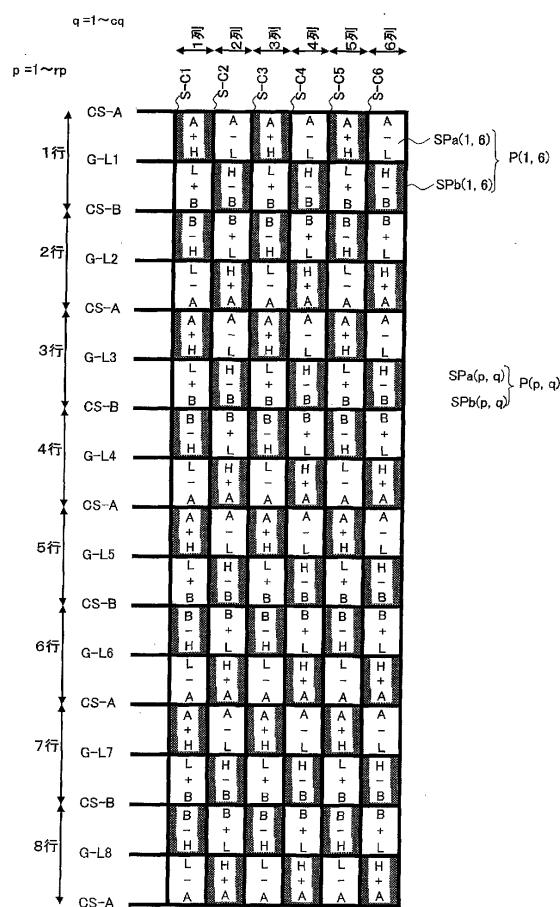

図1に示した液晶表示装置は、複数の行（1～rp）および複数の列（1～cq）を有するマトリクス状（rp、cq）に配列され、それぞれの画素P（p、q）、（但し、1p～rp、1q～cq）が2つの副画素SPa（p、q）およびSPb（p、q）を有する例を説明する。図1は、信号線S-C1、S-C2、S-C3、S-C4…S-Ccq、走査線G-L1、G-L2、G-L3、…G-Lrpおよび補助容量配線CS-AおよびCS-Bと、各画素P（p、q）および各画素を構成する副画素SPa（p、q）およびSPb（p、q）の相対的な配置の一部分（8行6列）を模式的に示している。

40

【0062】

図1に示したように、1つの画素P（p、q）は画素の中央付近を水平に貫く走査線G-Lpの上下に副画素SPa（p、q）およびSPb（p、q）を有している。すなわち、副画素SPa（p、q）およびSPb（p、q）は各画素において列方向に配列されて

50

いる。それぞれの副画素 S P a ( p, q ) および S P b ( p, q ) の補助容量電極の一方 (不図示) は、隣接の補助容量配線 C S - A または C S - B に接続されている。また、各画素 P ( p, q ) に表示画像に応じた信号電圧 (「表示信号電圧」、「データ信号電圧」ともいう。) を供給する信号線 S - C q は図面上で各画素の間に垂直に (列方向に) 延びるよう設けられており、各信号線の右隣の副画素 (画素) が各々有する TFT 素子 (不図示) に信号電圧を供給する構成となっている。図 1 に示した構成は、一本の補助容量配線、または一本の走査線を 2 つの副画素で共有する構成であり、画素の開口率を高くできる利点を有している。

#### 【 0 0 6 3 】

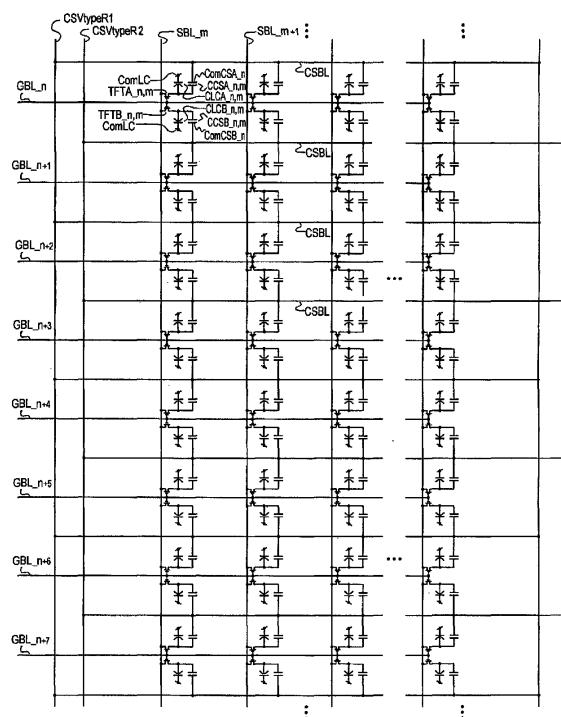

図 2 は、図 1 に示した画素配列を有する液晶表示装置のある領域の等価回路図である。

この液晶表示装置は、行および列を有するマトリクス状に配置された画素を有しており、

それぞれの画素は、2 つの副画素を有している。それぞれの副画素 (記号 A および B が 2

つの副画素を示す。) は、液晶容量 C L C A \_ n , m および C L C B \_ n , m と、補助容

量 C C S A \_ n , m および C C S B \_ n , m を有している。液晶容量は副画素電極と対向

電極 C o m L C とこれらの間に設けられた液晶層とによって構成されており、補助容量は

補助容量電極と、絶縁膜と、補助容量対向電極 (C o m C S A \_ n 、C o m C S B \_ n )

とで構成されている。2 つの副画素は、それぞれ対応する T F T A \_ n , m および T F T

B \_ n , m を介して共通の信号線 (ソースバスライン) S B L \_ m に接続されている。T

F T A \_ n , m および T F T B \_ n , m は、共通の走査線 (ゲートバスライン) G B L \_

n に供給される走査信号電圧によってオン / オフ制御され、2 つの TFT がオン状態にあ

るときに、2 つの副画素のそれぞれが有する副画素電極および補助容量電極に、共通の信

号線から表示信号電圧が供給される。2 つの副画素の内的一方の補助容量対向電極は、C

S バスライン (C S B L ) を介して、補助容量幹線 (C S 幹線) C S V t y p e R 1 に接

続されており、他方の補助容量対向電極は、補助容量幹線 (C S 幹線) C S V t y p e R

2 に接続されている。

#### 【 0 0 6 4 】

図 2 で注目すべき点は、列方向に隣接する行の画素の副画素に対応する C S バスライン

が互いに電気的に共通である点である。具体的には、n 行の副画素 C L C B \_ n , m に対

応する C S バスライン C S B L と、これに列方向に隣接した行の画素の副画素 C L C A \_

n + 1 , m に対応する C S バスライン C S B L とが電気的に共通である点である。

#### 【 0 0 6 5 】

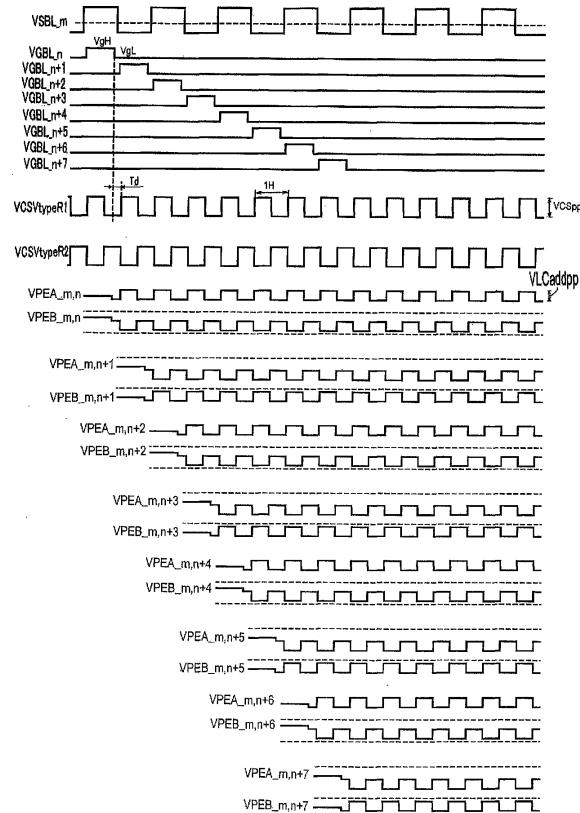

図 3 A および図 3 B に、ゲートバスラインの電圧波形を基準とした C S バスラインに供

給される振動電圧の振動の周期および位相および各副画素電極の電圧を示す。一般に、液

晶表示装置は各画素の液晶層に印加される電界の向きを一定時間間隔で (例えば垂直走査

期間毎に) 反転させているので、各電界の向きに対応した 2 種類の駆動電圧波形について

考える必要がある。この 2 種類の駆動状態を各々図 3 A および図 3 B に示してある。

#### 【 0 0 6 6 】

図 3 A および図 3 B において、V S B L \_ m は m 列のソースバスライン S B L \_ m に供

給される表示信号電圧 (ソース信号電圧) の波形を示し、V G B L \_ n 等は、n 行のゲー

トバスライン G B L \_ n に供給される走査電圧 (ゲート信号電圧) の波形を示し、V C S

V t y p e R 1 および V C S V t y p e R 2 はそれぞれ C S 幹線 C S V t y p e R 1 およ

び C S V t y p e R 2 に供給される補助容量対向電圧としての振動電圧の波形を示し、V

P E A \_ m , n および V P E B \_ m , n はそれぞれの副画素の液晶容量の電圧波形を示し

ている。

#### 【 0 0 6 7 】

図 3 A および図 3 B で注目すべき第 1 の点は、C S V t y p e R 1 、C S V t y p e R

2 の電圧 V C S V t y p e R 1 、V C S V t y p e R 2 の振動の周期はいずれも水平走査

期間の 1 倍の時間 (1 H) であることである。

#### 【 0 0 6 8 】

図 3 A および図 3 B で注目すべき第 2 点は、V C S V t y p e R 1 、V C S V t y p e

10

20

30

40

50

R 2 の位相が次のようになっている点である。まず、CS 幹線間の位相に注目すれば、VC SV type R 2 は VC SV type R 1 より 0.5 H 時間だけ位相が遅れている。次に、CS 幹線の電圧とゲートバスラインの電圧に注目すれば、CS 幹線の電圧とゲートバスラインの電圧の位相は次のようになっている。図 3 A および図 3 B によれば各 CS 幹線に対応するゲートバスラインの電圧が VgH から VgL に変化する時刻と、CS 幹線電圧の各平坦部分の中央の時刻が一致している。すなわち、図 3 A および図 3 B に示した Td の値が 0.25 H 時間である。但し、これ以外の場合でも、Td の値が 0 H よりも大きく 0.5 H 時間よりも短い範囲であればよい。

## 【0069】

上記 CS 幹線の電圧の周期および位相に関する説明は図 3 A および図 3 B に基づいたものであるが、CS 幹線の電圧波形はこれに限られず、次の 2 つの条件のいずれかを満足すればよい。その第 1 の条件は、VC SV type R 1 は対応する任意のゲートバスラインの電圧が VgH から VgL に変化した後、最初の電圧変化が電圧増加であり、かつ VC SV type R 2 は対応する任意のゲートバスラインの電圧が VgH から VgL に変化した後、最初の電圧変化が電圧減少であることである。その第 2 の条件は、VC SV type R 1 は対応する任意のゲートバスラインの電圧が VgH から VgL に変化した後、最初の電圧変化が電圧減少であり、かつ VC SV type R 2 は対応する任意のゲートバスラインの電圧が VgH から VgL に変化した後、最初の電圧変化が電圧増加であることである。

## 【0070】

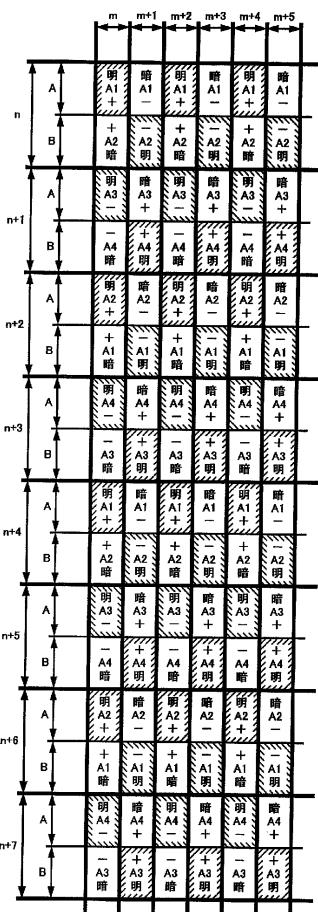

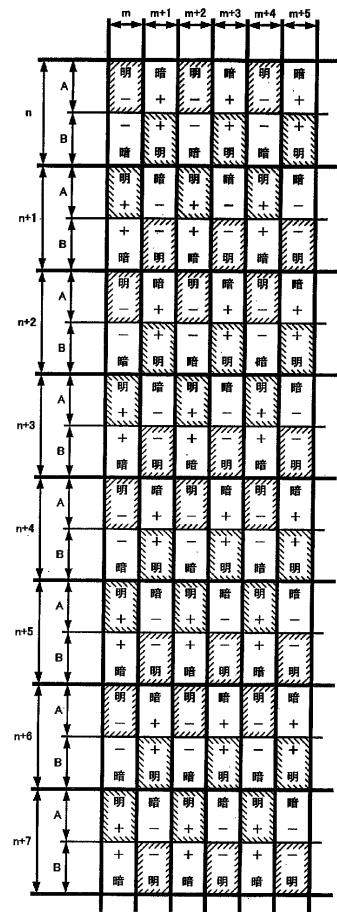

図 4 A および図 4 B にこの液晶表示装置の駆動状態をまとめて示す。液晶表示装置の駆動状態もまた図 3 A および図 3 B と同様に各副画素の駆動電圧の極性の異なる 2 つの場合に分けて示す。図 4 A の駆動状態は図 3 A の駆動電圧波形に対応し、図 4 B の駆動状態は図 3 B の駆動電圧波形に対応している。

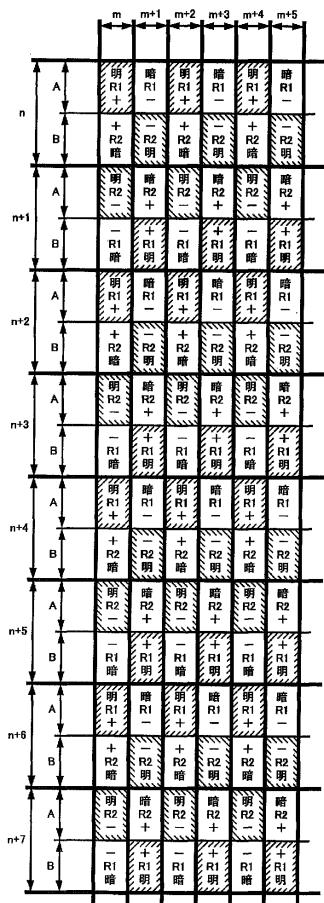

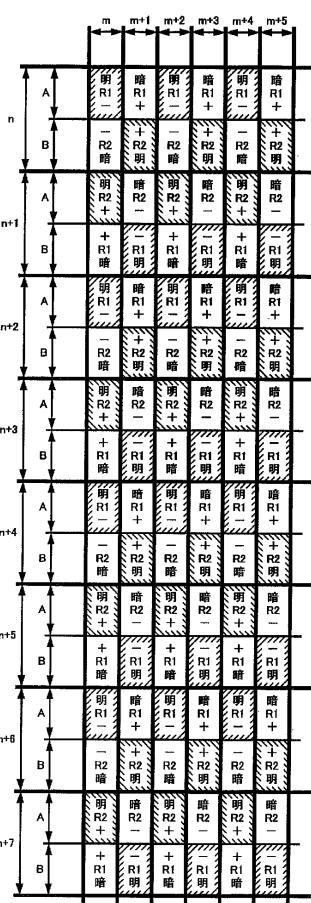

## 【0071】

図 4 A および図 4 B は、マトリクス状に配列された複数の画素のうちの (n 行から n + 7 行の 8 行) × (m 列から m + 5 列までの 6 列) の画素の駆動状態を模式的に示す図であり、それぞれの画素は、輝度の異なる副画素、即ち「明」と記した副画素および「暗」と記した副画素を有している。これらの図は、先に示した図 1 と基本的に等価である。

## 【0072】

図 4 A および図 4 B で注目すべき点は、面積階調表示パネルとして必要な要件を満足しているか否かである。面積階調表示パネルとして必要な要件は次の 5 点である。

## 【0073】

第 1 は、中間調表示状態で 1 つの画素が輝度の異なる複数の副画素で構成されている。

## 【0074】

第 2 は、前記輝度の異なる副画素の輝度順位が時刻によらず一定である。

## 【0075】

第 3 は、前記異なる輝度の副画素の配置が緻密に成されている。

## 【0076】

第 4 は、任意の垂直走査期間（以下、「フレーム」とする）で、画素単位で極性の異なる画素が緻密に配置されている。

## 【0077】

第 5 は、任意のフレームで、輝度順位の等しい副画素単位で、特に輝度の最も明るい副画素単位で極性の等しい副画素が緻密に配置されている。

## 【0078】

第 1 の要件について検証する。ここでは、1 つの画素が輝度の異なる 2 つの副画素で構成されている。具体的には、例えば図 4 A によれば n 行 m 列の画素は「明」と記した輝度の高い副画素と「暗」と記した輝度の低い副画素で構成されている。よって第 1 の要件は満たしている。

## 【0079】

10

20

30

40

50

第2の要件について検証する。この液晶表示装置は駆動状態の異なる2つの表示形態を一定時間毎に交互に表示している。2つの表示形態に対応する駆動状態を示してある図4Aと図4Bとを比較すると、輝度の高い副画素と輝度の低い副画素の位置が一致している。よって、第2の要件を満たしている。

#### 【0080】

第3の要件について検証する。図4Aおよび図4Bによれば、輝度順位の異なる副画素、すなわち「明」と記した副画素と「暗」と記した副画素が市松状に配置されている。また、この液晶表示装置を確認した結果、輝度の異なる副画素を用いたことによる解像度の低下等の表示上の不具合は視認できなかった。よって、第3の要件を満たしている。

#### 【0081】

第4の要件について確認する。図4Aおよび図4Bによれば、画素単位で極性の異なる画素が市松状に配置されている。具体的には、例えば図4Aにおいて $n + 2$ 行、 $m + 2$ 列の画素に注目すれば、この画素の極性は「+」であり、この画素から行方向および列方向に1画素毎に極性が「-」、「+」と変化している。また、第4の要件が満たされていない液晶表示装置では各画素の駆動極性が「+」、「-」で切り替わるのに同期したフリッカーと呼ばれる表示のちらつきが観測されると考えられるが、この液晶表示装置を目視で確認したところによるとフリッカーは見られなかった。よって、第4の要件は満たしている。

#### 【0082】

第5の要件について確認する。図4Aおよび図4Bにおいて、輝度順位の等しい副画素の駆動極性に注目すれば、2副画素行毎、すなわち1画素幅に駆動極性が反転している。具体的には、例えば図4Aの $n_B$ 行では $m + 1$ 、 $m + 3$ 、 $m + 5$ 列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「-」となっており、その下の $n_A$ 行では $m$ 、 $m + 2$ 、 $m + 4$ 列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「-」となっており、さらにその下の $n_B$ 行では $m + 1$ 、 $m + 3$ 、 $m + 5$ 列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「+」となっており、その下の $n_A$ 行では $m$ 、 $m + 2$ 、 $m + 4$ 列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「+」となっている。また、第5の要件が満たされていない液晶表示装置では各画素の駆動極性が「+」、「-」で切り替わるのに同期したフリッckerと呼ばれる表示のちらつきが観測されると考えられるが、この液晶表示装置を目視で確認したところによるとフリッckerは見られなかった。よって、第5の要件を満たしている。

#### 【0083】

この液晶表示装置をCS電圧の振幅VCSppを変化させつつ観測したところ、CS電圧の振幅VCSppを0V（すなわち、マルチ画素表示を行わない典型的な液晶表示装置に対応）から増大させるについて斜め観測時の白浮き現象が抑制されるといった視野角特性の改善効果が見られた。視野角特性の改善効果は表示する画像によって若干異なった印象を受けるもののVLCarddppの値が典型的な駆動（VCSppを0Vとした）での液晶表示装置の閾値電圧の0.5倍から2倍となるようにVCSppを設定した場合が最も良好であった。

#### 【0084】

このように、上記の液晶表示装置は、補助容量対向電極に振動電圧を印加することによりマルチ画素表示を行うことで視野角特性の改善を行った液晶表示装置であるが、補助容量対向電極に印加する振動電圧の振動周期は水平走査期間に等しい（または水平走査期間よりも短くてもよい）。このようにCSバスラインに供給する振動電圧の振動の周期が短いと、CSバスラインの負荷容量および抵抗の大きな大型の液晶表示装置あるいは水平走査期間の短い高精細の液晶表示装置さらには垂直走査期間および水平走査期間を短くした高速駆動の液晶表示装置に対してマルチ画素表示を行うことは比較的困難である。

#### 【0085】

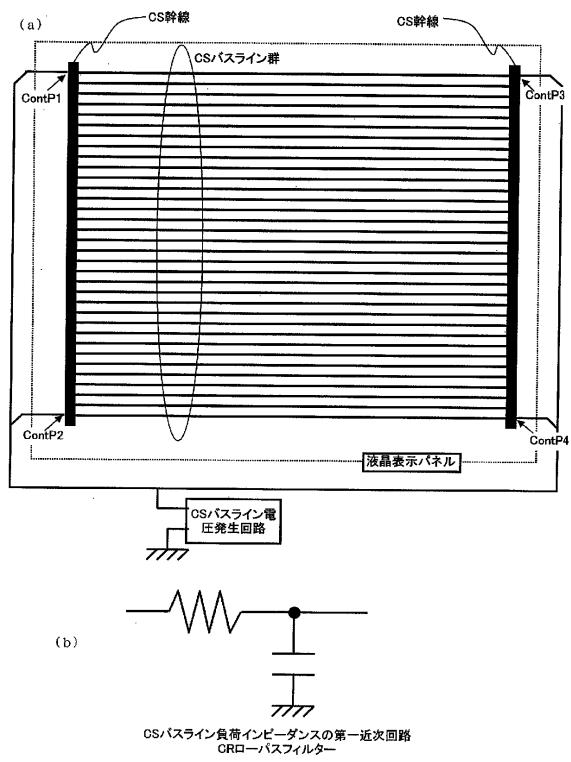

この問題を図5から図8を参照しながら説明する。

10

20

30

40

50

## 【0086】

図5(a)は、上述した液晶表示装置におけるCSバスラインに振動電圧を供給するための構成を模式的に示す図である。液晶表示パネルに設けられた複数のCSバスラインに対して、CS幹線から振動電圧が供給される。CS幹線には接続点ContP1およびP2、ContP3およびContP4を介してCSバスライン電圧発生回路から振動電圧が供給される。液晶表示パネルが大きくなると、表示パネルの中央部に位置する画素と接続点ContP1～ContP4との距離が長くなり、この間の負荷インピーダンスが無視できなくなる。負荷インピーダンスの主な構成要素は画素を構成する液晶層容量(CLc)と補助容量(CCS)とCSバスラインの抵抗RCSおよびCS幹線の抵抗Rmikである。この負荷インピーダンスは第一近似として、図5(b)に模式的に示すように、それらの容量および抵抗で構成されるローパスフィルターと考えることができる。この負荷インピーダンスの値は液晶表示パネル上の場所の関数になっており、前記の接続点、例えばContactP1、ContactP2、ContactP3、ContactP4からの距離の関数である。具体的には、接続点に近接した部分では負荷インピーダンスは小さく、接続点から離れるに従って負荷インピーダンスは増加する。

## 【0087】

すなわち、振動電圧発生回路で発生されたCSバスライン電圧は、CRローパスフィルターで近似されるCSバスラインの負荷の影響を受けるため、CSバスライン上では波形鈍りを生じてあり、かつその波形鈍りの程度はパネル内の場所によって異なる。

## 【0088】

上記マルチ画素表示においてCSバスラインに振動電圧を印加するのは1つの画素を2つ以上の副画素で構成し、各副画素で輝度を異ならせる目的のためである。すなわち、マルチ画素表示の液晶表示装置は各副画素電極の電圧波形をCSバスラインの振動電圧に依存した振動電圧とし、実効的な電圧をCSバスライン電圧の振動波形に依存して変化させる構成および駆動方法となっている。従って、CSバスライン電圧の波形が場所によって異なる場合には、副画素電極の実効的な電圧も場所によって異なるといった問題が発生する。言い換えれば、CSバスライン電圧の波形鈍りの程度が場所によって異なる場合には、場所によって表示輝度が異なり、表示の輝度ムラが発生するといった問題が生じる。

## 【0089】

CSバスラインの振動周期を長くすることにより、この表示輝度ムラを改善するのが、本発明による液晶表示装置の有する主な特徴の1つである。以下、このことについて説明する。

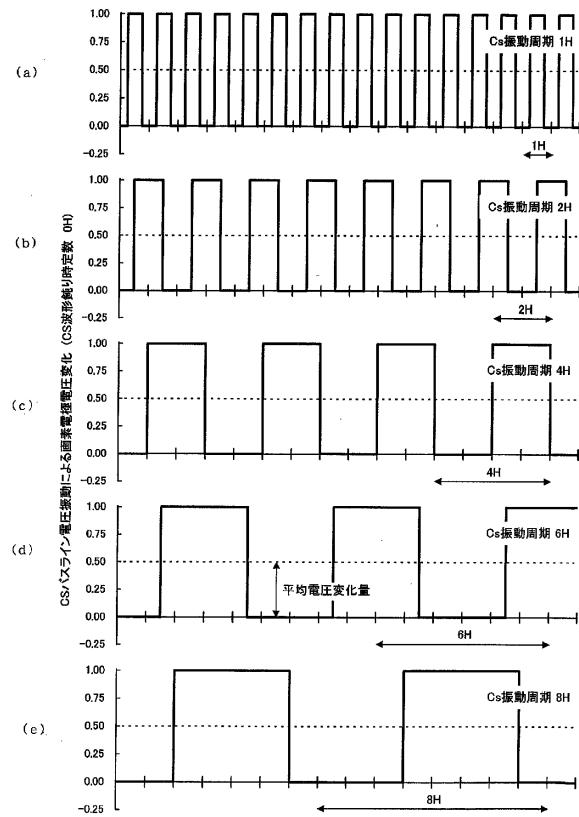

## 【0090】

図6および図7は、前記CS負荷を一定とした場合の副画素電極の振動電圧波形を模式的に示してある。図6および図7は、CSバスライン電圧が振動電圧で無い場合の副画素電極の電圧は「0V」、CSバスライン電圧の振動によって生じる副画素電極電圧の振動の振幅は「1V」とした場合の模式図である。図6(a)から(e)は、CS電圧波形鈍りが無い場合、すなわち前記CRローパスフィルターのCR時定数が「0H」の場合、図7(a)から(e)は、前記CRローパスフィルターのCR時定数が「0.2H」の場合に相当する波形鈍りを模式的に示してある。図6および図7はそれぞれCRローパスフィルターのCR時定数を前記の値として、CSバスラインの振動電圧の振動周期を異ならせた場合での画素電極電圧の電圧波形を模式的に示しており、図6(a)～(e)および図7(a)から(e)は、それぞれ、各波形の振動周期が1H、2H、4H、および8Hの場合を示している。

## 【0091】

図6と図7とを比較するとわかるように、振動周期が長くなるにつれて図6の波形と図7の波形との差異が小さくなっていることがわかる。この傾向を図8に定量的に示す。

## 【0092】

図8は、図7の波形を基に算出した振動電圧の平均値および実効値とCSバスライン電圧の振動周期(1目盛りは、1水平走査期間：1Hに対応)の関係を示している。図8か

10

20

30

40

50

らわかるように、CSバスラインの振動周期を長くすることにより、CR時定数0Hの場合と、0.2Hの場合の波形の平均値電圧および実効値電圧のずれ量が減少する。とりわけ、CSバスラインの振動電圧の振動周期をCSバスラインのCR時定数（CSバスラインの負荷インピーダンスの近似値）の8倍以上とした場合には、波形鈍りの影響を著しく低減できることがわかる。

#### 【0093】

このように、CSバスラインの振動電圧の振動周期を長くすることによりCSバスラインでの波形鈍りの影響による表示輝度ムラを低減することができる。特に、CSバスラインの振動電圧の振動周期をCSバスラインのCR時定数（CSバスラインの負荷インピーダンスの近似値）の8倍以上とした場合には、波形鈍りの影響を著しく低減できる。

10

#### 【0094】

本発明は、CSバスラインに印加する振動電圧の振動周期を長くすることのできる液晶表示装置の構造および駆動方法の好適な形態を提供する。CS電圧の振動周期を長くためには好適な構成は2つに大別され、それぞれTypeIとTypeIIと呼ぶことにする。

#### 【0095】

TypeIの構成を有する実施形態の液晶表示装置は、マトリックス駆動される液晶表示装置における同一列の画素であって、列方向に隣接する画素の副画素のうち、輝度順位の異なる副画素（例えば、第1副画素と第2副画素）に対応するCSバスラインを電気的に独立とする。すなわち、n行目の第1副画素と、n+1行目の第2副画素とのCSバスラインを電気的に独立にする。ここで、マトリックス駆動される液晶表示装置における同一列の画素とは、同一の信号線（典型的にはソースバスライン）によって駆動される画素である。また、マトリックス駆動される液晶表示装置における列方向に隣接する画素とは、時間軸上で順次選択される走査線（典型的にはゲートバスライン）群の中で、隣接の時刻で選択される走査線によって駆動される画素である。さらに、電気的に独立なCS幹線の種類をL種類とし、CSバスラインの振動の周期を水平走査期間のL倍とすることができる。前述のように、電気的な独立なCS幹線の数は、水平走査期間をCSバスラインの有する最大の負荷インピーダンスを近似したCR時定数で除した値の8倍の値よりも大きな数とするのが好ましい。さらに、後述するが前記8倍の値よりも大きな数であって且つ偶数とするのがより好ましい。なお、電気的に独立なCS幹線の種類の数（L種類）を電気的に独立なCS幹線の本数（L本）と表現することもある。電気的な等価なCS幹線をパネルの左右両側に設けた場合も、電気的に等価なCS幹線の本数は変化しない。

20

#### 【0096】

以下、図面を参照しながら本発明のTypeIの構成を有する実施形態の液晶表示装置およびその駆動方法を説明する。

#### 【0097】

まず、図9、図10A、図10Bおよび図11Bを参照しながら、CSバスラインの振動電圧の振動の周期を1水平走査期間の4倍として上述の面積階調表示を達成する液晶表示装置の例を説明する。説明は次の点を中心に図を用いつつ述べる。第1点は各副画素に接続した補助容量の補助容量対向電極とCSバスラインとの接続形態を中心とした液晶表示装置の構成について、第2点はゲートバスラインの電圧波形を基準としたCSバスラインの振動の周期および位相に関して、第3点は本実施形態での各副画素の駆動および表示状態について述べる。

30

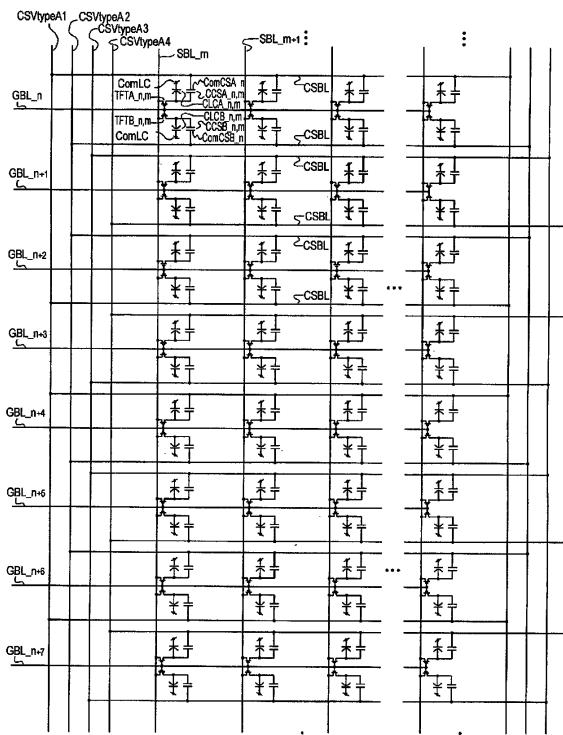

#### 【0098】

図9は、TypeIの構成を有する実施形態の液晶表示装置の等価回路を模式的に示す図であり、先の図2に対応する。共通する構成要素は共通の参照符号で示し、ここでは説明を省略する。図9の液晶表示装置は、電気的に独立な4つのCS幹線CSVtypA1～A4を有している点、および各CS幹線とCSバスラインの接続の状態において、図2の液晶表示装置と異なる。

40

#### 【0099】

図9で注目すべき第1の点は、列方向に隣接する行の画素の隣接の副画素（例えば、C

50

$L C B_n, m$  と  $C L C A_{n+1}, m$  に対応する副画素) に対応する CS バスラインが互いに電気的に独立である点である。具体的には、例えば、 $n$  行の副画素  $C L C B_n, m$  に対応する CS バスライン  $CSBL_B_n$  と、これに列方向に隣接した行の画素の副画素  $C L C A_{n+1}, m$  に対応する CS バスライン  $CSBL_A_{n+1}$  が電気的に独立している点である。

#### 【0100】

図 9 で注目すべき第 2 の点は、各 CS バスライン ( $CSBL$ ) はパネル端の 4 本の CS 幹線 ( $CSVtypeA1$ 、 $CSVtypeA2$ 、 $CSVtypeA3$ 、 $CSVtypeA4$ ) に接続されている点である。すなわち本実施形態の液晶表示装置では電気的に独立な CS 幹線の数は 4 種類である。

10

#### 【0101】

図 9 で注目するべき第 3 の点は、各 CS バスラインと 4 本の CS 幹線との接続状態、すなわち電気的に独立な CS 幹線の列方向での配列である。図 9 の CS バスラインと CS 幹線との接続の規則に従えば、CS 幹線  $CSVtypeA1$ 、 $CSVtypeA2$ 、 $CSVtypeA3$  および  $CSVtypeA4$  に接続される幹線は下の表 1 の通りとなる。

#### 【0102】

#### 【表 1】

| CS 幹線       | CS 幹線に接続される CS バスライン                                                                                                       | 左記 CS バスラインの一般表記                                                   |

|-------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| $CSVtypeA1$ | $CSBL_A_n, CSBL_B_{n+2}, CSBL_A_{n+4}, CSBL_B_{n+6}, CSBL_A_{n+8}, CSBL_B_{n+10}, CSBL_A_{n+12}, CSBL_B_{n+14}, \dots$     | $CSBL_A_{n+4 \cdot k}, CSBL_B_{n+2+4 \cdot k} (k=0,1,2,3,\dots)$   |

| $CSVtypeA2$ | $CSBL_B_n, CSBL_A_{n+2}, CSBL_B_{n+4}, CSBL_A_{n+6}, CSBL_B_{n+8}, CSBL_A_{n+10}, CSBL_B_{n+12}, CSBL_A_{n+14}, \dots$     | $CSBL_B_{n+4 \cdot k}, CSBL_A_{n+2+4 \cdot k} (k=0,1,2,3,\dots)$   |

| $CSVtypeA3$ | $CSBL_A_{n+1}, CSBL_B_{n+3}, CSBL_A_{n+5}, CSBL_B_{n+7}, CSBL_A_{n+9}, CSBL_B_{n+11}, CSBL_A_{n+13}, CSBL_B_{n+15}, \dots$ | $CSBL_A_{n+1+4 \cdot k}, CSBL_B_{n+3+4 \cdot k} (k=0,1,2,3,\dots)$ |

| $CSVtypeA4$ | $CSBL_B_{n+1}, CSBL_A_{n+3}, CSBL_B_{n+5}, CSBL_A_{n+7}, CSBL_B_{n+9}, CSBL_A_{n+11}, CSBL_B_{n+13}, CSBL_A_{n+15}, \dots$ | $CSBL_B_{n+1+4 \cdot k}, CSBL_A_{n+3+4 \cdot k} (k=0,1,2,3,\dots)$ |

20

30

#### 【0103】

なお、上の表 1 に示した 4 本の各幹線に接続される CS バスラインの組が電気的に独立な 4 種類の CS バスラインの組である。

#### 【0104】

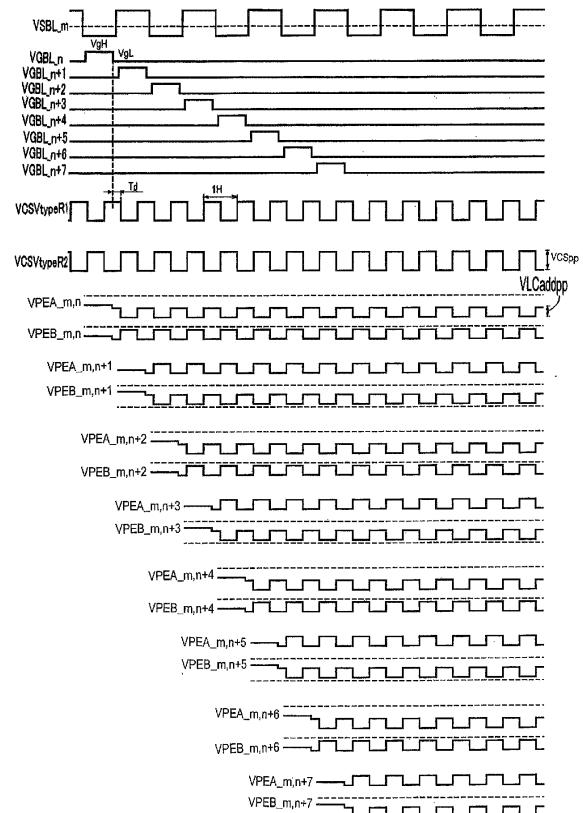

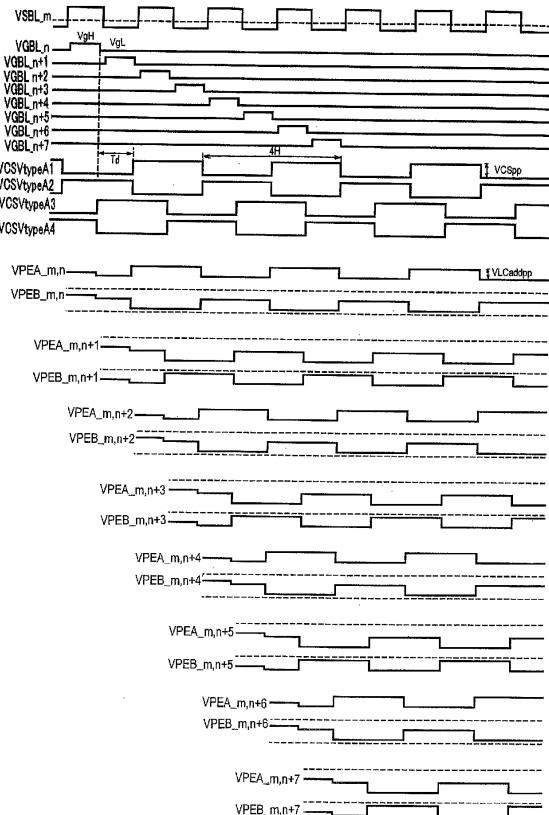

図 10 A および図 10 B にゲートバスラインの電圧波形を基準とした CS バスラインの振動の周期および位相および各副画素電極の電圧を示す。図 10 A および図 10 B は、先の図 3 A および図 3 B に対応する。共通する符号は同じ参照符号で示し、ここでは説明を省略する。一般に、液晶表示装置は各画素の液晶層に印加される電界の向きを一定時間間隔で反転させているので、各電界の向きに対応した 2 種類の駆動電圧波形について考える必要がある。この 2 種類の駆動状態を各々図 10 A および図 10 B に示してある。

40

#### 【0105】

図 10 A および図 10 B で注目すべき第 1 の点は、 $CSVtypeA1$ 、 $CSVtypeA2$ 、 $CSVtypeA3$ 、 $CSVtypeA4$  の電圧  $VCSVtypeA1$ 、 $VCSVtypeA2$ 、 $VCSVtypeA3$ 、 $VCSVtypeA4$  の振動の周期はいずれも水平走査期間の 4 倍の時間 (4 H) であることである。

#### 【0106】

図 10 A および図 10 B で注目すべき第 2 点は、 $VCSVtypeA1$ 、 $VCSVtypeA2$ 、 $VCSVtypeA3$ 、 $VCSVtypeA4$  の位相が次のようにになっている

50

点である。まず、CS幹線間の位相に注目すれば、VC SV type A 2はVC SV type A 1より2H時間だけ位相が遅れており、VC SV type A 3はVC SV type A 1より3H時間だけ位相が遅れており、VC SV type A 4はVC SV type A 1より1H時間だけ位相が遅れている。次に、CS幹線の電圧とゲートバスラインの電圧に注目すれば、CS幹線の電圧とゲートバスラインの電圧の位相は次のようになっている。図10Aおよび図10Bによれば各CS幹線に対応するゲートバスラインの電圧がVgHからVgLに変化する時刻と、CS幹線電圧の平坦部分の中央の時刻が一致している。すなわち、図10Aおよび図10Bに示したTdの値が1H時間である。但し、これ以外の場合でも、Tdの値が0Hよりも大きく2H時間よりも短い範囲であればよい。

## 【0107】

10

ここで、各CS幹線に対応するゲートバスラインとは、補助容量CSおよびTFT素子を介して同一の副画素電極に接続されたCSバスラインが接続されているCS幹線およびゲートバスラインである。図9によれば、この液晶表示装置において各CS幹線に対応するゲートバスライン、CSバスラインは下の表2のようになる。

## 【0108】

## 【表2】

| CS幹線      | 対応するゲートバスライン                                                                                             | 対応するCSバスライン                                                                                                                                   |

|-----------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| CSVtypeA1 | GBL_n, GBL_n+2, GBL_n+4,<br>GBL_n+6, GBL_n+8, ...<br>.....<br>[ GBL_n+2·k<br>(k = 0, 1, 2, 3, ...) ]     | CSBL_A_n, CSBL_B_n+2, CSBL_A_n+4,<br>CSBL_B_n+6, CSBL_A_n+8, ...<br>.....<br>[ CSBL_A_n+4·k, CSBL_B_n+2+4·k<br>(k = 0, 1, 2, 3, ...) ]        |

| CSVtypeA2 | GBL_n, GBL_n+2, GBL_n+4,<br>GBL_n+6, GBL_n+8, ...<br>.....<br>[ GBL_n+2·k<br>(k = 0, 1, 2, 3, ...) ]     | CSBL_B_n, CSBL_A_n+2, CSBL_B_n+4,<br>CSBL_A_n+6, CSBL_B_n+8, ...<br>.....<br>[ CSBL_B_n+4·k, CSBL_A_n+2+4·k<br>(k = 0, 1, 2, 3, ...) ]        |

| CSVtypeA3 | GBL_n+1, GBL_n+3, GBL_n+5,<br>GBL_n+7, GBL_n+9, ...<br>.....<br>[ GBL_n+1+2·k<br>(k = 0, 1, 2, 3, ...) ] | CSBL_A_n+1, CSBL_B_n+3,<br>CSBL_A_n+5,<br>CSBL_B_n+7, CSBL_A_n+9, ...<br>.....<br>[ CSBL_A_n+1+4·k, CSBL_B_n+3+4·k<br>(k = 0, 1, 2, 3, ...) ] |

| CSVtypeA4 | GBL_n+1, GBL_n+3, GBL_n+5,<br>GBL_n+7, GBL_n+9, ...<br>.....<br>[ GBL_n+1+2·k<br>(k = 0, 1, 2, 3, ...) ] | CSBL_B_n+1, CSBL_A_n+3,<br>CSBL_B_n+5,<br>CSBL_A_n+7, CSBL_B_n+9, ...<br>.....<br>[ CSBL_B_n+1+4·k, CSBL_A_n+3+4·k<br>(k = 0, 1, 2, 3, ...) ] |

20

30

## 【0109】

上記CS幹線の電圧の周期および位相に関する説明は図10Aおよび図10Bに基づいたものであるが、CS幹線の電圧波形はこれに限られず、次の2つの条件のいずれかを満足すればよい。

## 【0110】

その第1の条件は、VC SV type A 1は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧増加であり、かつVC SV type A 2は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧減少であり、かつVC SV type A 3は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧減少であり、かつVC SV type A 4は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧增加であることである。この条件は図10Aに示した駆動電圧波形に対応している。

40

## 【0111】

その第2の条件は、VC SV type A 1は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧減少であり、かつVC SV type A 2は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧増加であり、かつVC SV type A 3は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧増加であり、かつVC SV type A 4

50

は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧減少であることである。この条件は図10Bの駆動電圧波形に対応している。

#### 【0112】

但し、以下に説明する理由から、図10Aおよび図10Bに示した波形が好適に用いられる。

#### 【0113】

図10Aおよび図10Bでは、振動の周期が一定となっている。これにより、信号発生回路を簡略化することができる。

#### 【0114】

また、図10Aおよび図10Bでは、振動のデューティー比が一定となっている。これによって、振動の振幅を一定とすることができる、駆動回路を簡略化することができる。なぜなら、CSバスライン電圧を振動電圧とすることにより変化する液晶層の印加電圧の変化量は、振動の振幅と、振動のデューティー比に依存しているからである。よって、振動のデューティー比を一定とすることにより振動の振幅を一定とすることができます。デューティー比は例えば1：1に設定される。10

#### 【0115】

また、図10Aおよび図10Bでは、任意の振動電圧に対して、位相の180度異なる振動電圧（逆位相の振動電圧）が存在している。すなわち互いに電気的に独立な4種類のCS幹線は、位相が互いに180度異なる振動電圧を供給する対（2対で4本）によって構成されている。これによって、液晶容量を構成する対向電極に流れる電流量を最小化することができるため、対向電極に接続される駆動回路を簡略化することができる。20

#### 【0116】

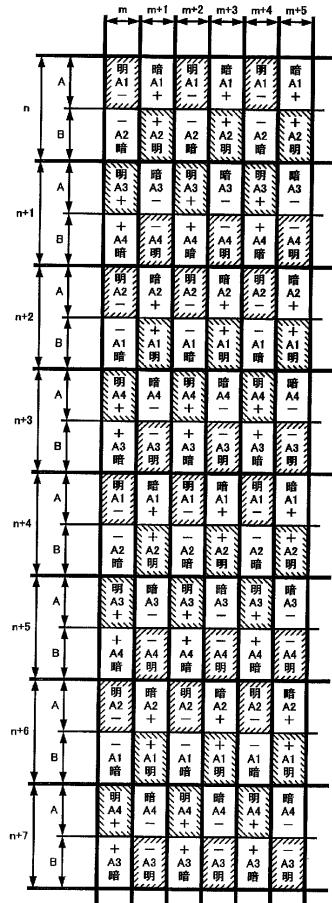

図11Aおよび図11Bに本実施形態の液晶表示装置の駆動状態をまとめて示す。液晶表示装置の駆動状態もまた図10Aおよび図10Bと同様に各副画素の駆動電圧の極性の異なる2つの場合に分けて示す。図11Aの駆動状態は図10Aの駆動電圧波形に対応し、図11Bの駆動状態は図10Bの駆動電圧波形に対応している。図11Aおよび図11Bは、先の図4Aおよび図4Bに対応している。

#### 【0117】

図11Aおよび図11Bで注目すべき点は、面積階調表示パネルとして必要な要件を満足しているか否かである。面積階調表示パネルとして必要な次の5つの要件について検証する。30

#### 【0118】

第1は、中間調表示状態で1つの画素が輝度の異なる複数の副画素で構成されている。

#### 【0119】

第2は、前記輝度の異なる副画素の輝度順位が時刻によらず一定である。

#### 【0120】

第3は、前記異なる輝度の副画素の配置が緻密に成されている。

#### 【0121】

第4は、任意のフレームで、画素単位で極性の異なる画素が緻密に配置されている。

#### 【0122】

第5は、任意のフレームで、輝度順位の等しい副画素単位で、特に輝度の最も明るい副画単位で極性の等しい副画素が緻密に配置されている。40

#### 【0123】

第1の要件について検証する。図11Aおよび図11Bによれば1つの画素が輝度の異なる2つの副画素で構成されている。具体的には、例えば図11Aによればn行m列の画素は「明」と記した輝度の高い副画素と「暗」と記した輝度の低い副画素で構成されている。よって第1の要件は満たしている。

#### 【0124】

第2の要件について検証する。本実施形態の液晶表示装置は駆動状態の異なる2つの表示形態を一定時間毎に交互に表示している。2つの表示形態に対応する駆動状態を示して50

ある図11Aおよび図11Bを比較すると、輝度の高い副画素と輝度の低い副画素の位置が一致している。よって、第2の要件を満たしている。

#### 【0125】

第3の要件について検証する。図11Aおよび図11Bによれば、輝度順位の異なる副画素、すなわち「明」と記した副画素と「暗」と記した副画素が市松状に配置されている。また、本実施形態の液晶表示装置を確認した結果、輝度の異なる副画素を用いたことによる解像度の低下等の表示上の不具合は視認できなかった。よって、第3の要件を満たしている。

#### 【0126】

第4の要件について確認する。図11Aおよび図11Bによれば、画素単位で極性の異なる画素が市松状に配置されている。具体的には、例えば図11Aにおいて $n+2$ 行、 $m+2$ 列の画素に注目すれば、この画素の極性は「+」であり、この画素から行方向および列方向に1画素毎に極性が「-」、「+」と変化している。また、第4の要件が満たされていない液晶表示装置では各画素の駆動極性が「+」、「-」で切り替わるのに同期したフリッカーと呼ばれる表示のちらつきが観測されると考えられるが、実施形態の液晶表示装置を目視で確認したところによるとフリッカーは見られなかった。よって、第4の要件は満たしている。

#### 【0127】

第5の要件について確認する。図11Aおよび図11Bにおいて、輝度順位の等しい副画素の駆動極性に注目すれば、2副画素行毎、すなわち1画素幅に駆動極性が反転している。具体的には、例えば $n\_B$ 行では $m+1$ 、 $m+3$ 、 $m+5$ 列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「-」となっており、その下の $n+1\_A$ 行では $m$ 、 $m+2$ 、 $m+4$ 列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「-」となっており、さらにその下の $n+1\_B$ 行では $m+1$ 、 $m+3$ 、 $m+5$ 列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「+」となっており、その下の $n+2\_A$ 行では $m$ 、 $m+2$ 、 $m+4$ 列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「+」となっている。また、第5の要件が満たされていない液晶表示装置では各画素の駆動極性が「+」、「-」で切り替わるのに同期したフリッckerと呼ばれる表示のちらつきが観測されると考えられるが、この液晶表示装置を目視で確認したところによるとフリッckerは見られなかった。よって、第5の要件を満たしている。

#### 【0128】

以上で説明した本実施形態の液晶表示装置をCS電圧の振幅V<sub>C S p p</sub>を変化させつつ観測したところ、CS電圧の振幅V<sub>C S p p</sub>を0V（本発明によらない典型的な液晶表示装置に対応）から増大させるについて斜め観測時の白浮き現象が抑制されたといった視野角特性の改善効果が見られた。視野角特性の改善効果は表示する画像によって若干異なった印象を受けるもののV<sub>L C a d d p p</sub>の値が典型的な駆動（V<sub>C S p p</sub>を0Vとした）での液晶表示装置の閾値電圧の0.5倍から2倍となるようにV<sub>C S p p</sub>を設定した場合が最も良好であった。

#### 【0129】

以上まとめると、本実施形態の液晶表示装置は補助容量対向電極に振動電圧を印加することにより面積階調表示（マルチ画素表示）を行うことで視野角特性の改善を行った液晶表示装置において、補助容量対向電極に印加する振動電圧の振動周期を水平走査期間の4倍にすることができる。しかるに、CSバスラインの負荷容量および抵抗の大きな大型の液晶表示装置あるいは水平走査期間の短い高精細の液晶表示装置さらには垂直走査期間および水平走査期間を短くした高速駆動の液晶表示装置に対して前記面積階調表示を容易に行うことが可能となる。

#### 【0130】

次に、図12、図13A、図13B、図14Aおよび図14Bを参照しながら、本発明のType Iの構成を有する他の実施形態の液晶表示装置の構成と動作を説明する。

10

20

30

40

50

## 【0131】

この液晶表示装置では、CSバスラインの振動電圧の振動の周期を1水平走査期間の2倍とすることで、上述の面積階調表示を達成する。説明は次の点を中心に図を用いつつ述べる。第1点は各副画素に接続した補助容量の補助容量対向電極とCSバスラインとの接続形態を中心とした液晶表示装置の構成について、第2点はゲートバスラインの電圧波形を基準としたCSバスラインの振動の周期および位相に関して、第3点は本実施形態での各副画素の駆動および表示状態について述べる。

## 【0132】

図12は、本発明のTyp e Iの構成を有する他の液晶表示装置の等価回路を模式的に示す図であり、先の液晶表示装置についての図9に対応する。共通する構成要素は共通の参考符号で示し、ここでは説明を省略する。図12の液晶表示装置は、電気的に独立な2つのCS幹線CSVtypeB1およびB2を有している点、および各CS幹線とCSバスラインの接続の状態において、図9の液晶表示装置と異なる。

10

## 【0133】

図12で注目すべき第1の点は、列方向に隣接する行の画素の隣接の副画素に対応するCSバスラインが互いに電気的に独立である点である。具体的には、n行の副画素CLC<sub>B\_n</sub>, mに対応するCSバスラインCSBL\_B<sub>n</sub>と、これに列方向に隣接した行の画素の副画素CLCA<sub>n+1</sub>, mに対応するCSバスラインCSBL\_A<sub>n+1</sub>が電気的に独立している点である。

## 【0134】

20

図12で注目すべき第2の点は、各CSバスライン(CSBL)はパネル端の2本のCS幹線(CSVtypeB1、CSVtypeB2)に接続されている点である。すなわち本実施形態の液晶表示装置では電気的に独立なCS幹線の数は2種類である。

## 【0135】

図12で注目すべき第3の点は、各CSバスラインと2本のCS幹線との接続状態、すなわち電気的に独立なCSバスラインの列方向での配列である。図12のCSバスラインとCS幹線との接続の規則に従えば、CS幹線CSVtypeB1、CSVtypeB2に接続されるCSバスラインは以下の表3の通りとなる。

## 【0136】

## 【表3】

30

| CS幹線      | CS幹線に接続されるCSバスライン                                                                                             | 左記CSバスラインの一般表記                             |

|-----------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| CSVtypeB1 | CSBL_A <sub>n</sub> ,<br>CSBL_A <sub>n+1</sub> ,<br>CSBL_A <sub>n+2</sub> ,<br>CSBL_A <sub>n+3</sub> ,<br>... | CSBL_A <sub>n+k</sub> ,<br>(k=0,1,2,3,...) |

| CSVtypeB2 | CSBL_B <sub>n</sub> ,<br>CSBL_B <sub>n+1</sub> ,<br>CSBL_B <sub>n+2</sub> ,<br>CSBL_B <sub>n+3</sub> ,<br>... | CSBL_B <sub>n+k</sub> ,<br>(k=0,1,2,3,...) |

## 【0137】

40

なお、上の表3に示した2本の各幹線に接続されるCSバスラインの組が電気的に独立な2種類のCSバスラインの組である。

## 【0138】

図13Aおよび図13Bにゲートバスラインの電圧波形を基準としたCSバスラインの振動の周期および位相および各副画素電極の電圧を示す。図13Aおよび図13Bは、先の実施形態の図10Aおよび図10Bに対応する。共通する符号は同じ参考符号で示し、ここでは説明を省略する。一般に、液晶表示装置は各画素の液晶層に印加される電界の向きを一定時間間隔で反転させているので、各電界の向きに対応した2種類の駆動電圧波形について考える必要がある。この2種類の駆動状態を各々図13Aおよび図13Bに示してある。

50

## 【0139】

図13Aおよび図13Bで注目すべき第1の点は、CSVtypeB1、CSVtypeB2の電圧VCSVtypeB1、VCSVtypeB2の振動の周期はいずれも水平走査期間の2倍の時間(2H)であることである。

## 【0140】

図13Aおよび図13Bで注目すべき第2点は、VCSVtypeB1、VCSVtypeB2の位相が次のようにになっている点である。まず、CS幹線間の位相に注目すれば、VCSVtypeB2はVCSVtypeB1より1H時間だけ位相が遅れている。次に、CS幹線の電圧とゲートバスラインの電圧に注目すれば、CS幹線の電圧とゲートバスラインの電圧の位相は次のようにになっている。図13Aおよび図13Bによれば各CS幹線に対応するゲートバスラインの電圧がVgHからVgLに変化する時刻と、CS幹線電圧の各平坦部分の中央の時刻が一致している。すなわち、図13Aおよび図13Bに示したTdの値が0.5H時間である。但し、これ以外の場合でも、Tdの値が0Hよりも大きく1H時間よりも短い範囲であればよい。

10

## 【0141】

ここで、各CS幹線に対応するゲートバスラインとは、補助容量CSおよびTFT素子を介して同一の副画素電極に接続されたCSバスラインが接続されているCS幹線およびゲートバスラインである。図13Aおよび図13Bによれば、この液晶表示装置において各CS幹線に対応するゲートバスラインおよびCSバスラインは下の表4のようになる。

## 【0142】

20

## 【表4】

| CS幹線      | 対応するゲートバスライン                                                                              | 対応するCSバスライン                                                                                                 |

|-----------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| CSVtypeB1 | GBL_n, GBL_n+1, GBL_n+2,<br>GBL_n+3, GBL_n+4, ...<br>[ GBL_n+k<br>(k = 0, 1, 2, 3, ...) ] | CSBL_A_n, CSBL_A_n+1, CSBL_A_n+2,<br>CSBL_A_n+3, CSBL_A_n+4, ...<br>[ CSBL_A_n+k<br>(k = 0, 1, 2, 3, ...) ] |

| CSVtypeB2 | GBL_n, GBL_n+1, GBL_n+2,<br>GBL_n+3, GBL_n+4, ...<br>[ GBL_n+k<br>(k = 0, 1, 2, 3, ...) ] | CSBL_B_n, CSBL_B_n+1, CSBL_B_n+2,<br>CSBL_B_n+3, CSBL_B_n+4, ...<br>[ CSBL_B_n+k<br>(k = 0, 1, 2, 3, ...) ] |

30

## 【0143】

上記CS幹線の電圧の周期および位相に関する説明は図13Aおよび図13Bに基づいたものであるが、CS幹線の電圧波形はこれに限られず、次の2つの条件のいずれかを満足すればよい。

## 【0144】

その第1の条件は、VCSVtypeB1は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧増加であり、かつVCSVtypeB2は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧減少であることである。図13Aはこの条件に該当する。

## 【0145】

40

その第2の条件は、VCSVtypeB1は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧減少であり、かつVCSVtypeB2は対応するゲートバスラインの電圧がVgHからVgLに変化した後、最初の電圧変化が電圧増加であることである。図13Bはこの条件に該当する。

## 【0146】

図14Aおよび図14Bに、本実施形態の液晶表示装置の駆動の状態をまとめた。本実施形態の液晶表示装置の駆動状態もまた図13Aおよび図13Bと同様に各副画素の駆動電圧の極性の異なる2つの場合に分けて示す。図14Aの駆動状態は図13Aの駆動電圧波形に対応し、図14Bの駆動状態は図13Bの駆動電圧波形に対応している。図14Aおよび図14Bは、先に示した実施形態の液晶表示装置についての図11Aおよび図11

50

Bに対応している。

**【0147】**

図14Aおよび図14Bで注目すべき点は、面積階調表示パネルとして必要な要件を満足しているか否かである。面積階調表示パネルとして必要な要件は、次の5点である。

**【0148】**

第1は、中間調表示状態で1つの画素が輝度の異なる複数の副画素で構成されている。

**【0149】**

第2は、前記輝度の異なる副画素の輝度順位が時刻によらず一定である。

**【0150】**

第3は、前記異なる輝度の副画素の配置が緻密に成されている。

10

**【0151】**

第4は、任意のフレームで、画素単位で極性の異なる画素が緻密に配置されている。

**【0152】**

第5は、任意のフレームで、輝度順位の等しい副画素単位で、特に輝度の最も明るい副画素単位で極性の等しい副画素が緻密に配置されている。

**【0153】**

第1の要件について検証する。図14Aおよび図14Bによれば1つの画素が輝度の異なる2つの副画素で構成されている。具体的には、例えば図14Aによればn行m列の画素は「明」と記した輝度の高い副画素と「暗」と記した輝度の低い副画素で構成されている。よって第1の要件は満たしている。

20

**【0154】**

第2の要件について検証する。本実施形態の液晶表示装置は駆動状態の異なる2つの表示形態を一定時間毎に交互に表示している。2つの表示形態に対応する駆動状態を示してある図14Aおよび図14Bを比較すると、輝度の高い副画素と輝度の低い副画素の位置が一致している。よって、第2の要件を満たしている。

**【0155】**

第3の要件について検証する。図14Aおよび図14Bによれば、輝度順位の異なる副画素、すなわち「明」と記した副画素と「暗」と記した副画素が市松状に配置されている。また、本実施形態の液晶表示装置を確認した結果、輝度の異なる副画素を用いたことによる解像度の低下等の表示上の不具合は視認できなかった。よって、第3の要件を満たしている。

30

**【0156】**

第4の要件について確認する。図14Aおよび図14Bによれば、画素単位で極性の異なる画素が市松状に配置されている。具体的には、例えば図14Aにおいてn+2行、m+2列の画素に注目すれば、該画素の極性は「+」であり、この画素から行方向および列方向に1画素毎に極性が「-」、「+」と変化している。また、第4の要件が満たされていない液晶表示装置では各画素の駆動極性が「+」、「-」で切り替わるのに同期したフリッカーと呼ばれる表示のちらつきが観測されると考えられるが、この液晶表示装置を目視で確認したところによるとフリッカーは見られなかった。よって、第4の要件は満たしている。

40

**【0157】**

第5の要件について確認する。図14Aおよび図14Bにおいて、輝度順位の等しい副画素の駆動極性に注目すれば、2副画素行毎、すなわち1画素行毎に駆動極性が反転している。具体的には、例えばn\_B行ではm+1、m+3、m+5列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「-」となっており、その下のn+1\_A行ではm、m+2、m+4列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「-」となっており、さらにその下のn+1\_B行ではm+1、m+3、m+5列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「+」となっており、その下のn+2\_A行ではm、m+2、m+4列の副画素の輝度順位記号が「明」であり、それら全ての極性反転記号は「+」となっている。また、第5の要件が満た

50

されていない液晶表示装置では各画素の駆動極性が「+」、「-」で切り替わるのに同期したフリッカーと呼ばれる表示のちらつきが観測されると考えられるが、本実施形態の液晶表示装置を目視で確認したところによるとフリッカーは見られなかった。よって、第5の要件を満たしている。

【0158】

以上で説明した本実施形態の液晶表示装置をCS電圧の振幅VCSppを変化させつつ発明者等が観測したところ、CS電圧の振幅VCSppを0V（面積階調表示を行わない典型的な液晶表示装置に対応）から増大させるについて斜め観測時の白浮き現象が抑制されるといった視野角特性の改善効果が見られた。しかしながら、VCSppの値をさらに増加させると、表示コントラストが低下するといった問題が発生した。従って、VCSppの値はこの問題が生じることなく、かつ十分な視野角改善効果が得られる範囲内で設定する必要がある。具体的には、視野角特性の改善効果は表示する画像によって若干異なった印象を受けるもののVLCarddppの値が典型的な駆動（VCSppを0Vとした）での液晶表示装置の閾値電圧の0.5倍から2倍となるようにVCSppを設定した場合が最も良好であった。

10

【0159】

以上をまとめると、Typ Iの構成を有する液晶表示装置は、補助容量対向電極に振動電圧を印加することによりマルチ画素表示を行うことで視野角特性の改善を行った液晶表示装置において、補助容量対向電極に印加する振動電圧の振動周期を水平走査期間の2倍にすることができる。しかるに、CSバスラインの負荷容量および抵抗の大きな大型の液晶表示装置あるいは水平走査期間の短い高精細の液晶表示装置さらには垂直走査期間および水平走査期間を短くした高速駆動の液晶表示装置に対して前記マルチ画素表示を容易に行なうことが可能となる。

20

【0160】

上記の実施形態では、電気的に独立なCS幹線の数（種類）が4本のものと、2本のものを例示したが、本発明のTyp Iの構成を有する液晶表示装置における電気的に独立なCS幹線の数（種類）はこれらに限られず、3本や5本あるいは6本以上であってもよい。但し、電気的に独立なCS幹線の数Lは、偶数であることが好ましい。これは、上述したように、電気的に独立なCS幹線が位相が互いに180度異なる振動電圧を供給する対（すなわち、Lが偶数）によって構成されていると、液晶容量を構成する対向電極に流れる電流量を最小化することができるためである。

30

【0161】

以下に、電気的に独立なCS幹線の数Lが6の場合とLが8の場合について、CS幹線と、対応するゲートバスラインおよびCSバスラインとの関係を表5および表6示す。また、Lが偶数の場合、CS幹線と、対応するゲートバスラインおよびCSバスラインとの関係は、L/2が奇数（L=2、6、10、14・・・）と、L/2が偶数（L=4、8、12、16・・・）とに大別できる。L/2が奇数の場合の一般的な関係を表5の後に示し、L/2が偶数の場合の関係をL=8の場合の表6の後に示す。

【0162】

【表5】

| CS幹線      | 対応するゲートバスライン                                                                                                 | 対応するCSバスライン                                                                                                                      |

|-----------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| CSVtypeC1 | GBL_n, GBL_n+3, GBL_n+6,<br>GBL_n+9, GBL_n+12, ...<br>.....<br>[ GBL_n+3·k<br>( k = 0, 1, 2, 3, ... ) ]      | CSBL_A_n, CSBL_A_n+3, CSBL_A_n+6,<br>CSBL_A_n+9, CSBL_A_n+12, ...<br>.....<br>[CSBL_A_n+3·k,<br>( k = 0, 1, 2, 3, ... ) ]        |

| CSVtypeC2 | GBL_n, GBL_n+3, GBL_n+6,<br>GBL_n+9, GBL_n+12, ...<br>.....<br>[ GBL_n+3·k<br>( k = 0, 1, 2, 3, ... ) ]      | CSBL_B_n, CSBL_B_n+3, CSBL_B_n+6,<br>CSBL_B_n+9, CSBL_B_n+12, ...<br>.....<br>[CSBL_B_n+3·k<br>( k = 0, 1, 2, 3, ... ) ]         |

| CSVtypeC3 | GBL_n+1, GBL_n+4, GBL_n+7,<br>GBL_n+10, GBL_n+13, ...<br>.....<br>[ GBL_n+1+3·k<br>( k = 0, 1, 2, 3, ... ) ] | CSBL_A_n+1, CSBL_A_n+4,<br>CSBL_A_n+7,<br>CSBL_A_n+10, CSBL_A_n+13, ...<br>.....<br>[CSBL_A_n+1+3·k<br>( k = 0, 1, 2, 3, ... ) ] |

| CSVtypeC4 | GBL_n+1, GBL_n+4, GBL_n+7,<br>GBL_n+10, GBL_n+13, ...<br>.....<br>[ GBL_n+1+3·k<br>( k = 0, 1, 2, 3, ... ) ] | CSBL_B_n+1, CSBL_B_n+4,<br>CSBL_B_n+7,<br>CSBL_B_n+10, CSBL_B_n+13, ...<br>.....<br>[CSBL_B_n+1+3·k<br>( k = 0, 1, 2, 3, ... ) ] |

| CSVtypeC5 | GBL_n+2, GBL_n+5, GBL_n+8,<br>GBL_n+11, GBL_n+14, ...<br>.....<br>[ GBL_n+2+3·k<br>( k = 0, 1, 2, 3, ... ) ] | CSBL_A_n+2, CSBL_A_n+5,<br>CSBL_A_n+8,<br>CSBL_A_n+11, CSBL_A_n+14, ...<br>.....<br>[CSBL_A_n+2+3·k<br>( k = 0, 1, 2, 3, ... ) ] |

| CSVtypeC6 | GBL_n+2, GBL_n+5, GBL_n+8,<br>GBL_n+11, GBL_n+14, ...<br>.....<br>[ GBL_n+2+3·k<br>( k = 0, 1, 2, 3, ... ) ] | CSBL_B_n+2, CSBL_B_n+5,<br>CSBL_B_n+8,<br>CSBL_B_n+11, CSBL_B_n+14, ...<br>.....<br>[CSBL_B_n+2+3·k<br>( k = 0, 1, 2, 3, ... ) ] |

## 【0163】

電気的に独立な補助容量幹線の数  $L$  の  $1 / 2$  が奇数であるとき、即ち  $L = 2, 6, 10, \dots$  であるとき、行方向、列方向にマトリックス状に配置された複数の画素が構成するある行を  $n$  行とし、任意の列の  $n$  行に属する画素が有する第1副画素の補助容量対向電極が接続された補助容量配線  $C S B L \_ A \_ n$ 、第2副画素の補助容量対向電極が接続された補助容量配線を  $C S B L \_ B \_ n$  で表し、 $k$  を自然数（0を含む）とすると、

$C S B L \_ A \_ n + (L / 2) \cdot k$  が第1補助容量幹線に接続され、

$C S B L \_ B \_ n + (L / 2) \cdot k$  が第2補助容量幹線に接続され、

$C S B L \_ A \_ n + 1 + (L / 2) \cdot k$  が第3補助容量幹線に接続され、

$C S B L \_ B \_ n + 1 + (L / 2) \cdot k$  が第4補助容量幹線に接続され、

$C S B L \_ A \_ n + 2 + (L / 2) \cdot k$  が第5補助容量幹線に接続され、

$C S B L \_ B \_ n + 2 + (L / 2) \cdot k$  が第6補助容量幹線に接続され、

$\dots$  以下同様の接続関係を繰り返し、

$C S B L \_ A \_ n + (L / 2) - 2 + (L / 2) \cdot k$  が第  $L - 3$  補助容量幹線に接続され、

$C S B L \_ B \_ n + (L / 2) - 2 + (L / 2) \cdot k$  が第  $L - 2$  補助容量幹線に接続され、

$C S B L \_ A \_ n + (L / 2) - 1 + (L / 2) \cdot k$  が第  $L - 1$  補助容量幹線に接続され、

$C S B L \_ B \_ n + (L / 2) - 1 + (L / 2) \cdot k$  が第  $L$  補助容量幹線に接続されるように構成すればよい。

## 【0164】

10

20

30

40

【表6】

| CS幹線      | 対応するケーブルライン                                                                                                      | 対応するCSn'ライン                                                                                                                                    |

|-----------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| CSVtypeD1 | GBL_n, GBL_n+4, GBL_n+8,<br>GBL_n+12, GBL_n+16, ...<br>.....<br>[ GBL_n+4·k<br>( k = 0, 1, 2, 3, ... ) ]         | CSBL_A_n, CSBL_B_n+4, CSBL_A_n+8,<br>CSBL_B_n+12, CSBL_A_n+16, ...<br>.....<br>[CSBL_A_n+8·k, CSBL_B_n+4+8·k,<br>( k = 0, 1, 2, 3, ... ) ]     |

| CSVtypeD2 | GBL_n, GBL_n+4, GBL_n+8,<br>GBL_n+12, GBL_n+16, ...<br>.....<br>[ GBL_n+4·k<br>( k = 0, 1, 2, 3, ... ) ]         | CSBL_B_n, CSBL_A_n+4, CSBL_B_n+8,<br>CSBL_A_n+12, CSBL_B_n+16, ...<br>.....<br>[CSBL_B_n+8·k, CSBL_A_n+4+8·k<br>( k = 0, 1, 2, 3, ... ) ]      |

| CSVtypeD3 | GBL_n+1, GBL_n+5, GBL_n+9,<br>GBL_n+13, GBL_n+17, ...<br>.....<br>[ GBL_n+1+4·k<br>( k = 0, 1, 2, 3, ... ) ]     | CSBL_A_n+1, CSBL_B_n+5, CSBL_A_n+9,<br>CSBL_B_n+13, CSBL_A_n+17, ...<br>.....<br>[CSBL_A_n+1+8·k, CSBL_B_n+5+8·k,<br>( k = 0, 1, 2, 3, ... ) ] |

| CSVtypeD4 | GBL_n+1, GBL_n+5, GBL_n+9,<br>GBL_n+13, GBL_n+17, ...<br>.....<br>[ GBL_n+1+4·k<br>( k = 0, 1, 2, 3, ... ) ]     | CSBL_B_n+1, CSBL_A_n+5, CSBL_B_n+9,<br>CSBL_A_n+13, CSBL_B_n+17, ...<br>.....<br>[CSBL_B_n+1+8·k, CSBL_A_n+5+8·k<br>( k = 0, 1, 2, 3, ... ) ]  |

| CSVtypeD6 | GBL_n+2, GBL_n+6,<br>GBL_n+10,<br>GBL_n+14, GBL_n+18, ...<br>.....<br>[ GBL_n+2+4·k<br>( k = 0, 1, 2, 3, ... ) ] | CSBL_A_n+2, CSBL_B_n+6, CSBL_A_n+10,<br>CSBL_B_n+14, CSBL_A_n+18, ...<br>.....<br>[CSBL_A_n+2+8·k, CSBL_B_n+6+8·k<br>( k = 0, 1, 2, 3, ... ) ] |

| CSVtypeD6 | GBL_n+2, GBL_n+6,<br>GBL_n+10,<br>GBL_n+14, GBL_n+18, ...<br>.....<br>[ GBL_n+2+4·k<br>( k = 0, 1, 2, 3, ... ) ] | CSBL_B_n+2, CSBL_A_n+6, CSBL_B_n+10,<br>CSBL_A_n+14, CSBL_B_n+18, ...<br>.....<br>[CSBL_B_n+2+8·k, CSBL_A_n+6+8·k<br>( k = 0, 1, 2, 3, ... ) ] |

| CSVtypeD7 | GBL_n+3, GBL_n+7, GBL_n+11,<br>GBL_n+15, GBL_n+19, ...<br>.....<br>[ GBL_n+3+4·k<br>( k = 0, 1, 2, 3, ... ) ]    | CSBL_A_n+3, CSBL_B_n+7, CSBL_A_n+11,<br>CSBL_B_n+15, CSBL_A_n+19, ...<br>.....<br>[CSBL_A_n+3+8·k, CSBL_B_n+7+8·k<br>( k = 0, 1, 2, 3, ... ) ] |

| CSVtypeC8 | GBL_n+3, GBL_n+7, GBL_n+11,<br>GBL_n+15, GBL_n+19, ...<br>.....<br>[ GBL_n+3+4·k<br>( k = 0, 1, 2, 3, ... ) ]    | CSBL_B_n+3, CSBL_A_n+7, CSBL_B_n+11,<br>CSBL_A_n+15, CSBL_B_n+19, ...<br>.....<br>[CSBL_B_n+3+8·k, CSBL_A_n+7+8·k<br>( k = 0, 1, 2, 3, ... ) ] |

## 【0165】

電気的に独立な補助容量幹線の数 L の  $1 / 2$  が偶数であるとき、即ち  $L = 4, 8, 12, \dots$  であるとき、行方向、列方向にマトリックス状に配置された複数の画素が構成するある行を n 行とし、任意の列の n 行に属する画素が有する第 1 副画素の補助容量対向電極が接続された補助容量配線 C S B L \_ A \_ n 、第 2 副画素の補助容量対向電極が接続された補助容量配線を C S B L \_ B \_ n で表し、k を自然数（0 を含む）とすると、

C S B L \_ A \_ n + L · k および C S B L \_ B \_ n + ( L / 2 ) + L · k が第 1 補助容量幹線に接続され、

C S B L \_ B \_ n + L · k および C S B L \_ A \_ n + ( L / 2 ) + L · k が第 2 補助容量幹線に接続され、

C S B L \_ A \_ n + 1 + L · k および C S B L \_ B \_ n + ( L / 2 ) + 1 + L · k が第 3 補助容量幹線に接続され、

C S B L \_ B \_ n + 1 + L · k および C S B L \_ A \_ n + ( L / 2 ) + 1 + L · k が第 4 補助容量幹線に接続され、

C S B L \_ A \_ n + 2 + L · k および C S B L \_ B \_ n + ( L / 2 ) + 2 + L · k が第 5 補助容量幹線に接続され、

C S B L \_ B \_ n + 2 + L · k および C S B L \_ A \_ n + ( L / 2 ) + 2 + L · k が第 6 補助容量幹線に接続され、

C S B L \_ A \_ n + 3 + L · k および C S B L \_ B \_ n + ( L / 2 ) + 3 + L · k が第

10

20

30

40

50

7 補助容量幹線に接続されており、

$C S B L\_B\_n + 3 + L \cdot k$  および  $C S B L\_A\_n + (L / 2) + 3 + L \cdot k$  が第 8 補助容量幹線に接続され、

・・・・・以下同様の接続関係を繰り返し、

$C S B L\_A\_n + (L / 2) - 2 + L \cdot k$  および  $C S B L\_B\_n + L - 2 + L \cdot k$  が第  $L - 3$  補助容量幹線に接続され、

$C S B L\_B\_n + (L / 2) - 2 + L \cdot k$  および  $C S B L\_A\_n + L - 2 + L \cdot k$  が第  $L - 2$  補助容量幹線に接続され、

$C S B L\_A\_n + (L / 2) - 1 + L \cdot k$  および  $C S B L\_B\_n + L - 1 + L \cdot k$  が第  $L - 1$  補助容量幹線に接続されており、

$C S B L\_B\_n + (L / 2) - 1 + L \cdot k$  および  $C S B L\_A\_n + L - 1 + L \cdot k$  が第  $L$  補助容量幹線に接続されればよい。

#### 【0166】

以上で説明したように、本発明によると、斜観測時の白浮特性を大幅に改善するマルチ画素方式の液晶表示装置を、大型の液晶表示装置、あるいは高精細の液晶表示装置、さらには垂直走査期間および水平走査期間を短くした高速駆動の液晶表示装置に容易に適用することが可能となる。なぜならば、CSバスラインに振動電圧を印加するマルチ画素方式の液晶表示装置を大型化すればCSバスラインの負荷容量あるいは負荷抵抗が増加しCSバスライン電圧の波形が鈍ったり、また液晶表示装置の高精細化、高速駆動化を行えばCSバスラインの振動周期が短くなるために波形鈍りの影響が顕著になり、表示画面内でVLCaddの実効値の変化が顕著になるため、表示ムラを発生する等の問題があるが、これらの問題はCSバスラインに印加する振動電圧の周期を長くすることによって改善できるからである。

#### 【0167】

特許文献5に記載されている液晶表示装置では、隣接行の画素の隣接する副画素に対応するCSバスラインを電気的に共通とし、かつ、電気的に独立なCS幹線を2種類とした場合ではCSバスライン電圧の振動の周期は1Hであったのに対し、本発明のTypeIの構成を有する液晶表示装置では隣接行の画素の隣接する副画素に対応するCSバスラインを電気的に独立とし、かつ、電気的に独立なCS幹線を2種類とした場合にCSバスライン電圧の振動の周期を2Hとし、電気的に独立なCS幹線を4種類とした場合ではCSバスライン電圧の振動の周期を4Hとすることができます。

#### 【0168】

本発明のTypeIの構成を有する液晶表示装置の構成あるいは駆動波形に基づけば、隣接行の画素の隣接する副画素に対応するCS幹線を電気的に独立とし、かつ、電気的に独立なCS幹線の種類をL種類とすればCSバスライン電圧の振動の周期を水平走査期間のL倍(LH)とすることができる。

#### 【0169】

次に、本発明のTypeIIの構成を有する実施形態の液晶表示装置およびその駆動方法を説明する。

#### 【0170】

上述したように、本発明のTypeIの構成を有する液晶表示装置は、電気的に独立な補助容量対向電極の組の数(電気的に独立なCS幹線の数)をLとすることによって、補助容量対向電極に印加する振動電圧の振動周期を水平走査期間HのL倍とすることを可能とした。これにより、補助容量対向電極配線の電気的負荷が大きな大型高精細の液晶表示装置においても前記マルチ画素表示を行うことが可能となるといった効果が得られる。

#### 【0171】

しかしながら、列方向に隣接する2つの画素(すなわち隣接する行に属する2つの画素)を構成する各副画素に補助容量対向電極を電気的に独立とする必要があった(例えば図9参照)。即ち、1画素あたり2本のCSバスラインが必要となるために、画素開口率が低下する。具体的には、例えば図15(a)に示すように、各副画素に対応するCSバス

10

20

30

40

50

ラインを各副画素の中央を横切るように配置すると、列方向に隣接する画素間からの光漏れを防止するために遮光層BM1を設ける必要がある。従って、2本のCSバスラインおよび遮光層BM1と重なる領域は、表示に寄与できなくなり、画素開口率を低下させることになる。

#### 【0172】

これに対し、TypeIIの構成を有する実施形態の液晶表示装置では、図15(b)に示したように、列方向に隣接する2つの画素の一方の副画素の補助容量対向電極と他方の副画素(前記一方の副画素と前記他方の副画素は列方向に隣接する)の補助容量対向電極とを共通のCSバスラインに接続し、このCSバスラインを列方向に隣接する2つの画素の間に配置することによって、CSバスラインを遮光層としても機能させることにより、図15(a)の構成に比べて、CSバスラインの本数を減らせる上に、別途設ける必要であった遮光層BM1を省略することにより、画素開口率を向上できるという利点が得られる。10

#### 【0173】

また、TypeIの構成を有する実施形態の液晶表示装置では、CSバスラインに印加する振動電圧の振動周期を水平走査期間のL倍とするためには、電気的に独立なCS幹線の数をL本とする必要があり、補助容量対向電極駆動電源もL個必要となる。従って、CSバスラインに印加する振動電圧の振動周期を任意に長周期にしようとする場合、それに応じてCS幹線の数、容量対向電極駆動電源の数が多数必要となる。このように、TypeIの構成を有する実施形態の液晶表示装置において、CSバスラインに印加する振動電圧を長周期化するためには、CS幹線の数および容量対向電極駆動電源を増大させる必要があることから、一定の制限を受ける。20

#### 【0174】

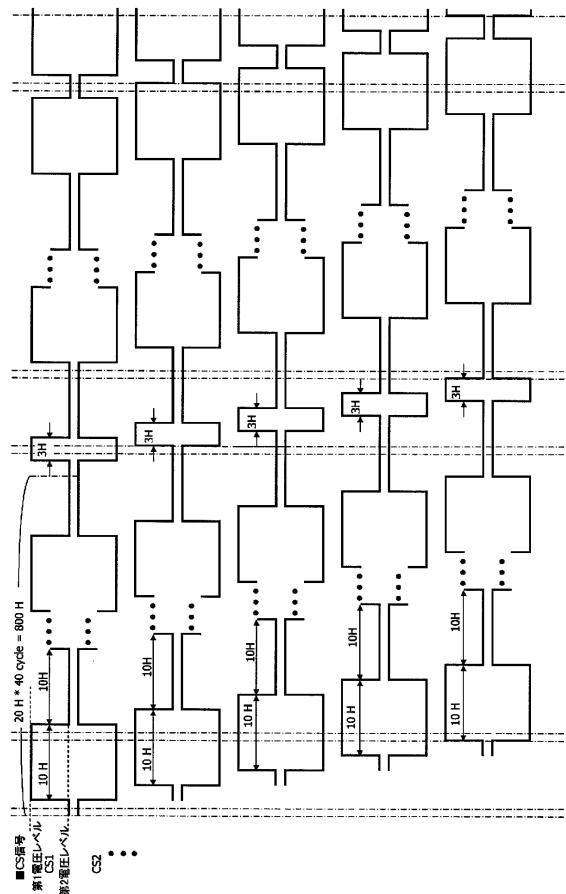

これに対し、本発明のTypeIIの構成を有する実施形態の液晶表示装置においては、電気的に独立なCS幹線の数をL(Lは偶数)とするとき、振動電圧の振動の周期を水平走査期間の2・K・L倍(Kは正の整数)とすることができます。

#### 【0175】

このように、本発明のTypeIIの構成を有する実施形態の液晶表示装置は、TypeIの構成を有する実施形態の液晶表示装置よりも、大型・高精細の液晶表示装置にさらに適している。30

#### 【0176】

以下、本発明のTypeIIの構成を有する具体的な実施形態を説明する。以下の説明では、図16Aおよび図16Bに示した駆動状態を実現する液晶表示装置を例示する。図16Aおよび図16Bは、それぞれ先に示した図4Aおよび図4Bに対応し、液晶層に印加される電界の向きが互いに逆の駆動状態を示している。以下では、図16Aに示す駆動状態を実現するための構成を説明する。なお、図16Bの示す駆動状態を実現するためには、図3Aおよび図3Bを参照しながら説明したのと同様に、図16Aに示す駆動状態を実現するためにはソースバスラインに印加する電圧および各補助容量電圧の極性を反転させればよい。これにより画素の表示極性(図中「+」或いは「-」で表示)を反転しつつ、且つ第1、第2副画素の位置(図中「明」或いは「暗」で表示)の位置を固定できる。但し、本発明はこれに限らずソースバスラインに印加する電圧のみを反転させても良い。この場合、第1、第2副画素の位置(図中「明」或いは「暗」で表示)の位置は画素の極性反転に伴って移動するため、前記固定の場合に発生する中間階調表示時の色のにじみ等の問題を改善できる。40

#### 【0177】

また、以下の実施形態の液晶表示装置は、図15(b)に示したように、列方向に隣接する2つの画素(n行目とn+1行目)の間に、n行目の画素の副画素電極18bとn+1行目の副画素電極18aとの間に、これら2つの副画素電極にそれぞれ対応する副画素の補助容量に補助容量対向電圧(振動電圧)を供給する共通のCSバスラインCSBLが設けられた構成を備えており、このCSバスラインCSBLがn行目の画素とn+1行目50

の画素との間を遮光する遮光層として機能する。CSバスラインCSBLは、絶縁膜を介して、一部が副画素電極18aおよび18bと重なるように配置されてもよい。

#### 【0178】

また、以下に例示する実施形態の液晶表示装置は、何れもCSバスラインに印加する振動電圧の振動周期を1水平走査期間よりも長く、電気的に独立なCS幹線の数をL(Lは偶数)とするとき、振動電圧の振動の周期を水平走査期間の2・K・L倍(Kは正の整数)となっている。すなわち、本発明のTypeIの構成を有する実施形態の液晶表示装置においては振動電圧の振動の周期はL倍にしかならなかったのに対し、本発明のTypeIIの構成を有する実施形態の液晶表示装置においては、2・K倍のファクタだけ更に振動周期を長くすることが可能であり、しかもKは電気的に独立なCS幹線の数に依存しないという利点を有している。Kは電気的に独立な個々のCS幹線とCSバスラインとの接続形態に依存して決まるパラメータであり、CS幹線に対する接続形態の1周期を構成する連続したCSバスラインの内で共通のCS幹線に接続されたCSバスラインの数(電気的に等価なCSバスラインの数)の1/2に対応する。10

#### 【0179】

本発明による液晶表示装置の面積階調表示(マルチ画素駆動)は、画素を2つの副画素に分割し、各副画素に接続された補助容量に異なる振動電圧(補助容量対向電圧)を供給することによって、明副画素と暗副画素を得る。明副画素は、例えば、TFTがオフとされた後の振動電圧の最初の変化が増大である場合に得られ、暗副画素は、逆に、TFTがオフとされた後の振動電圧の最初の変化が低下である場合に得られる。従って、TFTがオフされた後に振動電圧が増大されるべき副画素のCSバスラインを共通のあるCS幹線に接続し、TFTがオフされた後に振動電圧が低下されるべき副画素のCSバスラインを他の共通のCS幹線に接続すれば、CS幹線の数を減らすことができるようになる。このCSバスラインのCS幹線に対する接続形態による長周期化の効果を示すパラメータがKである。20

#### 【0180】

Kを大きくするとそれだけ振動電圧を長周期化できるが、Kは大き過ぎないことが好ましい。理由を以下に説明する。

#### 【0181】

Kを大きくすると共通のCS幹線に接続された副画素の数が増えることになる。それは異なるTFTに接続されており、TFTは異なるタイミング(1Hの倍数)でオフされる。従って、共通のCS幹線に接続されたある副画素のTFTがオフされた後、その振動電圧が最初に増大する(又は低下する)までの時間と、他の副画素のTFTがオフされた後、その振動電圧が最初に増大する(又は低下する)までの時間が異なることになる。Kが大きくなるほど、すなわち、共通のCS幹線に接続されるCSバスラインの数が大きくなるほど、この時間の差が大きくなり、ライン状の輝度むらとして視認されるおそれがある。この輝度むらを発生させないためには、目安として、上記の時間差が走査線の数(画素行の数)の5%以下とするとすることが好ましい。例えば、XGAの場合には、768行の5%以下とすると、上記時間差が38H以下となるように、Kを設定することが好ましい。なお、振動電圧の周期の下限値は、図8等を参照しながら上述した波形の鈍りによる輝度むらが生じないように設定する。例えば、45型のXGAの場合、振動周期が12H以上であれば、波形鈍りによる問題は生じない。これらのことから、45型程度の液晶テレビに適用する場合、Kを1または2として、Lを6、8、10、12とし、振動電圧の周期を12Hから48Hの範囲で設定すれば、輝度むらの無い高品位の表示を得ることが出来る。なお、電気的に独立なCS幹線の数Lは、振動電圧源(補助容量対向電極駆動電源)の数や、パネル上(TFT基板上)の配線の引きまわしなどを考慮して設定する。3040

#### 【0182】

以下に、K=1で、L=4、6、8、10、12とした例および、K=2で、L=4、6とした例を示し、本発明のTypeIIの構成を有する実施形態の液晶表示装置およびその駆動方法を詳細に説明する。以下の説明では、先の実施形態の説明との重複を避ける50

ためにCSバスラインとCS幹線との接続形態を中心に説明する。

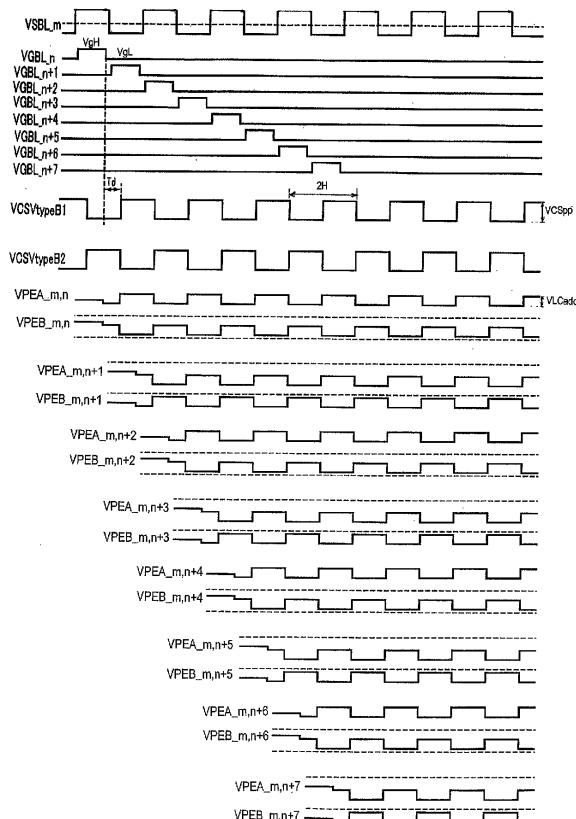

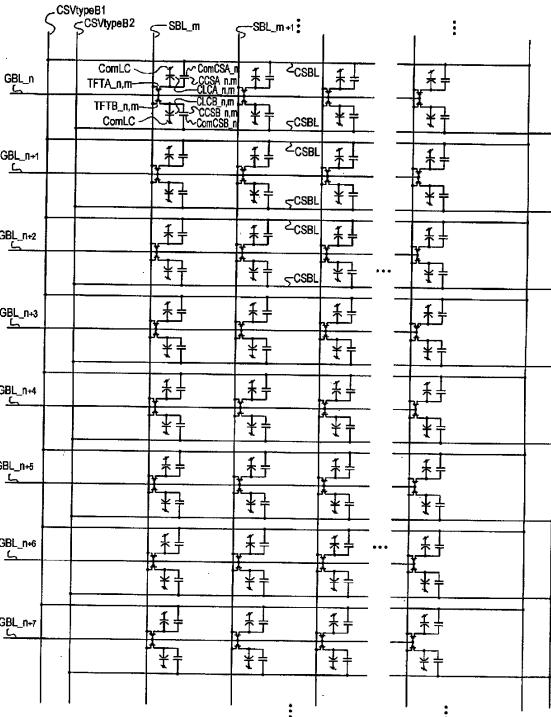

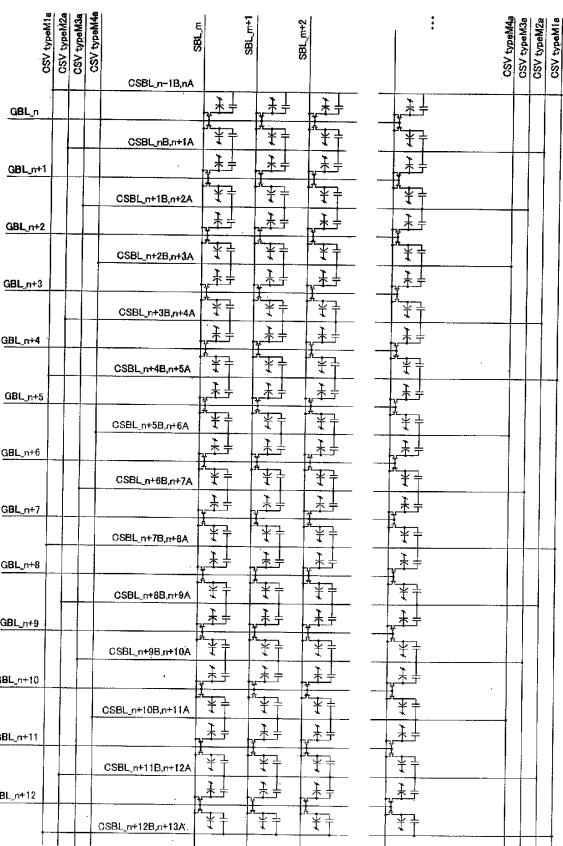

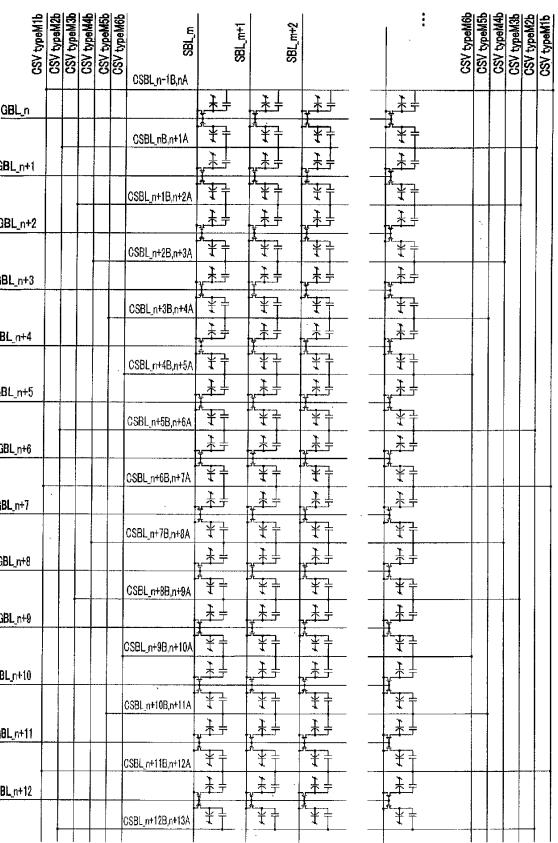

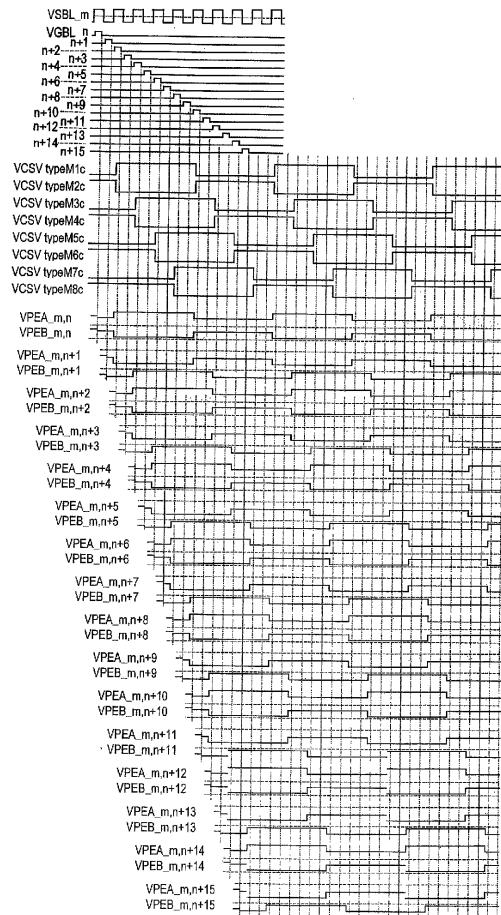

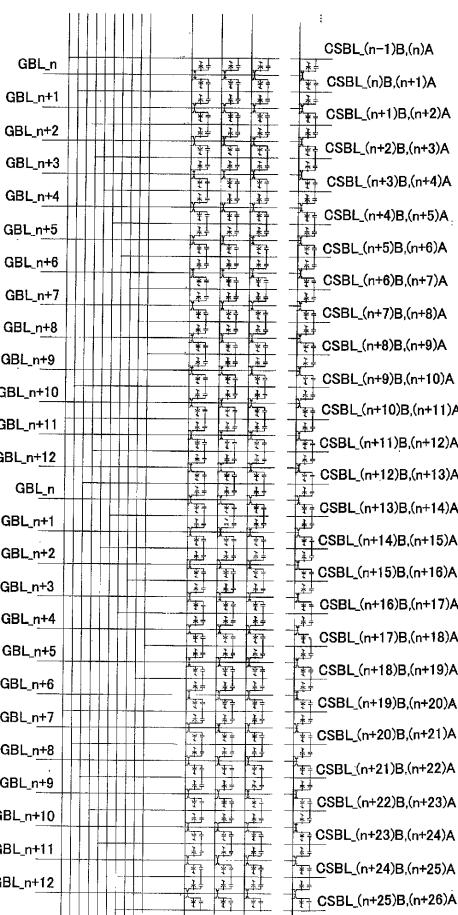

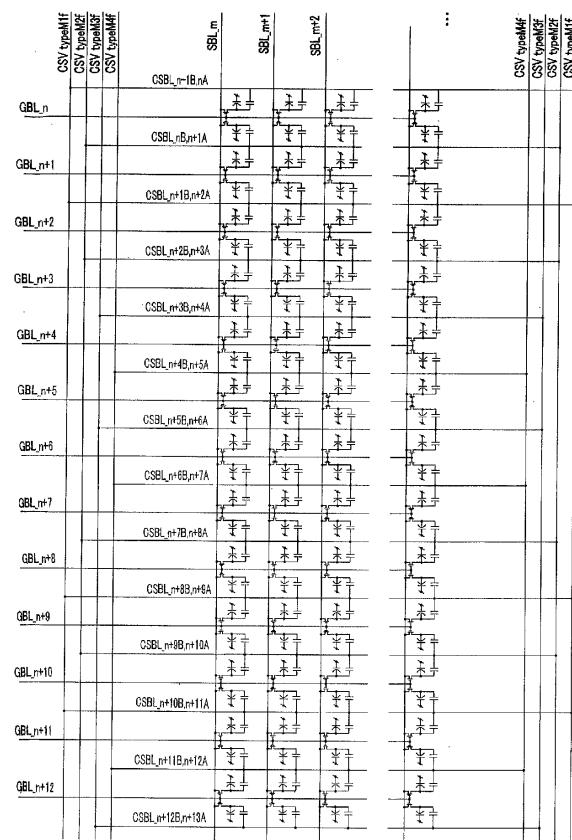

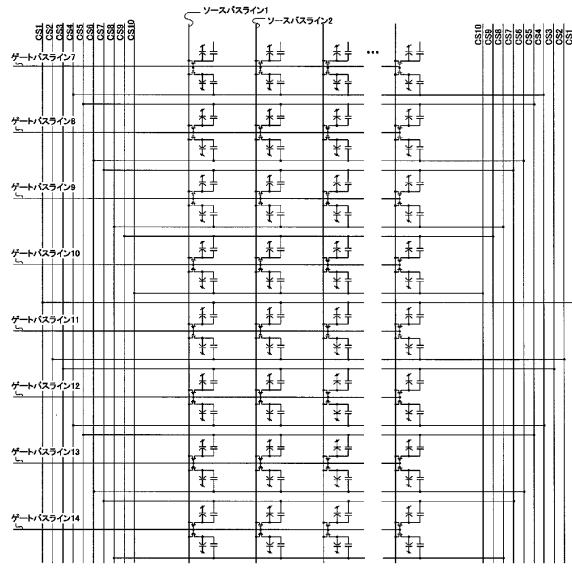

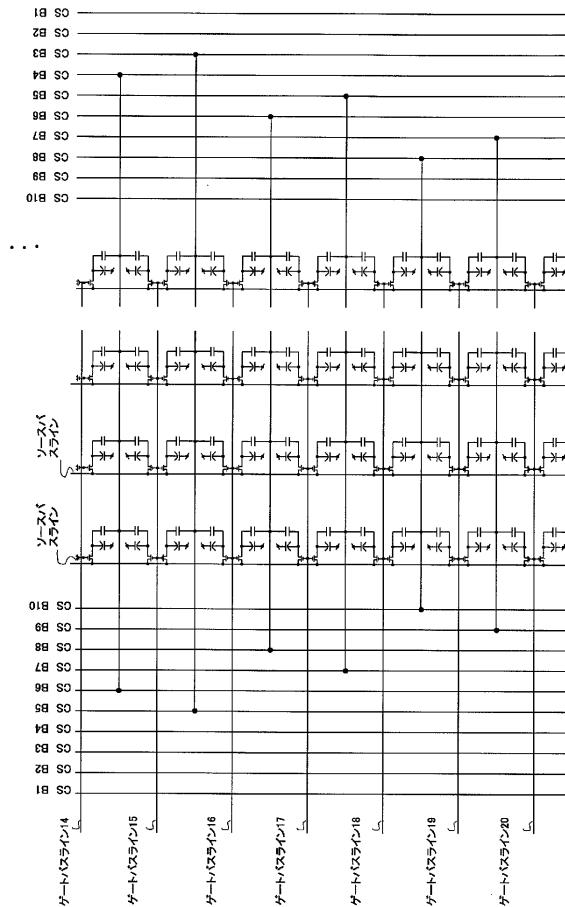

【0183】

[ $K = 1, L = 4$ 、振動周期：8H]

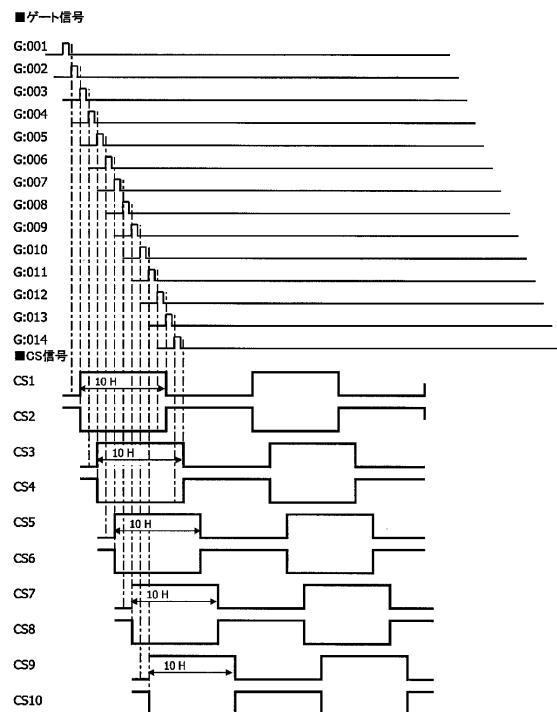

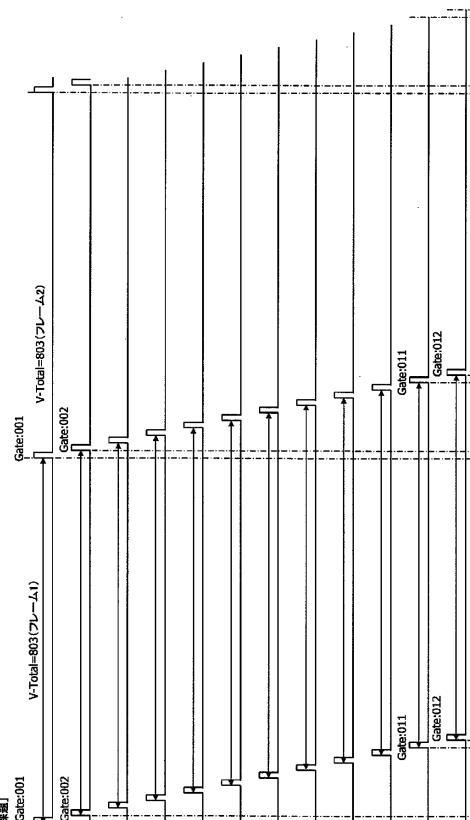

Type IIの構成を有する実施形態の液晶表示装置のマトリックス構成（CSバスラインの接続形態）を図17に、この液晶表示装置の駆動に用いられる信号の波形を図18に示す。また、図17の接続形態を表7に示す。図17のマトリックス構成に対して、図18のタイミングでCSバスラインに振動電圧を印加することで、図15Aに示した駆動状態が実現される。

【0184】

図17によれば各CSバスラインは図の左右端の各々4本のCS幹線の何れかに接続されている。よって電気的に独立なCSバスラインの数は4であり、 $L = 4$ となる。さらに図17によれば、CSバスラインとCS幹線の接続形態に一定の規則があり、その規則は図中のCSバスライン8本毎の周期性を持っていることが解る。よって、 $K = 1 (= 8 / (2L))$ となっている。

【0185】

【表7】

$L = 4, K = 1$

| CS幹線 | CS幹線に接続されるCSバスライン                            |

|------|----------------------------------------------|

| M1a  | CSBL <sub>n-1</sub> B, CSBL <sub>n</sub> A   |

|      | CSBL <sub>n+4</sub> B, CSBL <sub>n+5</sub> A |

| M2a  | CSBL <sub>n</sub> B, CSBL <sub>n+1</sub> A   |

|      | CSBL <sub>n+3</sub> B, CSBL <sub>n+4</sub> A |

| M3a  | CSBL <sub>n+1</sub> B, CSBL <sub>n+2</sub> A |

|      | CSBL <sub>n+6</sub> B, CSBL <sub>n+7</sub> A |

| M4a  | CSBL <sub>n+2</sub> B, CSBL <sub>n+3</sub> A |

|      | CSBL <sub>n+5</sub> B, CSBL <sub>n+6</sub> A |

但し  $n = 1, 9, 17, \dots$

10

20

30

【0186】

表7から、図17に示すCSバスラインは、任意のpについて

CSBL<sub>p</sub> B, CSBL<sub>p+1</sub> A

と

CSBL<sub>p+5</sub> B, CSBL<sub>p+6</sub> A

との関係を満足するタイプ（一型）

或いは

CSBL<sub>p+1</sub> B, CSBL<sub>p+2</sub> A

と

CSBL<sub>p+4</sub> B, CSBL<sub>p+5</sub> A

との関係を満足するタイプ（二型）

の2種類が存在していることがわかる。すなわち、M1aおよびM3aのCS幹線に接続されているCSバスラインは一型であり、M2aおよびM4aのCS幹線に接続されているCSバスラインは二型である。

【0187】

接続形態の1周期を構成する連続する8本のCSバスラインは、4本の一型（M1aに接続された2本とM3aに接続された2本）、と4本の二型（M2aに接続された2本とM4aに接続された2本）とで構成されている。

【0188】

これを、前述のパラメータL、Kを用いて示せば、任意のpについて

40

50

$C S B L \_ ( p + 2 \cdot ( K - 1 ) ) B, ( p + 2 \cdot ( K - 1 ) + 1 ) A$

と

$C S B L \_ ( p + 2 \cdot ( K - 1 ) + K \cdot L + 1 ) B, ( p + 2 \cdot ( K - 1 ) + K \cdot L + 2 ) A$

或いは、

$C S B L \_ ( p + 2 \cdot ( K - 1 ) + 1 ) B, ( p + 2 \cdot ( K - 1 ) + 2 ) A$  と

$C S B L \_ ( p + 2 \cdot ( K - 1 ) + K \cdot L ) B, ( p + 2 \cdot ( K - 1 ) + K \cdot L + 1 ) A$

の何れかで表される  $C S$  バスラインの組を電気的に等価にすれば良いことがわかる。但し  $p$  は  $p = 1, 3, 5, \dots$  もしくは  $p = 2, 4, \dots$  である。この条件を導入する理由は 型と 型との両方に属する  $C S$  バスラインは存在しないためである。

10

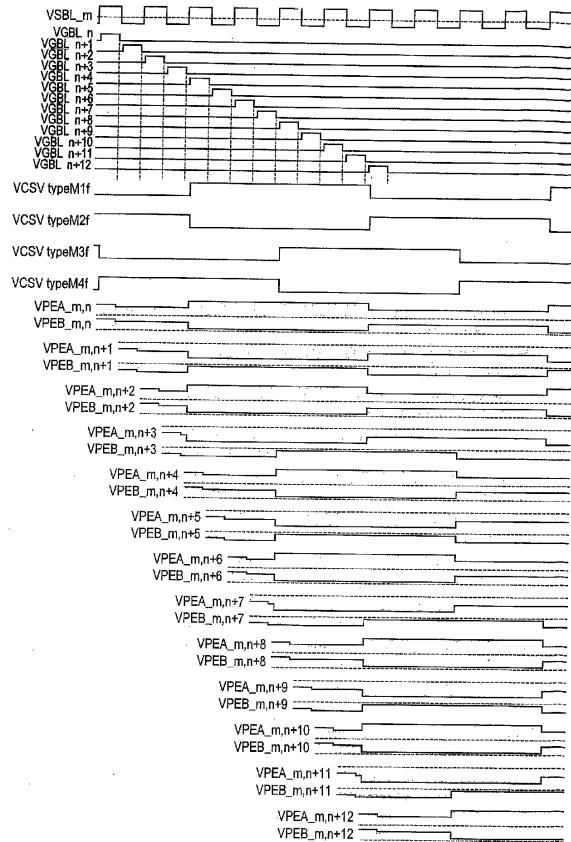

#### 【0189】

尚、図 18 によれば、このときの  $C S$  バスラインに印加される振動電圧の振動周期は 8 H、即ち水平走査期間 H の  $2 \cdot K \cdot L$  倍となっていることがわかる。

#### 【0190】

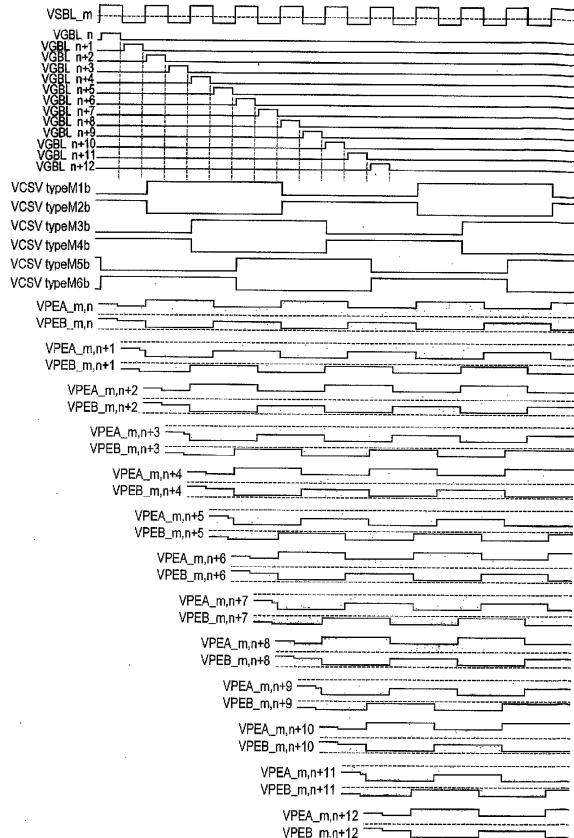

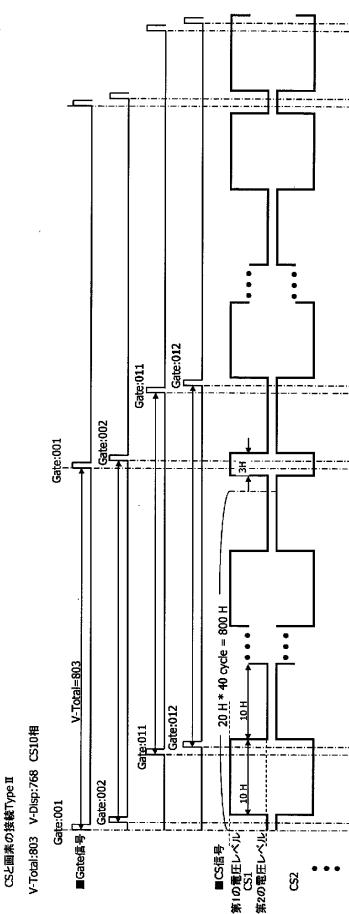

[  $K = 1, L = 6$  、 振動の周期 : 12 H ]

次に、電気的に独立な  $C S$  幹線の数が 6 本の場合の接続形態を図 19 に、そのときの駆動波形を図 20 に示す。また、図 19 の接続形態を表 8 に示す。

#### 【0191】

図 20 によれば各  $C S$  バスラインは図の左右端の各々 6 本の  $C S$  幹線の何れかに接続されている。よって電気的に独立な  $C S$  バスラインの数は 6 であり、 $L = 6$  となる。

20

#### 【0192】

さらに図 19 によれば、 $C S$  バスラインと  $C S$  幹線の接続形態に一定の規則があり、その規則は図中の  $C S$  バスライン 12 本毎の周期性を持っている。よって、 $K = 1 (= 12 / (2L))$  となっている。

#### 【0193】

【表 8】

$L = 6, K = 1$

| CS 幹線 | CS 幹線に接続される CS バスライン        |

|-------|-----------------------------|

| M1b   | $CSBL_{(n-1)} B, (n) A$     |

|       | $CSBL_{(n+6)} B, (n+7) A$   |

| M2b   | $CSBL_{(n)} B, (n+1) A$     |

|       | $CSBL_{(n+5)} B, (n+6) A$   |

| M3b   | $CSBL_{(n+1)} B, (n+2) A$   |

|       | $CSBL_{(n+8)} B, (n+9) A$   |

| M4b   | $CSBL_{(n+2)} B, (n+3) A$   |

|       | $CSBL_{(n+7)} B, (n+8) A$   |

| M5b   | $CSBL_{(n+3)} B, (n+4) A$   |

|       | $CSBL_{(n+10)} B, (n+11) A$ |

| M6b   | $CSBL_{(n+4)} B, (n+5) A$   |

|       | $CSBL_{(n+9)} B, (n+10) A$  |

但し  $n = 1, 13, 25, \dots$

#### 【0194】

表 8 から、図 19 に示す  $C S$  バスラインの接続は、

$C S B L \_ ( p ) B, ( p + 1 ) A$

と

$C S B L \_ ( p + 7 ) B, ( p + 8 ) A$

30

40

50

或いは

$$C S B L \_ ( p + 1 ) B , ( p + 2 ) A$$

と

$$C S B L \_ ( p + 6 ) B , ( p + 7 ) A$$

但し、 $p = 1, 3, 5, \dots$  もしくは  $p = 2, 4, \dots$

の組が電気的に等しいCSバスラインとなっている事がわかる。

### 【0195】

これを、前述のパラメータ  $L, K$  を用いて示せば、任意の  $p$  について、

$$C S B L \_ ( p + 2 \cdot ( K - 1 ) ) B , ( p + 2 \cdot ( K - 1 ) + 1 ) A$$

と

$$C S B L \_ ( p + 2 \cdot ( K - 1 ) + K \cdot L + 1 ) B , ( p + 2 \cdot ( K - 1 ) + K \cdot L + 2 ) A$$

或いは、

$$C S B L \_ ( p + 2 \cdot ( K - 1 ) + 1 ) B , ( p + 2 \cdot ( K - 1 ) + 2 ) A$$

$$C S B L \_ ( p + 2 \cdot ( K - 1 ) + K \cdot L ) B , ( p + 2 \cdot ( K - 1 ) + K \cdot L + 1 ) A$$

A

の何れかで表されるCSバスラインの組を電気的に等価にすれば良いことがわかる。但し  $p$  は  $p = 1, 3, 5, \dots$  もしくは  $p = 0, 2, 4, \dots$  である。

### 【0196】

尚、図20によれば、このときのCSバスラインに印加される振動電圧の振動周期は  $1 / 2H$ 、即ち水平走査期間の  $2 \cdot K \cdot L$  倍となっていることがわかる。

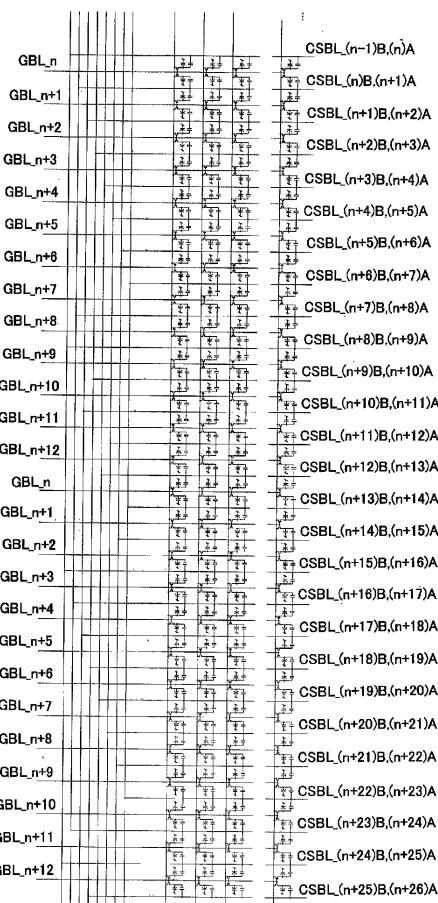

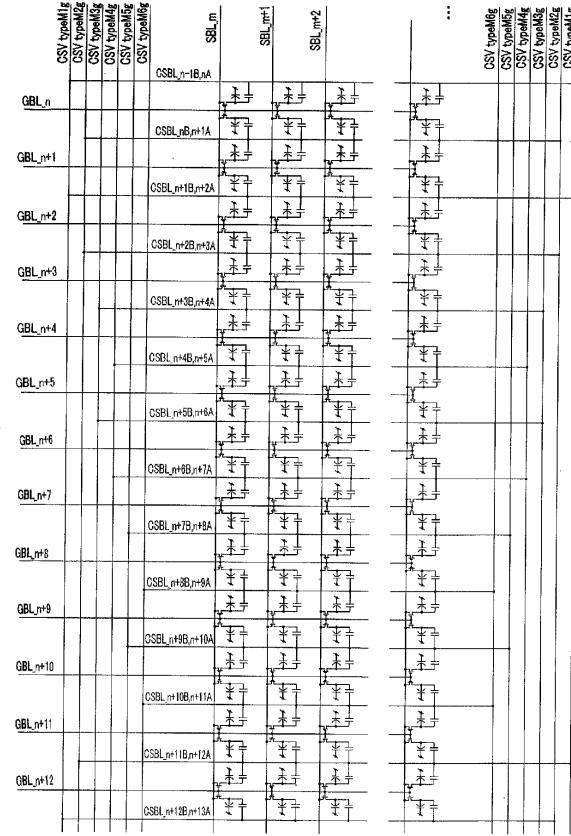

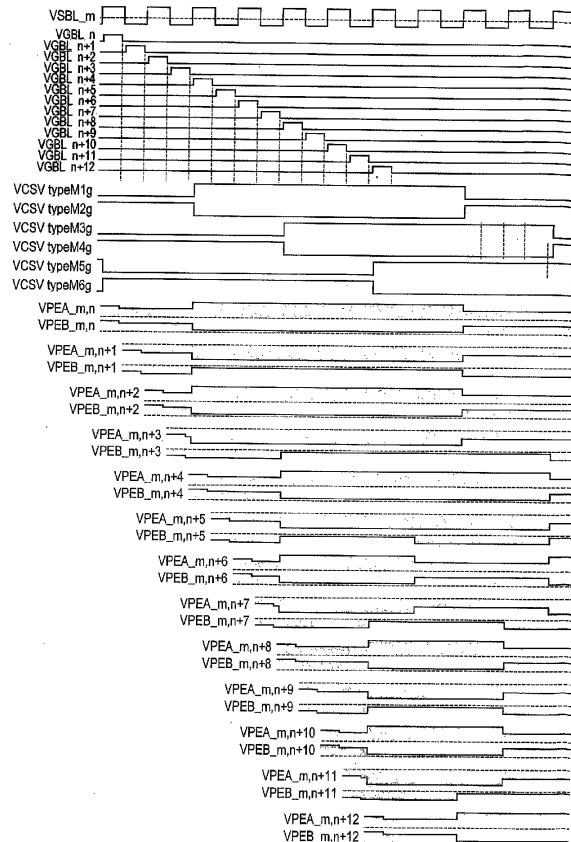

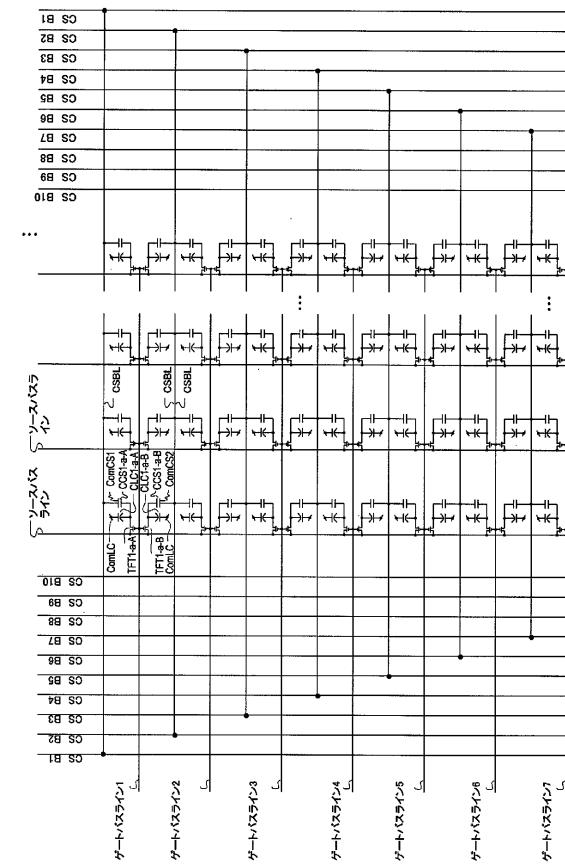

### 【0197】

[  $K = 1, L = 8$  、振動の周期 :  $16H$  ]

次に、電気的に独立なCSバスラインの数が8本の場合の接続形態を図21に、そのときの駆動波形を図22に示す。また、図21の接続形態を表9に示す。

### 【0198】

図21によれば各CSバスラインは図の左端の8本のCS幹線の何れかに接続されている。よって電気的に独立なCSバスラインの数は8であり、 $L = 8$  となる。

### 【0199】

さらに図21によれば、CSバスラインとCS幹線の接続形態に一定の規則があり、その規則は図中のCSバスライン16本毎の周期性を持っている。よって、 $K = 1 (= 16 / (2L))$  となっている。

### 【0200】

10

20

30

## 【表9】

$L = 8, K = 1$

| CS幹線 | CS幹線に接続されるCSバスライン                             |

|------|-----------------------------------------------|

| M1c  | CSBL <sub>n-1</sub> B, CSBL <sub>n+8</sub> A  |

| M2c  | CSBL <sub>n</sub> B, CSBL <sub>n+7</sub> A    |

| M3c  | CSBL <sub>n+1</sub> B, CSBL <sub>n+10</sub> A |

| M4c  | CSBL <sub>n+2</sub> B, CSBL <sub>n+9</sub> A  |

| M5c  | CSBL <sub>n+3</sub> B, CSBL <sub>n+12</sub> A |

| M6c  | CSBL <sub>n+4</sub> B, CSBL <sub>n+11</sub> A |

| M7c  | CSBL <sub>n+5</sub> B, CSBL <sub>n+14</sub> A |

| M8c  | CSBL <sub>n+6</sub> B, CSBL <sub>n+13</sub> A |

10

20

但し  $n = 1, 17, 33, \dots$

## 【0201】

表9から、図21に示すCSバスラインの接続は、

CSBL<sub>p</sub> B, CSBL<sub>p+1</sub> A

と

CSBL<sub>p+9</sub> B, CSBL<sub>p+10</sub> A

あるいは

CSBL<sub>p+1</sub> B, CSBL<sub>p+2</sub> A

30

と

CSBL<sub>p+8</sub> B, CSBL<sub>p+9</sub> A但し、 $p = 1, 3, 5, \dots$  もしくは  $p = 0, 2, 4, \dots$

の組が電気的に等しいCSバスラインとなっている事がわかる。

## 【0202】

これを、前述のパラメータL, Kを用いて示せば、任意のpについて、

CSBL<sub>(p+2·(K-1))</sub> B, CSBL<sub>(p+2·(K-1)+1)</sub> A

と

CSBL<sub>(p+2·(K-1)+K·L+1)</sub> B, CSBL<sub>(p+2·(K-1)+K·L+2)</sub> A

40

あるいは、

CSBL<sub>(p+2·(K-1)+1)</sub> B, CSBL<sub>(p+2·(K-1)+2)</sub> A とCSBL<sub>(p+2·(K-1)+K·L)</sub> B, CSBL<sub>(p+2·(K-1)+K·L+1)</sub> Aの何れかで表されるCSバスラインの組を電気的に等価にすれば良いことがわかる。但し  $p$  は  $p = 1, 3, 5, \dots$  もしくは  $p = 0, 2, 4, \dots$  である。

## 【0203】

尚、図22によれば、このときのCSバスラインに印加される振動電圧の振動周期は16H、即ち水平走査期間の $2·K·L$ 倍となっていることがわかる。

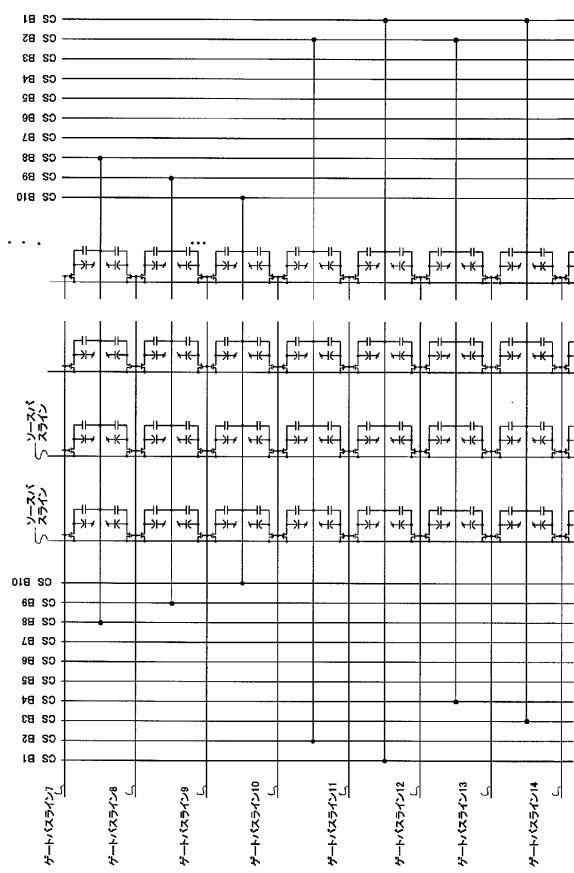

## 【0204】

50

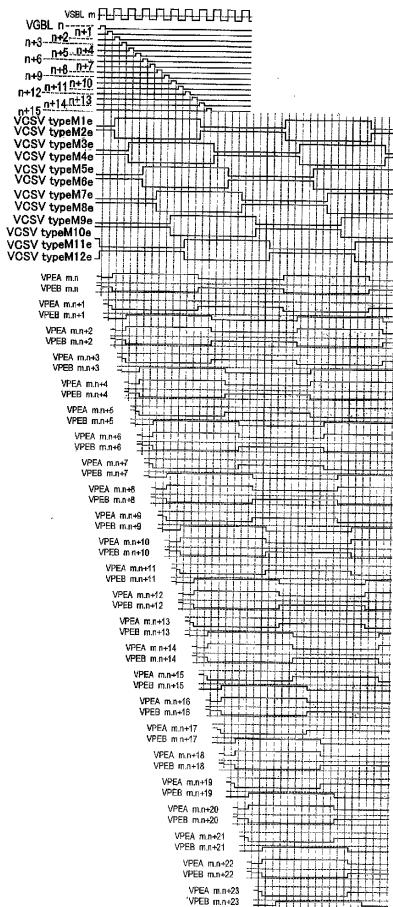

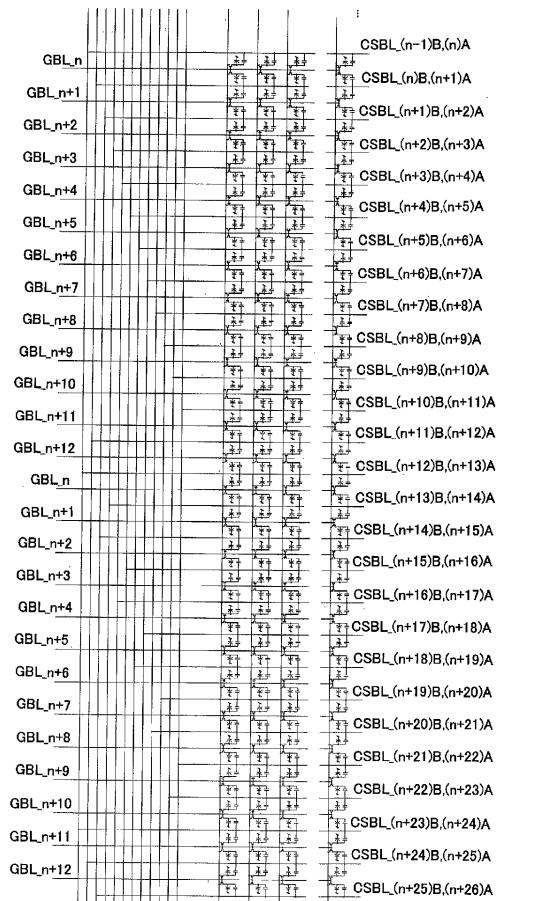

[  $K = 1$  、  $L = 10$  、 振動の周期 : 20H ]

次に、電気的に独立なCSバスラインの数が10本の場合の接続形態を図23に、そのときの駆動波形を図24に示す。また、図23の接続形態を表10に示す。

**【0205】**

図23によれば各CSバスラインは図の左右端の各々10本のCS幹線の何れかに接続されている。よって電気的に独立なCSバスラインの数は10であり、 $L = 10$ となる。さらに図23によれば、CSバスラインとCS幹線の接続形態に一定の規則があり、その規則は図中のCSバスライン20本毎の周期性を持っている。よって、 $K = 1$  ( $= 20 / (2L)$ ) となっている。

**【0206】**

**【表10】**

$L = 10, K = 1$

| CS幹線 | CS幹線に接続されるCSバスライン                |

|------|----------------------------------|

| M1d  | CSBL <sub>n-1</sub> B, (n) A     |

|      | CSBL <sub>n+10</sub> B, (n+11) A |

| M2d  | CSBL <sub>n</sub> B, (n+1) A     |

|      | CSBL <sub>n+9</sub> B, (n+10) A  |

| M3d  | CSBL <sub>n+1</sub> B, (n+2) A   |

|      | CSBL <sub>n+12</sub> B, (n+13) A |

| M4d  | CSBL <sub>n+2</sub> B, (n+3) A   |

|      | CSBL <sub>n+11</sub> B, (n+12) A |

| M5d  | CSBL <sub>n+3</sub> B, (n+4) A   |

|      | CSBL <sub>n+14</sub> B, (n+15) A |

| M6d  | CSBL <sub>n+4</sub> B, (n+5) A   |

|      | CSBL <sub>n+13</sub> B, (n+14) A |

| M7d  | CSBL <sub>n+5</sub> B, (n+6) A   |

|      | CSBL <sub>n+16</sub> B, (n+17) A |

| M8d  | CSBL <sub>n+6</sub> B, (n+7) A   |

|      | CSBL <sub>n+15</sub> B, (n+16) A |

| M9d  | CSBL <sub>n+7</sub> B, (n+6) A   |

|      | CSBL <sub>n+18</sub> B, (n+19) A |

| M10d | CSBL <sub>n+8</sub> B, (n+7) A   |

|      | CSBL <sub>n+17</sub> B, (n+18) A |

但し  $n = 1, 21, 41, \dots$

**【0207】**

表10から、図23に示すCSバスラインの接続は、

CSBL<sub>p</sub> B, (p+1) A

と

CSBL<sub>p+11</sub> B, (p+12) A

あるいは

CSBL<sub>p+1</sub> B, (p+2) A

と

CSBL<sub>p+10</sub> B, (p+11) A

但し、 $p = 1, 3, 5, \dots$  もしくは  $p = 0, 2, 4, \dots$

の組が電気的に等しいCSバスラインとなっている事がわかる。

**【0208】**

これを、前述のパラメータL, Kを用いて示せば、任意のpについて、

10

20

30

40

50

$C S B L \_ ( p + 2 \cdot ( K - 1 ) ) B, ( p + 2 \cdot ( K - 1 ) + 1 ) A$

と

$C S B L \_ ( p + 2 \cdot ( K - 1 ) + K \cdot L + 1 ) B, ( p + 2 \cdot ( K - 1 ) + K \cdot L + 2 ) A$

或いは、

$C S B L \_ ( p + 2 \cdot ( K - 1 ) + 1 ) B, ( p + 2 \cdot ( K - 1 ) + 2 ) A$  と

$C S B L \_ ( p + 2 \cdot ( K - 1 ) + K \cdot L ) B, ( p + 2 \cdot ( K - 1 ) + K \cdot L + 1 ) A$

の何れかで表される CS バスラインの組を電気的に等価にすれば良いことがわかる。但し p は  $p = 1, 3, 5, \dots$  もしくは  $p = 0, 2, 4, \dots$  である。

10

#### 【 0 2 0 9 】

尚、図 2 4 によれば、このときの CS バスラインに印加される振動電圧の振動周期は 2 0 H、即ち水平走査期間の  $2 \cdot K \cdot L$  倍となっていることがわかる。

#### 【 0 2 1 0 】

[  $K = 1, L = 12$  、 振動の周期 : 2 4 H ]