(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-18066

(P2005-18066A)

(43) 公開日 平成17年1月20日(2005.1.20)

(51) Int.Cl.<sup>7</sup>**G09G 3/36**

**G02F 1/133**

**G09G 3/20**

F 1

G09G 3/36

G02F 1/133 550

G09G 3/20 612K

G09G 3/20 621B

G09G 3/20 621M

テーマコード(参考)

2H093

5C006

5C080

審査請求 未請求 請求項の数 15 O L (全 13 頁) 最終頁に続く

|              |                              |           |                                                                                   |

|--------------|------------------------------|-----------|-----------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2004-184686 (P2004-184686) | (71) 出願人  | 390019839<br>三星電子株式会社<br>大韓民国京畿道水原市靈通区梅灘洞 416                                     |

| (22) 出願日     | 平成16年6月23日 (2004.6.23)       | (74) 代理人  | 100094145<br>弁理士 小野 由己男                                                           |

| (31) 優先権主張番号 | 2003-040684                  | (74) 代理人  | 100106367<br>弁理士 稲積 朋子                                                            |

| (32) 優先日     | 平成15年6月23日 (2003.6.23)       | (72) 発明者  | 文 勝 煥<br>大韓民国京畿道龍仁市水枝邑上▲ヒョン▼<br>里現代アイパーク6次アパート205棟1<br>504号                       |

| (33) 優先権主張国  | 韓国 (KR)                      | F ターム(参考) | 2H093 NA16 NA43 NA47 NB14 NB16<br>NC10 NC12 NC22 NC34 NC49<br>ND49 ND50 ND54 NH14 |

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその駆動方法

## (57) 【要約】

【課題】 データ駆動ICの個数を減らし、コストを節減する。

【解決手段】 スイッチング素子を含む画素、スイッチング素子に連結され、奇数番目のゲート線及び偶数番目のゲート線が一対をなして第1ゲートオン信号及び第2ゲートオン信号を各々伝達するゲート線、スイッチング素子に連結され、データ電圧を伝達するデータ線を含む。スイッチング素子のうち、同一なデータ線の両側に各々連結されている第1スイッチング素子及び第2スイッチング素子は、奇数番目のゲート線及び偶数番目のゲート線に各々連結されている。映像データは、奇数番目のデータと偶数番目のデータとに分離された後、一定の時間の間隔で出力される。第1ゲートオン信号は第1スイッチング素子に印加され、第2ゲートオン信号は第2スイッチング素子に印加される。第1ゲートオン信号及び第2ゲートオン信号が所定の時間の間重複する。

【選択図】 図5

## 【特許請求の範囲】

## 【請求項 1】

行列状に配列されている複数のスイッチング素子を含む画素と、前記スイッチング素子に連結され、奇数番目のゲート線と偶数番目のゲート線とが一対をなして第1ゲートオン信号及び第2ゲートオン信号を各々伝達する複数のゲート線と、前記スイッチング素子に連結され、データ電圧を伝達する複数のデータ線と、外部から映像データを受信して二つのグループに分離した後、一定の時間の間隔で出力する信号制御部と、

前記第1ゲートオン信号を前記第1スイッチング素子に印加する第1ゲート駆動部と、前記第2ゲートオン信号を前記第2スイッチング素子に印加する第2ゲート駆動部と、を含むゲート駆動部と、

前記データ線にデータ電圧を印加するデータ駆動部と、を含み、

前記スイッチング素子は、同一のデータ線の両側に各々連結されている第1スイッチング素子及び第2スイッチング素子を含み、

前記第1スイッチング素子及び第2スイッチング素子は、前記奇数番目のゲート線及び偶数番目のゲート線に各々連結されている液晶表示装置。

## 【請求項 2】

前記信号制御部は、前記映像データを、奇数番目のゲート線に連結されたスイッチング素子へのデータと偶数番目のゲート線に連結されたスイッチング素子へのデータとに分離する、請求項1に記載の液晶表示装置。

## 【請求項 3】

前記第1ゲートオン信号及び第2ゲートオン信号は所定の時間の間重畳する、請求項1に記載の液晶表示装置。

## 【請求項 4】

前記所定の時間は一水平周期1Hの半周期である、請求項3に記載の液晶表示装置。

## 【請求項 5】

前記信号制御部は、各々複数の信号からなる第1制御信号群及び第2制御信号群を含む制御信号を生成し、

前記第1制御信号群は前記第1ゲート駆動部に印加され、次いで1/2Hが経過した後、前記第2制御信号群が前記第2ゲート駆動部に印加される、請求項4に記載の液晶表示装置。

## 【請求項 6】

前記第1制御信号群及び第2制御信号群は、各々垂直同期開始信号STV及び複数のクロック信号を含む、請求項5に記載の液晶表示装置。

## 【請求項 7】

前記複数のクロック信号は、第1クロック信号及び第2クロック信号を含み、

前記第1クロック信号及び第2クロック信号の周期は2Hで、位相が互いに反対である、請求項6に記載の液晶表示装置。

## 【請求項 8】

前記スイッチング素子は非晶質シリコンからなる、請求項1に記載の液晶表示装置。

## 【請求項 9】

前記第1ゲート駆動部及び第2ゲート駆動部は、前記スイッチング素子と同一な基板上に形成される、請求項8に記載の液晶表示装置。

## 【請求項 10】

前記第1ゲート駆動部及び第2ゲート駆動部は、前記スイッチング素子が形成される時に同時に形成される、請求項8に記載の液晶表示装置。

## 【請求項 11】

前記第1スイッチング素子及び第2スイッチング素子に印加される前記データ電圧の極性は互いに反対である、請求項1に記載の液晶表示装置。

## 【請求項 12】

10

20

30

40

50

前記画素は、行列状に配列される赤色、緑色、及び青色画素を含み、同一な列に属する同一な色相の画素に含まれるスイッチング素子は、同一なゲート駆動部に連結される、請求項1に記載の液晶表示装置。

### 【請求項 1 3】

ゲート駆動部、データ電圧を伝達する複数のデータ線及び前記データ線に連結されたスイッチング素子を含む液晶表示装置の駆動方法であって、

前記ゲート駆動部は、第1ゲートオン信号を伝達する奇数番目のゲート線に連結された第1ゲート駆動部及び第2ゲートオン信号を伝達する偶数番目のゲート線に連結された第2ゲート駆動部を含んでおり、

前記スイッチング素子は、前記データ線の両側に各々位置する複数の第1スイッチング素子及び第2スイッチング素子を含んでいる場合に、 10

制御信号及び複数のクロック信号を、各々前記第1ゲート駆動部にまず印加し、一水平周期(1H)の半周期後に前記第2ゲート駆動部に印加する段階と、

前記第1ゲートオン信号を前記第1スイッチング素子に供給し、一水平周期の半周期後に前記第2ゲートオン信号を前記第2スイッチング素子に供給する段階と、

該当するデータ電圧を前記第1スイッチング素子及び第2スイッチング素子に各々印加する段階と、

前記第1ゲートオン信号及び第2ゲートオン信号を、各々一水平周期の間印加する段階と、

## を含む液晶表示装置の駆動方法。

### 【請求項 14】

前記第1ゲートオン信号及び第2ゲートオン信号は所定の時間の間重畠する、請求項13に記載の液晶表示装置の駆動方法。

### 【請求項15】

前記所定の時間は一水平周期の半周期である、請求項 1 4 に記載の液晶表示装置の駆動方法。

## 【発明の詳細な説明】

## 【技術分野】

【 0 0 0 1 】

本発明は、液晶表示装置及びその駆動方法に関する。

## 【背景技术】

【 0 0 0 2 】

一般的に、液晶表示装置は、二つの表示板及びその間に充填されている誘電率異方性を有する液晶層を含む。液晶層に電場を印加し、この電場の強さを調節して液晶層を通過する光の透過率を調節することによって、所望の画像を得る。このような液晶表示装置は、携帯が便利な平板表示装置（F P D）の代表的なものであり、その中でも、薄膜トランジスタ（T F T）をスイッチング素子として利用したT F T - L C Dが主に利用されている。

【 0 0 0 3 】

TFT-LCDは、行列状に配列されているスイッチング素子を含む複数の画素を含む。各画素は、スイッチング素子を通じて映像信号に該当するデータ電圧を選択的に受け入れる。TFT-LCDはまた、スイッチング素子に連結された複数のゲート線及び複数のデータ線を含み、各ゲート線は、スイッチング素子を各々ターンオンさせるゲートオン電圧を伝達し、各データ線は、ターンオンされたスイッチング素子を通じて各画素にデータ電圧を伝達する。

〔 0 0 0 4 〕

このような T F T - L C D は、ゲート線にゲートオン電圧を印加するゲート駆動部、デ

一タ線に画像信号を印加するデータ駆動部、及びこれらを制御する信号制御部を含む。

【0005】

ゲート駆動部は、信号制御部からの垂直同期開始信号によってゲートオン電圧の出力を開始し、一列に配列されたゲート線に順にゲートオン電圧を印加する。

【0006】

一方、このようなTFT-LCDにおいて、TFTの材料としては非晶質または多結晶シリコンが用いられている。

【0007】

多結晶シリコンTFT-LCDは、電子移動度が高いため、駆動部をガラス基板に容易に集積することができるが、非晶質シリコン(a-Si)TFT-LCDは、電子移動度が低いため、液晶表示板組立体には画素だけを備え、駆動ICを別途に製作してガラス基板上に搭載して用いる。

10

【0008】

例えば、XGA級の解像度を実現しようとする場合、 $1024 \times 3 \times 768$ 個のサブ画素を駆動しなければならないので、384チャンネルのデータ駆動ICを8個及び256チャンネルのゲート駆動ICを3個を用いたり、384チャンネルのデータ駆動ICを4個及び256チャンネルのゲート駆動ICを6個を用いることができる。ここで、後者の場合、ゲート線のピッチがデータ線のピッチの約3倍であるので、ゲート駆動部を構成するゲート駆動ICを一側にだけ搭載することができず、両側に搭載して駆動するデュアルバンク駆動を実施する。

20

【0009】

ここで、デュアルバンク駆動の場合、シングルバンク駆動と比べて、ゲート線が2倍に増加し、その分ゲート駆動部を構成するシフトレジスタのシフト速度も2倍にしなければならない問題点がある。特に、非晶質シリコンTFTにゲート駆動部を集積する場合は、より大きな問題となる。

【発明の開示】

【発明が解決しようとする課題】

【0010】

本発明が目的とする技術的課題は、前記のような問題点を解決すると同時に、データ駆動ICの個数を減らして、コストを節減することができる方法を提供することにある。

30

【課題を解決するための手段】

【0011】

前記のような技術的課題を達成するための本発明の一実施例による液晶表示装置は、行列状に配列されている複数のスイッチング素子を含む画素、複数のゲート線、及びデータ線を含む。前記複数のゲート線は、前記スイッチング素子に連結され、奇数番目のゲート線及び偶数番目のゲート線が一対をなして、第1ゲートオン信号及び第2ゲートオン信号を各々伝達する。前記データ線は、前記スイッチング素子に連結され、データ電圧を伝達する。ここで、前記スイッチング素子のうち、同一なデータ線の両側に各々連結されている第1スイッチング素子及び第2スイッチング素子は、前記奇数番目のゲート線及び偶数番目のゲート線に各々連結されている。また、信号制御部、ゲート駆動部、及びデータ駆動部をさらに含み、前記信号制御部は、外部から映像データを受信して二つのグループに分離した後、一定の時間の間隔で出力する。前記ゲート駆動部は、前記第1ゲートオン信号を前記第1スイッチング素子に印加する第1ゲート駆動部と、前記第2ゲートオン信号を前記第2スイッチング素子に印加する第2ゲート駆動部とを含む。前記データ駆動部は、前記データ線にデータ電圧を印加する。ここで、前記信号制御部は、前記映像データを奇数番目のデータ及び偶数番目のデータに分離することができる。

40

【0012】

また、前記第1ゲートオン信号及び第2ゲートオン信号は、所定の時間の間重畳するが、前記所定の時間は1Hの半周期であるのが好ましい。

【0013】

50

一方、前記信号制御部は、各々複数の信号からなる第1制御信号群及び第2制御信号群を含む制御信号を生成する。前記第1制御信号群は前記第1ゲート駆動部に印加され、次いで1/2Hが経過した後で、前記第2制御信号群が前記第2ゲート駆動部に印加されるのが好ましい。ここで、前記第1制御信号群及び第2制御信号群は、各々垂直同期開始信号STV及び複数のクロック信号を含み、前記複数のクロック信号は、第1クロック信号及び第2クロック信号を含む。前記第1クロック信号及び第2クロック信号の周期は2Hで、位相が互いに反対であるのが好ましい。

【0014】

前記スイッチング素子は非晶質シリコンからなることができ、前記第1ゲート駆動部及び第2ゲート駆動部は、前記スイッチング素子と同一な基板上に形成されるができる。また、前記スイッチング素子が形成される時に同時に形成されるのが好ましい。

【0015】

前記第1スイッチング素子及び第2スイッチング素子に印加される前記データ電圧の極性は互いに反対であるのが好ましい。

【0016】

前記画素は、行列状に配列される赤色、緑色、及び青色画素を含み、同一な列に属する同一な色相の画素に含まれるスイッチング素子は、同一なゲート駆動部に連結されるのが好ましい。

【0017】

本発明の他の実施例によれば、第1ゲートオン信号を伝達する奇数番目のゲート線及び第2ゲートオン信号を伝達する偶数番目のゲート線に各々連結された第1ゲート駆動部及び第2ゲート駆動部、データ電圧を伝達する複数のデータ線、前記データ線に連結され、両側に各々位置する複数の第1スイッチング素子及び第2スイッチング素子を含む液晶表示装置の駆動方法は、制御信号及び複数のクロック信号を各々前記第1ゲート駆動部にまず印加し、1水平周期(1H)の半周期後に前記第2ゲート駆動部に印加する段階、前記第1ゲートオン信号を前記第1スイッチング素子に供給し、1Hの半周期後に前記第2ゲートオン信号を前記第2スイッチング素子に供給する段階、そして該当するデータ電圧を前記第1スイッチング素子及び第2スイッチング素子に各々印加する段階を含み、前記第1ゲートオン信号及び第2ゲートオン信号は、各々1H期間の間印加される。この時、前記第1ゲートオン信号及び第2ゲートオン信号は所定の時間の間重複し、前記所定の時間は1Hの半周期であるのが好ましい。

【発明の効果】

【0018】

本発明によれば、ゲート駆動部400L、400Rは、1H期間の間にゲートオン電圧(Von)を印加し、データ駆動部500は、1Hの後半の1/2Hの間にデータ電圧を画素に印加するので、多結晶ゲート駆動ICに比べて相対的に遅いシフト速度を補完しながら、同一な速度でデータ電圧を画素に印加することができる。これにより、ゲート駆動部400L、400Rを画素のスイッチング素子であるTFTと同時に形成し、同一な基板上に集積することができる。その結果、空間的な負担を減らす一方で、データ駆動ICの数も半分に減らして、コストを節減することができる。

【発明を実施するための最良の形態】

【0019】

添付した図面を参考にして、本発明の実施例について、本発明の属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。

【0020】

図面は、各種の層及び領域を明確に表現するために厚さを拡大して示している。明細書全体を通じて類似した部分については同一な図面符号を付けている。層、膜、領域、板などの部分が他の部分の“上に”あるとする時、これは他の部分の“すぐ上に”ある場合に限らず、その中間に更に他の部分がある場合も含む。逆に、ある部分が他の部分の“すぐ上に”あるとする時、これは中間に他の部分がない場合を意味する。

10

20

30

40

50

## 【0021】

本発明の実施例による液晶表示装置について、図面を参照して詳細に説明する。

## 【0022】

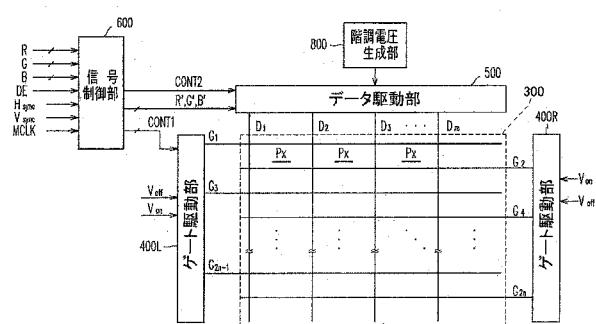

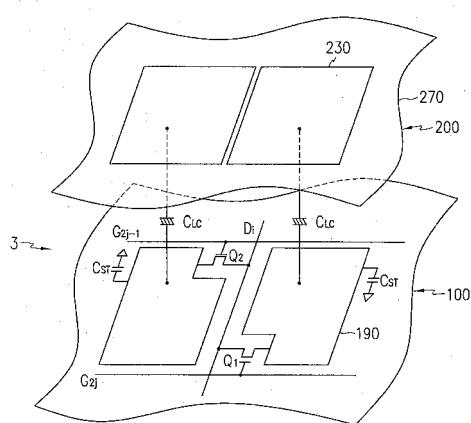

図1は、本発明の一実施例による液晶表示装置のブロック図であり、図2は、本発明の一実施例による液晶表示装置の二つの画素に対する等価回路図である。

## 【0023】

図1のよう、本発明の一実施例による液晶表示装置は、液晶表示板組立体300、前記液晶表示板組立体に連結されたゲート駆動部400L、400R、データ駆動部500、データ駆動部500に連結された階調電圧生成部800、そしてこれらを制御する信号制御部600を含む。

10

## 【0024】

液晶表示板組立体300は、等価回路として見れば、複数の表示信号線G1-G2n、D1-Dmと、これに連結され、ほぼ行列状に配列された複数の画素Pxとを含む。

## 【0025】

表示信号線G1-G2n、D1-Dmは、ゲート信号（走査信号ともいう。）を伝達する複数のゲート線G1-G2nと、データ信号を伝達するデータ信号線またはデータ線D1-Dmとを含む。ゲート線G1-G2nは、ほぼ行方向にのびて、互いにほぼ平行であり、データ線D1-Dmは、ほぼ列方向にのびて、互いにほぼ平行である。

## 【0026】

各画素は、表示信号線G1-G2n、D1-Dmに連結されたスイッチング素子Q1、Q2と、これに連結された液晶蓄電器CLC及び維持蓄電器CSTとを含む。維持蓄電器は、必要に応じて省略することができる。

20

## 【0027】

スイッチング素子Q1、Q2は、下部表示板100に備えられており、非晶質シリコンからなる3端子素子である。スイッチング素子Q1、Q2の制御端子及び入力端子は、各々ゲート線G1-G2n及びデータ線D1-Dmに連結され、出力端子は、液晶蓄電器CLC及び維持蓄電器CSTに連結されている。また、スイッチング素子Q1、Q2は、一つのデータ線D1-Dmに対して左側及び右側に連結されている。さらに、スイッチング素子Q1、Q2は、奇数番目のゲート線G1、G3・・・G2n-1及び偶数番目のゲート線G2、G4・・・G2nに各々連結されている。

30

## 【0028】

液晶蓄電器CLCは、下部表示板100の画素電極190及び上部表示板200の共通電極270を二つの端子とする。二つの電極190、270の間の液晶層3は誘電体として機能する。画素電極190は、スイッチング素子Q1に連結されている。共通電極270は、上部表示板200の全面に形成され、共通電圧Vcomが印加される。図2とは異なって、共通電極270が下部表示板100に備えられることもあり、この時には、二つの電極190、270が全て線形または棒形に形成される。

## 【0029】

維持蓄電器CSTは、下部表示板100に備えられた別個の信号線（図示せず）と画素電極190とが重なって形成され、この別個の信号線には、共通電圧Vcomなどの定められた電圧が印加される。しかし、維持蓄電器CSTは、画素電極190が絶縁体を媒介としてすぐ上の前段ゲート線と重なって形成されることもできる。

40

## 【0030】

一方、色の表示を実現するためには、各画素が色相を表示しなければならないが、これは、画素電極190に対応する領域に赤色、緑色、または青色の色フィルター230を備えることによって可能となる。図2で、色フィルター230は、上部表示板200の該当領域に形成されているが、これとは異なって、下部表示板100の画素電極190上または下に形成することもできる。

## 【0031】

液晶表示板組立体300の二つの表示板100、200のうちの少なくとも一つの外側

50

面には、光を偏光させる偏光子（図示せず）が付着されている。

【0032】

階調電圧生成部800は、画素の透過率に関連する二組の階調電圧を生成する。二組のうちの一組は、共通電圧Vcomに対してプラス値を有し、もう一組は、マイナス値を有する。

【0033】

ゲート駆動部400L、400Rは、液晶表示板組立体300の左側及び右側に配置され、奇数番目のゲート線G1、G3…G2n-1及び偶数番目のゲート線G2、G4…G2nに各々連結されており、外部からのゲートオン電圧(Von)とゲートオフ電圧(Voff)との組み合わせからなるゲート信号をゲート線G1-G2nに印加する。ゲート駆動部400L、400Rは、スイッチング素子と同じ基板上に、すなわち下部表示板100上に形成されている。

【0034】

データ駆動部500は、液晶表示板組立体300のデータ線D1-Dmに連結されて、階調電圧生成部800からの階調電圧を選択してデータ信号として画素に印加する、通常複数の集積回路からなる。

【0035】

信号制御部600は、ゲート駆動部400L、400R及びデータ駆動部500などの動作を制御する制御信号を生成して、各々該当する制御信号をゲート駆動部400L、400R及びデータ駆動部500に提供する。

【0036】

以下、このような液晶表示装置の表示動作について、さらに詳細に説明する。

【0037】

信号制御部600は、外部のグラフィック制御器（図示せず）からRGB映像信号(R、G、B)及びその表示を制御する入力制御信号、例えば垂直同期信号(Vsync)と水平同期信号(Hsync)、メインクロック(MCLK)、データタイネーブル信号(DE)などの提供を受ける。信号制御部600は、入力制御信号に基づいてゲート制御信号(CONT1)及びデータ制御信号(CONT2)などを生成し、映像信号(R、G、B)を液晶表示板組立体300の動作条件に合うように適切に処理した後、ゲート制御信号(CONT1)をゲート駆動部400L、400Rに送り出し、データ制御信号(CONT2)及び処理した映像信号(R'、G'、B')をデータ駆動部500に送り出す。

【0038】

ゲート制御信号(CONT1)は、ゲートオンパルス(ゲートオン電圧の区間)の出力開始を指示する垂直同期開始信号(STV)、ゲートオンパルスの出力時期を制御するゲートクロック信号(CPV)、及びゲートオンパルスの幅を限定する出力イネーブル信号(OE)などを含む。

【0039】

データ制御信号(CONT2)は、映像データ(R'、G'、B')の入力開始を指示する水平同期開始信号(STH)、データ線D1-Dmに該当データ電圧の印加を指示するロード信号(LOAD)、共通電圧Vcomに対するデータ電圧の極性(以下、“共通電圧に対するデータ電圧の極性”を略して“データ電圧の極性”という)を反転させる反転信号(RVS)、及びデータクロック信号(HCLK)などを含む。

【0040】

データ駆動部500は、信号制御部600からのデータ制御信号(CONT2)に応じて、一つの行の画素に対応する映像データ(R'、G'、B')を順に受信し、階調電圧生成部800からの階調電圧のうちの各映像データ(R'、G'、B')に対応する階調電圧を選択することにより、映像データ(R'、G'、B')を該当データ電圧に変換する。

【0041】

ゲート駆動部400L、400Rは、信号制御部600からのゲート制御信号(CONT1)に応じて、ゲートオン電圧(Von)をゲート線G1-G2nに印加し、このゲート線G1-G2n

10

20

30

40

50

に連結されたスイッチング素子Q1、Q2をターンオンさせる。

【0042】

一つのゲート線G1-G2nにゲートオン電圧(Von)が印加され、これに連結された一つの行のスイッチング素子Q1、Q2がターンオンされている間、データ駆動部500は、各データ電圧を該当データ線D1-Dmに供給する。データ線D1-Dmに供給されたデータ電圧は、ターンオンされたスイッチング素子Q1、Q2を通じて該当画素に印加される。ここで、一般に、一つの行のスイッチング素子がターンオンされている期間を“1H”または“一水平周期”というが、本発明による実施例は、ゲート線の個数が通常の2倍のデュアルバンク駆動であるので、ゲートオン電圧(Von)が印加される時間は1/2Hでなければならない。しかし、本発明の一実施例では、一つの行に印加される時間は1Hであるが隣接する行に印加されるゲートオン電圧(Von)が1/2Hの分重畠するようにして、全体的にシングルバンク駆動と同一な速度を有する。これについては後ほど詳細に説明する。

【0043】

このような方式で、1フレーム期間の間に全てのゲート線G1-G2nに対して順にゲートオン電圧(Von)を印加して、全ての画素にデータ電圧を印加する。1フレームが終了すれば、次のフレームが始まり、各画素に印加されるデータ電圧の極性が直前のフレームでの極性と反対になるように、データ駆動部500に印加される反転信号(RVS)の状態が制御される(フレーム反転)。この時、1フレーム期間内でも、反転信号(RVS)の特性に応じて、一つのデータ線を通じて流れるデータ電圧の極性が変わったり(ライン反転)、一つの画素行に印加されるデータ電圧の極性が互いに異なることができる(ドット反転)。

【0044】

以下、本発明の一実施例によるゲート駆動部の構造及び動作について、図3乃至図5を参照してより詳細に説明する。

【0045】

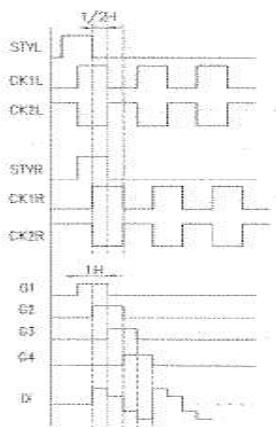

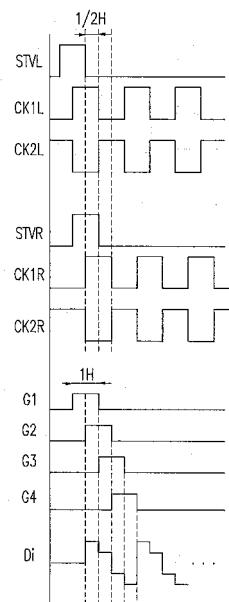

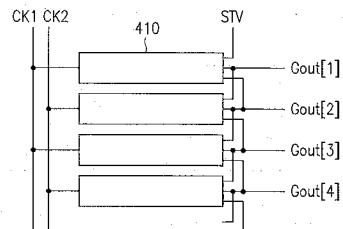

図3aは、本発明の一実施例によるゲート駆動部のブロック図であり、図3bは、図3aに示したシフトレジスタの等価回路図であり、図3に示したゲート駆動部の動作を説明するための信号波形図である。

【0046】

図3aのように、ゲート駆動部400L、400Rは、一列に配列された複数のシフトレジスタ410を含む。

【0047】

ここで、シフトレジスタ410は、画素のスイッチング素子が形成される時に同時に形成され、同一な基板上に集積することができる。即ち、別途のゲート駆動ICを備えて基板に搭載して用いるのではなく、液晶表示板組立体300を形成する時にゲート駆動部400L、400Rとスイッチング素子とを同時に形成することができる。

【0048】

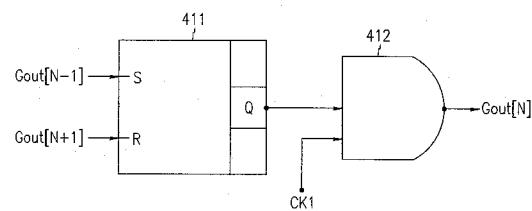

シフトレジスタ410は、図3bのように、SRラッチ411及びANDゲート412で等価回路的に示すことができる。

【0049】

ゲート駆動部400L、400Rは、信号制御部600からの垂直同期開始信号(STV)に応じて、ゲートオン電圧(Von)の出力を開始して、一列に配列されたゲート線G1-G2nに順にゲートオン電圧(Von)を印加する。

【0050】

第1のシフトレジスタ410は、垂直同期開始信号(STV)及びクロック信号(CK1)に同期してゲートオン電圧(Von)の出力を開始し、第2のシフトレジスタからは、前段のシフトレジスタの出力電圧及びクロック信号(CK1)に同期してゲートオン電圧(Von)の出力を開始する。このようなシフトレジスタ410の動作をより詳細に検討する。

【0051】

SRラッチ411は、前段ゲート出力[Gout(N-1)]、つまり前段シフトレジスタの出

10

20

40

50

力が入力されるセット入力端子 (S) と、後段ゲート出力 [Gout (N+1)]、つまり後段シフトレジスタの出力が入力されるリセット入力端子 (R) とを有している。AND ゲート 412 は、SR ラッチ 411 の出力及びクロック信号 (CK1) を二つの入力としてゲート信号を生成して出力する。

【0052】

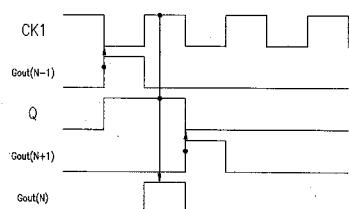

図 4 は、シフトレジスタ 410 の動作を示す説明図である。セット端子 (S) に入力される前段ゲート出力 [Gout (N-1)] 及びリセット端子 (R) に入力される後段ゲート出力 [Gout (N+1)] が、全てロー (“0”) である初期状態では、SR ラッチ 411 の出力もローである。後段ゲート出力 [Gout (N+1)] がローを維持する間に前段ゲート出力 [Gout (N-1)] がハイ (“1”) に変われば、SR ラッチ 411 の出力 (Q) がハイに変わる。後段ゲート出力 [Gout (N+1)] がローを維持する間に前段ゲート出力 [Gout (N-1)] が再びローに変わっても、SR ラッチ 411 の出力は変化しない。前段ゲート出力 [Gout (N-1)] がローを維持する間に後段ゲート出力 [Gout (N+1)] がハイに変われば、SR ラッチ 411 の出力 (Q) はハイからローに変わる。SR ラッチ 411 の出力 (Q) は、前段ゲート出力 [Gout (N-1)] がローからハイに変わる時点から後段ゲート出力 [Gout (N+1)] がローからハイに変わる時点までハイを維持し、その時以外はローとなる。

【0053】

AND ゲート 412 は、SR ラッチ 411 の出力 (Q) 及びクロック信号 (CK1) が両方ハイである時にのみハイのゲート出力 [Gout (N)] を生成する。詳しくは、ゲート出力 [Gout (N)] は、SR ラッチ 411 の出力 (Q) がハイの間にクロック信号 (CK1) がローからハイに変わる時にハイとなり、クロック信号 (CK1) がローになったり、SR ラッチ 411 の出力 (Q) がローになれば、ローに変わる。

【0054】

このような方式で、各シフトレジスタ 410 は、前段ゲート出力 [Gout (N-1)] 及び後段ゲート出力 [Gout (N+1)] に基づいて、そして、クロック信号 (CK1, CK2) に同期して、ゲート出力 [Gout (N)] を生成する。隣接したシフトレジスタ 410 は、互いに異なるクロック信号 (CK1, CK2) を受信するが、二つのクロック信号 (CK1, CK2) は、位相が反対で、2H の周期を有する。各クロック信号 (CK1, CK2) は、画素のスイッチング素子を駆動することができるよう、ハイの場合にはゲートオン電圧 (Von) であり、ローの場合にはゲートオフ電圧 (Voff) である。

【0055】

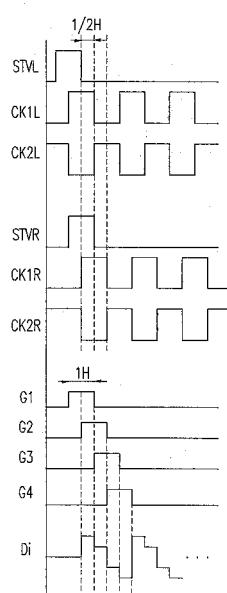

図 5 は、本発明の一実施例による信号の波形図である。

【0056】

図 5 には、左側及び右側のゲート駆動部 400L, 400R に印加される垂直同期開始信号 (STVL, STVR) 及びクロック信号 (CK1L, CK2L, CK2R, CK2R) の波形と共に、ゲート信号及びデータ電圧信号を示した。

【0057】

信号制御部 600 は、まず左側ゲート駆動部 400L に垂直同期開始信号 (STVL) を印加し、次いで 1/2H が経過した後、右側ゲート駆動部 400R に垂直同期開始信号 (STVR) を印加する。これと同時に、左側ゲート駆動部 400L にクロック信号 (CK1L, CK2L) を入力し、再び 1/2H が経過した後、右側ゲート駆動部 400R にクロック信号 (CK1R, CK2R) を入力する。即ち、垂直同期開始信号 (STVL, STVR) 及びクロック信号 (CK1L, CK2L, CK1R, CK2R) 毎に 1/2H の間隔を置いて印加すれば、二つのゲート駆動部 400L, 400R は、1/2H の間隔で動作する。以下、各ゲート信号のハイ区間の長さは 1H になり、隣接するゲート信号は 1/2H の間重複する。左側ゲート駆動部 400L に連結された奇数番目のゲート線 (G1, G3) を見れば、信号の間隔が 1H であることが分かり、偶数番目のゲート線 (G2, G4) についても同一である。

【0058】

一方、データ駆動部 500 は、データ線 (Di) の左右に連結された画素にデータ電圧を印加するが、一つの画素に電圧を印加する時間は 1/2H である。つまり、ゲートオン電

10

20

30

40

50

圧 (Von) は 1 H 期間の間印加され、1 H の後半の 1 / 2 H の間のみデータ電圧が画素に印加されるので、左右の画素に印加される全ての時間は 1 H となる。

【0059】

ゲートオン電圧 (Von) をスイッチング素子 Q1 に供給して 1 / 2 H 後に、ゲートオン電圧 (Von) をスイッチング素子 Q2 に供給するので、ゲートオン電圧 (Von) が重畠するよう印加される。これにより、ターンオンされたスイッチング素子を通じて意図しなかった画素にデータ電圧が印加されることがある。例えば、第 1 ゲートオン電圧と第 2 ゲートオン電圧とが 1 / 2 H の間重畠するので、2 つのスイッチング素子 Q1、Q2 が同時にターンオンされ、スイッチング素子 (Q2) を通じてデータ電圧が印加される一方、スイッチング素子 Q1 を通じてもデータ電圧が印加される。しかし、前記のように、シフトレジスタ 410 のシフト速度が遅く、スイッチング素子 Q1 を十分にターンオンさせていない状態であるので、少しのデータ電圧だけが印加される。そして、スイッチング素子 Q1 が十分にターンオンされた後に印加されるデータ電圧により、直前に印加された少しのデータ電圧は無視され、もともと印加しようとしたデータ電圧で画素を充電することができる。

【0060】

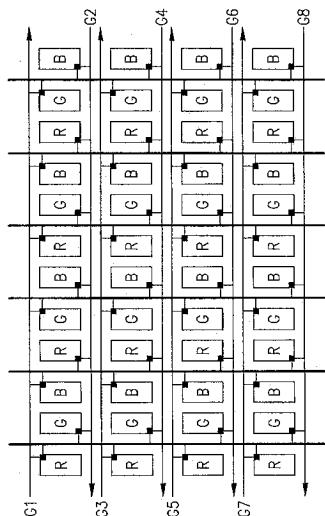

図 6 は、本発明の一実施例による画素の配置図である。

【0061】

図 6 のように、同一な色相の画素は、同一なゲート駆動部 400L、400R に連結されている。例えば、第 1 列の赤色画素 (R) は全て左側ゲート駆動部 400L に連結されており、第 2 列の緑色画素 (G) は全て右側ゲート駆動部 400R に連結されている。このよう 20 にすれば、上下に配列された同一な色相の画素は、同一なゲート駆動部 400L、400R に連結されるので、ゲート信号の遅延による表示歪曲現象を最少化することができる。

【0062】

一方、一つのデータ線 D1 - Dm に 2 つの画素が連結されているので、信号制御部 600 は、一つの画素行に該当するデータをラインメモリに記憶させた後、奇数番目のゲート線 (G1、G3 ...) に連結された画素のデータと、偶数番目のゲート線 (G2、G4 ...) に連結された画素のデータとに分けて、データ駆動部 500 に供給する。データ駆動部 500 は、ゲート線 G1 - G2n に 1 H 期間の間ゲートオン電圧 (Von) が印加されれば、ターンオンされたスイッチング素子を通じて該当する画素に 1 / 2 H 期間の間データ電圧を印加する。

【0063】

また、データ駆動部 500 は、一つのデータ線 D1 - Dm に連結された左右の画素に互いに反対の極性を有するデータ電圧を印加してドット反転を行う。このような方式で、データ線を左右の画素が共有する一方、高画質を実現することができるドット反転を行い、出力バッファー (図示せず) を共有することにより、データ駆動 IC のコストを節減することができる。

【0064】

つまり、従来のデュアルバンク駆動の場合、ゲート駆動 IC を基板の左右に搭載して用いたため、液晶表示板組立体 300 のサイズが大きくなかった。ところが、前記した駆動方式による本発明では、ゲート駆動部 400L、400R を構成するシフトレジスタ 401 をスイッチング素子を形成する時に同時に形成することにより、液晶表示板組立体 300 のサイズが大きくなるのを防止すると共に、データ駆動 IC の個数を減らすことができるの 40 で、コストの節減を実現することができる。以上のように、非晶質シリコンは多結晶シリコンに比べて相対的に電子移動度が遅いことを考慮することにより、ゲート駆動部を液晶表示板組立体に集積することができる。

【0065】

以上、本発明の好ましい実施例について詳細に説明したが、本発明の権利範囲はこれに限定されず、本請求の範囲で定義している本発明の基本概念を利用した当業者の様々な変形及び改良形態も本発明の権利範囲に属するものである。

【図面の簡単な説明】

10

20

30

40

50

## 【0066】

【図1】本発明の一実施例による液晶表示装置のブロック図である。

【図2】本発明の一実施例による液晶表示装置の一つの画素に対する等価回路図である。

【図3a】本発明の一実施例によるゲート駆動部のブロック図である。

【図3b】図3aに示したシフトレジスタの等価回路図である。

【図4】図3に示したゲート駆動部の動作を説明する波形図である。

【図5】本発明の一実施例による信号の波形図である。

【図6】本発明の一実施例による液晶表示装置の画素の配置図である。

## 【符号の説明】

## 【0067】

1000、200 表示板

190 画素電極

270 共通電極

300 液晶表示板組立体

400L、400R ゲート駆動部

500 データ駆動部

600 信号制御部

800 階調電圧生成部

10

【図1】

【図2】

【図3a】

【図3 b】

【図4】

【図5】

【図6】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

G 0 9 G 3/20 6 2 2 D

G 0 9 G 3/20 6 2 3 U

G 0 9 G 3/20 6 2 4 B

F ターム(参考) 5C006 AC11 AC24 AC26 AF71 BB16 BB21 BC03 BC06 BC16 BC20

BF03 FA43 FA51

5C080 AA10 BB05 DD22 FF07 FF11 JJ02 JJ04

【要約の続き】

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2005018066A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2005-01-20 |

| 申请号            | JP2004184686                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 申请日     | 2004-06-23 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 文勝煥                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 文勝煥                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G02F1/133 G02F1/1362 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| CPC分类号         | G02F1/136286 G09G3/3614 G09G3/3648 G09G3/3677 G09G3/3688 G09G2300/0408 G09G2300/0426 G09G2300/08 G09G2310/0205 G09G2310/0251 G09G2310/0281 G09G2310/0297 G09G3/3696                                                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.612.K G09G3/20.621.B G09G3/20.621.M G09G3/20.622.D G09G3/20.623.U G09G3/20.624.B G11C19/00 G11C19/00.J                                                                                                                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA43 2H093/NA47 2H093/NB14 2H093/NB16 2H093/NC10 2H093/NC12 2H093/NC22 2H093/NC34 2H093/NC49 2H093/ND49 2H093/ND50 2H093/ND54 2H093/NH14 5C006/AC11 5C006/AC24 5C006/AC26 5C006/AF71 5C006/BB16 5C006/BB21 5C006/BC03 5C006/BC06 5C006/BC16 5C006/BC20 5C006/BF03 5C006/FA43 5C006/FA51 5C080/AA10 5C080/BB05 5C080/DD22 5C080/FF07 5C080/FF11 5C080/JJ02 5C080/JJ04 2H193/ZA04 2H193/ZA08 2H193/ZC34 2H193/ZF22 2H193/ZF24 2H193/ZF36 2H193/ZF44 5B074/AA10 5B074/CA01 |         |            |

| 优先权            | 1020030040684 2003-06-23 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

### 摘要(译)

要解决的问题：通过减少数据驱动IC的数量来降低成本。一种像素，包括开关元件，连接到该开关元件的栅极线，一对奇数栅极线和偶数栅极线，并分别传输第一栅极导通信号和第二栅极导通信号。以及用于传输数据电压的数据线。在开关元件中，分别连接到同一数据线的两侧的第一开关元件和第二开关元件分别连接到奇数栅极线和偶数栅极线。视频数据被分成奇数数据和偶数数据，然后以规则的时间间隔输出。第一栅极导通信号被施加到第一开关元件，并且第二栅极导通信号被施加到第二开关元件。第一栅极导通信号和第二栅极导通信号彼此重叠预定时间。[选择图]图5