(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-271847

(P2004-271847A)

(43) 公開日 平成16年9月30日(2004.9.30)

(51) Int.Cl.<sup>7</sup>

**G02F** 1/1345

**G02F** 1/1368

**G09F** 9/00

**G09F** 9/30

**G09G** 3/20

F 1

G02F 1/1345

G02F 1/1368

G09F 9/00 352

G09F 9/30 330Z

G09G 3/20 612R

テーマコード(参考)

2H092

5C006

5C080

5C094

5G435

審査請求 未請求 請求項の数 9 O L (全 15 頁) 最終頁に続く

(21) 出願番号

特願2003-61778 (P2003-61778)

(22) 出願日

平成15年3月7日 (2003.3.7)

(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目2番3号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 將行

最終頁に続く

(54) 【発明の名称】画像表示装置

## (57) 【要約】

【課題】検査を低成本で正確に行なうことが可能な画像表示装置を提供する。

【解決手段】このLCDモジュールは、検査時に各N型TFT26およびデマルチブレクサ20を介して各奇数番の組のデータ線6に奇数データ信号DOを与えるための奇数データ端子36と、検査時に各N型TFT27およびデマルチブレクサ20を介して各偶数番の組のデータ線6に偶数データ信号DEを与えるための偶数データ端子35と、検査時にN型TFT26, 27のゲートに制御信号Cを与えるための制御端子34とを備える。したがって、検査時に使用する端子数が少なくてすみ、検査装置の低成本化を図ることができる。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

絶縁基板上に形成された画像表示装置であって、

複数行複数列に配置された複数の画素表示回路と、それぞれ前記複数行に対応して設けられた複数の走査線と、それぞれ前記複数列に対応して設けられた複数のデータ線とを含む画像表示パネル、

それらの第1の電極がそれぞれ前記複数のデータ線に接続され、前記画像表示パネルの通常動作時に非導通にされる複数のトランジスタ、

前記複数のトランジスタのうちの各奇数番のトランジスタの第2の電極に接続された第1の検査端子、10

前記複数のトランジスタのうちの各偶数番のトランジスタの第2の電極に接続された第2の検査端子、および

前記複数のトランジスタのゲートに接続され、前記画像表示パネルの検査時に前記複数のトランジスタを制御するための制御信号を受ける第1の制御端子を備える、画像表示装置。20

**【請求項 2】**

さらに、それぞれ前記複数のデータ線に対応して設けられ、各々が前記通常動作時に前記画素表示回路に画素を表示させるための画素電位を受ける複数のデータ端子を備え、

前記第1の検査端子、前記第2の検査端子および前記第1の制御端子の各々のサイズは、前記データ端子のサイズよりも大きい、請求項1に記載の画像表示装置。20

**【請求項 3】**

さらに、それぞれ前記複数のデータ線に対応して設けられ、各々が前記通常動作時に前記画素表示回路に画素を表示させるための画素電位を受ける複数のデータ端子を備え、前記複数のデータ端子は所定のピッチで配列され、

前記第1の検査端子、前記第2の検査端子および前記第1の制御端子は前記複数のデータ端子のピッチよりも大きなピッチで配列されている、請求項1または請求項2に記載の画像表示装置。

**【請求項 4】**

前記第1の検査端子、前記第2の検査端子および前記第1の制御端子の各々は、前記通常動作時に前記複数のトランジスタを非導通にする所定の電位を受ける、請求項1から請求項3のいずれかに記載の画像表示装置。30

**【請求項 5】**

前記第1の検査端子、前記第2の検査端子および第1の制御端子の各々は、前記検査後に半導体チップが実装される領域に配置され、前記通常動作時に実装された半導体チップから前記所定の電位を受ける、請求項4に記載の画像表示装置。

**【請求項 6】**

さらに、それぞれ前記第1の検査端子、前記第2の検査端子および前記第1の制御端子に接続され、各々が、前記検査後に半導体チップが実装される領域に配置され、前記通常動作時に実装された半導体チップから前記複数のトランジスタを非導通にする所定の電位を受ける3つのパッドを備える、請求項1から請求項3のいずれかに記載の画像表示装置。40

**【請求項 7】**

複数のモジュール領域が前記絶縁基板上に設けられ、

前記画像表示パネル、前記複数のトランジスタ、前記第1の検査端子、前記第2の検査端子および前記第1の制御端子は、各モジュール領域に形成され、

前記画像表示装置は、

さらに、前記複数のモジュール領域外に形成され、複数の前記第1の検査端子に接続された第1の共通端子、

前記複数のモジュール領域外に形成され、複数の前記第2の検査端子に接続された第2の共通端子、および

それぞれ複数の前記第1の制御端子に対応して設けられて前記複数のモジュール領域外に50

形成され、各々が前記検査時に制御信号を受けて対応の第1の制御端子に与える複数の第2の制御端子を備え、

各モジュール領域は、前記検査後に前記第1の共通端子、前記第2の共通端子および前記複数の第2の制御端子から切離される、請求項1に記載の画像表示装置。

#### 【請求項8】

複数のモジュール領域が前記絶縁基板上に設けられ、

前記画像表示パネルは各モジュール領域に形成され、

前記複数のトランジスタおよび前記第1の制御端子は、各画像表示パネルに対応して設けられて前記複数のモジュール領域外に形成され、

前記第1および第2の検査端子は、複数の前記画像表示パネルに共通に設けられて前記複数のモジュール領域外に形成され、10

各モジュール領域は、前記検査後に複数組の前記複数のトランジスタ、複数の前記第1の制御端子、前記第1の検査端子および前記第2の検査端子から切離される、請求項1に記載の画像表示装置。

#### 【請求項9】

前記画像表示パネルは、前記検査後に前記複数のトランジスタ、前記第1の検査端子、前記第2の検査端子および前記第1の制御端子から切離される、請求項1に記載の画像表示装置。20

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は画像表示装置に関し、特に、絶縁基板上に形成され、出荷前に検査される画像表示装置に関する。20

##### 【0002】

##### 【従来の技術】

近年、液晶パネルの高解像度化が進められ、LCD (liquid crystal display) モジュールとFPC (flexible printed circuit board) を接続するための端子の数が増加している。また、LCDモジュールの小型化が進められ、端子のピッチが狭くなっている。液晶パネルの検査は、各端子にプローブを当てて行なうが、端子数の増加および端子ピッチの狭小化にともない検査装置のコストアップが生じている。30

##### 【0003】

検査装置のコストダウンを図る方法としては、液晶パネルの奇数番のデータ線を1つの検査端子に接続するとともに、偶数番のデータ線をもう1つの検査端子に接続し、2つの検査端子を用いて検査した後に2つの端子を除去する方法がある（たとえば特許文献1参照）。

##### 【0004】

##### 【特許文献1】

特開平5-5897号公報

##### 【0005】

##### 【発明が解決しようとする課題】

このような2つの検査端子を複数の液晶パネルに共通に設ければ、さらに検査装置のコストダウンを図ることができるとも考えられる。しかし、単に複数の液晶パネルの奇数番のデータ線を1つの検査端子に接続するとともに偶数番のデータ線をもう1つの検査端子に接続しただけでは、各液晶パネルを個別に正確に検査することができない。

##### 【0006】

それゆえに、この発明の主たる目的は、検査を低コストで正確に行なうことが可能な画像表示装置を提供することである。

##### 【0007】

##### 【課題を解決するための手段】

10

20

30

40

50

この発明に係る画像表示装置は、絶縁基板上に形成された画像表示装置であって、複数行複数列に配置された複数の画素表示回路と、それぞれ複数行に対応して設けられた複数の走査線と、それぞれ複数列に対応して設けられた複数のデータ線とを含む画像表示パネルと、それらの第1の電極がそれぞれ複数のデータ線に接続され、画像表示パネルの通常動作時に非導通にされる複数のトランジスタと、複数のトランジスタのうちの各奇数番のトランジスタの第2の電極に接続された第1の検査端子と、複数のトランジスタのうちの各偶数番のトランジスタの第2の電極に接続された第2の検査端子と、複数のトランジスタのゲートに接続され、検査時に複数のトランジスタを制御するための制御信号を受ける第1の制御端子とを備えたものである。

【0008】

10

【発明の実施の形態】

【実施の形態1】

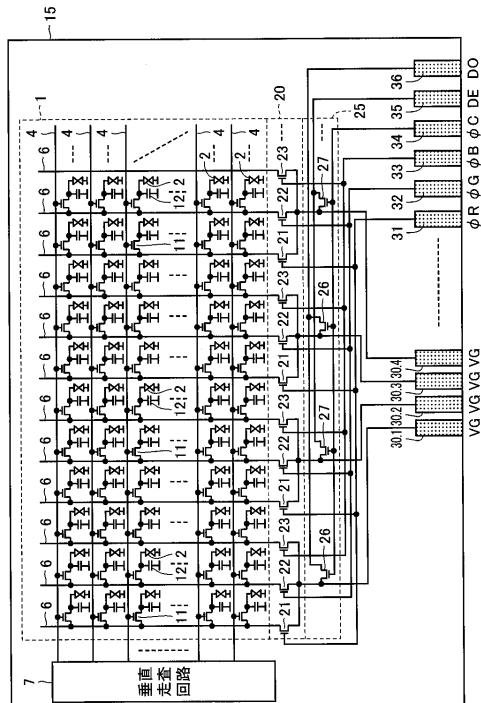

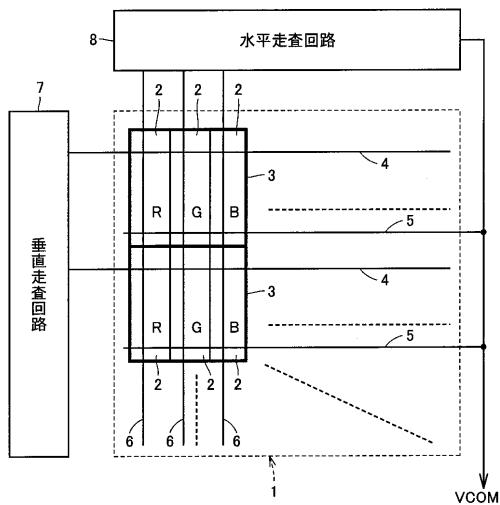

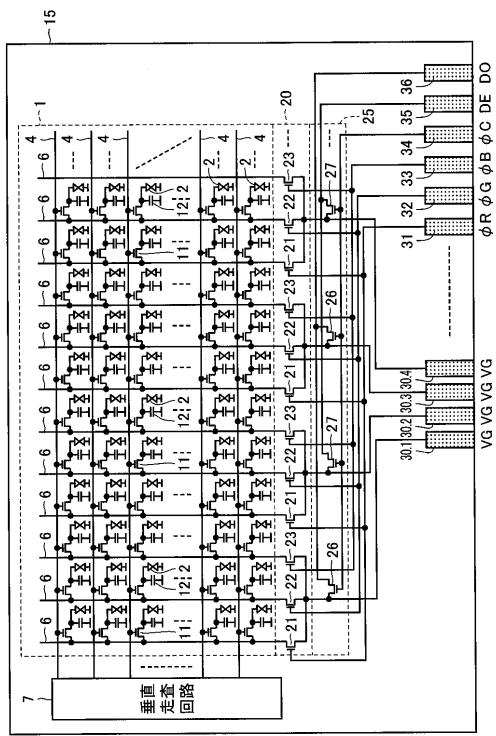

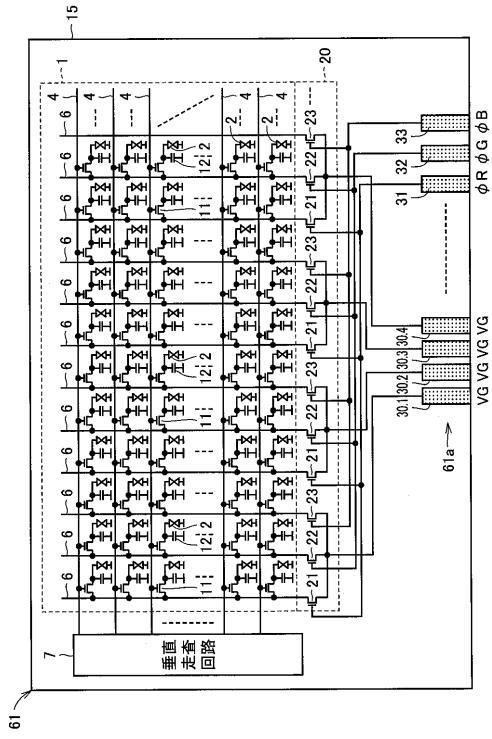

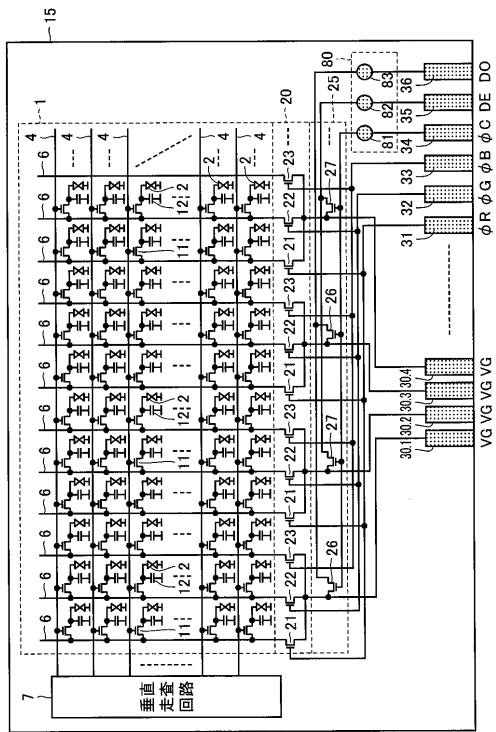

図1は、この発明の実施の形態1によるカラー液晶表示装置の構成を示すブロック図である。図1において、このカラー液晶表示装置は、液晶パネル1、垂直走査回路7および水平走査回路8を備え、たとえば携帯電話機に設けられる。

【0009】

20

液晶パネル1は、複数行複数列に配置された複数の液晶セル2と、それぞれ複数行に対応して設けられた複数の走査線4と、それぞれ複数行に対応して設けられた複数の共通電位線5と、それぞれ複数列に対応して設けられた複数のデータ線6とを含む。複数の共通電位線5は、互いに接続されている。

【0010】

液晶セル2は、各行において3つずつ予めグループ化されている。各グループの3つの液晶セル2には、それぞれR, G, Bのカラーフィルタが設けられている。各グループの3つの液晶セル2は、1つの画素3を構成している。

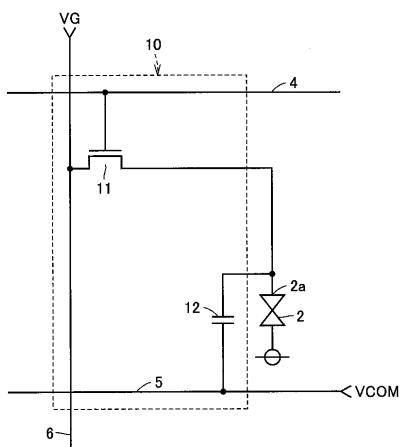

【0011】

30

各液晶セル2には、図2に示すように、液晶駆動回路10が設けられている。液晶駆動回路10は、N型TFT(薄膜トランジスタ)11およびキャパシタ12を含む。N型TFT11は、データ線6と液晶セル2の一方電極2aとの間に接続され、そのゲートは走査線4に接続される。キャパシタ12は、液晶セル2の一方電極2aと共通電位線5との間に接続される。共通電位線5には、共通電位VCOMが与えられる。液晶セル2の他方電極は、対向電極に接続される。対向電極には、一般には共通電位VCOMと同電位が与えられる。

【0012】

図1に戻って、垂直走査回路7は、画像信号に従って、複数の走査線4を所定時間ずつ順次選択し、選択した走査線4を選択レベルの「H」レベルにする。走査線4が選択レベルの「H」レベルにされると、図2のN型TFT11が導通し、その走査線4に対応する各液晶セル2の一方電極2aとその液晶セル2に対応するデータ線6とが結合される。

【0013】

40

水平走査回路8は、画像信号に従って、垂直走査回路7によって1本の走査線4が選択されている間に、各データ線6に階調電位VGを与えるとともに共通電位線5に共通電位VCOMを与える。液晶セル2の光透過率は、その電極間電圧に応じて変化する。

【0014】

垂直走査回路7および水平走査回路8によって液晶パネル1の全液晶セル2が走査されると、液晶パネル1に1つのカラー画像が表示される。

【0015】

50

図3は、図1および図2に示したカラー液晶表示装置の組立部品であるLCDモジュールの構成を示す回路ブロック図である。図3において、このLCDモジュールは、ガラス基板15と、その表面に形成された液晶パネル1、垂直走査回路7、1:3デマルチプレクサ20、検査用端子切換回路25、複数(たとえば240)のデータ端子30.1~30.4,...、R端子31、G端子32、B端子33、制御端子34、偶数データ端子35、

および奇数データ端子 3 6 を備える。

【 0 0 1 6 】

端子 3 0 . 1 ~ 3 0 . 4 , … , 3 1 ~ 3 6 は、ガラス基板 1 5 の 1 辺に沿って所定のピッチで配置される。検査時は、端子 3 1 ~ 3 6 の各々はプローブを介して検査装置に接続される。検査後は、端子 3 0 . 1 ~ 3 0 . 4 , … , 3 1 ~ 3 6 は F P C に接続される。データ端子 3 0 . 1 ~ 3 0 . 4 , … の各々には、F P C から階調電位 V G が与えられる。R 端子 3 1 には、R 用のデータ線 6 を選択するための信号 R が与えられる。G 端子 3 2 には、G 用のデータ線 6 を選択するための信号 G が与えられる。B 端子 3 3 には、B 用のデータ線 6 を選択するための信号 B が与えられる。制御端子 3 4 には、制御信号 C が与えられる。偶数データ端子 3 5 には、偶数データ信号 D E が与えられる。奇数データ端子 3 6 には、奇数データ信号 D O が与えられる。10

【 0 0 1 7 】

1 : 3 デマルチプレクサ 2 0 は、液晶パネル 1 の 2 4 0 組の R 用データ線 6 、 G 用データ線 6 および B 用データ線 6 に対応して設けられた 2 4 0 組の N 型 T F T 2 1 ~ 2 3 を含む。N 型 T F T 2 1 ~ 2 3 は、それぞれ対応の組の R 用データ線 6 、 G 用データ線 6 および B 用データ線 6 の一方端と対応のデータ端子（たとえば 3 0 . 1 ）との間に接続され、そのゲートはそれぞれ R 端子 3 1 、 G 端子 3 2 および B 端子 3 3 に接続される。10

【 0 0 1 8 】

信号 R , G , B のうちの信号 R が「 H 」レベルにされると、各 N 型 T F T 2 1 が導通し、各 R 用データ線 6 と対応のデータ端子とが結合される。信号 R , G , B のうちの信号 G が「 H 」レベルにされると、各 N 型 T F T 2 2 が導通し、各 G 用データ線 6 と対応のデータ端子とが結合される。信号 R , G , B のうちの信号 B が「 H 」レベルにされると、各 N 型 T F T 2 3 が導通し、各 B 用データ線 6 と対応のデータ端子とが結合される。20

【 0 0 1 9 】

検査用端子切換回路 2 5 は、2 4 0 組の R 用データ線 6 、 G 用データ線 6 および B 用データ線 6 のうちの各奇数番の組に対応して設けられた N 型 T F T 2 6 と、各偶数番の組に対応して設けられた N 型 T F T 2 7 とを含む。各 N 型 T F T 2 6 は、対応の N 型 T F T 2 1 ~ 2 3 のドレインと奇数データ線 3 6 との間に接続され、そのゲートは制御端子 3 4 に接続される。各 N 型 T F T 2 7 は、対応の N 型 T F T 2 1 ~ 2 3 のドレインと偶数データ端子 3 5 との間に接続され、そのゲートは制御端子 3 4 に接続される。30

【 0 0 2 0 】

制御信号 C が「 H 」レベルにされると、N 型 T F T 2 6 , 2 7 が導通し、奇数番目の組の N 型 T F T 2 1 ~ 2 3 のドレインと奇数データ端子 3 6 が接続されるとともに、偶数番目の組の N 型 T F T 2 1 ~ 2 3 のドレインと偶数データ端子 3 5 が接続される。

【 0 0 2 1 】

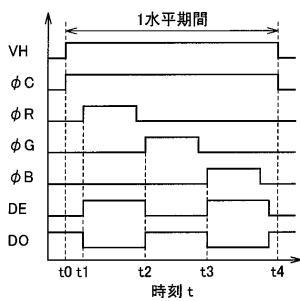

図 4 は、図 3 に示した L C D モジュールの検査方法を示すタイムチャートである。検査時は、端子 3 1 ~ 3 6 の各々は、プローブを介して検査装置に接続される。ある時刻 t 0 において複数の走査線 4 のうちのいずれかの走査線 4 が選択され、その走査線 4 の電位 V H が「 H 」レベルに立上げられる。これにより、その走査線 4 に対応する各 N 型 T F T 1 1 が導通し、各データ線 6 が導通した N 型 T F T 1 1 を介して液晶セル 2 に接続される。また時刻 t 0 において制御信号 C が「 H 」レベルに立上げられて N 型 T F T 2 6 , 2 7 が導通し、奇数番の組の N 型 T F T 2 1 ~ 2 3 のドレインが N 型 T F T 2 6 を介して奇数データ端子 3 6 に接続されるとともに、偶数番の組の N 型 T F T 2 1 ~ 2 3 のドレインが N 型 T F T 2 7 を介して偶数データ端子 3 5 に接続される。40

【 0 0 2 2 】

次いで時刻 t 1 において信号 R が「 H 」レベルに立上げられて各 N 型 T F T 2 1 が導通し、各奇数番の R 用データ線 6 が N 型 T F T 2 1 , 2 6 を介して奇数データ端子 3 6 に接続されるとともに、各偶数番の R 用データ線 6 が N 型 T F T 2 1 , 2 7 を介して偶数データ端子 3 5 に接続される。また時刻 t 1 において奇数データ信号 D O が「 L 」レベルに立50

下げられるとともに偶数データ信号 D E が「H」レベルに立上げられ、各奇数番の R 用データ線 6 が「L」レベルにされるとともに各偶数番の R 用データ線 6 が「H」レベルにされる。時刻 t 1 から所定時間経過後に信号 R が「L」レベルに立下げられて各 N 型 TFT 2 1 が非導通になり、選択された走査線 4 に対応する各 R 用液晶セル 2 へのデータ信号の書きが終了する。

#### 【 0 0 2 3 】

次に、時刻 t 2 において信号 G が「H」レベルに立上げられて各 N 型 TFT 2 2 が導通し、各奇数番の G 用データ線 6 が N 型 TFT 2 2 , 2 6 を介して奇数データ端子 3 6 に接続されるとともに、各偶数番の G 用データ線 6 が N 型 TFT 2 2 , 2 7 を介して偶数データ端子 3 5 に接続される。また時刻 t 2 において奇数データ信号 D O が「H」レベルに立上げられるとともに偶数データ信号 D E が「L」レベルに立下げられ、各奇数番の G 用データ線 6 が「H」レベルにされるとともに各偶数番の G 用データ線 6 が「L」レベルにされる。時刻 t 2 から所定時間経過後に信号 G が「L」レベルに立下げられて各 N 型 TFT 2 2 が非導通になり、選択された走査線 4 に対応する各 G 用液晶セル 2 へのデータ信号の書きが終了する。

#### 【 0 0 2 4 】

次いで時刻 t 3 において信号 B が「H」レベルに立上げられて各 N 型 TFT 2 3 が導通し、各奇数番の B 用データ線 6 が N 型 TFT 2 3 , 2 6 を介して奇数データ端子 3 6 に接続されるとともに、各偶数番の B 用データ線 6 が N 型 TFT 2 3 , 2 7 を介して偶数データ端子 3 5 に接続される。また時刻 t 3 において奇数データ信号 D O が「L」レベルに立下げられるとともに偶数データ信号 D E が「H」レベルに立下げられ、各奇数番の B 用データ線 6 が「L」レベルにされるとともに各偶数番の B 用データ線 6 が「H」レベルにされる。時刻 t 3 から所定時間経過後に信号 B が「L」レベルに立下げられて各 N 型 TFT 2 3 が非導通になり、選択された走査線 4 に対応する各 B 用液晶セル 2 へのデータ信号の書きが終了する。次に、時刻 t 4 において走査線 4 の電位 V H が「L」レベルに立下げられ、1 本の走査線 4 に対応する各液晶セル 2 へのデータ信号の書きが終了する。

#### 【 0 0 2 5 】

以上の動作を各走査線 4 ごとに行なうことにより、液晶パネル 1 の全液晶セル 2 に「H」レベルまたは「L」レベルのデータ信号を書込むことができる。液晶パネル 1 が正常か否かは、たとえば各液晶セル 2 の光透過率を検出することにより判定される。たとえば隣接する 2 本のデータ線 6 が短絡している場合は、それらのデータ線 6 に対応する各液晶セル 2 には、「H」レベルと「L」レベルの中間レベルの電位が書き込まれ、その液晶セル 2 は正常なデータ線 6 に対応する液晶セル 2 と異なる光透過率を示す。したがって、液晶パネル 1 が正常か否かを容易に判定することができる。

#### 【 0 0 2 6 】

検査において正常と判定された LCD モジュールの端子 3 0 . 1 ~ 3 0 . 4 , ... , 3 1 ~ 3 6 は、FPC に接続される。端子 3 4 ~ 3 6 の各々は、FPC により、N 型 TFT 2 6 , 2 7 を非導通にするような電位（たとえば接地電位 GND）に固定される。階調電位 V G の書きは、図 4 で示したデータ信号 D E , D O の書きと同様に行なわれる。すなわち、図 4 の時刻 t 1 ~ t 2 の間は、データ端子 3 0 . 1 ~ 3 0 . 4 , ... の各々に R 用階調電位 V G が与えられ、R 用液晶セル 2 の各々に R 用階調電位 V G が書き込まれる。時刻 t 2 ~ t 3 の間は、データ端子 3 0 . 1 ~ 3 0 . 4 , ... の各々に G 用階調電位 V G が与えられ、G 用液晶セル 2 の各々に G 用階調電位 V G が書き込まれる。時刻 t 3 ~ t 4 の間は、データ端子 3 0 . 1 ~ 3 1 . 4 , ... の各々に B 用階調電位 V G が与えられ、B 用液晶セル 2 の各々に B 用階調電位 V G が書き込まれる。このようにして、液晶パネル 1 の各液晶セル 2 に階調電位 V G が書き込まれ、液晶パネル 1 の 1 つのカラー画像が表示される。

#### 【 0 0 2 7 】

この実施の形態 1 では、各奇数番の組の N 型 TFT 2 1 ~ 2 3 のドレインと奇数データ端子 3 6 の間に N 型 TFT 2 6 を接続し、各偶数番の組の N 型 TFT 2 1 ~ 2 3 のドレインと偶数データ端子 3 5 の間に N 型 TFT 2 7 を接続し、N 型 TFT 2 6 , 2 7 のゲートを

10

20

30

40

50

制御端子 3 4 に接続する。検査時は N 型 TFT 2 6 , 2 7 を導通させて端子 3 5 , 3 6 に検査用のデータ信号 D E , D O を与え、通常動作時は N 型 TFT 2 6 , 2 7 を非導通状態に固定する。したがって、検査時に必要な端子の数が少なくてすみ、検査装置の低コスト化を図ることができる。また、複数の LCD モジュールの複数の奇数データ端子 3 6 を互いに接続するとともに複数の偶数データ端子 3 5 を互いに接続した場合でも、各 LCD モジュール用の制御信号 C のレベルを制御することにより、各 LCD モジュールを個別に正確に検査することができる。

#### 【 0 0 2 8 】

なお、液晶パネル 1 は、ガラス基板 1 5 表面の所定領域に走査線 4 、データ線 6 、 N 型 TFT 1 1 およびキャパシタ 1 2 を含むアレイ基板を形成した後に、そのアレイ基板の表面に液晶を介して対向基板を配置することにより形成される。実施の形態 1 では、液晶パネル 1 の組立後に液晶セル 2 の光透過率を検査することとしたが、液晶パネル 1 の組立前すなわち対向基板を配置する前の状態で、キャパシタ 1 2 の電荷量をモニタリングすることによりアレイ基板を検査してもよい。

#### 【 0 0 2 9 】

また、この実施の形態 1 では、検査用端子切換回路 2 5 を N 型 TFT で構成したが、 P 型 TFT で構成してもよいし、 N 型 TFT および P 型 TFT の並列接続体すなわちトランスマーケットで接続してもよい。

#### 【 0 0 3 0 】

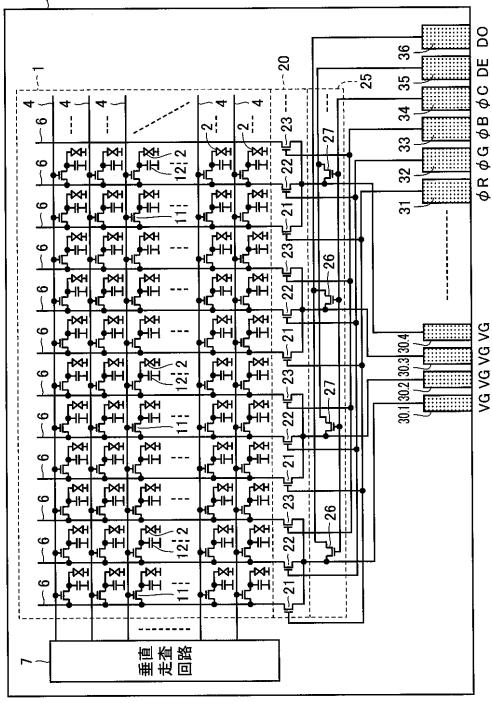

また、図 5 に示すように、検査時に使用する端子 3 1 ~ 3 6 の各々のサイズをデータ端子 3 0 . 1 ~ 3 0 . 4 , ... の各々のサイズよりも大きくするとよい。これにより、プローブの位置精度を低下させることができ、検査装置のコストダウンを図ることができる。

#### 【 0 0 3 1 】

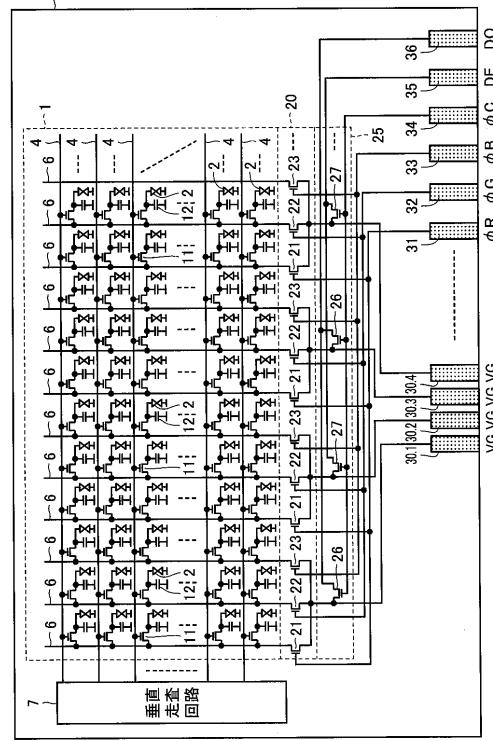

また、図 6 に示すように、検査時に使用する端子 3 1 ~ 3 6 のピッチをデータ端子 3 0 . 1 ~ 3 0 . 4 , ... のピッチよりも大きくするとよい。この場合も、プローブの位置精度を低下させることができ、検査装置のコストダウンを図ることができる。また、図 5 の変更例と図 6 の変更例を組合せ、検査時に使用する端子 3 1 ~ 3 6 の大きさおよびピッチをデータ端子 3 0 . 1 ~ 3 0 . 4 , ... の大きさおよびピッチよりも大きくすると、検査装置の一層のコストダウンを図ることができる。

#### 【 0 0 3 2 】

[ 実施の形態 2 ]

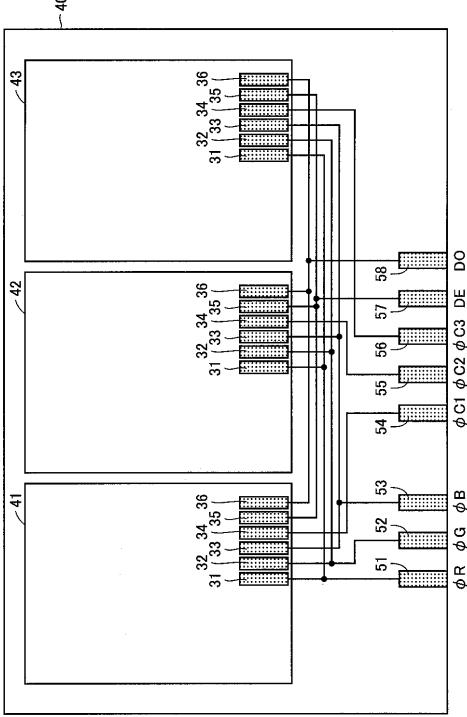

図 7 は、この発明の実施の形態 2 により LCD モジュールの検査方法を説明するための図である。図 7 において、この検査方法では、ガラス基板 4 0 の表面に複数（図では 3 つ）の LCD モジュール 4 1 ~ 4 3 が形成される。LCD モジュール 4 1 ~ 4 3 の各々は、図 3 で示したものと同じである。LCD モジュール 4 1 ~ 4 3 の各々の検査時に使用される端子 3 1 ~ 3 6 は、ガラス基板 4 0 の 1 辺に対向して配置される。また、ガラス基板 4 0 のその 1 辺に沿って、 R 端子 5 1 、 G 端子 5 2 、 B 端子 5 3 、制御端子 5 4 ~ 5 6 、偶数データ端子 5 7 、および奇数データ端子 5 8 が配置される。

#### 【 0 0 3 3 】

LCD モジュール 4 1 ~ 4 3 の R 端子 3 1 は、ともに R 端子 5 1 に接続される。LCD モジュール 4 1 ~ 4 3 の G 端子 3 2 は、ともに G 端子 5 2 に接続される。LCD モジュール 4 1 ~ 4 3 の B 端子 3 3 は、ともに B 端子 5 3 に接続される。LCD モジュール 4 1 ~ 4 3 の制御端子 3 4 は、ともに制御端子 5 4 ~ 5 6 に接続される。LCD モジュール 4 1 ~ 4 3 の偶数データ端子 3 5 は、ともに偶数データ端子 5 7 に接続される。LCD モジュール 4 1 ~ 4 3 の奇数データ端子 3 6 は、ともに奇数データ端子 5 8 に接続される。

#### 【 0 0 3 4 】

検査時は、端子 5 1 ~ 5 8 の各々がプローブを介して検査装置に接続される。端子 5 1 ~ 5 8 には、それぞれ信号 R , G , B , C 1 , C 2 , C 3 , D E , D O が与えられる。LCD モジュール 4 1 ~ 4 3 を検査する場合は、それぞれ制御信号 C 1 ~ C 3 が「 H 」レベルにされる。LCD モジュール 4 1 ~ 4 3 の各々は、実施の形態 1 と同じ

10

20

30

40

50

方法で検査される。検査の終了後は、LCDモジュール41～43の各々はガラス基板40から切出される。このとき、LCDモジュール41～43の各々は、不要となった端子51～58および配線から切離される。

#### 【0035】

この実施の形態2では、1回のプロービングで複数のLCDモジュール41～43を検査できるので、分断されたLCDモジュールを1つずつ検査する場合に比べ、プロービングの回数が少なくてすみ、プロービングの切換に必要な時間が短くてすむ。また、プロービングの回数が少なくてすみので、プローブの磨耗や折れ曲がりを軽減することができ、プローブの寿命を延ばすことができる。したがって、テストコストの大幅な低減化を図ることができる。

10

#### 【0036】

なお、この実施の形態2でも、液晶パネル1を組立てる前の状態で、キャパシタ12の電荷量をモニタリングすることにより各アレイ基板を検査してもよい。

#### 【0037】

#### [実施の形態3]

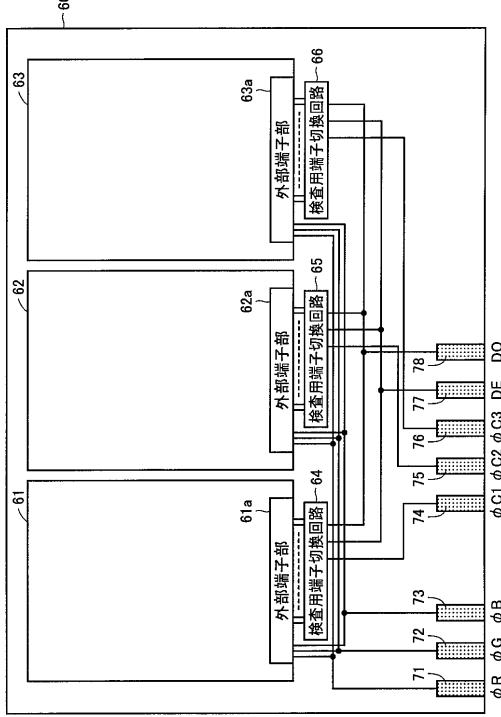

図8は、この発明の実施の形態3によるLCDモジュールの検査方法を説明するための図である。図8において、この検査方法では、ガラス基板60の表面に複数(図では3つ)のLCDモジュール61～63が形成される。LCDモジュール61～63の外部端子部61a～61cは、ガラス基板60の1辺に対向して配置される。LCDモジュール61～63の外部端子部61a～61cに沿って、それぞれ検査用端子切換回路64～66が設けられる。また、ガラス基板60のその1辺に沿って、R端子71、G端子72、B端子73、制御端子74～76、偶数データ端子77、および奇数データ端子78が設けられる。

20

#### 【0038】

図9は、LCDモジュール61の構成を示す回路ブロック図であって、図3と対比される図である。図9を参照して、LCDモジュール61が図3のLCDモジュールと異なる点は、検査用端子切換回路25、制御端子34、偶数データ端子35および奇数データ端子36が除去されている点である。外部端子部61aは、データ端子30.1～30.4、…、R端子31、G端子32、およびB端子33を含む。ガラス基板15は、ガラス基板60の一部を構成している。LCDモジュール62、63もLCDモジュール61と同じ構成である。

30

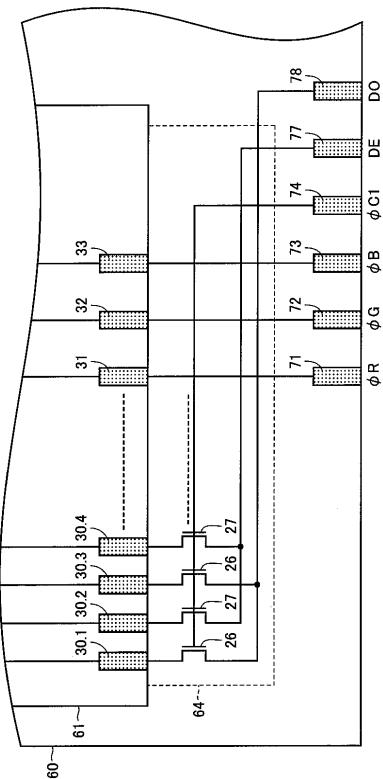

#### 【0039】

検査用端子切換回路64は、図10に示すように、奇数番のデータ端子30.1、30.3、…の各々に対応して設けられたN型TFT26と、偶数番のデータ端子30.2、30.4、…の各々に対応して設けられN型TFT27とを含む。各N型TFT26は、対応の奇数番のデータ端子と奇数データ端子78との間に接続され、そのゲートは制御端子74に接続される。各N型TFT27は、対応の偶数番のデータ端子と偶数データ端子77との間に接続され、そのゲートは制御端子74に接続される。なお、図10では、制御端子75、76の図示は省略されている。検査用端子切換回路65、66も検査用端子切換回路64と同じ構成である。ただし、検査用端子切換回路65のN型TFT26、27のゲートは制御端子75に接続され、検査用端子切換回路66のN型TFT26、27のゲートは制御端子76に接続される。

40

#### 【0040】

検査時は、端子71～78の各々がプローブを介して検査装置に接続される。端子71～78には、それぞれ信号R、G、B、C1、C2、C3、DE、DOが与えられる。LCDモジュール61～63を検査する場合は、それぞれ制御信号C1～C3が「H」レベルにされる。LCDモジュール61～63の各々は、実施の形態1と同様に検査される。検査の終了後は、LCDモジュール61～63の各々はガラス基板60から切出される。このとき、LCDモジュール61～63の各々は、不要となった検査用端子切換回路64～66、端子71～78および配線から切離される。

50

## 【0041】

この実施の形態3では、実施の形態2と同じ効果が得られる他、不要となったN型TFT26, 27を非導通状態に固定する処置(N型TFT26, 27のゲートおよびドレインに接地電位GNDを印加すること)が不要となる。また、LCDモジュールの構成が簡単になる。

## 【0042】

なお、この実施の形態3では、ガラス基板60上に複数のLCDモジュール61～63を設けた場合について説明したが、図10から分かるように、この検査方法は、ガラス基板60上に1つのLCDモジュール61を設けた場合でも有効である。

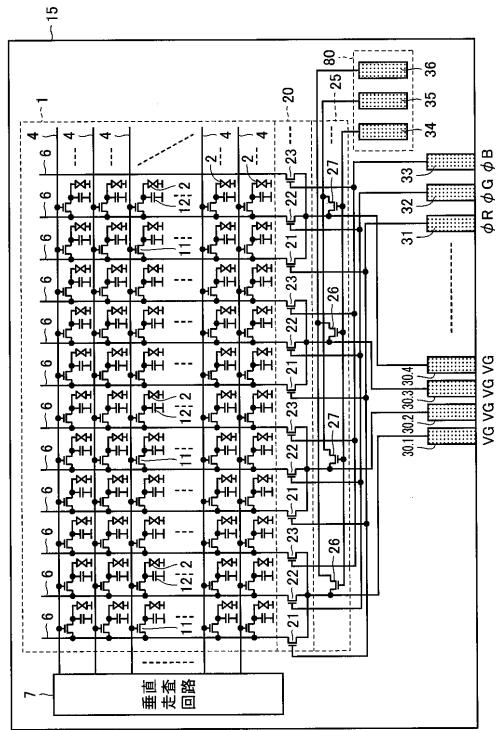

## 【0043】

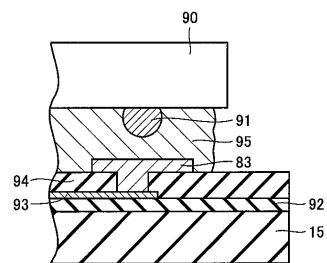

図11は、この発明の実施の形態4によるLCDモジュールの構成を示す回路ブロック図であって、図3と対比される図である。図11を参照して、このLCDモジュールが図3のLCDモジュールと異なる点は、端子34～36と検査用端子切換回路25の間の3本の配線がCOG(chip on glass)実装領域80を通過し、3本の配線のCOG実装領域80内の所定の位置にパッド81～83がそれぞれ設けられている点である。検査の終了後には、COG実装領域80を覆うようにして半導体チップが実装される。このとき、半導体チップの接地電位GNDの電極が3つのパッド81～83と導通状態にされ、パッド81～83は接地電位GNDに固定される。半導体チップには、図示しない電源端子および接地端子より、電源電位VDDおよび接地電位GNDが与えられる。半導体チップは、DC-DCコンバータなどを含んでいる。

## 【0044】

図12は、COG実装領域80に実装された半導体チップ90の一部を示す断面図である。図12において、ガラス基板15の表面に絶縁膜92が形成され、絶縁膜92の表面に金属配線93が形成される。この金属配線93は、奇数データ端子36および各N型TFT26のドレインに接続される。

## 【0045】

金属配線93を覆うようにして絶縁膜94が形成され、絶縁膜94の所定領域に開口部が形成され、金属配線93の所定部分が露出される。絶縁膜94の開口部を覆うようにして金属端子であるパッド83が形成される。パッド83の表面に異方性導電樹脂95が塗布され、半導体チップ90の接地端子であるバンプ電極91がパッド83上に位置するよう半導体チップ90が搭載される。これにより、バンプ電極91とパッド83は電気的に接続される。

## 【0046】

この実施の形態4では、検査後に半導体チップ90を実装することにより、検査用端子切換回路25のN型TFT26, 27を非導通状態に固定する。したがって、LCDモジュールの外部から端子34～36に接地電位GNDを与える必要がなくなるので、FPCの端子数を少なくすることができ、FPCの幅を狭くすることができる。

## 【0047】

なお、図13に示すように、端子34～36をCOG実装領域80内に設けてもよい。端子34～36は、半導体チップ90の実装により、接地電位GNDに固定される。この変更例では、実施の形態4と同じ効果が得られる他、パッド81～83を別途設ける必要がない。

## 【0048】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

## 【0049】

## 【発明の効果】

10

20

30

40

50

以上のように、この発明に係る画像表示装置では、複数行複数列に配置された複数の画素表示回路と、それぞれ複数行に対応して設けられた複数の走査線と、それぞれ複数列に対応して設けられた複数のデータ線とを含む画像表示パネルと、それらの第1の電極がそれぞれ複数のデータ線に接続され、画像表示パネルの通常動作時に非導通にされる複数のトランジスタと、複数のトランジスタのうちの各奇数番のトランジスタの第2の電極に接続された第1の検査端子と、複数のトランジスタのうちの各偶数番のトランジスタの第2の電極に接続された第2の検査端子と、複数のトランジスタのゲートに接続され、検査時に複数のトランジスタを制御するための制御信号を受ける第1の制御端子とが設けられる。

したがって、第1の検査端子、第2の検査端子および第1の制御端子を検査装置に接続すれば検査できるので、検査に使用する端子のが少なくてすみ、検査装置のコストダウンを図ることができる。また、複数の画像表示装置の複数の第1の検査端子を互いに接続するとともに複数の第2の検査端子を互いに接続した場合でも、画像表示装置を1つずつ正確に検査することができる。

10

20

30

40

## 【図面の簡単な説明】

【図1】この発明の実施の形態1によるカラー液晶画像装置の構成を示すブロック図である。

【図2】図1に示した液晶セルに対応して設けられる液晶駆動回路の構成を示す回路図である。

【図3】図1に示したカラー液晶表示装置の組立部品であるLCDモジュールの構成を示す回路ブロック図である。

【図4】図3に示したLCDモジュールの検査方法を説明するためのタイムチャートである。

【図5】実施の形態1の変更例を示す回路ブロック図である。

【図6】実施の形態1の他の変更例を示す回路ブロック図である。

【図7】この発明の実施の形態2によるLCDモジュールの検査方法を説明するための図である。

【図8】この発明の実施の形態3によるLCDモジュールの検査方法を説明するための図である。

【図9】図8に示したLCDモジュールの構成を示す回路ブロック図である。

【図10】図8に示した検査用端子切換回路の構成を示す回路ブロック図である。

【図11】この発明の実施の形態4によるLCDモジュールの構成を示す回路ブロック図である。

【図12】図11に示したLCDモジュールへの半導体チップの実装方法を説明するための断面図である。

【図13】実施の形態4の変更例を示す回路ブロック図である。

## 【符号の説明】

1 液晶パネル、2 液晶セル、3 画素、4 走査線、5 共通電位線、6 データ線、

7 垂直走査回路、8 水平走査回路、10 液晶駆動回路、11, 21~23, 26,

27 N型TFT、12 キャパシタ、15, 40, 60 ガラス基板、20 1:3 デ

マルチプレクサ、25, 64~66 検査用端子切換回路、30 データ端子、31, 5

1, 71 R端子、32, 52, 72 G端子、33, 53, 73 B端子、34, 54

~56, 74~76 制御端子、35, 57, 77 偶数データ端子、36, 58, 78

奇数データ端子、41~43, 61~63 LCDモジュール、61a~63a 外部

端子部、80 COG実装領域、81~83 パッド、90 半導体チップ、91 バン

プ電極、92, 94 絶縁膜、93 金属配線、95 異方性導電樹脂。

【 四 1 】

【 図 2 】

【図3】

【 四 4 】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 1 3】

---

フロントページの続き

|                           |             |            |

|---------------------------|-------------|------------|

| (51) Int.Cl. <sup>7</sup> | F I         | テーマコード(参考) |

| G 09 G 3/36               | G 09 G 3/20 | 621M       |

|                           | G 09 G 3/20 | 670Q       |

|                           | G 09 G 3/20 | 680G       |

|                           | G 09 G 3/36 |            |

(72)発明者 野尻 勲

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 村井 博之

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

F ターム(参考) 2H092 JB22 JB31 JB77 NA30 PA06

5C006 AC11 AF59 AF65 BB16 BC02 BC06 EB01 FA42 FA51

5C080 AA10 BB05 DD15 FF11 JJ02 JJ03 JJ04 JJ06

5C094 AA41 AA43 AA44 BA03 BA43 CA19 EA03 GB10

5G435 AA17 AA19 BB12 CC09 KK05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 画像表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2004271847A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 公开(公告)日 | 2004-09-30 |

| 申请号            | JP2003061778                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2003-03-07 |

| [标]申请(专利权)人(译) | 三菱电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 三菱电机株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 野尻勲<br>村井博之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 野尻 勲<br>村井 博之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G02F1/1345 G01R31/00 G02F1/13 G02F1/133 G02F1/1343 G02F1/136 G02F1/1362 G02F1/1368<br>G09F9/00 G09F9/30 G09G3/00 G09G3/20 G09G3/36 H01L21/336                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| CPC分类号         | G02F1/1309 G02F1/1345 G02F2001/136254 G02F2203/69 G09G3/006 G09G3/3648 G09G3/3688<br>G09G2310/0297 G09G2330/12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G02F1/1345 G02F1/1368 G09F9/00.352 G09F9/30.330.Z G09G3/20.612.R G09G3/20.621.M G09G3<br>/20.670.Q G09G3/20.680.G G09G3/36 G02F1/13.101 G09F9/30.330                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| F-TERM分类号      | 2H092/JB22 2H092/JB31 2H092/JB77 2H092/NA30 2H092/PA06 5C006/AC11 5C006/AF59 5C006<br>/AF65 5C006/BB16 5C006/BC02 5C006/BC06 5C006/EB01 5C006/FA42 5C006/FA51 5C080/AA10<br>5C080/BB05 5C080/DD15 5C080/FF11 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C094<br>/AA41 5C094/AA43 5C094/AA44 5C094/BA03 5C094/BA43 5C094/CA19 5C094/EA03 5C094/GB10<br>5G435/AA17 5G435/AA19 5G435/BB12 5G435/CC09 5G435/KK05 2H088/FA12 2H088/FA13 2H088<br>/FA25 2H088/FA28 2H088/FA30 2H088/HA02 2H088/HA06 2H088/HA08 2H192/AA24 2H192/DA12<br>2H192/FB23 2H192/HA93 2H192/HB03 2H192/HB04 2H192/HB13 2H192/HB14 |         |            |

| 代理人(译)         | 森田俊夫<br>堀井裕<br>酒井 将行                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | JP2004271847A5<br>JP3964337B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

## 摘要(译)

能够以低成本准确地进行检查的图像显示装置。解决方案：此LCD模块具有一个奇数数据端子36，用于在检查时通过每个N型TFT 26和多路分解器20将奇数数据信号DO施加到每个奇数组数据线6，并在检查时将每个N数施加到数据线6。在检查期间，通过TFT 27和解复用器20向偶数数据线6提供偶数数据信号DE，并向N型TFT 26和27的栅极提供控制信号φC。还有一个控制端子34。因此，可以减少检查时使用的端子数量，并且可以减少检查装置的成本。[选择图]图3