(19)日本国特許庁 (JP)

# 公開特許公報 (A)

特開2003-249507

(P2003-249507A)

(43)公開日 平成15年9月5日(2003.9.5)

(51)Int.Cl<sup>7</sup>

識別記号

F I

テマコード (参考)

H 01 L 21/336

G 02 F 1/1368

2 H 09 2

G 02 F 1/1368

H 01 L 29/78

616 A 5 F 11 0

H 01 L 29/786

審査請求 未請求 請求項の数 6 O L (全 26数)

(21)出願番号 特願2003-63322(P2003-63322)

(71)出願人 000005821

(62)分割の表示 特願2000-280673(P2000-280673)の分割

松下電器産業株式会社

(22)出願日 平成12年9月14日(2000.9.14)

大阪府門真市大字門真1006番地

(31)優先権主張番号 特願2000-131264(P2000-131264)

南野 裕

(32)優先日 平成12年4月28日(2000.4.28)

大阪府門真市大字門真1006番地 松下電器

(33)優先権主張国 日本(JP)

産業株式会社内

(31)優先権主張番号 特願2000-197536(P2000-197536)

千田 耕司

(32)優先日 平成12年6月30日(2000.6.30)

大阪府門真市大字門真1006番地 松下電器

(33)優先権主張国 日本(JP)

産業株式会社内

(74)代理人 100097445

弁理士 岩橋 文雄 (外2名)

最終頁に続く

(54)【発明の名称】薄膜トランジスタ及びそれを用いた液晶表示装置

(57)【要約】

【課題】光照射時のOFF電流(光伝導電流)を抑え、高性能、高信頼性を実現した薄膜トランジスタを提供する。

【解決手段】チャネル領域と、該チャネル領域の両側に配置されたソース領域およびドレイン領域とが形成された多結晶シリコン半導体層を有し、前記チャネル領域と前記ドレイン領域との間には空乏層が形成され、該空乏層の幅と前記チャネル領域に光が照射された場合に発生する光伝導電流とは比例関係を有し、前記光伝導電流を所定許容値内とするために、空乏層の幅を前記比例関係に基づいて求めた値以下とした構成である薄膜トランジスタを提供する。

## 【特許請求の範囲】

【請求項1】チャネル領域と、チャネル領域の両側に配置されたソース領域およびドレイン領域とが形成され、前記ソース領域とチャネル領域との間、またはドレイン領域とチャネル領域との間の少なくともいずれかに、不純物濃度がソース領域およびドレイン領域よりも低い低濃度不純物領域が形成された多結晶シリコン半導体層を有する薄膜トランジスタであって、

前記低濃度不純物領域の長さを  $L$  ( $\mu m$ )、ソース - ドレイン間電圧を  $V_{1c}$  (V)、前記チャネル領域のチャネル幅を  $W$  ( $\mu m$ ) とした場合、 $L > (W \cdot V_{1c}) / 36$  の関係を満たすことを特徴とする薄膜トランジスタ。

【請求項2】前記チャネル領域のチャネル長を  $L$  ( $\mu m$ ) とした場合、 $L < 1.5 \cdot (W / L)$  の関係を満たすことを特徴とする請求項1に記載の薄膜トランジスタ。

【請求項3】前記チャネル領域のチャネル幅  $W$  ( $\mu m$ ) が  $2 \mu m$  以下であることを特徴とする請求項2に記載の薄膜トランジスタ。

【請求項4】前記低濃度不純物領域のシート抵抗が  $20 k\Omega$  以上、 $100 k\Omega$  以下であることを特徴とする請求項2または請求項3に記載の薄膜トランジスタ。

【請求項5】前記低濃度不純物領域が、ドレイン領域とチャネル領域との間にのみ形成されていることを特徴とする請求項4に記載の薄膜トランジスタ。

【請求項6】請求項1～5のいずれかの薄膜トランジスタをスイッチング素子として備えた液晶パネル部を有する液晶表示装置。

## 【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】本発明は、薄膜トランジスタ及びそれを用いた液晶表示装置に関する。

## 【0002】

【従来の技術】(第1の従来技術)従来、アモルファスシリコン(以下、「a-Si」と称する)で形成されているアクティブラチクス型の液晶表示装置の画素の駆動性能は、a-Siで十分に満たされているが、同一の基板上に同じプロセスで信号線の駆動回路を構成することは性能上困難であり、単結晶Siによって形成された外付けの駆動回路(ドライバー)を用いてパネルを駆動している。

【0003】しかしながら、a-Siの移動度は  $0.5 \sim 1 \text{ cm}^2 \cdot \text{s}^{-1} \cdot \text{V}^{-1}$  であり、今後、液晶パネルの画素数が増大した場合、一般的には最大1水平期間に相当する画素のTFTをONする時間はますます短くなり、画素への書き込み能力が不足する。

【0004】これに対して、画素のTFTをポリシリコン(以下、「p-Si」と称する)で作成することによ

り、このTFTの移動度は、a-Siで作成された場合に比較して1桁から2桁以上高いため画素への充電能力が高くなる。従って、液晶パネルの高精細化が進むにつれて、画素TFTをp-Siで形成することは有利である(FPD Expo Forum 97、2-14)。

【0005】一般的にp-Si TFTの構造としては、ゲート電極がチャネル層上方に位置するトップゲート型、ゲート電極がチャネル層に対して基板側に存在するボトムゲート型の2種類が存在する。トップゲート型構造は、ボトムゲート型構造に比較して、不純物をゲート電極をマスクとして自己整合的にドーピングすることにより寄生容量の小さいTFTを作成することが可能であり微細化に有利である。

【0006】上記トップゲート型のTFTを例えば液晶表示装置に適用し該TFTの裏面より光を照射した場合、バックライトの光は直接TFTのチャネル領域に照射される。そして、前記チャネル領域に光が照射されると、この部分で光伝導電流が発生しOFF電流が大きくなるという問題があった。ここで、「光伝導電流」について説明する。

【0007】半導体中の光伝導電流の発生のメカニズムは太陽電池などを中心にこれまで多くの論文(たとえば、田中一宣編著、「アモルファス半導体の基礎」、1982年)などに紹介されているが、p-Si TFTでの光伝導電流の発生メカニズムについて論じられたものは少ない。

【0008】一般的に、光伝導電流の発生は、電界の印加された状態でバンドギャップを介して電子/正孔対が生成され、生成された電子/正孔対が電界によりドリフトし、それぞれの領域で多数キャリヤの増加に対しキャリヤの再結合電流という形で観測されるものである。ゲート電極下のチャネル領域は、逆バイアス条件下においてチャネル直下に正孔が誘起されるがそのキャリヤの濃度は非常に低い。これに対しドレイン側の多数キャリヤである電子は、n-領域のシート抵抗が  $20 k\Omega \sim 100 k\Omega$  の範囲では  $10^{16} / \text{cm}^3 \sim 10^{18} / \text{cm}^3$  程度のキャリヤ密度であると推定される。この場合、n-領域の多数キャリヤである電子はチャネル側に向かって拡散し拡散電位  $V_d$  を形成する。尚、空乏層の幅は  $W_d$  で表される。

【0009】光が照射されることにより、この空乏化した領域で電子/正孔対が発生する。発生した電子/正孔対は互いに電界にひかれて電子はドレイン方向、ホールはチャネル方向に移動する。ドレイン側に移動した電子ならびにチャネル側に移動した正孔はそれぞれの領域で再結合して消滅する。この再結合に消費される電荷がそれぞれソースおよびドレイン電極により供給され、これが光伝導電流として観測される。

【0010】(第2の従来技術)また、p-Si TFTは高移動度であるので、画面内のアクティブラチック

ス素子と信号駆動回路の一部あるいは全部をガラス基板上に同時に形成することができる。しかしながら、p-Si TFTは、a-Si TFTやMOS型電解効果トランジスタに比較してOFF電流が大きいという欠点を有している。

【0011】そこで、このOFF電流低減のために、特開平5-136417号公報に開示されているように、TFTのソース領域またはドレイン領域の少なくとも一方に隣接して、低濃度不純物領域（LDD領域）を設ける方法が行われている（第1の従来の方法）。

【0012】また、LDD領域を形成する他の方法として、LDD領域をTaO<sub>x</sub>の有無によりコントロールする方法（Euro Display' 96 pp547）が開示されている（第2の従来の方法）。

【0013】LDD領域がOFF電流低減に有効であるメカニズムについては、特開平5-136417号公報に開示されているように、LDD領域がドレイン領域に対して高抵抗であるため、チャンネル／LDD領域の接合部にかかる電界が、LDD領域を設けない場合に対して小さくなるためと考えられている。

【0014】以上の2つの方法では、いずれの方法もLDD領域をマスク合わせによりTaO<sub>x</sub>の有無を制御、あるいはレジスト膜の有無を制御することによりドーピング濃度の違う部分を形成している。この方法では確実にLDDの領域を確保するために、LDD領域の長さはマスクあわせの寸法精度以上の長さを確保しなければならない。

【0015】これに対し、特開平7-140485号公報に示すように、LDD領域をゲート電極に対して自己整合的に形成する第3の従来の方法がある。本方法は、ゲート電極となるAlを陽極酸化することによって、その側面にAlの酸化物層を形成し、これをマスクとしてN型あるいはP型の不純物元素を導入して、ソース領域、ドレイン領域及び前記側面の酸化物層とほぼ同じ厚みを持った低濃度不純物層を作成することを可能とするものである。

【0016】この方法を用いれば、ゲート電極に対して自己整合的にLDD領域を形成することが可能で、LDD領域形成のためのマスクを削減できると共に、不純物濃度の高い領域の長さを、陽極酸化したAlの側面に存在する酸化物の膜厚に相当する0.1μm～0.5μm程度とかなり小さく形成することが可能である。

【0017】

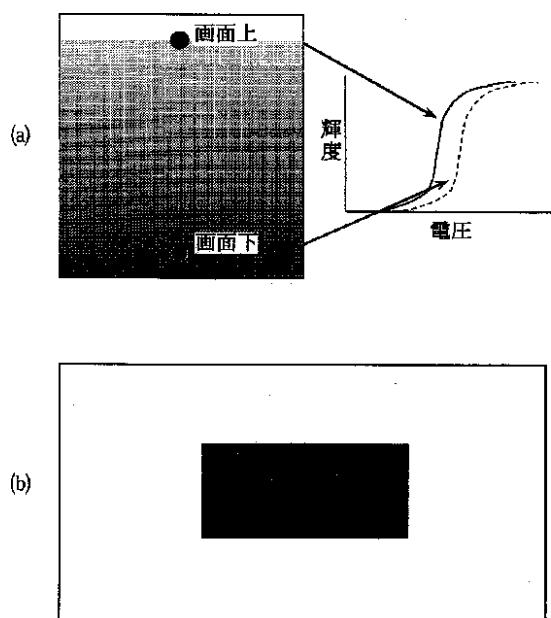

【発明が解決しようとする課題】（第1の従来例に対する課題）上記のような光伝導電流によってOFF電流が増加（オフ特性の劣化）した場合、次のような問題が発生する。オフ特性の劣化により引き起こされる画質劣化は、輝度傾斜とクロストークである。輝度傾斜とは、図38（a）に示すように、画面の上部と下部で、液晶の電流／輝度特性が異なることにより発生するものであ

り、画面の上部と下部で輝度の差が生じる。一方、クロストークとは、図38（b）のように白の中央部に黒のボックスパターンを表示した場合、黒の画像が上下あるいは左右方向に尾を引くような現象である。また、その他、オフ特性の劣化はフリッカーの増加、輝度むらの発生など画質に大きな影響を与える。

【0018】（第2の従来例に対する課題）LDD構造はOFF電流低減に関して効果が高いのであるが、TFTのゲート電極下のチャンネルが反転するON状態においては、比較的高抵抗層であるLDD領域がチャンネル領域に直列に挿入されることによりON電流が低下するという欠点を有している。

【0019】本来、LDD領域はソースならびにドレイン領域である部分に対して高抵抗でありTFTの特性が上がるに従ってその抵抗の影響が顕著に現れる傾向をもつ。よって、この高抵抗領域であるLDD領域の長さは、そのOFF電流を低減させるに十分であり、かつ高いON電流を確保するに十分に低い抵抗値を持つものでなければならない。

【0020】しかしながら、現状ではLDD領域の長さの指針を決める方法が皆無であり、OFF電流低減のために必要以上にLDD領域を確保する必要がある。一般的には1.5μmよりも長いLDD領域を確保する必要があり、その結果、TFTのON電流を低下させる原因となっている。

【0021】また、第3の従来例に示す方法によれば、LDD領域を0.1μm～0.5μm程度とかなり小さく形成することが可能であるが、一般に液晶パネルのドライバあるいは画素のTFTとして用いる場合、その駆動電圧は5～15V程度であり、一般のICと比較してかなり高い。従って、LDD領域が0.1μm～0.5μmの場合、その効果が不十分となり本プロセスでは十分にOFF電流を下げることができない。

【0022】そこで、本発明では、上記の点に鑑み、光照射時のOFF電流（光伝導電流）を抑える構成をとることにより、輝度傾斜やクロストーク等の画質劣化を抑制し、高性能、高信頼性を実現した薄膜トランジスタの提供を第1の目的としている。

【0023】また、OFF電流を抑えるとともに、LDD領域の長さを必要最小限に押さえてON電流の減少を抑制する構成をとることにより、高性能、高信頼性を実現した薄膜トランジスタの提供を第2の目的とするものである。

【0024】

【課題を解決するための手段】即ち、上記課題を解決するために、本発明の薄膜トランジスタは、チャネル領域と、該チャネル領域の両側に配置されたソース領域およびドレイン領域とが形成された多結晶シリコン半導体層を有し、前記チャネル領域と前記ドレイン領域との間に空乏層が形成され、該空乏層の幅と前記チャネル領域

に光が照射された場合に発生する光伝導電流とは比例関係を有し、前記光伝導電流を所定許容値内とするために、空乏層の幅を前記比例関係に基づいて求めた値以下とした構成であることを特徴としている。

【0025】上記のように、空乏層幅が光伝導電流と比例関係を有することが新たに見い出され、これにより、空乏層幅を制御することで光伝導電流を所定の許容値以下とすることが達成され、輝度傾斜やクロストーク等の画質劣化のない薄膜トランジスタを提供することができる。

【0026】また、本発明の薄膜トランジスタは、上記の薄膜トランジスタであって、前記ドレイン領域のシート抵抗を  $R (k \Omega)$  、前記チャネル領域のチャネル幅を  $W (\mu m)$  とした場合、式(1)の関係を満たすことを特徴としている。尚、Aは光伝導電流と光強度によって定められる定数である。

$$(R + 30) \cdot W < A \dots (1)$$

【0027】また、本発明の薄膜トランジスタは、上記の薄膜トランジスタであって、前記ドレイン領域のシート抵抗を  $R (k \Omega)$  、前記チャネル領域のチャネル幅を  $W (\mu m)$  とした場合、式(2)の関係を満たすことを特徴としている。

$$(R + 30) \cdot W < 1 \times 10^3 \dots (2)$$

【0028】上記(1)式、(2)式のように、新たに制御できる因子(ドレイン領域のシート抵抗)とチャネル領域のチャネル幅との関係によって、光照射時のOFF電流(光伝導電流)を抑制する範囲を規定することができる。そして、上記(1)式、(2)式の関係を満たす薄膜トランジスタは、光照射時のOFF電流の増加を抑えることができるので、クロストークや輝度傾斜を防ぐことができ、従って、高性能、高信頼性を実現することができる。

【0029】また、本発明の薄膜トランジスタは、上記の薄膜トランジスタであって、前記チャネル領域のチャネル幅Wが  $2 \mu m$  以下であることを特徴としている。

【0030】上記(2)式の関係は、チャネル領域のチャネル幅Wを  $2 \mu m$  以下とする場合であっても、シート抵抗Rとチャネル幅Wによって、光照射時のOFF電流の増加を抑えることができる。

【0031】また、本発明の薄膜トランジスタは、上記の薄膜トランジスタであって、前記ドレイン領域のシート抵抗が  $20 k \Omega$  以上、  $100 k \Omega$  以下であることを特徴とする。

【0032】このように規制するのは、シート抵抗が  $20 k \Omega$  以下ではOFF電流は急激に大きくなり、また、シート抵抗を  $100 k \Omega$  以上にした場合、トランジスタのON電流が低下しパネルの動作が不安定となるためである。ドレイン領域のシート抵抗の範囲を  $20 k \Omega$  以上  $100 k \Omega$  以下とすることにより、OFF電流の低減を図ることができるとともに、ON電流

の減少は起こらない薄膜トランジスタを提供することができる。

【0033】また、本発明の薄膜トランジスタは、チャネル領域と、該チャネル領域の両側にソース領域およびドレイン領域とが配置された多結晶シリコン半導体層を有し、液晶表示装置にスイッチング素子として備えられる薄膜トランジスタであって、前記液晶表示装置を構成するバックライトの輝度を  $2000 (cd/m^2)$  以上とする場合、前記ソース領域と前記チャネル領域との間、または前記ドレイン領域と前記チャネル領域との間の少なくともいずれか一方に、不純物濃度がソース領域およびドレイン領域よりも低い低濃度不純物領域が形成され、該低濃度不純物領域の長さLは、 $1.0 \mu m$  以下であることを特徴としている。

【0034】このように、低濃度不純物領域を形成することにより、空乏層の広がりを長さLが  $1.0 \mu m$  以下とされた低濃度不純物領域の範囲内とすることができる、従って、光伝導電流(OFF電流)が増加しない薄膜トランジスタとすることができる。

【0035】また、本発明の請求項1に記載の発明は、チャネル領域と、チャネル領域の両側に配置されたソース領域およびドレイン領域とが形成され、前記ソース領域とチャネル領域との間、またはドレイン領域とチャネル領域との間の少なくともいずれかの間に、不純物濃度がソース領域およびドレイン領域よりも低い低濃度不純物領域が形成された多結晶シリコン半導体層を有する薄膜トランジスタであって、前記低濃度不純物領域の長さをL( $\mu m$ )、ソース-ドレイン間電圧を  $V_{1c}$  ( $V$ )、前記チャネル領域のチャネル幅を  $W (\mu m)$  とした場合、式(3)の関係を満たすことを特徴としている。

$$L > (W \cdot V_{1c}) / 36 \dots (3)$$

【0036】このような関係を満たすことにより、薄膜トランジスタのOFF時には、前記低濃度不純物領域がキャリアの枯渇する高抵抗層となるためOFF電流の低減を図ることができる。そして、前記(1)式より、LDD領域の長さの指針を決めることができ、OFF電流低減のために必要以上にLDD領域を確保する必要はなくなるのである。

【0037】また、請求項2に記載の発明は、請求項1に記載の薄膜トランジスタであって、前記チャネル領域のチャネル長をL( $\mu m$ )とした場合、式(4)の関係を満たすことを特徴としている。

$$L < 1.5 \cdot (W / L) \dots (4)$$

【0038】このような関係を更に満たすことにより、薄膜トランジスタのON時には、ゲート電極からの電界の作用により、ゲート電極下の低濃度不純物領域はキャリアとなる電子が蓄積して低抵抗領域となり、ON電流の減少は起こらない。よって、前記薄膜トランジスタは、ON電流を十分確保すると共にOFF電流を小さく

押さえることが可能となる。

【0039】また、請求項3に記載の発明は、請求項2に記載の薄膜トランジスタであって、前記チャネル領域のチャネル幅W(μm)が2μm以下であることを特徴としている。

【0040】上記(2)式の関係は、チャネル領域のチャネル幅Wを2μm以下とする場合であっても、シート抵抗Rとチャネル幅Wによって、光照射時のOFF電流の増加を抑えることができる。

【0041】また、請求項4に記載の発明は、請求項2または請求項3に記載の薄膜トランジスタであって、前記低濃度不純物領域のシート抵抗が20k/以上、100k/以下であることを特徴としている。

【0042】また、請求項5に記載の発明は、請求項4に記載の薄膜トランジスタであって、前記低濃度不純物領域が、ドレイン領域とチャネル領域との間にのみ形成されていることを特徴としている。

【0043】低濃度不純物領域を設けるのは、本来的にはドレイン領域に作用する電界を緩和するためであり、かかる観点からすれば、ドレイン領域とチャネル領域の双方に低濃度不純物領域を設ける必要はない。そこで、ドレイン領域とチャネル領域との間、または前記ドレイン領域と前記チャネル領域との間の少なくとも一方に低濃度不純物領域を形成すれば、薄膜トランジスタの面積を小さくすることが可能となる。

【0044】また、本発明は、チャネル領域と、該チャネル領域の両側に配置されたソース領域およびドレイン領域とが形成された多結晶シリコン半導体層を有し、前記チャネル領域と前記ドレイン領域との間には空乏層が形成され、該空乏層の幅と前記チャネル領域に光が照射された場合に発生する光伝導電流とは比例関係を有し、前記光伝導電流を所定許容値内とするために、空乏層の幅を前記比例関係に基づいて求めた値以下とした薄膜トランジスタをスイッチング素子として備えた液晶パネル部と、前記液晶パネル部に裏面側より光を供給するバックライト部と、を備えた液晶表示装置であって、前記ドレイン領域のシート抵抗をR(k/ )、前記バックライト部の輝度をB(cd/m<sup>2</sup>)、前記チャネル領域のチャネル幅をW(μm)とした場合、式(5)の関係を満たすことを特徴としている。尚、Cは光伝導電流によって定められる定数である。

$$(R + 30) \cdot B \cdot W < C \dots (5)$$

【0045】また、本発明の液晶表示装置は、上記液晶表示装置であって、前記ドレイン領域のシート抵抗をR(k/ )、前記バックライト部の輝度をB(cd/m<sup>2</sup>)、前記チャネル領域のチャネル幅をW(μm)とした場合、式(6)の関係を満たすことを特徴としている。

$$(R + 30) \cdot B \cdot W < 1 \times 10^6 \dots (6)$$

【0046】また、本発明のEL装置は、薄膜トランジ

スタを有する基板に形成された画素電極上層に発光層を有し、該発光層上層に対向電極が形成されたEL装置であって、前記薄膜トランジスタは、チャネル領域と、該チャネル領域の両側に配置されたソース領域およびドレイン領域とが形成された多結晶シリコン半導体層を有し、前記チャネル領域と前記ドレイン領域との間には空乏層が形成され、該空乏層の幅と前記チャネル領域に光が照射された場合に発生する光伝導電流とは比例関係を有し、前記光伝導電流を所定許容値内とするために、空乏層の幅を前記比例関係に基づいて求めた値以下とした薄膜トランジスタであり、該薄膜トランジスタのチャネル領域に照射される光強度をB(cd/m<sup>2</sup>)とした場合、式(5)の関係を満たすことを特徴としている。尚、Cは光伝導電流によって定められる定数である。

$$(R + 30) \cdot B \cdot W < C \dots (5)$$

【0047】また、本発明のEL表示装置は、上記EL表示装置であって、前記ドレイン領域のシート抵抗をR(k/ )、前記チャネル領域に照射される光強度をB(cd/m<sup>2</sup>)、前記チャネル領域のチャネル幅をW(μm)とした場合、式(6)の関係を満たすことを特徴としている。

$$(R + 30) \cdot B \cdot W < 1 \times 10^6 \dots (6)$$

【0048】また、本発明の薄膜トランジスタの製造方法は、絶縁性基板上に多結晶シリコン半導体層を形成する多結晶シリコン半導体層形成工程と、前記多結晶シリコン半導体層上にゲート絶縁膜を形成するゲート絶縁膜形成工程と、前記ゲート絶縁膜上にゲート電極をパターン状に形成するゲート電極形成工程と、前記ゲート電極の側面を酸化し、該ゲート電極の側面を覆う金属酸化膜を形成する陽極酸化工程と、前記多結晶シリコン半導体層に前記ゲート電極をマスクとして不純物をドープする不純物ドープ工程と、を有する薄膜トランジスタの製造方法であって、前記陽極酸化工程において形成される金属酸化膜の膜厚を制御して、前記不純物ドープ工程において形成される低濃度不純物領域の長さLを1.0μm以下とすることを特徴としている。

【0049】また、本発明の薄膜トランジスタは、絶縁性基板上に多結晶シリコン半導体層を形成する多結晶シリコン半導体層形成工程と、前記多結晶シリコン半導体層上にゲート絶縁膜を形成するゲート絶縁膜形成工程と、前記ゲート絶縁膜上にゲート電極をパターン状に形成するゲート電極形成工程と、前記多結晶シリコン半導体層に前記ゲート電極をマスクとして不純物をドープする第1の不純物ドープ工程と、前記第1の不純物ドープ工程により、不純物がドープされた半導体領域上に遮蔽膜を形成し、該遮蔽膜を異方性エッチングによりパターン状に形成する遮蔽膜形成工程と、前記多結晶シリコン半導体層に前記遮蔽膜をマスクとして不純物をドープして、遮蔽膜の下部領域とそれ以外の領域で不純物濃度差が存在するようにして、ソース領域とチャネル領域との

間、またはドレイン領域とチャネル領域との間の少なくともいざれか一方に、不純物濃度がソース領域及びドレイン領域よりも低い低濃度不純物領域を形成し、該低濃度不純物領域の長さを1.0μm以下とする第2の不純物ドープ工程と、を有することを特徴としている。

【0050】また、本発明のは、上記の薄膜トランジスタの製造方法であって、前記低濃度不純物領域の長さLが1.0μm以下のものを良品とする検査工程を含むことを特徴としている。

#### 【0051】

##### 【発明の実施の形態】[第1の発明群]

(第1の発明群の概念)まず、第1の発明群の概念について説明した後、具体的な実施の形態について図面に基づいて説明する。

【0052】第1の発明群では、TFTへの光照射時の光伝導電流を抑えることを目的としている。

【0053】そこで、上記目的を達成するために、本願発明者らは、前記光伝導電流と相関性を有するパラメータを探索し、その結果、空乏層幅が光伝導電流と比例関係を有することを新たに見い出した。この比例関係に基づいて空乏層幅を制御(小さく)することによって、光伝導電流を許容値以下とすることが達成され、輝度傾斜やクロストーク等の画質劣化のない薄膜トランジスタを提供することができる。

【0054】尚、前記「空乏層幅」とは、後述する図2(a)に示すように、電界強度が立ち上がる2点のそれとの接線間の距離と定義する。

【0055】また、従来、バックライトの輝度B及びチャネル領域のチャネル幅Wは、光伝導電流と相関性があることは分かっており、これら2つの制御パラメータに基づいてTFTの設計を行っていた。しかし、前記2つの制御パラメータだけでは光伝導電流抑制に対して十分でなく、TFTを設計する上で誤差が生じることもある。

【0056】そこで、本願発明者らは、前記「空乏層幅と光伝導電流との比例関係」に関して更に鋭意検討を加え、ドレイン領域のシート抵抗も光伝導電流に対して相関性があることを新たに見い出した。これにより、シート抵抗Rという新たな因子を評価基準とすることにより制御パラメータが3つとなり、従来の制御パラメータが2つのものに比較して薄膜トランジスタの設計の精度が向上し、光伝導電流を顕著に抑制することができる。以下に、空乏層幅と光伝導電流との関係についてまず説明し、その後、バックライトの輝度Bと、ドレイン領域のシート抵抗Rと、チャネル領域のチャネル幅Wとの関係について説明する。そして、光伝導電流を抑制するためのTFTの具体的な作製手法の原理について説明する。

【0057】まず、本願発明者らは、TFTを構成するチャネル領域のチャネル幅と光伝導電流の関係を測定するとともに、ドレイン領域のシート抵抗と光伝導電流の

関係を測定した。更に、シミュレーションにより動作解析を行い、空乏層幅の範囲を求めた。

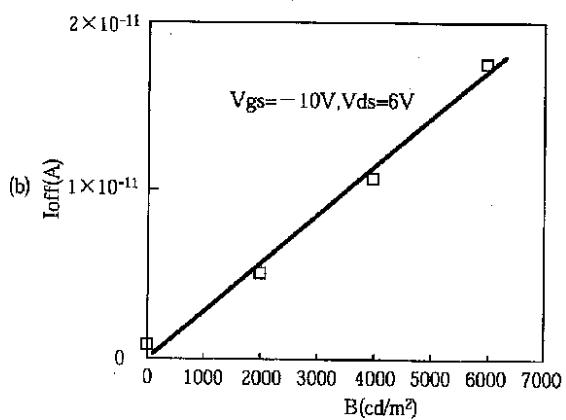

【0058】図1(a)は、TFTを構成するチャネル領域のチャネル幅Wと光伝導電流(OFF電流: I<sub>OFF</sub>)との関係を示すグラフである。尚、実線は6000cd/cm<sup>2</sup>、破線は4000cd/cm<sup>2</sup>、1点鎖線は2000cd/cm<sup>2</sup>の光を照射した場合のチャネル幅Wと光伝導電流I<sub>OFF</sub>の関係を示している。

【0059】図1(a)より、光照射時のOFF電流I<sub>OFF</sub>は、チャネル幅Wに比例することが明らかである。

また、図1(b)は、バックライト輝度と光伝導電流との関係を示すグラフであるが、OFF電流I<sub>OFF</sub>は、バックライト輝度Bに比例することが確認できた。

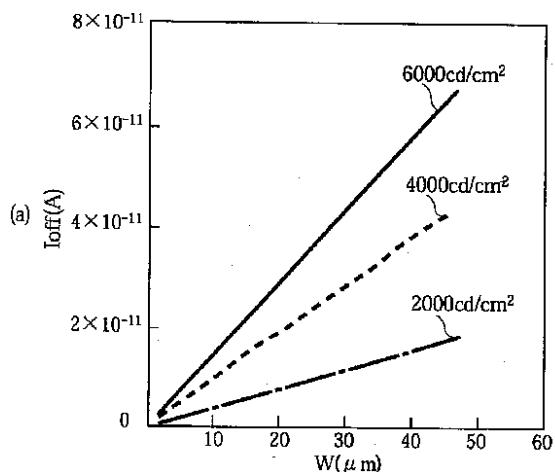

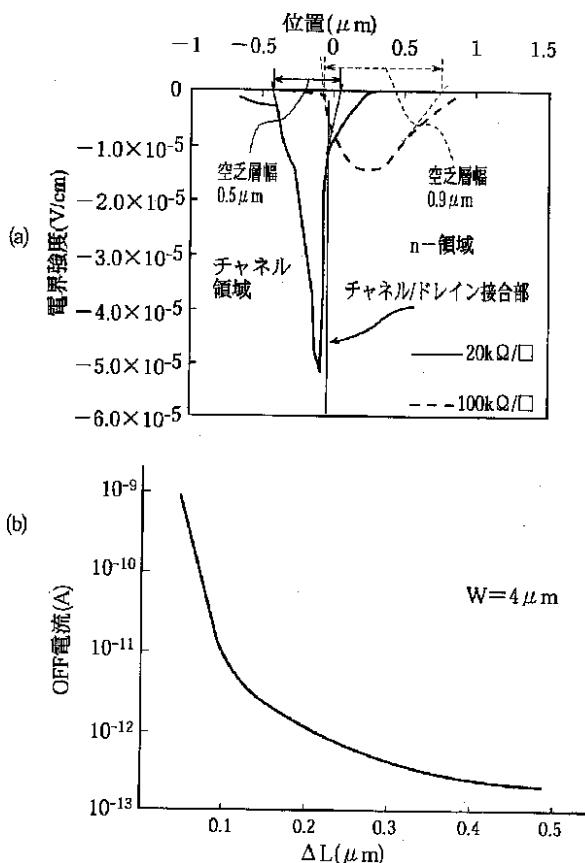

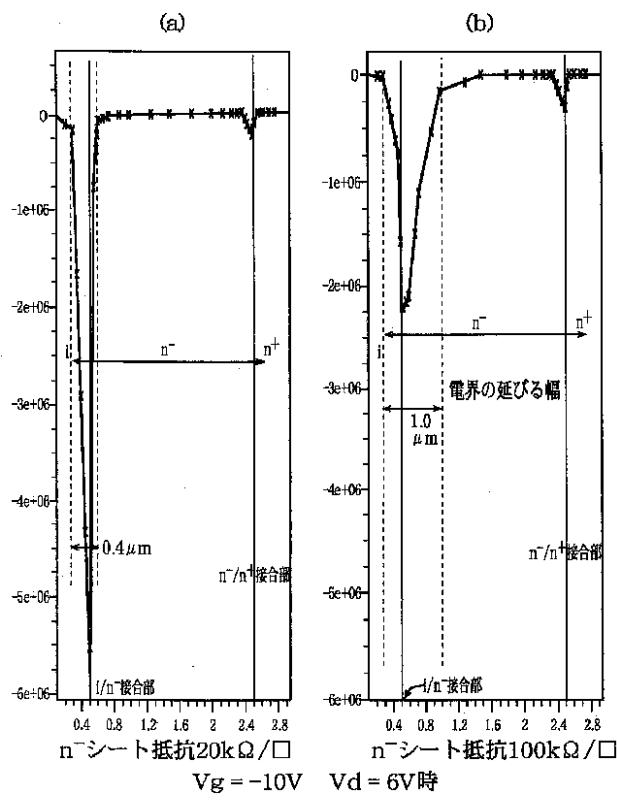

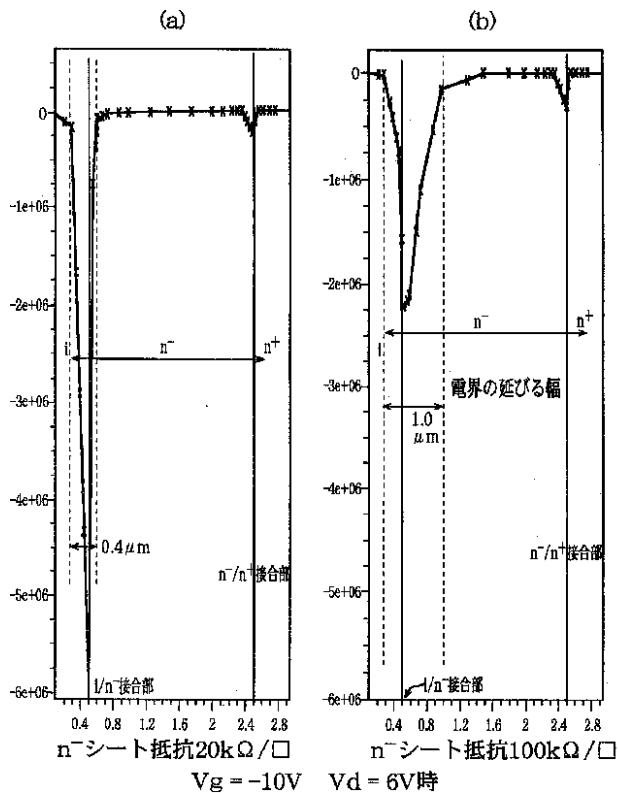

【0060】図2(a)はTFTをOFF状態にした場合の電界をシミュレーションした結果を示すグラフである。図2(a)に示すシミュレーション結果により、電界はほぼチャネル/ドレイン領域の接合部にのみ集中しており、LDD領域のシート抵抗が20k/(実線)の場合、空乏層幅は約0.5μm程度であり、その空乏層領域は主にチャネル側に伸びていることが分かる。これに対して、シート抵抗が100k/(破線)の場合、空乏層幅は0.9μm程度であり、LDD領域に拡がっていることが確認される。

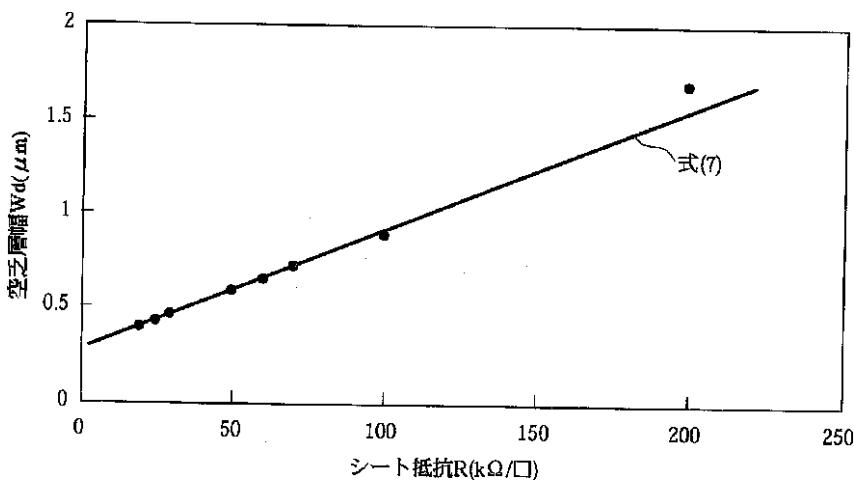

【0061】これにより、シート抵抗が変化することにより空乏層幅も変化することが新たに見い出された。そこで、本願発明者らは、シート抵抗と空乏層幅との関係を調査した。その結果を図3に示す。図3はシミュレーションにより得られたシート抵抗と空乏層幅との関係を示す。空乏層幅W<sub>d</sub>はシート抵抗Rに比例することが確認された。これはp/n接合の場合における空乏層の拡がりと同様、キャリヤ濃度の低い領域に空乏層は伸びるためであると考えられる。そして、図3のシート抵抗と空乏層幅との関係を下記(7)式に示す。

$$W_d = 8 \times 10^{-3} \cdot R + 0.24 \dots (7)$$

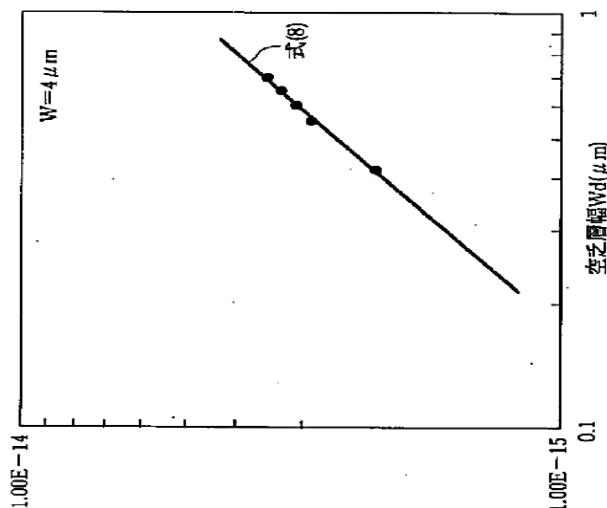

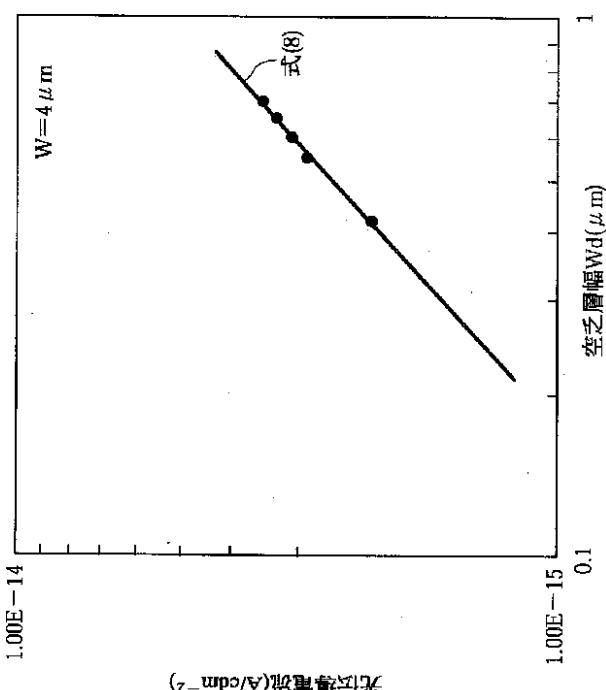

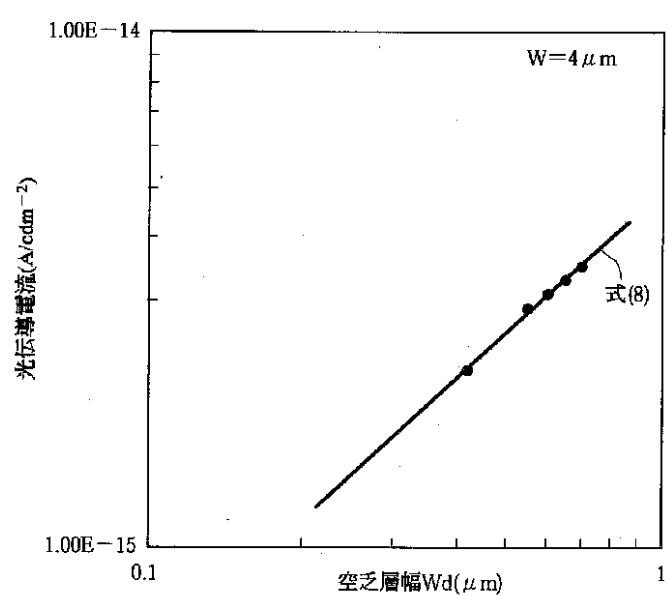

【0062】図4はシミュレーション(W=4μmの場合)により求められた空乏層幅と、該空乏層幅に対応するシート抵抗での光伝導電流と、の関係を測定した結果を示す。

【0063】空乏層幅と光伝導電流をそれぞれ対数でプロットすると、ほぼ傾きが1の直線が得られた。これは、光伝導電流が空乏領域により発生することを示唆するものである。そして、空乏層幅W<sub>d</sub>と光伝導電流の関係は下記(8)式のように表すことができる。

$$I_{photo} = 5 \times 10^{-15} \cdot W_d \dots (8)$$

【0064】尚、上記(8)式で、I<sub>photo</sub>は、チャネル幅が4μmでの光強度が1(cd/m<sup>2</sup>)当たりの値である。

【0065】このように上記(8)式より、空乏層幅W<sub>d</sub>が光伝導電流I<sub>photo</sub>と比例関係を有することが見い出され、これにより、空乏層幅を制御(小さく)するこ

とで光伝導電流を許容値以下とすることができる、輝度傾斜やクロストーク等の画質劣化ない、高性能、高信頼性を実現した薄膜トランジスタを提供することができる。尚、前記「許容値」とは、例えば後述するが、10 pA以下の値である。

【0066】また、前述した図1(a)より、 $I_{off}$ は\*

$$I_{off} (4 / (W \cdot B)) = 5 \times 10^{-15} \cdot Wd \dots (10)$$

そして、上記(7)、(10)式より空乏層幅 $Wd$ を消去すると、下記(11)式が得られる。ここで、図1(a)より $I_{off}$ はチャネル幅 $W$ に比例する。

$$R = I_{off} \cdot 10^{17} / (B \cdot W) - 30 \dots (11)$$

【0069】ところで、一般的に高品位の画質を維持するためには、 $I_{off}$ は10 pA以下の値が必要である。\*

$$V = V0 \{ 1 - \exp (T / (R_{off} \times C_{tot})) \} \dots (12)$$

ここで、 $C_{tot} = C_s + C_{lc}$

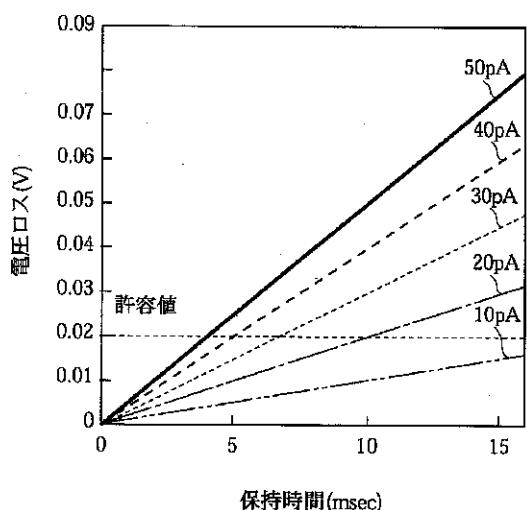

【0071】また、TFTのOFF電流( $R_{off} = V_{sd} / I_{off}$ )をパラメータとした場合の、時間と電圧ロスのシミュレーション結果を図6に示す。図6より、16 m sec(1/60Hz)の保持時間で、電圧ロスを0.0\*

$$(R + 30) \cdot B \cdot W < 10 \cdot 10^{-12} \cdot 10^{17} = 1 \times 10^6 \dots (6)$$

また、薄膜トランジスタを使用される条件によっては、OFF電流を抑制する値は変化するので、下記(5)式のように表すことができる。

$$(R + 30) \cdot B \cdot W < C \dots (5)$$

尚、 $C$ は光伝導電流によって定められる定数である。

【0073】このようにして、上記(6)式を満たす薄膜トランジスタは、光伝導電流を抑制することができるものであり、従って、クロストークや輝度傾斜を防ぐことができ、画質が優れ、高性能、高信頼性を実現することができる。

【0074】また、上記式(6)は液晶パネルとしてのバックライト輝度を含んだ式であるが、一般的に薄膜トランジスタは常にバックライトを備えた透過型のみとは

$$(R + 30) \cdot W < (I_{off} \cdot 10^{17}) / B \dots (11')$$

【0077】上記(11')の右辺を、 $I_{off}$ と $B$ とによって定められる定数 $A$ で置き換えると、下記(1)式で表すことができる。

$$(R + 30) \cdot W < A \dots (1)$$

( $A$ は光伝導電流と光強度によって定められる定数)

【0078】また、前記TFTの構成において、LDD領域を形成することにより、該LDD領域以上には空乏層は広がらず、前述したように空乏層幅と比例関係にある光伝導電流を抑制することができる。図16は、チャネル領域とLDD領域において、TFTをOFF状態にした場合( $V_g = -10V$ 、 $V_d = 6V$ 時)の電界をシミュレーションした結果を示す。

【0079】前記シミュレーション結果より、電界のかかる領域はシート抵抗に依存しており、LDD領域のシート抵抗が $20k\Omega$ の場合は $0.4\mu m$ 程度、シート抵抗が $100k\Omega$ の場合は $1.0\mu m$ であるこ

\*チャネル幅 $W$ 及び光強度 $B$ に比例するので、 $I_{off}$ と $I_{photo}$ とは下記(9)式の関係を満たす。

$$I_{off} = I_{photo} \cdot (W / 4) \cdot B \dots (9)$$

【0067】そこで、上記(9)式と(8)式より $I_{photo}$ を消去すると、下記(10)式のようになる。

$$【0068】$$

$$I_{off} = 5 \times 10^{-15} \cdot Wd \dots (10)$$

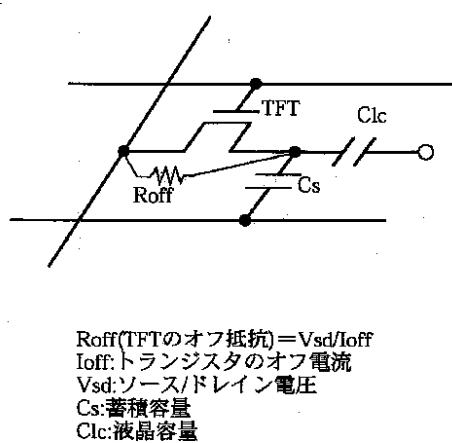

\*その理由について以下に説明する。図5にアクティブマトリックスの等価回路を示す。

10 【0070】TFTのOFF抵抗 $R_{off}$ が小さくなると、次の書き込みまで電荷が保持できなくなり電圧ロスとなる。時間T後の画素電圧 $V$ は(12)式で記述される。

$$V = V0 \{ 1 - \exp (T / (R_{off} \times C_{tot})) \} \dots (12)$$

\*2V以下に抑制するためには、バックライト照射状態でOFF電流を10 pA以下にする必要があることが確認される。

【0072】よって、前記(11)式の $I_{off}$ を10 pA以下とすると次式が得られる。

$$(R + 30) \cdot 10^{12} \cdot 10^{17} = 1 \times 10^6 \dots (6)$$

限らない。従って、バックライト輝度 $B$ を最高 $5000cd/m^2$ と仮定すると、前記(6)式は

$$(R + 30) \cdot W < 2 \times 10^2 \dots (2')$$

となり、前記(2')式を満たす薄膜トランジスタは、バックライトの輝度 $B$ に関係なく、即ち、透過、反射型を問わない薄膜トランジスタとすることができます。

【0075】尚、好ましくは、上記(2')式は、薄膜トランジスタの設計上の余裕を考慮して、下記(2)式で表すことができる。

$$30 (R + 30) \cdot W < 1 \times 10^3 \dots (2)$$

【0076】また、前記(11)式は、下記(11')式のように表すことができる。即ち、

$$(R + 30) \cdot W < (I_{off} \cdot 10^{17}) / B \dots (11')$$

とが確認できた。

【0080】尚、前記チャネル幅は $4\mu m$ で行っているが、チャネル領域のチャネル幅 $W$ を微細化し、 $2\mu m$ 以下とする場合には、特に、前記関係式(1)式、(2)式は薄膜トランジスタを作製する上で有効な指針となる。また、以下の実施の形態では、前記シミュレーションに基づき、TFTを作製したものについて具体的に説明する。

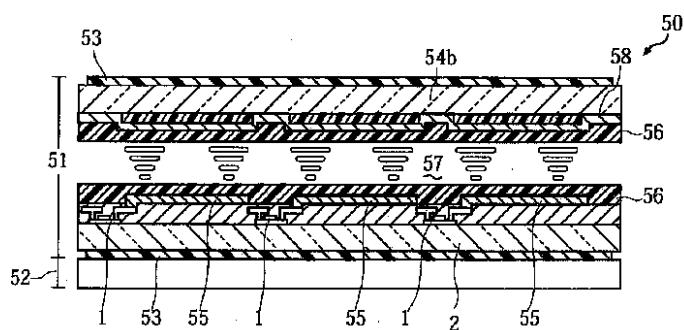

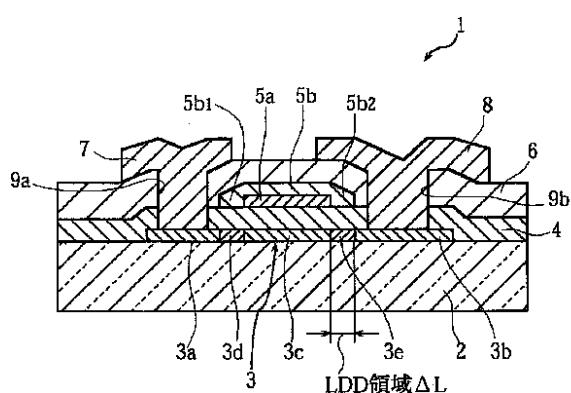

【0081】(実施の形態1-1)図7は、本発明の実施の形態1に係る薄膜トランジスタを画素スイッチング素子として使用した液晶表示装置の概略断面図、図8は、本発明の実施の形態1に係る薄膜トランジスタの概略断面図、図9は、図8の概略平面図である。

【0082】図7に示すように、液晶表示装置50は、液晶パネル部51と、該液晶パネル部51の裏面側に配置されたバックライト部52等とを備えた透過型液晶表

示装置である。前記液晶パネル部51は、偏光板53・53、ガラス基板2・54b、マトリックス状に配置された薄膜トランジスタ1、画素電極55、配向膜56、液晶層57、共通電極58等より構成されている。

【0083】前記ガラス基板2上には薄膜トランジスタ1(以下、TFTと称する)および画素電極55を形成し、前記基板54bには共通電極58を形成している。また、前記基板2・54bにはそれぞれ、ポリイミド樹脂等よりなる配向膜56・56を形成し、前記配向膜56・56を配向方向が互いに直交する方向に予めラビング処理しており、基板2・54bは、図示せぬスペーサーを介して対向配置されている。

【0084】また、前記基板2・54b間には液晶層57が挟持されており、前記液晶層57内の液晶は90度捻じれ配向している。さらに、前記2・54bの外側面には偏光板53・53が、規制する光の振動方向が互いに平行となるように配置されている。

【0085】また、前記液晶パネル部51の裏面(下方)側にはバックライト部52を配置している。前記バックライト部52は、冷陰極管等の発光素子と、光を均一化するための光分散板等より構成されている。

【0086】次に、前記薄膜トランジスタについて、図8、図9を用いて説明する。

【0087】薄膜トランジスタ1は、ガラス基板2上に、膜厚が500の多結晶シリコン層3、膜厚が100のSiO<sub>2</sub>(二酸化シリコン)から成るゲート絶縁層4、アルミニウムから成るゲート電極5a、及びSiO<sub>2</sub>から成る層間絶縁層6が順に積層されて構成されている。

【0088】また、前記多結晶シリコン層3は、ゲート電極5aの直下に位置するチャネル領域3cと、濃度が高いソース領域3a(n+層)と、不純物濃度が高いドレイン領域(n+層)3bとから構成されている。また、本実施の形態においては、LDD領域(n-層)3d・3eの長さLは0.4μmに設定されている。また、前記チャネル領域3cのチャネル幅Wは5μmに設定されている。

【0089】ここで、前記ドレイン領域のシート抵抗をR(k/ )、このアクティブマトリックスTFTが使われる液晶表示装置50のバックライト部52の輝度をB(cd/m<sup>2</sup>)、前記チャネル領域3cのチャネル幅をW(μm)とした場合、下記(6)式を満たすように設計する。

$$(R + 30) \cdot B \cdot W = I_{off} < 1 \times 10^{-6} \dots (6)$$

【0090】また、TFT1には、更に、例えばアルミニウムから成るソース電極7及びドレイン電極8が設けられており、ソース電極7は、ゲート絶縁層4及び層間絶縁層6に形成されているコンタクトホール9aを介して、ソース領域3aに接続され、また、ドレイン電極8は、ゲート絶縁層4及び層間絶縁層6に形成されている

コンタクトホール9bを介して、ドレイン領域3bに接続されている。

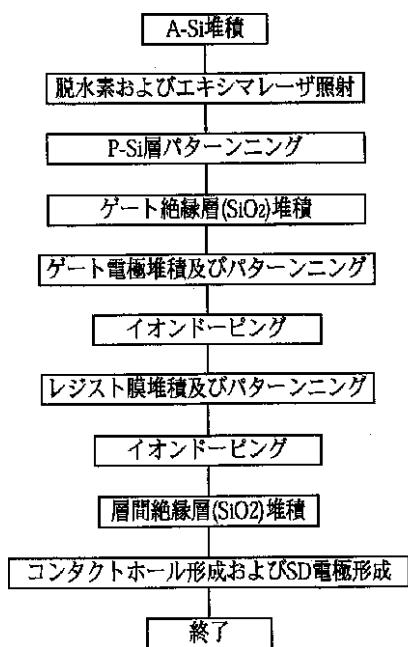

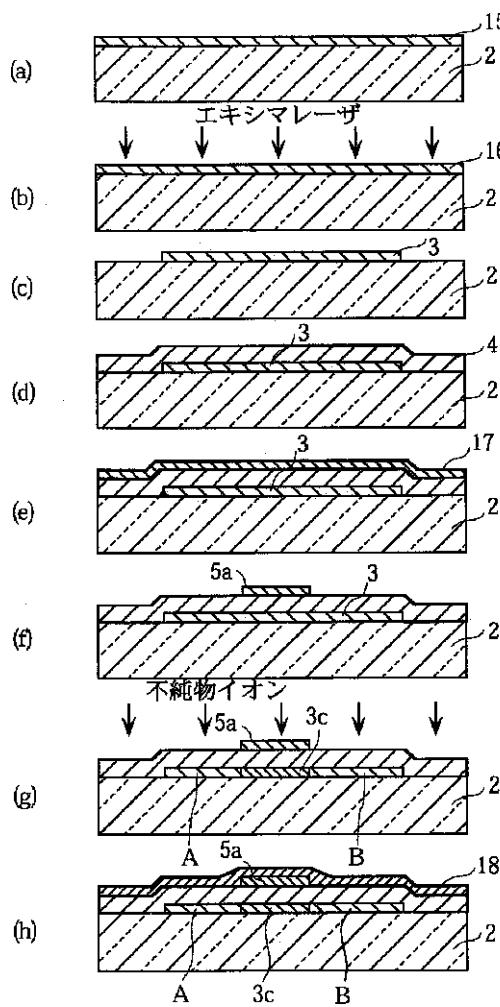

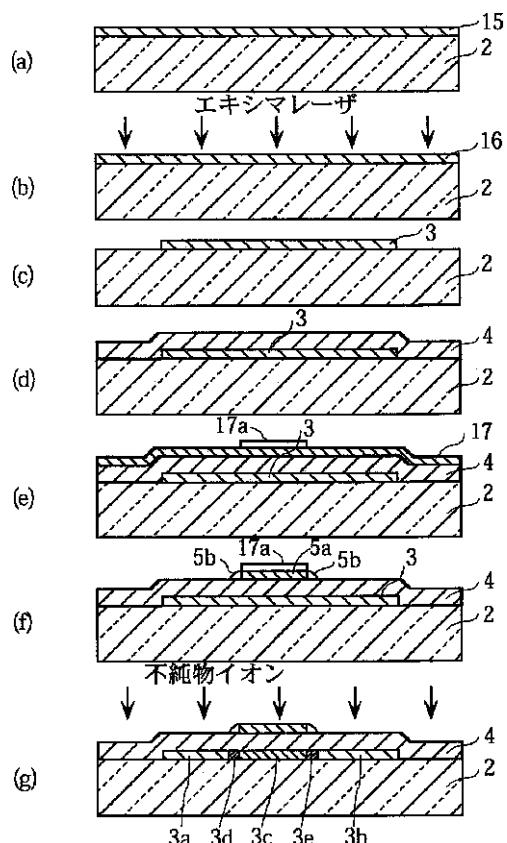

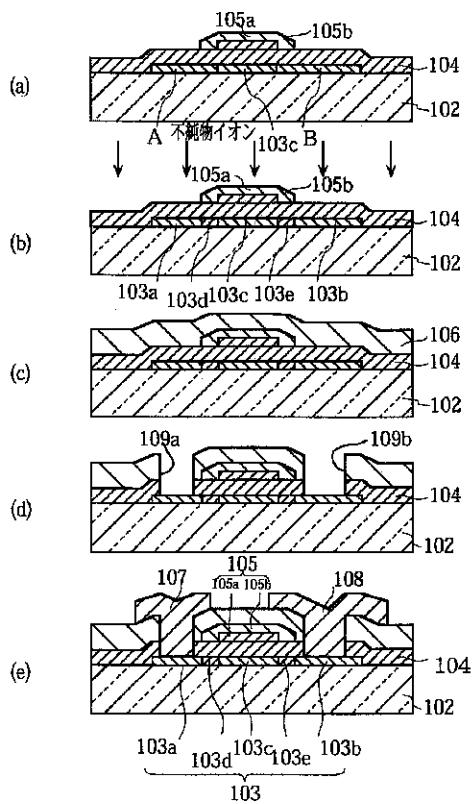

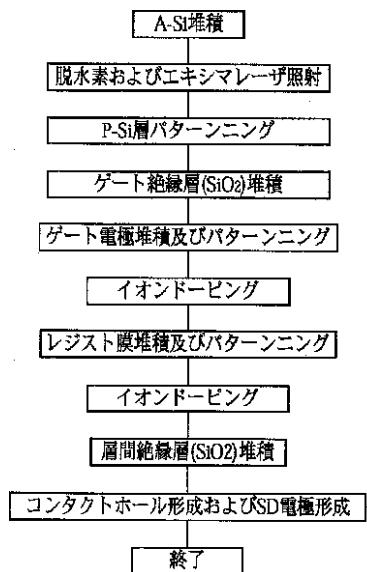

【0091】次に、薄膜トランジスタの製造方法を説明する。図10は本発明の実施の形態1-1に係る薄膜トランジスタの製造方法を示す概略断面図、図11は同じく薄膜トランジスタの製造方法を示す概略断面図、図12は同じく薄膜トランジスタの製造方法を示すフローチャートである。

【0092】(1)先ず、プラズマCVD法により、ガラス基板2上に膜厚が500のa-Si層15を堆積させ、次いで400で脱水素処理を行なう(図10(a))。この脱水素処理は、結晶化を行う際に水素の脱離によるSi膜のアブレーションの発生を防ぐことを目的としている。尚、a-Siを形成する工程はプラズマCVD以外でも減圧CVDやスパッタなどのプロセスを用いることは可能である。また、プラズマCVDその他の方法を用いてポリシリコン膜を直接堆積することもできる。この場合は、後述するレーザーによるアニール工程が不要となる。

【0093】(2)次いで、波長308nmのエキシマーレーザーを用いたレーザーアニールによりa-Si層15の溶融再結晶化(p-Si化)を行ない、多結晶シリコン層16を形成する(図10(b))。

【0094】(3)次いで、多結晶シリコン層16を所定形状に島化して、多結晶シリコン層3を形成する(図10(c))。

【0095】(4)次いで、ガラス基板2上に、多結晶シリコン層3を覆うようにして、ゲート絶縁層4となる、厚さが1000のSiO<sub>2</sub>(二酸化シリコン)層を形成する(図10(d))。

【0096】(5)次いで、ゲート電極5aとなる、アルミニウムから成る金属層17を製膜する(図10(e))。

【0097】(6)次いで、金属層17を所定形状にパターニングしてゲート電極5aを形成する(図10(f))。

【0098】(7)次いで、ゲート電極5aをマスクとして使用し、不純物のドープを行なう(図10(g))。具体的にはイオンドーピング法により不純物としてリンイオンをドーピングする。これにより、ゲート電極5aの直下に位置するチャネル領域3cは、不純物がドープされない領域となる。そして、多結晶シリコン層3のチャネル領域3cを除く領域は、不純物がドープされた層となる。尚、この場合のドーピング加速電圧は80kVでビーム電流密度は1μA/cm<sup>2</sup>とし、高加速n型領域を作成するものである。

【0099】(8)次いで、ゲート電極5aを覆って、フォトレジスト18を製膜する(図10(h))。

【0100】(9)次いで、フォトレジスト18を異方性エッチングによりパターン状に形成して、レジスト膜

5 b を形成する(図11(i))。この際、異方性エッチングにより正確なレジスト膜5 b のパターンを形成することができる。

【0101】(10)次いで、図11(j)に示すように、レジスト膜5 b をマスクとして使用し、第2回目の不純物のドープを行なう。具体的には、イオンドーピング法により不純物としてリンイオンをドーピングする。この場合のドーピング加速電圧は12kVでビーム電流密度は0.5μA/cm<sup>2</sup>とし、低加速で高濃度のn型領域を作成するものである。

【0102】(11)次いで、層間絶縁層(SiO<sub>x</sub>)6を製膜する(図11(k))。

【0103】(12)次いで、層間絶縁層6及びゲート絶縁層4にコンタクトホール9a・9bを開口する(図11(L))。

【0104】(13)そして、スパッタ法により、例えばA1などの金属層をコンタクトホール9a・9bに充填し、金属層の上部を所定形状にパターニングしてソース電極7及びドレイン電極8を形成する(図11(m))。こうして、TFT1が作製される。

【0105】前記の例では、nチャネルTFTについて説明したけれども、pチャネルTFTについても同様の製造プロセスにより製造することができる。

【0106】前記製造方法により作成した薄膜トランジスタの裏面より、5000cd/m<sup>2</sup>の光を照射した場合、OFF電流はほぼ5pAとなる。前述したように、バックライト照射状態でOFF電流を10pA以下にする必要があるので、本実施の形態に係る薄膜トランジスタは、良好な表示特性を確保できる。

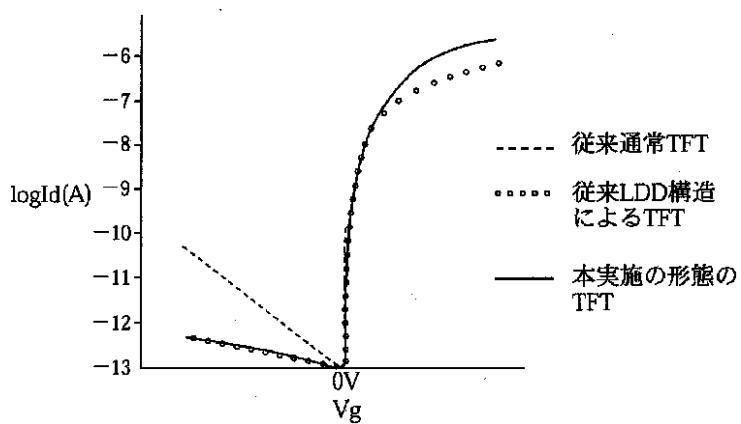

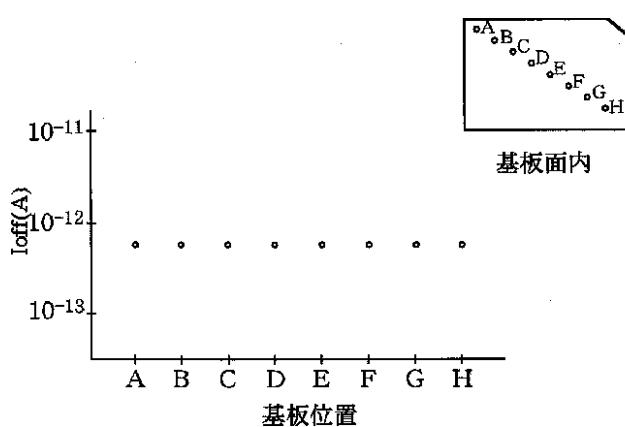

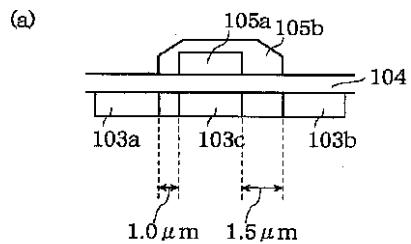

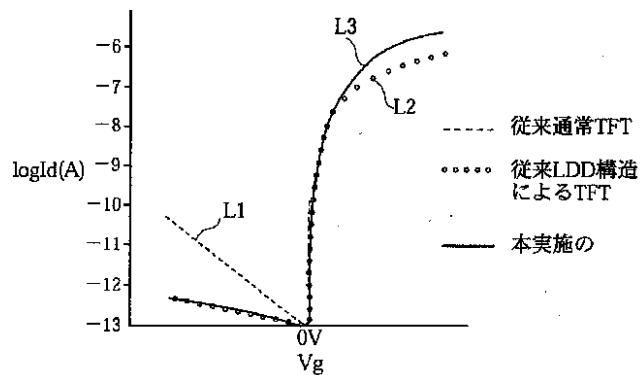

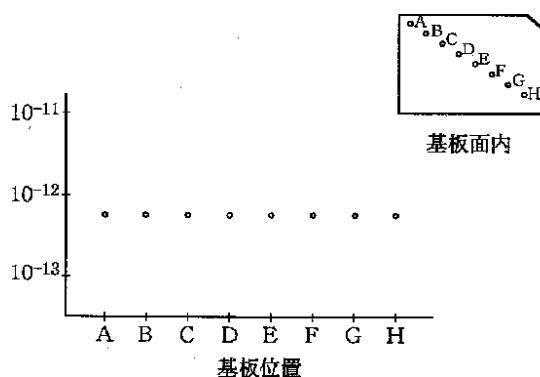

【0107】また、薄膜トランジスタの電圧/電流特性を図13に、更にOFF電流の基板面内のばらつきを図14に示す。図13に示すように、本実施の形態に係るTFT1(L3のグラフ)は、安定した大きいON電流と小さいOFF電流を確保できた。また、図14より、このようにして作製されたTFT1は、基板面内上でのばらつきを小さくすることができる。

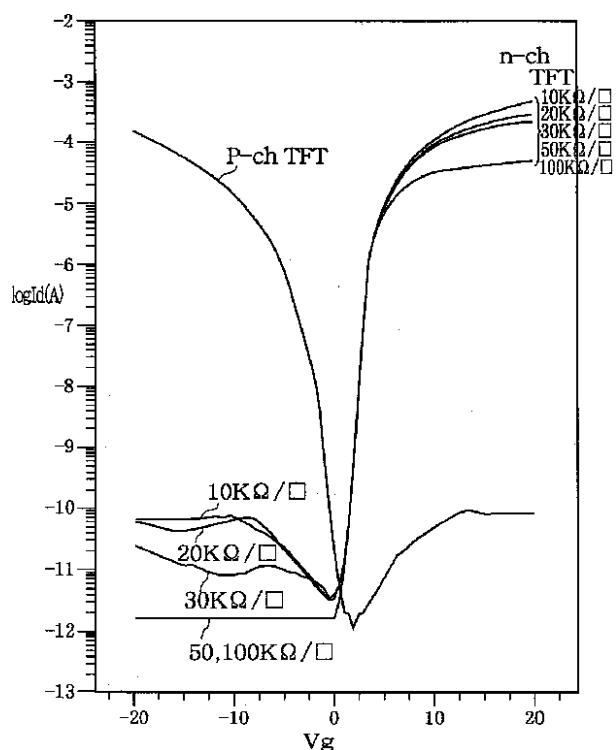

【0108】図15にn型領域の濃度をパラメータとした、薄膜トランジスタのVg-Id特性をシミュレーションした結果を示す。LDD領域のシート抵抗が20k

/以下でOFF電流は急激に大きくなる。従って、\*40

\*LDD領域のシート抵抗は少なくとも20k/以上の値が必要である。一方、LDD領域のシート抵抗を100k/以上にした場合、トランジスタのON電流が低下しパネルの動作が不安定となった。従って、LDD領域のシート抵抗の範囲は、20k/以上100k/以下とすることが望ましい。

【0109】一般的に、バックライト輝度は最大5000cd/m<sup>2</sup>程度であり、その場合、光伝導電流を10pA以下に抑えるための空乏層幅Wdを求める以下

10 ようになる。即ち、前記(10)式にW=4、B=5000、I<sub>off</sub>=10×10<sup>-12</sup>を代入することにより空乏層幅を求めることができ、Wd=0.4μmとなる。

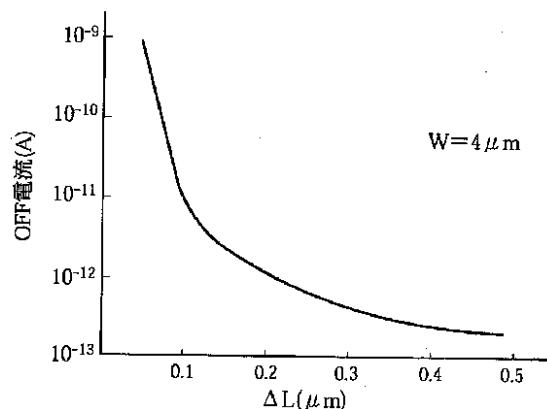

【0110】前記空乏層幅は、LDD領域の長さ以上にならないので、LDD領域の長さLを0.4μm以下とすることにより実効的な空乏層領域が0.4μm以下となり、光伝導電流を抑制(10pA以下と)した構成とすることができる。尚、LDD領域が0.1μmより小さくなると電界緩和効果がなくなり、図2(b)に示すように、OFF電流が増大するので、前記LDD領域20は0.1μmより大きい方が望ましい。

【0111】また、前記(10)式において、バックライト輝度Bが、例えば2000cd/m<sup>2</sup>の場合には、空乏層幅Wdは1μmとなる。

【0112】従って、空乏層幅は、LDD領域の長さ以上にならないので、LDD領域の長さLを1.0μm以下とすることにより実効的な空乏層領域が1.0μm以下となり、光伝導電流を抑制することができる。尚、より好ましくは0.4μm以下とするのが良い。

【0113】また、検査工程において、LDD領域が1.0μmを超えるようなデバイスはOFF特性を満足できない。従って、LDD領域の長さLが1.0μm以下であるものを良品とする検査工程を行うことにより、良品、不良品を選別することができる。パネル工程での材料ロスを削減することができる。

【0114】また、表1に示すように、実験例1~3(即ち、前記(2)式を満たすもの)は、光照射時のOFF電流を抑制することができるが、実験例4、5(即ち、前記(6)式を満たさないもの)は、光照射時のOFF電流を抑制することができないことが確認された。

【表1】

|      | B(cd/m <sup>2</sup> ) | W(μm) | R(kΩ/□) | OFF電流 |

|------|-----------------------|-------|---------|-------|

| 実験例1 | 3000                  | 4     | 50      | ○     |

| 実験例2 | 5000                  | 2     | 50      | ○     |

| 実験例3 | 5000                  | 3     | 30      | ○     |

| 実験例4 | 3000                  | 4     | 80      | ×     |

| 実験例5 | 5000                  | 4     | 50      | ×     |

【0115】このようにして、前記(6)式により、新たに制御できる因子(ドレン領域のシート抵抗)とチャネル領域のチャネル幅との関係によって、光照射時のOFF電流(光伝導電流)を抑制する範囲を規定すること

50 ができる。よって、上記(6)式の関係を満たす薄膜トランジスタを作製することにより、OFF電流の増加を抑えることができるので、クロストークや輝度傾斜を防ぐことができ、高性能、高信頼性を実現した薄膜トラン

ジスタの提供をすることができる。

【0116】(実施の形態1-2)本発明の実施の形態1-2に係る薄膜トランジスタの製造方法について説明する。

【0117】本実施の形態1-2の薄膜トランジスタは陽極酸化によって、LDD領域の長さを0.2μm~0.5μmと小さく形成されたものである。これより、ドレイン側の領域は高濃度不純物領域となるので、LDD領域の長さ以上に空乏層幅が広がることはないので、光伝導電流を抑制することができるものである。具体的な製造方法の説明を以下に説明する。図17は本発明の実施の形態1-2に係る薄膜トランジスタの製造方法を示す概略断面図、図18は同じく、薄膜トランジスタの製造方法を示す概略断面図である。

【0118】前述した実施の形態1-1と同様にして、ガラス基板2上にa-Si層15を堆積させ、次いで、波長308nmのエキシマレーザーを用いたレーザーニールによりa-Si層15の溶融再結晶化(p-Si化)を行ない、多結晶シリコン層16を形成する。次いで、多結晶シリコン層16を所定形状に島化して、多結晶シリコン層3を形成する。次いで、ガラス基板2上に、多結晶シリコン層3を覆うようにして、ゲート絶縁層4を形成する。(図17(a)~(d))。

【0119】次いで、金属層17を製膜し、該金属層17上にフォトレジスト17aをパターン状に形成し、エッチング技術により前記金属膜17をパターニングしてゲート電極5aを形成する。次いで、ゲート電極5aの側面を陽極酸化して、酸化絶縁層5bを形成する。(図17(f))。

【0120】次いで、図17(g)に示すようにして、ゲート電極5aをマスクとして使用し、不純物のドープを行なう。具体的にはイオンドーピング法により不純物としてリンイオンをドーピングする。これにより、ゲート電極5aの直下に位置するチャネル領域3cは、不純物がドープされない領域となる。そして、酸化絶縁層5b・5b直下に位置する領域にLDD領域3d・3eが形成され、それらの外側にチャネル領域3a、ドレイン領域3bが形成される。

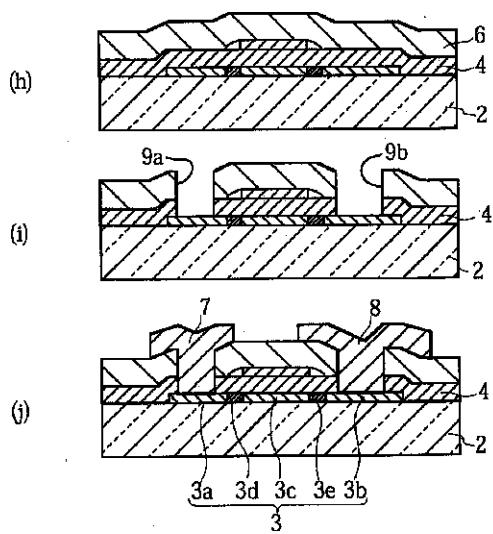

【0121】次いで、図18(h)~(j)に示すようにして、層間絶縁層(SiO<sub>x</sub>)6を製膜し、次いで、層間絶縁層6及びゲート絶縁層4にコンタクトホール9a・9bを開口し、そして、スパッタ法により、例えばA1などの金属層をコンタクトホール9a・9bに充填し、金属層の上部を所定形状にパターニングしてソース電極7及びドレイン電極8を形成する。こうして、TFTが作製される。

【0122】本実施の形態の陽極酸化によれば、LDD領域の長さを0.2μm~0.5μmと小さくすることが可能である。これよりドレイン側の領域は高濃度不純物領域となるので、本長さ以上に空乏層幅が広がること

がない。従って、光伝導電流を小さく抑えることができる。

【0123】これにより、薄膜トランジスタのOFF時には、前記低濃度不純物領域がキャリアの枯渇する高抵抗層となるためOFF電流の低減を図ることができる。そして、前記(2)式より、LDD領域の長さの指針を決めることができ、OFF電流低減のために必要以上にLDD領域を確保する必要はなくなる。また、前記(2)式は、更に(6)式を満たすことにより、薄膜トランジスタのON時には、ゲート電極からの電界の作用により、ゲート電極下の低濃度不純物領域はキャリアとなる電子が蓄積して低抵抗領域となり、ON電流の減少は起こらない。よって、(2)式および(6)式を満たす薄膜トランジスタは、ON電流を十分確保すると共にOFF電流を少なく押さえることが可能となる。

【0124】加えて、不純物ドーピングは、加速電圧が10kV以上30kV以下及びビーム電流密度が0.05μA/cm<sup>2</sup>以上1μA/cm<sup>2</sup>以下の低速でのイオンドーピング法を用いることにより、イオンドーピング時でのイオンの加速電圧が低いために、ドーピング時における損傷を少なくすることができます。また、不純物ドーピング時でレジストをマスクとした場合でも、レジストが変質することなくきれいに除去できる。

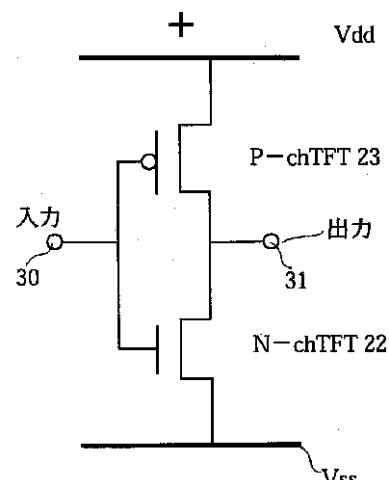

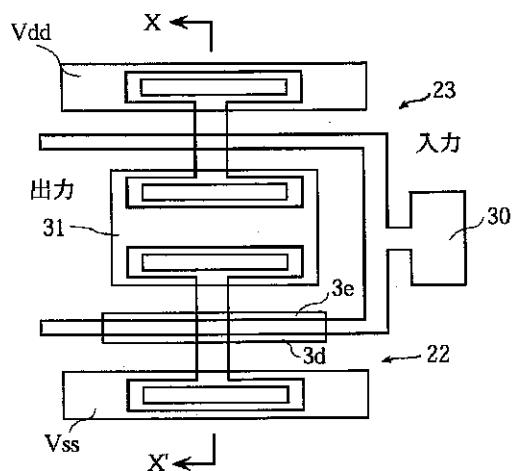

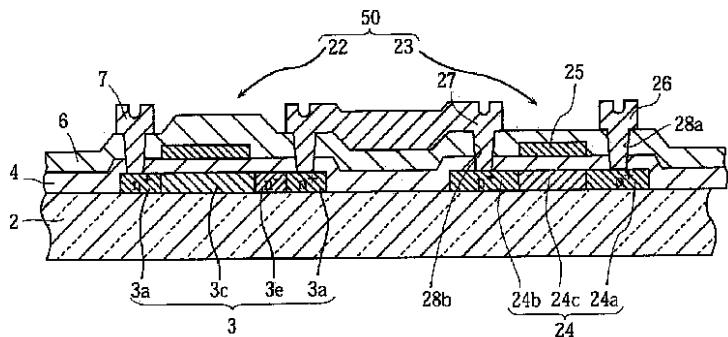

【0125】(実施の形態1-3)本発明の実施の形態3について、図19~図22を参照しながら説明する。図19は本発明の実施の形態1-3に係る薄膜トランジスタを用いたC-MOSインバータの配線パターンを示す平面図であり、図20はその等価回路図であり、図21は図19の矢視X-X'断面図である。

【0126】C-MOSインバータ50は、例えば液晶表示装置の駆動回路を構成する。このC-MOSインバータ50は、nチャネルTFT22とpチャネルTFT23とから構成されている。nチャネルTFT22は、上記実施の形態1のnチャネルTFT1と同様の構成を有しており、対応する部分には同一の参照符号を付す。

【0127】pチャネルTFT23は、LDD構造でない通常タイプのTFTである。即ち、TFT23は、ガラス基板2上に、多結晶シリコン層24、SiO<sub>2</sub>(二酸化シリコン)から成るゲート絶縁層4、アルミニウムから成るゲート電極25、及びSiO<sub>2</sub>から成る層間絶縁層6が、順に積層されて構成されている。多結晶シリコン層24は、ゲート電極25の直下に位置するチャネル領域24c、チャネル領域24cの両側に配置されるソース領域24a(p+層)及びドレイン領域24b(p+層)とから構成されている。更に、このTFT23には、例えばアルミニウムから成るソース電極26及びドレイン電極27が設けられている。ソース電極26は、ゲート絶縁層4及び層間絶縁層6に形成されているコンタクトホール28aを介して、ソース領域24aに接続されている。また、ドレイン電極27は、ゲート絶

縁層4及び層間絶縁層6に形成されているコンタクトホール28bを介して、ドレイン領域24bに接続されている。そして、nチャネルTFT22のゲート電極5及びpチャネルTFT23のゲート電極25は、図20に示すように入力端子30に共通に接続されている。また、nチャネルTFT22のドレイン電極8及びpチャネルTFT23のドレイン電極27は、図19に示すように出力端子31に共通に接続されている。

【0128】本実施の形態1-3においては、nチャネルTFTのドレイン側のみを前記実施の形態1-1で説明したLDD構造とし、TFTのサイズを小さくすることができ、ソース・ドレイン間距離を6μm程度に抑えることが可能であり、ソース、ドレインの両方にLDD領域を形成する場合に比較して約50%以下のサイズとすることができる、TFTの微細化を図ることができる。

【0129】尚、nチャネルTFT及びpチャネルTFTの両者ともLDD構造とするようにしてもよい。但し、アレイ基板に占める回路面積を小さく抑えるために、nチャネルTFT及びpチャネルTFTのいずれか一方のみをLDD構造とする場合には、nチャネルTFT側とするのが望ましい。なぜなら、pチャネルTFTのキャリアであるホールと、nチャネルTFTのキャリアである電子の各移動度を比較すると、電子の方が格段に大きい。従って、pチャネルTFTとnチャネルTFTとに、同じ電界が印加された場合、nチャネルTFTの方がキャリアによって受ける衝撃が大きく、そのためnチャネルTFTの方が劣化し易い。よって、TFTの劣化を防止して信頼性の向上を図る観点からすると、nチャネルTFTの方をLDD構造とするのが望ましいからである。

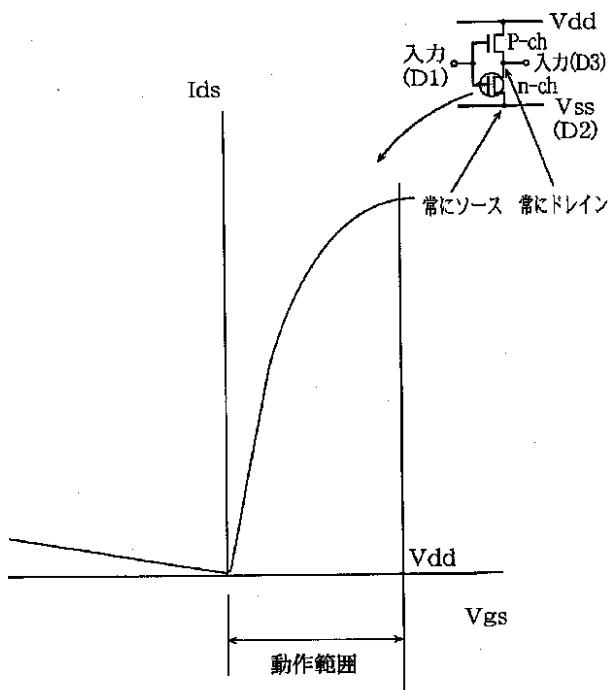

【0130】C-MOSインバータにおけるon/off時でのn-chトランジスタのバイアス状態における動作ポイントを図22に示す。このようにインバータにおけるn-chTFTにおいては、マイナス側の電源に対しゲート電極の極性は常に0Vより高い電圧で動作する。したがってマイナス側の電源は常にn-chTFTのソース電極となって作用し、出力側は常にドレイン電極となって作用する。従ってこの部分を出力側部分のみを上記構成とした回路を用いることは、アレイ基板における回路部分のしめる面積の縮小に寄与する。またこの部分での寄生容量の減少に寄与する。

【0131】(その他の事項)実施の形態1-1~1-3では、1種類の濃度を有するLDD領域について説明したが、本発明はこれに限定されるものではなく、濃度差が異なる複数のLDD領域を設けるようにしてもよい。即ち、LDD領域を、チャネル領域に向かうに連れて不純物濃度が段階的に低下していく複数の接合領域から構成することによって、多段階的に不純物濃度を変化させることができるので、半導体層での電界の集中をより緩和することができる。

【0132】また、前記LDD領域はドレイン領域とチャネル領域との間にのみ形成されても良く、このように構成することにより、OFF電流の低減等の効果を奏すると共に、薄膜トランジスタの面積を小さくすることが可能となる。

【0133】また、実施の形態1-1~1-3では、トップゲート型のTFTを用いて説明したが、ボトムゲート型のTFTに本発明を適用することもできる。

【0134】また、実施の形態1-1~1-3で説明した薄膜トランジスタは、液晶表示装置以外にも、EL装置にも適用することが可能である。即ち、実施の形態1-1~1-3に記載の薄膜トランジスタをスイッチング素子として基板上に複数形成し、該基板を備えたEL装置とすることにより、光伝導電流を抑制した構成とすることができる。

【0135】[第2の発明群]

(第2の発明群の概念)本発明は、薄膜トランジスタ(以下「TFT」と称する)のOFF電流を抑えるとともに、LDD領域の長さを必要最小限に押さえてON電流の減少を抑制する構成をとることにより、高性能、高信頼性を有するTFTを実現することを目的とするものである。そこで、本発明者らは、真に必要なLDD領域の長さを求めるために、LDD領域部分をシミュレーションにより動作解析を行い、電界のかかる領域がどの程度かを求めた。

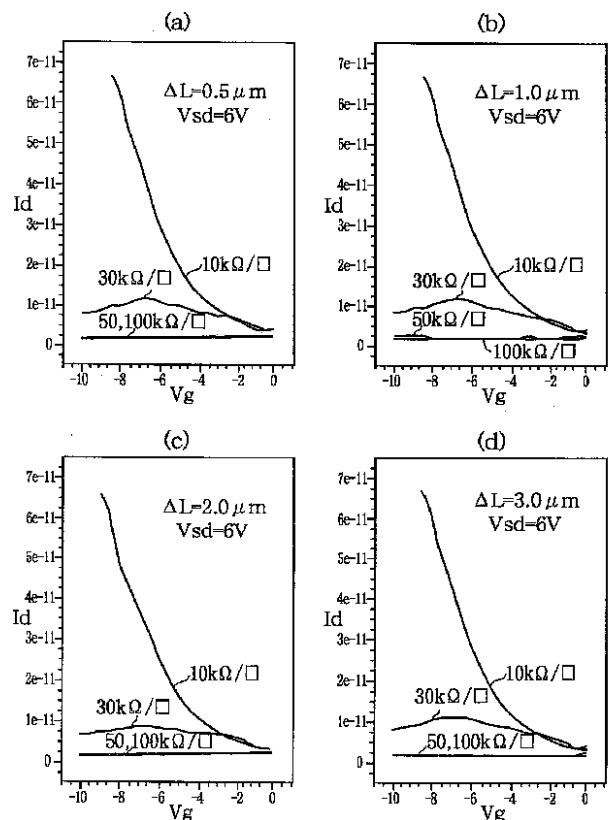

【0136】図23は、シート抵抗をパラメータとしてLDD領域を0.5μmから3μmまで変化させた場合のVg-Id特性をシミュレーションした結果を示すグラフである。

【0137】この結果より、Vg-Id特性はLDD領域の濃度に対して大きな依存性を持つが、LDD領域の長さに対しては依存性を持たないことが確認された。以下にこの原因について考察する。

【0138】図24にチャネル領域とLDD領域において、TFTをOFF状態にした場合(Vg=-10V、Vd=6V時)の電界をシミュレーションした結果を示す。

【0139】前記シミュレーション結果より、電界のかかる領域はシート抵抗に依存しており、シート抵抗が20k/の場合は0.4μm程度、シート抵抗が100k/の場合は1.0μmであることが確認できた。

【0140】従って、電界のかかる領域以上にLDD領域を大きくしても電界の緩和効果には効果が無く、単にトランジスタのチャネル領域に抵抗が直列に挿入されるだけであることが解った。

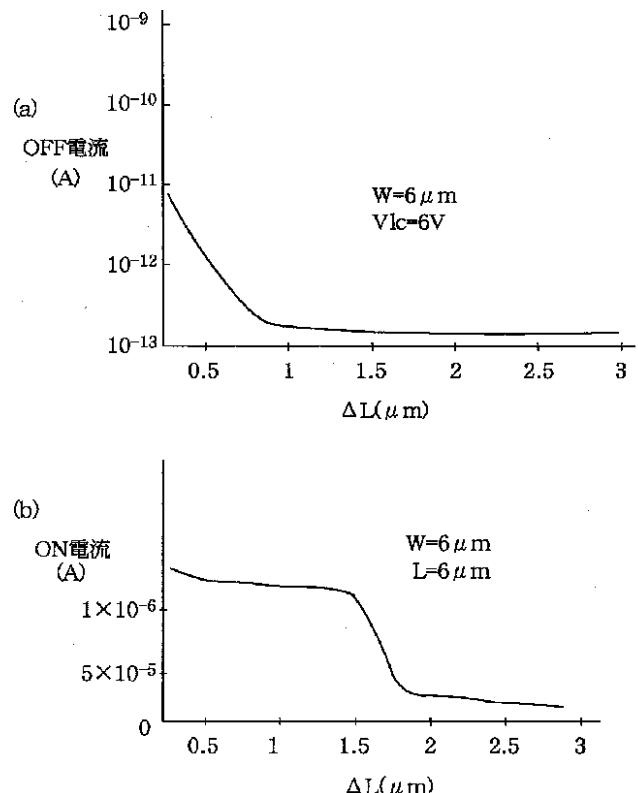

【0141】また、図25は、実際のLDD領域を持つTFTの、LDD領域の長さ(L)とOFF電流及びLDD領域の長さ(L)とON電流との関係を示すグラフである。尚、LDD領域のシート抵抗は100k

/ である。

【0142】図25(a)に示すように、LDD領域を1μmより長くしても、OFF電流の低減効果は無く、前述したシミュレーション結果を反映している。また、図25(b)に示すように、LDD領域が1.5μmより長くなると、ON電流を十分確保することができずON電流は低減した。この結果より、LDD領域の範囲を1μm以上1.5μm以下とすることにより、ON電流を十分確保すると共にOFF電流を小さく押さえることが可能となる。尚、以下の実施の形態では、前記シミュレーションに基づき、TFTを作製したものについて具体的に説明する。また、実際のTFTの作製工程においては、前述のLDD領域を確実に確保するために、後に説明するが、マスク合わせの際の合わせマークにより決定することができる。

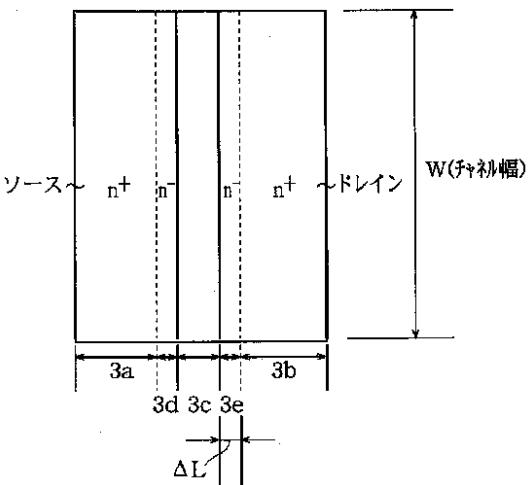

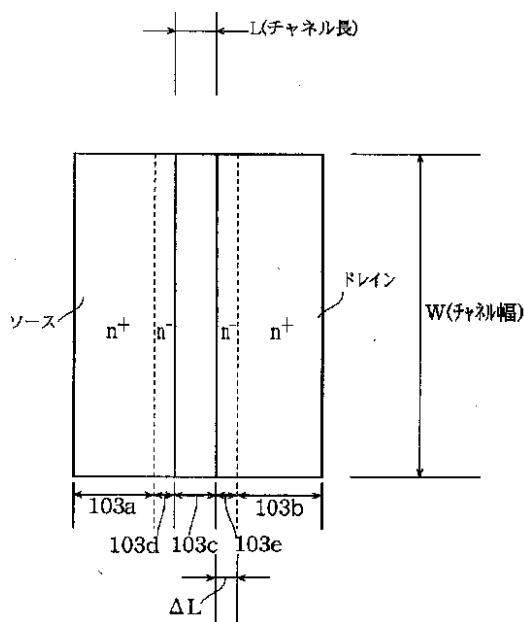

【0143】(実施の形態2-1)図26は、実施の形態2-1に係る薄膜トランジスタの簡略化した断面図、図27は、図26の概略平面図である。

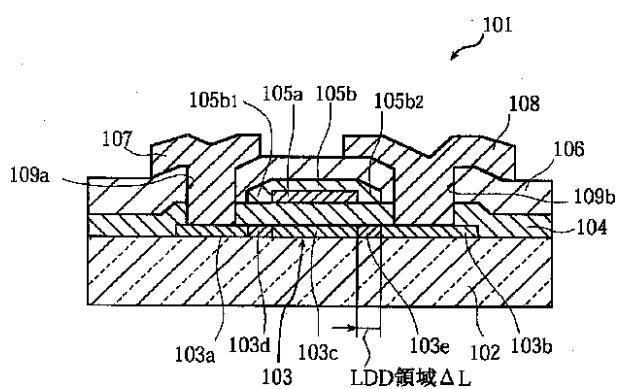

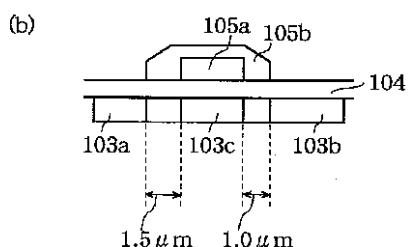

【0144】本実施の形態2-1では、本発明をnチャネル薄膜トランジスタに適用した例が示されている。この薄膜トランジスタ(以下、TFTと称する)101は、ガラス基板102上に、膜厚が500の多結晶シリコン層103、膜厚が1000のSiO<sub>2</sub>(二酸化シリコン)から成るゲート絶縁層104、アルミニウムから成るゲート電極105、及びSiO<sub>2</sub>から成る層間絶縁層106が順に積層されて構成されている。前記ゲート電極105aは、レジスト膜105bに覆われて形成されている。尚、前記レジスト膜105bの代わりに金属膜を用いても良い。

【0145】また、前記多結晶シリコン層103は、ゲート電極105aの直下に位置するチャネル領域103cと、不純物濃度が高いソース領域103a(n+層)と、不純物濃度が高いドレイン領域(n+層)103bと、不純物濃度が低い低濃度不純物領域(LDD領域:n-層)103d, 103eとから構成されている。低濃度不純物領域103dは、ソース領域103aとチャネル領域103cとの間に介在し、低濃度不純物領域103eは、ドレイン領域103bとチャネル領域103cとの間に介在している。これら低濃度不純物領域103d, 103eは、レジスト膜105bのゲート電極105aからはみ出た部分105b1, 105b2の直下に位置している。従って、低濃度不純物領域103dとソース領域103aとの接合面は、レジスト膜105bの端面(図1の左側端面)とほぼ一致しており、低濃度不純物領域103dとチャネル領域103cとの接合面は、ゲート電極105aの端面(図1の左側端面)とほぼ一致している。また、低濃度不純物領域103eとドレイン領域103bとの接合面は、レジスト膜105bの端面(図1の右側端面)とほぼ一致しており、低濃度不純物領域103dとチャネル領域103cとの接合面

は、ゲート電極105aの端面(図1の右側端面)とほぼ一致している。また、本発明においては、前記低濃度不純物領域の長さLは、1μm以上1.5μm以下、チャネル幅Wは5μmに設定されている。

【0146】また、TFT101には、更に、例えばアルミニウムから成るソース電極107及びドレイン電極108が設けられており、ソース電極107は、ゲート絶縁層104及び層間絶縁層106に形成されているコンタクトホール109aを介して、ソース領域103aに接続され、また、ドレイン電極108は、ゲート絶縁層104及び層間絶縁層106に形成されているコンタクトホール109bを介して、ドレイン領域103bに接続されている。

【0147】次に、本発明の実施の形態2-1に係る薄膜トランジスタの製造方法を説明する。図28、図29は本発明の実施の形態2-1に係る薄膜トランジスタの製造方法を示す概略断面図、図30は、本発明の実施の形態2-1に係る薄膜トランジスタの製造方法を示すフローチャートである。

【0148】(1)先ず、プラズマCVD法により、ガラス基板102上に膜厚が500のa-Si層105を堆積させ、次いで400で脱水素処理を行なう(図28(a))。この脱水素処理は、結晶化を行なう際に水素の脱離によるSi膜のアブレーションの発生を防ぐことを目的としている。尚、a-Siを形成する工程はプラズマCVD以外でも減圧CVDやスパッタなどのプロセスを用いることは可能である。またプラズマCVDその他の方法を用いてポリシリコン膜を直接堆積することもできる。この場合は、後述するレーザーによるアニール工程が不要となる。

【0149】(2)次いで、波長308nmのエキシマーレーザーを用いたレーザーニールによりa-Si層115の溶融再結晶化(p-Si化)を行ない、多結晶シリコン層116を形成する(図28(b))。

【0150】(3)次いで、多結晶シリコン層116を所定形状に島化して、多結晶シリコン層103を形成する(図28(c))。

【0151】(4)次いで、ガラス基板102上に、多結晶シリコン層103を覆うようにして、ゲート絶縁層104となる、厚さが1000のSiO<sub>2</sub>(二酸化シリコン)層を形成する(図28(d))。

【0152】(5)次いで、ゲート電極105aとなる、アルミニウムから成る金属層117を製膜する(図28(e))。

【0153】(6)次いで、金属層117を所定形状にパターニングしてゲート電極105aを形成する(図28(f))。

【0154】(7)次いで、ゲート電極105aをマスクとして使用し、第1回目の不純物のドープを行なう(図28(g))。具体的にはイオンドーピング法によ

り不純物としてリンイオンをドーピングする。これにより、ゲート電極105aの直下に位置するチャネル領域103cは、不純物がドープされない領域となる。そして、多結晶シリコン層103のチャネル領域103cを除く領域A、Bは、不純物がドープされたn-層となる。尚、この場合のドーピング加速電圧は80kVでビーム電流密度は $1\mu\text{A}/\text{cm}^2$ とし、高加速で低濃度のn型領域を作成するものである。

【0155】(8)次いで、ゲート電極105aを覆つて、フォトレジスト118を製膜する(図28(h))。

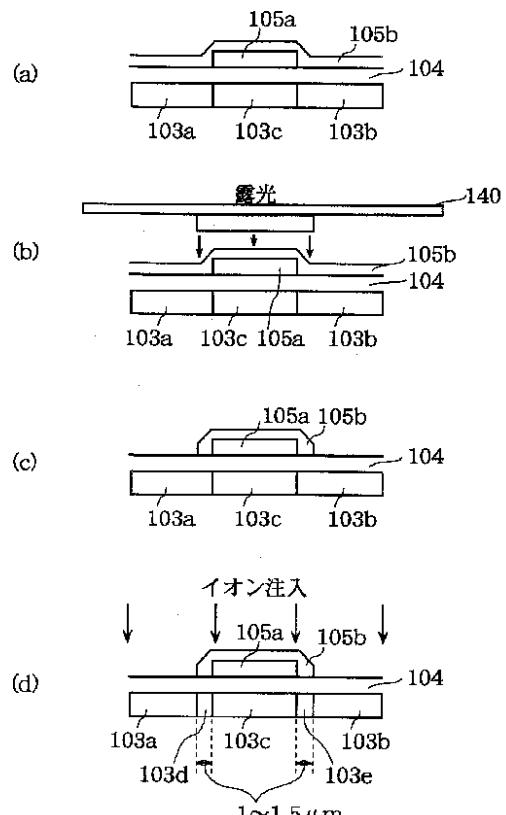

【0156】(9)次いで、フォトレジスト118をバーニングしてレジスト膜105bを形成する(図29(a))。ここで、(9)の工程については、図31～図34を用いて詳しく説明する。図31は、LDD領域を形成する工程を説明する概略断面工程図、図32は、フォトマスクと基板の斜視図、図33は同じく平面図、図34は、LDD領域形成後の薄膜トランジスタの概略断面図である。

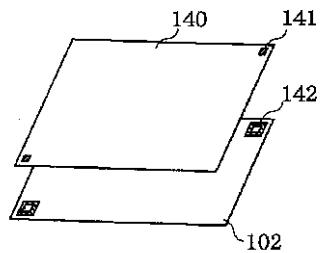

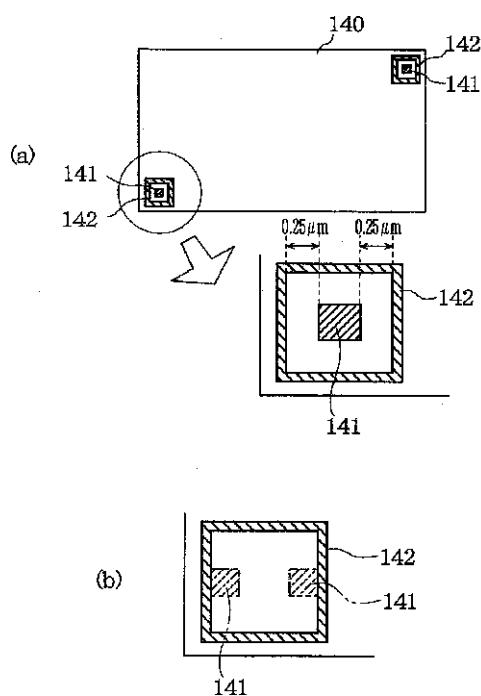

【0157】図7に示すように、フォトマスク140と基板102とは対向するように配置され、フォトマスク140の上方位置には位置合わせ用光源(図示せぬ)が配置されており、前記位置合わせ用光源よりフォトマスク140及び基板102にそれぞれ形成された位置合わせマーク141・142にレーザービームを入射し、それぞれの位置合わせマークの位置信号を読むことによって位置合わせを行うようにしている。

【0158】前記フォトマスク140の所定位置(フォトマスクの隅の102箇所)には、略正方形の位置合わせマーク141が形成されている。また、フォトマスク140の中央位置には、基板102に転写する遮蔽膜のパターン(図示せぬ)が形成されている。

【0159】また、ガラス基板102上には、前記位置合わせマーク141と対応する位置に、位置合わせマーク142が形成されている。該位置合わせマーク142は、周囲を黒い領域で囲まれた略正方形の透明な領域とされている。尚、図示せぬが、前記位置合わせマーク141・142の形状は正方形に限定されるものではなく、例えば、円形状等とすることもできる。

【0160】そして、図33(a)に示すように、フォトマスク140と基板102との位置がずれていない場合には、フォトマスク140に形成された位置合わせマーク141は、基板102に形成された位置合わせマーク142の透明な領域の中央に位置し、その状態でLDD領域を形成した場合には、該LDD領域103d・103eの長さLは $1.25\mu\text{m}$ となるように設定されている。

【0161】また、前記基板102とフォトマスク140の位置がずれ、位置合わせマーク142内に位置合わせマーク141が入っていなければ、形成されるLDD

領域の長さは $1.5\mu\text{m}$ より大きくなることが分かり、従って、そのような場合には、位置合わせマーク142内に位置合わせマーク141が入るように基板とフォトマスクの位置を合わせるようにする。尚、前記位置合わせマーク141を位置合わせマーク142の中央に合わせるようにしても、実際には、図33(b)に示すように、紙面上、左右にぶれる場合がある。しかし、本発明の場合、位置合わせ装置の精度は $\pm 0.25\mu\text{m}$ であるので、位置合わせマーク42内に位置合わせマーク41を位置するようにすることができる。このようにして、図34に示すように、形成されるLDD領域3d・3eの長さを $1\sim1.5\mu\text{m}$ 以内とすることができる。尚、位置合わせ装置の精度は、 $\pm 0.25\mu\text{m}$ であるが、さらに精度の良い位置合わせ装置を用いれば、LDD領域のばらつきを更に小さくすることができる。

【0162】次に、前記基板とフォトマスクの位置合わせの工程について説明する。

【0163】図31(a)に示すように、ゲート電極105a上に遮蔽膜となるフォトレジストを形成する。

【0164】次に、図31(b)、(c)に示すように、該フォトレジストにフォトマスク140を介して露光を行い、現像を行って所定のパターン状の遮蔽膜105bを形成する。

【0165】この場合、前述したように、位置合わせマーク142の透明部分内に位置合わせマーク141が入っていることを確認してから露光を行うようとする。

【0166】(10)次いで、図29(b)に示すように、レジスト膜105bをマスクとして使用し、第2回目の不純物のドープを行なう。具体的には、イオンドーピング法により不純物としてリンイオンをドーピングする。この場合のドーピング加速電圧は12kVでビーム電流密度は $0.5\mu\text{A}/\text{cm}^2$ とし、低加速で高濃度のn型領域を作成するものである。

【0167】これにより、多結晶シリコン層103のうち、レジスト膜105bの直下に位置する領域を除く領域にイオンがドープされる。よって、1回目のイオンドーピングにより不純物が既にドープされている領域A、Bのうち、レジスト膜105bに覆われていない領域(ソース領域103a、ドレイン領域103bに相当する)では、更に不純物がドープされることになり、不純物高濃度領域(n+層)となる。一方、領域A、Bのうち、レジスト膜105bに覆われている領域(低濃度不純物領域103d、103eに相当する)では、2回目のイオンドーピングによっては、不純物がドープされず、低濃度不純物領域(n-層)となる。こうして、ソース領域103a(n+層)とチャネル領域103cの間に、低濃度不純物領域103d(n-層)を形成し、また、ドレイン領域103b(n+層)とチャネル領域103cの間に、低濃度不純物領域103e(n-層)を形成することができる。しかも、ゲート電極105a

をマスクとして第1回目のイオンドーピングを行ない、更に、レジスト膜5bをマスクとして第2回目のイオンドーピングを行なうので、ソース領域103a、低濃度不純物領域103d, 103e及びドレイン領域103bを自己整合的に形成することができ、ゲート電極5とソース領域103aの重なり部分、並びにゲート電極105とドレイン領域103bの重なり部分を、考慮にいれない程度に小さく抑えることができる。よって、LDD領域の長さが1~1.5μmとした薄膜トランジスタを形成することができ、OFF電流を低くすることができると共に、ON電流の低下を可及的に抑えることができる。

【0168】(11)次いで、層間絶縁層(SiO<sub>x</sub>)106を製膜する(図29(c))。

【0169】(12)次いで、層間絶縁層106及びゲート絶縁層104にコンタクトホール109a, 109bを開口する(図29(d))。

【0170】(13)そして、スパッタ法により、例えばA1などの金属層をコンタクトホール109a, 109bに充填し、金属層の上部を所定形状にパターニングしてソース電極107及びドレイン電極108を形成する(図29(e))。こうして、TFT101が作製される。

【0171】前記の例では、nチャネルTFTについて説明したけれども、pチャネルTFTについても同様の製造プロセスにより製造することができる。

【0172】前記製造方法により作成した薄膜トランジスタの電圧/電流特性を図35に示す。更にそのOFF電流の基板面内のばらつきを図36に示す。

【0173】図35に示すように、本実施の形態2-1に係るTFT101(L3のグラフ)は、高抵抗領域であるLDD領域が1~1.5μmと小さいので、安定した大きいON電流と小さいOFF電流を確保できた。

【0174】また、アライナのあわせ精度が向上すれば更にLDD領域の長さを小さくすることが可能であることは言うまでもない。また、n-領域のキャリヤ濃度を大きくすることによって、電界のかかる領域は小さくなるが、一方電界のピーク値は高くなる為に、OFF電流は増加する。

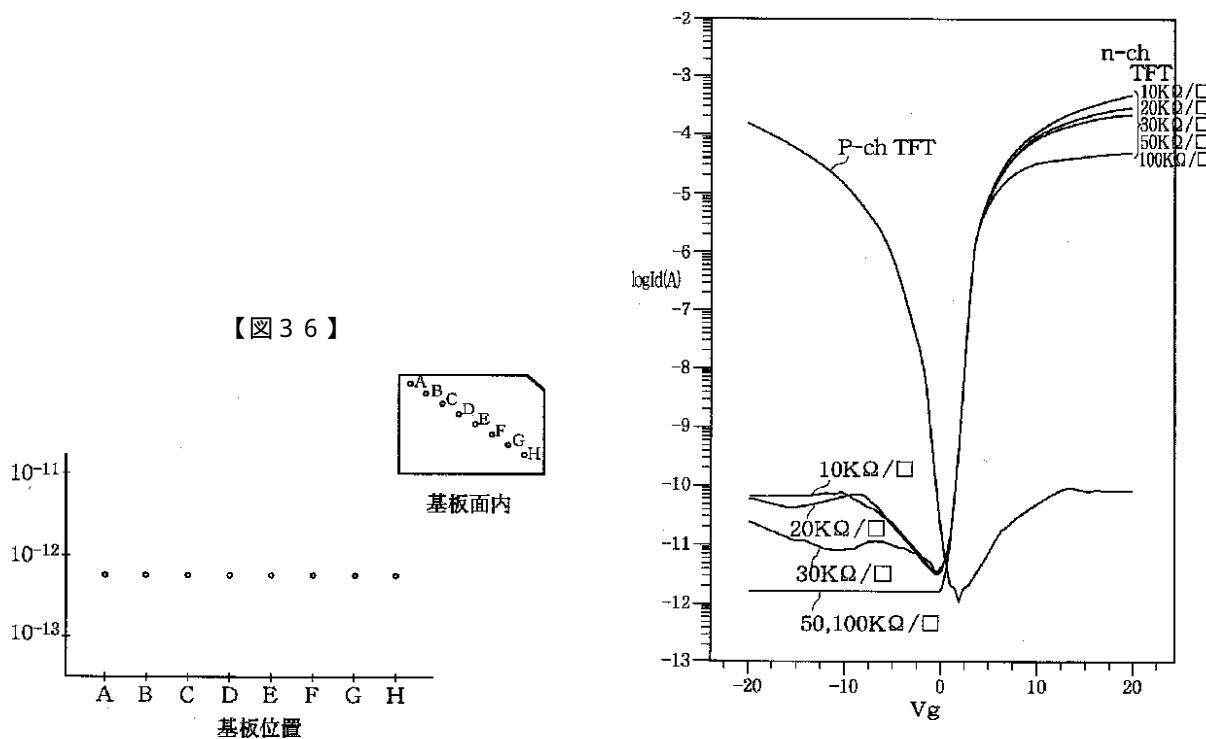

【0175】図37にLDD領域の濃度をパラメータとした、薄膜トランジスタのVg-Id特性をシミュレーションした結果を示す。

【0176】LDD領域のシート抵抗が20k/以下でOFF電流は急激に大きくなる。従って、n-領域のシート抵抗は少なくとも20k/以上の値が必要である。一方、LDD領域のシート抵抗を100k/

以上にした場合、トランジスタのON電流が低下しパネルの動作が不安定となった。従って、LDD領域のシート抵抗の範囲は、20k/以上100k/以下とすることが望ましい。

【0177】加えて、最初の不純物ドーピングは、加速電圧が10kV以上30kV以下及びビーム電流密度が0.05μA/cm<sup>2</sup>以上1μA/cm<sup>2</sup>以下の低速でのイオンドーピング法を用いることにより、イオンドーピング時でのイオンの加速電圧が低いために、ドーピング時における損傷を少なくすることができる。

【0178】また、1回目の不純物ドーピング時でレジストをマスクとした場合でも、レジストが変質することなくきれいに除去できる。

【0179】あるいは2回目の不純物ドーピングは加速電圧が30kV以上及びビーム電流密度が1μA/cm<sup>2</sup>以上の高速でのイオンドーピング法を用い、2回目のイオンドーピング時でも十分なイオンをポリシリコンに注入することも可能である。

【0180】また、本実施の形態2-1で、TFT101を構成するLDD領域の長さLは1μm以上1.5μm以下とし、ソース-ドレイン間電圧V1cを6V、チャネル幅Wを6μmの条件で行っている。ところで、一般的にOFF電流は、ソース/ドレイン間の電界により決定され、V1cは、チャネル領域/LDD領域にのみ印加されるため、電界の強さはV1c/Lと表わされる(Solid State Electron, 38, 2075(1995))。そして、電界の強さは、次式で表される。

$$4 \times 10^6 < V1c / L < 6 \times 10^6$$

【0181】そして、OFF電流は、チャネル幅Wに比例するので、前記LDD領域の長さLと前記ソース-ドレイン間電圧V1cとチャネル幅Wとの関係を以下の式(3)に表すことができる。

$$L > (W \cdot V1c) / 36 \dots (3)$$

【0182】前記(3)式の意味について説明する。TFTの小型化が進んだ場合には、前記L、Wの値は小さくなり、それに伴って、ソース-ドレイン間電圧V1cは低下する。そこで、LDD領域の長さLとソース-ドレイン間電圧V1cとチャネル幅Wとを変化させたTFTの特性を表2に示す。

【表2】

を満たす実験例1、3、4、6は、ON電流を確保することができた。

【0186】尚、上記(4')式よりもさらにON電流を確保するための好ましい条件として、下記(4)式により、ON電流を確保することができる。

$$L < 1.5 \cdot (W/L) \dots (4)$$

【0187】このように、薄膜トランジスタのOFF時には、前記低濃度不純物領域がキャリアの枯渇する高抵抗層となるためOFF電流の低減を図ることができる。

- 10 そして、前記(3)式より、LDD領域の長さの指針を決めることができ、OFF電流低減のために必要以上にLDD領域を確保する必要はなくなる。また、前記(3)式は、更に(4)式を満たすことにより、薄膜トランジスタのON時には、ゲート電極からの電界の作用により、ゲート電極下の低濃度不純物領域はキャリアとなる電子が蓄積して低抵抗領域となり、ON電流の減少は起こらない。よって、(3)式および(4)式を満たす薄膜トランジスタは、ON電流を十分確保すると共にOFF電流を小さく押さえることが可能となる。尚、前記チャネル幅は $5 \mu m$ で行っているが、チャネル領域のチャネル幅Wを微細化し、 $2 \mu m$ 以下とする場合には、特に、前記関係式(3)式、(4)式は薄膜トランジスタを作製する上で有効な指針となる。

- 20 【0188】(実施の形態2-2)本実施の形態2-2では、前記実施の形態2-1の製造工程において、レジスト膜105bを形成する場合に、前記位置合わせマークを用いてLDD領域の長さを $1 \mu m$ 以上 $1.5 \mu m$ 以下とせずに、LDD領域の長さが $1 \mu m$ 以上 $1.5 \mu m$ 以下の条件を満たしているものを良品とする検査工程によって、LDD領域を前記範囲内とする薄膜トランジスタを得ることができる。従って、ON電流を十分確保すると共にOFF電流を小さく押さえることが可能となる。尚、本実施の形態2-2では、LDD領域を $1 \mu m$ 以上 $1.5 \mu m$ 以下に限定するものではなく、前記実施の形態2-1で説明した(3)式、(4)式の範囲とすることでできる。

- 30 【0189】(その他の事項)前記実施の形態2-1、2-2では、1種類の濃度を有する低濃度不純物領域について説明したが、本発明はこれに限定されるものではなく、濃度差が異なる複数の低濃度不純物領域を設けるようにしてもよい。即ち、低濃度不純物領域を、チャネル領域に向かうに連れて不純物濃度が段階的に低下していく複数の接合領域から構成することによって、多段階的に不純物濃度を変化させることができるので、半導体層での電界の集中をより緩和することができる。

- 40 【0190】また、前記低濃度不純物領域はドレイン領域とチャネル領域との間にのみ形成されても良く、このように構成することにより、OFF電流の低減等の効果を奏すると共に、薄膜トランジスタの面積を小さくすることが可能となる。さらに、このような薄膜トランジ

|      | $V_{IC}$ (V) | $\Delta L$ ( $\mu m$ ) | $V_{IC} / \Delta L$ | W ( $\mu m$ ) | $W \cdot V_{IC} / 36$ | $3 \cdot (W/L)$ | ON電流 | オフ電流 |

|------|--------------|------------------------|---------------------|---------------|-----------------------|-----------------|------|------|

| 実験例1 | 6            | 1                      | $6 \cdot 10^6$      | 5             | 0.83                  | 1.25            | ○    | ○    |

| 実験例2 | 6            | 1.5                    | $4 \cdot 10^6$      | 5             | 0.83                  | 1.25            | ○    | ○    |

| 実験例3 | 3            | 0.5                    | $6 \cdot 10^6$      | 5             | 0.41                  | 1.25            | ○    | ○    |

| 実験例4 | 3            | 0.75                   | $4 \cdot 10^6$      | 3             | 0.25                  | 0.75            | ○    | ×    |

| 実験例5 | 6            | 2                      | $3 \cdot 10^6$      | 5             | 0.83                  | 1.25            | ○    | ○    |

| 実験例6 | 6            | 0.5                    | $12 \cdot 10^6$     | 5             | 0.83                  | 1.25            | ○    | ×    |

| 実験例7 | 3            | 1                      | $3 \cdot 10^6$      | 3             | 0.25                  | 0.75            | ○    | ×    |

( $L = 1.2 \mu m$ 、ON電流○：ON電流確保、OFF電流○：OFF電流抑制)

【0183】表2に示すように、実験例1～5、7(即ち、前記(1)式を満たすもの)は、OFF電流を抑制することができるが、実験例6(即ち、前記(3)式を満たさないもの)は、OFF電流を抑制することができない。

【0184】また、前記チャネル領域のチャネル幅をWとした場合、LDD領域の長さLとチャネル領域のチャネル幅Lとチャネル幅Wとの関係は、下記(4')式で表すことができる。

$$L < 3 \cdot (W/L) \dots (4')$$

【0185】前記(4)式は、ON電流の制限を示すものであり、ON電流は $W/L$ に比例することにより導かれる条件であり、ON電流の条件は、 $W/L = 0.5$ で

Lが $1.5 \mu m$ 以下で減少する実験結果より導かれたものである。そして、表1に示すように、前記(4)式

タは液晶表示装置以外への適用も可能である。

【0191】また、C-MOSインバータ回路であつて、pチャネル薄膜トランジスタとnチャネル薄膜トランジスタのうち、少なくともnチャネル薄膜トランジスタを、実施の形態2-1、2-2に係る薄膜トランジスタで構成することもできる。

## 【0192】

【発明の効果】以上に説明したように、本発明の構成によれば、本発明の課題を十分に達成することができる。

【0193】即ち、第1の発明群では、ON電流を十分確保すると共に、光照射時の光伝導電流を小さく押さえることが可能となり、消費電力が小さく、信頼性向上並びに特性向上に対して、極めてその効果は大である。

【0194】また、第2の発明群では、ON電流を十分確保すると共に、OFF電流を小さく押さえることが可能となり、消費電力が小さく、合わせて信頼性向上並びに特性向上に対して、極めてその効果が大である薄膜トランジスタを提供することができる。

## 【図面の簡単な説明】

【図1】TFTを構成するチャネル領域のチャネル幅Wと光伝導電流(OFF電流: I<sub>OFF</sub>)との関係、及びバックライト輝度と光伝導電流との関係を示す図

【図2】TFTをOFF状態にした場合の電界をシミュレーションした結果を示す図

【図3】シミュレーションにより得られたシート抵抗と空乏層幅との関係を示す図

【図4】シミュレーション(W=4μmの場合)により求められた空乏層幅と該空乏層幅に対応するシート抵抗での光伝導電流との関係を測定した結果を示す図

【図5】アクティブマトリックスの等価回路を示す図

【図6】画素電圧ロスのシミュレーション結果を示す図

【図7】本発明の実施の形態1-1に係る薄膜トランジスタを画素スイッチング素子として使用した液晶表示装置の概略断面図

【図8】本発明の実施の形態1-1に係る薄膜トランジスタの概略断面図

【図9】図8の概略平面図

【図10】本発明の実施の形態1-1に係る薄膜トランジスタの製造方法を示す概略断面図

【図11】同じく薄膜トランジスタの製造方法を示す概略断面図

【図12】同じく薄膜トランジスタの製造方法を示すフローチャート

【図13】薄膜トランジスタの電圧/電流特性を示す図

【図14】OFF電流の基板面内のはらつきを示す図

【図15】n型領域の濃度をパラメータとした、薄膜トランジスタのV<sub>g</sub>-I<sub>d</sub>特性をシミュレーションした結果を示す図

【図16】TFTをOFFした場合の電界をシミュレーションした結果を示す図

【図17】本発明の実施の形態1-2に係る薄膜トランジスタの製造方法を示す概略断面図

【図18】同じく、薄膜トランジスタの製造方法を示す概略断面図

【図19】本発明の実施の形態1-3に係る薄膜トランジスタを用いたC-MOSインバータの配線パターンを示す平面図

【図20】図19の等価回路図

【図21】図19の矢視X-X'断面図

【図22】C-MOSインバータにおけるon/off時でのn-chトランジスタのバイアス状態における動作ポイントを示す図

【図23】シート抵抗をパラメータとしてLDD領域を0.5μmから3μmまで変化させた場合のV<sub>g</sub>-I<sub>d</sub>特性をシミュレーションした結果を示す図

【図24】チャンネル領域とLDD領域において、TFTをOFF状態にした場合(V<sub>g</sub>=-10V, V<sub>d</sub>=6V時)の電界をシミュレーションした結果を示す図

【図25】実際のLDD領域を持つTFTの、LDD領域の長さ(L)とOFF電流及びLDD領域の長さ(L)とON電流との関係を示す図

【図26】実施の形態2-1に係る薄膜トランジスタの簡略化した断面図

【図27】図26の概略平面図

【図28】図28は本発明の実施の形態2-1に係る薄膜トランジスタの製造方法を示す概略断面図

【図29】本発明の実施の形態2-1に係る薄膜トランジスタの製造方法を示す概略断面図

【図30】本発明の実施の形態2-1に係る薄膜トランジスタの製造方法を示すフローチャート

【図31】LDD領域を形成する工程を説明する概略断面工程図

【図32】フォトマスクと基板の斜視図

【図33】フォトマスクと基板の平面図

【図34】LDD領域形成後の薄膜トランジスタの概略断面図

【図35】実施の形態2-1に係る薄膜トランジスタの電圧/電流特性を示す図

【図36】実施の形態2-1に係る薄膜トランジスタのOFF電流の基板面内のはらつきを示す図

【図37】LDD領域の濃度をパラメータとした、TFTのV<sub>g</sub>-I<sub>d</sub>特性をシミュレーションした結果を示す図

【図38】輝度傾斜とクロストークについて説明するための概略図

## 【符号の説明】

1 薄膜トランジスタ

2 ガラス基板

3 多結晶シリコン層

50 3a ソース領域

|                                       |                                               |

|---------------------------------------|-----------------------------------------------|

| 3 b ドレイン領域                            | * 5 8 共通電極                                    |

| 3 c チャネル領域                            | 1 0 1 ガラス基板                                   |

| 3 d、3 e 低濃度不純物領域 ( L D D 領域 : n - 層 ) | L L D D 領域の長さ                                 |

| 4 ゲート絶縁層                              | L チャネル領域の長さ                                   |

| 5 a ゲート電極                             | W チャネル領域の幅                                    |

| 5 b レジスト膜                             | 1 0 1 薄膜トランジスタ                                |

| 6 層間絶縁層                               | 1 0 2 ガラス基板                                   |

| 7 ソース電極                               | 1 0 3 多結晶シリコン層                                |

| 8 ドレイン電極                              | 1 0 3 a ソース領域                                 |

| 9 a、9 b コンタクトホール                      | 1 0 3 b ドレイン領域                                |

| 1 5 a - S i 層                         | 1 0 3 c チャネル領域                                |

| 1 6 多結晶シリコン層                          | 1 0 3 d、1 0 3 e 低濃度不純物領域 ( L D D 領域 : n - 層 ) |

| 1 7 金属層                               | 1 0 4 ゲート絶縁層                                  |

| 1 8 フォトレジスト                           | 1 0 5 a ゲート電極                                 |

| 2 2 ポリシリコン                            | 1 0 5 b レジスト膜                                 |

| 2 3 酸化シリコン膜                           | 1 0 6 層間絶縁層                                   |

| 2 4 コンタクトホール                          | 1 0 7 ソース電極                                   |

| 2 5 ゲート電極                             | 1 0 8 ドレイン電極                                  |

| 2 6 ゲート電極パターン                         | 20 1 0 9 a、1 0 9 b コンタクトホール                   |

| 2 7 ドレイン電極                            | 1 1 5 a - S i 層                               |

| 3 0 層間絶縁膜                             | 1 1 7 金属層                                     |

| 3 1 ソース電極                             | 1 1 8 フォトレジスト                                 |

| 3 2 ドレイン電極                            | 1 2 2 n チャネル TFT                              |

| 5 0 液晶表示装置                            | 1 2 3 p チャネル TFT                              |

| 5 1 液晶パネル部                            | 1 2 4 多結晶シリコン層                                |

| 5 2 バックライト部                           | 1 2 5 ゲート電極                                   |

| 5 3 偏光板                               | 1 2 6 ソース電極                                   |

| 5 4 b ガラス基板                           | 1 2 7 ドレイン電極                                  |

| 5 5 画素電極                              | 30 1 4 0 フォトマスク                               |

| 5 6 配向膜                               | 1 4 1、1 4 2 位置合わせマーク                          |

| 5 7 液晶層                               | *                                             |

【図3】

【図20】

【図1】

【図2】

【図4】

【図5】

$R_{off}$  (TFTのオフ抵抗) =  $V_{sd}/I_{off}$

$I_{off}$ : トランジスタのオフ電流

$V_{sd}$ : ソース/ドレイン電圧

$C_s$ : 蓄積容量

$Cl_c$ : 液晶容量

【図6】

【図7】

【図9】

【図8】

【図12】

【図13】

【図10】

【図11】

【図14】

【図15】

### 【図16】

### 【図17】

### 【図 18】

〔図19〕

### 【図21】

### 【図32】

## 【図22】

### 【図23】

【図26】

### 【図24】

### 【図25】

### 【図27】

## 【図29】

【図28】

【図30】

【図31】

【図33】

【図34】

【図35】

【図37】

【図36】

【図38】

## フロントページの続き

(72)発明者 岡田 隆史 F ターム(参考) 2H092 JA24 JA25 JA26 JA34 JA37

大阪府門真市大字門真1006番地 松下電器

産業株式会社内 JA41 JA46 KA03 KA04 MA02

(72)発明者 山野 敦浩 MA05 MA08 MA13 MA14 MA15

大阪府門真市大字門真1006番地 松下電器 MA17 MA24 MA29 MA30 NA25

産業株式会社内 PA01 PA02 PA03 PA06 PA11

PA12 PA13

5F110 AA06 BB01 BB04 CC02 DD02

EE03 FF02 GG02 GG13 GG25

GG29 GG43 GG45 GG47 HJ01

HJ12 HL03 HL23 HM15 NN02

NN23 NN72 PP03 PP35 QQ11

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 薄膜晶体管和使用该薄膜晶体管的液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号     | <a href="#">JP2003249507A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2003-09-05 |

| 申请号         | JP2003063322                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 申请日     | 2000-09-14 |

| 申请(专利权)人(译) | 松下电器产业有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人      | 南野裕<br>千田耕司<br>岡田隆史<br>山野敦浩                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 发明人         | 南野 裕<br>千田 耕司<br>岡田 隆史<br>山野 敦浩                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号      | G02F1/1368 H01L21/336 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号       | G02F1/1368 H01L29/78.616.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号   | 2H092/JA24 2H092/JA25 2H092/JA26 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JA46 2H092/KA03 2H092/KA04 2H092/MA02 2H092/MA05 2H092/MA08 2H092/MA13 2H092/MA14 2H092/MA15 2H092/MA17 2H092/MA24 2H092/MA29 2H092/MA30 2H092/NA25 2H092/PA01 2H092/PA02 2H092/PA03 2H092/PA06 2H092/PA11 2H092/PA12 2H092/PA13 5F110/AA06 5F110/BB01 5F110/BB04 5F110/CC02 5F110/DD02 5F110/EE03 5F110/FF02 5F110/GG02 5F110/GG13 5F110/GG25 5F110/GG29 5F110/GG43 5F110/GG45 5F110/GG47 5F110/HJ01 5F110/HJ12 5F110/HL03 5F110/HL23 5F110/HM15 5F110/NN02 5F110/NN23 5F110/NN72 5F110/PP03 5F110/PP35 5F110/QQ11 2H192/AA24 2H192/BC31 2H192/CB02 2H192/CB34 2H192/CB52 2H192/CB53 2H192/DA12 2H192/FB02 2H192/GD73 2H192/HA84 |         |            |

| 优先权         | 2000131264 2000-04-28 JP<br>2000197536 2000-06-30 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

## 摘要(译)

解决的问题：提供一种薄膜晶体管，该薄膜晶体管通过抑制光照射期间的截止电流（光导电流）来实现高性能和高可靠性。形成具有在沟道区的两侧上设置有沟道区和源极区和漏极区的多晶硅半导体层，并且在沟道区和漏极区之间设置耗尽层。形成耗尽层的宽度，并且当沟道区域被光照射时产生的光导电流具有比例关系，并且为了将光导电流保持在预定的允许值内，形成了耗尽层。提供一种薄膜晶体管，该薄膜晶体管的结构的宽度小于或等于基于比例关系获得的值。