特開2003-195330

(P2003-195330A)

(43)公開日 平成15年7月9日(2003.7.9)

(51) Int.CI<sup>7</sup>

識別記号

F I

テマコード(参考)

G 0 2 F 1/1343

1/1368G 0 2 F 1/1343

1/1368

2 H 0 9 2

審査請求 未請求 請求項の数 110 L (全 14数)

(21)出願番号 特願2001-396509(P2001-396509)

(71)出願人 000005108

株式会社日立製作所

(22)出願日 平成13年12月27日(2001.12.27)

東京都千代田区神田駿河台四丁目6番地

(72)発明者 仲吉 良彰

千葉県茂原市早野3300番地 株式会社日立

製作所ディスプレイグループ内

(72)発明者 柳川 和彦

千葉県茂原市早野3300番地 株式会社日立

製作所ディスプレイグループ内

(74)代理人 100083552

弁理士 秋田 収喜

最終頁に続く

(54)【発明の名称】 液晶表示装置

(57)【要約】

【課題】 画素領域の開口率の向上。

【解決手段】 液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、並設される複数のゲート信号線とこれらゲート信号線に交差して並設される複数のドレイン信号線とで囲まれた領域を画素領域とし、これら各画素領域に、ゲート信号線からの走査信号によって作動されるスイッチング素子と、このスイッチング素子を介してドレイン信号線からの映像信号が供給される画素電極と、対向電圧信号線を介して前記映像信号に対して基準となる信号が供給される対向電極とが形成され、前記対向電極は、複数の絶縁層の積層体の下層に形成され、前記対向電圧信号線は、非透光性の導電体からなるとともに、前記複数の絶縁層の積層体の上層に形成され、前記ゲート信号線およびドレイン信号線をも被つて格子状パターンをなし、その一部にて前記複数の絶縁層の積層体に形成されたスルーホールを通して前記対向電極に電気的に接続されている。

## 【特許請求の範囲】

【請求項1】 液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、並設される複数のゲート信号線とこれらゲート信号線に交差して並設される複数のドレイン信号線とで囲まれた領域を画素領域とし、これら各画素領域に、ゲート信号線からの走査信号によって作動されるスイッチング素子と、このスイッチング素子を介してドレイン信号線からの映像信号が供給される画素電極と、対向電圧信号線を介して前記映像信号に対して基準となる信号が供給される対向電極とが形成され、

前記対向電極は、複数の絶縁層の積層体の下層に形成され、

前記対向電圧信号線は、非透光性の導電体からなるとともに、前記複数の絶縁層の積層体の上層に形成され、前記ゲート信号線およびドレイン信号線をも被って格子状パターンをなし、その一部にて前記複数の絶縁層の積層体に形成されたスルーホールを通して前記対向電極に電気的に接続されていることを特徴とする液晶表示装置。

【請求項2】 前記対向電圧信号線と対向電極との電気的接続は、前記複数の絶縁層の間に形成された画素電極を構成する導電層と同時に形成される他の導電層を介してなされていることを特徴とする請求項1に記載の液晶表示装置。

【請求項3】 前記対向電圧信号線と対向電極との電気的接続は、前記複数の絶縁層の間に形成されたドレイン信号線を構成する導電層と同時に形成される他の導電層を介してなされていることを特徴とする請求項1に記載の液晶表示装置。

【請求項4】 前記対向電圧信号線と対向電極との電気的接続は2箇所あるいはそれ以上の個所でなされていることを特徴とする請求項1ないし3のうちいずれかに記載の液晶表示装置。

【請求項5】 液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、並設される複数のゲート信号線とこれらゲート信号線に交差して並設される複数のドレイン信号線とで囲まれた領域を画素領域とし、これら各画素領域に、ゲート信号線からの走査信号によって作動されるスイッチング素子と、このスイッチング素子を介してドレイン信号線からの映像信号が供給される画素電極と、対向電圧信号線を介して前記映像信号に対して基準となる信号が供給される対向電極とが形成され、

前記対向電極は複数の絶縁層の積層体の下層に形成され、前記画素電極は前記積層体の複数の絶縁層のうちの2つの絶縁層の間に形成され前記ドレイン信号線の延在方向に沿って延在され該方向に交差する方向に並設された複数の電極群からなるとともに、

前記対向電圧信号線は、非透光性の導電体からなるとともに、前記複数の絶縁層の積層体の上層に形成され、前

記ゲート信号線およびドレイン信号線をも被って格子状パターンをなし、その一部にて前記複数の絶縁層の積層体に形成されたスルーホールを通して前記対向電極に電気的に接続されていることを特徴とする液晶表示装置。

【請求項6】 画素領域を平面的に観た場合に、ドレイン信号線を被って形成された前記対向電圧信号線とそれに隣接して配置される画素電極との間の距離は、互いに隣接して配置される画素電極との間の距離よりも大きく設定されていることを特徴とする請求項5に記載の液晶表示装置。

【請求項7】 画素領域を平面的に観た場合に、ドレイン信号線を被って形成された前記対向電圧信号線とそれに隣接して配置される画素電極との間の距離は、該対向電圧信号線とそれに近接して配置される対向電極との間の距離よりも大きく設定されていることを特徴とする請求項5、6のうちいずれかに記載の液晶表示装置。

【請求項8】 液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、並設される複数のゲート信号線とこれらゲート信号線に交差して並設される複数のドレイン信号線とで囲まれた領域を画素領域とし、これら各画素領域に、ゲート信号線からの走査信号によって作動されるスイッチング素子と、このスイッチング素子を介してドレイン信号線からの映像信号が供給される画素電極と、対向電圧信号線を介して前記映像信号に対して基準となる信号が供給される対向電極とが形成され、

前記対向電圧信号線は、その表面が陽極化成されたA1あるいはその合金から構成されるとともに複数の絶縁層の積層体の下層に形成され、

前記対向電極は、透光性の導電体からなるとともに、前記複数の絶縁層の積層体の上層に形成され、前記ゲート信号線およびドレイン信号線をも被って格子状パターンをなし、その一部にて前記複数の絶縁層の積層体に形成されたスルーホールを通して前記対向電圧信号線に容量結合されていることを特徴とする液晶表示装置。

【請求項9】 液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、並設される複数のゲート信号線とこれらゲート信号線に交差して並設される複数のドレイン信号線とで囲まれた領域を画素領域とし、これら各画素領域に、ゲート信号線からの走査信号によって作動されるスイッチング素子と、このスイッチング素子を介してドレイン信号線からの映像信号が供給される画素電極と、対向電圧信号線を介して前記映像信号に対して基準となる信号が供給される対向電極とが形成され、

前記対向電圧信号線は、その表面が陽極化成されたA1あるいはその合金から構成されるとともに複数の絶縁層の積層体の下層に形成され、かつこの対向電圧信号線の少なくとも一部の下層に該対向電圧信号線から露出された導電材料層を備え、

前記対向電極は、前記複数の絶縁層の積層体の上層に形成され、前記ゲート信号線およびドレイン信号線をも被って格子状パターンをなし、その一部にて前記複数の絶縁層の積層体に形成されたスルーホールを通して前記導電材料層に電気的に接続されていることを特徴とする液晶表示装置。

【請求項10】対向電極は透光性の導電層で構成されていることを特徴とする請求項9に記載の液晶表示装置。

【請求項11】複数の絶縁層の前記積層体の2つの絶縁層の間にドレイン信号線が形成され、前記対向電極と導電材料層との間に前記ドレイン信号線の材料と同一の材料層が介在されていることを特徴とする請求項9, 10のうちいずれかに記載の液晶表示装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は液晶表示装置に係り、特に横電界方式と称される液晶表示装置に関する。

【0002】

【従来の技術】横電界方式と称される液晶表示装置は、液晶を介して対向配置される各基板の一方の基板の液晶側の面の画素領域に画素電極とこの画素電極との間に電界を発生せしめる対向電極とを備え、該電界のうち基板とほぼ平行な成分によって液晶を拳動させる構成となっている。

【0003】そして、このような構成をアクティブマトリクス型のものに適用させたものは、まず、前記一方の基板の液晶側の面に、並設された複数のゲート信号線とこれら各ゲート信号線と交差するようにして並設された複数のドレイン信号線とで囲まれた各領域を前記画素領域としている。

【0004】そして、これら各画素領域に、ゲート信号線からの走査信号によって作動する薄膜トランジスタと、この薄膜トランジスタを介してドレイン信号線からの映像信号が供給される前記画素電極と、該映像信号に對して基準となる信号が供給される前記対向電極とが備えられている。

【0005】ここで、画素電極と対向電極はそれぞれ一方向に延在する帯状のパターンとして形成され、それら各電極は2個あるいはそれ以上の個数で形成して交互に配置させるのが通常である。

【0006】また、このような構成において、対向電極をドレイン信号線をも被って形成される絶縁膜の上面に形成させるとともに、該ドレイン信号線とその中心軸をほぼ一致させ該ドレイン信号線の幅よりも大きな幅をして該ドレイン信号線に沿って形成された構成のものも知られている。

【0007】ドレイン信号線からの電気力線がその上方の対向電極に終端させやすくし、画素電極に終端させるのを防止するためである。画素電極に該電気力線が終端

するとそれがノイズとなってしまうからである。

【0008】

【発明が解決しようとする課題】しかしながら、このような構成からなる液晶表示装置は、対向電極に信号を供給する対向電圧信号線を必要とし、それが画素領域内を走行して配置させるために画素領域のいわゆる開口率を向上させる妨げとなっていたという不都合があった。

【0009】また、対向電極と対向電圧信号線は絶縁層を介して配置されることが多く、それらの電気的接続は該絶縁層に形成した小さなスルーホールを通して行なうため、該接続のさらなる信頼性が望まれていた。近年における高精細化の傾向に伴うものである。

【0010】本発明は、このような事情に基づいてなされたもので、その目的は画素領域の開口率を向上させた液晶表示装置を提供することにある。

【0011】また、本発明の他の目的は、対向電極と対向電圧信号線の信頼性ある接続を図った液晶表示装置を提供することにある。

【0012】

【課題を解決するための手段】本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

手段1. 本発明による液晶表示装置は、たとえば、液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、並設される複数のゲート信号線とこれらゲート信号線に交差して並設される複数のドレイン信号線とで囲まれた領域を画素領域とし、これら各画素領域に、ゲート信号線からの走査信号によって作動されるスイッチング素子と、このスイッチング素子を介してドレイン信号線からの映像信号が供給される画素電極と、対向電圧信号線を介して前記映像信号に対して基準となる信号が供給される対向電極とが形成され、前記対向電極は、複数の絶縁層の積層体の下層に形成され、前記対向電圧信号線は、非透光性の導電体からなるとともに、前記複数の絶縁層の積層体の上層に形成され、前記ゲート信号線およびドレイン信号線をも被って格子状パターンをなし、その一部にて前記複数の絶縁層の積層体に形成されたスルーホールを通して前記対向電極に電気的に接続されていることを特徴とするものである。

【0013】手段2. 本発明による液晶表示装置は、たとえば、手段1の構成を前提として、前記対向電圧信号線と対向電極との電気的接続は、前記複数の絶縁層の間に形成された画素電極を構成する導電層と同時に形成される他の導電層を介してなされていることを特徴とするものである。

【0014】手段3. 本発明による液晶表示装置は、たとえば、手段1の構成を前提として、前記対向電圧信号線と対向電極との電気的接続は、前記複数の絶縁層の間に形成されたドレイン信号線を構成する導電層と同時に形成される他の導電層を介してなされていることを特徴

とするものである。

【0015】手段4. 本発明による液晶表示装置は、たとえば、手段1ないし3のうちいずれかの構成を前提として、前記対向電圧信号線と対向電極との電気的接続は2箇所あるいはそれ以上の箇所でなされていることを特徴とするものである。

【0016】手段5. 本発明による液晶表示装置は、たとえば、液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、並設される複数のゲート信号線とこれらゲート信号線に交差して並設される複数のドレイン信号線とで囲まれた領域を画素領域とし、これら各画素領域に、ゲート信号線からの走査信号によって作動されるスイッチング素子と、このスイッチング素子を介してドレイン信号線からの映像信号が供給される画素電極と、対向電圧信号線を介して前記映像信号に対して基準となる信号が供給される対向電極とが形成され、前記対向電極は複数の絶縁層の積層体の下層に形成され、前記画素電極は前記積層体の複数の絶縁層のうちの2つの絶縁層の間に形成され前記ドレイン信号線の延在方向に沿って延在され該方向に交差する方向に並設された複数の電極群からなるとともに、前記対向電圧信号線は、非透光性の導電体からなるとともに、前記複数の絶縁層の積層体の上層に形成され、前記ゲート信号線およびドレイン信号線をも被って格子状パターンをなし、その一部にて前記複数の絶縁層の積層体に形成されたスルーホールを通して前記対向電極に電気的に接続されていることを特徴とするものである。

【0017】手段6. 本発明による液晶表示装置は、たとえば、手段5の構成を前提として、画素領域を平面的に観た場合に、ドレイン信号線を被って形成された前記対向電圧信号線とそれに隣接して配置される画素電極との間の距離は、互いに隣接して配置される画素電極との間の距離よりも大きく設定されていることを特徴とするものである。

【0018】手段7. 本発明による液晶表示装置は、たとえば、手段5、6のうちいずれかの構成を前提として、画素領域を平面的に観た場合に、ドレイン信号線を被って形成された前記対向電圧信号線とそれに隣接して配置される画素電極との間の距離は、該対向電圧信号線とそれに近接して配置される対向電極との間の距離よりも大きく設定されていることを特徴とするものである。

【0019】手段8. 本発明による液晶表示装置は、たとえば、液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、並設される複数のゲート信号線とこれらゲート信号線に交差して並設される複数のドレイン信号線とで囲まれた領域を画素領域とし、これら各画素領域に、ゲート信号線からの走査信号によって作動されるスイッチング素子と、このスイッチング素子を介してドレイン信号線からの映像信号が供給される画素電極と、対向電圧信号線を介して前記映像信号に対して基

10 20 30 40 50

準となる信号が供給される対向電極とが形成され、前記対向電圧信号線は、その表面が陽極化成されたA1あるいはその合金から構成されるとともに複数の絶縁層の積層体の下層に形成され、前記対向電極は、透光性の導電体からなるとともに、前記複数の絶縁層の積層体の上層に形成され、前記ゲート信号線およびドレイン信号線をも被って格子状パターンをなし、その一部にて前記複数の絶縁層の積層体に形成されたスルーホールを通して前記対向電圧信号線に容量結合されていることを特徴とするものである。

【0020】手段9. 本発明による液晶表示装置は、たとえば、液晶を介して対向配置される各基板のうち一方の基板の液晶側の面に、並設される複数のゲート信号線とこれらゲート信号線に交差して並設される複数のドレイン信号線とで囲まれた領域を画素領域とし、これら各画素領域に、ゲート信号線からの走査信号によって作動されるスイッチング素子と、このスイッチング素子を介してドレイン信号線からの映像信号が供給される画素電極と、対向電圧信号線を介して前記映像信号に対して基準となる信号が供給される対向電極とが形成され、前記対向電圧信号線は、その表面が陽極化成されたA1あるいはその合金から構成されるとともに複数の絶縁層の積層体の下層に形成され、かつこの対向電圧信号線の少なくとも一部の下層に該対向電圧信号線から露出された導電材料層を備え、前記対向電極は、前記複数の絶縁層の積層体の上層に形成され、前記ゲート信号線およびドレイン信号線をも被って格子状パターンをなし、その一部にて前記複数の絶縁層の積層体に形成されたスルーホールを通して前記導電材料層に電気的に接続されていることを特徴とするものである。

【0021】手段10. 本発明による液晶表示装置は、たとえば、手段9の構成を前提として、対向電極は透光性の導電層で構成されていることを特徴とするものである。

【0022】手段11. 本発明による液晶表示装置は、たとえば、手段9、10のうちいずれかの構成を前提として、複数の絶縁層の前記積層体の2つの絶縁層の間にドレイン信号線が形成され、前記対向電極と導電材料層との間に前記ドレイン信号線の材料と同一の材料層が介在されていることを特徴とするものである。

【0023】なお、本発明は以上の構成に限定されず、本発明の技術思想を逸脱しない範囲で種々の変更が可能である。

【0024】

【発明の実施の形態】以下、本発明による液晶表示装置の実施例を図面を用いて説明をする。

実施例1.

《全体構成》図2は、本発明による液晶表示装置の一実施例を示す全体構成図である。同図は等価回路図であるが、実際の幾何学的配置に対応させて描いている。

【0025】同図において、液晶を介して互いに対向配置される一対の透明基板SUB1、SUB2があり、該液晶は一方の透明基板SUB1に対する他方の透明基板SUB2の固定を兼ねるシール材SLによって封入されている。

【0026】シール材SLによって囲まれた前記一方の透明基板SUB1の液晶側の面には、そのx方向に延在しy方向に並設されたゲート信号線GLとy方向に延在しx方向に並設されたドレイン信号線DLとが形成されている。

【0027】各ゲート信号線GLと各ドレイン信号線DLとで囲まれた領域は画素領域を構成するとともに、これら各画素領域のマトリクス状の集合体は液晶表示部ARを構成するようになっている。

【0028】また、x方向に並設される各画素領域のそれぞれにはそれら各画素領域内に走行された共通の対向電圧信号線CLが形成されている。この対向電圧信号線CLは各画素領域の後述する対向電極CTに映像信号に対して基準となる電圧を供給するための信号線となるものである。

【0029】各画素領域には、その片側のゲート信号線GLからの走査信号によって作動される薄膜トランジスタTFTと、この薄膜トランジスタTFTを介して片側のドレイン信号線DLからの映像信号が供給される画素電極PXが形成されている。

【0030】この画素電極PXは、前記対向電圧信号線CLと接続された対向電極CTとの間に電界を発生させ、この電界によって液晶の光透過率を制御させるようになっている。

【0031】前記ゲート信号線GLのそれぞれの一端は前記シール材SLを超えて延在され、その延在端は垂直走査駆動回路Vの出力端子が接続される端子を構成するようになっている。また、前記垂直走査駆動回路Vの入力端子は液晶表示パネルの外部に配置されたプリント基板からの信号が入力されるようになっている。

【0032】垂直走査駆動回路Vは複数個の半導体装置からなり、互いに隣接する複数のゲート信号線GLどおしがグループ化され、これら各グループ毎に一個の半導体装置があてがわれるようになっている。

【0033】同様に、前記ドレイン信号線DLのそれぞれの一端は前記シール材SLを超えて延在され、その延在端は映像信号駆動回路Heの出力端子が接続される端子を構成するようになっている。また、前記映像信号駆動回路Heの入力端子は液晶表示パネルの外部に配置されたプリント基板からの信号が入力されるようになっている。

【0034】この映像信号駆動回路Heも複数個の半導体装置からなり、互いに隣接する複数のドレイン信号線DLどおしがグループ化され、これら各グループ毎に一個の半導体装置があてがわれるようになっている。

【0035】また、前記各対向電圧信号線CLは図中右側の端部で共通に接続され、その接続線はシール材SLを超えて延在され、その延在端において端子CLTを構成している。この端子CLTからは映像信号に対して基準となる電圧が供給されるようになっている。

【0036】前記各ゲート信号線GLは、垂直走査回路Vからの走査信号によって、その一つが順次選択されるようになっている。

【0037】また、前記各ドレイン信号線DLのそれぞれには、映像信号駆動回路Heによって、前記ゲート信号線GLの選択のタイミングに合わせて映像信号が供給されるようになっている。

【0038】なお、上述した実施例では、垂直走査駆動回路Vおよび映像信号駆動回路Heは透明基板SUB1に搭載された半導体装置を示したものであるが、たとえば透明基板SUB1とプリント基板との間を跨って接続されるいわゆるテープキャリア方式の半導体装置であってもよく、さらに、前記薄膜トランジスタTFTの半導体層が多結晶シリコン(p-Si)から構成される場合、透明基板SUB1面に前記多結晶シリコンからなる半導体素子を配線層とともに形成されたものであってもよい。

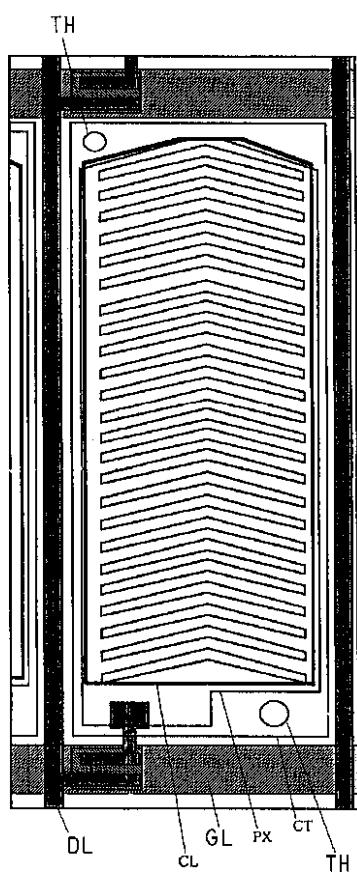

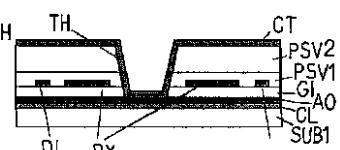

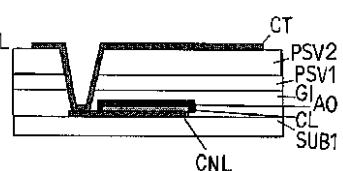

【0039】《画素構成》図1(a)は前記画素領域の一実施例の構成を示す平面図である。また、図1(b)は図1(a)のb-b線における断面図、図1(c)は図1(a)のc-c線における断面図、図1(d)は図1(a)のd-d線における断面図である。

【0040】各図において、透明基板SUB1の液晶側の面に、まず、x方向に延在しy方向に並設される一対のゲート信号線GLが形成されている。これらゲート信号線GLは後述の一対のドレイン信号線DLとともに矩形状の領域を囲むようになっており、この領域を画素領域として構成するようになっている。

【0041】そして、この画素領域内における透明基板SUB1の表面には透光性の導電材からなる対向電極CTが該画素領域の周辺の僅かな領域を除く中央部に形成されている。透光性の導電材としては、たとえば、ITO(Indium Tin Oxide)、ITZO(Indium Tin Zinc Oxide)、IZO(Indium Zinc Oxide)、SnO<sub>2</sub>、In<sub>2</sub>O<sub>3</sub>等が用いられる。

【0042】このようにゲート信号線GLおよび対向電極CTが形成された透明基板SUB1の表面には該ゲート信号線GL等をも被ってたとえばSiNからなる絶縁膜GIが形成されている。

【0043】この絶縁膜GIは、後述のドレイン信号線DLの形成領域においては前記ゲート信号線GLに対する層間絶縁膜としての機能を、後述の薄膜トランジスタTFTの形成領域においてはそのゲート絶縁膜としての機能を有するようになっている。

【0044】そして、この絶縁膜GIの表面であって、

前記ゲート信号線G Lの一部に重畳するようにしてたとえばアモルファスSiからなる半導体層ASが形成されている。

【0045】この半導体層ASは、薄膜トランジスタTFTのそれであって、その上面にドレイン電極SD1およびソース電極SD2を形成することにより、ゲート信号線の一部をゲート電極とする逆スタガ構造のMIS型トランジスタを構成することができる。

【0046】ここで、前記ドレン電極SD1およびソース電極SD2はドレン信号線DLの形成の際に同時に形成されるようになっている。

【0047】すなわち、y方向に延在されx方向に並設されるドレン信号線DLが形成され、その一部が前記半導体層ASの上面にまで延在されてドレン電極SD1が形成され、また、このドレン電極SD1と薄膜トランジスタTFTのチャネル長分だけ離間されてソース電極SD2が形成されている。

【0048】また、このソース電極SD2は画素領域側に若干延在されて後述する画素電極PXとの電気的接続を図るためのコンタクト部COTが形成されている。

【0049】そして、透明基板SUB1の表面には前記ドレン信号線DL、ドレン電極SD1、およびソース電極SD2をも被って保護膜PSV1が形成されている。この保護膜PSV1はたとえばSiN膜等の無機材料層からなり、後述の保護膜PSV2とともに、前記薄膜トランジスタTFTの液晶との直接の接触を回避せようになっている。該薄膜トランジスタTFTの液晶との接触により特性が変化してしまうのを防止するためである。

【0050】この保護膜PSV1の表面には、たとえば透光性の導電材で形成される画素電極PXが形成されている。該透光性の導電材として、たとえば、ITO(Indium Tin Oxide)、ITZO(Indium Tin Zinc Oxide)、IZO(Indium Zinc Oxide)、SnO<sub>2</sub>、In<sub>2</sub>O<sub>3</sub>等が用いられる。

【0051】ここで、この画素電極PXは、図中ほぼx方向に延在しy方向に並設される多数の帯状の電極群から構成されているが、各電極はその延在方向のほぼ中央部に屈曲部を有する山型形状のパターンで形成されている。

【0052】このような画素電極PXは、特にその辺端部(エッヂ)において前記対向電極CTとの間に電界を生じせしめるようになっているが、上述のパターンとすることにより、いわゆるマルチドメイン方式を採用した構成となっている。

【0053】すなわち、液晶はその分子配列が同じ状態でも、液晶表示パネルに入射する光の入射方向によって透過光の偏光状態が変化するので、入射方向に対応して光の透過率が異なってしまう。

【0054】このような液晶表示パネルの視角依存性は50

視角方向に対し視点を斜めに傾けると、輝度の逆転現象を引き起こすことになり、カラー表示の場合に画像が色づくという表示特性を有する。

【0055】このため、前記画素電極PXをその延在方向に少なくとも一つの屈曲部を形成したパターンとし、さらにこのパターンを平行にシフトした形状で対向電極CTを形成し、これら各電極の屈曲点を結んだ仮想の線を境にし一方の領域と他方の領域とで各電極間に作用する電界の方向を異ならしめ、これにより、視野角に依存する画像の色づきを補償するようしている。

【0056】なお、この実施例では、対向電極CTは画素領域のほぼ全域にわたって形成されたものであるが、そのうち実際に対向電極として機能するのは上述したように画素電極PXを平行にシフトした部分となる。

【0057】そして、画素電極PXの電極群はそれらが互いに電気的に接続するために周辺において同一の材料で一体に形成されるようになっている。このことから、画素電極PXは全体として画素領域の周辺の僅かな領域を除く中央部に形成された導電層にそのx方向に延在されy方向に並設された多数スリット(山形状スリット)を形成したパターンとして形成される。

【0058】また、このようなパターンの画素電極PXの一部は前記保護膜PSV1に予め形成されたスルーホールを通して前記薄膜トランジスタTFTのソース電極SD2のコンタクト部COTに電気的接続がなされるようになっている。

【0059】さらに、透明基板SUB1の表面には該画素電極PXをも被って保護膜PSV2が形成されている。この保護膜PSV2はたとえば樹脂からなる有機材料からなっている。

【0060】この保護膜PSV2は、前記保護膜PSV1とともに薄膜トランジスタTFTの液晶の直接の接触を回避する保護膜PSVとして機能することは上述した通りであるが、その材料として有機材料を用いることで表面を平坦化でき、その上方面に形成する配向膜のランディング性を良好にできる。

【0061】さらに、この保護膜PSV2の表面には前記対向電極CTに信号を供給するための対向電圧信号線CLが形成されている。この対向電圧信号線CLは電気40抵抗の小さい材料が選定され、このことから金属等が用いられている。

【0062】また、対向電圧信号線CLは、ドレン信号線DLおよびゲート信号線GLを被うようにした格子状パターンをなし、その開口部は画素領域の周辺の僅かな部分を除いた中央部、すなわち実質的な画素領域を露呈させるように形成されている。

【0063】このようなパターンで形成された対向電圧信号線CLは、前記液晶表示部ARの周辺のうちいかなる個所、および複数からでも対向電圧信号を供給することができる。このため、対向電圧信号線CLにおける対

向電圧信号の波形歪みを無くすことことができ、スマア、輝度傾斜の発生を低減させることができる。

【0064】また、対向電圧信号線CLの全体として電気抵抗、給電抵抗を小さくできることから、いわゆるコモン反転駆動において、横スメアを1/3以下に低減させることができるようなる。

【0065】そして、ドレイン信号線DLをその長手方向に沿って被う対向電圧信号線CLはその中心軸をほぼ一致させて該ドレイン信号線DLよりも幅が大きく形成されている。これにより、ドレイン信号線DLからのノイズの原因となる電界を該対向電圧信号線CL側に終端させ、画素電極PXに終端させにくくしている。

【0066】この場合、ドレイン信号線DLと対向電圧信号線CLとの間の寄生容量は、それらの間に介在される有機材料からなる保護膜PSV2によって大幅に低減されるようになっている。このような保護膜PSV2は誘電率が小さいからである。

【0067】同様に、ドレイン信号線DLをその長手方向に沿って被う対向電圧信号線CLもその中心軸をほぼ一致させて該ドレイン信号線DLよりも幅が大きく形成されている。

【0068】この場合、該対向電圧信号線CLは薄膜トランジスタTFTも被うように形成されている。該対向電圧信号線CLは非透光性の金属で形成され、該薄膜トランジスタTFTに照射される外来光を遮光し、該薄膜トランジスタTFTの特性劣化を防止できるからである。

【0069】なお、該対向電極信号線CLは画素領域内において画素電極PXの一部と重畳する領域を有するようになっており、この領域において、保護膜PSV2を誘電体膜とする容量素子Cstgが形成されている。

【0070】この容量素子Cstgは、たとえば画素電極PXに供給された映像信号を比較的長く蓄積させる等の機能をもたせるようになっている。

【0071】そして、このように対向電極CTが形成された透明基板SUB1の上面には該対向電極CTをも被って配向膜(図示せず)が形成されている。この配向膜は液晶と直接に当接する膜で、その表面に形成されたラビングによって該液晶の分子の初期配向方向を決定づけるようになっている。

【0072】なお、透明基板SUB1と液晶を介して配置される透明基板SUB2の液晶側の面には、カラーフィルタが形成されている。このカラーフィルタはたとえば赤(R)、緑(G)、青(B)の各色のフィルタからなり、y方向に並設される各画素領域群にたとえば赤色のフィルタが共通に形成され、該画素領域群にx方向に順次隣接する画素領域群に共通に赤(R)色、緑(G)色、青(B)色、赤(R)色、……、というような配列で形成されている。

【0073】そして、カラーフィルタが形成された透明

10

基板の表面にはこれらカラーフィルタをも被って平坦化膜が形成されている。この平坦化膜は塗布によって形成できる樹脂膜からなり、該カラーフィルタの形成によって顕在化する段差をなくすために設けられる。

【0074】そして、この平坦化膜の表面には配向膜が形成され、この配向膜は液晶と直接に当接する膜で、その表面に形成されたラビングによって該液晶の分子の初期配向方向を決定づけるようになっている。

【0075】ここで、この実施例では、透明基板SUB2の液晶側の面にはブラックマトリクスが形成されていない構成となっている。透明基板SUB1の液晶側の面に形成された対向電圧信号線CLが該ブラックマトリクスと同様の機能をもつようになるからである。これにより、透明基板SUB1に対する透明基板SUB2の合わせの精度を向上させることができるようになる。

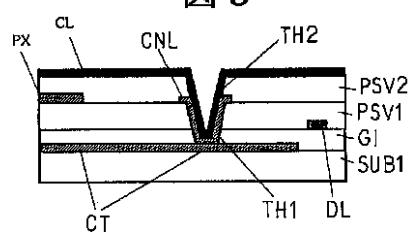

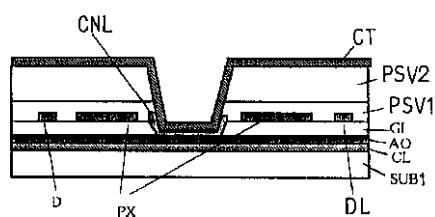

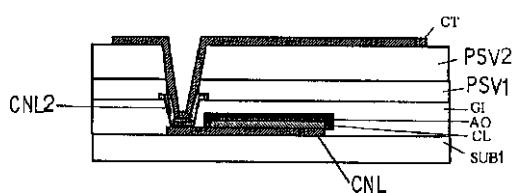

【0076】実施例2.図3は、本発明による液晶表示装置の他の実施例を示す構成図で、図1(b)に対応した図となっている。

【0077】図1(b)の場合と比較して異なる構成は、対向電極CTと対向電圧信号線CLとのスルーホールTHを通しての接続において、画素電極PXを構成する材料層と同一の導電層CNLを介在させていることにある。

【0078】すなわち、保護膜PSV1の上面に画素電極PXを形成する際に、該保護膜PSV1に形成したスルーホールTH1を通して前記対向電極CTと接続される導電層を同時に形成し、その後、保護膜PSV2の上面に形成された対向電圧信号線CLを該保護膜PSV2に形成したスルーホールTH2を通して前記導電層に接続させることによって構成できる。

【0079】このようにした場合、対向電極CTと対向電圧信号線CLとの接続部の接触面積の増大を図ることができ、接続を信頼性あるものとすることができます。

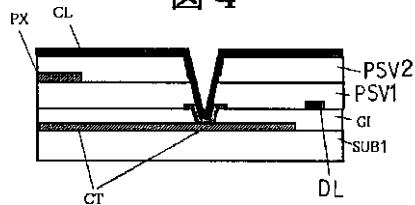

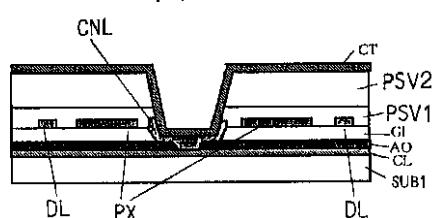

【0080】実施例3.図4は、本発明による液晶表示装置の他の実施例を示す構成図で、図3に対応した図となっている。

【0081】図3の場合と比較して異なる構成は、対向電極CTと対向電圧信号線CLとのスルーホールTHを通しての接続において、ドレイン信号線DLを構成する材料層と同一の導電層CNLを介在させていることある。

【0082】対向電極CTとして透光性の導電材を用い、また、対向電圧信号線CLとしてたとえばA1あるいはその合金を用いた場合、それらの接続抵抗は大きくなることから、前記ドレイン信号線DLとしてたとえばCr、Mo、W、他の高融点金属あるいはこれらを含む合金等を用い、上述した構成とすることによって、対向電極CTと対向電圧信号線CLとの接続抵抗の低減を図った構成とすることができます。

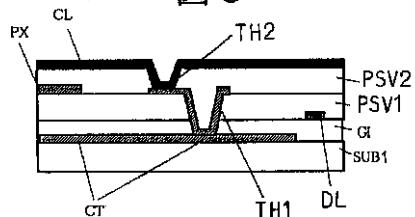

【0083】実施例4.図5は、本発明による液晶表示

40

装置の他の実施例を示す構成図で、図3に対応した図となっている。

【0084】図3の場合と比較して異なる構成は、保護膜PSV1および絶縁膜GIに形成するスルーホールTH1と絶縁膜PSV2に形成するスルーホールTH2はそれらの中心軸を一致させることなく、それぞれ別な個所に形成することにある。

【0085】このようにした場合、有機材料からなる保護膜PSV2の表面は、保護膜PSV1および絶縁膜GIのスルーホールTH1の形成個所においても平坦化されようになる。

【0086】このことは、保護膜PSV2に形成される凹陥部はスルーホールTH2のみとなるが、その深さは比較的浅いことから、該保護膜PSV2の表面に形成される配向膜のラビング性を向上させることができる。

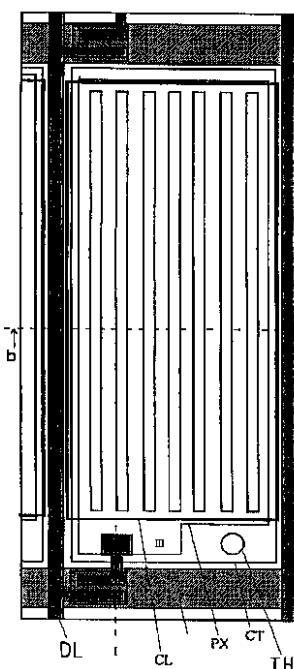

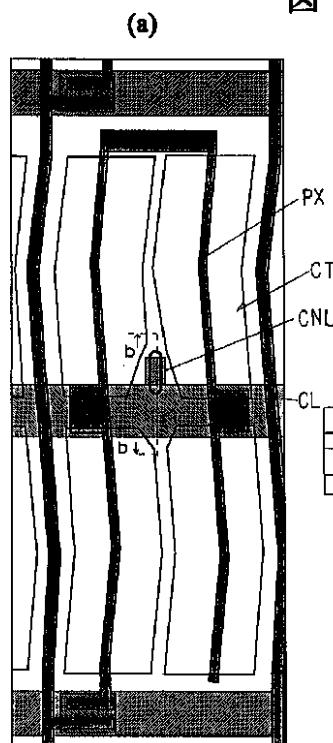

【0087】実施例5.図6は本発明による液晶表示装置の他の実施例を示す構成図で、図1(a)に対応する図となっている。

【0088】図1(a)の場合と比較して異なる構成は、対向電極CTと対向電圧信号線CLとの接続を図る部分が1個のみならず2個設けられていることにある。

【0089】上述した構成から明らかなように、対向電極CTと対向電圧信号線CLとの接続は保護膜PSV2、PSV1、および絶縁膜GIの比較的多層である積層体に形成されたスルーホールTHを通して行なわなければならぬことから、接続不良の発生を回避するための冗長構成となっている。

【0090】一方のスルーホールは画素領域を囲む一方のゲート信号線GLに近接させて形成し、他方のスルーホールは他方のゲート信号線GLに近接させて形成している。

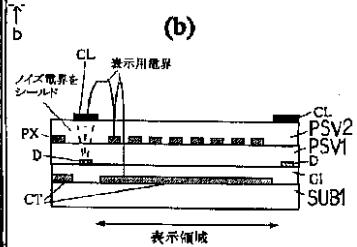

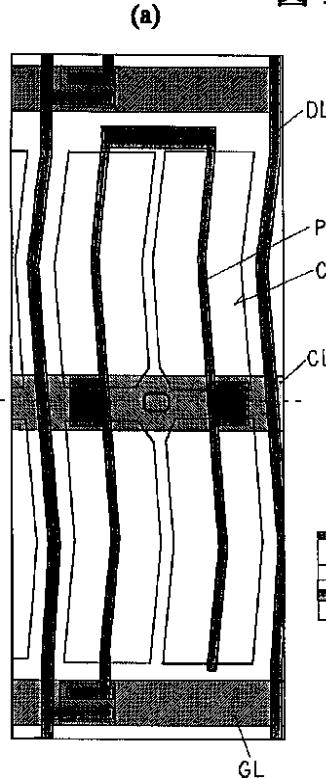

【0091】実施例6.図7(a)は本発明による液晶表示装置の他の実施例を示す平面図で、図1(a)と対応した図となっている。また、図7(b)は図7(a)のb-b線における断面図を示している。

【0092】図1(a)の場合と比較して異なる構成は画素電極PXにあり、この画素電極PXはy方向にほぼ直線状に延在しx方向に並設された電極群から構成されていることにある。

【0093】この場合においても、電極群からなる各画素電極PXはその上下端で互いに接続された構成となっている。

【0094】また、これら画素電極PXをも被って保護膜PSV2が形成され、この保護膜PSV2の上面にドレイン信号線DLおよびゲート信号線GLを被って形成される対向電圧信号線CLが形成されている。

【0095】このように構成した場合、前記対向電圧信号線CLの開口部の領域内に形成された各画素電極PXのうちドレイン信号線DLに隣接する画素領域は該対向電圧信号線CLにより近接させて配置でき、該対向電圧

信号線CLに対向電極CTの機能をもたせてそれらの間に電界を発生せしめるようにできる。

【0096】このことから、前記対向電圧信号線CLの開口部の領域において無駄な領域を形成することなく、画素領域とすることができる、その開口率を向上させることができる。

【0097】すなわち、ドレイン信号線DLからの電界はその上部に形成された対向電圧信号線DL側にほぼ集中的に終端され、該対向電圧信号線CLの両側に放射状に拡がってしまう分が減少することになる。このため、該対向電圧信号線CLの近傍においても表示に寄与できる画素領域として構成できるからである。

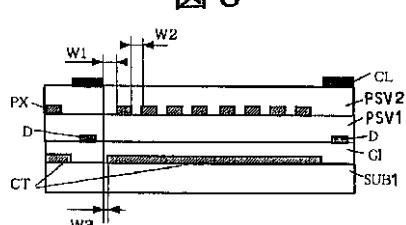

【0098】また、上述した構成のようにすることにより、図7(b)に対応する図である図8に示すように、対向電圧信号線CLとそれに隣接する画素電極PXとの距離W1を各画素電極PXの間の距離W2に対して異なった値に設定するようになる。このことは、たとえば画素電極PXの本数が既に定められており、画素領域間の距離を可変するような設定をするような場合において、対向電圧信号線CLとそれに隣接する画素電極PXの前記距離W1を調整することにより、最適な画素構成を容易に実現することができる。

【0099】さらに、対向電圧信号線CLは誘電率の小さな保護膜PSV2の上面に形成されているため、該対向電圧信号線CLとそれに隣接する画素電極PXとの間の電界強度は、対向電極CTと画素電極PXとの間の電界の強度よりも大きくなる。このため、画素内の輝度均一化を図るために、W1 > W2が望ましく、さらに前記保護膜PSV2の膜厚をdとした場合、W1 > W2 + dとすることが好ましい。

【0100】さらに、ドレイン信号線DLからのノイズをより低減させるには、図8に示すようにW1 > W3となるように設定することが望ましい。ここで、W3は対向電圧信号線CLに近接して配置される対向電極CTとの離間距離である。このように構成することによって、ドレイン信号線DLからのノイズ電界は、同じ電位である対向電圧信号線CLおよび対向電極CTのなす等電位面に閉じ込められ、外部へのノイズ電界の漏出が抑制されるからである。

【0101】ここで、対向電圧信号線CLはドレイン信号線DLに対してその走行方向に平行な辺がそれぞれ1/3 × W1以上にはみ出して形成することが好ましい。

【0102】なお、上述した実施例において、各画素電極PXをその長手方向に一つあるいは複数の屈曲部を設けることによってマルチドメイン方式を採用するようにしてもよいことはもちろんである。この場合、これにともない、ドレイン信号線DLおよび対向電圧信号線CLをも画素電極PXをx方向にシフトさせたように屈曲部を有するパターンとすれば、上述した効果を奏することができる。

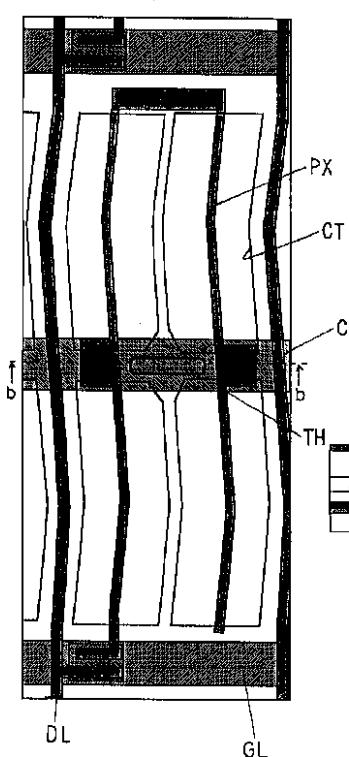

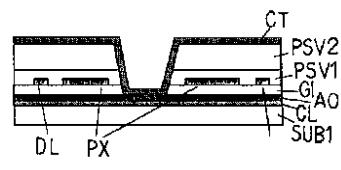

【0103】実施例7.図9(a)は本発明による液晶表示装置の他の実施例を示す平面図で、図7(a)と対応した図となっている。また、図9(b)は図9(a)のb-b線における断面図を示している。

【0104】図7(a)の場合と比較して異なる構成は、まず、画素電極PXが絶縁膜GI上にてドレイン信号線DLと同層に形成されている。

【0105】そして、該画素電極PXおよびドレイン信号線DLをも被って保護膜PSV1、保護膜PSV2が順次形成され、該保護膜PSV2の上面にドレイン信号線DLおよびゲート信号線GLをも被って格子状パターンの対向電極CTが形成されている。

【0106】さらに、この対向電極CTは保護膜PSV2、保護膜PSV1および絶縁膜GIに貫通して形成されたスルーホールTHを通して該絶縁膜GIの下層として形成された対向電圧信号線CLに電気的に接続されている。

【0107】なお、画素電極PX、対向電極CT(ドレイン信号線DL)はその走行方向に沿って複数の屈曲部が形成されてマルチドメイン方式が採用されている。

【0108】この場合、対向電圧信号線CLはゲート信号線GLの形成の際に同時に形成され、それらはたとえばA1あるいはその合金層からなるとともに、その表面に陽極化成された酸化膜AOが形成されたものが考えられる。

【0109】本実施例は、陽極化成された対向電圧信号線CLの一部を露呈させるようにして保護膜PSV2、保護膜PSV1および絶縁膜GIにスルーホールTHを形成し、このスルーホールTHを被うようにして対向電極CTを形成していることにある。

【0110】すなわち、対向電極CTと対向電圧信号線CLとの電気的接続は前記酸化膜AOを介した容量結合によってなされており、これにより、該接続部における酸化膜AOの除去を行なわない構成としている。

【0111】対向電極CTは格子状のパターンからなることから、この対向電極CTから給電を行なうことができ、対向電圧信号線CLには直接の給電を行なわなくてよいわゆるコモン電位を安定化させる役割りを有する。

【0112】このことから、他の実施例とし、図10に示すように、陽極化成された対向電圧信号線CLと対向電極CTとの電気的接続部の間にさらにドレイン信号線DLと同一の導電層CNLを介在させるようにしてもよいことはもちろんである。

【0113】また、このような容量結合の構成を行なった場合、対向電圧信号線CLと対向電極CTとをそれ材料を異にするようにしてもよい。それらの間に応力が発生し結合部でクラックが発生しても直接的な電気的接続が図れるからである。

【0114】実施例8.図11(a)は本発明による液晶表示装置の他の実施例を示す平面図で、図9(a)と

対応した図となっている。また、図11(b)は図11(a)のb-b線における断面図を示している。

【0115】図9(a)の場合と比較して、対向電圧信号線CLはA1(あるいはMo、Ti、Ta、W、Zr、Siまたはこれらの一もしくは複数との合金)で構成され、その表面には陽極化成による酸化膜AOが形成されているのは同様であるが、その一部の下層にA1あるいはその合金以外に他の導電層(たとえばCr、Mo、W、Ti、Zrあるいはこれらの一もしくは複数の合金)CNLが形成され、かつ対向電圧信号線CLの形成領域以外の領域にまで延在されて形成されていることがある。

【0116】この導電層CNLの該延在部は対向電極CTとのコンタクト部として機能するようになっている。前記対向電圧信号線CLを陽極化成しても、前記金属層は陽極化成されることはなく、該対向電圧信号線CLと充分に電気的接続が図れる端子部を形成できるからである。

【0117】なお、前記導電層CNLは前記延在部を除く部分において対向電圧信号線CLの形成領域の全域に形成されていてもよいことはもちろんである。換言すれば、前記導電層CNLは対向電圧信号線CLと同パターンでしかもその一部において延在部が形成されたパターンとして形成されるようにしてもよい。

【0118】図12は、本発明による液晶表示装置の他の実施例を示す断面図で、図11(b)に対応した図となっている。

【0119】前記導電層CNLと対向電極CTとの間にドレイン信号線DLの材料層と同一の導電層CNL2を介して接続を図った構成としたものである。

【0120】このようにした場合、前記金属層と対向電極CTとの接触面積を増大でき、接続の信頼性を向上させることができる。

【0121】実施例9.上記実施例8に示した構成の他の実施例として、前記金属層をITO、IZO等の透光性の導電層に代えて構成してもよい。

【0122】このようにした場合、対向電極CTも透光性の導電層であることから、それらの接続部においてたとえ面積を増大させても、画素領域の開口率を低減させることにはならないという効果を奏する。

【0123】実施例10.図13(a)は、本発明による液晶表示装置の他の実施例を示す断面図で、図11(a)に対応した図となっている。図13(b)は図13(a)のb-b線における断面図である。

【0124】図11(a)の場合と比較して異なる構成は、対向電極CTと対向電圧信号線CLとの電気接続部において、該対向電圧信号線CLの表面に形成されている酸化膜AOを、その陽極化成時に、部分的に形成されないようにして構成したものである。

【0125】すなわち、対向電圧信号線CLが形成され

た透明基板SUB1ごと電界溶液中に浸漬させ、該対向電圧信号線CLを一方の電極、該電界溶液中に浸漬された別個の他の電極板を他方の電極として電圧を印加することにより(陽極化成)、該対向電圧信号線CLの表面上に陽極酸化膜を形成させている。

【0126】この場合、該対向電圧信号線CLの対向電極CTとの接続個所において、レジスト膜を選択的に形成した状態で陽極化成を行なう。この陽極化成が終了した段階で該レジスト膜を除去することで、その部分にA1あるいはその合金の表面が露出した対向電圧信号線CLを得ることができる。

【0127】なお、前記レジストの形成は、ホトレジストを全面に形成した後、マスク露光により露光し、不要部のレジストを除去する通常の露光処理で行なう。

【0128】この場合、対向電極CTは、対向電圧信号線CL上の酸化膜AOの除去部のみでなくその周辺の酸化膜AO形成領域上にも形成された構成とすることが望ましい。

【0129】さもなくとも、化成されていないA1あるいはその合金が直接絶縁膜GIと相対することになり、いわゆるヒロック発生の懸念があるからである。

【0130】実施例11.図14は、本発明による液晶表示装置の他の実施例を示す断面図で、図13(b)に対応した図となっている。

【0131】図13(b)の場合と比較して異なる構成は、対向電極CTと対向電圧信号線CLとの接続において、絶縁膜GI上に形成されているドレイン信号線DLの材料と同一の導電層CNLを介在させるようにしたことがある。

【0132】このようにした場合、対向電圧信号線CLのA1あるいはその合金とITO等の透光性の導電層との直接の接続を回避でき、接続抵抗の増大を抑制することができるようになる。透光性の前記導電層は酸化物であるため、A1あるいはその合金と直接に接触させた場合、該A1あるいはその合金が酸化されてしまうため、接続抵抗が増大してしまうからである。

【0133】実施例12.図15(a)ないし(c)は本発明による液晶表示装置の他の実施例を示す説明図である。

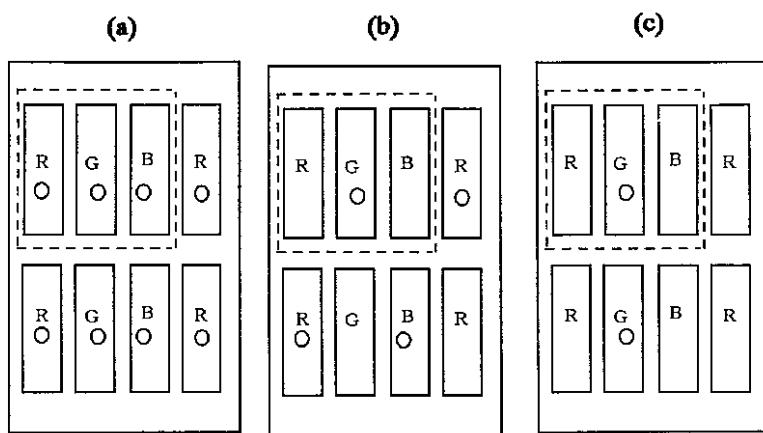

【0134】各図は対向電圧信号線CLと対向電極CTとの接続を、たとえば図15(a)では各画素ごとに、図15(b)では隣接する複数の画素においてその一つの画素ごとに、図15(c)ではカラー表示用の3画素においてその一つの画素ごとに設けていることにある。

【0135】上述したように、対向電圧信号線CLあるいは対向電極CTは各画素領域を画するようにした格子状のパターンとなっていることから、それらの接続においては場所的にも数的にも任意なものとして設定することができる。

【0136】しかし、対向電圧信号線CLと対向電極C

Tとの接続を輝度の比較的高い画素内に位置づけることにより、該輝度への影響を防止することができる。

【0137】また、透明基板SUB1と透明基板SUB2との間にいずれかの基板に形成したいわゆる支柱状のスペーサを設ける場合において、該スペーサを形成する画素領域と、対向電圧信号線CLと対向電極CTとの接続を図る画素領域とを別個にするようにしてもよい。

【0138】この場合、特定が素領域の立体構造が他の画素に比べ相対的に複雑になることを抑制でき、立体構造の差による予期せぬ不良が特定画素にのみ発生するような憂いを予め回避できる。

【0139】

【発明の効果】以上説明したことから明らかなように、本発明による液晶表示装置によれば、画素領域の開口率を向上させることができる。また、対向電極と対向電圧信号線の信頼性ある接続を図ることができる。

【図面の簡単な説明】

【図1】本発明による液晶表示装置の画素の一実施例を示す構成図である。

【図2】本発明による液晶表示装置の一実施例を示す構成図である。

【図3】本発明による液晶表示装置の画素の他の実施例を示す断面図である。

【図4】本発明による液晶表示装置の画素の他の実施例を示す断面図である。

【図5】本発明による液晶表示装置の画素の他の実施例を示す断面図である。

【図6】本発明による液晶表示装置の画素の他の実施例を示す平面図である。

【図7】本発明による液晶表示装置の画素の他の実施例を示す構成図である。

【図8】本発明による液晶表示装置の画素の他の実施例を示す断面図である。

【図9】本発明による液晶表示装置の画素の他の実施例を示す構成図である。

【図10】本発明による液晶表示装置の画素の他の実施例を示す断面図である。

【図11】本発明による液晶表示装置の画素の他の実施例を示す構成図である。

【図12】本発明による液晶表示装置の画素の他の実施例を示す断面図である。

【図13】本発明による液晶表示装置の画素の他の実施例を示す構成図である。

【図14】本発明による液晶表示装置の画素の他の実施例を示す断面図である。

【図15】本発明による液晶表示装置の画素の他の実施例を示す説明図である。

【符号の説明】

SUB1…透明基板、GL…ゲート信号線、DL…ドレイン信号線、CL…対向電圧信号線、TFT…薄膜トランジスタ

ンジスタ、Cstg...容量素子、PX...画素電極、CT...対向電極、CNL...導電層、GI...絶縁膜(\*縁膜)、PSV1...保護膜(無機材料)、PSV2...保護膜(有機材料)。

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図8】

図8

【図6】

図6

【図7】

図7

(a)

(b)

【図9】

図9

(a)

(b)

【図10】

図10

【図14】

図14

【図11】

図11

(b)

【図12】

図12

【図13】

図13

(b)

【図15】

図15

フロントページの続き

Fターム(参考) 2H092 GA06 GA14 GA17 GA25 GA26

GA29 HA04 JA24 JB16 JB58

NA07

|                |                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2003195330A</a>                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2003-07-09 |

| 申请号            | JP2001396509                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2001-12-27 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | 仲吉 良彰<br>柳川 和彦                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 仲吉 良彰<br>柳川 和彦                                                                                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G02F1/134363 G02F1/1343 G02F1/1362 G02F2201/122                                                                                                                                                                                                                                                                                                                            |         |            |

| FI分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 2H092/GA06 2H092/GA14 2H092/GA17 2H092/GA25 2H092/GA26 2H092/GA29 2H092/HA04 2H092/JA24 2H092/JB16 2H092/JB58 2H092/NA07 2H192/AA24 2H192/AA42 2H192/BB04 2H192/BB13 2H192/BB53 2H192/BB73 2H192/BB84 2H192/BC31 2H192/CB05 2H192/CC04 2H192/CC55 2H192/DA42 2H192/DA72 2H192/EA04 2H192/EA43 2H192/EA62 2H192/EA72 2H192/GA03 2H192/GA41 2H192/GD61 2H192/HA86 2H192/JA32 |         |            |

| 其他公开文献         | JP4162890B2<br>JP2003195330A5                                                                                                                                                                                                                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

为了提高像素区域的开口率。在彼此相对的基板之一的液晶侧表面上彼此平行地布置的多条栅极信号线和彼此平行地布置的多条栅极信号线之间夹有液晶。由漏极信号线围绕的区域被定义为像素区域，并且通过来自栅极信号线的扫描信号和来自漏极信号线的视频信号操作的开关元件通过开关元件被提供给这些像素区域中的每个。经由对电压信号线向其提供作为视频信号的基准的信号的对电极，该对电极形成在多个绝缘层的层叠体的下层。相对电压信号线由不透明的导体构成，并形成在多个绝缘层的层叠体的上层，并覆盖栅极信号线和漏极信号线而形成栅格图案。然而，其一部分通过形成在多个绝缘层的层叠体中的通孔电连接到对电极。