(19)日本国特許庁 (JP)

(12) 公開特許公報 (A) (11)特許出願公開番号

特開2002-258810

(P2002-258810A)

(43)公開日 平成14年9月11日(2002.9.11)

| (51) Int.Cl <sup>7</sup> | 識別記号 | F I           | テ-マコード <sup>8</sup> (参考) |

|--------------------------|------|---------------|--------------------------|

| G 0 9 G 3/36             |      | G 0 9 G 3/36  | 2 H 0 9 3                |

| G 0 2 F 1/133            | 550  | G 0 2 F 1/133 | 5 C 0 0 6                |

|                          | 575  |               | 5 C 0 8 0                |

| G 0 9 G 3/20             | 621  | G 0 9 G 3/20  | 621 M                    |

|                          | 623  |               | 623 A                    |

審査請求 未請求 請求項の数 90 L (全 25数) 最終頁に続く

(21)出願番号 特願2001-59394(P2001-59394)

(22)出願日 平成13年3月5日(2001.3.5)

(71)出願人 000005108

株式会社日立製作所

東京都千代田区神田駿河台四丁目6番地

(71)出願人 000233088

日立デバイスエンジニアリング株式会社

千葉県茂原市早野3681番地

(72)発明者 勇 広宣

千葉県茂原市早野3300番地 株式会社日立

製作所ディスプレイグループ内

(74)代理人 100075096

弁理士 作田 康夫

最終頁に続く

(54)【発明の名称】 液晶表示装置

(57)【要約】

【課題】小型の駆動回路を表示部と同一基板上に形成した液晶表示装置を実現する。

【解決手段】画素に階調電圧を供給する駆動回路の幅を、画素と同じ幅で形成する。駆動回路は複数の表示データ線により伝えられた表示データをもとに、階調電圧を出力する電圧選択回路を有し、電圧選択回路を構成する演算素子を表示データ線毎に設け、該演算素子を同じ導電型のトランジスタにより構成する。

## 【特許請求の範囲】

【請求項1】第1の基板と、第2の基板と、上記第1の基板と第2の基板とに挟まれた液晶組成物と、上記第1の基板に設けられた複数の画素と、

前記複数の画素に映像信号電圧を供給する複数の映像信号線と、

前記映像信号線に映像信号電圧を出力する駆動回路とを備える液晶表示装置であって、

前記駆動回路は、電圧レベルが時間とともに変化する階調電圧と、表示データ信号と、時間制御信号とが入力し、前記表示データ信号の値に応じて、前記階調電圧から1つの電圧を選択し前記映像信号線に出力する選択回路を具備し、

前記選択回路には前記表示データ信号を供給する複数の表示データ信号線が接続され、前記表示データ信号線の隣り合う2本の間には演算回路が設けられ、

前記演算回路は表示データ信号が制御端子に入力する表示データ用スイッチング素子と、時間制御信号が制御端子に入力する時間信号用スイッチング素子とを有し、

前記表示データ用スイッチング素子と前記時間信号用スイッチング素子とは並列に接続されて前記演算回路を形成し、

前記演算回路は直列に接続されて前記選択回路を形成することを特徴とする液晶表示装置。

【請求項2】前記表示データ用スイッチング素子と前記時間信号用スイッチング素子とは同じ導電型のトランジスタであることを特徴とする請求項1に記載の液晶表示装置。

【請求項3】前記第1の基板はシリコン基板であることを特徴とする請求項1に記載の液晶表示装置。

【請求項4】第1の基板と、第2の基板と、上記第1の基板と第2の基板とに挟まれた液晶組成物と、上記第1の基板にマトリクス状に設けられた複数の画素と、

列方向に延在し行方向に複数本並んで配置され前記複数の画素に映像信号電圧を供給する映像信号線と、

前記映像信号線に映像信号電圧を出力する駆動回路とを備える液晶表示装置であって、

前記駆動回路は、複数の階調電圧の中から映像信号電圧を選択する選択回路と、前記選択回路にタイミング信号を出力するシフトレジスタと、前記選択回路に電圧レベルが時間とともに変化する階調電圧を供給する階調電圧線と、前記選択回路に表示データ信号を供給する複数の表示データ信号線と、時間に応じて値が変化する時間制御信号を前記選択回路に供給する時間制御信号線と、前記選択回路にシフトレジストからのタイミング信号を供給するタイミング信号線とを有し、

前記選択回路は、行方向に延在し列方向に複数本並んで配置された前記表示データ信号線の隣り合う2本の間に設けられた演算回路と表示データ取り込み回路とを有し、

前記演算回路は表示データ信号が制御端子に入力する表示データ用スイッチング素子と、時間制御信号が制御端子に入力する時間信号用スイッチング素子とを有し、前記表示データ用スイッチング素子と前記時間信号用スイッチング素子とは並列に接続されて前記演算回路を形成し、

前記演算回路は直列に接続されて前記選択回路を形成し、

前記タイミング信号線は前記シフトレジスタから列方向に延在して、複数の前記表示データ取り込み回路に接続され、

前記タイミング信号線を形成する導電層は、前記表示データ取り込み回路の制御端子と同層の導電層からなることを特徴とする液晶表示装置。

【請求項5】前記表示データ用スイッチング素子と前記時間信号用スイッチング素子とは同じ導電型のトランジスタであることを特徴とする請求項4に記載の液晶表示装置。

【請求項6】前記第1の基板はシリコン基板であることを特徴とする請求項4に記載の液晶表示装置。

【請求項7】第1の基板と、第2の基板と、上記第1の基板と第2の基板とに挟まれた液晶組成物と、上記第1の基板に設けられた複数の画素と、

前記複数の画素に映像信号電圧を供給する複数の映像信号線と、

前記映像信号線に映像信号電圧を出力する駆動回路とを備える液晶表示装置であって、

前記駆動回路は、電圧レベルが時間とともに変化する階調電圧を供給する階調電圧線と、表示データ信号を供給する複数の表示データ信号線と、時間制御信号を供給する時間制御信号線と、前記表示データ信号線の値に応じて、前記階調電圧から1つの電圧を選択し前記映像信号線に出力する選択回路とを有し、

前記選択回路は表示データ信号線毎に演算回路と、前記演算回路の演算結果に従い前記階調電圧を前記映像信号線に出力する出力回路とを有し、

前記演算回路は表示データ信号が制御端子に入力する表示データ用スイッチング素子と、時間制御信号が制御端子に入力する時間信号用スイッチング素子とを有し、

前記表示データ用スイッチング素子と前記時間信号用スイッチング素子とは並列に接続されて前記演算回路を形成し、

前記表示データ信号線毎に形成された演算回路と前記出力回路は直列に接続されて選択回路を形成し、

前記演算回路は、前記表示データ用スイッチング素子と時間信号用スイッチング素子のOR回路であり、

前記選択回路は直列に接続された全ての前記演算回路が、オン状態となることで、定電圧を演算結果として前記出力回路に出力することを特徴とする液晶表示装置。

50 【請求項8】前記表示データ用スイッチング素子と前記

時間信号用スイッチング素子とは同じ導電型のトランジスタであることを特徴とする請求項7に記載の液晶表示装置。

【請求項9】前記第1の基板はシリコン基板であることを特徴とする請求項7に記載の液晶表示装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、液晶表示装置に係わり、特に、各画素に映像信号電圧を供給する回路に適用して有効な技術に関する。

【0002】

【従来の技術】画素毎に能動素子（例えば、薄膜トランジスタ）を有し、この能動素子をスイッチング駆動するアクティブマトリクス型液晶表示装置は、ノート型パソコン等の表示装置として広く使用されている。

【0003】このアクティブマトリクス型液晶表示装置の1つに、TFT (Thin Film Transistor) 方式の液晶表示モジュールが知られている。TFT方式の液晶表示モジュールでは、薄膜トランジスタ (TFT) を介して画素電極に映像信号電圧（階調電圧）を印加するため、各画素間のクロストークがなく、単純マトリクス型液晶表示装置のようにクロストーク防止するための特殊な駆動方法を用いることなく、多階調表示が可能である。しかしながら、階調電圧を画素電極に供給する方法として、デジタルデータである表示データの値から階調電圧を選択する所謂D/A変換の方法を用いる場合に、多階調化が進むと表示データのビット数が増加し、それに伴い、回路規模が大きくなるといった問題や、更には回路の動作速度が不十分であるといった問題が生じる。また前記問題は駆動回路を表示部と同一基板上に形成する駆動回路一体型の液晶表示装置では、有効表示部以外の駆動回路部が大きくなってしまうために、特に問題となっている。

【0004】しかしながら、映像機器からの出力信号がアナログ信号からデジタル信号に変更される傾向に伴い、駆動回路一体型の液晶表示装置においても、液晶表示装置にデジタル信号を入力し、液晶パネル上に形成した駆動回路で、デジタル信号を多階調の映像信号電圧に変換する駆動方法がのぞまれている。アクティブマトリクス型液晶表示装置において、デジタル信号入力による多階調表示を可能にするために、各画素に多階調の映像信号電圧を印加する駆動方法として、特開平5-35200号公報に記載されている方法が知られている。

【0005】前記公報（特開平5-35200号）に記載されている方法は、2<sup>m</sup>個の電圧バスラインを設け、この2<sup>m</sup>個の電圧バスラインから供給される階調電圧を、1走査期間（1走査ライン）の間2<sup>k</sup>個の階段状に変化させる。そして、nビットの表示データの上位mビットの値により、前記2<sup>m</sup>個の電圧バスラインのいずれかの一つを選択し、また、nビットの表示データの下位

k（k = n - m）ビットの値により、当該選択された電圧バスライン上の階調電圧の階段状に変化する電圧レベルの一つを選択して、各画素の画素電極に印加するものである。

【0006】例えば、表示データが3ビット（n = 3）であり、また、mが1、kが2である場合、2本の電圧バスラインを設け、この2本の電圧バスライン上の階調電圧の電圧レベルを、1走査期間の間、それぞれ4個の階段状に変化させるようにし、そして、3ビットの表示データの上位1ビットの値により、2本の電圧バスラインのいずれか1本の電圧バスライン上の階調電圧を選択し、当該選択された電圧バスライン上の4個の階段状に変化する電圧レベルの一つを、3ビットの表示データの下位2ビットの値により選択し、各画素の画素電極に印加すようにしたものである。

【0007】前記公報に記載された駆動方法によれば、各画素に映像信号電圧を印加する回路の動作速度を低減でき、画像全体としてD/A変換による映像信号電圧のばらつきを少なくでき、また、電圧バスラインの本数を低減することが可能である。

【0008】しかし、高画質化に対応するために階調数が増加すると、階段状に変化する電圧レベルを選択する選択回路の回路規模が大きくなり、当該選択回路を液晶表示パネル内に組み込む場合には、当該選択回路の占有面積が大きくなり、液晶表示パネルが大型化するという問題が生じる。前記問題点を解決する液晶表示装置として、特開2000-194330号公報に記載されている選択回路の幅を狭くする方法が知られている。

【0009】【発明が解決しようとする課題】近年、液晶表示装置においては、64階調、あるいは256階調へとより多階調化が進みつつある。そして、前記公報（特開2000-194330号公報）に記載された駆動回路では、64階調、あるいはそれ以上の多階調を実現する場合に、駆動回路が長くなることに伴う問題点については考慮されていない。また、液晶表示装置においては、高解像度化も進んでおり画素の高密度化に伴い、駆動回路を形成する領域、所謂占有面積を小さくすること、特に必要最小限の素子数についても考慮されていない。

【0010】本発明は前記従来技術の問題点を解決するためになされたものであり、本発明は液晶表示装置において、駆動回路の回路規模を小さくし、回路の占有面積を小さくすることが可能となる技術を提供することにある。

【0011】本発明の前記目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

【0012】

【課題を解決するための手段】本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記のとおりである。

【0013】液晶表示装置の駆動回路と表示部とを同一基板上に設け、駆動回路には、電圧レベルが時間とともに変化する階調電圧と、表示データ信号と、時間制御信号とを供給し、駆動回路に設けられた選択回路は表示データ信号の値に応じて、階調電圧から1つの電圧を選択し映像信号線に出力する構成とする。選択回路は隣り合う2本の表示データ信号線の間に設けられた演算回路を有し、演算回路は表示データ信号線が制御端子に入力する表示データ用スイッチング素子と、時間制御信号線が制御端子に入力する時間信号用スイッチング素子とを有し、表示データ用スイッチング素子と時間信号用スイッチング素子とは並列に接続されて演算回路を形成し、演算回路は直列に接続されて選択回路を形成する。

【0014】表示データ用スイッチング素子と時間信号用スイッチング素子とを並列に接続して演算回路を形成することで、回路の占有面積が小さな駆動回路を実現できる。

#### 【0015】

【発明の実施の形態】以下、本発明実施の形態を図面を参照して説明する。なお、発明の実施の形態を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

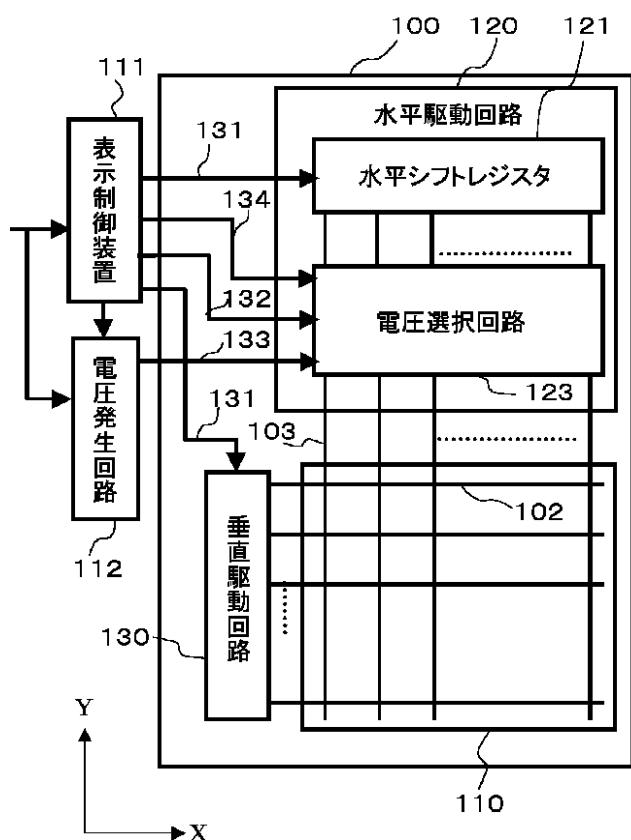

【0016】図1は、本発明の実施の形態である液晶表示モジュールの概略構成を示すブロック図である。本実施の形態の液晶表示モジュールは、液晶パネル（液晶表示素子）100と、表示制御装置111と、電圧発生回路112とで構成される。液晶パネル100は、表示部110と、水平駆動回路（映像信号線駆動回路）120と、垂直駆動回路（走査信号線駆動回路）130とから構成される。また、表示部110と水平駆動回路120と垂直駆動回路130とは同一基板上に設けられている。なお、表示制御装置111と電圧発生回路112とを、液晶パネル100と分離して示しているが、液晶パネル100と同一基板上に設けることも可能である。

【0017】表示制御装置111は外部から送信されてくるクロック信号、ディスプレイタイミング信号、水平同期信号、垂直同期信号等の制御信号を基に、水平駆動回路120および、垂直駆動回路130を制御する。表示制御装置111は液晶パネル100に表示すべき画像データである表示データを水平駆動回路120に供給する。電圧発生回路112は液晶パネル100が表示を行うために必要な電圧を発生する。水平駆動回路120は表示データに従い電圧発生回路112から供給される任意の電圧（階調電圧）を表示部110に出力し、表示部110では垂直駆動回路130から出力する信号（走査信号）に従い階調電圧を画素（図示せず）に取り込む。

【0018】水平駆動回路120からは垂直方向（図中Y方向）に、複数本の映像信号線（ドレイン信号線または垂直信号線ともいう）103が表示部110にまで延びてあり、また複数本の映像信号線103は水平方向

（X方向）に並んで設けられている。階調電圧は映像信号線103により表示部110に供給される。垂直駆動回路130からは水平方向（X方向）に複数本の走査信号線（ゲート信号線または水平信号線ともいう）102が表示部110にまで延びており、また複数本の走査信号線102は垂直方向（Y方向）に並んで設けられている。走査信号は走査信号線102により表示部110に伝えられる。

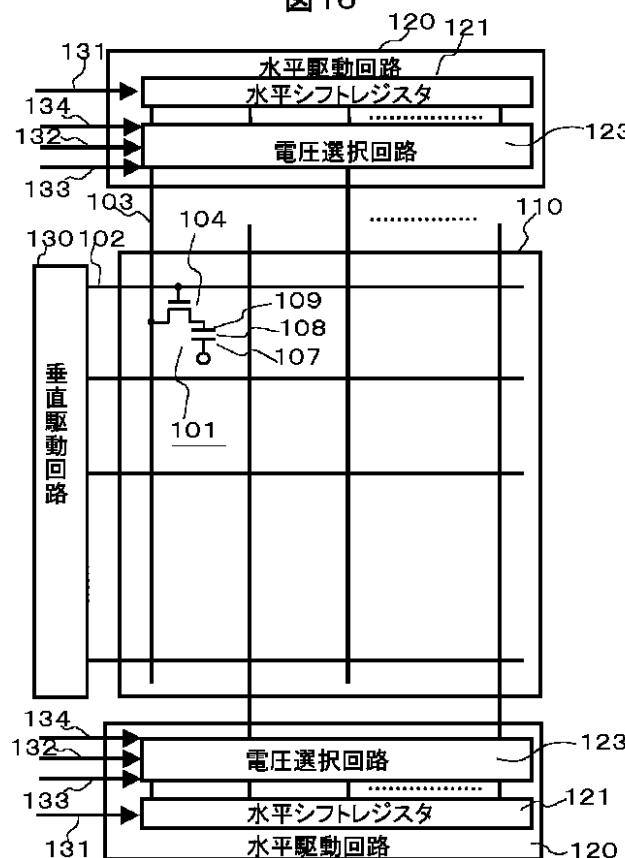

【0019】水平駆動回路120は、水平シフトレジスタ121と、電圧選択回路123とから構成される。表示制御装置111からタイミング制御信号線131が水平シフトレジスタ121及び垂直駆動回路130に接続され、表示データ線132と時間制御信号線134とが電圧選択回路123に接続されている。また階調電圧線133が電圧発生回路112から電圧選択回路123に接続され階調電圧が供給されている。なお、各回路の電源電圧線については表示を省略したが、必要な電圧が供給されているものとする。

【0020】表示制御装置111は、垂直同期信号入力後に、第1番目のディスプレイタイミング信号が入力されると、これを第1番目の表示ラインと判断してタイミング制御信号線131により垂直駆動回路130にタイミング制御信号の一つであるスタートパルスを出力する。次に、表示制御装置111は水平同期信号に基づいて、1水平走査時間毎に、走査信号線102を順次選択するようにシフトクロックを垂直駆動回路130に出力する。垂直駆動回路130は、シフトクロックに従い走査信号線102を選択し、走査信号線102に走査信号を出力する。

【0021】また、表示制御装置111は、ディスプレイタイミング信号が入力されると、これを表示開始と判断し、表示データを水平駆動回路120に出力する。表示制御回路111から表示データは順次出力されるが、水平シフトレジスタ121は表示制御装置111から送られてくるタイミング制御信号の一つであるシフトクロックに従い、各映像信号線103に出力すべき表示データを選択するタイミング信号を電圧選択回路123に出力する。

【0022】電圧選択回路123はタイミング信号に従い表示データを取り込み、該表示データに従い電圧発生回路112が供給する階調電圧の中から任意の電圧を選択して映像信号線103に出力する。なお、電圧選択回路123については後で詳述する。

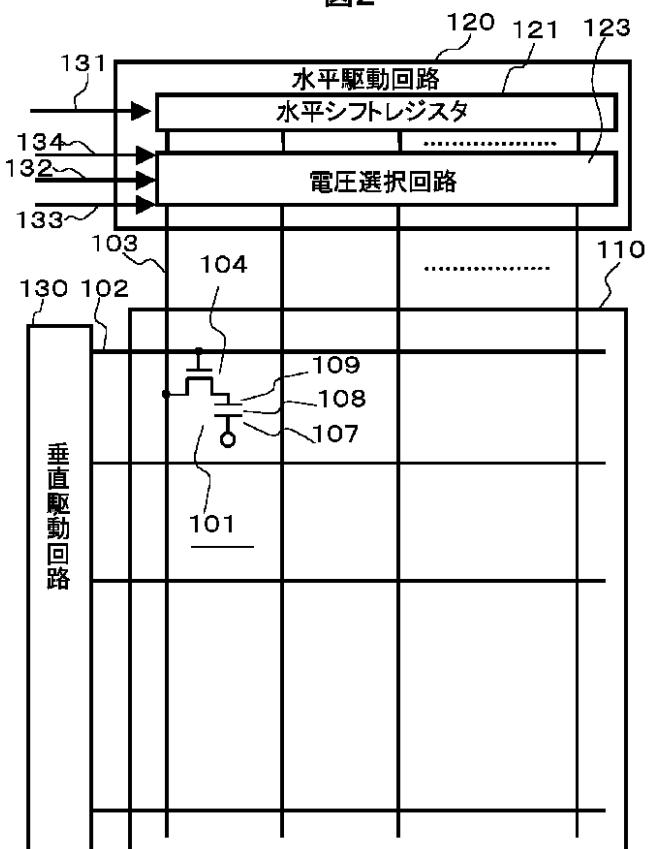

【0023】図2に、本発明の実施の形態である液晶パネル100の等価回路図を示す。なお、図2は回路図ではあるが、実際の幾何学的配置にも対応している。

【0024】表示部110は、マトリクス状に配置される画素部101を有している。ただし、図2では図を簡略化するため1つの画素部だけを示している。各画素部101は、スイッチング素子104と画素電極109を

有している。各画素部は隣接する2本の走査信号線102と、隣接する2本の映像信号線103との交差領域（4本の信号線で囲まれた領域）に配置される。

【0025】前述したように、走査信号線102には垂直駆動回路130から1水平走査時間毎に、走査信号が順次出力している。この走査信号によりスイッチング素子104のオン・オフが制御される。映像信号線103には階調電圧が供給されており、スイッチング素子104がオンになると、映像信号線103から画素電極109に階調電圧が供給される。画素電極109に対向するように対向電極（コモン電極）107が配置されており、画素電極109と対向電極107との間には液晶層（図示せず）が設けられている。なお、図2に示す回路図上では画素電極109と対向電極107との間は等価的に液晶容量108が接続されているように表示した。

【0026】画素電極109と対向電極107との間に電圧を印加することにより、液晶層の光に対する性質が変化し表示が行われる。液晶パネルが表示する画像を構成する各画素の階調は、画素電極109に供給される電圧に従う。そのため、液晶パネルが表示する階調数の増加に従い、画素電極109に供給される電圧（階調電圧）の数も増加する。また、表示部110においては、全体の面積に対して画素電極109の占める面積に従い、表示部110の明るさが決まるため、画素部101において画素電極109はなるべく大きくなるように形成される。言い換えると、液晶パネルでは画素電極109以外の構成が占める面積はなるべく狭くなるよう工夫されている。

【0027】前述したように、画素電極109に供給される階調電圧は電圧選択回路123から出力する。液晶パネル100の表示する階調数が増加した場合に、電圧選択回路123は多くの階調数の中から映像信号線103に出力する電圧を選択することになる。また、表示制御装置111から電圧選択回路123に接続されている表示データ線132で伝えられるデータ量も増加する。そのため、液晶パネル100の表示する階調数が増加した場合に、表示データ線132の本数が増加しそれに伴い電圧選択回路123の回路規模が大きくなってしまうという問題が生じる。そこで、電圧選択回路123をなるべく小さな回路で構成し、液晶パネル内に効率よく配置することとした。また、特に駆動回路が表示部と同一基板上に形成される、所謂駆動回路一体型の液晶表示装置において、液晶表示装置は小型化が進み、階調数が増加した場合の問題点についても解決することとした。以下図3を用いて電圧選択回路123について説明する。

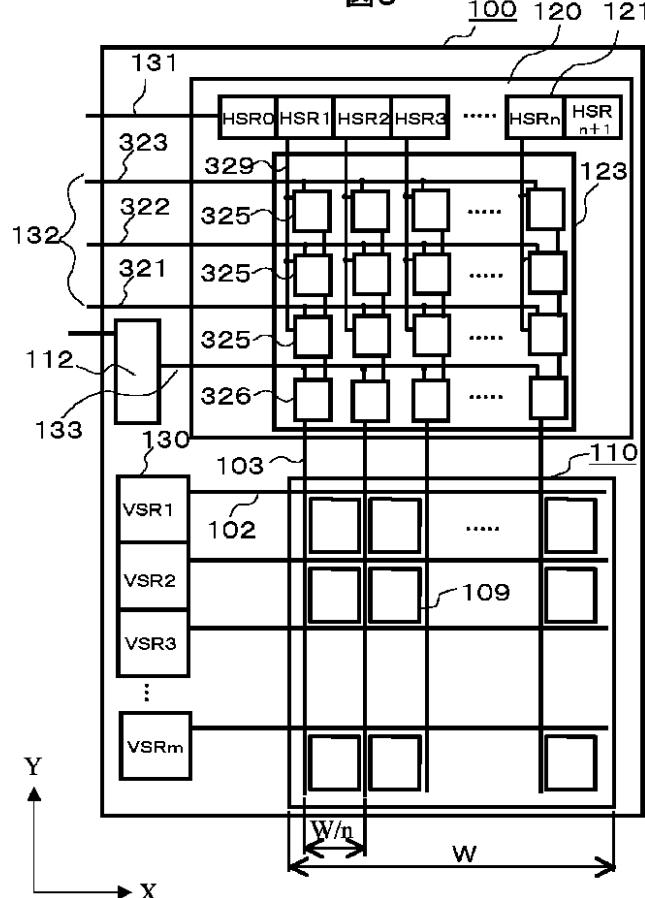

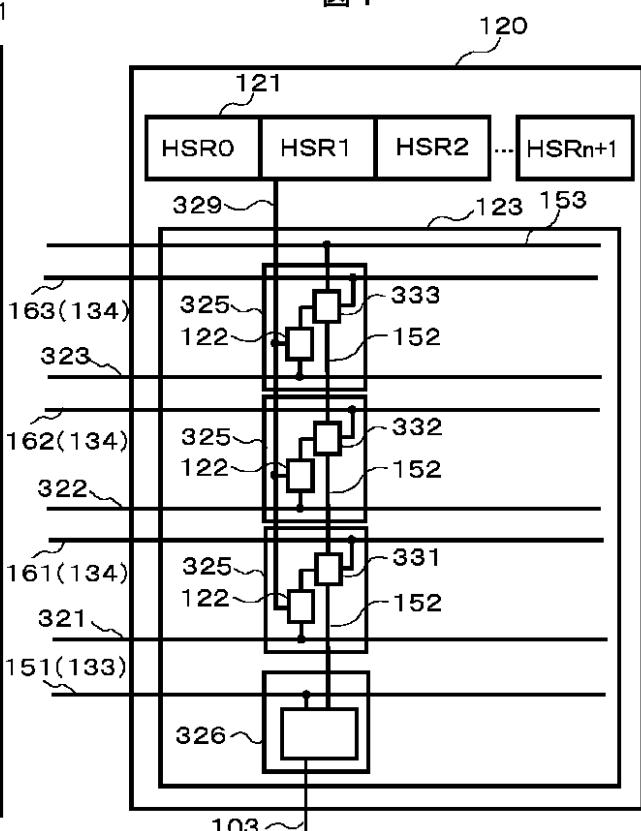

【0028】図3は電圧選択回路123の内部回路の幅と、映像信号線103の間隔との関係を説明するプロック図である。電圧選択回路123には表示データ演算回路325と階調電圧出力回路326とが設けられており、表示データ演算回路325と階調電圧出力回路326を50

6とは、映像信号線103の延長線上に並ぶように設けられている。

【0029】表示制御回路111（図示せず）から水平駆動回路120には表示データ線（321～323）が接続されている。この表示データ線（321～323）は、図1及び図2で説明した表示データをデジタルデータとした場合に、ビット単位に信号線を設けたものであり、図1及び図2の表示データ線132をビット単位に表示したものである。また、表示制御回路111からは制御信号線134が電圧選択回路123に接続されているが、図3では省略している。

【0030】表示データ線（321～323）には順次表示データが出力されており、水平シフトレジスタ121からは表示データを取り込むタイミング信号が output されている。タイミング信号線329が水平シフトレジスタ121から電圧選択回路123に接続されており、このタイミング信号線329によりタイミング信号が電圧選択回路123に伝えられる。HSR1からHSRnは双方向シフトレジスタである。水平シフトレジスタ121は双方向シフトレジスタHSRで構成されている。双方向シフトレジスタHSRからタイミング制御信号線131の信号（シフトクロック）に従いタイミング信号が output する。タイミング信号は映像信号線毎に表示データ信号線（321～323）に出力された表示データを表示データ演算回路325に取り込むタイミングを示している。なお、双方向シフトレジスタHSR0とHSRn+1はダミーの双方向シフトレジスタである。また、図3では液晶パネル100と同一基板上に電圧発生回路112が設けられており、電圧発生回路112から階調電圧線133が階調電圧出力回路326に接続されている。

【0031】表示部110には映像信号線103が略等間隔で複数本（n本）設けられている。この映像信号線103の間隔は、表示部110に設けられた画素電極109の幅と略同じである。すなわち、一定の面積の表示部110内において、設けられる画素数は規格で定められている。そのため、表示部110の大きさと画素数により、画素が設けられる領域の大きさが定まる。映像信号線の間隔も画素を設ける領域の大きさに従い選ばれている。例えば、表示部110の図中横方向（X方向）の画素数をn個とし、表示部110の横幅をWとした場合に画素ピッチはW/nとなり、映像信号線103の間隔は画素ピッチとほぼ同じW/nになる。また、映像信号線103の延長線上に設けられる表示データ演算回路325と階調電圧出力回路326の幅も画素ピッチW/nとほぼ同じになるよう設けられる。

【0032】1本の映像信号線103の延長線上には、当該映像信号線103に階調電圧を出力するために、表示データ演算回路325と階調電圧出力回路326が設けられる。例えば、任意の1本の映像信号線を中心に考

えると、隣り合う映像信号線103の延長線上にも同じく表示データ演算回路325と階調電圧出力回路326が設けられている。そのため、表示データ演算回路325と階調電圧出力回路326の幅を、画素ピッチの幅内に収めないと、隣の表示データ演算回路325または階調電圧出力回路326と重なってしまうという問題が生じる。すなわち、表示部を小さくした場合や、画素数を増加させた場合に、画素ピッチ内に駆動回路を形成するためには、回路の幅も考慮しなくてはいけないという問題が生じる。

【0033】そこで、表示データ演算回路325と階調電圧出力回路326を、画素ピッチの幅内に効率よく収めるために、本実施の形態では、表示データ演算回路325の配置を表示データ線の配置に合わせて表示データ線毎に分割して、映像信号線103の延長線上に並べて設けている。

【0034】図3に示すように、表示データ線(321～323)は表示制御回路111から出力して、表示データ演算回路325に接続している。本実施の形態では8階調の表示データに対応する3ビットの場合を示しており、表示データ線(321～323)は3本である。なお、本実施の形態では説明を簡明にするため、表示データ線数が3本の場合について述べるが、表示データ線数は、表示データに従い任意に選ぶことが可能である。

【0035】表示データ演算回路325は各表示データ線(321～323)毎、分割して設けられており、表示データの各ビット毎の値に対して演算を行い、演算結果を階調電圧出力回路326に伝達する。階調電圧出力回路326は表示データ演算回路325での演算結果をもとに表示データに従った階調電圧を出力する。

【0036】前述したように映像信号線103の間隔は、表示部110に設けられた画素電極109の大きさで制限される。対して隣合う表示データ線の間隔は、表示データ演算回路325が設けられるように、十分に広くとることが可能である。図3に示すように、表示データ演算回路325は映像信号線103の延長線上(図中Y方向)に各表示データ線に対応する構成毎分割して、一列に並んで設けることで、映像信号線103の間隔内に収まることができる。ただし、表示データ線の間隔は無制限に広くとれるわけではなく、なるべく、小さくすることが必要であることを本願発明者は見出した。表示データ演算回路325の幅だけではなく、長さをも短くすることについては後述する。

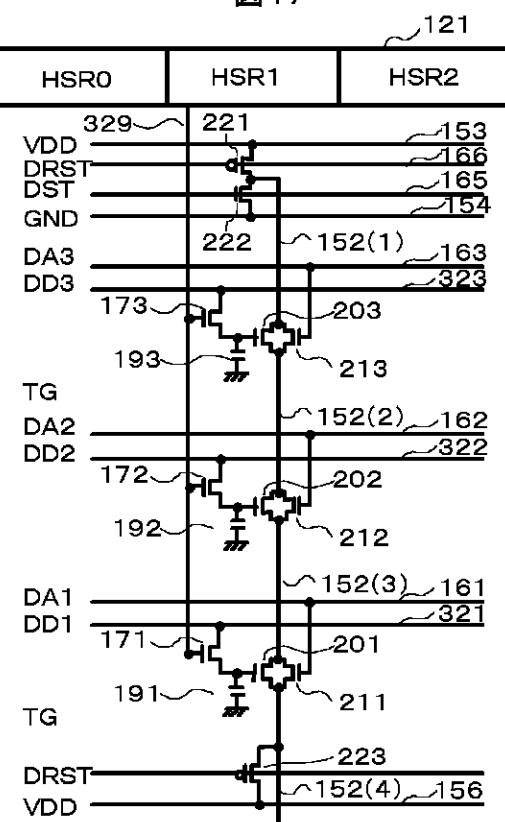

【0037】次に図4を用いて表示データ線毎に分割して設けられる電圧選択回路123について詳細に説明する。図4は、電圧選択回路123の回路構成を示す概略プロック図である。なお、図4では、図面が複雑になることを避けて、1本の映像信号線103について、電圧選択回路123の構成を示している。

【0038】電圧選択回路123には前述したように表

示データ線毎に表示データ演算回路325が設けられている。各表示データ演算回路325には、時間制御信号線(161～163)が接続されている。なお、時間制御線(161～163)は図1～図3において制御信号線134で示した信号線の内のひとつであり、図示していない表示制御装置111から供給されている。同図において、122は表示データ保持回路である。表示データ保持回路122は水平シフトレジスタ121から出力するタイミング信号線329の信号に従って、表示データ線(321～323)の表示データを記録する。

【0039】また、331、332、333は演算伝達回路であり、表示データ保持回路122の出力と、時間制御信号線(161～163)の信号との間で演算を行い、演算結果を演算結果信号線152に出力する。演算伝達回路(331～333)は、演算結果信号線152で直列に接続されている。また、階調電圧出力回路326も演算結果信号線152で演算伝達回路(331～333)と直列に接続されている。階調電圧出力回路326は演算伝達回路(331～333)が伝達する演算結果に従い、電圧バスライン151上の階調電圧を選択して映像信号線103に出力する。なお、電圧バスライン151は図1～図3において階調電圧線133でしめた信号線の内で、時間と共に電圧値が変化するものを示している。また、図4では電圧バスラインを1本の配線で示したが、複数本の配線で構成することも可能である。

【0040】本実施の形態では、演算伝達回路(331～333)と階調電圧出力回路326とが、表示データ線の本数よりも少ない演算結果信号線152で接続されているため、配線領域が省略可能になっている。すなわち、3本の表示データ線(321～323)で伝達されるデータを演算伝達回路(331～333)で演算しその結果を1本の演算結果信号線152で縦方向に伝えており、配線数が少なくなっている。また、演算伝達回路(331～333)を縦に並べて設けることで、映像信号線103に階調電圧を出力する構成の幅を狭くすることが可能になっている。

【0041】次に、階調電圧出力回路326により階調電圧が選択され、映像信号線103に出力される方法について説明する。階調電圧出力回路326には、電圧バスライン151が接続されている。電圧バスライン151の電圧値は、時間に従い変化しており、また、電圧値の変化は一定の周期で繰り返されている。そこで、時間に従い変化する電圧バスライン151上の電圧が希望の電圧値である時に、階調電圧出力回路326により電圧バスライン151と映像信号線103とを電気的に接続し、電圧バスライン151上の電圧が希望の電圧値ではない時に、電圧バスライン151と映像信号線103とを電気的に切断することで、希望の電圧を映像信号線上に階調電圧として出力することができる。

【0042】以下簡単に電圧選択回路123の動作について説明する。まず、表示データ保持回路122に水平シフトレジスタ121が出力するタイミング信号により表示データが保持される。次に、演算伝達回路(331～333)には表示データ保持回路122の値が伝えられる。時間制御信号線(161～163)の時間制御信号の値は時間に従い変化しており、演算伝達回路(331～333)では表示データ保持回路122の値と時間制御信号線(161～163)の時間制御信号の値との間で演算が行われる。演算伝達回路(331～333)の演算結果は階調電圧出力回路326に伝達される。電圧バスライン151の電圧が表示データの示す階調電圧と一致した時に、演算伝達回路(331～333)の演算結果が出力され、階調電圧出力回路326は電圧バスライン151から映像信号線103に階調電圧を出力する。

【0043】次に引き続き図4を用いて、各演算伝達回路(331～333)をスイッチング回路で構成し、定電圧線153の電位を演算結果信号線152に出力して階調電圧出力回路326に伝えることで、階調電圧出力回路326が希望の階調電圧を出力する方法について説明する。

| 演算伝達回路 | ケース1 | ケース2 | ケース3 | ケース4 | ケース5 | ケース6 | ケース7 | ケース8 |

|--------|------|------|------|------|------|------|------|------|

| 333    | —    | —    | —    | —    | SW   | SW   | SW   | SW   |

| 332    | —    | —    | SW   | SW   | —    | —    | SW   | SW   |

| 331    | —    | SW   | —    | SW   | —    | SW   | —    | SW   |

【0048】表1の中で、( - )は演算伝達回路(331～333)が常にONである状態を示しており、また、SWは演算伝達回路(331～333)がスイッチング回路として働く事を示している。演算伝達回路(331～333)はスイッチング回路であるが、演算伝達回路(331～333)が常にONであるように設定することは、スイッチング回路が無く導通状態と同じと考えられる。前述したように、スイッチング回路を直列に接続した場合では、スイッチング回路が全てONと1つでもOFFの2つの状態しか選ぶことができないが、表1に示したように、m個のスイッチング回路の中からどのスイッチング回路を選ぶかで状態を分けると、2<sup>m</sup>個の状態を選ぶことができる。

【0049】そこで、時間制御信号線のデータを時間に従い2<sup>m</sup>個の状態に変化するよう設定すれば、時間制御信号線のデータをもとに、2<sup>m</sup>個に区分された時間のうち1つの区分間に全ての演算伝達回路(331～333)を導通状態とすることができ、定電圧線153の電圧を階調電圧出力回路326に伝えることができる。

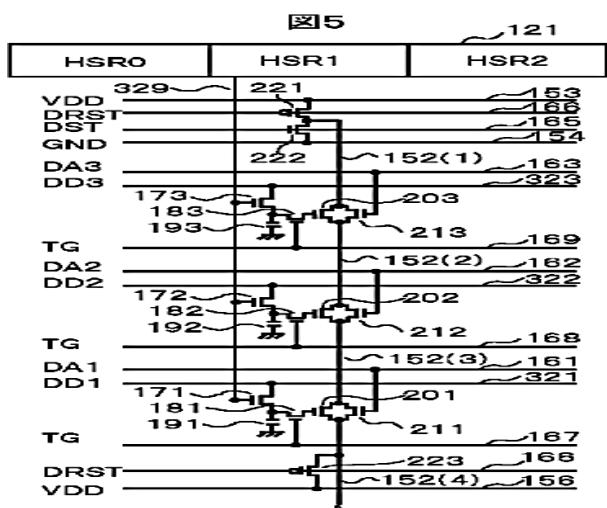

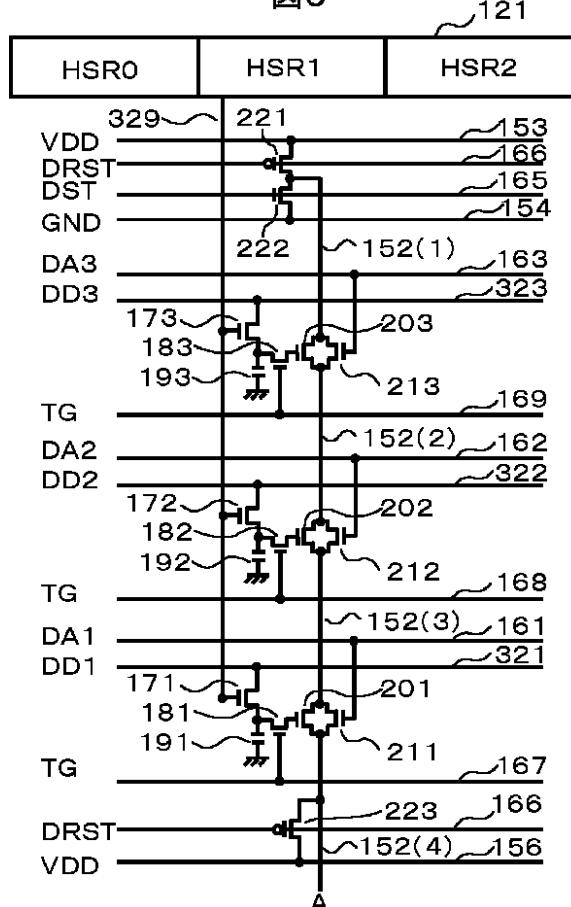

【0050】図5、図6は、本実施の形態において、電圧選択回路123の回路構成を示す回路図である。図5、図6においても、説明を簡略化するために、表示デ

\* 【0044】ここで、演算伝達回路(331～333)は、演算結果信号線152で直列に接続されているので、演算伝達回路(331～333)で表現できる状態は、演算伝達回路(331～333)が全てONで、階調電圧出力回路326に定電圧線153の電圧が伝えられる状態と、演算伝達回路(331～333)の1つでもOFFで、階調電圧出力回路326に定電圧線153の電圧が伝わらない状態の2つの状態だけである。階調電圧出力回路326に伝えられるタイミングが2つでは、多階調の電圧を出力することは困難である。

【0045】そこで、本実施の形態では、表示データ演算回路325を、m個の演算伝達回路(331～333)の中からスイッチング回路として機能させる回路を選択する構成としている。本構成とすることで、m個の演算伝達回路(331～333)が、演算結果信号線152で直列に接続されても、2<sup>m</sup>の状態を表わすことが可能である。

【0046】表1に、演算伝達回路(331～333)の内、どの演算伝達回路をスイッチング回路とするかを選ぶ、選びかたを示す。

【0047】

【表1】

ータが3ビットの場合を示している。なお、図5のAで示す線の端は図6のAで示す端部につながっている。図5において、信号線の両端に符号が記されたものについては、左端には信号線に伝えられる各信号を表わす符号を示し、右端には各信号線を示す符号を記した。

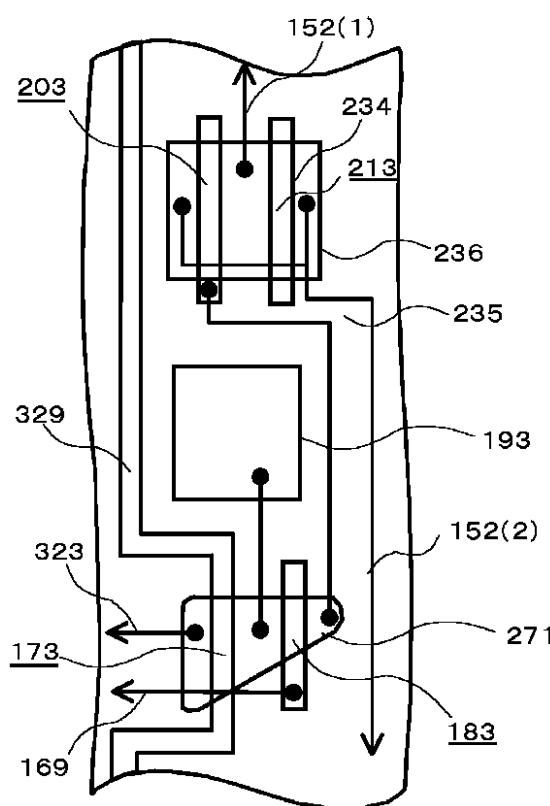

【0051】図5に示すように、図4の演算伝達回路(331～333)は表示データ演算素子(201～203)と時間データ演算素子(211～213)の各2つのn型トランジスタから構成されている。図4の表示データ演算回路325は表示データ演算素子(201～203)と時間データ演算素子(211～213)の他に、データ取り込み素子(171～173)とメモリ容量(191～193)と表示データ転送素子(181～183)から構成されている。表示データ演算回路には表示データ(DD1～DD3)を供給する表示データ線(321～323)と、時間制御信号(DA1～DA3)を供給する時間制御信号線(161～163)と、表示データ転送素子(181～183)を制御する制御信号TGを供給する転送信号線(167～169)が接続されている。制御信号TGによりメモリ容量(191～193)に保持された表示データが表示データ転送素子(181～183)を介して表示データ演算素子(2

01～203)に伝えられる。153、156は定電圧線で電源電圧VDDを供給している。154も定電圧線で電源電圧GNDを供給している。165は演算結果信号線セット信号線で、166は演算結果信号線リセット信号線である。

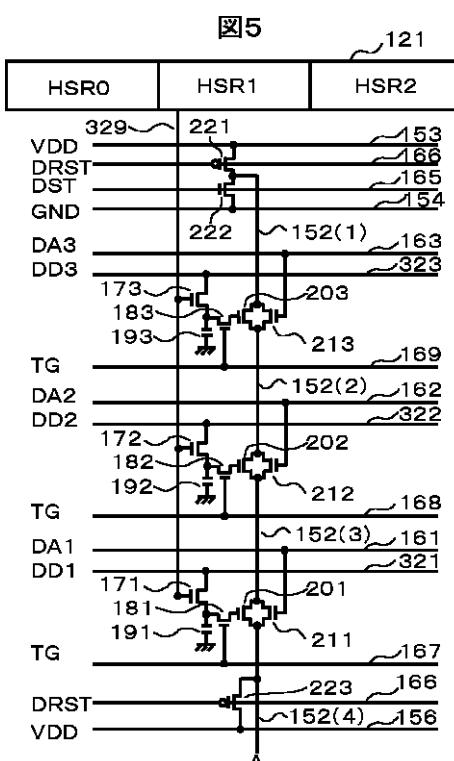

【0052】次に、図6に示す、141はレベルシフト回路で、142はゲート回路で、151は電圧バスラインである。

【0053】図5に示すように、表示データ演算回路を表示データ線毎に分割して設け、表示データ演算回路を同じ導電型のトランジスタで構成することで、液晶表示装置において電圧選択回路123が占める領域の幅だけでなく、長さも短くすることが可能である。

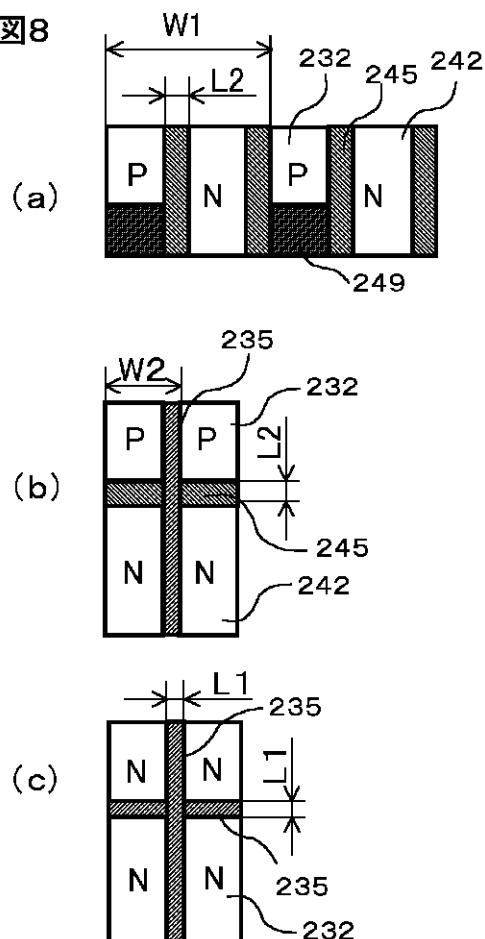

【0054】以下、まず図5の回路について詳述する前に、図7、図8、図9を用いて表示データ演算回路等を形成する素子の形成領域の大きさについて説明する。

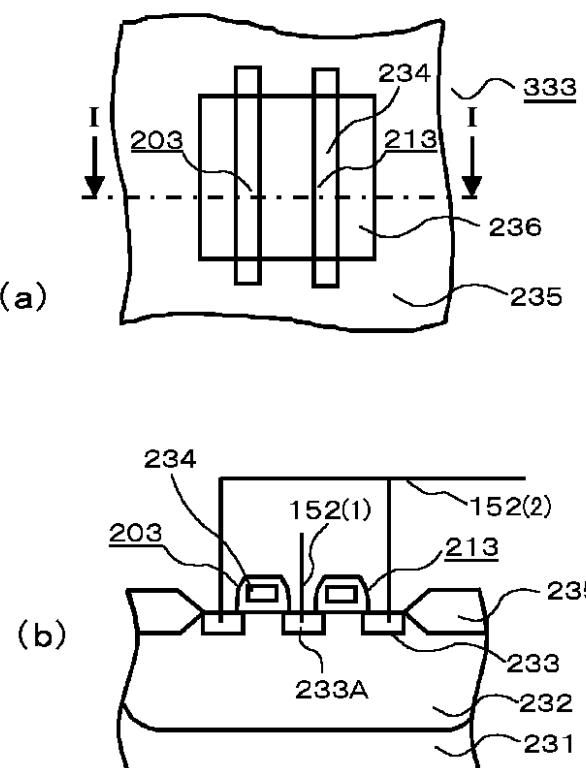

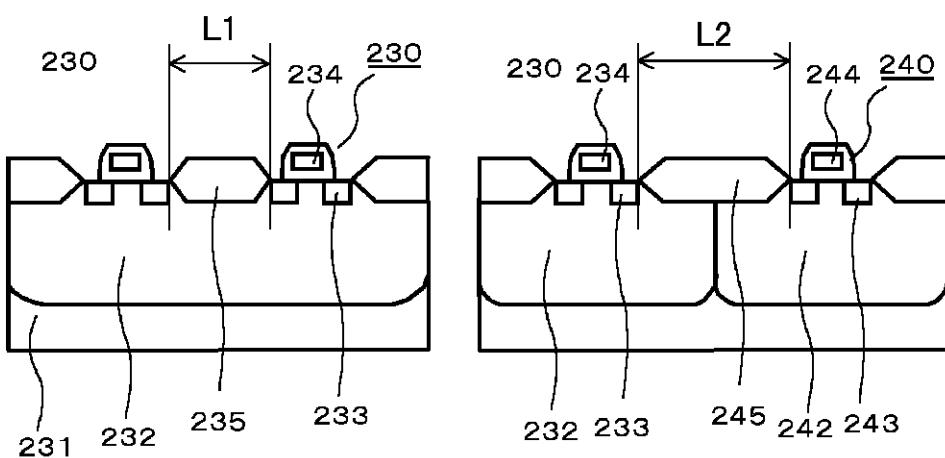

【0055】図7は、2個のトランジスタを隣り合わせて形成した構成を示す断面概略図である。なお、図7は従来例であり、一般的なトランジスタの構成を示している。図7(a)は同じ導電型のトランジスタを並べて形成した場合であり、n型トランジスタ230を2個並べた構成を示している。図7(b)は異なる導電型のトランジスタを並べた場合であり、図中左側がn型トランジスタ230であり、右側がp型トランジスタ240である。

【0056】図7(a)において、232はp型ウエルであり、半導体基板231にイオン打ち込み等の方法により形成される。p型ウエル232にはソース/ドレン領域を形成するn型半導体層233がイオン打ち込み等により形成されている。234はゲート電極であり、ゲート絶縁膜を介してp型ウエル232上に形成される。p型ウエル232はLOCOS(Local Oxidation of Silicon)等の素子分離領域235で分離されている。素子分離領域235は同一基板上に多数個の素子を形成する場合に、各素子を電気的に絶縁して配置するためのものである。各n型トランジスタ230は素子分離領域235で分離された領域に形成されている。L1は素子分離領域235の長さである。

【0057】図7(b)は異なる導電型のトランジスタを並べて形成した場合である。240はp型トランジスタであり、242はn型ウエル、243はp型半導体層、244はゲート電極である。異なる導電型のトランジスタを並べて形成する場合には、同じ導電型のトランジスタを並べて形成する場合に比較して、素子間の電位差が大きくなるためや、p型ウエル232とn型ウエル242が隣接するために、寄生トランジスタが発生しやすい等の理由で、素子分離領域245の長さL2は素子分離領域235の長さL1に対して長くする必要がある。

【0058】このように、同一基板上にトランジスタを並べて形成する場合には、異なる導電型のトランジスタを隣り合わせて並べると、素子分離領域が広くなり、形成領域の面積に無駄が生じる問題がある。

【0059】図8を用いて、トランジスタの並べ方と形成領域の面積について説明する。図8は、一対のトランジスタからなる回路を並べて設ける場合を示している。

図8(a)は異なる導電型のトランジスタを横に並べ回路を構成する場合を示しており、一対のp型トランジスタとn型トランジスタからなるトランジスタで回路を形成している。なお、回路は2個示している。W1は一つの回路を形成するための幅である。図8(a)に示すように、回路の幅W1には素子分離領域245の長さL2が含まれている。また、p型ウエル232の大きさとn型ウエル242の大きさが同じで無い場合には、利用されない領域249が生じてしまう。

【0060】図8(b)は異なる導電型のトランジスタを縦に並べた場合を示している。一対のp型のトランジスタとn型のトランジスタを縦に並べて一つの回路を構成し、同じ構成の回路を横方向に並べた構成を示している。図8(b)では、一つの回路に必要な幅はW2である。幅W2はW1に対して狭くなるため、前述したように、画素ピッチの幅内に回路を形成する場合には有効である。しかしながら、縦方向に並べられたp型ウエルとn型ウエルとの間には素子分離領域245が設けられており、その長さはL2であり、同じ導電型のトランジスタを並べる場合に比較して長くなっている。

【0061】図8(c)に、一対の同じ導電型のトランジスタを縦に並べて回路を構成する場合を示す。図8(c)では素子分離領域235の長さがL1であり、長さL2に比較して短くなっている。長さL1とL2の差は、せいぜい数μm程度であるが、一対のトランジスタで構成される回路が、縦に連続して設けられる場合には、長さの差はその和になるため無視できなくなる。たとえば、図3の表示データ演算回路325に用いる場合では、表示データ数が3ビットで表現されているため、3倍の長さとなる。液晶パネルの表示する階調数が増加し、表示データのビット数が8ビット、16ビットと増加する程、トランジスタの並べ方により無駄な領域を減少させる事が有効になる。

【0062】本実施の形態では、図5に示すように、データ取り込み素子(171～173)、表示データ転送素子(181～183)、表示データ演算素子(201～203)、時間データ演算素子(211～213)を同じ導電型のトランジスタで構成しており、トランジスタを並べて設けるために生じる素子分離領域を更に小さな面積とすることが可能である。なお、図5ではn型トランジスタを用いて説明しているが、n型トランジスタと同様にp型トランジスタを用いて同じ導電型のトランジスタを並べて設ける構成とすることは当然可能である。

る。

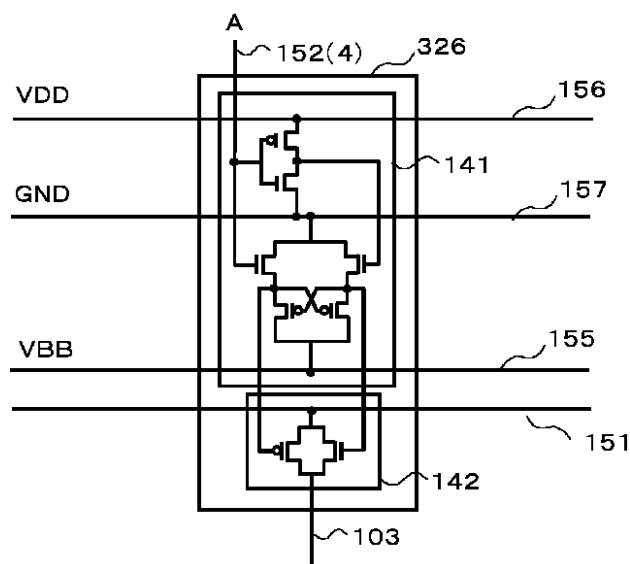

【0063】図9に、図5の表示データ演算素子203と時間データ演算素子213のレイアウトを示す。図9(a)はレイアウトを示す概略平面図であり、図9(b)は図9(a)のI-I線に沿った概略断面図である。

【0064】図9(a)において、素子分離領域235はLOCOS法により形成され、フィールド酸化膜として半導体基板231を覆っている。236は素子分離領域(フィールド酸化膜)235に開けられたアクティブ領域である。アクティブ領域236にはトランジスタで表示データ演算素子203と時間データ演算素子213が形成されている。234はゲート電極である。図9(a)では図を簡明にするため、配線の記載を省略し、図9(b)に接続状態を線で示した。前述した図5に示すように、表示データ演算素子203と時間データ演算素子213には、演算結果信号線152が接続されている。また、図5に示すように、表示データ演算素子(201~203)と時間データ演算素子(211~213)は同一基板上に形成可能なためソース/ドレイン領域の共有化が可能であり、ソース/ドレイン領域が同電位となるように接続される。このため、図9(b)に示すように、表示データ演算素子203と時間データ演算素子213のソース/ドレイン領域233Aは共有するように形成され、他層による配線も不要である。またソース/ドレイン領域233Aを共有することで、表示データ演算素子(201~203)と時間データ演算素子(211~213)の間には、素子分離領域235を設ける必要がない。

【0065】図9に示すように、表示データ演算素子203と時間データ演算素子213は、2トランジスタで演算伝達回路333を構成しているが、同じ導電型のトランジスタで構成することで、素子分離領域235及び配線領域が省略可能であるため、2個のトランジスタよりも小さな占有面積となっている。そのため、表示データ演算回路325をコンパクトな構成とすることができる。また、表示データ演算素子(201~203)と時間データ演算素子(211~213)の間は、他層による配線も省略されており、配線により生じる容量も減少することができ、高速駆動にも適している。

【0066】また、図5、図9に示すように、演算伝達回路(331~333)は、表示データ演算素子(201~203)が1個のトランジスタで構成され、時間データ演算素子(211~213)も1個のトランジスタにより構成されている。演算伝達回路(331~333)は表示データと時間制御信号との間で演算を行うものであるため、表示データ用の素子と時間制御信号用の素子が必要である。そのため、演算伝達回路(331~333)は少なくとも2個の素子が必要である。すなわち、図5に示す演算伝達回路(331~333)は最

小の単位の素子で構成されていることになる。さらに図9に示すように同じ導電型のトランジスタ2個で演算伝達回路(331~333)を構成することで、前述したように演算伝達回路(331~333)の占有面積を最小単位である2個のトランジスタにより形成する場合よりも小さくすることが可能になっている。

【0067】図10に表示データ演算回路325のレイアウトを示す。図10では図を簡明にするため、タイミング信号線329以外の配線の記載を省略し、接続状態を線で示している。図9を用いて説明したように、表示データ演算素子203と時間データ演算素子213は演算伝達回路333を構成するトランジスタである。データ取り込み素子173と表示データ転送素子183はメモリ容量193を構成する電極と同電位のソース/ドレイン領域を共有している。そのため、データ取り込み素子173と表示データ転送素子183も同一基板上に形成することができ、データ取り込み素子173と表示データ転送素子183との間の素子分離領域及び、配線領域を省略することが可能である。

【0068】図10に示すように、タイミング信号線329はデータ取り込み素子173のゲート電極と同じ導電層で形成されている。また、タイミング信号線329は演算伝達回路333とメモリ容量193とに隣接して形成され、データ取り込み素子173ではタイミング信号線329の一部がゲート電極として利用されている。

【0069】データ取り込み素子173と表示データ転送素子183のアクティブ領域271はゲート電極と重なる領域の形状が台形となるように形成されている。この形状により、ゲート電極の下に生じる電荷が移動しやすい方向が生じる。すなわち、トランジスタがオン状態でゲート電極に電圧が印加されているときに、ゲート電極下のアクティブ領域には電荷が生じている。この電荷はオフ状態に変わる時にソース・ドレイン領域のどちらかに流れ込むことになる。図10のようにアクティブ領域と重なるゲート電極端辺の長さに差があると、電荷は重なる端辺の長さが長い方に流れ込み易くなる。

【0070】データ取り込み素子173の場合、メモリ容量193に正極性の信号を取り込もうとしても、メモリ容量193から表示データ信号線323に流れ込む負の電荷は微量である。そのため、トランジスタ(データ取り込み素子173)がオフになったときに、ゲート電極下の電荷がメモリ容量193側に流れ込んでしまうと、メモリ容量193に充分な信号を書き込めないことになる。そのため、アクティブ領域271の形状を図10に示すようにして、電荷が表示データ信号線323へ流れ込み易くしている。なお、表示データ転送素子183も同様な効果を有しており信号が次の回路に伝達し易くなっている。

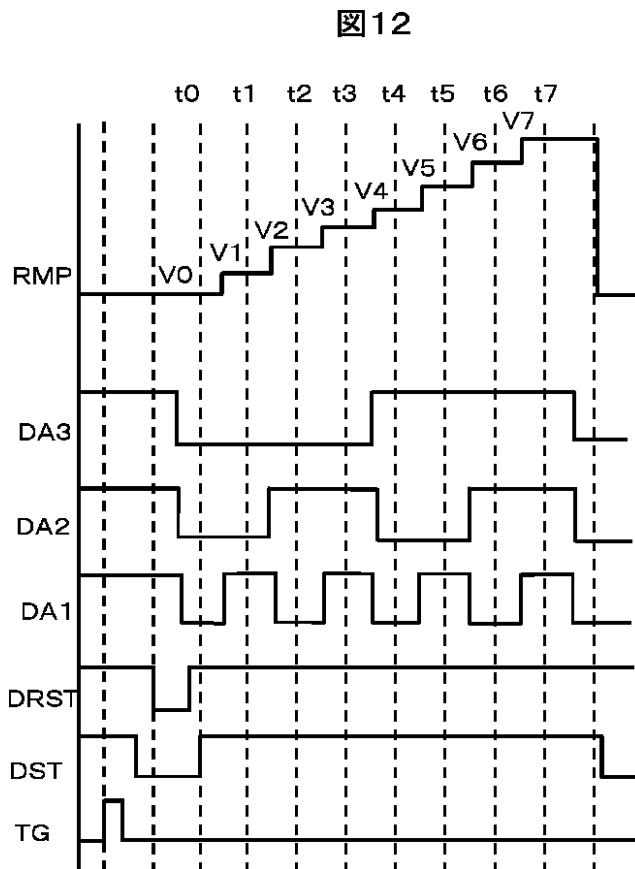

【0071】次に以下、図11、図12に示す各信号のタイミングチャートを用いて、図5、図6に示す回路の

動作について説明する。

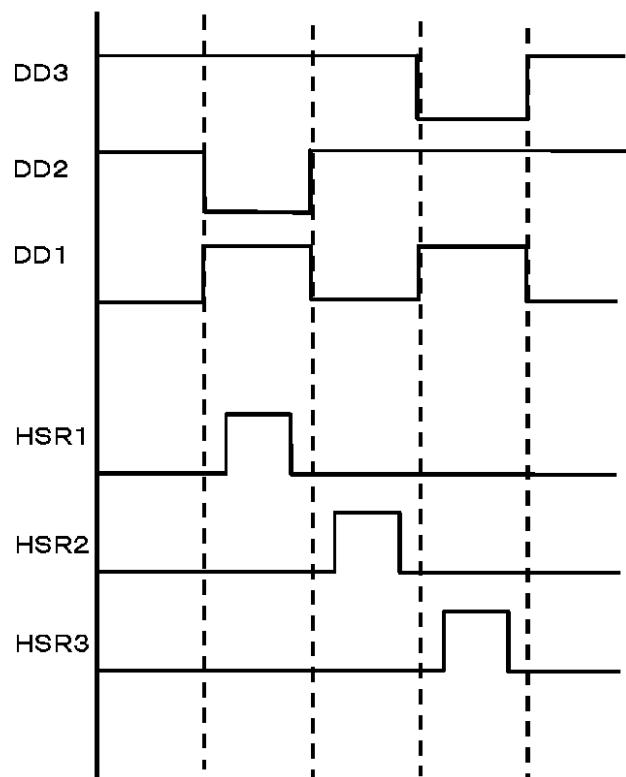

【0072】まず図11に、表示データ線(321～323)に出力される表示データ(DD1～DD3)と、水平シフトレジスタ121から出力されるタイミング信号H S R 1～H S R 3を示す。図5の表示データ線(321～323)には表示データ(DD1～DD3)が出力され、水平シフトレジスタ121からは順番にタイミング信号(H S R 1～H S R 3)が出力する。なお、図11においてはタイミング信号を、H S R 1からH S R 3の3個の信号で示したが、タイミング信号は映像信号線の数に合わせて必要な数が水平シフトレジスタから出力するものとする。

【0073】表示データ(DD1～DD3)はDD1が最下位ビットである3ビットのデータを表わしている。タイミング信号H S R 1が出力している期間の各ビットの値は、表示データDD1の値はハイレベルであり、表示データDD2の値はロウレベルであり、表示データDD3の値はハイレベルとなっている。本実施例の場合では表示データ(DD1～DD3)は、ハイレベルを「1」でロウレベルを「0」で表現することとしており、タイミング信号H S R 1が出力している期間の表示データの値は下位ビットから(1, 0, 1)となる。

【0074】図11において、表示データ(DD1～DD3)が(1, 0, 1)の状態で、タイミング信号線329にタイミング信号H S R 1が出力すると、表示データ転送素子181～183がオン状態になり、表示データ(DD1～DD3)がメモリ容量(191～193)

に取り込まれる。表示データ(DD1～DD3)が(1, 0, 1)の場合、メモリ容量191はハイレベルの電圧が取り込まれ、メモリ容量192はロウレベル、メモリ容量193はハイレベルの電圧が取り込まれる。

【0075】次に、メモリ容量(191～193)に表示データが取り込まれた後の動作について、図12を用いて説明する。図12においてR M Pは階調電圧であり、図6の電圧バスライン151に電圧発生回路112(図示せず)から供給される。階調電圧R M Pは図12に示すように、時間と共に電圧が階段状に変化する。なお、図12では、表示データ(1, 1, 1)の場合に階調電圧V0が画素電極に書き込まれ、表示データ(0, 0, 0)の場合に階調電圧V7が書き込まれるものとする。

【0076】図12において、まず、転送信号T Gがハイレベルになることで、表示データ転送素子(191～193)がオン状態になり、メモリ容量(191～193)に保持された表示データが、表示データ演算素子(201～203)に転送される。

【0077】ここで、表示データに従った電位が、表示データ演算素子(201～203)のゲート電極に伝えられるが、表示データ演算素子(201～203)のゲート電極には、1走査期間前の電位が蓄えられているた

10

20

30

40

50

め、各メモリ容量(191～193)に蓄えられた電位と1走査期間前の電位との容量分割で決まる電位が表示データ演算素子(201～203)のゲート電極の電位となる。なお、表示データ(DD1～DD3)が図11に示すような(1, 0, 1)の場合では、表示データ演算素子201と203はオン状態で、表示データ演算素子202はオフ状態となる。

【0078】次に、時間制御パルス(D A 1～D A 3)がハイレベルの状態で、演算結果信号線セット信号D S Tをロウレベルにして、演算結果信号線セット素子222をオフにする。次に演算結果信号線リセット信号D R S Tをロウレベルにし演算結果信号線リセット素子221、223をオンとすることで、演算結果信号線152は定電圧線153、156に接続されてハイレベルになる。演算結果信号線152がハイレベルであると、図6に示す階調電圧出力回路326のレベルシフト回路141から、ゲート回路142は電圧バスライン151と映像信号線103とを電気的に接続する電圧が供給される。すなわち、演算結果信号線152がハイレベルの間は、映像信号線103には電圧バスライン151から階調電圧が输出されていることになる。

【0079】前述したように、図12においてR M Pは階調電圧であり、時間と共に電圧が階段状に変化する。そのため、演算結果信号線152がハイレベルである期間、映像信号線103には図12に示す階調電圧R M Pが输出されている。

【0080】次に、時間制御パルス(D A 1～D A 3)を時間制御信号線(161～163)に出力開始する。その後、演算結果信号線リセット信号D R S Tをハイレベルにし、さらに演算結果信号線セット信号D S Tをハイレベルにする。演算結果信号線セット信号D S Tがハイレベルになると、演算結果信号線セット素子222がオンとなり演算結果信号線152(1)はG N D線に接続されロウレベルとなる。

【0081】図12においてt0のタイミングでは、全ての時間制御パルス(D A 1～D A 3)がロウレベルであるため、時間データ演算素子(211～213)は全てオフである。そのため、表示データ演算素子の全てがオンでなければ、すなわち表示データが(1, 1, 1)でなければ、演算結果信号線152(4)の電位はV D Dに保たれており、ゲート回路142はオン状態のままである。

【0082】例えば、図11に示した表示データは(1, 0, 1)であるので、t0では表示データ演算回路202がオフとなり、演算結果信号線152(4)の電位はV D Dに保たれることになる。その後時間が経過して、t3では時間制御パルス(D A 1～D A 3)が(0, 1, 0)となるために、時間データ演算素子212がオンとなる。このため、表示データが(1, 0, 1)であるため、表示データ演算回路203と201と

がオン状態であることから、演算結果信号線152(1)～(4)がGND線154に接続されて、演算結果信号線152(4)がロウレベルとなり、ゲート回路142は電圧バスライン151と映像信号線103とを電気的に接続を切断する。そのため、映像信号線103には切断時の電圧バスライン151の電圧V3が保持される。

【0083】これ以降は、演算結果信号線リセット信号DRSTがロウレベルになり、演算結果信号線152をハイレベルにするまで、映像信号線103と電圧バスライン151とが電気的に接続されることはない。

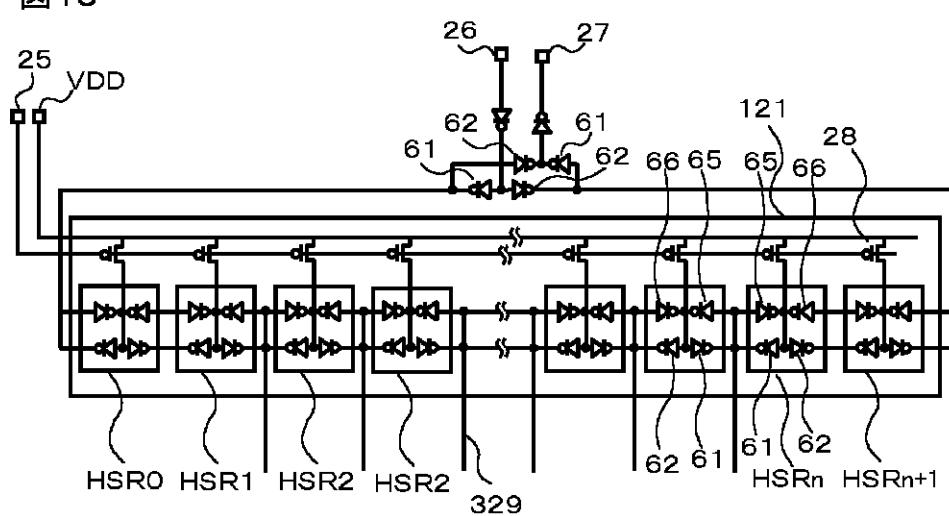

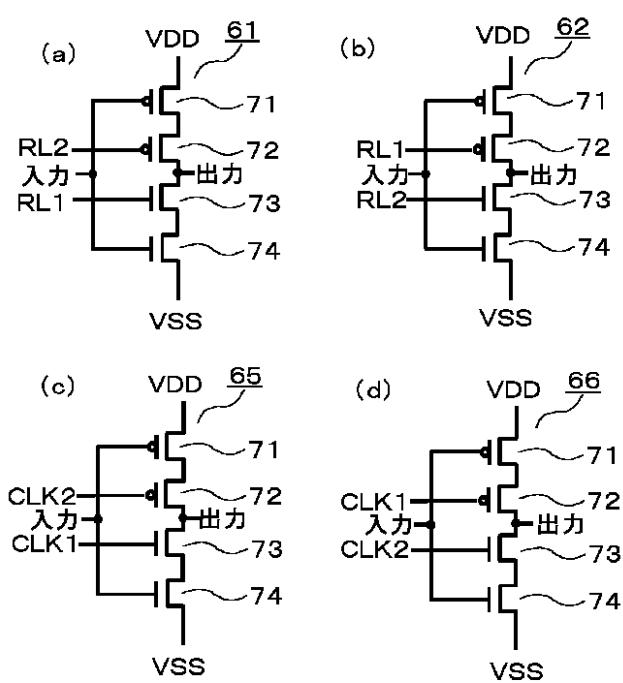

【0084】次に図13を用いて、水平シフトレジスタ121の回路構成を示す。HSRは双方向シフトレジスタであり、左右双方向に信号をシフトすることが可能である。双方向シフトレジスタHSRはクロックドインバータ61、62、65、66で構成されている。

【0085】25は水平走査リセット信号入力端子である。26は水平走査スタート信号入力端子で、クロックドインバータ61により図13の左から右へ走査が行われるスタート信号が水平シフトレジスタ121に供給され、右から左へ走査が行われる場合には、クロックドインバータ62によりスタート信号が水平シフトレジスタ121に供給される。27は水平走査終了信号出力端子である。

【0086】次に、図14(a)(b)を用いて、双方向シフトレジスタHSRに用いられるクロックドインバータ61、62を説明する。RL1は第1水平方向設定線、RL2は第2水平方向設定線である。

【0087】第1水平方向設定線RL1は、図13では左から右に走査する場合Hレベルで、第2水平方向設定線RL2は、図13では右から左に走査する場合Hレベルである。図13では図を見やすくするために結線を省略してあるが、第1水平方向設定線RL1、第2水平方向設定線RL2は共に双方向シフトレジスタHSRを構成するクロックドインバータ61、62に接続されている。

【0088】クロックドインバータ61は図14(a)に示すように、p型トランジスタ71、72とn型トランジスタ73、74からなる。p型トランジスタ72は第2水平方向設定線RL2に接続されており、n型トランジスタ73は第1水平方向設定線RL1に接続されている。そのため第1水平方向設定線RL1がHレベルで第2水平方向設定線RL2がLレベルの場合、クロックドインバータ61はインバータとして働き、第2水平方向設定線RL2がHレベルで第1水平方向設定線RL1がLレベルの場合ハイインピーダンスとなる。

【0089】逆にクロックドインバータ62は図14(b)に示すように、p型トランジスタ72は第1水平方向設定線RL1に接続されており、n型トランジスタ73は第2水平方向設定線RL2に接続されている。そ

のため第2水平方向設定線RL2がHレベルの場合インバータとして働き、第1水平方向設定線RL1がHレベルの場合ハイインピーダンスとなる。

【0090】次にクロックドインバータ65は図14(c)に示す回路構成であり、CLK1がHレベルで、CLK2がLレベルの場合に、入力を反転出力し、CLK1がLレベルで、CLK2がHレベルの場合に、ハイインピーダンスとなる。

【0091】また、クロックドインバータ66は、図14(d)に示す回路構成であり、CLK2がHレベルで、CLK1がLレベルの場合に、入力を反転出力し、CLK2がLレベルで、CLK1がHレベルの場合に、ハイインピーダンスとなる。図13では、クロック信号線の結線を省略してあるが図14のクロックドインバータ65、66にはクロック信号線CLK1、CLK2が接続されている。

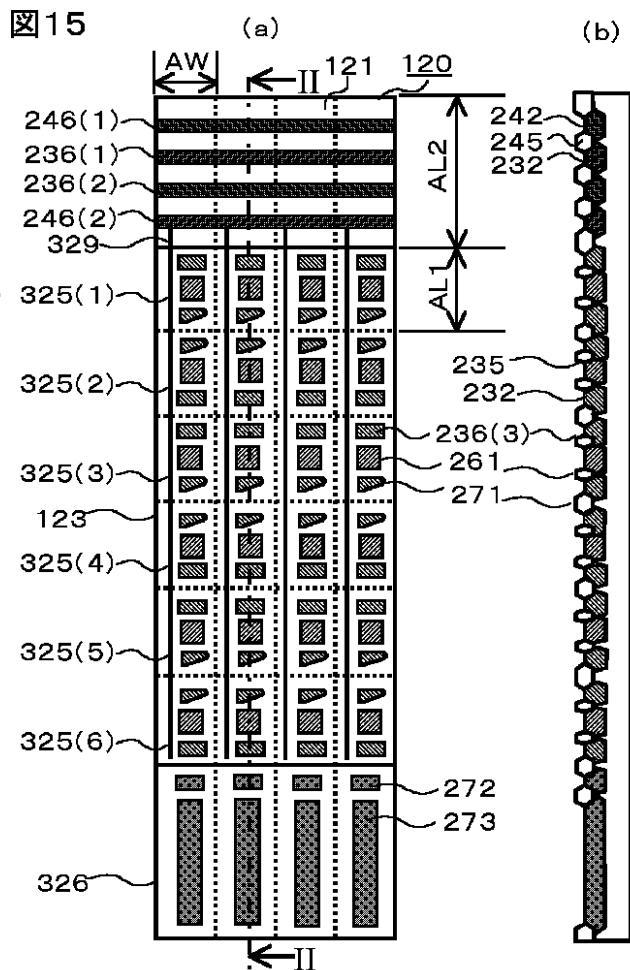

【0092】次に図15を用いて、水平駆動回路120を構成するトランジスタのレイアウトを示す。図15(a)は概略平面図で、図を簡明にするために、映像信号線103(図示せず)4本分の水平駆動回路120を示している。映像信号線毎に設けられる水平駆動回路120の幅AWは、前述したように画素ピッチにより定められている。図15(b)は図15(a)のII-II線での概略断面図である。

【0093】121は水平シフトレジスタである。水平シフトレジスタ121は図14に示すように、n型トランジスタとp型トランジスタが並んで構成されている。246はp型トランジスタのアクティブ領域で、236はn型トランジスタのアクティブ領域である。246(1)には例えば図13、図14に示すクロックドインバータ61とクロックドインバータ62のp型トランジスタが横に並んで、幅AWに収まるように設けられる。同じく236(1)にはクロックドインバータ61とクロックドインバータ62のn型トランジスタが設かれ、246(2)にはクロックドインバータ65とクロックドインバータ66のp型トランジスタが設けられ、236(2)にはクロックドインバータ65とクロックドインバータ66のn型トランジスタが設けられる。

【0094】図15(b)に示す242はn型ウエルで、232はp型ウエル。245はn型ウエルとp型ウエルとの間に設けられる素子分離領域である。AL2は水平シフトレジスタ121の形成領域の長さを示している。

【0095】325は表示データ演算回路である。図15では縦に6個並んで設けられたものを示した。表示データ演算回路325(1)～(6)は各表示データ線毎に設けられるため、表示データのビット数が増加するとその構成も縦に長くなってしまう。そのため、表示データ演算回路325は図5に示すようにn型のトランジスタから構成されている。236は図5に示す表示データ

演算素子（図5中201～203）と時間データ演算素子（図5中211～213）が形成されるアクティブ領域である。表示データ演算素子と時間データ演算素子は図9に示すようにアクティブ領域236に図中横に並ぶように設けられる。図15（b）に示す232はn型ウエルで、235はn型ウエルとn型ウエルとの間に設けられる素子分離領域である。AL1は表示データ演算回路325の形成領域の長さを示している。

【0096】261は図5に示すメモリ容量（191～193）が設けられる領域である。271は図5に示すデータ取り込み素子（図5中171～173）と表示データ転送素子（図5中181～183）が形成されるアクティブ領域である。データ取り込み素子と表示データ転送素子も、表示データ演算素子と時間データ演算素子と同じように、アクティブ領域271に横に並べて設けられる。

【0097】329はタイミング信号線で、水平シフトレジスタ121から出力して各データ取り込み素子に接続されている（ただし図15では、データ取り込み素子への配線は省略した）。タイミング信号線329は表示データ演算回路325にタイミング信号を伝えるため、表示データ演算回路325（1）から325（6）まで、表示データ演算回路に沿って形成される。そのため、表示データのビット数が増加して、表示データ演算回路の数が増加した場合に、タイミング信号線329は縦に長くなる。

【0098】タイミング信号線329が長くなると、配線抵抗値が大きくなる。タイミング信号は高周波数のパルスであるため、配線抵抗値が大きくなると、波形なまりが生じる。タイミング信号に波形なまりが生じると、データ取り込み素子に表示データを取り込むタイミングにずれが生じる。たとえば、表示データ演算回路325（1）では表示データを取り込んでいるのに、表示データ演算回路325（6）では表示データを取り込んでいないといった不具合が生じ、表示品質を低下させる。タイミング信号線329の配線抵抗値及び、容量を考慮すると、表示データ演算回路325の長さAL1はなるべく短い方が望ましい。

【0099】水平シフトレジスタ121の長さAL2と、表示データ演算回路325の長さAL1とを単体で40比べると、AL2の方が長いが、表示データのビット数が増加すると、表示データ演算回路325全体の長さはAL1とビット数の積となるため、表示データ演算回路325の長さAL1を短くすることが、回路全体の長さを短くすることにも、タイミング信号線329の長さを短くすることに有効である。そのため、表示データ演算回路325はn型のトランジスタで構成され、素子分離領域235の長さを短くすることで、表示データ演算回路325の長さAL1を短くしている。

【0100】326は階調電圧出力回路で、272はレ

ベルシフタ回路141のp型トランジスタのアクティブ領域で、273はレベルシフタ回路141のn型トランジスタのアクティブ領域である。アクティブ領域273はトランジスタのオン／オフする速度を速くするために、他のアクティブ領域に比較して大きくなっている。

【0101】以上説明したように、水平駆動回路120を構成するトランジスタのレイアウトについて考慮した場合に、同じ導電型のトランジスタを用いて回路を構成し、画素ピッチの幅に収まるように駆動回路を構成し、駆動回路の長さを短くすることが可能である。また、液晶パネルの表示部の面積が小さくなり、表示階調数や画素数が増えても、表示部に対して小さな面積の駆動回路を実現できる。また、駆動回路の長さを短くすることで、階調数が増加しても表示データを取り込むタイミング信号線の配線抵抗を低く押さえることができ、表示データ取り込みエラーを低減することが可能である。

【0102】次に図16に2系統の水平駆動回路120を設けた場合の構成をしめす。図16では上下に分けて記載したが、片側に2系統の水平駆動回路120を設けることも可能である。また、図17に2系統の水平駆動回路120を設けた場合に可能となる電圧選択回路123の回路構成を示す。図16に示す水平駆動回路120では、1系統の電圧選択回路123に表示データを取り込む間に、他方の系統の電圧選択回路123で階調電圧を選択することができる。そのため、図17に示すように、表示データ転送素子を省略することが可能となる。

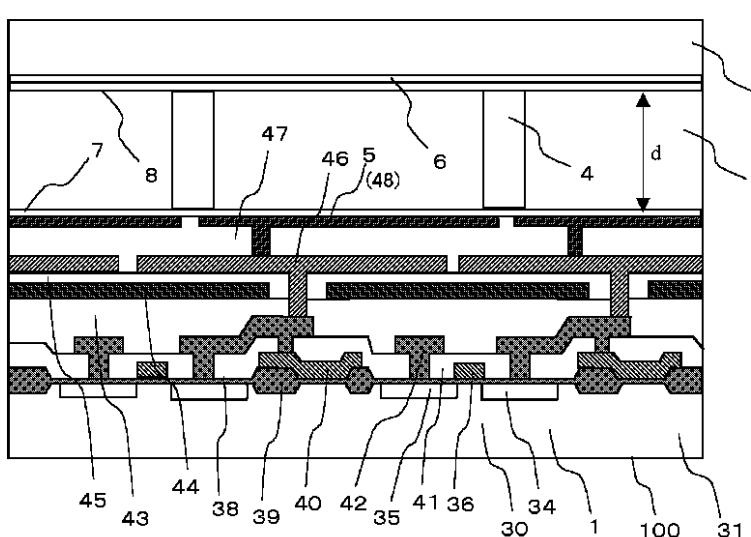

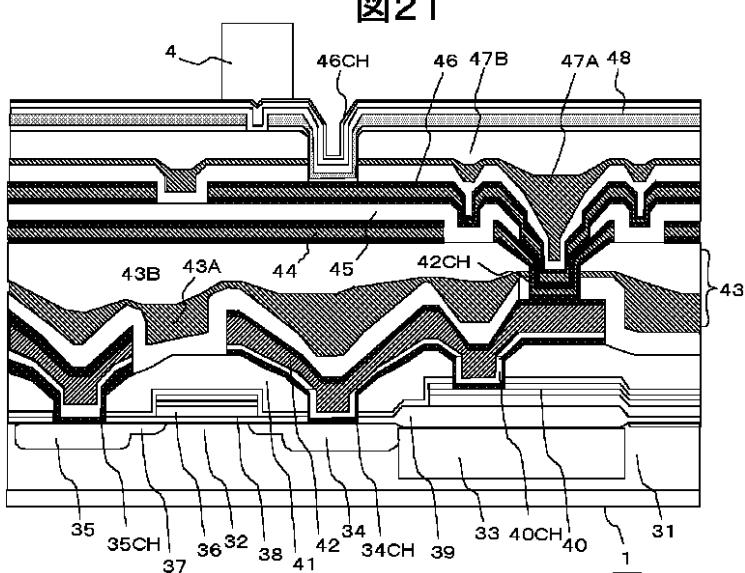

【0103】次に図18を用いて、本発明による液晶表示装置の画素部を説明する。図18は本発明の一実施例を説明する模式断面図である。図18において、100は液晶パネル、1は第1の基板である駆動回路基板、2は第2の基板である透明基板、3は液晶組成物、4はスペーサである、スペーサ4は駆動回路基板1と透明基板2との間に一定の間隔であるセルギャップ（cell gap）dを形成している。このセルギャップdに液晶組成物3が挟持されている。5は反射電極で駆動回路基板1に形成されている。6は対向電極で反射電極5との間で液晶組成物3に電圧を印加する。7、8は配向膜で液晶分子を一定方向に配向させる。30はアクティブ素子で反射電極5に電圧を供給する。

【0104】34はドレイン領域、35はソース領域、36はゲート電極、38は絶縁膜、39はトランジスタ間を電気的に分離するフィールド酸化膜、40は保持電極で絶縁膜38を介し駆動回路基板1との間で容量を形成する。41は第1の層間膜、42は第1の導電膜、43は第2の層間膜、44は第1の遮光膜、45は第3の層間膜、46は第2の遮光膜、47は第4の層間膜、48は反射電極5を形成する第2の導電膜である。

【0105】本実施例の液晶パネルは反射型であり、液晶パネル100に照射された光は、透明基板2側（図中

上側) から入射し、液晶組成物 3 を透過し反射電極 5 で反射し再度液晶組成物 3、透明基板 2 を透過して液晶パネル 100 から出射する。液晶パネルを反射型とし、駆動回路基板 1 の液晶組成物 3 側の面に反射電極 5 を形成した場合、駆動回路基板 1 に不透明なシリコン基板等を用いることが可能である。また、アクティブ素子 30 や配線を反射電極 5 の下に設けることができ、画素となる反射電極 5 を広くし、所謂高開口率を実現することができる利点がある。また、液晶パネル 100 に照射される光による熱を駆動回路基板 1 の裏面から放熱できるといつた利点もある。

【0106】次に液晶パネルに電界制御複屈折モード (ELECTRICALLY CONTROLLED BIREFRINGENCE MODE) を用いた場合の動作を説明する。液晶パネル 100 には偏光素子により直線偏光となった光が入射する。反射電極 5 と対向電極 6 との間に電圧を印加すると液晶組成物 3 の誘電異方性により、液晶分子配列が変化しその結果、液晶パネル 100 中の複屈折率が変化する。電界制御複屈折モードは、この複屈折率の変化を光透過率の変化として利用し像を形成するものである。

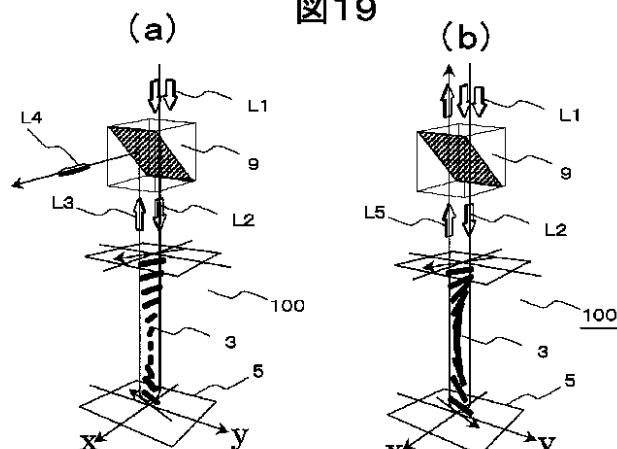

【0107】さらに図 19 を用いて、電界制御複屈折モードの 1 つである単偏光板ツイストネマティクモード (SPTN) について説明する。9 は偏光ビームスプリッタで光源 (図示せず) からの入射光 L1 を 2 つの偏光に分割し、直線偏光となった光 L2 を出射する。図 19 では、液晶パネル 100 に入射させる光に、偏光ビームスプリッタ 9 を透過した光 (P 波) を用いる場合を示しているが、偏光ビームスプリッタ 9 で反射した光 (S 波) を用いることも可能である。液晶組成物 3 は液晶分子長軸が駆動回路基板 1 と透明基板 2 に対して平行に配列し、誘電異方性が正のネマティク液晶を用いる。また、液晶分子は配向膜 7、8 により約 90 度ねじれた状態で配向している。

【0108】まず図 19 (a) に電圧が印加されていない場合を示す。液晶パネル 100 に入射した光は液晶組成物 3 の複屈折性により橢円偏光となり反射電極 5 面では円偏光となる。反射電極 5 で反射した光は再度液晶組成物 3 中を通過し再び橢円偏光となり出射時には直線偏光に戻り、入射光 L2 に対して 90 度位相が回転した光 L3 (S 波) として出射する。出射光 L3 は再び偏光ビームスプリッタ 9 に入射するが、偏光面で反射され出射光 L4 となる。この出射光 L4 をスクリーン等に照射して表示を行う。この場合、電圧を印加していない場合に光が出射する所謂ノーマリー・ホワイト (ノーマリオーブン) と呼ばれる表示方式となる。

【0109】対して図 19 (b) に液晶組成物 3 に電圧が印加されている場合を示す。液晶組成物 3 に電圧が印加されると、液晶分子が電界方向に配列するため、液晶内で複屈折が起こらない。そのため、直線偏光で液晶パネル 100 に入射した光 L2 はそのまま反射電極 5 で反

射され入射光 L2 と同じ偏光方向の光 L5 として出射する。出射光 L5 は偏光ビームスプリッタ 9 を透過し光源に戻る。そのため、スクリーン等に光が照射されないため、黒表示となる。

【0110】単偏光板ツイストネマティクモードでは、液晶の配向方向が基板と平行であるため、一般的な配向方法を用いることができ、プロセス安定性が良い。またノーマリー・ホワイトで使用するため、低電圧側でおこる表示不良に対して裕度を持たせることができる。すなわち、ノーマリー・ホワイト方式では、暗レベル (黒表示) が高電圧を印加した状態で得られる。この高電圧の場合には液晶分子のほとんどが基板面に垂直な電界方向に揃っているので、暗レベルの表示は、低電圧時の初期配向状態にあまり依存しない。さらに、人間の目は、輝度ムラを輝度の相対的な比率として認識し、かつ、輝度に対し対数スケールに近い反応を有する。そのため、人間の目は暗レベルの変動には敏感である。こうした理由から、ノーマリー・ホワイト方式は、初期配向状態による輝度ムラに対して有利な表示方式である。

【0111】上述した電界制御複屈折モードでは高いセルギャップの精度が求められる。すなわち、電界制御複屈折モードでは、光が液晶中を通過する間に生じる異常光と常光との間の位相差を利用して、透過光強度は異常光と常光との間のリタデーション  $n \cdot d$  に依存する。ここで、 $n$  は屈折率異方性で、 $d$  はスペーサ 4 によって形成される透明基板 2 と駆動回路基板 1 との間のセルギャップである。

【0112】このため、本実施例の場合、表示ムラを考慮しセルギャップ精度は、 $\pm 0.05 \mu m$  以下とした。また、反射型では液晶に入射した光は反射電極で反射し再度液晶を通過するため、同じ屈折率異方性  $n$  の液晶を用いる場合、透過型に対してセルギャップ  $d$  は半分になる。一般の透過型液晶表示素子の場合セルギャップ  $d$  は  $5 \sim 6 \mu m$  程度であるのに対し、本実施例では約  $2 \mu m$  である。

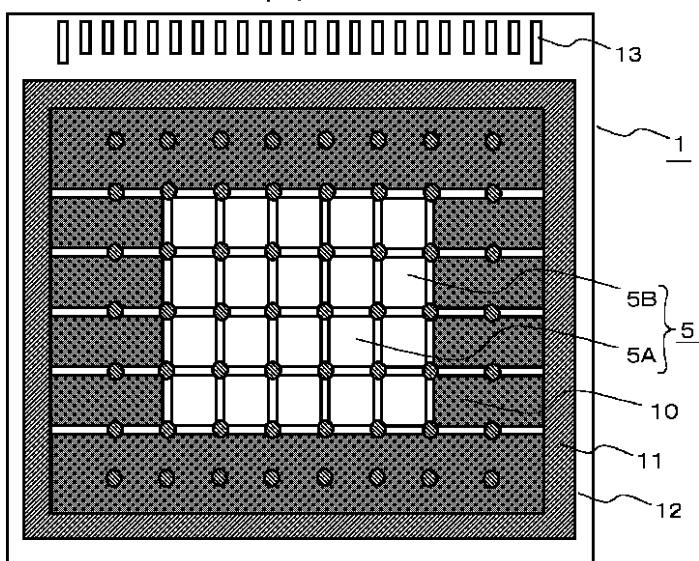

【0113】本実施例では高いセルギャップ精度と、より狭いセルギャップに対応するため、従来からあるビーズ分散法に代わり柱状のスペーサを駆動回路基板 1 上に形成する方法を用いた。

【0114】図 20 に駆動回路基板 1 上に設けられた反射電極 5 とスペーサ 4 との配置を説明する模式平面図を示す。一定の間隔を保つように多数のスペーサ 4 が駆動回路基板全面にマトリックス状に形成されている。反射電極 5 は液晶表示素子が形成する像の最小の画素である。図 20 では簡略化のため、符号 5A、5B で示す縦 4 画素、横 5 画素で示した。

【0115】図 20 では縦 4 画素、横 5 画素の画素が、表示領域を形成している。液晶表示素子で表示する像はこの表示領域に形成される。表示領域の外側にはダミー画素 10 が設けられている。このダミー画素 10 の周辺

にスペーサ4と同じ材料で周辺枠11が設けられている。さらに、周辺枠11の外側にはシール材12が塗布される。13は外部接続端子で液晶パネル100に外部からの信号を供給するのに用いられる。

【0116】スペーサ4と周辺枠11の材料には、樹脂材料を用いた。樹脂材料として例えば、株式会社JSR製の化学增幅型ネガタイプレジスト「BPR-113」(商品名)を用いることができる。反射電極5が形成された駆動回路基板1上にスピンドルコート法等でレジスト材を塗布し、マスクを用いてレジストをスペーサ4と周辺枠11のパターンに露光する。その後除去剤を用いレジストを現像してスペーサ4と周辺枠11とを形成する。

【0117】スペーサ4と周辺枠11とをレジスト材等を原料として形成すると、塗布する材料の膜厚でスペーサ4と周辺枠11の高さを制御でき、高い精度でスペーサ4と周辺枠11を形成することができる。また、スペーサ4の位置はマスクパターンで決めることができ、希望する位置に正確にスペーサ4を設けることができる。液晶プロジェクタでは画素上にスペーサ4が存在すると、拡大投映された像にスペーサによる影が見えてしまう問題がある。スペーサ4をマスクパターンによる露光、現像で形成することで、映像表示した際に、問題とならな位置にスペーサ4を設けることができる。

【0118】また、スペーサ4と同時に周辺枠11を形成しているので、液晶組成物3を駆動回路基板1と透明基板2との間に封入する方法として、液晶組成物3を駆動回路基板1に滴下しその後透明基板2を駆動回路基板1に貼り合せる方法を用いることができる。

【0119】液晶組成物3を駆動回路基板1と透明基板2の間に配置し、液晶パネル100を組立てた後は、周辺枠11により囲まれた領域内に液晶組成物3が保持される。また、周辺枠11の外側にはシール材12が塗布され、液晶組成物3を液晶パネル100内に封入する。前述したように、周辺枠11はマスクパターンを用いて形成されるので、高い位置精度で駆動回路基板1上に形成することができる。そのため、液晶組成物3の境界を高い精度で定めることができる。また、周辺枠11はシール材12の形成領域の境界も高い精度で定めることができる。

【0120】シール材12は駆動回路基板1と透明基板2とを固定する役目と、液晶組成物3にとって有害な物質が進入することを阻止する役目がある。流動性があるシール材12を塗布した場合に、周辺枠11はシール材12のストップとなる。シール材12のストップとして、周辺枠11を設けることで、液晶組成物3の境界やシール材12の境界での設計裕度を狭くすることができ、液晶パネル100の端辺から表示領域までの間を狭く(挿縫縁化)することができる。

【0121】周辺枠11と表示領域との間にはダミー画素10が設けられている。ダミー画素10は最外部の画

素5Bと内部の画素5Aとの表示品質を均一にするためのものである。内部の画素5Aには隣合う画素が存在するため、隣合う画素との間で不要な電界が生じ、隣合う画素が無い場合に比較して表示品質が低下している。対して最外部の画素5Bで、ダミー画素10が無い場合には、表示品質を低下する不要な電界が生じていないので、表示品質が内部の画素5Bに比較して良くなっている。一部の画素に表示品質の差が生じると、それが表示ムラとなる。そのため、ダミー画素10を設けて画素5A、5Bと同じように信号を供給し最外部の画素5Bと内部の画素5Aとの表示品質を同等にしている。

【0122】さらに、表示領域を囲むように周辺枠11が形成されていることから、駆動回路基板1をラビング処理する際に、周辺枠11により周辺枠11の近傍がうまくラビングできない問題がある。液晶組成物3を一定の方向に配向するため、配向膜を形成しラビング処理が行われる。本実施例の場合、駆動回路基板1にスペーサ4、周辺枠11が形成された後に、配向膜7が塗布される。その後、液晶組成物3が一定方向に配向するよう、配向膜7を布等を用いて擦ることでラビング処理が行われる。

【0123】ラビング処理において、周辺枠11が駆動回路基板1より突出しているため、周辺枠11の近傍の配向膜7は、周辺枠11による段差により充分に擦られない。そのため、周辺枠11の近傍には液晶組成物3の配向が不均一な部分が生じやすい。液晶組成物3の配向不良による表示ムラを目立たなくするため、周辺枠11の内側数画素をダミー画素10とすることで、表示に寄与しない画素としている。

【0124】ところが、ダミー画素10を設け、画素5A、5Bと同じように信号を供給すると、ダミー画素10と透明基板2との間には液晶組成物3が存在するため、ダミー画素10による表示も観察されてしまうという問題が生じる。ノーマリホワイトで使用する場合、液晶組成物3に電圧を印加しないと、ダミー画素10が白く表示される。そのため、表示領域の境が明確でなくなり、表示品質をそこなう。ダミー画素10を遮光することも考えられるが、画素と画素の間隔は数μmのため、表示領域の境に精度良く遮光枠を形成することは困難である。そこで、ダミー画素10には黒表示となるような電圧を供給し、表示領域を囲む黒枠として観察されるようにした。

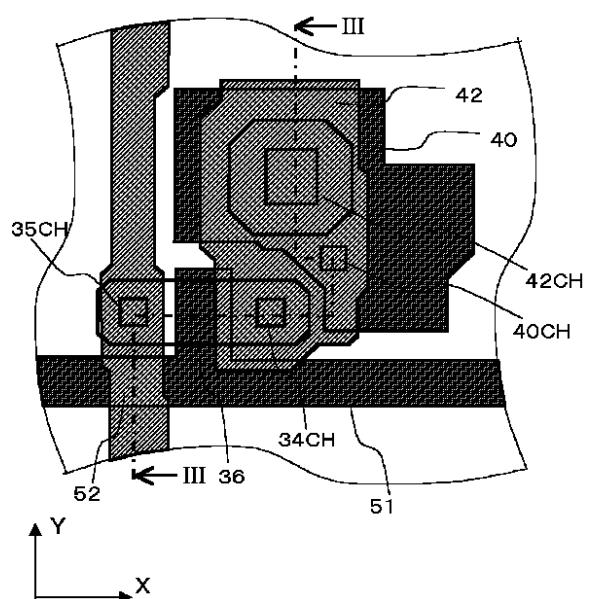

【0125】次に、図21、図22を用いて駆動回路基板1上に設けられるアクティブ素子30とその周辺の構成を説明する。図21、図22において図18と同じ符号は同じ構成を示す。図21はアクティブ素子30周辺を示す概略平面図である。図21は図22のIII-III線における断面図であるが、図21と図22との各構成間の距離は一致していない。また図22は走査信号線51とゲート電極36、映像信号線52とドレイン領

域 35、ソース領域 34、保持電極 40、と第 1 の導電層 42 と、コンタクトホール 35CH、34CH、40CH、42CH の位置関係を示すもので、その他の構成は省略した。

【0126】図 21において、31は駆動回路基板であるシリコン基板、32は駆動回路基板 31にイオン打ち込みで形成した半導体領域（n型ウエル）、33はチャネルストッパー、34はn型ウエル 32にイオン打ち込みで導電化し形成したソース領域、35はn型ウエル 32にイオン打ち込みで形成したドレイン領域である。なお、ソース、ドレインは本来その間のバイアス極性によって決まるもので、液晶表示素子ではその極性は動作中反転する。そのため、ドレイン領域とソース領域は動作中入れ替わる。しかし、以下の説明では、便宜上一方をドレイン領域、他方をソース領域と固定して表現する。

【0127】36はゲート電極、37はゲート電極端部の電界強度を緩和するオフセット領域、38は絶縁膜、39はトランジスタ間を電気的に分離するフィールド酸化膜、40は保持電極で絶縁膜 38を介しシリコン基板 31との間で容量を形成する。ゲート電極 36と保持電極 40は、絶縁膜 38にアクティブ素子 30のしきい値を低くするための導電層と低抵抗の導電層とを積層した2層膜からなっている。2層膜としては例えばポリシリコンとタンゲステンシリサイドの膜を用いることができる。41は第1の層間膜、42は第1の導電膜である。第1の導電膜 42は接触不良を防止するバリアメタルと低抵抗の導電膜の多層膜からなっている。第1の導電膜として、例えばチタンタンゲステンとアルミの多層金属膜をスパッタで形成して用いることができる。

【0128】図 22において 51は走査信号線である。走査信号線 51は、図 22 中、X 方向に延在し Y 方向に並設されていて、アクティブ素子 30をオン・オフする走査信号が供給される。走査信号線 51はゲート電極と同じ 2 層膜からなっており、例えばポリシリコンとタンゲステンシリサイドを積層した 2 層膜を用いることができる。映像信号線 52は Y 方向に延在し X 方向に並設されていて、反射電極 5 に書き込まれる映像信号が供給される。映像信号線 52は第1の導電膜 42と同じ多層金属膜からなっており、例えばチタンタンゲステンとアルミの多層金属膜を用いることができる。

【0129】映像信号は絶縁膜 38と第1の層間膜 41に空けられたコンタクトホール 35CH を通り第1の導電膜 42によりドレイン領域 35に伝わる。走査信号線 51に走査信号が供給されると、アクティブ素子 30はオンになり、映像信号は半導体領域（n型ウエル）32からソース領域 34に伝わり、コンタクトホール 34CH を通り第1の導電膜 42に伝わる。第1の導電膜 42に伝わった映像信号は、コンタクトホール 40CH を通り保持電極 40に伝わる。また、図 21 に示すようにコンタクトホール 42CH を通り反射電極 5 へと伝わって

いく。コンタクトホール 42CH はフィールド酸化膜 39の上に形成されている。フィールド酸化膜 39は膜厚が厚いため、フィールド酸化膜の上は他の構成に比較して高い位置となっている。コンタクトホール 42CH はフィールド酸化膜 39 上に設けられることで、上層の導電膜により近い位置とすることができ、コンタクトホールの接続部の長さを短くしている。

【0130】第2の層間膜 43は、第1の導電膜 42と第2の導電膜 44とを絶縁している。第2の層間膜 43 10は、各構成物により生じている凹凸を埋める平坦化膜 43A とその上を覆う絶縁膜 43B との 2 層で形成されている。平坦化膜 43A は SOG (spin on glass) を塗布して形成している。絶縁膜 43B は TEOS 膜であり、反応ガスとして TEOS (Tetraethylorthosilicate) を用い SiO<sub>2</sub> 膜を CVD により形成したものである。

【0131】第2の層間膜 43の形成後、CMP (ケミカル・メカニカル・ポリシング) により第2の層間膜 43 20は研磨される。第2の層間膜 43 は CMP により研磨することで平坦化する。平坦化された第2の層間膜の上に第1の遮光膜 44 が形成される。第1の遮光膜 44 は第1の導電膜 42 と同じタンゲステンとアルミの多層金属膜で形成している。

【0132】第1の遮光膜 44 は駆動回路基板 1 の略全面を被っており、開口は図 21 に示すコンタクトホール 42CH の部分だけある。第1の遮光膜 44の上に第3の層間膜 45 が TEOS 膜で形成されている。さらに第3の層間膜 45 の上に第2の遮光膜 46 が形成されている。第2の遮光膜 46 は第1の導電膜 42 と同じタンゲステンとアルミの多層金属膜で形成している。第2の遮光膜 46 はコンタクトホール 42CH で第1の導電膜 42 と接続されている。コンタクトホール 42CH では、接続をとるために第1の遮光膜 44 を形成する金属膜と第2の遮光膜 46 を形成する金属膜とが積層されている。

【0133】第1の遮光膜 44 と第2の遮光膜 46 を導電膜で形成し、間に第3の層間膜 45 を絶縁膜（誘電膜）で形成し、第1の遮光膜 44 に電圧を供給すると、第1の遮光膜 44 と第2の遮光膜 46 とで保持容量を形成することができる。また、駆動電圧に対する第3の層間膜 45 の耐圧と、膜厚を薄くして容量を大きくすることを考慮すると、第3の層間膜 45 は 150 nm から 450 nm が好ましく、より好ましくは、約 300 nm である。

【0134】次に、図 23 に駆動回路基板 1 に透明基板 2 を重ね合わせた図を示す。駆動回路基板 1 の周辺部には、周辺枠 11 が形成されており、液晶組成物 3 は周辺枠 11 と駆動回路基板 1 と透明基板 2 とに囲まれた中に保持される。重ね合わせられた、駆動回路基板 1 と透明基板 2 との間で周辺枠 11 の外側には、シール材 12 が塗布

される。シール材12により駆動回路基板1と透明基板2とが接着固定され液晶パネル100が形成される。

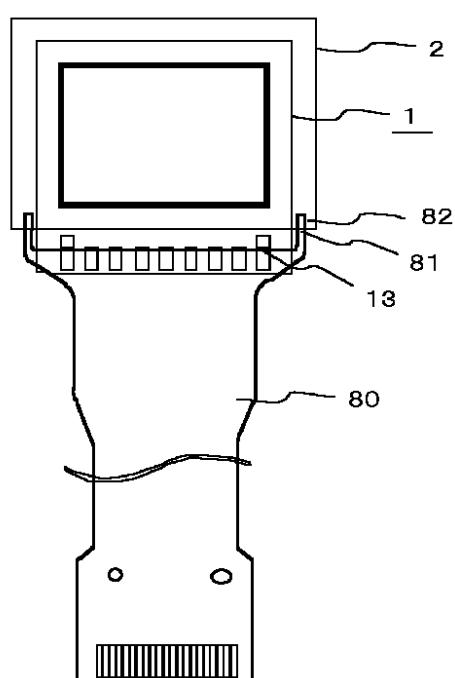

【0135】次に図24に示すように、液晶パネル100に外部からの信号を供給するフレキシブルプリント配線板80が外部接続端子13に接続される。

【0136】フレキシブルプリント配線板80の両外側の端子は他の端子に比較して長く形成され、透明基板2に形成された対向電極5に接続され、対向電極用端子81を形成している。すなわち、フレキシブルプリント配線板80は、駆動回路基板1と透明基板2の両方に接続されている。

【0137】従来の対向電極5への配線は駆動回路基板1に設けられた外部接続端子にフレキシブルプリント配線板が接続され、駆動回路基板1を経由して対向電極5に接続されるものであった。本実施例の透明基板2にはフレキシブルプリント配線板80との接続部82がもうけられ、フレキシブルプリント配線板80と対向電極5とが直接接続される。すなわち、液晶パネル100は透明基板2と駆動回路基板1とが重ね合わされて形成されるが、透明基板2の一部は駆動回路基板1より外側に出で接続部82を形成しており、この透明基板2の外側に出た部分でフレキシブルプリント配線板80と接続されている。

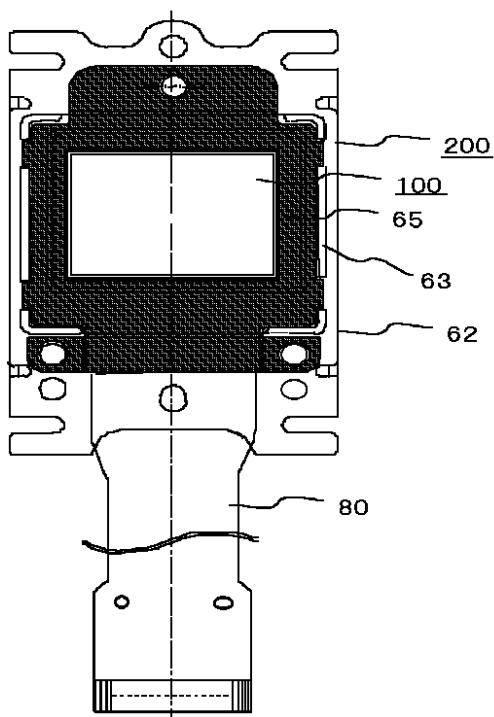

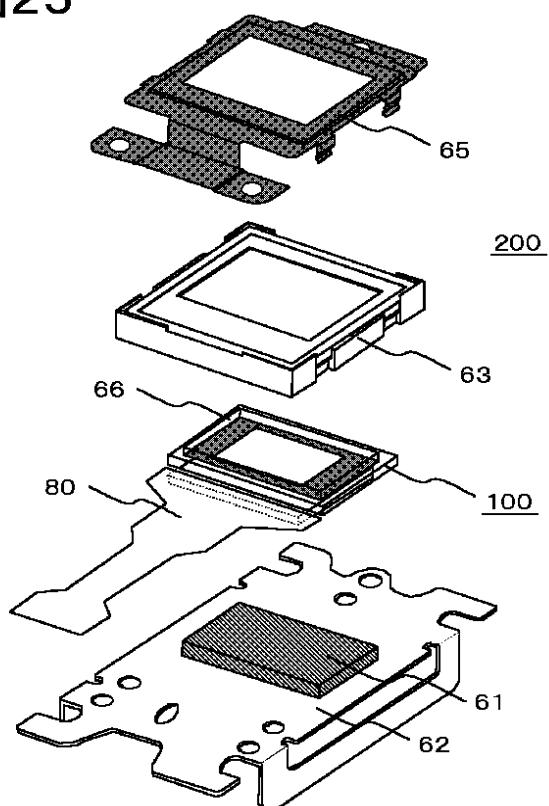

【0138】図25、図26に液晶表示装置200の構成を示す。図25は液晶表示装置200を構成する各構成物の分解組立て図である。また図26は液晶表示装置200の平面図である。

【0139】図25に示すように、フレキシブルプリント配線板80が接続された液晶パネル100は、クッション材61を間に挟んで、放熱板62に配置される。クッション材61は高熱伝導性であり、放熱板62と液晶パネル100との隙間を埋めて、液晶パネル100の熱が放熱板62に伝わり易くする役目を持つ。63はモールドで、放熱板62に接着固定されている。

【0140】また図26に示すように、フレキシブルプリント配線板80はモールド63と放熱板62との間を通りモールド63の外側に取り出されている。65は遮光板で、光源からの光が液晶表示装置200を構成する他の部材にあたることを防いでいる。66は遮光枠で液晶表示装置200の表示領域の外枠を表示する。

【0141】以上、本発明者によってなされた発明を、前記発明の実施の形態に基づき具体的に説明したが、本発明は、前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

【0142】

【発明の効果】本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記のとおりである。

【0143】本発明によれば、液晶パネル内に水平駆動

回路を組み込む場合に、水平駆動回路が占有する面積を少なくすることが可能となる。また、本発明によれば、液晶表示素子を小型化することが可能となる。

【図面の簡単な説明】

【図1】本発明の実施の形態の液晶表示装置の全体の概略構成を示すブロック図である。

【図2】本発明の実施の形態の液晶表示装置の液晶パネルの等価回路を示す回路図である。

【図3】本発明の実施の形態の液晶表示装置の水平駆動回路と表示部の概略構成を示すブロック図である。

【図4】本発明の実施の形態の液晶表示装置の水平駆動回路の概略構成を示すブロック図である。

【図5】本発明の実施の形態の液晶表示装置の電圧選択回路の概略構成を示す回路図である。

【図6】本発明の実施の形態の液晶表示装置の電圧選択回路の概略構成を示す回路図である。

【図7】従来のトランジスタを2個並べて設ける場合の構成を示す概略断面図である。

【図8】トランジスタの並べ方と形成領域の面積を説明する概略平面図である。

【図9】本発明の実施の形態の液晶表示装置に用いられる素子のレイアウトを示す概略平面図である。

【図10】本発明の実施の形態の液晶表示装置に用いられる演算回路のレイアウトを示す概略平面図である。

【図11】本発明の実施の形態の液晶表示装置の動作を説明するタイミング波形図である。

【図12】本発明の実施の形態の液晶表示装置の動作を説明するタイミング波形図である。

【図13】本発明の実施の形態の液晶表示装置に用いられるシフトレジスタを示す概略回路図である。

【図14】本発明の実施の形態の液晶表示装置に用いられるクロックドインバータを示す概略回路図である。

【図15】本発明の実施の形態の液晶表示装置に用いられる水平駆動回路を構成するトランジスタのレイアウトを示す概略平面図である。

【図16】本発明の実施の形態の液晶表示装置に用いられた水平駆動回路を構成を示す概略ブロック図である。

【図17】本発明の実施の形態の液晶表示装置に用いられた水平駆動回路を構成を示す概略回路図である。

【図18】本発明による液晶表示装置の画素部の構成を示す概略断面図である。

【図19】本発明による液晶表示装置の一実施の形態を説明する概略図である。

【図20】本発明による液晶表示装置の一実施の形態を説明する表示領域の概略平面図である。

【図21】本発明による液晶表示装置の一実施の形態を説明するアクティブ素子周辺の概略断面図である。

【図22】本発明による液晶表示装置の一実施の形態を

説明するアクティブ素子周辺の概略平面図である。

【図23】本発明による液晶表示装置の模式組立て図である。

【図24】本発明による液晶表示装置の模式組立て図である。

【図25】本発明による液晶表示装置の模式組立て図である。

【図26】本発明による液晶表示装置の模式組立て図である。

#### 【符号の説明】

10...ダミー画素、11...周辺枠、12...シール材、13...外部接続端子、25...水平走査リセット信号入力端子、26...水平走査スタート信号入力端子、27...水平走査終了信号出力端子、28...リセット用トランジスタ、30...アクティブ素子、34...ドレイン領域、35...ソース領域、36...ゲート領域、38...絶縁膜、39...フィールド酸化膜、61~62...クロックドインバータ、65~66...クロックドインバータ、100...液晶パネル、101...画素部、102...走査信号線、103...映像信号線、104...スイッチング素子、107...対向電極、108...液晶容量、109...画素電極、110...表示部、111...表示制御装置、112...電圧発生回路、120...水平駆動回路、121...水平シフトレジスタ、122...表示データ保持回路、123...電圧選択回路、130...垂直駆動回路、131...タイミング制御信\*

\*号線、132...表示データ線、133...階調電圧線、134...時間制御信号線、141...レベルシフタ回路、142...ゲート回路、151...電圧バスライン、152...演算結果信号線、153~157...定電圧線、161~163...時間制御信号線、165...演算結果信号線セット信号線、166...演算結果信号線リセット信号線、167~169...転送信号線、171~173...データ取り込み素子、181~183...表示データ転送素子、191~193...メモリ容量、201~203...表示データ演算素子、211~213...時間データ演算素子、221...演算結果信号線リセット素子、222...演算結果信号線セット素子、230...n型トランジスタ、231...半導体基板、232...p型ウエル、233...n型半導体層、234...ゲート電極、235...素子分離領域、236...アクティブ領域、240...p型トランジスタ、242...n型ウエル、243...p型半導体層、244...ゲート電極、245...素子分離領域、246...アクティブ領域、249...利用されない領域、260...コンデンサ、261...コンデンサアクティブ領域、271~273...アクティブ領域、321~323...表示データ線、325...表示データ演算回路、326...階調電圧出力回路、328...表示データ保持回路、329...タイミング信号線、331~333...演算伝達回路。

【図6】

図6

【図9】

図9

【図1】

図1

【図2】

図2

【図7】

図7

(a)

(b)

【図3】

図3

【図4】

図4

【図13】

図13

【図5】

図5

【図8】

図8

【図18】

図18

【図10】

図10

【図11】

図11

【図14】

図14

【図19】

図19

【図12】

【図15】

【図20】

図20

図23

【図16】

図16

【図17】

図17

【図21】

図21

【図24】

図24

【図22】

図22

【図26】

図26

【図25】

図25

## フロントページの続き

(51) Int.Cl.<sup>7</sup> 識別記号

G 09 G 3/20 6 8 0

F I テ-マコ-ド<sup>®</sup> (参考)

G 09 G 3/20 6 8 0 G

(72)発明者 竹本 一八男

千葉県茂原市早野3300番地 株式会社日立

製作所ディスプレイグループ内

(72)発明者 宮沢 敏夫

千葉県茂原市早野3300番地 株式会社日立

製作所ディスプレイグループ内

(72)発明者 松本 克巳

千葉県茂原市早野3681番地 日立デバイス

エンジニアリング株式会社内

F ターム(参考) 2H093 NA16 NC03 NC16 NC22 NC24

NC34 NC50 ND06 ND22 ND34

ND42 NE01 NE03

5C006 AA02 AC21 BB16 BC11 BC16

BC20 BF03 BF49 BF50 FA41

5C080 AA10 BB05 DD22 GG02 JJ02

JJ03 JJ04 JJ06 KK02

|                |                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2002258810A</a>                                                                                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2002-09-11 |

| 申请号            | JP2001059394                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2001-03-05 |

| [标]申请(专利权)人(译) | 株式会社日立制作所<br>日立器件工程株式会社                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所<br>日立设备工程有限公司                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 勇 広宣<br>竹本一八男<br>宮沢敏夫<br>松本克巳                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 勇 広宣<br>竹本一八男<br>宮沢敏夫<br>松本克巳                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| CPC分类号         | G09G3/2011 G09G3/3611 G09G3/3688 G09G2300/0408 G09G2300/0426 G09G2310/0232 G09G2310/0259 G09G2310/027 G09G2310/0283 G09G2320/0233                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/133.575 G09G3/20.621.M G09G3/20.623.A G09G3/20.680.G                                                                                                                                                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NC03 2H093/NC16 2H093/NC22 2H093/NC24 2H093/NC34 2H093/NC50 2H093/ND06 2H093/ND22 2H093/ND34 2H093/ND42 2H093/NE01 2H093/NE03 5C006/AA02 5C006/AC21 5C006/BB16 5C006/BC11 5C006/BC16 5C006/BC20 5C006/BF03 5C006/BF49 5C006/BF50 5C006/FA41 5C080/AA10 5C080/BB05 5C080/DD22 5C080/GG02 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 5C080/KK02 2H193/ZA04 2H193/ZF03 2H193/ZF37 2H193/ZP01 2H193/ZP03 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

## 摘要(译)

实现了在与显示单元相同的基板上形成有小的驱动电路的液晶显示装置。向像素提供灰度电压的驱动电路形成为具有与像素相同的宽度。驱动电路具有电压选择电路，该电压选择电路基于由多条显示数据线传输的显示数据输出灰度电压，并且为每条显示数据线提供构成电压选择电路的算术元件。该元件由相同导电类型的晶体管组成。