(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3918496号

(P3918496)

(45) 発行日 平成19年5月23日(2007.5.23)

(24) 登録日 平成19年2月23日(2007.2.23)

(51) Int.C1.

F 1

|                       |                 |

|-----------------------|-----------------|

| GO2F 1/1368 (2006.01) | GO2F 1/1368     |

| GO2F 1/1343 (2006.01) | GO2F 1/1343     |

| GO2F 1/1333 (2006.01) | GO2F 1/1333 505 |

請求項の数 2 (全 31 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2001-322951 (P2001-322951)  |

| (22) 出願日  | 平成13年10月22日 (2001.10.22)      |

| (65) 公開番号 | 特開2003-131245 (P2003-131245A) |

| (43) 公開日  | 平成15年5月8日 (2003.5.8)          |

| 審査請求日     | 平成16年1月30日 (2004.1.30)        |

|           |                                              |

|-----------|----------------------------------------------|

| (73) 特許権者 | 000005108<br>株式会社日立製作所<br>東京都千代田区丸の内一丁目6番6号  |

| (74) 代理人  | 100100310<br>弁理士 井上 学                        |

| (72) 発明者  | 渡辺 邦彦<br>千葉県茂原市早野3300番地 株式会社日立製作所ディスプレイグループ内 |

| (72) 発明者  | 浮須 雅弘<br>千葉県茂原市早野3300番地 株式会社日立製作所ディスプレイグループ内 |

| (72) 発明者  | 有吉 知幸<br>千葉県茂原市早野3300番地 株式会社日立製作所ディスプレイグループ内 |

最終頁に続く

(54) 【発明の名称】 液晶表示装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

互いに対向して配置された一対の基板と前記一対の基板の主面間に挟まれた液晶層とを備え、

前記一対の基板の一方の前記液晶層に面する主面には、スイッチング素子と、前記スイッチング素子に接続された画素電極と、前記スイッチング素子の前記液晶層側に少なくとも珪素と窒素を含む材料層からなる保護膜とが形成され、

前記保護膜は少なくとも第1の材料層と前記第1の材料層より前記液晶層側に設けられた第2の材料層とを含み、

前記第2の材料層の珪素に対する窒素の組成比は前記第1の材料層のそれより小さい液晶表示装置。 10

## 【請求項 2】

前記第2の材料層の珪素に対する窒素の組成比は0より大きく且つ1.0以下の範囲にある請求項1に記載の液晶表示装置。

## 【発明の詳細な説明】

## 【0001】

## 【発明の属する技術分野】

本発明は液晶表示装置及びその製造方法に係り、その液晶層に電界を印加する電極に残留する不要な電荷を除去し、その表示画面において画像を速やかに切り替え、又は表示動作終了時に画像を速やかに消去するに好適な液晶表示パネル(液晶表示素子)の構造、及び

その製造方法に関する。

【0002】

【従来の技術】

パーソナル・コンピュータ、モニタ、テレビジョン等の表示装置として液晶表示装置が広く用いられている。液晶表示装置は、一対の基板と、この一対の基板間に挟まれた液晶層（一対の基板間に封止された液晶組成物からなる層）、及びこの一対の基板の少なくとも一方の液晶層に対向する主面に形成された電極群を備えた液晶表示パネルを有する。液晶表示装置の表示動作は、表示すべき情報に応じて上記電極群により上記液晶層内に印加される電界を制御し、この液晶層の光透過率を変調して行う。液晶表示パネルの上記基板主面内において、上記液晶層の光透過率が変調される領域（上記表示動作が行われる領域）10は、表示画面、表示領域、又は有効表示領域とも呼ばれる。

【0003】

液晶表示装置は、その表示動作における上記液晶層内の液晶分子の振る舞い、及びこれに適合された上記液晶表示パネル内の電極構造により、アクティブ・マトリクス型、パッシブ・マトリクス型の2種に別けられる。前者の液晶表示装置は、上記表示領域を構成する各画素にアクティブ素子（スイッチング素子）が夫々形成される特徴を有する。このアクティブ素子として、例えば、薄膜トランジスタ（TFT）や薄膜ダイオード（TFD）が用いられている。

【0004】

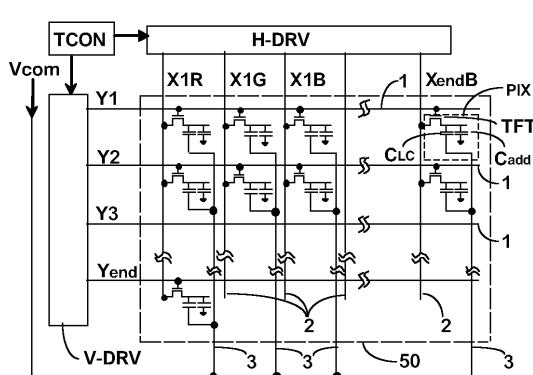

アクティブ・マトリクス型の液晶表示装置の一例を、図15に示した薄膜トランジスタを用いた液晶表示装置の等価回路図を参照して説明する。20

【0005】

図15に示す如く、液晶表示装置の表示画面SCR（破線で囲まれた領域）には、 $x$ 方向に延び且つこの $x$ 方向に交差する $y$ 方向に並設された複数の走査信号線1と、 $y$ 方向に延び且つ $x$ 方向に並設された複数の映像信号線（データ線とも呼ばれる）2が設けられる。また、これら複数の走査信号線の一つと複数の映像信号線の一つに夫々接続された複数の薄膜トランジスタTFTが設けられる。複数の薄膜トランジスタTFTは、ゲート電極に印加される電圧に応じてスイッチングされる所謂電界効果型トランジスタであり、その各々のゲート電極には上記複数の走査信号線1の一つが接続される。薄膜トランジスタTFTのドレイン電極には、上記複数の映像信号線の一つが接続され、ソース電極には上記液晶層に電界を印加する画素電極が接続される。画素電極は、これとともに液晶層に印加する電界を発生させる対向電極（共通電極とも呼ばれる）と併せて容量 $C_{Lc}$ として示される。表示すべき画像に応じた映像信号電圧は、上記映像信号線2からこれに接続される複数の薄膜トランジスタTFT（図15において $y$ 方向に並ぶ）に供給され、薄膜トランジスタTFTの各々は、そのゲート電極に上記走査信号線1のいずれか一つから走査信号電圧が印加されるタイミングに応じて上記映像信号電圧を画素電極に供給する。従って、液晶表示装置の表示画面SCRには、上記複数の薄膜トランジスタTFTの一つとこれを通して映像信号電圧が印加される容量 $C_{Lc}$ とを有する画素PIXが二次元的に形成される。30。なお、上述の如く、薄膜トランジスタTFTのゲート電極（これにより電荷の移動が制御されるチャネル層）から見て、映像信号線2側の電極をドレイン、画素電極（容量 $C_{Lc}$ ）側の電極をソースと記したが、これらの電極の名称は、双方の電位の相対的な関係に入れ替る。しかし、本明細書においては、便宜的に薄膜トランジスタTFTの映像信号線側をドレイン電極、画素電極側をソース電極と呼ぶ。40

【0006】

一方、上記画素電極とともに容量 $C_{Lc}$ を構成する対向電極には、基準電圧（Reference Voltage） $V_{com}$ が基準電圧線3を通して供給される。この対向電極及び基準電圧線3は、液晶層への電圧印加（液晶層の光透過率変調）の態様に応じ、上述の走査信号線、映像信号線、薄膜トランジスタ、及び画素電極が形成される基板（TFT基板とも呼ばれる）、又は、このTFT基板に対して液晶層を挟んで対向する別の基板のいずれかに形成される。前者の液晶表示装置は、その液晶層にTFT基板の主面に沿う電界が生じるため50

、面内スイッチング (In-Plane-Switching, IPS と略される) 型、や横電界型とも呼ばれる。これに対し、後者の液晶表示装置は、その液晶層にこの厚み方向に沿う電界が生じるため、縦電界型とも呼ばれる。なお、縦電界型の液晶表示装置においては、複数の画素電極 (例えば、上記表示画面 S C R 内に配置される全て) に一つの対向電極が対応して、その画素毎に上記容量  $C_{Lc}$  が形成されることもあり、TFT 基板に対向する別の基板の主面上において対向電極が基準電圧線 3 の機能も兼ねることもある。このような縦電界型の構造は、TFT 基板からこれに対向する基板に向けて液晶層中の液晶分子の長軸方向を徐々に旋回するツイステッド・ネマティック液晶を用いた液晶表示装置 (所謂、TN 型) や、TFT 基板の正面に対して液晶分子の長軸を所定の角度で傾けて配向させる所謂垂直配向型 (VA 型) の液晶表示装置に適用される。

10

#### 【0007】

上記走査信号線 2 の各々は、駆動回路 (垂直走査回路、又はゲート・ドライバともいう) V - D R V の出力端子に夫々電気的に接続されて、上記走査信号を受ける。上記映像信号線の各々は、上述のそれとは別の駆動回路 (映像信号駆動回路、又はドレイン・ドライバともいう) H - D R V の出力端子に接続されて、上記映像信号を受ける。液晶表示装置で表示すべき画像のデータは、その外部より制御回路 (タイミング・コンバータともいう) T C O N に入力され、ここで液晶表示装置の動作に適した走査信号及び映像信号 (階調信号を含むことのある) が発生される。

#### 【0008】

また、図 15 に示される画素 P I X には、上記容量  $C_{Lc}$  とは別の容量  $C_{add}$  も設けられている。この容量  $C_{add}$  は、付加容量、又は蓄積容量とも呼ばれ、各画素の画素電極に映像信号に応じて供給された電荷を、この画素電極に次の映像信号に応じた電荷が供給される時刻まで保持するために設けられる。

20

#### 【0009】

##### 【発明が解決しようとする課題】

上述のように、アクティブ・マトリクス型は、画素電極が設けられる基板上に電界効果型トランジスタやダイオードのようなアクティブ素子 (スイッチング素子) も形成せねばならない。従って、この基板正面には、アクティブ素子を設けたことにより起伏が生じる。

#### 【0010】

一方、上記液晶層の光透過率を画像に応じて変調するには、画素電極が設けられた基板の最上面 (液晶層に接する面) に対して液晶層中の液晶分子を所望の態様で配向させる所謂初期配向条件を満たすことが重要である。この初期配向条件を満たすには、例えば、基板の最上面に形成された配向膜正面に機械的又は光学的な処理を施し、この配向膜が形成される基板正面に対する液晶分子の長軸方向の向きや傾きを調整することが必要となる。従って、この配向膜正面を基板正面並みに平坦にすることが理想的である。このような要請の下、現実にはアクティブ素子が設けられた基板に、このアクティブ素子を覆うように絶縁膜を形成し、この基板の最上面 (この基板正面に形成され且つ液晶層に接する膜の正面) の起伏を上記初期配向条件が満たされる範囲で (少なくともアクティブ素子により生じる段差が低減されるように) 均している。このような絶縁膜は、保護膜、平坦化層 (Leveling Layer)、又はパッシベーション膜 (Passivation Layer) とも呼ばれる。

30

#### 【0011】

しかしながら、本発明者らは、液晶表示装置の動作電源をオフにしたとき、その表示画面にそれまで表示されていた画像が薄っすら残る所謂「残像」の問題を見出し、これが上述のアクティブ素子を覆う絶縁膜にも起因すると考えた。

#### 【0012】

本発明者らが、このような考えに到った経緯は次のとおりである。

#### 【0013】

液晶表示装置の画像表示動作 (液晶駆動ともいう) 中に液晶層に印加された電圧が、アクティブ素子を備えた基板 (以下、TFT 基板と例示) に形成された絶縁膜にも印加され、その誘電率ゆえに絶縁膜の上面及び下面に電荷が蓄積される。アクティブ素子として電界

40

50

効果型トランジスタを設けた TFT 基板には、上述のゲート電極とチャネル層とを隔てる所謂ゲート絶縁膜と、このトランジスタを覆う上述の保護膜とが形成される。ゲート絶縁膜は、その一面に接するゲート電極や走査信号線と、その他面に接するソース電極、ドレイン電極、及び映像信号線とで、これに蓄積された電荷を掃き出し易い。しかし、保護膜はその一面がソース電極、ドレイン電極、及び映像信号線、又はゲート電極及び走査信号線に接するのみで、その他面は上述の配向膜又は液晶層という電気を通し難い材料にしか接しない。このため、上記保護膜に蓄積された電荷が、液晶表示装置をオフした後も放電されることなく保護膜に相当な時間に亘って残留するため、この残留電荷により液晶層にオフセット電圧が印加されて、その表示画面に上述の残像が生じる。このように液晶表示装置の電源を遮断した後も、電源遮断前に書き込まれた画像が表示画面に一定時間保持される現象を、画像の「焼き付き」とも呼ぶ。10

#### 【0014】

本発明者らは、このような残像が以下のシチュエーションにおいて発生し易いことも見出した。

- (1) TFT 基板に形成されたゲート絶縁膜、保護膜等の誘電体膜が、比較的電荷を蓄積し易い（例えば、その膜厚が薄い、その材料の誘電率が高い）。

- (2) 液晶の駆動電圧（液晶層に印加される電圧）が比較的高い。

- (3) 液晶材料自体の抵抗率が比較的大きい。

#### 【0015】

このような知見に基づき、本発明者らは上記残像を解決するためには、TFT 基板に形成されるゲート絶縁膜や保護膜等の誘電体膜の形状又は物性を、電荷が溜まり難いように設定することが必要であると考えた。例えば、これら誘電体膜の膜厚を厚くしたり、これらの比誘電率を低下させるような条件で誘電体膜を形成することが望ましい。20

#### 【0016】

このような要請に対する一つの解は、例えば日本国特許第 2938521 号公報に開示されている。この公報には、薄膜トランジスタ上に窒化珪素 (SiN) 膜、及び非晶質珪素 (アモルファス・シリコン, a-Si) 膜を順次積層して保護膜を形成し、光照射下においては導電性材料でもある当該アモルファス・シリコン膜に一定の電位を印加して当該保護膜の面内での電荷蓄積状態を均一化して、液晶表示装置に生じる輝度ムラを抑制する発明が開示されている。この公報は、上記保護膜の表面全域を一定の電位に保持することで、長時間の画像表示動作後でも上記輝度ムラを抑えられることも教示する。30

#### 【0017】

しかしながら、本発明者らは、上記特許公報が開示する発明を上述の残像抑止に適用するに際し、次の問題に直面した。

#### 【0018】

まず、面内スイッチング型（横電界型）の液晶表示装置では、液晶を駆動する電界を形成する画素電極及び対向電極のいずれも保護膜で覆うことが、液晶層中の液晶分子を初期配向する上で望ましい。しかしながら、画素電極と対向電極との間に生じる電界は、保護膜を通して液晶層に入らざるを得ないため、この保護膜が上述の如き導電性材料からなる薄膜を含むと、この薄膜内の電流発生に費やされる。従って、画素電極と対向電極との間に生じる電界は、実質上液晶層に入れず、その中に存在する液晶分子の配向を制御できなくなる（液晶層の光透過率を変調できなくなる）といつても過言でない。40

#### 【0019】

上記公報に開示された発明の効果を確認するために、従来の面内スイッチング型の液晶表示装置の保護膜上に導電性を示す非晶質珪素膜を 20 nm 程度の厚さで成膜した。その結果、この液晶表示装置では液晶を駆動することができず、画質評価すら不可能であることが判明した。

#### 【0020】

一方、アクティブ・マトリクス型の液晶表示装置全般においても、上記公報に記載された発明の適用には次の問題が指摘される。例えば、ボトム・ゲート型と呼ばれる基板正面側

にゲート電極を、その上部にチャネル層となる半導体膜を配置して構成される薄膜トランジスタにおいて、上記非晶質珪素膜はこれとともに上記保護膜をなす絶縁膜を通して半導体膜（薄膜トランジスタのチャネル層）と対向する。従って、半導体膜にはゲート電極及び一定の電位に保たれた非晶質珪素膜の双方から電界が印加され、例えば、ゲート電極の電圧を当該薄膜トランジスタの閾値電圧より下げるにしても、半導体膜は実質的に電界が印加された状態を暫く保つ。この結果、薄膜トランジスタのオフ電流の増加とこれに起因する残像の発生に例示される新たな問題が生じる。また、基板正面側に半導体膜（チャネル層）を、その上部にゲート電極を配置したトップ・ゲート型の薄膜トランジスタや、薄膜ダイオードをスイッチング素子として用いたアクティブ・マトリクス型の液晶表示装置においても、これと上記一定の電位に保たれた非晶質珪素膜との間に生じる寄生容量で、スイッチング素子の誤動作が指摘される。

#### 【0021】

以上の検討を総括すれば、残像発生の原因たる保護膜に蓄積された電荷が長時間に亘りこれに残留する現象を、この保護膜の面内を一定の電位に保持することで解決することを試みるも、輝度ムラは生じないが残像は残る結果に到らざるを得なかった。従って、上記特許公報が教示する絶縁性の保護膜上に導電性材料の膜を付加する方法でも、残像と輝度ムラとの抑制、及び薄膜トランジスタのオフ電流と液晶層への駆動電界の印加とを両立することが極めて困難である。

#### 【0022】

この残像問題を、ゲート絶縁膜の改善のみで対処するも、この絶縁膜が液晶表示装置のスイッチング素子である薄膜トランジスタの電気特性に影響するため、この膜厚を厚くしたり、比誘電率を低下させて電気容量を低減することは却って弊害を招く。また、保護膜はゲート絶縁膜に比べて、その形状及び物性に対する制約が少ないが、薄膜トランジスタのオフ電流に影響したり、これを形成するプラズマCVD装置の処理能力の制約等から、ゲート絶縁膜と同様に膜厚や比誘電率を残像緩和のためだけに調整することは非現実的である。

#### 【0023】

本発明の目的の一つは、アクティブ・マトリクス型液晶表示装置における、上述の如き残像抑制と輝度ムラ、及びスイッチング素子の電気的特性と液晶層への電界印加効率の夫々におけるトレード・オフの関係を解決することにある。

#### 【0024】

##### 【課題を解決するための手段】

上述の目的に鑑み、本発明は以下に例示される液晶表示装置を提供する。

#### 【0025】

その一つは、互いに対向して配置された一対の基板と該一対の基板の正面間に挟まれた液晶層とを備え、上記一対の基板の一方の上記液晶層に面する正面にはスイッチング素子及びこれに接続された画素電極を有する画素領域と該スイッチング素子の該液晶層側に複数の材料層を積層してなる保護膜とが形成された液晶表示装置で、上記複数の材料層は少なくとも第1の層（材料層）とこの第1の層より上記液晶層側（上記一対の基板の一方の正面から見て第1の層の上部）に設けられた第2の層（材料層）とを含み、且つこの第2の層は上記第1の層より低く且つ珪素より高い抵抗率を示すことを特徴とする。ここでいう珪素には、単結晶シリコンや多結晶シリコン、非晶質シリコン等の所謂液晶表示装置に備えられたスイッチング素子のチャネルを構成する半導体材料が例示される。従って、上述の保護膜に含まれる第2の層は、この保護膜に含まれる第1の層より低く且つ上記スイッチング素子のチャネル層より高い抵抗率を示すとも特徴付けられる。

#### 【0026】

これらの第1の層と第2の層とは、光照射により第1の層が $1 \times 10^{13} \text{ cm}^{-2}$ 以上の抵抗率を示し且つ第2の層が $1 \times 10^{11} \text{ cm}^{-2}$ 以下の抵抗率を示すことからも特徴付けられる。このような保護膜の光伝導特性は、例えば $500 \text{ kLx}$ （キロ・ルクス）又はそれ以上の照度の光を第1の層及び第2の層に照射するか、これらの層が形成される基板

10

20

30

40

50

正面の反対側から当該保護膜構造に照射することで測定される。

【0027】

上述のように、スイッチング素子が形成された基板主面上に第1の層及び第2の層をこの順に形成してなる本発明による保護膜構造をその比誘電率から記述すると、上記第2の層は上記第1の層より高い比誘電率を有し且つ該第2の材料層の比誘電率は7.5以上の値を有する。

【0028】

また、上述のスイッチング素子の液晶層側に形成される保護膜を少なくとも珪素と窒素とを含む材料:  $Si_xN_yX_z$  (Xはその他の構成元素の総称)で形成するとき、上記第2の層の珪素に対する窒素の組成比( $y/x$ )は上記第1の材料層のそれより小さいという特徴を有する。

【0029】

以上に記した保護膜を構成する第1の層及び第2の層は、さらに次の少なくとも一形態を満たすことが推奨される。

【0030】

その一つは、上記第2の層の抵抗率を、上記第1の層の抵抗率の1/100より低くすることである。

【0031】

また他の一つは、上記第2の層の抵抗率を、上記液晶層の抵抗率より低くすることである。

【0032】

更に他の一つは、上記第2の層の厚みを、上記保護膜全体の厚さの1/2以下にすることであり、なお望ましくは、第2の層の厚さを10nm以上にすることである。

【0033】

以上、本発明による液晶表示装置において基板上に設けられたスイッチング素子を覆う新規な保護膜の特徴をその断面構造として記したが、この保護膜の特徴を上記基板の液晶層側の上面から捉えると次の少なくとも一つとして記される。

【0034】

その特徴の一つは、互いに対向して配置された一対の基板とこれらの正面間に挟まれた液晶層とを備え、上記一対の基板の一方の上記液晶層に面する正面にはスイッチング素子及びこれに接続された画素電極を有する画素領域とこのスイッチング素子の上記液晶層側に接する保護膜とが形成された液晶表示装置において、上記保護膜はその上記液晶層に対向する面に光が照射されることによりその抵抗率が光照射を行わないときの抵抗率の1/100以下に減少することである。ここでいう光照射とは、例えば500kLx又はそれ以上の照度の光を保護膜の上面に照射することである。

【0035】

また、その特徴の別の一つは、互いに対向して配置された一対の基板とこれらの正面間に挟まれた液晶層とを備え、上記一対の基板の一方の上記液晶層に面する正面にはスイッチング素子及びこれに接続された画素電極を有する画素領域とこのスイッチング素子の上記液晶層側に接する保護膜とが形成された液晶表示装置において、上記保護膜の上記液晶層に対向する面は $1 \times 10^{13} \cdot cm \sim 1 \times 10^{15} \cdot cm$ の範囲にある暗抵抗率を示し且つ当該面への500キロ・ルクスの照度の光照射により $1 \times 10^9 \cdot cm \sim 1 \times 10^{11} \cdot cm$ の抵抗率を示すことである。

【0036】

更に、その特徴の別の一つは、互いに対向して配置された一対の基板とこれらの正面間に挟まれた液晶層とを備え、上記一対の基板の一方の上記液晶層に面する正面にはスイッチング素子及びこれに接続された画素電極を有する画素領域とこのスイッチング素子の上記液晶層側に接する保護膜とが形成された液晶表示装置において、上記保護膜の上記液晶層に対向する面は7.5以上の比誘電率を示すを示すことである。

【0037】

10

20

30

40

50

また、上記保護膜を少なくとも珪素と窒素とを含む材料： $Si_xN_yX_z$ （Xはその他の構成元素の総称）で形成するとき、その特徴は互いに対向して配置された一対の基板とこれらの正面間に挟まれた液晶層とを備え、上記一対の基板の一方の上記液晶層に面する正面にはスイッチング素子及びこれに接続された画素電極を有する画素領域とこのスイッチング素子のチャネル層に接する保護膜とが形成された液晶表示装置において、上記保護膜の上記液晶層に対向する面の珪素に対する窒素の組成比（y/x比）は0より大きく且つ1.0以下の範囲に入る値となることである。

【0038】

以上に記した少なくとも一つの特徴を有する液晶表示装置において、上記保護膜の上記液晶層側に配向膜を形成するとよく、また、この液晶表示装置をツイスティッド・ネマティック（TN）型のように画素電極とともに上記液晶層に電界を印加する対向電極を上記一対の基板の他方に設けて構成する場合、この画素電極は保護膜と液晶層との間（望ましくは、保護膜と配向膜との間）に設けるとよい。

【0039】

一方、以上に記した少なくとも一つの特徴を有する液晶表示装置を面内スイッチング型のように画素電極と対向電極とを上記一対の基板の一方に設ける場合、この画素電極は保護膜に対して液晶層の反対側（一対の基板の一方の正面側）に設けるとよい。

【0040】

本発明による上述の液晶表示装置は、上記一対の基板の一方の正面に複数のスイッチング素子を形成する第1の工程と、上記スイッチング素子の上部に複数のガスが導入されたプラズマを用いる化学気相蒸着法で保護膜を形成する第2の工程とを含む製造方法において、この第2の工程に次の特徴の少なくとも一つを反映させることにより、上記保護膜を構成する上記第2の層の抵抗率をこの保護膜を構成する上記第1の層より低くすることができる。

【0041】

その特徴の一つは、少なくとも第1の組成を有する上記第1材料層を蒸着した後に、上記複数の原料ガスの導入比を変えて上記第1の組成とは異なる第2の組成を有する上記第2材料層を蒸着することである。

【0042】

また、その特徴の他の一つは、少なくとも上記第1材料層を蒸着した後に、上記プラズマに供給する電力を上記第1材料層の蒸着時のそれより低くして上記第2材料層を蒸着することである。

【0043】

上記第2の工程において、上記複数の原料ガスとして珪素を含む第1のガス（例えば、モノシリラン）と窒素を含む第2のガス（例えば、アンモニア）とを用いる場合、上記第1のガスに対する上記第2のガスの導入量比は上記第1材料層の蒸着時にて1.0より大きく設定し、且つ上記第2材料層蒸着時にて0より大きく且つ1.0以下の範囲に設定することが望ましい。

【0044】

また、上記第2の工程において、上記第2材料層の蒸着時に上記プラズマに導入される高周波電力を上記第1材料層の蒸着時より低く抑え、例えば、 $0.2\text{W/cm}^2$ 以下に設定するとよい。

【0045】

以上に記した本発明の作用並びに効果、及びその望ましき実施形態の詳細に関しては、後述の説明で明らかになろう。

【0046】

【発明の実施の形態】

以下、本発明の具体的な実施形態をこれに関連する図面を参照して説明する。以下の説明にて参照する図面で、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

### 《第1実施例》

本発明による液晶表示装置の第1実施例を、上述の面内スイッチング型液晶表示装置に用いられるTFT基板の構造及びその製造工程を例示して説明する。

#### 【0047】

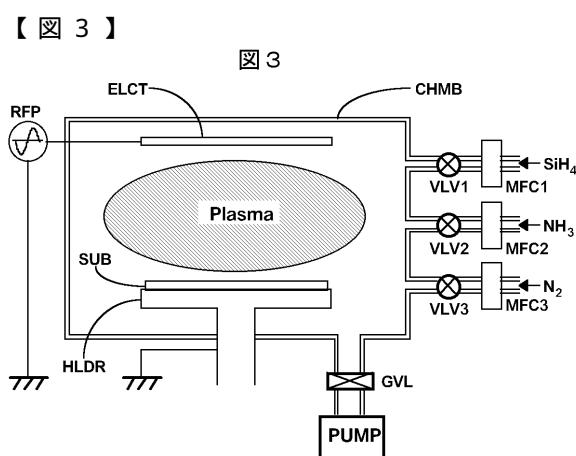

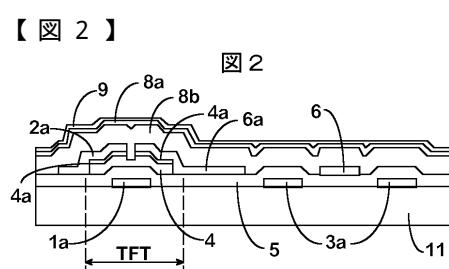

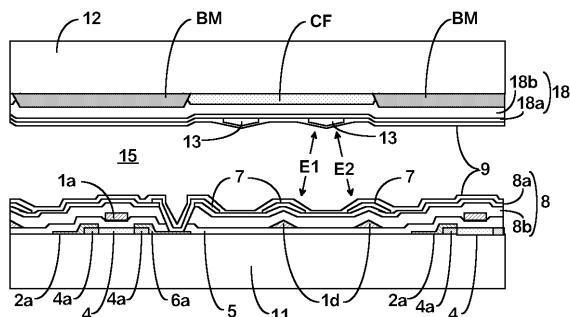

図1は面内スイッチング型の液晶表示装置に用いられるTFT基板の正面（液晶層に面する）に形成された複数の画素の一つを拡大して示す平面図であり、図2は図1の一点鎖線C-C'沿いにTFT基板を切断したときの断面図である。

#### 【0048】

図1は、図の下側に示された走査信号線1から分岐したゲート電極1a、このゲート電極1aを覆う半導体層（チャネル層）4、図の左側に示された映像信号線2から分岐したドレイン電極2a、及び画素電極6と一緒に形成されたソース電極6aを備えた薄膜トランジスタTFTと、y方向に延び且つx方向に並ぶ前述の画素電極6と、図の上側に示された基準電圧線3からy方向に分岐し且つx方向沿いに画素電極と離間して並ぶ対向電極3aとを有する画素を示す。この画素において光が透過する領域は、液晶層を挟んでTFT基板に対向する他の基板（対向基板、カラー・フィルタ基板とも呼ばれる）に形成された遮光膜（以下、ブラック・マトリクスと呼ぶ）の開口で規定される。図1において、ブラック・マトリクスの開口は、その縁を示す破線BMOで囲まれた領域となる。なお、図2に示されるTFT基板の断面では、液晶層及びTFT基板に対向する上記他の基板は省略されている。TFT基板の正面には、図1の中央に示された上述の画素と同様な構造を有する複数の画素が二次元的に配置される。このような複数の画素の配置様の一例を、図1は中央の画素を囲む他の8つの画素（部分的に描かれる）の配置として示す。

#### 【0049】

始めに、図1及び図2を参照して、本実施例におけるTFT基板の製造工程を説明する。製造工程の多くは、既存の液晶表示基板、又は液晶表示パネルの製造方法に採用されている技術を利用するため、簡単に説明する。また、本発明による液晶表示装置の作製に特徴的な製造工程については、適宜、図面を加えて、これを参照しながら説明する。

#### 【0050】

工程1：TFT基板11として、370mm×470mm×1.1mmのガラス基板を用意した。この正面には、前述の如く、図1に示すような画素が二次元的に形成されるが、工程1の段階では単なるガラス面に過ぎない。このようなガラス基板をTFT基板11として用いることにより、対角38cmの表示画面を有する液晶表示パネル（液晶セルともいう）が作製できる。

#### 【0051】

工程2：このガラス基板11の正面（図2では上面）を洗浄した後、この正面に金属や合金等からなる第1の導電膜を、例えばスパッタリング法（Sputtering Method）で形成する。本実施例では、厚さ200nmのクロム（Cr）薄膜をスパッタリング法で形成した。このクロム薄膜上にフォト・レジスト（感光性の有機材料）を塗布し、このフォト・レジストにフォト・マスク（複数のスリットが形成された遮光板）を通して光を照射し、フォト・レジストを部分的に感光させた。その後、フォト・レジストの現像処理で、その感光した部分を選択的に除去し、これにより形成されたフォト・レジストの開口から上記クロム薄膜を部分的に露出させる。工程2における以上の処理を総括して、フォト・リソグラフ法とも呼ぶ。上記フォト・マスクに形成された複数のスリットは、上述の走査信号線1（ゲート・バスラインとも呼ぶ）、ゲート電極1a、基準電圧線3（面内スイッチング型液晶表示装置においては、対向電圧信号線、コモン・バスラインとも呼ばれる）、対向電極3aの夫々の輪郭に相似する形状を有する。また、上記フォト・マスクで、TFT基板の表示領域に相当する部分の外側（周縁部分）に形成されたフォト・レジストを露光する場合、フォト・マスクの周縁部分にTFT基板と外部回路とを接続する端子（図示せず）、表示領域内の薄膜トランジスタを静電気等による絶縁破壊から保護する保護回路（図示せず）等に対応したスリットを設けても良い。なお、上記フォト・レジスト及びこれを現像する薬品によっては、フォト・レジストの感光されない部分が現像処理で除去される

10

20

20

30

40

50

が、このような相違は本発明による TFT 基板の作製を阻むものではない。

【0052】

工程3：工程2が終了した段階で、クロムからなる第1の導電膜の上面には、上記走査信号線、ゲート電極等に類似した形状のフォトレジストが残る。この第1の導電膜の上面を、例えば硝酸第2セリウム・アンモニウム水溶液等の薬品（クロムをエッチングするエッチャント）で処理し、レジストに覆われない第1導電膜（クロム薄膜）をTFT基板11正面から除去する。この処理をエッチング法という。TFT基板11上に第1導電膜からなる走査信号線2、ゲート電極2a、基準電圧線3、対向電極3a等が形成された後、これらの上面に残るフォト・レジストを例えば硫酸等で除去し、続いて純水（イオン交換樹脂で濾過された水）で洗浄する。

10

【0053】

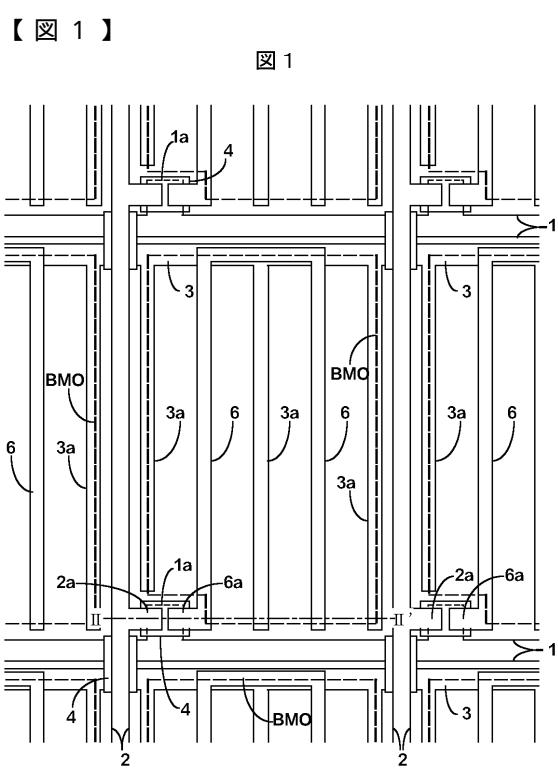

工程4：第1導電膜による配線（走査信号線等）や電極（ゲート電極等）のパターンが形成されたTFT基板11の上面に、絶縁膜5と半導体膜4をこの順で積層させる。絶縁膜5は、後述の薄膜トランジスタにおけるゲート絶縁膜にもなる。本実施例では、絶縁膜5を非晶質の窒化珪素膜（SiN<sub>x</sub>）で、半導体膜4を非晶質の珪素膜（a-Si）で夫々形成する。絶縁膜5及び半導体膜4はともに珪素を含む材料ゆえ、本実施例では化学蒸着法（Chemical Vapor Deposition Method, CVD法とも呼ばれる）を用い、TFT基板正面にこれらを連続的に成長させた。本実施例では、絶縁膜5及び半導体膜4の原料ガスでプラズマを発生させ、このプラズマにTFT基板11の上面（被加工面）を対向させるプラズマCVD法（Plasma Enhanced CVD Method）を用いた。プラズマCVDに用いた装置を、図3に模式的に示す。詳細は後述するが、TFT基板は試料（Specimen）SPCMとしてホルダ（Holder）HLDRに置かれる。

20

【0054】

プラズマCVDによる非晶質の窒化珪素膜及び珪素膜の連続成長の終了間際に、半導体膜4に導電性を与える不純物元素を添加して蒸着することで、半導体膜4の上面付近に電子密度の高いn<sup>+</sup>型の領域4aを形成する。本実施例では、不純物元素としてIV族の珪素（Si）に比べて価電子の多いV族元素の一つである磷（P）をドーパントに用いた。このn<sup>+</sup>型半導体層4aは、次に形成される第2金属膜と半導体層4とを低い電気抵抗で接続させる（オーミック接触させる）。なお、本実施例では、絶縁膜5、半導体膜の意図的に不純物が導入されない部分（図2に半導体膜4として表示）、及び半導体膜の意図的に不純物を導入した部分（図2にn<sup>+</sup>型半導体層4aとして表示）の厚みを、夫々400nm, 250nm, 50nmとした。n<sup>+</sup>型半導体層4aはCVD等による半導体膜の蒸着時に形成しなくとも、例えば、成長後の半導体膜にドーパントのイオンを注入するイオン打込み（Ion Implantation）や、半導体膜に金属や合金からなる第2導電膜を接合した後に熱処理等で金属や合金の原子を半導体膜に移動させる方法でも、形成できる。また、透過型電子顕微鏡像においては、半導体膜における意図的に不純物がドープされない領域（真性半導体領域とも呼べる、以降、便宜的にi型領域という）と意図的に不純物がドープされた領域（上記n<sup>+</sup>型領域）とを判別することは難しく、図2における半導体膜4とn<sup>+</sup>型半導体層4aとは一つの半導体層として観察される。

30

【0055】

工程5：絶縁膜5及び半導体膜4の成膜が終了した後、先述のフォト・リソグラフ法で半導体膜4上にフォト・レジストのパターンを形成した。このパターンは、ゲート電極1aの上部、及び走査信号線1並びに基準電圧線3の映像信号線2と交差する部分の上部に夫々残されたフォト・レジストの「島（Island）」からなる。

40

【0056】

工程6：次に、その上面に上記フォト・レジストの島が形成されない半導体膜4を6フッ化硫黄（SF<sub>6</sub>）と塩化水素（HCl）とを用いたドライ・エッチング法にて除去し、ゲート電極1a上に薄膜トランジスタのチャネル層となる半導体膜4（上記n<sup>+</sup>型領域も含む）と、走査信号線1並びに基準電圧線3の後述の映像信号線2と交差する夫々の部分の上に映像信号線2の断線を防ぐ半導体膜4とを残す。その後、上記レジストの島を先述の

50

工程 3 に倣い、除去する。なお、絶縁膜 5 は、この段階で TFT 基板 11 の主面の少なくとも表示領域の全域に残る。

【 0 0 5 7 】

工程 7：次に、上記半導体膜 4 ( $n^+$  型領域 4 a も含む) 及び上記絶縁膜 5 を覆うように金属又は合金からなる第 2 の導電膜をスパッタリング法で形成する。本実施例では、第 2 の導電膜を厚さ 200 nm のクロムからなる薄膜で形成した。このクロムからなる第 2 の導電膜に工程 2 で述べたフォト・リソグラフ法及び工程 3 で述べたエッチング法を施し、映像信号線 2 (ドレイン・バスラインとも呼ばれる)、ドレイン電極 2 a、画素電極 6、及びソース電極 6 a を形成した。この一連の工程では、工程 2 で述べたように、フォト・マスクの周縁に外部回路と接続される端子 (図示せず) や上記保護回路のパターン (図示せず) 等を設け、これらをエッチング法で映像信号線 2 等とともに形成しても良い。本工程においては、クロムのエッチャントによるエッチングが終了した後、フォト・レジストを除去せず、次の工程 8 に入る。

【 0 0 5 8 】

工程 8：ドレイン電極 2 a 及びソース電極 6 a 上に夫々フォト・レジストを残したまま、工程 6 と同様に 6 フッ化硫黄と塩化水素との混合気体を用いて上記半導体膜 4 ( $n^+$  型領域 4 a も含む) にドライ・エッチングを施した。このエッチング工程で用いるエッチング・ガスに対し、非晶質の珪素膜はクロム薄膜に比べてエッチングされ易いため、半導体膜 4 はドレイン電極 2 a 及びソース電極 6 a をマスクとしてエッチングされる。このドライエッチングにより、上述の  $n^+$  型領域 4 a を含めた半導体膜 4 は、その上面からプロセス設計値にして 100 nm 相当の厚みでエッチングされる。工程 4 で述べたとおり、 $n^+$  型領域 4 a の厚みは 50 nm であるため、その上にドレイン電極 2 a やソース電極 6 a 等の第 2 導電膜が形成されない半導体膜 4 においては、その上面沿いに形成される  $n^+$  型領域 4 a が完全に除去される。従って、工程 7 の終了時にドレイン電極 2 a からソース電極 6 a へと延びていた  $n^+$  型領域 4 a は、双方の電極間で分断され、更にこの間における半導体膜 4 の i 型領域も薄くなる。薄膜トランジスタに限ってみれば、その構造は本工程により概ね完成する。半導体膜 4 のドライ・エッチングの後、工程 3 と同様にフォト・レジストを薬液で除去した。

【 0 0 5 9 】

工程 9：本工程では、上述の薄膜トランジスタ、画素電極 6、及び対向電極 3 a の上部に、先述の残像を低減するに好適な保護膜 8 を形成する。本実施例では、工程 4 と同様に、プラズマ CVD 法で TFT 基板の最上面 (本工程を始める段階での) に組成の異なる 2 種類の非晶質の窒化珪素 ( $SiN_x$ ) からなる薄膜を順次積層し、この 2 層の窒化珪素膜 (図 2 の上から 8 a, 8 b) で保護膜 8 を構成した。2 層の窒化珪素膜 8 a, 8 b は、TFT 基板の少なくとも表示領域に相当する部分の全域に形成した。プラズマ CVD による窒化珪素膜形成は、図 3 に模式的に示す蒸着装置を用いた。

【 0 0 6 0 】

この蒸着装置は、筐体 CHMB 内に被加工物 (試料 SPCM) が置かれるホルダ HLD とこれに対向する電極 ELC が設けられ、接地電位に接続されたホルダ HLD に対し、高周波電源 RFP に接続された電極 ELC が容量結合して、この間にプラズマ (P1 asma) を発生させる。プラズマは、バルブ GVL を通して筐体 CHMB に接続された排気装置 PUMP で筐体 CHMB 内の圧力を調整し、高周波電源 RFP から電極 ELC に供給される電力を調整することで、筐体 CHMB に供給されるガスの電離状態を維持する。プラズマを発生させるガスとして、図 3 にはモノシリコン (Monosilane:  $SiH_4$ )、アンモニア (Ammonia:  $NH_3$ )、及び窒素 ( $N_2$ ) が示される。これらのガスの筐体 CHMB への供給量は、夫々の流路に設けられた流量計 MFC1, MFC2, MFC3 で各々の流量をモニターしながら、バルブ VLV1, VLV2, VLV3 により適宜調整される。

【 0 0 6 1 】

上記 2 層の窒化珪素膜 8 a, 8 b は、膜の組成別に蒸着装置を替えて成長させても、また

10

20

30

40

50

複数の反応室（図3における筐体CHMB）とこれらの間で被加工物を減圧雰囲気下で搬送するシステムを備えた蒸着装置を用いて膜の組成に応じて別の反応室で成長させても良い。但し、以下に述べる本実施例では、蒸着装置も反応室も替えず、かつ反応室内の放電を止めることなく連続的に形成した。

#### 【0062】

なお、上側の窒化珪素膜8a、下側の窒化珪素膜8bの夫々の成膜条件は表1に記載のとおりである。

表1

| パラメータ（単位）                                   | 下側窒化珪素膜8b | 上側窒化珪素膜8a     |

|---------------------------------------------|-----------|---------------|

| SiH <sub>4</sub> 流量 (cm <sup>3</sup> /min.) | 130       | 350           |

| NH <sub>3</sub> 流量 (cm <sup>3</sup> /min.)  | 1200      | 100           |

| N <sub>2</sub> 流量 (cm <sup>3</sup> /min.)   | 2500      | 2000          |

| 反応圧力 (Pa)                                   | 266       | 266           |

| 高周波電力 (W)                                   | 2500      | 350           |

| 基板温度 (°C)                                   | 250       | 250           |

| 膜厚 (nm)                                     | 500       | 0, 10, 20, 30 |

10

20

30

40

#### 【0063】

表1に示される如く、本発明者らは上側窒化珪素膜8aの厚さが異なる4種類のTFT基板を作製し、その比較を後述の如く行った。なお、4種類のTFT基板の一つは、上側窒化珪素膜8aが形成されない所謂本発明者らが従来作製していたものである。

#### 【0064】

本工程の特徴は、保護膜8を形成する過程で、下側の窒化珪素膜8bの成長時における原料ガスの流量比、即ち、モノシランガス流量(SiH<sub>4</sub>流量)とアンモニアガス流量(NH<sub>3</sub>流量)とを上側の窒化珪素膜8aの成長開始時点で逆転させたことにある。

#### 【0065】

本発明者らは、従来、アンモニアガス（又はその代用となり得る窒化物ガス）のプラズマへの供給量をモノシランガス（又はその代用となり得る珪素化合物ガス）のそれより大きく設定して成長させた非晶質の窒化珪素膜を保護膜として利用していた。これに対し、本発明者らは先述の残像を低減するに際し、非晶質の窒化珪素膜の成長条件を検討したところ、上述のプロセス条件による非晶質の窒化珪素膜の成長終了間に、モノシランガス（又はその代用となり得る珪素化合物ガス）のプラズマへの供給量のアンモニアガス（又はその代用となり得る窒化物ガス）のそれに対する比率を高めるにつれて残像が解消し易くなる傾向を見出した。特に、モノシランガス（又はその代用となり得る珪素化合物ガス）のプラズマへの供給量がアンモニアガス（又はその代用となり得る窒化物ガス）のそれより大きく設定して保護膜を形成した液晶表示パネルの表示画面においては、その動作終了時における残像が概ね無視できた。従って、本発明者らは本実施例において、表1に示す条件で従来の窒化珪素膜8b上に、新たに窒化珪素膜8aを形成した。このような2層構造の保護膜の詳細については、後述する。

#### 【0066】

工程10：上述の如く、TFT基板の少なくとも液晶表示パネルの表示領域に相当する部分に形成された2層構造の保護膜の上面に、ポリイミド等の有機材料からなる配向膜9を形成する。TFT基板を液晶表示パネルに組込むと、この配向膜が液晶層に接する。従つ

50

て、配向膜上面にはラビング等の機械的な処理、または特定の偏光成分を有する光の照射を施し、これに接する液晶分子を所望の方向に配向させる。本実施例では、配向膜上面に液晶分子を配向させる特性を与える処理を、TFT基板と対向基板とを貼り合せる前に行う。従って、配向膜9上面の処理が完了した時点で、図2に示されるような断面を有するTFT基板が完成する。なお、配向膜9にラビング処理を施す場合、その処理後に配向膜を焼成する。

#### 【0067】

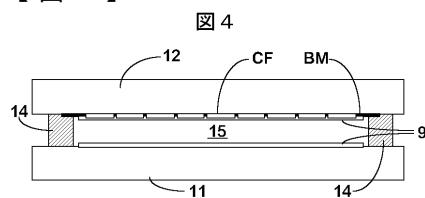

次に、上述の如く作製されたTFT基板に対向基板を貼り合せて、面内スイッチング型の液晶表示装置を完成させる。図4は、完成された液晶表示パネルの断面を模式的に描いたもので、図1に示される画素構造と図2に示される断面を有するTFT基板11は、その主面上に形成された薄膜等のうち、配向膜9以外は全て省略されている。一方、対向基板12のTFT基板11に対向する主面には、上述のブラック・マトリクスBMが形成され、その開口(図1参照)には画素毎にカラー・フィルタCFが設けられる。従って、巨視的に見れば、ブラックマトリクスBMとカラー・フィルタCFとは対向基板12の主面に対して略同じ層として描かれる。このように主面にカラー・フィルタが形成された対向基板12は、カラー・フィルタ基板と呼ばれることもある。ブラックマトリクスBMとカラー・フィルタCFとの上部には、保護膜(オーバコート膜とも呼ばれる、図示せず)が形成され、さらに保護膜上部にはTFT基板と同様に配向膜9が形成されている。なお、本実施例における面内スイッチング型の液晶表示装置は、TFT基板11主面上に図1の如く画素電極と対向電極とを互いに離間させて画素領域(光が透過する領域)を構成するため、対向基板12主面に電極は形成されていない。このような液晶表示装置の組立工程の概要を、以下に説明する。

#### 【0068】

TFT基板11及び対向基板12の互いに対向し合う主面の少なくとも一方の周縁に、シール材と呼ばれる粘着性の有機材料を塗布する。次に、図4の如く、TFT基板11と対向基板12とを重ね合わせ、シール材で双方の主面の周縁を接着し、続いてアニーリング(Annealing)等によりシール材を硬化させる。シール材は、TFT基板11及び対向基板12の少なくとも一方の主面の表示領域となる部分(画素やカラー・フィルタが設けられる部分)を概ね囲むように当該主面に塗布される。従って、TFT基板11と対向基板12とを貼り合せた段階で、液晶表示パネルの断面には図4に示す如く、これらの主面とシール材14により囲まれた空間が形成される。この空間には、シール材14に設けられた開口(封止口)から液晶材料(又はカイラル剤等を含む液晶組成物)15が注入される。なお、本実施例に用いた液晶材料16の抵抗率は $1 \times 10^{13} \Omega \cdot cm$ である。

#### 【0069】

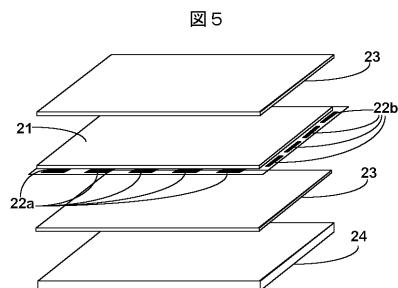

図5には、上述の如く作製された液晶表示パネル21を組込んだ液晶表示装置の分解斜視図が描かれる。液晶表示パネル21のTFT基板周縁の一部は対向基板より外側に突き出でて、この突き出た部分には液晶表示パネル21内に設けられた薄膜トランジスタ等に信号を供給する駆動回路(液晶表示パネルに対して外部回路)22a, 22bが電気的に接続される端子が形成される(図示せず)。

#### 【0070】

液晶表示パネル21の上面及び下面の夫々に偏光板23を貼り、その下面側をバックライト・ユニット24に対向させ、お互いを固定することで液晶表示装置は概ね完成する。バックライト・ユニット24は、導光板等を用いたサイド・エッジ型や、複数の線状ランプを液晶表示パネル21の下面に対向させる直下型等に分類されるが、本実施例に採用されるバック・ライトユニットはその種類を問わない。

#### 《残像抑制に対する効果》

上述した本発明の第1実施例による面内スイッチング型液晶表示装置の残像特性に関する検討結果を以下に述べる。

#### 【0071】

この液晶表示装置に用いるTFT基板の製造方法における工程9にて述べたように、本発

10

20

30

40

50

明者らは従来の保護膜として形成される非晶質窒化珪素膜 8 b 上に新たに設けられる非晶質窒化珪素膜 8 a の厚みが異なる 4 種類の TFT 基板を作製した。この 4 種類の TFT 基板に形成された窒化珪素膜 8 a の膜厚は夫々、0 nm ( 窒化珪素膜 8 a が形成されない従来の TFT 基板 ) , 10 nm , 20 nm , 及び 30 nm である。これらの TFT 基板を夫々用いて作製した 4 種類の液晶表示装置の性能を、以下に記す 2 種類の評価基準で比較した。

#### 【 0072 】

いずれの基準による比較も、液晶表示パネルの表示画面に表示される画像を切替える直前の基準電圧 ( 対向電極 3 a に印加される電圧  $V_{COM}$  、コモン電圧とも呼ばれる ) と切替えた直後の基準電圧との差が、表示画面に残像が生じる時間を決めるという事実に基づく。即ち、表示画像の切替の前後における基準電圧の差は、表示画像の切替からの時間が経過するに伴い、減少 ( 緩和 ) していく。本発明者等は、この現象に着眼して上記基準電圧差の緩和に要する緩和時間を測定して残像を評価した。なお、以下に記す基準電圧  $V_{COM}$  とは対向電極 3 b に印加される電圧、ゲート電圧とはゲート電極 1 a に印加される電圧、ドレイン電圧とはドレイン電極 2 a に印加される電圧である。

#### 【 0073 】

##### 〔評価方法 A 〕

液晶表示パネルにおいて、その表示画面で黒表示を行う ( 液晶層の光透過率を最小にする ) ときの対向電極 3 a を接地電位 ( グランド電位 ) に設定する。換言すれば、対向電極 3 a の電位を 1 フレームの画像表示毎に変える所謂コモン反転駆動ではない駆動方法 ( 例えば、ドット反転駆動 ) で液晶表示パネルの画像表示を行う。このような動作状態にある液晶表示パネルの電源をオフすると、その直前に画素電極 6 と対向電極 3 a との電位差により、これらの電極間に位置する保護膜 8 に生じた電荷は、対向電極 3 a の基準電圧により保護膜 8 に溜まる。従って、液晶表示パネルの電源がオフされるや否や、保護膜 8 は所謂充電状態になる。これにより保護膜 8 の電位が上がるため、配向膜 9 を挟んで保護膜 8 に対向する液晶層の光透過率も上がる。よって、液晶表示装置の表示画面は一時的に白表示を行い、又はそれに近い輝度を示す。なお、本明細書における「白表示」とは、液晶層の光透過率がこれに印加される階調電圧の範囲において最大となる場合に限らず、その光透過率が上記「黒表示」状態におけるそれよりも高ければ、白以外の色 ( 例えば、灰色 ) を表示する動作も含む。

#### 【 0074 】

液晶表示パネルの動作がオフされたことにより上記保護膜 8 に溜まる電荷は、そのオフ時刻からの時間経過とともに保護膜 8 からの漏洩により減少し、保護膜の充電状態も緩和される。これにより、接地電位に接続された対向電極 3 a から基準電圧が保護膜 8 の残留電荷に阻まれることなく液晶層に印加されるため、液晶層の光透過率が徐々に低下して液晶表示パネルの表示画面も黒表示に変わる。

#### 【 0075 】

このとき、液晶表示パネルの表示画面 ( 又は、ここに配置される画素 ) の輝度を測定し、液晶表示パネルの電源をオフした直後に測定された最大の輝度値 ( 白輝度とも呼ぶ ) が半減するに要した時間で、上記 4 つの液晶表示パネルの残像緩和特性を夫々評価した。具体的には、受光素子を液晶表示パネルの特定の部分に対向させ、その部分の輝度の変化を連続的にモニターする所謂定点観測を行った。上記最大の輝度値 ( 白輝度 ) が測定された時刻からその半値が測定された時刻までの時間が短いほど、液晶表示パネルに設けられた保護膜の残像緩和特性が良いものと評価される。

#### 【 0076 】

膜厚 0 nm , 10 nm , 20 nm , 30 nm の保護膜 ( 非晶質の窒化珪素膜 ) 8 a を夫々有する 4 種類の液晶表示装置の評価は、1 種類毎に 2 台の液晶表示パネルを用意して行った。

#### 【 0077 】

まず、上記保護膜 8 a の膜厚が 0 nm の ( 保護膜 8 a がない ) 液晶表示パネル 2 台の残像

10

20

30

40

50

緩和時間は、夫々 125 秒、114 秒であった。次に、保護膜 8a の膜厚が 10 nm の液晶表示パネル 2 台の残像緩和時間は、夫々 105 秒と 92 秒であり、若干の効果は確認できた。

#### 【 0078 】

さらに、保護膜 8a の膜厚が 20 nm の液晶表示パネル 2 台、及び保護膜 8a の膜厚が 30 nm の液晶表示パネル 2 台のいずれも、略 0 秒の残像緩和時間を示し、その残像緩和特性の顕著な向上を証した。なお、略 0 秒の残像緩和時間とは、輝度の最大値が測定された時刻からこの最大輝度の半値が測定された時刻までに要した時間が 1 秒未満と非常に短く、本発明者らによる測定手法では実質的に測定不能であることを意味する。いずれにしても、保護膜 8a を保護膜 8b 上に形成することによる残像緩和特性の大幅な改善が確認できた。

#### 【 0079 】

##### 〔評価方法 B 〕

図 1 及び図 2 に示されるゲート電極 1a に直流 10 V を、ドレイン電極 2a に 3 ~ 4 V の範囲で変動する矩形波パターンの電圧を夫々印加し、対向電極 3a を接地電位に接続する。この状態で、さらにドレイン電極 2a へ直流 1 V を印加し、上記矩形波を 4 ~ 5 V の範囲で変動させる。このように、ドレイン電極 2a に印加される矩形の電圧波形を振幅の中心を上げたときに生じる輝度の時間変化（相対フリッカ）を測定する。具体的な測定手法として、例えば、上記評価方法 A と同様に液晶表示パネルの輝度モニタリングが適用できる。本評価方法では、上記直流成分をドレイン電極 2a に印加した時刻から液晶表示パネルの輝度の減衰を測定する。上述の如く、ドレイン電極 2a の電位に直流成分が加わることでも、保護膜 8 に余剰な電荷が発生し、これが保護膜 8 に残留することで表示画面から消したい画像が「残像」として表示画面に残る。相対フリッカ強度は、この表示画面に消すべき画像が生じる強度をも反映し、これを以って残像の評価を行うことができる。つまり相対フリッカ強度が早く 0 に落ちる液晶表示パネルほど、その残像緩和特性は良好と判断される。

#### 【 0080 】

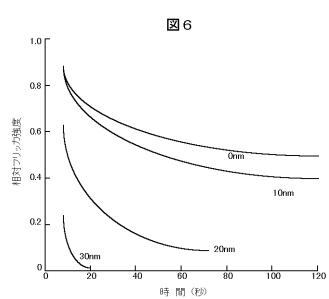

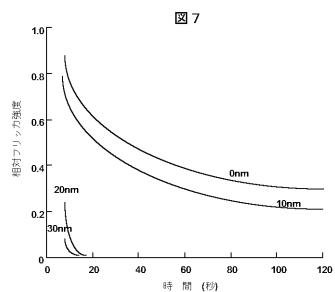

上述の評価方法 A と同様に、評価方法 B も膜厚 0 nm, 10 nm, 20 nm, 30 nm の保護膜（非晶質の窒化珪素膜）8a を夫々有する 4 種類の液晶表示装置（バックライト・ユニットを装着）を 1 種類につき 2 台用意して行った。測定は、液晶表示装置のバックライト・ユニットの輝度を  $25 \text{ Cd} / \text{m}^2$  (カンデラ) /  $\text{m}^2$  及び  $250 \text{ Cd} / \text{m}^2$  に夫々設定して行い、この 2 種類の実験結果を図 6 (バックライト輝度 =  $25 \text{ Cd} / \text{m}^2$ ) 及び図 7 (バックライト輝度 =  $250 \text{ Cd} / \text{m}^2$ ) に示す。

#### 【 0081 】

この評価結果からも、保護膜 8a を保護膜 8b 上に形成することによる液晶表示装置の残像緩和特性の改善が確認され、保護膜 8a を 20 nm 以上の厚さで形成したときに残像緩和特性が顕著に向上することが認められた。また、図 6 のグラフと図 7 のグラフとを比較すると、バックライト輝度を高く設定して測定された図 7 のグラフのいずれもが、図 6 に示される夫々より良好な残像緩和特性を示す。このような傾向に対し、本発明者らは保護膜 8、特に本発明により新たに TFT 基板上に形成した保護膜（非晶質窒化珪素膜）8a に生じる光伝導（Photoconduction）が、保護膜 8 からの残留電荷の放出（放電）を促し、液晶表示装置における残像緩和を改善させたものと考察した。

#### 【 0082 】

##### 《保護膜の特徴》

上述の如く、本発明による液晶表示装置の一例は、新規な構造を有する保護膜を採用することにより、良好な残像緩和特性を示す。そこで、この保護膜の構造的な特徴及び物理的な性質について、種々の観点から以下に説明する。

#### 【 0083 】

上述の新規な保護膜は、本発明の第 1 実施例による液晶表示装置の TFT 基板製造工程の工程 9 で説明したように、2 層の非晶質の窒化珪素膜から構成される。これら 2 層の窒化

10

20

30

40

50

珪素膜を、上述した蒸着装置により膜厚 200 nm の実験サンプルとして作製し、夫々の物理的な性質及び化学的な組成を、表 2 に纏めた。

表 2

| パラメータ                                      | 窒化珪素膜 8 b            | 窒化珪素膜 8 a            |

|--------------------------------------------|----------------------|----------------------|

| Si <sub>x</sub> N <sub>y</sub> 組成比 (y/x 比) | 1. 28                | 0. 91                |

| 比誘電率                                       | 6. 5                 | 9. 4                 |

| 暗抵抗率 (単位: Ω cm)                            | 3 × 10 <sup>15</sup> | 3 × 10 <sup>13</sup> |

| 光抵抗率 (単位: Ω cm)                            | 1 × 10 <sup>15</sup> | 1 × 10 <sup>9</sup>  |

10

## 【0084】

表 2 において、暗抵抗率 (Dark Resistivity) は暗室で測定された非晶質の窒化珪素膜の抵抗率で、セレン光電池やこれに類する光電装置の暗抵抗と同様な条件で測定される。一方、光抵抗率 (Photo Resistivity) は、非晶質の窒化珪素膜に光を照射して、その内部に光伝導を発生させたときの窒化珪素膜の抵抗率である。光抵抗率は、夫々の窒化珪素膜に 500 kLx (キロ・ルクス) の白色光を照射して測定した。なお、1Lx (ルクス) とは、1m<sup>2</sup> の面に 1Lm (ルーメン) の光束が入射したときの照度を表わし、1Lx = 1Lm / m<sup>2</sup> なる式で表わされる関係にある。また、F [Lm] の光束を立体角 θ に放出する点光源の光度 I は、先述の 1Cd (カンデラ) なる単位で表わされ、I [Cd] = dF / dθ ( = F / θ : θ が微小な場合) なる関係にある。参考までに、全ての方向の光度 I が均一な均等点光源から、その全立体角 4π に放射される全光束 F は、F = 4πI [Lm] として表わされる。透過型の液晶表示装置ではバックライト・ユニットやフロントライト・ユニット等の照明装置からの光を液晶表示パネルの正面に入射させ、また反射型の液晶表示装置ではその外側から液晶表示パネルの正面に入射する光を液晶表示パネルの内部で反射させて当該正面から出射させるため、いずれの場合も保護膜は相当量の光に曝される。本発明者らは、この事実と本発明による液晶表示装置の「残像抑止に対する効果」にて先述した知見と併せて検討し、図 2 に示される窒化珪素膜 8 b の上 (液晶層側) に新たに窒化珪素膜 8 a を形成したことによる液晶表示装置の残像低減には、この新たな窒化珪素膜 8 a に生じる光伝導が寄与する可能性を考えた。

20

## 【0085】

本発明者らは、この可能性をプラズマ CVD 法による成長条件を変えて作製した数種類の窒化珪素膜 8 a から検討した。まず、窒化珪素膜 8 a を窒化珪素膜 8 b 上に形成する工程で、蒸着装置内にプラズマを発生させる高周波電力 (周波数帯からして、Radio Frequency Power, 又は RF 電力とも呼ばれる) を変え、数種類の液晶表示装置を作製した。この高周波電力は、図 3 に示す蒸着装置において、電極 ELC からプラズマに印加される。

30

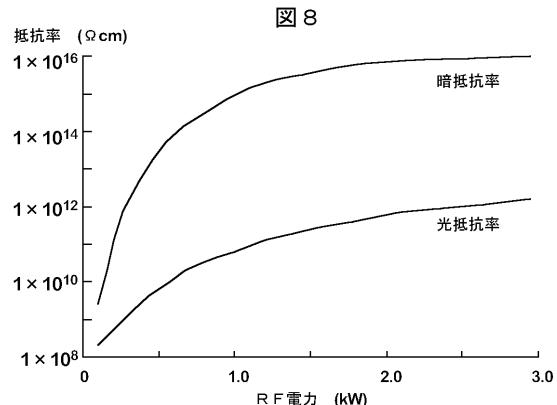

## 【0086】

これらの液晶表示装置の残像緩和特性を比較した結果、窒化珪素膜 8 a 成長時の高周波電力を小さくする程、この特性が向上する結果を得た。更に、窒化珪素膜 8 a のテスト・サンプルを、同様にプラズマに印加される高周波電力を変えて、数種類作製し、その暗抵抗率及び光抵抗率を調べ、図 8 に示す結果を得た。液晶表示装置の残像緩和特性に対応するように、高周波電力を窒化珪素膜 8 b の成長時に印加するそれより低減するにつれて、これらの抵抗率も減少することが判明した。

40

## 【0087】

次に、上述の結果に基づいて高周波電力を 350 W に設定し、窒化珪素膜 8 a の成長時に CVD 装置 (蒸着装置) へ供給する SiH<sub>4</sub> 及び NH<sub>3</sub> の原料ガス流量比 (NH<sub>3</sub> 流量 /

50

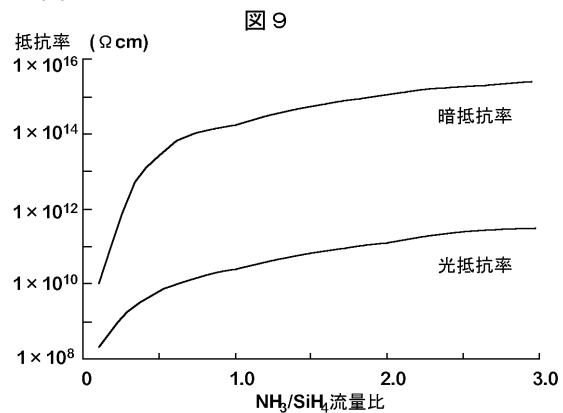

$\text{SiH}_4$  流量)を変え、数種類の窒化珪素膜 8 a のテストサンプルを作製した。このテストサンプルの暗抵抗率及び光抵抗率を上述の要領で測定し、これと上記原料ガス流量比との相関をプロットして、図 9 のグラフに示す結果を得た。また、テストサンプル同様に原料ガス流量比を夫々変えて窒化珪素膜 8 a を窒化珪素膜 8 b 上に形成して数種類の液晶表示装置を作製し、その残像緩和特性を調べた。その結果、窒化珪素膜 8 a の成長期間において原料ガス流量比を小さくする ( $\text{NH}_3$  流量に対する  $\text{SiH}_4$  流量を増やす) ほど、この窒化珪素膜 8 a を保護膜の一つとして備えた液晶表示装置の表示画面から残像は速やかに消えた。また、窒化珪素膜 8 a の抵抗率を制御する上で、上記原料ガス流量比 ( $\text{NH}_3$  流量 /  $\text{SiH}_4$  流量) を 1.0 以下、即ち、 $\text{SiH}_4$  流量を  $\text{NH}_3$  流量以上に設定して窒化珪素膜 8 a を作製することが望ましいという例も見出した。 10

#### 【0088】

以上、プラズマ CVD 法による成長条件を変えて作製した窒化珪素膜 8 a のテストサンプルの抵抗率とこれらの窒化珪素膜 8 a を夫々備えた液晶表示装置の残像緩和特性との関係を纏めたとき、窒化珪素膜 8 a の抵抗率と液晶層の抵抗率との関係が残像緩和特性を左右する可能性を見出した。液晶の抵抗率は、液晶表示装置の種類にもよるが、概ね  $1 \times 10^{11} \sim 1 \times 10^{13}$  cm の範囲にある。一方、図 8、図 9 の光抵抗率に着眼すれば、液晶表示装置の照明ユニットやこの外部から入射する光に曝される窒化珪素膜 8 a 内には、少なからずも光伝導が生じ、その抵抗率が液晶層より低くなりえると考えられる。 20

#### 【0089】

例えば、表 2 の窒化珪素膜 8 b のみからなる保護膜を備えた液晶表示装置と、この窒化珪素膜 8 b の液晶層側に窒化珪素膜 8 a を追加した保護膜を備えた液晶表示装置とを比べてみると、前者では窒化珪素膜 8 b の液晶層側の面に生じた電荷は液晶層の導電性を以っても排出されず、この面に永く留まるのに対し、後者では窒化珪素膜 8 b の液晶層側の面に接した窒化珪素膜 8 a の導電性により速やかに排出されると結論できる。従って、窒化珪素膜に限らず、保護膜を構成する少なくとも 2 種類の材料層は、アクティブ素子側の材料層 (第 1 実施例では窒化珪素膜 8 b) に対して液晶層側の材料層の抵抗率、例えば上述の光抵抗率を低くすることが一つの目安となる。しかしながら、液晶層側の材料層の抵抗率が低すぎると先述の日本特許 2938521 号の例で指摘した弊害も生じる。そこで、保護膜を構成する液晶層側の材料層 (換言すれば、別の保護膜材料層によりアクティブ素子又はスイッチング素子から離間されている層) を作製する上での目安を次のように提示する。 30

#### 【0090】

その目安の一つは、この材料層の抵抗率を半導体のそれより大きくすることである。本発明者らの検討によれば、日本特許 2938521 号に記載される非晶質珪素膜は、 $10^0 \sim 10^{11}$  cm の暗抵抗率と  $10^6 \sim 10^7$  cm の光抵抗率 (500 kLx の白色光照射に対する) を示す。これに対し、実験的な知見に因れば、500 kLx の白色光照射に対する液晶層側材料層の抵抗率 (光抵抗率) を  $1 \times 10^8$  cm 以上とすることで上述の弊害は回避できる。また、この液晶層側材料層の暗抵抗率は、 $1 \times 10^{11}$  cm より大きくしてもよい。 40

#### 【0091】

別の目安としては、この液晶層側の材料層を絶縁体又はそれに近い性質に保つことが望ましいとする観点から、その比誘電率に着目する。液晶層側に形成される保護膜材料層の比誘電率は、表 2 の窒化珪素膜 8 b (6.5) より大きく且つ非晶質珪素膜 (10 ~ 13 の範囲にある) より低くすることが推奨される。例えば、液晶層側の材料層の比誘電率を 7 以上且つ 10 未満の範囲に設定し、その導電性をアクティブ素子側に形成される保護膜材料層より高く且つ半導体より低くするとよい。

#### 【0092】

また、上記第 1 実施例で検討した窒化珪素膜で液晶層側の保護膜材料層を構成する場合、その組成が  $\text{Si}_x \text{N}_y \text{X}_z$  (X はその他の構成元素の総称) なる化学式において、 $0 < y / x \leq 1.0$  なる条件を満たすことが望ましい。ここで珪素、窒素以外の元素の総称とし 50

てあげた  $X$  は存在しなくとも ( $z = 0$  でも)、本発明の実施を阻むものでない。化学量論的に窒化珪素の組成は、 $\text{Si}_3\text{N}_4$  (上記  $y / x$  比にして約 1.3) と表記されるが、これに比べて本発明による液晶表示装置で液晶層側に追加される新たな保護膜の組成は、 $\text{Si}$  - リッチとなる。保護膜を構成する窒化珪素膜は、そのアクティブ素子 (スイッチング素子) 側に形成される材料層の絶縁性を高める上で、その液晶層側の材料層を含めて非晶質膜として形成することが望ましい。上記  $\text{Si}_x\text{N}_y\text{X}_z$  ( $X$  はその他の構成元素の総称) の絶縁性からみた望ましき組成範囲の一例は、 $0.5 < y / x < 1.0$  である。

#### 【0093】

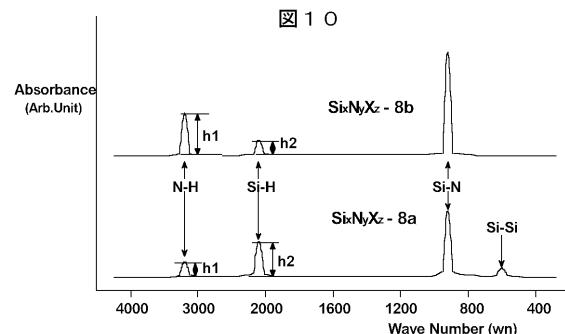

なお、本発明者らが窒化珪素で保護膜を作製した実験で得た知見に拠れば、そのスイッチング素子側の層及び液晶層側の層の各組成における  $N / Si$  比率は、上述の原料ガス流量比 ( $\text{NH}_3$  流量 /  $\text{SiH}_4$  流量の比) で制御でき、ほぼ一致しているとも見做せた。また、図 2 に例示される保護膜 8 を構成する窒化珪素膜 8a, 8b の組成は、フーリエ変換赤外分光法 (FT-IR 法) やラザフォード後方散乱法 (RBS 法) 等の分析手法で同定することができる。図 10 には、FT-IR 法による窒化珪素膜 8a, 8b の分析結果 (スペクトル) の一例を並べて示す。これらのスペクトルの横軸は保護膜に照射される赤外光の波数 (単位:  $\text{wn}$  (Wave Number),  $1 \text{wn} = 1 \text{cm}^{-1}$ ) を、縦軸は保護膜による赤外光の吸収度 (任意単位) を表す。窒化珪素膜 8b のスペクトル ( $\text{SiN}-8b$ ) 及び窒化珪素膜 8a のスペクトル ( $\text{SiN}-8a$ ) のいずれにおいても、 $3200 \text{wn}$  近傍に窒素と水素との結合 (N-H) による吸収が、 $2000 \sim 2100 \text{wn}$  にかけて珪素と水素との結合 (Si-H) による吸収が、 $900 \text{wn}$  近傍に珪素と窒素との結合 (Si-N) による吸収が、夫々観測される。しかしながら、窒化珪素膜 8a のスペクトル ( $\text{SiN}-8a$ )においては、窒化珪素膜 8b のスペクトル ( $\text{SiN}-8b$ ) に比べて、下記の如き特徴の少なくとも一つが見受けられる。

#### 【0094】

特徴 1:  $900 \text{wn}$  近傍の珪素 - 窒素結合の吸収度が小さい。

#### 【0095】

特徴 2:  $3200 \text{wn}$  近傍の窒素 - 水素結合の吸収度  $h_1$  に対する  $2000 \sim 2100 \text{wn}$  の珪素 - 水素結合の吸収度  $h_2$  の比率が増え、そのピーク高さが同じ又は逆転する ( $h_1 < h_2$  となる) こともある。

#### 【0096】

特徴 3:  $600 \text{wn}$  近傍に珪素 - 硅素結合 (Si-Si) の赤外光吸収のピークが生じる。

#### 【0097】

なお、図 10において窒化珪素膜 8b のスペクトル ( $\text{SiN}-8b$ ) と窒化珪素膜 8a のスペクトル ( $\text{SiN}-8a$ ) とを並べて表示する都合上、前者のベースラインを後者のそれより縦軸方向にずらしている。また、例示される窒化珪素膜 8a の抵抗率は、窒化珪素膜 8b の  $1 \times 10^{15} \text{ cm}$  より少なくとも 2 衍程度低かった。

#### 【0098】

抵抗率、比誘電率、及び窒化珪素膜の 3 つの観点で論じた本発明による第 1 実施例の液晶表示装置の保護膜を、これが形成される基板 (本実施例では TFT 基板 11) の液晶層側、即ち、基板正面に形成された薄膜構造の液晶層に面する最上面から眺めると、その特徴は以下の如く記される。

#### 【0099】

まず、抵抗率の観点において、上記保護膜は、その上記液晶層に対向する面への光照射によりその抵抗率が該光照射を行わないとときの抵抗率の  $1 / 100$  以下に減少する特徴を有する。この特徴は、例えば保護膜上面に抵抗測定用のプローブを接触させ、この上面に  $500 \text{kLx}$  又はそれ以上の照度の光を照射して確認できる。この保護膜上面の抵抗率の一例は、これに光を照射しないとき (例えば、暗室内で)  $1 \times 10^{13} \text{ cm} \sim 1 \times 10^{15} \text{ cm} \cdot \text{cm}$  の範囲にあり、これに  $500 \text{kLx}$  又はそれ以上の照度の光を照射したときに  $1 \times 10^9 \text{ cm} \cdot \text{cm} \sim 1 \times 10^{11} \text{ cm} \cdot \text{cm}$  の範囲にある。

10

20

30

40

50

## 【0100】

次に、比誘電率の観点において、上記保護膜の上記液晶層に対向する面（例えば、保護膜の最上面）は7.5以上の比誘電率を示す。更に本発明による液晶表示装置の望ましき一例において、この比誘電率は9.0以上の値を示す。

## 【0101】

最後に、上記保護膜を少なくとも珪素と窒素を含む材料( $\text{Si}_x\text{N}_y\text{X}_z$ , Xはその他の構成元素の総称)で形成する観点で、上記保護膜の上記液晶層に対向する面（例えば、保護膜の最上面）の珪素に対する窒素の組成比( $y/x$ )は0より大きく且つ1.0以下の範囲にある。換言すれば、この保護膜はその液晶側において窒化珪素： $\text{Si}_3\text{N}_4$ の化学量論比より珪素の含有比率の高い材料で形成される。

## 【0102】

以上に記した基板の上面から捉えた上記保護膜の特徴のいずれもこの保護膜がスイッチング素子に接している特徴を兼ね備え、その保護膜が液晶層側で低い抵抗率を示しながらもスイッチング素子側における短絡や電荷（電子や正孔）の漏洩を充分に抑えている。液晶表示装置の製造ラインにおいて、先述の本発明による保護膜の断面構造の特徴を確認することは言わば製品の破壊検査となる。しかしながら、TFT基板上に本発明による保護膜を形成し、これに覆われるスイッチング素子の動作を確認した後、ここで述べた本発明による保護膜の最上面（液晶層側の面）から記述される特徴の少なくとも一つを確認することにより、本発明による液晶表示装置の品質をその製造過程にて非破壊検査で管理できる。

## 【0103】

以上、抵抗率、比誘電率、及び窒化珪素膜の種々の観点で本発明による第1実施例の液晶表示装置に採用した保護膜の特徴を論じたが、この保護膜を上記液晶層側の材料層（以下、上側層と記す）及び上記スイッチング素子側の材料層（以下、下側層と記す）に他の材料層を加えた3層以上の積層構造として形成しても本発明の実施を阻むものではない。例えば、上側層と下側層の間に双方とも異なる材料層を挟んで保護膜を構成しても、下側層よりスイッチング素子側に下側層と異なる材料層を形成して保護膜を構成してもよい。また、上側層は保護膜の最上層として形成し且つこの保護膜を構成する他の材料層より抵抗率を十分小さくすることが上記液晶表示装置の残像緩和特性を向上する上で理想的であるがさせることができ、この上側層と配向膜との間に上側層と異なる材料層を形成して保護膜を構成しても本発明の効果を損なうものではない。要は、上述の特徴の少なくとも一つを満たす下側層と上側層とを基板正面に対してこの順に積層して保護膜が構成されることにある。次に、上記上側層並びに上記下側層のみならず、それ以外の他の層を加えて保護膜を構成する場合を含めて、保護膜全体における上側層の種々の特徴を個別に列挙する。

## 【0104】

例えば、上側層の暗抵抗率を、保護膜を構成する他の層の暗抵抗率と比較して1/100以下に抑えることが望ましい。換言すれば、保護膜に含まれる上側層以外の材料層で最も低い暗抵抗率を示す層に対して、その暗抵抗率より少なくとも2桁低い暗抵抗率を示すように上側層を成長させることが望ましい。

## 【0105】

別の一例では、上側層又はこれと保護膜を構成する下側層以外の層を、その光抵抗率がその暗抵抗率の1/100倍以下となるように形成することが望ましい。

## 【0106】

さらに別の一例では、上側層の膜厚又はこれと下側層上に形成される上側層以外の少なくとも1層とを併せた膜厚を、保護膜全体の膜厚の半分以下にすることが望ましい。このような保護膜の下側層より液晶層側（又は、配向膜側）に形成された少なくとも1層の膜厚は、10nm以上にするとなおよい。

## 【0107】

さらに別の一例では、保護膜の下側層より液晶層側（又は、配向膜側）に形成された少なくとも1層が、この液晶層の抵抗率より低い光抵抗率を示すとよく、加えて当該液晶の抵

10

20

30

40

50

抗率より低い暗抵抗率を示すとなおよい。

【0108】

以上に述べた保護膜は、これを構成する各材料層を上述のプラズマCVD法のみならず、他の化学気相蒸着法で形成してもよい。また、いずれの化学気相蒸着法においても原料ガスの供給量や蒸着条件を適宜変えて連続的に異なる化学組成の材料層を積層すると液晶表示装置の作製効率も上がる。

【0109】

プラズマCVD装置を用いた化学気相蒸着法で保護膜を作製する場合、その反応室（図3に例示される筐体CHMB）に供給される原料ガス（ $Si_xN_y$ 膜の場合、 $SiH_4$ ガスと $NH_3$ ガス）の全流量に対する高周波電力（プラズマに印加される）を成膜すべき層毎に応じて変えると良い。この物理量は、プラズマに印加される高周波電力を原料ガスの流量和で除した所謂「単位ガス流量当りのRF電力」として定義され、上述の上側層成長時における単位ガス流量当りのRF電力値は下側層成長時におけるそれに比べて小さくするといい。絶縁性が優先される下側層は、例えば $1 \times 10^{15}$  cm又はそれ以上の抵抗率を示すように形成されるが、上側層はZnSやGaAsのような半絶縁性半導体に近い抵抗率を示すように形成されることが推奨され、その抵抗率は下側層のそれから2桁程度又はそれ以上低い値にすることが望まれる。このような2種類の材料層を連続的に積層する場合、下側層と上側層との界面付近における蒸着条件制御が保護膜全体の性質を決める。上述の如く原料ガスの全流量及びプラズマに印加する電力の少なくとも一つを適切に制御することにより、上記界面付近での蒸着条件を確実に切り替えられ、上側層の抵抗率を上述の如き所望の範囲に設定できる。特に上側層の厚みを下側層のそれより薄くする場合、この効果は大きい。

【0110】

さらに、上記保護膜をスイッチング素子及びブラック・マトリクスの少なくとも一方の上に形成するとよく、例えば、スイッチング素子やブラック・マトリクス、さらにはカラーフィルタのいずれかにより基板主面上に生じる起伏が上記下側層で均される。従って、配向膜や電極膜を保護膜上に形成するとき、これらの上面に対する液晶層中の液晶分子の配向方向が確実に制御できる。スイッチング素子としては、第1実施例に示した薄膜トランジスタのみならず、薄膜ダイオードを用いてもよい。また、薄膜トランジスタは、図2に示すゲート電極上に半導体膜からなるチャネル層を形成したボトム・ゲート構造のみならず、半導体膜からなるチャネル層上にゲート電極を設けたトップ・ゲート構造としてもよく、また、この半導体膜は上述の非晶質の珪素薄膜に限らず、多結晶の珪素薄膜としても、さらにこの多結晶の結晶粒の寸法（Grain Size）を大きくした擬似単結晶（Pseudo Single Crystal）の珪素薄膜としても本発明の実施を阻むものでない。

【0111】

一方、上記保護膜は画素電極又はこれと対向電極との上部に形成すると、その効果もより顕著になり、例えば上述の面内スイッチングのみならず、端電界スイッチング（Fringe Field Switching）により液晶を駆動する液晶表示装置に適用しても、その効果の恩恵を受けられる。

【0112】

また、保護膜の下側層より液晶層側に形成される少なくとも1層（上記上側層等）に生じる光伝導に着眼すれば、液晶表示パネルを照射する光源装置（バックライト・ユニット又はフロントライト・ユニットと呼ばれる照明装置）を備えた液晶表示装置に適用することにより、その残像緩和特性を当該光源装置の点灯動作により上げることができる。

【0113】

以上に述べた本発明による液晶表示装置に備えられた保護膜の変形例のいくつかは、第2実施例及び第3実施例にて紹介される。

《第2実施例》

本発明による液晶表示装置の第2実施例として、上述の保護膜を備えたツイスティッド・ネマティック（Twisted Nematic, TNとも記す）型の液晶表示装置を図11及び図12

10

20

30

40

50

を主に参照して説明する。本実施例の液晶表示装置は、互いの正面を離間させて対向する一対の基板（図4に示す如く、これらの基板11, 12の正面間に液晶層15が封入される）の一方にスイッチング素子を備えた画素電極を、他方に対向電極を夫々設ける構造において、第1実施例の液晶表示装置の構造と異なる。しかしながら、本実施例においてもスイッチング素子と画素電極とが設けられた上記一対の基板の一方を便宜的にTFT基板と呼ぶ。また、この一対の基板の他方（対向電極が設けられた基板）には後述の如く、カラーフィルタも設けられることから便宜的にカラーフィルタ基板と呼ぶ。

#### 【01114】

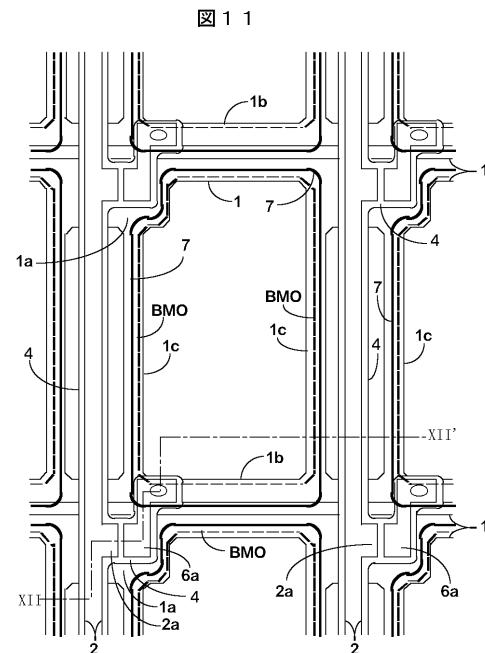

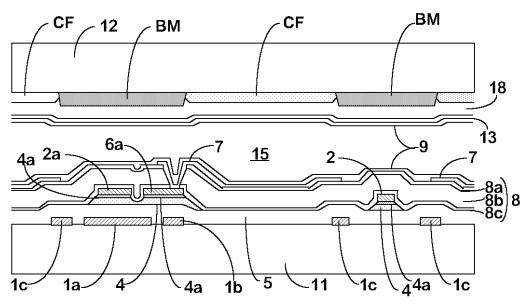

図11は、本実施例の液晶表示装置に用いられるTFT基板11の正面（液晶層に面する）に形成された複数の画素の一つを拡大して示す平面図であり、図12は図11の一点鎖線XII-XII'沿いに液晶表示パネル（液晶層15及びカラーフィルタ基板12も含む）を切断したときの断面図である。

10

#### 【01115】

図11は、図の下側に示された走査信号線1の一部分として形成されたゲート電極1a、このゲート電極1aを覆う半導体層（チャネル層）4、図の左側に示された映像信号線2から分岐したドレイン電極2a、及び半導体層4上でドレイン電極2aの一端と離間し且つ対向するように形成されたソース電極6aを備えた薄膜トランジスタTFTと、このソース電極6aに接続された画素電極7とを有する画素を示す。画素電極7は、図12の如く、保護膜8上に配置されるため、第1実施例のそれ（6）とは異なる参照番号で表わす。ソース6a電極が上記クロム薄膜等の金属膜又はモリブデン（Mo）-アルミニウム（Al）薄膜等の合金膜で形成される一方、画素電極7はインジウム-錫-酸化物（ITO）やインジウム-亜鉛-酸化物（IZO）に代表される光透過率の高い酸化物導電膜で形成される。ソース電極6aは、映像信号線2やドレイン電極2aとともに同じ材料又は同じプロセスで形成しても良く、また、映像信号線2に許容される抵抗率によっては、ソース電極6a、映像信号線2、及びドレイン電極2aを上記酸化物導電膜で形成しても良い。各画素には、一対の走査信号線1と一対の映像信号線2とで囲まれた領域に広がる一つの画素電極7が設けられる。TFT基板11の正面には、このような複数の画素が二次元的に配置される。この画素配置の一例を、図11の中央に示された画素を囲む他の8つの画素（部分的に描かれる）により示す。

20

#### 【01116】

30

一方、カラーフィルタ基板12上には図12に示される如く、基板正面にブラック・マトリクスBM及びカラーフィルタCFが形成され、これらを覆うように保護膜18が形成される。この保護膜18は、 $Si_xN_y$  ( $1.0 < y/x$ )の化学式で表わされる窒化珪素膜で形成され、TFT基板11側に形成される保護膜8の下側層8bと同様に、その厚みを以て基板正面に生じた起伏を緩和する。この起伏とは、TFT基板11の正面に走査信号線1、映像信号線2、及び薄膜トランジスタを形成することにより、カラーフィルタ基板12の正面にブラックマトリクスBM、及びカラーフィルタCFを形成することにより、夫々生じる基板厚さ方向の段差（Steps）を指す。なお、本実施例において、TFT基板11側に形成される保護膜8の詳細は後述する。

#### 【01117】

40

保護膜18上には、対向電極13が形成される。対向電極13は、上述の画素電極7と同様に光透過率の高い酸化物導電膜（又はこれに類似する透明導電膜）からなり、液晶を挟んでTFT基板11に形成された複数の画素電極7に対向し得る広さを有する。即ち、画素毎にTFT基板11上に対向電極3aを設ける第1実施例の構造と異なり、本実施例の対向電極13は、少なくとも2画素、必要に応じては表示画面を構成する全画素に対し、1つの酸化物導電膜又は透明導電膜として形成される。本実施例の対向電極13は、TFT基板正面に配置する必要がないため、第1実施例のそれ（3a）とは異なる参照番号で表わす。対向電極13上には配向膜9が形成されるが、その詳細は第1実施例で述べたTFT基板11上に形成される配向膜9と略同じであるため、説明は省略する。

#### 【01118】

50

図11に示されるカラーフィルタ基板12側の唯一の構造物はブラック・マトリクスBMの開口の輪郭BMOである。破線で示されたブラック・マトリクス開口の輪郭BMO内には、図12の如くカラーフィルタCFが設けられる。ブラック・マトリクス開口の輪郭BMOの TFT 基板11正面への投影が画素電極7の輪郭内に収まるように、 TFT 基板11とカラーフィルタ基板12との位置を合わせ、またはカラーフィルタ基板12上のブラック・マトリクスBMに開口を形成することにより、画素電極7の周囲から液晶層への光の迷い込みが抑制される。

#### 【0119】

一方、 TFT 基板11の正面で走査信号線1やゲート電極1aと、映像信号線2、ソース電極6a、ドレイン電極2aとは、第1実施例と同様に絶縁膜(ゲート絶縁膜)5により基板の厚さ方向に隔てられる。基板11正面と絶縁膜5との間には、走査信号線1に沿って(図11のx方向に)延びる導電層1b及びこの導電層1bから映像信号線に沿いに1画素分隔でられた別の走査信号線1に夫々接合された導電層1cが形成されている。これらの導電層1b, 1cは、図11に示されるように導電層1cに接合される走査信号線1とともに1つの画素電極7の周縁に重なる。画素電極7の周縁と上記対向電極13との間には、画素電極7の周縁より内側の領域と対向電極13との間に生じる電界(液晶層の光透過率を制御するに好適な電界)に比べて不規則な電界(所謂、端電界:Fringe Field)が生じる。この端電界は、例えば液晶層の光透過率を最小にすべく画素電極7の電位を制御しても、その周縁沿いに光の漏洩をもたらす。

#### 【0120】

これに対し、上述の導電層1b, 1c及び走査信号線1からなる言わばループ構造は、絶縁膜5, 7を挟んで画素電極7の周縁に重なるため、端電場による光の漏洩を抑える。このような効果から、このループ構造をなす導電層及び走査信号線は、遮光膜又は遮光構造とも呼ばれる。図11に示される如く、このループ構造は画素電極7の映像信号線2の延伸方向(図11のy方向)に沿う両側に夫々設けられた一対の導電層1cを含む。また、このループ構造に含まれる走査信号線1は、これが重なる画素電極7に接続されるスイッチング素子の制御に関与しないもの、例えば、この画素電極7に映像信号線2沿いに隣接する別の画素電極7に接続されるスイッチング素子の制御に関与するものを選ぶ。

#### 【0121】

従って、本実施例による液晶表示装置(液晶表示パネル)に設けられた各画素において光が透過する領域は、画素電極7正面の縁に沿って重なるブラック・マトリクスの開口BMOと上記ループ状の遮光構造とにより規制される。

#### 【0122】

一方、本実施例による液晶表示装置の上記絶縁膜5と映像信号線2、ソース電極6a、並びにドレイン電極2aとの間に形成される半導体層4は、映像信号線2に沿って TFT 基板11の端部まで延び、その TFT 基板11正面内の輪郭内には上記映像信号線2、上記ソース電極6a、及び上記ドレイン電極2aが収まる。このような半導体層4の平面形状は、成型された映像信号線2、ソース電極6a、及びドレイン電極2aをマスクとして半導体層4をエッチングしたことに起因する。このような半導体層4の形状は、映像信号線2の断線や後述の保護膜8上に形成された導電膜(例えば、画素電極7)を保護膜に設けた開口を通して映像信号線2、ソース電極6a、又はドレイン電極2aに接続するときの導電膜の断線を防止するに好ましい。

#### 【0123】

本実施例による液晶表示装置においても、ボトム・ゲート型の薄膜トランジスタがスイッチング素子として設けられ、これを覆うように保護膜8が形成される。従って、本実施例による TFT 基板は、第1実施例の工程7に若干の相違はあるものの、その工程1乃至工程8を概ね踏襲して製造される。しかし、画素電極7を保護膜上に形成するため、第1実施例の工程8と工程9との間に次の工程が加わる。

#### 【0124】

工程8-1: 保護膜8上にフォト・レジストを形成し、後述の画素電極7が電気的に接続

10

20

30

40

50

するソース電極 6 a の一部分上に位置する保護膜 8 をフォトリソグラフ法により局所的に露光し、続いて現像により除去した。これにより、上記ソース電極 6 a の一部分上にはフォト・レジストの開口が形成される。次に、フォト・レジストの開口で露出された保護膜 8 をエッティングし、上記ソース電極 6 a の一部分を露出する開口 (Through Hole) を形成した。

【 0 1 2 5 】

工程 8 - 2 : 工程 8 - 1 で形成したフォト・レジストを薬液で除去した。

【 0 1 2 6 】

工程 8 - 3 : 保護膜 8 上にスパッタリング法で酸化インジウム (  $\text{In}_2\text{O}_3$  ) と酸化スズ (  $\text{SnO}_2$  ) からなる透明導電膜を 150 nm 形成した。透明導電膜は工程 8 - 1 で保護膜に設けた開口の内壁にも形成され、その底部において上記ソース電極 6 a の一部分に接触する。その後、透明導電膜上にフォト・レジストを塗布した。

10

【 0 1 2 7 】

工程 8 - 4 : 工程 8 - 3 にて形成したフォト・レジストを基板 1 1 主面内における画素電極 7 の配置に応じた遮光パターンを有するフォト・マスクを用いて露光し、画素電極 7 が形成される部分以外のフォト・レジストを現像により除去した。次に、このフォト・レジストで覆われない透明導電膜をエッティングし、図 1 1 や図 1 2 に示される如く、画素電極 7 間の透明導電膜を除去した。最後に、画素電極 7 上に残るフォト・レジストを薬液で除去した。

【 0 1 2 8 】

20

工程 8 - 4 が完了した段階で、第 1 実施例の工程 9 に準ずる工程を開始する。従って、本実施例において、配向膜 9 は保護膜 8 とこの上に形成された画素電極 7 との上部に形成される。

【 0 1 2 9 】

本実施例では、図 1 2 に示す如く、3 層の材料層 8 a , 8 b , 8 c をスイッチング素子からこの逆順に積層して保護膜 8 を構成している。3 層とも  $\text{Si}_x\text{N}_y\text{X}_z$  ( X はその他の構成元素の総称、いずれも  $y / x > 0$  ) なる化学式で記述される窒化珪素材料からなり、主たる構成元素として珪素 ( Si ) と窒素 ( N ) とを含む材料と述べても過言ではない。

【 0 1 3 0 】

30

このうち、材料層 8 a は上述した本発明による保護膜構造の上側層 ( 第 1 実施例の窒化珪素膜 8 a ) に、材料層 8 b はこの保護膜構造の下側層 ( 第 1 実施例の窒化珪素膜 8 b ) に夫々対応する。材料層 8 c は、上記工程 8 - 1 における保護膜 8 のエッティング条件を制御し、ソース電極 6 a 上に形成される開口の内壁を適度の斜面に成型する効果を奏する。材料層 8 c は材料層 8 b に比べて薄く形成され、その窒素 / 硅素の組成比 ( y / x ) は材料層 8 b より小さい所謂  $\text{Si}-\text{rich}$  な層である。材料層 8 a と材料層 8 c とを比較すると、材料層 8 c は材料層 8 a と同じ厚さか、これより薄くするとよい。また、材料層 8 c の窒素 / 硅素組成比 ( y / x ) は材料層 8 a のそれ以上とすることが望ましい。但し、材料層 8 a と材料層 8 c との関係については、厚さ及び組成に関するこれらの推奨された条件を外しても、本発明の実施を阻むには至らない。

【 0 1 3 1 】

40

図 1 2 に示す如く、材料層 8 c は離間されたドレイン電極 2 a とソース電極 6 a とに夫々接し、これらの電極を隔てる溝 ( 半導体層 4 に到る ) を跨ぐ。しかしながら、材料層 8 c によるドレイン電極 2 a とソース電極 6 a との短絡は無視できると述べても過言でない。その理由は、材料層 8 c の抵抗率がドレイン電極 2 a とソース電極 6 a とを隔てる溝が到達する半導体層 4 ( 薄膜トランジスタのチャネルとなる真性半導体層 ) に比べて充分に高く、また、これらの電極と接する部分における電気抵抗も充分に高いことにある。従って、上述の化学式 :  $\text{Si}_x\text{N}_y\text{X}_z$  における珪素、窒素以外の構成元素として導電性の高い遷移金属が珪素や窒素の量に比べて顕著に増えない限り、ドレイン電極 2 a とソース電極 6 a とは材料層 8 c にて電気的に略分離される。

【 0 1 3 2 】

50

一方、材料層 8 b に比べて抵抗率の低い材料層 8 a 上には、インジウム - 錫 - 酸化物 (ITO) やインジウム - 亜鉛 - 酸化物 (IZO) 等の透明導電膜からなる画素電極 7 が形成される。従って、個々の画素電極 7 を構成する透明導電膜は上記工程 8 - 4 で画素毎にエッチングで分離されるも、材料層 8 b のような従来の保護膜に比べて顕著な光伝導を示す材料層 8 a で互いに導通されるように見える。しかしながら、材料層 8 a の抵抗率は材料層 8 b のそれより低いものの、液晶表示装置の画像表示動作に応じて個々の画素電極 7 に分配された電荷を、画素電極 7 間で再配分するには高い値に留まる。これは、インジウム - 錫 - 酸化物からなる画素電極 7 の例で、その抵抗率が  $1.7 \sim 3.0 \times 10^4 \cdot \text{cm}$  であることからも理解できる。よって、画素電極 7 が金属並みの抵抗率、即ち  $1 \times 10^3 \cdot \text{cm}$  を示せば、画像表示動作中の材料層 8 a による画素電極 7 間の電気的な短絡は無視できる。

#### 【0133】

その反面、材料層 8 a は特に液晶表示装置の画像表示動作を終了させた時点で独特な効果を発揮する。液晶表示装置の画像表示動作が終了する時点で、各画素に設けられたスイッチング素子（本実施例では薄膜トランジスタ）への走査信号の印加が打ち切られる。このため、画素電極 7 には画像表示動作の終了直前に取り込んだ映像信号に相当する電荷が残留する。この残留電荷を画素電極 7 から除去して液晶表示装置の表示画面から残像を消す試みは、液晶表示装置の駆動方法の観点からなされているが、十分な効果を得るに至らない。これに対し、本実施例の如く、従来の保護膜より抵抗率の低い材料層 8 a と画素電極 7 とを接合させると、画素電極 7 内の残留電荷の少なくとも一部を材料層 8 a に逃すことができる。

#### 【0134】

この材料層 8 a の効果は、従来の保護膜との比較により以下の如く説明できる。従来の保護膜では残留電荷を画素電極 7 から逃がすには抵抗率が高すぎ、その結果、画素電極 7 の残留電荷はスイッチング素子のチャネルを通して映像信号線 2 へ徐々に漏洩して画素電極 7 から排出されるのみであった。このため、液晶表示装置の画像表示動作終了後も、その画素電極 7 には相当量の電荷が永らく残り、表示画面に液晶表示装置のユーザが認識できる程度の残像を表示させた。これに対して、本実施例の材料層 8 a は液晶表示パネルの液晶層に対向する面から電荷を短時間で排出しきれないと想定しても、特定の画素電極 7 に電荷が局在し続ける状態を短時間で解消することは画素電極 7 と材料層 8 a との微弱な導通が画素電極 7 内の残留電荷を材料層 8 a に逃していくという上述の説明から明らかである。即ち、液晶表示装置の画素電極 7 間における残留電荷量の差がユーザにその表示画面の残像を認識させると考えれば、本実施例の液晶表示装置における画素電極 7 の残留電荷の材料層 8 a への漏洩が画素電極 7 間の残留電荷量の差を縮め、その表示画面の残像を抑制する効果が得られることが理解できる。

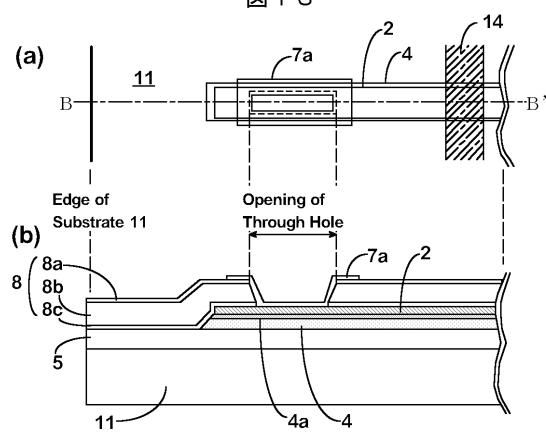

#### 【0135】

本実施例による液晶表示装置において、上述の材料層 8 a による画素電極からの残留電荷の排出に望ましい構造の一例として、図 13 に改善された映像信号線端子を示す。図 11 に示される映像信号線 2 は、この下に設けられた半導体層 4 (半導体層 4 a も含む) とともに TFT 基板 11 の端部まで延び、シール材 14 (図 4 参照) の外側に出たところで図 13 に示される端子 (映像信号線端子) が設けられる。図 13 (a) は、この端子の一つの平面構造を拡大して示す平面図であり、図 13 (b) は図 13 (a) の B - B' 線に沿った断面図 (但し、TFT 基板 11 及びその上の積層構造のみ) である。

#### 【0136】

この映像信号線端子は、上記工程 8 で作製した保護膜 8 の最上面から映像信号線 2 に到る開口を上記工程 8 - 1 及び 8 - 2 で上述の保護膜 8 の最上面からソース電極 6 a に到る開口とともに形成し、続いてこの開口の底部から保護膜 8 の最上面に延びる透明導電膜 7 a を上記工程 8 - 3 及び 8 - 4 で上述の画素電極 7 とともに作製する。従って、図 13 (a) 及び (b) に示す開口 (Opening of Through Hole) に形成された透明導電膜 7 a が映像信号線 2 に供給すべき映像信号を受ける端子となる。この端子には、図 15 に示す映

像信号駆動回路 H - D R V の出力端子が直接又はフレキシブル印刷回路基板を通して電気的に接続される。

【 0 1 3 7 】

図 13 ( a ) 及び ( b ) に示す開口に透明導電膜 7 a を設けることなく、この開口により露出された映像信号線 2 に映像信号駆動回路 H - D R V からの出力を接続する場合に比べ、この開口に透明導電膜 7 a を設ける端子構造では、映像信号駆動回路を構成する半導体素子の電極又はこの半導体素子からの出力信号を伝送する配線の端子との電気的な接続面積が広がり、また液晶表示パネル雰囲気による映像信号線 2 の導電層の腐食が防げる。

【 0 1 3 8 】

本実施例においては、この透明導電膜 7 a が保護膜 8 を構成する材料層 8 a とも接觸するため、上述の如くこれに漏洩する画素電極 7 の残留電荷をこの端子を通して液晶表示パネルの外部回路（図 13 の場合、映像信号駆動回路）にも逃がせられる。材料層 8 a 上に、これより抵抗率の高い別の材料層を設けても、開口の内壁（図 13 ( a ) に示される斜面）において材料層 8 a と透明導電膜 7 a が接觸するため、上述の効果を損なうものではない。但し、この別の材料層が材料層 8 b に近い絶縁性を示す場合は、その厚さを材料層 8 a より薄くして、材料層 8 a と画素電極 7 との間にトンネル電流が生じるようにするとよい。このような端子構造を、TFT 基板 11 又はこれを通して液晶表示パネルの所望の部分（例えば、カラーフィルタ基板 12 に設けられた共通電極 13 ）に基準電圧又は接地電位を印加する端子として設けられると、その効果は更に顕著となる。なお、このような端子構造が映像信号駆動回路 H - D R V から映像信号線 2 への信号供給に支障を来さないことは、この材料層 8 a に画素電極 7 を接觸させても画像表示動作に支障を及ぼさない上述の説明から明らかである。また、保護膜 8 の最上面から絶縁膜 5 を通して走査信号線 1 に到る開口を形成し、この開口の底部から保護膜 8 の最上面へ延びる透明導電膜を形成して走査信号線端子を設けても、上述の映像信号線端子と同様な効果が得られる。

【 0 1 3 9 】

図 13 ( a ) 及び ( b ) に示す端子構造は、第 1 実施例で述べた面内スイッチング型の液晶表示装置にも適用できる。この場合、上記工程 8 - 1 乃至 8 - 4 を上記工程 9 の後に行うとよい。また、フォトリソグラフィを用いた保護膜 8 の開口形成工程においては、TFT 基板 11 主面の略全域に亘って保護膜 8 上面にフォト・レジストを塗布することが推奨されるが、このフォトレジストの露光及び現像は TFT 基板 11 の周縁部に限定して施してもよい。

【 0 1 4 0 】

なお、本明細書に記される透明導電膜とは、液晶層から出射される光をガラス、プラスチックのような光透過率の高い材料からなる基板に伝播させるに十分な光透過率を有する導電膜を便宜的に表し、この導電膜がこれに入射する光を吸収する特性を有することを排除するものではない。また、本実施例では、TFT 基板に対向する基板をカラーフィルタ基板と名付けたが、カラーフィルタを画素電極 7 上に電着等の技術を用いて形成しても本発明の実施を阻むものでなく、このような実施形態においては上述のカラーフィルタ基板は TFT 基板に対向する対向基板と言い替えられる。さらに、本実施例でスイッチング素子として用いた薄膜トランジスタは、MIM ( Metal-Insulator-Metal ) 型の積層構造等を用いたダイオードに置き換えて本発明の実施に支障はなく、この場合を含めると、上記 TFT 基板（スイッチング素子が設けられる基板）は第 1 基板に、これに対向する基板（本実施例におけるカラーフィルタ基板）は第 2 基板に、夫々言い替えることができる。

《 第 3 実施例 》

本発明による液晶表示装置の第 3 実施例として、上述の保護膜を垂直配向型 ( Vertically Aligned type, VA 型とも記す ) の液晶表示装置に適用した例を図 14 の断面図を参照して説明する。

【 0 1 4 1 】

VA 型の液晶表示装置の詳細は、例えば特開 2000-122065 号公報に説明されているため、これに特徴的な液晶分子の配向形態やその電界に対する動作についての説明は

10

20

20

30

40

50

省き、これに特徴的な画素構造のみを以下に説明する。

【0142】

VA型の液晶表示装置では、スイッチング素子及びこれに接続される画素電極7を第1の基板11の主面上に、この画素電極とともに液晶層15に電界を形成する対向電極13を第2の基板12(液晶層15を挟んで第1の基板と対向する)の主面上に夫々形成する。このような構造は、上記第2実施例のTN型液晶表示装置に共通するが、VA型の液晶表示装置では、画素電極7及び対向電極13の少なくとも一方を画素内(図14においてはカラーフィルタCFに対向する部分)において互いに離間された複数の導電層として形成し、又はその液晶層15側の主面に少なくとも2種類の斜面を形成する構造に特徴を有する。このような電極構造は、1つの画素において液晶層15に対する印加方向が異なる少なくとも2種類の電界を発生させる。VA型の液晶表示装置の一つの特徴として、画素電極及び対向電極の少なくとも一方の電極が基板主面内において他方の電極と対向しない部分を画素内(例えば、ブラックマトリクスの開口やカラーフィルタ層の輪郭で規定される領域内)に有することが指摘できる。

【0143】

本実施例では、図14に示す如く画素電極7と対向電極13の各々を画素内で分割している。分割された画素電極7及び対向電極13の各部分は、図1に示す面内スイッチング型液晶表示装置の画素電極6や対向電極3aと同様に画素の周縁で導通される。また、画素電極7の各部分には右上方向に向いた第1斜面と左上方向に向いた第2斜面の所謂第1基板11主面に対する傾きの異なる2種類の斜面が形成される。これに対し、対向電極13の各部分には左下方向に向いた第1斜面と右下方向に向いた第2斜面の所謂第2基板12主面に対する傾きの異なる2種類の斜面が形成される。画素電極7の各部分と対向電極の各部分は、前者の第1斜面が後者の第1斜面に、前者の第2斜面が後者の第2斜面に夫々液晶層を挟んで対向するように配置される。これにより、画素電極7の第1斜面と対向電極13の第1斜面との間には電界E1が、画素電極7の第2斜面と対向電極13の第2斜面との間には電界E2が画素電極7への信号電圧印加により夫々生じる。しかし、電界E1による液晶分子の挙動(配向方向の変位)と電界E2による液晶分子の挙動は、液晶表示パネルの表示画像を観察する側(図14の上側)において互いに異なるよう見える。即ち、一つの画素に送られた映像信号に対して、この画素内に異なる液晶分子の配向状態が存在する。なお、図14に示された第1基板側及び第2基板側の配向膜9少なくとも一方、またはこれら双方を取り除いた方が、液晶分子を上述の如く配向できるという報告もある。

【0144】

液晶表示装置による画像表示の問題点として、表示画面の法線方向に対する角度(所謂視野角)の増大に対するコントラスト低下が上げられる。これは、或る画素から液晶層を通して出射される光の強度が視野角の増大により所望の値からずれることに起因する。しかしながら、本実施例の画素では、視野角に応じて電界E1により配向された液晶分子が伝搬する光の強度のずれを電界E2により配向された液晶分子が伝搬する光の強度が補償し、またその逆の補償をも行うことにより、コントラストの低下を防ぐ効果を奏する。

【0145】

本実施例のTFT基板では、トップ・ゲート構造の薄膜トランジスタが採用されている。この特徴は、第1の基板11主面に対して薄膜トランジスタのチャネルとなる半導体層4上にゲート電極1aを配置した構造にあり、第1実施例及び第2実施例で図示した薄膜トランジスタのそれとは絶縁膜5を挟んでゲート電極1aとソース電極6a及びドレイン電極2aとの配置が逆転している。本実施例のようなトップ・ゲート構造は、半導体層4の作製を他の配線層に比べて第1の基板の加工工程の始めに行う必要のある場合に好適で、例えば、非晶質の半導体層4にレーザ照射でアニーリングを施し、この半導体層4を多結晶又は単結晶に近い状態に変える上で推奨される。なお、本実施例の液晶表示装置において、薄膜トランジスタを第1実施例や第2実施例の如き、ボトム・ゲート構造に置換ても支障はない。

10

20

30

40

50

## 【0146】

画素電極7の上面に上述の如き斜面を形成するために、絶縁膜5上にはゲート電極1aとともに保持容量電極1dを設け、エッチャントを適宜選択することにより、その上面に傾斜を持たせる。このゲート電極1a及び保持容量電極を覆うように保護膜8を形成し、これに薄膜トランジスタのソース電極6a上面に到る開口を設け、この開口の底部のソース電極6上から保護膜8の上面に透明導電膜を延ばして画素電極7を形成する。本実施例による保護膜8を構成する材料層8a, 8bは第2実施例の材料層8a, 8bに夫々準じて形成され、また画素電極7も第2実施例のそれに準じて形成される。また、本実施例による保護膜8も、第2実施例で述べた様な効果を奏し、本実施例の走査信号線端子を図13(a), や図13(b)に示したように形成することにより、その効果も顕著となる。

10

## 【0147】

一方、本実施例の第2の基板にも第1の基板に設けた材料層8a, 8bと夫々同様な組成の材料層18a, 18bを積層した保護膜18が形成される。材料層18bに比べて抵抗率の低い材料層18aの上面(図14においては下面)には、上述の画素電極7と同様な透明導電膜からなる対向電極13が形成される。対向電極13の上面(図14においては下面)に斜面を形成する上で、液晶層15から光を第2基板12側に伝搬することを考慮し、その下地膜として上述の保持容量電極1dのような三角状の断面を有する金属膜又は合金膜を設けることは避けた。その代わり、透明導電膜をエッティングにより個々の対向電極13にパターン化した後、条件を変えてエッティングし直して斜面を形成した。

## 【0148】

20

本実施例のように、対向電極13を第2基板12上に互いに離間させて形成する場合も、本発明による保護膜18(オーバーコート膜とも呼ばれる)を採用することが望ましい。特に、液晶表示装置の対向電極の電位をフレーム毎、または所定数の走査信号線2を動作させる毎に変化させるコモン反転駆動において、第2の基板12側にも対向電極13間で残留電荷量が相違し得る。従って、残像の解消に当り、各対向電極13から残留電荷を排出し、対向電極13間に生じる電位差を解消することが肝心である。このように本発明による保護膜18をスイッチング素子が設けられた第1基板に対向する第2基板に形成することは、第2実施例で述べたTN型の液晶表示装置においても、画素群に応じて対向電極13を分割する場合に残像低減の効果を奏する。

## 【0149】

30

以上、第1乃至第3実施例において、本発明による保護膜構造を適用した液晶表示装置を説明したが、この保護膜構造の適用範囲はこれらの実施例の開示に限定されるものでない。また、従来の保護膜に対し、これより液晶層側に設けられる抵抗率の低い新たな保護膜は、その実施形態に応じて上述の如く窒化珪素層や材料層と呼ばれるに限らない。例えば、基板主面上に上述の材料層8bと材料層8aをこの順に積層する工程において、前者は第1保護膜層(8b)、後者は第2保護膜層(8a)とも称される。

## 【0150】

## 【発明の効果】

以上に述べた本発明による液晶表示装置は、その液晶表示パネル単体からこれを組込んだ液晶表示モジュール製品に到る全体に関し、次のような効果をもたらす。

40

## 【0151】

第1に、液晶表示装置の表示画面に生じる残像を緩和する特性が向上されるため、画像表示品質に優れた液晶表示装置及び液晶表示モジュールが提供できる。

## 【0152】

第2に、上述のような画像表示品質に優れた液晶表示装置(液晶表示パネル)を、新たな製造装置を導入することなく、既存の蒸着装置による成膜条件の制御のみでも製造できるため、その量産化プロセス条件が容易に設定でき、また、液晶表示装置及びこれを組込んだモジュールの製造歩留まりも高く維持できる。

## 【0153】

第3に、残像を解消するために液晶表示装置の駆動方式を複雑にする必要がなくなり、液

50

晶表示パネルに実装される駆動回路の簡素化、小型化が実現できる。

【0154】

第4に、バックライト、サイドライト(エッジライト)、フロントライトの形態に関わらず、光源装置を組合せた液晶表示パネルにおいて、これに照射される光により本発明による上述の保護膜表面(又はその近傍)に光伝導(光導電現象)が生じるため、表示画面から残像を瞬時に消すことも可能となる。

【図面の簡単な説明】

【図1】図1は、本発明の第1実施例による面内スイッチング型の液晶表示装置を構成する一対の基板の一方の主面上に形成された複数の画素の一つを拡大して示す平面図である。

【図2】図2は、図1の一点鎖線II-II'沿いにTFT基板を切断したときの断面図である。

【図3】図3は、プラズマCVDによる窒化珪素膜形成に用いた蒸着装置を模式的に示す断面図である。

【図4】図4は、液晶表示パネルの断面を模式的に示す説明図である。

【図5】図5は、液晶表示パネル21を組込んだ液晶表示装置の分解斜視図である。

【図6】図6は、本発明の実施例1の面内スイッチング型液晶表示装置の残像緩和特性を、バックライト輝度: 25 Cd/m<sup>2</sup>における相対フリッカ強度測定で評価した結果を示すグラフである。

【図7】図7は、本発明の実施例1の面内スイッチング型液晶表示装置の残像緩和特性を、バックライト輝度: 250 Cd/m<sup>2</sup>における相対フリッカ強度測定で評価した結果を示すグラフである。

【図8】図8は、本発明の実施例1による保護膜8の液晶層側に設けられる非晶質窒化珪素膜8aの成長条件(プラズマに印加される高周波電力)と暗抵抗率及び光抵抗率との相関を示すグラフである。

【図9】図9は、本発明の実施例1による保護膜8の液晶層側に設けられる非晶質窒化珪素膜8aの成長条件(原料ガスの供給比率)と暗抵抗率及び光抵抗率との相関を示すグラフである。

【図10】図10は、本発明の実施例1による保護膜8の液晶層側に設けられる非晶質窒化珪素膜8a(下側)及びスイッチング素子側に設けられる非晶質窒化珪素膜8b(上側)の赤外光吸収スペクトルの一例を示す図である。

【図11】図11は、本発明の第2実施例によるTN型の液晶表示装置(液晶表示パネル)に形成された複数の画素の一つを拡大して示す平面図である。

【図12】図12は、図11の一点鎖線XII-XII'沿いにTFT基板を切断したときの断面図である。

【図13】図13は、本発明の第2実施例による液晶表示装置に好適な映像信号線端子の一つを拡大して示し、図13(a)はその平面構造を示す平面図、図13(b)は図13(a)のB-B'線に沿った断面図である。

【図14】図14は、本発明の第3実施例によるVA型の液晶表示装置(液晶表示パネル)に形成された画素及びその近傍の断面図である。

【図15】図15は、薄膜トランジスタを用いた液晶表示装置の等価回路図である。

【符号の説明】

1...走査信号線, 1a...ゲート電極, 2...映像信号線, 2a...ドレイン電極, 3...基準電圧線, 3a...対向電極, 4...半導体層(i型), 5...絶縁膜(ゲート絶縁膜), 6...画素電極(保護膜より下に形成), 6a...ソース電極, 7...画素電極(保護膜上に形成), 8...保護膜, 8a...保護膜(上側層), 8b...保護膜(下側層), 9...配向膜, 11...基板(TFT基板), 12...基板(対向基板), 13...対向電極, 14...シール材, 15...液晶層, 18...保護膜, 18a...保護膜(上側層), 18b...保護膜(下側層), B M...ブラック・マトリクス, B M O...ブラック・マトリクスの開口の輪郭, V-D R V...駆動回路(垂直走査回路), H-D R V...駆動回路(映像信号駆動回路), T C O N...制御回路

10

20

30

40

50

o

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

図 1 2

【 図 1 4 】

义 1 4

【 13 】

图 1 3

【 図 15 】

15

---

フロントページの続き

(72)発明者 中谷 光雄

千葉県茂原市早野3300番地 株式会社日立製作所ディスプレイグループ内

(72)発明者 鈴木 雅彦

千葉県茂原市早野3300番地 株式会社日立製作所ディスプレイグループ内

(72)発明者 栗山 英樹

千葉県茂原市早野3300番地 株式会社日立製作所ディスプレイグループ内

(72)発明者 芦沢 啓一郎

千葉県茂原市早野3300番地 株式会社日立製作所ディスプレイグループ内

審査官 右田 昌士

(56)参考文献 特開平02-059723(JP, A)

特開平06-258663(JP, A)

特開平07-193249(JP, A)

特開平05-160121(JP, A)

特開平07-159786(JP, A)

特開平11-282011(JP, A)

特開平07-244277(JP, A)

特開平07-162003(JP, A)

特開平04-330783(JP, A)

特開2001-177101(JP, A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1362

G02F 1/1333

G02F 1/1343

G02F 1/1335

H01L 29/78

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置及其制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP3918496B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2007-05-23 |

| 申请号            | JP2001322951                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2001-10-22 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 当前申请(专利权)人(译)  | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | 渡辺邦彦<br>浮須雅弘<br>有吉知幸<br>中谷光雄<br>鈴木雅彦<br>栗山英樹<br>芦沢啓一郎                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 渡辺 邦彦<br>浮須 雅弘<br>有吉 知幸<br>中谷 光雄<br>鈴木 雅彦<br>栗山 英樹<br>芦沢 啓一郎                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G02F1/1368 G02F1/1343 G02F1/1333 G02F1/1362                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G02F1/136227 G02F1/134363 G02F2001/133397                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G02F1/1368 G02F1/1343 G02F1/1333.505                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 2H090/HA03 2H090/HB02X 2H090/HB03X 2H090/HC03 2H090/HD07 2H090/LA01 2H090/LA04 2H092 /GA14 2H092/GA17 2H092/GA27 2H092/JA24 2H092/JB57 2H092/JB58 2H092/KB14 2H092/KB21 2H092/KB24 2H092/MA08 2H092/NA05 2H190/HA03 2H190/HB02 2H190/HB03 2H190/HC03 2H190 /HD07 2H190/LA01 2H190/LA04 2H192/AA24 2H192/BA02 2H192/BA17 2H192/BA32 2H192/BB02 2H192/BC31 2H192/CB02 2H192/CB05 2H192/CC16 2H192/EA04 2H192/EA22 2H192/EA43 2H192 /EA62 2H192/EA66 2H192/FA65 2H192/HA14 2H192/HA91 |         |            |

| 代理人(译)         | 井上 学                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 其他公开文献         | JP2003131245A                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

**摘要(译)**

要解决的问题：减少在液晶显示装置的显示屏上发生的残留图像。解决方案：在液晶显示装置中，所述液晶显示装置具有彼此面对布置的一对基板和保持在这些基板的主表面之间的液晶层，并且形成有像素区域，所述像素区域具有在其上连接有开关元件和像素电极的像素区域。在上述基板对中的一个面对上述液晶的表面，以及在这些开关元件的上述液晶层侧的保护膜，上述保护膜通过层叠包括至少第一材料的多个材料层而形成从第一材料层放置在上述液晶侧的层和第二材料层，上述第二材料层的电阻率设定为低于第一材料层的电阻率并且高于硅的电阻率或半导体层形成的电阻率上述开关元件的通道。

| パラメータ (単位)                                  | 下側塗化珪素膜 8 b | 上側塗化珪素膜 8 a   |

|---------------------------------------------|-------------|---------------|

| SiH <sub>4</sub> 流量 (cm <sup>3</sup> /min.) | 130         | 350           |

| NH <sub>3</sub> 流量 (cm <sup>3</sup> /min.)  | 1200        | 100           |

| N <sub>2</sub> 流量 (cm <sup>3</sup> /min.)   | 2500        | 2000          |

| 反応圧力 (Pa)                                   | 266         | 266           |

| 高周波電力 (W)                                   | 2500        | 350           |

| 基板温度 (°C)                                   | 250         | 250           |

| 膜厚 (nm)                                     | 500         | 0, 10, 20, 30 |