(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3770380号

(P3770380)

(45) 発行日 平成18年4月26日(2006.4.26)

(24) 登録日 平成18年2月17日(2006.2.17)

(51) Int.CI.

F 1

|             |              |                  |             |              |             |

|-------------|--------------|------------------|-------------|--------------|-------------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/36</b>  |             |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | <b>G02F</b> | <b>1/133</b> | <b>550</b>  |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G02F</b> | <b>1/133</b> | <b>575</b>  |

|             |              |                  | <b>G09G</b> | <b>3/20</b>  | <b>621F</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b>  | <b>641P</b> |

請求項の数 4 (全 44 頁)

(21) 出願番号 特願2001-174845 (P2001-174845)

(22) 出願日 平成13年6月8日 (2001.6.8)

(65) 公開番号 特開2003-36055 (P2003-36055A)

(43) 公開日 平成15年2月7日 (2003.2.7)

審査請求日 平成15年5月12日 (2003.5.12)

(31) 優先権主張番号 特願2000-284267 (P2000-284267)

(32) 優先日 平成12年9月19日 (2000.9.19)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2001-150169 (P2001-150169)

(32) 優先日 平成13年5月18日 (2001.5.18)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 110000338

特許業務法人原謙三國際特許事務所

(74) 代理人 100080034

弁理士 原 謙三

(72) 発明者 宮田 英利

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(72) 発明者 塩見 誠

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

画素を有し、前記画素にフレームごとに階調データに基づく階調電圧を印加することで階調表示を行う液晶表示装置において、

表示すべきフレームの階調データおよび直前のフレームの階調データに基づいて、表示すべきフレームの階調データを補正階調データに変換する変換部と、

前記変換部にて変換された補正階調データに基づいて階調電圧を前記画素に印加する駆動部と、

前記画素に含まれ、印加された階調電圧により階調表示が可能な液晶セルとを備え、

前記変換部は、表示すべきフレームの階調データの上位桁および直前のフレームの階調データの上位桁に基づいて、予め記憶された、上位桁のみからなる設定階調データの中から、所定の設定階調データを特定し、特定された設定階調データと、表示すべきフレームの階調データの下位桁とを加算することにより補正階調データを生成することを特徴とする液晶表示装置。

## 【請求項 2】

請求項1に記載の液晶表示装置において、

前記変換部は第1入力および第2入力を有し、

前記第2入力には、入力される階調データを記憶してその階調データを1フレーム分遅らせて出力する記憶部が接続されており、

階調データは、前記第1入力に入力されるとともに、前記記憶部を介して前記第2入力

に入力されることを特徴とする液晶表示装置。

【請求項 3】

画素を有し、前記画素にフレームごとに階調データに基づく階調電圧を印加することで階調表示を行う液晶表示装置において、

表示すべきフレームの階調データおよび直前のフレームの階調データに基づいて、表示すべきフレームの階調データを補正階調データに変換する変換部と、

前記変換部にて変換された補正階調データに基づいて階調電圧を前記画素に印加する駆動部と、

前記画素に含まれ、印加された階調電圧により階調表示が可能な液晶セルとを備え、

10 前記変換部は、表示すべきフレームの階調データの上位桁および直前のフレームの階調データの上位桁に基づいて、予め記憶された、上位桁のみからなる設定階調データの中から、所定の設定階調データを特定し、特定された設定階調データと、表示すべきフレームの階調データの下位桁および直前のフレームの階調データの下位桁に基づいて変換された表示すべきフレームの階調データの下位桁とを加算することにより補正階調データを生成することを特徴とする液晶表示装置。

【請求項 4】

請求項 1 に記載の液晶表示装置において、

前記変換部は第 1 入力および第 2 入力を有し、

20 前記第 2 入力には、入力される階調データを記憶してその階調データを 1 フレーム分遅らせて出力する記憶部が接続されており、

階調データは、前記第 1 入力に入力されるとともに、前記記憶部を介して前記第 2 入力に入力されることを特徴とする液晶表示装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、階調表示が可能な液晶表示装置に関するものである。

【0002】

【従来の技術】

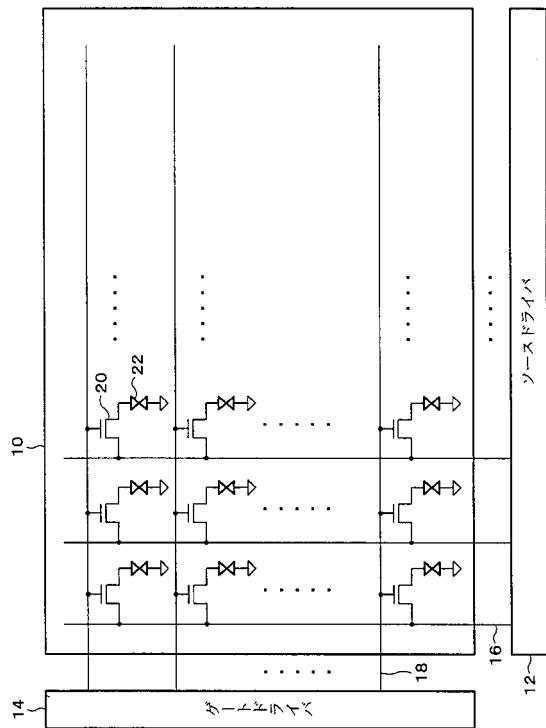

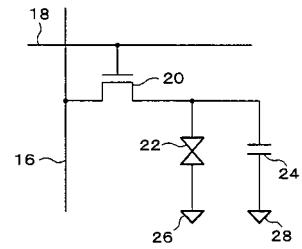

図 14 は、スイッチング素子としての薄膜トランジスタ（以下「TFT」という。）を備えたアクティブマトリクス型の液晶パネル 10、およびこの液晶パネルを駆動するドライバ（ソースドライバ 12、ゲートドライバ 14）を備えた液晶表示装置の構成を示す概略構成図である。液晶パネル 10 は、画面縦方向に互いに平行に配置された複数のソースバスライン 16 と、画面横方向に互いに平行に配置された複数の走査ライン 18 を有している。液晶パネル 10 の外側において、ソースバスライン 16 はソースドライバ 12 に接続されており、走査ライン 18 はゲートドライバ 14 に接続されている。また、ソースバスライン 16 と走査ライン 18 とはほぼ直交しており、その交点に対応して画素が形成されている。この画素には、TFT 20 および液晶セル 22 が配置されている。

【0003】

この液晶パネル 10 によって画像を表示する際には、ゲートドライバ 14 で各走査ライン 18 に接続された TFT 20 を走査ライン 18 ごとに順次 ONさせつつ、ソースドライバ 12 で各走査ライン 18 に対応した階調データ（画像データ）に応じた階調電圧を各走査ライン 18 に対応する画素に書き込んでいく。

【0004】

図 15 は、図 14 の液晶パネル 10 における各画素の等価回路を示す回路図である。液晶セル 22 は、TFT 20 のドレンと、全画素間で共通の共通電極 26 とに接続されている。また、図 14 には示していないが、画素には負荷容量 24 が設けられている。この負荷容量 24 は、TFT 20 のドレンと全画素間で共通の負荷容量電極 28 とに接続されている。

【0005】

画素の動作時には、TFT 20 が ON（ゲート ON）の状態でソースバスライン 16 か

10

20

30

40

50

ら階調データに応じた階調電圧が液晶セル22に印加される。階調電圧は階調データに応じて設定されており、階調データに応じて各画素に1フレームごとに印加される。液晶セル22に電圧が印加されると、液晶セル22内の液晶分子はその誘電異方性により長軸方向(ダイレクター)が変化される。液晶分子は光学異方性を有するため、その方向が変化されると液晶セル22を透過する光の偏光方向も変化する。そして、液晶セル22に設けられる偏光板などの作用を伴って、液晶セル22に印加する階調電圧によって液晶セル22を透過する光の光量が制御される。これにより、各画素の輝度を表示させたい階調輝度にすることができ、画像表示を行うことができる。

#### 【0006】

液晶セル22に対して階調電圧が印加される際には、負荷容量24にも同じ階調電圧が印加される。負荷容量24は、印加される階調電圧に応じた電荷を蓄積する。TFT20がONからOFF(ゲートOFF)に切り換わった後も次のフレームで再び階調電圧が印加されるまでは負荷容量24は電荷を保持する。これにより、液晶セル22に階調電圧が印加された状態が1フレームの間ににおいて保持される。

#### 【0007】

フレーム間において画素の階調輝度を変化させる際、その変化前では液晶分子のダイレクターは前のフレームの階調輝度を表示する方向になっている。現フレームの階調電圧が画素に印加されると、それに伴って液晶分子のダイレクターが変化する。これによりその画素の光学特性が変化し、その画素の階調輝度を変化させることができる。

#### 【0008】

ところで、液晶分子が印加電圧の変化に応答するためにはある程度の時間が必要となる。例えば、ネマチック液晶の場合の応答速度は、表示モードによって異なるが、およそ数msから数十msのオーダーである。これは、TFT20がOFFされるまでに液晶分子の応答が完了せず、OFF後もダイレクターが変化することを意味する。

#### 【0009】

ここで、液晶分子は誘電異方性を有しているため、液晶分子のダイレクターが変化すると必然的に液晶セル22内の液晶の誘電率が変化し、液晶セル22の電極間の容量(電気容量)が変化することになる。上述したように液晶分子のダイレクターの変化はTFT20のOFF後も続く。一方、液晶セル22および負荷容量24への電荷の供給はTFT20のOFF後は停止される。したがって、TFT20のOFF後において液晶セル22の容量が変化すると、液晶セル22の電極間の電圧が変化することになる。つまり、液晶セル22の電圧は、TFT20のOFF後においてTFT20のON時に印加された階調電圧から変化することになる。

#### 【0010】

したがって、液晶分子が1フレーム内で応答する特性を有していても、液晶セル22の電圧が1フレーム内で変化するため表示させたい階調輝度を得ることができない場合がある。逆に、表示させたい階調輝度に達するには数フレーム(例えば3フレーム)間にわたって同じ階調電圧を印加しなければならない場合がある。

#### 【0011】

なお、印加電圧に対する液晶分子の応答の遅さを補正する技術は、例えば特開昭64-10299号公報に開示されている。しかし、上記公報に開示されている技術では、その装置構成において補正回路を用いており、この補正回路によって逐次出力するデータを予測するものであるため、補正回路の構成が複雑なものとなるとともに、処理速度の低下が問題となりやすい。さらに、その補正回路に入力されるデータの一方が、直前に補正回路にて補正された後でメモリに記憶されたものであり、補正されたデータを用いてさらに次のデータを補正するようになっており、装置構成が複雑なものとなっている。また、上記公報に開示されている技術では、上記のような液晶セル22の容量の変化による影響は考慮されておらず、これに対処するための具体的なデータの変換方法も開示されていない。

#### 【0012】

10

20

30

40

50

本発明は上記の課題に鑑みてなされたものであり、簡素で処理速度が大きい装置構成により、液晶表示素子において階調変化時に伴う画素電極の電圧の変化を低減して階調表示のズレを抑制し、見かけ上の液晶分子の応答速度を向上させることで、動画表示時の画質を向上させることを目的としている。

#### 【0013】

##### 【課題を解決するための手段】

上記の課題を解決するために、本発明の液晶表示装置は、画素を有し、前記画素にフレームごとに階調データに基づく階調電圧を印加することで階調表示を行う液晶表示装置において、表示すべきフレームの階調データおよび直前のフレームの階調データに基づいて、表示すべきフレームの階調データを補正階調データに変換する変換部と、前記変換部にて変換された補正階調データに基づいて階調電圧を前記画素に印加する駆動部と、前記画素に含まれ、印加された階調電圧により階調表示が可能な液晶セルとを備え、前記変換部は、表示すべきフレームの階調データの上位桁および直前のフレームの階調データの上位桁に基づいて、予め記憶された、上位桁のみからなる設定階調データの中から、所定の設定階調データを特定し、特定された設定階調データと、表示すべきフレームの階調データの下位桁とを加算することにより補正階調データを生成することを特徴としている。

#### 【0014】

上記の構成では、直前のフレームと表示すべきフレームとの間の液晶セルの容量（電気容量）の変化による影響を考慮した階調電圧を画素に印加することができる。これにより、液晶セルの容量が変化することによる階調表示のズレを補正することができる。その結果、特に動画表示時などにおいて入力される階調データをより忠実に再現した表示が可能になる。

#### 【0015】

また、上記の構成では、階調データの予め定めた上位桁（上位ビット）に基づいて階調データの変換を行う。これにより、変換部で扱うデータ量を削減することができ、変換部の簡素化を図ることができる。例えば、変換部における補正階調データを記憶する部分の容量の削減を図ることができる。

#### 【0016】

また、上記の構成では、階調データの残りの下位桁（下位ビット）を加算することにより、上位桁のみに基づく変換を行ったことによる誤差を小さくすることができる。

#### 【0017】

あるいは、本発明の液晶表示装置は、前記変換部が、表示すべきフレームの階調データの上位桁および直前のフレームの階調データの上位桁に基づいて、予め記憶された、上位桁のみからなる設定階調データの中から、所定の設定階調データを特定し、特定された設定階調データと、表示すべきフレームの階調データの下位桁および直前のフレームの階調データの下位桁に基づいて変換された表示すべきフレームの階調データの下位桁とを加算することにより補正階調データを生成することを特徴としている。

#### 【0018】

上記の構成では、階調データの残りの下位桁を変換してから加算することにより、さらに誤差を小さくすることが可能となる。

#### 【0019】

本発明の液晶表示装置は、上記の液晶表示装置において、さらに、前記変換部が第1入力および第2入力を有し、前記第2入力には、入力される階調データを記憶してその階調データを1フレーム分遅らせて出力する記憶部が接続されており、階調データは、前記第1入力に入力されるとともに、前記記憶部を介して前記第2入力に入力されることが好ましい。

#### 【0020】

上記の構成では、表示すべきフレームの階調データを変換部の第1入力に直接入力するとともに記憶部を介して変換部の第2入力に入力する。この記憶部は、入力された階調データを1フレーム分遅らせて出力するものである。これにより、簡素な構成で表示すべき

10

20

30

40

50

## フレームの階調データと直前のフレームの階調データとを変換部に入力することができる

【0021】

### 【発明の実施の形態】

#### 〔参考形態1〕

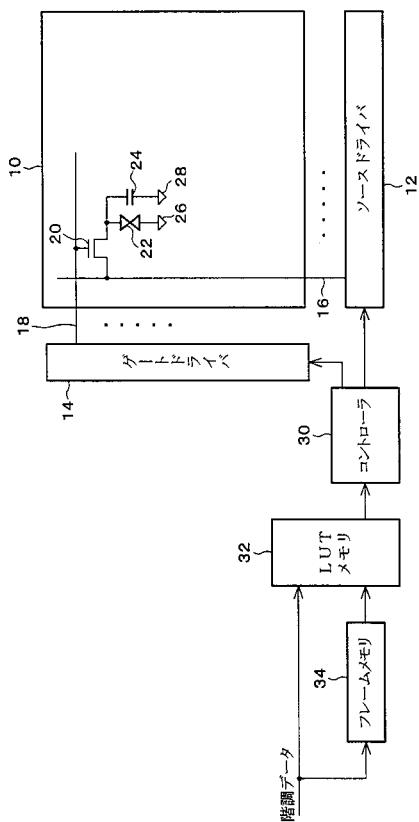

本発明の参考となる形態について図1から図11に基づいて説明すれば、以下の通りである。図1は、本参考形態に係るアクティブマトリクス型の液晶表示装置（LCD）の構成を示すブロック図である。なお、図1において液晶パネル10、ソースドライバ（駆動部）12、ゲートドライバ14等は、上記従来の技術の項において図14に基づいて説明したものと同等であり、図1ではこれらを簡略化して示している。図14および図15に示した構成要素と同等の機能を有する構成要素については同一の符号を用いる。

【0022】

ソースドライバ12およびゲートドライバ14は、コントローラ（LCDコントローラ、ゲートアレイ）30によって制御される。コントローラ30は、ソースバスライン16を介して各画素に書き込むべき階調電圧を指定するための階調データ（画像データ）をソースドライバ12に対して送る。ここで、階調データはデジタルデータである。また、コントローラ30は、ゲートドライバ14に対して走査タイミングを指示する信号を与えるとともに、ソースドライバ12に対して上記走査タイミングと同期して階調電圧を切り換えて出力するための信号を与える。

【0023】

コントローラ30によりソースドライバ12に送られる階調データは、後述するルックアップテーブル（LUT）を備えたメモリであるルックアップテーブルメモリ（変換部、メモリ）32（以下「LUTメモリ32」と記す。）からコントローラ30に対して出力されるものである。LUTメモリ32はSRAMにより構成されており、2つの入力を有している。この2つの入力のうちの一方（以下「第1入力」という。）には、階調データを伝送するデータバスラインが直接接続されており、他方（以下「第2入力」という。）には、データバスラインがフレームメモリ（記憶部、1フレーム遅延回路）34を介して接続されている。

【0024】

なお、図1ではLUTメモリ32およびフレームメモリ34がそれぞれ1つ備えられた構成となっているが、液晶パネル10がRGBのカラー表示可能なものであり、階調データがRGBのカラーデータである場合には、LUTメモリ32およびフレームメモリ34をRGBの階調データごとに独立に備えておけばよい。また、LUTメモリ32の代わりにFPGA（Field-Programmable Gate Array）等の演算素子を用いることも可能である。

【0025】

フレームメモリ34は、1フレーム分の階調データを記憶することができる FIFO（First-in First-out）方式のメモリである。したがって、フレームメモリ34ではデータの入出力の同時処理を行うことができる。また、フレームメモリ34を介すことにより、簡単な構成で階調データを1フレーム分遅らせて出力することができる。

【0026】

したがって、表示すべきフレームの階調データ（以下「表示フレーム階調データ」という。）は、LUTメモリ32の第1入力に入力されると同時にフレームメモリ34にも入力される。このとき、フレームメモリ34からは表示すべきフレームの1フレーム前のフレーム（直前のフレーム）の階調データ（以下「前フレーム階調データ」という。）が出力され、LUTメモリ32の第2入力に入力される。

【0027】

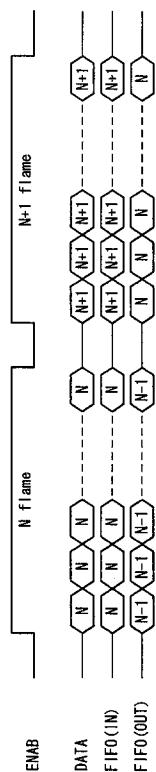

この入出力関係を図2を用いて説明する。図2は、フレームメモリ34に対する階調データの入出力の関係を示すタイミングチャートである。データバスラインに階調データ（DATA）が存在していることを示す信号（ENAB）がハイ（High）の期間に、フレームメモリ

10

20

30

40

50

34に表示フレーム階調データ(FIFO(IN))が順次書き込まれ、同時にフレームメモリ34から前フレーム階調データ(FIFO(OUT))が順次出力される。

#### 【0028】

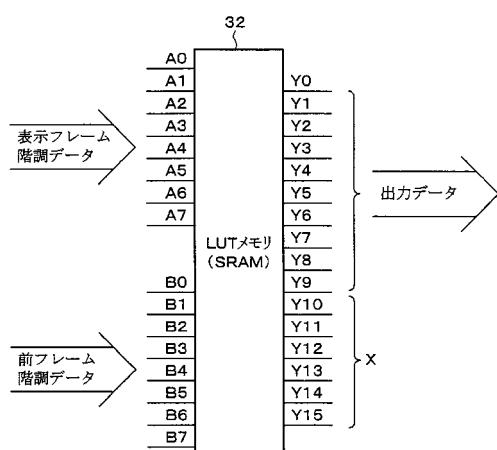

SRAMからなるLUTメモリ32のピン接続は図3の通りである。図3はLUTメモリ32のピン接続図である。LUTメモリ32のアドレスA0～A7には表示フレーム階調データが、アドレスB0～B7には前フレーム階調データ、つまりフレームメモリ34の出力が入力される。そして、LUTメモリ32に記憶されたルックアップテーブルに基づいてこれらの入力により特定される階調データが出力される。具体的には、アドレスA0～A7およびアドレスB0～B7に入力される各階調データに基づいてLUTメモリ32のアドレスが指定され、指定されたアドレスに記憶されている階調データがアドレスY0～Y9から出力される。本参考形態ではLUTメモリ32から0ビットから9ビットのアドレスを用いて階調データを出力するものとし、他のアドレスY10～Y15をNC(ノーコネクション)とした。

#### 【0029】

このように、LUTメモリ32は表示フレーム階調データと前フレーム階調データとに基づいて、予め定められてLUTメモリ32に記憶されたルックアップテーブルから特定の階調データを出力するようになっている。これにより、演算などの処理を介することなく階調データの変換を行うことができ、処理速度の低下を抑制することができる。

#### 【0030】

次に、LUTメモリ32に記憶させるルックアップテーブルについて説明する。従来の技術の項で図14および図15に基づいて説明したように、フレーム間で画素の階調が変化する場合には、ゲートOFF後においてもその画素の液晶分子のダイレクターが継続して変化することがある。このとき、液晶分子のダイレクターの変化に起因して液晶セル22の電極間の容量(以下、単に「液晶セル22の容量」という。)が変化する。このため、液晶セル22の電極間の電圧(以下、単に「液晶セル22の電圧」という。)がゲートON時に印加した階調電圧から変化することがある。

#### 【0031】

現在の TFT を備えた液晶パネルの表示駆動では、上述したようにソースドライバにデジタルデータで階調データが送られており、ソースドライバ側で階調変化時にその変化量ごとに、かつ、画素ごとに出力する階調電圧を変化させることは難しい。

#### 【0032】

そこで、本参考形態では上述した液晶セル22における階調変化時の容量変化による階調電圧のずれを補うことで、特に動画表示における画質の向上を図る。そのために、ソースドライバ12へ送る階調データを、予め決めてLUTメモリ32に記憶させておいたルックアップテーブルにより、すなわち前フレーム階調データおよび表示フレーム階調データで予め設定された定数を特定することにより決定するものである。このルックアップテーブルに設定されたソースドライバ12へ送るための階調データは、直前のフレームと表示すべきフレームとの間の液晶セルの容量の変化に基づいて定められている。なお、LUTメモリ32を用いることにより構成が簡素になり、かつ、処理速度を容易に向上させることができるため好ましい。

#### 【0033】

フレーム間で階調が変化する場合には、後のフレームに印加する階調電圧の値として、そのフレーム間での液晶セル22の容量変化の比率に応じた値を付加した値とすることが好ましい。これにより、液晶分子のダイレクターの変化が終了した後、つまり液晶分子の応答が完了した後に、液晶セル22の電圧が表示させたい階調輝度に応じた階調電圧(以下「理想階調電圧」という。)となるようにすることができる。ただし、実際には液晶分子の応答速度などにより適切な電圧値は変化し得る。

#### 【0034】

ここでは、簡単のためゲートON時には液晶分子がほとんど応答せず、フレームの期間内には液晶分子の応答が完了すると仮定する。この場合に、液晶分子の応答完了時に液晶

10

20

30

40

50

セル22の電圧が理想階調電圧となるようにゲートON時に印加すべき階調電圧を決定する方法の一例について説明する。

#### 【0035】

階調数が256の場合、0, 1, 2, ..., n, ..., m, ..., 255階調のときの階調電圧を、それぞれV0, V1, V2, ..., Vn, ...,Vm, ...V255とし、各階調における液晶セル22の容量をC0, C1, C2, ..., Cn, ..., Cm, ...C255とする。なお、これらは液晶セル22が定常状態にあるとき、すなわち静止画表示のときの値とする。

#### 【0036】

ある画素にn階調が表示されて定常状態になっているとすると、この時の液晶セル22の電圧はVnであり液晶セル22の容量はCnである。このとき、次のフレームでm階調の表示に変更する場合、液晶セル22に蓄えなければならない電荷量Qは、10

$$Q = Cm \times Vm \dots (1)$$

である。しかし、上述の仮定（ゲートON時に液晶分子がほとんど応答しないという仮定）に基づくと、液晶セル22の容量がCnからCmへ変化する前であり、かつ、液晶セル22の容量がまだCnの状態で、TFT20がOFFになることになる。したがって、この時点では液晶セル22にVmを印加した場合に実際に液晶セル22に蓄えられる電荷量Q'は、

$$Q' = Cn \times Vm \dots (2)$$

となってしまう。つまり、液晶セル22が電荷をQだけ蓄えるために必要な電圧V'を求める、(1)より、20

$$Q' = Cn \times V' = Cn \times (Cm / Cn \times Vm) \dots (3)$$

が成り立つことから、

$$V' = Cm / Cn \times Vm \dots (4)$$

となる。

#### 【0037】

ルックアップテーブルとしてLUTメモリ32に記憶される階調データ（以下「設定階調データ」という。）は、上記式(4)に基づいて得られる結果に液晶セル22の階調間の応答性、画素の負荷容量24などを考慮して決定すればよい。または、液晶パネル10において実際の階調間の応答性を視覚的に判断して決定することもできる。いずれの方法によって決定した場合も大差はないが、視覚的に決定した場合では人間の感覚による影響も含まれることになる。30

#### 【0038】

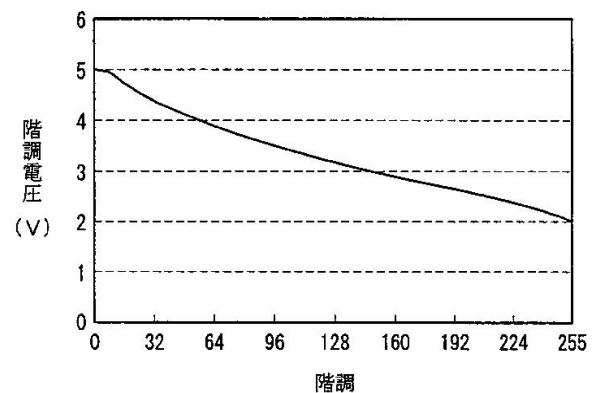

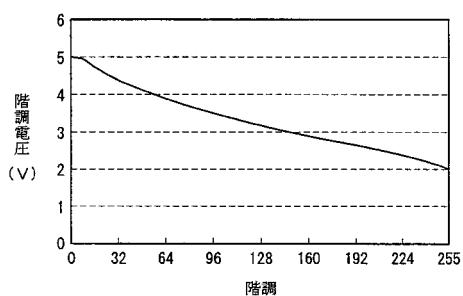

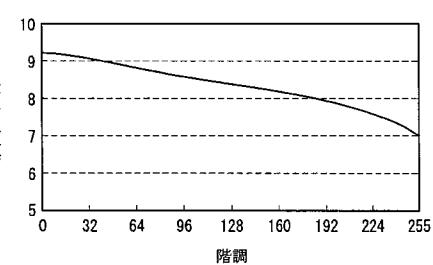

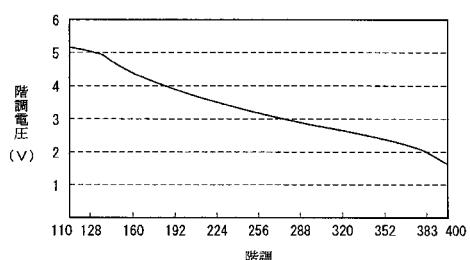

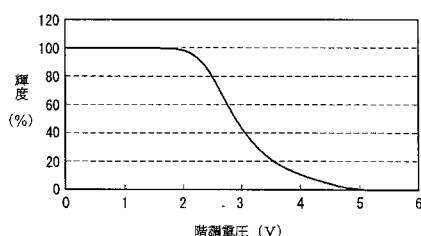

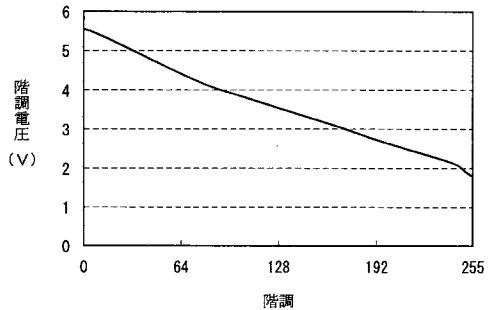

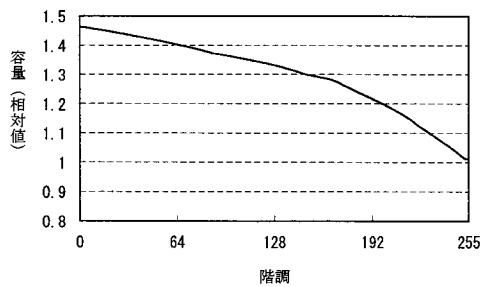

ルックアップテーブルの具体例について説明する。図4は液晶パネル10における各階調と階調電圧との関係を示すグラフである。図5は液晶パネル10における各階調と液晶セル22の容量（相対値）との関係を示すグラフである。

#### 【0039】

図4および図5のデータと、上記式(4)に基づいてルックアップテーブルを作成すると図9のようになる。図9は、図4、図5および上記式(4)に基づいて求めたルックアップテーブルを示している。なお、図9の第1列目はLUTメモリ32のアドレスB0～B7に入力される階調データ、つまり前フレーム階調データを表し、図9の第1行目はLUTメモリ32のアドレスA0～A7に入力される階調データ、つまり表示フレーム階調データを表している。そして、前フレーム階調データで特定される所定の行に属し、かつ、表示フレーム階調データで特定される所定の列に属する値が、その前フレーム階調データおよび表示フレーム階調データに対して出力される設定階調データを表している。また、図9には、前フレーム階調データおよび表示フレーム階調データがそれぞれ0, 32, 64, 96, 128, 160, 192, 224, 255の各階調の場合のみを示している。

#### 【0040】

図9のルックアップテーブルでは、静止画表示の場合、つまり前フレーム階調データと40

表示フレーム階調データとが等しい場合、LUTメモリ32に入力される8ビットデータ範囲（v0からv255）は128階調から383階調（256階調分）に変換される（LUTメモリ32に入力される階調データを、v0, v1, ..., v255と記す）。このように変換するのは、次に説明する動画表示の場合において出力する設定階調データ、つまりコントローラ30に入力される階調データが負の値となるのを避けるためである。つまり、入力される階調データを128階調シフトさせることで、負の値となるべき設定階調データを128階調未満の正の値の設定階調データに対応付けることができる。したがって、図4および図5における階調、並びに図9から図11における前フレーム階調データおよび表示フレーム階調データはシフト前の階調データであり、図9から図11における設定階調データはシフト後の階調データである。

10

#### 【0041】

また、動画表示の場合、つまり前フレーム階調データと表示フレーム階調データとが異なる場合、120階調から391階調の範囲内に変換される。したがって、動画表示の場合では、静止画表示の場合の設定階調データの範囲を含み、かつ、その範囲よりも広い範囲の設定階調データに変換されることになる。ソースドライバ12もこれに伴った広い範囲の階調電圧を出力することができる。つまり、ソースドライバ12は液晶セル22の黒表示に対応する階調電圧から白表示に対応する階調電圧までの範囲に加え、その上下における所定の範囲の電圧をも出力することができる。

#### 【0042】

このような設定階調データに対する階調電圧の値の関係を図12に、また、上記階調電圧に対する輝度（%）の関係を図13に示す。図12は、設定階調データと階調電圧の値との関係を示すグラフであり、図13は、階調電圧と輝度の関係を示すグラフである。

20

#### 【0043】

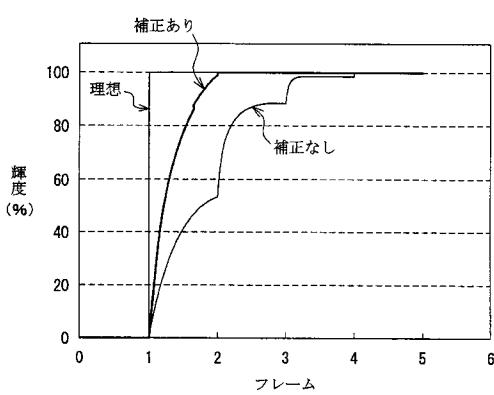

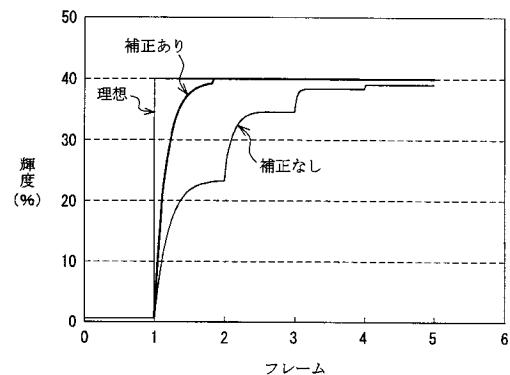

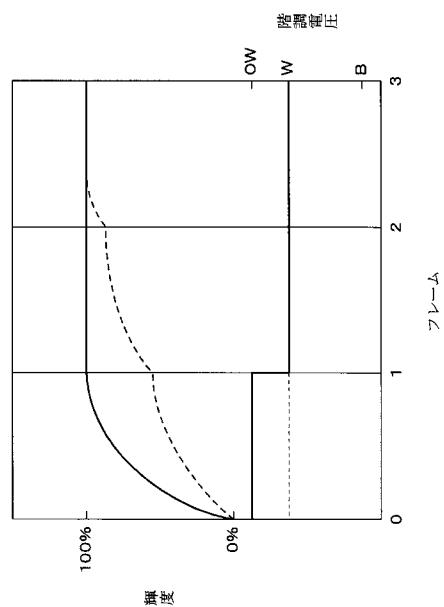

図6から図8は、ルックアップテーブルを用いて階調データを補正した場合と、補正しなかった場合とにおいて、表示の切り換えの応答特性を示すグラフである。ここで、図6は、図9のルックアップテーブルの場合であり、第0フレームと第1フレームとの間で、黒表示（v0）から白表示（v255）へ切り換えられ、その後白表示を維持した場合の輝度（%）の変化を示している。

#### 【0044】

第0フレームから第1フレームへ切り換わった瞬間に輝度が0%から100%に変化することが理想的である。しかし、実際には液晶分子の応答速度の遅さや、液晶セル22の容量変化に起因して徐々に輝度が上昇する。ここで、補正を行わない場合では、上述の理由によって1フレーム経過後も輝度が100%に達していない。このように、1フレーム経過後も輝度が理想値に達しない場合には、表示が入力された信号に対して間違ったものとなる。各フレームで表示させたい階調の輝度を得るには、そのフレーム内で輝度が理想値に達することが必要である。補正を行った場合では、液晶セル22の容量変化による影響が抑制されるため応答性が改善される。

30

#### 【0045】

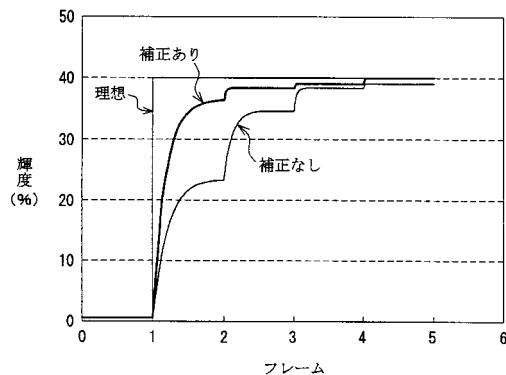

しかし、液晶分子の応答速度が遅くなる条件では上記の補正では応答性が充分に改善されない場合もある。図7は、液晶分子の応答速度が遅くなる条件として、例えば第0フレームと第1フレームとの間で中間調表示（v32）から中間調表示（v192）へ切り換えられ、その後中間調表示（v192）を維持した場合の輝度（%）の変化を示している。この場合、上記の補正を行っても1フレーム経過後も輝度が理想値に達していない。このような液晶分子の応答速度が遅くなる階調変化では、図9のルックアップテーブルにおける設定階調データに対して、その遅くなる分も加えた値を設定階調データとすることが好ましい。その値を厳密に計算することは困難であるが、液晶分子の応答速度を考慮して計算し、さらに実際の表示に基づいてその値を修正することにより決定することができる。

40

#### 【0046】

なお、設定階調データの値を修正する場合には、上記式（4）に基づいた図9のルック

50

アップデーブルにおける設定階調データの値に対して10階調程度の範囲内に設定することが望ましい。設定階調データを修正した場合には、表示する輝度が理想値を越えることがあるが、設定階調データが上記の範囲内であれば、表示する輝度が理想値を越えたとしても1フレーム内で理想値に戻ると考えられる。ただし、この範囲は表示階調や液晶材料、表示モード等によって異なる場合もある。

#### 【0047】

このようにして求めた設定階調データを図10に示す。図10は、図9のルックアップテーブルを修正したルックアップテーブルの一例である。なお、図10では図9から変更した設定階調データにアンダーラインを付している。

#### 【0048】

図10の設定階調データでも、静止画表示の場合、v0からv255は128階調から383階調(256階調分)に変換される。図10のルックアップテーブルでは図9のものに対して、相対的に階調数が低い中間調表示から相対的に階調数が高い中間調表示への変化の場合の設定階調データの値が大きくなっている。これは、このような変化において液晶分子の応答速度が特に遅いからである。なお、逆に相対的に階調数が高い中間調表示から相対的に階調数が低い中間調表示への変化の場合の設定階調データの値を変更する必要がある場合もある。

#### 【0049】

図8は、上記と同様に第0フレームと第1フレームとの間で中間調表示(v32)から中間調表示(v192)へ切り換えられ、その後中間調表示(v192)を維持した場合の輝度(%)の変化を示している。ただし、図8の場合は、図10のルックアップテーブルを補正に用いている。この場合、上記の補正を行うことで1フレーム経過後には輝度が理想値に達することになる。

#### 【0050】

なお、ソースドライバ12が液晶セル22の黒表示に対応する階調電圧から白表示に対応する階調電圧までの範囲外の電圧を出力することができない場合には、図11に示すように中間調表示の範囲でのみ補正を行うように設定階調データを定めておけばよい。図11は、上記のようなソースドライバ12を用いた場合のルックアップテーブルの一例である。

#### 【0051】

この場合、設定階調データは0階調から255階調(256階調分)となる。この補正では、白表示から黒表示への切り換えのような階調変化においては補正の効果は得られないが、中間調表示の範囲での切り換えにおいて応答速度の改善が得られ、動画表示性能の向上を図ることができる。

#### 【0052】

ここで、ルックアップテーブルに設定されるべき設定階調データについての説明を補足する。

#### 【0053】

図9に示したルックアップテーブルは、ステップ充放電特性に基づいて設定されたものであるが、液晶分子の応答に要する時間(応答時間)によっては不適切なこともある。そこで、液晶分子の応答時間が長いことを考慮し、図10に示したルックアップテーブルのように、容量変化に基づく補正(上記式(4)に基づく補正)よりさらに大きく補正した設定階調データを設定することが好ましい。ここで、単純で効果的だが、実際には使用できない補正方法を説明することで、上記のような補正を行うことの効果を説明する。

#### 【0054】

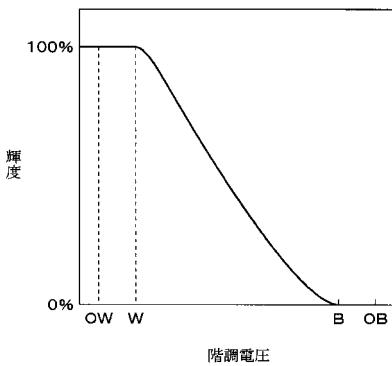

図31は、階調電圧と輝度との関係を示す仮想的なグラフである。図31では、表示階調電圧、つまり、輝度が0%から100%まで変化する範囲に対応する階調電圧の外側に、補正のために用いる階調電圧であるオーバーブラック階調電圧OBおよび、オーバーホワイト階調電圧OWを仮定する。オーバーブラック階調電圧OBおよびオーバーホワイト階調電圧OWは、あらゆる階調変化の組み合わせに対して、それぞれ十分高電圧および低

10

20

30

40

50

電圧となるように設定されているものとする。つまり、図9に示したルックアップテーブルにおける全ての設定階調データに対応する階調電圧に対して、オーバーブラック階調電圧OBは十分高電圧となるように設定されており、オーバーホワイト階調電圧OWは十分低電圧となるように設定されている。なお、黒表示（輝度0%）に対応する階調電圧をブラック階調電圧B、白表示（輝度100%）に対応する階調電圧をホワイト階調電圧Wとする。

#### 【0055】

ここで、暗い階調から明るい階調へ変化させる際にオーバーホワイト階調電圧OWを適用し、明るい階調から暗い階調へ変化させる際にオーバーブラック階調電圧OBを適用すると、全ての階調変化に対する液晶分子の応答を1フレーム以内におさめることは可能である。10

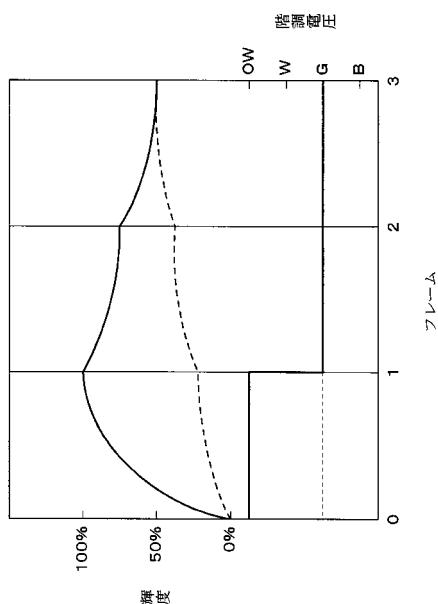

#### 【0056】

しかし、このような補正を行うと、実際には次のような不都合が生じ得る。図32は、第0フレームの開始とともに、黒表示から白表示へ切り替え、その後第1および第2フレームで白表示を維持する際の階調電圧および輝度の変化を示すグラフであり、実線は第0フレームでオーバーホワイト階調電圧OWを用いた場合を示し、破線は第0フレームでホワイト階調電圧Wを用いた場合、つまり補正を行わない場合を示している。また、図33は、第0フレームの開始とともに、黒表示から灰表示（輝度50%）へ切り替え、その後第1および第2フレームで灰表示を維持する際の階調電圧および輝度の変化を示すグラフであり、実線は第0フレームでオーバーホワイト階調電圧OWを用いた場合を示し、破線は第0フレームで灰表示に対応するグレー階調電圧Gを用いた場合、つまり補正を行わない場合を示している。図32では、オーバーホワイト階調電圧OWを用いることにより、補正を行わない場合のフレーム間での段階的な応答が解消され、良好な高速応答を示すようになる。ところが、図33では、オーバーホワイト階調電圧OWを用いることにより、第1フレームまでに白表示にまで到達してしまう。すなわち、目的とする階調をはるかに越えて応答してしまうことになる。もちろん、オーバーホワイト階調電圧OWを用いた場合は目的の階調に達するのに要する時間が約1/6フレーム時間となり、応答時間短縮効果はあるといえばあるが、例え応答時間が短縮されたとしても目的とする階調が得られないのでは意味がない。さらに、行き過ぎた応答はその後の第1フレーム以降に悪影響を残すことになる。すなわち、行き過ぎた階調から目的の階調に戻すために、2から3フレーム時間を要することになる。この第1フレーム以降では、応答時間短縮のための補正是行われない。なぜなら、第1フレーム以降に表示すべき階調は灰表示で一定しており、階調変化がなく、静止画表示の扱いとなるからである。20

#### 【0057】

以上の例は非常に極端ではあるが、応答時間が短縮されても1フレーム時間経過したときの表示階調が目的とする階調と大きく異なるような補正を行えば、同様の現象が起こることになる。この現象が起こることを避けるためには、LUTメモリ32のルックアップテーブルに設定されるべき設定階調データは、その設定階調データに応じた階調電圧が印加されてから1フレームに相当する時間（1フレーム時間）が経過するとき、つまり次のフレームにおける階調電圧が印加される直前において表示している輝度が、目的の輝度（表示すべき階調の輝度、理想値）に対して90%～110%の範囲、つまり輝度の誤差が±10%の範囲となるような階調であることが好ましい。この範囲を越えるような設定階調データを用いると、その設定階調データにより表示するフレームの輝度が目的とする輝度からかけ離れた輝度として観察されるばかりでなく、そのフレーム以降のフレームにおける異常表示をもたらすことになりかねない。この点は、以下に説明する他の形態に関しても同様である。40

#### 【0058】

上記輝度の誤差が±10%の範囲となるように設定階調データを設定することが好ましい点は、次の実験により確認された。

#### 【0059】

10

20

30

40

50

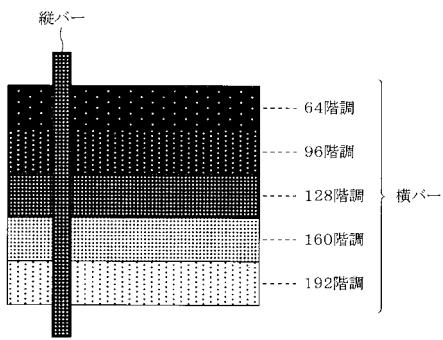

図40に示す評価映像を9種類のディスプレイに表示させ、その評価映像を50人の被験者に主観評価させる実験を行った。図40は、この実験に用いた評価映像を示す概念図である。この評価映像は、中間調の横階調バーからなる表示パターン上に、中間調の縦バーを横スクロールさせるものである。この評価映像の表示領域は640ドット×480ドットとした。また、横階調バーは64階調、96階調、128階調、160階調、192階調の各横バーを上から順に並べたものであり、縦バーは64階調、128階調、192階調のものをランダムに変化させたものである。また、縦バーの横スクロール速度は、4ドット/フレーム(60Hz)とした。

#### 【0060】

被験者による評価項目は、縦バーの周辺のエッジぼけであり、図41に示す基準で判定させた。図41は、本実験の評価基準を示す図表である。実験に用いた9種類のディスプレイの各形態は、図42に示す通りであり、各ディスプレイでは、輝度の誤差が図42に示す範囲に収まるように設定してある。図42は、本実験に用いた各ディスプレイの形態、各ディスプレイに設定されている輝度の誤差、および評価結果を示す図表である。評価結果は、図41に示した評価基準の点数の全被験者間での平均値で表している。液晶表示装置としての液晶テレビでは、CRTのようなインパルス型ディスプレイのように輝度の誤差が0%、評価結果5.0とするのは難しいが、輝度の誤差が±10%以内では評価結果3.0以上となり、多くの被験者が少なくとも表示エラーが邪魔にならないと判断した。したがって、輝度の誤差が±10%以内では実用上問題のないレベルであることがわかつた。

10

#### 【0061】

ルックアップテーブルに予め設定階調データを設定することによって補正を行う本発明の補正方法は、液晶パネル10の電気的特性ばかりでなく、液晶分子そのものの応答特性、人間の視覚特性にも合わせた適切な補正階調を設定しうる点で、特に汎用性に優れた補正方法であるといえる。

#### 【0062】

なお、LUTメモリ32による変換を演算化して、メモリー容量の削減、接続ピン数の削減などを図る工夫もあり得る。このような場合でも、階調変化において、1フレーム時間が経過したときに表示している階調の、目的の階調に対する誤差が±10%以内に収まるようにすることが好ましい。例えば、互いに近い階調間での応答速度が遅いことによる階調差をフィードバックして、小さい変化を埋め合わせるような演算方式とすることが望ましい。

30

#### 【0063】

以上のように、本参考形態に係る液晶表示装置は、各画素における各フレーム間での階調変化を認識するために前フレーム階調データを記憶するフレームメモリ34を有している。そして、予めLUTメモリ32に記憶させたルックアップテーブルを参照し、フレームメモリ34に記憶している前フレーム階調データと、表示フレーム階調データとに基づいて特定される設定階調データをコントローラ30に出力する。すなわち、LUTメモリ32は前フレーム階調データと表示フレーム階調データとに基づいて、記憶されたルックアップテーブルにより階調データを変換して出力する。

40

#### 【0064】

LUTメモリ32からコントローラ30に出力された階調データは、ソースドライバ12に書き込まれる。そして、ソースドライバ12によりその階調データに対応する階調電圧がソースバスライン16を介してその階調データに対応する画素の液晶セル22および負荷容量24に書き込まれ、その画素において階調表示が行われる。

#### 【0065】

ルックアップテーブルによる階調データの変換は、階調変化の際に目標とする階調表示が得られるような階調電圧に対応する階調データへの変換とする。これにより液晶パネル10に最適な階調電圧を印加することができ、特に動画像の品位を向上させることができる。

50

## 【0066】

なお、ルックアップテーブルを求める際には、簡易的には上述した式(4)に基づくことができるが、実際の液晶セル22ではゲートON時から液晶分子が徐々に応答するため、その計算値からずれことがある。特に1フレーム以内に液晶分子の応答が完了しないような場合には、計算値よりも補正量を大きくすることが好ましい。

## 【0067】

ここで、LUTメモリ32としてSRAMを用いるとフレーム周波数の高い高精細な画像データにも対応できるため好ましい。

## 【0068】

このようにすることにより、コントローラ30から出力されるデータを従来と同様なソースドライバ12等に対して出力することができる。つまり、コントローラ30以降の構成として、従来のソースドライバ12等を用いることができる。

10

## 【0069】

ただし、従来と同様なソースドライバ12の場合では、ソースドライバ12が出力できる階調電圧の範囲が、液晶セル22の白表示に対応する階調電圧と黒表示に対応する階調電圧との間に限られている場合がある。この場合には、例えば、表示を白表示から黒表示へ変化させるときに、黒表示に対応する階調電圧をそのまま出力するしかなく、適切な補正を行うことができない場合がある。これに対して、ソースドライバ12が白表示に対応する階調電圧と黒表示に対応する階調電圧との範囲外の階調電圧（例えば、白表示に対応する階調電圧より上の階調電圧、および黒表示に対応する階調電圧より下の階調電圧）を出力することが可能であれば、上記のような場合でも適切な補正が可能になる。

20

## 【0070】

補正後においても液晶セル22に階調電圧を印加するために、本参考形態では、LUTメモリ32を用いて前フレーム階調データと表示フレーム階調データとにより印加する階調電圧に対応する階調データを選択する。このため、階調変換を簡単に行うことができる。

## 【0071】

以上のように、本参考形態では、階調変化時に起こる印加電圧の変化を、その変化を予め加味した階調電圧を印加することにより最小限に抑え、1フレーム内で液晶分子を応答させ、特に動画像の表示性能の向上を図ることができる。

30

## 【0072】

また、LUTメモリ32を用いることで、階調変化時に伴う印加電圧のズレを加味した階調電圧を印加することができるシステムを、より簡単に構成することができる。

## 【0073】

## 〔実施形態〕

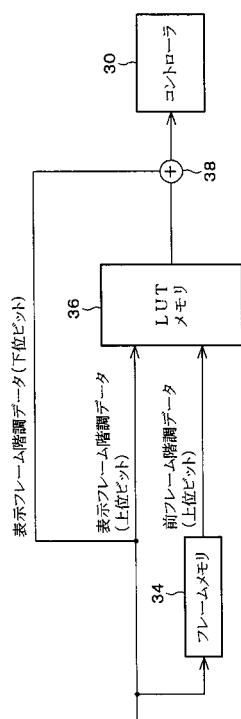

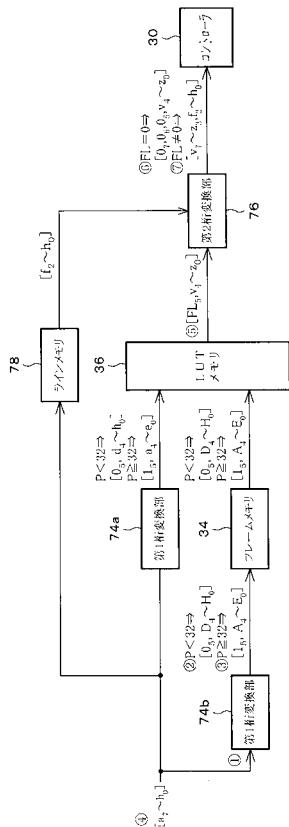

本発明の実施形態について図16から図19に基づいて説明すれば、以下の通りである。本実施形態に係るアクティブマトリクス型の液晶表示装置の構成は、基本的には参考形態1において図1に基づいて説明したものと同等であるため、ここでは相違点のみ説明する。本実施形態に係るアクティブマトリクス型の液晶表示装置では、LUTメモリ32の代わりにLUTメモリ（変換部、メモリ）36を備えるとともに、LUTメモリ36の入出力が参考形態1の場合と異なっている。

40

## 【0074】

図16は、本実施形態に係るLUTメモリ36周辺の構成を示すブロック図である。LUTメモリ36には、表示フレーム階調データおよび前フレーム階調データの各上位ビット（上位桁）のみが入力される。LUTメモリ36は、入力される表示フレーム階調データおよび前フレーム階調データの各上位ビットに基づいて、予め定められてLUTメモリ36に記憶されたルックアップテーブルから特定の設定階調データを出力するようになっている。LUTメモリ36から出力される設定階調データも、入力に対応した上位ビットのみの設定階調データである。そして、LUTメモリ36から出力された上位ビットのみの設定階調データと、表示フレーム階調データの下位ビット（下位桁）とを加算器38に

50

て加算してコントローラ30に入力する。

**【0075】**

参考形態1で説明したように、階調データのすべてのビットに基づいて階調データの変換を行うことにより最適な変換、つまり最も誤差の少ない変換を行うことができる。しかし、例えば8ビット(256階調)の階調データにおいて、下位2ビット(4階調分)程度を階調データの変換の考慮に入れないとしても、それによる誤差の程度はごく小さく、実用上問題がないと考えられる。一方、階調データの上位ビットのみに基づいてLUTメモリ36による変換を行うことにより、より容量の小さいLUTメモリ36およびフレームメモリ34を利用することができ、装置のコストダウンを図ることができる。例えば、LUTメモリ36は、図3に示したLUTメモリ32に対して、表示フレーム階調データの上位ビットを入力するためのアドレスA0～A5、前フレーム階調データの上位ビットを入力するためのアドレスB0～B5、および変換した上位ビットのみの設定階調データを出力するためのアドレスY0～Y5のみを有しておればよいことになる。10

**【0076】**

このように、階調データの変換の際に下位ビットを考慮に入れないことにより、フレーム間で画素の階調が変化する場合に、(下位ビットの値)/(全ビットの値)に相当する誤差が生じることになる。しかし、この場合でも、参考形態1で説明した補正の効果は小さくなるものの、その効果が得られなくなるわけではなく、十分な効果を得ることが可能である。

**【0077】**

本実施形態の構成において適切なルックアップテーブルをLUTメモリ36に設定し、適切なルックアップテーブルをLUTメモリ32に設定した参考形態1の構成の場合と比較した。フレーム間におけるあらゆる階調データの変化に関して、本実施形態の構成による上位6ビットのみに基づく階調データの変換と、参考形態1の構成による8ビットすべてに基づく階調データの変換とを比較すると、コントローラ30に入力される階調データ(以下「補正階調データ」という。なお、参考形態1では設定階調データが補正階調データとなる。)において、各変換の間の差がほとんど場合では4階調未満におさまった。上記の差が4階調以上になったのは、隣り合うフレーム間における全65536通りの階調変化において334通りとなり、その割合は約0.5%であった。最も上記の差が大きくなかったのは、前フレーム階調データが251階調、表示フレーム階調データが87階調の場合であり、その差は補正階調データにおいて22階調、階調電圧の差において0.35Vとなつた。20

**【0078】**

図17は、上記の比較において、LUTメモリ32に設定したルックアップテーブルの一部を示す図表であり、図18は、LUTメモリ36に設定したルックアップテーブルの一部を示す図表である。ここで、補正(階調データの変換)を行わない場合における87階調に対応する階調電圧は4.025Vであった。また、前フレーム階調データが251階調であり表示フレーム階調データが87階調の場合、階調データの変換を8ビットすべてに基づいて行なったときの階調電圧は5.495V(1階調に相当)であったのに対して、上位6ビットのみに基づいて行なったときの階調電圧は5.145V(23階調に相当)であった。したがって、階調データの変換を8ビットすべてに基づいて行なったときと、上位6ビットのみに基づいて行なったときとの階調電圧の差は0.35V(22階調の差に相当)となった。しかし、補正を行わない場合の階調電圧は4.025Vであるのに対して、上位6ビットのみに基づく変換による補正を行う場合の階調電圧は5.145Vであるため、補正を行わない場合に対して1V以上大きい階調電圧を印加することになり、その効果は大きい。30

**【0079】**

以上のように、本実施形態では、変換部を構成するLUTメモリ36が、表示フレーム階調データおよび前フレーム階調データに基づいて、表示フレーム階調データを補正階調データに変換する。このとき、LUTメモリ36は、表示フレーム階調データの上位ビッ50

ト(上位桁)および前フレーム階調データの上位ビットに基づいて、記憶している上位ビットのみの設定階調データを特定する。上位ビットとして利用するビット数は特に限定されないが、例えば8ビットに対して上位6ビットを利用するとよい。このように、階調データの予め定めた上位ビットに基づいて階調データの変換を行うことにより、LUTメモリ36で扱うデータ量を削減することができる。したがって、入出力ピン数がより少なく、容量もより小さいLUTメモリ36を利用することができ、回路部品の簡素化を図ることができる。

#### 【0080】

なお、LUTメモリ36により特定された上位ビットのみの設定階調データに対して、加算器38により表示フレーム階調データの残りの下位ビット(下位桁)を加算することにより補正階調データとし、コントローラ30に入力することが望ましい。このとき、加算器38も変換部を構成する。これにより、上位ビットのみに基づく階調データの変換を行ったことにより生じる誤差を小さくすることができる。10

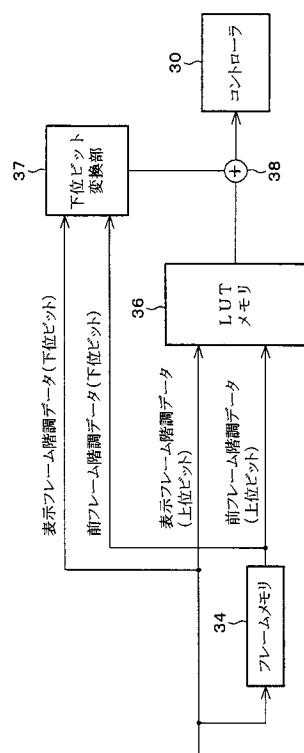

#### 【0081】

また、下位ビットに関しても、前フレーム階調データの下位ビットに基づいて、下位ビット変換部37により表示フレーム階調データの下位ビットを変換し、その変換結果とLUTメモリ36により特定された上位ビットのみの設定階調データとを加算器38によりさらに加算するようにしてもよい。この場合の構成は図19のようになる。図19は、本実施形態の变形例に係るLUTメモリ36周辺の構成を示すブロック図である。このとき、下位ビット変換部37も変換部を構成する。20

#### 【0082】

表示フレーム階調データおよび前フレーム階調データの各下位ビットが示す値が等しい場合は、表示フレーム階調データの下位ビットをそのまま加算するようにしてもよいが、これらが異なる場合には表示フレーム階調データの下位ビットを変換した方がよい。例えば、表示フレーム階調データの下位ビットが前フレーム階調データの下位ビットより大きい場合には、表示フレーム階調データの下位ビットをより大きい値に変換し、逆に、表示フレーム階調データの下位ビットが前フレーム階調データの下位ビットより小さい場合には、表示フレーム階調データの下位ビットをより小さい値に変換した方がよい。

#### 【0083】

具体例を用いて説明すると次のようになる。なお、以下の具体例で用いる2進数の値は説明のためのものであり、必ずしも実際の値として適切であるとは限らない。前フレーム階調データが「00000000」であり、表示フレーム階調データが「10000011」であり、参考形態1のように8ビットすべてに基づいて最適な変換を行うと「11001100」となるとする。そして、上位6ビットを用いて変換を行うと「110000(00)」となつたとする。上位6ビットを用いた変換結果に対して、表示フレーム階調データの下位2ビットである「11」を単純に加算すると「11000011」となり、8ビットすべてに基づいて最適な変換を行った場合の「11001100」と比較して「1001」の誤差が生じる。30

#### 【0084】

これに対して、表示フレーム階調データの下位2ビットである「11」が、前フレーム階調データの下位2ビットである「00」より大きいため、表示フレーム階調データの下位2ビットを下位ビット変換部37により「100」に変換してから加算すると、「11000100」とすることができる。このときの誤差は「1000」となり、上記単純に加算した場合より誤差を小さくすることができる。40

#### 【0085】

下位ビット変換部37は、LUTメモリにより構成してもよく、単純な演算を行う演算回路により構成してもよい。LUTメモリにより構成する場合は、LUTメモリ36の場合と同じように、入力される表示フレーム階調データおよび前フレーム階調データの各下位ビットに基づいて、予め定められて記憶されたルックアップテーブルから特定のデータを出力するようにすればよい。また、下位ビット変換部37から出力するデータは厳密な50

ものでなくともよいため、入力される表示フレーム階調データおよび前フレーム階調データの各下位ビットに対して、予め定めた単純な演算を施して出力するようにすればよい。例えば、表示フレーム階調データの下位ビットと前フレーム階調データの下位ビットとの差の定数倍を出力するようにしてもよい。

#### 【0086】

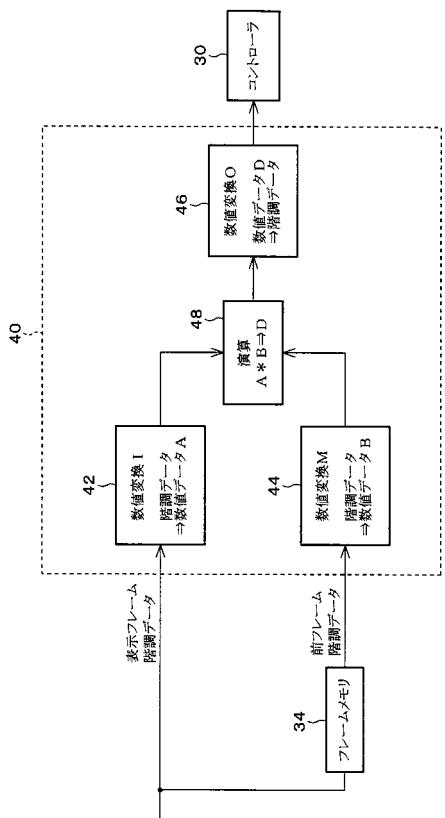

##### 〔参考形態2〕

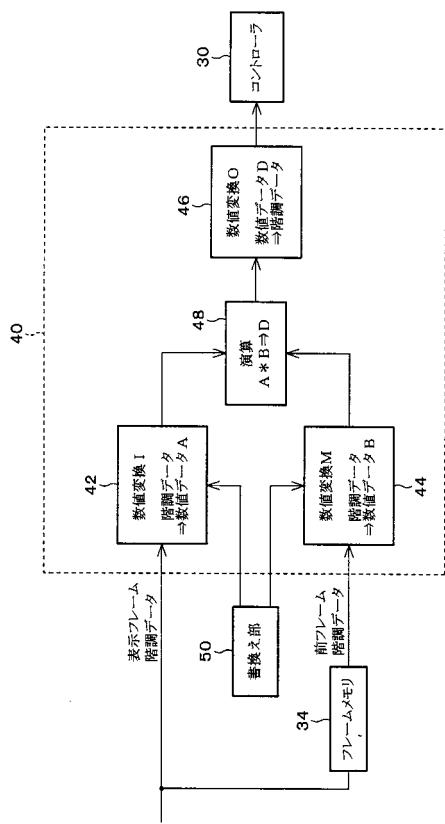

本発明の第2の参考形態について図20から図25に基づいて説明すれば、以下の通りである。本参考形態に係るアクティブマトリクス型の液晶表示装置の構成は、基本的には参考形態1において図1に基づいて説明したものと同等であるため、ここでは相違点のみ説明する。本参考形態に係るアクティブマトリクス型の液晶表示装置では、LUTメモリ 10 32の代わりに変換演算回路40を備えている。

#### 【0087】

表示フレーム階調データおよび前フレーム階調データに基づいて、簡単な演算のみにより適切な階調データへ変換することは難しい。それは、その変換のための演算には、表示すべき階調に応じて液晶セル22の電極間に印加すべき電圧(上記式(4)のVm)、および直前に表示していた階調に対する階調変化に起因する液晶セル22の電極間の容量比(上記式(4)のCm/Cn)が必要となるが、それらの値は階調に関する単純な関数等にあてはまらないためである。

#### 【0088】

そこで、本参考形態の変換演算回路40では、階調データを液晶セル22の電極間の電圧および容量に相当する値に変換するためのテーブルを用い、そのテーブルによる変換結果に対して演算を行い、その演算結果を再び対応する階調データへ変換するという処理を行う。このような処理を行なうことで、簡単な変換および演算で補正階調データを生成することができるようになる。

#### 【0089】

図20は、本参考形態に係る変換演算回路40周辺の構成を示すブロック図である。変換演算回路40は、第1～第3LUTメモリ42・44・46、および演算器48を備えている。変換演算回路40において、表示フレーム階調データは第1LUTメモリ42に入力され、前フレーム階調データは第2LUTメモリ44に入力される。第1LUTメモリ42および第2LUTメモリ44は、それぞれ表示フレーム階調データおよび前フレーム階調データの各階調に対応して予め設定しておいた数値データを記憶しており、入力される各階調データに対応する数値データを出力するようになっている。つまり、第1LUTメモリ42および第2LUTメモリ44では、入力される各階調データを、予め設定された対応する数値データに変換する。以下では、第1LUTメモリ42におけるこの変換を数値変換I、第2LUTメモリ44におけるこの変換を数値変換Mという。数値変換Iおよび数値変換Mによる変換結果としての数値データを一般的にいうときには、それぞれ数値データAおよび数値データBというものとする。第1LUTメモリ42および第2LUTメモリ44からそれぞれ出力される数値データAおよび数値データBは、演算器48に入力される。演算器48では、数値データAおよび数値データBの簡単な演算、例えば四則演算を行う。この演算結果としての数値データを一般的にいうときには、数値データDというものとする。演算器48から出力される数値データDは、第3LUTメモリ46に入力される。第3LUTメモリ46は、演算器48からの数値データDに対応して予め設定しておいた補正階調データを記憶しており、入力される数値データDに対応する補正階調データをコントローラ30に対して出力するようになっている。つまり、第3LUTメモリ46では、入力される数値データDを、予め設定された対応する補正階調データに変換する。以下では、第3LUTメモリ46におけるこの変換を数値変換Oという。

#### 【0090】

変換および演算の例を示す。アクティブマトリクス型の液晶表示装置では、発明が解決しようとする課題の項で説明したように、表示すべき階調を変化させる際に、液晶セル22内の液晶の誘電率が変化することにより、液晶セル22の電圧が変化する(電圧降下ま

10

20

30

40

50

たは電圧上昇が起こる）。このため、表示すべき階調に適した階調電圧を印加することができなくなる。上述したように、アクティブマトリクス型の液晶表示装置では、表示すべき階調に応じて液晶セル22の電極間に印加すべき電圧（上記式（4）のVm）、および直前に表示していた階調に対する階調変化に起因する液晶セル22の電極間の容量比（上記式（4）のCm/Cn）を、簡単な関数で表すことは困難である。そのため、階調データをそのまま用いて演算することにより適切な変換を行うことは難しい。

#### 【0091】

そこで、本参考形態では、階調データを、液晶セル22の電圧の値や液晶セル22の容量の値を反映した数値に一旦変換する。この変換を行うために、表示フレーム階調データおよび前フレーム階調データの各階調に対応した数値データを第1LUTメモリ42および第2LUTメモリ44に予め記憶させておく。そして、入力される表示フレーム階調データおよび前フレーム階調データに基づいて第1LUTメモリ42および第2LUTメモリ44を参照することにより、対応する数値データを得るようにする。10

#### 【0092】

第1LUTメモリ42および第2LUTメモリ44に記憶させておく数値データについては、以下のように定める。ここでは、表示フレーム階調データが示す階調をm、前フレーム階調データが示す階調をnとする。また、m階調が表示されて定常状態となっているときの液晶セル22の電圧をVm、液晶セル22の容量をCm、n階調が表示されて定常状態となっているときの液晶セル22の容量をCnとする。そして、n階調からm階調へ変化させる場合に液晶セル22の電圧として必要な電圧（補正を含んだ電圧）をVpとすると、上記式（4）と同様に、20

$$V_p = C_m / C_n \times V_m \quad \dots \quad (5)$$

とすることができる。

#### 【0093】

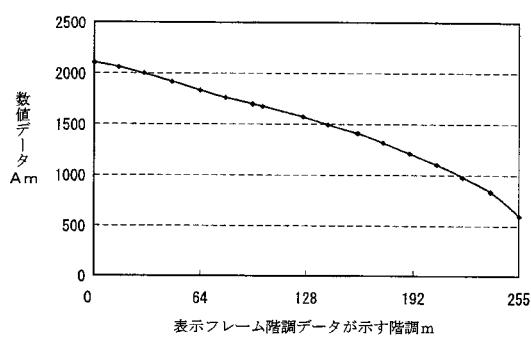

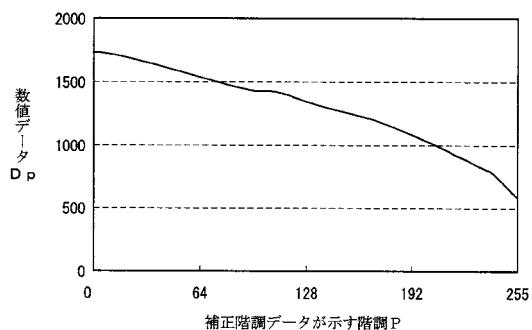

そこで、m階調に対して第1LUTメモリ42のルックアップテーブルに記憶させる数値データをAm = ×Vm×Cmとし、n階調に対して第2LUTメモリ44のルックアップテーブルに記憶させる数値データをBn = 1/Cn×とする。ここで、およびについて後述するが、これらは予め定めた定数である。そして、演算器48における演算としては、数値データAmと数値データBnとの積とする。つまり、演算器48を乗算器とする。その演算結果を数値データDpとすると、Dp = × × Vpとなる。そして、ルックアップテーブルとして第3LUTメモリ46に記憶させる補正階調データが示す階調を、数値データDpに対してP階調とする。このP階調は、コントローラ30を介して液晶セル22に電圧Vpを印加するための階調である。30

#### 【0094】

つまり、変換演算回路40では、

$$m = V_m, C_m \quad \dots \quad (6)$$

$$n = C_n \quad \dots \quad (7)$$

$$A_m = (V_m \times C_m) \times \quad \dots \quad (8)$$

$$B_n = (1 / C_n) \times \quad \dots \quad (9)$$

$$D_p = A_m \times B_n \quad \dots \quad (10)$$

$$P = D_p \quad \dots \quad (11)$$

の変換および演算により階調データの変換を行う。ここで、式（6）および式（8）の変換を第1LUTメモリ42で、式（7）および式（9）の変換を第2LUTメモリ44で、式（10）の演算を演算器48で、式（11）の変換を第3LUTメモリ46で行う。なお、式（6）～式（11）において「」または「」はルックアップテーブルを用いた変換を表し、「=」は演算を表している。また、ここでは式（8）および式（9）もルックアップテーブルを用いた変換に含めているが、これらは演算により行ってよい。さらに、式（6）および式（7）についても演算により行ってよいが、式（6）および式（7）を演算により行う場合、その演算は複雑なものになることが予想されるため、上記変換によることが望ましい。40

## 【0095】

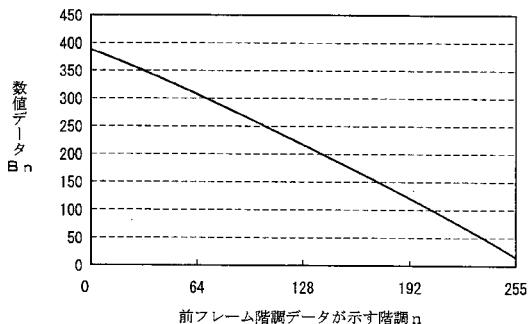

上記変換および演算の内容についてさらに詳しく述べる。なお、ここで用いた液晶パネル10は、図21および図22に示す特性を有するものである。図21は本参考形態で用いた液晶パネル10の定常状態における各階調と階調電圧との関係を示すグラフである。図22は本参考形態で用いた液晶パネル10の定常状態における各階調と液晶セル22の容量(相対値)との関係を示すグラフである。

## 【0096】

$V_m$ および $C_m$ は図21および図22から読み取られる実数値であるため、デジタルの演算には適していない。そこで、これらの値を等倍して桁落ちによる誤差が生じ難いよう 10 にする必要がある。ここで、数値データ $A_m$ は、 $V_m \times C_m$ の値に対応するものであり、この値の階調間における最小差は0.00848であった。したがって、上記誤差をなくすために、例えば $V_m \times C_m$ を120倍することにより上記最小差を約1にする。また、数値データ $B_n$ は、 $1 / C_n$ の値に対応するものであり、この値の階調間における最小差は0.000124であった。したがって、上記誤差をなくすために、例えば $1 / C_n$ を8070倍することにより上記最小差を約1にする。このとき、 $= 120$ 、 $= 8070$ である。

## 【0097】

これら $A_m$ および $B_n$ はそれほど厳密な値でなくてもよく、仮に上記最小差が1未満となり隣り合う階調データ間で数値データ $A_m$ または数値データ $B_n$ が同一の値となった場合でも、それほど大きな誤差は生じない。また、実施形態と同様に、下位ビットを考慮しなく 20 ても十分な補正の効果が得られる場合が多い。これは、上述したように、4階調程度の誤差であればその誤差による表示への影響の程度はごく小さく、実用上問題がないと考えられるためである。

## 【0098】

上記のように、 $= 120$ 、 $= 8070$ とすることにより、上記式(5)、(8)～(10)より、

$$A_m = 120 \times C_m \times V_m$$

$$B_n = 8070 \times (1 / C_n)$$

$$D_p = A_m \times B_n = 8070 \times 120 \times V_p$$

となる。なお、上記各式に基づいて数値データ $A_m$ 、 $B_n$ 、 $D_p$ を算出する際には、小数点以下を切り捨てるものとする。 30

## 【0099】

この場合、図21および図22に示したグラフの値から、数値データ $A_m$ は964( $m=0$ )から219( $m=255$ )の値となり、数値データ $B_n$ は5523( $n=0$ )から7926( $n=255$ )の値となった。これらの値をそのまま用いてもよいが、数値データをシフトしてより小さい値に設定しておくことにより容量の削減を図ることができる。つまり、

$$B_n = 8070 \times (1 / C_m) - 5523$$

$$D_p = A_m \times (B_n + 5523) - 1209537$$

のよう 40 に数値データ $B_n$ をシフトして数値データ $B_n$ の最小値が0となるようにしたもの を用いることが望ましい。これにより、第2LUTメモリ44の容量を削減することができる。なお、数値データ $A_m$ についても数値データ $B_n$ のようにして最小値が0となるよう にシフトさせてもよい。ただし、数値データ $A_m$ は964( $m=0$ )から219( $m=255$ )の値であって10ビット分の容量が必要であるが、シフトさせた場合でも745( $m=0$ )から0( $m=255$ )の値であって同じく10ビット分の容量が必要となる。したがって、容量的には変わらないため、シフトさせなくてもよい。

## 【0100】

このとき、表示フレーム階調データと数値データ $A_m$ との関係、前フレーム階調データと数値データ $B_n$ との関係、数値データ $D_p$ と階調データ $P$ との関係は、それぞれ図23から図25のようになつた。図23から図25は、上記各関係を示す図表である。

## 【0101】

数値データ  $A_m$ ,  $B_n$ ,  $D_p$  をそれぞれ第1 LUTメモリ42、第2 LUTメモリ44、第3 LUTメモリ46に記憶させておく場合、より小さい容量のメモリを用いるようするためには、実施形態と同様に表示フレーム階調データおよび前フレーム階調データの例えば上位6ビットのみに基づいて第1 LUTメモリ42および第2 LUTメモリ44による変換を行うようにしてもよい。この場合でも、補正の効果がほとんど損なわれないようになることができる。

## 【0102】

以上のように、本参考形態では、変換部を構成する変換演算回路40が、表示フレーム階調データおよび前フレーム階調データに基づいて、表示フレーム階調データを補正階調データに変換する。ここで、変換演算回路40には、表示フレーム階調データによって特定される数値データA(第1変換値)、および前フレーム階調データによって特定される数値データB(第2変換値)が予め記憶されている。また、変換演算回路40は、特定された数値データAおよび数値データBに基づく演算により補正階調データを生成する。

10

## 【0103】

これによると、表示フレーム階調データおよび前フレーム階調データから補正階調データを生成する処理において、複雑な演算を要する処理については予め記憶された数値データAおよび数値データBへの変換により行い、簡単な演算が可能な処理については演算により行うことができる。したがって、すべての処理を演算により行うことによる演算の複雑化を抑えて変換演算回路40の構成の簡素化を図ることができる。また、あらゆる階調変化の組み合わせ(表示フレーム階調データが示す階調と前フレーム階調データが示す階調との組み合わせ)に対応した補正階調データを記憶しておくことによる記憶容量の増大を抑えて変換演算回路40の簡素化を図ることができる。

20

## 【0104】

## 〔参考形態3〕

本発明の第3の参考形態について説明すれば、以下の通りである。本参考形態に係るアクティブマトリクス型の液晶表示装置の構成は、基本的には参考形態2において図20に基づいて説明したものと同等であり、参考形態2と異なるのは、変換や演算の内容である。

## 【0105】

30

本参考形態では、上記式(5)を、

$$\begin{aligned} \log(V_p) &= \log(C_m / C_n \times V_m) \\ &= \log(C_m \times V_m) - \log(C_n) \dots (12) \end{aligned}$$

と変形した式(12)を利用する。このように上記式(5)の両辺の対数をとったのは、演算器48による演算を乗算より単純な演算である減算とするためである。したがって、この対数は常用対数でも自然対数でもよい。ここで、 $\times$ を、参考形態2における定数やと同様、デジタル化における桁落ちを防ぐために予め定めた定数として、

$$A_m = \times \log(C_m \times V_m) \dots (13)$$

$$B_n = \times \log(C_n) \dots (14)$$

$$D_p = \times \log(V_p) \dots (15)$$

40

とすると、

$$D_p = A_m - B_n \dots (16)$$

とすることができる。

## 【0106】

つまり、変換演算回路40では、

$$m \quad V_m, C_m \dots (17)$$

$$n \quad C_n \dots (18)$$

$$A_m \quad \times \log(V_m \times C_m) \dots (19)$$

$$B_n \quad \times \log(C_n) \dots (20)$$

$$D_p = A_m - B_n \dots (21)$$

50

P D p

... (22)

の変換および演算により階調データの変換を行う。ここで、式(17)および式(19)の変換を第1LUTメモリ42で、式(18)および式(20)の変換を第2LUTメモリ44で、式(21)の演算を演算器48で、式(22)の変換を第3LUTメモリ46で行う。したがって、演算器48は減算器となる。なお、式(17)～式(22)において「+」または「-」はルックアップテーブルを用いた変換を表し、「=」は演算を表している。また、ここでは式(19)および式(20)もルックアップテーブルを用いた変換に含めているが、これらは演算により行ってもよい。さらに、式(17)および式(18)についても演算により行ってもよいが、式(17)および式(18)を演算により行う場合、その演算は複雑なものになることが予想されるため、上記変換によることが望ましい。

## 【0107】

なお、この表示フレーム階調データの階調mから数値データAmへの変換をデジタル処理で実現するためには、数値データAmはデジタル値を取らなければならないため、参考形態2と同様、数値データAmの値が整数値(デジタル値)となるように定数を設定する。

## 【0108】

ここで、上記数値データAmおよび数値データBnの意味について考え、一般的な液晶セル22に対して数値データAmおよび数値データBnを設定する際の条件について説明する。

## 【0109】

まず、数値データAmおよび数値データBnの意味を考えるために、簡単な場合として数値データAmおよび数値データBnがそれぞれ表示フレーム階調データが示す階調mおよび前フレーム階調データが示す階調nに対して線形(1次式)的に変化する場合を想定し、例えば、補正階調データが示す階調Pが、

$$P = m + a \times (m - n) \dots (23)$$

のような関係にある場合を考える。この場合、表示フレーム階調データがどのような階調であっても、変換後の補正階調データが示す階調Pは、表示フレーム階調データが示す階調mに対して、階調変化による階調の差(m-n)の定数a倍を加算した値になる。以下では、この $a \times (m - n)$ を「負荷」と称する。この場合、

$$A_m = (1 + a) \times m \dots (24)$$

$$B_n = a \times n \dots (25)$$

$$P = D_p \dots (26)$$

となる。

## 【0110】

ここで、表示フレーム階調データが示す階調mと数値データAmとの関係を示す関数A(m)、前フレーム階調データが示す階調nと数値データBnとの関係を示す関数B(n)を想定する。

## 【0111】

まず、数値データAmについて考える。上記負荷を変えるためには上記定数aを変える必要があり、そのためには式(24)より関数A(m)の傾きを変えればよいことがわかる。したがって、表示フレーム階調データが示す階調mにおいて、前フレーム階調データからの階調変化に対して大きい負荷を加えたいところでは、関数A(m)の傾きの絶対値を大きくし、前フレーム階調データからの階調変化に対して小さい負荷を加えたいところでは、関数A(m)の傾きの絶対値を小さくすればよい。なお、ここで「傾きの絶対値」としたのは、関数A(m)の傾きは液晶セル22の表示特性によって正負いずれの値もとり得るからである。具体的には、液晶セル22がノーマリーホワイトの場合は関数A(m)の傾きが負となり、液晶パネル10がノーマリーブラックの場合は関数A(m)の傾きが正となる。

## 【0112】

10

20

30

40

50

実際には、関数 A ( m ) は線形的に変化するものではなく曲線的に変化するものであると予想される。上記のことから、数値データ A m を設定する際には、表示フレーム階調データが示す階調 m において、大きい負荷を加えたいところでは関数 A ( m ) の傾きが大きくなるように数値データ A m を設定し、小さい負荷を加えたいところでは関数 A ( m ) の傾きが小さくなるように数値データ A m を設定すればよい。

#### 【 0 1 1 3 】

また、同じ階調 q ( m = n = q ) で比較したとき、関数 A ( q ) の傾きの絶対値は、常に関数 B ( q ) の傾きの絶対値よりも大きくなるようにする必要がある。関数 A ( q ) の傾きの絶対値と関数 B ( q ) の傾きの絶対値とが等しいと、式 ( 2 1 ) より、階調 q での静止画表示 ( m = n = q の場合 ) と、階調 ( q + 1 ) での静止画表示 ( m = n = ( q + 1 ) の場合 ) との間で補正階調データが示す階調が同じ値を示すことになり静止画表示の階調つぶれを起こすからである。また、関数 A ( q ) の傾きの絶対値が、関数 B ( q ) の傾きの絶対値よりも小さいと、階調が逆転することになるからである。10

#### 【 0 1 1 4 】

さらに、関数 A ( q ) の傾きの絶対値は 1 以上である必要がある。数値データ A m はデジタルデータであるため、1 未満の値は 0 となる。関数 A ( q ) の傾きが 0 となった場合でも上記と同様に静止画表示の階調つぶれを起こすからである。

#### 【 0 1 1 5 】

したがって、数値データ A m の値は表示フレーム階調データ m の値よりも大きくなり、最低でも表示フレーム階調データの 4 倍 ( 2 ビット分 ) 程度の大きさが必要である。20

#### 【 0 1 1 6 】

関数 A ( m ) の傾きの絶対値は最低 1 であり、かつ、上記のように常に関数 B ( q ) の傾きの絶対値よりも大きくなる必要がある。ここで、階調によっては数値データ B n の変化、つまり関数 B ( q ) の傾きの絶対値を大きく、例えば 2 ~ 3 程度にして数値データ B n の補正への寄与を大きくする必要がある場合もある。したがって、関数 A ( m ) の傾きの絶対値は 4 程度の大きさが必要となる場合、つまり、数値データ A m の変化が表示フレーム階調データの変化の 4 倍 ( 2 ビット分 ) 程度の大きさが必要となる場合もある。そして、関数 A ( m ) の傾きの絶対値、つまり数値データ A m の変化の状態が決まると、A 0 ( 表示フレーム階調データの階調 m = 0 に対する数値データ A m ) 、および A max ( 表示フレーム階調データの階調 m が最大値 ( 8 ビットの場合 m = 255 ) に対する数値データ A m ) も決まることになるが、これらは液晶セル 22 の特性により定まるものである。30

#### 【 0 1 1 7 】

次に、数値データ B n について考える。式 ( 2 5 ) より、数値データ B n も前フレーム階調データに対する負荷を決定する値であることがわかる。そして、関数 B ( n ) の傾きの絶対値は、上記のように関数 A ( m ) の傾きの絶対値よりも小さくなる必要がある。

#### 【 0 1 1 8 】

また、階調 q での静止画表示 ( m = n = q の場合 ) を考え、

$$D q = A q - B q \quad \dots \quad ( 2 7 )$$

とすると、式 ( 2 2 ) によって対応付けられる数値データ D q に対応する変換後の補正階調データが示す階調は階調 q となる必要がある。これは、この関係がずれると、静止画表示の際の表示階調がずれることになるからである。40

#### 【 0 1 1 9 】

上記のように関数 A ( m ) の傾きの絶対値と関数 B ( n ) の傾きの絶対値との間に相関関係があることから、数値データ B n の変化の割合により数値データ A m の最大値が決まることになる。また、上記式 ( 2 1 ) において数値データ D p が負の値にならないように、数値データ A m の最小値を数値データ B n の最大値より大きくする必要がある。このように、数値データ A m と数値データ B n とは相関がある値になる。

#### 【 0 1 2 0 】

上記のような条件を考慮して数値データ A m および数値データ B n を設定するようすれば、必ずしも液晶セル 22 ごとにその特性を実験により求めなくてもよくなる。ただし50

、上記の条件を考慮しても数値データ A m および数値データ B n を一義的に定めることはできないため、実際の表示状態を確認しながら数値データ A m および数値データ B n を設定する必要がある。

#### 【 0 1 2 1 】

図 2 1 および図 2 2 に示した特性を有する液晶パネル 1 0 において、表示フレーム階調データが示す階調 m と数値データ A m との関係、前フレーム階調データが示す階調 n と数値データ B n との関係、および数値データ D p と変換後の補正階調データが示す階調 P との関係を示すグラフの一例をそれぞれ図 2 6 から図 2 8 に示す。

#### 【 0 1 2 2 】

以上のように、本参考形態では、参考形態 2 と同様に、変換部を構成する変換演算回路 4 0 が、表示フレーム階調データおよび前フレーム階調データに基づいて、表示フレーム階調データを補正階調データに変換する。ここで、変換演算回路 4 0 には、表示フレーム階調データによって特定される数値データ A ( 第 1 変換値 ) 、および前フレーム階調データによって特定される数値データ B ( 第 2 変換値 ) が予め記憶されている。また、変換演算回路 4 0 は、特定された数値データ A および数値データ B に基づく演算により補正階調データを生成する。

#### 【 0 1 2 3 】

これにより、参考形態 2 の場合と同様の効果を得ることができる。さらに、本参考形態の場合は演算器 4 8 を減算器とすることができる、変換演算回路 4 0 の構成のより簡素化を図ることができる。

#### 【 0 1 2 4 】

##### 〔 参考形態 4 〕

本発明の第 4 の参考形態について図 2 9 に基づいて説明すれば、以下の通りである。本参考形態に係るアクティブマトリクス型の液晶表示装置の構成は、基本的には参考形態 2 および3 において図 2 0 に基づいて説明したものと同等であるため、ここでは相違点のみ説明する。

#### 【 0 1 2 5 】

本参考形態に係るアクティブマトリクス型の液晶表示装置では、さらに書換え部 5 0 が設けられているとともに、変換演算回路 4 0 において、第 1 L U T メモリ 4 2 および第 2 L U T メモリ 4 4 に設定されている数値データ A の群および数値データ B の群を書換え部 5 0 により書き換えることができるようになっている。

#### 【 0 1 2 6 】

このように、第 1 L U T メモリ 4 2 および第 2 L U T メモリ 4 4 に設定されている各数値データの群を書き換え可能とすることにより、特性が異なる液晶パネル 1 0 を用いる場合に変換演算回路 4 0 を液晶パネル 1 0 の特性に適応させることができ、変換演算回路 4 0 に汎用性をもたせることができる。

#### 【 0 1 2 7 】

書換え部 5 0 は、数値データ A の群および数値データ B の群のうちの少なくとも一方の群を書き換えることができればよい。これにより、例えば用いる液晶パネル 1 0 が同一種類のものの間で、個体差による特性のバラツキがあるような場合に、そのバラツキの影響に変換演算回路 4 0 を適応させて、表示状態の最適化を図ることができる。

#### 【 0 1 2 8 】

さらに、表示モード、用いる液晶材料、パネル設計等が異なる液晶パネル 1 0 にも適応できるようにするために、両方の群を書き換え可能とし、適応できる範囲を広くしておくことが望ましい。

#### 【 0 1 2 9 】

以上のように、変換部を構成する変換演算回路 4 0 において、記憶している数値データ A の群 ( 第 1 変換値の群 ) および数値データ B の群 ( 第 2 変換値の群 ) の少なくとも一方を外部から書き換え可能であることが望ましい。

#### 【 0 1 3 0 】

10

20

20

30

40

50

**[参考形態5]**

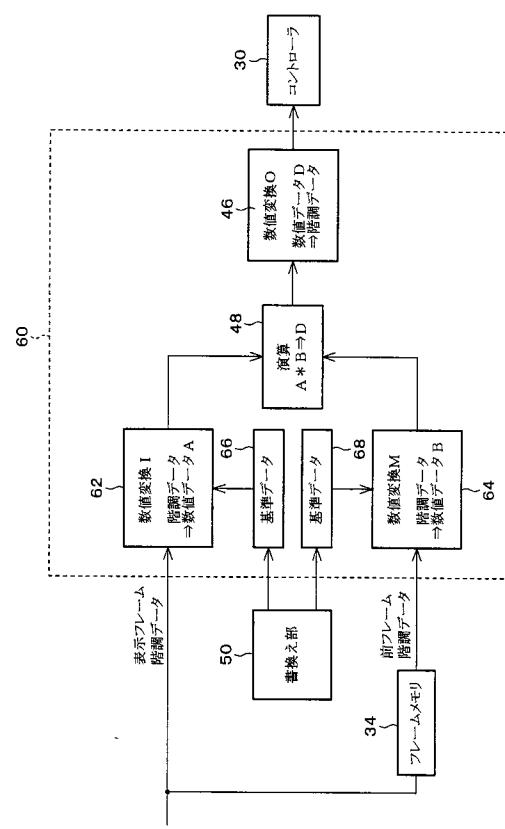

本発明の第5の参考形態について図30に基づいて説明すれば、以下の通りである。本参考形態に係るアクティブマトリクス型の液晶表示装置の構成は、基本的には参考形態2および3において図20に基づいて説明したものと同等であるため、ここでは相違点のみ説明する。

**[0131]**

本参考形態に係るアクティブマトリクス型の液晶表示装置では、図20の変換演算回路40に相当する変換演算回路60において、第1LUTメモリ42の代わりに第1補間部62および第1基準データメモリ66が設けられ、第2LUTメモリ44の代わりに第2補間部64および第2基準データメモリ68が設けられている。第1補間部62および第2補間部64には、それぞれ第1基準データメモリ66および第2基準データメモリ68から後述する基準データが送られるようになっている。10

**[0132]**

変換演算回路60では、各階調に対応する数値データAmおよび数値データBmがすべて記憶されているのではなく、第1基準データメモリ66および第2基準データメモリ68にそれぞれ予め記憶された所定階調おきの数値データAmおよび数値データBmである基準データに基づいて、第1補間部62および第2補間部64において演算により補間することによって各階調に対応する数値データAmおよび数値データBmを算出するようになっている。つまり、表示フレーム階調データや前フレーム階調データが入力されると、第1補間部62や第2補間部64にて補間ににより算出した数値データAmや数値データBmを用いて数値変換Iや数値変換Mを行う。20

**[0133]**

基準データは、例えば16階調おきに設定する場合、0階調、16階調、32階調、…、240階調、255階調に対応する数値データAmおよび数値データBmを採用することができる。そして、各基準データの間の階調に対応する数値データAmおよび数値データBmは、当該各基準データを例えれば線形補間することにより求めることができる。例えば階調m( $0 < m < 16$ )に対応する数値データAmは、

$$Am = A_0 + (A_{16} - A_0) / 16 \times m$$

により求めることができる。ここで、A0およびA16は、それぞれ0階調および16階調に対応する数値データAmである。30

**[0134]**

また、さらに、参考形態4と同様に書換え部50を設け、第1基準データメモリ66内の基準データの群および第2基準データメモリ68内の基準データの群のうちの少なくとも一方の群を書換え部50により外部から書き換えることができるようにしておくことが望ましい。これにより、特性が異なる液晶パネル10に変換演算回路60を適応させることができ、変換演算回路60に汎用性をもたせることができる。

**[0135]**

以上のように、本参考形態では、参考形態2および3と同様に、変換部を構成する変換演算回路60が、表示フレーム階調データおよび前フレーム階調データに基づいて、表示フレーム階調データを補正階調データに変換する。ここで、変換演算回路60には、表示フレーム階調データによって特定される基準データ(第1基準値)、および前フレーム階調データによって特定される基準データ(第2基準値)が予め記憶されている。また、変換演算回路60は、特定された各基準データに基づいて補間を行うことにより、数値データA(第1変換値)および数値データB(第2変換値)を算出する。そして、変換演算回路60は、特定された数値データAおよび数値データBに基づく演算により補正階調データを生成する。40

**[0136]**

これによると、各階調に対応する数値データAおよび数値データBをすべて記憶させておく必要がないため、変換演算回路60に必要な記憶容量を小さくすることができる。なお、補間は比較的簡単な演算であるため、補間を行うための第1補間部62および第2補

10

20

30

40

50

間部 64 は比較的簡単な回路構成で実現可能である。したがって、第 1 補間部 62 および第 2 補間部 64 を含むことによる回路構成の複雑化も抑えることができる。

#### 【0137】

##### 〔参考形態 6〕

本発明の第 6 の参考形態について図 34 から図 39 に基づいて説明すれば、以下の通りである。

#### 【0138】

本発明に係る液晶表示装置において、LUT メモリやフレームメモリの容量削減は、コントローラのチップサイズの縮小（ピン数削減等も含む）などと関連しており、考慮しておくことが好ましい。上述したように、実施形態においては、LUT メモリ 36 によって階調データの上位ビットのみを変換する構成（図 16 参照）を開示し、参考形態 2、4、5においては、演算器 48 を導入することにより LUT メモリの容量削減を可能とする構成（図 20、図 29、図 30 参照）を開示した。10

#### 【0139】

本参考形態では、実施形態のように、変換するビット数を少なくして LUT メモリやフレームメモリの容量削減を図るとともに、表示フレーム階調データとして LUT メモリ 36 に入力される階調データ、および前フレーム階調データとしてフレームメモリ 34 に格納されるデータが、予め、各階調データが示す階調がある閾値以上の場合は上位数ビット（もとの階調データのビット数より小さいビット数）に変換され、ある閾値未満の場合は下位数ビット（もとの階調データのビット数より小さいビット数）に変換される。そして、その変換された階調データに基づいて、LUT メモリ 36 における階調データの変換が行われる。20

#### 【0140】

階調データが 8 ビットである場合を例として、本参考形態の構成による効果について説明する。まず、この効果を説明するために、LUT メモリによる変換を演算で置き換えた場合の実際上の課題を確認する。上述しているように、本発明の目的は、1 フレーム時間経過したときの表示輝度が目的の階調輝度とほぼ一致するように階調データを補正することである。この補正内容としては、電荷モデルに基づいて単純に設定できる部分もあるが、液晶分子の応答特性に対する最適化が必要な部分も多い。我々は検討の結果、この液晶分子の特性により左右される部分をも反映できる演算を見いだしているが、液晶モードや階調電圧等の機種ごとの条件によっては、演算に用いる最適なパラメータが順当に見出されないこともある。LUT メモリを用いると、このような部分をも常に補正できる汎用性および自由度を得ることができる。30

#### 【0141】

ところで、階調データの上位ビットのみを用いて階調データの変換を行う方法について実施形態で説明した。例えば 8 ビットの階調データの上位 4 ビットを用いることには、16 階調刻みで階調変換がなされることになる。これは現実にメモリサイズを劇的に減少させるが、表示品位上懸念すべき点もある。すなわち、8 ビットの階調データが示す 256 階調のうち、例えば 224 階調と 239 階調のように非常に明るい階調の領域では、それぞれの階調を同一視しても表示品位上あまり問題にならないが、例えば 0 階調と 15 階調のように暗い階調の領域では、人間の視覚の特性では明らかに異なった表示として認識される。したがって、暗い領域における 16 階調の差が区別できないと、それがたとえ 1 フレームであっても表示品位を著しく低下させ、問題となることがある。40

#### 【0142】

例えばテレビ映像では、暗い画像が動く場面は映画等で多用されているため、上記のような表示品位の低下の問題を有する液晶表示装置でテレビ映像を表示すると、写りの悪いディスプレイとして認識されるおそれがある。我々は、表示シーンによっては、2 階調差を無視した状態、すなわち下位 1 ビットのみを無視した状態までしか許容できないことがあることに気付いた。逆に、ノート型パソコン等のように、もともとバランスのよい階調と、データ重視の画像を表示するためのディスプレイでは上記の問題は起こりにくい。50

たがって、このような用途に用いられる液晶表示装置では、実施形態のように、思い切って下位数ビットを削るようにすることも可能となる。

#### 【0143】

図34は、階調とビットとの関係を表した図表である。8ビットの階調データの上位4ビットのみを用いる場合、0階調から255階調への階調変化と、0階調から240階調への階調変化とは、いずれも、上位4ビットが[0, 0, 0, 0]の前フレーム階調データと、上位4ビットが[1, 1, 1, 1]の表示フレーム階調データとに基づいて変換される同じ補正階調データを用いることになる。このとき、同じ補正階調データを用いることによる輝度の誤差は例えれば10%程度となる。一方、255階調から31階調への階調変化と、255階調から16階調への階調変化とは、いずれも、上位4ビットが[1, 1, 1, 1]の前フレーム階調データと、上位4ビットが[0, 0, 0, 1]の表示フレーム階調データとに基づいて変換される同じ補正階調データを用いることになる。このとき、同じ補正階調データを用いることによる輝度の誤差は例えば70%以上になることがあります、そのような液晶表示装置は実際には使用できないような場合もある。

#### 【0144】

なお、一般に階調輝度は2.2で合わせられている、つまり輝度が階調の2.2乗に比例するように設定されているため、同じ階調数のずれでも、暗い領域ほど輝度の変化率が大きくなる。図43は、階調と輝度との一般的な関係を示す図表である。255階調の輝度に対する240階調の輝度はその変化率が約12.5%であるのに対し、31階調の輝度に対する16階調の輝度はその変化率が約76%となる。

#### 【0145】

本参考形態では、LUTメモリを用いて階調データを変換することによる汎用性および自由度を失うことなく、上記のように特に暗い階調の領域で階調差が失われてしまわないようにしつつ、装置全体におけるメモリ容量の削減を図る構成について説明する。

#### 【0146】

本参考形態に係るアクティブマトリクス型の液晶表示装置の構成は、基本的には実施形態において図16に基づいて説明したものと同等であるため、ここでは相違点のみ説明する。本参考形態に係るアクティブマトリクス型の液晶表示装置では、図35に示すように、LUTメモリ36の第1入力に対する階調データの入力側、およびフレームメモリ34に対する階調データの入力側にそれぞれ第1桁変換部74a・74bが設けられており、30 LUTメモリ36とコントローラ30との間に第2桁変換部76が介在している。表示フレーム階調データは第1桁変換部74aにて変換されてLUTメモリ36の第1入力に入力され、表示フレーム階調データの予め定められた下位数ビットはラインメモリ78を介して第2桁変換部76に送られる。前フレーム階調データは第1桁変換部74bにて変換されてフレームメモリ34に一旦格納され、LUTメモリ36の第2入力に入力される。図35は、本参考形態に係るLUTメモリ36周辺の構成を示すブロック図である。

#### 【0147】

ここで、本参考形態における表記について説明する。 [...] 内の記号a~h、A~H、v~zは、階調データの各ビットの値（具体的には「0」または「1」）を表している。ここで、小文字で表したa~hは表示フレーム階調データとしてLUTメモリ36に入力される階調データを示しており、大文字で表したA~Hは前フレーム階調データとしてLUTメモリ36に入力される階調データを示している。 [...] 内の記号FLは、フラグとして設定されたビットの値（具体的には「0」または「1」）を表している。 [...] 内の記号または数字に付した添字は、その記号または数字が階調データの第何ビットのものであるかを表している。つまり、例えば「[0<sub>5</sub>]」は、階調データの第5ビットが「0」であることを表しており、「[a<sub>7</sub>]」は、階調データの第7ビットが「a」であることを表している。また、「P」は、階調データが示す階調を表している。

#### 【0148】

図36および図37は、図35において丸付数字1から7を付した部分における階調データの内容を示す概念図である。丸付数字1で示される8ビットの階調データは、第1桁

変換部 7 4 b に入力され、第 1 桁変換部 7 4 b によりその階調データが示す階調 P に応じて異なる変換が施される。すなわち、予め定めた階調を基準として、階調データが示す階調 P が上記予め定めた階調以上である場合と、階調 P が上記予め定めた階調未満である場合とで、その階調データに対して異なる変換を施す。なお、丸付数字 4 で示される 8 ビットの階調データも、第 1 桁変換部 7 4 a に入力され、第 1 桁変換部 7 4 a により第 1 桁変換部 7 4 b と同様の変換が施される。以下では、主に第 1 桁変換部 7 4 b に関して説明する。

#### 【 0 1 4 9 】

上記予め定めた階調は、例えば 3 2 階調であり、3 2 階調未満の領域は暗い階調であつて、この領域については階調データの変換の際に下位ビットを無視すると上述した表示品位の低下の問題が顕著になるものとする。なお、階調 P が 3 2 階調未満であるか否かは、 $[ A_7, B_6, C_5 ] = [ 0_7, 0_6, 0_5 ]$  であるか否かによって判別することができる。

#### 【 0 1 5 0 】

第 1 桁変換部 7 4 b では、次のような処理が行われる。階調 P が 3 2 階調未満である場合には、上位 2 ビット、つまり第 7 および第 6 ビットの  $[ A_7, B_6 ]$  を削除するとともに、第 5 ビットをフラグとして用い、階調 P が 3 2 階調未満であったことを、第 5 ビットを  $[ 0_5 ]$  とすることにより表す。このように変換すると、階調データは丸付数字 2 のようになる。このように変換した丸付数字 2 の階調データは、8 ビットから 6 ビットに縮小されているものの、もとの階調データが有していた情報をすべて保持していることになる。

#### 【 0 1 5 1 】

一方、階調 P が 3 2 階調以上である場合には、階調データを下位側に 3 ビット分シフトさせてもとの下位 3 ビット、つまり第 2 から第 0 ビットの  $[ F_2, G_1, H_0 ]$  を削除するとともに、第 5 ビットをフラグとして用い、階調 P が 3 2 階調以上であったことを、第 5 ビットを  $[ 1_5 ]$  とすることにより表す。このように変換すると、階調データは丸付数字 3 のようになる。このように変換した丸付数字 3 の階調データは、8 ビットから 6 ビットに縮小され、3 2 階調以上の領域では階調データの変換に大きく影響しないと考えられる下位 3 ビット分の情報が削除されて 8 階調刻みで記憶されることになる。

#### 【 0 1 5 2 】

第 1 桁変換部 7 4 b にて変換された階調データは、フレームメモリ 3 4 により 1 フレーム時間遅延され、前フレーム階調データとして LUT メモリ 3 6 に入力される。

#### 【 0 1 5 3 】

また、表示フレーム階調データとしての階調データも、第 1 桁変換部 7 4 a により上記と同様に 8 ビットから 6 ビットに縮小され LUT メモリ 3 6 に入力される。なお、表示フレーム階調データの下位 3 ビット、つまり第 2 から第 0 ビットの  $[ f_2, g_1, h_0 ]$  はラインメモリ 7 8 に入力される。

#### 【 0 1 5 4 】

図 3 8 は、LUT メモリ 3 6 の入出力ビット数を概念的に示した概念図である。上述したように、LUT メモリ 3 6 は、前フレーム階調データとして 6 ビット分の入力、表示フレーム階調データとして 6 ビット分の入力を有している。また、これらの入力によって特定される設定階調データとして、6 ビットの階調データが LUT メモリ 3 6 に設定されており、LUT メモリ 3 6 は 6 ビット分の出力を有している。

#### 【 0 1 5 5 】

LUT メモリ 3 6 に設定されている設定階調データは、図 3 7 に示す丸付数字 5 のようになっている。ここで、第 5 ビットにはフラグである  $[ F_L_5 ]$  が設定されており、その設定階調データ、すなわち第 4 から第 0 ビットの  $[ v_4, w_3, x_2, y_1, z_0 ]$  が示す階調が 3 2 階調未満であるか、3 2 階調以上であるかを表している。ここでは、 $F_L = 0$  の場合、その設定階調データが示す階調が 3 2 階調未満であり、 $F_L = 0$  ( $F_L = 1$ ) の場合、その設定階調データが示す階調が 3 2 階調以上であるものとする。

10

20

30

40

50

## 【0156】

LUTメモリ36から出力される設定階調データは、第2桁変換部76に入力される。第2桁変換部76では、入力される設定階調データの第5ビットに設定されたフラグであるFLの値に応じた桁変換を行う。FL=0の場合、その設定階調データは32階調未満であるため、第7から第5ビットを[0<sub>7</sub>, 0<sub>6</sub>, 0<sub>5</sub>]に設定し、丸付数字6のような8ビットの補正階調データに変換する。FL=0の場合、その設定階調データは32階調以上であるため、丸付数字5の設定階調データを上位側に3ビット分シフトさせるとともに、第2から第0ビットの下位3ビットの値として、ラインメモリ78にて一旦記憶された[f<sub>2</sub>, g<sub>1</sub>, h<sub>0</sub>]を付加し、丸付数字7のような8ビットの補正階調データに変換する。下位3ビットの値を付加するのは、明るい階調の領域についてより安定した静止画を得るために、および表示フレーム階調データの下位3ビットが有していた情報を付加することにより6ビットのルックアップテーブルによる変換を補うためである。このように、ラインメモリ78やラインメモリ78にて接続される経路は、表示品位のさらなる向上のために設けるものであり、省略することも可能である。

## 【0157】

このようにして変換して得られた補正階調データは、コントローラ30に送られる。

## 【0158】

LUTメモリ36には、表示フレーム階調データ（前フレーム階調データ）が示す階調Pが暗い領域の場合には表示フレーム階調データ（前フレーム階調データ）の下位5ビット、および階調Pが暗い領域であることを示すフラグが入力され、階調Pが明るい領域の場合には表示フレーム階調データ（前フレーム階調データ）の上位5ビット、および階調Pが明るい領域であることを示すフラグが入力されるため、LUTメモリ36にこれらに基づく適切な設定階調データを設定しておくことにより適切な変換が可能である。

## 【0159】

上記の構成では、フレームメモリ34には、その設定階調データが示す階調Pが32階調未満の場合はそのままの階調を表す階調データが、32階調以上の場合は8階調刻みの階調データが格納されることになる。そして、フレームメモリ34は、1画素あたりの容量が6ビットとなる。また、上記の構成では、LUTメモリ36は図38に示したように、前フレーム階調データが6ビット、表示フレーム階調データが6ビット、出力される設定階調データが6ビットであることから、1画素当たりの容量が6+6+6=18ビットとなる。参考形態1のような構成（図1参照）では、フレームメモリ34の1画素あたりの容量が8ビットであり、LUTメモリ32の1画素あたりの容量が8+8+8=24ビットである。したがって、本参考形態の構成により、参考形態1の構成に対して、LUTメモリ36の容量を1/64に削減することができる。なお、フレームメモリ34の容量は1/4に削減することができる。

## 【0160】

また、液晶表示装置の用途によっては、256分の1階調の精度は必要としないが、64階調程度までは十分な精度を保持したい場合も考えられる。もし64階調未満では表示フレーム階調データおよび前フレーム階調データの最下位1ビットをLUTメモリ36による変換に考慮する必要があれば、上記の構成において、64階調未満は2階調刻みで、64階調以上は8階調刻みでLUTメモリ36に表示フレーム階調データおよび前フレーム階調データを入力させるようにしてもよい。このとき、図36の丸付数字2に代えて、図39の丸付数字2'を適用すればよい。階調Pが64階調未満であるか否かは、[A<sub>7</sub>, B<sub>6</sub>]=[0<sub>7</sub>, 0<sub>6</sub>]であるか否かによって判別することができる。階調Pが64階調未満である場合には、上位2ビット、つまり第7および第6ビットの[A<sub>7</sub>, B<sub>6</sub>]を削除するとともに、残りの下位6ビットを下位側に1ビット分シフトさせて第0ビットの[H<sub>0</sub>]を削除する。また、第5ビットをフラグとして用い、階調Pが64階調未満であったことを、第5ビットを[0<sub>5</sub>]とすることにより表す。

## 【0161】

この場合も、安定した静止画を得るために、明るい階調の領域では下位3ビットの[f

10

20

30

40

50

$_{_2}, g_1, h_0]$  を、暗い階調の領域では下位 1 ビットの [  $h_0$  ] をラインメモリ 7 8 等にて一旦記憶し、第 2 衍変換部 7 6 において設定階調データに付加するようにすることができる。また、この場合も、上記と同様に容量を削減することができる。

#### 【 0 1 6 2 】

以上のように、本参考形態では、変換部を構成する LUT メモリ 3 6 および第 2 衍変換部 7 6 が、表示フレーム階調データおよび前フレーム階調データに基づいて、表示フレーム階調データを補正階調データに変換する。また、衍変換部を構成する第 1 衍変換部 7 4 a・7 4 b が、表示フレーム階調データおよび前フレーム階調データの衍を変換する。この第 1 衍変換部 7 4 a・7 4 b は、階調データ（表示フレーム階調データ、前フレーム階調データ）が示す階調が予め定めた閾値より明側、すなわち明るい輝度に対応する階調である場合にはその階調データの下位ビット（下位衍）を削除し、階調データが示す階調が予め定めた閾値より暗側、すなわち暗い輝度に対応する階調である場合にはその階調データの上位ビット（上位衍）を削除することで、その階調データのビット数（衍数）が小さくなるように変換する。そして、上記変換部には、第 1 衍変換部 7 4 a・7 4 b にてそれぞれ変換された表示フレーム階調データと前フレーム階調データとによって特定される設定階調データが予め記憶されており、特定した設定階調データに基づいて補正階調データを生成する。

#### 【 0 1 6 3 】

上記の構成では、LUT メモリ 3 6 における設定階調データを記憶するための容量の削減を図ることができる。また、階調データのうち、LUT メモリ 3 6 による変換により大きく影響する部分を残して階調データのビット数を小さくすることができ、表示品位が低下することを抑制することができる。

#### 【 0 1 6 4 】

また、本液晶表示装置に入力される階調データは、第 1 衍変換部 7 4 a を介してフレームメモリ 3 4 の第 1 入力に入力されるとともに、第 1 衍変換部 7 4 b を介してフレームメモリ 3 4 に入力され、フレームメモリ 3 4 から LUT メモリ 3 6 の第 2 入力に入力されることが好ましい。上記の構成では、フレームメモリ 3 4 に対して、ビット数が小さくなるように第 1 衍変換部 7 4 a・7 4 b にて変換された後の階調データが入力される。したがって、フレームメモリ 3 4 における容量の削減をも図ることができる。ただし、入力される階調データが、フレームメモリ 3 4 を介して第 1 衍変換部 7 4 b に入力され、第 1 衍変換部 7 4 b から LUT メモリ 3 6 の第 2 入力に入力されるようにすることも可能である。

#### 【 0 1 6 5 】

第 1 衍変換部 7 4 a・7 4 b により階調データの下位ビットまたは上位ビットを削除して、その階調データのビット数が小さくなるように変換する際には、変換した階調データに下位ビットまたは上位ビットの何れを削除したかを示すフラグ（フラグビット）を設定する。LUT メモリ 3 6 では、第 1 衍変換部 7 4 a・7 4 b により削除されなかつた残りのビットおよび設定されたフラグに基づいて予め記憶されている設定階調データが特定される。この設定階調データは、LUT メモリ 3 6 に入力された階調データのビット数（6 ビット）からフラグとしてのビットを除いたビット数（5 ビット）に相当するビット数からなり、補正階調データにおいて階調を示すための部分（[  $v_4, w_3, x_2, y_1, z_0$  ]）と、その階調を示すための部分が補正階調データにおいて下位ビットに対応するものであるか、上位ビットに対応するものであるかを示すフラグ（フラグビット）（FL）とからなっている。第 2 衍変換部 7 6 では、このフラグに基づいて、設定階調データにおける上記階調を示すための部分を、必要に応じてシフト等させることにより、補正階調データの対応するビットに設定するとともに、残りのビットを予め定めた値、例えば「0」で埋めてもとの階調データのビット数に等しいビット数に復元する。このとき、補正階調データの下位ビットを埋める際には、表示フレーム階調データの下位ビットを用いてよい。

#### 【 0 1 6 6 】

なお、階調データは、通常、その階調データが示す階調が暗側であるほど、その階調デ

10

20

30

40

50

ータは小さい値、すなわちより下位側のビットのみで表すことができる値であり、明側になるほど、その階調データは大きい値、すなわちより上位側のビットを含めて表される値となる。

#### 【0167】

本参考形態では、桁変換部を構成する2つの第1桁変換部74a・74bを備えた構成について説明したが、桁変換部を構成する1つの第1桁変換部を設け、その第1桁変換部の出力をLUTメモリ36の第1入力およびフレームメモリ34に入力するようにしてもよい。

#### 【0168】

以上のように、実施形態欄において説明した液晶表示装置は、画素を有し、前記画素にフレームごとに階調データに基づく階調電圧を印加することで階調表示を行う液晶表示装置であって、表示すべきフレームの階調データおよび直前のフレームの階調データが入力され、表示すべきフレームの階調データを変換して出力する変換部と、前記変換部から出力される変換された階調データに基づいて階調電圧を前記画素に印加する駆動部と、前記画素に含まれ、印加された階調電圧により階調表示が可能な液晶セルとを備え、前記変換部には、表示すべきフレームの階調データと直前のフレームの階調データとによって特定される出力すべき階調データが予め記憶されていることを特徴としている。10

#### 【0169】

上記の構成では、表示すべきフレームの階調データと直前のフレームの階調データによって特定される所定の階調データを変換部によって出力し、その階調データに応じた階調電圧を画素に印加することができる。したがって、直前のフレームと表示すべきフレームとの間の液晶セルの容量（電気容量）の変化による影響を考慮した階調電圧を画素に印加することができる。これにより、液晶セルの容量が変化することによる階調表示のずれを補正することができる。その結果、特に動画表示時などにおいて入力される階調データをより忠実に再現した表示が可能になる。20

#### 【0170】

実施形態欄において説明した液晶表示装置は、上記の液晶表示装置において、さらに、前記変換部が第1入力および第2入力を有し、前記第2入力には、入力される階調データを記憶してその階調データを1フレーム分遅らせて出力する記憶部が接続されており、階調データは、前記第1入力に入力されるとともに、前記記憶部を介して前記第2入力に入力されることが好ましい。30

#### 【0171】

上記の構成では、表示すべきフレームの階調データを変換部の第1入力に直接入力するとともに記憶部を介して変換部の第2入力に入力する。この記憶部は、入力された階調データを1フレーム分遅らせて出力するものである。これにより、簡素な構成で表示すべきフレームの階調データと直前のフレームの階調データとを変換部に入力することができる。40

#### 【0172】

実施形態欄において説明した液晶表示装置は、上記変換部が第1入力および第2入力を有する液晶表示装置において、さらに、前記変換部が、前記第1入力および第2入力に入力される階調データによって特定されるアドレスに記憶されている階調データを出力するメモリであることが好ましい。

#### 【0173】

上記の構成では、演算などの処理を介すことなく階調データの変換を行うことができる。したがって、階調データを変換する処理を設けることによる処理速度の低下を抑制することができる。

#### 【0174】

実施形態欄において説明した液晶表示装置は、上記何れかの液晶表示装置において、さらに、前記駆動部が出力する階調電圧の範囲が、静止画像を表示する際の前記液晶セルの階調表示範囲に対応する階調電圧の範囲を含み、かつ、その範囲よりも広いことが好まし50

い。

**【0175】**

液晶セルによる表示を例えば階調表示範囲の上限（下限）へ他の階調から変化させるような場合、液晶セルの容量の変化による影響を補正するためにはその上限（下限）に対応する階調電圧以上（以下）の電圧を印加させることが好ましい場合がある。上記の構成では、このような場合に対応できるため上記の補正を適切に行うことができる。

**【0176】**

実施形態欄において説明した液晶表示装置は、上記何れかの液晶表示装置において、さらに、前記変換部に記憶されている階調データが、表示すべきフレームの階調データを静止画像として表示する場合の階調電圧を  $V_m$ 、表示すべきフレームの階調データを静止画像として表示した場合の前記液晶セルの電気容量を  $C_m$ 、直前のフレームの階調データを静止画像として表示した場合の前記液晶セルの電気容量を  $C_n$  としたとき、

$$V' = C_m / C_n \times V_m$$

で求められる階調電圧に対応する階調データであることが好ましい。

**【0177】**

上記の構成では、液晶セルの容量の変化による影響を補正することができる変換部から出力すべき階調データを、上式に基づいて容易に設定することができる。

**【0178】**

実施形態欄において説明した液晶表示装置は、画素を有し、前記画素にフレームごとに階調データに基づく階調電圧を印加することで階調表示を行う液晶表示装置であって、表示すべきフレームの階調データおよび直前のフレームの階調データに基づいて、表示すべきフレームの階調データを補正階調データに変換する変換部と、前記変換部にて変換された補正階調データに基づいて階調電圧を前記画素に印加する駆動部と、前記画素に含まれ、印加された階調電圧により階調表示が可能な液晶セルとを備え、前記変換部には、表示すべきフレームの階調データと直前のフレームの階調データとによって特定される設定階調データが予め記憶されており、特定した設定階調データに基づいて補正階調データを生成することを特徴としている。

**【0179】**

このように、変換部は変換して出力する階調データそのものを記憶しているのではなく、記憶している階調データに対して簡単な演算等を施して出力するようになっていてよい。

**【0180】**

この液晶表示装置において、前記変換部は、表示すべきフレームの階調データの上位桁および直前のフレームの階調データの上位桁に基づいて設定階調データを特定し、表示すべきフレームの階調データの上位桁を特定した設定階調データに置き換えて変換し、その変換結果に基づいて補正階調データを生成することが好ましい。

**【0181】**

上記の構成では、階調データの予め定めた上位桁（上位ビット）に基づいて階調データの変換を行う。これにより、変換部で扱うデータ量を削減することができ、変換部の簡素化を図ることができる。例えば、変換部における補正階調データを記憶する部分の容量の削減を図ることができる。

**【0182】**

実施形態欄において説明した液晶表示装置は、上記上位桁に基づく変換を行う液晶表示装置において、さらに、前記変換部が、表示すべきフレームの階調データの上位桁および直前のフレームの階調データの上位桁に基づいて、表示すべきフレームの階調データの上位桁を変換するとともに、変換された表示すべきフレームの階調データの上位桁と、表示すべきフレームの階調データの下位桁とを加算することにより補正階調データを生成することが好ましい。

**【0183】**

上記の構成では、階調データの残りの下位桁（下位ビット）を加算することにより、上

10

20

30

40

50

位桁のみに基づく変換を行ったことによる誤差を小さくすることができる。

**【0184】**

あるいは、実施形態欄において説明した液晶表示装置は、上記上位桁に基づく変換を行う液晶表示装置において、さらに、前記変換部が、表示すべきフレームの階調データの上位桁および直前のフレームの階調データの上位桁に基づいて、表示すべきフレームの階調データの上位桁を変換するとともに、表示すべきフレームの階調データの下位桁および直前のフレームの階調データの下位桁に基づいて、表示すべきフレームの階調データの下位桁を変換し、表示すべきフレームの階調データの変換された上位桁と変換された下位桁とを加算することにより補正階調データを生成することが好ましい。

**【0185】**

上記の構成では、階調データの残りの下位桁を変換してから加算することにより、さらに誤差を小さくすることが可能となる。

**【0186】**

実施形態欄において説明した液晶表示装置は、画素を有し、前記画素にフレームごとに階調データに基づく階調電圧を印加することで階調表示を行う液晶表示装置であって、表示すべきフレームの階調データおよび直前のフレームの階調データに基づいて、表示すべきフレームの階調データを補正階調データに変換する変換部と、前記変換部にて変換された補正階調データに基づいて階調電圧を前記画素に印加する駆動部と、前記画素に含まれ、印加された階調電圧により階調表示が可能な液晶セルとを備え、前記変換部には、表示すべきフレームの階調データに対応する第1変換値、および直前のフレームの階調データに対応する第2変換値が予め記憶されており、前記変換部は、表示すべきフレームの階調データおよび直前のフレームの階調データにそれぞれ対応する第1変換値および第2変換値を用いた演算により補正階調データを生成することを特徴としている。

**【0187】**

上記の構成では、表示すべきフレームの階調データおよび直前のフレームの階調データから補正階調データを生成する処理において、複雑な演算を要する処理については予め記憶された第1変換値および第2変換値への変換により行い、簡単な演算が可能な処理については演算により行うことができる。したがって、すべての処理を演算により行うことによる演算の複雑化を抑えて変換部の構成の簡素化を図ることができる。また、あらゆる場合に対応した変換値を記憶しておくことによる記憶容量の増大を抑えて変換部の簡素化を図ることができる。

**【0188】**

実施形態欄において説明した液晶表示装置は、上記変換部に第1変換値および第2変換値が記憶されている液晶表示装置において、さらに、前記変換部が、記憶している第1変換値の群および第2変換値の群の少なくとも一方を外部から書き換え可能としていることが好ましい。

**【0189】**

上記の構成では、変換部に記憶されている第1変換値の群および第2変換値の群を書き換え可能とすることにより、特性が異なる液晶セルを備えた液晶パネルを用いるような場合に柔軟に適応できる。つまり、第1変換値の群および第2変換値の群を書き換えることで、液晶セルの特性に合った補正階調データを生成することが可能になる。

**【0190】**

実施形態欄において説明した液晶表示装置は、画素を有し、前記画素にフレームごとに階調データに基づく階調電圧を印加することで階調表示を行う液晶表示装置であって、表示すべきフレームの階調データおよび直前のフレームの階調データに基づいて、表示すべきフレームの階調データを補正階調データに変換する変換部と、前記変換部にて変換された補正階調データに基づいて階調電圧を前記画素に印加する駆動部と、前記画素に含まれ、印加された階調電圧により階調表示が可能な液晶セルとを備え、前記変換部には、表示すべきフレームの階調データに対応する第1変換値を算出するための第1基準値、および直前のフレームの階調データに対応する第2変換値を算出するための第2基準値が予め記

10

20

30

40

50

憶されており、前記変換部は、第1基準値および第2基準値に基づいて補間を行うことによりそれぞれ第1変換値および第2変換値を算出するとともに、表示すべきフレームの階調データおよび直前のフレームの階調データにそれぞれ対応する第1変換値および第2変換値を用いた演算により補正階調データを生成することを特徴としている。

**【0191】**

上記の構成では、各階調に対応する第1変換値および第2変換値をすべて記憶させておく必要がないため、変換部に必要な記憶容量を小さくすることができる。また、補間は比較的簡単な演算で行うことが可能であるため、比較的簡単な回路構成で実現可能である。したがって、変換部における回路構成の複雑化も抑えることができる。

**【0192】**

実施形態欄において説明した液晶表示装置は、上記変換部に第1基準値および第2基準値が記憶されている液晶表示装置において、さらに、前記変換部が、記憶している第1基準値の群および第2基準値の群の少なくとも一方を外部から書き換え可能としていることが好ましい。

**【0193】**

上記の構成では、上述の場合と同様に特性が異なる液晶セルを備えた液晶パネルを用いる場合に柔軟に適応できる。

**【0194】**

実施形態欄において説明した液晶表示装置は、画素を有し、前記画素にフレームごとに階調データに基づく階調電圧を印加することで階調表示を行う液晶表示装置であって、表示すべきフレームの階調データおよび直前のフレームの階調データに基づいて、表示すべきフレームの階調データを補正階調データに変換する変換部と、表示すべきフレームの階調データおよび直前のフレームの階調データの桁を変換する桁変換部と、前記変換部にて変換された補正階調データに基づいて階調電圧を前記画素に印加する駆動部と、前記画素に含まれ、印加された階調電圧により階調表示が可能な液晶セルとを備え、前記桁変換部は、階調データが示す階調が予め定めた閾値より明側である場合にはその階調データの下位桁を削除し、階調データが示す階調が前記閾値より暗側である場合にはその階調データの上位桁を削除することで、その階調データの桁数が小さくなるように変換し、前記変換部には、前記桁変換部にて変換された表示すべきフレームの階調データと直前のフレームの階調データとによって特定される設定階調データが予め記憶されており、特定した設定階調データに基づいて補正階調データを生成することを特徴としている。

**【0195】**

上記の構成では、上述したように、直前のフレームと表示すべきフレームとの間の液晶セルの容量の変化による影響を考慮した階調電圧を画素に印加することができ、液晶セルの容量が変化することによる階調表示のずれを補正することができる。

**【0196】**

ここで、上記の構成では、さらに、桁変換部により、表示すべきフレームの階調データおよび直前のフレームの階調データに関して、階調データが示す階調に応じてその階調データの一部を削除してその階調データの桁数が小さくなるように変換する。そして、変換部には、桁変換部により変換された表示すべきフレームの階調データと、直前のフレームの階調データとによって特定される設定階調データが予め記憶されている。このように階調データの桁数を小さくしてそのデータ量を小さくすることは、変換部にて設定階調データを特定するためのデータが小さくなることになり、記憶しておくべき設定階調データの量も小さくなる。これにより、変換部における設定階調データを記憶するための容量の削減を図ることができる。

**【0197】**

また、桁変換部により階調データの桁数を変換する際には、その階調データが示す階調が所定値より明側である場合には下位桁を削除し、暗側である場合には上位桁を削除する。これにより、変換部による変換により大きく影響する部分を残して階調データの桁数を小さくすることができ、表示品位が低下することを抑制することができる。

10

20

30

40

50

## 【0198】

実施形態欄において説明した液晶表示装置は、上記桁変換部を備える液晶表示装置において、さらに、前記変換部は第1入力および第2入力を有し、前記第2入力には、入力される階調データを記憶してその階調データを1フレーム分遅らせて出力する記憶部が接続されており、階調データは、前記桁変換部を介して前記第1入力に入力されるとともに、前記桁変換部を介して前記記憶部に入力され、前記記憶部から前記第2入力に入力されることが好みしい。

## 【0199】

上記の構成では、上述したように、簡素な構成で表示すべきフレームの階調データと直前のフレームの階調データとを変換部に入力することができる。また、記憶部には、桁数が小さくなるように桁変換部にて変換された後の階調データが入力される。したがって、記憶部における容量の削減をも図ることができる。

10

## 【0200】

上記桁変換部を備える液晶表示装置において、階調データが256階調表示用の階調データであり、階調データが示す最も暗い階調を0階調とすると、前記閾値は、例えば32階調であることが好みしい。このとき、階調データは8ビットの階調データであり、前記桁変換部は、階調データの変換を行う際に、階調データの上位3桁または下位3桁を削除するとともに、上位桁または下位桁の何れを削除したかを示すフラグビットを設定するようすればよい。

## 【0201】

20

あるいは、上記桁変換部を備える液晶表示装置において、階調データが256階調表示用の階調データであり、階調データが示す最も暗い階調を0階調とすると、前記閾値は、例えば64階調であってもよい。このとき、階調データは8ビットの階調データであり、前記桁変換部は、階調データの変換を行う際に、階調データの上位2桁または下位3桁を削除するとともに、上位桁または下位桁の何れを削除したかを示すフラグビットを設定し、かつ、上位2桁を削除した場合にはさらに最下位1桁を削除するようすればよい。

## 【0202】

実施形態欄において説明した液晶表示装置は、上記液晶表示装置において、さらに、前記変換部に予め記憶されている階調データが、その階調データに基づいて前記画素の階調表示を行った場合に、その階調データに基づく階調電圧が前記画素に印加されてから1フレームに相当する時間が経過したときのその画素の輝度が、本来表示すべき輝度の90%から110%の範囲内に入るよう設定されていることが好みしい。

30

## 【0203】

また、実施形態欄において説明した液晶表示装置の駆動方法は、印加された階調電圧により階調表示が可能な液晶セルを含む画素を有し、前記画素にフレームごとに階調データに基づく階調電圧を印加することで階調表示を行う液晶表示装置の駆動方法であって、表示すべきフレームの階調データおよび直前のフレームの階調データに基づいて予め記憶されている階調データの中から階調データを特定し、特定した階調データに基づく階調電圧を前記画素に印加して表示すべきフレームの階調表示を行わせるように前記液晶表示装置を駆動し、前記予め記憶されている階調データは、その階調データに基づいて前記画素の階調表示を行った場合に、その階調データに基づく階調電圧が前記画素に印加されてから1フレームに相当する時間が経過したときのその画素の輝度が、本来表示すべき輝度の90%から110%の範囲内に入るよう設定されていることを特徴としている。

40

## 【0204】

上記の範囲を越えるような階調データを用いると、その階調データにより表示するフレームの輝度が本来表示すべき輝度、すなわち表示すべきフレームの階調データが示す階調に対応する輝度からかけ離れた輝度として観察されるばかりでなく、そのフレーム以降のフレームにおける異常表示をもたらすことになりかねない。上記の構成および方法では、このような問題の発生を抑えることができる。

## 【0205】

50

### 【発明の効果】

本発明の液晶表示装置では、直前のフレームと表示すべきフレームとの間の液晶セルの容量（電気容量）の変化による影響を考慮した階調電圧を画素に印加することができる。これにより、液晶セルの容量が変化することによる階調表示のずれを補正することができる。その結果、特に動画表示時などにおいて入力される階調データをより忠実に再現した表示が可能になる。

### 【0206】

また、本発明の液晶表示装置では、変換部で扱うデータ量を削減することができ、変換部の簡素化を図ることができる。

### 【0207】

さらに、本発明の液晶表示装置では、階調データの残りの下位桁を加算することにより、上位桁のみに基づく変換を行ったことによる誤差を小さくすることができる。

### 【0208】

あるいは、本発明の液晶表示装置では、階調データの残りの下位桁を変換してから加算することにより、さらに誤差を小さくすることが可能となる。

### 【図面の簡単な説明】

【図1】 本発明の第1の参考形態に係る液晶表示装置の構成を示すブロック図である。

【図2】 図1の液晶表示装置におけるフレームメモリに対する階調データの入出力の関係を示すタイミングチャートである。

### 【図3】 図1の液晶表示装置におけるLUTメモリのピン接続図である。

【図4】 図1の液晶表示装置における液晶パネルの各階調と階調電圧との関係を示すグラフである。

【図5】 図1の液晶表示装置における液晶パネルの各階調と液晶セルの容量との関係を示すグラフである。

【図6】 ルックアップテーブルを用いて階調データを補正した場合と、補正しなかった場合とにおいて、表示の切り換えの応答特性を示すグラフである。

【図7】 ルックアップテーブルを用いて階調データを補正した場合と、補正しなかった場合とにおいて、表示の切り換えの応答特性を示すグラフである。

【図8】 ルックアップテーブルを用いて階調データを補正した場合と、補正しなかった場合とにおいて、表示の切り換えの応答特性を示すグラフである。

### 【図9】 図4、図5および式(4)に基づいて求めたルックアップテーブルである。

【図10】 図9のルックアップテーブルを修正したルックアップテーブルの一例である。

【図11】 液晶セルの黒表示に対応する階調電圧から白表示に対応する階調電圧までの範囲外の電圧を出力することができないソースドライバを用いた場合のルックアップテーブルの一例である。

【図12】 図1の液晶表示装置における液晶パネルの設定階調データと階調電圧との関係を示すグラフである。

【図13】 図1の液晶表示装置における液晶パネルの階調電圧と輝度との関係を示すグラフである。

【図14】 スイッチング素子としての薄膜トランジスタを有するアクティブマトリクス型の液晶パネル、およびこの液晶パネルを駆動するドライバを備えた液表示装置の構成を示す概略構成図である。

### 【図15】 図14の液晶パネルにおける各画素の等価回路を示す回路図である。

### 【図16】 本発明の実施形態に係るLUTメモリ周辺の構成を示すブロック図である。

【図17】 図1のLUTメモリに設定したルックアップテーブルの一部を示す図表である。

【図18】 図16のLUTメモリに設定したルックアップテーブルの一部を示す図表である。

### 【図19】 本発明の実施形態の変形例に係るLUTメモリ周辺の構成を示すブロック図

10

20

30

40

50

である。

【図 2 0】 本発明の第2の参考形態に係る変換演算回路周辺の構成を示すブロック図である。

【図 2 1】 本発明の第2の参考形態で用いた液晶パネルの定常状態における各階調と階調電圧との関係を示すグラフである。

【図 2 2】 本発明の第2の参考形態で用いた液晶パネルの定常状態における各階調と液晶セルの容量との関係を示すグラフである。

【図 2 3】 本発明の第2の参考形態における表示フレーム階調データと数値データとの関係を示す図表である。

【図 2 4】 本発明の第2の参考形態における前フレーム階調データと数値データとの関係を示す図表である。 10

【図 2 5】 本発明の第2の参考形態における数値データと階調データとの関係を示す図表である。

【図 2 6】 本発明の第3の参考形態における表示フレーム階調データと数値データとの関係を示すグラフである。

【図 2 7】 本発明の第3の参考形態における前フレーム階調データと数値データとの関係を示すグラフである。

【図 2 8】 本発明の第3の参考形態における数値データと補正階調データとの関係を示すグラフである。 20

【図 2 9】 本発明の第4の参考形態に係る変換演算回路周辺の構成を示すブロック図である。

【図 3 0】 本発明の第5の参考形態に係る変換演算回路周辺の構成を示すブロック図である。 20

【図 3 1】 階調電圧と輝度との関係を示す仮想的なグラフである。

【図 3 2】 第0フレームの開始とともに、黒表示から白表示へ切り換え、その後第1および第2フレームで白表示を維持する際の階調電圧および輝度の変化を示すグラフである。

【図 3 3】 第0フレームの開始とともに、黒表示から灰表示（輝度50%）へ切り換え、その後第1および第2フレームで灰表示を維持する際の階調電圧および輝度の変化を示すグラフである。 30

【図 3 4】 階調とピットとの関係を表した図表である。

【図 3 5】 本発明の第6の参考形態に係るLUTメモリ周辺の構成を示すブロック図である。

【図 3 6】 図35において丸付数字1から3を付した部分における階調データの内容を示す概念図である。

【図 3 7】 図35において丸付数字4から7を付した部分における階調データの内容を示す概念図である。

【図 3 8】 図35におけるLUTメモリの入出力ビット数を概念的に示した概念図である。

【図 3 9】 図36の階調データの内容を一部変形した概念図である。 40

【図 4 0】 映像の評価実験に用いた評価映像を示す概念図である。

【図 4 1】 映像の評価実験の評価基準を示す図表である。

【図 4 2】 映像の評価実験に用いた各ディスプレイの形態、各ディスプレイに設定されている輝度の誤差、および評価結果を示す図表である。

【図 4 3】 階調と輝度との一般的な関係を示す図表である。

#### 【符号の説明】

1 0 液晶パネル

1 2 ソースドライバ（駆動部）

1 4 ゲートドライバ

1 6 ソースバスライン

50

|       |                 |

|-------|-----------------|

| 1 8   | 走査ライン           |

| 2 0   | T F T           |

| 2 2   | 液晶セル            |

| 2 4   | 負荷容量            |

| 2 6   | 共通電極            |

| 3 0   | コントローラ          |

| 3 2   | LUTメモリ(変換部、メモリ) |

| 3 4   | フレームメモリ(記憶部)    |

| 3 6   | LUTメモリ(変換部、メモリ) |

| 3 7   | 下位ビット変換部(変換部)   |

| 3 8   | 加算器(変換部)        |

| 4 0   | 変換演算回路(変換部)     |

| 4 2   | 第1LUTメモリ        |

| 4 4   | 第2LUTメモリ        |

| 4 6   | 第3LUTメモリ        |

| 4 8   | 演算器             |

| 5 0   | 書換え部            |

| 6 0   | 変換演算回路(変換部)     |

| 6 2   | 第1補間部           |

| 6 4   | 第2補間部           |

| 6 6   | 第1基準データメモリ      |

| 6 8   | 第2基準データメモリ      |

| 7 4 a | 第1桁変換部(桁変換部)    |

| 7 4 b | 第1桁変換部(桁変換部)    |

| 7 6   | 第2桁変換部(変換部)     |

| 7 8   | ラインメモリ          |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

|                |     | 表示フレーム階調データ |     |     |     |     |     |     |     |     |

|----------------|-----|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

|                |     | 0           | 32  | 64  | 96  | 128 | 160 | 192 | 224 | 255 |

| 前フレーム<br>階調データ | 0   | 128         | 168 | 208 | 252 | 295 | 335 | 371 | 389 | 391 |

|                | 32  | 127         | 160 | 203 | 246 | 285 | 332 | 369 | 389 | 391 |

|                | 64  | 127         | 154 | 192 | 237 | 276 | 318 | 365 | 386 | 391 |

|                | 96  | 126         | 149 | 184 | 224 | 267 | 309 | 347 | 382 | 390 |

|                | 128 | 125         | 145 | 178 | 216 | 256 | 301 | 341 | 379 | 390 |

|                | 160 | 124         | 140 | 172 | 209 | 247 | 288 | 333 | 373 | 390 |

|                | 192 | 123         | 130 | 164 | 199 | 235 | 277 | 320 | 367 | 389 |

|                | 224 | 121         | 127 | 153 | 187 | 221 | 262 | 305 | 352 | 389 |

|                | 255 | 120         | 125 | 142 | 171 | 202 | 241 | 283 | 335 | 383 |

【図10】

|                |     | 表示フレーム階調データ |     |     |     |     |     |     |     |     |

|----------------|-----|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

|                |     | 0           | 32  | 64  | 96  | 128 | 160 | 192 | 224 | 255 |

| 前フレーム<br>階調データ | 0   | 128         | 168 | 208 | 252 | 295 | 335 | 371 | 389 | 391 |

|                | 32  | 127         | 160 | 203 | 246 | 285 | 332 | 369 | 389 | 391 |

|                | 64  | 127         | 154 | 192 | 237 | 276 | 318 | 365 | 386 | 391 |

|                | 96  | 126         | 149 | 184 | 224 | 267 | 309 | 347 | 382 | 390 |

|                | 128 | 125         | 145 | 178 | 216 | 256 | 301 | 341 | 379 | 390 |

|                | 160 | 124         | 140 | 172 | 209 | 247 | 288 | 333 | 373 | 390 |

|                | 192 | 123         | 130 | 164 | 199 | 235 | 277 | 320 | 367 | 389 |

|                | 224 | 121         | 127 | 153 | 187 | 221 | 262 | 305 | 352 | 389 |

|                | 255 | 120         | 125 | 142 | 171 | 202 | 241 | 283 | 335 | 383 |

【図12】

【図11】

|                |     | 表示フレーム階調データ |    |    |     |     |     |     |     |     |

|----------------|-----|-------------|----|----|-----|-----|-----|-----|-----|-----|

|                |     | 0           | 32 | 64 | 96  | 128 | 160 | 192 | 224 | 255 |

| 前フレーム<br>階調データ | 0   | 0           | 40 | 80 | 124 | 167 | 207 | 243 | 255 | 255 |

|                | 32  | 0           | 32 | 75 | 118 | 157 | 204 | 241 | 255 | 255 |

|                | 64  | 0           | 26 | 64 | 109 | 148 | 190 | 237 | 255 | 255 |

|                | 96  | 0           | 21 | 56 | 96  | 139 | 181 | 219 | 254 | 255 |

|                | 128 | 0           | 17 | 50 | 88  | 128 | 173 | 213 | 251 | 255 |

|                | 160 | 0           | 12 | 44 | 81  | 119 | 160 | 205 | 245 | 255 |

|                | 192 | 0           | 2  | 36 | 71  | 107 | 149 | 192 | 239 | 255 |

|                | 224 | 0           | 0  | 25 | 59  | 93  | 134 | 177 | 224 | 255 |

|                | 255 | 0           | 0  | 14 | 43  | 74  | 113 | 155 | 207 | 255 |

【図13】

【 図 1 4 】

【 図 1 5 】

【図16】

【 図 17 】

【図18】

|     | 表示フレーム階調データ |    |    |    |    |    |    |    |

|-----|-------------|----|----|----|----|----|----|----|

|     | 83          | 84 | 85 | 86 | 87 | 88 | 89 | 90 |

| 244 | 21          | 23 | 24 | 25 | 26 | 26 | 27 | 28 |

| 245 | 21          | 23 | 24 | 25 | 26 | 26 | 27 | 28 |

| 246 | 21          | 23 | 24 | 25 | 26 | 26 | 27 | 28 |

| 247 | 21          | 23 | 24 | 25 | 26 | 26 | 27 | 28 |

| 248 | 19          | 20 | 21 | 22 | 23 | 23 | 24 | 25 |

| 249 | 19          | 20 | 21 | 22 | 23 | 23 | 24 | 25 |

| 250 | 19          | 20 | 21 | 22 | 23 | 23 | 24 | 25 |

| 251 | 19          | 20 | 21 | 22 | 23 | 23 | 24 | 25 |

| 252 | 3           | 0  | 1  | 2  | 3  | 0  | 1  | 2  |

| 253 | 3           | 0  | 1  | 2  | 3  | 0  | 1  | 2  |

| 254 | 3           | 0  | 1  | 2  | 3  | 0  | 1  | 2  |

| 255 | 3           | 0  | 1  | 2  | 3  | 0  | 1  | 2  |

【図19】

【図20】

【図21】

【図22】

【図23】

| 表示フレーム<br>階調データm | 数値データ<br>Am |

|------------------|-------------|

| 0                | 964         |

| 1                | 963         |

| 2                | 962         |

| .                | .           |

| .                | .           |

| 254              | 223         |

| 255              | 219         |

【図24】

| 表示フレーム<br>階調データn | 数値データ<br>Bn |

|------------------|-------------|

| 0                | 0           |

| 1                | 1           |

| 2                | 2           |

| .                | .           |

| .                | .           |

| 254              | 2391        |

| 255              | 2403        |

【図25】

| 数値データ<br>Dp | 階調データ<br>P |

|-------------|------------|

| 0           | 255        |

| 1           | 255        |

| 2           | 255        |

| .           | .          |

| 14514       | 255        |

| 14515       | 254        |

| .           | .          |

| 46875       | 254        |

| .           | .          |

| 3581537     | 1          |

| .           | .          |

| 3586098     | 1          |

| 3586097     | 0          |

| .           | .          |

| 6431127     | 0          |

【図26】

【図28】

【図27】

【図 29】

【図 30】

【図 31】

【図 32】

【図33】

【図34】

| 階調  | ビット |   |   |   |   |   |   |   |

|-----|-----|---|---|---|---|---|---|---|

|     | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0   | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 255 | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 240 | 1   | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 255 | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 31  | 0   | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 16  | 0   | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

【図35】

【図36】

| ビット | 7              | 6              | 5              | 4              | 3              | 2              | 1              | 0              |

|-----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| ①   | A <sub>z</sub> | B <sub>z</sub> | C <sub>z</sub> | D <sub>z</sub> | E <sub>z</sub> | F <sub>z</sub> | G <sub>z</sub> | H <sub>z</sub> |

| ②   | -              | -              | 0 <sub>z</sub> | D <sub>z</sub> | E <sub>z</sub> | F <sub>z</sub> | G <sub>z</sub> | H <sub>z</sub> |

| ③   | -              | -              | 1 <sub>z</sub> | A <sub>z</sub> | B <sub>z</sub> | C <sub>z</sub> | D <sub>z</sub> | E <sub>z</sub> |

【図37】

| ビット | 7              | 6              | 5                          | 4              | 3              | 2              | 1              | 0              |

|-----|----------------|----------------|----------------------------|----------------|----------------|----------------|----------------|----------------|

| ④   | a <sub>z</sub> | b <sub>z</sub> | c <sub>z</sub>             | d <sub>z</sub> | e <sub>z</sub> | f <sub>z</sub> | g <sub>z</sub> | h <sub>z</sub> |

| ⑤   | -              | -              | F <sub>L<sub>z</sub></sub> | v <sub>z</sub> | w <sub>z</sub> | x <sub>z</sub> | y <sub>z</sub> | z <sub>z</sub> |

| ⑥   | 0 <sub>z</sub> | 0 <sub>z</sub> | 0 <sub>z</sub>             | v <sub>z</sub> | w <sub>z</sub> | x <sub>z</sub> | y <sub>z</sub> | z <sub>z</sub> |

| ⑦   | v <sub>z</sub> | w <sub>z</sub> | x <sub>z</sub>             | y <sub>z</sub> | z <sub>z</sub> | f <sub>z</sub> | g <sub>z</sub> | h <sub>z</sub> |

【図38】

| 表示フレーム階調データ |  | 6ビットデータ    |         |

|-------------|--|------------|---------|

|             |  | 前フレーム階調データ | 6ビットデータ |

|             |  | 6ビットデータ    | 6ビットデータ |

【図 3 9】

| ビット | 7              | 6              | 5              | 4              | 3              | 2              | 1              | 0              |

|-----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| ①   | A <sub>1</sub> | B <sub>1</sub> | C <sub>1</sub> | D <sub>1</sub> | E <sub>1</sub> | F <sub>1</sub> | G <sub>1</sub> | H <sub>1</sub> |

| ②   | -              | -              | 0 <sub>1</sub> | C <sub>1</sub> | D <sub>1</sub> | E <sub>1</sub> | F <sub>1</sub> | G <sub>1</sub> |

| ③   | -              | -              | 1 <sub>1</sub> | A <sub>1</sub> | B <sub>1</sub> | C <sub>1</sub> | D <sub>1</sub> | E <sub>1</sub> |

【図 4 0】

【図 4 1】

| 点数 | 評価基準                |

|----|---------------------|

| 5  | エッジぼけが分からない         |

| 4  | エッジぼけが分かるが、気にならない   |

| 3  | エッジぼけが気になるが、邪魔にならない |

| 2  | エッジぼけが邪魔になる         |

| 1  | エッジぼけが非常に邪魔になる      |

【図 4 2】

| 番号 | ディスプレイの形態   | 輝度の誤差     | 評価結果 |

|----|-------------|-----------|------|

| 1  | 20型液晶テレビ 1  | -30%~-20% | 2.4  |

| 2  | 20型液晶テレビ 2  | -20%~-10% | 2.8  |

| 3  | 20型液晶テレビ 3  | -10%~-5%  | 3.3  |

| 4  | 20型液晶テレビ 4  | -5%~0%    | 3.8  |

| 5  | 20型ブラウン管テレビ | 0%        | 5.0  |

| 6  | 20型液晶テレビ 5  | 0%~5%     | 3.9  |

| 7  | 20型液晶テレビ 6  | 5%~10%    | 3.5  |

| 8  | 20型液晶テレビ 7  | 10%~20%   | 2.7  |

| 9  | 20型液晶テレビ 8  | 20%~30%   | 2.2  |

【図 4 3】

| 階調  | 輝度 (%) |

|-----|--------|

| 0   | 0.00   |

| 16  | 0.23   |

| 31  | 0.97   |

| 240 | 87.51  |

| 255 | 100.00 |

---

フロントページの続き

(72)発明者 富沢 一成

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

(72)発明者 宮地 弘一

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

(72)発明者 陣田 章仁

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

審査官 濱本 穎広

(56)参考文献 特開平11-126050(JP,A)

特開平04-268599(JP,A)

特開平11-326868(JP,A)

特開平10-198322(JP,A)

国際公開第01/071701(WO,A1)

特開平09-081083(JP,A)

特開2001-343956(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00-3/38

G02F 1/133

|                |                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP3770380B2</a>                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2006-04-26 |

| 申请号            | JP2001174845                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2001-06-08 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 宫田英利<br>塙見誠<br>富沢一成<br>宮地弘一<br>陣田章仁                                                                                                                                                                                                                                                                                                                  |         |            |

| 发明人            | 宮田 英利<br>塙見 誠<br>富沢 一成<br>宮地 弘一<br>陣田 章仁                                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                          |         |            |

| CPC分类号         | G09G3/3648 G09G3/3611 G09G2320/02 G09G2320/0252 G09G2320/0261 G09G2340/16                                                                                                                                                                                                                                                                            |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/133.575 G09G3/20.621.F G09G3/20.641.P                                                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 2H093/NA55 2H093/NC29 2H093/NC34 2H093/NC50 2H093/ND01 2H093/ND06 2H193/ZA04 2H193/ZD25 2H193/ZE01 5C006/AA16 5C006/AF04 5C006/AF44 5C006/AF46 5C006/BB16 5C006/BC03 5C006/BC06 5C006/BC13 5C006/BC16 5C006/FA14 5C006/FA19 5C006/FA56 5C006/GA03 5C080/AA10 5C080/BB05 5C080/DD08 5C080/DD30 5C080/EE29 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ05 |         |            |

| 优先权            | 2000284267 2000-09-19 JP<br>2001150169 2001-05-18 JP                                                                                                                                                                                                                                                                                                 |         |            |