(19)日本国特許庁 (JP)

(12) 特許公報 (B2)

(11)特許番号

特許第3506235号

(P3506235)

(45)発行日 平成16年3月15日(2004.3.15)

(24)登録日 平成15年12月26日(2003.12.26)

(51)Int.Cl.<sup>7</sup>

G 0 9 G 3/36

G 0 2 F 1/133 5 2 5

G 0 9 G 3/20 6 1 2

6 2 3

6 4 2

F I

G 0 9 G 3/36

G 0 2 F 1/133 5 2 5

G 0 9 G 3/20 6 1 2 U

6 2 3 B

6 4 2 A

請求項の数 6 (全 31 頁)

(21)出願番号 特願2000-248964(P2000-248964)

(22)出願日 平成12年8月18日(2000.8.18)

(65)公開番号 特開2002-62852(P2002-62852A)

(43)公開日 平成14年2月28日(2002.2.28)

審査請求日 平成14年7月9日(2002.7.9)

(73)特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(72)発明者 渡邊 卓哉

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(74)代理人 100080034

弁理士 原 謙三

審査官 濱本 賢広

(56)参考文献 特開 平11-249624 (JP, A)

特開 平5-56374 (JP, A)

特開 平11-305735 (JP, A)

特開 平11-249623 (JP, A)

最終頁に続く

(54)【発明の名称】 液晶表示装置の駆動装置および駆動方法

1

(57)【特許請求の範囲】

【請求項1】同相入力端子及び逆相入力端子と、同相出力端子及び逆相出力端子とを備え、第1及び第2增幅回路からなる差動增幅回路と、

上記入力端子を介してそれぞれ入力される同相および逆相の入力信号を切替信号に基づいて切り替えて第1及び第2增幅回路へ入力する第1切替回路と、

第1及び第2增幅回路からそれぞれ出力される出力信号を交流化信号に基づいて切り替えて上記出力端子を介してマトリックス状に配された画素へ出力する第2切替回路と、

或る画素に印加されるオフセット電圧と、該画素に隣接する画素のうち斜め上および斜め下の画素にそれぞれ印加されるオフセット電圧とは、極性が互いに逆であり且つ絶対値が互いに等しくなるように、上記第1及び第2

2

切替回路をそれぞれ切り替える切替制御回路とを備えている液晶表示装置の駆動装置。

【請求項2】上記切替制御回路は、水平同期信号又は1水平同期期間毎に出力される信号に同期して、1フレーム内では1水平同期期間毎に上記第1及び第2切替回路を切り替えることを特徴とする請求項1に記載の液晶表示装置の駆動装置。

【請求項3】上記切替制御回路は、水平ライン数が偶数か奇数かを識別し、この識別結果に基づいて、上記第1及び第2切替回路を逆相の切替信号による切り替えと、同相の切替信号による切り替えとをフレーム毎に交互に行う制御と、上記第1及び第2切替回路を逆相の切替信号による切り替えのみを行う制御とを選択的に切り替えることを特徴とする請求項2に記載の液晶表示装置の駆動装置。

【請求項4】上記切替制御回路は、水平同期信号、または1水平同期期間毎に出力される信号を1／2分周し、これを切替信号として上記の第1切替回路へ出力する第1分周回路と、

垂直同期信号を1／2分周する第2分周回路と、

上記の第2分周回路の出力と、水平ライン数が偶数か奇数かを識別する識別信号とに基づき、水平ライン数が奇数の場合に第1開閉制御信号を生成する一方、水平ライン数が偶数の場合に奇数番目のフレームにおいて第1開閉制御信号を生成すると共に偶数番目のフレームにおいて上記の第2開閉制御信号を生成する開閉制御信号生成回路と、

上記の第1開閉制御信号が入力され、上記の切替信号の逆相信号を上記交流化信号として上記の第2切替回路へ出力するために閉状態になる第1スイッチ回路と、

上記の第2開閉制御信号が入力され、上記切替信号の同相信号を上記交流化信号として上記の第2切替回路へ出力するために閉状態になる第2スイッチ回路とを備えたことを特徴とする請求項1又は3に記載の液晶表示装置の駆動装置。

【請求項5】同相入力端子及び逆相入力端子と、同相出力端子及び逆相出力端子とを有し、第1及び第2增幅回路からなる差動增幅回路を備え、上記入力端子を介してそれぞれ入力される同相および逆相の入力信号を切替信号に基づいて切り替えて第1及び第2增幅回路へ入力すると共に、第1及び第2增幅回路からそれぞれ出力される出力信号を交流化信号に基づいて切り替えて上記出力端子を介してマトリックス状に配された画素へ出力する液晶表示装置の駆動方法であって、

或る画素に印加されるオフセット電圧と、該画素に隣接する画素のうち斜め上および斜め下の画素に印加されるオフセット電圧とは、極性が互いに逆であり且つ絶対値が互いに等しくなるように、上記切替信号および上記交流化信号を制御することを特徴とする液晶表示装置の駆動方法。

【請求項6】水平同期信号、または1水平同期期間毎に出力される信号に基づいて上記切替信号を制御し、垂直同期信号と水平ライン数が偶数か奇数かを識別する識別信号とに基づいて、上記切替信号の逆相信号と同相信号とをそれぞれ生成し、水平ライン数が偶数の場合には、上記切替信号の逆相信号と同相信号とをそれぞれフレーム毎に交互に切り替えて上記交流化信号とする一方、水平ライン数が奇数の場合には、上記逆相信号のみを上記交流化信号とするように制御することを特徴とする請求項5に記載の液晶表示装置の駆動方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、製造上のバラツキなどによる偶発的に発生したオフセット電圧をプラス側とマイナス側で同等に出力する差動增幅回路を備えた液

晶表示装置の駆動装置および駆動方法に関するものである。

【0002】

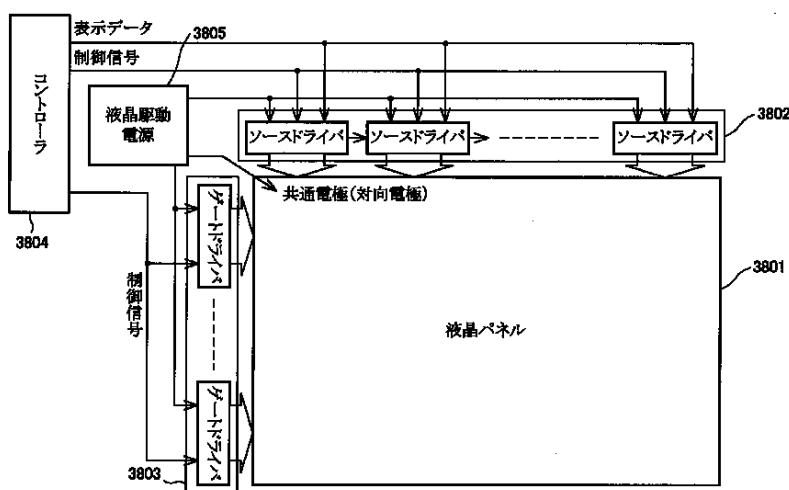

【従来の技術】図6に、アクティブマトリックス方式の代表例であるTFTを用いた液晶表示装置の構成を示す。3801はTFT液晶パネルを示し、3802は複数のソースドライバを備えたソースドライバICを示し、3803は複数のゲートドライバを備えたゲートドライバICを示し、3804はコントロール回路を示し、3805は液晶駆動電源（電源回路）を示す。

【0003】上記コントロール回路3804は、ゲートドライバIC3803へ垂直同期信号を送ると共に、ソースドライバIC3802及びゲートドライバIC3803へ水平同期信号を送る。外部から入力された表示データ（R、G、Bに分離された各表示データ）は、コントロール回路3804を介してデジタル信号でソースドライバIC3802へ入力される。ソースドライバIC3802は、入力された表示データを時分割で内部にラッピングし、その後、コントロール回路3804からの水平同期信号に同期してデジタル／アナログ変換を行い、液晶駆動出力端子から階調表示用のアナログ電圧を出力するようになっている。

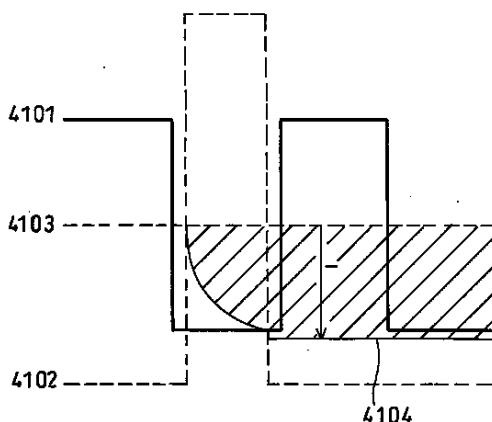

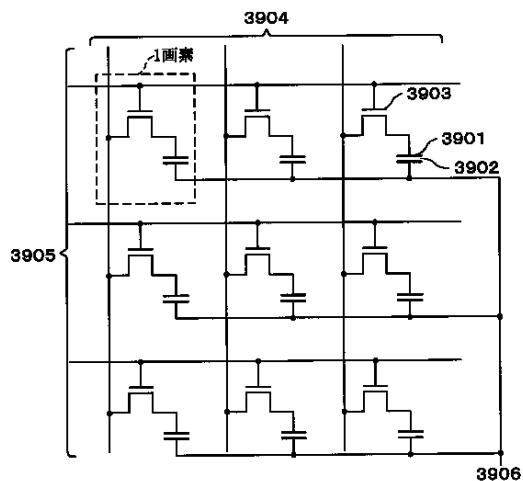

【0004】図42に、TFT液晶パネルの構成図を示す。3901は画素電極を示し、3902は画素容量を示し、3903はTFT（スイッチ素子）を示し、3904はソース信号ラインを示し、3905はゲート信号ラインを示し、3906は対向電極を示す。

【0005】上記ソース信号ライン3904には、上記ソースドライバIC3802から、表示画素の明るさに応じて変化する階調表示電圧が与えられる。上記ゲート信号ライン3905には、上記ゲートドライバIC3803から、縦方向に配設されたTFT3903が順次オンするように走査信号が与えられる。オン状態のTFT3903を介して該TFTのドレインに接続された画素電極3901にソース信号ライン3904の電圧が印加され、上記対向電極3906との間の画素容量3902に蓄積され、これにより、液晶の光透過率が変化し、該変化に応じた表示が行われる。

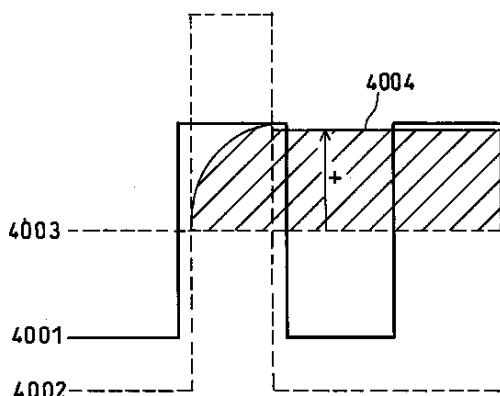

【0006】図12及び図13に液晶駆動波形の一例を示す。4001及び4101はソースドライバから出力される駆動波形を示し、4002及び4102はゲートドライバから出力される駆動波形を示し、4003及び4103は対向電極の電位を示し、4004及び4104は画素電極の電圧波形を示す。

【0007】液晶材料に印加される電圧は、画素電極3901と対向電極3906の電位差であり、図中には斜線で示している。液晶パネルは長期信頼性を確保するために、交流で駆動する必要がある。図12は、上記ソースドライバの出力電圧が対向電極の電圧より高い時に上記ゲートドライバの出力によりTFT3903がオン

し、画素電極3901へ対向電極3906に対して正極性の電圧が印加され、その後、TFT3903がオフしてその電位が維持される場合を示している。

【0008】一方、図13は、逆に、上記ソースドライバの出力電圧が対向電極3906の電圧より低い時に上記ゲートドライバの出力によりTFT3903がオンして、画素電極3901へ対向電極3906に対して負極性の電圧が印加され、その後、TFT3903がオフしてその電位が維持される場合を示している。このように、図12の波形電圧と図13の波形電圧とを交互に印加することで、液晶材料に加わる電圧を交流化して駆動することが可能となる。

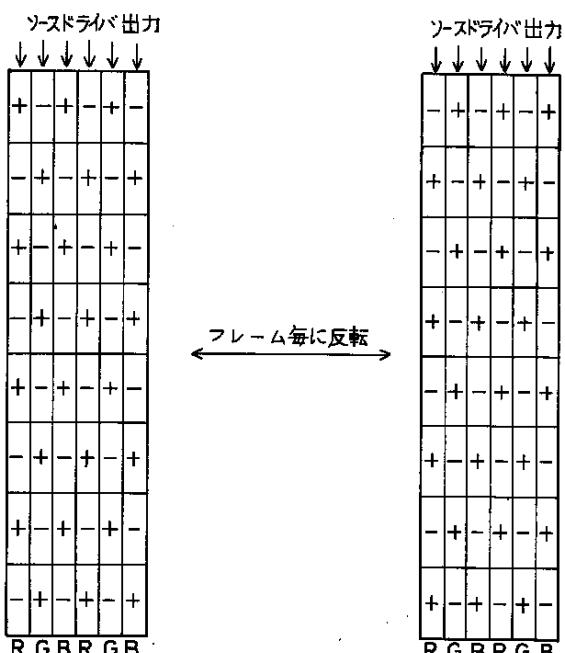

【0009】図14に、駆動電圧を交流化する際の、液晶パネル3801上の交流化の極性配列の一例を示す。これは、ドット反転駆動と呼ばれる方式によるものであり、1つの表示画面（フレーム）内では正極性と負極性とが上下左右とも交互に配列され、かつ、フレーム毎に極性が反転される。この方法では、ソースドライバIC3802においては、例えば奇数番目の出力端子が正極性の電圧を出力している時、偶数番目の出力端子は負極性の電圧を出力しており、逆に、奇数番目の出力端子が負極性の電圧を出力している時、偶数番目の出力端子は正極性の電圧を出力している。

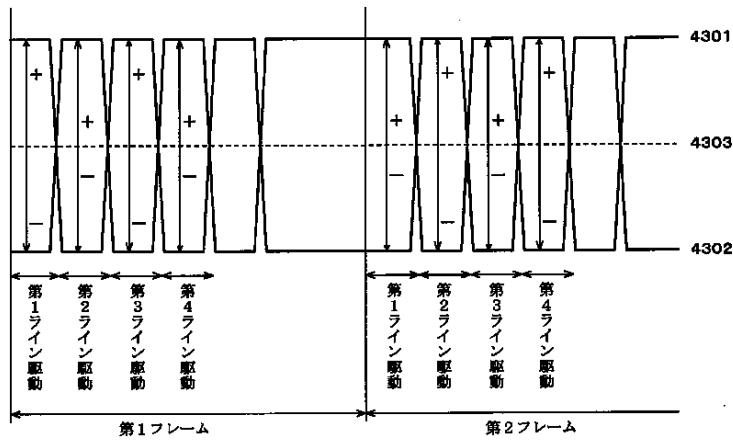

【0010】図15に、ドット反転駆動におけるソースドライバの駆動波形例を示す。図15中、4301は奇数番目の上記出力端子の出力電圧波形を示し、4302は偶数番目の上記出力端子の出力電圧波形を示し、4303は対向電極3906の電圧を示す。図15に示すように、奇数番目の出力端子と偶数番目の出力端子においては、常に対向電極3906に対して逆の極性の電圧が出力される。

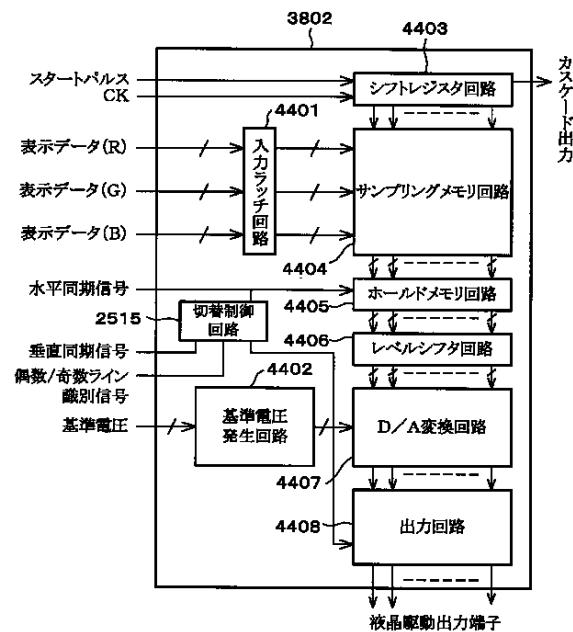

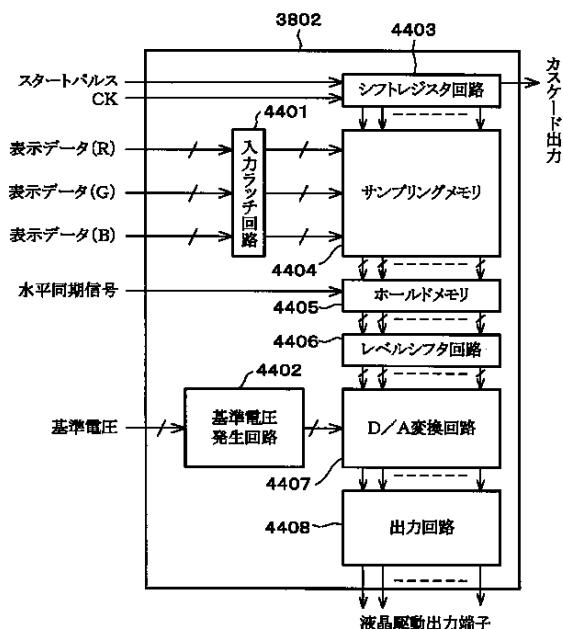

【0011】図16は、上記ソースドライバIC3802の構成を示すブロック図の一例を示す。ここでは、関連するソースドライバのみ説明する。ゲートドライバは公知のものを使用するので、ここでは、説明を省略する。入力されたデジタル信号の表示データ（R、G、B）は、シフトレジスタ4403の動作に基づいて時分割でサンプリングメモリ4404に記憶され、その後、水平同期信号でホールドメモリ4405に一括転送される。上記シフトレジスタ4403は、スタートパルス及びクロック（CK）に基づいて動作するようになっている。上記ホールドメモリ4405のデータは、レベルシフタ回路4406を介してD/A変換回路4407でアナログ電圧に変換され、出力回路4408により、液晶駆動出力端子を介して階調表示駆動電圧（液晶駆動電圧）として出力される。なおホールドメモリ4405により1水平同期期間、表示データは、ラッチされ維持されている。そして、次の水平同期新により表示データが取り込まれ、ラッチされる。

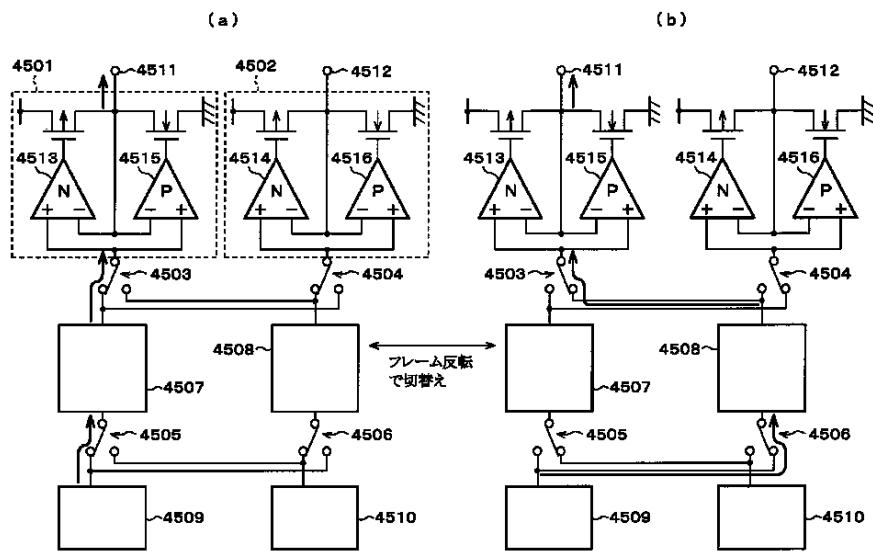

【0012】図17（a）および図17（b）に、従来

の技術（第1従来技術）に係るドット反転駆動を行うソースドライバICの出力回路のブロック構成図とその動作の一例とを示す。図17（a）および図17（b）には、図16の内、4405、4407、4408で示される各ブロックのみを、2出力端子分の回路として示している。

【0013】図17（a）および図17（b）において、4501は奇数番目の出力端子を駆動する出力回路でオペアンプを使用したボルテージフォロワを示し、4502は偶数番目の出力端子を駆動する出力回路で4501と同じオペアンプを使用したボルテージフォロワを示し、4503、4504、4505、及び4506は液晶駆動出力の出力電圧極性を切り替える出力交流化スイッチをそれぞれ示し、4507は正極性電圧のデジタル／アナログ変換を行うD/A変換回路を示し、4508は負極性電圧のデジタル／アナログ変換を行うD/A変換回路を示し、4509及び4510は表示データを保持するホールドメモリをそれぞれ示し、4511は奇数番目の出力端子を示し、4512は偶数番目の出力端子を示す。また、オペアンプ4501の内部の4513及び4502内部の4514はNチャンネルMOS入力のオペアンプを示し、オペアンプ4501の内部の4515及び4502内部の4516はPチャンネルMOS入力のオペアンプを示す。

【0014】上記構成を有する回路による液晶駆動波形の交流化について説明すると、以下の通りである。

【0015】上記出力交流化スイッチ4503から4506が図17（a）の状態にあるとき、上記ホールドメモリ4509に記憶されている奇数番目の出力端子4511の表示データは、正極性のD/A変換回路4507へ入力され、D/A変換後のアナログ電圧は、ボルテージフォロワ4501を介して奇数番目の出力端子4511から液晶パネル3801へ出力される。この時の出力電圧は、正極性の液晶駆動電圧となる。

【0016】これに対して、出力交流化スイッチ4503乃至4506が図17（b）の状態にあるとき、ホールドメモリ4509に記憶されている奇数番目の出力端子4511の表示データは、負極性のD/A変換回路4508に入力され、D/A変換後のアナログ電圧は、ボルテージフォロワ4501を介して奇数番目の出力端子4511から液晶パネルへ出力される。この時の出力電圧は、負極性の駆動駆動電圧となる。

【0017】偶数番目の出力端子4512の駆動電圧の極性は、奇数番目の出力端子4511と逆になる。すなわち、出力交流化スイッチ4503から4506が図17（a）の状態にあるとき、ホールドメモリ4510に記憶されている偶数番目の出力端子4512の表示データは、負極性のD/A変換回路4508に入力され、D/A変換後のアナログ電圧は、ボルテージフォロワ4502を介して偶数番目の出力端子4512から液晶パネ

ルへ出力される。この時の出力電圧は、負極性の液晶駆動電圧となる。

【0018】一方、出力交流化スイッチ4503から4506が図17(b)の状態にあるとき、ホールドメモリ4510に記憶されている偶数番目の出力端子の表示データは、正極性のD/A変換回路4507に入力され、D/A変換後のアナログ電圧は、ボルテージフォロワ4502を介して偶数番目の出力端子4512より液晶パネルに出力される。この時の出力電圧は、正極性の液晶駆動電圧となる。図17(a)および図17(b)には、以上の動作のうち、奇数番目の出力端子の信号の流れのみを示す。このように、図17(a)の状態と、図17(b)の状態とを出力交流化スイッチ4503から4506を用いてフレーム反転で交互に切り替えることにより、液晶パネル3801を駆動するために必要な駆動波形の交流化を行っている。

【0019】図17(a)および図17(b)の回路構成において、1つの出力端子は、正極性電圧の出力の場合も負極性電圧の出力の場合も、常に同じオペアンプ回路で駆動される。一般に、液晶駆動回路の出力端子の重要な機能として、動作電源電圧フルレンジの出力ダイナミックレンジが要求される。通常のLSIで使用されるエンハンスマント型のMOSトランジスタを使用することを想定すると、その閾値電圧による動作不可領域をなくすために、図17(a)および図17(b)に示すように、NチャンネルMOSトランジスタ入力のオペアンプ4513とPチャンネルMOSトランジスタ入力のオペアンプ4515の両方を1つの出力回路4501内に持たなければならない。このため回路規模が大きくなり、LSI化した場合のチップサイズの増大を招く。更に、オペアンプが1出力当り2回路有るために、回路の消費電力が大きくなる。

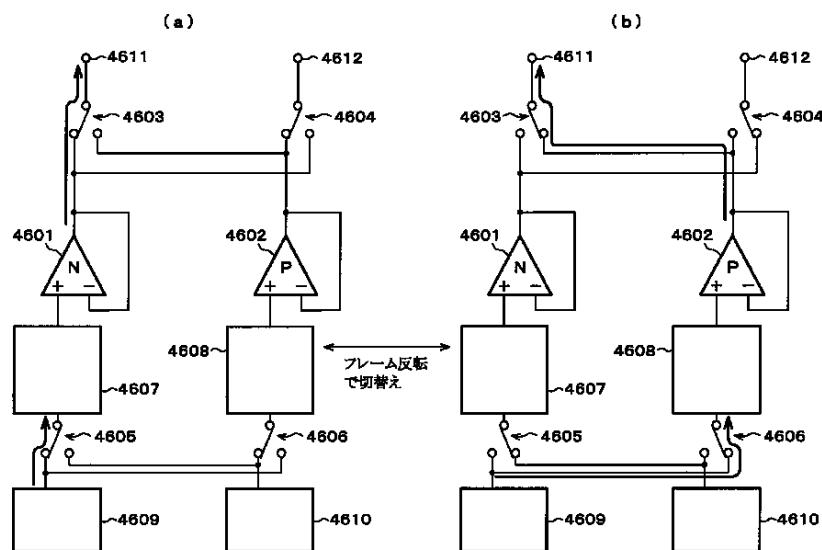

【0020】図18(a)および図18(b)に、他の従来の技術(第2従来技術)に係るドット反転駆動を行うソースドライバICの出力回路のブロック構成図とその動作の例を示す。図18(a)および図18(b)には、図16の内、4405、4407、4408で示される各ブロックのみを、2出力端子分の回路として示している。

【0021】図18(a)および図18(b)において、4601はNチャンネルMOSトランジスタ入力のオペアンプを使用したボルテージフォロワを示し、4602はPチャンネルMOSトランジスタ入力のオペアンプを使用したボルテージフォロワを示し、4603、4604、4605、及び4606は液晶駆動出力の出力電圧極性を切り替える出力交流化スイッチを示し、4607は正極性のデジタル/アナログ変換を行うD/A変換回路を示し、4608は負極性のデジタル/アナログ変換を行うD/A変換回路を示し、4609及び4610は表示データを保持するホールドメモリを示し、46

10

20

30

40

50

11は奇数番目の出力端子を示し、4612は偶数番目の出力端子を示す。

【0022】図18(a)および図18(b)の出力電圧の交流化は、図17(a)および図17(b)の場合と同じく出力交流化スイッチ4603から4606によって行われる。図17(a)および図17(b)の場合と異なるのは、正極性用のD/A変換回路4607の出力は直接NチャンネルMOSトランジスタ入力のオペアンプ4601へ送られ、負極性用のD/A変換回路4608の出力は直接PチャンネルMOSトランジスタ入力のオペアンプ4602へ送られ、各々のオペアンプの出力が、スイッチ4603及び4604を介して所望の出力端子へ送られる点である。

【0023】ここでは、正極性用のD/A変換回路4607は、動作電源電圧の約2分の1以上の電圧のみを出力するため、オペアンプとしてNチャンネル入力の回路のみで十分であり、同様に、負極性用のD/A変換回路4608は、動作電源電圧の約2分の1以下の電圧のみを出力するため、オペアンプとしてPチャンネル入力の回路のみで十分である。図18(a)および図18(b)の構成では、図17(a)および図17(b)の構成に対して、オペアンプ回路が出力端子当り半分ですむため、チップサイズの低減と低消費電力化が図れる。

【0024】しかしながら、図18(a)および図18(b)の構成は、1つの出力を駆動するオペアンプ回路が正極性の場合と負極性の場合とで異なっている。すなわち、図18(a)および図18(b)の液晶駆動出力端子は、正極性電圧を出力する時はオペアンプ4601で駆動される(図18(a)参照)一方、負極性電圧を出力する時はオペアンプ4602で駆動される(図18(b)参照)。ここで、オペアンプ4601とオペアンプ4602とが、製造上のバラツキなどによる偶発的に発生するオフセット電圧を持っている場合を以下に説明する。

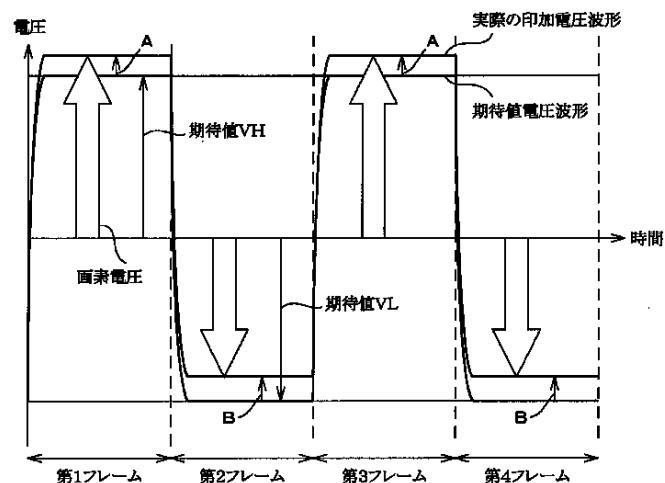

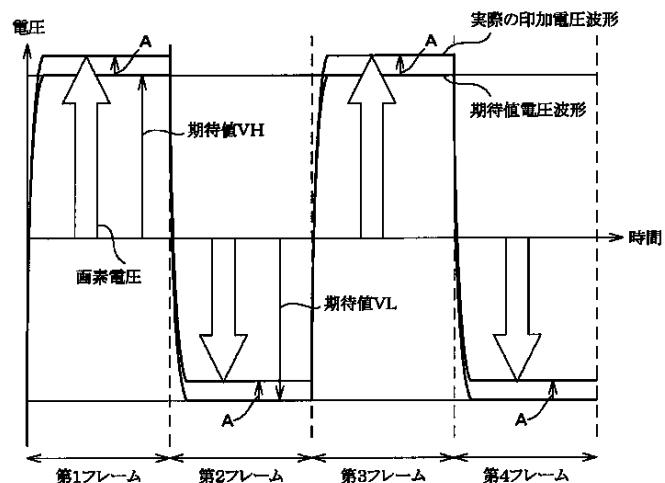

【0025】オペアンプ4601が偶発的に発生するオフセット電圧Aを持ち、オペアンプ4602が偶発的に発生するオフセット電圧Bを持つ場合の液晶駆動電圧波形を図19に示す。図19において、正極性電圧を出力する時と負極性電圧を出力する時とでは、期待値電圧からの偏差がそれぞれ異なる。したがって、液晶表示画素に印加される駆動電圧の平均電圧には、2つの偏差の差の成分( $(A - B)/2$ )が、誤差電圧として残留する。この誤差電圧は、駆動出力端子毎に偶発的に発生するものであるから、液晶表示装置の画素間での印加電圧の差となり、結果として表示むらが発生することになる。

【0026】比較のために、図20に、図17(a)および図17(b)の構成の場合の液晶駆動電圧波形を示す。図17(a)および図17(b)の構成では、正極性電圧、負極性電圧ともに1つの出力回路で駆動される

ため、いずれの場合も期待値電圧からの偏差は同じである。この偏差は、画素に印加される電圧としては、正極性の場合と負極性の場合で互いに打ち消し合う方向である。したがって、図17(a)および図17(b)の構成では、液晶駆動出力端子間の偏差のバラツキは、表示画素で平均化されることになり、表示上の問題にはならない。

【0027】上記第2従来技術(図18参照)の場合、正極性電圧と負極性電圧を別々のオペアンプ回路から出力する場合に対して、更なる回路規模の削減、及び消費電力の低減を実現した第3従来技術(例えば、特開平1-305735号公報を参照)が知られている。この第3従来技術について、図21を参照しながら説明すると以下のとおりである。

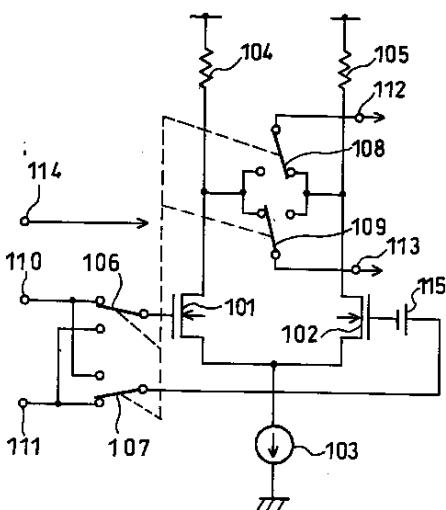

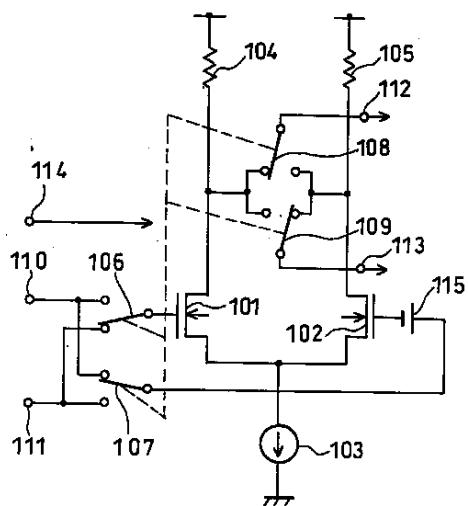

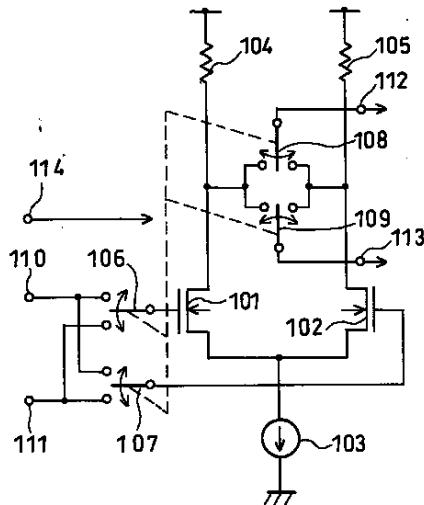

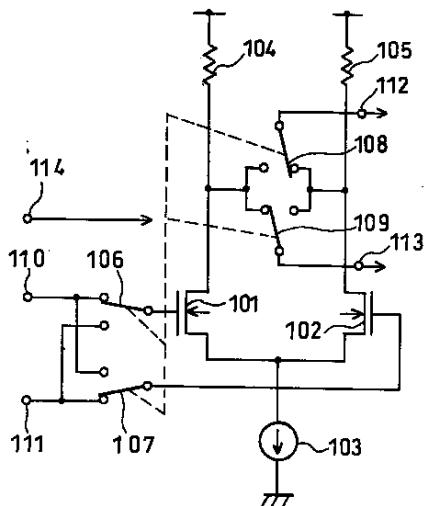

【0028】図21に、上記第3従来技術に係る差動增幅回路の構成例を示す。なお、図21は、NチャネルMOSトランジスタを入力トランジスタとして使用した場合を示すものである。

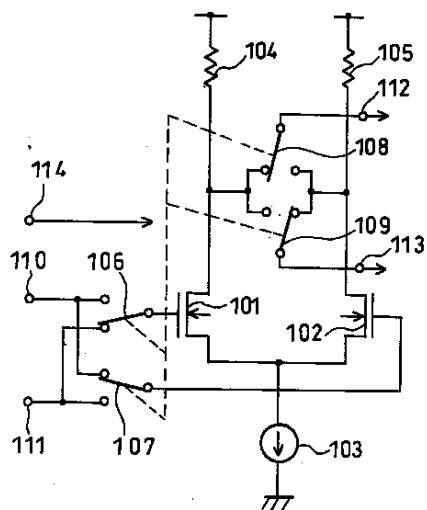

【0029】図21において、101及び102はNチャネルMOSによる入力トランジスタをそれぞれ示し、103は上記差動增幅回路に動作電流を与える定電流源を示し、104は上記入力トランジスタ101の負荷抵抗(抵抗素子)を示し、105は上記入力トランジスタ102の負荷抵抗(抵抗素子)を示し、106及び107は入力信号を切り替えるスイッチをそれぞれ示し、108及び109は出力信号を切り替えるスイッチをそれぞれ示し、110は同相入力端子を示し、111は逆相入力端子を示し、112は同相出力端子を示し、113は逆相出力端子を示し、114は上記スイッチ106から109を同時に切り替える切替信号入力端子を示す。

【0030】上記入力トランジスタ101及び上記負荷抵抗104と、上記入力トランジスタ102及び上記負荷抵抗105とは増幅回路を構成し、トランジスタ101と102は差動対を構成する。また、スイッチ106から109は、切替信号114により連動して制御される。

【0031】図22は、図21の回路の1つの動作状態を示す。図23は、図21の回路の他の動作状態を示す。以下に、図22及び図23を参照しながら、上記差動增幅回路の動作を説明する。

【0032】図22に示す状態では、同相入力端子110はスイッチ106を介して入力トランジスタ101のゲートに接続され、そのドレインに接続された負荷抵抗104の働きで、スイッチ109を介して逆相出力信号として逆相出力端子113から出力される。一方、逆相入力端子111はスイッチ107を介して入力トランジスタ102のゲートに接続され、そのドレインに接続された負荷抵抗105の働きで、スイッチ108を介して同相出力信号として同相出力端子112から出力され

る。つまり、同相入力信号は、入力トランジスタ101及び負荷抵抗104で増幅される一方、逆相入力信号は、入力トランジスタ102及び負荷抵抗105で増幅される。

【0033】一方、図23に示す状態では、同相入力端子110はスイッチ107を介して入力トランジスタ102のゲートに接続され、そのドレインに接続された負荷抵抗105の働きで、スイッチ109を介して逆相出力信号として逆相出力端子113より出力される。また、逆相入力端子111はスイッチ106を介して入力トランジスタ101のゲートに接続され、そのドレインに接続された負荷抵抗104の働きで、スイッチ108を介して同相出力信号として同相出力端子112より出力される。つまり、同相入力信号は、入力トランジスタ102及び負荷抵抗105で増幅される一方、逆相入力信号は、入力トランジスタ101及び負荷抵抗104で増幅される。

【0034】以上のように、図22に示す状態と図23に示す状態とでは、同相入力信号の増幅回路と逆相入力信号の増幅回路とを、完全に入れ替えて使用している。

【0035】ここで、差動增幅回路を構成する入力トランジスタ101と102の間において、及び/又は負荷抵抗104と105の間において、製造上の理由などにより偶発的に発生する特性の不一致が存在する場合について、図24及び図25を参照しながら、以下に説明する。

【0036】本来同じ特性を持つべき差動增幅回路の2つの素子において差が生じた場合、出力電圧が理想的な状態からずれてしまい、オフセットを持つ。このすれば、入力端子の一方に定電圧源を接続したものとしてモデル化できる。この様子を図24、及び図25に示す。図24及び図25に示す115は、上記差動增幅回路のオフセットを1つの定電圧源でモデル化したものである。なお、図24に示すスイッチ素子は図22に示す状態と同一であり、図25に示すスイッチ素子は図23に示す状態と同一である。

【0037】図24においては、定電圧源115は、スイッチ107を介して逆相入力端子111と接続されている。一方、図25においては、定電圧源115は、スイッチ107を介して同相入力端子110と接続されている。このように、本差動增幅回路は、スイッチ106から109を使用しているので、差動增幅回路の偶発的に発生するバラツキによるオフセットを、逆相入力端子111側に入れた状態と、同相入力端子110側に入れた状態とで切り替えることができる。これら2つの状態では、同相出力端子110及び逆相出力端子111に現れるオフセットは、符号が逆で絶対値が等しい状態となる。

【0038】以上より、オペアンプが製造上のバラツキなどによる偶発的に発生するオフセット電圧を持ってい

る場合、正極性のオフセット電圧を出力する場合と負極性のオフセット電圧を出力する場合とでは、期待値電圧からの偏差が等しくなる。

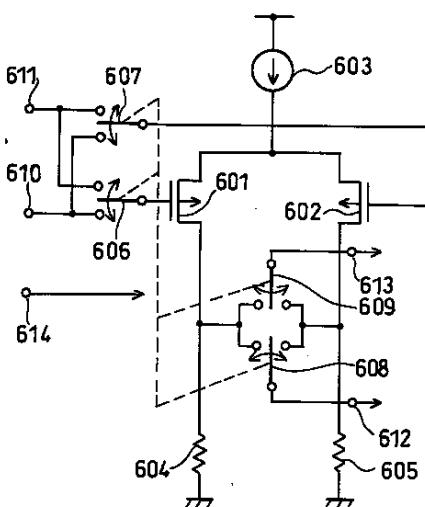

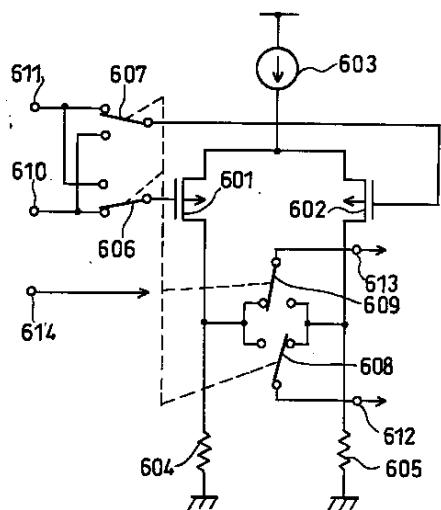

【0039】図26に、上記第2従来技術に係る差動增幅回路の他の例を示す。なお、図26は、PチャンネルMOSトランジスタを入力トランジスタに使用した場合を示すものである。

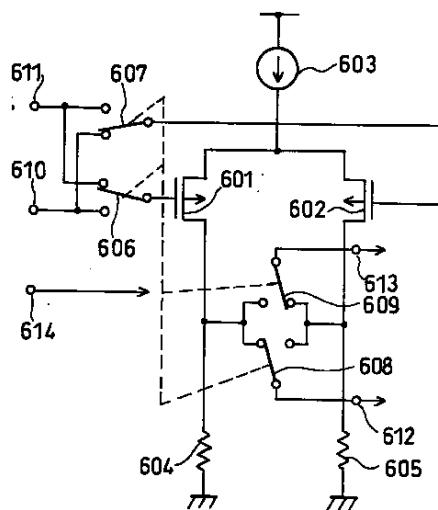

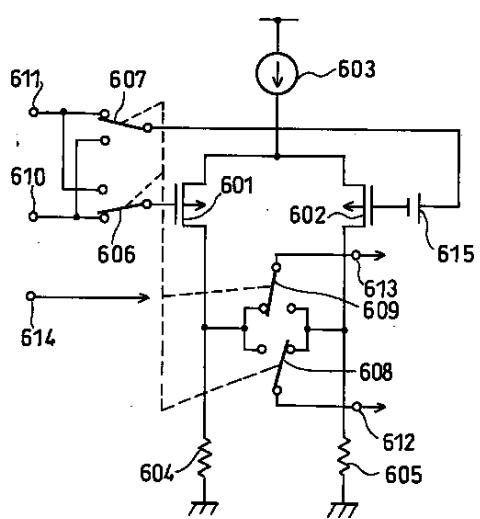

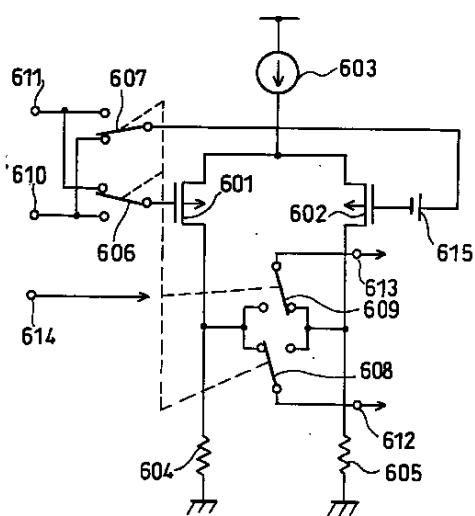

【0040】図26において、601及び602はPチャンネルMOSによる入力トランジスタをそれぞれ示し、603は本差動增幅回路に動作電流を与える定電流源を示し、604は入力トランジスタ601の負荷抵抗（抵抗素子）を示し、605は入力トランジスタ602の負荷抵抗（抵抗素子）を示し、606及び607は入力信号を切り替えるスイッチをそれぞれ示し、608及び609は出力信号を切り替えるスイッチをそれぞれ示し、610は同相入力端子を示し、611は逆相入力端子を示し、612は同相出力端子を示し、613は逆相出力端子を示し、614はスイッチ606乃至609を同時に切り替える信号を入力するための切替信号入力端子を示す。

【0041】図26の動作を図27及び図28を用いて説明すると以下のとおりである。

【0042】図27に示す状態では、同相入力端子610はスイッチ606を介して入力トランジスタ601のゲートに接続され、そのドレインに接続された負荷抵抗604の働きで、スイッチ609を介して逆相出力信号として逆相出力端子613から出力される。一方、逆相入力端子611はスイッチ607を介して入力トランジスタ602のゲートに接続され、そのドレインに接続された負荷抵抗605の働きで、スイッチ608を介して同相出力信号として同相出力端子612から出力される。つまり、同相入力信号は、入力トランジスタ601及び負荷抵抗604で増幅される一方、逆相入力信号は、入力トランジスタ602及び負荷抵抗605で増幅される。

【0043】一方、図28に示す状態では、同相入力端子610はスイッチ607を介して入力トランジスタ602のゲートに接続され、そのドレインに接続された負荷抵抗605の働きで、スイッチ609を介して逆相出力信号として逆相出力端子613より出力される。また、逆相入力端子611はスイッチ606を介して入力トランジスタ601のゲートに接続され、そのドレインに接続された負荷抵抗604の働きで、スイッチ608を介して同相出力信号として同相出力端子612より出力される。つまり、同相入力信号は、入力トランジスタ602及び負荷抵抗605で増幅される一方、逆相入力信号は、入力トランジスタ601及び負荷抵抗604で増幅される。

【0044】以上の様に、図27に示す状態と図28に示す状態とでは、同相入力信号の増幅回路と逆相入力信

号の増幅回路とを、完全に入れ替えて使用している。

【0045】ここで、差動增幅回路を構成する入力トランジスタ601と602の間において、及び／又は負荷抵抗604と605の間において、製造上の理由などにより偶発的に発生する特性の不一致が存在する場合について、図29及び図30を参照しながら、以下に説明する。

【0046】本来同じ特性を持つべき差動增幅回路の2つの素子において差が生じた場合、出力電圧が理想的な状態からずれてしまい、オフセットを持つ。このすれば、入力端子の一方に定電圧源を接続したものとしてモデル化できる。この様子を図29、及び図30に示す。図29、及び図30に示す615は、上記差動增幅回路のオフセットを1つの定電圧源でモデル化したものである。なお、図29に示すスイッチ素子は図27に示す状態と同一であり、図30に示すスイッチ素子は図28に示す状態と同一である。

【0047】図29においては、定電圧源615は、スイッチ607を介して逆相入力端子611と接続されている。一方、図30においては、定電圧源615は、スイッチ607を介して同相入力端子610と接続されている。このように、本差動增幅回路は、スイッチ606から609を使用しているので、差動增幅回路の偶発的に発生するバラツキによるオフセットを、逆相入力端子611側に入れた状態と、同相入力端子610側に入れた状態とで切り替えることができる。これら2つの状態では、同相出力端子610及び逆相出力端子611に現れるオフセットは、符号が逆で絶対値が等しい状態となる。

【0048】以上より、オペアンプが製造上のバラツキなどにより偶発的に発生するオフセット電圧を持っている場合でも、正極性のオフセット電圧を出力する場合と負極性のオフセット電圧を出力する場合とでは、期待値電圧からの偏差が等しくなる。

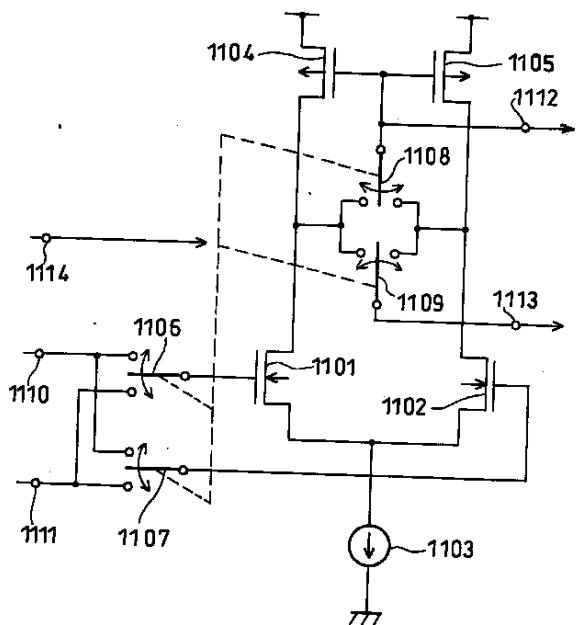

【0049】図31に、図21の差動增幅回路の負荷素子をカレントミラー構成の能動負荷に変えた回路構成を示す。図31は、NチャンネルMOSトランジスタを入力トランジスタとして使用した場合を示すものである。

【0050】図31において、1101及び1102はNチャンネルMOSによる入力トランジスタをそれぞれ示し、1103は本回路に動作電流を与える定電流源を示し、1104は入力トランジスタ1101の負荷となるPチャンネルMOSによる負荷トランジスタを示し、1105は入力トランジスタ1102の負荷となるPチャンネルMOSによる負荷トランジスタを示し、1106及び1107は入力信号を切り替えるスイッチをそれぞれ示し、1108及び1109は出力信号を切り替えるスイッチをそれぞれ示し、1110は同相入力端子を示し、1111は逆相入力端子を示し、1112は同相出力端子を示し、1113は逆相出力端子を示し、11

14はスイッチ1106～1109を同時に切り替える信号を入力するための切替信号入力端子を示す。

【0051】上記差動增幅回路は、負荷素子がトランジスタによるカレントミラー構成の能動負荷である点において、図21の構成例(受動負荷)と異なっている。図22に対応する状態においては、同相入力信号は、入力トランジスタ1101及び負荷トランジスタ1104で増幅される一方、逆相入力信号は、入力トランジスタ1102及び負荷トランジスタ1105で増幅される。これに対して、図23に対応する状態においては、同相入力信号は、入力トランジスタ1102及び負荷トランジスタ1105で増幅される一方、逆相入力信号は、入力トランジスタ1101及び負荷トランジスタ1104で増幅される。

【0052】以上、何れの場合でも、上記負荷トランジスタ1104及び1105は、互いに、カレントミラー構成となっているので、たとえ両負荷トランジスタに特性のバラツキがあっても、負荷トランジスタ1104及び1105に流れる電流は常に等しくなり、この結果、同相入力信号及び逆相入力信号は同じ増幅度で増幅されることになり、左右対称な出力波形が得られることになる。

【0053】以上のように、図31に示す構成を有する差動增幅回路でも、同相入力信号の増幅回路と逆相入力信号の増幅回路とを、完全に入れ替えて使用することができる。

【0054】また、上記差動增幅回路を構成する入力トランジスタ1101と1102の間において、製造上の理由などにより偶発的に発生する特性の不一致が存在する場合でも、詳細には説明しないが、図21と同様の構成を有している。したがって、本差動增幅回路においては、スイッチ1106乃至1109を使用しているので、差動增幅回路の偶発的に発生するバラツキによるオフセットを、逆相入力端子1111側に入れた状態と、同相入力端子1110側に入れた状態とで切り替えることができる。これら2つの状態では、同相出力端子1110及び逆相出力端子1111に現れるオフセットは、符号が互いに逆で絶対値が等しい状態となる。

【0055】以上より、オペアンプが製造上のバラツキなどにより偶発的に発生するオフセット電圧を持っている場合、正極性のオフセット電圧を出力する場合と負極性のオフセット電圧を出力する場合とでは、期待値電圧からの偏差が等しくなる。

【0056】図32に、図26の差動增幅回路の負荷素子をカレントミラー構成の能動負荷に変えた回路構成を示す。図32は、PチャンネルMOSトランジスタを入力トランジスタとして使用した場合を示すものである。

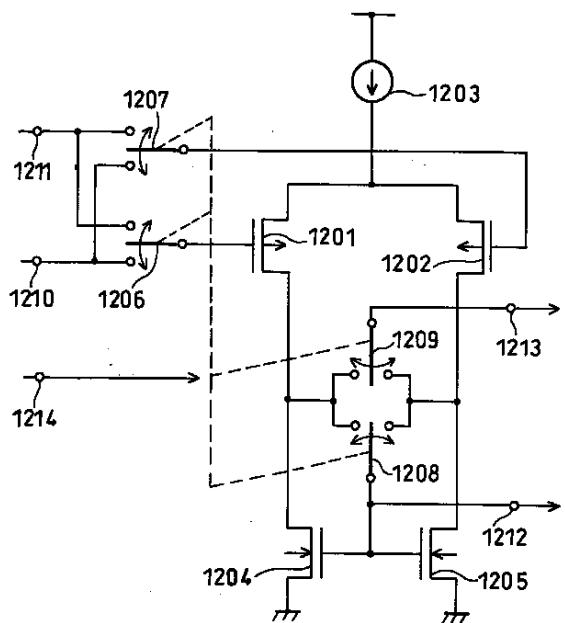

【0057】図32において、1201及び1202はPチャンネルMOSによる入力トランジスタをそれぞれ示し、1203は本回路に動作電流を与える定電流源を

示し、1204は入力トランジスタ1201の負荷となるNチャンネルMOSによる負荷トランジスタを示し、1205は入力トランジスタ1202の負荷となるNチャンネルMOSによる負荷トランジスタを示し、1206及び1207は入力信号を切り替えるスイッチをそれぞれ示し、1208及び1209は出力信号を切り替えるスイッチをそれぞれ示し、1210は同相入力端子を示し、1211は逆相入力端子を示し、1212は同相出力端子を示し、1213は逆相出力端子を示し、1214はスイッチ1206～1209を同時に切り替える信号を入力するための切替信号入力端子を示す。

【0058】図32の構成は、負荷素子がトランジスタによるカレントミラー構成の能動負荷である点において、図26の構成(受動負荷)と異なっている。図27に対応する状態においては、同相入力信号は、入力トランジスタ1201及び負荷トランジスタ1204で増幅される一方、逆相入力信号は、入力トランジスタ1202及び負荷抵抗1205で増幅される。これに対して、図28に対応する状態においては、同相入力信号は、入力トランジスタ1202及び負荷トランジスタ1205で増幅される一方、逆相入力信号は、入力トランジスタ1201及び負荷トランジスタ1204で増幅される。

【0059】以上、何れの場合でも、上記負荷トランジスタ1204及び1205は、互いに、カレントミラー構成となっているので、両負荷トランジスタに特性のバラツキがあっても、負荷トランジスタ1204及び1205に流れる電流は常に等しくなり、この結果、同相入力信号及び逆相入力信号は同じ増幅度で増幅されることになり、左右対称な出力波形が得られることになる。

【0060】以上の様に、図32に示す構成を有する差動增幅回路でも、同相入力信号の増幅回路と逆相入力信号の増幅回路とを、完全に入れ替えて使用している。

【0061】また、上記差動增幅回路を構成する入力トランジスタ1201と1202の間において、製造上の理由などにより偶発的に発生する特性の不一致が存在する場合でも、詳細には説明しないが、図26と同様の構成を有している。したがって、上記差動增幅回路においては、スイッチ1206～1209を使用しているので、差動增幅回路の偶発的なバラツキによるオフセットを、逆相入力端子1211側に入れた状態と、同相入力端子1210側に入れた状態とで切り替えることができる。これら2つの状態では、同相出力端子1210及び逆相出力端子1211に現れるオフセットは、符号が互いに逆で絶対値が等しい状態となる。

【0062】以上より、オペアンプが製造上のバラツキなどにより偶発的に生じるオフセット電圧を持っている場合でも、正極性のオフセット電圧を出力する場合と負極性のオフセット電圧を出力する場合とでは、期待値電圧からの偏差が等しくなる。

【0063】ここで、図33を参照しながら、図31に

示す差動増幅回路と等価な差動増幅回路1301と、スイッチ及び出力部を具体化した例について説明する。なお、図33は、NチャンネルMOS入力のオペアンプである。

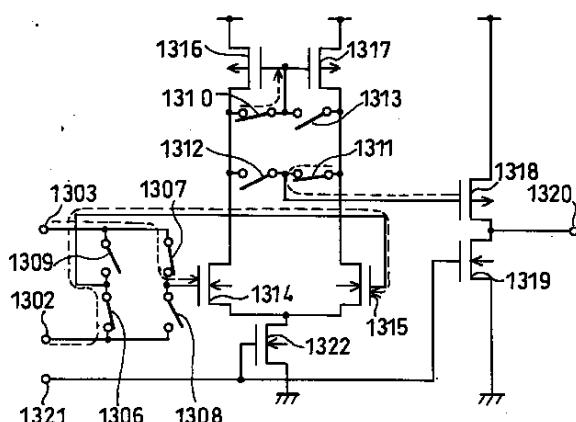

【0064】図33において、1302は同相入力端子を示し、1303は逆相入力端子を示し、1304及び1305はスイッチ切替信号入力端子をそれぞれ示し、1306から1309はスイッチをそれぞれ示し、1310から1313はスイッチをそれぞれ示し、1314及び1315はNチャンネルMOSの入力トランジスタをそれぞれ示し、1316および1317は入力トランジスタの能動負荷となるPチャンネルMOSの負荷トランジスタをそれぞれ示し、1318はPチャンネルMOSの出力トランジスタを示し、1319はNチャンネルMOSの出力トランジスタを示し、1320は出力端子を示し、1321はオペアンプに動作点を与えるためのバイアス電圧入力端子を示す。ここで、差動増幅回路1301を図21の抵抗負荷の差動増幅回路に置き換えた回路も、以下の説明と全く同一の動作をするため、ここでは詳細な説明を省略する。

【0065】図33において、1304及び1305が、図31で示したスイッチ切替信号入力端子1114に相当し、1304と1305とは互いに逆相の信号を入力する。スイッチ切替信号入力に応じた回路の動作を図34及び図35を参照しながら、以下に説明する。

【0066】図33において、入力トランジスタ1314及び1315が、図31で示した入力トランジスタ1101及び1102に相当し、負荷トランジスタ1316及び1317が、図31で示した負荷トランジスタ1104及び1105に相当する。

【0067】また、図33において、1307及び1309が、図31で示したスイッチ1106に相当し、1306及び1308が、図31で示したスイッチ1107に相当し、1310及び1313が、図31で示したスイッチ1108に相当し、1311及び1312が、図31で示したスイッチ1109に相当し、トランジスタ1322が、図31で示した定電流源1103に相当する。

【0068】切替入力信号1304に“L”レベル(ローレベル)が入力されると、スイッチはPチャンネルMOSトランジスタであるので、図34に示すように、スイッチ1306、1307、1310、及び1311がオン状態になる。この時、スイッチ切替信号入力端子1305には“H”レベル(ハイレベル)が入力されているため、スイッチ1308、1309、1312、及び1313はオフする。同相入力信号1302は、スイッチ1306を介して入力トランジスタ1315へ供給される。逆相入力信号1303は、スイッチ1307を介して入力トランジスタ1314へ供給される。また、スイッチ1310を介して負荷トランジスタ1316及び

10

1317にゲート信号が供給され、スイッチ1311を介して出力トランジスタ1318へゲート信号が与えられる。図34の場合、同相入力信号を増幅する回路は、トランジスタ1315及び負荷トランジスタ1317であり、逆相入力信号を増幅する回路は、トランジスタ1314及び負荷トランジスタ1316である。

20

【0069】スイッチ切替信号入力端子1305に“L”レベルが入力されると、図35において、スイッチ1308、1309、1312、及び1313がオン状態になる。この時、スイッチ切替信号入力端子1304には“H”レベルが入力されているため、スイッチ1306、1307、1310、及び1311はオフする。この時、同相入力信号1302は、スイッチ1308を介して入力トランジスタ1314へ供給される。逆相入力信号1303は、スイッチ1309を介して入力トランジスタ1315へ供給される。また、スイッチ1313を介して負荷トランジスタ1316及び1317にゲート信号が与えられ、スイッチ1312を介して出力トランジスタ1318へゲート信号が与えられる。図

20

35の場合、同相入力信号を増幅する回路は、入力トランジスタ1314及び負荷トランジスタ1316であり、逆相入力信号を増幅する回路は、入力トランジスタ1315及び負荷トランジスタ1317である。

30

【0070】図34及び図35に示したように、本差動増幅回路は、スイッチ1306から1313を切り替えることによって、同相入力信号の増幅回路と逆相入力信号の増幅回路とを入れ替えることができる。これにより、前述したように、差動増幅回路に製造上の特性バラツキ等による偶発的なオフセットが発生した場合でも、このオフセットは、この2つの状態で符号が互いに逆で絶対値が等しくなる。したがって、オペアンプに生じるオフセットのバラツキも、スイッチ1306から1313を切り替えることによって、オフセットの符号が互いに逆で絶対値が等しい状態を実現することができる。

30

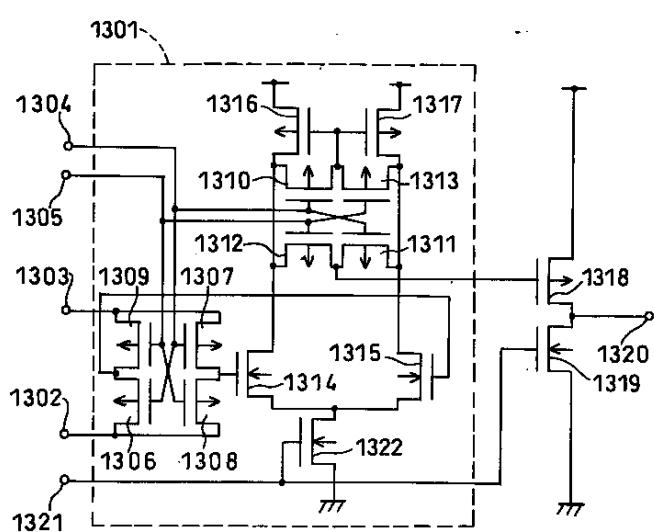

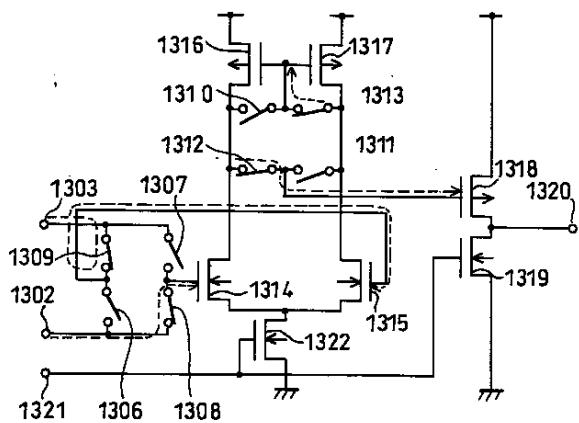

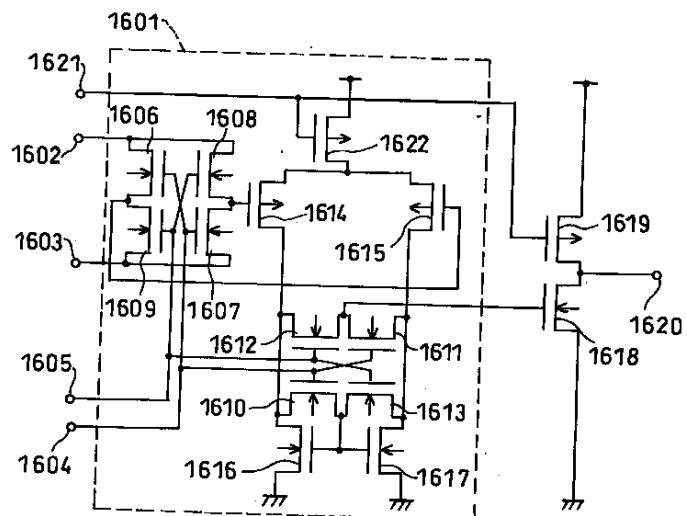

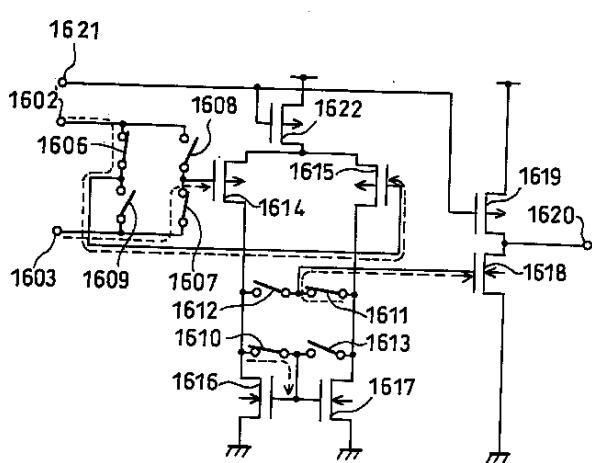

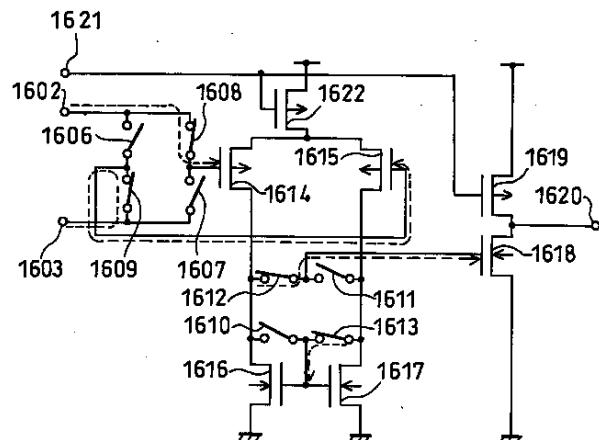

【0071】次に、図36を参照しながら、図32に示す差動増幅回路と等価な差動増幅回路1601と、スイッチ及び出力部を具体化した例を説明する。なお、図36は、PチャンネルMOS入力のオペアンプである。

40

【0072】図36において、1602は同相入力端子を示し、1603は逆相入力端子を示し、1604及び1605はスイッチ切替信号入力端子をそれぞれ示し、1606～1609はスイッチをそれぞれ示し、1610～1613はスイッチをそれぞれ示し、1614及び1615はPチャンネルMOSの入力トランジスタをそれぞれ示し、1616および1617は入力トランジスタの能動負荷となるNチャンネルMOSの負荷トランジスタをそれぞれ示し、1618はNチャンネルMOSの出力トランジスタを示し、1619はPチャンネルMOSの出力トランジスタを示し、1620は出力端子を示し、1621はオペアンプに動作点を与えるためのバイ

50

アス電圧入力端子を示す。ここで、差動增幅回路1601を図36で述べた抵抗負荷の差動增幅回路に置き換えた回路も、以下の説明と全く同一の動作をするため、ここでは詳細な説明を省略する。

【0073】図36において、1604及び1605が、図32で示したスイッチ切替信号入力端子1214に相当し、1604と1605とは互いに逆相の信号を入力する。スイッチ切替信号入力に応じた回路の動作を図37及び図38を参照しながら、以下に説明する。

【0074】図36において、入力トランジスタ1614及び1615が、図32で示した入力トランジスタ1201及び1202に相当し、負荷トランジスタ1616及び1617が、図32で示した負荷トランジスタ1204及び1205に相当する。また、図36において、1607及び1609が、図32で示したスイッチ1206に相当し、1606及び1608が、図32で示したスイッチ1207に相当し、1610及び1613が、図32で示したスイッチ1208に相当し、1611及び1612が、図32で示したスイッチ1209に相当し、トランジスタ1622が、図32で示した定電流源1203に相当する。

【0075】スイッチ切替信号入力端子1604に“H”レベル(ハイレベル)が入力されると、スイッチはNチャンネルMOSトランジスタであるので、図37に示すように、スイッチ1606、1607、1610、及び1611がオン状態になる。この時、スイッチ切替信号入力端子1605には“L”レベル(ローレベル)が入力されているため、スイッチ1608、1609、1612、及び1613はオフする。同相入力信号1602は、スイッチ1606を介して入力トランジスタ1615へ供給される。逆相入力信号1603は、スイッチ1607を介して入力トランジスタ1614へ供給される。また、スイッチ1610を介して負荷トランジスタ1616及び1617にゲート信号が供給され、スイッチ1611を介して出力トランジスタ1618へゲート信号が与えられる。図37の場合、同相入力信号を増幅する回路は、入力トランジスタ1615及び負荷トランジスタ1617であり、逆相入力信号を増幅する回路は、入力トランジスタ1614及び負荷トランジスタ1616である。

【0076】スイッチ切替信号入力端子1605に“H”レベルが入力されると、図38において、スイッチ1608、1609、1612、及び1613がオン状態になる。この時、スイッチ切替信号入力端子1604には“L”レベルが入力されているため、スイッチ1606、1607、1610、及び1611はオフする。この時、同相入力信号1602は、スイッチ1608を介して入力トランジスタ1614へ供給される。逆相入力信号1603は、スイッチ1609を介して入力トランジスタ1615へ供給される。また、スイッチ1

613を介して負荷トランジスタ1616及び1617にゲート信号が与えられ、スイッチ1612を介して出力トランジスタ1618へゲート信号が与えられる。図38の場合、同相入力信号を増幅する回路は、入力トランジスタ1614及び負荷トランジスタ1616であり、逆相入力信号を増幅する回路は、入力トランジスタ1615及び負荷トランジスタ1617である。

【0077】図37及び図38に示したように、上記差動增幅回路は、スイッチ1606～1613を切り替えることによって、同相入力信号の増幅回路と逆相入力信号の増幅回路とを入れ替えることができる。これにより、前述したように、差動增幅回路に製造上のバラツキ等により偶発的に発生するオフセットが発生した場合でも、このオフセットは、この2つの状態で符号が互いに逆で絶対値が等しくなる。したがって、オペアンプに生じるオフセットのバラツキも、スイッチ1606～1613を切り替えることによって、オフセットの符号が逆で絶対値が等しい状態を実現することができる。なお、図37及び図38において、点線は、信号の流れを示すものである。

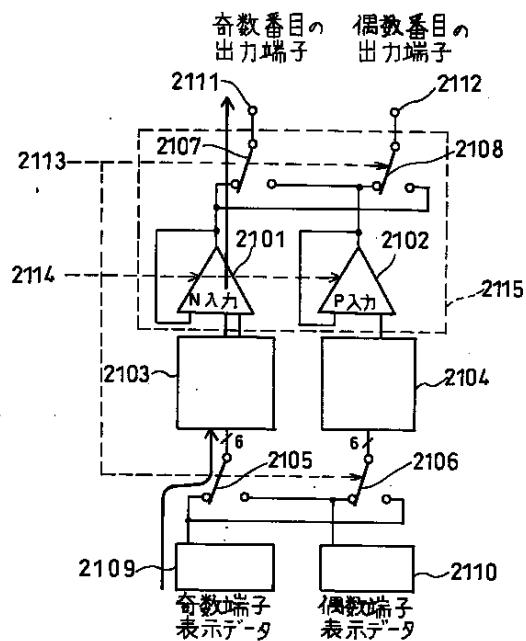

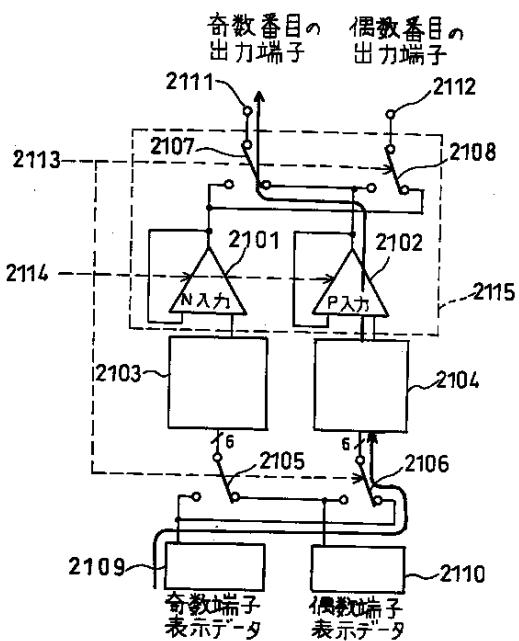

【0078】図39及び図40は、前述の差動增幅回路を使用したドット反転駆動を行う液晶駆動回路の出力ブロック図であり、隣り合う2つの出力回路部分のみを示す。図39及び図40は、液晶駆動電圧の極性を切り替えた場合の動作をそれぞれ示している。

【0079】図39及び図40において、2101は図33で示したNチャンネルMOSトランジスタ入力のオペアンプを示し、2102は図36で示したPチャンネルMOSトランジスタ入力のオペアンプを示し、2103は正極性の液晶駆動電圧を発生するD/A変換回路を示し、2104は負極性の液晶駆動電圧を発生するD/A変換回路を示し、2105～2108は液晶駆動電圧を交流化するためのスイッチを示し、2109は奇数番目の出力端子の表示データを記憶するラッチ回路を示し、2110は偶数番目の出力端子の表示データを記憶するラッチ回路を示し、2111は奇数番目の出力端子を示し、2112は偶数番目の出力端子を示し、2113は交流化スイッチ切替信号入力を示し、2114は図33や図36で示したオペアンプのスイッチ切替信号を示す。なお、ここでのラッチ回路2109や2110は、図16のホールドメモリを示し、レベルシフタ回路は省略された形で説明している。

【0080】以下、これらの図を使用して奇数番目の出力端子の動作について説明する。偶数番目の出力端子については、その駆動電圧極性が逆になるだけで同一の動作をするため、詳細な説明を省略する。

【0081】図39は、奇数番目の出力端子2111が正極性駆動電圧を出力し、偶数番目の出力端子2112が負極性駆動電圧を出力する場合を示す。この場合、奇数番目の出力端子の表示データは、ラッチ回路2109

からスイッチ2105を介して正極性用D/A変換回路2103へ送られ、その出力がオペアンプ2101に与えられた後、スイッチ2107を介して奇数番目の出力端子2111から出力される（図39中の太線で示す矢印を参照）。

【0082】図40は、奇数番目の出力端子2111が負極性駆動電圧を出力し、偶数番目の出力端子2112が正極性駆動電圧を出力する場合を示す。この場合、奇数番目の出力端子の表示データは、ラッチ回路2109からスイッチ2106を介して負極性用D/A変換回路2104へ送られ、その出力がオペアンプ2102に与えられた後、スイッチ2107を介して奇数番目の出力端子2111から出力される（図40中の太線で示す矢印を参照）。

【0083】ここで、オペアンプが製造上の理由等で特性が異なり、偶発的に発生するオフセット電圧を持つ場合について説明する。前述したように、ここで示すオペアンプはスイッチ切替信号により、そのオフセットの符号を反転させることができ、このときのオフセット電圧の絶対値は同じであることから、オペアンプ2101がオフセット電圧A又は-Aに切り替えることができ、オペアンプ2102がオフセット電圧B又は-Bに切り替えることができるものとする。この場合、奇数番目の出力端子の出力電圧は、正極性出力時はA又は-Aのオフセットを持ち、負極性出力時はB又は-Bのオフセットを持つことになる。オフセットの符号の選択は、前述のオペアンプのスイッチ切替信号で行われる。

【0084】次に、図7は、図39及び図40における差動増幅回路2115の具体的構成例を示すものであり、図7において、2501は図33で示したNチャンネルMOSトランジスタ入力のオペアンプに対応し、2502は図36で示したPチャンネルMOSトランジスタ入力のオペアンプに対応している。図7の2501内のスイッチ回路2501aは、図33のスイッチ1306～1309からなり、図7の2501内のスイッチ回路2501bは、図33のスイッチ1310～1313からなる。また、図7の2502内のスイッチ回路25

02aは、図36のスイッチ1606～1609からなり、図7の2502内のスイッチ回路2502bは、図36のスイッチ1610～1613からなる。

【0085】また、図7において、2507及び2508は、図39及び図40におけるスイッチ2107及び2108にそれぞれ対応している。更に、図7において、出力端子2511及び2512は、図39及び図40における出力端子2111及び2112にそれぞれ対応している。図7中、VBNおよびVBPは、オペアンプに動作点を与えるためのバイアス電圧入力端子をそれぞれ示す。更に、図7中の2513は図39及び図40中の2113（交流化スイッチ切替信号入力）に対応し、図7中の2514は図39及び図40中の2114（図33及び図36で示したオペアンプのスイッチ切替信号入力端子）に対応する。

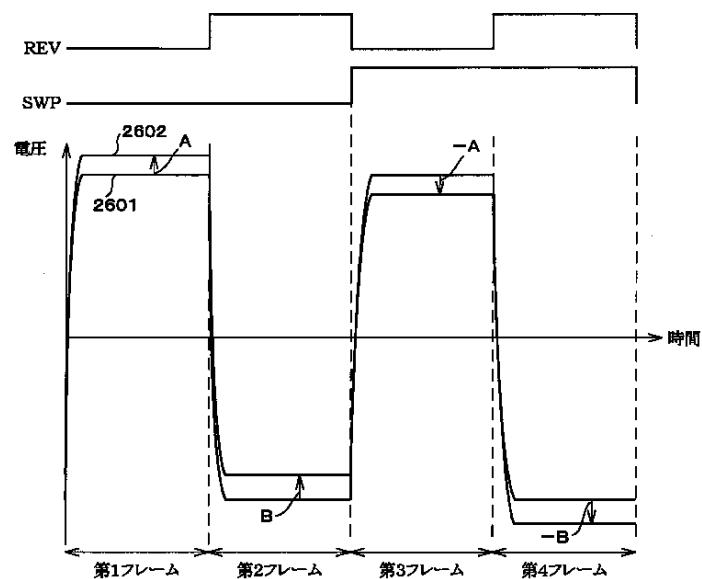

【0086】そして、交流化スイッチ切替信号REV、及びオペアンプのスイッチ切替信号SWPと出力の関係を示したもののが、図41と表1である。

【0087】図41において、2601は奇数番目の出力端子からの出力電圧により駆動される画素電圧の理想値を示し、2602はオフセット電圧が加味された実際の電圧を示す。交流化スイッチ切替信号REVは、1フレーム毎に反転しており、オペアンプのスイッチ切替信号SWPは2フレーム毎に反転している。この結果、画素電圧の理想値と実際の電圧との差は、1フレーム毎に順次、A、B、-A、-Bと変化し、4フレームで最初の状態に戻る。

【0088】ここで、第1フレームと第3フレームの偏差、及び第2フレームと第4フレームの偏差は互いに逆符号で等しくなる。フレームの周期が液晶材料の反応時間に対して十分短ければ、第1フレームと第3フレームとで偏差は打ち消され、また、第2フレームと第4フレームとで偏差が打ち消される。偶数番目の出力端子でも同様に4フレーム毎に偏差は打ち消される。これらをまとめると表1のようになる。

【0089】

【表1】

| 入力信号  |       | 出力端子       |            |

|-------|-------|------------|------------|

| S W P | R E V | 奇数番目の出力端子  | 偶数番目の出力端子  |

| ローレベル | ローレベル | 正極性（偏差 A）  | 負極性（偏差 B）  |

| ローレベル | ハイレベル | 負極性（偏差 B）  | 正極性（偏差 A）  |

| ハイレベル | ローレベル | 正極性（偏差 -A） | 負極性（偏差 -B） |

| ハイレベル | ハイレベル | 負極性（偏差 -B） | 正極性（偏差 -A） |

【0090】以上より、液晶駆動出力端子毎の偏差のバラツキは、各々の表示画素での打ち消し動作により、人の目に表示むらとして識別されることはなく、良質な表示を行うことが可能となる。

#### 【0091】

【発明が解決しようとする課題】しかしながら、上記従来の技術によれば、ソースドライバの出力回路部（図16参照）を構成する差動増幅器（オペアンプ回路）の構造上の条件のバラツキ等により偶発的に発生するオフセット電圧（このオフセット電圧は、主として、差動増幅器の入力段を構成する差動部で発生する。）が液晶表示素子への理想の駆動電圧からの誤差を生み、これにより表示画像が適切に表示されず、いわゆる表示むらが発生し、表示品位を低下させる要因となっていた。

【0092】上記第1従来技術では、一つの出力端子に正極性電圧および負極性電圧の双方を出力（フルレンジ）できるようにNチャンネルMOSトランジスタを入力段にもつオペアンプとPチャンネルMOSトランジスタを入力段にもつオペアンプ2個を有する構成を示した。これにより、図20に示すようにオフセット電圧に起因する偏差A、-Aを2フレームで打ち消していた。しかしながら、この回路構成は、1出力端子毎にオペアンプ2個を有するので、回路規模が大きくチップサイズの増大を招来するという不具合があった。しかも、比較的消費電力が大きいオペアンプ回路が多くなるので、低消費電力化のネックにもなっていた。

【0093】一方、上記第2従来技術では、正極性電圧は入力段にNチャンネルMOSトランジスタを使用したオペアンプから出力すると共に、負極性電圧は入力段にPチャンネルMOSトランジスタを使用したオペアンプから出力し、正極性／負極性電圧を切替スイッチで切り替えてフルレンジ出力にしていた。これによれば、オペアンプ回路の数が半減するので、回路規模の縮小および低消費電力化が実現できる。

【0094】しかしながら、上記第2従来技術では、NチャンネルMOSトランジスタを使用したオペアンプ回

路で発生するオフセット電圧による偏差Aと、PチャンネルMOSトランジスタを使用したオペアンプ回路で発生するオフセット電圧による偏差Bを打ち消すことができず（図19参照）、液晶表示素子への理想の駆動電圧からの誤差が解消できず、これにより、表示画像が適切に表示されず、いわゆる表示むらが発生し、表示品位を低下させる要因となっていた。

【0095】また、上記第3従来技術では、前述の正極性電圧は入力段にNチャンネルMOSトランジスタを使用したオペアンプから出力すると共に、負極性電圧は入力段にPチャンネルMOSトランジスタを使用したオペアンプ回路から出力し、正極性電圧／負極性電圧を切替スイッチで切り替えてフルレンジ出力にするのに加えて、更にオペアンプ入力端子（同相入力端子および逆相入力端子）への入力信号として、同相入力信号もしくは逆相入力信号を切り替えて入力することで、前述の正極性電圧／負極性電圧に加えて、入力信号切り替えによって新たに正極性電圧／負極性電圧（前述の正極性電圧／負極性電圧を反転したもの）を作りだすことによって、NチャンネルMOSトランジスタを使用したオペアンプ回路で発生するオフセット電圧による偏差A、-A、PチャンネルMOSトランジスタを使用したオペアンプで発生するオフセット電圧による偏差Bと-Bをフレーム間で切り替えることで4フレーム間で上記偏差を打ち消し（図41および表1を参照）、いわゆる表示むらの発生をなくしていた。

【0096】本発明は上記問題点に鑑みなされたものであり、その目的は、正極性電圧出力用オペアンプと負極性電圧出力用オペアンプとを別々に設け、同相入力信号と逆相入力信号を切り替えて出力する液晶表示装置の駆動装置および駆動方法において、フレーム間での偏差の相殺ではなく、ある画素に存在する偏差をその画素の周辺画素に持たせる偏差で上記表示むらを識別できなくなるという従来技術（フレーム間での偏差の相殺）とは異なる手法を提供することにある。

【0097】本発明の背景には、液晶表示パネルの高画

素化、高微細化が進み、画素サイズが小さくなつたことから、1個1個の画素の識別は難しくなり、人の視覚は周辺画素も含めて感知されるようになったことが挙げられる。つまり、ある画素に印加されるオフセット電圧と、その画素の周辺画素に印加されるオフセット電圧の極性を逆にすることで空間的に均一（同一フレーム内）に偏差を分散させ、いわゆる表示むらを視覚的には感じられないようとするものである。

## 【0098】

【課題を解決するための手段】本発明に係る液晶表示装置の駆動装置は、上記の課題を解決するために、同相入力端子及び逆相入力端子と、同相出力端子及び逆相出力端子とを備え、第1及び第2增幅回路からなる差動增幅回路と、上記入力端子を介してそれぞれ入力される同相および逆相の入力信号を切替信号に基づいて切り替えて第1及び第2增幅回路へ入力する第1切替回路と、第1及び第2增幅回路からそれぞれ出力される出力信号を交流化信号に基づいて切り替えて上記出力端子を介してマトリックス状に配された画素へ出力する第2切替回路と、或る画素に印加されるオフセット電圧と、該画素に隣接する画素のうち斜め上および斜め下の画素にそれぞれ印加されるオフセット電圧とは、極性が互いに逆であり且つ絶対値が互いに等しくなるように、上記第1及び第2切替回路をそれぞれ切り替える切替制御回路とを備えた構成を有している。

【0099】上記の発明によれば、同相入力信号と逆相入力信号が切り替えられると共に、上記增幅回路の出力がそれぞれ切り替えられてマトリックス状に配された画素に出力され、これにより液晶表示装置が駆動される。

【0100】ところで、本来、同じ回路特性を有すべき第1及び第2增幅回路に、製造上のバラツキ等に起因して、回路特性において差が生じた場合、出力信号にオフセット電圧が生じてしまう。また、近年、液晶表示パネルの高画素化、高微細化が進み、画素サイズが小さくなつておらず、1個1個の画素の識別は難しくなり、その結果、人の視覚は周辺画素も含めて感知されるようになつていている。

【0101】そこで、上記発明においては、上記增幅回路の出力が切替制御回路によって適宜切り替えられ、ある画素に印加されるオフセット電圧と、その画素の周辺画素に印加されるオフセット電圧の極性を逆にすることで空間的に均一にオフセット電圧（偏差）を分散させ、いわゆる表示むらを視覚的には感じられないよう正在している。

【0102】このように、フレーム間でのオフセット電圧の相殺ではなく、ある画素に存在するオフセット電圧をその画素の周辺画素の逆極性のオフセット電圧で相殺することによって、上記表示むらを識別できなくしている。これにより、液晶表示パネルの高画素化、高微細化が更に進んでも対応が可能となり、非常に信頼性の高い

液晶表示装置の駆動装置を提供することができる。

【0103】上記発明において、オフセット電圧の上記相殺は次のように行われる。すなわち、上記切り替え制御回路は、或る画素に印加されるオフセット電圧と、該画素に隣接する画素のうち斜め上および斜め下の画素にそれぞれ印加されるオフセット電圧とは、極性が互いに逆であり且つ絶対値が互いに等しくなるように、上記第1及び第2切替回路をそれぞれ切り替える。これにより、或る画素のオフセット電圧は、該画素に隣接する画素のうち斜め上および斜め下の合計4個の画素にそれぞれ印加される絶対値が等しく逆極性のオフセット電圧によって打ち消されるので、表示むらを改善できる。

【0104】上記切替制御回路は、水平同期信号又は1水平同期期間毎に出力される信号に同期して、1フレーム内では1水平同期期間毎に上記第1及び第2切替回路を切り替えることが好ましい。

【0105】上記切替制御回路は、水平ライン数が偶数か奇数かを識別し、この識別結果に基づいて、上記第1及び第2切替回路を逆相の切替信号による切り替えと、同相の切替信号による切り替えとをフレーム毎に交互に行う制御と、上記第1及び第2切替回路を逆相の切替信号による切り替えのみを行う制御とを選択的に切り替えることが好ましい。

【0106】上記切替制御回路は、例えば、次の構成により実現できる。すなわち、上記切替制御回路は、水平同期信号、または1水平同期期間毎に出力される信号を1/2分周し、これを切替信号として上記の第1切替回路へ出力する第1分周回路と、垂直同期信号を1/2分周する第2分周回路と、上記の第2分周回路の出力と、水平ライン数が偶数か奇数かを識別する識別信号とに基づき、水平ライン数が奇数の場合に第1開閉制御信号を生成する一方、水平ライン数が偶数の場合に奇数番目のフレームにおいて第1開閉制御信号を生成すると共に偶数番目のフレームにおいて上記の第2開閉制御信号を生成する開閉制御信号生成回路と、上記の第1開閉制御信号が入力され、上記の切替信号の逆相信号を上記交流化信号として上記の第2切替回路へ出力するために閉状態になる第1スイッチ回路と、上記の第2開閉制御信号が入力され、上記切替信号の同相信号を上記交流化信号として上記の第2切替回路へ出力するために閉状態になる第2スイッチ回路とを備えていることが好ましい。

【0107】この場合、水平同期信号、または1水平同期期間毎に出力される信号は、第1分周回路によって1/2分周され、第1切替回路の切替信号として使用される。垂直同期信号は第2分周回路によって1/2分周されて開閉制御信号生成回路に出力される。この開閉制御信号生成回路には、水平ライン数が偶数か奇数かを識別する識別信号が入力されている。

【0108】上記の開閉制御信号生成回路は、これらの入力信号に基づき、水平ライン数が奇数の場合に第1開

閉制御信号を生成する一方、偶数の場合にフレーム毎に異なる開閉制御信号を生成する（フレーム毎に第1開閉制御信号と第2開閉制御信号とを交互に生成する）。つまり、上記の開閉制御信号生成回路は、水平ライン数が偶数の場合に、奇数番目のフレームにおいて第1開閉制御信号を生成すると共に、偶数番目のフレームにおいて上記の第2開閉制御信号を生成するようになっている。

【0109】水平ライン数が奇数の場合、第1開閉制御信号が第1スイッチ回路に入力されるので、第1スイッチ回路が閉状態になる。これにより、上記の切替信号の逆相信号が上記交流化信号として上記の第2切替回路へ出力される。

【0110】これに対して、水平ライン数が偶数の場合、奇数番目のフレームにおいては、第1開閉制御信号が第1スイッチ回路に入力されるので、第1スイッチ回路が閉状態になる。これにより、上記切替信号の逆相信号が上記交流化信号として上記の第2切替回路へ出力される。一方、水平ライン数が偶数の場合、偶数番目のフレームにおいては、第2開閉制御信号が第2スイッチ回路に入力されるので、第2スイッチ回路が閉状態になる。これにより、上記の切替信号の同相信号が上記交流化信号として上記の第2切替回路へ出力される。

【0111】以上のように、構成を複雑化することなく、第1切替回路を切り替えるための信号から第2切替回路を切り替えるための交流化信号を容易に生成できる。

【0112】本発明に係る液晶表示装置の駆動方法は、同相入力端子及び逆相入力端子と、同相出力端子及び逆相出力端子とを有し、第1及び第2增幅回路からなる差動增幅回路を備え、上記入力端子を介してそれぞれ入力される同相および逆相の入力信号を切替信号に基づいて切り替えて第1及び第2增幅回路へ入力すると共に、第1及び第2增幅回路からそれぞれ出力される出力信号を交流化信号に基づいて切り替えて上記出力端子を介してマトリックス状に配された画素へ出力する液晶表示装置の駆動方法において、次の措置を講じたことを特徴としている。

【0113】すなわち、上記駆動方法は、或る画素に印加されるオフセット電圧と、該画素に隣接する画素のうち斜め上および斜め下の画素に印加されるオフセット電圧とは、極性が互いに逆であり且つ絶対値が互いに等しくなるように、上記切替信号および上記交流化信号を制御することを特徴としている。

【0114】上記の駆動方法によれば、切替信号および交流化信号を制御することによって、或る画素のオフセット電圧と、該画素に隣接する画素のうち斜め上および斜め下の合計4個の画素にそれぞれ印加されるオフセット電圧とは、絶対値が等しく且つ極性が逆になる。これにより、或る画素のオフセット電圧は、上記4個の隣接する画素のオフセット電圧によって打ち消されるので、

表示むらを更に改善できる。

【0115】上記切替信号は、水平同期信号、または1水平同期期間毎に出力される信号に基づいて制御され、垂直同期信号と水平ライン数が偶数か奇数かを識別する識別信号とに基づいて、上記切替信号の逆相信号と同相信号とをそれぞれ生成し、水平ライン数が偶数の場合には、上記切替信号の逆相信号と同相信号とをそれぞれフレーム毎に交互に切り替えて上記交流化信号とする一方、水平ライン数が奇数の場合には、上記逆相信号のみを上記交流化信号とするように制御されが好ましい。この場合、複雑な構成を必要とすることなく、交流化信号が切替信号に基づいて容易に生成できる。

【0116】

【発明の実施の形態】本発明の実施の一形態について図1乃至図11に基づいて説明すれば、以下のとおりである。

【0117】本実施の形態に係るTFTを用いた液晶表示装置を模式的に示したものが図6である。従来技術との差異は、ソースドライバへの制御信号として、更に、垂直同期信号と、偶数／奇数ライン識別信号とが加わったことである。図6のソースドライバ3802のブロック図を図1に示す。

【0118】図1中のシフトレジスタ回路4403、サンプリングメモリ回路4404、ホールドメモリ回路4405、レベルシフタ回路4406、D/A変換回路4407、基準電圧発生回路4402、入力ラッピング回路4401は、図16の対応する回路とそれぞれ同じであるので、説明を省略する。出力回路4408は、正極性電圧出力用オペアンプと負極性電圧出力用オペアンプとを別々に設けた回路構成のものである。

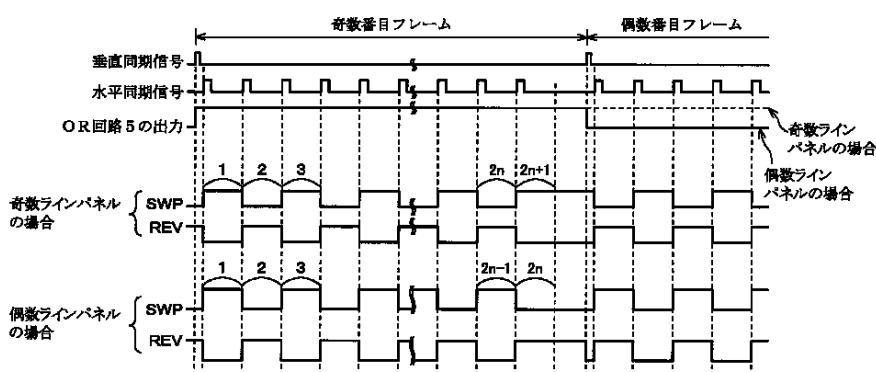

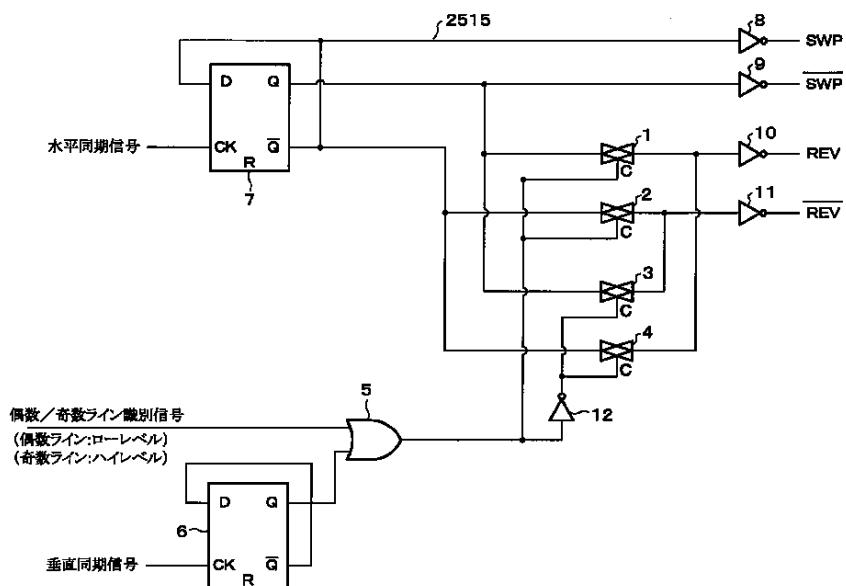

【0119】図1の切替制御回路2515の回路構成例を図2に示す。この切替制御回路2515の中には、後述のSWP（上記2つのオペアンプのスイッチ切替信号）/REV（交流化スイッチ切替信号）切替スイッチ回路も含まれている。

【0120】また、切替制御回路2515の入力信号波形および出力信号波形を図3に示す。更に、液晶表示パネル上の画素での、上記出力回路4408からのオフセット電圧出力分布を図4および図5に示す。なお、図4は、水平ライン数（図42でのゲート信号ライン3905に相当する行数）が偶数の場合（偶数ラインパネル）を示し、図5は水平ライン数が奇数の場合（奇数ラインパネル）を示している。

【0121】図4では行数が8ラインとして表示する一方、図5では7ラインで表示し、また、列数は、何れも、8ラインの液晶パネルとして表示しているが、これは説明の便宜上のものであり、本発明はこれに限定されるものではない。

【0122】上記の切替制御回路2515は、基本的には、水平同期信号の周波数を1/2分周する回路であ

り、例えば、図2に示すように、Dフリップフロップ7の入力端子Dと出力端子/Qとを接続し、クロック入力端子CKに水平同期信号を入力すると共に、Dフリップフロップ7の出力端子/Qはインバータ回路8を介してスイッチ切替信号SWPとして出力される一方、出力端子Qはインバータ回路9を介してスイッチ切替信号/SWPとして出力されるという簡単な回路構成で実現できる。

【0123】これにより、水平同期信号の立ち上がりに同期して変化する上記電圧出力用オペアンプのスイッチ切替信号SWPを生成する(SWPは、水平同期信号の立ち上がりに同期してローレベルからハイレベルに、またはハイレベルからローレベルに変化する。)。なお、/SWPは、SWPの反転信号である。

【0124】また、上記の交流化スイッチ切替信号REVも、1水平同期信号の立ち上がりに同期して変化する信号である(REVは、水平同期信号の立ち上がりに同期してローレベルからハイレベルに、またはハイレベルからローレベルに変化する。)。なお、/REVは、REVの反転信号である。この交流化スイッチ切替信号REVは、上記信号SWPから生成することが最も容易であり、これについて以下に説明する。

【0125】この交流化スイッチ切替信号REVの生成方法は、液晶表示パネルが偶数ラインパネル(水平ライン数が偶数)か奇数ラインパネル(水平ライン数が奇数)かで異なり、スイッチ切替信号SWPを切り替えて生成する。具体的には、次のとおりである。

【0126】すなわち、偶数ラインパネルの場合、第1フレーム(奇数番目のフレームであり、図4の

【0127】

【数1】

①

【0128】で示すフレーム)では、スイッチ切替信号SWPの反転信号(信号/SWP)を交流化スイッチ切替信号REVとして使用し、スイッチ切替信号SWPを、交流化スイッチ切替信号/REVとして使用する。次の第2フレーム(偶数番目のフレームであり、図4の

【0129】

【数2】

②

【0130】で示すフレーム)では、スイッチ切替信号SWPを交流化スイッチ切替信号REVとして使用し、スイッチ切替信号/SWPを交流化スイッチ切替信号/REVとして使用する。そして、第1フレームと第2フレームの上記動作を交互に繰り返す。

【0131】これに対して、奇数ラインパネルの場合、常に、スイッチ切替信号SWPを、交流化スイッチ切替信号/REVとして使用すると共に、スイッチ切替信号

/SWPを、交流化スイッチ切替信号REVとして使用する。

【0132】これらは、図2の信号SWPおよび/SWPの生成回路の出力段に、偶数ラインパネル(例えば、ローレベル)か、または奇数ラインパネル(例えば、ハイレベル)を識別する識別信号により、上記信号状態に切り替えるスイッチ手段と、さらに偶数ラインパネルの場合に第1フレームと第2フレームとで上記スイッチ手段を切り替える手段(これは、図2での1/2分周回路において、水平同期信号の代わりに、垂直同期信号をDフリップフロップのクロック入力端子CKに入力することで実現できる。)を設けることにより容易に実現できる。上記スイッチ手段としては、MOSトランジスタやトランスマッシュゲート等のアナログスイッチを用いればよい。

【0133】図2は、上記スイッチ手段としてトランスマッシュゲート1~4で構成した例を示している。トランスマッシュゲート1は、上記Dフリップフロップ7の出力端子Qとインバータ回路10との間に設けられ、トランスマッシュゲート2は、上記Dフリップフロップ7の出力端子/Qとインバータ回路11との間に設けられ、トランスマッシュゲート3は、上記Dフリップフロップ7の出力端子Qとインバータ回路11との間に設けられ、トランスマッシュゲート4は、上記Dフリップフロップ7の出力端子/Qとインバータ回路10との間に設けられ、上記インバータ回路10の出力端子から交流化スイッチ切替信号REVが出力され、上記インバータ回路11の出力端子から交流化スイッチ切替信号/REVが出力されるようになっている。

【0134】上記トランスマッシュゲート1~2のコントロール端子Cには後述するOR回路5の出力信号が印加され、上記トランスマッシュゲート3~4のコントロール端子Cには上記OR回路5の出力信号がインバータ回路12を介して印加されている。上記トランスマッシュゲート1~4は、コントロール端子Cにハイレベルが印加されているときに導通状態になる一方、ローレベルが印加されているときには非導通状態となり、前述の動作を行う。

【0135】なお、上記の偶数/奇数ライン識別信号がOR回路5の一方の入力端子に印加され、このOR回路5の他方の入力端子にはDフリップフロップ6の出力端子Qが接続されている。このDフリップフロップ6のクロック入力端子CKには垂直同期信号が印加され、その出力端子/Qと入力端子Dとが接続されている。

【0136】図2の構成によれば、偶数/奇数ライン識別信号がハイレベルの場合(奇数ラインパネルの場合)、Dフリップフロップ6からの信号に関係なく、OR回路5の出力は、常に、ハイレベルとなる(図3参照)。これにより、トランスマッシュゲート1~2が導通状態となり、スイッチ切替信号SWPが交流化スイ

スイッチ切替信号／REVとして使用されると共に、スイッチ切替信号／SWPが交流化スイッチ切替信号REVとして使用される。

【0137】これに対して、偶数／奇数ライン識別信号がローレベルの場合（偶数ラインパネルの場合）、OR回路5の出力信号は、第1フレーム（図4の

【0138】

【数3】

①

【0139】で示すフレーム）と第2フレーム（図4の【0140】

【数4】

②

【0141】で示すフレーム）とで異なる（図3参照）。

【0142】第1フレーム（奇数番目のフレーム）のときには、垂直同期信号の立ち上がりに同期して、Dフリップフロップ6の出力端子Qがローレベルからハイレベルに変化するので、OR回路5の出力信号はハイレベルとなる。これにより、トランスマッショングート1・2は、コントロール端子Cにハイレベルの信号が印加されるので、導通状態となり、スイッチ切替信号SWPが交流化スイッチ切替信号／REVとして使用され、スイッチ切替信号／SWPが交流化スイッチ切替信号REVとして使用される。つまり、スイッチ切替信号と交流化スイッチ切替信号とは、逆相の関係になる（図3参照）。

【0143】一方、第2フレーム（偶数番目のフレーム）のときには、垂直同期信号の立ち上がりに同期して、Dフリップフロップ6の出力端子Qがハイレベルからローレベルに変化するので、OR回路5の出力信号はローレベルとなる。これにより、トランスマッショングート3・4は、コントロール端子Cにハイレベルの信号が印加されるので、導通状態となり、スイッチ切替信号／SWPが交流化スイッチ切替信号／REVとして使用され、スイッチ切替信号SWPが交流化スイッチ切替信号REVとして使用される。スイッチ切替信号と交流化スイッチ切替信号とは、同相の関係になる（図3参照）。

【0144】また、図2では、1/2分周回路であるDフリップフロップ6・7のリセット入力端子Rへの配線は省略しているが、複数個のソースドライバで構成されている場合、各ソースドライバ内のスイッチ切替信号SWPと交流化スイッチ切替信号REVの位相を合わせるため、電源投入時にリセット信号を入れるか、この図2の例では2フレーム毎にリセット信号を入れる方が好ましい。

【0145】なお、図2は、スイッチ切替信号SWP、及び交流化スイッチ切替信号REVを生成する構成を示す

しているが、本発明はこれに限定されるものではなく、例えば、マイクロコンピュータで構成されたコントローラから、上記タイミングでスイッチ切替信号SWP、及び交流化スイッチ切替信号REVを出力するようにプログラムさせていてもよい。

【0146】また、図7での“H”側DACよりは、図39での2103からの入力信号である一方、“L”側DACよりは、図39での2104からの入力信号である。

【0147】図7のオペアンプにスイッチ切替信号SWP及び／SWPと、交流化スイッチ切替信号REV及び／REVを入力すると、これらの信号により出力端子に出力される出力信号のオフセット電圧は、前述の表1に表されるようになる。

【0148】なお、図7中、VBNおよびVBPはオペアンプの動作点を与えるためのバイアス電圧入力端子であり、オペアンプが歪みの無い増幅が行えるように適切なバイアス電圧が印加されているものとする。

【0149】図4（偶数ラインパネル）の

【0150】

【数5】

①

【0151】で示すフレーム（第1フレーム（奇数番目のフレーム））の

【0152】

【数6】

①

【0153】で示す行において、交流化スイッチ切替信号REVがローレベル（L）である一方、信号SWPがハイレベル（H）であるとすれば、

【0154】

【数7】

①

【0155】で示す行における奇数番目の画素には-Aのオフセット電圧が、一方、偶数番目の画素には-Bのオフセット電圧が含まれた信号が出力されることになる。

【0156】そして、次の

【0157】

【数8】

②

【0158】で示す行では、交流化スイッチ切替信号REVが反転しハイレベル（H）となり、一方、スイッチ切替信号SWPも反転しローレベル（L）となるので、

【0159】

【数9】

31

②

【0160】で示す行の奇数番目の画素には+Bのオフセット電圧が、一方、偶数番目の画素には+Aのオフセット電圧が含まれた信号が出力される。以降、同様に繰り返されて最下行である

【0161】

【数10】

⑧

【0162】で示す行まで出力される。

【0163】それから、

【0164】

【数11】

②

【0165】で示すフレーム（第2フレーム（奇数番目のフレーム））の

【0166】

【数12】

①

【0167】で示す行において、スイッチ切替信号SWPはハイレベル（H）となるので、奇数番目の画素には-Bのオフセット電圧が、一方、偶数番目の画素には-Aのオフセット電圧が含まれた信号が出力されることになる。

【0168】そして、次の

【0169】

【数13】

②

【0170】で示す行では、交流化スイッチ切替信号REVが反転しローレベル（L）となり、一方、スイッチ切替信号SWPも反転しローレベル（L）となるため、

【0171】

【数14】

②

【0172】で示す行の奇数番目の画素には+Aのオフセット電圧が、一方、偶数番目の画素には+Bのオフセット電圧が含まれた信号が出力される。以降、同様に繰り返されて最下行の

【0173】

【数15】

⑧

【0174】で示す行まで出力される。

【0175】以上の動作は、

【0176】

【数16】

①

【0177】で示すフレーム→

【0178】

【数17】

②

【0179】で示すフレーム→

10 【0180】

【数18】

①

【0181】で示すフレーム→

【0182】

【数19】

②

20 【0183】で示すフレームと反復して、前述の動作が繰り返されることになる。これらの動作により、偶数ラインパネルの各画素への印加電圧に含まれるオフセット電圧の分散状態を示したものが、図4である。

【0184】図4のオフセット電圧の分散（分布）状態から、正極性電圧（入力段がNチャンネルMOSトランジスタであるオペアンプによるオフセット電圧+A、-Aが信号に含まれる。）のみ抽出したものが図8である。

【0185】一方、図4のオフセット電圧の分散状態から、負極性電圧（入力段がPチャンネルMOSトランジスタであるオペアンプによるオフセット電圧+B、-Bが信号に含まれる。）のみ抽出したものが図9である。

【0186】何れの場合も、ある画素に印加されたオフセット電圧が例えば+A（-B）とすると、斜め上下（対角線上）の4個の画素にそれぞれ印加されたオフセット電圧は-A（+B）となることがわかる。これは、奇数パネルラインでも同様である（図5、図10、および図11参照）。スイッチ切替信号SWP及び交流化スイッチ切替信号REVの信号状態による出力関係は、偶数パネルラインと同じであるので、説明は省略する。

【0187】このように、正極性のオフセット電圧(+A、+B)が印加された画素の斜め上下の画素には必ず同じ値（絶対値が同じ）の負極性のオフセット電圧(-A、-B)が印加されることになる。あるいは、その逆である。これにより、前述したように、液晶表示パネルの高画素化、高微細化が進み、画素サイズが十分小さくなつたことから、ある画素に印加されるオフセット電圧と、その画素の周辺画素（正確には斜め上下の画素）に印加されるオフセット電圧の極性を逆にし配置することで空間的に均一に偏差を分散させ、いわゆる表示むらを視覚的に感じられないようにすることができる。

【0188】以上説明した液晶表示パネルの駆動方法（同一フレーム内にて、斜め上下の周辺画素に正負逆で絶対値が等しいオフセット電圧を印加する駆動方法）の具体的実現方法は、一例であり、特にこれに限定されるものではない。本主旨を逸脱しない範囲で様々なに変更可能であることは言うまでもない。

【0189】例えば、図2での切替制御回路2515において、水平同期信号（ラッチ信号とも言う）を用いているが、水平同期信号とほぼ同じタイミングで出力されるスタートパルス信号（この場合は、ソースドライバ内のシフトレジスタ回路4403を転送されていない、つまり、コントローラ3804から出力された直後の信号）を使用しても同じような回路構成にて実現できる。

【0190】また、図2での切替制御信号は、ソースドライバ内で生成された例で説明しているが、切替制御回路を図6のコントローラ3804内で生成し、スイッチ切替信号SWPや交流化スイッチ切替信号REVをソースドライバに出力した構成でも良いし、水平同期信号の1/2分周回路部もしくは垂直同期信号の1/2分周回路部やこれらに付随する切替スイッチ部をコントローラかソースドライバに分離して設置しても勿論良い。

【0191】本発明は、以上のように、同相及び逆相の入力信号を増幅する第1及び第2増幅回路と、上記2つの入力信号を選択的に切り替えて上記の第1及び第2増幅回路へ入力すると共に、上記の第1又は第2増幅回路の一方によって増幅された同相入力信号を逆相出力信号として出力する一方、上記第1又は第2増幅回路の他方によって増幅された逆相入力信号を同相出力信号として出力されるので、同相出力信号に生じるオフセットと、逆相出力信号に生じるオフセットとは、逆極性で絶対値が等しくなる液晶駆動装置において、オペアンプのスイッチ切替信号SWPと交流化信号REVを1水平同期信号ごとに切り替えることで、正極性のオフセット電圧(+A, +B)が加味された画素の斜め上下の画素には必ず同じ値で負極性のオフセット電圧(-A, -B)が加味されることになる。或いは、その逆である。これにより、1画素のサイズが十分小さいため、同一フレーム内でいわゆる表示むらを視覚的に感じられないようにすることができ、非常に表示品位の良い液晶表示を実現できる。このことは、例えば、フレーム周波数を低くした場合や、液晶材料の応答速度が速くなった場合への対応で効果を奏する。また、前述のように、消費電力の大きいオペアンプを削減したタイプに適用することによる低消費電力のメリットはそ

のまま維持されている。

【0192】本発明の液晶表示装置を駆動する液晶駆動装置は、ドット反転方式により液晶表示装置を駆動する液晶駆動装置の出力段が、同相の表示入力信号と逆相の表示入力信号を第1の切替手段で切り替えて増幅し、さらに第2の切替手段で切り替えて出力する第1の差動増幅部と第2の差動増幅部で構成されている液晶駆動装置であって、前記第1の切替手段と前記第2の切替手段を、各々前記液晶表示装置を走査する水平同期信号あるいは1水平同期期間ごとに出力される信号に同期を取り、1フレーム内では1水平同期期間ごとに切り替える制御手段を有したことの特徴としている。

【0193】前記制御手段には、前記液晶表示装置が偶数行パネルか奇数行パネルかを識別し、この識別結果により、前記第1の切替手段と前記第2の切替手段を逆相の切替信号による切り替えと、同相の切替信号による切り替えをフレーム毎に交互に行う制御と、前記第1の切替手段と前記第2の切替手段を逆相の切替信号による切り替えのみを行う制御に切り替える手段を更に有していることが好ましい。

【0194】本発明の液晶表示装置の駆動方法は、ドット反転方式により液晶表示装置を駆動する液晶駆動装置の出力段が、同相の表示入力信号と逆相の表示入力信号を第1の切替手段で切り替えて増幅し、さらに第2の切替手段で切り替えて出力する第1の差動増幅部と第2の差動増幅部で構成されている液晶駆動装置による液晶表示装置の駆動方法であって、前記第1の切替手段と前記第2の切替手段を、各々前記液晶表示装置を走査する水平同期信号あるいは1水平同期期間ごとに出力される信号に同期を取って切り替えることで、前記第1の差動増幅部と前記第2の差動増幅部の出力に含まれる各々の偏差が前記液晶表示装置の画素への信号電圧に加味されて印加される際、任意の画素に加味される偏差に対して、その画素の斜め上下の4画素には、前記偏差とは絶対値が同じで極性が異なる偏差が印加されるように駆動することの特徴としている。

【0195】前記駆動方法は、前記液晶表示装置が偶数行パネルか奇数行パネルかを識別し、この識別結果により、前記第1の切替手段と前記第2の切替手段を逆相の切替信号による切り替えと、同相の切替信号による切り替えをフレーム毎に交互に行う制御と、前記第1の切替手段と前記第2の切替手段を逆相の切替信号による切り替えのみを行う制御に切り替える手段を更に有していることが好ましい。

【0196】

【発明の効果】本発明に係るは、以上のように、同相入力端子及び逆相入力端子と、同相出力端子及び逆相出力端子とを備え、第1及び第2増幅回路からなる差動増幅回路と、上記入力端子を介してそれぞれ入力される同相および逆相の入力信号を切替信号に基づいて切り替えて

第1及び第2增幅回路へ入力する第1切替回路と、第1及び第2增幅回路からそれ出力される出力信号を交流化信号に基づいて切り替えて上記出力端子を介してマトリックス状に配された画素へ出力する第2切替回路と、或る画素に印加されるオフセット電圧と、該画素に隣接する画素のうち斜め上および斜め下の画素にそれぞれ印加されるオフセット電圧とは、極性が互いに逆であり且つ絶対値が互いに等しくなるように、上記第1及び第2切替回路をそれぞれ切り替える切替制御回路とを備えていることを特徴としている。

【0197】上記発明においては、上記增幅回路の出力が切替制御回路によって適宜切り替えられ、ある画素に印加されるオフセット電圧と、その画素の周辺画素に印加されるオフセット電圧の極性を逆にして空間的に均一にオフセット電圧（偏差）を分散させ、いわゆる表示むらを視覚的には感じられないようしている。

【0198】このように、フレーム間でのオフセット電圧の相殺ではなく、ある画素に存在するオフセット電圧をその画素の周辺画素の逆極性のオフセット電圧で相殺することによって、上記表示むらを識別できなくしている。これにより、液晶表示パネルの高画素化、高微細化が更に進んでも対応が可能となり、非常に信頼性の高い液晶表示装置の駆動装置を提供することができる。

【0199】上記発明において、オフセット電圧の上記相殺は次のように行われる。すなわち、上記切り替え制御回路は、或る画素に印加されるオフセット電圧と、該画素に隣接する画素のうち斜め上および斜め下の画素にそれぞれ印加されるオフセット電圧とは、極性が互いに逆であり且つ絶対値が互いに等しくなるように、上記第1及び第2切替回路をそれぞれ切り替える。これにより、或る画素のオフセット電圧は、該画素に隣接する画素のうち斜め上および斜め下の合計4個の画素にそれぞれ印加される絶対値が等しく逆極性のオフセット電圧によって打ち消されるので、表示むらを更に改善できるという効果を併せて奏する。

【0200】上記切替制御回路は、水平同期信号又は1水平同期期間毎に出力される信号に同期して、1フレーム内では1水平同期期間毎に上記第1及び第2切替回路を切り替えることが好ましい。

【0201】上記切替制御回路は、水平ライン数が偶数か奇数かを識別し、この識別結果に基づいて、上記第1及び第2切替回路を逆相の切替信号による切り替えと、同相の切替信号による切り替えとをフレーム毎に交互に行う制御と、上記第1及び第2切替回路を逆相の切替信号による切り替えのみを行う制御とを選択的に切り替えることが好ましい。

【0202】上記切替制御回路は、例えば、次の構成により実現できる。すなわち、上記切替制御回路は、水平同期信号、または1水平同期期間毎に出力される信号を1/2分周し、これを切替信号として上記の第1切替回

路へ出力する第1分周回路と、垂直同期信号を1/2分周する第2分周回路と、上記の第2分周回路の出力と、水平ライン数が偶数か奇数かを識別する識別信号とに基づき、水平ライン数が奇数の場合に第1開閉制御信号を生成する一方、水平ライン数が偶数の場合に奇数番目のフレームにおいて第1開閉制御信号を生成すると共に偶数番目のフレームにおいて上記の第2開閉制御信号を生成する開閉制御信号生成回路と、上記の第1開閉制御信号が入力され、上記の切替信号の逆相信号を上記交流化信号として上記の第2切替回路へ出力するために閉状態になる第1スイッチ回路と、上記の第2開閉制御信号が入力され、上記切替信号の同相信号を上記交流化信号として上記の第2切替回路へ出力するために閉状態になる第2スイッチ回路とを備えていることが好ましい。

【0203】この場合、水平同期信号、または1水平同期期間毎に出力される信号は、第1分周回路によって1/2分周され、第1切替回路の切替信号として使用される。垂直同期信号は第2分周回路によって1/2分周されて開閉制御信号生成回路に出力される。この開閉制御信号生成回路には、水平ライン数が偶数か奇数かを識別する識別信号が入力されている。

【0204】上記の開閉制御信号生成回路は、これらの入力信号に基づき、水平ライン数が奇数の場合に第1開閉制御信号を生成する一方、偶数の場合にフレーム毎に異なる開閉制御信号を生成する（フレーム毎に第2開閉制御信号と第1開閉制御信号とを交互に生成する）。つまり、上記の開閉制御信号生成回路は、水平ライン数が偶数の場合に、奇数番目のフレームにおいて第1開閉制御信号を生成すると共に、偶数番目のフレームにおいて上記の第2開閉制御信号を生成するようになっている。

【0205】水平ライン数が奇数の場合、第1開閉制御信号が第1スイッチ回路に入力されるので、第1スイッチ回路が閉状態になる。これにより、上記の切替信号の逆相信号が上記交流化信号として上記の第2切替回路へ出力される。

【0206】これに対して、水平ライン数が偶数の場合、奇数番目のフレームにおいては、第1開閉制御信号が第1スイッチ回路に入力されるので、第1スイッチ回路が閉状態になる。これにより、上記切替信号の逆相信号が上記交流化信号として上記の第2切替回路へ出力される。一方、水平ライン数が偶数の場合、偶数番目のフレームにおいては、第2開閉制御信号が第2スイッチ回路に入力されるので、第2スイッチ回路が閉状態になる。これにより、上記の切替信号の同相信号が上記交流化信号として上記の第2切替回路へ出力される。

【0207】以上のように、構成を複雑化することなく、第1切替回路を切り替えるための信号から第2切替回路を切り替えるための交流化信号を容易に生成できるという効果を併せて奏する。

【0208】本発明に係る液晶表示装置の駆動方法は、

或る画素に印加されるオフセット電圧と、該画素に隣接する画素のうち斜め上および斜め下の画素に印加されるオフセット電圧とは、極性が互いに逆であり且つ絶対値が互いに等しくなるように、上記切替信号および上記交流化信号を制御することを特徴としている。

【0209】上記の駆動方法によれば、切替信号および交流化信号を制御することによって、或る画素のオフセット電圧と、該画素に隣接する画素のうち斜め上および斜め下の合計4個の画素にそれぞれ印加されるオフセット電圧とは、絶対値が等しく且つ極性が逆になる。これにより、或る画素のオフセット電圧は、上記4個の隣接する画素のオフセット電圧によって打ち消されるので、表示むらを更に改善できるという効果を奏する。

【0210】上記切替信号は、水平同期信号、または1水平同期期間毎に出力される信号に基づいて制御され、垂直同期信号と水平ライン数が偶数か奇数かを識別する識別信号とに基づいて、上記切替信号の逆相信号と同相信号とをそれぞれ生成し、水平ライン数が偶数の場合には、上記切替信号の逆相信号と同相信号とをそれぞれフレーム毎に交互に切り替えて上記交流化信号とする一方、水平ライン数が奇数の場合には、上記逆相信号のみを上記交流化信号とするように制御されることが好ましい。この場合、複雑な構成を必要とすることなく、交流化信号が切替信号に基づいて容易に生成できるという効果を併せて奏する。

#### 【図面の簡単な説明】

【図1】本発明の液晶表示装置の駆動装置の要部構成例を示すブロック図である。

【図2】図1の切替制御回路の回路構成例を示す回路図である。

【図3】上記切替制御回路の要部信号波形を示す波形図である。

【図4】水平ライン数が偶数の場合の液晶表示パネル上の画素に印加されるオフセット電圧出力分布を示す説明図である。

【図5】水平ライン数が奇数の場合の液晶表示パネル上の画素に印加されるオフセット電圧出力分布を示す説明図である。

【図6】本発明と従来技術を説明するものであり、アクティブラミックス方式の代表例であるTFT液晶表示装置のブロック構成例を示す説明図である。

【図7】本発明と従来技術を説明するものであり、差動增幅回路の具体的構成例を示す回路図である。

【図8】図4のオフセット電圧出力の分布状態から、正極性電圧のみ抽出したものを示す説明図である。

【図9】図4のオフセット電圧出力の分布状態から、負極性電圧のみ抽出したものを示す説明図である。

【図10】図5のオフセット電圧出力の分布状態から、正極性電圧のみ抽出したものを示す説明図である。

【図11】図5のオフセット電圧出力の分布状態から、

負極性電圧のみ抽出したものを示す説明図である。

【図12】従来の液晶駆動波形の一例を示す波形図であり、ソースドライバの出力電圧が対向電極の電圧より高い時に上記ゲートドライバの出力によりTFTがオンし、画素電極へ対向電極に対して正極性の電圧が印加される場合を示している。

【図13】従来の液晶駆動波形の一例を示す波形図であり、ソースドライバの出力電圧が対向電極の電圧より低い時にゲートドライバの出力がTFTをオンして、画素電極へ対向電極に対して負極性の電圧が印加される場合を示している。

【図14】従来において、液晶駆動電圧を交流化する際の液晶パネル上の交流化の極性配列の一例を示す説明図である。

【図15】従来のドット反転駆動におけるソースドライバの駆動波形例を示す説明図である。

【図16】従来のソースドライバICの構成例を示すブロック図である。

【図17】(a) (b)は、第1従来技術に係るドット反転駆動を行うソースドライバICの出力回路のブロック構成図である。

【図18】(a) (b)は、第2従来技術に係るドット反転駆動を行うソースドライバICの出力回路のブロック構成図である。

【図19】従来のオペアンプが偶発的なオフセット電圧を持つ場合の液晶駆動電圧波形例を示す波形図である。

【図20】図17(a)および図17(b)の構成の場合の液晶駆動電圧波形を示す波形図である。

【図21】第3従来技術に係る差動増幅回路の構成例を示す回路図である。

【図22】図21の差動増幅回路の動作を示す説明図である。

【図23】図21の差動増幅回路の他の動作を示す説明図である。

【図24】図22の差動増幅回路を構成するトランジスタ間において、及び／又は負荷抵抗間において、製造上の理由などにより偶発的に発生する特性の不一致が存在する場合の動作を示す説明図である。

【図25】図23の上記差動増幅回路を構成するトランジスタ間において、及び／又は負荷抵抗間において、製造上の理由などにより偶発的に発生する特性の不一致が存在する場合の動作を示す説明図である。

【図26】上記第2従来技術に係る他の差動増幅回路を示す回路図である。

【図27】図26の差動増幅回路の動作を示す説明図である。

【図28】図26の差動増幅回路の他の動作を示す説明図である。

【図29】図27の上記差動増幅回路を構成するトランジスタ間において、及び／又は負荷抵抗間において、製

造上の理由などにより偶発的に発生する特性の不一致が存在する場合の動作を示す説明図である。

【図30】図28の上記差動増幅回路を構成するトランジスタ間において、及び／又は負荷抵抗間において、製造上の理由などにより偶発的に発生する特性の不一致が存在する場合の動作を示す説明図である。

【図31】図21の差動増幅回路の負荷素子をカレントミラー構成の能動負荷に変えた回路構成を示す回路図である。

【図32】図26の差動増幅回路の負荷素子をカレントミラー構成の能動負荷に変えた回路構成を示す回路図である。

【図33】図31に示す差動増幅回路と等価な差動増幅回路と、スイッチ及び出力部を具体化した例を示す回路図である。

【図34】図33のオペアンプの動作を示す回路図である。

【図35】図33のオペアンプの他の動作を示す回路図である。

【図36】図32に示す差動増幅回路と等価な差動増幅回路と、スイッチ及び出力部を具体化した例を示す回路図である。

【図37】図36のオペアンプの動作を示す回路図である。

【図38】図36のオペアンプの他の動作を示す回路図である。

【図39】差動増幅回路を使用したドット反転駆動を行う液晶駆動回路の出力ブロック図であり、奇数番目の出力端子が正極性駆動電圧を出力し、偶数番目の出力端子＊

＊が負極性駆動電圧を出力する場合を示す。

【図40】差動増幅回路を使用したドット反転駆動を行う液晶駆動回路の出力ブロック図であり、奇数番目の出力端子が負極性駆動電圧を出力し、偶数番目の出力端子が正極性駆動電圧を出力する場合を示す。

【図41】図41は、交流化スイッチ切替信号及びオペアンプのスイッチ切替信号と出力の関係を示す説明図である。

【図42】従来のTFT液晶パネルの構成を示す説明図である。

#### 【符号の説明】

|       |                        |

|-------|------------------------|

| 1・2   | トランスマッショングート（第1スイッチ回路） |

| 3・4   | トランスマッショングート（第2スイッチ回路） |

| 5     | OR回路                   |

| 6     | Dフリップフロップ（第2分周回路）      |

| 7     | Dフリップフロップ（第1分周回路）      |

| 8～12  | インバータ回路                |

| 2515  | 切替制御回路                 |

| 4408  | 出力回路                   |

| 2501a | スイッチ回路（第1切替回路）         |

| 2501b | スイッチ回路（第1切替回路）         |

| 2502a | スイッチ回路（第1切替回路）         |

| 25012 | スイッチ回路（第1切替回路）         |

| 2507  | スイッチ（第2切替回路）           |

| 2508  | スイッチ（第2切替回路）           |

| SWP   | スイッチ切替信号（切替信号）         |

| REV   | 交流化スイッチ切替信号（交流化信号）     |

【図3】

【図1】

【図12】

【図2】

【図5】

| (奇数ラインペネル)                |   |   |   |   |   |   |   | REV | SW |

|---------------------------|---|---|---|---|---|---|---|-----|----|

| ①                         | ② | ③ | ④ | ⑤ | ⑥ | ⑦ | ⑧ |     |    |

| ① -A -B -A -B -A -B -A -B | L | H |   |   |   |   |   |     |    |

| ② +B +A +B +A +B +A +B +A | H | L |   |   |   |   |   |     |    |

| ③ -A -B -A -B -A -B -A -B | L | H |   |   |   |   |   |     |    |

| ④ +B +A +B +A +B +A +B +A | H | L |   |   |   |   |   |     |    |

| ⑤ -A -B -A -B -A -B -A -B | L | H |   |   |   |   |   |     |    |

| ⑥ +B +A +B +A +B +A +B +A | H | L |   |   |   |   |   |     |    |

| ⑦ -A -B -A -B -A -B -A -B | L | H |   |   |   |   |   |     |    |

【図4】

| (偶数ラインパネル)                |                           |                           |                           |                           |                           |                           |                           | REV | SWP |

|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|-----|-----|

| ①                         | ②                         | ③                         | ④                         | ⑤                         | ⑥                         | ⑦                         | ⑧                         | L   | H   |

| ① -A -B -A -B -A -B -A -B | ② +B +A +B +A +B +A +B +A | ③ -A -B -A -B -A -B -A -B | ④ +B +A +B +A +B +A +B +A | ⑤ -A -B -A -B -A -B -A -B | ⑥ +B +A +B +A +B +A +B +A | ⑦ -A -B -A -B -A -B -A -B | ⑧ +B +A +B +A +B +A +B +A | H   | L   |

## ②フレーム

|     | (1) | (2) | (3) | (4) | (5) | (6) | (7) | (8) |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| (1) | +B  | +A  | +B  | +A  | +B  | +A  | +B  | +A  |

| (2) | -A  | -B  | -A  | -B  | -A  | -B  | -A  | -B  |

| (3) | +B  | +A  | +B  | +A  | +B  | +A  | +B  | +A  |

| (4) | -A  | -B  | -A  | -B  | -A  | -B  | -A  | -B  |

| (5) | +B  | +A  | +B  | +A  | +B  | +A  | +B  | +A  |

| (6) | -A  | -B  | -A  | -B  | -A  | -B  | -A  | -B  |

| (7) | +B  | +A  | +B  | +A  | +B  | +A  | +B  | +A  |

## ②フレーム

|     | (1) | (2) | (3) | (4) | (5) | (6) | (7) | (8) |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| (1) | -B  | -A  | -B  | -A  | -B  | -A  | -B  | -A  |

| (2) | +A  | +B  | +A  | +B  | +A  | +B  | +A  | +B  |

| (3) | -B  | -A  | -B  | -A  | -B  | -A  | -B  | -A  |

| (4) | +A  | +B  | +A  | +B  | +A  | +B  | +A  | +B  |

| (5) | -B  | -A  | -B  | -A  | -B  | -A  | -B  | -A  |

| (6) | +A  | +B  | +A  | +B  | +A  | +B  | +A  | +B  |

| (7) | -B  | -A  | -B  | -A  | -B  | -A  | -B  | -A  |

| (8) | +A  | +B  | +A  | +B  | +A  | +B  | +A  | +B  |

#### A：正極性電圧

B：負極性電圧

+ : 正側のオフセット

## 一：負側のオフセット

【図6】

[図24]

【図9】

(偶数ラインパネル)

①フレーム (負極性Bのみ抽出)

|   | ①  | ②  | ③  | ④  | ⑤ | ⑥ | ⑦ | ⑧ | REV | SWP |

|---|----|----|----|----|---|---|---|---|-----|-----|

| ① | -B | -B | -B | -B |   |   |   |   | L   | H   |

| ② | +B | +B | +B | +B |   |   |   |   | H   | L   |

| ③ | -B | -B | -B | -B |   |   |   |   | L   | H   |

| ④ | +B | +B | +B | +B |   |   |   |   | H   | L   |

| ⑤ | -B | -B | -B | -B |   |   |   |   | L   | H   |

| ⑥ | +B | +B | +B | +B |   |   |   |   | H   | L   |

| ⑦ | -B | -B | -B | -B |   |   |   |   | L   | H   |

| ⑧ | +B | +B | +B | +B |   |   |   |   | H   | L   |

②フレーム (負極性Bのみ抽出)

|   | ①  | ②  | ③  | ④  | ⑤ | ⑥ | ⑦ | ⑧ | H | H |

|---|----|----|----|----|---|---|---|---|---|---|

| ① | -B | -B | -B | -B |   |   |   |   | L | L |

| ② | +B | +B | +B | +B |   |   |   |   | H | L |

| ③ | -B | -B | -B | -B |   |   |   |   | L | H |

| ④ | +B | +B | +B | +B |   |   |   |   | H | L |

| ⑤ | -B | -B | -B | -B |   |   |   |   | L | H |

| ⑥ | +B | +B | +B | +B |   |   |   |   | H | L |

| ⑦ | -B | -B | -B | -B |   |   |   |   | L | H |

| ⑧ | +B | +B | +B | +B |   |   |   |   | H | L |

【図10】

(奇数ラインパネル)

①フレーム (正極性Aのみ抽出)

|   | ①  | ②  | ③  | ④  | ⑤ | ⑥ | ⑦ | ⑧ | REV | SWP |

|---|----|----|----|----|---|---|---|---|-----|-----|

| ① | -A | -A | -A | -A |   |   |   |   | L   | H   |

| ② | +A | +A | +A | +A |   |   |   |   | H   | L   |

| ③ | -A | -A | -A | -A |   |   |   |   | L   | H   |

| ④ | +A | +A | +A | +A |   |   |   |   | H   | L   |

| ⑤ | -A | -A | -A | -A |   |   |   |   | L   | H   |

| ⑥ | +A | +A | +A | +A |   |   |   |   | H   | L   |

| ⑦ | -A | -A | -A | -A |   |   |   |   | L   | H   |

| ⑧ | +A | +A | +A | +A |   |   |   |   | H   | L   |

②フレーム (正極性Aのみ抽出)

|   | ①  | ②  | ③  | ④  | ⑤ | ⑥ | ⑦ | ⑧ | H | L |

|---|----|----|----|----|---|---|---|---|---|---|

| ① | +A | +A | +A | +A |   |   |   |   | H | L |

| ② | -A | -A | -A | -A |   |   |   |   | L | H |

| ③ | +A | +A | +A | +A |   |   |   |   | H | L |

| ④ | -A | -A | -A | -A |   |   |   |   | L | H |

| ⑤ | +A | +A | +A | +A |   |   |   |   | H | L |

| ⑥ | -A | -A | -A | -A |   |   |   |   | L | H |

| ⑦ | +A | +A | +A | +A |   |   |   |   | H | L |

【図7】

【図25】

【図8】

(偶数ラインパネル)

①フレーム (正極性Aのみ抽出)

|   | ①  | ②  | ③  | ④  | ⑤  | ⑥  | ⑦  | ⑧  | REV | SWP |

|---|----|----|----|----|----|----|----|----|-----|-----|

| ① | -A |    | -A |    | -A |    | -A |    | L   | H   |

| ② |    | +A |    | +A |    | +A |    | +A | H   | L   |

| ③ | -A |    | -A |    | -A |    | -A |    | L   | H   |

| ④ |    | +A |    | +A |    | +A |    | +A | H   | L   |

| ⑤ | -A |    | -A |    | -A |    | -A |    | L   | H   |

| ⑥ |    | +A |    | +A |    | +A |    | +A | H   | L   |

| ⑦ | -A |    | -A |    | -A |    | -A |    | L   | H   |

| ⑧ |    | +A |    | +A |    | +A |    | +A | H   | L   |

(奇数ラインパネル)

①フレーム (負極性Bのみ抽出)

|   | ①  | ② | ③  | ④ | ⑤  | ⑥ | ⑦  | ⑧ | REV | SWP |

|---|----|---|----|---|----|---|----|---|-----|-----|

| ① | -B |   | -B |   | -B |   | -B |   | L   | H   |

| ② | +B |   | +B |   | +B |   | +B |   | H   | L   |

| ③ | -B |   | -B |   | -B |   | -B |   | L   | H   |

| ④ | +B |   | +B |   | +B |   | +B |   | H   | L   |

| ⑤ | -B |   | -B |   | -B |   | -B |   | L   | H   |

| ⑥ | +B |   | +B |   | +B |   | +B |   | H   | L   |

| ⑦ | -B |   | -B |   | -B |   | -B |   | L   | H   |

②フレーム (正極性Aのみ抽出)

|   | ①  | ② | ③  | ④ | ⑤  | ⑥ | ⑦  | ⑧ |

|---|----|---|----|---|----|---|----|---|

| ① | -A |   | -A |   | -A |   | -A |   |

| ② | +A |   | +A |   | +A |   | +A |   |

| ③ | -A |   | -A |   | -A |   | -A |   |

| ④ | +A |   | +A |   | +A |   | +A |   |

| ⑤ | -A |   | -A |   | -A |   | -A |   |

| ⑥ | +A |   | +A |   | +A |   | +A |   |

| ⑦ | -A |   | -A |   | -A |   | -A |   |

| ⑧ | +A |   | +A |   | +A |   | +A |   |

②フレーム (負極性Bのみ抽出)

|   | ①  | ② | ③  | ④ | ⑤  | ⑥ | ⑦  | ⑧ |

|---|----|---|----|---|----|---|----|---|

| ① | +B |   | +B |   | +B |   | +B |   |

| ② | -B |   | -B |   | -B |   | -B |   |

| ③ | +B |   | +B |   | +B |   | +B |   |

| ④ | -B |   | -B |   | -B |   | -B |   |

| ⑤ | +B |   | +B |   | +B |   | +B |   |

| ⑥ | -B |   | -B |   | -B |   | -B |   |

| ⑦ | +B |   | +B |   | +B |   | +B |   |

【図13】

【図14】

【図15】

【図21】

【図16】

【図22】

【図17】

【図18】

【図19】

【図23】

【図20】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図34】

【図33】

【図35】

【図42】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

---

フロントページの続き

(58)調査した分野(Int.Cl.?, D B名)

G09G 3/00 – 3/38

G02F 1/133

|                |                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置的驱动装置和驱动方法                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 公开(公告)号        | <a href="#">JP3506235B2</a>                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2004-03-15 |

| 申请号            | JP2000248964                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2000-08-18 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人         | 渡邊卓哉                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 发明人            | 渡邊 卓哉                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G09G3/3614 G09G3/3685 G09G2310/027 G09G2320/0233                                                                                                                                                                                                                                                                                                                                                   |         |            |

| FI分类号          | G09G3/36 G02F1/133.525 G09G3/20.612.U G09G3/20.623.B G09G3/20.642.A                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 2H093/NA07 2H093/NA34 2H093/NA36 2H093/NC09 2H093/NC11 2H093/NC34 2H093/ND09 2H193 /ZA04 2H193/ZB43 2H193/ZC20 2H193/ZD32 5C006/AA22 5C006/AB03 5C006/AC02 5C006/AC26 5C006/AF46 5C006/BB16 5C006/BC03 5C006/BC06 5C006/BC13 5C006/BC16 5C006/BF25 5C006 /FA20 5C006/FA25 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD05 5C080/EE28 5C080/FF09 5C080/JJ01 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/KK02 |         |            |

| 其他公开文献         | JP2002062852A                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                          |         |            |

#### 摘要(译)

要解决的问题：提供一种用于驱动液晶显示装置的装置和方法，该装置和方法使得显示不均匀性不是通过使帧之间的偏移电压无效而是通过用偏移电压抵消存在于像素中的偏移电压来实现的。像素的周边像素。解决方案：这是液晶显示装置的驱动装置，其在输出电路4408中具有第一和第二放大器电路，并且在同相输入信号和反相信号之间切换，并且还在放大器的输出之间切换。电路并将它们输出到以矩阵形式排列的像素，并且驱动装置设置有转换控制电路2515，用于在上述放大器电路的输出之间进行切换，使得偏移电压施加到某个像素和要施加到像素的周边像素的偏移电压具有彼此相反的极性。

| 入力信号  |       | 出力端子       |            |

|-------|-------|------------|------------|

| S W P | R E V | 奇数番目の出力端子  | 偶数番目の出力端子  |

| ローレベル | ローレベル | 正極性（偏差 A）  | 負極性（偏差 B）  |

| ローレベル | ハイレベル | 負極性（偏差 B）  | 正極性（偏差 A）  |

| ハイレベル | ローレベル | 正極性（偏差 -A） | 負極性（偏差 -B） |

| ハイレベル | ハイレベル | 負極性（偏差 -B） | 正極性（偏差 -A） |