(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-233743

(P2004-233743A)

(43) 公開日 平成16年8月19日(2004.8.19)

(51) Int.Cl.<sup>7</sup>

**G09G 3/36**

**G02F 1/133**

**G09G 3/20**

**H04M 1/00**

**H04M 1/73**

F 1

G09G 3/36

G02F 1/133 505

G09G 3/20 611A

G09G 3/20 612F

G09G 3/20 612J

テーマコード(参考)

2H093

5C006

5C080

5KO27

審査請求 未請求 請求項の数 10 O L (全 28 頁) 最終頁に続く

(21) 出願番号

(22) 出願日特願2003-23424 (P2003-23424)

平成15年1月31日 (2003.1.31)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(71) 出願人 000233088

日立デバイスエンジニアリング株式会社

千葉県茂原市早野3681番地

(74) 代理人 100085811

弁理士 大日方 富雄

(72) 発明者 内田 孝俊

千葉県茂原市早野3681番地 日立デバイスエンジニアリング株式会社内

(72) 発明者 坂巻 五郎

東京都小平市上水本町五丁目20番1号

株式会社日立製作所半導体グループ内

最終頁に続く

(54) 【発明の名称】表示駆動制御装置および表示装置を備えた電子機器

## (57) 【要約】

【課題】カラー液晶パネルとそれを駆動する液晶表示駆動制御装置とマイクロプロセッサを備えたシステムにおけるマイクロプロセッサの負担を軽減するとともに消費電力を低減する。

【解決手段】液晶パネルに表示される画像データを記憶するメモリ(206)を内蔵し該メモリから順次画像データを読み出してカラー液晶パネルの各画素の3原色の画像信号をそれぞれ生成し外部出力端子から出力する液晶表示駆動制御装置に、内蔵メモリから読み出された2つの画像データを演算処理して透かし表示用のデータを生成する透過演算回路(211)を設け、該透過演算回路により生成された表示データをドライバ回路(218)へ供給して該ドライバ回路により液晶パネルの駆動信号を生成し出力するようにした。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

表示画像データを記憶する表示メモリを備え、前記表示メモリから順次表示画像データを読み出してカラー表示装置の駆動信号を生成し出力する表示駆動制御装置であって、前記表示装置の第1の表示領域と前記表示装置の第2の表示領域の共通の信号線を駆動する信号を生成し出力する駆動回路と、前記第1の表示領域の特性に応じた階調電圧情報を前記第2の表示領域の特性に応じた階調電圧情報を設定可能な設定手段と、該設定手段の設定情報に応じて前記駆動回路へ供給される階調電圧を生成する一つの階調電圧生成回路とを備えてなることを特徴とする表示駆動制御装置。

**【請求項 2】**

前記第1の表示領域の選択線をスキャン駆動した後、前記第2の表示領域の選択線をスキャン駆動するように構成され、

前記階調電圧生成回路は、前記第1の表示領域の駆動の際には前記設定手段の対応する第1設定情報に応じた階調電圧を生成し、前記第2の表示領域の駆動の際には前記設定手段の対応する第2設定情報に応じた階調電圧を生成するようにされ、

前記第1の表示領域の駆動から前記第2の表示領域の駆動へ移行する際に所定の間合い時間が設けられ、この間合い時間に第1設定情報に応じた階調電圧の生成から第2設定情報に応じた階調電圧の生成への切替えが行なわれるように構成されていることを特徴とする請求項1に記載の表示駆動制御装置。

**【請求項 3】**

前記設定手段は、設定情報が変更可能なレジスタであることを特徴とする請求項1または2に記載の表示駆動制御装置。

**【請求項 4】**

表示画像データを記憶する表示メモリを備え、前記表示メモリから順次表示画像データを読み出してカラー表示装置の駆動信号を生成し出力する表示駆動制御装置であって、外部から入力される画像データを所定の比率で間引くことにより圧縮された画像データを生成するリサイズ回路を備えてなることを特徴とする表示駆動制御装置。

**【請求項 5】**

前記比率を所定の範囲で任意に設定可能な設定手段を有することを特徴とする請求項4に記載の表示駆動制御装置。

**【請求項 6】**

前記画像データの間引きビットの位置を設定可能な設定手段を有することを特徴とする請求項5に記載の表示駆動制御装置。

**【請求項 7】**

前記比率に従って画像データの間引きを行なう際に間引きのための計数に関与させない画素数を設定可能な設定手段を有することを特徴とする請求項4, 5または6に記載の表示駆動制御装置。

**【請求項 8】**

前記圧縮された画像データを格納する前記表示メモリの格納位置を設定可能な設定手段を有することを特徴とする請求項4, 5, 6または7に記載の表示駆動制御装置。

**【請求項 9】**

表示画像データを記憶する表示メモリを備え、前記表示メモリから順次表示画像データを読み出してカラー表示装置の駆動信号を生成し出力する表示駆動制御装置であって、外部から入力される画像データを所定の比率で間引くことにより圧縮された画像データを生成するリサイズ回路と、

前記表示メモリの後段に設けられ、該表示メモリから読み出された第1画像データと第2画像データに対してビットシフト処理を行なってから加算することにより2つの画像の合成表示データを得る透過演算回路と、を備え

前記表示メモリは表示装置の一画面分の表示データよりも大きなデータを格納可能な記憶容量を有するように構成され、

10

20

30

40

50

前記表示メモリの一画面分の表示データが格納された記憶領域以外の記憶領域に前記リサイズ回路により圧縮されたデータが格納され、

前記透過演算回路によって前記一画面分の表示データと前記圧縮データとを合成した表示データを生成し、該合成表示データに基づいて前記駆動信号を生成して出力するように構成されてなることを特徴とする表示駆動制御装置。

#### 【請求項 10】

請求項 1 ~ 9 のいずれかに記載の表示駆動制御装置と、該表示駆動制御装置によって駆動される表示装置と、前記表示メモリに書き込まれる表示データの生成およびその書き込み位置情報に関する設定を行なうシステム制御装置と、を備え、

前記システム制御装置は、前記リサイズ回路により圧縮した画像データを前記表示メモリに格納させる場合にも、圧縮しない画像データを格納させる場合にも、同一の画像データ群を転送することを特徴とする表示装置を備えた電子機器。

10

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は、表示装置を駆動制御する表示駆動制御装置さらには半導体集積回路化された表示駆動制御装置に適用して有効な技術に関し、例えば携帯電話器等の携帯用電子機器に用いられるカラー液晶パネルを駆動する液晶表示駆動制御装置およびそれを用いた携帯電話器などの電子機器に利用して有効な技術に関する。

##### 【0002】

20

##### 【従来の技術】

近年、携帯電話器や PDA (パーソナル・デジタル・アシスタンツ) などの携帯用電子機器の表示装置としては、一般に複数の表示画素がマトリックス状に 2 次元配列されたドットマトリックス型液晶パネルが用いられており、機器内部にはこの液晶パネルの表示制御を行なう半導体集積回路化された液晶表示制御装置 (液晶コントローラ) や該制御装置の制御下で液晶パネルを駆動する液晶ドライバもしくは液晶コントローラと液晶ドライバを内蔵した液晶表示駆動制御装置 (液晶コントローラドライバ) が搭載されている。

##### 【0003】

従来、携帯用電子機器に用いられる液晶パネルは、モノクロ静止画表示のものが多かった。しかしながら、近年、携帯用電子機器の高機能化に伴い、表示部に表示される内容の多様化が進んでおり、カラー表示や動画表示を行なうものが主流になって来ている。

30

##### 【0004】

ところで、カラー液晶パネルを有する機器においては、カラー表示の利点を生かして背景画像の一部に文字や記号などの情報画像を透かしたような状態で表示させたり、メモリに記憶されている画像データから該画像を縮小した画像のデータを生成するリサイズ機能など、元になる画像データを処理して多種多様な表示が行なわれている。従来、このような処理は電子機器に搭載されているマイクロプロセッサのソフトウェア処理により行なうのが一般的であった。

##### 【0005】

40

##### 【発明が解決しようとする課題】

液晶パネルのカラー化や表示画面の大型化に伴う画像データの増加、動画表示の導入に伴ってマイクロプロセッサに要求される処理内容がますます多くなる。そのため、透かし表示のためのデータ処理をマイクロプロセッサのソフトウェア処理により行なう場合には、電子機器に搭載されるマイクロプロセッサとして高機能かつ高速処理可能なものが要求され、システムのコストアップを招く要因となるとともに、処理を開始してから実際に透かし画像が表示されるまでの時間が長くなるという課題がある。

##### 【0006】

しかも、マイクロプロセッサのソフトウェア処理により透かし表示を行なう場合、第 1 の画像の透過率を  $\alpha$  とすると、第 1 の画像データに対しては  $\alpha$  を掛ける乗算を、また第 2 の画像データに対しては  $(1 - \alpha)$  を掛ける乗算を行なってさらにそれらを加算する処理 (

50

以下、ブレンディングと称する)を行なう必要があり、処理内容が複雑である。

【0007】

また、ソフトウェア処理による透かし表示では、外部メモリに記憶されている元になる画像データを読み出してデータを処理して液晶コントローラドライバLSIに送ることになるため、透かし表示と透かし無し表示を繰り返し行なうには、表示を切り替える度にマイクロプロセッサがいちいち外部メモリから画像データを読み出して液晶コントローラドライバLSIに表示データを送る必要があり、消費電力と処理時間の増加を免れることができないという課題がある。

【0008】

また、携帯用電子機器に搭載される液晶コントローラドライバLSIには、液晶パネルに表示する画像データを格納するメモリを内蔵したものが多く使用されているが、液晶パネルのカラー化や表示画面の大型化に伴って内蔵メモリの大容量化が必要になる。しかしながら、内蔵メモリの大容量化はチップサイズの増大ひいてはチップコストの増加を招くため、少ない記憶容量で所望の表示を行なえるようにするため効率の良いメモリ管理手法が要求される。

【0009】

さらに、近年の携帯電話器には、本体の内側と外側の両方にそれぞれ液晶パネルを有するものが出現しているが、このように2つの液晶パネルを有する電子機器では、それぞれの液晶パネルに対応して液晶コントローラドライバLSIを設けたのではコストが非常に高くなるため一つの液晶コントローラドライバLSIで2つの液晶パネルを駆動することができる技術が要求される。しかしながら、2つの液晶パネルを駆動可能な液晶コントローラドライバLSIを実現しようとすると、メモリに必要とされる記憶容量が多くなったりいずれか一方のパネルの表示が不要な場合における消費電力の抑制など解決すべき課題が多くなる。

【0010】

この発明の目的は、カラー液晶パネルとそれを駆動制御する液晶表示駆動制御装置とマイクロプロセッサを備えたシステムにおけるマイクロプロセッサの負担を軽減することができる表示駆動制御装置を提供することにある。

この発明の他の目的は、カラー液晶パネルとそれを駆動制御する液晶表示駆動制御装置とマイクロプロセッサを備えたシステムにおける消費電力を低減することができる表示駆動制御装置を提供することにある。

【0011】

この発明のさらに他の目的は、カラー液晶パネルとそれを駆動制御する液晶表示駆動制御装置を備えたシステムにおいて、内蔵メモリを効率良く管理してチップサイズひいてはコストを低減することができる表示駆動制御装置を提供することにある。

この発明のさらに他の目的は、2以上の液晶パネルを備えたシステムにおいて、1つの表示駆動制御装置により2以上の液晶パネルを制御しそれぞれのパネルに応じて最適な駆動を実行することができる表示駆動制御装置を提供することにある。

【0012】

この発明の前記ならびにそのほかの目的と新規な特徴については、本明細書の記述および添附図面から明らかになるであろう。

【0013】

【課題を解決するための手段】

本願において開示される発明のうち代表的なものの概要を説明すれば、下記のとおりである。

すなわち、液晶パネルに表示される画像データを記憶するメモリを内蔵し該メモリから順次画像データを読み出してカラー液晶パネルの各画素の3原色の画像信号をそれぞれ生成し外部出力端子から出力する液晶表示駆動制御装置に、内蔵メモリから読み出された2つの画像データを処理して透かし表示用のデータを生成可能な画像データ処理回路を設け、該画像データ処理回路により生成された表示データをドライバ回路へ供給して該ドライバ

10

20

30

40

50

回路により液晶パネルの駆動信号を生成し出力させるようにしたものである。

【0014】

上記した手段によれば、マイクロプロセッサのソフトウェア処理を行なわなくても透かし表示を実現することができる。また、内蔵メモリの後段に透かし表示用のデータを生成可能な画像データ処理回路が設けられているため、透かし表示と透かし無し表示を繰り返し行ないたいような場合にも、表示を切り替える度にマイクロプロセッサがいちいち液晶コントローラドライバLSIに表示データを送る必要がなくなり、システム全体としての消費電力を低減することができる。

【0015】

また、望ましくは、上記画像データ処理回路は、画像データをビットシフトする1組のビットシフタと、該ビットシフタによりそれぞれビットシフトさせた第1の画像データと第2の画像データとを加算する加算器とから構成する。かかる手段によれば、ビットシフタという比較的簡単な回路によって透かし表示に必要な透過率50%や25%，12.5%....のような画像データを得ることができ、ビットシフタと加算器とから画像データ処理回路を構成することができるため、複雑な演算回路が不要であり、表示駆動制御装置のコストアップを回避しつつマイクロプロセッサに負担をかけることなく透かし表示を実現することができる。

【0016】

さらに、望ましくは、上記内蔵メモリは液晶パネルの1画面分の画像データ量よりも大きな記憶容量を有するように構成し、1画面分の画像データを記憶した内蔵メモリの残りの領域に該1画面分の画像データと重ね合わされる他の画像データを記憶させるようにする。これにより、少ない記憶容量の内蔵メモリに効率良く透かし表示に必要な画像データを保持させることができる。

【0017】

また、2以上の液晶パネル用の駆動信号を生成して出力する液晶表示駆動制御装置において、いずれか一方の液晶パネルを表示駆動し他方のパネルは非表示とするような制御を行なうとともに、内蔵メモリの記憶容量を各パネルに対応した画像データを合計した大きさとし、非表示のパネルに対応した記憶領域を利用して透かし表示のために重ね合わされる他の画像データを記憶させるようにする。これにより、比較的小さな記憶容量の内蔵メモリに効率良く透かし表示に必要な画像データを保持させることができる。

【0018】

さらに、外部から供給された画像データを処理して該画像を縮小した画像のデータを生成するリサイズ機能を設け、該リサイズ機能により生成された画像データを1画面分の画像データを記憶している内蔵メモリの残りの領域またはいずれか非表示のパネルに対応した記憶領域に格納せしめるようにする。これにより、比較的小さな記憶容量の内蔵メモリに表示画面もしくは背景画像の一部（ウィンド領域）に他の画像を縮小表示させる場合に必要な画像データを保持させることができる。ここで、望ましくは、リサイズ機能を有効にするか無効にするか指定することができるレジスタを設ける。これにより、マイクロプロセッサ側にリサイズ機能を持つシステムまたはマイクロプロセッサ側にリサイズ機能を持たないシステムのいずれにも適用することができる液晶表示駆動制御装置が得られる。

【0019】

【発明の実施の形態】

以下、この発明の好適な実施の形態を図面に基づいて説明する。

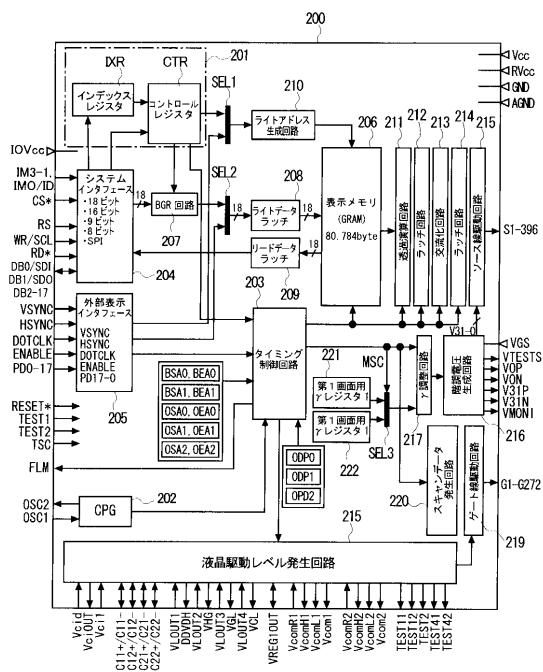

図1は、本発明に係る液晶表示駆動制御装置（液晶コントローラドライバ）の一実施例を示すブロック図である。特に制限されるものでないが、実施例の液晶コントローラドライバは、一個の半導体チップ上に半導体集積回路として形成される。

【0020】

この実施例の液晶コントローラドライバ200は、外部のマイクロプロセッサもしくはマイクロコンピュータ（以下、マイコンと略す）等からの指令に基づいてチップ内部全体を制御する制御部201、外部からの発振信号もしくは外部端子に接続された振動子からの

10

20

30

40

50

発振信号に基づいてチップ内部の基準クロックパルスを生成するパルスジェネレータ 202、このクロックパルスに基づいてチップ内部の種々の回路の動作タイミングを与えるタイミング信号を発生するタイミング制御回路 203、図示しないシステムバスを介してマイコン等との間で主としてインストラクションや静止画像データなどのデータの送受信を行なうシステム・インターフェース 204、図示しない表示データバスを介して主としてアプリケーションプロセッサなどからの動画データや水平・垂直同期信号 HSYNC, VSYNC を受ける外部表示インターフェース 205 が設けられている。前記アプリケーションプロセッサからの動画データは、ドットクロック信号 DOTCLK に同期して供給される。

#### 【0021】

10

また、この実施例の液晶コントローラドライバ 200 には、表示データをビットマップ方式で記憶する SRAM (Static Random Access Memory) などの読み出し書き込み可能な揮発性メモリからなる表示メモリ 206、マイコンからの書き込みデータのビットの並び替えなどのビット処理を行なうビット変換回路 207、ビット変換回路 207 で変換された画像データまたは外部表示インターフェース 205 を介して入力された画像データを取り込んで保持するライトデータラッチ回路 208、表示メモリ 206 から読み出された画像データを保持するリードデータラッチ回路 209、上記表示メモリ 206 に対する書き込みアドレスを生成するアドレスカウンタなどからなるライトアドレス生成回路 210、液晶パネルへの表示のために表示メモリ 206 から読み出された画像データに基づいて透かし表示のための演算を行なう透過演算手段 211、該透過演算手段 211 より出力された表示データを取り込んで保持するラッチ回路 212 が設けられている。透過演算手段 211 は透過演算をせずに表示データをそのまま通過させることも可能である。

20

#### 【0022】

20

特に制限されるものでないが、この実施例では表示メモリ 206 から画像データを読み出すためのリードアドレスを生成するカウンタはタイミング制御回路 203 内に設けられている。表示メモリ 206 は、複数のメモリセルを含むメモリアレイと、ライトアドレス生成回路 210 やタイミング制御回路 203 から供給されるアドレスをデコードしてメモリアレイ内のワード線やビット線を選択する信号を生成するアドレスデコーダと、メモリセルから読み出された信号を増幅したり、書き込みデータに応じてメモリアレイ内のビット線に所定の電圧を印加したりするセンスアンプを有する。

30

#### 【0023】

30

さらに、この実施例の液晶コントローラドライバ 200 には、表示データラッチ回路 212 にラッチされた表示データから液晶の劣化を防止する交流駆動のためのデータに変換する交流化回路 213、該回路で変換されたデータを保持するラッチ回路 214、液晶パネルの駆動に必要な複数レベルの電圧を発生する液晶駆動レベル発生回路 215、該液晶駆動レベル発生回路 215 で生成された電圧に基づいてカラー表示や階調表示に適した波形信号を生成するのに必要な階調電圧を生成する階調電圧生成回路 216、液晶パネルの特性を補正するため図 17 に示すような特性の階調電圧を設定する調整回路 217、上記階調電圧生成回路 216 から供給される階調電圧の中からラッチ回路 214 にラッチされている表示データに応じた電圧を選択して液晶パネルの信号線としてのソース線に印加される電圧 (ソース線駆動信号) S1 ~ S396 を出力するソース線駆動回路 215、液晶パネルの選択線としてのゲート線 (コモン線とも呼ばれる) に印加される電圧 (ゲート線駆動信号) G1 ~ G272 を出力するゲート線駆動回路 219、液晶パネルのゲート線を 1 本ずつ順番に選択レベルに駆動するためのスキャンデータを生成するシフトレジスタなどからなるスキャンデータ発生回路 220 等が設けられている。

40

なお、図 1 において、SEL1, SEL2, SEL3 はデータセレクタで、それぞれタイミング制御回路 203 から出力される切替え信号によって制御され、複数の入力信号のいずれかを選択的に通過させる。

#### 【0024】

50

制御部 201 には、液晶コントローラドライバ 200 の動作モードなどチップ全体の動作状態を制御するためのコントロールレジスタ CTR や、該コントロールレジスタ CTR や前記表示メモリ 206 の参照のためのインデックス情報を記憶するインデックス IXR などのレジスタが設けられており、外部のマイコン等がインデックスレジスタ IXR に書き込みを行なうことで実行するインストラクションを指定すると、制御部 201 が指定されたインストラクションに対応した制御信号を生成し出力する。また、制御部 201 が実行するインストラクションは、外部から供給されるレジスタ選択信号 RS と書き込み制御信号 WR と 16 ビットのデータバス信号 DB0 ~ DB15 によって指定されるように構成されている。

## 【0025】

10

このように構成された制御部 201 による制御によって、液晶コントローラドライバ 200 は、マイコン等からの指令およびデータに基づいて国外の液晶パネルに表示を行なう際に、画像データを表示メモリ 206 に順次書き込んで行く描画処理を行なうと共に、表示メモリ 206 から周期的に表示データを読み出す読み出し処理を行なって液晶パネルのソース線に印加する信号とゲート線に印加する信号を生成して出力する。

## 【0026】

システム・インターフェース 204 は、マイコン等のシステム制御装置との間で表示メモリ 206 への描画の際などに必要とされるレジスタへの設定データや表示データ等の信号の送受信を行なう。この実施例では、IM3-1 および IM0 / ID 端子の状態に応じて 80 系インターフェースとして 18 ビット、16 ビット、9 ビット、8 ビットのパラレル入出力またはシリアル入出力のいずれかが選択可能に構成されている。

20

## 【0027】

また、マイコンとシステム・インターフェース 204との間には、上記レジスタ選択信号 RS と書き込み制御信号 WR の他、データ送信先のチップを選択するチップセレクト信号 CS\*、読み出しを許可するリードイネーブル信号 RD\* などが送信される制御信号線、レジスタ設定データや表示データなど 18 ビットのデータ信号 DB0 ~ DB17 が送受信されるデータ信号線とが設けられる。ここで、符号に \* が付されている信号は、ロウレベルが有効レベルとされる信号であることを意味している。

## 【0028】

なお、データ信号線 DB0 ~ DB17 のうち DB0 と DB1 はシリアルデータ通信線を兼用するように構成されている。書き込み制御信号 WR の入力端子は、シリアル・インターフェースが指定されたときに同期用のシリアルクロック SCL が入力される端子と兼用されており、シリアルデータはシリアルクロック信号 SCL と同期して入出力される。シリアル・インターフェースを選択することにより、データ信号線 DB2 ~ DB18 が不要となり、基板上に設けられるシステムバスの幅を小さくすることができる。

30

## 【0029】

この実施例の液晶コントローラドライバ 200 に入力される信号としては、上記以外に例えばチップ内部を初期状態にするリセット信号 RESET\* や内部回路の試験のためのテスト信号 TEST1, TEST2、テスト用クロック信号 TSC などがある。また、本実施例の液晶コントローラドライバ 200 のチップには、これらの信号の入出力端子の他に、液晶駆動レベル発生回路 215 や階調電圧生成回路 216 で生成された電圧を出力する端子、液晶駆動レベル発生回路 215 の制御信号を入力する端子などが設けられているが、これらは本発明に直接関係しないので説明は省略する。

40

## 【0030】

本実施例の液晶コントローラドライバ 200 は、2 つの液晶パネルを有するシステムにおいて 2 つの液晶パネルを 1 つの液晶コントローラドライバチップで駆動できるように構成されており、例えば駆動対象の 2 つの液晶パネルの特性が異なる場合にそれぞれの液晶パネルの特性を補正するような階調電圧を発生できるように上記調整回路 217 が構成されている。これとともに、駆動対象の 2 つの液晶パネルの特性を設定するためのレジスタ 221, 222 が設けられ、それぞれの液晶パネルの駆動時にセレクタ SEL3 によ

50

って所望の特性データが設定されているレジスタ221または222が選択され、そのレジスタに設定されている特性データが調整回路217に供給され、調整回路217からの制御信号により階調電圧生成回路216により生成される階調電圧を動的に変化させることができるように構成されている。特性データを保持するレジスタ221, 222の代わりに不揮発性メモリ素子からなる設定手段を用いるようにしてもよい。

【0031】

セレクタSEL3は、タイミング制御回路203から出力されるメイン画面とサブ画面の切替え信号MSCによって制御され、タイミング制御回路203はメイン画面駆動時とサブ画面駆動時に切替え信号MSCを変化させる。レジスタ221, 222は、外部のマイコン等が前記システム・インターフェース204を介して設定することができるよう 10 されている。このレジスタ221, 222も制御部201のコントロールレジスタCTRに設けることができる。

【0032】

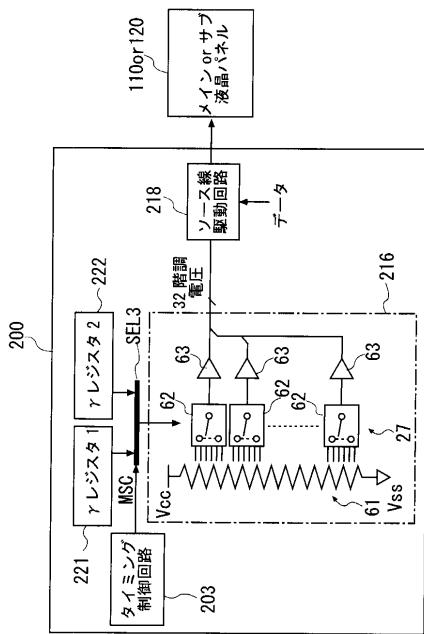

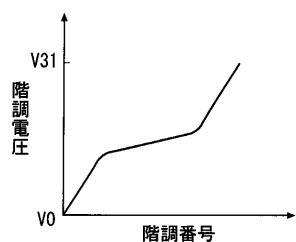

特に制限されるものでないが、この実施例の階調電圧生成回路216は32段階の階調電圧V31～V0を生成できるように構成されている。発生する電圧を切替え可能な階調電圧生成回路216は、例えば図8のように電源電圧端子Vcc-Vss間に接続されたラダー抵抗61と、該ラダー抵抗61で抵抗分割された任意の電圧を選択するスイッチ素子を有する複数の選択回路62と、各選択回路62により選択された電圧をインピーダンス変換して出力する複数のバッファアンプ63とからなり、2つのレジスタ221または222の設定値で各選択回路62内のスイッチ素子を切り替えることにより所望のレベルの電圧を出力させる構成とすることで実現することができる。また、図8の階調電圧生成回路216においては、使用する液晶パネルの特性に応じてレジスタ221と222の設定値を変更することにより最適な表示画質が得られる。レジスタ221と222のビット数が充分でない場合には、セレクタSEL3の後段にデコーダを設けるようにしてもよい。

【0033】

図1に示されている調整回路217は図8の選択回路62に相当する。なお、階調電圧生成回路216で生成された32段階の階調電圧V31～V0を用いて、ソース線駆動回路218においていすれか隣接する2つの電圧（例えばV21とV22）を1水平期間の前半と後半でそれぞれ選択することで実効的に中間の電圧（V21+V22）/2を発生させることによって、実質的に64段階の階調表示が可能である。

【0034】

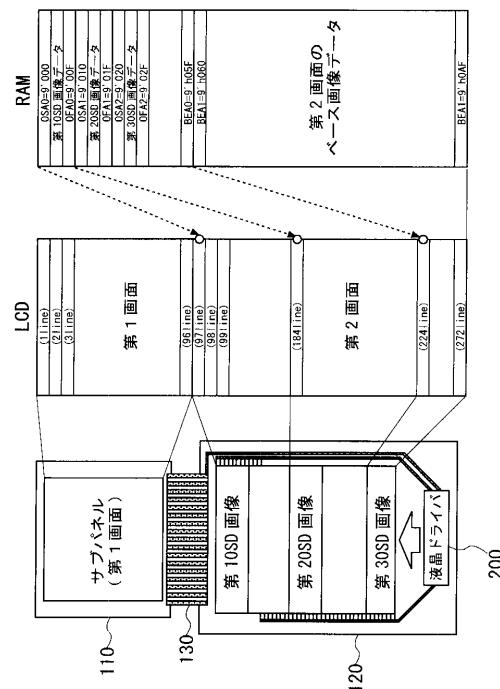

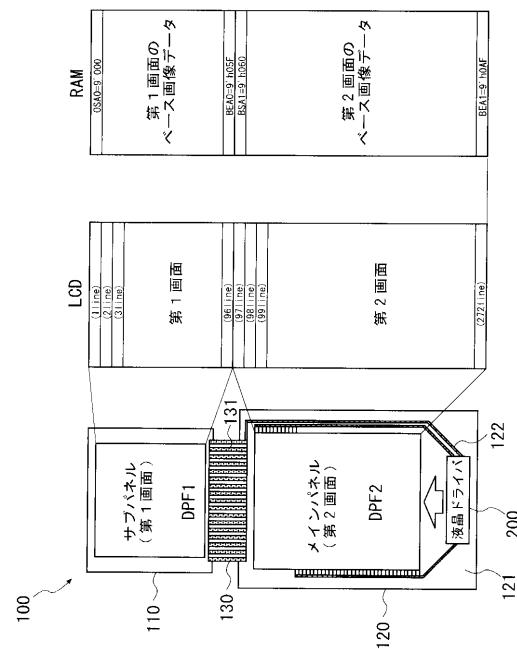

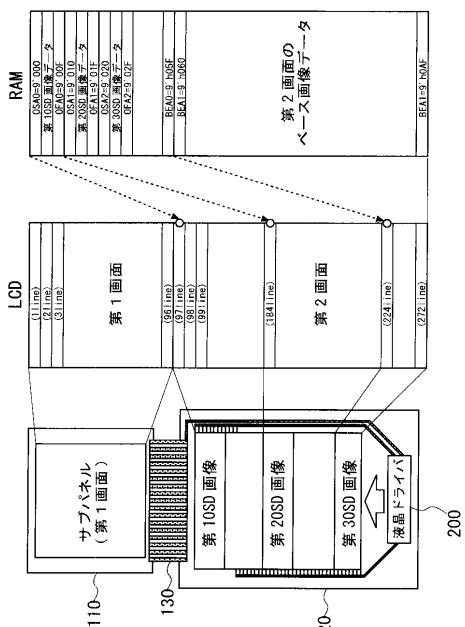

図2には、本実施例の液晶コントローラドライバ200により駆動される液晶表示デバイスの構成例が示されている。図2に示されている液晶表示デバイス100は、2つの液晶パネル110と120とがFPCと呼ばれるフレキシブルプリント配線ケーブル130により結合され、一方の液晶パネル120のガラス基板121上に実施例の液晶コントローラドライバ200が実装され、第1の液晶パネル110のソース線と第2の液晶パネル120のソース線はFPC130上の配線131によりそれぞれ対応するもの同士が接続されている。2つの液晶パネル110と120がFPC130により結合されているため、FPC130を湾曲させることで例えばそれぞれの液晶パネルの背面同士が向き合い表示面が各々180°異なる方向を向くような状態で配置させる実装が可能になる。

【0035】

なお、液晶パネル110および120がカラーパネルの場合、RGB（赤、緑、青）の3ドットで構成された画素がマトリックス状に配列され、例えば各ライン（行）毎にRGBの画素が順に繰返し配置され、列方向には同一色の画素が並ぶように配置されたものが使用される。液晶パネルの各画素は、TFT（薄膜トランジスタ）からなるスイッチ素子と画素電極とから構成され、画素電極と液晶を挟んで対抗する共通電極との間に画像データに応じた電圧が印加される。そして、同一行の画素のスイッチ素子のゲート電極が連続するように形成されてゲート線を構成し、同一列の画素のスイッチ素子のソース端子は上記ゲート線と交差する方向に配設されたソース線に接続される。

## 【0036】

図2に示されている液晶表示デバイスは、例えば折畳み式の携帯電話器に適用された場合、一方は上蓋ケースの内側にあって蓋を開いた状態で待ち受け画面等を表示し、他方は上蓋ケースの外側にあって通常は時刻等を表示し着信があると着信表示をしたりするのに使用される。かかる携帯電話器においては、上蓋を開いた状態で見える内側の画面が重要であり、内側の液晶パネルはTFTなどを使用した高精細なカラー液晶パネルで構成されかつバックライトにより明るく表示されることが多い一方、蓋を閉じた状態で見える背面画面は補助的なものでありそのような画面を表示する外側の液晶パネルはモノクロ表示やバックライト無しの反射型のものが使用されることが多い。

## 【0037】

10

このように2つの液晶パネルの表示品質が異なる場合、各液晶パネルの特性も異なるものとなる。本実施例の液晶コントローラドライバ200は、上記のように特性の異なる2つの液晶パネルを駆動する場合に、一方の液晶パネルの駆動状態から他方の液晶パネルの駆動状態へ移る際に上記セレクタSEL3を切り替えて、調整回路217に供給されるレジスタ221, 222の設定値を変えることにより、階調電圧生成回路216がそれぞれのパネルの特性に応じて異なる32段階の階調電圧を発生してソース線駆動回路218へ与え、ソース線駆動回路218がそれらの階調電圧の中から表示データに応じた電圧を選択することで液晶駆動信号を生成して出力することができるよう構成されているため、各液晶パネルにおいて最適な表示画質を得ることが可能となる。

## 【0038】

20

さらに、本実施例の液晶コントローラドライバ200には、図1に示されているように、表示メモリ206内のデータ書き込み位置を指定するアドレス（始点および終点）を設定するレジスタBSA, BEA; OSA, OSEや画面上への表示位置を設定するレジスタODP等が設けられており、タイミング制御回路203かこれらのレジスタの設定値に基づいてタイミング制御信号を生成するよう構成されている。図1には示されていないが、これらのレジスタBSA, BEA; OSA, OSEやODPを有効にするか無効にするか設定可能なイネーブルレジスタ（図4参照）も設けられている。また、タイミング制御回路203はフレーム同期信号FLMも生成して出力する。

## 【0039】

30

なお、図1においては、図示の都合で、上記アドレス設定用レジスタBSA, BEA; OSA, OSEや表示位置レジスタODPがタイミング制御回路203の近傍に示されているが、実施例の液晶コントローラドライバでは、これらのレジスタはコントロールレジスタCTR内に設けられている。

## 【0040】

アドレス設定用レジスタが2組あるのは、背景となるベース画像データの格納位置を指定するアドレスおよびこれと重ね合わされて表示される画像（以下、OSD画像と称する）データの格納位置を指定するアドレスをそれぞれ任意に設定できるようにするためである。表示位置レジスタODPは1組である。これは、ベース画像の表示位置は液晶パネルの画面全体に固定されており、OSD画像の表示位置を可変にするためである。OSD画像を複数表示させることができるようにしたい場合には、アドレス設定レジスタOSA, OSEと表示位置レジスタODPをそれぞれ複数設けるようにすればよい。

## 【0041】

40

本実施例の液晶コントローラドライバ200においては、2つの液晶パネルを有するシステムにおいて2つの液晶パネルを1つの液晶コントローラドライバで駆動し、2つの液晶パネルのそれぞれにベース画像を表示できるようにするため、ベース画像のアドレス設定用レジスタが2組設けられている。すなわち、第1ベース画像の開始アドレスを設定する始点レジスタBSA0と終了アドレスを設定する終点レジスタBEA0および第2ベース画像の開始アドレスを設定する始点レジスタBSA1と終了アドレスを設定する終点レジスタBEA1である。

## 【0042】

また、本実施例の液晶コントローラドライバ200には、OSD画像を同時に3個表示可能にするため、OSD画像のアドレス設定用レジスタが3組設けられている。すなわち、第1OSD画像の開始アドレスを設定する始点レジスタOSA0と終了アドレスを設定する終点レジスタOEA0、第2OSD画像の開始アドレスを設定する始点レジスタOSA1と終了アドレスを設定する終点レジスタOEA1および第3OSD画像の開始アドレスを設定する始点レジスタOSA2と終了アドレスを設定する終点レジスタOEA2である。表示位置レジスタも3つのOSD画像に対応して3つ(ODP0, ODP1, ODP2)設けられている。

【0043】

本実施例の液晶コントローラドライバ200においては、図2に示すような2つの液晶パネルを有する表示デバイスの2つの表示画面DPF1とDPF2に表示可能な2つのベース画像データを記憶可能な容量を有するように表示メモリ206が構成されている。表示画面DPF1は前記液晶パネル110に対応し、表示画面DPF2は前記液晶パネル120に対応する。

【0044】

2つの画像を重ね合わせて液晶パネル120に透かし表示を行なう場合には、図3に示すように、2つの表示画面DPF1とDPF2のうち一方の画面(図では第1画面)に対応する画像データの記憶領域に、OSD画像データを記憶するように構成されている。なお、第1画面の記憶領域にOSD画像データを記憶した場合、液晶パネル110の表示画面DPF1には有効な表示(ベース画像の表示)がなされないような駆動制御が行なわれる。

【0045】

逆に、液晶パネル110の表示画面DPF1に透かし表示を行ない、液晶パネル120の表示画面DPF2には表示を行なわないような場合には、表示メモリ206の表示画面DPF1の画像データ記憶領域にベース画像データを記憶し、表示画面DPF2の画像データ記憶領域にOSD画像データを記憶するようにしてもよい。

【0046】

携帯電話器においては、蓋を開いた状態では内側の液晶パネルの表示が重要で外側の液晶パネルの表示は消しても良い一方、蓋を閉じた状態では外側の液晶パネルの表示が重要であり内側の液晶パネルの表示は消費電力低減のため消すようにしていることを考慮したものである。このような表示メモリ206の記憶管理を行なうことにより、少ない記憶容量を利用して多種多様な表示が可能になる。言い換えると、本実施例の適用により可能になる表示内容の多様性に比較して予め用意すべき表示メモリの記憶容量を小さくして液晶コントローラドライバ200のチップサイズの増加を抑制することができる。

【0047】

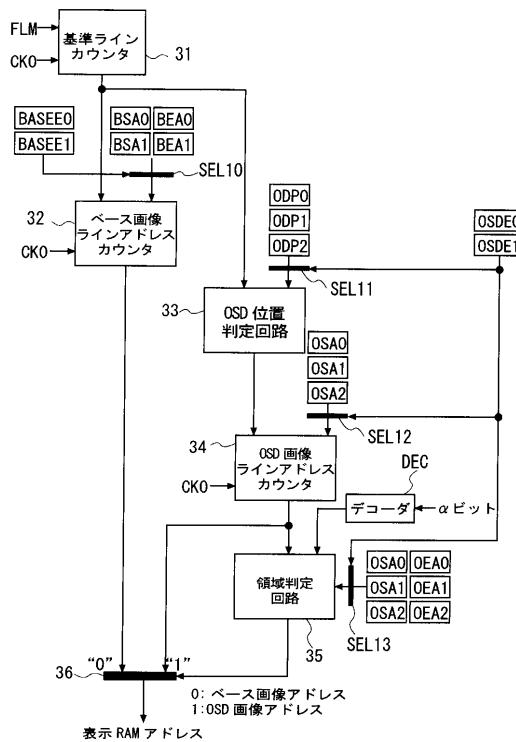

図4には、表示メモリ206から表示データを読み出すためのアドレスを生成するため上記タイミング制御回路203に設けられるリードアドレス生成部の構成例が示されている。

図4に示されているように、リードアドレス生成部は、液晶パネルのスキャンラインすなわち駆動電圧が印加されるゲート線を示す値を生成するための基準ラインカウンタ31と、表示メモリ206からベース画像データを読み出すためのアドレスを生成するベース画像ラインアドレスカウンタ32と、OSD画像の表示位置を判定するためのOSD位置判定回路33と、表示メモリ206からOSD画像データを読み出すためのアドレスを生成するOSD画像ラインアドレスカウンタ34と、OSD画像の表示領域であるか否かを判定するための領域判定回路35と、該領域判定回路35における判定結果に基づいてベース画像ラインアドレスカウンタ32の計数値またはOSD画像ラインアドレスカウンタ34の計数値のいずれかを選択して表示メモリのリードアドレスとして出力するセレクタ36とを備えている。

【0048】

基準ラインカウンタ31は、フレーム同期信号FLMに同期してリセットされ、1ライン

10

20

30

40

50

周期に相当する周期を有する基準クロックCK0に同期して更新される。ベース画像ラインアドレスカウンタ32は、コントロールレジスタCTR内の第1ベース画像の開始アドレスを設定する始点レジスタBSA0および終了アドレスを設定する終点レジスタBEA0の値並びに第2ベース画像の開始アドレスを設定する始点レジスタBSA1および終了アドレスを設定する終点レジスタBEA1の値と、基準ラインカウンタ31の値とを比較し、基準ラインカウンタ31の値が第1ベース画像の始点と終点との間にあるときおよび第2ベース画像の始点と終点との間にあるときに、表示ラインの切り替えに合わせてアドレスを更新する。

#### 【0049】

特に制限されるものでないが、図4のリードアドレス生成部には、上記アドレス設定用レジスタBSA0, BEA0; BSA1, BEA1を有効にするか無効にするか設定可能なイネーブルレジスタBASEE0, BASEE1およびレジスタBSA0, BEA0; BSA1, BEA1の値を通過させたり遮断したりするゲート兼セレクタSEL10が設けられている。

#### 【0050】

OSD位置判定回路33は、コントロールレジスタCTR内の表示位置レジスタODP0, ODP1, ODP2の設定値と基準ラインカウンタ31の値を比較し、表示ラインがOSD画像の表示開始位置に達したか否か判定し、達したときはコントロールレジスタCTR内のOSD画像の始点レジスタOSA0, OSA1, OSA2の値をOSD画像ラインアドレスカウンタ34にロードさせた後、表示ラインの切り替えに合わせてアドレスを更新する。

#### 【0051】

領域判定回路35は、コントロールレジスタCTR内のOSD画像の始点レジスタOSA0, OSA1, OSA2およびOSD画像の終点レジスタOEA0, OEA1, OEA2の値とOSD画像ラインアドレスカウンタ34の値とを比較して表示ラインがOSD画像の表示領域に入っているか否か判定する。これとともに、領域判定回路35は、表示メモリ206から読み出されたOSD画像データに含まれている透過率を表わすビットをデコードするデコーダDECからの出力に基づいてセレクタ36を切り替えて、ベース画像ラインアドレスカウンタ32の計数値またはOSD画像ラインアドレスカウンタ34の計数値のいずれかを表示メモリのリードアドレスとして出力させる。

#### 【0052】

特に制限されるものでないが、図4のリードアドレス生成部には、上記表示位置レジスタODP0, ODP1, ODP2とOSD画像の始点レジスタOSA0, OSA1, OSA2およびOSD画像の終点レジスタOEA0, OEA1, OEA2を有効にするか無効にするか設定可能なイネーブルレジスタOSDE0, OSDE1およびレジスタODP0, ODP1, ODP2とOSA0, OSA1, OSA2とOEA0, OEA1, OEA2の値をそれぞれ通過させたり遮断したりするゲート兼セレクタSEL11, SEL12, SEL13が設けられている。

#### 【0053】

図4のリードアドレス生成部においては、ビットが透かし表示を指示しているときは、液晶パネルの1ライン表示周期の前半にOSD画像ラインアドレスカウンタ34の計数値を出力し、後半にベース画像ラインアドレスカウンタ32の計数値を出力するようにセレクタ36の切り替えを行なわれる。また、ビットがベース画像の100%表示を指示しているときは、液晶パネルの1ライン表示周期の間ずっとベース画像ラインアドレスカウンタ32の計数値を出力し、ビットがOSD画像の100%表示を指示しているときは、液晶パネルの1ライン表示周期の間ずっとOSD画像ラインアドレスカウンタ34の計数値を出力するようにセレクタ36が制御される。

#### 【0054】

さらに、ビットがプリンキングを指示しているときは0.5秒あるいは1秒のような比較的長い時間間隔でベース画像ラインアドレスカウンタ32の計数値とOSD画像ライン

10

20

30

40

50

アドレスカウンタ34の計数値を交互に出力するようにセレクタ36が制御される。表1に、本実施例の液晶コントローラドライバにおける3ビットのビットと表示内容との関係を示す。

【0055】

【表1】

| $\alpha_2$ | $\alpha_1$ | $\alpha_0$ | 表示内容                      |

|------------|------------|------------|---------------------------|

| 0          | 0          | 0          | ベース画像データ 100%表示           |

| 0          | 0          | 1          | —                         |

| 0          | 1          | 0          | —                         |

| 0          | 1          | 1          | —                         |

| 1          | 0          | 0          | ベース画像データ、OSD画像データ 50%透過表示 |

| 1          | 0          | 1          | ベース画像データとOSD画像データ1のプリント   |

| 1          | 1          | 0          | OSD画像データ 100%表示           |

| 1          | 1          | 1          | ベース画像データとOSD画像データ2のプリント   |

10

【0056】

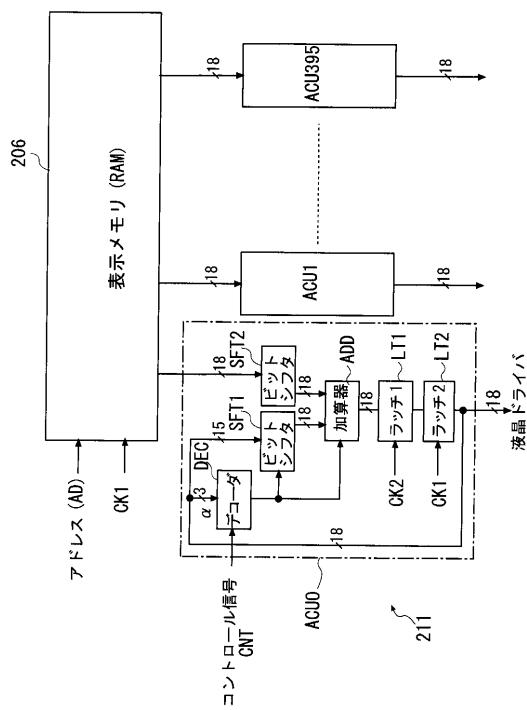

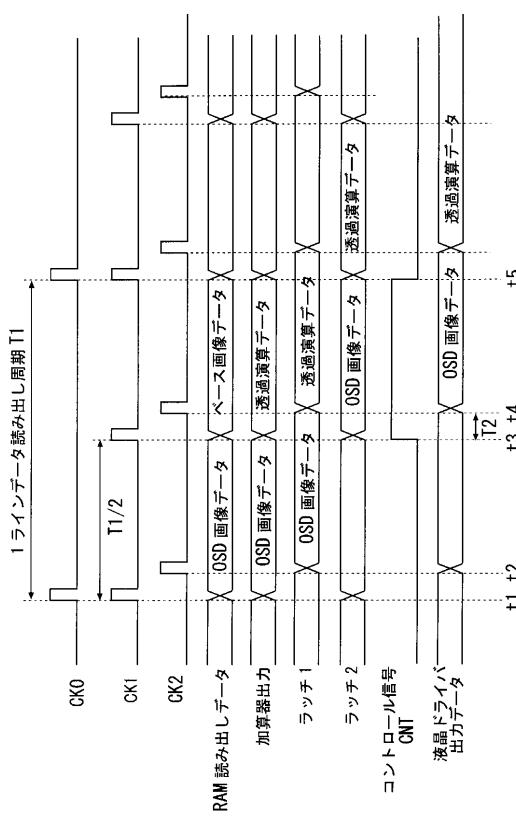

図5には上記透過演算回路211の構成例が、また図6にはその動作タイミングが示されている。

この実施例では表示メモリ206から液晶パネルの1ライン分すなわち396画素分の表示データが同時に読み出されるように構成されている。読み出された表示データは1画素当たりRGBそれぞれ6ビット計18ビットで構成されており、透過演算回路211には396個の画素の表示データに対応して396個の単位演算回路ACU0～ACU395が設けられている。図5には、代表として単位演算回路ACU0～ACU395のうちの一つACU0についてその具体的な構成例が示されている。図示しないが、他の単位演算回路ACU1～ACU395も同様な構成を有する。以下、単位演算回路ACU0について説明し、他の単位演算回路ACU1～ACU395については説明を省略する。

20

【0057】

単位演算回路ACU0は、2つのビットシフタSFT1, SFT2と、これらのビットシフタSFT1, SFT2でビットシフト処理された18ビットのデータを加算する加算器ADDと、加算器ADDの出力を一時的に保持する第1のラッチ回路LT1と、ラッチ回路LT1の出力を取り込む第2のラッチ回路LT2と、ラッチ回路LT2に取り込まれた表示データのうち透過率を示す3ビットのビットをデコードしてビットシフタSFT1, SFT2および加算器ADDに対する制御信号を生成するデコーダDECとから構成されている。ラッチ回路LT1はクロック信号CK2に同期して、またラッチ回路LT2はクロック信号CK2と同一の周期で位相の異なるクロック信号CK1に同期してそれぞれデータをラッチする。クロック信号CK1は前記基準クロックCK0を分周することにより生成される。

30

【0058】

上記ビットシフタSFT1, SFT2のうちSFT1には表示メモリ206から読み出された18ビットの表示データが入力され、SFT2には第2のラッチ回路LT2に取り込まれた表示データが入力される。ビットシフタSFT1, SFT2は、それぞれデコーダDECの出力に応じて18ビットの表示データに対して1ビットシフト処理またはシフト無しのいずれかの動作をするように制御され、1ビットシフト処理では上位側のビットをそれぞれ下位側へ1ビットだけシフトする。従って、1ビットシフト処理すると18ビットの画像データはその LSB のビットが消滅する。加算器ADDは、デコーダDECの出力に応じて1ビットシフトのときはビットシフタSFT1, SFT2から供給されるRGBの各6ビットのうち下位5ビット同士の加算を行なうように構成されている。

40

50

## 【0059】

また、この実施例の単位演算回路 A C U 0 は、デコーダ D E C がそのコントロール信号 C N T によって非動作状態にされているときには、ビットシフタ S F T 1 が入力された表示データをスルーさせ、加算器 A D D がビットシフタ S F T 1 から入力された表示データをスルーさせるように構成されている。デコーダ D E C が非動作状態のとき加算器 A D D をスルー状態にさせる代わりに、ビットシフタ S F T 2 が入力されたデータを遮断してオール“0”のデータを出力し、加算器 A D D はこのオール“0”的データとビットシフタ S F T 1 から入力された表示データとを加算した結果を出力するように構成しても良い。デコーダ D E C のコントロール信号 C N T はタイミング制御回路 203 から供給される。

## 【0060】

この実施例では、表示メモリ 206 からベース画像データと O S D 画像データを時分割で読み出すようにしているが、ベース画像データと O S D 画像データを同時に読み出す方式も考えられる。ただし、その場合には透過処理が行なわないときにも表示メモリ 206 からベース画像データと O S D 画像データが読み出されるので不要な画像データを遮断する仕組みが必要になるとともに、透過処理が行なわれる場合よりも透過処理が行なわれない場合の方が多くのシステムに使用される場合に無駄な読み出し動作による無駄な消費電力が多くなる。従って、本実施例のように時分割でベース画像データと O S D 画像データを読み出す方がトータルの消費電力が少ない回路を構築することができる。

## 【0061】

次に、透過演算回路 211 の動作を、図 6 のタイミングチャートを用いて説明する。

この実施例の液晶コントローラドライバ 200 においては、ブレンディングを行なう場合、まず O S D 画像データが読み出され、その後でベース画像データが読み出されるよう 20 にされる。また、透過演算回路 211 を動作させるクロック信号 C K 1, C K 2 は液晶パネルの 1 ライン表示周期 T 1 の 1/2 の周期に設定されているとともに、ビットをデコードするデコーダ D E C を制御するコントロール信号 C N T は 1 ラインの表示期間の前半は無効レベル(ロウレベル)にされ、後半は有効レベル(ハイレベル)にされるように生成される。

## 【0062】

クロック信号 C K 1 に同期して表示メモリ 206 から O S D 画像データが読み出される(タイミング t 1)と、その画像データはビットシフタ S F T 1 および加算器 A D D をスルーしてクロック信号 C K 2 に同期してラッチ回路 L T 1 にラッチされる(タイミング t 2)。ラッチ回路 L T 1 にラッチされた O S D 画像データはクロック信号 C K 1 の次のパルスに同期してラッチ回路 L T 2 にラッチされる(タイミング t 3)。

## 【0063】

このとき、表示メモリ 206 から次の表示データであるベース画像データが読み出される。また、ラッチ回路 L T 2 にはビットを含む O S D 画像データがラッチされており、クロック信号 C K 1 の立上りに同期してコントロール信号 C N T がハイレベルに変化されると、ビットをデコードしてビットシフタ S F T 1, S F T 2 を活性化させる。これよって、ビットシフタ S F T 1 と S F T 2 ではそれぞれベース画像データと O S D 画像データのビットシフト処理が行なわれ、このビットシフトされた 2 つの画像データが加算器 A D D で加算された結果(透過演算データ)が出力される(図 6 の期間 T 2)。

## 【0064】

この加算器 A D D から出力された透過演算データはクロック信号 C K 2 に同期してラッチ回路 L T 1 にラッチされる(タイミング t 4)。そして、ラッチ回路 L T 1 にラッチされた透過演算データはクロック信号 C K 1 のその次のパルスに同期してラッチ回路 L T 2 にラッチされ、液晶ドライバ(交流化回路およびソース線駆動回路)へ供給される(タイミング t 5)。

## 【0065】

なお、この実施例においては、ビットシフタ S F T 1, S F T 2 が 1 ビットシフトを行なうことで透過率 50% のブレンディング画像を生成して出力する場合を例にとって説明 50

したが、ラッチ回路 L T 2 の保持データをビットシフタ S F T 1 側へ帰還させる経路や加算器 A D D へ帰還させる経路を設けることにより、透過率 25% や 75% の画像データを生成させることができる。

#### 【 0 0 6 6 】

例えば 1 ライン表示期間の前半で表示メモリから読み出された O S D 画像データの ビットが透過率 75% を示しているときは、表示メモリからベース画像データを読み出す前に、ラッチ L T 1 にラッチされている O S D 画像データをビットシフタ S F T 2 に供給して 1 ビットシフトを行なって 50% のデータとしてラッチ L T 2 にラッチした後に、再度ビットシフタ S F T 2 へ供給して 2 回目の 2 ビットシフト処理を行なって 25% のデータとしてラッチ L T 1 にラッチする。そして、この 25% のデータとラッチ回路 L T 2 に保持されている 50% のデータを加算器 A D D に供給して 75% の O S D 画像データを得る。しかし後、表示メモリからベース画像データを読み出してビットシフタ S F T 1 を 2 回通して 25% のデータを生成し、この 25% ベース画像データと前記 75% の O S D 画像データを加算器 A D D で加算して出力する。

#### 【 0 0 6 7 】

同様にして、先ず 25% の O S D 画像データを生成してから 75% ベース画像データを生成し、それらを加算することで透過率 25% の画像データとして出力することも可能である。なお、ビットシフタ S F T 1, S F T 2 を、デコーダ D E C からの出力に応じてそれぞれ一度に 2 ビットシフトや 3 ビットシフトを行なえるように構成しても良い。これにより、透過率 75% や 25% の画像データの生成に要する時間を短縮することができる。

#### 【 0 0 6 8 】

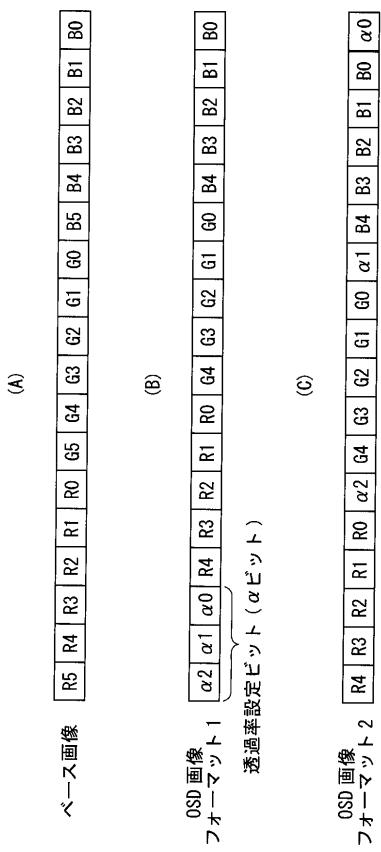

ここで、本実施例の液晶コントローラドライバ 200 におけるベース画像データと O S D 画像データのデータフォーマットの例を、図 7 を用いて説明する。

ベース画像データと O S D 画像データは各々 18 ビットで構成されている。このうちベース画像データは、図 7 ( A ) のように、R G B の各色がそれぞれ 6 ビットで表わされる。O S D 画像データは、R G B の各色がそれぞれ 5 ビットで表わされるが、チップ外部からは図 7 ( B ) のように先頭 3 ビットに ビット 2, 1, 0 が配置されたデータまたは図 7 ( C ) のように R G B の各色の最下位ビットにそれぞれ ビット 2, 1, 0 が分配配置されたデータのいずれのフォーマットのデータも受け付け可能にされている。そして、図 7 ( B ) のようなフォーマットのデータが入力されるとチップ内部のビット処理回路 207 ( 図 1 参照 ) でビットの並びを図 7 ( C ) のように変換して表示メモリ 206 に格納するように構成されている。入力された画像データが図 7 ( B ) または図 7 ( C ) のいずれのフォーマットのデータであるかはデータを入力するインストラクションによって指定される。

#### 【 0 0 6 9 】

ところで、前述したように、本実施例の液晶コントローラドライバ 200 は、特性の異なる 2 つの液晶パネルを駆動する場合に、一方の液晶パネルの駆動状態から他方の液晶パネルの駆動状態へ移る際に、それぞれのパネルの特性に応じて階調電圧生成回路 216 が異なる階調電圧を発生可能に構成されている。そして、階調電圧を切り替えるため 2 つのレジスタ 221 と 222 およびセレクタ S E L 3 を備えている。しかしに、セレクタ S E L 3 によってレジスタ 221 または 222 から 調整回路 217 に供給される設定値を切り替える実施例のような方式では、階調電圧生成回路 216 の応答遅れによって出力される電圧がすぐには上昇せず、切替り時に画質が低下するおそれがある。なお、階調電圧生成回路 216 の応答遅れは、主として階調電圧生成回路 216 内に設けられているバッファアンプ 63 における遅延である。

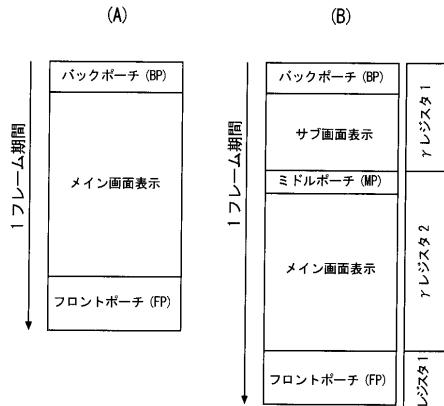

#### 【 0 0 7 0 】

そこで、この実施例では、タイミング制御回路 203 から出力される信号のタイミングを調整することにより、表示が一方のパネルの画面から他方のパネルの画面へ移る際に、図 9 ( B ) に示すようにタイムラグ ( 以下、ミドルポーチと称する ) M P を設け、このミドルポーチ M P の期間においてはいずれのパネルのどのゲートラインにも電圧が印加されな

10

20

30

40

50

いように制御を行なうことによって表示画質の低下を防止するように構成されている。図9(A)は従来の1画面駆動における動作を、図9(B)は本実施例の液晶コントローラドライバによる駆動によって前記第1液晶パネル110に表示されるサブ画面から第2液晶パネル120に表示されるメイン画面へ表示が移る場合の動作を模式的に示したものである。

#### 【0071】

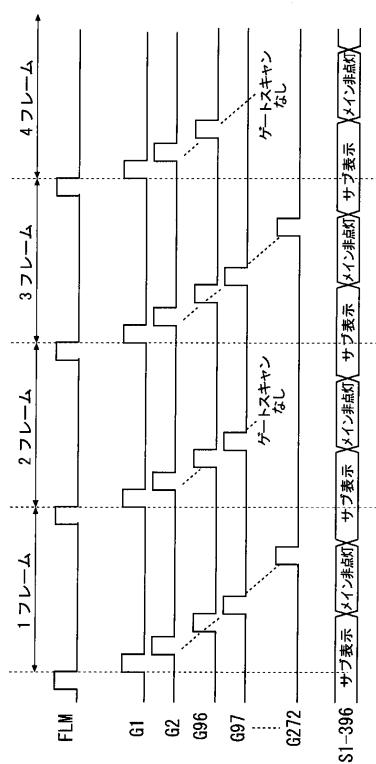

図9(B)に示されているように、本実施例では、サブ画面表示の際にはレジスタ1(221)が選択されてその設定値に基づいて階調電圧が生成され、メイン画面表示の際にはレジスタ2(222)が選択されてその設定値に基づいて異なる階調電圧が生成される。そして、レジスタ1からレジスタ2への切替えはミドルポーチMPの期間に行なわれる。さらに、表示がメイン画面からサブ画面に戻る際にはもともと帰線期間としてフロントポーチと呼ばれる間合い時間FPとバックポーチと呼ばれる間合い時間BPが設けられており、この間に選択レジスタをレジスタ2からレジスタ1へ切り替えて階調電圧の切替えを行なう。上記のような制御を行なうことによって、表示画質の低下を招くことなく異なる特性を有する液晶パネル110から120へ、また120から110へ表示駆動を移すことができる。

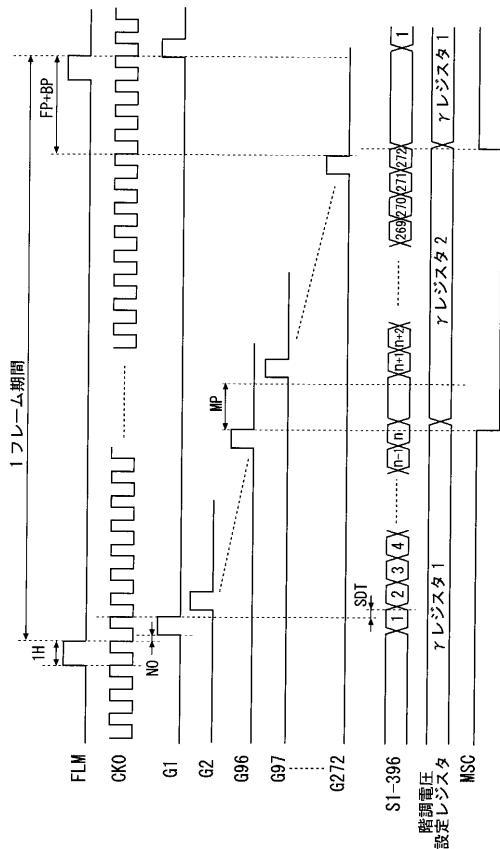

#### 【0072】

図10には、上記ミドルポーチを設けた表示切替え制御を行なう場合のゲート線駆動信号G1～G272のタイミングチャートが示されている。図10において、FLMはフレーム同期信号、CK0は基準クロック信号、G1～G96はサブ画面を提供する第1パネルのゲート線の駆動信号、G97～G272はメイン画面を提供する第2パネルのゲート線の駆動信号、S1～S396は第1パネルと第2パネルに共通のソース線の駆動信号、MSCはメイン画面とサブ画面の切替え信号である。全ソース線の駆動信号S1～S396は同時に出力され、ゲート線駆動信号G1～G272に同期して切替えが行なわれる。図10に示されているように、ゲート線駆動信号G96とG97との間にミドルポーチMPが設けられ、ゲート線駆動信号G272とG1との間にフロントポーチFPおよびバックポーチBPが設けられており、これらの期間に切替え信号MSCによるセレクタSEL3の切替えでレジスタの設定値の選択が行なわれる。

#### 【0073】

上記のように表示画面の切替えの際にミドルポーチ期間を設けることにより、表示画質の低下を招くことなく異なる特性を有する液晶パネル120から110へ表示駆動を移すことができる。なお、上記実施例では、1つの階調電圧生成回路216に2つのレジスタ221, 222の設定値を選択して与える方式であるため、設定値が切り替わった際にバッファアンプ63で応答遅れが発生する。

#### 【0074】

そこで、特性がそれぞれ異なる階調電圧生成回路を2つ用意しておく方式が考えられる。このような方式によれば、表示パネルに応じて2つの階調電圧生成回路の出力を切り替えるようにすれば応答遅れをかなり短くすることができるが、階調電圧生成回路を2つ設けると回路規模が非常に大きくなってしまうという不具合がある。これに対し、実施例のように階調電圧生成回路を1つにしてレジスタの設定値で発生電圧を切り替えるように構成することにより、回路規模の増加を最小限に抑えることが可能となる。

#### 【0075】

なお、コントロールレジスタCTRの一部にミドルポーチMPの期間を指定するレジスタを設け、タイミング制御回路203がこのレジスタの設定値に応じてミドルポーチMPの期間を可変制御する実施例も考えられる。そして、その場合、ミドルポーチMPの期間を1水平期間すなわち基準クロックCK0の周期の整数倍で可変制御するように構成すれば、比較的簡単な回路でミドルポーチMPの期間を可変とすることが可能である。このミドルポーチMPの期間は、階調電圧生成回路や液晶パネルの特性にもよるが最大でも7水平期間程度あれば充分であると考えられる。

#### 【0076】

10

20

30

40

50

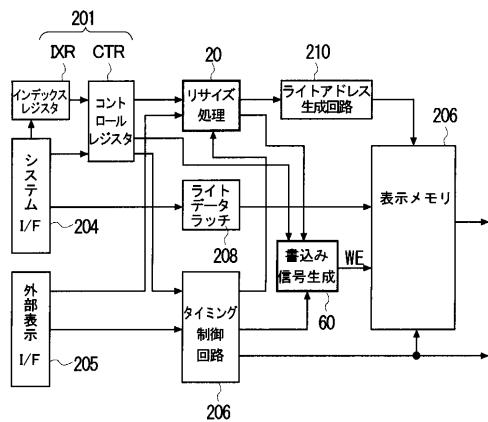

次に、本発明の第2の実施例を、図11～図16を用いて説明する。第2の実施例は、第1の実施例のブレンディング等の機能に加え、入力された画像を1/2, 1/3, ……のように縮小するリサイズ機能を液晶コントローラドライバ200に設けたものである。具体的には、図11のようにライトアドレス生成回路210の前段にリサイズ処理回路20を設けるようにしたものである。また、リサイズ処理回路20における縮小率を設定するためのリサイズレジスタRSZや縦方向と横方向の余り画素数を設定するための余りレジスタRCV, RCHがコントロールレジスタCTR内に設けられる。特に制限されるものでないが、この実施例のリサイズレジスタRSZには、縮小率を設定するビットの他に、間引き画素の位置を設定するビットが設けられる。

## 【0077】

10

リサイズ回路20とレジスタレジスタRSZ, RCV, RCH以外は、図1に示されているものと同一の構成で良い。図11には、図1に示されている回路ブロックのうち第2実施例に関する書き込み系の回路のみ示され、読み出し系の回路は省略されている。図1には示されていないが図11に示されている書き込み信号生成回路60は、表示メモリ206への書き込みの際に許可信号(ライトイネーブル信号)WEを生成する回路で、図1においてはタイミング制御回路206内に設けられている。

## 【0078】

20

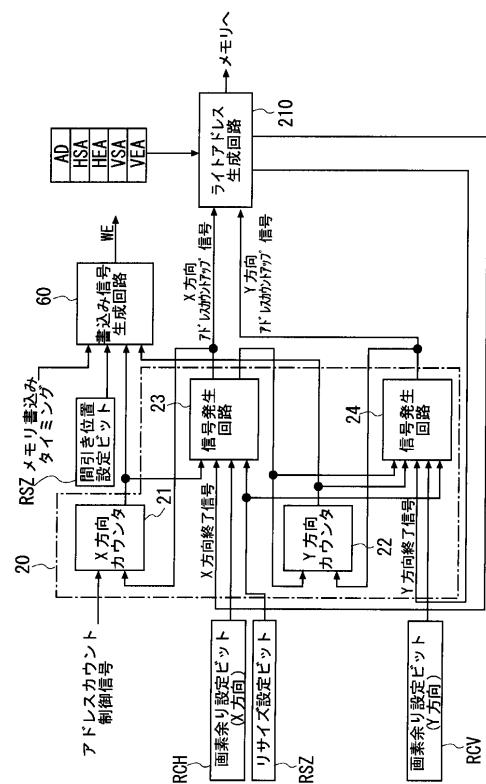

図12には、リサイズ回路20の具体的な構成例が示されている。

リサイズ回路20は、X方向すなわちライン方向のアドレスを計数するX方向カウンタ21と、Y方向すなわち列方向のアドレスを計数するY方向カウンタ22と、X方向カウンタ21のリセット信号およびY方向カウンタ22のクロック信号を発生する信号発生回路23と、Y方向カウンタ22のリセット信号を発生する信号発生回路24とからなる。

## 【0079】

30

X方向カウンタ21は、タイミング制御回路206から供給されるアドレスカウント制御信号(クロック信号)によってカウントアップ動作し、信号発生回路23からのリセット信号によりリセットされ、所定の値の計数を繰返し実行する。アドレスカウント制御信号はチップ外部から供給される書き込み制御信号WR等に基づいて生成される。信号発生回路23は、X方向カウンタ21のカウントアップ信号とライトアドレス生成回路210からのX方向終了信号と余りレジスタRCHからのX方向余り設定ビット信号およびリサイズレジスタRSZからの縮小率設定信号とに基づいて、X方向カウンタ21のリセット信号およびY方向カウンタ22のクロック信号を発生する。

## 【0080】

40

Y方向カウンタ22は、信号発生回路23からのクロック信号によってカウントアップ動作し、信号発生回路24からのリセット信号によりリセットされ、所定の値の計数を繰返し実行する。信号発生回路24は、Y方向カウンタ23のカウントアップ信号とライトアドレス生成回路210からのY方向終了信号と余りレジスタRCVからのY方向余り設定ビット信号およびリサイズレジスタRSZからの縮小率設定信号とに基づいて、Y方向カウンタ23のリセット信号を発生する。X方向カウンタ21のリセット信号およびY方向カウンタ23のリセット信号は、ライトアドレス生成回路210に供給されて内部のアドレスカウンタを更新させる。

## 【0081】

50

ライトアドレス生成回路210は、コントロールレジスタCTRに設けられている書き込み開始アドレスレジスタADおよび書き込み範囲を示すウィンドアドレスを保持するレジスタHSA, HEA, VSA, VEAを参照して、表示メモリ206に対するライトアドレスを生成する。書き込み開始アドレスレジスタADおよびウィンドアドレスレジスタHSA, HEA, VSA, VEAは、本実施例のリサイズ処理のみでなくベース画像よりも小さな画像を表示メモリ206の任意の位置に書き込んで重ね合わせ表示を行なう場合にも使用できるレジスタであり、もともとそのようなレジスタを有する液晶コントローラドライバにおいては、これらのレジスタを新たに設ける必要がない。

## 【0082】

50

また、X方向カウンタ21のカウントアップ信号とY方向カウンタ23のカウントアップ信号は、書き込み信号生成回路60に供給され、書き込み信号生成回路60はこれらの信号とタイミング制御回路203からの書き込みタイミング信号およびリサイズレジスタRSZからの間引き位置設定ビット信号とに基づいて書き込み信号WEを生成するように構成されている。

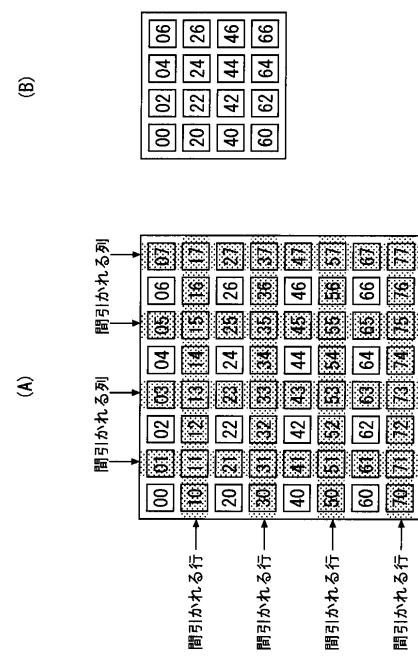

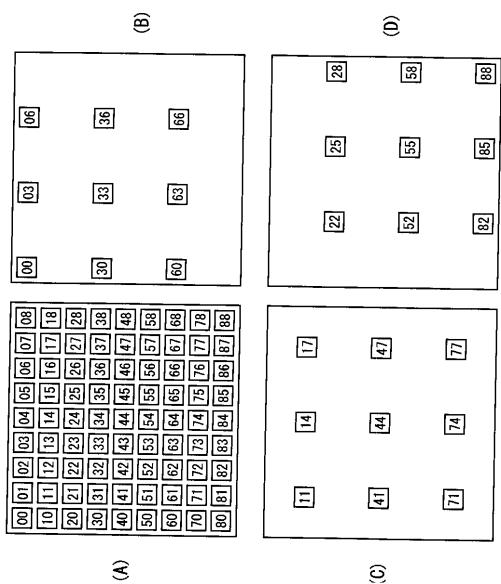

#### 【0083】

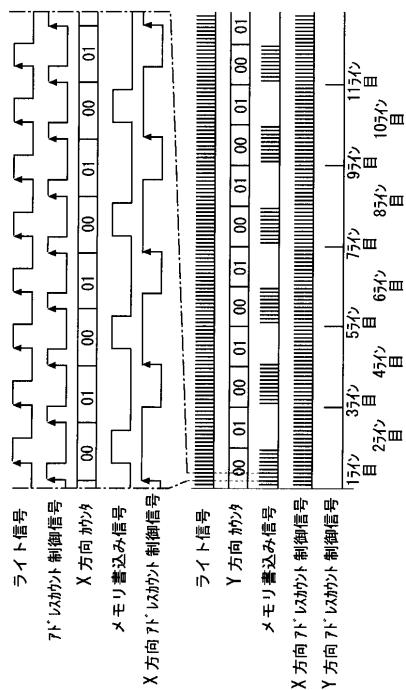

ここで、図12のリサイズ処理回路20による画像縮小処理の原理を、図14および図15を用いて説明する。図14は1/2縮小、図15は1/3縮小を示す。図示しないが、1/4縮小や1/5縮小も同様の原理で可能である。この縮小率がリサイズレジスタRSZの縮小率設定ビットにより指定されるようにされている。

10

#### 【0084】

本実施例のリサイズ処理回路20は、図14(A)に示すように書き込み画像データを所定の割合で間引くことにより、図14(B)に示すように縮小した画像を得てこれを表示メモリ206の指定された領域に書き込むものである。図14(A)では、偶数行と偶数列を間引く例が示されているが、奇数行と奇数列を間引くようにしても縮小した画像を得ることができる。いずれの行および列を間引くかは、リサイズレジスタRSZ内の間引き位置設定ビットにより指定可能にされている。

#### 【0085】

図15(A)には外部から供給される縮小前の画像データが、図15(B)には1/3縮小において1番目の行と列を間引いて記憶するように設定された場合に表示メモリ206に書き込まれる画素データが、また図15(C)には1/3縮小において2番目の行と列を間引いて記憶するように設定された場合に表示メモリ206に書き込まれる画素データが、さらに図15(D)には1/3縮小において3番目の行と列を間引いて記憶するように設定された場合に表示メモリ206に書き込まれる画素データが示されている。

20

#### 【0086】

図13には、縮小率が1/2に設定された場合におけるリサイズ処理回路20の入出力信号および内部信号のタイミングが示されている。図13から分かるように、書き込み信号WEは基準となるライト信号の2周期に1回だけ有効レベル(ハイレベル)にされる。また、X方向カウンタ21とY方向カウンタ23はそれぞれ計数値が「01」になるとリセットされるつまり10進数で見ると「0」と「1」を繰り返す。縮小率が1/3に設定された場合にはX方向カウンタ21とY方向カウンタ23はそれぞれ計数値が「10」になるとリセットされ、縮小率が1/4に設定された場合にはそれぞれ計数値が「11」になるとリセットされる。カウンタが2ビットの場合、1/4縮小まで可能である。カウンタを3ビット構成とすることにより、1/8縮小まで可能にすることができる。

30

#### 【0087】

表2にリサイズレジスタRSZの縮小率設定ビットの割当てと画像サイズとの関係を、表3にリサイズレジスタRSZの間引き位置設定ビットの割当てと間引き位置との関係を、表4に縦方向の余り画素数を設定するための余りレジスタRCVのビット割当てと余り画素数との関係をそれぞれ示す。なお、横方向の余り画素数を設定するための余りレジスタRCHの構成は縦方向の余りレジスタRCVのそれと同様であるので、省略する。

40

#### 【0088】

#### 【表2】

| RSZ2 | RSZ1 | RSZ0 | 書き込みサイズ |

|------|------|------|---------|

| 0    | 0    | 0    | 1/1     |

| 0    | 0    | 1    | 1/2     |

| 0    | 1    | 0    | 1/3     |

| 0    | 1    | 1    | 1/4     |

| 1    | 0    | 0    | 1/5     |

| 1    | 0    | 1    | 1/6     |

| 1    | 1    | 0    | 1/7     |

| 1    | 1    | 1    | 1/8     |

10

【 0 0 8 9 】

【表 3】

| DWP2 | DWP1 | DWP0 | 1/2縮小 | 1/3縮小 | 1/4縮小 | 1/8縮小 |

|------|------|------|-------|-------|-------|-------|

| 0    | 0    | 0    | 1画素目  | 1画素目  | 1画素目  | 1画素目  |

| 0    | 0    | 1    | 2画素目  | 2画素目  | 2画素目  | 2画素目  |

| 0    | 1    | 0    | 設定禁止  | 3画素目  | 3画素目  | 3画素目  |

| 0    | 1    | 1    | 設定禁止  | 設定禁止  | 4画素目  | 4画素目  |

| 1    | 0    | 0    | 設定禁止  | 設定禁止  | 設定禁止  | 5画素目  |

| 1    | 0    | 1    | 設定禁止  | 設定禁止  | 設定禁止  | 6画素目  |

| 1    | 1    | 0    | 設定禁止  | 設定禁止  | 設定禁止  | 7画素目  |

| 1    | 1    | 1    | 設定禁止  | 設定禁止  | 設定禁止  | 8画素目  |

20

【 0 0 9 0 】

【表 4】

30

| RCV2 | RCV1 | RCV0 | 余り画素(縦) |

|------|------|------|---------|

| 0    | 0    | 0    | 0       |

| 0    | 0    | 1    | 1       |

| 0    | 1    | 0    | 2       |

| 0    | 1    | 1    | 3       |

| 1    | 0    | 0    | 4       |

| 1    | 0    | 1    | 5       |

| 1    | 1    | 0    | 6       |

| 1    | 1    | 1    | 7       |

40

【 0 0 9 1 】

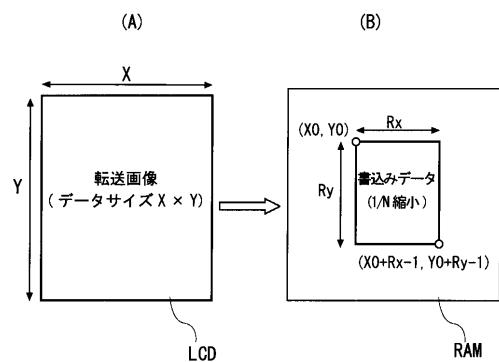

ここで、図16(A)に示すようなデータサイズが $X \times Y$ である転送画像( $X, Y$ は画素数)を $1/N$ に縮小して、図16(B)のように表示メモリ(RAM)の任意の記憶領域(開始位置 $X_0, Y_0$ )に格納する場合を例にとって、外部のマイコンによるコントローラレジスタCTR内の所定のレジスタへの設定の仕方を説明する。なお、 $N$ は正の整数である。

【 0 0 9 2 】

50

外部のマイコンは、リサイズレジスタ R S Z の間引き位置設定領域に (N - 1) をセットする。(N - 1) とするのは、N = 1 のときに縮小率が 1 / 1 であり、表 2 より縮小率が 1 / 1 の場合には間引き位置設定ビット R S Z 2 , R S Z 1 , R S Z 0 は “0 0 0” (1 0 進数の ‘0’ に相当) となるためである。リサイズレジスタ R S Z の間引き位置設定ビットには、表 3 に従って縮小率に応じて設定禁止にならない範囲で自由に設定することができる。レジスタ R C V に設定する縦方向の余り画素数 L は、余り演算式  $L = X \bmod N$  を用いて、前記画素数 X と縮小率 N とから求めることができる。同様に、レジスタ R C H に設定する横方向の余り画素数 M は、余り演算式  $M = Y \bmod N$  を用いて、前記画素数 X と縮小率 N とから求めることができる。

## 【0093】

10

また、外部のマイコンは、上記レジスタの他に、表示メモリの書き込み開始アドレスを設定するレジスタ A D にアドレス X 0 , Y 0 を設定し、書き込み領域設定レジスタ H S A , H E A , V S A , V E A にそれぞれ X 0 , X 0 + R x - 1 , Y 0 , Y 0 + R y - 1 を設定する必要がある。なお、ここで R x , R y はそれぞれ表示メモリ 206 内のデータ書き込み領域のサイズであり、前記転送画像の画素数 X , Y および余り画素数 L , M と縮小率 N を用いて、 $R x = (X - L) / N$  ,  $R y = (Y - M) / N$  なる式により求めることができる。

## 【0094】

本実施例に従うと、外部のマイコン等は予め所定のレジスタを設定し、リサイズを指示するインストラクションを入力して通常の書き込みデータと同様のデータ転送を実行すれば、液晶コントローラドライバ 200 内で自動的に画像の縮小が行なわれ、縮小された画像データが表示メモリ 206 に格納される。本機能を利用すると、例えば複数の画像のサムネイル（縮小画像が並んだ一覧表）を作成したり、カメラ付き携帯電話器において相手方から送られてきた画像を画面全体に表示してその一部に自己のカメラで撮影した画像を縮小表示させるようなことを短時間に行なうことができるようになるという利点がある。

20

## 【0095】

30

又メイン画像パネルとサブ画像パネルを持つカメラ付き携帯電話機において、第一の実施例と合わせて、表示 R A M のメモリ空間をメイン画像パネルとサブ画像パネルと更に ブレンディング及びリサイズ用の空間を設けることにより、表示 R A M の占有面積が大きくなるものの、カメラを使う時に撮影しようとする画像をメイン画面全体に表示させることにより撮影画面を確認しつつ、サブ画面で撮影相手に撮影しようとする画像をリサイズにより縮小表示して確認してもらえるようにしながら、ブレンディングによりメインパネルに時間や携帯の状態等の情報を透かした状態で表示を行うことができ、更に外部から送られてきた画像をリサイズして ブレンディングによりメインパネルに透けた状態で重ね合わせて表示を行うことができる。又この時に、本発明における 特性の補正を行うことにより、メイン画像パネルとサブ画像パネルの両方を画質の劣化を招くことなく一つの階調電圧生成回路からの電圧で駆動し、消費電力、チップ面積の低減を図ることができる。

## 【0096】

40

なお、前記書き込み開始アドレス設定用レジスタ A D および書き込み領域設定レジスタ H S A , H E A , V S A , V E A への設定の仕方によって、リサイズ回路 20 により圧縮された画像データを第 1 画像の記憶領域に格納させ、図 1 の実施例の透過演算回路 211 や関連するレジスタを利用して第 2 画像の記憶領域に記憶されているベース画像データと圧縮画像データを合成した画像を第 2 液晶パネル 120 に表示させることも可能である。

## 【0097】

次に、本発明の第 3 の実施例を説明する。第 3 の実施例は、第 1 の実施例の機能に加え、表示がなされない側の液晶パネルのゲート線を表示時よりも長い周期でスキャンすることで液晶の劣化を防止するようにしたものである。

図 2 に示されているようなソース線を共通にする 2 つの液晶パネル 110 および 120 を有する液晶表示デバイス 100 を駆動するシステムでは、一方の液晶パネルの表示が不要で表示を停止させる場合にも他方の液晶パネルの表示駆動のためにソース線に印加された電圧が非表示の液晶パネルの液晶にも印加されてしまう。このとき、非表示の液晶パネル

50

のゲート線のスキャン動作を停止させると、液晶に交流電圧が印加されなくなって液晶の劣化を招くおそれがある。

【0098】

そこで、この実施例の液晶コントローラドライバは、非表示の液晶パネルのゲート線に対してもスキャン動作を行なって液晶の劣化を防止し、かつそのスキャン周期を通常表示駆動の際よりも充分に長くすることで消費電力の低減を図るようにしている。図18には、一例として第1液晶パネル110のサブ画面は通常の表示を行ない第2液晶パネル120のメイン画面の表示を停止させる場合のゲート線駆動信号のタイミングの例が示されている。

【0099】

図18のタイミングに従うと、第1液晶パネル110のゲート線G1～G96には各フレーム毎に1回ずつ駆動パルスが印加されるのに対し、第2液晶パネル120のゲート線G97～G272には奇数フレーム毎に駆動パルスが印加される。図示の都合上、図18においては、非表示の第2液晶パネル120のゲート線G97～G272に対して奇数フレーム毎に駆動パルスを印加する場合を示したが、非表示の液晶パネルのゲート線に対するスキャンの周期は、液晶の劣化を防止可能な範囲でできるだけ長い時間に設定するのが望ましい。これにより、非表示の液晶パネルのゲート線には所定のインターバルをもって駆動パルスが印加されるようになる。その結果、非表示の液晶パネルにおいても液晶に交番電圧が印加されるようになって液晶の劣化が防止される。

【0100】

なお、この実施例の液晶コントローラドライバは、非表示の液晶パネルのゲート線のスキャン動作に合わせてソース線には黒色を表示させる画素データに対応した電圧を印加するように構成されている。実施例の液晶パネルは黒色を表示させる画素データに対応した電圧が白色を表示させる画素データに対応した電圧よりも低いので、白色を表示させる場合よりも画素電極の充放電に伴う電力損失が少なくて済むためである。白色を表示させる画素データに対応した電圧の方が低い液晶パネルに対しては、非表示の際に色を表示させる電圧を印加するようにしてもよい。

【0101】

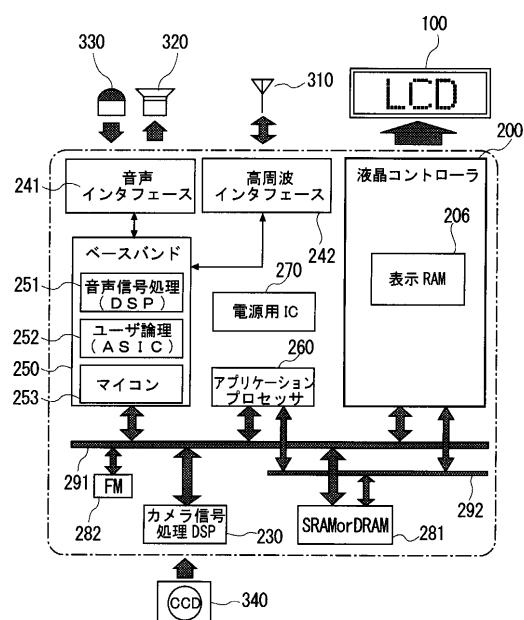

図19は、本発明に係る液晶表示駆動制御装置（液晶コントローラドライバ）を備えたシステムの一例としての携帯電話器の全体構成を示すブロック図である。

この実施例の携帯電話器は、表示手段としての液晶表示デバイス100、送受信用のアンテナ310、音声出力用のスピーカ320、音声入力用のマイクロホン330、CCD（チャージ・カップルド・デバイス）やMOSセンサなどからなる固体撮像素子340、該固体撮像素子340からの画像信号を処理するDSP（Digital Signal Processor）などからなる画像信号処理回路230、本発明に係る液晶表示駆動制御装置としての液晶コントローラドライバ200、スピーカ320やマイクロホン330の信号の入出力を行なう音声インターフェース241、アンテナ310との間の信号の入出力を行なう高周波インターフェース242、音声信号や送受信信号に係る信号処理等を行なうベースバンド部250、MPEG方式等に従った動画処理等マルチメディア処理機能や解像度調整機能、ジャバ高速処理機能等を有するマイクロプロセッサなどからなるアプリケーションプロセッサ260、電源用IC270およびデータ記憶用のメモリ281、282等を備えてなる。

【0102】

アプリケーションプロセッサ260は、固体撮像素子340からの画像信号の他、高周波インターフェース242を介して他の携帯電話器から受信した動画データも処理する機能を有する。液晶コントローラドライバ200とベースバンド部250とアプリケーションプロセッサ260とメモリ281、282と画像信号処理回路230はシステムバス291によりデータ転送可能に接続されている。図19の携帯電話システムでは、システムバス291の他に表示データバス292が設けられ、この表示データバス292には液晶コントローラドライバ200とアプリケーションプロセッサ260およびメモリ281が接続

10

20

30

40

50

されている。

#### 【0103】

なお、上記ベースバンド部250は、例えばDSP(Digital Signal Processor)などからなり音声信号処理を行なう音声信号処理回路251、カスタム機能(ユーザ論理)を提供するASIC(application specific integrated circuits)252、ベースバンド信号の生成や表示制御、システム全体の制御等を行なうシステム制御装置としてのマイコン253等により構成される。

#### 【0104】

メモリ281, 282のうち281は揮発性メモリで通常SRAMやSDRAMにより構成され、さまざまな画像処理を行った画像データ等が保存されるフレームバッファ等として用いられる。メモリ282は不揮発性メモリで例えば所定のブロック単位で一括消去可能なフラッシュメモリにより構成され、表示制御を含む携帯電話器システム全体の制御プログラムや制御データの記憶用に使用される。

#### 【0105】

前記実施例の液晶コントローラドライバを用いた本システムでは、液晶表示デバイス100として、表示画素がマトリックス状に配列されたドットマトリックス方式のカラーTFT液晶パネルを用いることができる。さらに、液晶表示デバイス100が図2に示されているような2画面を有するものである場合にも1つの液晶コントローラドライバで駆動することができる。

#### 【0106】

以上本発明者によってなされた発明を実施例に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。例えば、前記実施例の液晶表示駆動制御装置により駆動されるカラー液晶パネルは、同一列にはRGBのうち同一色の画素が配置されていると説明したが、例えば液晶コントローラドライバ200と液晶パネルとの間に液晶パネルへ送るRGB画像信号の転送順序をR-G-BからG-B-R, B-R-Gのように変える回路を設けたりすることで、列方向にもRGBが順に配置されているような液晶パネルに対しても本発明を適用することができる。また、前記実施例においては、液晶表示駆動制御装置にゲート線駆動回路219が設けられていると説明したが、ゲート線駆動回路が別の半導体集積回路として構成されている場合にも本発明を適用することができる。

#### 【0107】

以上の説明では主として本発明者によってなされた発明をその背景となつた利用分野である液晶表示装置の駆動制御装置およびそれを適用した携帯電話器について説明したが、この発明はそれに限定されるものでなく、液晶以外のドットマトリックス型の表示装置の駆動制御装置および携帯電話器以外のPHS(Personal Handy phone System)、PDAなど種々の携帯型電子機器に適用することができる。

#### 【0108】

##### 【発明の効果】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

すなわち、本発明に従うと、透かし表示のための演算を液晶表示駆動制御装置の側で行なうため、カラー液晶パネルとそれを駆動する液晶表示駆動制御装置とマイクロプロセッサを備えたシステムにおけるマイクロプロセッサの負担を軽減することができる。

#### 【0109】

また、本発明に従うと、透かし表示と透かし無し表示を繰り返し行なう場合に、表示を切り替える度にマイクロプロセッサがいちいち外部メモリから画像データを読み出して液晶表示駆動制御装置へデータを送る必要がなく、液晶表示駆動制御装置内の表示メモリにある画像データを用いてインストラクションのみで表示内容を切り替えることができるため、表示の切替えが速くかつ消費電力の少ない表示システムを実現することができる。

10

20

30

40

50

## 【0110】

さらに、本発明に従うと、内蔵メモリの記憶容量を2つの液晶パネルの画像データを合計した大きさとし、いずれか使用しないパネルに対応した記憶領域を利用して透かし表示のために重ね合わされる他の画像データを記憶させるため、記憶容量の小さな内蔵メモリを効率良く管理して多様な表示を行なうことができるとともに、同様な機能を有するシステムに比べて液晶表示駆動制御装置に内蔵される表示メモリの記憶容量を減少させ、チップサイズひいてはコストを低減することができる。

## 【0111】

また、本発明に従うと、使用する液晶パネルの特性に応じた階調電圧を生成することができるため、2以上の液晶パネルを備えたシステムにおいて1つの表示駆動制御装置により2以上の液晶パネルをそれぞれのパネルの特性に応じて最適駆動することができるという効果がある。

## 【図面の簡単な説明】

【図1】本発明に係る表示駆動制御装置を適用した液晶コントローラドライバの第1の実施例を示すブロック図である。

【図2】第1の実施例の液晶コントローラドライバによって駆動可能な液晶表示デバイスの構成例と表示メモリの画像データ記憶領域との対応を示す説明図である。

【図3】2つの表示パネルを有する液晶表示デバイスの一方の画面に透かし画像を表示する場合の表示領域と画像データ記憶領域との対応を示す説明図である。

【図4】第1の実施例の液晶コントローラドライバ内のタイミング制御回路に設けられるリードアドレス生成部の構成例を示すブロック図である。

【図5】第1の実施例の液晶コントローラドライバ内の表示メモリの後段に設けられる透過演算回路の構成例を示すブロック図である。

【図6】第1の実施例の透過演算回路における信号のタイミングを示すタイミングチャートである。

【図7】第1の実施例の液晶コントローラドライバで扱われる1画素の画像データのデータフォーマットを示す説明図である。

【図8】第1の実施例の液晶コントローラドライバを構成する階調電圧生成回路の構成例を示すブロック図である。

【図9】従来の液晶コントローラドライバと第1の実施例を適用した液晶コントローラドライバにより駆動される液晶パネルの画面の表示タイミングを示す説明図である。

【図10】第1の実施例を適用した液晶コントローラドライバにより駆動される2つの液晶パネルの表示画面の駆動タイミングを示すタイミングチャートである。

【図11】第2の実施例を適用した液晶コントローラドライバの書き込み系回路の構成を示すブロック図である。

【図12】第2の実施例を適用した液晶コントローラドライバを構成するリサイズ処理回路の構成例を示すブロック図である。

【図13】第2の実施例のリサイズ処理回路における信号のタイミングを示すタイミングチャートである。

【図14】図14(A)は第2の実施例のリサイズ処理の原理を示す説明図、図14(B)は縮小された画像データのイメージを示す説明図である。

【図15】第2の実施例のリサイズ処理による1/3縮小の3つのパターンを示す説明図である。

【図16】第2の実施例におけるリサイズ処理前の画像データとリサイズ処理後のメモリ内の圧縮データの格納状態を示す説明図である。

## 【図17】液晶パネルの特性を補正する階調電圧を示す図である。

【図18】第3の実施例を適用した液晶コントローラドライバにおけるインターバル・スキャンの動作タイミングを示すタイミングチャートである。

【図19】本発明を適用した液晶コントローラドライバの応用システムの一例としての携帯電話器の全体構成を示すブロック図である。

10

20

30

40

50

## 【符号の説明】

- 1 0 0 表示装置 (液晶デバイス)

1 1 0 第1液晶パネル

1 2 0 第2液晶パネル

1 3 0 フレキシブル配線ケーブル (FPC)

2 0 0 表示駆動制御装置 (液晶コントローラドライバ)

2 0 1 制御部

2 0 2 クロック信号生成回路 (パルスジェネレータ)

2 0 3 タイミング制御回路

2 0 6 表示メモリ (表示メモリ)

2 0 7 ピット処理回路

2 1 0 ライトアドレス生成回路

2 1 1 透過演算回路

10

【図1】

【図2】

【 四 3 】

【 図 4 】

〔 図 5 〕

〔 四 6 〕

【 図 7 】

【 义 8 】

〔 四 9 〕

【 図 1 0 】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

| F I         | テーマコード(参考) |

|-------------|------------|

| G 09 G 3/20 | 6 1 2 R    |

| G 09 G 3/20 | 6 3 1 B    |

| G 09 G 3/20 | 6 3 1 V    |

| G 09 G 3/20 | 6 3 2 C    |

| G 09 G 3/20 | 6 3 3 Q    |

| G 09 G 3/20 | 6 4 1 C    |

| G 09 G 3/20 | 6 4 2 J    |

| G 09 G 3/20 | 6 5 0 C    |

| G 09 G 3/20 | 6 5 0 M    |

| G 09 G 3/20 | 6 6 0 C    |

| G 09 G 3/20 | 6 6 0 K    |

| G 09 G 3/20 | 6 8 0 D    |

| H 04 M 1/00 | W          |

| H 04 M 1/73 |            |

(72)発明者 田邊 圭

東京都小平市上水本町五丁目20番1号 株式会社日立製作所半導体グループ内

(72)発明者 黒川 康人

東京都小平市上水本町五丁目20番1号 株式会社日立製作所半導体グループ内

F ターム(参考) 2H093 NA16 NA44 NA51 NA61 NC13 NC14 NC29 NC34 NC49 NC50

ND17 ND39 ND60 NG01

5C006 AA22 AB01 AC17 AC21 AF02 AF03 AF04 AF27 AF38 AF44

AF47 AF53 AF71 BB16 BC16 BF02 BF04 BF24 BF28 FA04

FA05 FA16 FA47

5C080 AA10 BB06 CC03 CC07 DD25 DD26 EE29 EE30 FF11 JJ01

JJ02 JJ04 JJ06

5K027 AA11 BB14 BB17 FF22 GG04 MM17

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示设备和控制设备                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2004233743A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2004-08-19 |

| 申请号            | JP2003023424                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2003-01-31 |

| [标]申请(专利权)人(译) | 株式会社瑞萨科技<br>日立器件工程株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 瑞萨科技公司<br>日立设备工程有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| [标]发明人         | 内田孝俊<br>坂巻五郎<br>田邊圭<br>黒川康人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 内田 孝俊<br>坂巻 五郎<br>田邊 圭<br>黒川 康人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/34 G09G3/36 G09G5/02 G09G5/39 H04M1/00 H04M1/73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G09G5/39 G09G3/3666 G09G3/3696 G09G5/02 G09G2320/0276 G09G2330/021 G09G2340/0414<br>G09G2340/0421 G09G2340/10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| FI分类号          | G09G3/36 G02F1/133.505 G09G3/20.611.A G09G3/20.612.F G09G3/20.612.J G09G3/20.612.R<br>G09G3/20.631.B G09G3/20.631.V G09G3/20.632.C G09G3/20.633.Q G09G3/20.641.C G09G3/20.642.J<br>G09G3/20.650.C G09G3/20.650.M G09G3/20.660.C G09G3/20.660.K G09G3/20.680.D H04M1/00.W<br>H04M1/73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA44 2H093/NA51 2H093/NC13 2H093/NC14 2H093/NC29 2H093/NC34<br>2H093/NC49 2H093/NC50 2H093/ND17 2H093/ND39 2H093/ND60 2H093/NG01 5C006/AA22<br>5C006/AB01 5C006/AC17 5C006/AC21 5C006/AF02 5C006/AF03 5C006/AF04 5C006/AF27 5C006/AF38<br>5C006/AF44 5C006/AF47 5C006/AF53 5C006/AF71 5C006/BB16 5C006/BC16 5C006/BF02<br>5C006/BF04 5C006/BF24 5C006/BF28 5C006/FA04 5C006/FA05 5C006/FA16 5C006/FA47 5C080<br>/AA10 5C080/BB06 5C080/CC03 5C080/CC07 5C080/DD25 5C080/DD26 5C080/EE29 5C080/EE30<br>5C080/FF11 5C080/JJ01 5C080/JJ02 5C080/JJ04 5C080/JJ06 5K027/AA11 5K027/BB14 5K027/BB17<br>5K027/FF22 5K027/GG04 5K027/MM17 2H193/ZA04 2H193/ZD21 5K127/AA16 5K127/AA17 5K127<br>/BA05 5K127/CB02 5K127/CB03 5K127/CB30 5K127/CB31 5K127/GD07 5K127/MA14 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

**摘要(译)**

解决的问题：在包括彩色液晶面板，用于驱动彩色液晶面板的液晶显示驱动控制装置和微处理器的系统中，减轻微处理器的负担并减少功耗。解决方案：内置用于存储要在液晶面板上显示的图像数据的存储器（206），并从该存储器顺序读取图像数据，以生成彩色液晶面板的每个像素的三种原色的图像信号，以生成外部输出端子。从该装置输出的液晶显示驱动控制装置设置有透明计算电路（211），用于计算从内置存储器读取的两个图像数据并生成用于水印显示的数据，并且透明计算电路生成该数据。显示数据被提供给驱动器电路（218），并且驱动器电路生成并输出用于液晶面板的驱动信号。[选择图]图3