(19)日本国特許庁 (JP)

# 公開特許公報 (A) (11)特許出願公開番号

特開2003-308048

(P2003-308048A)

(43)公開日 平成15年10月31日(2003.10.31)

| (51) Int.Cl <sup>7</sup> | 識別記号 | F I           | テ-マコード <sup>8</sup> (参考) |

|--------------------------|------|---------------|--------------------------|

| G 0 9 G 3/36             |      | G 0 9 G 3/36  | 2 H 0 9 3                |

| G 0 2 F 1/133            | 575  | G 0 2 F 1/133 | 5 C 0 0 6                |

| G 0 9 G 3/20             | 611  | G 0 9 G 3/20  | 611 E 5 C 0 8 0          |

|                          | 632  |               | 632 C                    |

|                          | 641  |               | 641 C                    |

審査請求 未請求 請求項の数 100L (全 12数) 最終頁に続く

(21)出願番号 特願2002-112713(P2002-112713)

(71)出願人 303018827

N E C 液晶テクノロジー株式会社

神奈川県川崎市中原区下沼部1753番地

(22)出願日 平成14年4月15日(2002.4.15)

(72)発明者 古賀 弘一

東京都港区芝五丁目7番1号 日本電気株式会社内

(72)発明者 奥苑 登

東京都港区芝五丁目7番1号 日本電気株式会社内

(74)代理人 100099830

弁理士 西村 征生

最終頁に続く

(54)【発明の名称】 液晶表示装置

(57)【要約】

【課題】 液晶表示装置において、より多階調の表現を可能にする。

【解決手段】 開示される液晶表示装置は、液晶パネル101A上に配置された各単位画素pが複数の副画素p<sub>1</sub>、p<sub>2</sub>、p<sub>3</sub>からなる液晶表示装置において、副画素p<sub>1</sub>、p<sub>2</sub>、p<sub>3</sub>をそれぞれ分割副画素p<sub>11</sub>、p<sub>12</sub>と、p<sub>21</sub>、p<sub>22</sub>と、p<sub>31</sub>、p<sub>32</sub>に分割するとともに、副画素を構成する各分割副画素p<sub>11</sub>、p<sub>21</sub>、p<sub>31</sub>と、p<sub>12</sub>、p<sub>22</sub>、p<sub>32</sub>に対して、それぞれ異なる階調-輝度特性をもつように駆動するドライバIC201、202を設ける。

## 【特許請求の範囲】

【請求項1】 液晶パネル上に配置された各単位画素が複数の副画素からなる液晶表示装置において、前記副画素を複数の分割副画素に分割するとともに、副画素を構成する各分割副画素がそれぞれ異なる階調・輝度特性をもつように駆動するドライバ手段を設けたことを特徴とする液晶表示装置。

【請求項2】 前記副画素を構成する各分割副画素がそれぞれ異なる面積を有するとともに、前記ドライバ手段が、大きい面積を有する分割副画素には輝度間隔が広い階調・輝度特性を付与し、小さい面積を有する分割副画素には輝度間隔が狭い階調・輝度特性を付与することを特徴とする請求項1記載の液晶表示装置。

【請求項3】 前記輝度間隔が狭い階調・輝度特性が、前記輝度間隔が広い階調・輝度特性の1階調分を補間するものであることを特徴とする請求項2記載の液晶表示装置。

【請求項4】 前記輝度間隔が広い階調・輝度特性が、前記ドライバ手段に対する階調電圧設定入力の上位ビットによって定まり、前記輝度間隔が狭い階調・輝度特性が、前記階調電圧設定入力の下位ビットによって定まるものであることを特徴とする請求項2又は3記載の液晶表示装置。

【請求項5】 前記副画素を構成する各分割副画素が同じ面積を有するとともに、前記ドライバ手段が、一方の分割副画素には駆動入力に基づく電圧・輝度特性の上半部のダイナミックレンジを付与し、他方の分割副画素には駆動入力に基づく電圧・輝度特性の下半部のダイナミックレンジを付与することを特徴とする請求項1記載の液晶表示装置。

【請求項6】 前記上半部の電圧・輝度特性と、下半部の電圧・輝度特性とが、同一ビット数の階調電圧設定入力によって定まるものであることを特徴とする請求項5記載の液晶表示装置。

【請求項7】 前記階調電圧設定入力が、原階調電圧設定入力に対してフレームレートコントロール(FRC)処理を施したものであることを特徴とする請求項4又は6記載の液晶表示装置。

【請求項8】 前記ドライバ手段が、前記副画素に対して同一位置関係にある分割副画素ごとに同一の階調・輝度特性をもつように駆動する出力を発生する、複数のドライバからなることを特徴とする請求項1乃至7のいずれか一に記載の液晶表示装置。

【請求項9】 前記ドライバ手段が、前記副画素に対して同一位置関係にある分割副画素ごとに同一の階調・輝度特性をもつように駆動する複数の出力を発生する、单一のドライバからなることを特徴とする請求項1乃至7のいずれか一に記載の液晶表示装置。

【請求項10】 前記副画素が、カラー画像を表示する単位画素を原色の構成に応じて分解したものであること

を特徴とする請求項1乃至9のいずれか一に記載の液晶表示装置。

## 【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】この発明は、多階調表示可能な液晶表示装置に係り、詳しくは、既存の性能のドライバを用いて、その性能以上の多階調表示が可能な液晶表示装置に関する。

## 【0002】

【従来の技術】フラットパネルを用いた画像表示装置としては、液晶表示装置や、プラズマ表示装置等が知られているが、これらの表示装置における入力インターフェースには、通常、デジタル信号が用いられている。入力インターフェースとしてデジタル信号を用いる表示装置において、表示可能な階調数は、取り扱う信号のビット数によって定まり、多階調になるほどビット数が増加する。液晶表示装置の場合について言えば、現在用いられているうちで、最も階調数が大きいソースドライバは8ビット(256階調)であって、これ以上の階調を表現することはできない。

【0003】例えば、単純にビット数を増加して、12ビットのソースドライバを開発したとした場合、8ビットのソースドライバと比較すると、各階調を生成するためのデジタル・アナログコンバータ(以下、DACという)を構成する抵抗の分割数や、分割した抵抗を選択するためのスイッチ回路の数は、 $2^{12} / 2^8 = 4096 / 256 = 16$ 倍となって、回路規模が著しく大きくなり、チップサイズの拡大等の理由から、コスト的にも上昇することを避けられない。そこで、既存の回路システムを用いて、既存のシステムより多い階調表現を可能にすることが考えられるが、そのための一つの方法として、1個の画素を複数の副画素に分割して使用する方法が提案されている。

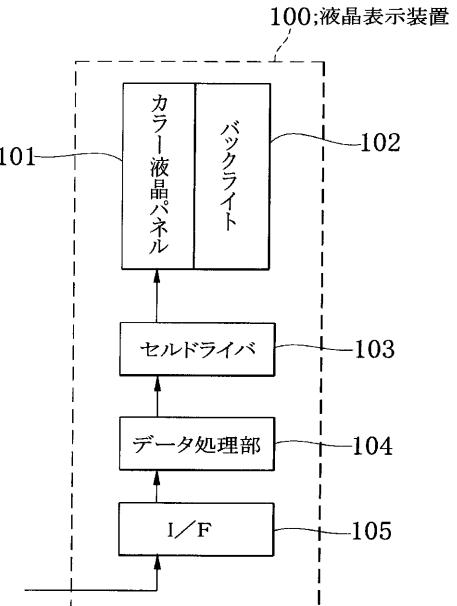

【0004】このような提案の一例として、特開2001-34232号公報に開示されたものがある。図13は、従来の、及び本発明が適用される液晶表示装置の構成例を示すブロック図である。液晶表示装置100は、図13に示すように、カラー液晶パネル101と、バックライト102と、セルドライバ103と、データ処理部104と、入出力部(I/F)105とから概略構成されている。

【0005】カラー液晶パネル101は、平面上に配列された液晶セルによってカラー画像を表示する。バックライト102は、液晶パネルに背面から白色光を与えて、透過光によってカラー画像表示を行わせるための光源となる。セルドライバ103は、入力データによって液晶パネルの各液晶セルを駆動するための駆動信号を発生する。データ処理部104は、入力デジタル信号によって、セルドライバ103に入力データを供給するためのデータ処理を行う。I/F105は、外部入出力と

のインターフェースをとる。セルドライバ103は、液晶セルを駆動するトランジスタのソースを垂直方向（カラム方向）の配列に従って制御するソースドライバ（不図示）と、トランジスタのゲートを水平方向（ロウ方向）の配列に従って制御するゲートドライバ（不図示）とからなっている。

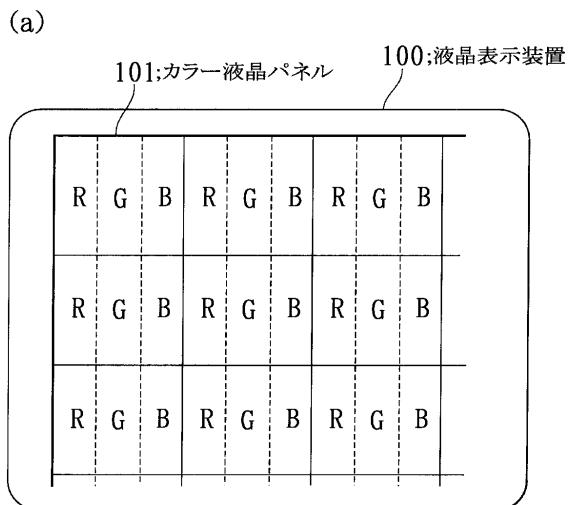

【0006】図14は、従来の液晶表示装置における表示画面の構成例を説明するものであって、前述の特開2001-34232号公報に開示されているものである。同図において（a）は、カラー液晶パネルの表示画面の部分的拡大図、（b）は、各画素の分割の例を示す図である。従来の液晶表示装置におけるカラー液晶パネル101の表示画面は、図14（a）に示すように、カラーフィルタを用いた場合に、各行ごとに、水平方向にR（赤）画素、G（緑）画素及びB（青）画素が、順次繰り返して配列されるように構成されている。このように、カラーフィルタを用いることによって、これらのR画素、G画素及びB画素を介して、それぞれ赤、緑及び青の画像データによるカラー表示が行われるが、カラー液晶パネル101の各画素を構成する液晶セル自体においては、モノクロ画像が表示されている。

【0007】すなわち、カラー液晶パネル101においては、図14（a）に示された一組のR画素とG画素とB画素とを1単位の画素として用い、それぞれにモノクロ表示が行われる。カラー画像の単位画素は、カラーフィルタを用いた際のR画素、G画素及びB画素によって構成されているので、一つの単位画素によって表示可能な輝度値の数は、R画素、G画素及びB画素のそれぞれの画素によって表示可能な輝度値の3倍になる。

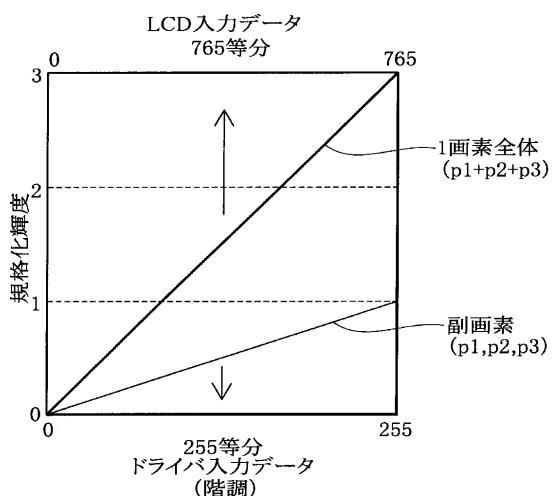

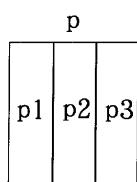

【0008】そこで、設定値間の輝度幅を分割して、例えれば、3分の1ごとに細かく設定することによって、表示画像の階調を細かくすることができる。図14（b）に示すように、一つの単位画素pを、3個の副画素p1、p2、p3に分割するものとすると、副画素p1、p2、p3の各々が、8ビットの表示を行うものとした場合、各副画素が表示可能な輝度値は0から255までなので、単位画素pによって表示可能な輝度値は、0から765（255×3）となり、この輝度値の最小値0を画像データの最小値に対応させ、最大輝度値765を画像データの最大値に対応させることによって、高階調の表示画像を得ることができる。

【0009】データ処理部104では、画像データから変換された輝度値を単位画素pに対して供給する際に、p1、p2、p3の3副画素に対して、ほぼ均等に分散させる。具体的には、8ビットの表示を行うカラー表示ディスプレイに8ビットの画像データが入力された場合、画像データは0から255までの値で構成されるが、この画像データの最小値をカラー表示ディスプレイの最小輝度値0に対応させ、画像データの最大値をカラー表示ディスプレイの最大輝度値765に対応させる。

【0010】図15は、従来の液晶表示装置における、単位画素の輝度値と各副画素の輝度値との関係を示している。データ処理部104は、画像データから得られた輝度値を、図15に示すように、副画素p1、p2、p3に振り分ける。例えば、単位画素の輝度値0に対しては、副画素p1、p2、p3に0、0、0を配分し、単位画素の輝度値1に対しては、副画素p1、p2、p3に0、0、1を配分し、単位画素の輝度値2に対しては、副画素p1、p2、p3に0、1、1を配分するというようにして、以下、輝度値765まで、同様の方法で各副画素の輝度値を配分する。このように、図14に示された従来の液晶表示装置においては、輝度値は、液晶表示装置100に対する入力階調に等しい。

【0011】従来例においては、図14（b）に示すように、液晶表示装置100においては、単位画素pを3個の相等しい副画素p1、p2、p3に分割して、3個の副画素の階調（ドライバへの入力データ）を合算することによって、ほぼ3倍の階調数を得ている。図16は、従来の液晶表示装置における、入力階調と輝度との関係を示したものであって、液晶表示装置100への入力階調（あるいは、各分割画素のドライバへのデータ入力）と輝度（図15では規格化輝度）との関係は線形になっているので、各副画素p1、p2、p3の輝度値の総和が、単位画素pの輝度値に等しくなっている。

#### 【0012】

【発明が解決しようとする課題】図14～図16に示された従来の液晶表示装置100では、各副画素p1、p2、p3への入力階調は、それらの輝度値との関係を線形に設定しているため、単位画素が表現できる階調数は、最大でも各副画素が処理することができる階調数の3倍にしかならない。従って、例えば、各副画素が処理することができる階調数が256階調である場合には、単位画素が処理できる階調数は、765階調にしかならない。そのため、従来の液晶表示装置によって、より高度の多階調表示を行うことは不可能であった。

【0013】これに対して、多階調表示を行うための一手段として、フレームレートコントロール（以下、FRCという）の手法が知られている。FRCとは、例えば、10ビットの画像データを分割して4個の8ビット画像を形成し、この4個の画像データを、フレーム周波数を上げて、順次、表示することによって、8ビットの画像データによって、10ビットの階調表示を行うものである。

【0014】FRCを行えば、容易に多階調表示を行うことができるが、FRCによる画像表示の場合、人間の視覚機能によって生じる残像効果を利用していることから、フリッカ（画面のちらつき）が多発するという問題がある。フリッカを解消するためには、フレーム周波数を高くして、高速で表示切り替えを行う必要があるが、液晶表示装置のドライバIC、又は液晶表示装置自体の

応答速度には限界があるため、高速での表示切り替えは困難であった。

【0015】この発明は上述の事情に鑑みてなされたものであって、液晶表示装置において、FRCを行うことなしに、所望の程度の多階調表示を行うことが可能な液晶表示装置を提供することを目的としている。

【0016】

【課題を解決するための手段】上記課題を解決するため、請求項1記載の発明は液晶表示装置に係り、液晶パネル上に配置された各単位画素が複数の副画素からなる液晶表示装置において、前記副画素を複数の分割副画素に分割するとともに、副画素を構成する各分割副画素がそれぞれ異なる階調・輝度特性をもつように駆動するドライバ手段を設けたことを特徴としている。

【0017】また、請求項2記載の発明は、請求項1記載の液晶表示装置に係り、前記副画素を構成する各分割副画素がそれぞれ異なる面積を有するとともに、前記ドライバ手段が、大きい面積を有する分割副画素には輝度間隔が広い階調・輝度特性を付与し、小さい面積を有する分割副画素には輝度間隔が狭い階調・輝度特性を付与することを特徴としている。

【0018】また、請求項3記載の発明は、請求項2記載の液晶表示装置に係り、前記輝度間隔が狭い階調・輝度特性が、前記輝度間隔が広い階調・輝度特性の1階調分を補間するものであることを特徴としている。

【0019】また、請求項4記載の発明は、請求項2又は3記載の液晶表示装置に係り、前記輝度間隔が広い階調・輝度特性が、前記ドライバ手段に対する階調電圧設定入力の上位ビットによって定まり、前記輝度間隔が狭い階調・輝度特性が、前記階調電圧設定入力の下位ビットによって定まるものであることを特徴としている。

【0020】また、請求項5記載の発明は、請求項1記載の液晶表示装置に係り、前記副画素を構成する各分割副画素が同じ面積を有するとともに、前記ドライバ手段が、一方の分割副画素には駆動入力に基づく電圧・輝度特性の上半部のダイナミックレンジを付与し、他方の分割副画素には駆動入力に基づく電圧・輝度特性の下半部のダイナミックレンジを付与することを特徴としている。

【0021】また、請求項6記載の発明は、請求項5記載の液晶表示装置に係り、前記上半部の電圧・輝度特性と、下半部の電圧・輝度特性とが、同一ビット数の階調電圧設定入力によって定まるものであることを特徴としている。

【0022】また、請求項7記載の発明は、請求項4又は6記載の液晶表示装置に係り、前記階調電圧設定入力が、原階調電圧設定入力に対してフレームレートコントロール(FRC)処理を施したものであることを特徴としている。

【0023】また、請求項8記載の発明は、請求項1乃

至7のいずれか一に記載の液晶表示装置に係り、前記ドライバ手段が、前記副画素に対して同一位置関係にある分割副画素ごとに同一の階調・輝度特性をもつように駆動する出力を発生する、複数のドライバからなることを特徴としている。

【0024】また、請求項9記載の発明は、請求項1乃至7のいずれか一に記載の液晶表示装置に係り、前記ドライバ手段が、前記副画素に対して同一位置関係にある分割副画素ごとに同一の階調・輝度特性をもつように駆動する複数の出力を発生する、単一のドライバからなることを特徴としている。

【0025】また、請求項10記載の発明は、請求項1乃至9のいずれか一に記載の液晶表示装置に係り、前記副画素が、カラー画像を表示する単位画素を原色の構成に応じて分解したものであることを特徴としている。

【0026】

【発明の実施の形態】以下、図面を参照して、この発明の実施の形態について説明する。説明は、実施例を用いて具体的に行う。

#### 第1実施例

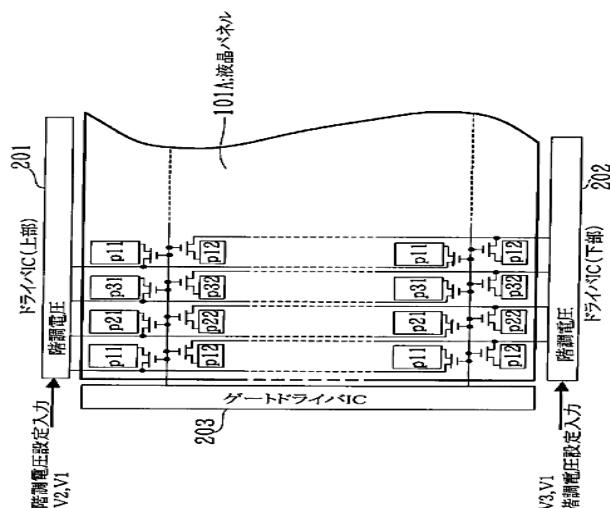

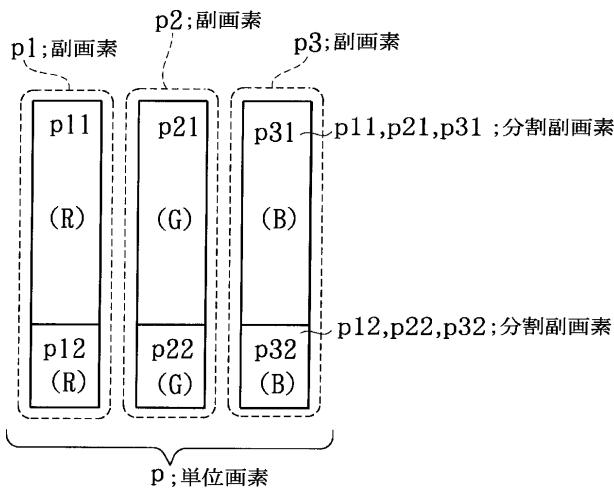

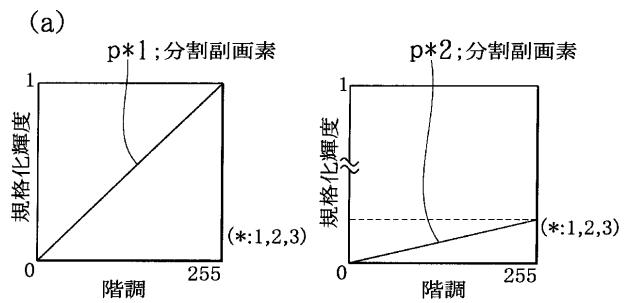

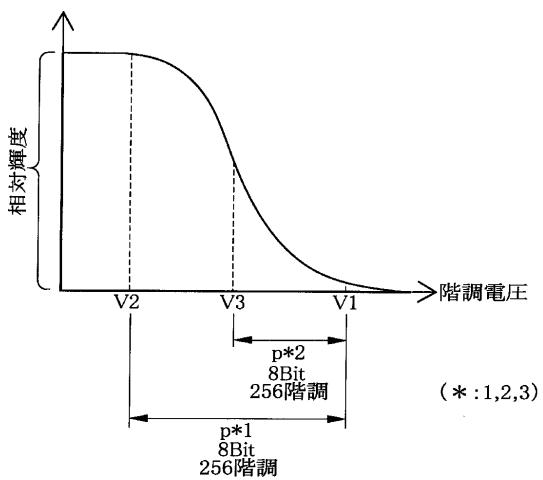

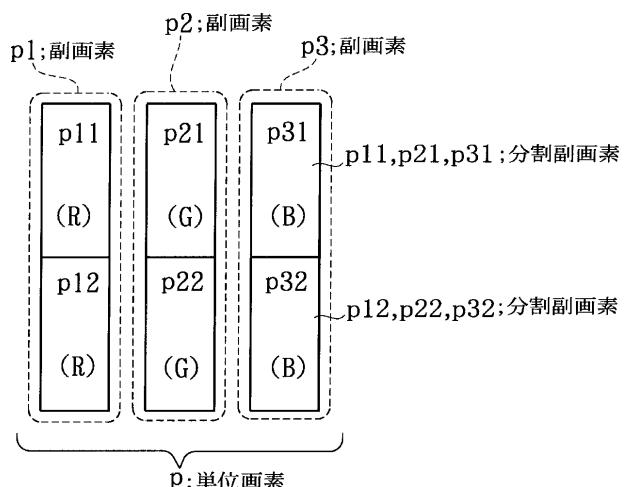

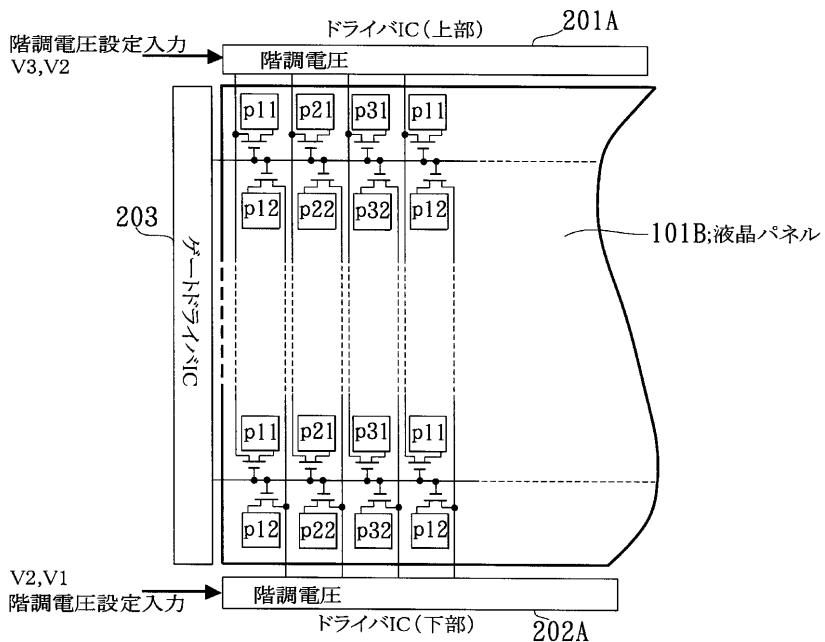

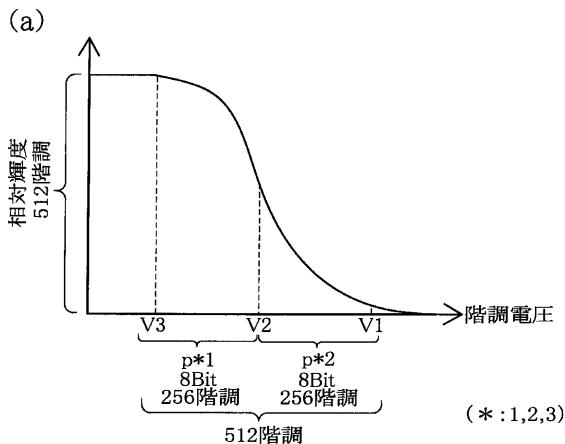

図1は、本発明の第1実施例である液晶表示装置の基本構成を示す回路図、図2は、本実施例の液晶表示装置における、単位画素の構成を示す図、図3は、本実施例の液晶表示装置における、階調と規格化輝度との関係を示す図、図4は、本実施例の液晶表示装置における、階調電圧と相対輝度との関係を示す図である。

【0027】図1においては、この例の液晶表示装置における、液晶パネル101Aと、ソースドライバIC(以下においては、ソースドライバICを、単にドライバICと略称する)201, 202と、ゲートドライバIC203との概略構成が示されている。図1に示すように、液晶パネル101Aに対して、垂直方向に画素列をスイッチングするドライバICとして、液晶パネル101Aの上辺に配置された第1のドライバIC(上部)201と、下辺に配置された第2のドライバIC(下部)202とが設けられているとともに、水平方向に画素行を走査するゲートドライバIC203が設けられている。

【0028】液晶パネル101Aにおいては、ゲートドライバIC203からの1本の出力ごとに、第1の組の分割副画素p11, p21, p31と、第2の組の分割副画素p12, p22, p32とからなる分割副画素群が、水平方向に多数、繰り返して配置されている。そして、第1のドライバIC201の出力は、第1の組の分割副画素p11, p21, p31をスイッチングするそれぞれのTFT(Thin Film Transistor)のデータ電極に接続され、第2のドライバIC202の出力は、第2の組の分割副画素p12, p22, p32をスイッチングするそれぞれのTFTのデータ電極に接続されている。

7

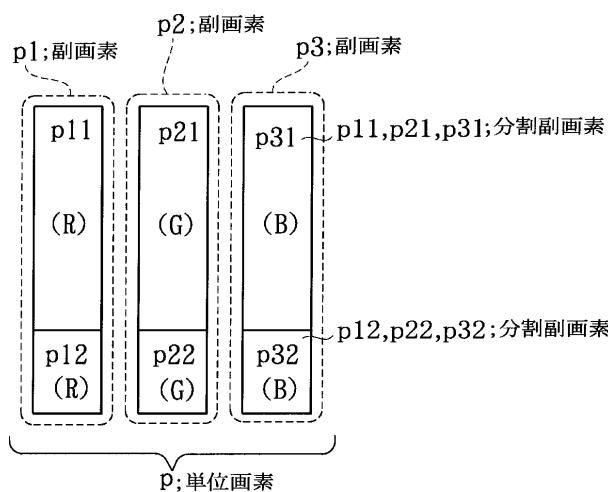

【0029】図2においては、図1に示された各分割副画素の構成が、さらに詳細に説明されている。図2に示すように、分割副画素p11, p12は、組になって副画素p1を形成し、分割副画素p21, p22は、組になって副画素p2を形成し、分割副画素p31, p32は、組になって副画素p3を形成するとともに、副画素p1, p2, p3によって、単位画素pを形成している。そして、図1に示されたように、副画素p1, p2, p3をスイッチングする各TFTのゲート電極が、液晶パネルの走査を制御するゲートドライバIC203の一つの出力に対して、共通に接続されている。

【0030】上辺のドライバIC201には、データ処理部104から、副画素を駆動するための階調電圧設定入力として、V2からV1までの間で変化する電圧が与えられる。ここで、V2は、分割副画素p11, p21, p31に対して印加される駆動電圧（ドライバIC出力電圧）の最大駆動電圧値であり、V1は、分割副画素p11, p21, p31に対して印加される駆動電圧の最小駆動電圧値である。従って、上辺のドライバIC201の印加電圧のダイナミックレンジは、V2 - V1 20の範囲の電圧となる。

【0031】また、下辺のドライバIC202には、データ処理部104から、副画素を駆動するための階調電圧設定入力として、V3からV1までの間で変化する電圧が与えられる。ここで、V3は、分割副画素p12、p22、p32に対して印加される駆動電圧の最大駆動電圧値であり、V1は、上辺のドライバIC201の階調電圧設定入力V1と同じ電圧値である。従って、下辺のドライバIC202の印加電圧のダイナミックレンジは、V3-V1の範囲の電圧となる。ここで、各電圧V3、V2、V1の大小の関係は、V2>V3>V1となる。

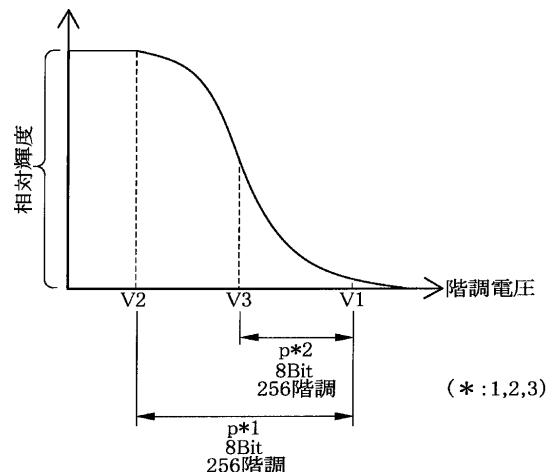

【0032】次に、図1乃至図4を参照して、この例の液晶表示装置の動作を説明する。図3は、ドライバICによって液晶セルへ印加される階調電圧と、液晶パネルの輝度との関係を示し、ドライバICとして、既存の8ビットディジタルドライバを使用した例を示している。8ビットディジタルドライバを使用した場合、上辺のドライバIC201の出力は、階調電圧設定入力V2-V1の範囲で、256階調の表現が可能である。同様に、下辺のドライバIC202の出力は、階調電圧設定入力V3-V1の範囲で、256階調の表現が可能である。

【0033】図2に示されたように、分割副画素は、p11, p21, p31の組（以下、p\*1と称す）と、p12, p22, p32の組（以下、p\*2と称す）とでは、面積が異なっている。ここで、16ビットのデジタル映像データの上位8ビットを上辺のドライバIC201へ入力し、下位8ビットを下辺のドライバIC202へ入力した場合に、分割副画素の組p\*1とp\*2との規格化輝度の比が、256:1になるように構成す

る。

【0034】図3(a)は、分割副画素の組  $p * 1$  と  $p * 2$  の、それぞれの階調と規格化輝度の関係を示している。いま、分割副画素  $p 11$  と  $p 12$  とに注目した場合、分割副画素  $p 11$  の規格化輝度最大値を 1 とすると、分割副画素  $p 12$  の規格化輝度最大値は  $1 / 256$  となる。このとき、分割副画素に対して印加する駆動電圧として、分割副画素  $p 11$  に対しては、上辺のドライバ I C 201 によって、ダイナミックレンジ  $V2 - V1$  の電圧振幅の範囲で、ドライバ I C 内部にあるラダー抵抗(不図示)によって、256階調の特性を持つ電圧値を与える、分割副画素  $p 12$  に対しては、下辺のドライバ I C 202 によって、ダイナミックレンジ  $V3 - V1$  の電圧振幅の範囲で、ドライバ I C 内部にあるラダー抵抗(不図示)によって、256階調の特性を持つ電圧値を与える。

【0035】図4に示すように、階調電圧設定入力V2は、液晶パネルの階調・輝度特性の中で、液晶セルへ印加する電圧の最大値であり、また、V1は最小値である。一方、V3は、16ビットのデジタルデータのうち、下位8ビット分の重みに相当する相対輝度となる電圧値を与える。

【0036】図3(b)は、液晶パネルの階調-輝度特性の一部を拡大して示したものであって、点a~b, b~cのそれぞれの間隔は、分割副画素p11, p21, 又はp31の1階調を示し、この間隔をさらに、256階調に分割して、分割副画素p12, p22, 又はp32によって表現する。分割副画素の組p\*1と、分割副画素の組p\*2との面積比を、規格化輝度の比と同じ256:1としていることから、分割副画素の組p\*1で上位階調の輝度を表現し、分割副画素の組p\*2で下位階調の輝度を表現していて、副画素p1, p2, p3のそれぞれの輝度は、各分割副画素の合計の輝度となる。

【0037】従って、16ビットのデジタルデータを扱う場合、上位8ビットを分割副画素の組  $p * 1$  を駆動する上辺のドライバIC 201へ入力し、下位8ビットを分割副画素の組  $p * 2$  を駆動する下辺のドライバIC 202へ入力すれば、副画素  $p_1, p_2, p_3$  における、1副画素の階調表現数は、 $256 \times 256 = 65536$  階調となる。このことから、副画素  $p_1, p_2, p_3$  上に、それぞれR, G, Bのカラーフィルタを形成するカラー液晶パネルでは、 $65536^3$  色の表現を行うことができ、また、カラーフィルタを含まないモノクロ液晶パネルでは、 $65536 \times 3$  階調の表現を行うことができる。

【0038】このように、この例の液晶表示装置では、副画素  $p_1$  ,  $p_2$  ,  $p_3$  を、それぞれ分割副画素  $p_1$  1 ,  $p_2$  1 ,  $p_3$  1 と  $p_1$  2 ,  $p_2$  2 ,  $p_3$  2 に分割するとともに、対応する分割副画素の分割比（面積比）を 1 以外の値として、それぞれ別のドライバ I<sub>C</sub> で駆動す

るようとしたので、複雑な回路構成を必要とせずに、既存のドライバICを使用して、従来の液晶表示装置による表現以上の多階調表現を行うことができる。

【0039】なお、第1実施例では、分割副画素の分割比を1と異ならせるものとしたが、分割副画素の分割比は、1(同面積)としてもよい。以下においては、この場合の実施例について説明する。

#### 【0040】 第2実施例

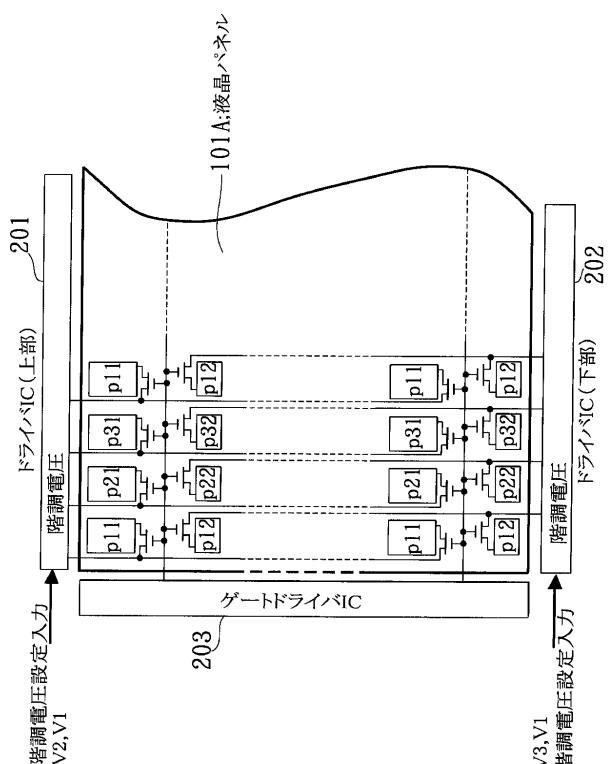

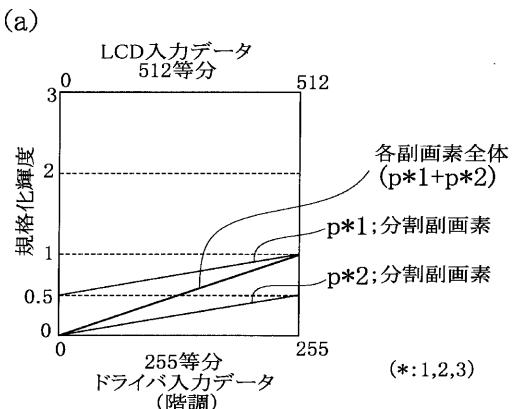

図5は、本発明の第2実施例である液晶表示装置の基本構成を示す回路図、図6は、本実施例の液晶表示装置における、単位画素の構成を示す図、図7は、本実施例の液晶表示装置における、階調電圧と相対輝度との関係を示す図、図8は、本実施例の液晶表示装置における、階調と規格化輝度との関係を示す図である。

【0041】図5においては、この例の液晶表示装置における、液晶パネル101Bと、ドライバIC201A, 202Aと、ゲートドライバIC203との概略構成が示されている。この例の液晶パネル101Bは、分割副画素の面積比が第1実施例の場合の液晶パネル101と異なる。液晶パネル101Bの上辺に配置された第1のドライバIC201Aと、下辺に配置された第2のドライバIC202A、及び水平方向に画素行を走査するゲートドライバIC203の構成は、図1に示された第1実施例の場合の、ドライバIC201, 202、及びゲートドライバIC203の構成と同様であるが、分割副画素の面積比が、第1実施例の場合と異なるに対応して、ドライバIC201A, 202Aの発生する電圧が、第1実施例の場合と異なる。

【0042】図6においては、図5に示された各分割副画素の構成が、さらに詳細に説明されている。図6に示す、R画素の分割副画素p11, p12と副画素p1、G画素の分割副画素p21, p22と副画素p2、B画素の分割副画素p31, p32と副画素p3の構成、及び副画素p1, p2, p3と単位画素pの構成は、図2に示された第1実施例の場合と同様であるが、分割副画素の面積が、図6に示すように、p\*1とp\*2とで同じであって、面積比が1になっている点が、第1実施例の場合と異なる。

【0043】図7(a)においては、ドライバICの1出力あたりの階調分解能が8ビット(256階調)である場合の、ドライバICの階調電圧設定入力に対する単位画素の相対輝度特性を示している。各ドライバICには、階調情報をもつ8ビットのデジタルデータが入力されるが、各ドライバICは、階調電圧設定入力で与えられた電圧範囲を256階調分に分割した電圧値を内部にもつていて、入力デジタルデータの階調に相当する電圧値を選択して、データ電極へ出力する。一般的に、ドライバIC内部にもつ256等分の電圧は、内部のレーダー抵抗(不図示)の値を調整することによって、各階調の電圧が、液晶の電圧-輝度特性に合致するように設

定されている。

【0044】液晶パネル101Bの上辺に接続される、分解副画素の組p\*1を駆動するドライバIC201Aへは、V3からV2の範囲の階調電圧設定入力を供給するので、この際の各副画素の印加電圧のダイナミックレンジは、V3-V2となる。また、液晶パネル101Bの下辺に接続される、分解副画素の組p\*2を駆動するドライバIC202Aへは、V2からV1の範囲の階調電圧設定入力を供給するので、この際の各副画素の印加電圧のダイナミックレンジは、V2-V1となる。図6に示されたように、各副画素p1, p2, p3を構成する分割副画素は、上下に等分割されている関係上、V2としては、分割副画素の組p\*1の最小輝度であって、分割副画素の組p\*2の最大輝度となる電圧値を入力する。

【0045】図8は、各副画素の0~255階調の階調電圧(ドライバ入力データ)に対する規格化輝度を示したものである。単位画素pの全体の規格化輝度の最大値を3と定義した場合、副画素p1, p2, p3の最大規格化輝度は、それぞれ、3等分した1となる。また、副画素を構成する分割副画素の規格化輝度は、分割副画素の組p\*1とp\*2とで、印加される階調電圧範囲が異なるため、p\*1では0.5~1の範囲となり、p\*2では0~0.5の範囲となるので、副画素p1, p2, p3のそれぞれの輝度は合計されて、2倍のp\*1+p\*2となる。

【0046】さらに、1単位画素の輝度は、各副画素の輝度の合計で表現されるため、副画素p1, p2, p3の最大輝度が1の場合、1単位画素の最大輝度はその3倍の3となる。このことを階調数で表すと、副画素上に、R, G, Bのカラーフィルタが形成されているカラー液晶パネルの場合、図8(a)に示すように、1分割副画素の階調数は256階調であり、1副画素で表現可能な階調数は2倍の512階調となって、さらに1単位画素では、 $512^3$ 色の表現が可能となる。また、カラーフィルタを含まないモノクロ液晶パネルの場合は、図8(b)に示すように、1副画素あたり512階調なので、1単位画素では、3倍の1536階調となる。

【0047】図7(b)においては、各ドライバICへ入力されるデジタルデータにFRONT処理を施すことによって、1分割副画素の表現階調数を10ビット相当にしたときの例を示している。この場合、各副画素p1, p2, p3では、1024の2倍の2048階調の表現が可能になるので、単位画素pの階調数は、カラー液晶パネルのとき $2048^3$ 色となり、モノクロ液晶パネルとしたとき、3倍の6144階調となる。

【0048】このように、この例の液晶表示装置では、副画素p1, p2, p3を、それぞれ分割副画素p11, p21, p31とp12, p22, p32に等分割して、それぞれ別のドライバICで駆動するようにした

ので、複雑な回路構成を必要とせずに、既存のドライバICを使用して、従来の液晶表示装置による表現以上の多階調表現を行うことができる。この例の場合、第1実施例の場合と比較して表現可能な階調数は少なくなるが、同一副画素を分割した分割副画素の面積が同じなので、プロセス上の構成が第1実施例の場合より容易になる。

【0049】第1実施例、第2実施例においては、ドライバICを液晶パネルの上辺と下辺とに分割して設けるものとしたが、ドライバICをいずれかの1辺のみに設けることも可能である。以下においては、ドライバICを液晶パネルの上辺のみに設ける場合の実施例について説明する。

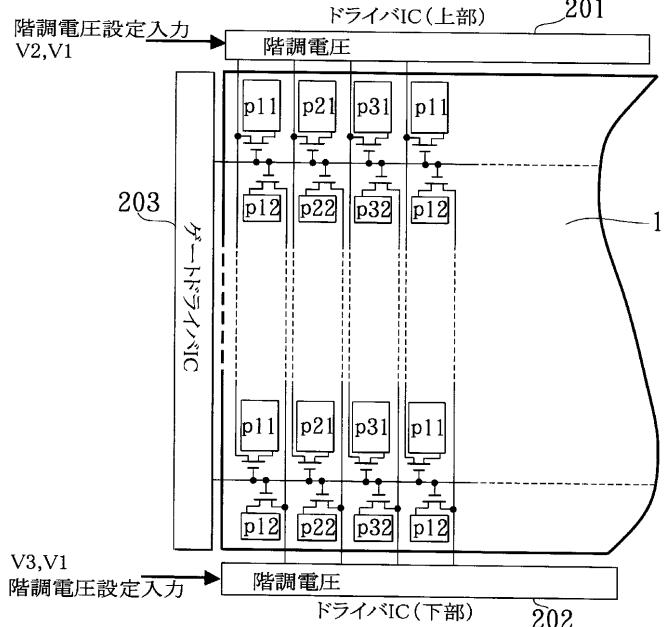

### 【0050】 第3実施例

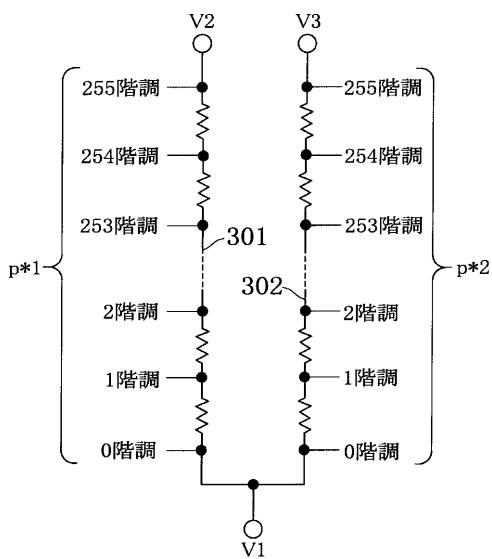

図9は、本発明の第3実施例である液晶表示装置の基本構成を示す回路図、図10は、本実施例の液晶表示装置における、単位画素の構成を示す図、図11は、本実施例の液晶表示装置における、階調電圧生成用ラダー抵抗の構成の関係を示す図、図12は、本実施例の液晶表示装置における、階調電圧と相対輝度との関係を示す図である。

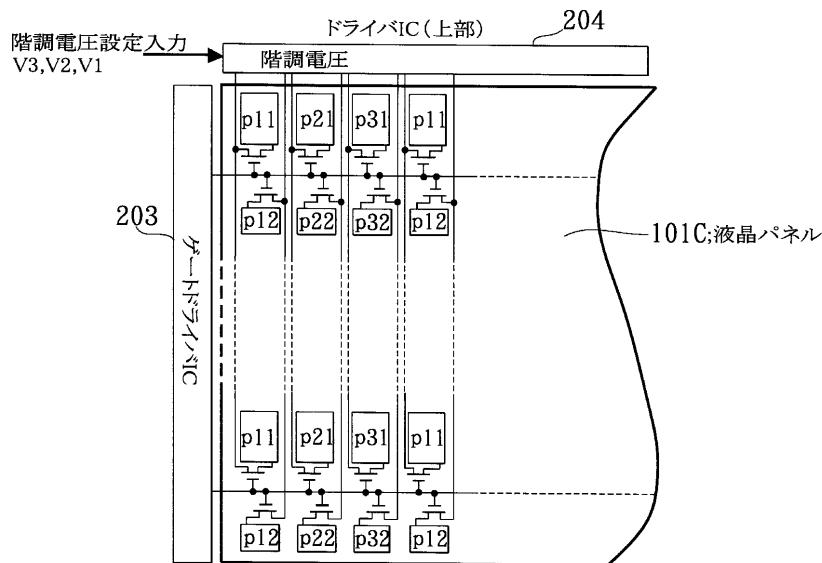

【0051】図9においては、この例の液晶表示装置における、液晶パネル101Cと、ドライバIC204と、ゲートドライバIC203との概略構成が示されている。この例の液晶パネル101Cは、分割副画素の配置は第1実施例の場合の液晶パネル101と同じである。各副画素を駆動するドライバIC204は、液晶パネル101Cの上辺に配置されていて、分割副画素の組p\*1とp\*2とを同一ドライバICから駆動するように構成されている点が、第1実施例及び第2実施例の場合と異なっている。図10においては、図9の液晶表示装置における各分割副画素の構成が示されているが、第1実施例の場合と同様なので、以下においてはその説明を省略する。

【0052】図11においては、ドライバIC204における、階調電圧生成用ラダー抵抗の構成が示されている。階調電圧生成用ラダー抵抗は、分割副画素の組p\*1用の抵抗分圧器301と、分割副画素の組p\*2用の抵抗分圧器302とからなっている。抵抗分圧器301は、階調電圧設定入力V2-V1間で、0階調から25階調までの256階調分の階調電圧を生成して、分割副画素の組p\*1の各分割副画素へ供給する。抵抗分圧器302は、階調電圧設定入力V3-V1間で、0階調から255階調までの256階調分の階調電圧を生成して、分割副画素の組p\*2の各分割副画素へ供給する。

【0053】抵抗分圧器301のV1のノードと、抵抗分圧器302のV1のノードとは、ドライバIC204の内部で接続されている。抵抗分圧器301によって、V2-V1間の階調電圧設定入力に基づいて生成された階調電圧は、ドライバIC204の奇数番目の出力を介

して分割副画素の組p\*1の各分割副画素へ供給され、抵抗分圧器302によって、V3-V1間の階調電圧設定入力に基づいて生成された階調電圧は、ドライバIC204の偶数番目の出力を介して分割副画素の組p\*2の各分割副画素へ供給される。

【0054】この例における階調電圧と相対輝度との関係は、第1実施例の場合と同様であって、図12に示すように、階調電圧設定入力V2は、液晶パネルの階調-輝度特性の中で、液晶セルへ印加する電圧の最大値であり、また、V1は最小値である。一方、V3は、16ビットのデジタルデータのうち、下位8ビット分の重みに相当する相対輝度となる電圧値を与える。

【0055】このように、この例の液晶表示装置では、同一のドライバIC204から分割副画素の組p\*1とp\*2とを駆動するようにしたので、分割副画素の組p\*1を駆動する階調電圧設定入力のV1ノードと、分割副画素の組p\*2を駆動する階調電圧設定入力のV1ノードとをドライバIC204の内部で接続することができ、従って、V1ノードが、上辺のドライバIC201と、下辺のドライバIC202とに分離している第1実施例の場合のように、両ドライバIC間の階調電圧設定入力の誤差に基づいて、出力階調にばらつきが生じることを防止できる。

【0056】以上、この発明の実施例を図面により詳述してきたが、具体的な構成はこの実施例に限られたものではなく、この発明の要旨を逸脱しない範囲の設計の変更等があってもこの発明に含まれる。例えば、第1実施例と第2実施例の場合に、第1のドライバICと第2のドライバICの位置は、液晶パネルの上辺と下辺に限らず、逆の位置関係であってもよい。また、第3実施例の場合に、ドライバICは、液晶パネルの上辺に限らず、下辺にあってもよい。

【0057】また、FRC処理は、第2実施例の場合に限らず、第1実施例及び第3実施例の場合にも適用することができる。また、第3実施例において、同一副画素を構成する分割副画素の面積比は、第1実施例の場合と同様に1と異なるものとしたが、第2実施例の場合と同様に1であるとしてもよい。さらに、この発明は、カラーライズ表示装置の場合に限らず、液晶パネルを構成する単位画素が1個の画素からなるモノクロライズ表示装置の場合にも適用することができる。

### 【0058】

【発明の効果】以上説明したように、本発明の液晶表示装置によれば、各副画素を分割副画素から構成して、それぞれ別のドライバICで駆動することによって、複雑な回路構成を必要とせずに、既存のドライバICを使用して、従来の液晶表示装置による表現以上の多階調表現を行うことができる。また、本発明の液晶表示装置によれば、各副画素を分割副画素から構成して、同一のドライバICで駆動することによって、新規のドライバIC

を必要とするが、従来の液晶表示装置による表現以上の多階調表現を行うことができる。

【図面の簡単な説明】

【図1】本発明の第1実施例である液晶表示装置の基本構成を示す回路図である。

【図2】同実施例の液晶表示装置における、単位画素の構成を示す図である。

【図3】同実施例の液晶表示装置における、階調と規格化輝度との関係を示す図である。

【図4】同実施例の液晶表示装置における、階調電圧と相対輝度との関係を示す図である。

【図5】本発明の第2実施例である液晶表示装置の基本構成を示す回路図である。

【図6】同実施例の液晶表示装置における、単位画素の構成を示す図である。

【図7】同実施例の液晶表示装置における、階調電圧と相対輝度との関係を示す図である。

【図8】同実施例の液晶表示装置における、階調と規格化輝度との関係を示す図である。

【図9】本発明の第3実施例である液晶表示装置の基本構成を示す回路図である。

\*【図10】同実施例の液晶表示装置における、単位画素の構成を示す図である。

【図11】同実施例の液晶表示装置における、階調電圧生成用ラダー抵抗の構成を示す図である。

【図12】同実施例の液晶表示装置における、階調電圧と相対輝度との関係を示す図である。

【図13】従来の、及び本発明が適用される液晶表示装置の構成例を示すブロック図である。

【図14】従来の液晶表示装置における表示画面の構成例を示す図である。

【図15】従来の液晶表示装置における、単位画素の輝度値と各副画素の輝度値との関係を示す図である。

【図16】従来の液晶表示装置における、入力階調と輝度との関係を示す図である。

【符号の説明】

100A, 100B, 100C 液晶パネル

201, 201A ドライバIC

202, 202A ドライバIC

203 ゲートドライバIC

204 ドライバIC

301, 302 抵抗分圧器

【図1】

【図13】

【図2】

【図3】

【図4】

【図11】

【図6】

〔図5〕

【図7】

【図8】

【図9】

【図10】

【図12】

【図15】

【図14】

【図16】

| 一単位画素<br>輝度値 | 副画素p1 | 副画素p2 | 副画素p3 |

|--------------|-------|-------|-------|

| 0            | 0     | 0     | 0     |

| 1            | 0     | 0     | 1     |

| 2            | 0     | 1     | 1     |

| 3            | 1     | 1     | 1     |

| 4            | 1     | 1     | 2     |

| 5            | 1     | 2     | 2     |

| :            | :     | :     | :     |

| :            | :     | :     | :     |

| 762          | 254   | 254   | 254   |

| 763          | 254   | 254   | 255   |

| 764          | 254   | 255   | 255   |

| 765          | 255   | 255   | 255   |

(b)

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

G 09 G 3/20

識別記号

F I

テ-マコ-ト<sup>®</sup> (参考)

G 09 G 3/20

6 4 1 E

6 4 1 G

6 4 1 K

6 4 2 K

6 4 2

(72) 発明者 山口 真智彦

東京都港区芝五丁目7番1号 日本電気株

式会社内

F ターム(参考) 2H093 NA16 NA32 NA33 NA43 NA53

NA54 NA55 NC13 NC22 NC23

NC25 NC34

5C006 AA12 AA14 AA16 AA17 AA22

AC11 AF44 AF47 AF84 AF85

BB16 BC12 BF43 FA12 FA23

FA41 FA52 FA56

5C080 AA10 BB05 CC03 DD06 DD08

DD22 DD27 EE29 EE30 FF11

JJ01 JJ02 JJ03

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">JP2003308048A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2003-10-31 |

| 申请号            | JP2002112713                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2002-04-15 |

| [标]申请(专利权)人(译) | NEC液晶技术株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | NEC LCD科技有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 古賀 弘一<br>奥苑 登<br>山口 真智彦                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 古賀 弘一<br>奥苑 登<br>山口 真智彦                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| CPC分类号         | G09G3/3696 G09G3/2074 G09G3/3607 G09G3/3648                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G09G3/36 G02F1/133.575 G09G3/20.611.E G09G3/20.632.C G09G3/20.641.C G09G3/20.641.E<br>G09G3/20.641.G G09G3/20.641.K G09G3/20.642.K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA32 2H093/NA33 2H093/NA43 2H093/NA53 2H093/NA54 2H093/NA55 2H093<br>/NC13 2H093/NC22 2H093/NC23 2H093/NC25 2H093/NC34 5C006/AA12 5C006/AA14 5C006/AA16<br>5C006/AA17 5C006/AA22 5C006/AC11 5C006/AF44 5C006/AF47 5C006/AF84 5C006/AF85 5C006<br>/BB16 5C006/BC12 5C006/BF43 5C006/FA12 5C006/FA23 5C006/FA41 5C006/FA52 5C006/FA56<br>5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD06 5C080/DD08 5C080/DD22 5C080/DD27 5C080<br>/EE29 5C080/EE30 5C080/FF11 5C080/JJ01 5C080/JJ02 5C080/JJ03 2H193/ZA04 2H193/ZA08<br>2H193/ZA19 2H193/ZC02 2H193/ZC15 2H193/ZD23 2H193/ZD24 2H193/ZD25 2H193/ZF04 2H193<br>/ZF05 2H193/ZF37 |         |            |

| 代理人(译)         | 西村 征生                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 其他公开文献         | <a href="#">JP4143323B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

要解决的问题：在液晶显示设备中能够表达多个灰度。公开的液晶显示装置是其中布置在液晶面板101A上的每个单位像素p包括多个子像素p1, p2, p3的液晶显示装置。划分的子像素p11, p12, p21, p22和p31, p32被划分为不同的子像素p11, p21, p31和p12, p22, p32, 每个子像素具有不同的灰度级。-提供被驱动以具有亮度特性的驱动器IC 201和202。