(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4225777号

(P4225777)

(45) 発行日 平成21年2月18日(2009.2.18)

(24) 登録日 平成20年12月5日(2008.12.5)

(51) Int.CI.

F 1

**G09G 3/36 (2006.01)**

**G02F 1/133 (2006.01)**

**G09G 3/20 (2006.01)**

GO9G 3/36

GO2F 1/133 550

GO9G 3/20 611A

GO9G 3/20 612F

GO9G 3/20 612T

請求項の数 15 (全 39 頁) 最終頁に続く

(21) 出願番号

特願2002-367738 (P2002-367738)

(22) 出願日

平成14年12月19日 (2002.12.19)

(65) 公開番号

特開2003-302951 (P2003-302951A)

(43) 公開日

平成15年10月24日 (2003.10.24)

審査請求日

平成17年5月25日 (2005.5.25)

(31) 優先権主張番号

特願2002-31593 (P2002-31593)

(32) 優先日

平成14年2月8日 (2002.2.8)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100104695

弁理士 島田 明宏

(72) 発明者 熊田 浩二

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(72) 発明者 太田 隆滋

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(72) 発明者 香川 治人

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

最終頁に続く

(54) 【発明の名称】表示装置ならびにその駆動回路および駆動方法

(57) 【特許請求の範囲】

【請求項 1】

水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転することで周期的に反転させる駆動回路を備えた表示装置であって、

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路と、

前記第2の電極を基準として前記画像に応じた電圧信号を前記複数の映像信号線に供給する映像信号線駆動回路と、

前記容量性負荷への印加電圧の極性が反転する時には、前記各映像信号線を前記映像信号線駆動回路から電気的に切り離すと共に前記第2の電極に供給される電圧と同等の電圧レベルを提供する電極に短絡させる接続切換回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

10

20

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記駆動回路は、前記容量性負荷への印加電圧の極性反転に応じて第1の所定電圧と第2の所定電圧を交互に前記共通電極に与える共通電極駆動回路を含み、

前記共通電極駆動回路は、前記接続切換回路が前記各映像信号線と前記共通電極に供給される電圧と同等の電圧レベルを提供する電極とを短絡させている期間内に、前記共通電極に供給されている電圧を前記第1の所定電圧と前記第2の所定電圧との間で切り換えることを特徴とする、表示装置。

#### 【請求項2】

前記共通電極に供給される電圧と同等の電圧レベルを提供する電極は、前記共通電極であることを特徴とする、請求項1に記載の表示装置。

#### 【請求項3】

前記映像信号線駆動回路と前記共通電極駆動回路とは、同一基板上または同一チップ内に形成されたことを特徴とする、請求項1に記載の表示装置。

#### 【請求項4】

水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる駆動回路を備えた表示装置であって、

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路と、

前記第2の電極を基準として前記画像に応じた電圧信号を前記複数の映像信号線に供給する映像信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号線駆動回路は、

複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインと前記共通電極への供給電圧である共通電極信号と同等の電圧レベルが与えられる1つの電圧バスラインとかなる所定数の電圧バスラインと、

前記各映像信号線に対応して設けられ、前記所定数の電圧バスラインのうちいずれか1つの電圧バスラインを選択して対応する映像信号線に接続する電圧選択回路とを含み、

前記各電圧選択回路は、各水平走査期間内では、前記所定数の電圧バスラインのうち前

10

20

30

40

50

記映像信号に応じた基準電圧の与えられた電圧バスラインを選択して対応する映像信号線に接続し、前記容量性負荷への印加電圧の極性が反転する時には、前記共通電極信号と同等の電圧レベルの与えられた前記1つの電圧バスラインを選択して対応する映像信号線に接続することを特徴とする、表示装置。

【請求項5】

水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる駆動回路を備えた表示装置であって、

前記第1の電極としての複数の映像信号線と、

10

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路と、

前記第2の電極を基準として前記画像に応じた電圧信号を前記複数の映像信号線に供給する映像信号線駆動回路と

を備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

20

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号線駆動回路は、

前記複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインと、

前記容量性負荷への印加電圧の極性が反転する時には、前記複数の基準電圧バスラインのうちいずれか1つの基準電圧バスラインに、当該1つの基準電圧バスラインに与えるべき基準電圧に代えて前記共通電極への供給電圧である共通電極信号と同等の電圧レベルを与える電圧切換回路と、

前記各映像信号線に対応して設けられ、各水平走査期間内では、前記複数の基準電圧バスラインのうち前記映像信号に応じた基準電圧の与えられた基準電圧バスラインを選択して対応する映像信号線に接続すると共に、前記容量性負荷への印加電圧の極性が反転する時には、前記1つの基準電圧バスラインを選択して対応する映像信号線に接続する基準電圧選択回路と

を含むことを特徴とする、表示装置。

【請求項6】

40

前記共通電極信号と同等の電圧レベルは、前記共通電極信号であることを特徴とする、請求項4または5に記載の表示装置。

【請求項7】

前記駆動回路は、前記容量性負荷への印加電圧の極性反転に応じて前記共通電極の電位を切り換える共通電極駆動回路を含み、

前記映像信号線駆動回路と前記共通電極駆動回路とは、同一基板上または同一チップ内に形成されたことを特徴とする、請求項4または5に記載の表示装置。

【請求項8】

水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、

50

当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる交流化駆動方式の表示装置における駆動回路であって、

前記第2の電極を基準として前記画像に応じた電圧信号を前記第1の電極に供給する映像信号線駆動回路と、

前記容量性負荷への印加電圧の極性を反転させる時に、前記第1の電極を前記映像信号線駆動回路から電気的に切り離すと共に前記第2の電極に供給される電圧と同等の電圧レベルを提供する電極に短絡させる接続切換回路と、

前記容量性負荷への印加電圧の極性反転に応じて第1の所定電圧と第2の所定電圧を交互に前記第2の電極に与える第2電極駆動回路と

を備え、

10

前記表示装置は、

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記第2電極駆動回路は、前記接続切換回路が前記第1の電極と前記第2の電極に供給される電圧と同等の電圧レベルを提供する電極とを短絡させている期間内に、前記第2の電極としての前記共通電極に供給されている電圧を前記第1の所定電圧と前記第2の所定電圧との間で切り換えることを特徴とする、駆動回路。

30

#### 【請求項9】

前記第2の電極に供給される電圧と同等の電圧レベルを提供する電極は、前記第2の電極としての前記共通電極であることを特徴とする、請求項8に記載の駆動回路。

#### 【請求項10】

水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる交流化駆動方式の表示装置における駆動回路であって、

前記第2の電極を基準として前記画像に応じた電圧信号を前記第1の電極に供給する映像信号線駆動回路を備え、

40

前記表示装置は、

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画

50

素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号線駆動回路は、

複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインと前記共通電極への供給電圧である共通電極信号と同等の電圧レベルが与えられる1つの電圧バスラインとかなる所定数の電圧バスラインと、

前記各映像信号線に対応して設けられ、前記所定数の電圧バスラインのうちいずれか1つの電圧バスラインを選択して対応する映像信号線に接続する電圧選択回路とを含み、

前記各電圧選択回路は、各水平走査期間内では、前記所定数の電圧バスラインのうち前記映像信号に応じた基準電圧の与えられた電圧バスラインを選択して対応する映像信号線に接続し、前記容量性負荷への印加電圧の極性が反転する時には、前記共通電極信号と同等の電圧レベルの与えられた前記1つの電圧バスラインを選択して対応する映像信号線に接続することを特徴とする、駆動回路。

#### 【請求項11】

水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる交流化駆動方式の表示装置における駆動回路であって、

前記第2の電極を基準として前記画像に応じた電圧信号を前記第1の電極に供給する映像信号線駆動回路を備え、

前記表示装置は、

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号線駆動回路は、

前記複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインと、

前記容量性負荷への印加電圧の極性が反転する時には、前記複数の基準電圧バスラインのうちいずれか1つの基準電圧バスラインに、当該1つの基準電圧バスラインに与えるべき基準電圧に代えて前記共通電極への供給電圧である共通電極信号と同等の電圧レベルを与える電圧切換回路と、

前記各映像信号線に対応して設けられ、各水平走査期間内では、前記複数の基準電圧バスラインのうち前記映像信号に応じた基準電圧の与えられた基準電圧バスラインを選択して対応する映像信号線に接続すると共に、前記容量性負荷への印加電圧の極性が反転す

10

20

30

40

50

る時には、前記 1 つの基準電圧バスラインを選択して対応する映像信号線に接続する基準電圧選択回路と

を含むことを特徴とする、駆動回路。

**【請求項 1 2】**

水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第 1 および第 2 の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる交流化駆動方式の表示装置における駆動回路による駆動方法であって、

前記第 2 の電極を基準として前記画像に応じた電圧信号を前記第 1 の電極に供給する映像信号供給ステップと、

前記容量性負荷への印加電圧の極性が反転する時に、前記駆動回路のうち前記電圧信号を前記第 1 の電極に供給する回路部分から前記第 1 の電極を電気的に切り離すと共に、前記第 1 の電極と前記第 2 の電極に供給される電圧と同等の電圧レベルを提供する電極とを短絡させる接続切換ステップと、

前記容量性負荷への印加電圧の極性反転に応じて第 1 の所定電圧と第 2 の所定電圧を交互に第 2 の電極に与える第 2 電極駆動ステップと

を備え、

前記表示装置は、

前記第 1 の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第 2 の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記第 2 電極駆動ステップでは、前記第 1 の電極と前記第 2 の電極に供給される電圧と同等の電圧レベルを提供する電極とが短絡されている期間内に、前記第 2 の電極としての前記共通電極に供給されている電圧が前記第 1 の所定電圧と前記第 2 の所定電圧との間で切り換わることを特徴とする駆動方法。

**【請求項 1 3】**

前記第 2 の電極に供給される電圧と同等の電圧レベルを提供する電極は、前記第 2 の電極としての前記共通電極であることを特徴とする、請求項 1 2 に記載の駆動方法。

**【請求項 1 4】**

水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第 1 および第 2 の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる交流化駆動方式の表示装置における駆動回路による駆動方法であって、

前記第 2 の電極を基準として前記画像に応じた電圧信号を前記第 1 の電極に供給する映像信号供給ステップを備え、

前記表示装置は、

前記第 1 の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

10

20

30

40

50

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、 10

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号供給ステップは、前記各映像信号線に対応して設けられ、複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインと前記共通電極への供給電圧である共通電極信号と同等の電圧レベルが与えられる1つの電圧バスラインとからなる所定数の電圧バスラインのうちいずれか1つの電圧バスラインを選択して対応する映像信号線に接続する電圧選択ステップを含み、

前記各電圧選択ステップでは、各水平走査期間内には、前記所定数の電圧バスラインのうち前記映像信号に応じた基準電圧の与えられた電圧バスラインが選択されて対応する映像信号線に接続され、前記容量性負荷への印加電圧の極性が反転する時には、前記共通電極信号と同等の電圧レベルの与えられた前記1つの電圧バスラインが選択されて対応する映像信号線に接続されることを特徴とする、駆動方法。 20

### 【請求項15】

水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させて周期的に反転させる交流化駆動方式の表示装置における駆動回路による駆動方法であって、

前記第2の電極を基準として前記画像に応じた電圧信号を前記第1の電極に供給する映像信号供給ステップを備え、 30

前記表示装置は、

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、 40

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号供給ステップは、

前記容量性負荷への印加電圧の極性が反転する時には、複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインのうちいずれか1つの基準電圧バスラインに、当該1つの基準電圧バスラインに与えるべき基準電圧に代えて前記共通電極への供給電圧である 50

共通電極信号と同等の電圧レベルを与える電圧切換ステップと、

前記各映像信号線に対応して設けられ、各水平走査期間内には、前記複数の基準電圧バスラインのうち前記映像信号に応じた基準電圧の与えられた基準電圧バスラインを選択して対応する映像信号線に接続し、前記容量性負荷への印加電圧の極性が反転する時には、前記1つの基準電圧バスラインを選択して対応する映像信号線に接続する基準電圧選択ステップと

を含むことを特徴とする、駆動方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

10

本発明は、例えばアクティブマトリクス型液晶表示装置のような容量性負荷の電圧制御型アクティブマトリクス駆動の表示装置に関し、更に詳しくは、そのような表示装置における駆動回路に関する。

【0002】

【従来の技術】

携帯電話や、PDA (Personal Digital Assistant)、ノート型コンピュータ等の携帯用情報機器では、搭載バッテリーの持続時間の長期化の観点から、消費電力の低減化が強く求められている。一方、これらの携帯用情報機器においても処理性能の向上と利用の高度化などによって、より表示色の多い高品位の表示能力が要求されるようになってきている。このため、これらの携帯用情報機器で使用される表示装置においても、高品位の表示能力への要求に対応すべく、従来のパッシブマトリクス型液晶表示装置に代えて薄膜トランジスタ(TFT:Thin Film Transistor)によるアクティブマトリクス型液晶表示装置(以下「TFT-LCD装置」という)が使用されはじめている。

20

【0003】

TFT-LCD装置における液晶パネル(以下「TFT-LCDパネル」という)は、互いに対向する一対の基板(以下「第1および第2の基板」という)を有している。これらの基板は、所定の距離(典型的には数 $\mu m$ )だけ離されて固定されており、液晶材料がこれらの基板間に充填されて液晶層が形成されている。これらの基板のうち少なくとも一方は透明であり、透過型表示を行う場合には、両基板は共に透明であることが必要である。TFT-LCDにおいて、第1の基板上には互いに平行する複数の走査信号線と、走査信号線に対して直交するように交差する複数の映像信号線とが設けられている。走査信号線と映像信号線との各交差部には、画素電極と、画素電極に対応する映像信号線に電気的に接続するためのスイッチング素子である画素TFTとが設けられている。この画素TFTのゲート端子は走査信号線に接続され、ソース端子は映像信号線に接続され、ドレイン端子は上記画素電極に接続されている。

30

【0004】

上記第1の基板に対向する第2の基板上には、全面に対向電極としての共通電極が設けられている。この共通電極には共通電極駆動回路により適切な電圧が与えられる。従って、液晶層には画素電極と共通電極との電位差に相当する電圧が印加される。この印加電圧によって液晶層の光透過率を制御することができるので、映像信号線から適切な電圧が印加されることにより所望の画素表示を行うことができる。

40

【0005】

【特許文献1】

特開平6-337657号公報

【0006】

【発明が解決しようとする課題】

上記のようなTFT-LCDパネルに対しては、液晶の劣化を抑えると共に表示品位を維持するために交流化駆動が行われている。すなわち、液晶への印加電圧の極性が例えば1水平走査期間毎に反転するようにTFT-LCDパネルが駆動される。また、映像信号

50

線の電圧の振幅を抑えるために上記交流化駆動に応じて共通電極の電位を変化させる（以下「共通電極信号の交流化」という）という手法も使用されている。

#### 【0007】

しかし、この共通電極信号の交流化によって映像信号線の電圧の振幅が抑えられたとしても、上記交流化駆動のための極性反転時において映像信号線の電位変化は依然として大きい。したがって、映像信号線駆動回路には、TFT-LCDパネルにおける容量性負荷に対して、このような大きな電位変化を起こさせるのに必要な駆動能力が必要となる。このため、映像信号線駆動回路が消費する電力が大きなものとなり、これがTFT-LCD装置における低消費電力化の阻害要因となっている。

#### 【0008】

そこで本発明では、所定周期で極性を反転しつつ表示画像に応じた電圧を容量性負荷に印加する交流化駆動用の駆動回路の消費電力を低減した表示装置を提供することを目的とする。

#### 【0009】

##### 【課題を解決するための手段】

第1の発明は、水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる駆動回路を備えた表示装置であって、

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路と、

前記第2の電極を基準として前記画像に応じた電圧信号を前記複数の映像信号線に供給する映像信号線駆動回路と、

前記容量性負荷への印加電圧の極性が反転する時には、前記各映像信号線を前記映像信号線駆動回路から電気的に切り離すと共に前記第2の電極に供給される電圧と同等の電圧レベルを提供する電極に短絡させる接続切換回路と、

を備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記駆動回路は、前記容量性負荷への印加電圧の極性反転に応じて第1の所定電圧と第2の所定電圧を交互に前記共通電極に与える共通電極駆動回路を含み、

前記共通電極駆動回路は、前記接続切換回路が前記各映像信号線と前記共通電極に供給される電圧と同等の電圧レベルを提供する電極とを短絡させている期間内に、前記共通電極に供給されている電圧を前記第1の所定電圧と前記第2の所定電圧との間で切り換えることを特徴とする。

#### 【0010】

このような第1の発明によれば、容量性負荷への印加電圧の極性反転の際に、第1の電極は、映像信号線駆動回路から電気的に切り離されて、第2の電極に供給される電圧と同等の電圧レベルを提供する電極に短絡され、容量性負荷に蓄積されていた電荷が放電され

10

20

30

40

50

る。これにより、極性反転後に必要となる第1の電極の電位変化量が小さくなる。したがって、映像信号線駆動回路の駆動能力が従来よりも低くても、容量性負荷に対し従来と同様の電圧を印加することができるので、映像信号線駆動回路の消費電力を低減でき、さらに、映像信号線駆動回路内のバッファ回路を構成するトランジスタのサイズも縮小できる。その結果、表示装置の小型化および低コスト化を図ることができる。

より詳しくは、第1の発明によれば、水平および垂直走査に基づく画像表示において、すなわち所定期間の水平走査を垂直方向に少しずつその走査開始位置をずらしながら繰り返すことによって組み立てられる画像の表示において、容量性負荷への印加電圧の極性は水平走査線が切り換わるときに反転し、その反転時毎に第1の電極としての各映像信号線は、映像信号線駆動回路から電気的に切り離されて、第2の電極としての共通電極に供給される電圧と同等の電圧レベルを提供する電極に短絡され、容量性負荷に蓄積されていた電荷が放電される。これにより、映像信号線駆動回路の消費電力の低減等につき大きな効果が得られる。10

また、第1の発明によれば、短絡期間内に極性反転が行われるので、画素値の書き込みに使用できる時間が長くなる。

#### 【0011】

第2の発明は、第1の発明において、

前記共通電極に供給される電圧と同等の電圧レベルを提供する電極は、前記共通電極であることを特徴とする。20

#### 【0012】

第2の発明によれば、容量性負荷への印加電圧の極性反転の際に、第1の電極としての各映像信号線は映像信号線駆動回路から電気的に切り離されて第2の電極としての共通電極に短絡され、容量性負荷に蓄積されていた電荷が電源を介さずに直接に放電される。これにより、第1の発明と同様、映像信号線駆動回路の消費電力を低減すると共に映像信号線駆動回路内のバッファ回路を縮小化することができるので、表示装置の小型化および低コスト化を図ることができる。20

#### 【0013】

第3の発明は、第1の発明において、

前記映像信号線駆動回路と前記共通電極駆動回路とは、同一基板上または同一チップ内に形成されたことを特徴とする。30

#### 【0014】

第3の発明によれば、映像信号線駆動回路は接続切換回路を介して共通電極駆動回路と関連性を有するので、映像信号線駆動回路と共通電極駆動回路とが同一基板上または同一チップ内に形成されることで、表示装置の構成が簡素化される。

#### 【0015】

第4の発明は、水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる駆動回路を備えた表示装置であって、

前記第1の電極としての複数の映像信号線と、40

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路と、

前記第2の電極を基準として前記画像に応じた電圧信号を前記複数の映像信号線に供給する映像信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、50

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号線駆動回路は、

複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインと前記共通電極への供給電圧である共通電極信号と同等の電圧レベルが与えられる1つの電圧バスラインとかなる所定数の電圧バスラインと、 10

前記各映像信号線に対応して設けられ、前記所定数の電圧バスラインのうちいずれか1つの電圧バスラインを選択して対応する映像信号線に接続する電圧選択回路とを含み、

前記各電圧選択回路は、各水平走査期間内では、前記所定数の電圧バスラインのうち前記映像信号に応じた基準電圧の与えられた電圧バスラインを選択して対応する映像信号線に接続し、前記容量性負荷への印加電圧の極性が反転する時には、前記共通電極信号と同等の電圧レベルの与えられた前記1つの電圧バスラインを選択して対応する映像信号線に接続することを特徴とする。

#### 【0016】

このような第4の発明によれば、共通電極信号を基準電圧の1つとみなして所定数の基準電圧から1つの電圧を選択する回路構成、すなわち上記第1の発明における接続切換回路を電圧選択回路に含めた構成とすることができるので、映像信号線駆動回路の回路構成をコンパクトなものとすることができます。このため、映像信号線駆動回路を実現するICチップのサイズを小さくすることができる。

#### 【0017】

第5の発明は、水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる駆動回路を備えた表示装置であって、 30

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリックス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路と、

前記第2の電極を基準として前記画像に応じた電圧信号を前記複数の映像信号線に供給する映像信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、 40

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号線駆動回路は、

前記複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインと、 50

前記容量性負荷への印加電圧の極性が反転する時には、前記複数の基準電圧バスラインのうちいずれか1つの基準電圧バスラインに、当該1つの基準電圧バスラインに与えるべき基準電圧に代えて前記共通電極への供給電圧である共通電極信号と同等の電圧レベルを与える電圧切換回路と、

前記各映像信号線に対応して設けられ、各水平走査期間内では、前記複数の基準電圧バスラインのうち前記映像信号に応じた基準電圧の与えられた基準電圧バスラインを選択して対応する映像信号線に接続すると共に、前記容量性負荷への印加電圧の極性が反転する時には、前記1つの基準電圧バスラインを選択して対応する映像信号線に接続する基準電圧選択回路とを含むことを特徴とする。

## 【0018】

10

このような第5の発明によれば、1つの切換スイッチ手段としての電圧切換回路が増えるが、1つの基準バスラインとそれに対応する各基準電圧選択回路内の切換スイッチ手段とが基準電圧の選択と共通電極信号と同等の電圧レベルの選択とに共用される。これにより、全体としては第4の発明に比べて信号線駆動回路の回路量が更に低減されるので、信号線駆動回路を実現するICチップのサイズをより小さくすることができる。

## 【0019】

第6の発明は、第4または第5の発明において、

前記共通電極信号と同等の電圧レベルは、前記共通電極信号であることを特徴とする。

## 【0020】

20

第7の発明は、第4または第5の発明において、

前記駆動回路は、前記容量性負荷への印加電圧の極性反転に応じて前記共通電極の電位を切り換える共通電極駆動回路を含み、

前記映像信号線駆動回路と前記共通電極駆動回路とは、同一基板上または同一チップ内に形成されたことを特徴とする。

## 【0021】

このような第7の発明によれば、映像信号線駆動回路は接続切換回路を介して共通電極駆動回路と関連性を有するので、映像信号線駆動回路と共通電極駆動回路とが同一基板上または同一チップ内に形成されることで、表示装置の構成が簡素化される。

## 【0022】

30

第8の発明は、水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる交流化駆動方式の表示装置における駆動回路であって、

前記第2の電極を基準として前記画像に応じた電圧信号を前記第1の電極に供給する映像信号線駆動回路と、

前記容量性負荷への印加電圧の極性を反転させる時に、前記第1の電極を前記映像信号線駆動回路から電気的に切り離すと共に前記第2の電極に供給される電圧と同等の電圧レベルを提供する電極に短絡させる接続切換回路と、

前記容量性負荷への印加電圧の極性反転に応じて第1の所定電圧と第2の所定電圧を交互に前記第2の電極に与える第2電極駆動回路と

40

を備え、

前記表示装置は、

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

50

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記第2電極駆動回路は、前記接続切換回路が前記第1の電極と前記第2の電極に供給される電圧と同等の電圧レベルを提供する電極とを短絡させている期間内に、前記第2の電極としての前記共通電極に供給されている電圧を前記第1の所定電圧と前記第2の所定電圧との間で切り換えることを特徴とする。

10

#### 【0023】

第9の発明は、第8の発明において、

前記第2の電極に供給される電圧と同等の電圧レベルを提供する電極は、前記第2の電極としての前記共通電極であることを特徴とする。

#### 【0024】

第10の発明は、水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる交流化駆動方式の表示装置における駆動回路であって、

20

前記第2の電極を基準として前記画像に応じた電圧信号を前記第1の電極に供給する映像信号線駆動回路を備え、

前記表示装置は、

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

30

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号線駆動回路は、

複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインと前記共通電極への供給電圧である共通電極信号と同等の電圧レベルが与えられる1つの電圧バスラインとかなる所定数の電圧バスラインと、

40

前記各映像信号線に対応して設けられ、前記所定数の電圧バスラインのうちいずれか1つの電圧バスラインを選択して対応する映像信号線に接続する電圧選択回路とを含み、

前記各電圧選択回路は、各水平走査期間内では、前記所定数の電圧バスラインのうち前記映像信号に応じた基準電圧の与えられた電圧バスラインを選択して対応する映像信号線に接続し、前記容量性負荷への印加電圧の極性が反転する時には、前記共通電極信号と同等の電圧レベルの与えられた前記1つの電圧バスラインを選択して対応する映像信号線に接続することを特徴とする。

50

## 【0025】

第11の発明は、水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる交流化駆動方式の表示装置における駆動回路であって、

前記第2の電極を基準として前記画像に応じた電圧信号を前記第1の電極に供給する映像信号線駆動回路を備え、

前記表示装置は、

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

10

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

20

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号線駆動回路は、

前記複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインと、

前記容量性負荷への印加電圧の極性が反転する時には、前記複数の基準電圧バスラインのうちいずれか1つの基準電圧バスラインに、当該1つの基準電圧バスラインに与えるべき基準電圧に代えて前記共通電極への供給電圧である共通電極信号と同等の電圧レベルを与える電圧切換回路と、

前記各映像信号線に対応して設けられ、各水平走査期間内では、前記複数の基準電圧バスラインのうち前記映像信号に応じた基準電圧の与えられた基準電圧バスラインを選択して対応する映像信号線に接続すると共に、前記容量性負荷への印加電圧の極性が反転する時には、前記1つの基準電圧バスラインを選択して対応する映像信号線に接続する基準電圧選択回路とを含むことを特徴とする。

30

## 【0026】

第12の発明は、水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる交流化駆動方式の表示装置による駆動方法であって、

40

前記第2の電極を基準として前記画像に応じた電圧信号を前記第1の電極に供給する映像信号供給ステップと、

前記容量性負荷への印加電圧の極性が反転する時に、前記駆動回路のうち前記電圧信号を前記第1の電極に供給する回路部分から前記第1の電極を電気的に切り離すと共に、前記第1の電極と前記第2の電極に供給される電圧と同等の電圧レベルを提供する電極とを短絡させる接続切換ステップと、

前記容量性負荷への印加電圧の極性反転に応じて第1の所定電圧と第2の所定電圧を交互に第2の電極に与える第2電極駆動ステップとを備え、

前記表示装置は、

50

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記第2電極駆動ステップでは、前記第1の電極と前記第2の電極に供給される電圧と同等の電圧レベルを提供する電極とが短絡されている期間内に、前記第2の電極としての前記共通電極に供給されている電圧が前記第1の所定電圧と前記第2の所定電圧との間で切り換わることを特徴とする。

#### 【0027】

第13の発明は、第12の発明において、

前記第2の電極に供給される電圧と同等の電圧レベルを提供する電極は、前記第2の電極としての前記共通電極であることを特徴とする。

#### 【0028】

第14の発明は、水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第1および第2の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる交流化駆動方式の表示装置における駆動回路による駆動方法であって、

前記第2の電極を基準として前記画像に応じた電圧信号を前記第1の電極に供給する映像信号供給ステップを備え、

前記表示装置は、

前記第1の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第2の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号供給ステップは、前記各映像信号線に対応して設けられ、複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインと前記共通電極への供給電圧である共通電極信号と同等の電圧レベルが与えられる1つの電圧バスラインとからなる所定数の電圧

10

20

30

40

50

バスラインのうちいずれか 1 つの電圧バスラインを選択して対応する映像信号線に接続する電圧選択ステップを含み、

前記各電圧選択ステップでは、各水平走査期間内には、前記所定数の電圧バスラインのうち前記映像信号に応じた基準電圧の与えられた電圧バスラインが選択されて対応する映像信号線に接続され、前記容量性負荷への印加電圧の極性が反転する時には、前記共通電極信号と同等の電圧レベルの与えられた前記 1 つの電圧バスラインが選択されて対応する映像信号線に接続されることを特徴とする。

### 【 0 0 2 9 】

第 15 の発明は、水平および垂直走査に基づき表示すべき画像を示す映像信号としての電圧を、互いに対向する第 1 および第 2 の電極によって形成される容量を含む容量性負荷に印加し、かつ、当該容量性負荷への印加電圧の極性を水平走査線が切り換わる時に反転させることで周期的に反転させる交流化駆動方式の表示装置における駆動回路による駆動方法であって、

前記第 2 の電極を基準として前記画像に応じた電圧信号を前記第 1 の電極に供給する映像信号供給ステップを備え、

前記表示装置は、

前記第 1 の電極としての複数の映像信号線と、

前記複数の映像信号線と交差する複数の走査信号線と、

前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置された複数の画素形成手段と、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路とを備え、

前記各画素形成手段は、

対応する交差点を通過する走査信号線によってオンおよびオフされるスイッチング素子と、

対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成手段に共通的に設けられ、前記容量性負荷に含まれる所定容量が前記画素電極との間に形成されるように配置された前記第 2 の電極としての共通電極とを含み、

前記走査信号線駆動回路は、選択された走査信号線に前記スイッチング素子をオンさせる電圧を印加し、

前記映像信号供給ステップは、

前記容量性負荷への印加電圧の極性が反転する時には、複数の基準電圧がそれぞれ与えられる複数の基準電圧バスラインのうちいずれか 1 つの基準電圧バスラインに、当該 1 つの基準電圧バスラインに与えるべき基準電圧に代えて前記共通電極への供給電圧である共通電極信号と同等の電圧レベルを与える電圧切換ステップと、

前記各映像信号線に対応して設けられ、各水平走査期間内には、前記複数の基準電圧バスラインのうち前記映像信号に応じた基準電圧の与えられた基準電圧バスラインを選択して対応する映像信号線に接続し、前記容量性負荷への印加電圧の極性が反転する時には、前記 1 つの基準電圧バスラインを選択して対応する映像信号線に接続する基準電圧選択ステップとを含むことを特徴とする。

### 【 0 0 3 0 】

#### 【発明の実施の形態】

以下、本発明の実施形態について添付図面を参照して説明する。

< 1 . 第 1 の実施形態 >

< 1 . 1 全体の構成および動作 >

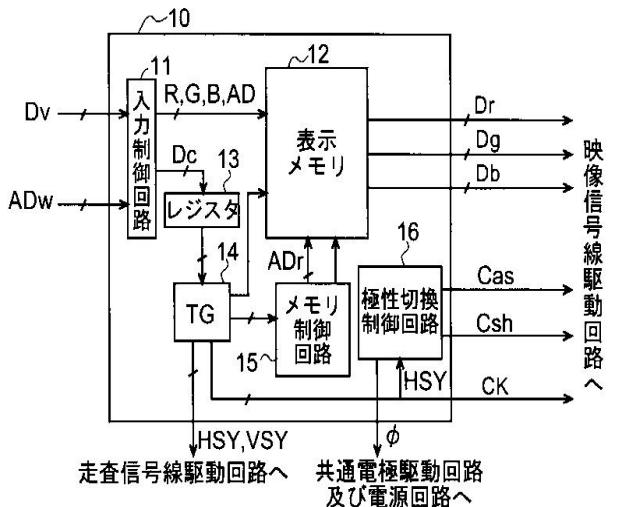

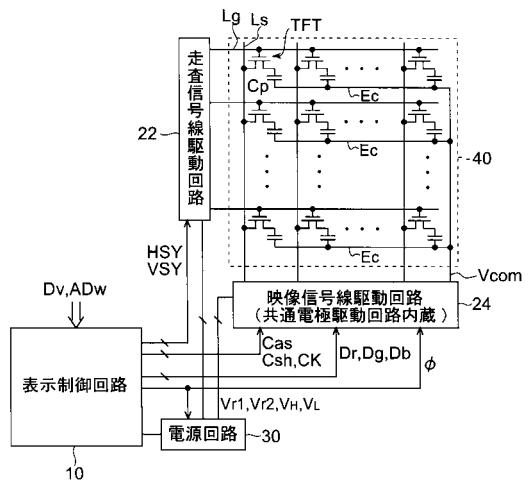

図 1 は、本発明の第 1 の実施形態に係る液晶表示装置の構成を示すブロック図である。この液晶表示装置は、表示制御回路 10 と、映像信号線駆動回路 21 と、走査信号線駆動回路 22 と、共通電極駆動回路 23 と、電源回路 30 と、アクティブマトリクス型液晶パネル 40 とを備えており、液晶の劣化等を抑えるために、液晶層に印加される電圧の極性

10

20

30

40

50

を1水平走査期間毎に反転する交流化駆動を行う。

**【0031】**

この液晶表示装置における表示部としての液晶パネル40は、外部のCPU等から受け取る画像データDvの表す画像における水平走査線にそれぞれが対応する複数本の走査信号線Lgと、それら複数本の走査信号線Lgのそれぞれと交差する複数本の映像信号線Lsと、それら複数本の走査信号線Lgと複数本の映像信号線Lsとの交差点にそれぞれ対応して設けられた複数の画素形成部とを含む。これら複数の画素形成部はマトリクス状に配置され、各画素形成部は、基本的には従来のアクティブマトリクス型液晶パネルにおける構成と同様の構成であって、対応する交差点を通過する映像信号線Lsにソース端子が接続されたスイッチング素子としてのTFTと、そのTFTのドレイン端子に接続された画素電極と、上記複数の画素形成部に共通的に設けられた対向電極である共通電極Ecと、上記複数の画素形成部に共通的に設けられ画素電極と共通電極Ecとの間に挟持された液晶層とからなる。そして、画素電極と共通電極Ecとそれらの間に挟持された液晶層により画素容量Cpが形成される。以下、このような液晶表示装置につき詳述するが、このような液晶表示装置としては、画素電極を形成するTFT基板とは異なる対向基板に共通電極Ecを形成するタイプの液晶表示装置や、対向基板ではなくTFT基板に共通電極Ecを形成するタイプの液晶表示装置などがある。なお以下では、液晶パネル40はn本の映像信号線Lsを備えるものとし、液晶パネル40における表示の階調数は64として説明する。

**【0032】**

本実施形態では、液晶パネル40に表示すべき画像（映像に限らずテキスト、グラフィック等も含む）を表す（狭義の）画像データおよび表示動作のタイミング等を決めるデータである表示制御データ（例えば表示用クロックの周波数を示すデータ）は、外部のCPU等から表示制御回路10に送られる（以下、外部から送られるこれらのデータを「広義の画像データ」といい、符号“Dv”で示すものとする）。すなわち、外部のCPU等は、広義の画像データDvを構成する（狭義の）画像データおよび表示制御データを、アドレス信号ADwを表示制御回路10に供給して、表示制御回路10内の後述の表示メモリおよびレジスタにそれぞれ書き込む。

**【0033】**

表示制御回路10は、レジスタに書き込まれた表示制御データに基づき、表示用のクロック信号CKや、水平同期信号HSY、垂直同期信号VSYを生成し、さらに水平同期信号HSYに基づき、交流化駆動のための極性反転制御信号、短絡制御信号Csh、およびアンプ休止制御信号Casを生成する。また、表示制御回路10は、外部のCPU等によって表示メモリに書き込まれた画像データを読み出して、3種類のデジタル画像信号Dr, Dg, Dbとして出力する。ここで、デジタル画像信号Drは、表示すべき画像の赤色成分を表す画像信号（以下「赤色画像信号」という）であり、デジタル画像信号Dgは、表示すべき画像の緑色成分を表す画像信号（以下「緑色画像信号」という）であり、デジタル画像信号Dbは、表示すべき画像の青色成分を表す画像信号（以下「青色画像信号」という）である。このようにして表示制御回路10によって生成される信号のうち、クロック信号CKは映像信号線駆動回路21に、水平同期信号HSYおよび垂直同期信号VSYは走査信号線駆動回路22に、デジタル画像信号信号Dr, Dg, Db、アンプ休止制御信号Casおよび短絡制御信号Cshは映像信号線駆動回路21に、極性反転制御信号は共通電極駆動回路23および電源回路30に、それぞれ供給される。なお既述のように、本実施形態における画像表示の階調数は64であるものとしているので、3種類のデジタル画像信号Dr, Dg, Dbのそれぞれのビット数は6ビットであり、表示制御回路10から映像信号線駆動回路21にデジタル画像信号Dr, Dg, Dbを供給するための信号線として、 $6 \times 3 = 18$ 本の信号線が配線される。

**【0034】**

電源回路30は、表示制御回路10や、映像信号線駆動回路21、走査信号線駆動回路22、共通電極駆動回路23を動作させるための電源電圧をそれらの回路に供給すると共

10

20

30

40

50

に、液晶パネル40に印加すべき信号を生成するための基準となる電圧である基準電圧を、映像信号線駆動回路21、走査信号線駆動回路22、および共通電極駆動回路23に供給する。ここで、映像信号線駆動回路21に供給される基準電圧Vr1, Vr2のそれぞれの値は、予め設定された2種類の値の間で極性反転制御信号に応じて交互に切り替わり、極性反転制御信号がHレベルのときにはVr1 < Vr2なる所定値となり、極性反転制御信号がLレベルのときにはVr1 > Vr2なる所定値となる。また、共通電極駆動回路23には、基準電圧としてVH > VLなる2種類の電圧VH, VLが供給される。

#### 【0035】

映像信号線駆動回路21には、上記のようにして、液晶パネル40に表示すべき画像を表すデータが画素単位でシリアルにデジタル画像信号Dr, Dg, Dbとして供給されると共に、タイミングを示す信号および制御信号としてのクロック信号CK、アンプ休止制御信号Casおよび短絡制御信号Cshや、基準電圧Vr1, Vr2が供給される。映像信号線駆動回路21は、これらの信号および基準電圧に基づき、液晶パネル40を駆動するための画像信号（以下「映像駆動信号」という）を映像信号線毎に生成し、これを液晶パネル40における対応する映像信号線Lsに印加する。

#### 【0036】

走査信号線駆動回路22は、水平同期信号HSYおよび垂直同期信号VSYに基づき、液晶パネル40における走査信号線Lgを1水平走査期間ずつ交番かつ順次に選択するために各走査信号線Lgに印加すべき走査信号を生成し、全走査信号線Lgのそれぞれを順に選択するためのアクティブな走査信号（TFTをオンさせる電圧）の各走査信号線Lgへの印加を1垂直走査期間を周期として繰り返す。

#### 【0037】

共通電極駆動回路23は、液晶パネル40の共通電極Ecに所定の電位を与えるための共通電極信号Vcomを生成する。本実施形態では、映像信号線Lsの電圧の振幅を抑えるために交流化駆動に応じて共通電極Ecの電位をも変化させている。すなわち、共通電極駆動回路23は、表示制御回路10からの極性反転制御信号に応じて、1水平走査期間毎に2種類の基準電圧VHとVLとの間で交互に切り換わる電圧信号、すなわち、極性反転制御信号がHレベルのときにはVLとなり極性反転制御信号がLレベルのときにはVHとなる電圧信号を生成し（VH > VL）、これを共通電極信号Vcomとして液晶パネル40における共通電極Ecに供給する。これにより、共通電極Ecの電位を基準とする映像信号線Lsの電圧の正負極性を、映像信号線Lsの電圧の振幅を抑えつつ1水平走査期間毎に反転することができる。

#### 【0038】

上記のようにして液晶パネル40において、映像信号線Lsには映像信号線駆動回路21からデジタル画像信号Dr, Dg, Dbに基づく映像駆動信号が供給され、走査信号線Lgには走査信号線駆動回路22から走査信号が供給され、共通電極Ecには共通電極駆動回路23から共通電極信号Vcomが供給される。これにより、液晶層には、デジタル画像信号Dr, Dg, Dbに応じて画素電極と共通電極Ecとの電位差に相当する電圧が印加され、この印加電圧は1水平走査期間毎に極性が反転する。液晶パネル40は、この印加電圧によって液晶層の光透過率を制御することにより、外部のCPU等から受け取った画像データの表すカラー画像を表示する。

#### 【0039】

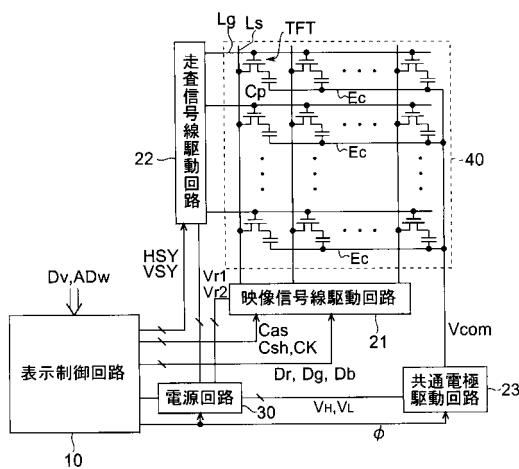

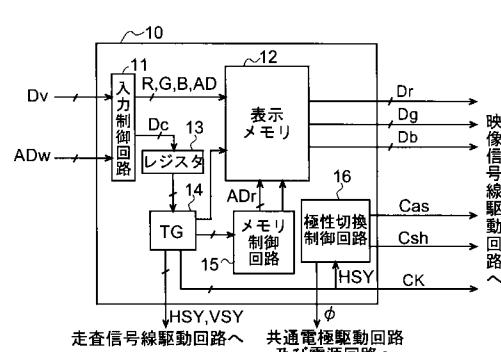

<1.2 表示制御回路>

図2は、上記液晶表示装置における表示制御回路10の構成を示すブロック図である。この表示制御回路10は、入力制御回路11と、表示メモリ12と、レジスタ13と、タイミング発生回路14と、メモリ制御回路15と、極性切換制御回路16とを備えている。

#### 【0040】

この表示制御回路10が外部のCPU等から受け取る広義の画像データDvを示す信号（以下、この信号も符号“Dv”で表すものとする）およびアドレス信号Adwは、入力

10

20

30

40

50

制御回路 11 に入力される。入力制御回路 11 は、アドレス信号 A Dw に基づき、広義の画像データ Dv を、3 種類のカラー画像データ R, G, B と表示制御データ Dc とに振り分ける。そして、カラー画像データ R, G, B を表す信号（以下、これらの信号も符号“R”, “G”, “B”で表すものとする）をアドレス信号 A Dw に基づくアドレス信号 Ad と共に表示メモリ 12 に供給することで、3 種類の画像データ R, G, B を表示メモリ 12 に書き込むと共に、表示制御データ Dc をレジスタ 13 に書き込む。ここで、3 種類の画像データ R, G, B は、画像データ Dv の表す画像の赤色成分、緑色成分、青色成分をそれぞれ表すデータである。表示制御データ Dc は、クロック信号 CK の周波数や画像データ Dv の表す画像を表示するための水平走査期間および垂直走査期間を指定するタイミング情報を含んでいる。

10

#### 【0041】

タイミング発生回路（以下「TG」と略記する）14 は、レジスタ 13 が保持する表示制御データに基づき、クロック信号 CK、水平同期信号 HSY および垂直同期信号 VSY を生成する。また、TG 14 は、表示メモリ 12 およびメモリ制御回路 15 をクロック信号 CK に同期させて動作させるためのタイミング信号を生成する。

#### 【0042】

メモリ制御回路 15 は、外部から入力されて入力制御回路 11 を介して表示メモリ 12 に格納された画像データ R, G, B のうち、液晶パネル 40 に表示すべき画像を表すデータを読み出すためのアドレス信号 Adr と、表示メモリ 12 の動作を制御するための信号とを生成する。これらのアドレス信号 Adr および制御信号は表示メモリ 12 に与えられ、これにより、液晶パネル 40 に表示すべき画像の赤色成分、緑色成分、青色成分を表すデータがそれぞれ赤色画像信号 Dr、緑色画像信号 Dg、青色画像信号 Db として表示メモリ 12 から読み出され、表示制御回路 10 から出力される。これら 3 種類のデジタル画像信号 Dr, Dg, Db は、既述のように映像信号線駆動回路 21 に供給される。

20

#### 【0043】

極性切換制御回路 16 は、TG 14 によって生成された水平同期信号 HSY に基づき、アンプ休止制御信号 Cas および短絡制御信号 Csh を生成する。ここで、アンプ休止制御信号 Cas は、共通電極 Ec の電位を基準とする映像信号線 Ls の電圧の極性を反転させる際（以下「極性反転時」という）に映像信号線駆動回路 21 における後述の各バッファ回路を所定期間だけ休止させるための制御信号であり、短絡制御信号 Csh は、極性反転時に各映像信号線 Ls と共通電極 Ec とを所定期間だけ短絡させるための制御信号である。これらのアンプ休止制御信号 Cas および短絡制御信号 Csh は、既述のように映像信号線駆動回路 21 に供給される。

30

#### 【0044】

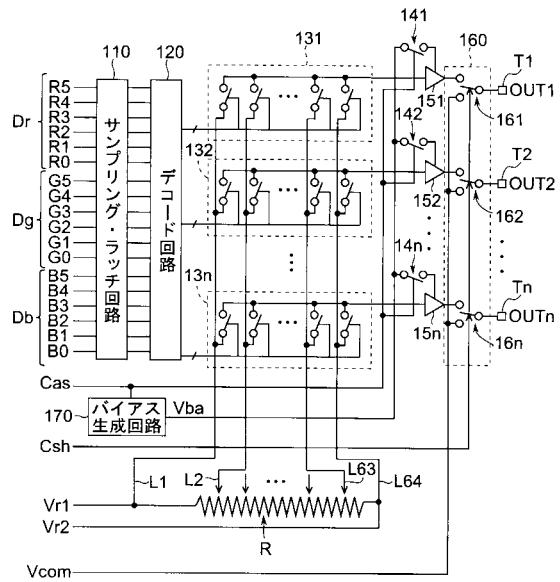

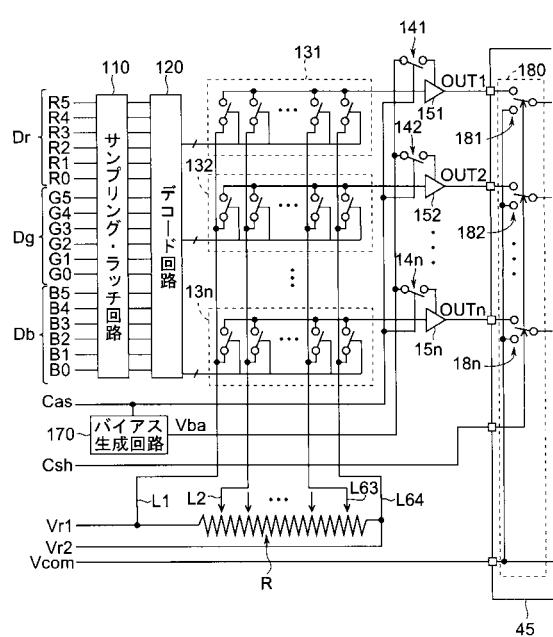

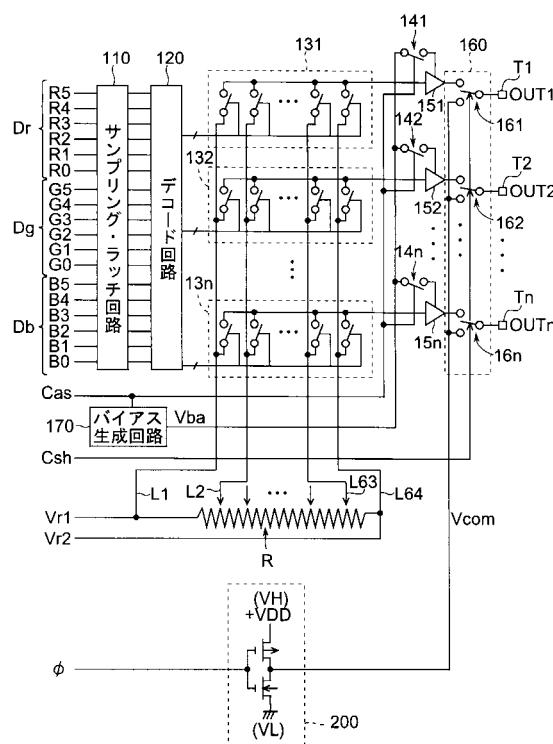

##### <1.3 映像信号線駆動回路>

図 3 は、上記の液晶表示装置における映像信号線駆動回路 21 の構成を示す回路図である。この映像信号線駆動回路 21 は、液晶パネル 40 における複数の映像信号線 Ls のそれぞれに供給すべき映像駆動信号を生成する回路であり、液晶パネル 40 における n 本の映像信号線 Ls に n 種類の映像駆動信号がそれぞれ供給される。この映像信号線駆動回路 21 は、サンプリング・ラッチ回路 110 と、デコード回路 120 と、n 個の基準電圧選択回路 131 ~ 13n と、n 個のバッファ回路 151 ~ 15n と、n 個のオン・オフ・スイッチである休止制御回路 141 ~ 14n と、n 個の切換スイッチ 161 ~ 16n からなる接続切換回路 160 と、各バッファ回路 151 ~ 15n に供給すべきアンプバイアス Vba を生成するバイアス生成回路 170 と、分圧用抵抗 R と、画像表示の階調数に対応する数の基準電圧すなわち 64 種類の基準電圧を各基準電圧選択回路 131 ~ 13n に供給するための 64 本の基準電圧バスライン L1 ~ L64 と、n 本の映像信号線 Ls にそれぞれ接続される n 個の出力端子 T1 ~ Tn とを備えている。

40

#### 【0045】

上記構成の映像信号線駆動回路 21 において、サンプリング・ラッチ回路 110 には、6 ビットの画像信号 R5 ~ R0 からなる赤色画像信号 Dr と、6 ビットの画像信号 G5 ~

50

G 0 からなる緑色画像信号 D g と、6 ビットの画像信号 B 5 ~ B 0 からなる青色画像信号 D b とを表示制御回路 1 0 から受け取り、これらの画像信号 R 5 ~ R 0 , G 5 ~ G 0 , B 5 ~ B 0 をサンプリングしてラッチし、ラッチ後の画像信号を内部画像信号として出力する。これらの内部画像信号は、デコード回路 1 2 0 に入力される。

#### 【 0 0 4 6 】

デコード回路 1 2 0 は、サンプリング・ラッチ回路 1 1 0 からの内部画像信号に基づき、n 本の映像信号線 L s にそれぞれ対応する n 群のデコード出力を生成し、n 群のデコード出力は、n 個の基準電圧選択回路 1 3 1 ~ 1 3 n にそれぞれ入力される。これらの n 群のデコード出力のそれぞれは、6 4 個の信号から構成され、それら 6 4 個の信号のうちいずれか 1 つが上記内部画像信号に応じてアクティブとなり、他の信号は非アクティブとなる。10

#### 【 0 0 4 7 】

分圧用抵抗 R は、一端に第 1 の基準電圧 V r 1 が他端に第 2 の基準電圧 V r 2 がそれぞれ与えられて分圧回路を構成し、この分圧回路は、第 1 および第 2 の基準電圧 V r 1 , V r 2 以外に 6 2 種類の基準電圧を生成する。このようにして生成される 6 2 種類の基準電圧と第 1 および第 2 の基準電圧 V r 1 , V r 2 とからなる 6 4 種類の基準電圧は、6 4 本の基準電圧バスライン L 1 ~ L 6 4 にそれぞれ与えられ、これらの基準電圧バスライン L 1 ~ L 6 4 によって各基準電圧選択回路 1 3 1 ~ 1 3 n に供給される。ここで、6 4 種類の基準電圧のそれぞれは、画像表示の各階調に応じた電圧を画素電極と共に電極 E c との間に印加するために使用される。20

#### 【 0 0 4 8 】

n 個の基準電圧選択回路 1 3 1 ~ 1 3 n は、n 本の映像信号線 L s にそれぞれ対応し、各基準電圧選択回路 1 3 1 ~ 1 3 n は、階調数に等しい個数すなわち 6 4 個のスイッチを含む。各基準電圧選択回路 1 3 1 ~ 1 3 n における 6 4 個のスイッチには、その基準電圧選択回路に入力されるデコード出力を構成する 6 4 個の信号がそれぞれ制御信号として入力される。そして、各スイッチは、それに入力される制御信号がアクティブであればオンし、非アクティブであればオフする。このようなスイッチにより、各基準電圧選択回路 1 3 1 ~ 1 3 n は、それに入力されるデコード出力に応じて、6 4 本の基準電圧バスライン L 1 ~ L 6 4 で供給される 6 4 種類の基準電圧のうちのいずれかを選択し、選択された基準電圧（以下「選択基準電圧」という）を出力する。このようにして n 個の基準電圧選択回路からそれぞれ出力される n 個の選択基準電圧は、n 個のバッファ回路 1 5 1 ~ 1 5 n にそれぞれ入力される。30

#### 【 0 0 4 9 】

各バッファ回路 1 5 1 ~ 1 5 n は、アンプバイアス V b a が供給されている間は、電圧ホロワ、すなわち、入力インピーダンスが極めて高く、且つ出力インピーダンスが極めて低く、電圧利得がほぼ 1 である增幅器として機能し、一方、アンプバイアス V b a の供給が停止されると、休止状態、すなわち、その消費電力は無視できる程度となり、且つその出力は高インピーダンス状態となる。

#### 【 0 0 5 0 】

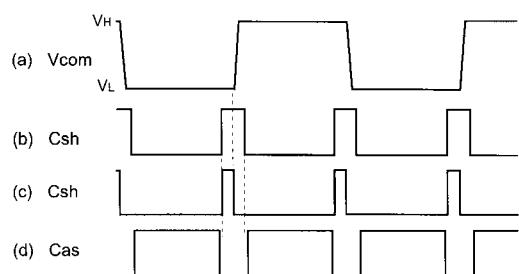

各バッファ回路 1 5 1 ~ 1 5 n には、休止制御回路 1 4 1 ~ 1 4 n が付設され、各休止制御回路 1 4 1 ~ 1 4 n は、それが付設されるバッファ回路 1 5 1 ~ 1 5 n へのアンプバイアス V b a の供給を制御する。すなわち、図 5 ( d ) に示すようなアンプ休止制御信号 C a s が表示制御回路 1 0 から映像信号線駆動回路 2 1 に供給され、各休止制御回路 1 4 1 ~ 1 4 n は、アンプ休止制御信号 C a s が H レベルのときには各バッファ回路 1 5 1 ~ 1 5 n へのアンプバイアス V b a の供給を許容し、アンプ休止制御信号 C a s が L レベルのときにはアンプバイアス V b a の各バッファ回路 1 5 1 ~ 1 5 n へ供給を遮断する。なお、短絡制御信号 C s h が H レベルとなる期間（これは各映像信号線 L s と共に電極 E c とを短絡させる期間に相当する）は、アンプ休止制御信号 C a s が L レベルとなる期間（以下「アンプ休止期間」という）と同一（図 5 ( b ) ）か、または、そのアンプ休止期間に含まれる所定期間となる（図 5 ( c ) ）。したがって、各映像信号線 L s が共通電極 E 4050

cと短絡している時には、バッファ回路151～15nの出力は常に高インピーダンス状態となっている。

#### 【0051】

n個のバッファ回路151～15nの出力信号は、接続切換回路160を構成するn個の切換スイッチ161～16nにそれぞれ入力される。各切換スイッチ161～16nは第1～第3の端子を有し、各切換スイッチ161～16nに入力された上記出力信号は第1の端子に与えられる。また、各切換スイッチ161～16nには、共通電極駆動回路23からの共通電極信号Vcomも入力され、各切換スイッチ161～16nにおける第2の端子に与えられる。切換スイッチ161～16nにおける第3の端子は、映像信号線駆動回路21の出力端子T1～Tnにそれぞれ接続されており、これらn個の出力端子T1～Tnは、液晶パネル40におけるn本の映像信号線Lsにそれぞれ接続される。そして、各切換スイッチ161～16nは、その第3の端子に対し、短絡制御信号CshがLレベルのときには第1の端子を接続し、短絡制御信号CshがHレベルのときには第2の端子を接続する。これにより、短絡制御信号CshがLレベルのときには、各バッファ回路151～15nの出力信号が各映像信号線Lsに供給され、短絡制御信号CshがHレベルのときには、共通電極信号Vcomが各映像信号線Lsに供給される。したがって、短絡制御信号CshがHレベルのときには、共通電極信号Vcomを伝達する信号線と各映像信号線Lsとが短絡されることになる。これは、共通電極Ecと各映像信号線Lsとの短絡を意味する。

#### 【0052】

##### <1.4 共通電極駆動回路>

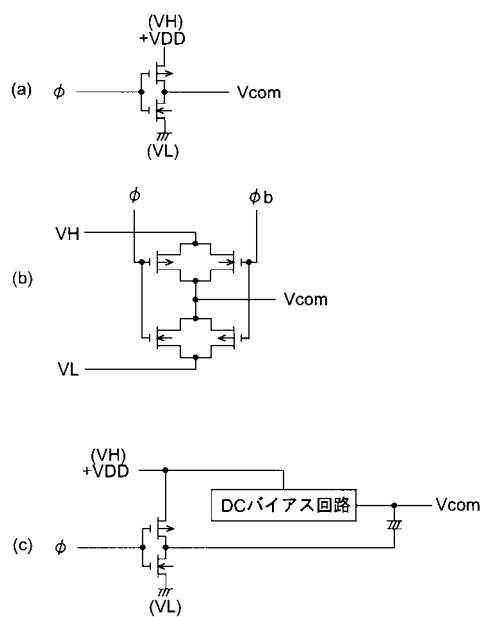

図4は、上記構成の液晶表示装置における共通電極駆動回路23の各種の構成例を示す回路図である。一般に共通電極駆動回路には、高い駆動能力が必要とされることから、通常、自己の消費電力が大きくなるアナログバッファ方式ではなくスイッチ回路を用いた方が採用されている。そこで、図4に示した各構成例も、アナログバッファ方式ではなく、スイッチング素子としてのMOSトランジスタを用いたスイッチ回路方式となっている。

#### 【0053】

第1の構成例では、図4(a)に示すように、共通電極駆動回路はpチャネルMOSトランジスタ(以下「pMOS」という)とnチャネルMOSトランジスタ(以下「nMOS」という)とからなり、両MOSトランジスタのドレイン端子が互いに接続され、pMOSのソース端子は基準電圧VHの与えられる電源ラインVDDに、nMOSのソース端子は基準電圧VLの与えられる接地ラインにそれぞれ接続される。そして、両MOSトランジスタのゲート端子には極性反転制御信号が入力され、互いに接続された両MOSトランジスタのドレイン端子の電圧が共通電極信号Vcomとして出力される。したがって、共通電極信号Vcomは、極性反転制御信号がHレベルのときにはVL(接地レベル)となり、極性反転制御信号がLレベルのときにはVH(所定の正の電源電圧)となる。

#### 【0054】

第2の構成例では、図4(b)に示すように、共通電極駆動回路は、互いに並列に接続されたpMOSとnMOSとからなるアナログスイッチを2個用いて構成され、第1のアナログスイッチの一端には基準電圧VHが、第2のアナログスイッチの一端には基準電圧VLがそれぞれ与えられると共に、両アナログスイッチの他端は互いに接続されている。また、第1のアナログスイッチを構成するpMOSおよび第2のアナログスイッチを構成するnMOSのゲート端子には極性反転制御信号が入力され、第1のアナログスイッチを構成するnMOSおよび第2のアナログスイッチを構成するpMOSのゲート端子には極性反転制御信号の反転信号bが入力される。そして、両アナログスイッチが互いに接続される接続点における電圧が共通電極信号Vcomとして出力される。したがって、この構成例においても、共通電極信号Vcomは、極性反転制御信号がHレベルのときにはVLとなり、極性反転制御信号がLレベルのときにはVHとなる。

#### 【0055】

10

20

30

40

50

第3の構成例では、図4(c)に示すように、共通電極駆動回路は、pMOSとnMOSからなる第1の構成例と同様の回路に加えて、DCバイアス回路と直流遮断用コンデンサとを含み、pMOSおよびnMOSのドレイン端子は、その直流遮断用コンデンサを介してDCバイアス回路の出力端子と接続され、その接続点の電圧が共通電極信号Vcomとして出力される。これにより、共通電極信号Vcomは、第1の構成例と同様の振幅(VH - VL)を維持したままで、DCバイアス回路によってその値が調整されることになる。

#### 【0056】

##### <1.5 液晶パネルの駆動方法>

次に、上記構成の液晶表示装置における液晶パネルの駆動方法について説明する。 10

#### 【0057】

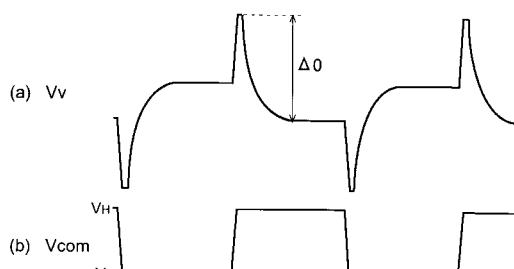

従来の液晶表示装置では、液晶パネルにおける液晶層への印加電圧の極性を1水平走査期間毎に反転する交流化駆動を行うと共に、映像信号線の電圧の振幅を抑えるために共通電極信号も交流化するという駆動方法を採用した場合、液晶パネルにおける映像信号線の電位Vvは図6(a)に示すように変化し、共通電極信号Vcomすなわち共通電極Ecの電位は図6(b)に示すように変化する。ただし、映像信号線の電位Vvは、映像信号線駆動回路と映像信号線との接続点から充分に離れた位置での電位を示すものとする(以下においても同様)。図6(a)に示されているように従来の液晶表示装置において、映像信号線駆動回路は、ノーマリホワイトモードの場合、最大で、黒表示のために液晶層に印加すべき電圧の2倍分だけ映像駆動信号を変化させる必要がある。 20

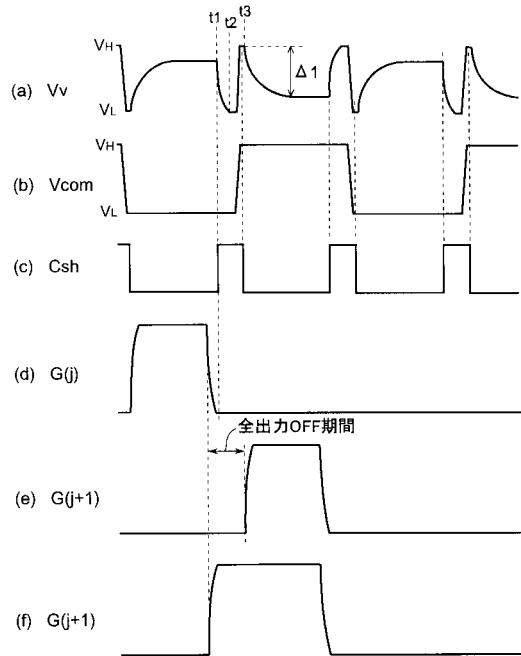

#### 【0058】

これに対し本実施形態では、水平同期信号HSYに基づき図7(c)に示すような短絡制御信号Cshが生成され、共通電極Ecの電位を基準とする映像信号線Lsの電圧の極性を反転させる際に、液晶パネル40における各映像信号線Lsは、その短絡制御信号Cshに基づき、映像信号線駆動回路21から電気的に切り離されると共に共通電極Ecに短絡される。すなわち、1水平期間毎の極性反転時において、その直前に選択されていた走査信号線Lgに印加される走査信号G(j)が非アクティブ(Lレベル)になって、当該走査信号線Lgに接続される全てのTFTがオフした後、例えば時刻t1(図7(a)参照)に短絡制御信号CshがHレベルとなり、液晶パネル40における各映像信号線Lsは、接続切換回路160により、映像信号線駆動回路21から電気的に切り離されて、共通電極信号Vcomを伝達する信号線に接続される。そして、各映像信号線Lsと共通電極Ecとが短絡されている期間(以下「短絡期間」といい、これは短絡制御信号CshがHレベルとなる期間と同一視できる)内に、各映像信号線Lsと共通電極Ecの間に形成される容量による蓄積電荷が放電されて、例えば時刻t2に各映像信号線Lsと共通電極Ecとがほぼ同電位となる。また、図7(b)(c)に示すように、短絡期間内に、共通電極Ecの電位を基準とする映像信号線Lsの電圧の正負極性が極性反転制御信号にに基づき反転する(以下、この正負極性の反転を単に「極性反転」といい、極性反転が行われている期間を「極性反転期間」という)。したがって、短絡期間内に共通電極信号Vcomの値も2種類の基準電圧VLとVHとの間で切り替わる。この共通電極信号Vcomの値の切り替えによって映像信号線Lsの電位Vvも、共通電極信号Vcomの変化分だけ変化する。その後、短絡制御信号CshがHレベルからLレベルへと変化すると、映像信号線駆動回路21内のバッファ回路151~15nが映像信号線にLsに接続される。そして、極性反転期間経過後の例えば時刻t3に、極性反転された映像駆動信号の各映像信号線Lsへの供給が開始され、次に選択される走査信号線Lgに接続されるTFTがオンすると(図7(e)参照)、それらのTFTに接続される画素電極に映像駆動信号が与えられる。 30

#### 【0059】

上記のような駆動方法によれば、液晶パネル40における映像信号線Lsの電位Vvの波形(電圧波形)は、図7(a)に示すようになる。この電圧波形のうち短絡制御信号CshがLレベルの区間の波形は、映像信号線駆動回路21内の出力バッファ回路151~ 40

15nの出力信号に基づく波形である。図7(a)を図6(a)と比較すればわかるように、本実施形態では、液晶層に印加される電圧を実質的に変更することなく、映像信号線駆動回路21内の出力バッファ回路151～15nが変化させるべき映像信号線Lsの電圧振幅を従来に比べて格段に小さくすることができる。すなわち、各映像信号線Lsと共に通電極Ecとを接続切換回路160によって短絡させるという動作(以下、単に「短絡動作」という)により、各映像信号線Lsと共に通電極Ecとがほぼ同電位となるので、映像信号線駆動回路21内のバッファ回路151～15nによる映像信号線Lsの電位Vvの変化量1は、従来の映像信号線駆動回路内のバッファ回路による映像信号線Lsの電位Vvの変化量0(図6(a))のほぼ半分程度となる。

## 【0060】

ここでは、短絡期間内に各映像信号線Lsと共に通電極Ecとはほぼ同電位になることを前提としているが、この前提が成立するためには、液晶パネル40において映像信号線Lsと共に通電極Ecの間に形成される容量の値と映像信号線Lsの抵抗値とに応じて、短絡制御信号CshがHレベルとなる短絡期間(短絡制御信号Cshのパルス幅)を設定する必要がある。ところで、抵抗とコンデンサからなる集中定数回路(積分回路)においてコンデンサに蓄積された電荷を放電させる場合、抵抗値と容量値との乗算値である時定数の3倍の期間が経過すると、コンデンサに初期時に蓄積されていた電荷の約95%が放電される。そこで本実施形態では、短絡期間は、1つの映像信号線Lsにおける配線抵抗値と配線容量値との乗算値である遅延時定数の少なくとも3倍の期間となるように設定されている。なお、実際には、接続切換回路160におけるスイッチのオン抵抗や共通電極駆動回路23におけるインピーダンス等をも考慮して短絡期間を決定する必要があるので、短絡期間の長さを上記遅延時定数の3倍以上とするのが好ましい。

## 【0061】

ところで、液晶パネル40における画素形成部への画素値の書き込み(画素値に相当する電圧による画素容量Cpの充電)のために使用できる時間は、各水平走査期間から短絡期間および極性反転期間を除いた時間である。したがって、上記駆動方法によれば、短絡期間内に極性反転が行われるので、1水平走査期間を固定値とした場合、画素値の書き込みに使用できる時間が長くなるという利点がある。

## 【0062】

なお図5(b)～(d)に示すように、少なくとも短絡期間では、アンプ休止制御信号CasはLレベルであって、全てのバッファ回路151～15nおよびバイアス生成回路170は休止状態となる。

## 【0063】

上記駆動方法では、上記極性切換期間の直後に選択される走査信号線Lgの走査信号G(j+1)がHレベル(アクティブ)となるのは、図7(c)～(e)に示すように、短絡制御信号CshがLレベルとなってからである。したがって、液晶パネル40における全てのTFTがオフのときに、各映像信号線Lsが共通電極Ecと短絡される。しかし、短絡制御信号CshがHレベルの期間(短絡期間)において走査信号G(j+1)がアクティブとなって走査信号G(j+1)を伝達する走査信号線Lgに接続される各TFTがオンし、それらのTFTに接続される画素電極が共通電極Ecに短絡されても、画素容量の充電時定数は映像信号線Lsの充電時定数の数十倍から数百倍であるので、短時間の短絡動作では、それらの画素電極の電位はほとんど変化しない。また、それらの画素電極の電位が変化したとしても、その電位変化は、次に書き込みたい画素値に相当する電位に近づく方向への変化となっている。したがって、図7(f)に示すように、上記極性反転の直後に選択される走査信号線Lgの走査信号G(j+1)は、短絡制御信号CshがLレベルとなる前にHレベルとなるようにしてもよい。

## 【0064】

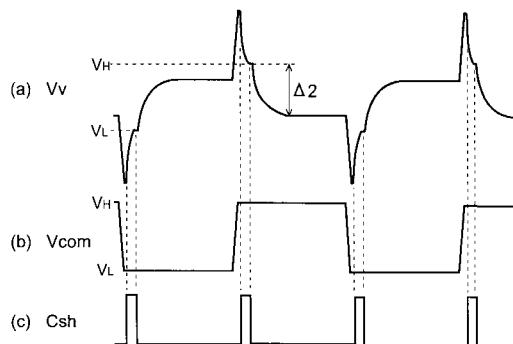

また、上記駆動方法では、短絡期間内に極性反転が行われるが、短絡期間外に極性反転を行ってもよい。例えば短絡期間前に極性反転を行う場合には、映像信号線Lsの電位Vv、共通電極信号Vcom、および短絡制御信号Cshの波形は、図8(a)～(c)に

10

20

30

40

50

示すようになる。この場合においても、映像信号線駆動回路 21 内のバッファ回路 151 ~ 15n による映像信号線 Ls の電位 Vv の変化量 2 は、短絡動作により、従来における映像信号線 Ls の電位変化量 0 (図 6 (a)) のほぼ半分程度であって、格段に小さい。

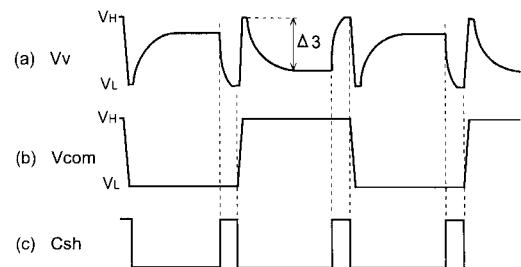

#### 【0065】

さらに、短絡期間後に極性反転を行う場合には、映像信号線 Ls の電位 Vv 、共通電極信号 Vcom および短絡制御信号 Chs の波形は、図 9 (a) ~ (c) に示すようになる。この場合においても、映像信号線駆動回路 21 内のバッファ回路 151 ~ 15n による映像信号線 Ls の電位 Vv の変化量 3 は、短絡動作により、従来における映像信号線 Ls の電位変化量 0 (図 6 (a)) のほぼ半分程度であって、格段に小さい。

10

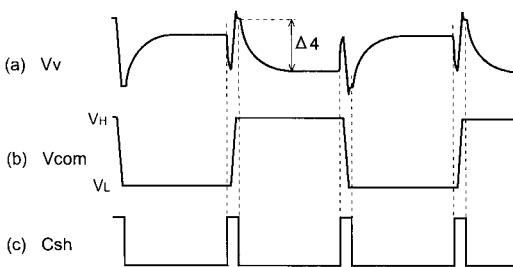

#### 【0066】

更にまた、短絡期間内に極性反転を行う場合であっても、短絡期間が短いために、短絡動作による放電が完了する前にバッファ回路 151 ~ 15n による各映像信号線 Ls の駆動が再開するような場合には、映像信号線 Ls の電位 Vv 、共通電極信号 Vcom 、および短絡制御信号 Chs の波形は、図 10 (a) ~ (c) に示すようになる。この場合、映像信号線駆動回路 21 内のバッファ回路 151 ~ 15n による映像信号線 Ls の電位 Vv の変化量 4 は、従来における映像信号線 Ls の電位変化量 0 (図 6 (a)) の半分よりも大きくなるが、従来の変化量 0 に比べれば格段に小さい。

#### 【0067】

以上のように、映像信号線 Ls と共通電極 Ec を短絡させるタイミング (短絡期間) は、映像信号線 Ls に対し共通電極 Ec を基準として印加される電圧の極性反転時 (極性反転期間) すなわち容量性負荷への印加電圧の極性反転時と完全に一致しなくとも 1 水平走査期間から見て同時と見なせる程度であればよく、また、その程度の同時性の範囲内であれば、それら短絡と極性反転との時間的前後関係も特に問題とはならない。なお、上記実施形態では、極性反転時に映像信号線 Ls と共通電極 Ec を短絡させること、つまり、映像信号線 Ls に共通電極信号 Vcom を供給することを示しているが、本発明は、共通電極信号 Vcom に限定されず、共通電極信号 Vcom と同等の電圧レベルを映像信号線 Ls に供給すればよい。例えば、共通電極駆動回路 23 と同様な回路をもう 1 つ設け、その回路から共通電極信号 Vcom と同等の電圧レベルを映像信号線 Ls に供給してもよい。もちろん、上記実施形態のように、共通電極信号 Vcom と同等の電圧レベルとして共通電極信号 Vcom を用いれば、共通電極駆動回路 23 以外に共通電極信号 Vcom と同等の電圧レベルを作成する回路を設けなくても済む。このことは、以下の実施形態についても同様であり、極性反転時に映像信号線 Ls 等と共通電極 Ec を短絡させること、つまり、映像信号線 Ls 等に共通電極信号 Vcom を供給することを前提として実施形態を記載しているが、共通電極信号 Vcom に限定されず、共通電極信号 Vcom と同等の電圧レベルを映像信号線 Ls 等に供給すればよい。すなわち、極性反転時に映像信号線 Ls 等と短絡させるべき電極は、共通電極 Ec に限定されず、共通電極信号 Vcom と同等の電圧レベルを提供する電極であればよい。

20

#### 【0068】

##### <1.6 効果>

40

上記実施形態では、液晶パネル 40 の交流化駆動のために 1 水平走査期間毎に極性反転が行われるが、その極性反転の際に各映像信号線 Ls は、映像信号線駆動回路 21 内の各バッファ回路 151 ~ 15n から電気的に切り離されると共に共通電極 Ec に短絡される。これにより、各映像信号線 Ls と共通電極 Ec との間に形成される容量による蓄積電荷が放電され、その後に、各映像信号線 Ls が映像信号線駆動回路 21 内の各バッファ回路 151 ~ 15n に再接続される。したがって、各バッファ回路 151 ~ 15n による映像信号線 Ls の電位 Vv の変化量 1 、 2 、 3 または 4 (短絡制御信号 Chs が L レベルのときの変化量) は、従来における映像信号線 Ls の電位変化量 0 に比べて各段に小さくなり、短絡期間内に各映像信号線 Ls と共通電極 Ec とが同電位となる場合には、従来の変化量 0 のほぼ半分となる。すなわち、次の水平走査期間において映像駆動信号

50

が変化すべき変化量（電圧変化）は、ノーマリホワイトモードの場合、従来は最大で黒表示に必要な電圧分の2倍であったが、本実施形態では、最大で黒表示に必要な電圧分でよい。その結果、本実施形態では、映像信号線駆動回路21におけるバッファ回路151～15nとして従来よりも駆動能力の低いバッファ回路を使用しても、液晶パネル40における液晶層に対し従来と同様の電圧を印加することができる。このため、従来よりも駆動能力の低いバッファ回路を使用することにより、映像信号線駆動回路21の消費電力を低減でき、さらに、バッファ回路151～15nを構成するトランジスタのサイズも縮小できるので、映像信号線駆動回路21を実現するICチップのサイズを小さくすることができる。これにより、液晶表示装置の小型化および低コスト化を図ることができる。

## 【0069】

10

なお、液晶パネル40における各映像信号線Lsの配線容量は、各映像信号線Lsに接続される1画素分の容量Cpに比べて充分に大きいので、短絡動作によって駆動能力の低いバッファ回路を使用可能にする上記手法は、短絡動作時において走査信号線Lgがアクティブであるか否かに拘わらず有効である。また、上記のように極性反転後の次の水平走査期間において映像信号線Lsの電位変化量が小さいことは、より一般的には、電源から映像信号線Lsへ供給すべき電流（消費電流）が少なくなることを意味する。すなわち、極性反転時の短絡動作により、映像信号線Lsと共に電極Ecとの間に形成される容量による充電電荷が電源を介さずに直接に放電するので、その直接的な放電に相当する分だけ、電源から映像信号線（映像信号線と共に電極との間の容量）への供給電流が削減され、映像信号線駆動回路21の消費電力が低減されることになる。なお既述のように、極性反転時に映像信号線Lsと共に電極Ecと短絡させる代わりに、共通電極信号Vcomと同等の電圧レベルを提供する他の電極と短絡させてもよいが、この場合には、映像信号線Lsと共に電極Ecとの間の容量による充電電荷を放電させるための電流が所定の回路を介して電源から供給されることもある。しかし、共通電極信号Vcomと同等の電圧レベルは、アナログバッファとして動作するバッファ回路151～15nではなく、共通電極駆動回路23と共にスイッチング素子としてのMOSトランジスタ等によって構成された回路から各映像信号線Lsに供給することができる。したがって、この場合においても、従来の構成に比べ、消費電力を大幅に低減することができる。

20

## 【0070】

30

また、上記実施形態では、短絡期間または短絡期間を含む所定期間は、各バッファ回路151～15nおよびバイアス生成回路170をアンプ休止制御信号Casにより休止させているため、このことも映像信号線駆動回路21の消費電力の低減に寄与する。

## 【0071】

ところで特開平6-337657号公報（特許文献1）には、垂直プランキング期間、映像信号線の出力電位と液晶画素の共通電極の電位とを同電位としたことを特徴とする液晶表示装置が開示されており、この液晶表示装置は、映像信号線の電位と共に電極の電位とを所定期間だけ同電位にすることにより消費電力を低減するという点では、上記実施形態と同様である。しかし、この液晶表示装置では、表示に関係のない垂直プランキング期間に映像信号線と共に電極との間の電位差をなくすことで液晶画素に対する充放電を低減し、これによって無駄な電力消費を抑えているのに対し、上記実施形態では、液晶パネル40の交流化駆動のための極性反転時に映像信号線Lsと共に電極Ecとを短絡する（同電位にする）ことでバッファ回路151～15nに必要とされる駆動能力を低く抑え、これによって信号線駆動回路21の消費電力を低減しており、両者は、消費電力低減という課題を解決するための基本的な考え方において相違する。しかも、上述のように水平走査期間毎に液晶パネル40（液晶層）への印加電圧の極性を反転させるような交流化駆動の場合には、両者は構成において相違するのみならず、消費電力の低減効果の程度において大きく相違し、特許文献1に記載の液晶表示装置では消費電力低減につき大きな効果を得ることはできない。

40

## 【0072】

なお、上記実施形態における共通電極駆動回路23は、スイッチング素子としてのMO

50

Sトランジスタを用いて構成されているので、消費電力が少ないにも拘わらず大きな駆動能力を有しており、上記実施形態のように1水平走査期間毎に各映像信号線Lsと共に共通電極Ecとを短絡させることは、共通電極駆動回路23にとっては負担にはならない。また、上記実施形態のようなアクティブマトリクス型の液晶表示装置においては、走査信号を非アクティブ(TFTがオフする電圧レベル)にした直後は、映像信号線Lsに供給される電圧レベルは液晶パネル40による表示に影響を与えないもので、上記の短絡動作は表示上問題となることはない。

#### 【0073】

##### <2. 第2の実施形態>

図11は、本発明の第2の実施形態に係る液晶表示装置における映像信号線駆動回路の構成を、液晶パネル45における映像信号線Lsへの信号供給部分の構成と共に示す回路図である。本実施形態に係る液晶表示装置では、上記第1の実施形態とは異なり、各映像信号線Lsを共通電極Ecに短絡させる接続切換回路180が液晶パネル45に内蔵されており、映像信号線駆動回路は接続切換回路160を含まない。すなわち、映像信号線駆動回路からは、バッファ回路151～15nの出力信号がOUT1～OUTnとして出力され、液晶パネル45内の接続切換回路180に入力される。また、短絡制御信号Cshおよび共通電極信号Vcomも、この接続切換回路180に入力される。この接続切換回路180は、第1の実施形態における接続切換回路160と同様、n個の切換スイッチ181～18nから構成され、映像信号線駆動回路からのn個の出力信号OUT1～OUTnは、これらの切換スイッチ181～18nにそれぞれ入力される。各切換スイッチ181～18nは第1～第3の端子を有し、各切換スイッチ181～18nに入力された出力信号OUT1～OUTnは、第1の端子に与えられる。各切換スイッチ181～18nにおける第2の端子には、共通電極駆動回路23からの共通電極信号Vcomが与えられる。切換スイッチ181～18nにおける第3の端子には、液晶パネル45における映像信号線Lsが接続される。そして、各切換スイッチ181～18nは、その第3の端子に対し、短絡制御信号CshがLレベルのときには第1の端子を接続し、短絡制御信号CshがHレベルのときには第2の端子を接続する。これにより、短絡制御信号CshがLレベルのときには、映像信号線駆動回路における各バッファ回路151～15nの出力信号OUT1～OUTnが各映像信号線Lsに供給され、短絡制御信号CshがHレベルのときには、共通電極信号Vcomが各映像信号線Lsに供給される。したがって、短絡制御信号CshがHレベルのときには、共通電極Ecと各映像信号線Lsとが短絡することになる。本実施形態における上記以外の構成については第1の実施形態と同様であるので、同一部分には同一の参照符号を付して説明を省略する。また、液晶パネルの駆動方法についても、本実施形態は第1の実施形態と同様であるので説明を省略する。

#### 【0074】

上記のような本実施形態においても、第1の実施形態と同様、液晶パネル45の交流化駆動のための極性反転の際に、液晶パネル45における各映像信号線Lsは、映像信号線駆動回路内の各バッファ回路151～15nから電気的に切り離されると共に共通電極Ecに短絡される。これにより、映像信号線駆動回路におけるバッファ回路151～15nとして従来よりも駆動能力の低いバッファ回路を使用しても、液晶パネル45における液晶層に対し従来と同様の電圧を印加することができる。したがって本実施形態によれば、従来よりも駆動能力の低いバッファ回路を使用することにより、映像信号線駆動回路の消費電力を低減でき、さらに、バッファ回路151～15nを構成するトランジスタのサイズも縮小できる。その結果、液晶表示装置の小型化および低コスト化を図ることができる。

#### 【0075】

##### <3. 第3の実施形態>

図12は、本発明の第3の実施形態に係る液晶表示装置の構成を示すブロック図である。この液晶表示装置では、図1に示した第1の実施形態に係る液晶表示装置における共通電極駆動回路23と同等の回路が、映像信号線駆動回路24に内蔵されている。したがつ

10

20

30

40

50

て本実施形態では、共通電極信号  $V_{com}$  を生成するための基準電圧  $V_H$ 、 $V_L$  および極性反転制御信号  $H$  は、映像信号線駆動回路 24 に供給され、共通電極信号  $V_{com}$  は、映像信号線駆動回路 24 から液晶パネル 40 の共通電極  $E_c$  に与えられる。図 13 は、この映像信号線駆動回路 24 の構成を示す回路図である。この映像信号線駆動回路 24 は、図 4(a) に示した既述の回路と同一構成の共通電極駆動回路 200 を内蔵しているが、その他の構成は第 1 の実施形態と同様であるので、同一部分には同一の参照符号を付して説明を省略する。また、液晶パネル 40 の駆動方法についても、本実施形態は第 1 の実施形態と同様であるので説明を省略する。なお、映像信号線駆動回路 24 は共通電極駆動回路 200 を内蔵しているので、その共通電極駆動回路 200 の出力信号が共通電極信号  $V_{com}$  として、接続切換回路 160 における各切換スイッチ 161 ~ 16n の第 2 の端子に与えられる。10

#### 【0076】

上記のような本実施形態においても、第 1 の実施形態と同様、液晶パネル 40 の交流化駆動のための極性反転の際に、液晶パネル 40 における各映像信号線  $L_s$  は、映像信号線駆動回路 24 内の各バッファ回路 151 ~ 15n から電気的に切り離されると共に共通電極  $E_c$  に短絡される。これにより、映像信号線駆動回路 24 におけるバッファ回路 151 ~ 15n として従来よりも駆動能力の低いバッファ回路を使用しても、液晶パネル 40 における液晶層に対し従来と同様の電圧を印加することができる。したがって本実施形態によれば、従来よりも駆動能力の低いバッファ回路を使用することにより、映像信号線駆動回路 24 の消費電力を低減でき、さらに、バッファ回路 151 ~ 15n を構成するトランジスタのサイズも縮小できる。その結果、液晶表示装置の小型化および低コスト化を図ることができる。20

#### 【0077】

また、第 1 および第 2 の実施形態や本実施形態のように、液晶パネルの交流化駆動のための極性反転の際にバッファ回路の出力信号に代えて共通電極信号  $V_{com}$  が映像信号線  $L_s$  に供給される場合には、上記のように共通電極駆動回路を映像信号線駆動回路に内蔵して 1 チップ化することにより、液晶表示装置の構成が簡素化される。なお、映像信号線駆動回路と共に共通電極駆動回路とを I C チップとして 1 チップ化する場合のみならず、液晶パネルを構成する同一基板上に映像信号線駆動回路と共に共通電極駆動回路とを形成する場合においても、同様の利点が得られる。30

#### 【0078】

##### <4. 第 4 の実施形態>

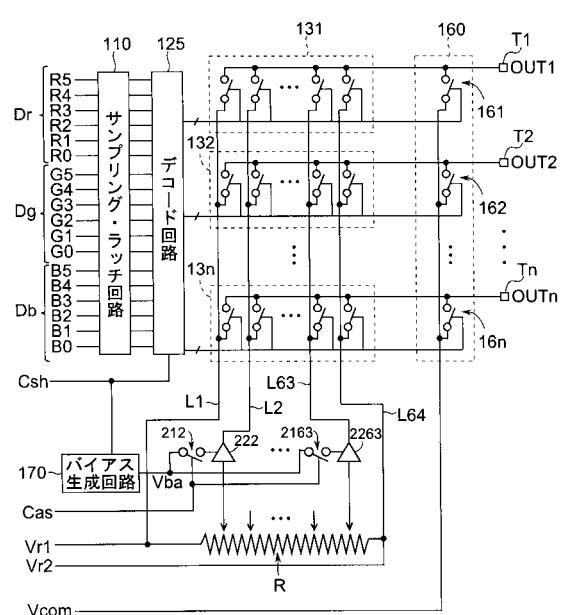

図 14 は、本発明の第 4 の実施形態に係る液晶表示装置における映像信号線駆動回路の構成を示す回路図である。本実施形態に係る液晶表示装置では、上記第 1 の実施形態とは異なり、映像信号線駆動回路において基準電圧選択回路 131 ~ 13n と接続切換回路 160 との間にバッファ回路 151 ~ 15n を設ける代わりに、抵抗  $R$  を用いて構成される分圧回路と、その分圧回路によって生成される 62 種類の基準電圧を伝達するための 62 本の基準電圧バスライン  $L_2$  ~  $L_{63}$  との間に、62 個のバッファ回路 222 ~ 2263 がそれぞれ配置されている。そして、各バッファ回路 222 ~ 2263 には、オン - オフ・スイッチが休止制御回路 212 ~ 2163 として付設され、各休止制御回路 212 ~ 2163 は、図 5(d) に示すようなアンプ休止制御信号  $C_{as}$  に基づき各バッファ回路 222 ~ 2263 へのアンプバイアス  $V_{ba}$  の供給を制御する。また、本実施形態では、短絡制御信号  $C_{sh}$  はデコード回路 125 に入力され、このデコード回路 125 は、短絡制御信号  $C_{sh}$  とサンプリング・ラッチ回路 110 からの内部画像信号とに基づき、n 本の映像信号線  $L_s$  にそれぞれ対応する n 群のデコード出力を生成する。本実施形態における上記以外の構成については第 1 の実施形態と同様であるので、同一部分には同一の参照符号を付して説明を省略する。また、液晶パネル 40 の駆動方法についても、本実施形態は第 1 の実施形態と同様であるので説明を省略する。40

#### 【0079】

上記構成における各バッファ回路 222 ~ 2263 は、アンプバイアス  $V_{ba}$  が供給さ50

れている間は、入力インピーダンスが極めて高く、かつ出力インピーダンスが極めて低く、電圧利得がほぼ 1 である増幅器、すなわち電圧ホロワとして機能し、一方、アンプバイアス V<sub>b</sub> の供給が停止されると、休止状態、すなわち、その消費電力が無視できる程度となり、且つその出力が高インピーダンス状態となる。なお、第 1 および第 2 の基準電圧 V<sub>r1</sub>, V<sub>r2</sub> は電源回路 30 から供給されるので、これらの基準電圧 V<sub>r1</sub>, V<sub>r2</sub> は、バッファ回路を介することなく基準電圧バスライン L1, L64 にそれぞれ与えられる。また、上記構成の映像信号線駆動回路では、基準電圧選択回路 131 ~ 13n と接続切換回路 160との間にはバッファ回路が存在しないので、基準電圧選択回路 131 ~ 13n から出力される選択基準電圧は、接続切換回路 160 における切換スイッチ 161 ~ 16n の第 1 の端子に与えられる。

10

#### 【0080】

上記構成において、デコード回路 125 からの n 群のデコード出力のそれぞれは、65 個（階調数 + 1 個）の信号から構成され、それらのうち 64 個の信号は、基準電圧選択回路 131 ~ 13n に入力され、短絡制御信号 Csh が L レベルのときには、第 1 の実施形態と同様、それら 64 個の信号のうちいずれか 1 つのみが上記内部画像信号に応じてアクティブとなる。n 群のデコード出力のそれぞれにおける残りの 1 つの信号は、接続切換回路 160 における切換スイッチ 161 ~ 16n に入力される。ここで、切換スイッチ 161 ~ 16n に入力されるデコード出力の信号は、短絡制御信号 Csh が L レベルのときには非アクティブとなり、短絡制御信号 Csh が H レベルのときにはアクティブとなる。また、短絡制御信号 Csh が H レベルのとき、n 群のデコード出力のうち基準電圧選択回路 131 ~ 13n に入力される信号は全て非アクティブとなる。したがって、短絡制御信号 Csh が L レベルのときには、サンプリング・ラッチ回路 110 からの内部画像信号に応じて基準電圧選択回路 131 ~ 13n から出力される選択基準電圧が、出力信号 OUT1 ~ OUTn として映像信号線駆動回路から出力されて液晶パネル 40 の映像信号線 Ls に供給され、一方、短絡制御信号 Csh が H レベルのときには、共通電極信号 Vcom が液晶パネル 40 の各映像信号線 Ls に供給される。これは、短絡制御信号 Csh が H レベルのときに共通電極 Ec と各映像信号線 Ls とが短絡されることを意味する。なお、このような映像信号線駆動回路では、基準電圧選択回路が接続切換回路 160 を含み、その基準電圧選択回路において、階調数に対応する 64 種類の基準電圧と共通電極信号 Vcom の電圧とからなる 65 種類の電圧から映像信号線毎に 1 つの電圧が選択され、選択された電圧が出力信号 OUT1 ~ OUTn として出力される、と見なすこともできる。

20

#### 【0081】

上記のような本実施形態においても、第 1 の実施形態と同様、液晶パネル 40 の交流化駆動のための極性反転の際に、液晶パネル 40 における各映像信号線 Ls は、映像信号線駆動回路内の各基準電圧選択回路 131 ~ 13n および各バッファ回路 222 ~ 2263 から電気的に切り離されると共に共通電極 Ec に短絡される。これにより、映像信号線駆動回路におけるバッファ回路 222 ~ 2263 として駆動能力の低いバッファ回路を使用しても、液晶パネル 40 における液晶層に対し従来と同様の電圧を印加することができる。したがって本実施形態によれば、従来よりも駆動能力の低いバッファ回路を使用することにより、映像信号線駆動回路の消費電力を低減でき、さらに、バッファ回路 222 ~ 2263 を構成するトランジスタのサイズも縮小できる。その結果、液晶表示装置の小型化および低コスト化を図ることができる。また、第 1 の実施形態と同様、短絡期間または短絡期間を含む所定期間は、各バッファ回路 222 ~ 2263 およびバイアス生成回路 170 はアンプ休止制御信号 Cas により休止状態となるため（図 5 参照）、このことも映像信号線駆動回路の消費電力の低減に寄与する。

30

#### 【0082】

上記に加えて、本実施形態では、共通電極信号 Vcom を基準電圧の 1 つとみなして 65 種類の基準電圧から 1 つの電圧を選択する回路構成、すなわち接続切換回路 160 を基準電圧選択回路に含めた構成とすることができますので、図 3 に示したように基準電圧選択回路 131 ~ 13n としてのスイッチ群とバッファ回路 151 ~ 15n と接続切換回路 1

40

50

60としてのスイッチ群とを順に配置した構成に比べ、映像信号線駆動回路の回路構成をコンパクトなものとすることができます。このため本実施形態によれば、第1の実施形態と同様の効果を奏する映像信号線駆動回路をよりサイズの小さいICチップとして実現することができ、その結果、更に液晶表示装置の小型化および低コスト化を図ることができる。

#### 【0083】

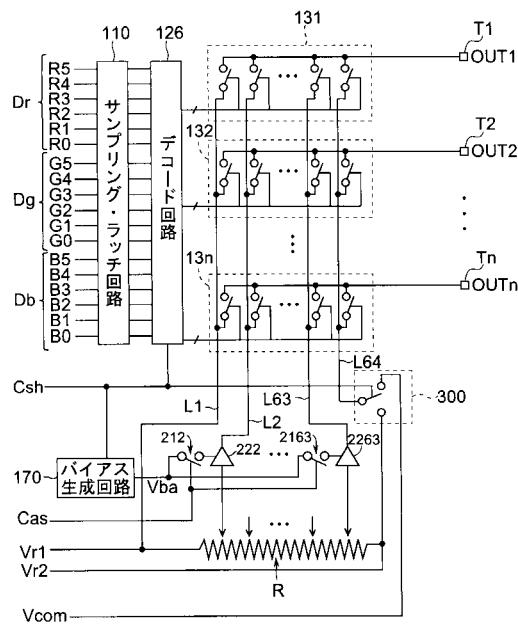

<5. 第5の実施形態>

図15は、本発明の第5の実施形態に係る液晶表示装置における映像信号線駆動回路の構成を示す回路図である。本実施形態に係る液晶表示装置は、上記第4の実施形態に係る映像信号線駆動回路において出力部に設けられた接続切換回路160に代えて、1個の切換スイッチからなる電圧切換回路300を備えており、外部の電源回路から供給される基準電圧V<sub>r2</sub>は、この電圧切換回路300を介して基準電圧バスラインL64に与えられる。そして、この電圧切換回路300には、その切換動作を制御する信号として短絡制御信号Cshが入力される。本実施形態におけるその他の構成は上記第4の実施形態と基本的に同様であるので、同一部分には同一の参照符号を付して説明を省略する。また、液晶パネル40の駆動方法についても、本実施形態は第1の実施形態等と同様であるので説明を省略する。

#### 【0084】

本実施形態に係る映像信号線駆動回路において、デコード回路126は、第4の実施形態におけるデコード回路125とほぼ同様であるが、短絡制御信号CshがHレベルのときの動作が異なる。すなわち、短絡制御信号CshがHレベルのとき、第4の実施形態では、基準電圧選択回路131～13nに入力される全てのデコード出力信号は非アクティブとなるが、本実施形態では、基準電圧選択回路131～13nにおけるスイッチのうち基準電圧バスラインL64の接続されるスイッチに入力されるデコード出力信号のみ、アクティブとなる。

#### 【0085】

また、本実施形態に係る映像信号線駆動回路において、電圧切換回路300は、第1～第3の端子を有し、第1の端子には基準電圧バスラインL64が接続され、第2の端子には基準電圧V<sub>r2</sub>が与えられ、第3の端子には共通電極信号Vcomが与えられる。そして電圧切換回路300は、短絡制御信号CshがLレベルのときには第1の端子を第2の端子に接続し、短絡制御信号CshがHレベルのときには第1の端子を第3の端子に接続する。これにより、基準電圧バスラインL64に対し、短絡制御信号CshがLレベルのときには基準電圧V<sub>r2</sub>が与えられ、短絡制御信号CshがHレベルのときには共通電極信号Vcomが与えられる。

#### 【0086】

したがって、短絡制御信号CshがLレベルのときには、サンプリング・ラッチ回路110からの内部画像信号に応じて基準電圧選択回路131～13nから出力される選択基準電圧が、出力信号OUT1～OUTnとして映像信号線駆動回路から出力されて液晶パネル40の映像信号線Lsに供給される。一方、短絡制御信号CshがHレベルのときには、共通電極信号Vcomが基準電圧選択回路131～13nを介して液晶パネル40の各映像信号線Lsに供給される。これは、短絡制御信号CshがHレベルのときに共通電極Ecと各映像信号線Lsとが短絡されることを意味する。

#### 【0087】

上記のような本実施形態においても、第4の実施形態と同様の効果が得られる。すなわち、映像信号線駆動回路におけるバッファ回路222～2263として駆動能力の低いバッファ回路を使用しても、液晶パネル40における液晶層に対し従来と同様の電圧を印加することができるので、映像信号線駆動回路の消費電力を低減でき、さらに、バッファ回路222～2263を構成するトランジスタのサイズも縮小できる。その結果、液晶表示装置の小型化および低コスト化を図ることができる。また、短絡期間または短絡期間を含む所定期間は、各バッファ回路222～2263およびバイアス生成回路170はアンプ

10

20

30

40

50

休止制御信号 C a s により休止状態となるため(図5参照)、このことも映像信号線駆動回路の消費電力の低減に寄与する。更に、第1の実施形態等に比べて必要なバッファ回路の個数が少なくなるという利点もある。

#### 【0088】

また、本実施形態では、64本の基準電圧バスラインのうち1本のバスライン L 64 が基準電圧 V r 2 の伝達と共に共通電極信号 V c o m の伝達と共に共用され、かつ、上記の他の実施形態における接続切換回路 160 の代わりに各基準電圧選択回路 131 ~ 13n における 1 つのスイッチが使用される。この構成では、n 個の切換スイッチ 161 ~ 16n からなる接続切換回路 160 によって短絡動作を行う場合に比べて、オン抵抗の小さい 1 個のスイッチが電圧切換回路 300 として必要となるが、接続切換回路 160 は不要となり、制御用の信号線を多数配線する必要がなくなる。このため、本実施形態によれば、上記効果に加えて、映像信号線駆動回路を実現する I C チップのサイズをより縮小できるという効果も得られる。10

#### 【0089】

##### < 6 . 第6の実施形態 >

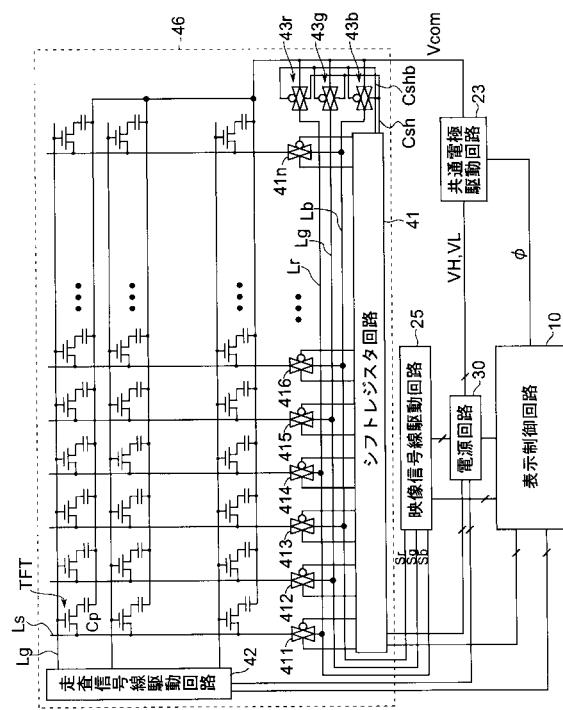

図16は、本発明の第6の実施形態に係る液晶表示装置の構成を回路図とブロック図との組み合わせによって示している。なお、以下では、上記他の実施形態と同様の構成要素および信号には同一の参照符号を付して詳しい説明を省略する。

#### 【0090】

本実施形態に係る液晶表示装置は、アナログドライバ方式の表示装置であって、第1の実施形態におけるものと同様の構成の表示制御回路 10 、共通電極駆動回路 23 、および電源回路 30 を備えているが、映像信号線駆動回路 25 および液晶パネル 46 の構成が第1の実施形態と相違する。20

#### 【0091】

映像信号線駆動回路 25 は、表示すべき画像の赤色成分を表すアナログ信号である赤色画像信号 S r と、表示すべき画像の緑色成分を表すアナログ信号である緑色画像信号 S g と、表示すべき画像の青色成分を表すアナログ信号である青色画像信号 S b とからなるアナログ映像信号を生成する。このアナログ映像信号 S r , S g , S b は、液晶パネル 46 を交流化駆動するために 1 水平期間毎に極性が反転される信号である。

#### 【0092】

液晶パネル 46 は、多結晶シリコンを用いた TFT をスイッチング素子とするアクティブマトリクス型の表示パネルであって、互いに対向する一対の基板(以下、第1および第2の基板という)を有している。これらの基板は、所定の距離(典型的には数  $\mu\text{m}$ )だけ離されて固定されており、液晶材料がこれらの基板間に充填されて液晶層が形成されている。これらの基板のうち少なくとも一方は透明である。液晶パネル 46 における第1の基板上には、複数の映像信号線 L s (以下では映像信号線 L s の数を n とする)と複数の走査信号線 L g とが格子状に配置されると共に、それら映像信号線 L s と走査信号線 L g との交差部にそれぞれ対応して複数の画素形成部がマトリクス状に配置されることで表示部が形成されている。各画素形成部は、ソース端子が映像信号線 L s にゲート端子が走査信号線 L g にそれぞれ接続された TFT と、その TFT のドレイン端子に接続された画素電極と、全ての画素形成部に共通的に設けられて画素電極との間に容量 C p が形成されるよう第2の基板の全面に形成された対向電極である共通電極と、全ての画素形成部に共通的に設けられて画素電極と共通電極との間に挿持される上記液晶層とから構成される。これに加えて、液晶パネル 46 における第1の基板上には、上記複数の走査信号線 L g に走査信号を供給する走査信号線駆動回路 42 と、映像信号線駆動回路 25 からのアナログ映像信号 S r , S g , S b をそれぞれ伝達するための映像信号バスライン L r , L g , L b と、これらの映像信号バスライン L r , L g , L b で伝達されるアナログ映像信号 S r , S g , S b をサンプリングして上記複数の映像信号線 L s に供給するための n 個のアナログスイッチ 411 ~ 41n からなるサンプリング回路と、このサンプリング回路を制御するシフトレジスタ回路 41 と、映像信号バスライン L r , L g , L b を極性反転の際に共4050

通電極に短絡するための接続切換回路とが形成されている。このようにして、液晶パネル46には、マトリクス状に配置された複数の画素形成部と格子状に形成された映像信号線Lsおよび走査信号線Lgと駆動回路の一部とが一体的に形成されている。

#### 【0093】

上記構成の液晶パネルにおいて、シフトレジスタ回路41は、1水平走査期間の間に1つのパルスを入力端から出力端へと順次転送すると共に、上記パルスが出力端に到達する毎に所定期間だけHレベルとなる信号すなわち極性反転の際に所定期間だけHレベルとなる信号である短絡制御信号Cshと、その論理レベルを反転させた信号である短絡制御反転信号Cshbとを生成する。

#### 【0094】

サンプリング回路を構成するn個のアナログスイッチ411～41nは、シフトレジスタ回路41によって転送されるパルスによって順次オンされ、このオン動作により、映像信号バスラインLr,Lg,Lb上のアナログ映像信号Sr,Sg,Sbが映像信号線Lsに供給されて、走査信号線駆動回路42によってオンされたTFTを介して画素電極に与えられる。

#### 【0095】

接続切換回路は、映像信号バスラインLr,Lg,Lbにそれぞれ対応して設けられ、映像信号バスラインLr,Lg,Lbと共に通電極信号Vcomを伝達する信号線との間にそれぞれ挿入された3個のアナログスイッチ43r,43g,43bから構成される。これらのアナログスイッチ43r,43g,43bには、上記の短絡制御信号Cshおよび短絡制御反転信号Cshbが制御信号として入力される。これにより、短絡制御信号CshがHレベルの期間のみ映像信号バスラインLr,Lg,Lbに共通電極信号Vcomが供給される。これは、短絡制御信号CshがHレベルのとき（極性反転時の所定期間だけ）映像信号バスラインLr,Lg,Lbが共通電極に短絡されることを意味する。

#### 【0096】

前述のように、映像信号線駆動回路25は、液晶パネル46における映像信号バスラインLr,Lg,Lbに対し、1水平期間毎に極性が反転するアナログ映像信号Sr,Sg,Sbを供給する。ただし、少なくとも短絡期間においては、例えば映像信号線駆動回路25内のバッファ回路の出力を高インピーダンス状態にすることにより、映像信号線駆動回路25が映像信号バスラインLr,Lg,Lbから電気的に切り離されるように構成されている。ところで、映像信号バスラインLr,Lg,Lbは第1の基板に形成され、共通電極は第2の基板の全面に形成されていることから、図示されていないが、映像信号バスラインLr,Lg,Lbと共に通電極との間には容量が形成されている。したがって、映像信号線駆動回路25は、一定周期で極性の反転する信号を容量性負荷に供給して当該容量性負荷を駆動するという点では、上記の他の実施形態における信号線駆動回路と同様である。

#### 【0097】

本実施形態では、前述のように、3個のアナログスイッチ43r,43g,43bからなる接続切換回路により、映像信号バスラインLr,Lg,Lbに与えられるべきアナログ映像信号Sr,Sg,Sbの極性が反転する毎に所定期間（短絡制御信号CshがHレベルの期間）だけ、各映像信号バスラインLr,Lg,Lbが共通電極に短絡され、このとき映像信号線駆動回路25は、各映像信号バスラインLr,Lg,Lbから電気的に切り離される。したがって、上記の他の実施形態と同様、映像信号線駆動回路25におけるバッファ回路として従来よりも駆動能力の低いバッファ回路を使用しても、液晶パネル46の映像信号バスラインLr,Lg,Lbに対し従来と同様の信号を供給することができる。このため本実施形態によれば、従来よりも駆動能力の低いバッファ回路を使用することにより、映像信号線駆動回路25の消費電力を低減でき、さらに、それらバッファ回路を構成するトランジスタのサイズも縮小できる。その結果、液晶表示装置の小型化および低コスト化を図ることができる。

#### 【0098】

10

20

30

40

50

## &lt; 7 . 変形例 &gt;

本発明は上記各実施形態に限定されるものではなく、本発明の範囲を逸脱しない限りにおいて種々の変形を施すことができる。例えば、上記各実施形態では、共通電極の電位を基準とする映像信号線 L<sub>s</sub> や映像信号バスライン L<sub>r</sub>, L<sub>g</sub>, L<sub>b</sub> に供給される信号（電圧）の極性は 1 水平期間毎に反転されるが、この極性反転の周期は 1 水平走査期間には限定されず、例えば 2 水平走査期間毎に極性を反転させるようにしてもよい。その場合においても、極性反転の際に上記のような短絡動作を行わせる構成によってバッファ回路に必要な駆動能力を低減することで、映像信号線駆動回路の消費電力や回路量を低減することができる。

## 【 0 0 9 9 】

10

また、上記第 1 ~ 第 5 の実施形態では、アンプ休止制御信号 C<sub>a s</sub> により、短絡期間または短絡期間を含む所定期間は、消費電力の低減化のために各バッファ回路およびバイアス生成回路を休止させているが、これらを休止させないようにしてもよいし、バイアス生成回路を常に動作させバッファ回路のみを休止させるようにしてもよい。ただし、バッファ回路を休止させない場合においても、短絡期間において各バッファ回路の出力が高インピーダンス状態となるように出力制御をするのが好ましい。

## 【 0 1 0 0 】

なお以上では、液晶表示装置を例に挙げて説明したが、容量性負荷に対して所定の周期で極性が反転する電圧信号を供給して当該容量性負荷を駆動する表示装置であれば、他の方式の表示装置に対しても本発明は適用可能である。また、上記各実施形態では、映像信号線 L<sub>s</sub> の電圧の振幅を抑えるために共通電極の電位（共通電極信号 V<sub>c o m</sub>）が交流化されているが、共通電極の電位が固定されている場合、例えば、液晶層への印加電圧の極性を 1 走査信号線每かつ 1 映像信号線毎に反転させつつ 1 フレーム毎にも反転させる駆動方式すなわちドット反転駆動方式を採用した場合にも、本発明は適用可能である。

20

## 【 0 1 0 1 】

## 【発明の効果】

第 1 の発明によれば、映像信号線駆動回路の駆動能力が従来よりも低くても、容量性負荷に対し従来と同様の電圧を印加することができるので、映像信号線駆動回路の消費電力を低減でき、さらに、映像信号線駆動回路内のバッファ回路を構成するトランジスタのサイズも縮小できる。より詳しくは、容量性負荷への印加電圧の極性は水平走査線が切り換わる時に反転し、その反転時毎の短絡動作によって、容量性負荷に蓄積されていた電荷が放電されるので、映像信号線駆動回路の消費電力の低減等につき大きな効果が得られる。その結果、表示装置の小型化および低コスト化を図ることができる。このため、例えば本発明の適用される液晶表示装置は、携帯用途の機器に好適である。また、短絡期間内に極性反転が行われるので、画素値の書き込みに使用できる時間が長くなる。

30

## 【 0 1 0 2 】

第 2 の発明によれば、容量性負荷への印加電圧の極性反転の際に、短絡動作によって、容量性負荷に蓄積されていた電荷が電源を介さずに直接に放電される。これにより、第 1 の発明と同様、映像信号線駆動回路の消費電力を低減すると共に映像信号線駆動回路内のバッファ回路を縮小化することができるので、表示装置の小型化および低コスト化を図ることができる。

40

## 【 0 1 0 3 】

第 3 の発明によれば、映像信号線駆動回路と共通電極駆動回路とが同一基板上または同一チップ内に形成されることで、液晶表示装置の構成が簡素化される。

## 【 0 1 0 4 】

第 4 の発明によれば、映像信号線駆動回路の回路構成をコンパクトなものとすることができる。このため、映像信号線駆動回路を実現する IC チップのサイズを小さくすることができます。

## 【 0 1 0 5 】

第 5 の発明によれば、1 つの基準バスラインとそれに対応する各基準電圧選択回路内の

50

切換スイッチ手段とが基準電圧の選択と共に通電極信号と同等の電圧レベルの選択と共に用されることで、信号線駆動回路の回路量が更に低減されるので、信号線駆動回路を実現するICチップのサイズをより小さくできる。

#### 【0106】

第6の発明によれば、容量性負荷への印加電圧の極性反転の際に、短絡動作によって、容量性負荷に蓄積されていた電荷が電源を介さずに直接に放電されることで、第5の発明と同様の効果を奏する。

#### 【0107】

第7の発明によれば、映像信号線駆動回路と共に通電極駆動回路とが同一基板上または同一チップ内に形成されることで、液晶表示装置の構成が簡素化される。

10

#### 【図面の簡単な説明】

【図1】 本発明の第1の実施形態に係る液晶表示装置の構成を示すブロック図である。

【図2】 第1の実施形態における表示制御回路の構成を示すブロック図である。

【図3】 第1の実施形態における映像信号線駆動回路の構成を示す回路図である。

【図4】 第1の実施形態における共通電極駆動回路の構成を示す回路図である。

【図5】 第1の実施形態における映像信号線駆動回路の休止制御を説明するための信号波形図である。

【図6】 従来の液晶表示装置における液晶パネルの駆動方法を説明するための電圧および信号波形図である。

【図7】 第1の実施形態における液晶パネルの第1の駆動方法を説明するための電圧および信号波形図である。

20

【図8】 第1の実施形態における液晶パネルの第2の駆動方法を説明するための電圧および信号波形図である。

【図9】 第1の実施形態における液晶パネルの第3の駆動方法を説明するための電圧および信号波形図である。

【図10】 第1の実施形態における液晶パネルの第4の駆動方法を説明するための電圧および信号波形図である。

【図11】 本発明の第2の実施形態における映像信号線駆動回路の構成を示す回路図である。

【図12】 本発明の第3の実施形態に係る液晶表示装置の構成を示すブロック図である。

30

【図13】 第3の実施形態における映像信号線駆動回路の構成を示す回路図である。

【図14】 本発明の第4の実施形態における映像信号線駆動回路の構成を示す回路図である。

【図15】 本発明の第5の実施形態における映像信号線駆動回路の構成を示す回路図である。

【図16】 本発明の第6の実施形態に係る液晶表示装置の構成を示す図である。

#### 【符号の説明】

1 0 ... 表示制御回路

40

2 1 , 2 4 , 2 5 ... 映像信号線駆動回路

2 2 ... 走査信号線駆動回路

2 3 ... 共通電極駆動回路

3 0 ... 電源回路

4 0 , 4 5 , 4 6 ... 液晶パネル

1 4 1 ~ 1 4 n ... 休止制御回路

1 5 1 ~ 1 5 n ... バッファ回路

1 6 1 ~ 1 6 n ... 切換スイッチ

1 8 1 ~ 1 8 n ... 切換スイッチ

2 0 0 ... 共通電極駆動回路

2 1 2 ~ 2 1 6 3 ... 休止制御回路

50

|                       |                        |    |

|-----------------------|------------------------|----|

| 2 2 2 ~ 2 2 6 3       | ... バッファ回路             |    |

| 3 0 0                 | ... 電圧切換回路             |    |

| 4 3 r , 4 3 g , 4 3 b | ... アナログスイッチ (接続切換回路)  |    |

| E c                   | ... 共通電極               |    |

| L 1 ~ L 6 4           | ... 基準電圧バスライン          |    |

| L s                   | ... 映像信号線              |    |

| L g                   | ... 走査信号線              |    |

| L r , L g , L b       | ... 映像信号バスライン          |    |

| D r , D g , D b       | ... 画像信号               |    |

| C s h                 | ... 短絡制御信号             | 10 |

| C a s                 | ... アンプ休止制御信号          |    |

|                       | ... 極性反転制御信号           |    |

| V b a                 | ... アンプバイアス            |    |

| V v                   | ... 映像信号線の電位           |    |

| V c o m               | ... 共通電極信号             |    |

| V r 1 , V r 2         | ... (映像信号線に印加される) 基準電圧 |    |

| V H , V L             | ... (共通電極に印加される) 基準電圧  |    |

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(51)Int.Cl.

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 1 B |

| G 0 9 G | 3/20 | 6 2 3 R |

| G 0 9 G | 3/20 | 6 2 3 Y |

| G 0 9 G | 3/20 | 6 2 4 E |

審査官 中村 直行

(56)参考文献 特開平11-030975 (JP, A)

特開平06-202157 (JP, A)

特開2001-265295 (JP, A)

特開平07-253764 (JP, A)

特開2001-147420 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00 - 3/38

G02F 1/133

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置，驱动电路及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">JP4225777B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2009-02-18 |

| 申请号            | JP2002367738                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2002-12-19 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 熊田浩二<br>太田隆滋<br>香川治人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 熊田 浩二<br>太田 隆滋<br>香川 治人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G09G3/3614 G09G3/3688 G09G2310/0248 G09G2310/027 G09G2330/021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F1分类号          | G09G3/36 G02F1/133.550 G09G3/20.611.A G09G3/20.612.F G09G3/20.612.T G09G3/20.621.B<br>G09G3/20.623.R G09G3/20.623.Y G09G3/20.624.E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-Term分类号      | 2H093/NA16 2H093/NA31 2H093/NA80 2H093/NC04 2H093/NC10 2H093/NC12 2H093/NC13 2H093/NC16 2H093/NC18 2H093/NC22 2H093/NC23 2H093/NC34 2H093/NC59 2H093/ND15 2H093/ND35 2H093/ND36 2H093/ND37 2H093/ND42 2H193/ZA04 2H193/ZE31 2H193/ZF03 2H193/ZF22 2H193/ZF36 2H193/ZF59 5C006/AA16 5C006/AA22 5C006/AC11 5C006/AC25 5C006/AC27 5C006/AC28 5C006/AF02 5C006/AF03 5C006/AF04 5C006/AF25 5C006/AF68 5C006/AF69 5C006/AF72 5C006/AF73 5C006/AF83 5C006/BB16 5C006/BC12 5C006/BC20 5C006/BF02 5C006/BF04 5C006/BF11 5C006/BF15 5C006/BF24 5C006/BF25 5C006/BF27 5C006/BF33 5C006/BF34 5C006/BF43 5C006/EB05 5C006/FA15 5C006/FA16 5C006/FA26 5C006/FA42 5C006/FA43 5C006/FA47 5C006/FA51 5C006/FA56 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD03 5C080/DD08 5C080/DD23 5C080/DD24 5C080/DD25 5C080/DD26 5C080/DD27 5C080/EE29 5C080/FF03 5C080/FF11 5C080/GG11 5C080/GG14 5C080/GG15 5C080/GG17 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/KK04 5C080/KK07 |         |            |

| 代理人(译)         | 岛田彰                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 审查员(译)         | 中村直之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 优先权            | 2002031593 2002-02-08 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 其他公开文献         | JP2003302951A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

**摘要(译)**

要解决的问题：提供一种显示装置，其中用于AC驱动的驱动电路的功耗降低，该驱动电路用于将与要显示的图像对应的电压施加到电容性负载。在有源矩阵型液晶显示装置中，所述缓冲电路被显示151～15n和对应于图像的视频信号线电压的信号线驱动电路是从基准电压选择电路131～13n的输入被连接N个转换开关161至16n设置在输出端子T1至Tn之间。这些切换开关161～16n中的基础上，短路控制信号Csh成为H电平，当极性反转为在液晶面板的交流驱动时，输出信号OUT1～所述视频信号线驱动电路，缓冲电路的OUTn的151至15n和公共电极信号Vcom。结果，在极性反转期间，每个视频信号线与缓冲电路151至15n断开预定时段，并且短路到公共电极。