特開2002 - 268614

(P2002 - 268614A)

(43)公開日 平成14年9月20日(2002.9.20)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I           | テ-マコード* (参考)    |

|--------------------------|------|---------------|-----------------|

| G 0 9 G 3/36             |      | G 0 9 G 3/36  | 2 H 0 9 3       |

| G 0 2 F 1/133            | 550  | G 0 2 F 1/133 | 5 C 0 0 6       |

| G 0 9 G 3/20             | 612  | G 0 9 G 3/20  | 612 E 5 C 0 8 0 |

|                          | 670  |               | 670 M 5 J 0 5 5 |

| H 0 3 K 17/16            |      | H 0 3 K 17/16 | D               |

審査請求 未請求 求項の数 19 O L (全 9 数) 最終頁に続く

(21)出願番号 特願2001 - 332969(P2001 - 332969)

(71)出願人 390019839

三星電子株式会社

(22)出願日 平成13年10月30日(2001.10.30)

大韓民国京畿道水原市八達区梅灘洞416

(31)優先権主張番号 2000 - 073804

(72)発明者 権 奎 亨

(32)優先日 平成12年12月6日(2000.12.6)

大韓民国京畿道龍仁市器興邑農書里山24番

(33)優先権主張国 韓国(KR)

地

(74)代理人 100086368

弁理士 萩原 誠

最終頁に続く

(54)【発明の名称】 液晶表示装置ドライバ回路

(57)【要約】

【課題】 カラーLCDドライバ回路において、正常時の回路性能は低下させずにESD特性を向上させること。

【解決手段】 第1～第N入力パッド、第1～第N静電気放電保護部及び出力ドライバ330を備える。出力ドライバ330は、第1～第N入力パッドを通じて入力される第1～第N電圧と各々一側が接続される第1～第N抵抗R31～R35を備え、この第1～第N抵抗R31～R35を通じて印加される各々の第1～第N電圧から液晶表示装置を駆動するための駆動電圧を生成する。第1～第N抵抗R31～R35は静電気パルスの印加時に出力ドライバ330の内部に流れる電流を低減するために具備される。

## 【特許請求の範囲】

【請求項1】 外部から相異なる電圧レベルを有する第1～第N(ここで、Nは1よりも大きい整数)電圧を受けるための第1～第N入力パッドと、前記各第1～第N入力パッドと接続され、前記入力パッドを通じて静電気パルスが印加される時に放電経路を形成する第1～第N静電気放電保護部と、前記第1～第N入力パッドを通じて入力される前記第1～第N電圧を各々受けるための第1～第N抵抗を備え、この第1～第N抵抗を通じて印加される前記各々の第1～第N電圧から液晶表示装置を駆動するための駆動電圧を生成する出力ドライバとを備え、前記第1～第N抵抗は、前記静電気パルスの印加時に前記出力ドライバの内部に流れる電流を低減するために具備されることを特徴とする液晶表示装置ドライバ回路。

【請求項2】 前記出力ドライバは、前記第1～第N抵抗を通じて各々の前記第1～第N電圧を入力し、所定の第1～第N制御信号に応答して前記第1～第N電圧を第1ノードに伝達する第1～第N電圧伝達部と、

前記第1ノードと一側が接続され、他側が所定の出力パッドと接続された第N+1抵抗とを備えることを特徴とする請求項1に記載の液晶表示装置ドライバ回路。

【請求項3】 前記電圧伝達部は、第1～第K(ここで、1<K<N)電圧を前記第1～第N制御信号のうち第1～第K制御信号に応答して前記第1ノードに伝達する第1～第K CMOS伝送ゲートと、第K+1～第N電圧を前記第1～第N制御信号のうち第K+1～第N制御信号に応答して前記第1ノードに伝達する第K+1～第N NMOSトランジスタとを備え、前記第1～第K電圧は、前記第K+1～第N電圧よりも高い電圧レベルを有することを特徴とする請求項2に記載の液晶表示装置ドライバ回路。

【請求項4】 前記電圧伝達部は、前記第1～第N電圧を所定の第1～第N制御信号に応答して前記第1ノードに伝達する第1～第N CMOS伝送ゲートを備えることを特徴とする請求項2に記載の液晶表示装置ドライバ回路。

【請求項5】 前記出力ドライバは、第1～第K(1<K<N)電圧を第1～第K制御信号に応答して前記第1ノードに伝達する第1～第K CMOS伝送ゲートと、NMOSトランジスタとPMOSトランジスタとの並列構造によりなり、前記第K+1～第N電圧を前記第K+1～第N制御信号に応答して前記第1ノードに伝達する第K+1～第N並列トランジスタとを備え、前記並列トランジスタの各PMOSトランジスタのゲートは、前記第1～第N電圧よりも高いレベルを有する高電圧と接続されて正常動作時にターンオフされることを特徴とする請求項2に記載の液晶表示装置ドライバ回

路。

【請求項6】 前記出力ドライバは、前記出力パッドと接続され、前記出力パッドを通じて外部から静電気パルスが印加される時に放電経路を形成する出力静電気放電保護部をさらに備えることを特徴とする請求項2に記載の液晶表示装置ドライバ回路。

【請求項7】 前記第1～第N入力パッドは第1～第K入力パッドを含み、前記第1～第N静電気放電保護部は第1～第K(ここで、1<K<N)静電気放電保護部を含み、この第1～第K静電気放電保護部は、

前記第1～第N電圧よりも高いレベルを有する高電圧と前記第1～第K入力パッドとの間に接続される第1保護素子と、

前記第1～第K入力パッドと接地電位との間に直列接続され、各ゲートが接地電位及び電源電圧のうちいずれか一つに接続される2つ以上のシングート酸化膜NMOSトランジスタよりなる第2保護素子とを各々備えることを特徴とする請求項1に記載の液晶表示装置ドライバ回路。

【請求項8】 前記第1～第N入力パッドは第K+1～第N入力パッドを含み、

前記第1～第N静電気放電保護部は第K+1～第N静電気放電保護部を含み、この第K+1～第N静電気放電保護部は、

前記高電圧と前記第K+1～第N入力パッドとの間に接続される第3保護素子と、

前記第K+1～第N入力パッドと接地電位との間に並列接続され、各ゲートが接地電位と接続される2つ以上のシングート酸化膜NMOSトランジスタよりなる第4保護素子とを各々備え、

前記第1～第K入力パッドを通じて印加される各電圧は前記第K+1～第N入力パッドを通じて印加される電圧よりも高いレベルを有することを特徴とする請求項7に記載の液晶表示装置ドライバ回路。

【請求項9】 前記第1～第N抵抗は拡散型抵抗で具現されることを特徴とする請求項1に記載の液晶表示装置ドライバ回路。

【請求項10】 外部から相異なる電圧レベルを有する第1～第N電圧を受けるための第1～第N入力パッドと、

前記各第1～第N入力パッドと接続され、前記入力パッドを通じて静電気パルスが印加される時に放電経路を形成する第1～第N静電気放電保護部と、

前記第1～第N入力パッドを通じて入力される第1～第N電圧を伝達するための第1～第N電圧伝達手段を備え、この第1～第N電圧伝達手段を通じて伝達された前記第1～第N電圧から液晶表示装置を駆動するための駆動電圧を生成する出力ドライバとを備え、前記第1～第N電圧のうち低いレベルの電圧を伝達する少なくとも一つの前記電圧伝達手段はPMOSトランジ

50

スタとN MOSトランジスタとの並列構造よりなることを特徴とする液晶表示装置ドライバ回路。

【請求項11】 前記出力ドライバは、前記並列構造の電圧伝達手段でPMOSトランジスタのゲートを前記第1～第N電圧よりも高いレベルを有する高電圧と接続して正常動作時にターンオフさせることを特徴とする請求項10に記載の液晶表示装置ドライバ回路。

【請求項12】 前記第1～第N電圧伝達手段は各々、所定の第1～第N制御信号に応答して前記第1～第N電圧を第1ノードに伝達することを特徴とする請求項10に記載の液晶表示装置ドライバ回路。

【請求項13】 前記第1～第N電圧伝達手段は、前記第1～第N電圧を所定の第1～第N制御信号に応答して前記第1ノードに伝達する第1～第N CMOS伝送ゲートを備えることを特徴とする請求項12に記載の液晶表示装置ドライバ回路。

【請求項14】 前記出力ドライバは、所定の出力パッドと接続され、前記静電気パルスが前記所定の出力パッドを通じて外部から印加される時に他の放電経路を形成する出力静電気放電保護部をさらに含むことを特徴とする請求項12に記載の液晶表示装置ドライバ回路。

【請求項15】 外部から相異なる電圧レベルを有する第1～第N電圧を受けるための第1～第N入力パッドと、

前記各第1～第N入力パッドと接続され、前記入力パッドを通じて静電気パルスが印加される時に放電経路を形成する第1～第N静電気放電保護部とを備え、前記第1～第N静電気放電保護部は、

少なくとも一つのシングート酸化膜トランジスタを含むことを特徴とする液晶表示ドライバ回路。

【請求項16】 第1～第N入力パッドは第1～第K入力パッドを含み、前記第1～第N静電気放電保護部は第1～第K（ここで、 $1 < K < N$ ）静電気放電保護部を含み、この第1～第K静電気放電保護部は、

前記第1～第N電圧よりも高いレベルを有する高電圧と前記第1～第K入力パッドとの間に接続される第1保護素子と、

前記第1～第K入力パッドと接地電位との間に直列接続され、各ゲートが接地電位及び電源電圧のうちいずれか一つに接続される2つ以上のシングート酸化膜N MOSトランジスタよりなる第2保護素子とを各々備えることを特徴とする請求項15に記載の液晶表示装置ドライバ回路。

【請求項17】 前記第1～第N入力パッドは第K+1～第N入力パッドを含み、

前記第1～第N静電気放電保護部は第K+1～第N静電気放電保護部を含み、この第K+1～第N静電気放電保護部は、

\*前記高電圧と前記第K+1～第N入力パッドとの間に接続される第3保護素子と、

前記K+1～第N入力パッドと接地電位との間に並列接続され、各ゲートが接地電位と接続される2つ以上のシングート酸化膜N MOSトランジスタよりなる第4保護素子とを各々備え、

前記第1～第K入力パッドを通じて印加される各電圧は、前記第K+1～第N入力パッドを通じて印加される電圧よりも高いレベルを有することを特徴とする請求項16に記載の液晶表示装置ドライバ回路。

【請求項18】 前記出力ドライバは、第1～第N入力パッドを通じて前記第1～第N電圧を各々受けけるための第1～第N抵抗を備え、この第1～第N抵抗を通じて受けた前記各々の第1～第N電圧から液晶表示装置を駆動するための駆動電圧を生成し、前記第1～第N抵抗は前記静電気パルスの印加時に前記出力ドライバの内部に流れる電流を低減するために具備されることを特徴とする請求項15に記載の液晶表示装置ドライバ回路。

【請求項19】 前記出力ドライバは、前記第1～第N抵抗を通じて前記第1～第N電圧を各々受け、前記第1～第N電圧を所定の第1～第N制御信号に応答して第1ノードに伝達する第1～第N電圧伝達手段と、

一側及び他側を有し、前記第1ノードと一側が接続され、他側が所定の出力パッドを接続された第N+1抵抗とをさらに備えることを特徴とする請求項18に記載の液晶表示装置ドライバ回路。

#### 【発明の詳細な説明】

##### 【0001】

【発明の属する技術分野】本発明は液晶表示装置ドライバ回路に係り、特に、静電気放電保護のための液晶表示装置ドライバ回路に関する。

##### 【0002】

【従来の技術】一般に、液晶表示装置（Liquid Crystal Device、以下、LCDと言う）ドライバ回路または集積回路は、LCDパネルに情報をディスプレイするために高いレベルのLCD電圧（V<sub>LCD</sub>）を駆動する。ここで、LCD電圧（V<sub>LCD</sub>）は外部から印加でき、あるいは内部の電荷ポンプ、演算増幅器またはバンドギャップ回路などのアナログ回路を用いて内部的に生成できる。このようなLCD電圧はLCD画面の画質を決定する重要な要因となる。

【0003】しかし、LCDドライバ回路において、電圧入力端または電圧出力端で生じる静電気放電（Electrostatic Discharge、以下、ESDと言う）現象により内部回路が損傷する場合がある。このため、LCDドライバを含むほとんどの半導体装置は、ESDによる損傷から半導体装置を保護するためにESD保護用素子を入力端または出力端に備える。

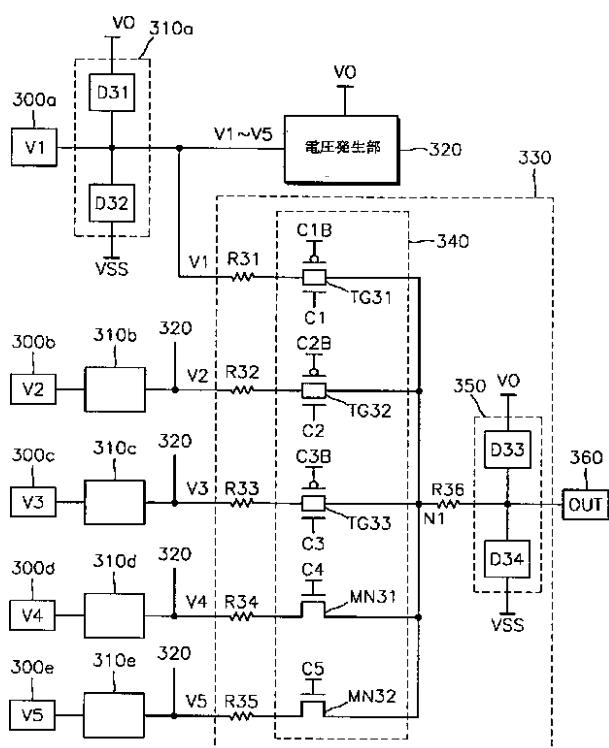

【0004】図1は、従来のESD保護のためのLCDドライバ回路を示した回路図である。図1に示された回路は、一般に、モノクロームLCDに適用されるドライバ回路の例であって、入力パッド10、抵抗R1、ESD保護部12、電圧発生部14及びLCD出力ドライバ16を含む。

【0005】図1に示された回路において、LCD電圧(VLCD) V1～V5は各々の入力パッドを通じて外部から印加されるか、あるいは電圧発生部14で極めて高いレベルの電圧を分配することにより生成される。具体的には示されていないが、第2～第5電圧V2～V5も第1電圧V1と同一の方式でLCD出力ドライバ16に印加できる。正常動作時にESD保護部12は動作しない。これに対して、入力パッド10を通じてESDパルスが印加されると、第1保護素子D1または第2保護素子D2がターンオンされてESDパルスによる大電流が放電される放電経路が形成される。この時、入力パッド10と接続された直列抵抗R1によりESDパルスによる大きい電流がダウンされて内部回路が保護される。

【0006】しかし、モノクロームLCDではなく、カラーLCDを駆動するLCDドライバ回路は、設計スペック上、LCD電圧(VLCD)の変化量が厳しく規定されている。例えば、特定テスト条件ではLCD電圧(VLCD)が入力されるパッド10に流れる電流と内部電圧発生部14で流れる電流との差が10uAの時にLCD電圧の変化量が10mV未満になるように設定されている。このため、カラーLCDドライバ回路では、図1の回路のように入力パッドと電圧発生部との間に電圧ドロップの主要因となる直列抵抗を接続することはできない。これにより、ESDパルスによる大電流が出力ドライバ16及び電圧発生部14に伝達されて物理的な損傷を起すようになる。すなわち、正極性または負極性のESDパルスが印加されると、パッド10と隣接したESD保護部12の第1、第2保護素子D1、D2を通じて1次的な放電がなされ、余分の電流がLCD出力ドライバ16に印加されるからである。

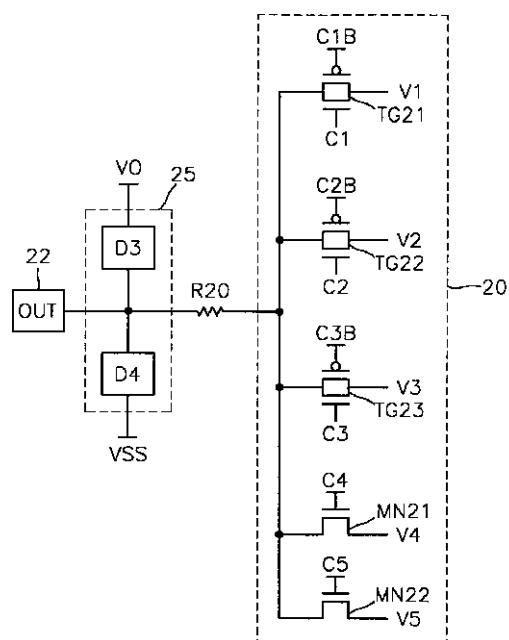

【0007】図2は、通常のカラーLCDドライバ回路に適用される出力ドライバを示した回路図である。図2を参照すれば、相対的に高い電圧レベルを有するLCD電圧V1～V3を伝達する各電圧伝達素子はCMOS伝送ゲートTG21～TG23で具現される。低い電圧レベルのLCD電圧V4及びV5を伝達する伝達素子はNMOSトランジスタMN21、MN22で具現される。また、出力パッド22を通じて印加されるESDパルスから内部回路を保護するためにESD保護部25が具備される。カラーLCDドライバの出力ドライバは設計スペック上ターンオン抵抗値を満足させるように設計されている。すなわち、印加されるLCD電圧V1～V5と比例して各伝送ゲートTG21～TG23及びNMOSトランジスタMN21、MN22のターンオン抵抗値が50

決まる。したがって、低い電圧レベルを有するLCD電圧V4及びV5を駆動する部分は、小さい幅のNMOSトランジスタMN21、MN22だけで所望の抵抗値を得ることができる。

#### 【0008】

【発明が解決しようとする課題】しかし、このように、NMOSトランジスタを用いる場合には、正極性のESDパルス印加時に順方向の放電経路がなく、また放電面積が極めて狭いため放電能力に劣るという問題がある。

【0009】また、従来のLCDドライバ回路は、入力パッドに接続される保護素子(例えば、図1のD1、D2)の放電効率が低いため、ESD保護特性が低下する可能性がある。すなわち、LCD電圧はLCDドライバの内部の他の回路の動作電圧よりも高いため、図1のESD保護部12は高電圧接合で形成される。しかし、このように、高電圧接合では動作電圧が高いため、大きい電流を駆動できなくなる。したがって、ESDパルスによる大電流が印加される場合、ESD保護能力が低下するという問題がある。

【0010】本発明は、カラーLCDドライバ回路において正常時の回路性能は低下させずにESD特性を向上させることができ、かつESD放電効率を高めることができ、それらの結果ESDパルスによる出力ドライバの損傷を防止できる静電気放電保護のための液晶表示装置ドライバ回路を提供することを目的とする。

#### 【0011】

【課題を解決するための手段】本発明による第1の静電気放電保護のための液晶表示装置ドライバ回路は、第1～第N入力パッド、第1～第N静電気放電保護部及び出力ドライバを備える。第1～第N入力パッドは外部から相異なる電圧レベルを有する第1～第N(N>1)電圧を受ける。第1～第N静電気放電保護部は、各第1～第N入力パッドと接続され、入力パッドを通じて静電気パルスが印加される時に放電経路を形成する。出力ドライバは、第1～第N入力パッドを通じて入力される第1～第N電圧と各々一側が接続される第1～第N抵抗を備え、この第1～第N抵抗を通じて印加される各々の第1～第N電圧から液晶表示装置を駆動するための駆動電圧を生成する。また、第1～第N抵抗は、静電気パルスの印加時に出力ドライバの内部に流れる電流を低減するために具備される。

【0012】本発明による第2の静電気放電保護のための液晶表示装置ドライバ回路は、第1～第N入力パッド、第1～第N静電気放電保護部及び出力ドライバを備える。第1～第N入力パッドは外部から相異なる電圧レベルを有する第1～第N電圧を受ける。第1～第N静電気放電保護部は各第1～第N入力パッドと接続され、入力パッドを通じて静電気パルスが印加される時に放電経路を形成する。出力ドライバは、第1～第N入力パッドを通じて入力される第1～第N電圧を伝達するための第

1～第N電圧伝達手段を備え、この第1～第N電圧伝達手段を通じて伝達された第1～第N電圧から液晶表示装置を駆動するための駆動電圧を生成する。第1～第N電圧のうち低いレベルの電圧を伝達する少なくとも一つの電圧伝達手段はPMOSトランジスタとNMOSトランジスタとの並列構造よりもなることを特徴とする。

【0013】本発明による第3の静電気放電保護のための液晶表示装置ドライバ回路は、第1～第N入力パッド、第1～第N静電気放電保護部を備える。第1～第N入力パッドは外部から相異なる電圧レベルを有する第1～第N電圧を受ける。第1～第N静電気放電保護部は各第1～第N入力パッドと接続され、入力パッドを通じて静電気パルスが印加される時に放電経路を形成する。ここで、第1～第N静電気放電保護部は少なくとも一つのシングレート酸化膜トランジスタを含むことを特徴とする。

#### 【0014】

【発明の実施の形態】以下、本発明による静電気放電保護のための液晶表示装置ドライバ回路の実施の形態について添付した図面を参照して下記のように説明する。

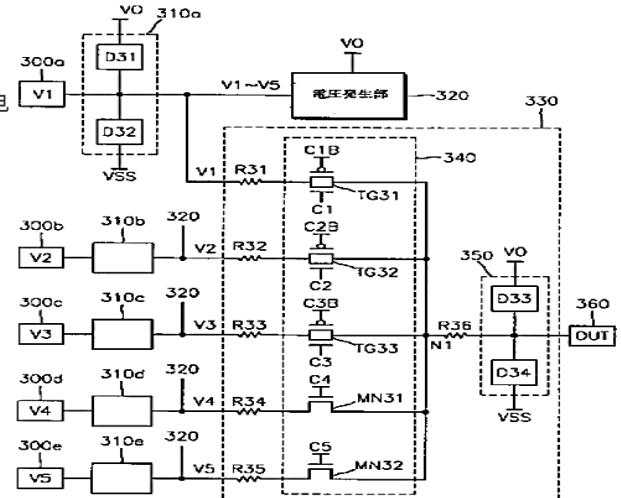

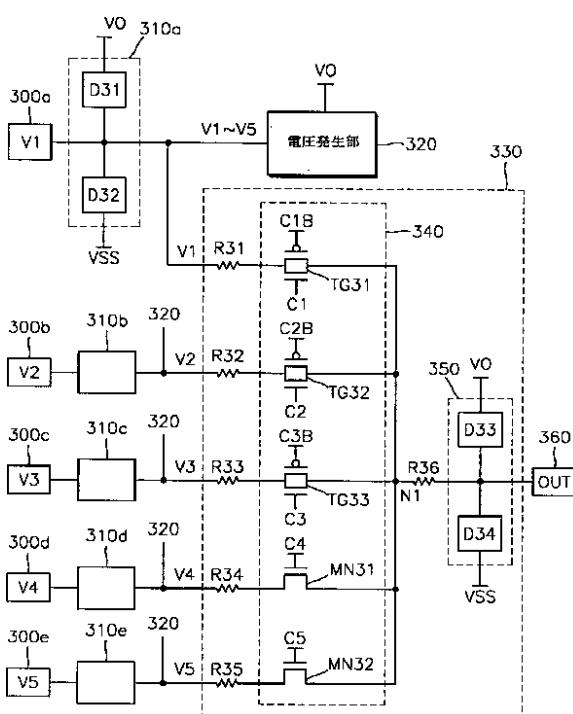

【0015】図3は、本発明の実施形態による静電気放電保護のための液晶表示装置(LCD)ドライバ回路を説明するための回路図である。図3を参照すれば、LCDドライバ回路は、入力パッド300a～300e、ESD保護部310a～310e、電圧発生部320及びLCD出力ドライバ330を備える。図3のLCDドライバ回路は、全てのLCDドライバ回路に適用可能であるが、特に、設計スペックが厳しいカラースーパーツイステッドネマスチック(Super Twisted Nematic、すなわちSTN)LCDドライバに効率よく適用可能である。

【0016】図3の入力パッド300a～300eは、外部から第1～第5LCD電圧(以下、単に第1～第5電圧と言う)V1～V5を各々入力する。ここで、第1～第5電圧V1～V5は各々相異なる電圧レベルを有する。そのうち第1電圧V1が最も高いレベルを有し、第2電圧V2～第5電圧V5は第1電圧V1よりも次第に低いレベルを有するように(例えば、V1>V2>V3>V4>V5に)設定される。

【0017】各々の入力パッド300a～300eにはESD保護部310a～310eが接続される。例えば、第1パッド300aと接続されたESD保護部310aは保護素子D31、D32よりなり、ESDパルスの印加時に放電経路を形成する。ここで、保護素子D31、D32はダイオードまたはトランジスタで具現できる。第1保護素子D31は第1電圧V1よりも高いレベルの高電圧V0と一側が接続され、他側は第1パッド300aの一側と接続される。第1保護素子D31がダイオードで具現される場合にはカソードが高電圧V0と接続され、アノードが第1パッド300aの一側と接続さ

れる。また、第2保護素子D32は一側が第1パッド300aの一側と接続され、他側は接地電位VSSと接続される。例えば、第2保護素子D32がダイオードで具現される場合、アノードは接地電位VSSと接続され、カソードは第1パッド300aの一側と接続される。他のESD保護部310b～310eの構造もESD保護部310aと同一のため、具体的な説明は省略する。

【0018】図3の電圧発生部320は、高レベルの電圧V0を適切に分配して相異なるレベルを有する第1～第5電圧V1～V5を生成する。具体的に示されてはいないが、電圧発生部320は内部に演算増幅器、バンドギャップ基準電圧発生回路、レベルシフタなどのアナログ回路を含む。外部から入力パッド300a～300eを通じて第1～第5電圧V1～V5が入力される時、電圧発生部320は動作しない。

【0019】LCD出力ドライバ330は、外部から印加されるLCD電圧V1～V5または電圧発生部320から印加されるLCD電圧V1～V5を所定の制御信号に応答してLCD駆動電圧として生成する。この時、生成された駆動電圧はLCDパネル(図示せず)に印加される。

【0020】図3を参照すれば、LCD出力ドライバ330は抵抗R31～R35、電圧伝達部340及びESD保護部350を含む。具体的に、各電圧V1～V5と電圧伝達部340との間に抵抗R31～R35が各々直列接続される。電圧伝達部340はCMOS伝送ゲートTG31～TG33及びNMOSトランジスタMN31、MN32よりなり、抵抗R31～R35を通じて印加された第1～第5電圧V1～V5を所定の制御信号に応答して第1ノードN1に伝達する。すなわち、伝送ゲートTG31は電圧伝達素子であって、抵抗R31を通じて印加される第1電圧V1を制御信号C1、C1Bに応答して第1ノードN1に伝達する。ここで、C1～C5はLCDドライバ回路の内部の制御回路(図示せず)から印加される信号であり、C1B～C3Bは各々C1～C3の反転された信号である。伝送ゲートTG32、TG33は、各々抵抗R32、R33を通じて印加される第2、第3電圧V2、V3を制御信号C2/C2B、C3/C3Bに応答して第1ノードN1に伝達する。すなわち、伝送ゲートTG31～TG33はLCD電圧のうち相対的に高いレベルを有する第1～第3電圧V1～V3を伝達する役割をする。また、NMOSトランジスタMN31、MN32のソースは各々抵抗R34、R35の一側と接続され、ドレインは第1ノードN1に接続される。すなわち、NMOSトランジスタMN31、MN32は、抵抗R34、R35を通じて印加される第4、第5電圧V4、V5を各々制御信号C4、C5に応答して第1ノードN1に伝達する。ここで、第4電圧V4及び第5電圧V5は第1～第3電圧V1～V3よりも相対的に低い電圧である。

【0021】LCD出力ドライバ330の抵抗R36は第1ノードN1と一側が接続され、他側が出力パッド360と接続される。ここで、抵抗R36は出力パッド360から印加されるESD電流を下げるために用いられる。また、出力ESD保護部350は出力パッド360を通じてESDパルスが印加される時に放電経路を形成する。ESD保護部350は各々ダイオードまたはトランジスタの保護素子D33, D34を備える。出力パッド360はLCD出力ドライバ330から出力される駆動電圧OUTをLCDパネル(図示せず)に出力する。

【0022】より具体的にLCDドライバ回路の動作について説明すれば、下記の通りである。前述したように、各抵抗R31～R35は第1～第5電圧V1～V5と電圧伝達部340の伝達素子との間に接続されている。したがって、入力パッド300a～300eからみると、各抵抗R31～R35は互いに並列接続されているため、全体の抵抗値は下がることが分かる。正常動作時に、ESD保護部310aは動作しない。

【0023】また、外部から入力パッド300a～300eを通じてESDパルスが印加されると、ESD保護部310aの保護素子D31, D32により放電経路が形成され、1次的な放電がなされる。ここで、保護素子D31, D32がダイオードであると仮定し、かつ説明する。例えば、正極性のESDパルスが印加されれば、第1保護素子D31がターンオンし放電経路が形成され、負極性のESDパルスが印加されれば、第2保護素子D32がターンオンし放電経路が形成される。この時、一部の電流は放電されるが、残りの電流はLCD出力ドライバ330に印加される。ところが、各電圧伝達素子TG31～TG33, MN31, MN32と直列接続された抵抗R31～R35により抵抗値が上がるため、各電圧伝達素子TG31～MN32に印加される電流は減る。したがって、ESDパルスが印加されれば、放電面積が十分に確保されなくとも、LCD出力ドライバ330の内部に印加される電流が減り、内部回路が保護されることになる。ここで、抵抗R31～R35を拡散型抵抗で具現する場合には寄生ダイオードが形成されるという効果が得られる。したがって、寄生ダイオードによる放電経路を形成できるという長所がある。

【0024】以上のように、本発明では、入力パッド300a～300eに直列接続される抵抗を用いない代わりに、出力ドライバ330で各LCD電圧V1～V5入力端に抵抗を接続させることにより、ESD放電特性を補償できる。

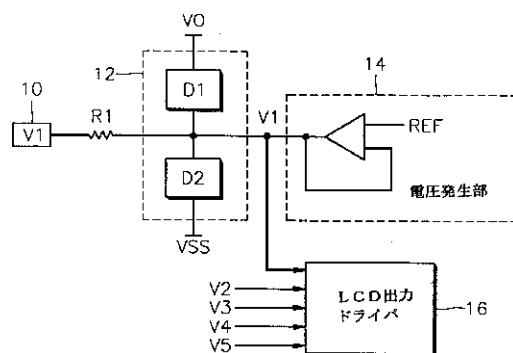

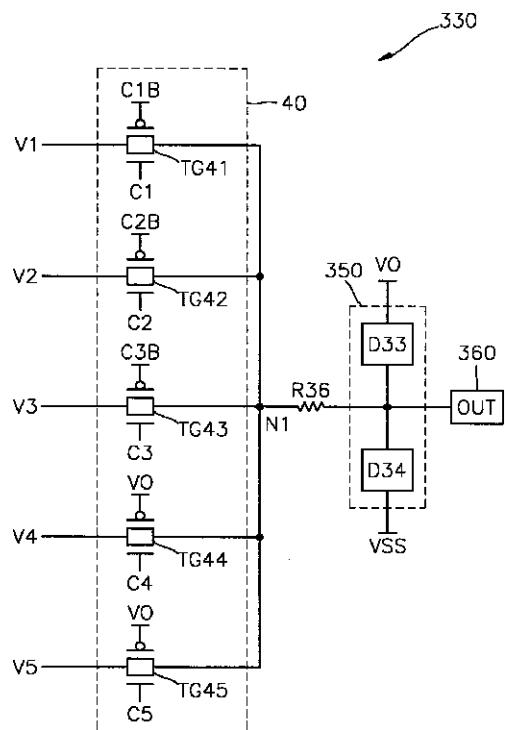

【0025】図4は、本発明の他の実施形態によるLCD出力ドライバ330を説明するための回路図である。図4を参照すれば、LCD出力ドライバ330は電圧伝達部40及びESD保護部350を含む。ESD保護部350は図3のESD保護部350と同一の構成及び機能を行うため、その具体的な説明は省略する。

【0026】図4を参照すれば、電圧伝達部40は伝送ゲートTG41～TG45を含む。各々の伝送ゲートTG41～TG45は第1～第5電圧V1～V5と接続され、各々の制御信号に応答して第1～第5電圧V1～V5を第1ノードN1に伝達する。第4、第5電圧V4, V5を伝達する伝達素子は、他の伝達素子と同様にCMOS伝送ゲートTG44, TG45で具現される。この場合、CMOS伝送ゲートTG44, TG45のPMOSトランジスタのゲートは、他の伝送ゲートと同様に反転制御信号C4B, C5Bに接続できるが、ここでは高電圧V0と接続する。また、第4、第5電圧V4, V5を伝達する伝達素子は、PMOSトランジスタとNMOSトランジスタとを並列接続させることにより具現できる。この場合、PMOSトランジスタのゲートは高レベルの電圧V0と接続される。

【0027】より具体的に図4のLCD出力ドライバ330について説明すれば下記の通りである。すなわち、図4のLCD出力ドライバ330は、低いレベルの電圧V4, V5を伝達する伝達素子をNMOSトランジスタだけで具現せず、PMOSトランジスタと並列接続させて具現する。正常動作時には、CMOS伝送ゲートTG44, TG45のPMOSトランジスタまたは並列構造のPMOSトランジスタのゲートが高電圧V0と接続されているので、これらPMOSトランジスタがターンオフされた状態が保たれる。したがって、正常動作時にはPMOSトランジスタがターンオフされているため、ターンオン抵抗は維持される。

【0028】しかし、入力パッド300a～300e(図3参照)を通じてESDパルスが印加された場合には、伝送ゲートTG44, TG45のPMOSトランジスタまたは並列接続されたPMOSトランジスタにより正極性のESD電流に対する順方向の放電経路が形成される。すなわち、従来は、電圧V4, V5を伝達する伝達素子がNMOSトランジスタだけで構成されるため、正極性のESDパルスに対する順方向の放電経路がなかったが、本発明では順方向の放電経路が形成されるので、ESD特性が改善される。

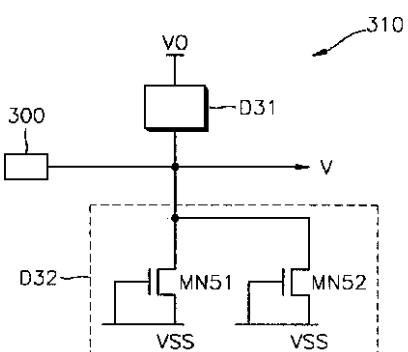

【0029】図5は、図3に示されたLCDドライバ回路のESD保護部310a～310eの他の実施形態を説明するための回路図である。図5のESD保護部310aはESD保護部310a～310eのうちいずれか一つであり、同様に入力パッド300aは第1～第5入力パッド300a～300eのうちいずれか一つである。

【0030】図5の第2保護素子D32は、シングート-酸化膜(thin gate-oxide、以下、thinxと記す)NMOSトランジスタMN51, MN52で具現される。すなわち、thinx NMOSトランジスタMN51, MN52は入力パッド300aと接地電位VSSとの間に並列接続される。すなわち、NMOSトランジスタMN51, MN52のドレイ

ンは入力パッド300と接続され、ゲート及びソースは接地電位VSSに接続される。ここで、保護素子D32は動作電圧は低いが大きい電流を駆動するため、前述のように、*thin-gox*トランジスタで具現される。すなわち、*thin-gox*トランジスタはターンオン電圧が低いものの電流駆動力が大きいという長所を有するので、ESD放電効率が高い。この*thin-gox*トランジスタはゲート酸化膜の厚さにより動作電圧が決まる。本発明では、入力パッド300を通じて入力される電圧が*thin-gox*トランジスタの降伏電圧よりも小さい場合（例えば、電圧V4, V5の場合）には、並列接続された*thin-gox*NMOSトランジスタMN51, MN52を用いて第2保護素子D32を具現する。

【0031】したがって、入力パッド300を通じてESDパルスが印加されれば、並列接続された*thin-gox*NMOSトランジスタMN51, MN52により電流が放電される面積が広がり、放電効率が向上する。ここで、NMOSトランジスタMN51, MN52のゲートは接地電位VSSに接続させて正常動作時に同トランジスタMN51, MN52をターンオフさせる。

【0032】前述したように、図5の回路は入力パッド300を通じて印加される電圧が*thin-gox*NMOSトランジスタMN51, MN52の降伏電圧よりも低い場合に適用可能であるので、望ましくは、図3のESD保護部310a～310eのうちESD保護部310d, 310eに適用される。

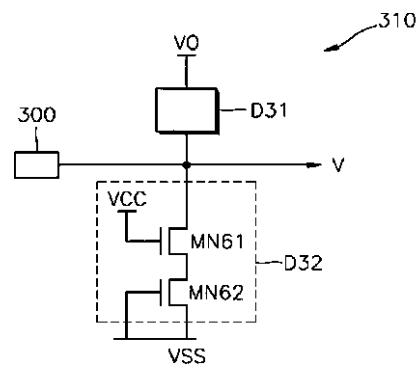

【0033】図6は、図3に示されたLCDドライバ回路のESD保護部310a～310eのさらに他の実施形態を示す回路図である。図6を参照すれば、第2保護素子D32は、入力パッド300と接地電位VSSとの間に直列接続された*thin-gox*NMOSトランジスタMN61, MN62で具現される。すなわち、NMOSトランジスタMN61のドレインは入力パッド300と接続され、ゲートは電源電圧VCCと接続される。また、NMOSトランジスタMN62のドレインはNMOSトランジスタMN61のソースと接続され、ゲート及びソースは接地電位VSSと接続される。

【0034】図6の回路は、図5の回路と比較する時、入力パッド300を通じて入力される電圧が*thin-gox*NMOSトランジスタMN61, MN62の降伏電圧、すなわち、耐電圧よりも大きい場合に適用可能である。したがって、望ましくは、図3のESD保護部310a～310eのうちESD保護部310a～310cに適用される。

【0035】すなわち、入力パッド300に印加される電圧が*thin-gox*トランジスタのゲート酸化膜の耐電圧よりも大きい場合にはゲート酸化膜が物理的に損傷されないようにする必要がある。したがって、NMOSトランジスタMN61は、ESDパルスが入力パッド\*50

\*300を通じて印加される時、NMOSトランジスタMN62のゲート-ソース間の電圧と、ゲート-ドレイン間の電圧がゲート酸化膜の降伏電圧を超えないようにする役割をする。このように、図6では、直列接続された2つ以上の*thin-gox*トランジスタを用いてESD保護部310a～310cを具現することにより、ESD放電効率を向上できる。また、図5及び図6に示されたESD保護部は、出力パッドと接続されたESD保護部にも適用可能である。

10 【0036】しかし、入力パッド300を通じて入力される電圧が接合降伏電圧よりも大きい場合には*thin-gox*トランジスタを用いる図6の回路を適用できない。したがって、この場合には、望ましくは、トリガ電圧が低く、大きい電流を駆動できるシリコン制御整流器（Silicon Controlled Rectifier、すなわちSCR）を用いて第1、第2保護素子D31, D32を具現する。

【0037】以上、最適な実施の形態を開示した。ここで、特定の用語が使用されたが、これは単に本発明を説明するために使用されたものであり、意味の限定や特許請求の範囲上に記載された本発明の範囲を制限するためには使用されたものではない。したがって、この技術分野の通常の知識を有した者なら、これより各種の変形及び均等な他の実施形態が可能であるということを理解できる。よって、本発明の真の技術的な保護範囲は特許請求の範囲上の技術的な思想によって定まるべきである。

### 【0038】

【発明の効果】以上述べたように、本発明によれば、カラーLCDドライバ回路において、正常時の回路性能は低下させずにESD特性を向上させることができるという効果がある。また、入力パッドまたは出力パッドに接続されたESD保護部の保護素子を*thin-gox*トランジスタを用いて具現することによりESD放電効率を向上させることができるという効果もある。そして、それらの結果、ESDパルスによる出力ドライバの損傷を防止できる。

### 【図面の簡単な説明】

【図1】従来の静電気放電保護のための液晶表示装置ドライバ回路を示した回路図である。

40 【図2】通常のカラー液晶表示装置ドライバ回路に適用される出力ドライバを説明するための回路図である。

【図3】本発明の実施形態による静電気放電保護のための液晶表示装置ドライバ回路を示した回路図である。

【図4】図3に示された回路のLCD出力ドライバの他の実施形態の回路図である。

【図5】図3に示された回路の静電気放電保護部の他の実施形態の回路図である。

【図6】図3に示された回路の静電気放電保護部のさらに他の実施形態の回路図である。

### 【符号の説明】

300a～300e 入力パッド

310a～310e, 350 静電気放電 (ESD)

保護部

320 電圧発生部

330 液晶表示装置 (LCD) 出力ドライバ

340 電圧伝達部

360 出力パッド

D31～D34 保護素子

\* R31～R36 抵抗

TG31～TG33, TG41～TG45 CMOS

伝送ゲート

MN31, MN32 NMOSトランジスタ

N1 第1ノード

MN51, MN52, MN61, MN62 シンゲー

ト酸化膜NMOSトランジスタ

\*

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

フロントページの続き

(51) Int.CI.<sup>7</sup>

H 0 3 K 17/687

識別記号

F I

H 0 3 K 17/687

テマコト<sup>®</sup> (参考)

G

A

F ターム(参考) 2H093 NB07 NC03 NC62 NC90

5C006 AA22 BC03 BC11 BF33 BF34

BF50 EB05

5C080 AA10 BB05 CC03 DD19 DD25

FF09 JJ02 JJ03

5J055 AX32 BX16 CX29 DX22 DX42

DX83 EX07 EY01 EY12 EY21

EZ67 GX01 GX02

|                |                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置驱动电路                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP2002268614A</a>                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2002-09-20 |

| 申请号            | JP2001332969                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2001-10-30 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 權奎亨                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 權奎亨                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G02F1/133 G02F1/1333 G09G3/20 G09G3/36 H02H7/00 H02H7/06 H03K17/16 H03K17/687                                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | G09G3/3685 G09G2330/04                                                                                                                                                                                                                                                                                                                                                     |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.612.E G09G3/20.670.M H03K17/16.D H03K17/687.G H03K17/687.A                                                                                                                                                                                                                                                                                 |         |            |

| F-TERM分类号      | 2H093/NB07 2H093/NC03 2H093/NC62 2H093/NC90 5C006/AA22 5C006/BC03 5C006/BC11 5C006/BF33 5C006/BF34 5C006/BF50 5C006/EB05 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD19 5C080/DD25 5C080/FF09 5C080/JJ02 5C080/JJ03 5J055/AX32 5J055/BX16 5J055/CX29 5J055/DX22 5J055/DX42 5J055/DX83 5J055/EX07 5J055/EY01 5J055/EY12 5J055/EY21 5J055/EZ67 5J055/GX01 5J055/GX02 2H193/ZF03 |         |            |

| 代理人(译)         | 萩原诚                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 优先权            | 1020000073804 2000-12-06 KR                                                                                                                                                                                                                                                                                                                                                |         |            |

| 其他公开文献         | <a href="#">JP4157695B2</a>                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                  |         |            |

#### 摘要(译)

解决的问题：在正常情况下，在不降低电路性能的情况下，改善彩色LCD驱动器电路中的ESD特性。提供第一至第N输入垫，第一至第N静电放电保护单元和输出驱动器330。输出驱动器330包括第一至第N电阻器R31至R35，每个电阻器的一侧连接至通过第一至第N输入垫输入的第一至第N电压，以及第一至第N电阻器R31至R35。从通过R35施加的第一至第N电压中的每一个产生用于驱动液晶显示装置的驱动电压。提供第一至第N电阻器R31至R35以在施加静电脉冲时减小在输出驱动器330内部流动的电流。