(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2001 - 27893

(P2001 - 27893A)

(43)公開日 平成13年1月30日(2001.1.30)

| (51) Int.Cl <sup>7</sup> | 識別記号 | 庁内整理番号 | F I           | 技術表示箇所 |

|--------------------------|------|--------|---------------|--------|

| G 0 9 G 3/36             |      |        | G 0 9 G 3/36  |        |

| G 0 2 F 1/133            | 550  |        | G 0 2 F 1/133 | 550    |

| G 0 9 G 3/20             | 622  | 622    | G 0 9 G 3/20  | 622 P  |

|                          | 624  |        |               | 624 B  |

審査請求 有 請求項の数 30 L (全 21数)

(21)出願番号 特願2000 - 167959(P2000 - 167959)

(71)出願人 500261592

權 五敬

大韓民国ソウル市松波區新川洞(番地なし)

ジャンミアパート14 - 1102

(22)出願日 平成12年6月5日(2000.6.5)

(72)発明者

權 五敬

大韓民国ソウル市松波區新川洞(番地なし)

ジャンミアパート14 - 1102

(31)優先権主張番号 1999P20721

(74)代理人 100095957

(32)優先日 平成11年6月4日(1999.6.4)

弁理士 亀谷 美明 (外3名)

(33)優先権主張国 韓国(KR)

(54)【発明の名称】 液晶表示装置のゲートドライバ

(57)【要約】

【課題】 データラインの数を従来の半分の水準に減少させながら同一な画像表現が可能になるようにしてコストの低減を可能にする液晶表示装置及びその駆動回路を提供すること。

【解決手段】 液晶表示装置の走査ラインに駆動信号を与えるゲートドライバは大きくシフトレジスタ部171, ロジック回路部172, レベルシフタ部173, また出力バッファ部174から構成される。ロジック回路部172は3入力オアゲート(O R 1, O R 2, ..., O R n)などで構成され, 各々のオアゲートはシフトレジスタ部171の出力を選択的に3個ずつ入力して論理演算する。

**【特許請求の範囲】**

【請求項1】 第1基板と第2基板また，その間に封入された液晶を含む液晶表示装置の走査ラインに駆動信号を与えるゲートドライバにおいて，水直同期信号のパルスをゲートパルスクロックによってシフトさせるシフトレジスタ部；前記シフトレジスタ部の出力信号のうち，選択的に複数個を入力して論理演算した後出力するロジック回路部；前記ロジック回路部の出力を一定レベルでシフトさせ順次的に出力するレベルシフター部；レベルシフトされた信号を順次走査ラインに与える出力バッフ

10 ア部を含むことを特徴とする液晶表示装置のゲートドライバ。

【請求項2】 前記ロジック回路部はオアゲートなどで構成されることを特徴とする請求項1記載の液晶表示装置のゲートドライバ。

【請求項3】 前記オアゲートなどは3入力オアゲートであることを特徴とする請求項1記載の液晶表示装置のゲートドライバ。

**【発明の詳細な説明】**

**【0001】**

【発明の属する技術分野】本発明は，液晶表示装置のゲートドライバに係り，特に高解像度を保持しながら生産コストが低減できるようにした液晶表示装置のゲートドライバに関する。

**【0002】**

【従来の技術】一般的な液晶ディスプレイ素子(liquid crystal display:LCD)は大きく上板と下板，また上板と下板の間に封入された液晶からなる。上板にはブラックマトリックス，共通電極，色相を表現するためのR(赤)，G(緑)，B(青)のカラーフィルタ層が配設される。下板にはデータラインとゲートラインとが交差しながら配設されてマトリックス形態の画素領域を有する。また各画素領域には一つの薄膜トランジスタ(FET:thin film transistor)と画素電極とが構成される。

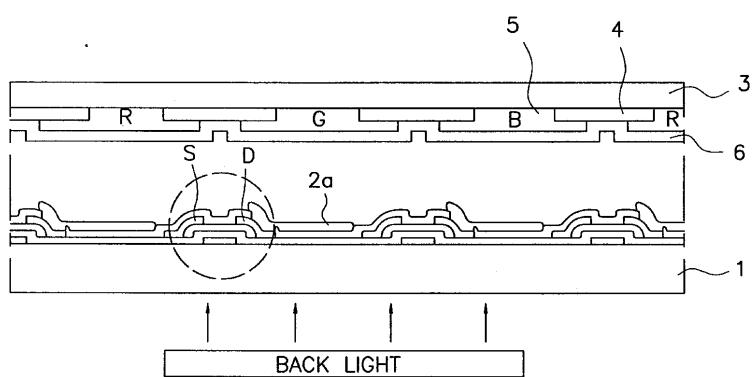

【0003】図24は一般的な液晶ディスプレイ素子の断面構造図である。図24に示したように，下板1には走査ライン(ゲートライン)から延伸されるゲート電極(Gate)と，データラインから延伸されるソース電極S及びドレーン電極Dから構成される薄膜トランジスタが，一定な間隔を置きマトリックスの形態で形成される。

【0004】各画素領域には各薄膜トランジスタ2のドレーン電極Dに連結される画素電極2aが形成される。

【0005】上板3には下板1に形成された画素電極2aを除外した部分で光の透過を遮断するためにブラックマトリックス層4がメッシュ形態で形成される。各ブラックマトリックス層4の間には色を表現するためのR，G，Bカラーフィルタ層5が形成される。また，カラー

フィルタ層5とブラックマトリックス層4とに亘って共通電極6が形成される。

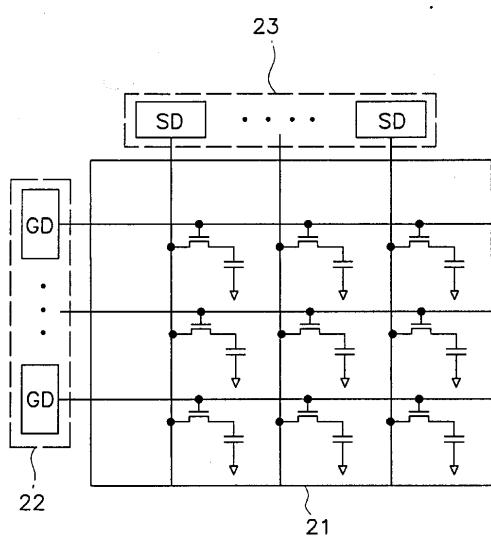

【0006】図25は一般的な液晶ディスプレイ素子の構成図である。図25に示したように下板及び上板またその間に封入された液晶から成り画像をディスプレイするパネル部21と，前記パネル部21のロー方向へ駆動信号を与えるゲートドライバGDから成るゲートドライバ22と，前記パネル部21のカラム方向へ駆動信号を与えるソースドライバSDから成るソースドライバ23とから構成される。

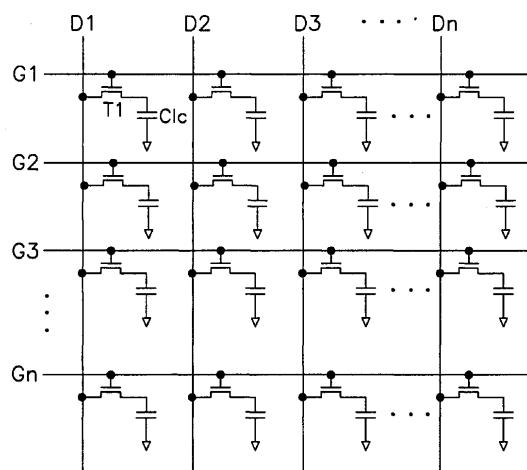

【0007】以下，添付の図面を参照して従来液晶表示装置及びその駆動回路を説明する。図26は従来技術による液晶表示装置の構成図である。図26に示したように，ロー方向に沿って互いに一定間隔を置き複数の走査ライン(G1，G2，…，Gn?1，Gn)などが形成され，各走査ラインなどを横ぎる方向へ複数のデータライン(D1，D2，…，Dn?1，Dn)などが形成される。

【0008】また，走査ラインとデータラインが交差する地点ごとに薄膜トランジスタT1などが構成され，各薄膜トランジスタごとに画素電極C<sub>Lc</sub>が連結される。

【0009】従って，走査ラインに順次駆動電圧が供給されて薄膜トランジスタがターンオンされ，ターンオンされた薄膜トランジスタを介して該当データラインの信号電圧が画素電極へ充電される。

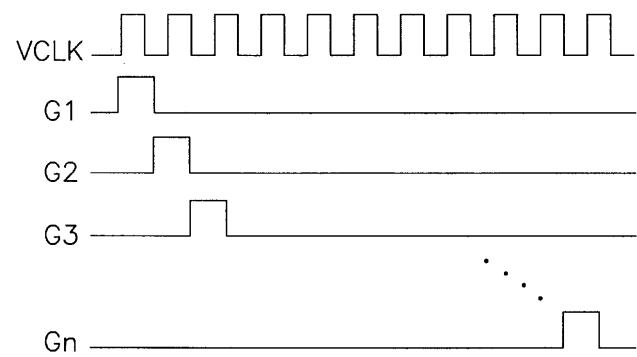

【0010】図27は従来液晶表示装置の走査ラインに与える駆動信号波形図である。図27に示したように1水平周期の間，1番目の走査ラインG1からn番目の走査Gnまで順次駆動信号が与えられるので，該当走査ラインによってターンオンされた薄膜トランジスタを介して該当データラインの信号電圧が画素電極へ伝えられて画像を表示する。

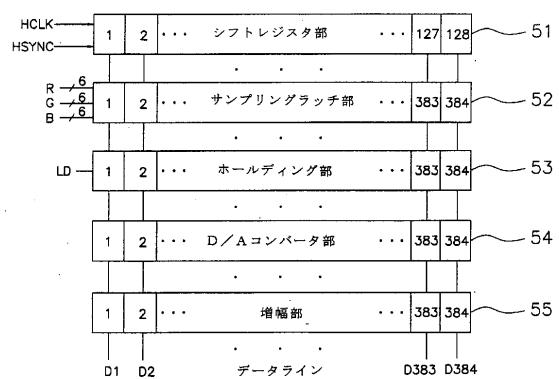

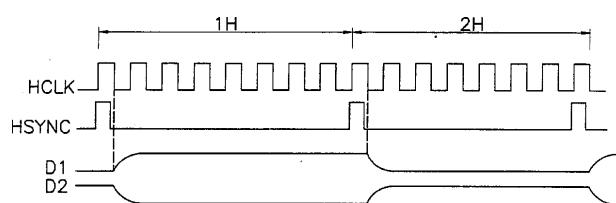

【0011】図28は従来液晶表示装置によるソースドライバの構成図であり，図29はソースドライバの動作波形図である。参考に図28に示したソースドライバは384チャンネル6ビットドライバを示した。即ち，R，G，Bデータが各々6ビットで成され，カラムライン(データライン)は384ラインから構成されたソースドライバである。

【0012】図28に示したように，シフトレジスタ部51と，サンプリングラッチ部52と，ホールディングラッチ部3と，デジタル／アナログコンバータ部54，また增幅部から構成される。

【0013】シフトレジスタ部51は水平同期信号パルス(HSYNC)をソースパルスクロックによってシフトさせてラッチクロックをサンプリングラッチ部52に出力する。

【0014】サンプリングラッチ部52はシフトレジスタ部51から出力されるラッチクロックによってデジタルR，G，Bデータをカラムライン別にサンプリング

してラッチさせる。

【0015】ホールディングラッチ部53はサンプリングラッチ部52にラッチされたR,G,Bデータをロード信号(LD:Load)によって同時に伝達されてラッチされる。

【0016】デジタル/アナログコンバータ部54はホールディングラッチ部53に貯蔵されたR,G,Bデータをロード信号(LD:Load)によって同時に伝えられラッチさせる。デジタル/アナログコンバータ部54はホールディングラッチ部53に貯蔵されたデジタルR,G,BにデータをアナログRGBデータで変換する。

【0017】増幅部55はアナログ信号で変換されたR,G,Bデータを一定幅で増幅してパネルのデータラインで出力する。即ち、1水平周期の間、デジタルR,G,Bデータをサンプルアンドホールディングの後にアナログRGBデータで変換し、これを電流増幅して出力するが、前記ホールディングラッチ部53がn番目のカラムラインに該当するR,G,Bデータをホールデドしていたらサンプリングラッチ部52はn+1番目のカラムラインに該当するR,G,Bデータをサンプリングする。

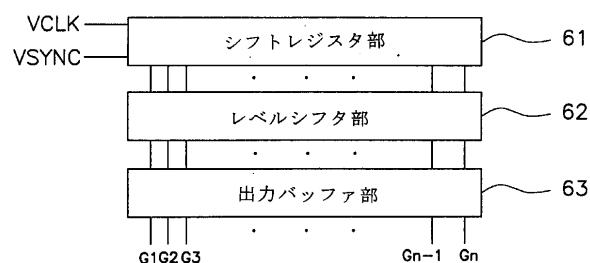

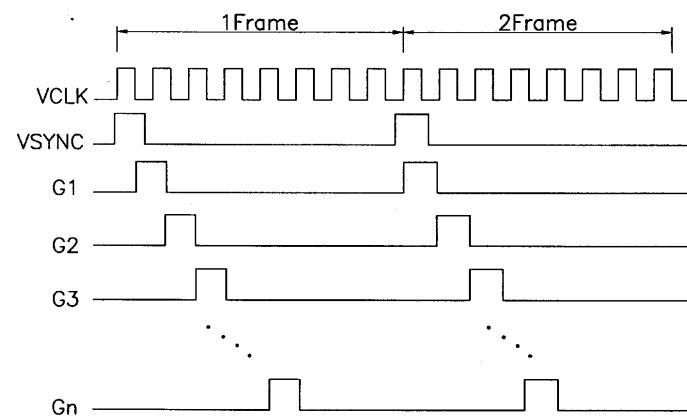

【0018】次に図30は従来液晶表示装置によるゲートドライバの構成図であり、図31はそれによる入力波形図である。図30に示したように、シフトレジスタ部61、レベルシフト部62、また出力バッファ部63から構成される。

【0019】シフトレジスタ部61は垂直同期信号パルス(VSYNC)をゲートパルスクロックによってシフトさせて走査ラインを順次インエーブルさせる。

【0020】レベルシフタ部62は走査ラインに与えられる信号を順次的にレベルシフトさせて出力バッファ部63で出力する。従って、出力バッファ部63と連結された複数の走査ラインは順次的にインエーブルされる。

【0021】以上のように、従来液晶表示装置は各々のデータラインごとに薄膜トランジスタを備えて、走査ラインに順次駆動電圧を供給して薄膜トランジスタをオン/オフさせ、そのうち、ターンオンされた薄膜トランジスタを介して該当データラインの信号電圧を画素領域に伝えて画像を表示する。

【0022】しかしながら、前記のような従来の液晶表示装置は、高解像度及び大型化を満たすためにさらに多い画素を構成しようとする場合、ドライバの数及びサイズが増加してコストが上昇することになり、これはパッケージングのみならず、ドライバとパネルとの間の接続などの新しい問題を生じた。

【0023】

【発明が解決しようとする課題】本発明は、このような問題点に鑑みてなされたもので、その目的とするところは、データラインの数を従来の半分の水準に減少させな

がら同一な画像表現が可能になるようにしてコストの低減を可能にする液晶表示装置及びその駆動回路を提供することである。

【0024】

【課題を解決するための手段】前述した課題を達成するために本発明は、第1基板と第2基板また、その間に封入された液晶を含める液晶表示装置において、第1基板上で一方向へ形成される走査ラインなど、走査ラインなどと交差する方向へ形成されるデータラインなど、各データラインの両側に各々形成される第1画素領域など及び第2画素領域など、データラインに格納された画像信号を第1画素領域に選択的に伝えるための第1スイッチング部、データラインに格納された画素信号を第2画素領域に選択的に伝えるための第2スイッチング部を含めて構成され、液晶表示装置のソースドライバは、第1基板と第2基板また、その間に封入された液晶を含める液晶表示装置のデータラインに画像信号を与えるソースドライバにおいて、水平同期信号のパルスをシフトさせてラッチクロックを出力するnクロックシフトレジスタ部、シフトレジスタ部から出力されるラッチクロックによって2n個のカラムラインのうち奇数番目のカラムラインに該当するデジタル画像信号をサンプリングしてラッチさせる第1サンプリングラッチ部、シフトレジスタ部から出力されるラッチクロックによって2n個のカラムラインのうち、偶数番目のカラムラインに該当するデジタル画像信号をサンプリングしてラッチさせる第2サンプリングラッチ部、第1ロード信号によって前記第1サンプリングラッチ部に貯蔵されたデータが伝えられてラッチされ、第2ロード信号によって前記第2サンプリングラッチ部に貯蔵されたデータが伝えられてラッチされるホールディングラッチ部、ホールディングラッチ部に貯蔵された奇数番目のカラムラインに該当するデジタル画像信号または偶数番目のカラムラインに該当するデジタル画像信号をアナログデータに切り換えるD/Aコンバータ部、D/Aコンバータ部から出力される奇数番目のカラムラインに該当するアナログ画像信号または偶数番目のカラムラインに該当するアナログ画像信号を一定幅で増幅させる増幅部を含めて構成する。

【0025】そして本発明は、第1基板と第2基板また、その間に封入された液晶を含む液晶表示装置の走査ラインに駆動信号を与えるゲートドライバにおいて、垂直同期信号のパルスをゲートパルスクロックによってシフトさせるシフトレジスタ部、シフトレジスタ部の出力信号のうち、選択的に複数個を入力して論理演算した後出力するロジック回路部、ロジック回路部の出力を一定レベルでシフトさせ順次的に出力するレベルシフター部、レベルシフトされた信号を順次走査ラインに与える出力バッファ部を含むことを特徴とする液晶表示装置のゲートドライバである。

【0026】ロジック回路部はオアゲートなどで構成さ

れ、さらに3入力オアゲートであることを特徴とする。

#### 【0027】

【発明の実施の形態】以下、図面に基づいて、本発明の実施の形態を詳細に説明する。まず、本発明の一実施の形態による液晶表示装置は隣接した二つの走査ラインに与える駆動信号を制御して一つのデータラインへその両側の画素領域に画像信号を伝えられるようにしてデータラインの数を半分で減少させるのにその特徴がある。

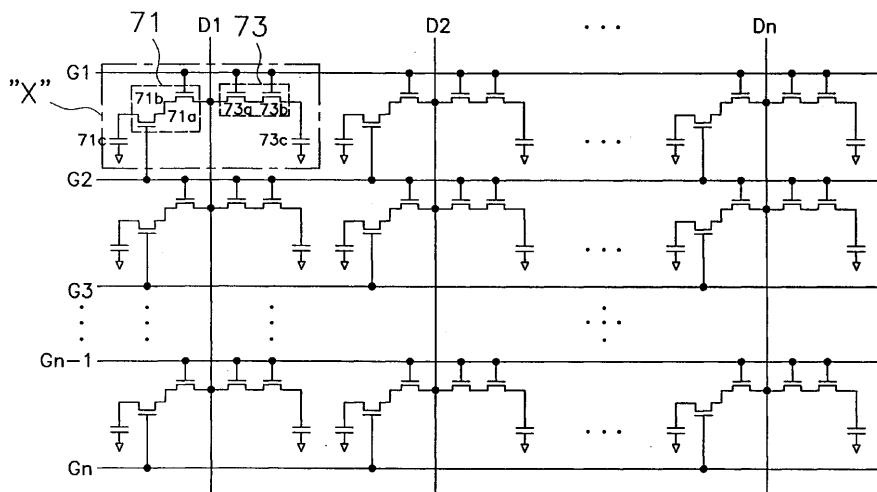

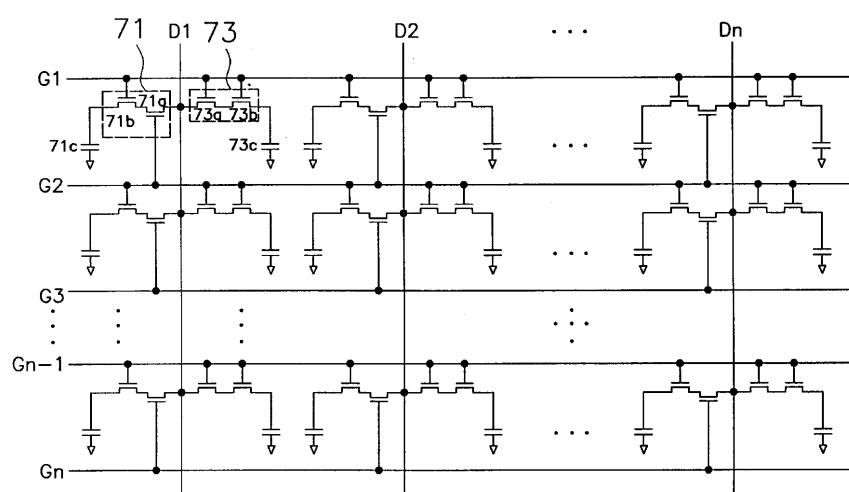

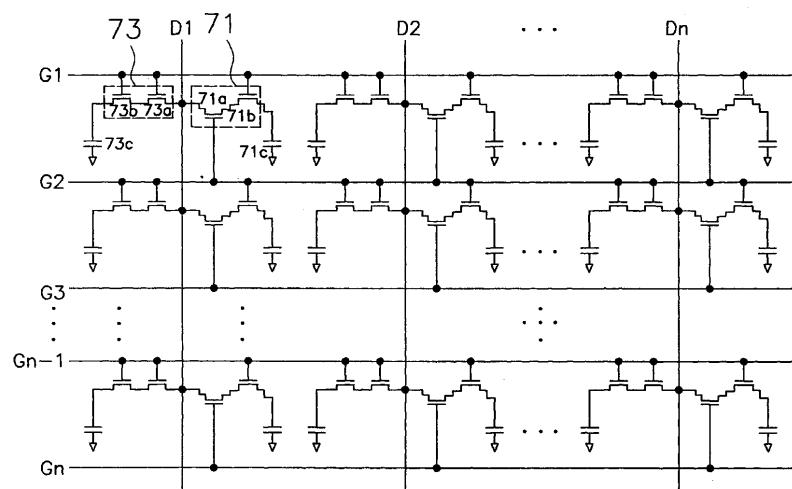

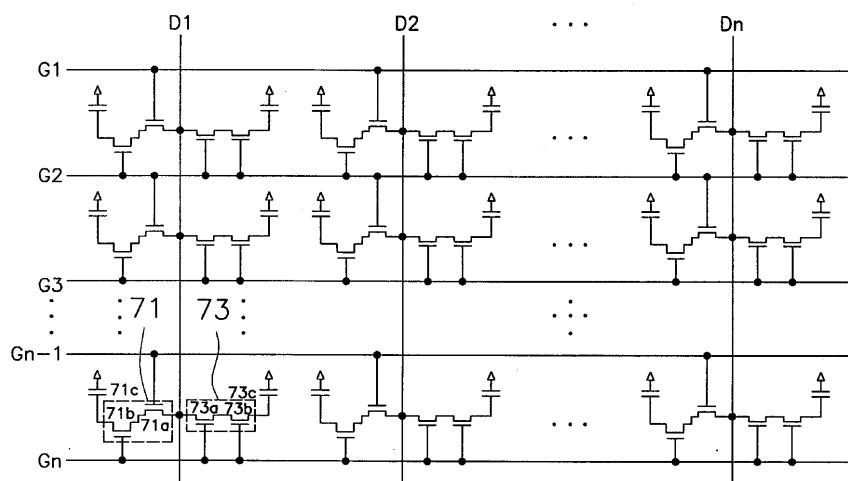

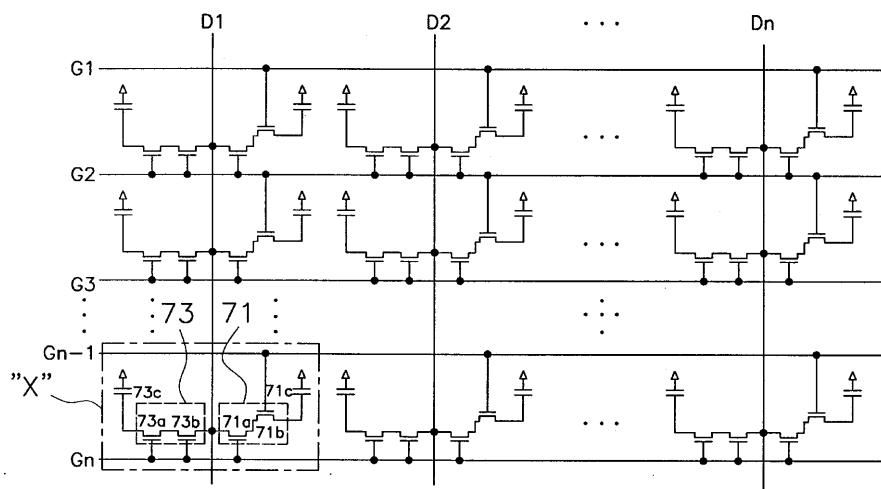

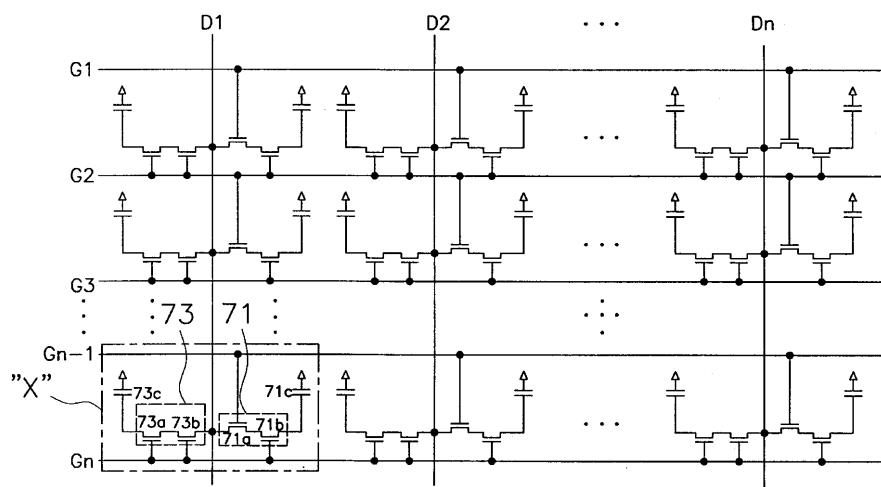

【0028】図1は本発明の第1実施例による液晶表示装置の構成図である。図1に示したようにロー方向へ走査ライン( $G_1, G_2, \dots, G_n ? 1, G_n$ )などが形成され、走査ライン( $G_1, G_2, \dots, G_n ? 1, G_n$ )などを横きるカラム方向へデータライン( $D_1, D_2, \dots, D_n ? 1, D_n$ )が交差する地点でデータライン( $D_1, D_2, \dots, D_n ? 1, D_n$ )を中心に左側の画素領域に画像信号を伝える第1スイッチング部71が形成され、データラインを中心に右側の画素領域に画像信号を伝える第2スイッチング部73が形成される。

【0029】また、第1スイッチング部71には第1画素電極71cが連結され、第2スイッチング部73には第2画素電極73cが連結される。ここで、前記第1スイッチング部71と、第2スイッチング部73は薄膜トランジスタから構成し、前記薄膜トランジスタはNタイプの薄膜トランジスタまたはPタイプの薄膜トランジスタから構成する。

【0030】また、図1の”X”部分を中心により詳細に説明する。データラインD1の左側に構成される第1スイッチング部71は、ソースまたはドレーンがデータラインD1に連結されゲートが該当走査ラインG1に連結された第1薄膜トランジスタ71aと、前記第1薄膜トランジスタ71aと直列で連結され、ゲートが次の走査ラインG2に連結される第2薄膜トランジスタ71bから構成される。

【0031】前記第2薄膜トランジスタ71bには第1画素電極71cが連結されて前記第1、第2薄膜トランジスタ71a、71bなどのオン／オフ動作によって選択的に画像信号が伝えられる。

【0032】前記データラインD1の右側に構成される第2スイッチング部73はゲートが該当走査ラインG1に連結され、ソースまたはドレーンがデータラインD1に連結される第3薄膜トランジスタ73aと、前記第3薄膜トランジスタ73aと直列で連結され、ゲートが該当走査ラインG1に連結される第4薄膜トランジスターから構成される。ここで、前記第2スイッチング部73は第3薄膜トランジスタ73aのみを構成することもできる。

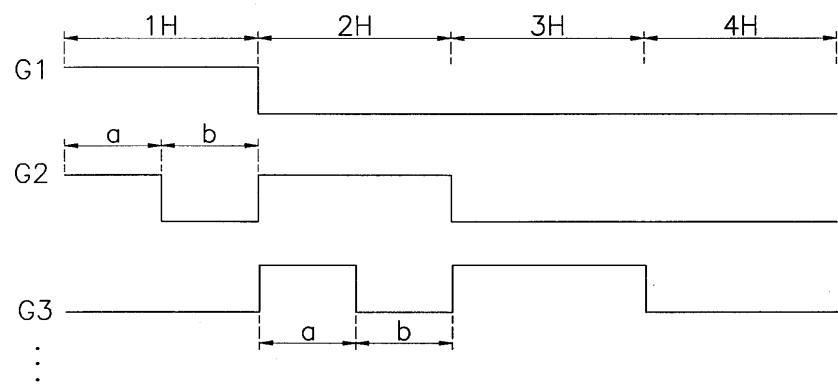

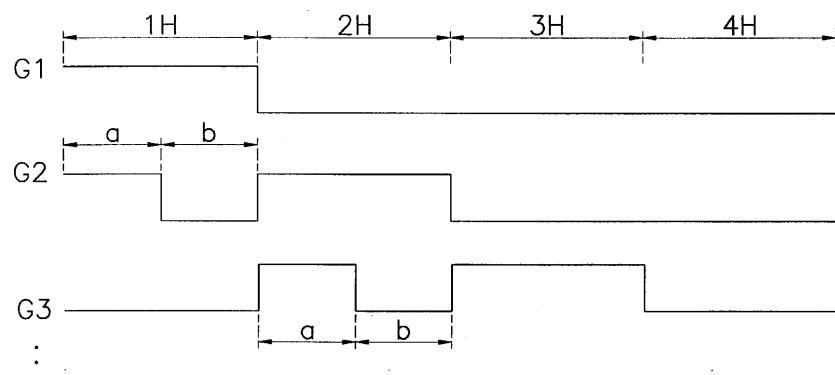

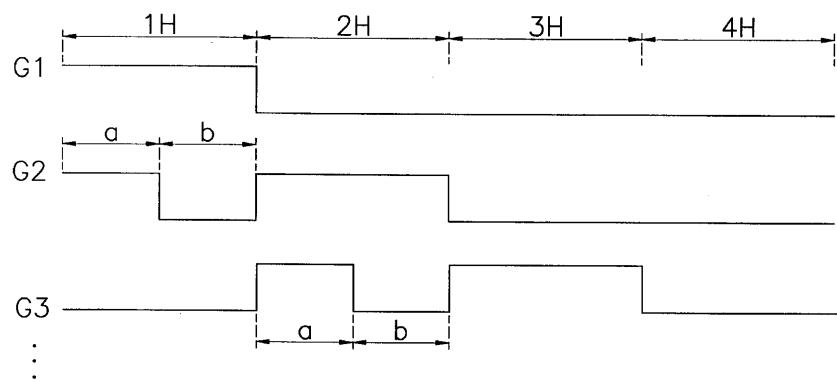

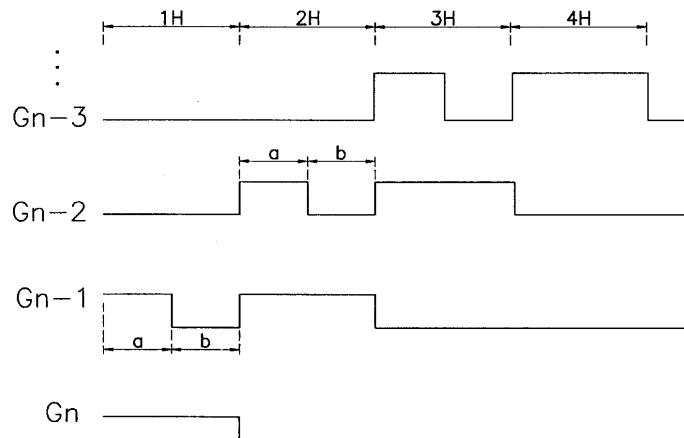

【0033】このように構成された本発明の第1実施例による液晶表示装置において、第1画素電極と第2画素電極に画像信号を伝える過程を図2に示した波形図を参

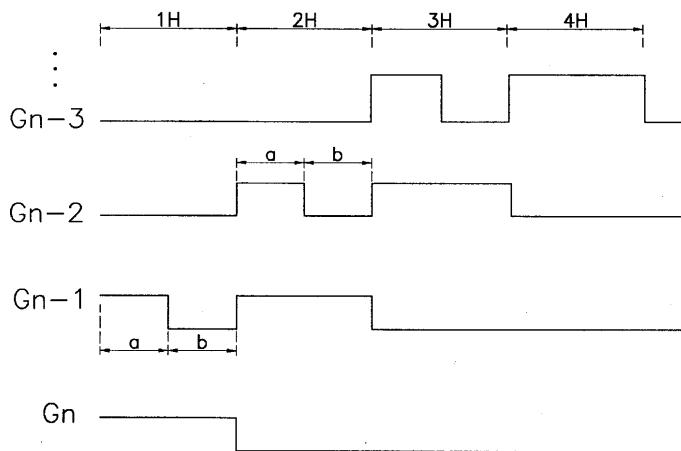

照して説明する。図2は本発明の第1実施例による液晶表示装置の走査ラインに与える駆動信号の波形を示すものである。

【0034】図2に示したように1水平周期を2区間に分けて第1区間aではデータライン( $D_1, D_2, \dots, D_n ? 1, D_n$ )を中心に左側と右側の画素領域に画像信号を与え、第2区間bでは右側の画素領域だけに画像信号を与える。即ち、1番目の走査ラインG1では1水平周期の間にハイ信号を与え、2番目の走査ラインG2に1/2水平周期の間(正確に1/2ではなくても構わない)、即ち、a区間の間だけハイ信号を与え、余分の1/2水平周期の間にはロー信号を与える。

【0035】従って、1番目の走査ラインG1と、2番目の走査ラインG2が全てのハイの間には第1スイッチング部71を構成している第1、第2薄膜トランジスタ71a、71bと第2スイッチング部73を構成している第3、第4薄膜トランジスタ73a、73bが全てターンオンの状態となって第1画素電極71cと第2画素電極73cに画像信号が伝えられる。

【0036】その後、2番目の走査ラインG2にロー信号を与えると、第2薄膜トランジスター71bがターンオフ状態となって第1画素電極71cには画像信号が伝えられず第2画素電極73cだけに画像信号が伝えられる。

【0037】このように1水平周期を2区間a、bに分けて一つのデータラインに格納された画像信号を左側及び右側の画素電極に選択的に伝えられる。結果的に走査ラインに与えられる駆動信号を制御して一つのデータラインが左側と右側の画素領域に画像信号を伝えるのでデータラインの数を従来に比べて半分に減少させることができ、これによってソースドライバの数も半分に減少させることができる。

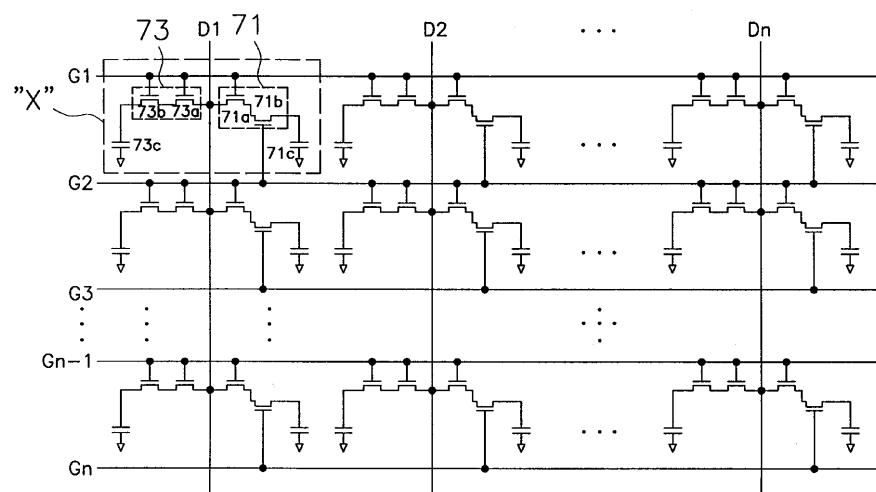

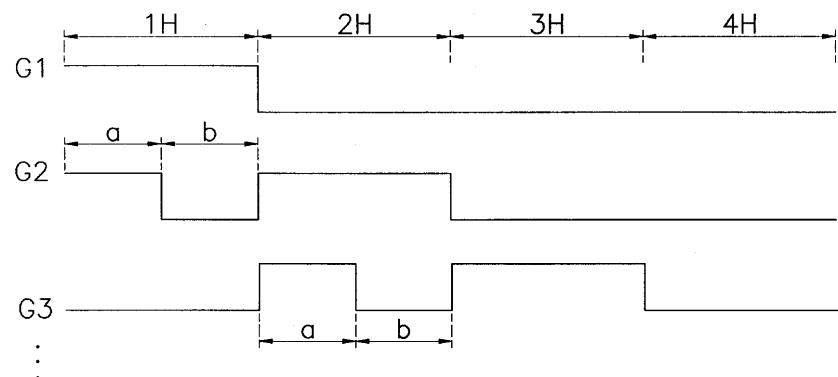

【0038】続いて、図3は本発明第2実施例による液晶表示装置の構成図である。図3に示したように、前記の第1実施例と比較して第1スイッチング部71を構成している第1薄膜トランジスタ71aと第2薄膜トランジスタ71bのゲート接続部位が相異することがわかる。

【0039】即ち、本発明の第2実施例による第1スイッチング部71はソースまたはドレーンがデータラインD1に連結され、ゲートが次回の走査ラインG2に連結される第1薄膜トランジスター71aと前記第1薄膜トランジスタ71aと直列で連結され、ゲートは該当走査ラインG1に連結される第1薄膜トランジスタ71bから構成される。このとき、第2スイッチング部73は第1実施例による構成と同一である。

【0040】このような本発明の第2実施例による液晶表示装置において走査ライン図4のような波形を与えると、液晶パネルの上端から下端へ移動しながら画像が表示され、一つのデータラインが左側と右側の画素領域に

画像信号を伝えてデータラインの数を減少することができる。

【0041】なお、図5は本発明の第3実施例による液晶表示装置の構成図であり、図6は走査ラインに与えられる駆動信号の波形図である。図5に示したように、本発明の第3実施例は第1スイッチング部71を前記データライン(D1, D2, …, Dn?1, Dn)の右側に構成し、第2スイッチング部73を右側に構成した。

【0042】即ち、本発明の第1、第2実施例では前記第1スイッチング部71をデータライン(D1, D2, …, Dn?1, Dn)の左側に構成したが、本発明の第3実施例では右側に構成した。このような本発明の第3実施例による液晶表示装置はローフィールドへ形成された複数の走査ライン(G1, G2, …, Gn?1, Gn)などと、前記走査ラインと交差する方向へ形成されたデータライン(D1, D2, …, Dn?1, Dn)と、各走査ラインと交差するデータライン(D1, D2, …, Dn?1, Dn)の左側に形成される第1スイッチング部71と、前記データライン(D1, D2, …, Dn?1, Dn)の左側に形成される第2スイッチング部73と、前記第1スイッチング部73に連結された第2画素電極73cから構成される。

【0043】これを図5の”X”部分を中心に、より詳細に説明する。第1スイッチング部71は走査ラインG1とデータラインD1が交差する地点でデータラインの右側に形成され、第1スイッチング部71を構成する第1薄膜トランジスタ71aと第2薄膜トランジスタ71bのうち、第2薄膜トランジスタ71bのゲートが次回の走査ラインG2に連結される。

【0044】即ち、ソースまたはドレーンがデータラインD1に連結され、ゲートが該当走査ラインG1に連結される第1薄膜トランジスタ71aと、第1薄膜トランジスタ71aと直列で連結され、ゲートが次回の走査ラインG2に連結される第2薄膜トランジスタ71bから構成される。

【0045】また、第2スイッチング部73はデータラインD1を中心に左側に形成され、二つの薄膜トランジスタから構成される。

【0046】即ち、ソースまたはドレーンがデータラインD1に連結され、ゲートが該当走査ラインG1に連結される第3薄膜トランジスタ73aと、第3薄膜トランジスター73aと直列で連結されゲートが該当走査ラインG1に連結される第4薄膜トランジスタ73bから構成される。ここで、第2スイッチング部73は一つの薄膜トランジスタから構成することができる。

【0047】このように構成された本発明の第3実施例に液晶表示装置は走査ラインに図6のような駆動信号を与える。図6に示したように、1水平周期の間に1番目の走査ラインG1にはハイ信号を与え、2番目の走査ラ

インG2にa区間の間だけハイ信号を与え、b区間の間にはロー信号を与える。

【0048】従って、1番目の走査ラインG1と2番目の走査ラインG2に全てハイ信号が与える場合には第1スイッチング部71及び第2スイッチング部73を構成している薄膜トランジスタが全てターンオンされて第1画素電極71cと第2画素電極73cに画像信号が伝えられる。

【0049】この後、1番目の走査ラインG1にはハイ信号が与えられ、2番目の走査ラインG2にロー信号が与えられる場合には第1スイッチング部71を構成している第2薄膜トランジスター71bがターンオフ状態となるので第1画素電極71cには画像信号が伝えられず第2画素電極73cだけに画像信号が伝えられる。このような過程を介して液晶パネルの上端から下端へ移動しながら画像が表示される。

【0050】なお、図7は本発明の第4実施例による液晶表示装置の構成図であり、図8は図7による波形図である。図7に示したように、本発明の第4実施例には20第3実施例と比較して第1スイッチング部71を構成している第1、第2薄膜トランジスター71a, 71bのゲート接続部位を異にして構成したものである。

【0051】即ち、第3実施例には第1スイッチング部71を構成している第1薄膜トランジスタ71aと第2薄膜トランジスタ71bのうち、第2薄膜トランジスタ71bのゲートが次回の走査ラインG2に連結されているが、本発明の第4実施例では第1薄膜トランジスタ71aのゲートが次回の走査ラインG2に連結されるよう構成した。

【0052】即ち、本発明第4実施例による第1スイッチング部71はソースまたはドレーンがデータラインD1に連結され、ゲートが次回走査ラインG2に連結される第1薄膜トランジスタ71aと直列で連結され、ゲートが該当走査ラインG2に連結される第2薄膜トランジスター71bで構成される。

【0053】従って、図8のように走査ラインに駆動信号を与えるとデータラインD1を中心に左側と右側に選択的に画像信号を与えることができる。また、画像は液晶パネルの上端から下端へ移動しながらディスプレイされる。

【0054】続いて、図9は本発明の第5実施例による液晶表示装置の構成図であり、図10は走査ラインに与える駆動信号の波形を示した。第5実施例には第1、第2スイッチング部を構成している薄膜トランジスタが形成される位置において、第1実施例ないし第4実施例の構成と差がある。

【0055】即ち、本発明の第1実施例ないし第4実施例にはデータライン(D1, D2, …, Dn?1, Dn)と走査ライン(G1, G2, …, Gn?1, Gn)とが交差する地点に薄膜トランジスタ及び画素電

極が形成されるが、前記データラインに対して1番目の走査ラインとの交差点から順次2番目、3番目、…、n番目の走査ラインと交差点に形成される。また、データラインとn番目の走査ラインが交差する地点では薄膜トランジスター及び画素電極が形成されない。

【0056】しかしながら、本発明の第5実施例ではデータラインに対して1番目の走査ラインが交差する地点には薄膜トランジスタ及び画素電極が形成されず、2番目の走査ラインから3番目、4番目、…、n番目走査ラインが交差する地点に薄膜トランジスタ及び画素電極が形成される。

【0057】本発明の第1実施例ないし第4実施例では走査ラインとデータラインが交差する地点に形成される4個の薄膜トランジスタなどのうち、いずれかの一つが次回の走査ラインに連結されたが、第5実施例では4個の薄膜トランジスタのうち、いずれかの一つが以前走査ラインに連結される構造を有する。

【0058】このような本発明の第5実施例の場合、図10のように走査ラインに駆動信号を与えると液晶パネルの下端から上端へ移動しながら画像が表示される。図10に示したように、1水平周期を2区間a、bに分けて走査ラインに駆動信号を与えることによってデータラインを中心に左側と右側の画素領域に選択的に画像信号を与えることができる。

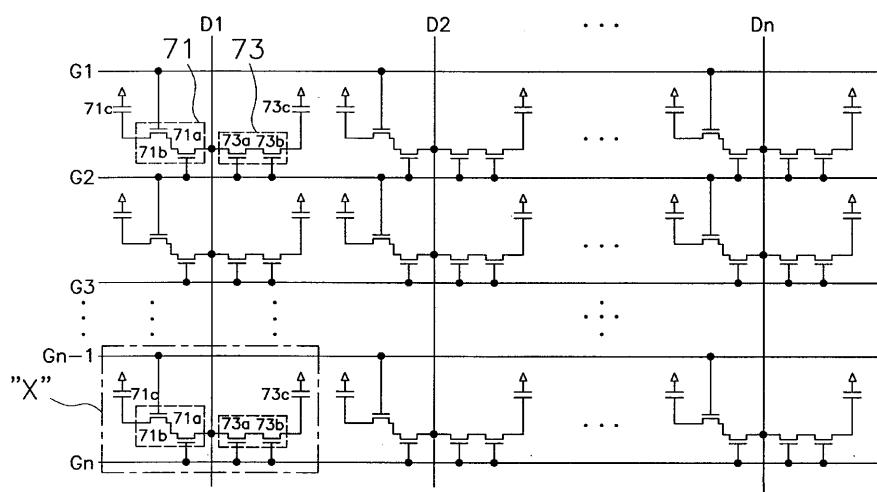

【0059】これをより詳細に説明すると次のようである。図9に示したように一方向へ複数の走査ライン(G1, G2, …, Gn?1, Gn)が形成され、各々走査ラインなどと交差する方向へデータライン(D1, D2, …, Dn?1, Dn)が形成される。各データライン(D1, D2, …, Dn?1, Dn)の左側には第1スイッチング部71が構成され、右側には第2スイッチング部73が構成される。

【0060】第1スイッチング部71及び第2スイッチング部73は薄膜トランジスタから構成され前記薄膜トランジスタはNタイプの薄膜トランジスタまたはPタイプの薄膜トランジスタから構成される。

【0061】前記データラインD1の左側には構成される第1スイッチング部71のうち、第2薄膜トランジスタ71bのゲートは以前走査ライン(Gn?1)に連結され第1薄膜トランジスタ71aのゲートは該当走査ラインGnに連結される。

【0062】各々データライン(D1, D2, …, Dn?1, Dn)の右側に形成される第2スイッチング部73は二つの薄膜トランジスタから構成され、前記二つの薄膜トランジスタ(第3、第4薄膜トランジスタ)のゲートは全て該当走査ラインGnに連結される。ここで、前記第2スイッチング部73を一つの薄膜トランジスタから構成することもできる。

【0063】これを図9の”X”部分を中心により詳細に説明する。図10に示したように1水平周期の間に該

当走査ラインにはハイ信号を与え、以前走査ラインGn?1は第1区間aの時だけハイ信号を与える。従って、該当走査ラインGnと以前走査ラインGn?1が全てハイである区間では第1、第2スイッチング部70, 73を構成している薄膜トランジスタなどが全てターンオン状態となって第1、第2画素電極71c, 73cに画像信号が伝えられる。

【0064】次に第2区間bの時には以前走査ライン(Gn?1)にロー信号を与えると前記第1スイッチング部71を構成している第2薄膜トランジスタ71bがターンオフ状態となって第1画素電極71cには画像信号が伝えられない。代わりに、データラインの右側の第2スイッチング部73は相変わらずターンオン状態を保持することになって前記第2画素電極73cだけに画像信号が伝えられる。

【0065】このようにデータラインを中心に左側と右側に選択的に画像信号を伝えることができ、データラインの数を半分に減少することができる。

【0066】図11は本発明の第6実施例による液晶表示装置の構成図であり、図12は本発明の第6実施例による液晶表示装置の走査ラインに与えられる駆動信号を波形図を示したものである。本発明の第6実施例による液晶表示装置は本発明の第5実施例と比較して第1スイッチング部71を構成している第1薄膜トランジスタ71aと第2薄膜トランジスタ71bのゲート接続部位が相異することがわかる。

【0067】即ち、本発明の第5実施例では第1薄膜トランジスタ71aのゲートが該当走査ラインGnに連結され、第2薄膜トランジスタ71bのゲートは以前走査ラインGn?1に連結されたが、本発明の第6実施例では第1薄膜トランジスタ71aのゲートが以前走査ラインGn?1に連結され、第2薄膜トランジスタ71bのゲートが該当走査ラインGnに連結される。このとき、第2スイッチング部73は第5実施例の構成と同一である。

【0068】このように走査ラインに図12のように駆動信号を与えると一つのデータラインを中心に左側と右側に選択的に画像信号を伝えられる。また、第5実施例と同じく液晶パネルの下端から上端へ移動しながら画像が表示される。

【0069】次に、図13は本発明の第7実施例による液晶表示装置の構成図であり、図14は走査ラインに与える駆動信号の波形図である。図13に示したように、本発明の第7実施例による液晶表示装置はデータラインを中心に右側に第1スイッチング部を構成し左側に第2スイッチング部を構成した。

【0070】図13のように一方向へ形成された走査ラインなど(G1, G2, …, Gn?1, Gn)、前記走査ラインと交差する方向へ形成されたデータライン(D1, D2, …, Dn?1, Dn)と、前記走査

ラインとデータラインが交差する地点でデータラインの両側に形成され、前記該当走査ラインと以前走査ラインによって制御される第1スイッチング部71及び第2スイッチング部73と、前記第1スイッチング部71と連結される第1画素電極71cと、前記第2スイッチング部73と連結される第2画素電極73cを含めて構成される。

【0071】これを図13の”X”部分をより詳細に説明すると次のようである。第1スイッチング部71はソースまたはドレーンがデータラインD1に連結され、ゲートが該当走査ラインGnに連結される第1薄膜トランジスタ71aと前記第1薄膜トランジスタ71aと直列で連結され、ゲートが以前走査ラインGn?1に連結される第2薄膜トランジスタ71bから構成される。

【0072】また、第2スイッチング部73はソースまたはドレーンがデータラインD1に連結されゲートが該当走査ラインGnに連結される第3薄膜トランジスタ73aと、前記第3薄膜トランジスタ73aと直列で連結されゲートが該当走査ラインGnに連結される第4薄膜トランジスタ73bから構成される。

【0073】前記第2スイッチング部73は第3薄膜トランジスタ73aだけを構成することができる。

【0074】このように構成された液晶表示装置の走査ラインに図14のように駆動信号を与えると、液晶パネルの下端から上端の方へ移動しながら画像が表示される。これは前記で説明した第5、第6の実施例と同じである。

【0075】なお、図15は本発明の第8実施例による液晶表示装置の構成図であり、図16は走査ラインに与えられる駆動信号の波形図である。本発明の第8実施例では第7実施例と比較して第1スイッチング部を構成している第1薄膜トランジスタ71aのゲートと第2薄膜トランジスタ71bのゲートの接続部位が相異する。

【0076】即ち、本発明の第8実施例による第1スイッチング部71はソースまたはドレーンがデータラインD1に連結され、ゲートが以前走査ライン(Gn?1)に連結される第1薄膜トランジスタ71aと、前記第1薄膜トランジスタ71aと直列で連結されゲートが該当走査ライン(Gn)だけに連結される第2薄膜トランジスタ71bから構成される。

【0077】ここで前記第2スイッチング部73は第7実施例による第2スイッチング部73と同一な構成を有する。

【0078】このような本発明の第8実施例による液晶表示装置の走査ラインに図16のように駆動信号を与えると液晶パネルの下端から上端の方へ移動しながら画像が表示される。

【0079】以上のように、本発明の一実施の形態による液晶表示装置は、一つのデータラインがその左側と右側の画素領域に画像信号を伝えられるようにして、デー

50 タラインの数を半分に減らすことができる。

【0080】このようにデータラインの数を半分で減らすことができるのでデータラインに駆動信号を与えるソースドライバの数も半分に減らすことができる。

【0081】以下、本発明の一実施の形態による液晶表示装置を駆動するための駆動回路について説明する。前記の本発明の一実施の形態による液晶表示装置はデータラインの数を半分に減少することができるが、これを満足させるためにはソースドライバの構成が変わらなければならない。

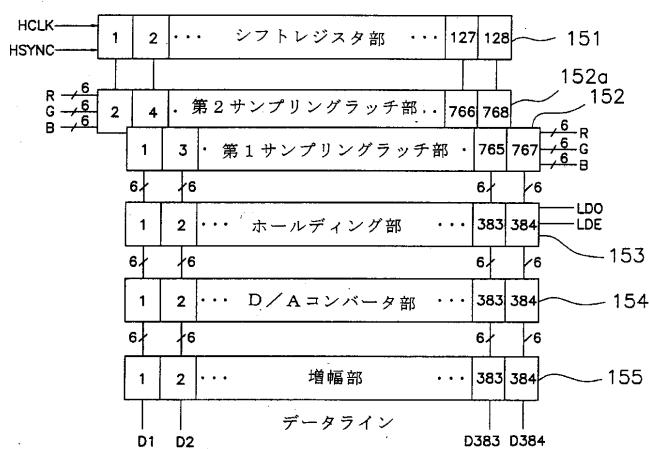

【0082】即ち、本発明の一実施の形態による液晶表示装置を駆動するためのソースドライバはデータラインが384ラインであれば総768ラインに相応する画像信号をハンドリングしなければならない。

【0083】このためにソースドライバを図17のように構成することができる。図17は本発明の一実施の形態によるソースドライバの第1実施例を示している。図17に示したソースドライバは従来のソースドライバと比較してサンプリングラッチ部のセル数を2倍に増加させた。これは本発明の一実施の形態によるソースドライバは384個のデータラインを駆動するが、実質的に784ラインの画像データをハンドリングをしなければならないからである。

【0084】図17に示したように、水平同期信号のパルスをソースパルスクロックによってシフトさせてラッチクロックを出力する384クロックシフトレジスタ部100と、シフトレジスタ部151から出力されるラッチクロックによって768個のカラムラインのうち、奇数番目のカラムラインに該当するデジタルR,G,Bデータをサンプリングしてラッチさせる第1サンプリングラッチ152と、偶数番目のカラムラインに該当するデジタルR,G,Bデータをサンプリングしてラッチさせる第2サンプリングラッチ部152aと、第1ロード信号によって第1サンプリングラッチ部152に貯蔵されたデータが伝えられてラッチされ、第2ロード信号によって第2サンプリングラッチ部152aに貯蔵されたデータが伝えられてラッチされるホールディングラッチ153と、ホールディングラッチ部153に貯蔵された奇数番目のカラムに該当するデジタルR,G,Bデータ

40 または偶数番目のカラムに該当するディジタルR,G,Bデータをアナログデータで変換するD/Aコンバータ部154と、D/Aコンバータ154から出力される奇数番目のカラムに該当するアナログR,G,Bデータまたは偶数番目のカラムに該当するアナログR,G,Bデータの電流を一定幅で増幅させる増幅部155から構成される。

【0085】このように本発明の第1実施例によるソースドライバは総768個のカラムラインのうち、奇数番目のカラムラインに該当する画像データをサンプリングしてラッチさせる第1サンプリングラッチ部152と、

偶数番目のカラムラインに該当する画像データをサンプリングしてラッチさせる第2サンプリングラッチ部152aとから構成される。

【0086】即ち、1水平周期を2区間に分けて1/2水平周期の間（正確に1/2ではなくても構わない）には奇数番目のカラムラインに該当するR,G,Bデータを第1サンプリングラッチ部152でサンプリング及びラッチさせ、余分の1/2水平周期の間には偶数番目のカラムラインに該当するR,G,Bデータを第2サンプリングラッチ部152aでサンプリング及びラッチせ10する。

【0087】従って、総768個のカラムラインに該当するR,G,Bデータをサンプリングすることができる。

【0088】このように第1サンプリングラッチ部152と、第2サンプリングラッチ部152aに分けてラッ15チされたデジタル画像信号は順次ホールディングラッチ153へ伝えられる。

【0089】即ち、第1ロード信号によって第1サンプリングラッチ部152に貯蔵された画像データがホール20ディングラッチ部153にロードされ、第2ロード信号によって第2サンプリングラッチ部152aに貯蔵された画像データがホールディングラッチ部153にロードされる。

【0090】ホールディングラッチ部153にロードされたR,G,BディジタルデータはD/Aコンバータ部154でアナログ信号に変換され、アナログ信号に変換されたR,G,Bデータは増幅部155で電流が増幅される。

【0091】また、1/2水平周期の間に奇数番目のカラムラインに該当するR,G,Bデータがパネルに与えられて表示され、余分の1/2水平周期の間には偶数番目のカラムラインに該当するR,G,Bデータがパネルに与えられて表示される。30

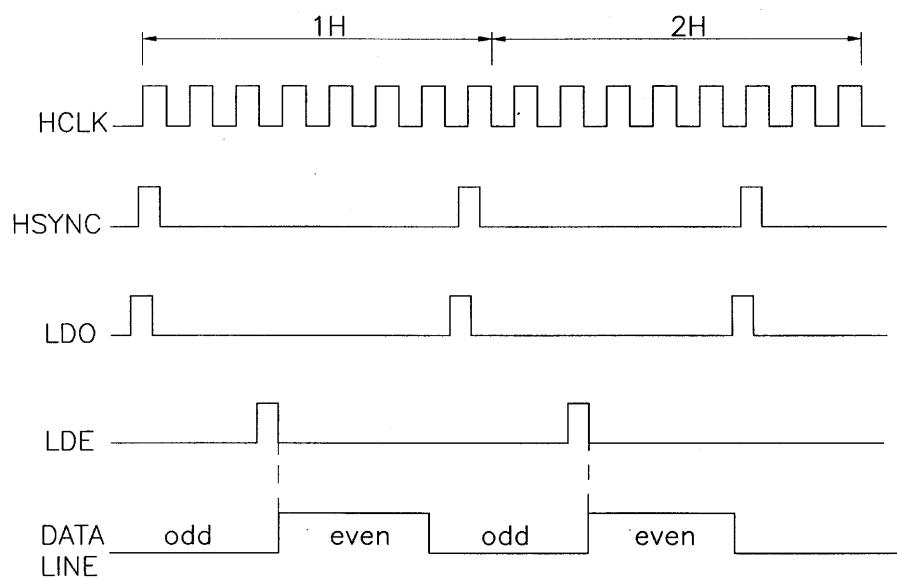

【0092】図18は図17によるソースドライバの動作波形図を示したもので1水平周期の間に奇数番目のカラムラインをサンプリングしたデジタルデータと偶数番目のカラムラインをサンプリングしたデジタルデータがホールディング部153でロードされることがわかる。

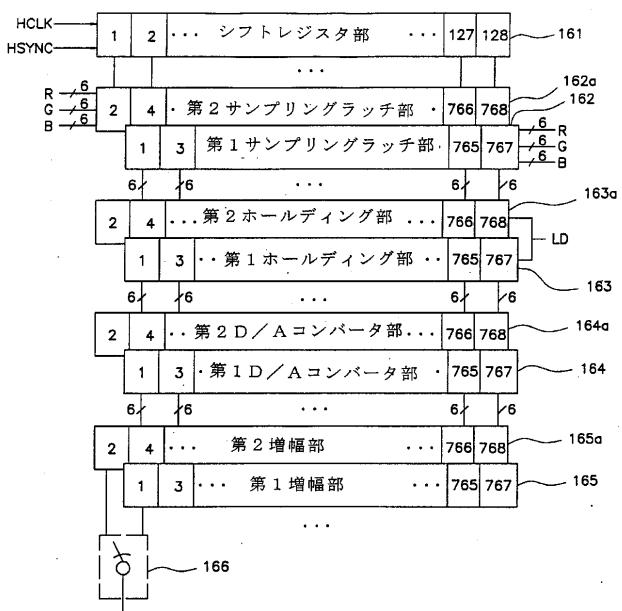

【0093】図19は本発明によるソースドライバの他の実施例を示した。図19に示したソースドライバは1水平周期の間に奇数番目のカラムラインと偶数番目まカラムラインに分けて液晶パネルに与えるために、サンプリングラッチ部162,162a,ホールディングラッチ部163,162a,DAC部164,164a,増幅部165,165aを各々二つずつ構成したものである。40

【0094】また、二つの増幅部165,165aの出力を選択的にデータラインに伝達するためにはスイッチング部166がさらに構成される。

【0095】従って、第1サンプリングラッチ部162は奇数番目のカラムラインに該当する画像信号をサンプリングし、第2サンプリングラッチ部162aは偶数番目のカラムラインに該当する画像信号をサンプリングする。

【0096】また、第1サンプリングラッチ部162にラッ10チされた奇数番目のカラムラインに該当する画像信号は、ロード信号LDによって奇数番目のカラムラインに該当する画像信号を貯蔵する第1ホールディングラッチ部163にロードされる。

【0097】第2サンプリングラッチ部162aにラッチされた偶数番目のカラムラインに該当する画像信号は、ロード信号LDによって偶数番目のカラムラインに該当する画像信号を貯蔵する第2ホールディングラッチ部163aにロードされる。

【0098】その後、第1ホールディングラッチ部163に貯蔵されたデジタル画像信号は第1DAC部164でアナログ信号に変換され、第2ホールディングラッチ部163aに貯蔵された画像信号を第2DAC部164aでアナログ信号に変換される。

【0099】ここで、第1DAC部164は奇数番目のカラムに該当するデジタル画像信号をアナログ信号に変換し、第2DAC部164aは偶数番目のカラムに該当するデジタル画像信号をアナログ信号に変換する。

【0100】アナログ信号に変換された奇数番目及び偶数番目のカラムに該当する画像信号をさらに一定幅で増幅させるが、前記増幅部または奇偶番目のカラムに該当するアナログ信号を増幅する第1増幅部165と偶数番目のカラムに該当するアナログ信号を増幅する第2増幅部165aで構成される。

【0101】従って、1/2水平周期の間には前記スイッチング166の動作によって奇数番目のカラムラインに該当するアナログ画像信号がデータラインに与えられ、余分の1/2水平周期の間には偶数番目のカラムラインに該当するアナログ画像信号がデータラインに与えられる。

【0102】ここで、前記スイッチング部166は1/2水平周期の間には第1増幅部165の出力とデータライン(D1,D2,...,Dn?1,Dn)を電気的に連結し、余分の1/2水平周期の間には第2増幅部165aの出力とデータライン(D1,D2,...,Dn?1,Dn)を電気的に連結する。

【0103】このように本発明の他の実施例によるソースドライバはサンプリングラッチ部、ホールディング、D/Aコンバータ部、また増幅部を各々2個ずつ構成するので、n個のカラムラインで2n個のカラムラインに当たる画像信号を液晶パネルに与えることができる。

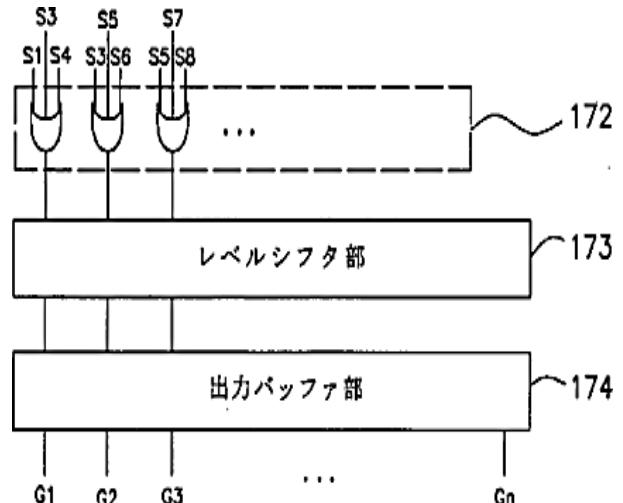

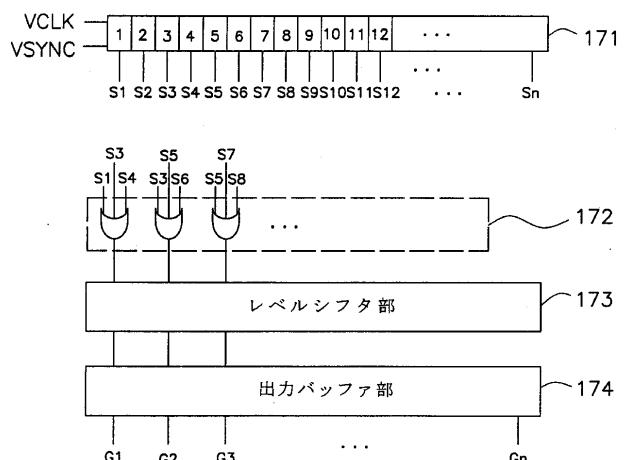

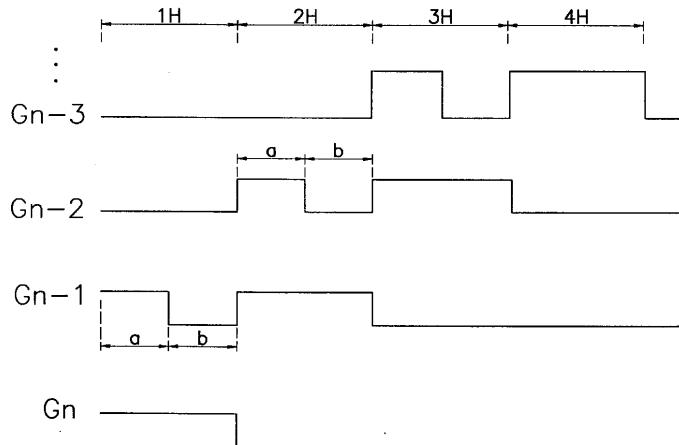

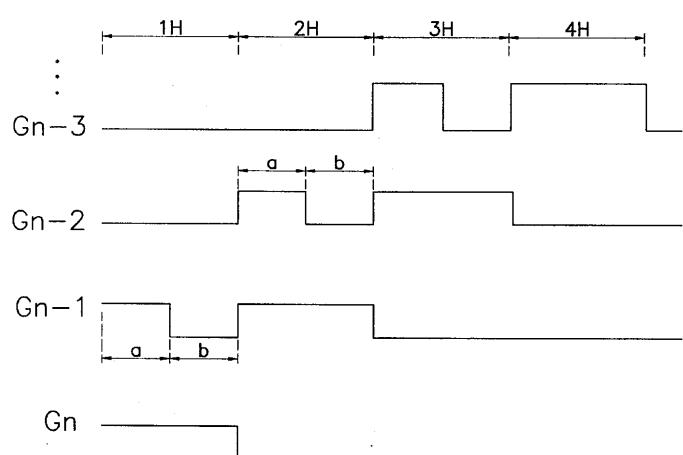

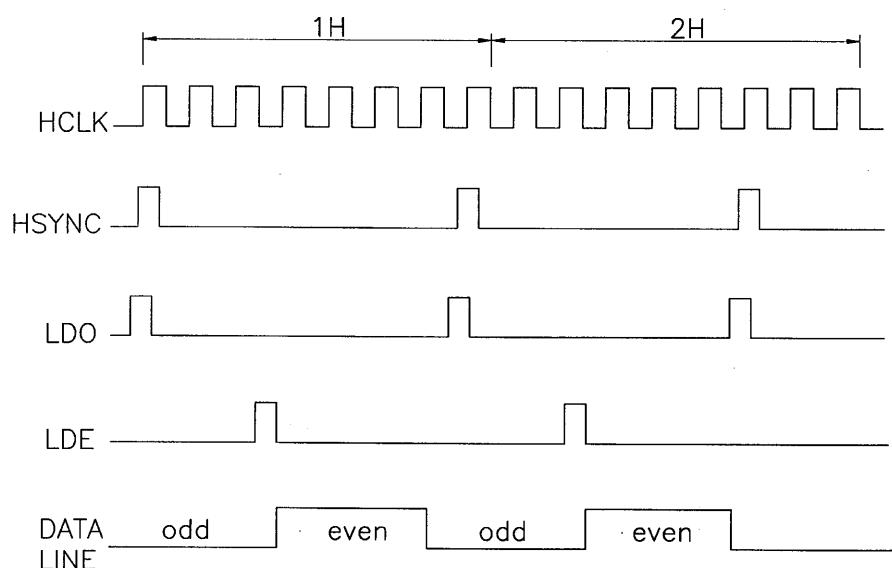

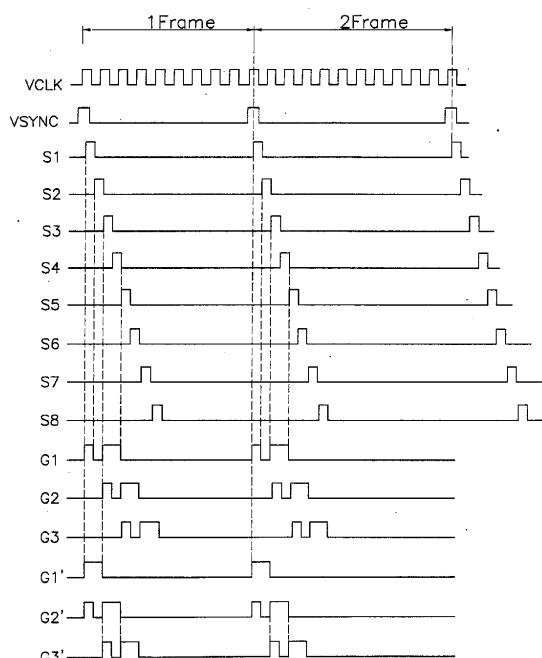

【0104】以下、本発明の一実施の形態による液晶表示装置によるゲートドライバを説明する。図21は本発明の一実施の形態によるゲートドライバの第1実施例を50

示した。図21に示したように、大きくシフトレジスタ部171、ロジック回路部172、レベルシフタ部173、また出力バッファ部174から構成される。

【0105】シフトレジスタ部171は垂直同期信号パルスVSYNCをゲートパルスクロックによってシフトさせる。

【0106】ロジック回路部172は3入力オアゲート(OR1, OR2, ..., ORn)などで構成され、各々のオアゲートはシフトレジスタ部171の出力を選択的に3個ずつ入力して論理演算する。

【0107】本発明の実施例によると、3入力オアゲートのうち、1番目のオアゲートOR1が前記シフトレジスタ部171の出力S1?Snのうち、S1, S3, S4を入力する。また、2番目のオアゲートOR2はS3, S5, S6を入力し、3番目のオアゲートOR3はS5, S7, S8を入力する。続いて、4番目、5番目、...、終わり番目まで続ける。

【0108】レベルシフタ部173は走査ラインに与えられる信号を順次レベルシフトさせて出力バッファ174へ出力する。従って、出力バッファ部174と連結された複数の走査ラインなどは順次インエーブルされる。

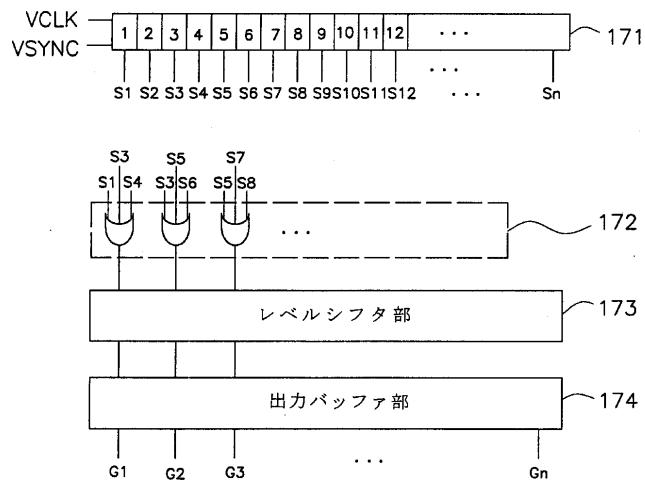

【0109】このような本発明の第1実施例によるゲートドライバの動作を図22に示した波形図を参照して説明する。図22に示したように、前記1番目の走査ラインG1には前記1番目のオアゲートOR1の出力波形が与えられ、2番目の走査ラインG2には2番目のオアゲートOR2の出力波形が与えられる。このように、1番目の走査ラインから終わり番目の走査ラインまで順次インエーブルされる。

【0110】ここで、前記走査ライン(G1, G2, ..., Gn?1, Gn)などに与えられる信号は1水平周期の間にハイ状態とロー状態を繰り返し、これは図2-8に示したいずれかの一つの走査ラインに与えられる駆動信号の波形と同じであることがわかる。

【0111】なお、図21に示した前記オアゲートの入力を異にすることもできるが、その例として1番目のオアゲートOR1にS1, S2を入力し、2番目のオアゲートOR2にはS1, S2, S4を入力し、3番目のオアゲートOR3にはS3, S5, S6を入力するなど終わり番目のオアゲートまで規則的に入力することもできる。

【0112】前記のようにオアゲートの入力を異にする場合には走査ラインに与えられる駆動信号は図22の下端部に示したG1', G2', G3'のような波形を有する。

【0113】以上説明のように、ゲートドライバ及びソースドライバを構成して1水平周期の間に2個の画素領域に画像信号を伝える本発明の液晶表示装置によるとデータラインの数を減少することができ、これによってソースドライバの数も減少することができる。

\*【0114】ここで、1水平周期の間に2個の画素領域に画像信号を伝えなければならないので各々画素領域に伝えるラインタイムが減少し、これによってアナログ回路の動作速度を2倍に速めなければならない問題が発生する。

【0115】かかる問題はドットインパージョンで著しく表れるので図23のような方式で画素電極に画像信号を書き込む。画像信号を書き込む順序は図23に示した番号順である。とが全て(+/-)の極性信号であるのでが書き込まれるとたんはプレチャージされるので1水平周期の半周期の間だけにも充電時間には大きい問題はない。

【0116】またとでは画像信号の極性が変わるので充電及び放電に長い時間が所要される。従って、から、へ移る間のプランキングの間、データライン、プレチャージまたはデータライン間のチャージシャーリング(charge sharing)で充電、放電時間を減少させる。

【0117】なお、はが書き込まれる間、プレチャージされるので書き込み時間には問題がないが、の書き込み時間には問題となり得るので、1水平周期の間、走査ラインに与える駆動信号のハイ区間aとロー区間bの値を調整しての書き込み時間を確保することができる。

【0118】以上、添付図面を参照しながら本発明にかかる液晶表示装置のソースドライバの好適な実施形態について説明したが、本発明はかかる例に限定されない。当業者であれば、特許請求の範囲に記載された技術的思想の範疇内において各種の変更例または修正例に想到しえることは明らかでありそれについても当然に本発明の技術的範囲に属するものと了解される。

### 【0119】

【発明の効果】以上のように本発明の液晶表示装置のゲートドライバは、次のような効果がある。第1、一つのデータラインがその左側と右側の二つの画素領域に選択的に画像信号を伝えることができるのでデータラインの数を半分で減少することができる。第2、データラインの数が半分で減少されるのでソースドライバの数も半分に減少させ得る。従って、素子のサイズを減少させることができ、同時にコストを低減することができる。第3、同一サイズでさらに多い画像をディスプレイすることができるので高解像度を実現することができる。

### 【画面の簡単な説明】

【図1】 本発明の第1実施例による液晶表示装置の構成図。

【図2】 図1による液晶表示装置の走査ラインに与えられる駆動信号の波形図。

【図3】 本発明の第2実施例による液晶表示装置の構成図。

【図4】 図3による液晶表示装置の走査ラインに与え

られる駆動信号の波形図。

【図5】 本発明の第3実施例による液晶表示装置の構成図。

【図6】 図5による液晶表示装置の走査ラインに与えられる駆動信号の波形図。

【図7】 本発明の第4実施例による液晶表示装置の構成図。

【図8】 図7による液晶表示装置の走査ラインに与えられる駆動信号の波形図。

【図9】 本発明の第5実施例による液晶表示装置の構成図。 10

【図10】 図9による液晶表示装置の走査ラインに与えられる駆動信号の波形図。

【図11】 本発明の第6実施例による液晶表示装置の構成図。

【図12】 図11による液晶表示装置の走査ラインに与えられる駆動信号の波形図。

【図13】 本発明の第7実施例による液晶表示装置の構成図。 20

【図14】 図13による液晶表示装置の走査ラインに与えられる駆動信号の波形図。

【図15】 本発明の第8実施例による液晶表示装置の構成図。

【図16】 図15による液晶表示装置の走査ラインに与えられる駆動信号の波形図。

【図17】 本発明の一実施の形態による液晶表示装置のソースドライバの構成図。

【図18】 図17による動作波形図。

【図19】 本発明の一実施の形態による液晶表示装置\*

\*のソースドライバの他の実施例を示した図。

【図20】 図19による動作波形図。

【図21】 本発明の一実施の形態による液晶表示装置のゲートドライバの構成図。

【図22】 図21による動作波形図。

【図23】 本発明の一実施の形態による液晶表示装置による画像信号の書き込み順序を示した図

【図24】 一般的な液晶ディスプレイ素子の断面構造図。

【図25】 一般的な液晶ディスプレイ素子の概略的構成図。

【図26】 従来技術による液晶表示装置の構成図。

【図27】 従来液晶表示装置の走査ラインに与える駆動信号の波形図。

【図28】 従来液晶表示装置によるソースドライバの構成図。

【図29】 従来液晶表示装置によるソースドライバの動作波形図。

【図30】 従来の液晶表示装置によるゲートドライバの構成図。

【図31】 従来液晶表示装置によるゲートドライバの動作波形図。

#### 【符号の説明】

71：第1スイッチング部

71a, 71b：第1, 第2薄膜トランジスタ

73：第2スイッチング部

73a, 73b：第3, 第4薄膜トランジスタ

73c：第2画素電極

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図23】

|   |   |    |    |   |   |

|---|---|----|----|---|---|

| - | - | ①+ | ②+ | - | - |

| + | + | ③- | ④- | + | + |

| - | - | +  | +  | - | - |

| + | + | -  | -  | + | + |

【図10】

【図28】

【図11】

【図29】

【図12】

【図25】

【図13】

【図14】

【図26】

【図15】

【図30】

【図16】

【図17】

【図19】

【図18】

【図20】

【図21】

【図22】

【図24】

【図27】

【図31】

|                |                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置的栅极驱动器                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2001027893A</a>                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2001-01-30 |

| 申请号            | JP2000167959                                                                                                                                                                                                                                                                                                                                                                    | 申请日     | 2000-06-05 |

| [标]申请(专利权)人(译) | 权五敬                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 权 五 敬                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 權 五 敬                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 權 五 敬                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G02F1/133 G09F9/30 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                            |         |            |

| CPC分类号         | G09G3/3677 G09G3/3614 G09G3/3648 G09G3/3659 G09G3/3688 G09G2300/0814 G09G2310/0251<br>G09G2310/027 G09G2310/0297 G09G2310/06                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.622.P G09G3/20.624.B G11C19/00 G11C19/00.J                                                                                                                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 2H093/NC22 2H093/NC24 2H093/NC26 2H093/NC34 2H093/ND20 2H093/ND54 2H193/ZA04 2H193/<br>/ZA19 2H193/ZC14 2H193/ZC34 5B074/AA10 5B074/CA01 5C006/AC24 5C006/BB16 5C006/BC03<br>5C006/BC06 5C006/BC13 5C006/BF26 5C006/FA42 5C006/FA43 5C006/FA51 5C080/AA10 5C080/<br>/BB05 5C080/DD07 5C080/DD22 5C080/DD23 5C080/DD27 5C080/FF11 5C080/JJ02 5C080/JJ03<br>5C080/JJ04 5C080/JJ06 |         |            |

| 优先权            | 1999P20721 1999-06-04 KR                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                       |         |            |

## 摘要(译)

解决的问题：提供一种液晶显示装置及其驱动电路，该液晶显示装置及其驱动电路通过实现相同的图像表示同时将数据线的数量减少到传统水平的一半来降低成本。用于将驱动信号提供给液晶显示装置的扫描线的栅极驱动器主要由移位寄存器部分171，逻辑电路部分172，电平移位器部分173和输出缓冲部分174组成。逻辑电路单元172由3输入或门( $OR_1, OR_2, \dots, OR_n$ )组成，并且每个或门选择性地输入移位寄存器单元171的三个输出以执行逻辑运算。