(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4835667号

(P4835667)

(45) 発行日 平成23年12月14日(2011.12.14)

(24) 登録日 平成23年10月7日(2011.10.7)

(51) Int.Cl.

F 1

**G09G 3/36 (2006.01)**

**G09G 3/20 (2006.01)**

**G02F 1/133 (2006.01)**

GO9G 3/36

GO9G 3/20 611D

GO9G 3/20 611J

GO9G 3/20 621B

GO9G 3/20 612T

請求項の数 11 (全 29 頁) 最終頁に続く

(21) 出願番号

特願2008-236441 (P2008-236441)

(22) 出願日

平成20年9月16日 (2008.9.16)

(62) 分割の表示

特願平10-241392の分割

原出願日

平成10年8月27日 (1998.8.27)

(65) 公開番号

特開2009-9156 (P2009-9156A)

(43) 公開日

平成21年1月15日 (2009.1.15)

審査請求日

平成20年9月16日 (2008.9.16)

(31) 優先権主張番号

特願平10-76813

(32) 優先日

平成10年3月25日 (1998.3.25)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100120640

弁理士 森 幸一

(74) 代理人 100118290

弁理士 吉井 正明

(74) 代理人 100094363

弁理士 山本 孝久

(72) 発明者 猪野 益充

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 前川 敏一

東京都港区港南1丁目7番1号 ソニー株式会社内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

(57) 【特許請求の範囲】

## 【請求項 1】

複数行分のゲートラインと複数列分の信号ラインとの交差部に対応して複数個の画素がマトリクス状に2次元配置されてなる表示部と、

前記複数列分の信号ラインの総本数の約数に設定された数の出力端子をそれぞれが有し、前記表示部の各画素に前記複数列分の信号ラインを介して信号電位を与える複数のドライバ回路と、

前記複数のドライバ回路の各々から出力される信号電位を時分割にて前記複数列分の信号ラインに対して、異なる3色の信号が供給される3つの信号ラインを単位として与える時分割スイッチと、を備え、

前記時分割スイッチは、反転駆動される画素において液晶を透過して出力される色光量を補完する電位が前記信号ラインに生じる順に前記信号電位を前記3つの信号ラインに与える

液晶表示装置。

## 【請求項 2】

前記複数のドライバ回路は、前記時分割スイッチの選択期間の間に生じるブランкиング期間においてその出力回路の動作を停止する機能を持つ

請求項1記載の液晶表示装置。

## 【請求項 3】

前記複数のドライバ回路に書き込むためのデータを一時的に記憶する記憶回路と、

前記複数のドライバ回路に対して同時に別々のデータを前記記憶回路から書き込むべく制御する制御回路とを有する

請求項 2 記載の液晶表示装置。

【請求項 4】

前記記憶回路は、第1の記憶回路と第2の記憶回路とからなり、

前記制御回路は、前記複数のドライバ回路に書き込むためのデータを前記第1の記憶回路に記憶すると共に前記第2の記憶回路に記憶されたデータを前記複数のドライバ回路に書き込み、前記第1の記憶回路に記憶されたデータを前記複数のドライバ回路に対して書き込むと共に前記複数のドライバ回路に書き込むためデータを前記第2の記憶回路に記憶するように前記第1、第2の記憶回路を制御する

10

請求項 3 記載の液晶表示装置。

【請求項 5】

1H (Hは水平走査期間) 反転駆動又は1Hコモン反転駆動において、前記時分割スイッチによって青色の信号が供給される信号ラインが1番目に、緑色の信号が供給される信号ラインが2番目に、赤色の信号が供給される信号ラインが3番目に選択される

請求項 2 記載の液晶表示装置。

【請求項 6】

ドット反転駆動において、前記時分割スイッチによって赤色の信号が供給される信号ラインが1番目に、緑色の信号が供給される信号ラインが2番目に、青色の信号が供給される信号ラインが3番目に選択される

20

請求項 2 記載の液晶表示装置。

【請求項 7】

前記時分割スイッチで選択する期間は、水平走査期間の3分の1以下の期間である

請求項 2 記載の液晶表示装置。

【請求項 8】

前記複数のドライバ回路の立ち上がり時間および立ち下がり時間は、前記時分割スイッチで選択する期間以下である

請求項 7 記載の液晶表示装置。

【請求項 9】

前記時分割スイッチの選択期間の間に生じるプランギング期間は、(水平走査期間 - 時分割スイッチの選択期間 × 3) / 3 以下である

30

請求項 7 記載の液晶表示装置。

【請求項 10】

複数行分のゲートラインと複数列分の信号ラインとの交差部に対応して複数個の画素がマトリクス状に2次元配置されてなる表示部と、

前記複数列分の信号ラインの総本数の約数に設定された数の出力端子をそれぞれが有し、前記表示部の各画素に前記複数列分の信号ラインを介して信号電位を与える複数のドライバ回路と、

前記複数のドライバ回路の各々から出力される信号電位を時分割にて前記複数列分の信号ラインに対して、互いに隣接する3つの信号ラインを単位として与える時分割スイッチと、を備え、

40

1H (Hは水平走査期間) 反転駆動又は1Hコモン反転駆動において、前記3つの信号ラインのうち青色の信号が供給される信号ラインが1番目に、緑色の信号が供給される信号ラインが2番目に、赤色の信号が供給される信号ラインが3番目に前記時分割スイッチによって選択される

液晶表示装置。

【請求項 11】

複数行分のゲートラインと複数列分の信号ラインとの交差部に対応して複数個の画素がマトリクス状に2次元配置されてなる表示部と、

前記複数列分の信号ラインの総本数の約数に設定された数の出力端子をそれぞれが有し

50

、前記表示部の各画素に前記複数列分の信号ラインを介して信号電位を与える複数のドライバ回路と、

前記複数のドライバ回路の各々から出力される信号電位を時分割にて前記複数列分の信号ラインに対して、互いに隣接する3つの信号ラインを単位として与える時分割スイッチと、を備え、

ドット反転駆動において、前記3つの信号ラインのうち赤色の信号が供給される信号ラインが1番目に、緑色の信号が供給される信号ラインが2番目に、青色の信号が供給される信号ラインが3番目に前記時分割スイッチによって選択される

液晶表示装置。

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明は、液晶表示装置（LCD；Liquid Crystal Display）に関し、特に各画素に信号電位を与えるドライバ回路を、液晶表示パネルの外部回路として設けてなるマトリクス型液晶表示装置に関する。

【背景技術】

【0002】

パーソナルコンピュータやワードプロセッサなどに用いられている液晶表示装置は、マトリクス型が主力となっている。このマトリクス型液晶表示装置は、応答速度や画像品質の面で優れており、近年のカラー化に最適な表示装置となってきている。この種の表示装置において、液晶表示パネルの各画素には、トランジスタあるいはダイオードなどの非線形な素子が用いられている。具体的には、ガラス基板上に薄膜トランジスタ（TFT；thin film transistor）を形成した構造となっている（例えば、特許文献1参照）。

20

【0003】

ところで、特に大型の液晶表示装置においては、各画素に所定の電圧を印加するドライバICを、液晶表示パネルの外部に設けた構成を採っている。そして、外部のドライバICの出力と液晶表示パネルの信号ラインとは、通常、1対1の対応関係となっている。すなわち、ドライバICの各出力端子からの出力電圧はそのまま対応する信号ラインに与えられるようになっている。

【0004】

30

したがって、例えばR（赤）、G（緑）、B（青）の各色ごとに1024本、即ち3072（=1024×3）本の信号ラインを持つXGA（extended graphics array）表示方式の液晶表示装置において、各信号ラインに対して例えば120本の出力ピン（出力端子）を持つ既存の汎用ドライバICを接続しようとすると、合計で26個のドライバICを必要とすることになる。

【0005】

【特許文献1】特開平10-161572号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

40

しかしながら、上述したように、表示方式によって総本数が決まる信号ラインに対して汎用ドライバICを使用すると、ドライバICのピン数が余ることが発生する。例えば、3072本の信号ラインに対して、120本の出力ピンを持つ汎用ドライバICを26個用いた場合、最後に配置されるドライバICの出力ピンが48（=120×26-3072）個だけ余ることになる。

【0007】

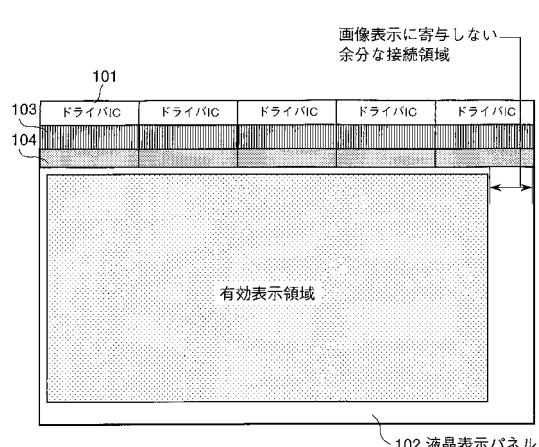

そして、液晶表示パネルのサイズの観点から考えると、図37に示すように、ドライバIC101の出力ピンにおける余分なピン部分が、画像表示に寄与しない余分な接続領域となり、液晶表示パネル102の左右の額縁部分を占めることになるため、液晶表示パネル102の水平方向のサイズが増すことになり、その結果、液晶表示装置全体のコンパク

50

ト化の妨げとなる。なお、図37において、ドライバIC101は、フレキシブルケーブル103を介して液晶表示パネル102上の接続部分104にて信号ラインの各々に接続される。

#### 【0008】

また、階調を伴うカラー表示を行う場合には、各画素の薄膜トランジスタに印加する電圧を出力する出力バッファ回路や階調制御回路の構成が複雑になり、ドライバIC自体も高価なものとなる。このような高価なドライバICを、その余った出力ピンに対応する回路部分が表示に全く寄与しない状態で用いることは無駄であり、また液晶表示装置のコストアップにもつながる。

#### 【0009】

本発明は、上記課題に鑑みてなされたものであり、その目的とするところは、外部ドライバICを用いる場合において、液晶表示パネルの水平方向の狭幅化を可能とし、加えて画像信号に対してより忠実な色再現を可能にする液晶表示装置を提供することにある。

#### 【課題を解決するための手段】

#### 【0010】

上記目的を達成するために、本発明による液晶表示装置は、複数行分のゲートラインと複数列分の信号ラインとの交差部に対応して複数個の画素がマトリクス状に2次元配置されてなる表示部と、前記複数列分の信号ラインの総本数の約数に設定された数の出力端子をそれぞれが有し、前記表示部の各画素に前記複数列分の信号ラインを介して信号電位を与える複数のドライバ回路と、前記複数のドライバ回路の各々から出力される信号電位を時分割にて前記複数列分の信号ラインに与える時分割スイッチと、を備え、

前記時分割スイッチは、異なる3色の信号が供給される3つの信号ラインに対応して設けられ、反転駆動される画素において液晶を透過して出力される色光量を補完する電位が前記信号ラインに生じる順に前記信号電位を前記3つの信号ラインに与える。

#### 【0011】

上記構成の液晶表示装置において、ドライバ回路の出力端子数を設定する際に、各々の出力端子数を信号ラインの総本数の約数に設定し、この出力端子数で決まる個数のドライバ回路を配置する。これにより、複数のドライバ回路に対して信号ラインには端数が生じない。したがって、ドライバ回路の出力端子を余らせることなく信号ラインの各々と接続することができるため、表示部には画像表示に寄与しない余分な接続領域が生じない。加えて、時分割スイッチによる選択駆動の下に、反転駆動される画素において液晶を透過して出力される色光量を補完する電位が信号ラインに生じる順に、複数のドライバ回路の各々から出力される信号電位を3つの信号ラインに与えることで、中間調付近での各色の透過率が一致するため、画像信号に対してより忠実な色再現が可能になる。

#### 【発明の効果】

#### 【0012】

本発明によれば、外部ドライバICを用いる場合において、液晶表示パネルの水平方向の狭幅化が可能になり、加えて画像信号に対してより忠実な色再現が可能になる。

#### 【発明を実施するための最良の形態】

#### 【0013】

以下、本発明の実施の形態について図面を参照しつつ詳細に説明する。

#### 【0014】

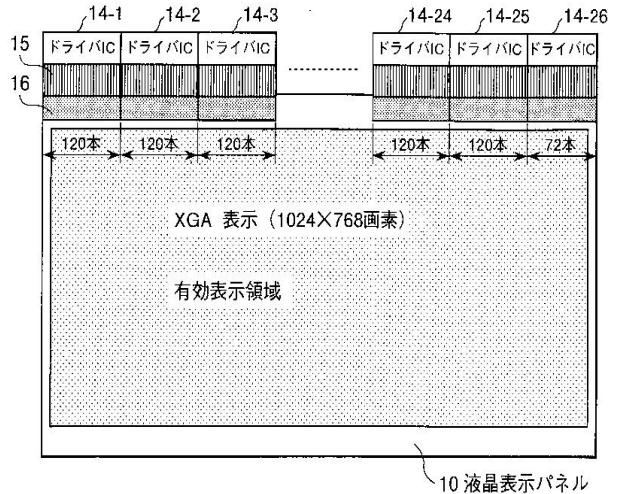

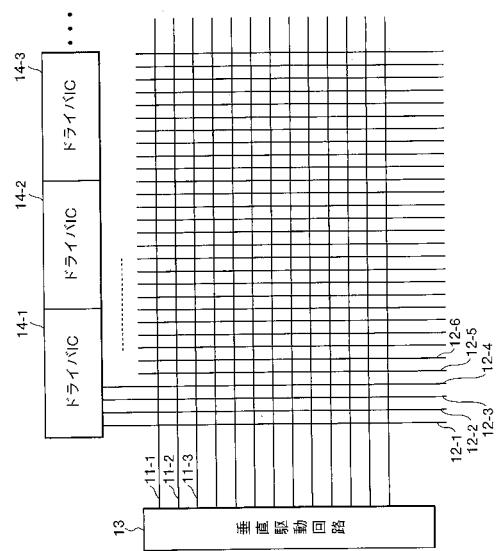

図1は、本発明に係るマトリクス型液晶表示装置における液晶表示部の配線図である。このマトリクス型液晶表示装置は、複数行分のゲートライン11-1, 11-2, 11-3, ... ...と複数列分の信号ライン12-1, 12-2, 12-3, .....が、液晶の表面にマトリクス状に配線され、その液晶の裏面側にバックライトが配置された構造となっている。そして、ゲートライン11-1, 11-2, 11-3, .....と信号ライン12-1, 12-2, 12-3, .....の交差点が画素となり、液晶表示パネル(表示部)10を形成している。この画素の構成については後述する。

#### 【0015】

複数行分のゲートライン 11-1, 11-2, 11-3, ……の各一端は、垂直駆動回路 13 の対応する行の各出力端にそれぞれ接続されている。垂直駆動回路 13 は、上記液晶表示パネルと同一の基板上に薄膜トランジスタによって形成されており、ゲートライン 11-1, 11-2, 11-3, ……に順に走査パルスを与えて各画素を行単位で選択することによって垂直走査を行う。なお、本例では、垂直駆動回路 13 を液晶表示パネル 10 の片側にのみ配する構成としたが、液晶表示パネル 10 の両側に配する構成であっても良いことは勿論である。

#### 【0016】

また、信号ライン 12-1, 12-2, 12-3, ……に画像データに応じた所定の電圧を印加する複数のドライバ IC 14-1, 14-2, 14-3, ……が、上記液晶表示パネル 10 の外部回路として設けられている。複数のドライバ IC 14-1, 14-2, 14-3, ……には、例えば 8 階調以上で 512 色以上の表示を可能にするデジタル画像データが入力される。

10

#### 【0017】

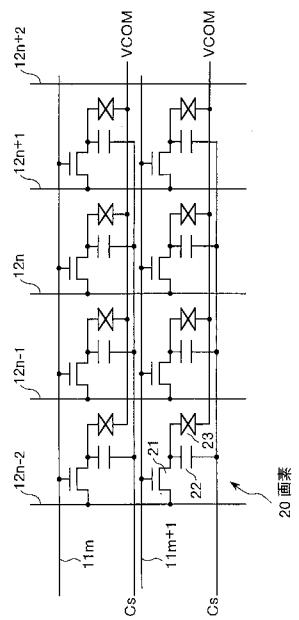

図 2 は、画素の回路構成図である。同図から明らかなように、各画素 20 は、薄膜トランジスタ 21、付加容量 22 および液晶容量 23 から構成されている。薄膜トランジスタ 21 は、そのゲート電極がゲートライン 11-1, 11-2, 11-3, ……に、そのソース電極が信号ライン 12-1, 12-2, 12-3, ……にそれぞれ接続されている。

#### 【0018】

この画素構造において、液晶容量 23 は、薄膜トランジスタ 21 で形成される画素電極と、これに対応して形成される対向電極との間で発生する容量を意味する。そして、この画素電極に保持される電位は、“H”もしくは“L”の電位で書き込まれる。ここで、“H”は高電圧書き込み状態を示し、“L”は低電圧書き込み状態を示す。

20

#### 【0019】

液晶の駆動に際しては、対向電極の電位（コモン電位 VCOM）を例えば 6 V の DC 電位に設定し、これに対して信号電圧を高電圧 H、低電圧 L で 1 フィールド周期にて周期的に変動させることにより、交流駆動が実現できる。この交流駆動は、液晶分子の分極作用を減少することができ、液晶分子の帶電もしくは電極表面に存在する絶縁膜の帶電を防ぐことが可能となる。

#### 【0020】

30

一方、画素 20 では、薄膜トランジスタ 21 がオン状態となると、液晶での光の透過率が変化するとともに、付加容量 22 が充電される。この充電により、薄膜トランジスタ 21 がオフ状態となっても、付加容量 22 の充電電圧による液晶での光透過率状態が、次に薄膜トランジスタ 21 がオン状態となるまでの間保持される。このような方式により、液晶表示パネル 10 の画像における画質向上が図られる。

#### 【0021】

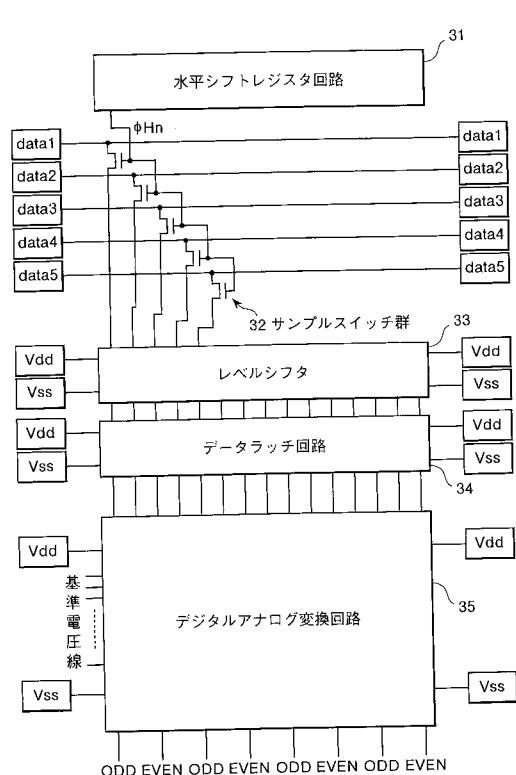

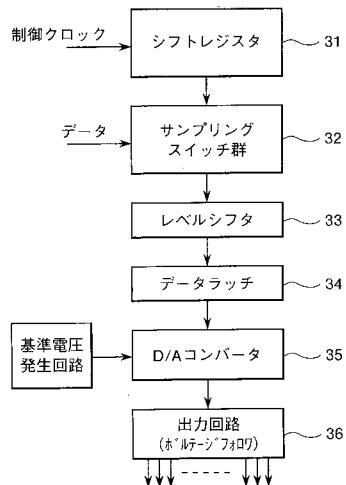

図 3 は、ドライバ IC 14-1, 14-2, 14-3, ……の内部構成の一例を示すブロック図である。図 3 から明らかなように、これらドライバ IC は、水平シフトレジスタ回路 31、サンプリングスイッチ群 32、レベルシフタ 33、データラッチ回路 34 およびデジタルアナログ変換回路 35 を有し、本例では、例えば 5 ビットのデジタル画像データ data1 ~ data5 や電源電圧 Vdd, Vss を水平シフトレジスタ回路 31 のシフト方向における両側から取り込む構成となっている。

40

#### 【0022】

上記構成のドライバ IC 14-1, 14-2, 14-3, ……において、水平シフトレジスタ回路 31 は、水平走査パルスを順次出力することによって水平走査（列走査）を行う。サンプリングスイッチ群 32 におけるサンプリングスイッチの各々は、水平シフトレジスタ回路 31 からの水平走査パルスに応答して、入力されるデジタル画像データ data1 ~ data5 を順次サンプリングする。

#### 【0023】

レベルシフタ 33 は、サンプリングスイッチ群 32 でサンプリングされた例えは 5 V の

50

デジタルデータを液晶駆動電圧のデジタルデータに昇圧する。データラッチ回路34は、レベルシフタ33で昇圧されたデジタルデータを1水平期間分蓄積するメモリである。デジタルアナログ変換回路35は、データラッチ回路34から出力される1水平期間分のデジタルデータをアナログ信号に変換して出力する。

【0024】

上述した構成の液晶表示装置において、本発明の特徴とするところは、液晶表示パネル10の信号ライン12-1, 12-2, 12-3, .....の各々と、複数のドライバIC14-1, 14-2, 14-3, .....の各出力ピン（出力端子）との接続部分の構成にある。以下に、その具体的な実施形態について説明する。

【0025】

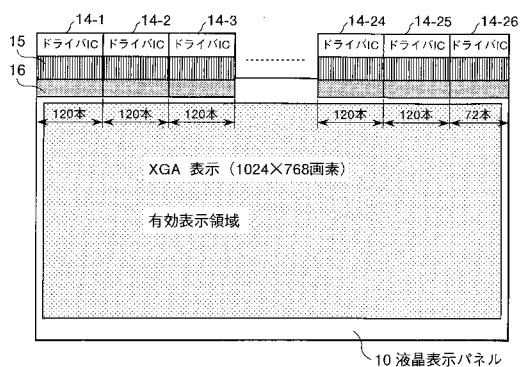

先ず、例えばXGA表示方式の液晶表示装置に適用した第1実施形態につき、図4を用いて説明する。

10

【0026】

液晶表示パネル10は、XGA表示の場合、R, G, Bの各色ごとに1024本、即ち3072（=1024×3）本の信号ライン12-1, 12-2, 12-3, .....を持っている。一方、ドライバIC14-1, 14-2, 14-3, .....として、例えば120本の出力ピンを持つ汎用ドライバICを用い、信号ライン12-1, 12-2, 12-3, .....の各々に対応して順に配置するものとする。

【0027】

このとき、120本の出力ピンを持つ汎用ドライバICを25個配置したとすると、信号ラインには72（=3072-120×25）本の端数が出る。そこで、この端数の72本の信号ラインを担うドライバICとして、120本の出力ピンを持つ汎用のドライバICではなく、72本の出力ピンを持つドライバICを用い、当該ドライバICを含む計26個のドライバIC14-1, 14-2, 14-3, ..., 14-26を水平方向に順に配置するようとする。

20

【0028】

この72本の出力ピンを持つドライバICは、例えば図4に示すように、ドライバICを順に配置する際に、例えば26番目に配置されるドライバIC14-26として用いられる。すなわち、他の25個のドライバIC14-1, 14-2, 14-3, ..., 14-25に割り当てられる信号ラインの本数は120本であるのに対し、26番目のドライバIC14-26に割り当てられる信号ラインの本数は72本となる。

30

【0029】

このように配置された26個のドライバIC14-1, 14-2, 14-3, ..., 14-26は、各々の出力ピンがフレキシブルケーブル15を介して液晶表示パネル10上の接続部分16にて信号ライン12-1, 12-2, 12-3, .....の各々に接続され、これら信号ライン12-1, 12-2, 12-3, .....を介して各画素に所定の電圧を印加するようになる。

【0030】

上述したように、ドライバIC14-1, 14-2, 14-3, .....として出力ピン数が同数の例えば汎用ドライバICを用いる場合において、これらのドライバICを信号ライン12-1, 12-2, 12-3, .....の各々と対応関係を持って順に配置する際に、信号ラインに端数が出るとき、ドライバIC14-1, 14-2, 14-3, .....のうちの1つの出力ピン数をその端数に設定することで、最終的に信号ラインには端数が生じず、ドライバICの出力ピンを余らせることなく信号ラインの各々と接続することができる。その結果、液晶表示パネル10には、画像表示に寄与しない余分な接続領域が生じない。

40

【0031】

なお、本実施形態においては、信号ラインの端数分を担うドライバICが配置される位置を最後（本例では、26番目）としたが、これに限られるものではなく、どの位置に配置することも可能である。また、本例で示した数値は一例に過ぎず、これらの数値に限定されるものではない。

【0032】

50

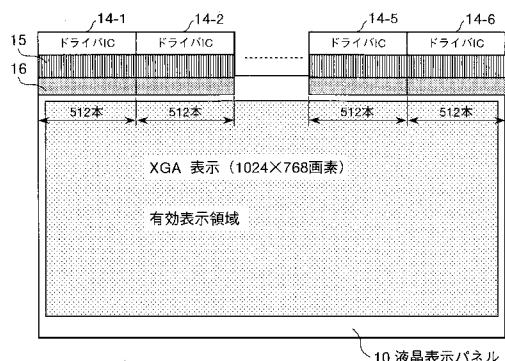

次に、例えば XGA 表示方式の液晶表示装置に適用した第 2 実施形態につき、図 5 を用いて説明する。

【0033】

液晶表示パネル 10 は、XGA 表示の場合、先述したように、R, G, B の各色ごとに 1024 本、即ち 3072 本の信号ライン 12-1, 12-2, 12-3, ..... を持っている。この 3072 本の信号ライン 12-1, 12-2, 12-3, ..... に対して、複数のドライバ IC 14-1, 14-2, 14-3, ..... を配置するのであるが、このとき、ドライバ IC 14-1, 14-2, 14-3, ..... の出力ピン数を、信号ライン 12-1, 12-2, 12-3, ..... の総本数（即ち、水平表示ドット数）の約数に設定する。

【0034】

XGA 表示では、信号ライン 12-1, 12-2, 12-3, ..... の総本数が 3072 本であることから、一例として、ドライバ IC 14-1, 14-2, 14-3, ..... の出力ピン数を 3072 の約数でかつ好ましくは 2 のべき乗（累乗）である 512 (= 29) 本に設定する。これにより、6 (= 3072 / 512) 個のドライバ IC が必要となり、この 6 個のドライバ IC 14-1, 14-2, 14-3, ..., 14-6 を信号ライン 12-1, 12-2, 12-3, ..... の各々と対応関係をもって順に配置すれば良いことになる。

【0035】

このように配置された 6 個のドライバ IC 14-1, 14-2, 14-3, ..., 14-6 は、各々の出力ピンがフレキシブルケーブル 15 を介して液晶表示パネル 10 上の接続部分 16 にて信号ライン 12-1, 12-2, 12-3, ..... の各々に接続され、これら信号ライン 12-1, 12-2, 12-3, ..... を介して各画素に所定の電圧を印加するようになる。

【0036】

上述したように、ドライバ IC 14-1, 14-2, 14-3, ..... の出力ピン数を設定する際に、各々の出力ピン数を信号ライン 12-1, 12-2, 12-3, ..... の総本数の約数に設定し、この出力ピン数で決まる個数のドライバ IC を配置することで、信号ラインには端数が生じず、ドライバ IC の出力ピンを余らせることなく信号ラインの各々と接続することができる。その結果、液晶表示パネル 10 には、画像表示に寄与しない余分な接続領域が生じない。

【0037】

なお、本例で示した数値は一例に過ぎず、これらの数値に限定されるものではない。ここで、ドライバ IC の個数が少なければ少ないほど低コスト化に有利であり、逆に多ければ回路の一部に不良箇所が発生した場合にその不良箇所を含む IC のみを交換することで対応できるという利点がある。したがって、ドライバ IC の出力ピン数を設定するに際しては、その出力ピン数で決まるドライバ IC の個数などを考慮して決めるようすれば良い。

【0038】

また、本実施形態では、XGA (1024 画素 × 768 画素) 表示に適用した場合について説明したが、他の表示方式、例えば NTSC (640 画素 × 480 画素) 表示、VGA (800 画素 × 600 画素) 表示、SXGA (1280 画素 × 1024 画素) 表示、UXGA (1600 画素 × 1400 画素) 表示にも適用できることは言うまでもない。

【0039】

さらに、上記各実施形態においては、外部ドライバ IC 14-1, 14-2, 14-3, ..... の各出力ピンと信号ライン 12-1, 12-2, 12-3, ..... とが 1 対 1 の対応関係にある液晶表示装置に適用した場合を例に採って説明したが、1 : 1 の対応関係にない液晶表示装置にも適用可能である。すなわち、いわゆる時分割駆動法を用いた液晶表示装置では、外部ドライバ IC の出力ピンと信号ラインとは 1 : 1 の対応関係になく、この種の液晶表示装置にも適用可能である。

【0040】

ここで、時分割駆動法とは、複数本の信号ラインを 1 単位（ブロック）とし、この 1 分割ブロック内の複数本の信号ラインに与える信号を時系列でドライバ IC から出力する一

10

20

30

40

50

方、液晶表示パネルには複数本の信号ラインを1単位として時分割スイッチを設け、これら時分割スイッチにてドライバICから出力される時系列の信号を時分割して複数本の信号ラインに順次与える駆動方法である。この時分割駆動法を用いることで、ドライバICの出力ピン数を削減できる。

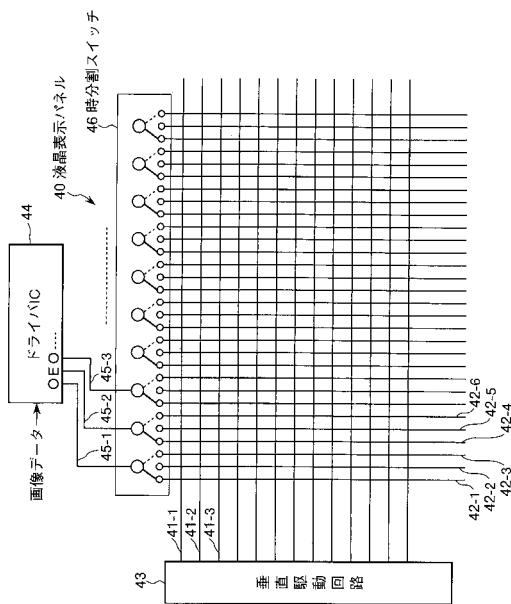

【0041】

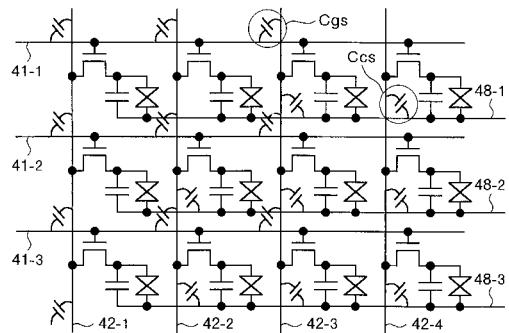

図6は、時分割駆動法を用いたマトリクス型液晶表示装置における液晶表示部の配線図である。このマトリクス型液晶表示装置は、複数行分のゲートライン41-1, 41-2, 41-3, .....と複数列分の信号ライン42-1, 42-2, 42-3, .....が、液晶の表面にマトリクス状に配線され、その液晶の裏面側にバックライトが配置された構造となっている。そして、ゲートライン41-1, 41-2, 41-3, .....と信号ライン42-1, 42-2, 42-3, .....の交差点が画素となり、液晶表示パネル40を形成している。この画素は、例えば図2に示す構成となっている。

【0042】

複数行分のゲートライン41-1, 41-2, 41-3, .....の各一端は、垂直駆動回路43の対応する行の各出力端にそれぞれ接続されている。垂直駆動回路43は、上記液晶表示パネルと同一の基板上に薄膜トランジスタによって形成されており、ゲートライン41-1, 41-2, 41-3, .....に順に走査パルスを与えて各画素を行単位で選択することによって垂直走査を行う。

【0043】

また、信号ライン42-1, 42-2, 42-3, .....に画像データに応じた所定の電圧を印加する複数のドライバIC(図6には、その1段目のドライバIC44のみを示す)が、上記液晶表示パネル40の外部回路として設けられている。このドライバIC44には、例えば8階調以上で512色以上の表示を可能にするデジタル画像データが入力される。ドライバIC44は、例えば図3に示す構成となっている。

【0044】

そして、ドライバIC44としては、ドット反転駆動用ICが用いられる。このドライバIC44は、ドット反転駆動を実現するために、各出力端子の奇数、偶数ごとに電位が反転する信号電圧を出力する。ここに、ドット反転駆動とは、隣接するドット(画素)に印加する電圧の極性を反転させる駆動法であり、画質向上に良好な駆動法とされている。

【0045】

すなわち、ドット反転駆動により、隣接の画素に印加する電圧を逆極性にすることにより、信号ラインとゲートラインのクロス容量に起因する信号ラインからの飛び込み電位がキャンセルされることから、画素電位が安定して入力されるようになり、液晶表示時のフリッカーが軽減されるため、画質を向上できるのである。

【0046】

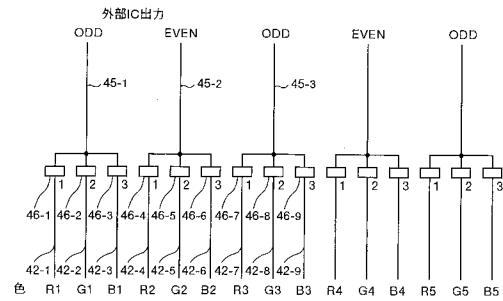

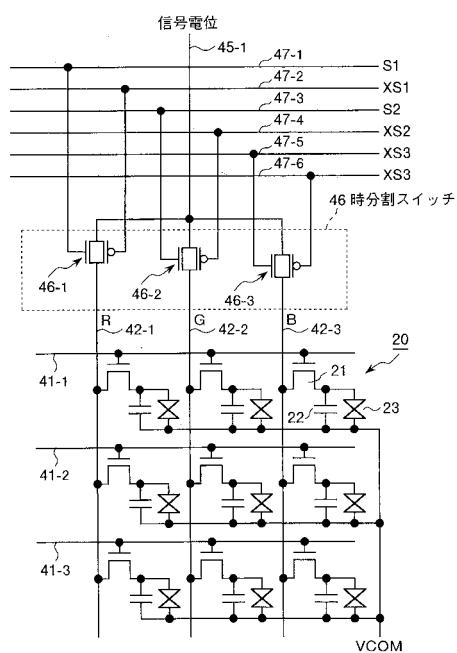

ドライバIC44はさらに、時分割駆動を実現するために、複数の信号ラインを1単位とし、これら複数の信号ラインに与える信号を時系列で出力する構成となっている。これに対応して、ドライバIC44の出力ライン45-1, 45-2, 45-3, .....と信号ライン42-1, 42-2, 42-3, .....の間には、CMOS、PMOSあるいはNMOS構成のアナログスイッチ(以下、時分割スイッチと称す)46が設けられている。

【0047】

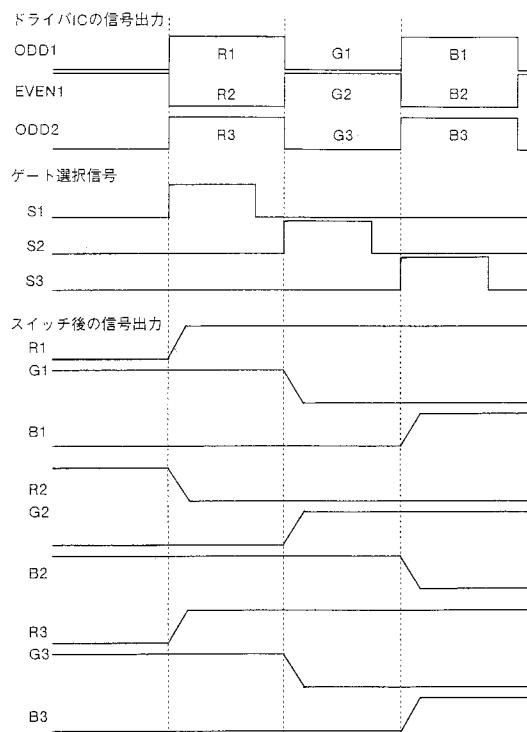

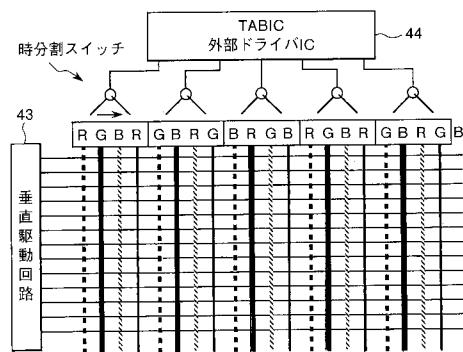

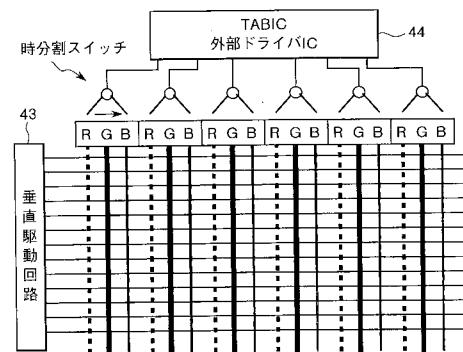

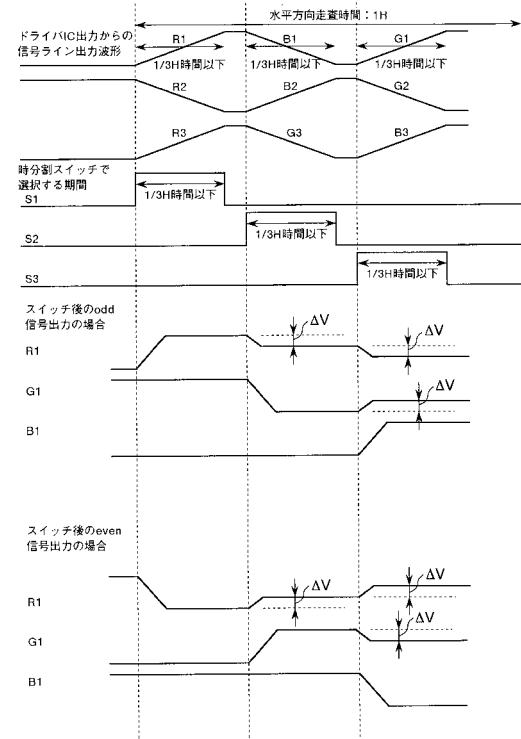

図7に、R, G, Bに対応した3時分割駆動の場合における時分割スイッチ46の接続構成の一例を示す。この3時分割駆動の場合には、ドライバIC44の各出力端子からは、R, G, Bの3画素分の信号電圧が順に時系列で出力ライン45-1, 45-2, 45-3, .....を介して出力される。

【0048】

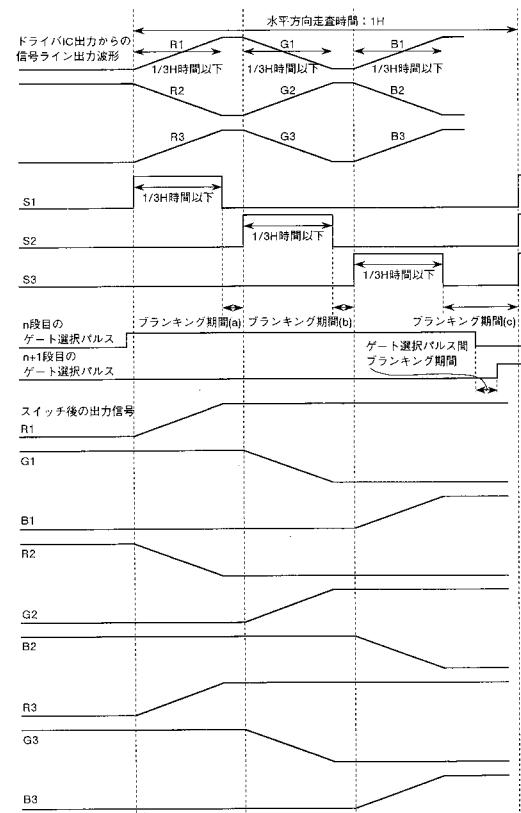

具体的には、図9のタイミングチャートに示すように、ドライバIC44の信号出力として、ODD端子1から出力ライン45-1にはR1, G1, B1の各画素の信号が、EVEN端子1から出力ライン45-2にはR2, G2, B2の各画素の信号が、ODD端子2から出力ライン45-3にはR3, G3, B3の各画素の信号が、.....という具合に出力さ

10

20

30

40

50

れる。

【0049】

これに対して、出力ライン45-1と3本の信号ライン42-1, 42-2, 42-3の間に時分割スイッチ46-1, 46-2, 46-3が、出力ライン45-2と3本の信号ライン42-4, 42-5, 42-6の間に時分割スイッチ46-4, 46-5, 46-6が、出力ライン45-3と3本の信号ライン42-7, 42-8, 42-9の間に時分割スイッチ46-7, 46-8, 46-9が、……という具合に、3時分割に対応して1本の出力ラインに対して時分割スイッチが3個ずつ設けられている。

【0050】

ここで、ある1組の時分割スイッチ46-1, 46-2, 46-3の具体的な構成について、

図10の回路図を用いて説明する。

10

【0051】

時分割スイッチ46-1, 46-2, 46-3は、PchMOSトランジスタおよびNchMOSトランジスタが並列接続されてなるCMOSアナログスイッチ（トランスマッシュションスイッチ）からなり、液晶表示パネル40と同一基板上に薄膜トランジスタによって形成されている。そして、3個の時分割スイッチ46-1, 46-2, 46-3の各入力端は共通に接続され、その共通接続点は出力ライン45-1に接続されている。

【0052】

これにより、ドライバIC44から時系列で出力される信号電位が、出力ライン45-1を経由して3個の時分割スイッチ46-1, 46-2, 46-3の各入力端に与えられる。これら時分割スイッチ46-1, 46-2, 46-3の各出力端は、3本の信号ライン41-1, 41-2, 41-3の各一端に接続されている。

20

【0053】

また、液晶表示パネル40と同一基板上において、1個の時分割スイッチにつき2本、計6本の制御ライン47-1～47-6が、ゲートライン41-1, 41-2, 43-3, ……の配線方向に沿って配線されている。そして、時分割スイッチ46-1の2つの制御入力端（即ち、Nch, PchMOSトランジスタの各ゲート）が制御ライン47-1, 47-2に、時分割スイッチ46-2の2つの制御入力端が制御ライン47-3, 47-4に、時分割スイッチ46-3の2つの制御入力端が制御ライン47-5, 47-6にそれぞれ接続されている。

【0054】

30

なお、ここでは、6本の制御ライン47-1～47-6に対する時分割スイッチ46-1, 46-2, 46-3の接続関係について説明したが、他の時分割スイッチ46-4, 46-5, 46-6, ……についても全く同じ接続関係となっている。

【0055】

6本の制御ライン47-1～47-6には、各組の3個の時分割スイッチを選択するための制御信号S1～S3, XS1～XS3が外部から与えられる。ただし、制御信号XS1～XS3は、制御信号S1～S3の反転信号である。この制御信号S1～S3, XS1～XS3は、ドライバIC44から出力される時系列の信号電位に同期して、各組の3個の時分割スイッチを順次オンさせるための信号である。

【0056】

40

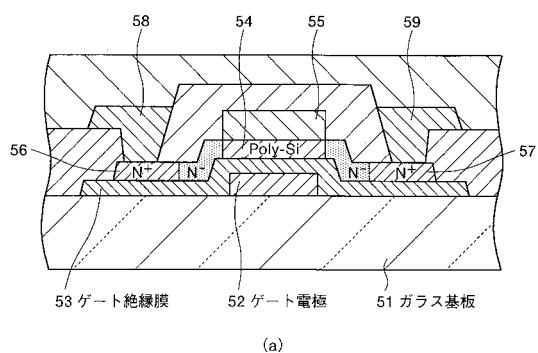

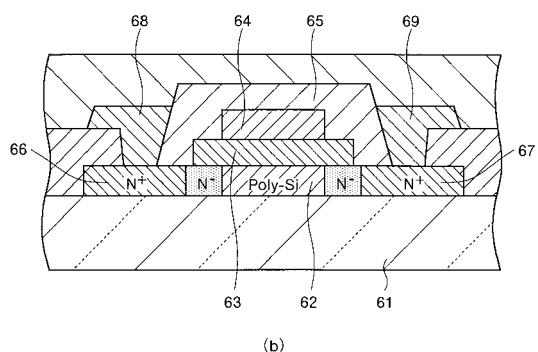

これら各組の時分割スイッチ46-1, 46-2, 46-3, 46-4, 46-5, 46-6, 46-7, 46-8, 46-9、……は、垂直駆動回路43を構成するトランジスタなどと共に、例えば図11(a)に示すボトムゲート構造あるいは同図(b)に示すトップゲート構造の薄膜トランジスタによって液晶表示パネル40内に形成される。

【0057】

図11(a)に示すボトムゲート構造の薄膜トランジスタでは、ガラス基板51の上にゲート電極52が形成され、その上にゲート絶縁膜53を介してポリシリコン(Poly-Si)層54が形成され、さらにその上に層間絶縁膜55が形成されている。また、ゲート電極52の側方のゲート絶縁膜53上には、N+拡散層からなるソース領域56およびドレイン領域57が形成され、これらの領域56, 57にはソース電極58およびドレ

50

イン電極 5 9 がそれぞれ接続されている。

【 0 0 5 8 】

図 1 1 ( b ) に示すトップゲート構造の薄膜トランジスタでは、ガラス基板 6 1 の上にポリシリコン層 6 2 が形成され、その上にゲート絶縁膜 6 3 を介してゲート電極 6 4 が形成され、さらにその上に層間絶縁膜 6 5 が形成されている。また、ポリシリコン層 6 2 の側方のガラス基板 6 1 上には、N+ 拡散層からなるソース領域 6 6 およびドレイン領域 6 7 が形成され、これらの領域 6 6 , 6 7 にはソース電極 6 8 およびドレイン電極 6 9 がそれぞれ接続されている。

【 0 0 5 9 】

これらの時分割スイッチ 4 6 -1 , 4 6 -2 , 4 6 -3 , 4 6 -4 , 4 6 -5 , 4 6 -6 , 4 6 -7 , 4 6 -8 , 4 6 -9 、……は、外部から与えられるゲート選択信号 S 1 , S 2 , S 3 ( 図 9 のタイミングチャートを参照 ) に応答して順次オン状態となることにより、ドライバ I C 4 4 から出力ライン 4 5 -1 , 4 5 -2 , 4 5 -3 , ……に出力される時系列の信号を、1 水平走査期間に 3 時分割して対応する信号ラインに供給する。

10

【 0 0 6 0 】

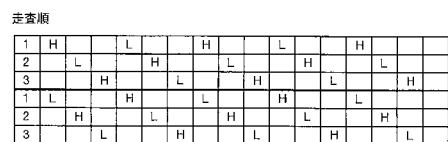

上述した 3 時分割駆動の場合には、時分割数が奇数であることから、図 8 から明らかなように、1 ラインの隣接画素間で極性が反転するドット反転駆動が行われる。なお、図 8 は、図 7 に示す 3 時分割駆動の場合の信号電圧の各画素への書き込み状態を示している。同図において、横方向は走査順、縦方向は時分割スイッチの動作順をそれぞれ示し、また H は高電圧、L は低電圧の書き込み状態をそれぞれ示している。

20

【 0 0 6 1 】

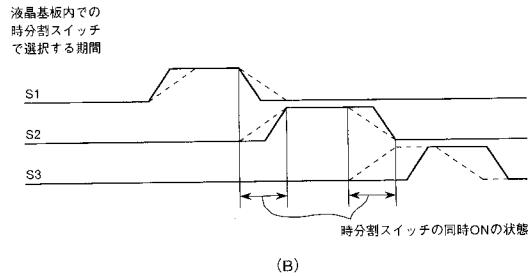

また、図 6 において、ドライバ I C 4 4 から信号ライン 4 2 -1 , 4 2 -2 , 4 2 -3 , ……に信号電位を入力する場合、時分割スイッチ 4 6 がオフとなった信号ラインはハイインピーダンス状態となり、外来の飛び込み電位等の影響を受けやすくなり、信号ラインの電位が変動しやすい。このため、例えば図 1 2 ( A ) に示すような 4 時分割などの場合は、1 つの画素が R , G , B 一組ではないので、各色ごとの信号ラインの電位変動が一定せず、縦方向の色むらの原因となる。

【 0 0 6 2 】

これに対し、図 1 2 ( B ) に示すように、R , G , B の 3 本の信号ラインを 3 時分割すれば、外来の飛び込み電位等に起因する各色ごとの信号ラインの電位変動がほぼ均一となるため、多少の電位変動は強調されないようにすることができる。言い換えれば、R ならば R 、G ならば G 、B ならば B で変動するため、ドライバ I C 4 4 に供給する色信号データにオフセットを持たせることで、所定の信号電位にすることが可能である。また、許容範囲内のソース電位の変動ならば、色度信号としてのずれは発生しなくなる。

30

【 0 0 6 3 】

以上の説明から明らかなように、液晶表示装置に時分割駆動を適用することにより、ドライバ I C 4 4 の出力ピン数を削減できることになる。具体的には、3 時分割駆動の場合には、時分割駆動を用いない場合に比べてドライバ I C 4 4 の出力ピン数を 1 / 3 に削減できるため、ドライバ I C のピン配列方向のサイズの縮小化が図れることになる。

【 0 0 6 4 】

40

このとき、先述した第 2 実施形態のように、ドライバ I C 4 4 の出力ピン数を信号ラインの総本数の約数に設定する場合を考えたとき、第 2 実施形態の数値に対応させると、信号ラインの総本数 3 0 7 2 に対する約数は 1 5 3 6 ( = 5 1 2 × 3 ) となる。このピン数の設定により、ドライバ I C と信号ラインとの接続部分において、画像表示に寄与しない余分な接続領域が生じないようにすることができる。

【 0 0 6 5 】

その結果、今後、S X G A (super X G A ) や U X G A (ultra X G A ) などのように、表示画素が増加する傾向にある表示方式に対して、ドット反転駆動によって良質な画質を安定して供給しつつ、液晶表示モジュールとしてコンパクト化が図れるとともに、安価な液晶表示パネルでカラー表示の多色化を実現することが可能となる。

50

## 【0066】

なお、上記実施形態においては、XGA表示方式を例に採って説明したが、水平方向の画素数が同じSHXGA(super half XGA)およびHXGA(half XGA)の各表示方式にも同様に適用可能である。

## 【0067】

SHXGA表示方式の規格は、1024画素×480画素の画像表示規格であり、アスペクト比を32:15とする。これは横スクロールすることなく、XGA規格信号を表示でき、またVGA(video graphics array)規格をフル表示できることを特徴としている。一方、HXGA表示方式の規格は、1024画素×384画素の画像表示規格であり、アスペクト比を8:3とする。これはXGA規格の携帯用端末規格と考えられている。 10

## 【0068】

これらの表示規格から明らかなように、XGA、SHXGA、HXGAの各表示方式は、水平方向の画素数がいずれも1024画素であることから、信号ラインの総本数はいずれも3072本であり、信号ラインを駆動するドライバIC44については共通に考えることができる。

## 【0069】

ところで、液晶表示装置の分野では近年、装置のコンパクト化、特に液晶表示パネルの狭幅化が積極的に押し進められている。液晶表示パネルの狭幅化を実現するには、液晶表示パネルの額縁部分のサイズ(以下、額縁サイズと略称する)をできるだけ小さくすれば良い。現行の製造技術のもとでは、一例として、4mm以下の額縁サイズが狙いとなる。 20

## 【0070】

一方、液晶表示パネルの外部回路であるドライバIC44の実装方式として例えばTAB(Tape Automated Bonding)方式を用いた場合、TABのパッドサイズが現行2mm程度であることから、額縁サイズ4mm以下を満足するためには、TABと時分割スイッチ46-1, 46-2, 46-3, 46-4, 46-5, 46-6, 46-7, 46-8, 46-9, .....との間の配線および接続に要する領域のサイズを2mm以下に抑えることが必要となる。

## 【0071】

以上のことを踏まえて、ドライバICの出力ピン数を信号ラインの総本数の約数に設定するようにした第2実施形態のもとに、R, G, B3時分割駆動の場合を例に採って、ドライバICの個数の設定についての具体例を各表示方式ごとに以下に説明する。 30

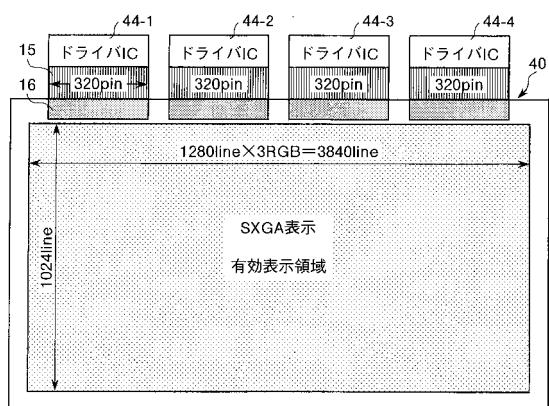

## 【0072】

先ず、SXGA表示方式の液晶表示装置の場合について説明する。SXGA表示方式の規格は、1280画素×1024画素であり、1画素がR, G, Bの3ドットからなることから、信号ラインの総本数(=水平方向のドット数)は3840(=1280×3)本となる。

## 【0073】

一方、現行のパターニング技術では、配線幅が4μm程度、配線間隔が3.5μm程度であることから、1本の配線につき7.5μm程度のスペースが必要となる。先述したように、液晶表示パネルの額縁サイズとして4mm以下を狙った場合、配線および接続に許容されるスペースは2mm以下であることから、額縁部分に配線可能な最大配線本数として、266(2mm/7.5μm)本程度という数値が導き出される。 40

## 【0074】

ただし、ドライバICの出力ピンのピッチに対して信号ラインの配線ピッチの方が広いことから、ドライバICの出力ピンと時分割スイッチとの間を電気的に接続するフレキシブルケーブルは、液晶表示パネルの額縁部分で左右に半分ずつ分けられることになることから、ドライバICの出力ピン数としては最大、最大配線可能本数(266本)の2倍、即ち532本程度となる。

## 【0075】

以上のことから明らかなように、SXGA表示方式の場合は、532本以下でかつ信号ライン数(3840ライン)の約数であることが条件となることから、ドライバICの出 50

力ピン数として例えば320本が設定される。そして、3時分割駆動の場合は、ドライバICの総出力ピン数としては、信号ライン数(3840ライン)の3分の1で良いことから、本例では、ドライバICの個数として、4( $=1280/320$ )個が設定される。

#### 【0076】

すなわち、SXGA表示方式の液晶表示装置において、3時分割駆動を採った場合には、図13に示すように、各々320本の出力ピンを持つ4個のドライバIC44-1~44-4が、液晶表示パネル40とは別体の外部基板(図示せず)上に一定の間隔をもって配置され、フレキシブルケーブル15を介して液晶表示パネル40の額縁の接続部分16にて時分割スイッチ(図示せず)と接続されることになる。

#### 【0077】

このように、SXGA表示方式の液晶表示装置において、3時分割駆動を採ることにより、ドライバICの出力ピン数として例えば320本を設定した場合、ドライバICの個数が4個で済むため、3時分割駆動を採らず、例えば384ピンの汎用ドライバICを用いると、10( $=3840/384$ )個のドライバICを必要としていた場合に比べて、スタンバイ電力は5分の2以下となる。

#### 【0078】

また、ドライバICのコスト低減にもつながる。しかも、今後、集積回路技術の進歩に伴い、これ以上のドライバICのピン数が期待され、それに伴って3個以下のドライバICの個数の設定も可能となるため、消費電力と製品コストのより低減を期待できることになる。

#### 【0079】

ところで、SXGA表示方式の水平走査時間は、規格上、21.537μs、15.63μs、12.504μsおよび10.971μsと決められている。この規格のもとで、図10および図13の構成を実現するためには、例えば一番短い水平走査時間である10.971μsに合わせる必要がある。

#### 【0080】

ここで、3時分割を行う訳であるから、10.971μsの3分割以下の時間で選択する必要がある。つまり、サンプリング時間が3.657μs以下であることが必要となる。同様に、水平走査時間が21.537μsならば7.179μs、15.63μsならば5.21μs、12.504μsならば4.168μs以下のサンプリング時間となる。

#### 【0081】

また、図14のタイミングチャートにおいて、ドライバIC44から信号ラインに対して出力される出力波形の立ち上がり、立ち下がり時間(スルーレート)については、上記サンプリング時間内に終了する必要があるため、選択期間よりも小さくする必要がある。なお、ドライバIC44の立ち上がり、立ち下がりの定義は、電位が0% 99.75%まで変位する時間である。一例として、信号ラインの信号振幅が9Vである場合、0.00225Vの誤差となる。

#### 【0082】

また、Rの時分割スイッチが選択された後、2つ目の時分割スイッチが選択されるまでの期間にブランкиング期間を設ける必要がある。これは、電位が確定した非選択信号ラインの信号電位が変動するためである。時分割スイッチに接続された選択信号ラインは大型化していくと、どうしても寄生容量や配線抵抗が存在するようになり、これに起因して選択ライン時間に遅延が発生する。すると、隣接する時分割スイッチが同時にオン/オフすることになるため、非選択の信号ラインの信号電位は確定できなくなる。

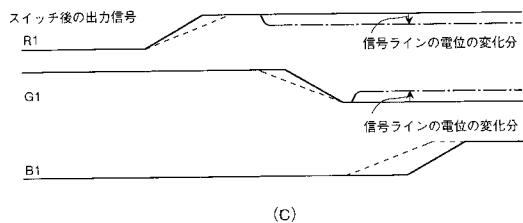

#### 【0083】

これを示したのが、図15の波形図である。図15において、(A)は入力端子での時分割スイッチで選択する期間を、(B)は液晶基板内での時分割スイッチで選択する期間を、(C)は時分割スイッチ後の信号出力をそれぞれ示している。また、実線がブランкиング期間を設けた場合を、点線がブランкиング期間を設けない場合をそれぞれ表している

10

20

30

40

50

。

## 【0084】

図15(C)から明らかなように、ランキング期間を設けない場合(点線)は、電位が確定した非選択信号ラインの信号電位が一点鎖線で示す如く変動することから、SXGA表示方式の液晶表示装置を作製する際には、図14のタイミングチャートに示すように、(水平方向の走査時間 - 選択時間 × 3) / 3 の時間以下のランキング期間(a), (b), (c)を設定することが必要である。また、ランキング期間(c)では、図14のタイミングに示すように、各段のゲートラインを選択するゲート選択パルスが切り替わらなければならない。

## 【0085】

10

このゲート選択パルスについても遅延時間が発生し、このため隣接するゲートラインが同時にオン/オフすることになり、画素電位の変動を引き起こすことになる。これを防止するために、ゲート選択パルスの切り替え期間にもランキング期間が必要となる。したがって、ランキング期間(c)として、(水平方向の走査時間 - 選択時間 × 3) / 3 で不十分であれば、それ以上の時間を必要とすることになる。現有する選択スイッチの駆動回路では、短いランキング期間は 40 ns は必要であり、これが最小値となる。

## 【0086】

また、図16に示す液晶画素の回路構成において、ゲートライン 41-1, 42-2, 41-3, ……と信号ライン(ソースライン) 42-1, 42-2, 43-3, 43-4, ……との間に寄生する容量 Cgs や、画素の対向電極にコモン電圧 VCOM を供給する Cs ライン 48-1, 48-2, 48-3, ……と信号ライン 42-1, 42-2, 43-3, 43-4, ……との間に寄生する容量 Ccs に起因する信号ライン 42-1, 42-2, 43-3, 43-4, ……からの飛び込み電位により、図17の波形図に示すように、ゲートライン 41-1, 42-2, 41-3, ……のゆれや Cs ライン 48-1, 48-2, 48-3, ……の周期的な変動が誘起される。その結果、横方向のクロストークが発生する。

20

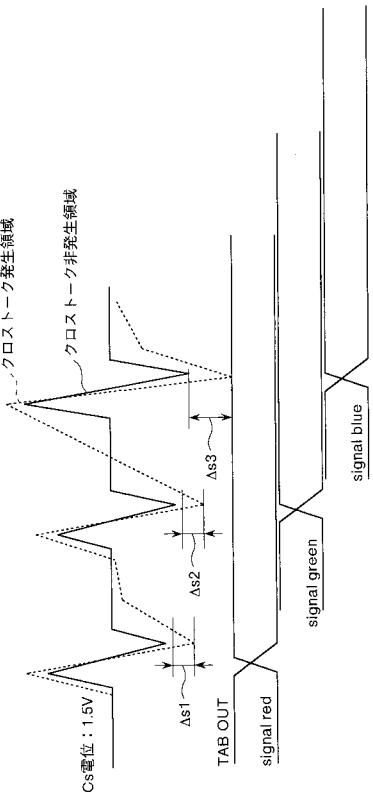

## 【0087】

特にこの Cs ライン 48-1, 48-2, 48-3, ……のゆれの変動電位が、図19に示す s1, s2, s3 となる。ここに、s1, s2, s3 は、クロストーク発生領域と非発生領域との電位差である。この電位差 s1, s2, s3 は、70 mV 以下であれば、画像として判断されないことがわかっている。つまり、現状、これを満たせば、横方向のクロストークとしては判断されない訳である。

30

## 【0088】

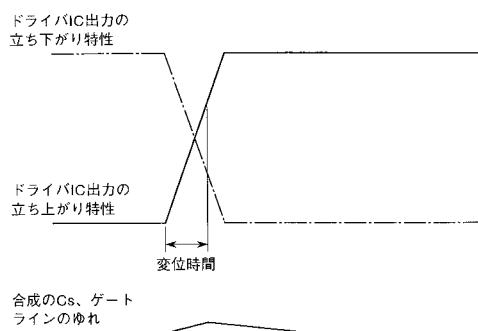

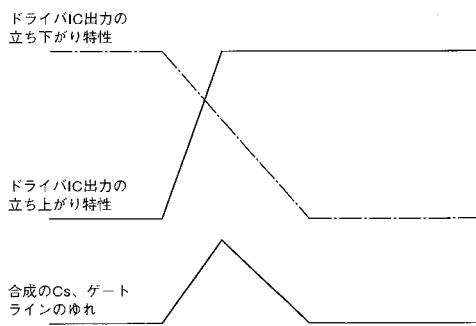

このゲートライン 信号ライン間容量 Cgs、Cs ライン 信号ライン間容量 Ccs に起因するゲートライン 41-1, 42-2, 41-3, ……のゆれや Cs ライン 48-1, 48-2, 48-3, ……の周期的な変動を防ぐために、大型液晶表示装置では、先述したように、隣接する画素間の極性を対向電極を基準に反転させるドット反転駆動方式を採用している。このドット反転駆動方式の場合には、立ち上がり時間、立ち下がり時間が、信号ライン 42-1, 42-2, 42-3, ……が 1 対 1 でドライバ IC 44 の出力ピンに接続されている従来の液晶表示装置に比べて無視できない時間となる。

40

## 【0089】

時分割数が 3 の場合には、Cs ライン 48-1, 48-2, 48-3, ……を安定させる時間は従来の 3 分の 1 となり、条件は厳しくなる。この対策として、特に、Cs ライン 48-1, 48-2, 48-3, ……のゆれに起因する横方向のクロストークをなくす必要がある。そのためには、図18の波形図に示すように、ドライバ IC 44 の立ち上がり波形と立ち下がり波形を時間軸に対して対称にする、即ち立ち上がり時間と立ち下がり時間を等しくする必要がある。

## 【0090】

このように、ドット反転駆動においては、ドライバ IC 44 の立ち上がり波形と立ち下がり波形を時間軸に対して対称にすることにより、逆極性の信号によって変動電位分をキャンセルできることになるため、ゲートライン 41-1, 41-2, 41-3, ……および Cs

50

ライン 48-1, 48-2, 48-3, ……の変動がほとんどなくなる。この変動分が小さければ小さいだけ、C s ライン 48-1, 48-2, 48-3, ……の電位が安定する時間は短くなる。

#### 【0091】

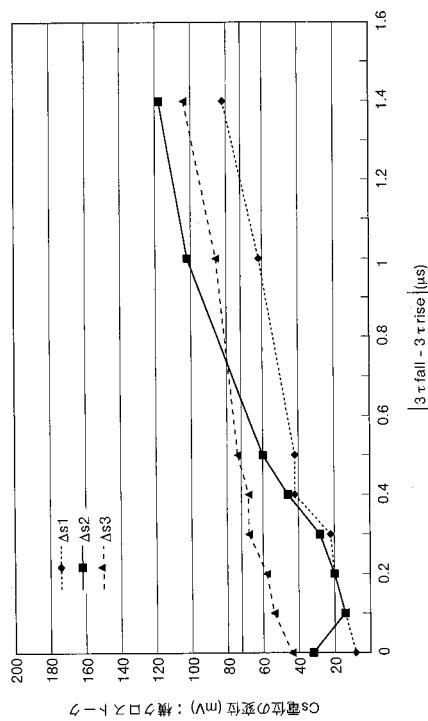

図20に、一例として、17インチSXGA表示方式の場合のシミュレーション結果を示す。このシミュレーション結果から考えると、3 rise (立ち上がり)、3 fall (立ち下がり)の時間差は、500ns以下であることが望ましいことがわかる。これにより、下記の条件を満たすことが必要となる。 $|3\ rise - 3\ fall| \leq 500\ ns$  もしくは、 $|2\ rise - 2\ fall| \leq 500\ ns$  ここに、3は0.5μs一定であり、3は0%から90%推移を、2は0%から86%推移をそれぞれ表している。10

#### 【0092】

ここで、立ち上がり波形と立ち下がり波形が対称性をあらわすものとして、0% 63%の変位時間、0% 86%の変位時間、0% 95%の変位時間、0% 98%の変位時間、0% 99.3%の変位時間、0% 99.8%の変位時間が同じであることが条件となる。図21に、SXGA表示方式の液晶表示装置を作製する場合における期間の数値の一例を示す。

#### 【0093】

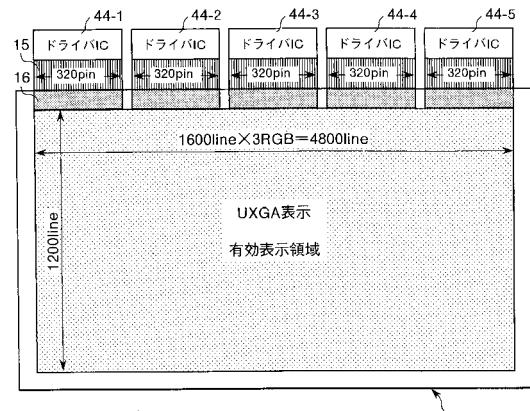

次に、UXGA表示方式の液晶表示装置の場合について説明する。UXGA表示方式の規格は、1600画素×1200画素であり、1画素がR, G, Bの3ドットからなることから、信号ラインの総本数は4800 (= 1600 × 3) 本となる。20

#### 【0094】

ここで、先述したSXGA表示方式の場合と同様の条件のもとに、ドライバICの出力ピン数として例えば320本を設定したとすると、3時分割駆動の場合は、ドライバICの総出力ピン数としては、信号ライン数(4800ライン)の3分の1で良いことから、本例では、ドライバICの個数として、5 (= 1600 / 320) 個が設定される。

#### 【0095】

すなわち、UXGA表示方式の液晶表示装置において、3時分割駆動を採った場合には、図22に示すように、各々320本の出力ピンを持つ5個のドライバIC 44-1~44-5が、液晶表示パネル40とは別体の外部基板(図示せず)上に一定の間隔をもって配置され、フレキシブルケーブル15を介して液晶表示パネル40の額縁の接続部分16にて時分割スイッチ(図示せず)と接続されることになる。30

#### 【0096】

このように、UXGA表示方式の液晶表示装置において、3時分割駆動を採ることにより、ドライバICの出力ピン数として例えば320本を設定した場合、ドライバICの個数が5個で済むため、3時分割駆動を採らず、例えば384ピンの汎用ドライバICを用いると、13 (= 4800 / 384 = 12余り92) 個のドライバIC(内、1個は92ピンのみ使用)を必要としていた場合に比べて、スタンバイ電力は13分の5以下となる。40

#### 【0097】

また、ドライバICのコスト低減にもつながる。しかも、今後、集積回路技術の進歩に伴い、これ以上のドライバICのピン数が期待され、それに伴って4個以下のドライバICの個数の設定も可能となるため、消費電力と製品コストのより低減が期待できることになる。

#### 【0098】

ところで、UXGA表示方式の水平走査時間は、規格上、16μs、13.333μs、12.308μs、11.429μs、10.667μs、10μsおよび9.412μsと決められている。この規格のもとで、図10および図22の構成を実現するためには、例えば一番短い水平走査時間である9.412μsに合わせる必要がある。ここで、3時分割を行う訳であるから、9.412μsの3分割以下の時間で選択する必要がある50

。つまり、サンプリング時間が  $3.137 \mu s$  以下であることが必要となる。

【0099】

同様に、水平走査時間が  $16 \mu s$  ならば  $5.333 \mu s$ 、  $13.333 \mu s$  ならば  $4.444 \mu s$ 、  $12.308 \mu s$  ならば  $4.103 \mu s$ 、  $11.429 \mu s$  ならば  $3.810 \mu s$ 、  $10 \mu s$  ならば  $3.333 \mu s$  以下のサンプリング時間となる。

【0100】

なお、ドライバIC44の出力波形の立ち上がり、立ち下がり時間（スルーレート）、ブランкиング期間の設定およびドライバIC44の出力の立ち上がり波形と立ち下がり波形との対称性については、先述したSXGA表示方式の場合と同様のことが言える。図23に、UXGA表示方式の液晶表示装置を作製する場合における期間の数値の一例を示す。

【0101】

以上、SXGA、UXGAの各表示方式の液晶表示装置の場合について述べたが、続いて、VGA、HVGA(half VGA)、QVGA(quarter VGA)の各表示方式の液晶表示装置の場合について述べる。

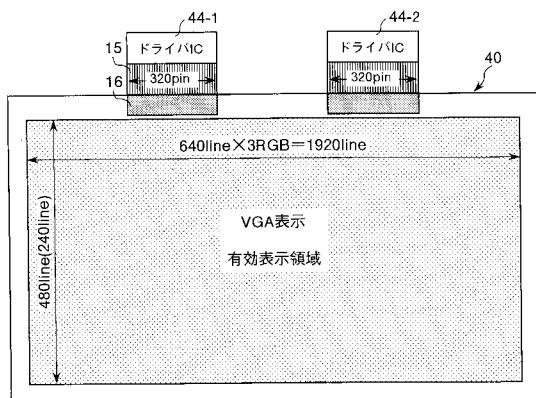

【0102】

先ず、VGA表示方式の液晶表示装置の場合について説明する。VGA表示方式の規格は、 $640$ 画素  $\times 480$ 画素であり、1画素がR, G, Bの3ドットからなることから、信号ラインの総本数は  $1920$  ( $= 640 \times 3$ ) 本となる。

【0103】

ここで、先述したSXGA、UXGAの各表示方式の場合と同様の条件のもとに、ドライバICの出力ピン数として例えば320本を設定したとすると、3時分割駆動の場合は、ドライバICの総出力ピン数としては、信号ライン数(4800ライン)の3分の1で良いことから、本例では、ドライバICの個数として、 $2$  ( $= 640 / 320$ ) 個が設定される。

【0104】

すなわち、VGA表示方式の液晶表示装置において、3時分割駆動を採った場合には、図24に示すように、各々320本の出力ピンを持つ2個のドライバIC44-1, 44-2が、液晶表示パネル40とは別体の外部基板(図示せず)上に一定の間隔をもって配置され、フレキシブルケーブル15を介して液晶表示パネル40の額縁の接続部分16にて時分割スイッチ(図示せず)と接続されることになる。

【0105】

このように、VGA表示方式の液晶表示装置において、3時分割駆動を採ることにより、ドライバICの出力ピン数として例えば320本を設定した場合、ドライバICの個数が2個で済むため、3時分割駆動を採らず、例えば384ピンの汎用ドライバICを用いると、 $6$  ( $= 1920 / 384 = 5$  余り  $10$ ) 個のドライバIC(内、1個は10ピンのみ使用)を必要としていた場合に比べて、スタンバイ電力は3分の1以下となる。

【0106】

また、ドライバICのコスト低減にもつながる。しかも、今後、集積回路技術の進歩に伴い、これ以上のドライバICのピン数が期待され、それに伴ってドライバICの1個の設定も可能となるため、消費電力と製品コストのより低減が期待できることになる。

【0107】

なお、HVGA表示方式の規格は、 $640$ 画素  $\times 240$ 画素であり、水平方向の画素数についてはVGA表示方式と同じであることから、信号ラインの総本数についても同じ1920本である。したがって、ドライバICの出力ピン数として例えば320本を設定した場合、設定されるドライバICの個数も同じ2個となる。

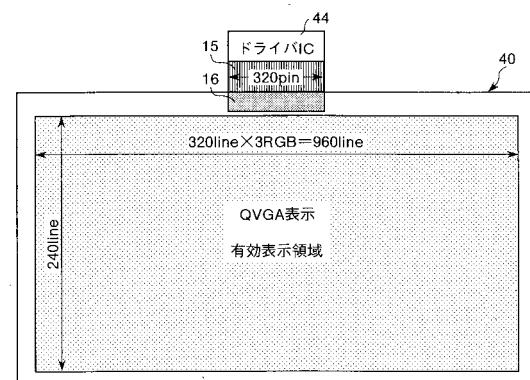

【0108】

一方、QVGA表示方式の規格は、 $320$ 画素  $\times 240$ 画素であることから、信号ラインの総本数は960本となる。ここで、ドライバICの出力ピン数として例えば320本を設定したとすると、3時分割駆動の場合は、ドライバICの総出力ピン数としては、信

10

20

30

40

50

号ライン数(960ライン)の3分の1で良いことから、QVGA表示方式では、図25に示すように、ドライバICの個数として、1(=320/320)個が設定される。

#### 【0109】

ところで、例えば、標準的なVGA規格IBM VGA (mode-4)表示方式では、その水平走査時間は31.778μsである。ここで、3時分割を行う訳であるから、31.778μsの3分割以下の時間で選択する必要がある。つまり、サンプリング時間が10.59μs以下であることが必要となる。QVGA表示方式では、例えば水平走査時間を63μsとすると、3時分割でサンプリング時間が10.59μs以下であることが必要となる。

#### 【0110】

なお、ドライバIC44の出力波形の立ち上がり、立ち下がり時間(スルーレート)、ブランкиング期間の設定およびドライバIC44の出力の立ち上がり波形と立ち下がり波形との対称性については、先述したSXGA表示方式の場合と同様のことが言える。図26に、VGA, QVGAの各表示方式の液晶表示装置を作製する場合における期間の数値の一例を示す。

#### 【0111】

上述したように、例えば3時分割駆動において、液晶表示パネル40の額縁サイズが規定されるとき、その規定された額縁サイズのもとに、その額縁部分の配線領域に配線可能な配線数によってドライバIC44の出力ピン数nを決定するとともに、表示方式によって決まる信号ラインの総本数をNとするとき、ドライバIC44の個数をN/n個に設定するようにしたことにより、時分割駆動を採らない場合に比べてドライバICの個数を大幅に削減でき、スタンバイ電力を大幅に軽減できるため、液晶表示装置全体の低消費電力化が可能となる。

#### 【0112】

ところで、表示方式に限らず、図14のタイミングチャートにおけるブランкиング期間(a), (b), (c)では、時分割スイッチ(アナログスイッチ)がオフ状態にあり、信号ラインの電位が確定状態にある。このため、外部ICであるドライバICからの出力に影響されない。したがって、このブランкиング期間(a), (b), (c)にドライバICの出力回路を駆動させることは、消費電力の無駄である。

#### 【0113】

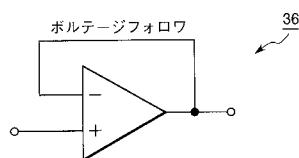

図3には、ドライバICの内部構成の一例を示したが、実際には、図27に示すように、D/Aコンバータ35の後段に出力回路36が配されているのが一般的である。そこで、ここでは、ブランкиング期間(a), (b), (c)に出力回路36を停止させ、消費電力の低減を図ることとする。この出力回路36は、図28に示すように、例えば、オペアンプと出力バッファからなるボルテージフォロワの回路構成となっている。

#### 【0114】

このボルテージフォロワ回路構成の出力回路36において、例えば、ブランкиング期間(a), (b), (c)にボルテージフォロワの電源をオフにすると、オペアンプ部に電流が流れなくなり、出力は高インピーダンス状態となる。このように、ブランкиング期間(a), (b), (c)に出力回路36を停止させることで、消費電力を低減することになる。

#### 【0115】

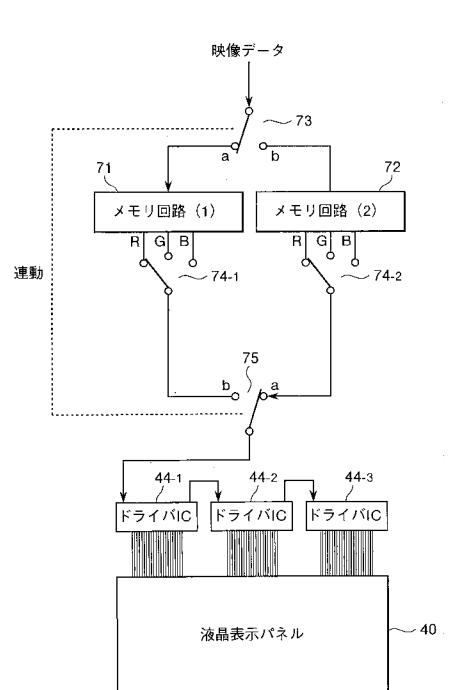

次に、信号ラインを駆動するドライバICへのデータの書き込みについて説明する。通常、液晶表示パネル40には、図29に示すように、例えば3個のドライバIC44-1, 44-2, 44-3を経由して各々1ライン分相当の記憶容量を持つ2個のメモリ回路(1)71, (2)72が接続されている。

#### 【0116】

そして、最初は、メモリ回路71に1ライン分のデータを記憶し、かかる後スイッチ73を切り替えて次の1ラインの期間中にメモリ回路72にデータを記憶しながら、スイッチ73に連動するスイッチ75でRのみを選択してメモリ回路71からRデータをスイッ

10

20

30

40

50

チ74-1を介して1ライン分読み出してドライバIC44-1, 44-2, 44-3に書き込み、次にGのみを選択して同様にGデータを1ライン分書き込み、最後にBのみを選択して同様にBデータを1ライン分書き込む。

【0117】

次の1ライン期間にはメモリ回路71とメモリ回路72とを入れ替えて同様の手順を繰り返すことによって画像を構成していく。一般的に、一番端のドライバICに1ドットずつ水平ドット数分のデータを転送していくと数珠状にデータが送られて1ライン分のデータが複数のドライバICにセットされ、その時点で液晶表示パネル40に一斉に1ライン分のデータを書き込むことで各色1ラインずつ画像を形成していく。この作業を垂直画素数×3回分繰り返すことで1枚の画像が構成される。

10

【0118】

ところが、昨今の液晶表示装置の高画素化に伴って水平方向の画素数も増え、また同時に、映像データの転送レートも早くなり、液晶表示パネルへの書き込み時間も短くなっている。一例として、SXGA表示方式の液晶表示装置を考えた場合、映像データが200MHz前後のデータ転送レートであり、この速度でデータが書き込めるドライバICは現時点では存在しない。

【0119】

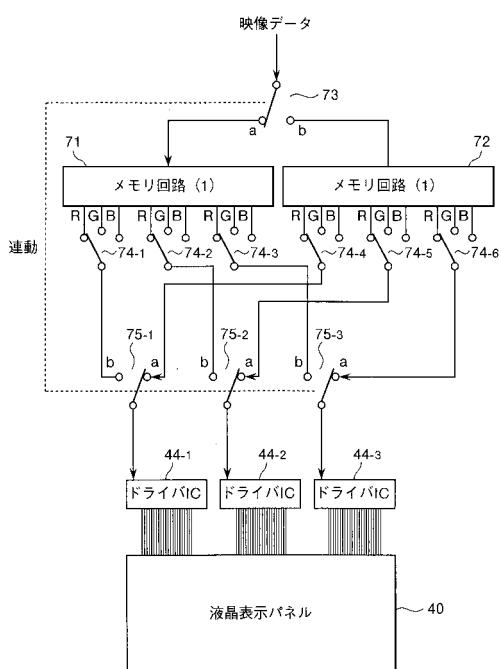

そこで、本実施形態においては、複数のドライバICに同時に別々のデータを書き込む手法を探ることで、既存のドライバICでも使用できるようにする。これを実現するための具体的な構成の一例を図30に示す。本例では、話を分かり易くするため、水平30画素(R, G, B合計90ドット)、ドライバIC内のシフトレジスタ31(図27参照)の段数を各々10段と仮定して説明する。

20

【0120】

図30に示すように、各々1ライン分相当の記憶容量を持つメモリ回路(1)71とメモリ回路(2)72が設けられ、これらを切り替えるスイッチ73を経由して映像データがメモリ回路71又はメモリ回路72に供給される。メモリ回路71, 72の出力側には、3端子ごとに1個ずつR, G, Bの各色を切り替えるスイッチ74-1~74-6が設けられ、さらにその後段に再度メモリ回路71とメモリ回路72とを切り替えるスイッチ75-1~75-3が設けられている。そして、スイッチ75-1~75-3の各選択出力がドライバIC44-1~44-3に与えられるようになっている。

30

【0121】

また、メモリ回路71, 72には、ドライバICの数と同じ数のR, G, Bの出力があり、これらは各々1~10ドット、11~20ドット、21~30ドットのデータを順に出力するように構成されている。一方、メモリ回路71, 72の前段および後段に配されているスイッチ53とスイッチ75-1~75-3は互いに運動しており、片方がメモリ回路71を選択すると、もう一方はメモリ回路72を選択するようになっている。

【0122】

上記の構成において、外部から入力される映像データは、最初はスイッチ73がメモリ回路71側に切り替わっていることにより、このスイッチ73を介してメモリ回路71に1ライン分蓄えられる。その後、スイッチ73がメモリ回路72側に切り替わることにより、次の1ライン分の映像データはメモリ回路72に蓄えられる。

40

【0123】

そのとき、メモリ回路71はドライバIC44-1に対して1~10ドット目のデータを出力し、ドライバIC44-2に対しては11~20ドット目のデータを出力し、又ドライバIC44-3に対しては21~30ドット目のデータを出力する。そして、次の1ラインではメモリ回路71とメモリ回路72とを入れ替えて、上記と同様の動作を行ってこれを繰り返すことにより、1枚の画像が構成される。

【0124】

このように、最初はメモリ回路71に1ライン分のデータを記憶し、次の1ライン期間中にメモリ回路72にデータを記憶しながら、スイッチ74-1~74-3でRのみを選択し

50

てメモリ回路 7 1 から R データを 1 つのドライバ I C 分だけ読み出して当該ドライバ I C に書き込み、同時に別のドライバ I C にも該当するデータを読み出して当該ドライバ I C に書き込み、G および B についても同様の方法にて書き込みを行うことにより、ドライバ I C の各々に同時に別々のデータを書き込むことができる。

【 0 1 2 5 】

これにより、各ドライバ I C にデータを書き込む速度を、ドライバ I C の数を n とすると、n 分の 1 に減速することができる、例えば映像データの転送レートが 2 0 0 M H z、ドライバ I C の数 n が 3 個であれば、約 6 7 M H z の動作速度を持つドライバ I C で処理できることになり、既存のドライバ I C でも十分に対応できることになる。また、1 ライン分全てのデータを各ドライバ I C に書き込む時間を n 分の 1 に短縮することができる、その分だけ液晶表示パネルへの書き込み時間を延ばすこともできる。 10

【 0 1 2 6 】

ところで、従来の液晶表示装置では、R, G, B の各々の電圧透過率特性は一致していなかった。その理由は、色ごとに波長が違うため、その波長に依存して液晶分子内での屈折率に差異が生じ、結果的に電圧、透過率特性が B に対して R が負の電圧側にずれているからである。

【 0 1 2 7 】

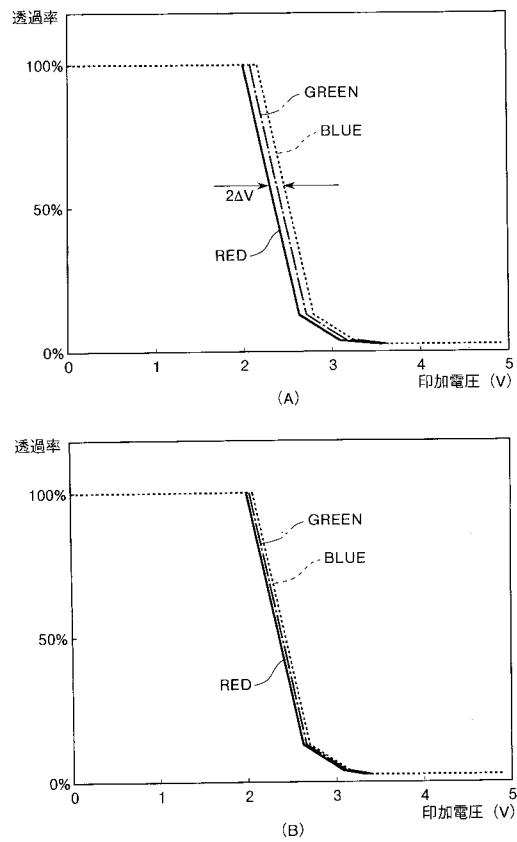

図 3 1 ( A ) に、T N (twist nematic) 液晶を使用した場合の液晶の透過率と液晶に印加する電圧の特性カーブ ( V - T カーブ ) を示す。この特性図から明らかのように、通常、R ( 透過波長が 6 0 0 n m ~ 6 6 0 n m ) 、G ( 透過波長が 3 7 0 n m ~ 4 6 0 n m ) 、G ( 透過波長が 5 3 0 n m ~ 5 5 0 n m ) で、V - T カーブがシフトしている。 20

【 0 1 2 8 】

これは波長に依存して液晶分子の屈折率に差異があるためである。波長の長い R の方が屈折率が小さいため、液晶に電圧を印加したとき、いち早く液晶による光の 9 0 度回転が損なわれる。B は屈折率が大きいため、光の 9 0 度回転が最後まで維持される。このため、V - T カーブにおいて、同じ電圧を印加しても透過率に差異が発生する。

【 0 1 2 9 】

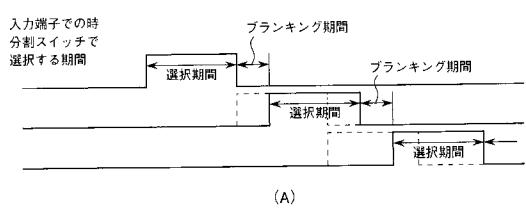

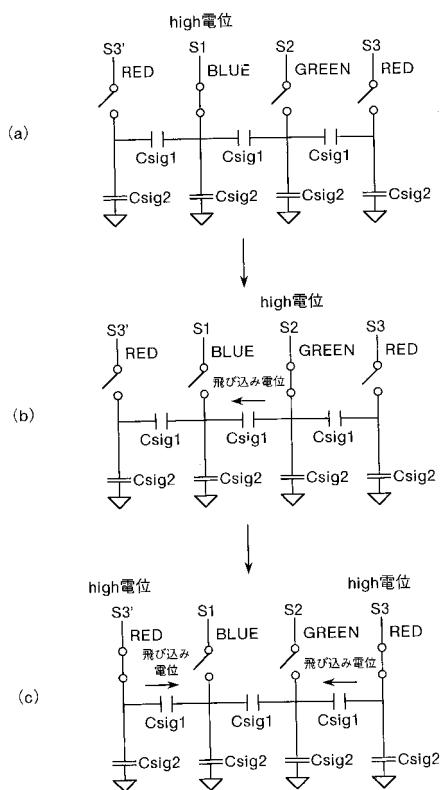

液晶基板内の水平方向に時分割スイッチ ( アナログスイッチ ) を配置した構成の本発明に係る液晶表示装置において、選択スイッチ以外の信号ラインはフローティング状態となっており、この状態では、隣接する信号ライン間での信号電位の飛び込みの影響を受ける。つまり、画素の信号ライン間にはライン間の容量が存在し、時分割スイッチの周辺の等価回路を示す図 3 2 において、例えばスイッチ S 1 が選択 ( a ) された後にスイッチ S 2 が選択 ( b ) されると、スイッチ S 2 の “ H ” レベルの信号がスイッチ S 1 に飛び込み、保持されている電圧が飛び込み容量分だけ増加する。 30

【 0 1 3 0 】

これは、信号ライン間の容量を C sig1 とし、一つの信号ラインの容量を C sig2 とすると、飛び込みによる電圧 V は、 $V = V_{sig} \times C_{sig1} / ( C_{sig1} + C_{sig2} ) \dots (1)$  となる。ここで、V sig は、選択された信号ラインに入力される信号電圧の振幅電圧である。この値を、ちょうど、液晶の V - T カーブでの中間調の同じ透過率の状態での印加電圧のシフト量を補完するように定めれば良い。 40

【 0 1 3 1 】

R と B の電圧のシフト量は 0 . 3 V であり、これを飛び込みによる電圧 V に当てはめる。ちなみに、1 H V C O M ( コモン ) 反転駆動法では、1 H 時間は同一極性の電圧が信号ラインに印加されるため、先に選択されたスイッチ S 1 については、次のスイッチ S 2 が選択された場合に、保持された信号ラインの電位は増加する。

【 0 1 3 2 】

また、スイッチ S 3 が次に選択 ( c ) される。これは、スイッチ S 1 に隣接するスイッチ S 3 から飛び込み電位が入力されることを意味する。最終的には、スイッチ S 1 に関しては 2 回、スイッチ S 2 に関しては 1 回、信号ライン間の飛び込みの影響を受けることになる。 50

## 【0133】

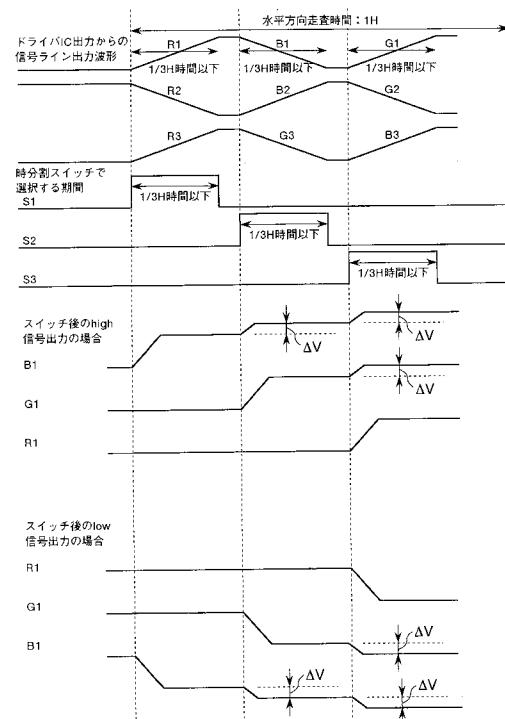

ここでは、この現象に着目して、液晶の色に依存してV-Tカーブの電圧シフトを補完する方法について述べる。ちなみに、1H反転駆動法に関しては、図33のタイミングチャートから明らかなように、1番目に選択される信号ラインをB、2番目に選択される信号ラインをG、3番目に選択される信号ラインをRとする配置として、先に述べたV-Tカーブの補完を行っている。

## 【0134】

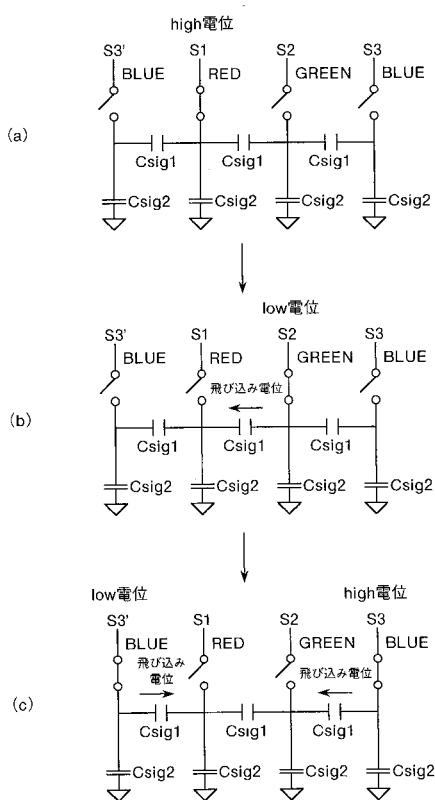

一方、ドット反転駆動を行う場合、隣接する信号ライン間には常に逆の極性が印加されるため、信号電位（振幅電位）としては、小さくなる方向で飛び込み電圧が発生する。つまり、図34に示すように、スイッチS1が“H”レベルで書き込まれ（a）、その後スイッチS2が“L”レベルで書き込まれると（b）、非選択状態のスイッチS1に対して“L”レベルの電位が飛び込む。その後、スイッチS3に“H”レベルが書き込まれるが（c）、スイッチS3に隣接するスイッチS1に対しては、同様に“H”レベルの飛び込みが発生する。

10

## 【0135】

しかし、スイッチS1に隣接するスイッチS3はドット反転駆動であるため“L”レベルとなる。これがスイッチS1に飛び込み、さらに電圧が減少する。結局、一番最初に選択されたスイッチS1に対しては、信号電圧を減少させる電圧が2回発生し、スイッチS2に対しては、信号電圧を減少させる電圧が1回発生する。

## 【0136】

20

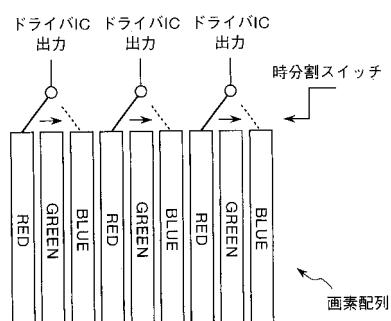

これを、液晶のR, G, BのV-Tカーブにおける電圧シフトを補完させるようにするために、図35のタイミングチャートから明らかなように、一番最初に選択される信号ラインをRとし、2番目をG、3番目をBとすることが好ましいことがわかる。

## 【0137】

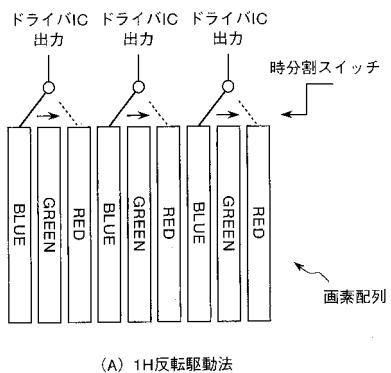

以上の方法を探ることにより、図31（B）に示すように、中間調での電圧-透過率の特性カーブは補完され、画像信号に忠実な表示が可能となる。図36には、本発明に係る画素配列と時分割スイッチの走査方向の関係を示す。同図において、（A）は1H反転駆動法の場合を、（B）はドット反転駆動法の場合をそれぞれ示している。

## 【0138】

なお、上述した方法は、信号ライン間に存在する容量を積極的に、液晶の電圧-透過率特性の補完に使用しているため、複雑な回路構成を必要とせず、色配列だけを所定の順番にすることにより達成できる点で、その効果は極めて大きいと言える。

30

## 【0139】

ただし、信号ライン間の容量Csig1と信号ライン自体の容量Csig2は、先に示した（1）式に対して、 $V = V_{sig} \times Csig1 / (Csig1 + Csig2)$ （液晶内での電圧-透過率特性のRとGの電圧差）の条件を満たすことが必要となる。例えば、液晶内での電圧-透過率特性のRとGの電圧差が0.15V、選択された信号ラインに入力される信号電圧の振幅電圧Vsigが9Vである場合、これを補正するには、 $Csig1 / (Csig1 + Csig2)$ が0.017となるように設計すれば良い。

## 【0140】

40

このように、各表示方式の液晶表示装置において、ドライバIC44からは、R, G, Bの電圧-透過率（V-T）特性のカーブを補正するような信号電位を発生するようにしたことにより、中間調付近でのR, G, Bの透過率が一致するため、画像信号に対してより忠実な色表現が可能となる。また、複雑な回路構成を必要としないため、製造歩留りを低下させることなく、色精度を向上させることができる。

## 【図面の簡単な説明】

## 【0141】

【図1】本発明に係るマトリクス型液晶表示装置における液晶表示部の配線図である。

【図2】画素の回路構成図である。

【図3】ドライバICの内部構成の一例を示すブロック図である。

50

【図4】本発明の第1実施形態を示す概略構成図である。

【図5】本発明の第2実施形態を示す概略構成図である。

【図6】時分割駆動を用いたマトリクス型液晶表示装置における液晶表示部の配線図である。

【図7】3時分割駆動の場合の時分割スイッチの接続構成図である。

【図8】3時分割駆動の場合の信号電圧の各画素への書き込み状態を示す図である。

【図9】3時分割駆動の場合の各信号のタイミングチャートである。

【図10】ある1組の時分割スイッチの具体的な構成を示す回路図である。

【図11】薄膜トランジスタの一例を示す断面構造図であり、(a)はボトムゲート構造の場合を、(b)はトップゲート構造の場合をそれぞれ示している。

10

【図12】4時分割の場合(A)と3時分割の場合(B)との比較図である。

【図13】SXGA表示方式の液晶表示装置の一例の構成図である。

【図14】SXGA表示方式の動作説明のためのタイミングチャートである。

【図15】プランギング期間を設けた場合(実線)と設けない場合(点線)の違いを説明するための波形図である。

【図16】液晶画素の回路構成を示す回路図である。

【図17】ドライバICの立ち上がり波形と立ち下がり波形が時間軸に対して非対称の場合の波形図である。

【図18】ドライバICの立ち上がり波形と立ち下がり波形が時間軸に対して対称の場合の波形図である。

20

【図19】Csラインの電位のゆれの説明図である。

【図20】17インチSXGA表示方式の場合のrise, fallの時間差とCsラインのゆれのシミュレーション結果を示す図である。

【図21】SXGA表示方式の場合の期間の数値の一例を示す図である。

【図22】UXGA表示方式の液晶表示装置の一例の構成図である。

【図23】UXGA表示方式の場合の期間の数値の一例を示す図である。

【図24】VGA表示方式の液晶表示装置の一例の構成図である。

【図25】QVGA表示方式の液晶表示装置の一例の構成図である。

【図26】VGA, QVGAの各表示方式の場合の期間の数値の一例を示す図である。

【図27】ドライバICの内部構成の他の例を示すブロック図である。

30

【図28】ドライバIC内の出力回路の構成の一例を示すブロック図である。

【図29】メモリ回路周辺の構成の従来例を示すブロック図である。

【図30】メモリ回路周辺の構成の改良例を示すブロック図である。

【図31】TN液晶を使用した場合の液晶のV-Tカーブの特性図である。

【図32】時分割スイッチの周辺の構成の一例を示す等価回路図である。

【図33】図30の等価回路の動作を説明するためのタイミングチャートである。

【図34】時分割スイッチの周辺の構成の他の例を示す等価回路図である。

【図35】図32の等価回路の動作を説明するためのタイミングチャートである。

【図36】画素配列と時分割スイッチの走査方向の関係を示す図であり、(A)は1H反転駆動法の場合を、(B)はドット反転駆動法の場合をそれぞれ示している。

40

【図37】従来例を示す概略構成図である。

【符号の説明】

【0142】

10, 40...液晶表示パネル、11-1~11-3, 41-1~41-3...ゲートライン、12-1~12-6, 42-1~42-6...信号ライン、13, 43...垂直駆動回路、14-1~14-3, 44-1~44-5...ドライバIC、20...画素、21...薄膜トランジスタ、22...付加容量、23...液晶容量、31...水平転送レジスタ、32...サンプリングスイッチ群、33...レベルシフタ、34...データラッシュ群、35...D/Aコンバータ(デジタルアナログ変換回路)、36...出力回路、71, 72...メモリ回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【図11】

(a)

(b)

【図12】

(A) 4時分割の場合

(B) 3時分割の場合

【図13】

【図14】

【図15】

【図18】

【図16】

【図17】

【図19】

【図20】

【図21】

| 水平走査時間        | 21.537μs | 15.63μs | 12.504μs | 10.971μs |

|---------------|----------|---------|----------|----------|

| 時分割スイッチで選択する  | 3μs      | 3μs     | 3μs      | 2μs      |

| 外部ICによるスルーレート | 2μs      | 2μs     | 2μs      | 1.5μs    |

| ランキング期間       | 2μs      | 1μs     | 1μs      | 1μs      |

| 反転表示方法        | ドット反転    | ドット反転   | ドット反転    | ドット反転    |

| ドット周波数        | 78.75MHz | 108MHz  | 135MHz   | 157.5MHz |

【図22】

40

【図23】

| 水平走査時間        | 16μs   | 13.333μs | 12.308μs | 11.429μs | 10.667μs | 10μs   | 9.412μs  |

|---------------|--------|----------|----------|----------|----------|--------|----------|

| 時分割スイッチで選択する  | 3μs    | 3μs      | 3μs      | 2.5μs    | 2μs      | 2μs    | 2μs      |

| 外部ICによるスルーレート | 2μs    | 2μs      | 2μs      | 2μs      | 1.5μs    | 1.5μs  | 1.5μs    |

| ランキング期間       | 1μs    | 1μs      | 1μs      | 1μs      | 1μs      | 1μs    | 1μs      |

| 反転表示方法        | ドット反転  | ドット反転    | ドット反転    | ドット反転    | ドット反転    | ドット反転  | ドット反転    |

| ドット周波数        | 135MHz | 162MHz   | 175.5MHz | 189MHz   | 202.5MHz | 216MHz | 229.5MHz |

【図25】

40

【図24】

【図26】

|                | VGA                              | QVGA(1)                           | QVGA(2)                           |

|----------------|----------------------------------|-----------------------------------|-----------------------------------|

| 画素数            | 水平: 640×3RGB<br>垂直: 480          | 水平: 320×3RGB<br>垂直: 240           | 水平: 320×3RGB<br>垂直: 240           |

| 水平走査時間         | 31.776μs                         | 63.492μs                          | 70.667μs                          |

| 時分割スイッチで選択する時間 | 6.774μs                          | 14.6μs                            | 10.0μs                            |

| 外部ICによるスルーレート  | 3μs                              | 3μs                               | 3μs                               |

| ランキング期間        | 期間(a),(b): 3μs<br>期間(c): 8.056μs | 期間(a),(b): 7μs<br>期間(c): 13.692μs | 期間(a),(b): 7μs<br>期間(c): 26.667μs |

| 反転表示方法         | 1H VCOM反転                        | 1H VCOM反転                         | 1H VCOM反転                         |

【図27】

【図28】

【図29】

【図30】

【図31】

【図3-2】

【図3-3】

【図3-4】

【図3-5】

【図36】

(A) 1H反転駆動法

【図37】

画像表示に寄与しない

余分な接続領域

102 液晶表示パネル

(B) ドット反転駆動法

## フロントページの続き

(51) Int.CI.

| F I     |       |         |

|---------|-------|---------|

| G 0 9 G | 3/20  | 6 2 3 D |

| G 0 9 G | 3/20  | 6 2 3 F |

| G 0 9 G | 3/20  | 6 2 3 L |

| G 0 9 G | 3/20  | 6 2 3 Q |

| G 0 9 G | 3/20  | 6 2 3 V |

| G 0 9 G | 3/20  | 6 3 1 D |

| G 0 9 G | 3/20  | 6 3 1 B |

| G 0 9 G | 3/20  | 6 4 2 K |

| G 0 9 G | 3/20  | 6 8 0 G |

| G 0 9 G | 3/20  | 6 4 1 Q |

| G 0 9 G | 3/20  | 6 2 1 M |

| G 0 2 F | 1/133 | 5 5 0   |

| G 0 2 F | 1/133 | 5 3 5   |

(72) 発明者 仲島 義晴

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 市川 弘明

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 寺口 晋一

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 後藤 尚志

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 岡 豪人

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 芥河 徹

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 坪田 浩嘉

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 一宮 誠

(56) 参考文献 特開平07-013528 (JP, A)

特開平09-033891 (JP, A)

特開平02-042420 (JP, A)

特開昭64-084297 (JP, A)

特許第2509017 (JP, B2)

(58) 調査した分野 (Int.CI., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 0 2 F 1 / 1 3 3

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 公开(公告)号        | <a href="#">JP4835667B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2011-12-14 |

| 申请号            | JP2008236441                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2008-09-16 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 猪野益充<br>前川敏一<br>仲島義晴<br>市川弘明<br>寺口晋一<br>後藤尚志<br>岡豪人<br>芥河徹<br>坪田浩嘉                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 猪野 益充<br>前川 敏一<br>仲島 義晴<br>市川 弘明<br>寺口 晋一<br>後藤 尚志<br>岡 豪人<br>芥河 徹<br>坪田 浩嘉                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| IPC分类号         | G09G3/36 G09G3/20 G02F1/133 G02F1/136 G02F1/13 G02F1/1345 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| CPC分类号         | G09G3/3688 G02F1/1345 G02F1/13452 G09G3/2011 G09G3/3607 G09G3/3614 G09G3/3648 G09G3/3655 G09G3/3666 G09G3/3696 G09G2300/0408 G09G2300/0876 G09G2310/027 G09G2310/0289 G09G2310/0297 G09G2310/06 G09G2310/066 G09G2320/0209 G09G2320/0223 G09G2330/021                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| FI分类号          | G09G3/36 G09G3/20.611.D G09G3/20.611.J G09G3/20.621.B G09G3/20.612.T G09G3/20.623.D G09G3/20.623.F G09G3/20.623.L G09G3/20.623.Q G09G3/20.623.V G09G3/20.631.D G09G3/20.631.B G09G3/20.642.K G09G3/20.680.G G09G3/20.641.Q G09G3/20.621.M G02F1/133.550 G02F1/133.535                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA31 2H093/NA51 2H093/NA61 2H093/NC10 2H093/NC12 2H093/NC16 2H093/NC18 2H093/NC29 2H093/ND54 2H193/ZA04 2H193/ZA07 2H193/ZB06 2H193/ZB08 2H193/ZC04 2H193/ZC12 2H193/ZC23 2H193/ZD11 2H193/ZD21 2H193/ZD23 2H193/ZF13 2H193/ZF16 2H193/ZF22 2H193/ZF32 2H193/ZF36 2H193/ZF42 2H193/ZF44 2H193/ZF59 2H193/ZQ06 5C006/AA16 5C006/AA22 5C006/AC21 5C006/AC27 5C006/AF04 5C006/AF07 5C006/AF43 5C006/AF46 5C006/AF73 5C006/AF83 5C006/BB16 5C006/BC16 5C006/BC23 5C006/BF02 5C006/BF05 5C006/BF11 5C006/BF24 5C006/BF43 5C006/BF46 5C006/FA26 5C006/FA42 5C006/FA43 5C006/FA52 5C006/FA56 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD05 5C080/DD10 5C080/DD23 5C080/DD28 5C080/EE29 5C080/EE30 5C080/FF11 5C080/GG15 5C080/GG17 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 |         |            |

| 代理人(译)         | 森浩一<br>吉井正明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|        |                           |

|--------|---------------------------|

| 审查员(译) | 一宫诚                       |

| 优先权    | 1998076813 1998-03-25 JP  |

| 其他公开文献 | JP2009009156A             |

| 外部链接   | <a href="#">Espacenet</a> |

## 摘要(译)

要解决的问题：使用外部驱动器IC在水平方向上减小液晶显示面板的宽度，此外，相对于图像信号更忠实地再现颜色。SOLUTION：用于通过多列信号线向液晶显示面板10的每个像素施加规定电压的多个驱动器IC 14-1,14-2 ..... 中的每一个的输出引脚的数量，设置为多个列的信号线总数的量度，以防止在信号线中出现分数。另外，借助于时分开关选择信号线以蓝色，绿色，红色的顺序进行，例如在1H反转驱动或1H共反转驱动中。Z