(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-129550

(P2008-129550A)

(43) 公開日 平成20年6月5日(2008.6.5)

(51) Int.Cl.

G09F 9/30 (2006.01)

G02F 1/1368 (2006.01)

F 1

G09F 9/30 338

G02F 1/1368

テーマコード(参考)

2 H 0 9 2

5 C 0 9 4

審査請求 未請求 請求項の数 13 O L (全 30 頁)

(21) 出願番号

(22) 出願日特願2006-317893 (P2006-317893)

平成18年11月27日 (2006.11.27)

(71) 出願人 502356528

株式会社 日立ディスプレイズ

千葉県茂原市早野3300番地

(74) 代理人 100083552

弁理士 秋田 収喜

大原 健

千葉県茂原市早野3300番地 株式会社

日立ディスプレイズ内

(72) 発明者 大井田 淳

千葉県茂原市早野3300番地 株式会社

日立ディスプレイズ内

(72) 発明者 斎藤 裕

千葉県茂原市早野3300番地 株式会社

日立ディスプレイズ内

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【要約】

【課題】 液晶表示パネルの各画素に形成される保持容量のばらつきを低減し、1枚の液晶表示パネルの表示領域における画質の面内ばらつきを低減する。

【解決手段】 複数の画素の集合で設定される表示領域を有し、各画素は、画素電極と、前記画素電極と絶縁層を介して設けられる導体層と、前記絶縁層により形成される保持容量コンデンサを有する基板を備える表示装置であって、前記基板の、ある画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を S 1、該重なる領域に介在する前記絶縁層の厚さを P A S D 1 とし、前記基板の、前記ある画素とは別の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を S 2、該重なる領域に介在する前記絶縁層の厚さを P A S D 2としたときに、S 1 > S 2 であれば、P A S D 1 > P A S D 2 になっている表示装置。

【選択図】

図 11

**【特許請求の範囲】****【請求項 1】**

複数の画素の集合で設定される表示領域を有し、各画素は、画素電極と、前記画素電極と絶縁層を介して設けられる導体層と、前記絶縁層により形成される保持容量コンデンサを有する基板を備える表示装置であって、

前記基板の、ある画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を  $S_1$ 、該重なる領域に介在する前記絶縁層の厚さを  $PASD_1$  とし、

前記基板の、前記ある画素とは別の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を  $S_2$ 、該重なる領域に介在する前記絶縁層の厚さを  $PASD_2$  としたときに、

前記画素電極と前記導体層が平面でみて重なる領域の面積の関係が  $S_1 > S_2$  である場合、

前記絶縁層の厚さの関係が  $PASD_1 > PASD_2$  になっていることを特徴とする表示装置。

**【請求項 2】**

前記ある画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を前記絶縁層の厚さで除した値  $S_1 / PASD_1$  と、前記別の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を前記絶縁層の厚さで除した値  $S_2 / PASD_2$  の関係が、等しくなるように構成していることを特徴とする請求項 1 に記載の表示装置。

**【請求項 3】**

前記基板は、複数本の走査信号線と、前記各画素に設けられ、かつ、前記画素電極および前記複数本の走査信号線のいずれかに接続される TFT 素子とを有し、

前記導体層は、前記画素電極に接続された TFT 素子が接続されている走査信号線とは異なる走査信号線であることを特徴とする請求項 1 または請求項 2 に記載の表示装置。

**【請求項 4】**

前記基板は、複数本の走査信号線と、前記走査信号線と並行する複数本の保持容量線を有し、

前記導体層は、前記保持容量線であることを特徴とする請求項 1 または請求項 2 に記載の表示装置。

**【請求項 5】**

前記基板は、一対の基板の間に液晶材料を封入した液晶表示パネルの、前記一対の基板のうちの一方の基板であることを特徴とする請求項 1 乃至請求項 4 のいずれか 1 項に記載の表示装置。

**【請求項 6】**

複数の画素の集合で設定される表示領域を有し、各画素は、画素電極と、前記画素電極と絶縁層を介して設けられる導体層と、前記絶縁層により形成される保持容量コンデンサを有する基板を備える表示装置であって、

前記表示領域にある複数の画素のうちの任意の 3 つの画素は、

第 1 の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を  $S_1$ 、該重なる領域に介在する前記絶縁層の厚さを  $PASD_1$  とし、

第 2 の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を  $S_2$ 、該重なる領域に介在する前記絶縁層の厚さを  $PASD_2$  とし、

第 3 の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を  $S_3$ 、該重なる領域に介在する前記絶縁層の厚さを  $PASD_3$  としたときに、

前記画素電極と前記導体層が平面でみて重なる領域の面積の関係が  $S_1 > S_2 > S_3$  である場合、

前記絶縁層の厚さの関係が  $PASD_1 > PASD_2 > PASD_3$  になっていることを特徴とする表示装置。

**【請求項 7】**

前記第 1 の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を前

10

20

30

40

50

記絶縁層の厚さで除した値  $S_1 / P A S D_1$  と、前記第 2 の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を前記絶縁層の厚さで除した値  $S_2 / P A S D_2$  と、前記第 3 の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を前記絶縁層の厚さで除した値  $S_3 / P A S D_3$  の関係が、等しくなるように構成していることを特徴とする請求項 6 に記載の表示装置。

#### 【請求項 8】

前記表示領域は矩形であり、

前記第 1 の画素は、前記矩形の表示領域の第 1 の辺の中心の近傍にあり、

前記第 2 の画素は、前記矩形の表示領域の前記第 1 の辺と第 2 の辺が接続する角部の近傍にあり、

10

前記第 3 の画素は、前記矩形の表示領域の前記第 2 の辺と、前記第 1 の辺に対向する第 3 の辺が接続する角部の近傍にあることを特徴とする請求項 6 または請求項 7 に記載の表示装置。

#### 【請求項 9】

前記表示領域は矩形であり、

前記第 1 の画素は、前記矩形の表示領域の第 1 の辺と第 2 の辺が接続する角部の近傍にあり、

前記第 2 の画素は、前記矩形の表示領域の前記第 1 の辺と、前記第 2 の辺に対向する第 3 の辺が接続する角部の近傍にあり、

前記第 3 の画素は、前記矩形の表示領域の前記第 3 の辺と、前記第 1 の辺に対向する第 4 の辺が接続する角部の近傍にあることを特徴とする請求項 6 または請求項 7 に記載の表示装置。

20

#### 【請求項 10】

前記表示領域は矩形であり、

前記第 1 の画素は、前記矩形の表示領域の中心またはその近傍にあり、

前記第 2 の画素は、前記矩形の表示領域の第 1 の辺の中心の近傍にあり、

前記第 3 の画素は、前記矩形の表示領域の前記第 1 の辺と第 2 の辺が接続する角部の近傍にあることを特徴とする請求項 6 または請求項 7 に記載の表示装置。

25

#### 【請求項 11】

前記基板は、前記矩形の表示領域の前記第 1 の辺に沿った方向に延在する複数本の走査信号線と、

30

前記矩形の表示領域の前記第 2 の辺に沿った方向に延在し、かつ、絶縁層を介して前記複数本の走査信号線と立体的に交差する複数本の映像信号線を有することを特徴とする請求項 8 乃至請求項 10 のいずれか 1 項に記載の表示装置。

#### 【請求項 12】

前記基板は、前記矩形の表示領域の前記第 2 の辺に沿った方向に延在する複数本の走査信号線と、

前記矩形の表示領域の前記第 1 の辺に沿った方向に延在し、かつ、絶縁層を介して前記複数本の走査信号線と立体的に交差する複数本の映像信号線を有することを特徴とする請求項 8 乃至請求項 10 のいずれか 1 項に記載の表示装置。

40

#### 【請求項 13】

前記基板は、一対の基板の間に液晶材料を封入した液晶表示パネルの、前記一対の基板のうちの一方の基板であることを特徴とする請求項 6 乃至請求項 12 のいずれか 1 項に記載の表示装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、表示装置に関し、特に、TFT 液晶表示パネルを備える液晶表示装置に適用して有効な技術に関するものである。

#### 【背景技術】

## 【0002】

従来、画像や映像を表示する表示装置には、TFT液晶表示装置がある。前記TFT液晶表示装置は、たとえば、テレビやパソコン・コンピュータ(PC)のディスプレイなどの大型の表示装置から、携帯電話端末などの小型の電子機器の表示装置(表示モジュール)まで、幅広く採用されている。

## 【0003】

前記TFT液晶表示装置は、一対の基板の間に液晶材料を封入した液晶表示パネルを有する表示装置である。前記液晶表示パネルの表示領域は、複数の画素の集合で設定されており、各画素には、TFT素子および画素電極が配置されている。このとき、各画素に配置されるTFT素子および画素電極は、前記一対の基板のうちの一方の基板に配置されており、TFT基板および画素電極が配置された基板は、一般に、TFT基板と呼ばれる。また、前記TFT基板において、画素電極は、TFT基板のソース電極と電気的に接続されている。

10

## 【0004】

また、前記TFT基板は、TFT素子および画素電極の他に、複数本の走査信号線や、前記複数本の走査信号線と絶縁層を介して立体的に交差する複数本の映像信号線を有する。このとき、TFT素子のゲート電極は複数本の走査信号線のいずれか1本に接続されており、TFT素子のドレイン電極は複数本の映像信号線のいずれか1本に接続されている。

20

## 【0005】

また、前記TFT液晶表示パネルがアクティブマトリクス型の場合、各画素は、あるフレームの映像信号(階調電圧)が画素電極に加わった後、次のフレームの映像信号が来るまで、その画素電極に加わった電圧(電荷)を保持しておく必要がある。そのため、各画素には、たとえば、画素電極と、その画素電極に接続されたTFT素子のゲート電極が接続されている走査信号線とは異なる走査信号線、または走査信号線と並行する保持容量線と、それらの間に介在する絶縁層とにより保持容量コンデンサを形成している。

30

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0006】

ところで、前記液晶表示装置のうち、たとえば、テレビなどに用いられる液晶表示装置は、近年、大画面化が進んでおり、前記液晶表示パネルのTFT基板が大型化している。TFT基板の製造過程において、ガラス基板上に導体膜を成膜するときには、たとえば、スパッタリング法を用いており、絶縁膜を成膜するときには、たとえば、CVD法を用いている。そのため、TFT基板(ガラス基板)が大型化し、導体膜や絶縁膜を成膜する領域の面積が大きくなると、その膜厚にばらつきが生じやすくなる。なお、ここでいう膜厚のばらつきは、たとえば、ガラス基板において、1枚のTFT基板として切り出す領域内の各箇所における膜厚のばらつきである。

## 【0007】

また、前記液晶表示パネルのTFT基板を製造するときには、たとえば、ガラス基板上に走査信号線、映像信号線、TFT素子などを形成した後、画素電極を形成するのが一般的である。このとき、画素電極は、たとえば、TFT素子のソース電極がある位置にスルーホールが形成された絶縁層の表面全体にITOなどの透明導体膜を成膜した後、たとえば、透明導体膜の上にエッチングレジストを形成し、透明導体膜をエッチングして形成する。前記エッチングレジストは、たとえば、透明導体膜の上に印刷または塗布したレジストを露光、現像して形成する。

40

## 【0008】

従来のTFT基板の製造方法において、たとえば、画素電極を形成するための透明導体膜の上に印刷または塗布したレジストを露光するときには、透明な基板の表面にクロム(Cr)膜などでパターンを描いたマスクを用いて行うのが一般的である。

## 【0009】

50

前記マスクのパターンは、あらかじめ設計されたレイアウト寸法に基づいて形成されている。前記レイアウト寸法は、たとえば、基板上に形成する走査信号線や映像信号線の幅、各画素に形成するTFT素子や画素電極の寸法などであり、通常は、各走査信号線の幅、各映像信号線の幅、各TFT素子の寸法、各画素電極の寸法が、それぞれ同じ寸法になるように設計されている。そのため、たとえば、前記画素電極を形成する工程において、透明導体膜上に印刷したレジストを露光するときに用いるマスクには、各画素の画素電極が同じ寸法になるようなパターンが描かれている。

#### 【0010】

すなわち、従来のようなマスクを用いた露光でエッチングレジストを形成し、前記画素電極を形成すると、前記ガラス基板の上に形成した絶縁層の膜厚にはらつきが生じているときでも、各画素における画素電極と走査信号線または保持容量線の平面でみて重なる領域の面積はほぼ一定になる。そのため、画素電極と走査信号線または保持容量線の間に介在する絶縁層の膜厚のはらつきにより1枚のTFT基板の表示領域にある各画素の保持容量にはらつきが生じ、1枚の液晶表示パネルの表示領域の画質に面内ばらつきが生じるという問題があった。

10

#### 【0011】

従来のTFT基板の製造方法では、このような保持容量のはらつきによる画質の面内ばらつきを低減する方法として、たとえば、保持容量が一定値以上になるように、走査信号線または保持容量線と画素電極が平面でみて重なる領域の面積を大きくしている。しかしながら、保持容量を大きくすると、たとえば、走査信号線駆動回路の出力を大きくする必要があり、液晶表示装置の消費電力の増加、液晶表示パネルの生産コストの上昇といった別の問題が生じる。

20

#### 【0012】

本発明の目的は、たとえば、液晶表示パネルの各画素に形成される保持容量のはらつきを低減し、1枚の液晶表示パネルの表示領域における画質の面内ばらつきを低減することが可能な技術を提供することにある。

30

#### 【0013】

本発明の他の目的は、たとえば、液晶表示パネルの各画素に形成される保持容量のはらつきを低減し、液晶表示装置の消費電力の増加を抑えることが可能な技術を提供することにある。

#### 【0014】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面によって明らかになるであろう。

#### 【課題を解決するための手段】

#### 【0015】

本願において開示される発明のうち、代表的なものの概略を説明すれば、以下の通りである。

#### 【0016】

(1) 複数の画素の集合で設定される表示領域を有し、各画素は、画素電極と、前記画素電極と絶縁層を介して設けられる導体層と、前記絶縁層とにより形成される保持容量コンデンサを有する基板を備える表示装置であって、前記基板の、ある画素において前記画素電極と前記導体層が平面でみて重なる領域の面積をS1、該重なる領域に介在する前記絶縁層の厚さをPASD1とし、前記基板の、前記ある画素とは別の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積をS2、該重なる領域に介在する前記絶縁層の厚さをPASD2としたときに、前記画素電極と前記導体層が平面でみて重なる領域の面積の関係がS1 > S2である場合、前記絶縁層の厚さの関係がPASD1 > PASD2になっている表示装置。

40

#### 【0017】

(2) 前記(1)の表示装置において、前記ある画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を前記絶縁層の厚さで除した値S1 / PASD1と、前

50

記別の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を前記絶縁層の厚さで除した値  $S_2 / P A S D_2$  の関係が、等しくなるように構成している表示装置。

#### 【0018】

(3) 前記(1)または(2)の表示装置において、前記基板は、複数本の走査信号線と、前記各画素に設けられ、かつ、前記画素電極および前記複数本の走査信号線のいずれかに接続されるTFT素子とを有し、前記導体層は、前記画素電極に接続されたTFT素子が接続されている走査信号線とは異なる走査信号線である表示装置。

#### 【0019】

(4) 前記(1)または(2)の表示装置において、前記基板は、複数本の走査信号線と、前記走査信号線と並行する複数本の保持容量線を有し、前記導体層は、前記保持容量線である表示装置。

#### 【0020】

(5) 前記(1)乃至(4)のいずれかの表示装置において、前記基板は、一対の基板の間に液晶材料を封入した液晶表示パネルの、前記一対の基板のうちの一方の基板である表示装置。

#### 【0021】

(6) 複数の画素の集合で設定される表示領域を有し、各画素は、画素電極と、前記画素電極と絶縁層を介して設けられる導体層と、前記絶縁層とにより形成される保持容量コンデンサを有する基板を備える表示装置であって、前記表示領域にある複数の画素のうちの任意の3つの画素は、第1の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を  $S_1$ 、該重なる領域に介在する前記絶縁層の厚さを  $P A S D_1$  とし、第2の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を  $S_2$ 、該重なる領域に介在する前記絶縁層の厚さを  $P A S D_2$  とし、第3の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を  $S_3$ 、該重なる領域に介在する前記絶縁層の厚さを  $P A S D_3$  としたときに、前記画素電極と前記導体層が平面でみて重なる領域の面積の関係が  $S_1 > S_2 > S_3$  である場合、前記絶縁層の厚さの関係が  $P A S D_1 > P A S D_2 > P A S D_3$  になっている表示装置。

#### 【0022】

(7) 前記(6)の表示装置において、前記第1の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を前記絶縁層の厚さで除した値  $S_1 / P A S D_1$  と、前記第2の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を前記絶縁層の厚さで除した値  $S_2 / P A S D_2$  と、前記第3の画素において前記画素電極と前記導体層が平面でみて重なる領域の面積を前記絶縁層の厚さで除した値  $S_3 / P A S D_3$  の関係が、等しくなるように構成している表示装置。

#### 【0023】

(8) 前記(6)または(7)の表示装置において、前記表示領域は矩形であり、前記第1の画素は、前記矩形の表示領域の第1の辺の中心の近傍にあり、前記第2の画素は、前記矩形の表示領域の前記第1の辺と第2の辺が接続する角部の近傍にあり、前記第3の画素は、前記矩形の表示領域の前記第2の辺と、前記第1の辺に対向する第3の辺が接続する角部の近傍にある表示装置。

#### 【0024】

(9) 前記(6)または(7)の表示装置において、前記表示領域は矩形であり、前記第1の画素は、前記矩形の表示領域の第1の辺と第2の辺が接続する角部の近傍にあり、前記第2の画素は、前記矩形の表示領域の前記第1の辺と、前記第2の辺に対向する第3の辺が接続する角部の近傍にあり、前記第3の画素は、前記矩形の表示領域の前記第3の辺と、前記第1の辺に対向する第4の辺が接続する角部の近傍にある表示装置。

#### 【0025】

(10) 前記(6)または(7)の表示装置において、前記表示領域は矩形であり、前記第1の画素は、前記矩形の表示領域の中心またはその近傍にあり、前記第2の画素は、

10

20

30

40

50

前記矩形の表示領域の第1の辺の中心の近傍にあり、前記第3の画素は、前記矩形の表示領域の前記第1の辺と第2の辺が接続する角部の近傍にある表示装置。

**【0026】**

(11) 前記(8)乃至(10)のいずれかの表示装置において、前記基板は、前記矩形の表示領域の前記第1の辺に沿った方向に延在する複数本の走査信号線と、前記矩形の表示領域の前記第2の辺に沿った方向に延在し、かつ、絶縁層を介して前記複数本の走査信号線と立体的に交差する複数本の映像信号線を有する表示装置。

**【0027】**

(12) 前記(8)乃至(10)のいずれかの表示装置において、前記基板は、前記矩形の表示領域の前記第2の辺に沿った方向に延在する複数本の走査信号線と、前記矩形の表示領域の前記第1の辺に沿った方向に延在し、かつ、絶縁層を介して前記複数本の走査信号線と立体的に交差する複数本の映像信号線を有する表示装置。

10

**【0028】**

(13) 前記(6)乃至(12)のいずれかの表示装置において、前記基板は、一対の基板の間に液晶材料を封入した液晶表示パネルの、前記一対の基板のうちの一方の基板である表示装置。

**【発明の効果】**

**【0029】**

本発明の表示装置は、複数の画素の集合で設定される表示領域の各画素が、画素電極と、前記画素電極と絶縁層を介して設けられる導体層と、前記絶縁層により形成される保持容量コンデンサを有する基板を備える。そして、前記基板の表示領域にある2つの画素に着目したときに、前記画素電極と前記導体層が平面でみて重なる領域（以下、重畳領域という）の面積が異なる場合、重畳領域の面積が大きい方が、介在する絶縁層が厚いことを特徴とする。このようにすることで、1枚の基板の表示領域にある各画素の保持容量のばらつきを低減することができる。そのため、1枚の基板（表示パネル）の表示領域における保持容量のばらつきによる画質の面内ばらつきを低減することができる。

20

**【0030】**

また、本発明の表示装置では、たとえば、従来のように各画素の保持容量が一定値以上になるように、画素電極と導体層の重畳領域の面積を大きくする必要はない。そのため、走査信号線駆動回路の出力を大きくする必要がなくなり、液晶表示装置の消費電力の増加を抑えることができる。

30

**【0031】**

またこのとき、一方の画素における画素電極と導体層の重畳領域の面積を絶縁層の厚さで除した値と、他方の画素における画素電極と導体層の重畳領域の面積を絶縁層の厚さで除した値の関係が、等しくなるように構成することが望ましい。

**【0032】**

また、本発明の表示装置において、前記基板は、たとえば、複数本の走査信号線と、前記各画素に設けられ、かつ、前記画素電極および前記複数本の走査信号線のいずれかに接続されるTFT素子とを有する。このとき、保持容量コンデンサの一方の電極になる導体層は、前記画素電極に接続されたTFT素子が接続されている走査信号線とは異なる走査信号線を利用する。

40

**【0033】**

また、前記基板は、複数本の走査信号線と、前記走査信号線と並行する複数本の保持容量線を有する基板でもよい。このとき、保持容量コンデンサの一方の電極になる導体層は、前記保持容量線を利用する。

**【0034】**

また、本発明は、上記の構成を満たしていれば、どのような表示形式の表示パネルの基板にも適用できるが、特に、液晶表示パネルを構成する一対の基板のうちの一方の基板に適用することが望ましい。

**【0035】**

50

また、本発明の表示装置は、上記のような2つの画素に着目した場合だけでなく、1枚の基板の表示領域にある3つの画素に着目した場合にも、前記画素電極と前記導体層の重畠領域の面積が異なる場合に、重畠領域の面積が広い保持容量コンデンサほど、重畠領域に介在する絶縁層が厚くなっている。すなわち、第1の画素における画素電極と導体層の重畠領域の面積をS1、該重畠領域に介在する絶縁層の厚さをPASD1とし、第2の画素における画素電極と導体層の重畠領域の面積をS2、該重畠領域に介在する絶縁層の厚さをPASD2とし、第3の画素における画素電極と導体層の重畠領域の面積をS3、該重畠領域に介在する絶縁層の厚さをPASD3としたときに、重畠領域の面積の関係がS1>S2>S3である場合、前記絶縁層の厚さの関係がPASD1>PASD2>PASD3になっている。

10

## 【0036】

ところで、本発明の表示装置に用いられる基板は、たとえば、マザーガラスと呼ばれる大型のガラス基板に複数枚分の基板を一括して形成した後、各基板として用いる領域を切り出す、いわゆる多面取りと呼ばれる製造方法で製造されることが多い。この場合、導体層の形成に用いる導体膜や絶縁層の形成に用いる絶縁膜は、一般に、マザーガラスの全面に成膜する。そのため、たとえば、1枚の基板における絶縁層の膜厚のばらつき（膜厚分布）は、マザーガラスの中心との位置関係によって異なる。このとき、本発明の表示装置に用いられる基板は、第1の画素、第2の画素、第3の画素の位置関係が、たとえば、以下に示す位置関係のいずれかの場合に、上記の関係を満たす。

20

## 【0037】

1つめの位置関係は、表示領域が矩形であり、第1の画素が前記矩形の表示領域の第1の辺の中心の近傍にあり、第2の画素が前記矩形の表示領域の前記第1の辺と第2の辺が接続する角部の近傍にあり、第3の画素が前記矩形の表示領域の前記第2の辺と、前記第1の辺に対向する第3の辺が接続する角部の近傍にあるという位置関係である。

30

## 【0038】

2つめの位置関係は、表示領域が矩形であり、第1の画素が前記矩形の表示領域の第1の辺と第2の辺が接続する角部の近傍にあり、第2の画素が前記矩形の表示領域の前記第1の辺と、前記第2の辺に対向する第3の辺が接続する角部の近傍にあり、第3の画素が前記矩形の表示領域の前記第3の辺と、前記第1の辺に対向する第4の辺が接続する角部の近傍にあるという位置関係である。

## 【0039】

3つめの位置関係は、表示領域が矩形であり、第1の画素が前記矩形の表示領域の中心またはその近傍にあり、第2の画素が前記矩形の表示領域の第1の辺の中心の近傍にあり、第3の画素が前記矩形の表示領域の前記第1の辺と第2の辺が接続する角部の近傍にあるという位置関係である。

## 【0040】

また、前記基板が、たとえば、液晶表示パネルに用いられる一対の基板のうちの一方の基板の場合、その基板には、たとえば、複数本の走査信号線と、絶縁層を介して前記複数本の走査信号線と立体的に交差する映像信号線が設けられている。このとき、矩形の表示領域の辺と走査信号線および映像信号線の関係は、たとえば、第1の辺に沿った方向に走査信号線が延在し、第2の辺に沿った方向に映像信号線が延在するような関係にある。またこのとき、矩形の表示領域の辺と走査信号線および映像信号線の関係は、第2の辺に沿った方向に走査信号線が延在し、第1の辺に沿った方向に映像信号線が延在するような関係でもよい。

40

## 【0041】

なお、本発明の表示装置は、たとえば、表示領域にある2つの画素における画素電極と導体層の重畠領域の面積を比較し、各画素における重畠領域の面積が異なる場合は、重畠領域の面積が小さい方の絶縁層が薄く、大きい方の絶縁層が厚いという関係を満たすことが主要な特徴である。すなわち、本発明の表示装置では、表示領域にある2つの画素における画素電極と導体層の重畠領域に介在する絶縁層の厚さを比較し、各画素における絶縁

50

層の厚さが異なる場合は、必ずしも、絶縁層が薄い方が重畠領域の面積が小さく、絶縁層が厚い方が重畠領域の面積が大きいというわけではない。

**【発明を実施するための最良の形態】**

**【0042】**

以下、本発明について、図面を参照して実施の形態（実施例）とともに詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは、同一符号を付け、その繰り返しの説明は省略する。

**【実施例1】**

**【0043】**

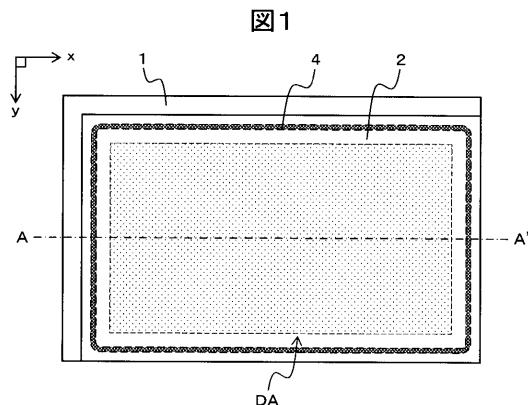

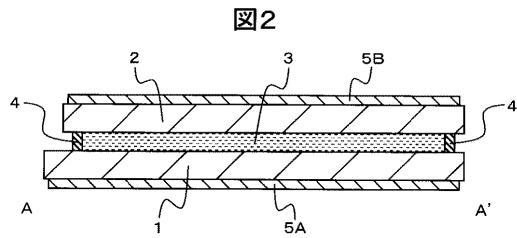

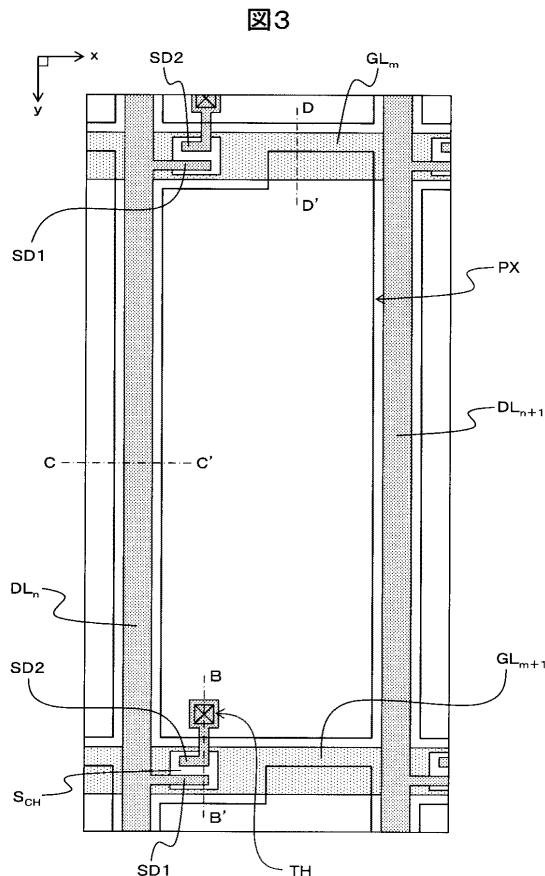

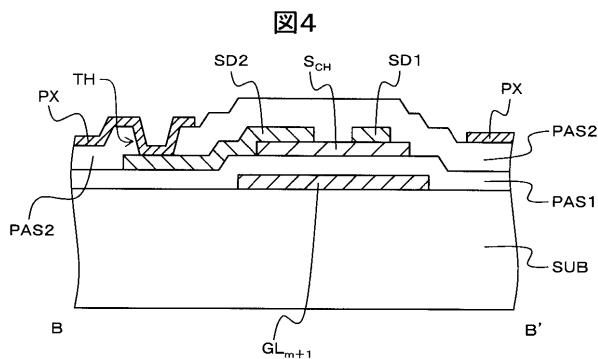

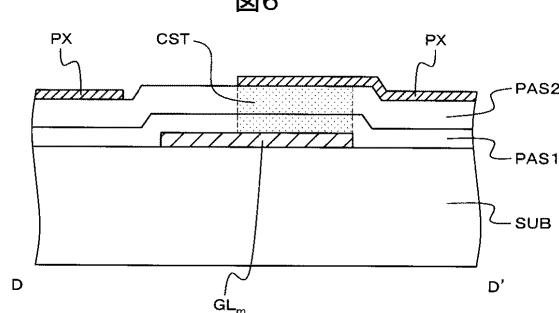

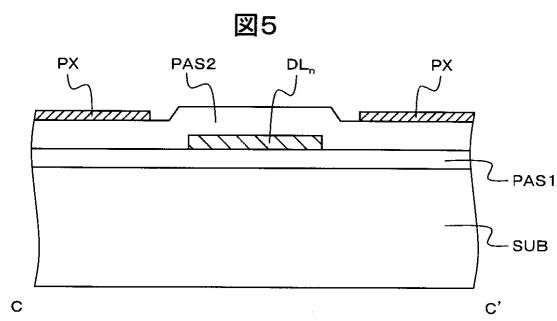

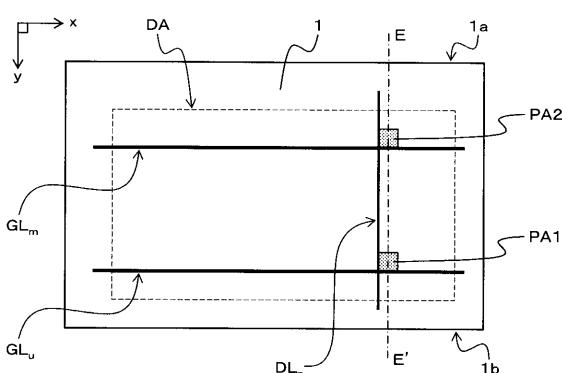

図1乃至図6は、本発明による実施例1の液晶表示パネルの概略構成を示す模式図である。

図1は、実施例1の液晶表示パネルの模式平面図である。図2は、図1に示したA-A'線における模式断面図である。図3は、図1に示した表示領域におけるTFT基板の1画素の構成例を示す模式平面図である。図4は、図3に示したB-B'線における模式断面図である。図5は、図3に示したC-C'線における模式断面図である。図6は、図3に示したD-D'線における模式断面図である。

**【0044】**

実施例1の液晶表示パネルは、図1および図2に示すように、一対の基板1,2の間に液晶材料3が封入されている。このとき、一対の基板1,2は、表示領域DAを囲むように環状に設けられたシール材4で接着されており、液晶材料3は、一対の基板1,2およびシール材4で囲まれた空間に封入されている。また、一対の基板1,2の外側には、たとえば、一対の基板1,2を挟むようにして一対の偏光板5A,5Bが設けられている。この一対の偏光板5A,5Bはそれぞれ、各基板1,2に貼り合わされている。また、図示は省略するが、たとえば、基板1と偏光板5Aの間、基板2と偏光板5Bの間には、1層から数層の位相差板が設けられていることもある。

**【0045】**

また、一対の基板1,2のうちの、平面でみた外形寸法が大きい方の基板1は、一般に、TFT基板と呼ばれ、たとえば、ガラス基板の表面に、複数本の走査信号線、複数本の走査信号線と絶縁層を介して立体的に交差する複数本の映像信号線、TFT素子、画素電極などが設けられている。また、実施例1の液晶表示パネルでは、画素電極と対向する共通電極（対向電極とも呼ばれる）は、平面でみた外形寸法が小さい方の基板2に設けられている。

**【0046】**

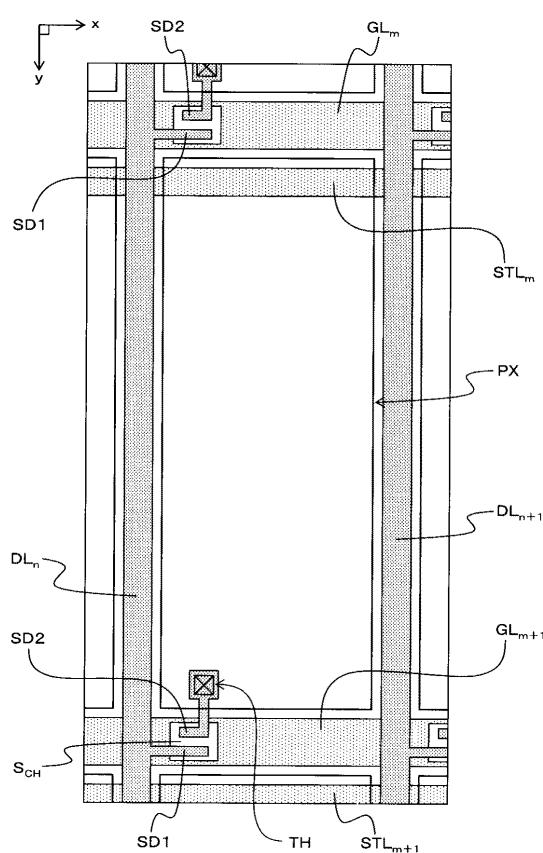

実施例1の液晶表示パネルにおいて、TFT基板1の表示領域DAの1画素の構成は、たとえば、図3乃至図6に示すようになっている。TFT基板1における1つの画素領域は、2本の隣接する走査信号線 $GL_m$ , $GL_{m+1}$ と、2本の隣接する映像信号線 $DL_n$ , $DL_{n+1}$ で囲まれた領域である。なお、カラー液晶表示パネルの場合、この1つの画素はサブ画素と呼ばれ、RGB方式のカラー液晶表示パネルの場合、走査信号線 $GL_m$ の延在方向に沿って並んだ3つのサブ画素で、映像の1画素（1ドット）を構成している。

**【0047】**

また、実施例1の液晶表示パネルでは、ガラス基板SUBの表面に走査信号線 $GL_m$ , $GL_{m+1}$ などの複数本の走査信号線が設けられており、その上に、第1の絶縁層PAS1を介して映像信号線 $DL_n$ , $DL_{n+1}$ などの複数本の映像信号線が設けられている。このとき、たとえば、各走査信号線の上には、各画素領域に対して配置されるTFT素子の半導体層（チャネル層） $S_{CH}$ が設けられている。また、TFT素子の半導体層 $S_{CH}$ の上には、たとえば、ドレイン電極SD1およびソース電極SD2が設けられており、ドレイン電極SD1は、映像信号線 $DL_n$ に接続されている。

**【0048】**

また、映像信号線 $DL_n$ やTFT素子の上には、第2の絶縁層PAS2を介して画素電

極 P X が設けられている。画素電極 P X は、画素毎に設けられており、スルーホール TH によって TFT 素子のソース電極 S D 2 に接続されている。

#### 【0049】

また、各画素電極 P X は、2 本の隣接する走査信号線 G L<sub>m</sub>, G L<sub>m+1</sub> のうちの、自身に接続されている TFT 素子のゲート電極が接続されている走査信号線 G L<sub>m+1</sub> ではないほうの走査信号線 G L<sub>m</sub> と平面でみて重なる領域と、重ならない領域がある。このうち、走査信号線 G L<sub>m</sub> と平面でみて重なる領域は、走査信号線 G L<sub>m</sub> と画素電極 P X を電極とし、介在する第 1 の絶縁層 P A S 1 および第 2 の絶縁層 P A S 2 を誘電体とする保持容量コンデンサが形成されている。この保持容量コンデンサの保持容量 C S T は、画素電極 P X と走査信号線 G L<sub>m</sub> の平面でみて重なる領域（重畳領域）の面積 S を、第 1 の絶縁層 P A S 1 および第 2 の絶縁層 P A S 2 の総厚 P A S D で除した値 S / P A S D に比例する。

10

#### 【0050】

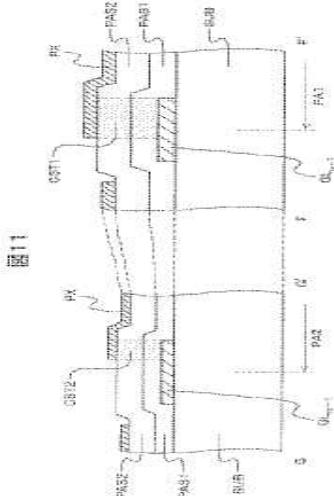

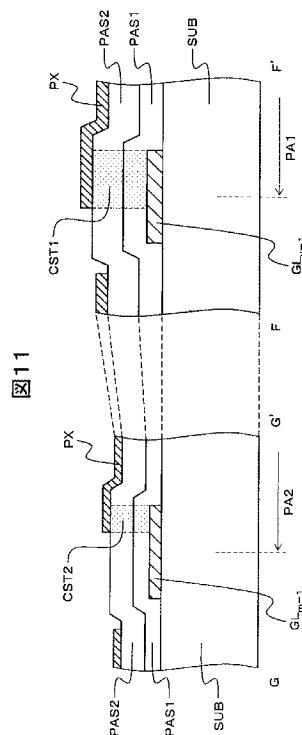

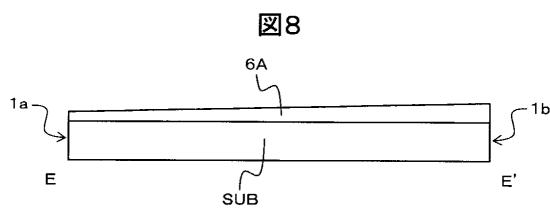

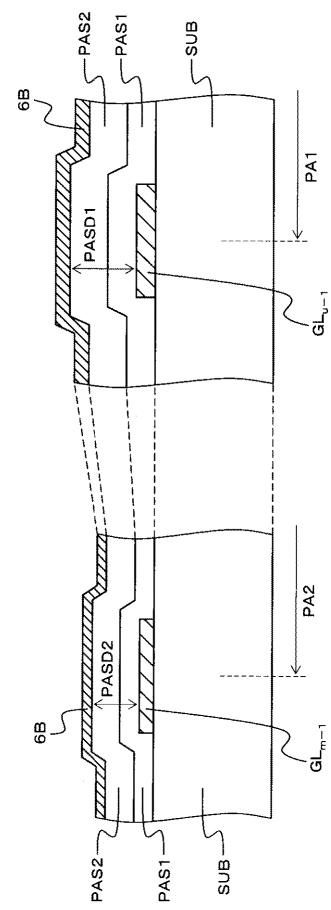

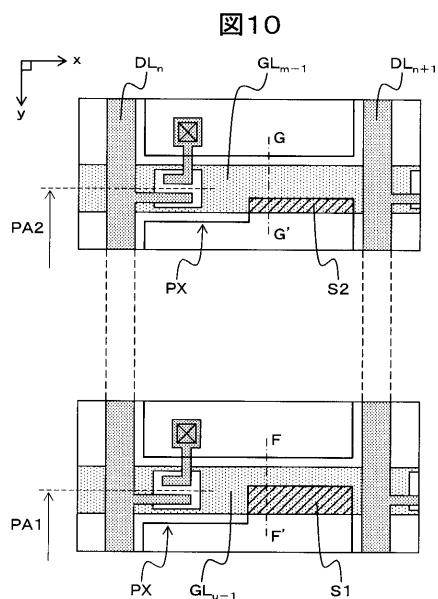

図 7 乃至図 11 は、実施例 1 の液晶表示パネルにおいて特徴となる構成および作用効果を説明するための模式図である。

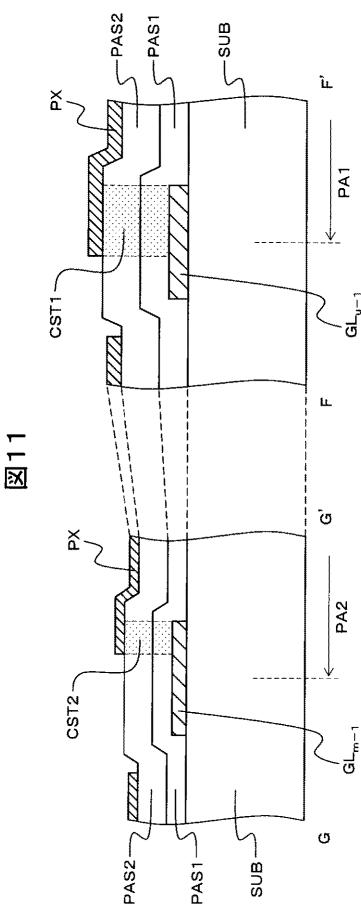

図 7 は、実施例 1 の液晶表示パネルにおける 2 つの画素の選択例を示す模式平面図である。図 8 は、ガラス基板に成膜した薄膜の、図 7 に示した E - E' 線における膜厚分布の一例を示す模式断面図である。図 9 は、画素電極を形成する工程の、図 7 に示した 2 つの画素における絶縁層の膜厚の関係の一例を示す模式断面図である。図 10 は、図 7 に示した 2 つの画素における画素電極と走査信号線の重畳領域の面積の関係の一例を示す模式平面図である。図 11 は、図 10 に示した F - F' 線および G - G' 線における模式断面図を横に並べて示した図である。

20

#### 【0051】

実施例 1 の液晶表示パネル（TFT 基板 1）において特徴となる構成を説明するにあたり、図 7 に示すように、ある走査信号線 G L<sub>u</sub> と映像信号線 D L<sub>n</sub> の交点の近傍にある画素 P A 1 と、別の走査信号線 G L<sub>m</sub> と映像信号線 D L<sub>n</sub> の交点の近傍にある画素 P A 2 との 2 つの画素に着目する。このとき、第 1 の画素 P A 1 は、2 本の走査信号線 G L<sub>u-1</sub>, G L<sub>u</sub> と、2 本の映像信号線 D L<sub>n</sub>, D L<sub>n+1</sub> で囲まれた領域に画素電極 P X があり、画素電極 P X と走査信号線 G L<sub>u-1</sub> が立体的に交差して保持容量 C S T 1 を形成しているとする。また、第 2 の画素 P A 2 は、2 本の走査信号線 G L<sub>m-1</sub>, G L<sub>m</sub> と、2 本の映像信号線 D L<sub>n</sub>, D L<sub>n+1</sub> で囲まれた領域に画素電極 P X があり、画素電極 P X と走査信号線 G L<sub>m-1</sub> が立体的に交差して保持容量 C S T 2 を形成しているとする。

30

#### 【0052】

このような TFT 基板 1 を製造するときには、たとえば、導体膜を成膜してエッチングする工程、絶縁膜を成膜する工程などを繰り返して、走査信号線などを形成していく。このとき、導体膜は、たとえば、スパッタリング法で成膜し、絶縁膜は、たとえば、C V D 法で成膜する。そのため、ガラス基板 S U B 上に導体膜や絶縁膜などの薄膜を成膜すると、たとえば、図 8 に示すように、ガラス基板 S U B の一方の端部 1 a から他方の端部 1 b にかけて、徐々に膜厚が厚くなるような薄膜 6 A が成膜される。

40

#### 【0053】

つまり、画素電極 P X を形成する工程において、第 2 の絶縁層 P A S 2 の表面に I T O 膜などの透明導体膜 6 B を形成すると、たとえば、図 9 に示すように、第 1 の画素 P A 1 の画素電極 P X が保持容量 C S T 1 を形成する走査信号線 G L<sub>u-1</sub> 上の第 1 の絶縁層 P A S 1 および第 2 の絶縁層 P A S 2 の総厚 P A S D 1 と、第 2 の画素 P A 2 の画素電極 P X が保持容量 C S T 2 を形成する走査信号線 G L<sub>m-1</sub> 上の第 1 の絶縁層 P A S 1 および第 2 の絶縁層 P A S 2 の総厚 P A S D 2 が異なり、第 1 の画素 P A 1 の絶縁層の総厚 P A S D 1 のほうが厚くなっている。

#### 【0054】

そのため、たとえば、従来のようなマスクを用いた露光、現像で第 1 の画素 P A 1 の画素電極 P X と第 2 の画素 P A 2 の画素電極 P X が同じ寸法になるようなエッチングレジス

50

トを形成し、各画素の画素電極 P X を形成すると、絶縁層の厚さのはらつきに応じて保持容量にばらつきが生じる。

#### 【 0 0 5 5 】

一方、実施例 1 の TFT 基板 1 では、第 1 の画素 PA 1 の画素電極 P X と対になって保持容量 CST 1 を形成する走査信号線 GL<sub>u-1</sub> の上の絶縁層の総厚 PASD 1 と、第 2 の画素 PA 2 の画素電極 P X と対になって保持容量 CST 2 を形成する走査信号線 GL<sub>m-1</sub> の上の絶縁層の総厚 PASD 2 が異なり、第 1 の画素 PA 1 の絶縁層の総厚 PASD 1 のほうが厚くなっている場合、図 10 および図 11 に示すように、第 1 の画素 PA 1 の画素電極 P X と走査信号線 GL<sub>u-1</sub> の重畠領域の面積 S 1 を、第 2 の画素 PA 2 の画素電極 P X と走査信号線 GL<sub>m-1</sub> の重畠領域の面積 S 2 よりも大きくする。またこのとき、各画素領域の画素電極と走査信号線の重畠領域の面積 S<sub>1,2</sub> は、第 1 の画素 PA 1 の保持容量 CST 1 と第 2 の画素 PA 2 の保持容量 CST 2 が等しくなるようにすることが望ましい。

10

#### 【 0 0 5 6 】

なお、上記の説明では、第 1 の画素 PA 1 の絶縁層の総厚 PASD 1 の方が厚い場合を例に挙げたが、これに限らず、逆の関係であってもよいことはもちろんである。つまり、第 1 の画素 PA 1 の絶縁層の総厚 PASD 1 が第 2 の画素 PA 2 の絶縁層の総厚 PASD 2 よりも薄い (PASD 1 < PASD 2) 場合、各画素の画素電極と走査信号線の重畠領域の面積 S<sub>1,2</sub> を S<sub>1 < S\_2</sub> にすればよい。

20

#### 【 0 0 5 7 】

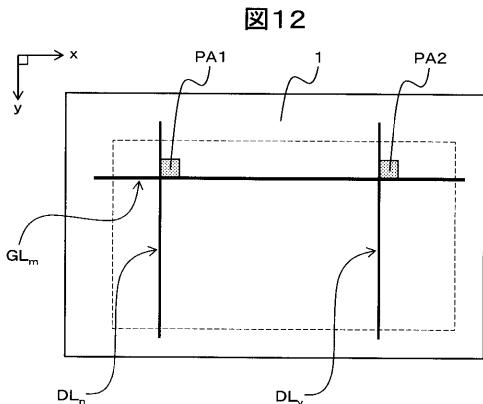

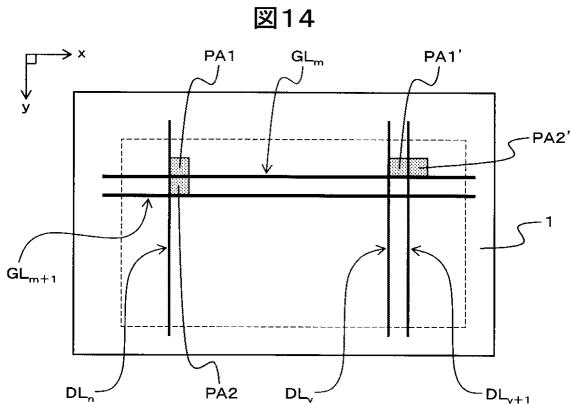

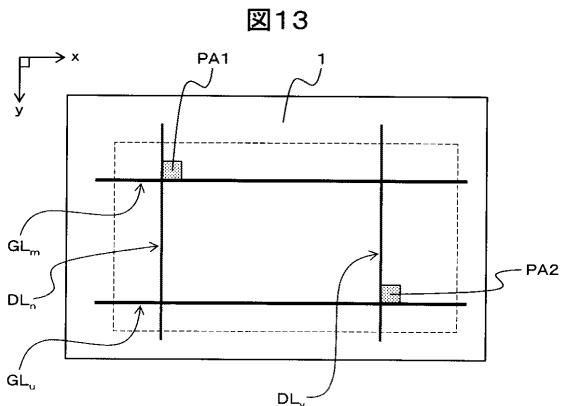

図 12 乃至図 14 は、実施例 1 の液晶表示パネルにおける 2 つの画素の別の選択例を示す模式平面図である。

#### 【 0 0 5 8 】

実施例 1 の液晶表示パネル (TFT 基板 1) の特徴について、上記の説明では、図 7 に示したように、ある映像信号線 DL<sub>n</sub> の延在方向 (y 方向) に沿って並んでいる画素の中から 2 つの画素 PA 1, PA 2 を選択した例を挙げている。しかしながら、実施例 1 の液晶表示パネルにおける画素電極と走査信号線の重畠領域の面積と介在する絶縁層の厚さの関係は、特定の 2 つの画素の間だけでなく、TFT 基板 1 の表示領域 DA にあるすべての画素の中から 2 つの画素に着目したときに成立することが望ましい。

30

#### 【 0 0 5 9 】

つまり、たとえば、図 12 に示すように、走査信号線 GL<sub>m</sub> とある映像信号線 DL<sub>n</sub> が交差する箇所の近傍にある第 1 の画素 PA 1 と、走査信号線 GL<sub>m</sub> と別の映像信号線 DL<sub>v</sub> が交差する箇所の近傍にある第 2 の画素 PA 2 に着目した場合に、各画素の第 1 の絶縁層 PAS 1 および第 2 の絶縁層 PAS 2 の総厚が異なるのであれば、絶縁層の総厚が厚い方の画素電極と走査信号線の重畠領域の面積を大きくする。

30

#### 【 0 0 6 0 】

また、その他にも、たとえば、図 13 に示すように、ある走査信号線 GL<sub>m</sub> とある映像信号線 DL<sub>n</sub> が交差する箇所の近傍にある第 1 の画素 PA 1 と、別の走査信号線 GL<sub>u</sub> と別の映像信号線 DL<sub>v</sub> が交差する箇所の近傍にある第 2 の画素 PA 2 に着目した場合に、各画素の第 1 の絶縁層 PAS 1 および第 2 の絶縁層 PAS 2 の総厚が異なるのであれば、絶縁膜の総厚が厚い方の画素電極と走査信号線の重畠領域の面積を大きくする。

40

#### 【 0 0 6 1 】

またさらに、たとえば、図 14 に示すように、ある走査信号線 GL<sub>m</sub> と映像信号線 DL<sub>n</sub> が交差する箇所の近傍にある第 1 の画素 PA 1 と、走査信号線 GL<sub>m+1</sub> と映像信号線 DL<sub>v</sub> が交差する箇所の近傍にある第 2 の画素 PA 2 に着目した場合に、各画素の第 1 の絶縁層 PAS 1 および第 2 の絶縁層 PAS 2 の総厚が異なるのであれば、絶縁層の総厚が厚い方の画素電極と走査信号線の重畠領域の面積を大きくする。同様に、走査信号線 GL<sub>m</sub> とある映像信号線 DL<sub>n</sub> が交差する箇所の近傍にある第 1 の画素 PA 1' と、走査信号線 GL<sub>m</sub> と別の映像信号線 DL<sub>v+1</sub> が交差する箇所の近傍にある第 2 の画素 PA 2' に着目した場合に、各画素の第 1 の絶縁層 PAS 1 および第 2 の絶縁層 PAS 2 の総厚が異

50

なるのであれば、絶縁層の総厚が厚い方の画素電極と走査信号線の重畠領域の面積を大きくする。

#### 【0062】

ただし、2つの画素が、たとえば、図14に示したように、隣接する場合、あるいは非常に近い位置関係にある場合、各画素の第1の絶縁層PAS1および第2の絶縁層PAS2の総厚の差は非常に小さい。そのため、たとえば、画素電極と走査信号線の重畠領域の面積が同じであっても、保持容量のばらつきは非常に小さい。したがって、実施例1の液晶表示パネルでは、隣接する2つの画素、あるいは非常に近い位置関係にある2つの画素における画素電極と走査信号線の重畠領域の面積が等しくてもよい。すなわち、実施例1の液晶表示パネルは、2つの画素における画素電極と走査信号線の重畠領域の面積が異なる場合には、必ず重畠領域の面積が大きい方の画素の画素電極と走査信号線の重畠領域に介在する絶縁層の総厚が厚いと言えるが、2つの画素における画素電極と走査信号線の重畠領域に介在する絶縁層の総厚が異なる場合には、必ずしも絶縁層の総厚が厚い方が重畠領域の面積が大きいとは言えない。

10

#### 【0063】

このように、TFT基板1の表示領域DAにある任意の2つの画素に着目し、各画素における画素電極と走査信号線の重畠領域の面積が異なる場合に、重畠領域の面積が大きい方の画素の画素電極と走査信号線の重畠領域に介在する絶縁層の総厚が厚くなつていれば、各画素の保持容量のばらつきが低減される。そのため、1枚の基板の表示領域における各画素の保持容量のばらつきによる画質の面内ばらつきが低減される。

20

#### 【0064】

また、実施例1の液晶表示パネルでは、たとえば、各画素の保持容量が一定値以上になるようにすべての画素の画素電極と導体層の重畠領域の面積を大きくする必要はない。そのため、走査信号線駆動回路の出力を大きくする必要がなくなり、液晶表示装置の消費電力の増加を抑えることができる。

#### 【0065】

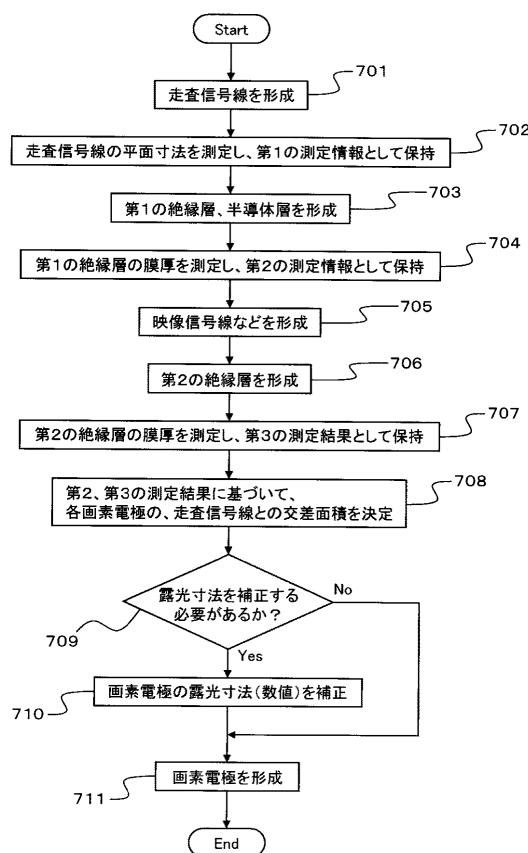

図15は、実施例1の液晶表示パネルに用いるTFT基板の製造方法の一例を示すフロー図である。

#### 【0066】

以下、実施例1の液晶表示パネルに用いるTFT基板の製造方法の一例について説明する。なお、実施例1のTFT基板の製造方法は、基本的には、従来のTFT基板の製造方法と同じ手順である。そのため、従来の製造方法と同じ工程については詳細な説明を省略する。

30

#### 【0067】

実施例1のTFT基板1を製造するときには、図15に示すように、まず、ガラス基板SUBの表面に走査信号線を形成する(ステップ701)。ステップ701は、たとえば、スパッタリング法でアルミニウム膜、またはアルミニウム膜を含む複数層の導体膜を成膜した後、エッチングして走査信号線を形成する。

#### 【0068】

次に、ステップ701で形成した走査信号線の平面寸法を測定し、第1の測定情報として保持する(ステップ702)。ステップ702は、たとえば、ガラス基板SUB上に形成された走査信号線の画像を取得し、幅や、ガラス基板SUBにおける端部の位置を測定する。

40

#### 【0069】

次に、たとえば、第1の絶縁層PAS1および半導体層SC<sub>H</sub>を形成する(ステップ703)。ステップ703は、たとえば、CVD法でSiN膜を成膜して第1の絶縁層PAS1を形成した後、続けて、たとえば、アモルファスシリコン(a-Si)膜を成膜し、アモルファスシリコン膜をパターニングして半導体層SC<sub>H</sub>を形成する。

#### 【0070】

次に、第1の絶縁層PAS1の膜厚を測定し、第2の測定情報として保持する(ステッ

50

プ704)。ステップ704は、たとえば、エリプソメータなどの膜厚計測器を用いて計測する。

【0071】

次に、映像信号線などを形成する(ステップ705)。ステップ705は、たとえば、スパッタリング法でアルミニウム膜、またはアルミニウム膜を含む複数層の導体膜を成膜した後、エッチングして映像信号線、TFT素子のドレイン電極SD1およびソース電極SD2を形成する。

【0072】

次に、第2の絶縁層PAS2を形成する(ステップ706)。ステップ706は、たとえば、CVD法で有機絶縁膜を成膜した後、ソース電極SD2の上にスルーホールTHを形成する。

10

【0073】

次に、第2の絶縁層PAS2の膜厚を測定し、第3の測定情報として保持する(ステップ707)。ステップ707は、たとえば、エリプソメータなどの膜厚計測器を用いて計測する。

【0074】

次に、第2の測定情報および第3の測定情報に基づいて、各画素の保持容量を形成する位置の絶縁層の厚さを求め、各画素に形成する画素電極の、走査信号線と平面で見て重なる領域の面積を決定する(ステップ708)。

20

【0075】

次に、ステップ708で決定した各画素電極と走査信号線の平面で見て重なる領域(重畳領域)の面積と第1の測定情報に基づく各画素電極の寸法を、あらかじめ用意された設計寸法に基づく露光寸法と比較し、露光寸法を補正する必要があるか否かを判定する(ステップ709)。ステップ709において、補正する必要があると判定した場合、画素電極の露光寸法を補正し(ステップ710)、その補正した露光寸法に基づいて画素電極を形成する(ステップ711)。ステップ711は、たとえば、第2の絶縁層PAS2の表面にITO膜などの透明導体膜を成膜し、透明導体膜の上にレジストを印刷または塗布した後、レジストを露光、現像してエッチングレジストを形成する。そして、エッチングレジストをマスクにして透明導体膜をパターニングして画素電極を形成した後、エッチングレジストを除去する。

30

【0076】

また、ステップ709において、補正する必要がないと判定した場合、あらかじめ用意された露光寸法に基づいて画素電極を形成する(ステップ711)。

【0077】

なお、図15に示したような手順でTFT基板1を製造する場合、ステップ711でレジストを露光するときには、たとえば、直描露光機と呼ばれる露光装置を用いることが望ましい。前記直描露光機は、たとえば、CADレイアウトデータなどの数値データ(描画用データ)に基づいて、感光性レジストに露光パターンを直接描画する露光装置である。直描露光機で露光パターンを描画する方法としては、たとえば、感光性レジストの露光領域全域を複数の小領域に分割し、前記描画用データに基づいて各小領域を露光する小領域と露光しない小領域にわけ、露光ヘッドを移動させながら前記露光する小領域のみを順次露光していく方法がある。

40

【0078】

前記直描露光機は、ガラス基板などの上にクロム(Cr)膜などでパターンを描いたマスクを使用しない露光装置であり、露光パターンを表現する数値データを書き換えることで、容易にレジストの露光領域(パターン)を変えることができ、TFT基板1の製造過程において、画素電極の形成に用いる露光パターンを隨時変更できる。そのため、第1の絶縁層PAS1や第2の絶縁層PAS2の膜厚のばらつきの変化に即座に対応でき、保持容量のばらつきが少ないTFT基板1を効率よく製造することができる。

【0079】

50

また、図15に示したフロー図では、第1の絶縁層PAS1の膜厚と第2の絶縁層PAS2の膜厚を、それぞれ別の工程で測定しているが、これに限らず、第2の絶縁層PAS2を形成した後、第1の絶縁層PAS1および第2の絶縁層PAS2の総厚を測定してもよいことはもちろんである。

#### 【0080】

また、ステップ702、ステップ704、およびステップ707は、すべての画素の保持容量が形成される領域について、走査信号線の平面寸法、第1の絶縁層PAS1の膜厚、および第2の絶縁層PAS2の膜厚を測定することが望ましい。しかしながら、液晶表示パネルの表示領域DAにある画素の数は膨大であり、すべての画素について計測するには膨大な時間を要する。また、成膜した薄膜（絶縁膜）の膜厚のばらつきは、たとえば、隣り合う画素領域などでは非常に小さく、保持容量のばらつきはほとんど無視できる。そのため、ステップ702、ステップ704、およびステップ707は、たとえば、表示領域DAをいくつかの小領域に分割し、小領域の中心などの代表点で測定した値を小領域にある各画素での測定値と見なすこともできる。

10

#### 【0081】

この場合、1つの小領域にある各画素における画素電極と走査信号線の重畠領域の面積はほぼ等しいが、画素電極と走査信号線の重畠領域に介在する絶縁層の総厚にはわずかではあるがばらつきが生じる。そのため、実施例1の液晶表示パネル（TFT基板1）は、画素電極と走査信号線の重畠領域の面積が異なる場合は重畠領域の面積が大きい方が介在する絶縁層が厚いと言えるが、その逆、介在する絶縁層が厚い方が重畠領域の面積が大きいとは必ずしも言えない。

20

#### 【0082】

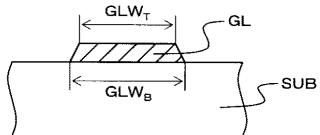

図16は、走査信号線の平面寸法の測定方法を説明するための模式断面図である。

#### 【0083】

図4、図6、図11などでは、走査信号線の断面形状が矩形になっているが、導体膜をエッチングして走査信号線GLを形成する場合、実際には、たとえば、図16に示すように、上底側が細い（狭い）台形状の断面になる。そのため、図15に示したステップ702で各走査信号線GLの平面寸法（幅）を測定するときには、走査信号線の下底側の幅GLW<sub>B</sub>または上底側の幅GLW<sub>T</sub>のどちらかに統一して測定する。

30

#### 【0084】

図17は、実施例1のTFT基板の1画素の別の構成例を説明するための模式平面図である。

#### 【0085】

実施例1では、TFT基板1の1画素の構成例として、たとえば、図3および図6に示すように、画素電極PXが、自身に接続されているTFT素子のゲート電極が接続されている走査信号線GL<sub>m+1</sub>ではないほうの走査信号線GL<sub>m</sub>と平面でみて重なる領域を有し、その領域において保持容量を形成している例を挙げた。しかしながら、実施例1の液晶表示パネルの場合、そのような構成に限らず、たとえば、図17に示すように、走査信号線GL<sub>m</sub>、GL<sub>m+1</sub>の間に、走査信号線と並行する保持容量線STL<sub>m</sub>を設け、画素電極PXと保持容量線STL<sub>m</sub>が立体的に交差する領域に保持容量を形成してもよいことはもちろんである。この場合も、画素電極PXと保持容量線STL<sub>m</sub>が平面でみて重なる領域（重畠領域）に介在する第1の絶縁層PAS1および第2の絶縁層PAS2の総厚に基づいて重畠領域の面積を決定し、それに合わせて画素電極PXの寸法を変えることで、1枚の液晶表示パネルの表示領域における保持容量のばらつきを低減でき、画質のばらつきを低減できる。

40

#### 【0086】

なお、実施例1で挙げた構成は、種々の液晶表示装置に適用可能であるが、特に、テレビやPCのディスプレイなどの大型の表示パネルを有する表示装置に適用すると、高い効果が得られる。

#### 【実施例2】

50

## 【0087】

実施例1では、液晶表示パネルの表示領域DAにおける任意の2つの画素における画素電極PXと走査信号線GLが平面でみて重なる領域(重畠領域)の面積と、重畠領域に介在する絶縁層の厚さの関係について説明した。

## 【0088】

実施例2は、実施例1で説明した関係を前提とし、液晶表示パネル(TFT基板1)の表示領域DAの、ある特定の3つの画素におけるこれらの関係について規定した実施例である。

## 【0089】

現在、液晶表示パネルに用いられるTFT基板1は、たとえば、1枚のマザーガラスから2面(2枚)のTFT基板1を切り出したり、4面(4枚)のTFT基板1を切り出したりして製造されている。10

## 【0090】

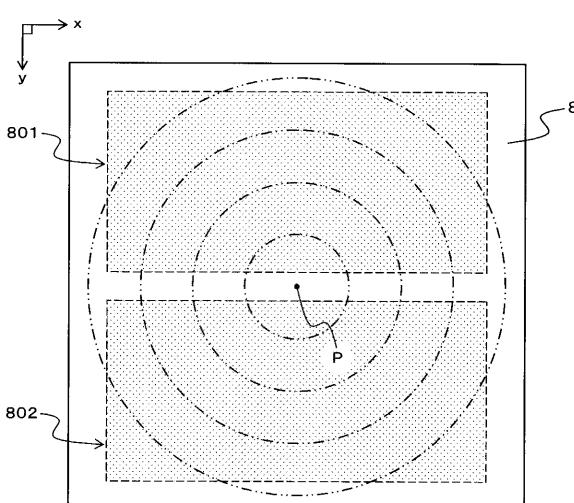

図18は、1枚のマザーガラスから2枚のTFT基板を切り出す場合の導体膜の膜厚分布を示す模式平面図である。

## 【0091】

1枚のマザーガラスから2枚のTFT基板1を切り出す、いわゆる2面取りの場合、図18に示すように、マザーガラス8には、2個の、TFT基板1として切り出す領域801, 802がある。この2個の領域801, 802にはそれぞれ、たとえば、1画素の構成が図3乃至図6に示したような構成のTFT基板1が形成される。そして、TFT基板1を形成した後、マザーガラス8から2個の領域801, 802を切り出して、液晶表示パネルを形成する。20

## 【0092】

このような2面取りの場合、たとえば、マザーガラス8の各領域801, 802に走査信号線GLを形成するための導体膜は、マザーガラス8の全面に形成される。このとき、マザーガラス8の全面に形成される導体膜の膜厚分布は、たとえば、図18に示すように、マザーガラス8の中心Pを中心とする同心円で表すことができる。このとき、導体の膜厚は、中心Pおよびその近傍が最も厚く、中心Pから遠ざかるにつれて徐々に薄くなっていく。また、映像信号線DLなどの形成に用いる導体膜を形成したときにも、同様の膜厚分布になる。これは、導体膜を形成する際に、たとえば、スパッタリング法で成膜するためである。30

## 【0093】

また、マザーガラス8上に、たとえば、第1の絶縁層PAS1の形成に用いる絶縁膜などを形成したときにも、その絶縁膜の膜厚分布は、導体膜の場合と同様の分布になる。これは、絶縁膜を形成する際に、たとえば、プラズマCVD法で成膜するためである。

## 【0094】

図19は、1枚のマザーガラスから4枚のTFT基板を切り出す場合の導体膜の膜厚分布を示す模式平面図である。

## 【0095】

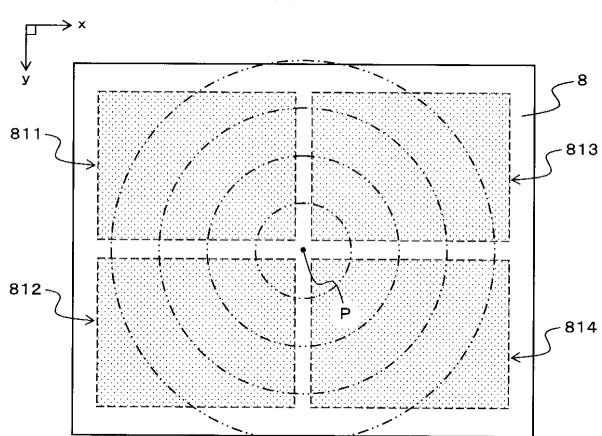

1枚のマザーガラスから4枚のTFT基板1を切り出す、いわゆる4面取りの場合、図19に示すように、マザーガラス8には、4個の、TFT基板1として切り出す領域811, 812, 813, 814がある。この4個の領域811～814にはそれぞれ、たとえば、1画素の構成が図3乃至図6に示したような構成のTFT基板1が形成される。そして、TFT基板1を形成した後、マザーガラス8から4個の領域811～814を切り出して、液晶表示パネルを形成する。40

## 【0096】

このような4面取りの場合も、たとえば、マザーガラス8の4個の領域811～814に、走査信号線GLを形成するための導体膜や、第1の絶縁層PAS1を形成するための絶縁膜などは、マザーガラス8の全面に形成(成膜)される。そのため、導体膜や絶縁膜の膜厚分布は、たとえば、図19に示すように、マザーガラス8の中心Pを中心とする同50

心円で表される。このとき、導体膜や絶縁膜の膜厚は、中心Pおよびその近傍が最も厚く、中心Pから遠ざかるにつれて、徐々に薄くなっていく。

#### 【0097】

図20は、1枚のマザーガラスから6枚のTFT基板を切り出す場合の導体膜の膜厚分布を示す模式平面図である。

#### 【0098】

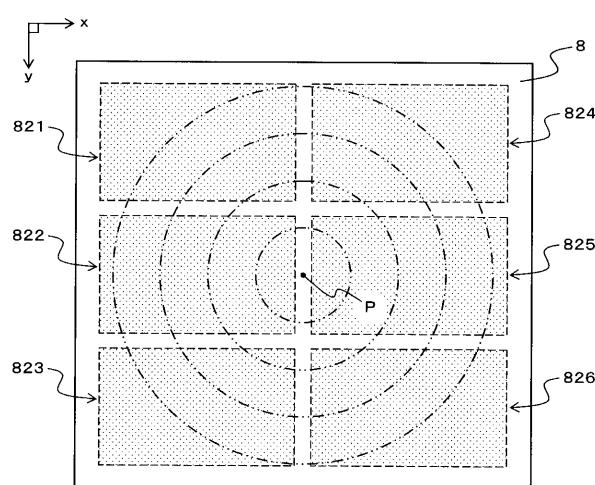

1枚のマザーガラスから6枚のTFT基板1を切り出す、いわゆる6面取りの場合、図20に示すように、マザーガラス8には、6個の、TFT基板1として切り出す領域821, 822, 823, 824, 825, 826がある。この6個の領域821～826にはそれぞれ、たとえば、1画素の構成が図3乃至図6に示したような構成のTFT基板1が形成される。そして、TFT基板1を形成した後、マザーガラス8から6個の領域821～826を切り出して、液晶表示パネルを形成する。10

#### 【0099】

このような6面取りの場合も、たとえば、マザーガラス8の6個の領域821～826に走査信号線GLを形成するための導体膜や、第1の絶縁層PAS1を形成するための絶縁膜などは、マザーガラス8の全面に形成(成膜)される。そのため、導体膜や絶縁膜の膜厚分布は、たとえば、図20に示すように、マザーガラス8の中心Pを中心とする同心円で表される。このとき、導体膜または絶縁膜の膜厚は、中心Pおよびその近傍が最も厚く、中心Pから遠ざかるにつれて徐々に薄くなっていく。

#### 【0100】

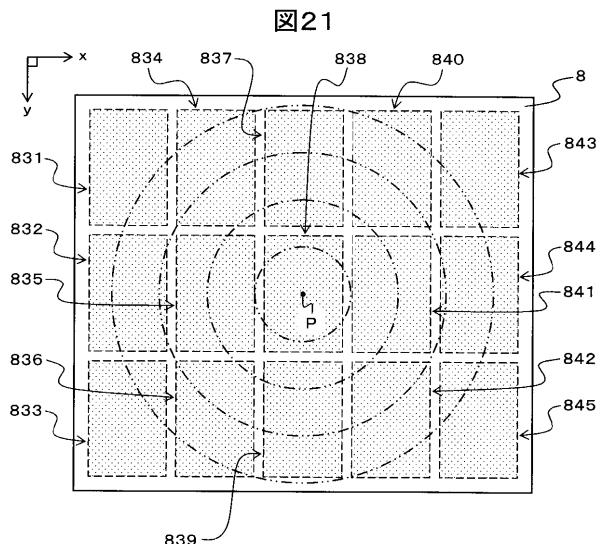

図21は、1枚のマザーガラスから15枚のTFT基板を切り出す場合の導体膜の膜厚分布を示す模式図である。20

#### 【0101】

1枚のマザーガラスから15枚のTFT基板1を切り出す、いわゆる15面取りの場合、図21に示すように、マザーガラス8には、15個の、TFT基板1として切り出す領域831, 832, 833, 834, 835, 836, 837, 838, 839, 840, 841, 842, 843, 844, 845がある。この15個の領域831～845にはそれぞれ、たとえば、1画素の構成が図3乃至図6に示したような構成のTFT基板1が形成される。そして、TFT基板1を形成した後、マザーガラス8から15個の領域831～845を切り出して、液晶表示パネルを形成する。30

#### 【0102】

このような15面取りの場合も、たとえば、マザーガラス8の15個の領域831～845に走査信号線GLを形成するための導体膜や、第1の絶縁層PAS1を形成するための絶縁膜などは、マザーガラス8の全面に形成(成膜)される。そのため、導体膜や絶縁膜の膜厚分布は、たとえば、図21に示すように、マザーガラス8の中心Pを中心とする同心円で表される。このとき、導体膜や絶縁膜の膜厚は、中心Pおよびその近傍が最も厚く、中心Pから遠ざかるにつれて徐々に薄くなっていく。

#### 【0103】

ここで、図18乃至図21に示したように、1枚のマザーガラス8から多面取りを行う場合に切り出される各領域、つまり1枚のTFT基板1が形成される領域における導体膜や絶縁膜の膜厚分布は、以下の4つのパターンに分類されることがわかる。40

#### 【0104】

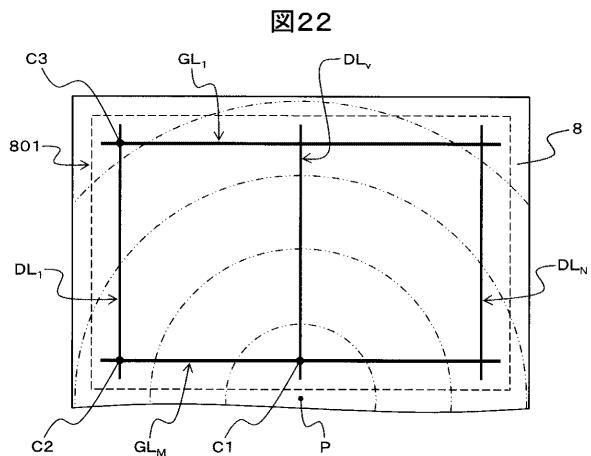

1つめのパターンは、導体膜または絶縁膜の膜厚の分布が、図18に示した領域801, 802、図21に示した領域837, 839のようになるパターンである。この1つめのパターンの特徴について、図22を用いて説明する。

#### 【0105】

図22は、1つめのパターンの膜厚分布における特定の3箇所の選択例を説明するための模式平面図である。

#### 【0106】

導体膜や絶縁膜の膜厚分布の1つめのパターンを説明するにあたって、図22に示すよ50

うに、2面取りの場合におけるマザーガラス8の1つの領域801を例に挙げる。図22において、 $GL_1$ ,  $GL_M$ は、表示領域の最も外側に配置されている走査信号線を示しており、 $DL_1$ ,  $DL_N$ は、表示領域の最も外側に配置されている映像信号線を示している。つまり、この2本の走査信号線 $GL_1$ ,  $GL_M$ と、2本の映像信号線 $DL_1$ ,  $DL_N$ に囲まれた領域が、本発明でいうところの表示領域DAになる。そして、この表示領域DAには、図示していない複数本の走査信号線と、表示領域DAの中央部に配置された映像信号線 $DL_v$ および図示していない複数本の映像信号線が配置されている。

#### 【0107】

1つめのパターンでは、領域801の表示領域の最も外側に配置される2本の走査信号線のうち、マザーガラス8の中心Pに近いほうの走査信号線 $GL_M$ と、映像信号線 $DL_v$ が立体的に交差する点C1の近傍にある1つの画素を第1の画素とする。また、前記走査信号線 $GL_M$ と、表示領域の最も外側に配置された2本の映像信号線のうちの1本の映像信号線 $DL_1$ が立体的に交差する点C2の近傍にある1つの画素を第2の画素とする。また、前記映像信号線 $DL_1$ と、表示領域の最外側に配置されたもう一方の走査信号線 $GL_1$ が立体的に交差する点C3の近傍にある1つの画素を第3の画素とする。

10

#### 【0108】

このとき、第1の画素、第2の画素、第3の画素の位置関係は、別の言い方をすれば、第1の画素は表示領域の1つの辺（第1の辺）の中心の近傍にあり、第2の画素は表示領域の前記第1の辺と他の辺（第2の辺）が接続する角部の近傍にあり、第3の画素は表示領域の前記第2の辺と、前記第1の辺と対向する辺（第3の辺）が接続する角部の近傍にあると言える。

20

#### 【0109】

この1つめのパターンにおいて、マザーガラス8の表面に、たとえば、第1の絶縁層PAS1や第2の絶縁膜PAS2を形成すると、その膜厚分布は、マザーガラス8の中心Pに近いほど厚く、中心Pから遠ざかるにつれて薄くなる。つまり、点C1の近傍にある第1の画素における第1の絶縁層PAS1および第2の絶縁層PAS2の膜厚の総厚をPASD1、点C2の近傍にある第2の画素における第1の絶縁層PAS1および第2の絶縁層PAS2の膜厚の総厚をPASD2、点C3の近傍にある第3の画素における第1の絶縁層PAS1および第2の絶縁層PAS2の膜厚の総厚をPASD3とすれば、各画素がある領域における絶縁層の総厚の関係はPASD1 > PASD2 > PASD3になる。

30

#### 【0110】

また、本発明のTFT基板1は、実施例1で説明したように、画素電極と走査信号線、または画素電極と保持容量線の重畠領域の面積は、画素電極と走査信号線または保持容量線の間に介在する絶縁層が薄い場合は面積が狭く、厚い場合は面積が大きくなるように形成する。そのため、第1の画素における画素電極と走査信号線の重畠領域の面積をS1、第2の画素における画素電極と走査信号線の重畠面積をS2、第3の画素における画素電極と走査信号線が重なる領域の面積をS3とすれば、各画素における画素領域と走査信号線の重畠領域の面積の関係はS1 > S2 > S3になっていることが望ましい。

#### 【0111】

なお、実施例1で説明したように、第1の画素、第2の画素、第3の画素の絶縁層の総厚の関係がPASD1 > PASD2 > PASD3であれば、画素領域と走査信号線の重畠領域の面積の関係はS1 > S2 > S3になるということは必ずしも言えないが、その逆、すなわち、第1の画素、第2の画素、第3の画素における画素領域と走査信号線の重畠領域の面積の関係がS1 > S2 > S3であれば、絶縁層の総厚の関係はPASD1 > PASD2 > PASD3になる。これが、1つめのパターンにおける画素電極と走査信号線または保持容量線の重畠領域の面積と、介在する絶縁層の膜厚の関係である。

40

#### 【0112】

なお、図22には、1つめのパターンの例として2面取りの場合を挙げているが、図21に示した15面取りの場合における領域837, 839も、同様の関係（特徴）を持つことはもちろんである。

50

**【 0 1 1 3 】**

このような関係を持つ液晶表示パネルでは、各画素領域に形成される保持容量のばらつきによる画質のばらつきを低減することが可能となる。

**【 0 1 1 4 】**

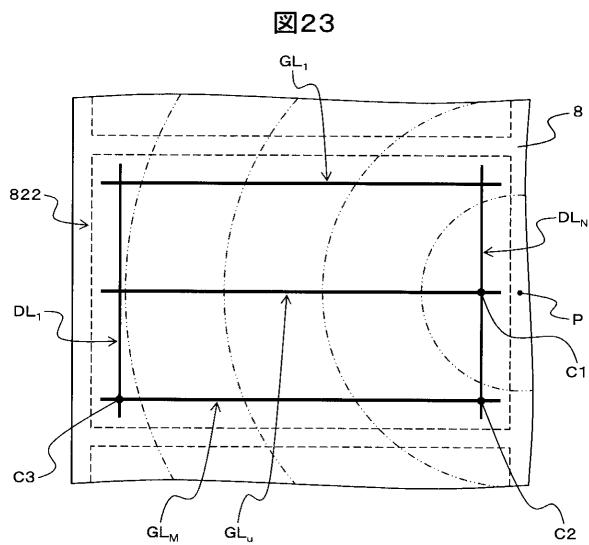

次に、2つめのパターンを説明する。2つめのパターンは、導体膜または絶縁膜の膜厚分布が、図20に示した領域822, 825、図21に示した領域832, 835, 841, 844のようになるパターンである。この2つめのパターンの特徴について、図23を用いて説明する。

**【 0 1 1 5 】**

図23は、2つめのパターンの膜厚分布における特定の3箇所の選択例を説明するための模式平面図である。

10

**【 0 1 1 6 】**

導体膜や絶縁膜の膜厚分布の2つめのパターンを説明するにあたっては、図23に示すように、6面取りの場合におけるマザーガラス8の1つの領域822を例に挙げる。図23において、 $GL_1$ ,  $GL_M$ は、表示領域の最も外側に配置されている走査信号線を示しており、 $DL_1$ ,  $DL_N$ は、表示領域の最も外側に配置されている映像信号線を示している。つまり、この2本の走査信号線 $GL_1$ ,  $GL_M$ と、2本の映像信号線 $DL_1$ ,  $DL_N$ に囲まれた領域が、本発明でいうところの表示領域DAになる。そして、この表示領域DAには、表示領域の中央部に配置された走査信号線 $GL_u$ および図示していない複数本の走査信号線、図示していない複数本の映像信号線が配置されている。

20

**【 0 1 1 7 】**

2つめのパターンでは、領域822の表示領域の最も外側に配置される2本の映像信号線のうち、マザーガラス8の中心Pに近いほうの映像信号線 $DL_N$ と、走査信号線 $GL_u$ が立体的に交差する点C1の近傍にある1つの画素を第1の画素とする。また、前記映像信号線 $DL_N$ と、表示領域の最も外側に配置された2本の走査信号線のうちの1本の走査信号線 $GL_M$ が立体的に交差する点C2の近傍にある1つの画素を第2の画素とする。また、前記走査信号線 $GL_M$ と、表示領域の最も外側に配置されたもう一方の映像信号線 $DL_1$ が立体的に交差する点C3の近傍にある1つの画素を第3の画素とする。

**【 0 1 1 8 】**

このとき、第1の画素、第2の画素、第3の画素の位置関係は、別の言い方をすれば、第1の画素は表示領域の1つの辺（第1の辺）の中心の近傍にあり、第2の画素は表示領域の前記第1の辺と他の辺（第2の辺）が接続する角部の近傍にあり、第3の画素は表示領域の前記第2の辺と、前記第1の辺と対向する辺（第3の辺）が接続する角部の近傍にあると言える。

30

**【 0 1 1 9 】**

この2つめのパターンにおいて、マザーガラス8の表面に、たとえば、第1の絶縁層PAS1や第2の絶縁層PAS2を形成すると、その膜厚分布は、マザーガラス8の中心Pに近いほど厚く、中心Pから遠ざかるにつれて薄くなる。つまり、点C1の近傍にある第1の画素における第1の絶縁層PAS1および第2の絶縁層PAS2の膜厚の総厚をPASD1、点C2の近傍にある第2の画素における第1の絶縁層PAS1および第2の絶縁層PAS2の膜厚の総厚をPASD2、点C3の近傍にある第3の画素における第1の絶縁層PAS1および第2の絶縁層PAS2の膜厚の総厚をPASD3とすれば、各画素がある領域における絶縁層の総厚の関係はPASD1 > PASD2 > PASD3になる。

40

**【 0 1 2 0 】**

また、本発明のTFT基板1は、実施例1で説明したように、画素電極と走査信号線、または画素電極と保持容量線が平面の重畠領域の面積は、画素電極と走査信号線または保持容量線の間に介在する絶縁層が薄い場合は面積が狭く、厚い場合は面積が大きくなるように形成する。そのため、第1の画素における画素電極と走査信号線の重畠領域の面積をS1、第2の画素における画素電極と走査信号線の重畠領域の面積をS2、第3の画素における画素電極と走査信号線の重畠領域の面積をS3とすれば、各画素における画素領域

50

と走査信号線の重畳領域の面積の関係は S<sub>1</sub> > S<sub>2</sub> > S<sub>3</sub> になっていることが望ましい。

【0121】

なお、実施例 1 で説明したように、第 1 の画素、第 2 の画素、第 3 の画素の絶縁層の総厚の関係が P A S D 1 > P A S D 2 > P A S D 3 であれば、画素領域と走査信号線の重畳領域の面積の関係は S<sub>1</sub> > S<sub>2</sub> > S<sub>3</sub> になるということは必ずしも言えないが、その逆、すなわち、第 1 の画素、第 2 の画素、第 3 の画素における画素領域と走査信号線の重畳領域の面積の関係が S<sub>1</sub> > S<sub>2</sub> > S<sub>3</sub> であれば、絶縁層の総厚の関係は P A S D 1 > P A S D 2 > P A S D 3 になる。これが、2つめのパターンにおける画素電極と走査信号線または保持容量線の重畠領域の面積と、介在する絶縁層の膜厚の関係である。

【0122】

なお、図 23 には、2つめのパターンの例として 6 面取りの場合を挙げているが、図 21 に示した 15 面取りの場合における領域 832, 835, 841, 844 も、同様の関係（特徴）を持つことはもちろんである。

【0123】

このような関係を持つ液晶表示パネルでは、各画素に形成される保持容量のばらつきによる画質のばらつきを低減することが可能となる。

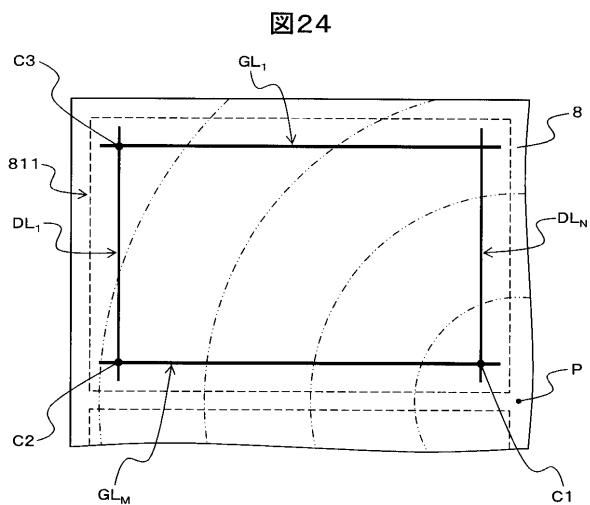

【0124】

次に、3つめのパターンを説明する。3つめのパターンは、導体膜または絶縁膜の膜厚の分布が、図 19 に示した領域 811, 812, 813, 814、図 20 に示した領域 821, 823, 824, 826、図 21 に示した領域 831, 833, 834, 836, 840, 842, 843, 845 のようになるパターンである。この3つめのパターンの特徴について、図 24 を用いて説明する。

【0125】

図 24 は、3つめのパターンの膜厚分布における特定の 3箇所の選択例を説明するための模式平面図である。

【0126】

導体膜や絶縁膜の膜厚分布の3つめのパターンを説明するにあたっては、図 24 に示すように、4面取りの場合におけるマザーガラス 8 の 1 つの領域 811 を例に挙げる。図 24において、G L<sub>1</sub>, G L<sub>M</sub> は、表示領域における最外に配置されている走査信号線を示しており、D L<sub>1</sub>, D L<sub>N</sub> は、表示領域における最外に配置されている映像信号線を示している。つまり、この 2 本の走査信号線 G L<sub>1</sub>, G L<sub>M</sub> と、2 本の映像信号線 D L<sub>1</sub>, D L<sub>N</sub> に囲まれた領域が、本発明でいうところの表示領域となる。そして、この表示領域には、図示していない複数本の走査信号線、図示していない複数本の映像信号線が配置されている。

【0127】

3つめのパターンでは、領域 711 内の表示領域の最外側に配置される 2 本の走査信号線および 2 本の映像信号線のうち、マザーガラス 8 の中心 P に近いほうの走査信号線 G L<sub>M</sub> と映像信号線 D L<sub>N</sub> が立体的に交差する点 C<sub>1</sub> の近傍にある 1 つの画素を第 1 の画素とする。また、前記走査信号線 G L<sub>M</sub> と、もう一方の最外側の映像信号線 D L<sub>1</sub> が立体的に交差する点 C<sub>2</sub> の近傍にある 1 つの画素を第 2 の画素とする。また、前記映像信号線 D L<sub>1</sub> と、もう一方の最外側の走査信号線 G L<sub>1</sub> が立体的に交差する点 C<sub>3</sub> の近傍にある 1 つの画素を第 3 の画素とする。

【0128】

このとき、第 1 の画素、第 2 の画素、第 3 の画素の位置関係は、別の言い方をすれば、第 1 の画素は表示領域の 2 つの辺（第 1 の辺と第 2 の辺）が接続する角部の近傍にあり、第 2 の画素は前記第 1 の辺と、前記第 2 の辺に対向する第 3 の辺が接続する角部の近傍にあり、第 3 の画素は前記第 3 の辺と、前記第 1 の辺に対向する第 4 の辺が接続する角部の近傍にあると言える。

【0129】

この3つめのパターンにおいて、マザーガラス 8 の表面に、たとえば、第 1 の絶縁層 P

A S 1 や第 2 の絶縁膜 P A S 2 を形成すると、その膜厚分布は、マザーガラス 8 の中心 P に近いほど厚く、中心 P から遠ざかるにつれて薄くなる。つまり、点 C 1 の近傍にある第 1 の画素における第 1 の絶縁層 P A S 1 および第 2 の絶縁層 P A S 2 の膜厚の総厚を P A S D 1 、点 C 2 の近傍にある第 2 の画素における第 1 の絶縁層 P A S 1 および第 2 の絶縁層 P A S 2 の膜厚の総厚を P A S D 2 、点 C 3 の近傍にある第 3 の画素における第 1 の絶縁層 P A S 1 および第 2 の絶縁層 P A S 2 の膜厚の総厚を P A S D 3 とすれば、各画素がある領域における絶縁層の総厚の関係は P A S D 1 > P A S D 2 > P A S D 3 になる。

#### 【 0 1 3 0 】

また、本発明の T F T 基板 1 は、実施例 1 で説明したように、画素電極と走査信号線、または画素電極と保持容量線の重畠領域の面積は、画素電極と走査信号線または保持容量線の間に介在する絶縁層が薄い場合は面積が狭く、厚い場合は面積が大きくなるように形成する。そのため、第 1 の画素における画素電極と走査信号線の重畠領域の面積を S 1 、第 2 の画素における画素電極と走査信号線の重畠面積を S 2 、第 3 の画素における画素電極と走査信号線が重なる領域の面積を S 3 とすれば、各画素における画素領域と走査信号線の重畠領域の面積の関係は S 1 > S 2 > S 3 になっていることが望ましい。

#### 【 0 1 3 1 】

なお、実施例 1 で説明したように、第 1 の画素、第 2 の画素、第 3 の画素の絶縁層の総厚の関係が P A S D 1 > P A S D 2 > P A S D 3 であれば、画素領域と走査信号線の重畠領域の面積の関係は S 1 > S 2 > S 3 になるということは必ずしも言えないが、その逆、すなわち、第 1 の画素、第 2 の画素、第 3 の画素における画素領域と走査信号線の重畠領域の面積の関係が S 1 > S 2 > S 3 であれば、絶縁層の総厚の関係は P A S D 1 > P A S D 2 > P A S D 3 になる。これが、3 つめのパターンにおける画素電極と走査信号線または保持容量線の重畠領域の面積と、介在する絶縁層の膜厚の関係である。

#### 【 0 1 3 2 】

また、図 2 4 には、3 つめのパターンの例として 4 面取りの場合の 1 つの領域 8 1 1 を挙げているが、4 面取りの場合、残りの領域 8 1 2 ~ 8 1 4 も、同様の関係（特徴）を持つ。また、4 面取りの場合に限らず、図 2 0 に示した 6 面取りの場合における領域 8 2 1 , 8 2 3 , 8 2 4 , 8 2 6 、図 2 1 に示した 15 面取りの場合における領域 8 3 1 , 8 3 3 , 8 3 4 , 8 3 6 , 8 4 0 , 8 4 2 , 8 4 3 , 8 4 5 も、同様の関係（特徴）を持つことはもちろんである。

#### 【 0 1 3 3 】

このような関係の表示パネルでは、各画素に形成される保持容量のばらつきによる画質のばらつきを低減することが可能となる。

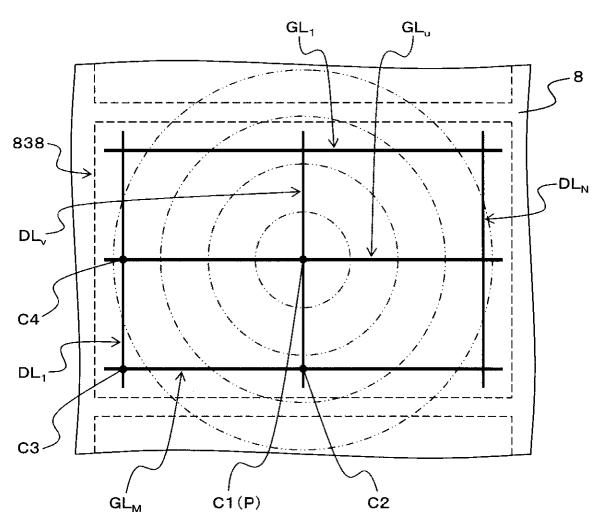

#### 【 0 1 3 4 】

最後に、4 つめのパターンを説明する。4 つめのパターンは、導体膜や絶縁膜の膜厚の分布が、図 2 1 に示した領域 8 3 8 のようになるパターンである。この 4 つめのパターンの特徴について、図 2 5 を用いて説明する。

#### 【 0 1 3 5 】

図 2 5 は、4 つめのパターンの膜厚分布および特定の 3 箇所の選択例を説明するための模式図である。

#### 【 0 1 3 6 】

導体膜や絶縁膜の膜厚分布の4 つめのパターンを説明するにあたっては、図 2 5 に示すように、15 面取りの場合におけるマザーガラス 8 の 1 つの領域 8 3 8 を例に挙げる。図 2 5 において、G L<sub>1</sub> , G L<sub>M</sub> は、表示領域の最外に配置されている走査信号線を示しており、D L<sub>1</sub> , D L<sub>N</sub> は、表示領域の最外に配置されている映像信号線を示している。つまり、この 2 本の走査信号線 G L<sub>1</sub> , G L<sub>M</sub> と、2 本の映像信号線 D L<sub>1</sub> , D L<sub>N</sub> に囲まれた領域が、本発明でいうところの表示領域となる。そして、この表示領域には、表示領域の中央部に配置された走査信号線 G L<sub>u</sub> 、同じく表示領域の中央部に走査信号線 G L<sub>v</sub> と立体的に交差するように配置された映像信号線 D L<sub>u</sub> のほか、図示していない複数本の走査信号線および複数本の映像信号線が配置されている。

10

20

30

40

50

## 【0137】

4つめのパターンでは、領域838の表示領域の中心、すなわち走査信号線 $GL_u$ と映像信号線 $DL_v$ が立体的に交差する点C1の近傍にある1つの画素を第1の画素、前記映像信号線 $DL_v$ と、表示領域の一方の最外側に配置される走査信号線 $GL_M$ が立体的に交差する点C2の近傍にある1つの画素を第2の画素とする。また、前記走査信号線 $GL_M$ と、表示領域の一方の最外側に配置される映像信号線 $DL_1$ が立体的に交差する点C3の近傍にある1つの画素を第3の画素とする。

## 【0138】

このとき、第1の画素、第2の画素、第3の画素の位置関係は、別の言い方をすれば、第1の画素は表示領域の中心またはその近傍にあり、第2の画素は表示領域の1つの辺(第1の辺)の中心の近傍にあり、第3の画素は前記第1の辺と他の辺(第2の辺)が接続する角部の近傍にあると言える。

10

## 【0139】

この4つめのパターンにおいて、マザーガラス8の表面に、たとえば、第1の絶縁層PAS1や第2の絶縁膜PAS2を形成すると、その膜厚分布は、マザーガラス8の中心Pに近いほど厚く、中心Pから遠ざかるにつれて薄くなる。つまり、点C1の近傍にある第1の画素における第1の絶縁層PAS1および第2の絶縁層PAS2の膜厚の総厚をPASD1、点C2の近傍にある第2の画素における第1の絶縁層PAS1および第2の絶縁層PAS2の膜厚の総厚をPASD2、点C3の近傍にある第3の画素における第1の絶縁層PAS1および第2の絶縁層PAS2の膜厚の総厚をPASD3とすれば、各画素がある領域における絶縁層の総厚の関係はPASD1 > PASD2 > PASD3になる。

20

## 【0140】

また、本発明のTFT基板1は、実施例1で説明したように、画素電極と走査信号線、または画素電極と保持容量線の重畠領域の面積は、画素電極と走査信号線または保持容量線の間に介在する絶縁層が薄い場合は面積が狭く、厚い場合は面積が大きくなるように形成する。そのため、第1の画素における画素電極と走査信号線の重畠領域の面積をS1、第2の画素における画素電極と走査信号線の重畠面積をS2、第3の画素における画素電極と走査信号線が重なる領域の面積をS3とすれば、各画素における画素領域と走査信号線の重畠領域の面積の関係はS1 > S2 > S3になっていることが望ましい。

30

## 【0141】

なお、実施例1で説明したように、第1の画素、第2の画素、第3の画素の絶縁層の総厚の関係がPASD1 > PASD2 > PASD3であれば、画素領域と走査信号線の重畠領域の面積の関係はS1 > S2 > S3になるということは必ずしも言えないが、その逆、すなわち、第1の画素、第2の画素、第3の画素における画素領域と走査信号線の重畠領域の面積の関係がS1 > S2 > S3であれば、絶縁層の総厚の関係はPASD1 > PASD2 > PASD3になる。これが、4つめのパターンにおける画素電極と走査信号線または保持容量線の重畠領域の面積と、介在する絶縁層の膜厚の関係である。

## 【0142】

また、図25に示した例では、映像信号線 $DL_v$ と走査信号線 $GL_M$ が立体的に交差する点C2の近傍にある1つの画素を第2の画素としたが、これに限らず、たとえば、走査信号線 $GL_u$ と映像信号線 $DL_1$ が立体的に交差する点C4の近傍にある1つの画素を第2の画素とした場合も、上記のような関係が成り立つことはもちろんである。

40

## 【0143】

なお、図25には、4つめのパターンの例として15面取りの場合の1つの領域838を挙げているが、15面取りに限らず、たとえば、3面×3面の9面取りの場合の中央の領域などでも、同様の関係(特徴)を持つことはもちろんである。

## 【0144】

このような関係の表示パネルでは、各画素に形成される保持容量のばらつきによる画質のばらつきを低減することが可能となる。

## 【0145】

50

なお、実施例 2 で説明したような関係を有する表示パネルは、実施例 1 で説明した方法と同様の方法で製造することができる。

【0146】

以上、本発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において、種々変更可能であることはもちろんである。

【0147】

たとえば、前記実施例では、液晶表示装置を例に挙げ、液晶表示パネルの TFT 基板 1 の構成について説明したが、本発明は、液晶表示装置に限らず、他の表示装置に適用することも可能である。つまり、図 3 乃至図 6 に示したような TFT 基板 1 と同等の構成であり、かつ同様の動作原理で映像や画像を表示する表示パネルを有する表示装置であれば、本発明を適用することで、画質むらの少ない表示装置を、低コストで製造することができる。そのような表示装置としては、たとえば、有機 EL (Electroluminescence) を用いた自発光型の表示パネルを有する表示装置がある。

10

【図面の簡単な説明】

【0148】

【図 1】実施例 1 の液晶表示パネルの模式平面図である。

【図 2】図 1 に示した A - A' 線における模式断面図である。

【図 3】図 1 に示した表示領域における TFT 基板の 1 画素の構成例を示す模式平面図である。

20

【図 4】図 3 に示した B - B' 線における模式断面図である。

【図 5】図 3 に示した C - C' 線における模式断面図である。

【図 6】図 3 に示した D - D' 線における模式断面図である。

【図 7】実施例 1 の液晶表示パネルにおける 2 つの画素の選択例を示す模式平面図である。

【図 8】ガラス基板に成膜した薄膜の、図 7 に示した E - E' 線における膜厚分布の一例を示す模式断面図である。

【図 9】画素電極を形成する工程の、図 7 に示した 2 つの画素における絶縁層の膜厚の関係の一例を示す模式断面図である。

30

【図 10】図 7 に示した 2 つの画素における画素電極と走査信号線の重畠領域の面積の関係の一例を示す模式平面図である。

【図 11】図 10 に示した F - F' 線および G - G' 線における模式断面図を横に並べて示した図である。

【図 12】実施例 1 の液晶表示パネルにおける 2 つの画素の別の選択例を示す模式平面図である。

【図 13】実施例 1 の液晶表示パネルにおける 2 つの画素の別の選択例を示す模式平面図である。

【図 14】実施例 1 の液晶表示パネルにおける 2 つの画素の別の選択例を示す模式平面図である。

【図 15】実施例 1 の液晶表示パネルに用いる TFT 基板の製造方法の一例を示すフロー図である。

40

【図 16】走査信号線の平面寸法の測定方法を説明するための模式断面図である。

【図 17】実施例 1 の TFT 基板の 1 画素の別の構成例を説明するための模式平面図である。

【図 18】1 枚のマザーガラスから 2 枚の TFT 基板を切り出す場合の導体膜の膜厚分布を示す模式平面図である。

【図 19】1 枚のマザーガラスから 4 枚の TFT 基板を切り出す場合の導体膜の膜厚分布を示す模式平面図である。

【図 20】1 枚のマザーガラスから 6 枚の TFT 基板を切り出す場合の導体膜の膜厚分布を示す模式平面図である。

50

【図21】1枚のマザーガラスから15枚のTFT基板を切り出す場合の導体膜の膜厚分布を示す模式図である。

【図22】1つめのパターンの膜厚分布における特定の3箇所の選択例を説明するための模式平面図である。

【図23】2つめのパターンの膜厚分布における特定の3箇所の選択例を説明するための模式平面図である。

【図24】3つめのパターンの膜厚分布における特定の3箇所の選択例を説明するための模式平面図である。

【図25】4つめのパターンの膜厚分布および特定の3箇所の選択例を説明するための模式図である。

10

【符号の説明】

【0149】

1 ... 基板 ( TFT 基板 )

2 ... 基板 ( 対向基板 )

3 ... 液晶材料

4 ... シール材

5 A , 5 B ... 偏光板

6 A ... 薄膜

6 B ... 透明導体膜

8 ... マザーガラス

S U B ... ガラス基板

20

G L<sub>1</sub> , G L<sub>m-1</sub> , G L<sub>m</sub> , G L<sub>m+1</sub> , G L<sub>u-1</sub> , G L<sub>u</sub> , G L<sub>M</sub> , G L ... 走査信号線

D L<sub>1</sub> , D L<sub>n</sub> , D L<sub>n+1</sub> , D L<sub>v</sub> , D L<sub>N</sub> , D L<sub>v+1</sub> , D L ... 映像信号線

S<sub>C</sub>H ... 半導体層 ( チャネル層 )

S D 1 ... ドレイン電極

S D 2 ... ソース電極

P A S 1 ... 第1の絶縁層

P A S 2 ... 第2の絶縁層

P X ... 画素電極

30

C S T 1 , C S T 2 ... 保持容量

S T L<sub>m</sub> ... 保持容量線

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図14】

【図13】

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【図21】

【図22】

【図23】

【図24】

【図25】

図25

---

フロントページの続き

(72)発明者 仲吉 良彰

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

Fターム(参考) 2H092 JA26 JB23 JB56 JB64 JB66 JB68 JB69 MA05 MA07 NA01

NA24

5C094 AA03 AA14 AA21 BA03 BA43 DA13 DA15 DA20 DB10 GB10

JA08

|                |                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 表示装置                                                                                                                                                                                                                                                                                                                           |         |            |

| 公开(公告)号        | <a href="#">JP2008129550A</a>                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2008-06-05 |

| 申请号            | JP2006317893                                                                                                                                                                                                                                                                                                                   | 申请日     | 2006-11-27 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                      |         |            |

| 申请(专利权)人(译)    | 日立显示器有限公司                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人         | 大原 健<br>大井田 淳<br>齐藤 裕<br>仲吉 良彰                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 大原 健<br>大井田 淳<br>齐藤 裕<br>仲吉 良彰                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G09F9/30 G02F1/1368                                                                                                                                                                                                                                                                                                            |         |            |

| F1分类号          | G09F9/30.338 G02F1/1368                                                                                                                                                                                                                                                                                                        |         |            |

| F-Term分类号      | 2H092/JA26 2H092/JB23 2H092/JB56 2H092/JB64 2H092/JB66 2H092/JB68 2H092/JB69 2H092/MA05 2H092/MA07 2H092/NA01 2H092/NA24 5C094/AA03 5C094/AA14 5C094/AA21 5C094/BA03 5C094/BA43 5C094/DA13 5C094/DA15 5C094/DA20 5C094/DB10 5C094/GB10 5C094/JA08 2H192/AA24 2H192/BC31 2H192/CB05 2H192/CC04 2H192/DA02 2H192/DA12 2H192/HA93 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                      |         |            |

### 摘要(译)

要解决的问题：减少形成在液晶显示面板的每个像素中的存储电容器的变化，并减小一个液晶显示面板的显示区域中的图像质量的面内变化。像素具有由一组多个像素设置的显示区域，并且每个像素由像素电极，经由像素电极和绝缘层设置的导体层以及绝缘层形成。一种显示装置，包括具有存储电容器的基板，其中，所述基板的像素电极和所述导体层在像素中的像素中重叠的区域的面积为S1，并且所述绝缘层的厚度介于所述重叠区域中。定义为PASD1，在不同于平面中的某个像素的像素中，像素电极和导电层重叠的基板区域的面积为S2，并且在重叠区域中插入的绝缘层的厚度为PASD2。然后，如果S1> S2，则显示设备为PASD1> PASD2。[选择图]图11