(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-276411

(P2006-276411A)

(43) 公開日 平成18年10月12日(2006.10.12)

(51) Int.CI.

**G02F 1/1368 (2006.01)**

**H01L 29/786 (2006.01)**

**H01L 21/336 (2006.01)**

F 1

**G02F 1/1368**

**H01L 29/78**    **612Z**

テーマコード(参考)

**2H092**

**5F11O**

審査請求 未請求 請求項の数 10 O L (全 27 頁)

(21) 出願番号

特願2005-94896 (P2005-94896)

(22) 出願日

平成17年3月29日 (2005.3.29)

(71) 出願人

000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人

100101214

弁理士 森岡 正樹

(72) 発明者

鎌田 豪

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通ディスプレイテクノロジーズ

株式会社内

(72) 発明者

田坂 泰俊

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通ディスプレイテクノロジーズ

株式会社内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】本発明は液晶表示装置に関し、良好な表示特性の得られる液晶表示装置を提供することを目的とする。

【解決手段】n本目のゲートバスラインに接続されたゲート電極とドレインバスラインに接続されたドレイン電極とをそれぞれ備えた第1及び第2のTFTと、第1のTFTのソース電極に接続された第1の画素電極と、第2のTFTのソース電極に接続された第2の画素電極と、(n+1)本目のゲートバスラインに接続されたゲート電極と第2の画素電極に接続されたソース電極とを備えた第3のTFTと、第1及び第2の画素電極と同層に形成され第3のTFTのドレイン電極23aに接続されたバッファ容量電極60と、蓄積容量バスラインに接続されたバッファ容量電極28とを備え、ドレイン電極23aと蓄積容量バスラインとの間を容量結合するバッファ容量部34とを有するように構成する。

【選択図】図8

## 【特許請求の範囲】

## 【請求項 1】

対向配置された一対の基板と、

前記基板間に封止された液晶層と、

一方の前記基板上に互いに並列して形成された複数のゲートバスラインと、

前記複数のゲートバスラインに絶縁膜を介して交差して形成された複数のドレインバス

ラインと、

前記ゲートバスラインに並列して形成された複数の蓄積容量バスラインと、

n 本目の前記ゲートバスラインに電気的に接続されたゲート電極と、前記ドレインバス

ラインに電気的に接続されたドレイン電極とをそれぞれ備えた第 1 及び第 2 のトランジス

タと、

前記第 1 のトランジスタのソース電極に電気的に接続された第 1 の画素電極と、

前記第 2 のトランジスタのソース電極に電気的に接続され、前記第 1 の画素電極から分

离された第 2 の画素電極と、

前記第 1 の画素電極が形成された第 1 の副画素と、前記第 2 の画素電極が形成された第

2 の副画素とを少なくとも備えた画素領域と、

(n + 1) 本目の前記ゲートバスラインに電気的に接続されたゲート電極と、前記第 2

の画素電極に接続されたソース電極と、前記蓄積容量バスラインに接続されたドレイン電

極とを備えた第 3 のトランジスタと、

前記第 3 のトランジスタのドレイン電極と前記蓄積容量バスラインとの間、又は前記第

3 のトランジスタのソース電極と前記第 2 の画素電極との間のいずれか一方を容量結合す

るバッファ容量部と

を有することを特徴とする液晶表示装置。

20

## 【請求項 2】

請求項 1 記載の液晶表示装置において、

前記バッファ容量部は、前記第 3 のトランジスタのドレイン電極に電気的に接続された

第 1 のバッファ容量電極と、前記第 1 のバッファ容量電極に対向して配置され、前記蓄積

容量バスラインに電気的に接続された第 2 のバッファ容量電極と、前記第 1 及び第 2 のバ

ッファ容量電極の間に配置された誘電体層とを有していること

を特徴とする液晶表示装置。

30

## 【請求項 3】

請求項 2 記載の液晶表示装置において、

前記第 1 のバッファ容量電極は、前記第 3 のトランジスタのドレイン電極と同層に形成

された第 1 のサブ電極と、前記第 1 又は第 2 の画素電極と同層に形成され、基板面に垂直

に見て前記第 1 のサブ電極に重なって配置され、前記第 1 のサブ電極に電気的に接続され

た第 2 のサブ電極とを有し、

前記バッファ容量部は、前記第 1 のサブ電極と前記第 2 のバッファ容量電極との間に形

成される容量 Cb1 と、前記第 2 のサブ電極と前記第 2 のバッファ容量電極との間に形

成される容量 Cb2 とを有すること

を特徴とする液晶表示装置。

40

## 【請求項 4】

請求項 2 記載の液晶表示装置において、

前記第 2 のバッファ容量電極は、前記蓄積容量バスラインと同層に形成された第 1 のサ

ブ電極と、前記第 1 又は第 2 の画素電極と同層に形成され、基板面に垂直に見て前記第 1

のサブ電極に重なって配置され、前記第 1 のサブ電極に電気的に接続された第 2 のサブ電

極とを有し、

前記バッファ容量部は、前記第 1 のサブ電極と前記第 1 のバッファ容量電極との間に形

成される容量 Cb1 と、前記第 2 のサブ電極と前記第 1 のバッファ容量電極との間に形

成される容量 Cb2 とを有すること

を特徴とする液晶表示装置。

50

**【請求項 5】**

請求項 2 記載の液晶表示装置において、

他方の前記基板上に形成された共通電極と、前記一対の基板間の間隔を維持する柱状スペーサとをさらに有し、

前記第 1 のバッファ容量電極に対向する領域の前記共通電極は、前記第 2 のバッファ容量電極として機能し、

前記柱状スペーサは、前記第 1 のバッファ容量電極の形成領域に形成され、前記誘電体層として機能すること

を特徴とする液晶表示装置。

**【請求項 6】**

請求項 2 記載の液晶表示装置において、

他方の前記基板上に形成された共通電極と、前記液晶を配向規制する絶縁性突起とをさらに有し、

前記第 1 のバッファ容量電極に対向する領域の前記共通電極は、前記第 2 のバッファ容量電極として機能し、

前記絶縁性突起の少なくとも一部は、前記第 1 のバッファ容量電極の形成領域に形成されていること

を特徴とする液晶表示装置。

**【請求項 7】**

請求項 2 記載の液晶表示装置において、

他方の前記基板上に形成された共通電極をさらに有し、

前記共通電極は、前記第 1 のバッファ容量電極に対向する領域の少なくとも一部で除去されていること

を特徴とする液晶表示装置。

**【請求項 8】**

請求項 2 記載の液晶表示装置において、

前記第 1 のバッファ容量電極は、前記第 1 又は第 2 の画素電極と同層に形成されていること

を特徴とする液晶表示装置。

**【請求項 9】**

請求項 2 記載の液晶表示装置において、

前記第 2 のバッファ容量電極は、前記第 1 又は第 2 の画素電極と同層に形成されていること

を特徴とする液晶表示装置。

**【請求項 10】**

請求項 2 記載の液晶表示装置において、

他方の前記基板上に形成された共通電極をさらに有し、

前記画素領域は、第 3 の画素電極が形成された第 3 の副画素をさらに有し、

前記第 3 の画素電極は、前記第 3 のトランジスタのドレイン電極に電気的に接続されて前記第 1 のバッファ容量電極としても機能し、

前記第 3 の画素電極に対向する領域の前記共通電極は、前記第 2 のバッファ容量電極としても機能すること

を特徴とする液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、電子機器の表示部等に用いられる液晶表示装置に関する。

**【背景技術】****【0002】**

近年、液晶表示装置は、テレビ受像機やパーソナル・コンピュータのモニタ装置等とし

10

20

30

40

50

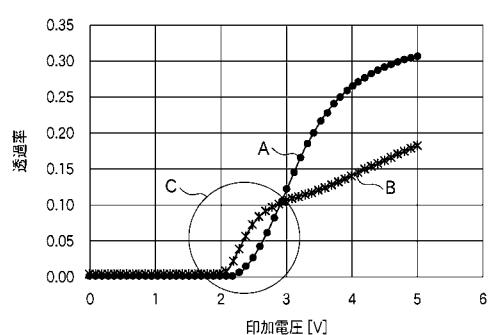

て用いられるようになっている。これらの用途では、表示画面をあらゆる方向から見ることのできる高い視角特性が求められている。図20は、VA(Vertically Aligned)モードの液晶表示装置の印加電圧に対する透過率特性(T-V特性)を示すグラフである。横軸は液晶層に対する印加電圧(V)を表し、縦軸は光の透過率を表している。線Aは表示画面に対し垂直な方向(以下、「正面方向」という)でのT-V特性を示し、線Bは表示画面に対して方位角90°、極角60°の方向(以下、「斜め方向」という)でのT-V特性を示している。ここで、方位角は、表示画面の右方向を基準として反時計回りに計った角度とする。また極角は、表示画面の中心に立てた垂線となす角とする。

#### 【0003】

図20に示すように、円Cで囲んだ領域近傍において、透過率(輝度)変化に歪みが生じている。例えば、印加電圧が約2.5Vの比較的低階調においては斜め方向の透過率が正面方向の透過率より高くなっているが、印加電圧が約4.5Vの比較的高階調においては斜め方向の透過率が正面方向の透過率より低くなっている。この結果、表示画面を斜め方向から見た場合には実効駆動電圧範囲での輝度差が小さくなってしまう。この現象は色の変化に最も顕著に現れる。

#### 【0004】

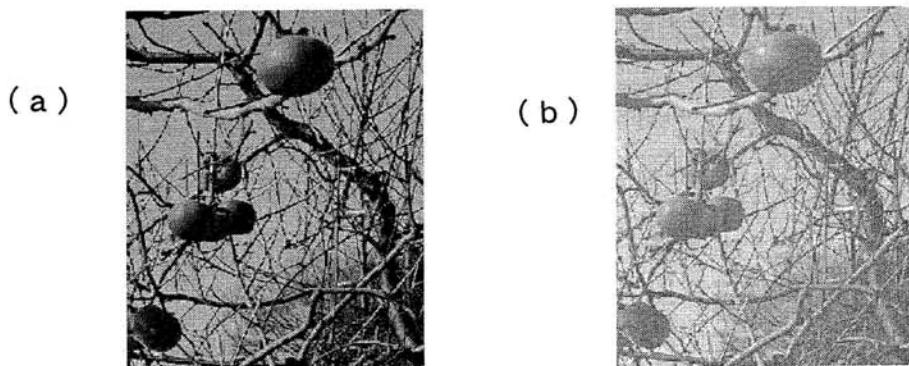

図21は表示画面に表示した画像の見え方の変化を示している。図21(a)は正面方向から見た画像を示し、図21(b)は斜め方向から見た画像を示している。図21(a)、(b)に示すように、表示画面を斜め方向から見ると、正面方向から見たときと比較して画像の色が白っぽく変化してしまう。

#### 【0005】

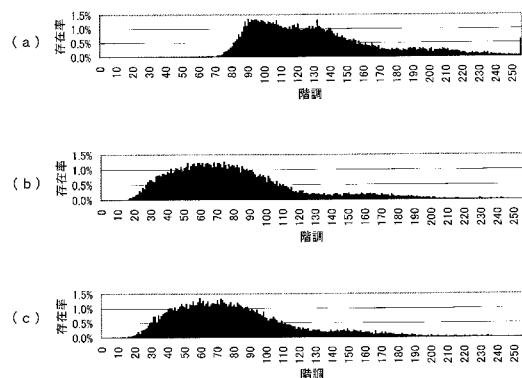

図22は、赤みがかった画像における赤(R)、緑(G)、青(B)3原色の階調ヒストグラムを示している。図22(a)はRの階調ヒストグラムを示し、図22(b)はGの階調ヒストグラムを示し、図22(c)はBの階調ヒストグラムを示している。図22(a)～(c)の横軸は階調(0～255の256階調)を表し、縦軸は存在率(%)を表している。図22(a)～(c)に示すように、この画像では比較的高階調のRと比較的低階調のG及びBとが高い存在率で存在している。このような画像をVAモードの液晶表示装置の表示画面に表示させて斜め方向から見ると、高階調のRが相対的に暗めに変化し、低階調のG及びBが相対的に明るめに変化する。これにより3原色の輝度差が小さくなるため、画面全体として色が白っぽくなる。

#### 【0006】

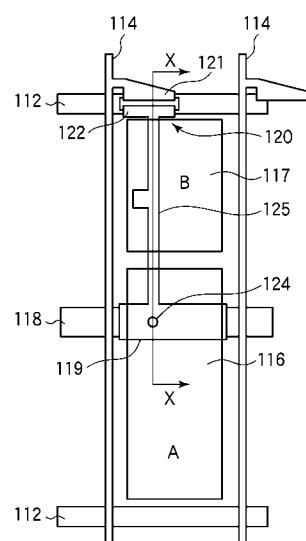

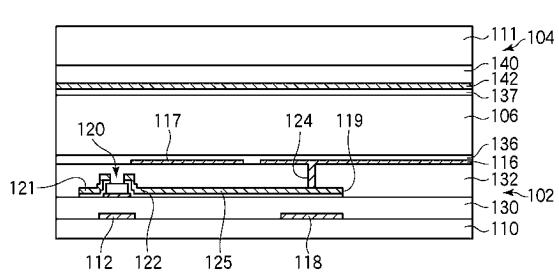

上記の現象は、従来型の駆動モードであるTN(Twisted Nematic)モードの液晶表示装置でも同様に生じる。特許文献1乃至3には、TNモードの液晶表示装置における上記の現象を改善する技術が開示されている。図23はこれらの公知技術に基づく基本的な液晶表示装置の1画素の構成を示し、図24は図23のX-X線で切断した液晶表示装置の断面構成を示し、図25はこの液晶表示装置の1画素の等価回路を示している。図23乃至図25に示すように、液晶表示装置は、薄膜トランジスタ(TFT)基板102と対向基板104と両基板102、104間に封止された液晶層106とを有している。

#### 【0007】

TFT基板102は、ガラス基板110上に形成された複数のゲートバスライン112と、絶縁膜130を介してゲートバスライン112に交差して形成された複数のドレインバスライン114とを有している。ゲートバスライン112及びドレインバスライン114の交差位置近傍には、スイッチング素子として画素毎に形成されたTFT120が配置されている。ゲートバスライン112の一部はTFT120のゲート電極として機能し、TFT120のドレイン電極121はドレインバスライン114に電気的に接続されている。また、ゲートバスライン112及びドレインバスライン114により画定された画素領域を横切って、ゲートバスライン112に並列して延びる蓄積容量バスライン118が形成されている。蓄積容量バスライン118上には、絶縁膜130を介して蓄積容量電極

10

20

30

40

50

119が画素毎に形成されている。蓄積容量電極119は、制御容量電極125を介してTFT120のソース電極122に電気的に接続されている。蓄積容量バスライン118、蓄積容量電極119、及びそれらの間に挟まれた絶縁膜130により蓄積容量Csが形成される。

#### 【0008】

ゲートバスライン112及びドレインバスライン114により画定された画素領域は、副画素Aと副画素Bとに分割されている。副画素Aには画素電極116が形成され、副画素Bには画素電極116から分離された画素電極117が形成されている。画素電極116は、コンタクトホール124を介して蓄積容量電極119及びTFT120のソース電極122に電気的に接続されている。一方、画素電極117は電気的にフローティング状態になっている。画素電極117は、保護膜132を介して制御容量電極125に重なる領域を有している。当該領域では、画素電極117、制御容量電極125、及びそれらの間の保護膜132により制御容量Ccが形成される。画素電極117は、制御容量Ccを介した容量結合によりソース電極122に間接的に接続されている。

#### 【0009】

対向基板104は、ガラス基板111上に形成されたカラーフィルタ(CF)樹脂層140と、CF樹脂層140上に形成された共通電極142とを有している。画素電極116と共に電極142と両電極116、142間に挟まれた液晶層106により副画素Aには液晶容量C1c1が形成され、画素電極117と共に電極142と両電極117、142間に挟まれた液晶層106により副画素Bには液晶容量C1c2が形成される。TFT基板102及び対向基板104の液晶層106との界面には、配向膜136、137がそれぞれ形成されている。

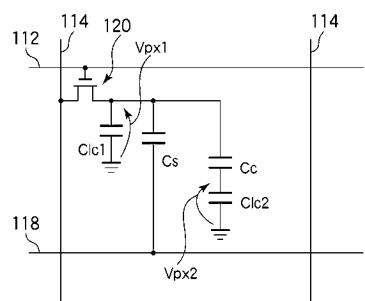

#### 【0010】

TFT120がオン状態になって画素電極116に電圧が印加され、副画素Aの液晶層106に電圧Vpx1が印加されるとする。このとき、液晶容量C1c2と制御容量Ccとの容量比に従って電位が分割されるため、副画素Bの画素電極117には画素電極116とは異なる電圧が印加される。副画素Bの液晶層106に印加される電圧Vpx2は、 $V_{px2} = (Cc / (C1c2 + Cc)) \times V_{px1}$

となる。実際の電圧比( $V_{px2} / V_{px1} (=Cc / (C1c2 + Cc))$ )は液晶表示装置の表示特性に基づく設計事項であるが、およそ0.6~0.8とするのが理想的である。

#### 【0011】

このように、液晶層106に印加される電圧が互いに異なる副画素A、Bが1画素内に存在すると、図20に示したようなT-V特性の歪みが副画素A、Bで分散される。このため、斜め方向から見たときに画像の色が白っぽくなる現象を抑制でき、視角特性が改善される。以下、上記の手法を容量結合HT(ハーフトーン・グレースケール)法とよぶ。

#### 【0012】

特許文献1乃至3ではTNモードの液晶表示装置を前提として上記の技術が記載されているが、近年TNモードに代わって主流となったVAモードの液晶表示装置に上記の技術を適用することによって、より高い効果が得られる。

#### 【0013】

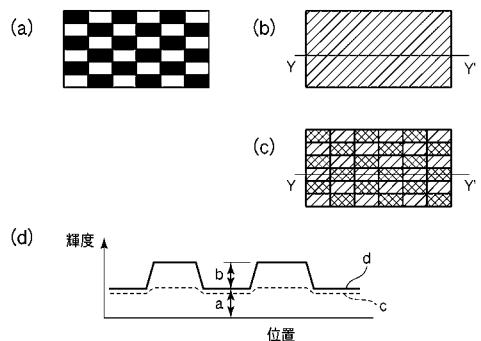

図26は、容量結合HT法を用いた従来の液晶表示装置に生じる焼付きを説明する図である。図26(a)は、焼付き試験の際に画面に表示する白黒のチェックパターンを示している。焼付き試験では、図26(a)に示すチェックパターンを一定時間(例えば48時間)連続表示させた直後に画面全体に同階調の中間調(32/64階調)を表示させて、チェックパターンが視認されるか否かを検査する。チェックパターンが視認された場合には、画面の輝度をチェックパターンの一方向に沿って測定し、焼付き率を算出する。ここで、視認されるチェックパターンのうち低輝度領域の輝度をaとし高輝度領域の輝度をa+b(>a)としたとき、b/aを焼付き率と定義した。

#### 【0014】

10

20

30

40

50

図26(b)は容量結合HT法を用いていない液晶表示装置に中間調を表示させた画面を示し、図26(c)は容量結合HT法を用いた従来の液晶表示装置に中間調を表示させた画面を示している。図26(b)に示すように、容量結合HT法を用いていない液晶表示装置では、中間調表示の際にチェックパターンはほとんど視認されなかつた。図26(b)のY-Y'線に沿って輝度を測定したところ、輝度は図26(d)の線cに示すような分布を有していた。焼付き率は0~5%に過ぎなかつた。これに対し、容量結合HT法を用いた液晶表示装置では、図26(c)に示すようなチェックパターンが視認された。図26(c)のY-Y'線に沿って輝度を測定したところ、輝度は図26(d)の線dに示すような分布を有していた。焼付き率は10%以上であった。このように、容量結合HT法を用いていない液晶表示装置では焼付きがほとんど発生しないのに対し、容量結合HT法を用いた液晶表示装置では比較的濃い焼付きが発生する。

10

### 【0015】

焼付きが発生した液晶表示装置の画素内の特性分布などを評価して解析した結果、焼付きは、電気的にフローティング状態の画素電極117の形成された副画素Bで発生していることが判明した。画素電極117は、極めて電気抵抗の高いシリコン窒化膜(SiN膜)等を介して制御容量電極125に接続され、また極めて電気抵抗の高い液晶層106を介して共通電極142に接続されている。このため、画素電極117に充電された電荷は容易に放電されないようになっている。一方、TFT120のソース電極122に電気的に接続された副画素Aの画素電極116にはフレーム毎に所定の電位が書き込まれ、かつ画素電極116は、SiN膜や液晶層に比較して極めて電気抵抗の低いTFT120の動作半導体層を介してドレインバスライン114に接続されている。このため、画素電極117に充電された電荷が放電されなくなることはない。

20

以上のように、容量結合HT法を用いた従来の液晶表示装置は、視角特性が向上するものの、焼付きが発生するため良好な表示特性が得られないという問題を有している。

### 【0016】

【特許文献1】特開平2-12号公報

【特許文献2】米国特許第4840460号明細書

【特許文献3】特許第3076938号公報

【特許文献4】特開2004-78157号公報

【特許文献5】特開2003-255303号公報

30

【発明の開示】

【発明が解決しようとする課題】

### 【0017】

本発明の目的は、良好な表示特性の得られる液晶表示装置を提供することにある。

【課題を解決するための手段】

### 【0018】

上記目的は、対向配置された一対の基板と、前記基板間に封止された液晶層と、一方の前記基板上に互いに並列して形成された複数のゲートバスラインと、前記複数のゲートバスラインに絶縁膜を介して交差して形成された複数のドレインバスラインと、前記ゲートバスラインに並列して形成された複数の蓄積容量バスラインと、n本目の前記ゲートバスラインに電気的に接続されたゲート電極と、前記ドレインバスラインに電気的に接続されたドレイン電極とをそれぞれ備えた第1及び第2のトランジスタと、前記第1のトランジスタのソース電極に電気的に接続された第1の画素電極と、前記第2のトランジスタのソース電極に電気的に接続され、前記第1の画素電極から分離された第2の画素電極と、前記第1の画素電極が形成された第1の副画素と、前記第2の画素電極が形成された第2の副画素とを少なくとも備えた画素領域と、(n+1)本目の前記ゲートバスラインに電気的に接続されたゲート電極と、前記第2の画素電極に接続されたソース電極と、前記蓄積容量バスラインに接続されたドレイン電極とを備えた第3のトランジスタと、前記第3のトランジスタのドレイン電極と前記蓄積容量バスラインとの間、又は前記第3のトランジスタのソース電極と前記第2の画素電極との間のいずれか一方を容量結合するバッファ容

40

50

量部とを有することを特徴とする液晶表示装置によって達成される。

**【発明の効果】**

**【0019】**

本発明によれば、良好な表示特性の得られる液晶表示装置を実現できる。

**【発明を実施するための最良の形態】**

**【0020】**

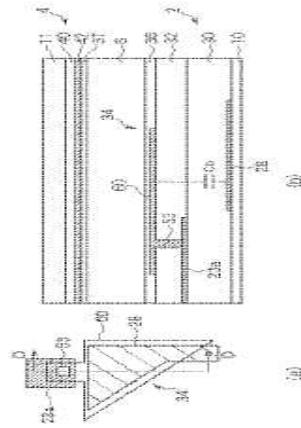

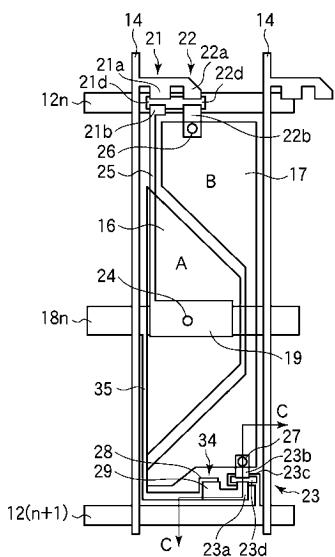

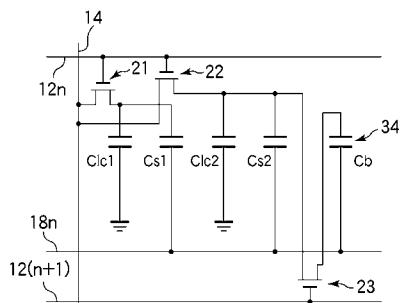

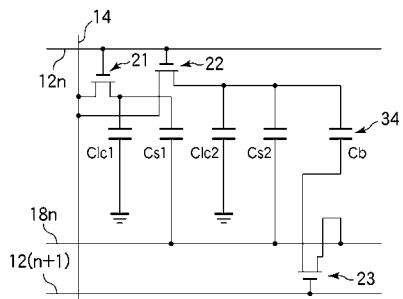

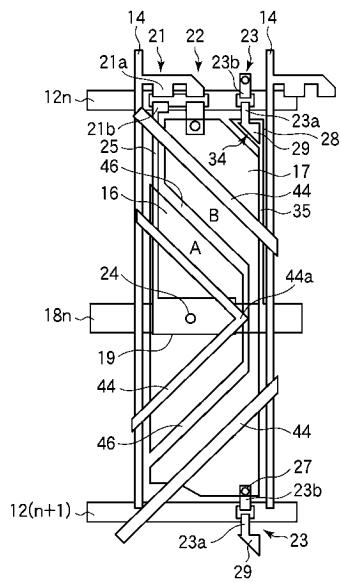

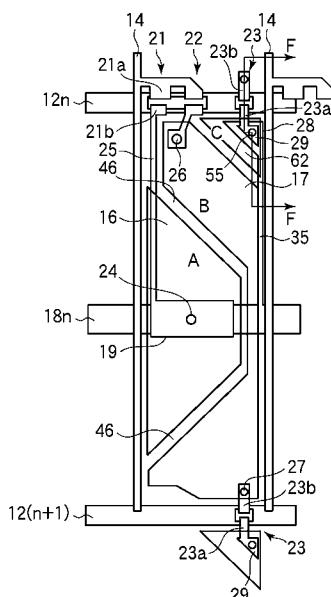

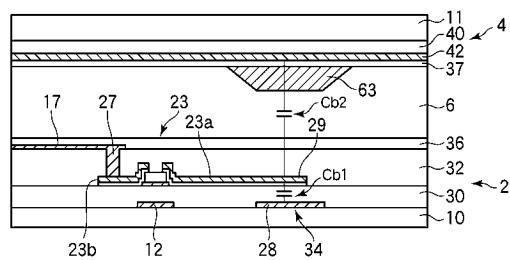

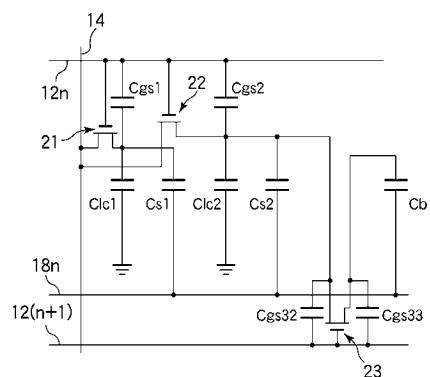

本発明の一実施の形態による液晶表示装置について図1乃至図19を用いて説明する。まず、本実施の形態の前提として、本願出願人による日本国特許出願（特願2004-323626号）に提案された液晶表示装置について説明する。図1は、上記特許出願に提案された液晶表示装置の1画素の構成を示している。図2は、図1のC-C線で切断した液晶表示装置の断面構成を示している。図3は、この液晶表示装置の1画素の等価回路を示している。図1乃至図3に示すように、TFT基板2は、ガラス基板10上に形成された複数のゲートバスライン12と、SiN膜等の誘電体からなる絶縁膜30を介してゲートバスライン12に交差して形成された複数のドレインバスライン14とを有している。ここで、複数のゲートバスライン12は例えば線順次走査され、図1及び図3では、n番目に走査されるn本目のゲートバスライン12nと、(n+1)番目に走査される(n+1)本目のゲートバスライン12(n+1)とを示している。ゲートバスライン12及びドレインバスライン14の交差位置近傍には、画素毎に形成された第1のTFT21及び第2のTFT22が互いに隣り合って配置されている。ゲートバスライン12の一部はTFT21、22のゲート電極として機能する。ゲートバスライン12上には、絶縁膜30を介してTFT21、22の動作半導体層（図示せず）が例えば一体的に形成されている。動作半導体層上にはチャネル保護膜21d、22dが例えば一体的に形成されている。TFT21のチャネル保護膜21d上には、ドレイン電極21a及びその下層のn型不純物半導体層（図示せず）と、ソース電極21b及びその下層のn型不純物半導体層（図示せず）とが所定の間隙を介して対向して形成されている。また、TFT22のチャネル保護膜22d上には、ドレイン電極22a及びその下層のn型不純物半導体層（図示せず）と、ソース電極22b及びその下層のn型不純物半導体層（図示せず）とが所定の間隙を介して互いに対向して形成されている。TFT21のドレイン電極21a及びTFT22のドレイン電極22aは、ドレインバスライン14にそれぞれ電気的に接続されている。TFT21のソース電極21b及びTFT22のソース電極22bは互いに分離されている。TFT21、22は並列に配置されている。TFT21、22上の基板全面には、SiN膜等の誘電体からなる保護膜32が形成されている。

**【0021】**

また、ゲートバスライン12及びドレインバスライン14により画定された画素領域を横切って、ゲートバスライン12に並列して延びる蓄積容量バスライン18が形成されている。図1及び図3では、ゲートバスライン12nとゲートバスライン12(n+1)との間に配置された蓄積容量バスライン18nを示している。蓄積容量バスライン18n上には、絶縁膜30を介して蓄積容量電極19が画素毎に形成されている。蓄積容量電極19は、接続電極25を介してTFT21のソース電極21bに電気的に接続されている。蓄積容量バスライン18n、蓄積容量電極19、及びとそれらの間に挟まれた絶縁膜30により第1の蓄積容量Cs1が形成される。

**【0022】**

ゲートバスライン12及びドレインバスライン14により画定された画素領域は、副画素Aと副画素Bとに分割されている。図1において、例えば台形状の副画素Aは画素領域の中央部左寄りに配置され、副画素Bは画素領域のうち副画素Aの領域を除いた上部、下部及び中央部右側端部に配置されている。画素領域内の副画素A、Bの配置は、例えば蓄積容量バスライン18nに対しほぼ線対称になっている。副画素Aには画素電極16が形成され、副画素Bには画素電極16から分離された画素電極17が形成されている。画素電極16、17は、共にITO等の透明導電膜により形成されている。高い視角特性を得るために、副画素Aに対する副画素Bの面積比が1/2以上4以下であることが望まし

10

20

30

40

50

い。画素電極 16 は、保護膜 32 が開口されたコンタクトホール 24 を介して、蓄積容量電極 19 及び TFT 21 のソース電極 21b に電気的に接続されている。画素電極 17 は、保護膜 32 が開口されたコンタクトホール 26 を介して TFT 22 のソース電極 22b に電気的に接続されている。また画素電極 17 は、保護膜 32 及び絶縁膜 30 を介して蓄積容量バスライン 18n に重なる領域を有している。当該領域では、蓄積容量バスライン 18n と画素電極 17 とそれらの間に挟まれた保護膜 32 及び絶縁膜 30 とにより第 2 の蓄積容量 C<sub>s</sub>2 が形成される。

#### 【 0 0 2 3 】

また、各画素領域の図 1 中下方には、第 3 の TFT 23 が配置されている。TFT 23 のゲート電極 23c は、当該画素の次段のゲートバスライン 12 (n+1) に電気的に接続されている。ゲート電極 23c 上には、絶縁膜 30 を介して動作半導体層 23e が形成されている。動作半導体層 23e 上には、チャネル保護膜 23d が形成されている。チャネル保護膜 23d 上には、ドレイン電極 23a 及びその下層の n 型不純物半導体層 23f と、ソース電極 23b 及びその下層の n 型不純物半導体層 23f とが所定の間隙を介して対向して形成されている。ソース電極 23b は、コンタクトホール 27 を介して画素電極 17 に電気的に接続されている。TFT 23 の近傍には、接続電極 35 を介して蓄積容量バスライン 18n に電気的に接続されたバッファ容量電極 28 が配置されている。バッファ容量電極 28 上には、絶縁膜 30 を介してバッファ容量電極 29 が配置されている。バッファ容量電極 29 は、ドレイン電極 23a に電気的に接続されている。互いに対向して配置されたバッファ容量電極 28、29、及びそれらの間に挟まれた絶縁膜 30 はバッファ容量部 34 を構成し、バッファ容量部 34 にはバッファ容量 C<sub>b</sub> (図 2 では C<sub>b</sub>1) が形成される。TFT 23 のドレイン電極 23a と蓄積容量バスライン 18nとの間には、バッファ容量 C<sub>b</sub> を介した容量結合により間接的に接続されている。このように、図 1 乃至図 3 に示す液晶表示装置は、画素毎に 3 つの TFT 21、22、23 が設けられている。以下、このような液晶表示装置の構造を「3 TFT ハーフトーン構造」ともいう。

#### 【 0 0 2 4 】

対向基板 4 は、ガラス基板 11 上に形成された CF 樹脂層 40 と、CF 樹脂層 40 上に形成され、蓄積容量バスライン 18 と同電位に維持される共通電極 42 とを有している。TFT 基板 2 と対向基板 4 との間には、例えば負の誘電率異方性を有する液晶が封止されて液晶層 6 が形成されている。副画素 A の画素電極 16、共通電極 42、及びそれらの間に挟まれた液晶層 6 により液晶容量 C<sub>1c</sub>1 が形成され、副画素 B の画素電極 17、共通電極 42、及びそれらの間に挟まれた液晶層 6 により液晶容量 C<sub>1c</sub>2 が形成される。TFT 基板 2 の液晶層 6 との界面には配向膜 (垂直配向膜) 36 が形成され、対向基板 4 の液晶層 6 との界面には配向膜 37 が形成されている。これにより、液晶層 6 の液晶分子は、電圧無印加時に基板面にほぼ垂直に配向する。

#### 【 0 0 2 5 】

容量結合 HT 法を用いた従来の液晶表示装置に比較的濃い焼付きが発生する要因は、副画素 B の画素電極が制御電極や共通電極に対してそれぞれ極めて高い電気抵抗を介して接続されるため、蓄えられた電荷が放電され難い点にある。これに対し、図 1 乃至図 3 に示す 3 TFT ハーフトーン構造の液晶表示装置では、副画素 B の画素電極 17 が TFT 22 を介してドレインバスライン 14 に接続されている。TFT 22 の動作半導体層の電気抵抗は、オフ状態であっても絶縁膜 30 や保護膜 32 等の電気抵抗よりも極めて低い。このため、画素電極 17 に蓄えられた電荷は容易に放電されるようになっている。したがって本実施の形態によれば、広視野角の得られるハーフトーン法を用いているのにもかかわらず、濃い焼付きが生じることがない。

#### 【 0 0 2 6 】

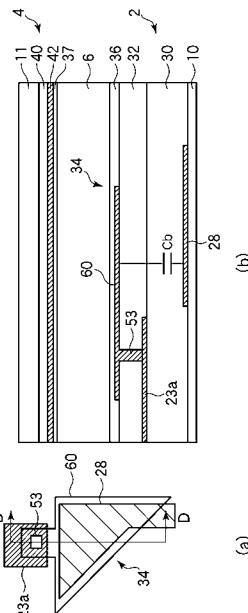

図 4 は、上記特許出願に提案された 3 TFT ハーフトーン構造の液晶表示装置の他の構成を示している。図 5 は、この液晶表示装置の 1 画素の等価回路を示している。図 4 及び図 5 に示すように、第 3 の TFT 23 のソース電極 23b は、バッファ容量電極 29 に電気的に接続されている。バッファ容量電極 29 は、副画素 B の画素電極 17 の一部の領域

10

20

30

40

50

に重なって配置されている。当該領域の画素電極 17 はバッファ容量部 34 の他方の電極として機能し、バッファ容量電極 29、画素電極 17、及びそれらの間に挟まれた保護膜 32 はバッファ容量部 34 を構成する。バッファ容量部 34 にはバッファ容量 Cb が形成される。なお画素電極 17 に電気的に接続されたバッファ容量電極を別途設け、当該バッファ容量電極とバッファ容量電極 29 とを誘電体層を介して重ねて配置してもよい。この場合、別途設けられたバッファ容量電極、バッファ容量電極 29、及びそれらの間に挟まれた誘電体層によりバッファ容量 Cb が形成される。画素電極 17 と TFT 23 のソース電極 23b とは、バッファ容量 Cb を介した容量結合により間接的に接続されている。

#### 【0027】

また、TFT 23 のドレイン電極 23a は、保護膜 32 を開口して形成されたコンタクトホール 50 を介して、繋ぎ替え電極 52 に電気的に接続されている。繋ぎ替え電極 52 は、画素電極 16、17 と同層に形成されている。繋ぎ替え電極 52 は、保護膜 32 及び絶縁膜 30 を開口して形成されたコンタクトホール 51 を介して、接続電極 35 及び蓄積容量バスライン 18n に電気的に接続されている。すなわち TFT 23 のドレイン電極 23a は、蓄積容量バスライン 18n に電気的に接続されている。

#### 【0028】

図 4 及び図 5 に示した液晶表示装置によても、図 1 乃至図 3 に示した液晶表示装置と同様の効果が得られる。ただし図 4 及び図 5 に示した液晶表示装置では、ドレイン電極 23a と接続電極 35 とを電気的に接続するために、繋ぎ替え電極 52 を用いた繋ぎ替えが必要になる。したがって、画素の開口率が若干低下する場合がある。

#### 【0029】

図 6 は、上記特許出願に提案された 3 TFT ハーフトーン構造の液晶表示装置のさらに他の構成を示している。図 1 乃至図 3 に示した液晶表示装置では、画素の開口率の低下によって輝度が低下してしまう場合もあり得る。開口率を低下させる最大の要因は TFT 23 にある。図 6 に示す液晶表示装置では、TFT 23 が次段のゲートバスライン 12(n+1) を跨ぐように配置される。これにより、画素領域内の TFT 23 の面積が減少し、開口率が向上する。

#### 【0030】

ただし、次段のゲートバスライン 12(n+1) を跨ぐように TFT 23 を配置すると、ドレイン電極 23a 又はソース電極 23b の一方が、隣接する次段の画素領域側に配置されることになる。例えばドレイン電極 23a 及びバッファ容量部 34 を次段の画素領域側に配置したとき、バッファ容量電極 28 と蓄積容量バスライン 18n との間を接続する接続電極 35 がゲートバスライン 12(n+1) を再度乗り越えるような構成にしてしまうと、これによって開口率の低下が生じてしまうので望ましくない。そこでバッファ容量電極 28 を、ゲートバスライン 12(n+1) とゲートバスライン 12(n+2) との間に配置された蓄積容量バスライン 18(n+1) に、接続電極 35 を介して接続する構成とした。蓄積容量バスライン 18 は全て同電位であるため、バッファ容量電極 28 を次段の蓄積容量バスライン 18(n+1) に接続しても何ら問題は生じない。

#### 【0031】

対向基板 4 上には、画素領域端部に対して斜めに延びる線状突起 44 が感光性樹脂等を用いて形成されている。線状突起 44 は、液晶の配向を規制する配向規制用構造物として機能する。また、配向規制用構造物として線状突起 44 の代わりに共通電極 42 にスリットが設けられていてもよい。画素電極 16 と画素電極 17 とを分離する線状のスリット 46 は、線状突起 44 に並列し、画素領域端部に対して斜めに延びている。スリット 46 は、TFT 基板 2 側の配向規制用構造物としても機能する。

#### 【0032】

ここで、3 TFT ハーフトーン構造の液晶表示装置に生じ得る問題点について説明する。図 23 乃至図 25 に示した容量結合 HT 法を用いた従来の液晶表示装置では、TFT 20 がオン状態になったときに、液晶容量 Clc と制御容量 Cc との容量比に従って電位が分割されることを利用して画素電極 116、117 の電位を異ならせている。これに対

10

20

30

40

50

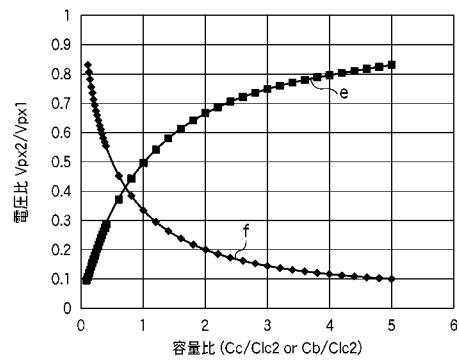

し、3 TFT ハーフトーン構造の液晶表示装置では、ゲートバスライン 12 n が選択状態になって TFT 21、22 がオン状態になると、副画素 A、B の各液晶容量  $C_{1c1}$ 、 $C_{1c2}$  に一旦同じ電圧が印加される。その後、次段のゲートバスラインが選択状態になって第 3 の TFT 23 がオン状態になると、副画素 B の液晶容量  $C_{1c2}$  に蓄えられた電荷がバッファ容量  $C_b$  に移動することにより副画素 B の液晶容量  $C_{1c2}$  の電圧が低下し、副画素 A の液晶容量  $C_{1c1}$  の電圧と副画素 B の液晶容量  $C_{1c2}$  の電圧とに差が生じる。したがって、容量比と電圧比との関係は、容量結合 HT 法を用いた液晶表示装置と 3 TFT ハーフトーン構造の液晶表示装置とで全く異なる。

#### 【0033】

図 7 は、3 TFT ハーフトーン構造の液晶表示装置及び容量結合 HT 法を用いた液晶表示装置における容量比の変化に対する電圧比の変化を示すグラフである。横軸は、容量結合 HT 法を用いた液晶表示装置における制御容量  $C_c$  と液晶容量  $C_{1c2}$  との容量比  $C_c / C_{1c2}$ 、又は 3 TFT ハーフトーン構造の液晶表示装置におけるバッファ容量  $C_b$  と液晶容量  $C_{1c2}$  との容量比  $C_b / C_{1c2}$  を表している。縦軸は、副画素 A の液晶層に印加される電圧  $V_{px1}$  及び副画素 B の液晶層に印加される電圧  $V_{px2}$  の電圧比  $V_{px2} / V_{px1}$  を表している。線 e は、容量結合 HT 法を用いた液晶表示装置の電圧比の変化を示し、線 f は、3 TFT ハーフトーン構造の液晶表示装置の電圧比の変化を示している。液晶の誘電率の変化により液晶容量  $C_{1c2}$  は印加電圧が低いほど小さく、印加電圧が高いほど大きくなるため、容量比  $C_c / C_{1c2}$  又は  $C_b / C_{1c2}$  の大きくなるグラフ右側は低電圧を印加した状態を表し、容量比  $C_c / C_{1c2}$  又は  $C_b / C_{1c2}$  の小さくなるグラフ左側は高電圧を印加した状態を表している。

10

20

#### 【0034】

画素を 2 つの副画素 A、B に 2 分割する場合、最適な電圧比  $V_{px2} / V_{px1}$  は 0.6 ~ 0.8 程度である。例えば電圧比  $V_{px2} / V_{px1}$  を 0.7 にするためには、容量結合 HT 法を用いた液晶表示装置では容量比  $C_c / C_{1c2}$  を 2.5 程度にする必要があった。すなわち容量結合 HT 法を用いた液晶表示装置では、制御容量  $C_c$  を液晶容量  $C_{1c2}$  のおよそ 2.5 倍と非常に大きい値にする必要があった。ただし、制御容量  $C_c$  は画素電極 17 の下層に形成できるため、輝度に貢献しない配向規制用の突起などと重ねて配置することにより開口率の低下はさほど生じない。また、制御容量電極 125 のパターンサイズは大きいため、パターニングの際に寸法ずれが生じても電圧比が大きく変化することはなく、表示むらが視認されることは少ない。

30

#### 【0035】

これに対して、3 TFT ハーフトーン構造の液晶表示装置では、液晶容量  $C_{1c2}$  のわずか 20% という小さなバッファ容量  $C_b$  ( $C_b / C_{1c2} = 0.2$ ) を設けることにより、電圧比  $V_{px2} / V_{px1}$  を 0.7 にすることができる。バッファ容量  $C_b$  の誘電体層となる絶縁膜 30 は、TFT のゲート電極のすぐ上層であるゲート絶縁膜と同層である。TFT の特性を安定化するためには、絶縁膜 30 (ゲート絶縁膜) の膜厚や誘電率を変えることは容易ではない。ところが 3 TFT ハーフトーン構造の液晶表示装置で必要なバッファ容量  $C_b$  は比較的小さいため、結果的に図 1、図 4 及び図 6 に示すように、極めて小さい電極面積のバッファ容量電極 28、29 を用いて十分な大きさのバッファ容量  $C_b$  が得られる。画素ピッチ (隣り合うドレインバスライン 14 間の間隔) が 100 μm 以下の比較的小さい画素を備えた液晶表示装置では、電極面積が小さい点は開口率の低下を抑制できるため有利であるが、その一方でわずかなパターン寸法のずれでバッファ容量  $C_b$  が大きく変動するため表示むらが視認され易いという欠点ともなる。

40

#### 【0036】

また図 2 に示すように、バッファ容量  $C_b$  は、バッファ容量電極 28、29 とそれらの間に挟まれた絶縁膜 30 とにより形成される容量  $C_{b1}$  だけではない。バッファ容量電極 29、共通電極 42、及びそれらの間に挟まれた液晶層 6 や保護膜 32 等により形成される容量  $C_{b2}$  も容量  $C_{b1}$  に並列に接続されている ( $C_b = C_{b1} + C_{b2}$ )。ほぼ一定の値である容量  $C_{b1}$  に対して、液晶層 6 の誘電率や厚さ (セル厚) が変動するため容

50

量  $C_{b2}$  は一定ではない。液晶層 6 の厚さと絶縁膜 30 の膜厚とが大きく異なるため容量  $C_{b2}$  は容量  $C_{b1}$  の 1 / 10 程度であるものの、容量  $C_{b2}$  の変動によりバッファ容量  $C_b$  が変動する。したがって、表示むらが視認され易いという問題が生じ得る。

#### 【0037】

一方、画素ピッチが 150  $\mu\text{m}$  を超えるような比較的大きい画素を備えたテレビ受像機向け等の液晶表示装置では、バッファ容量電極 28、29 のパターンサイズが比較的大きくなるため、パターニングの際に寸法のずれが生じてもバッファ容量  $C_b$  の変動は比較的小さく、表示むらが視認され難い。しかしその一方で、バッファ容量電極 28、29 による開口率への影響が無視できなくなる。バッファ容量  $C_b$  は既存の副画素 A、B とは独立して存在させる必要があるため、重ねて配置して開口率を向上させることはできない。

10

#### 【0038】

3 TFT ハーフトーン構造の液晶表示装置に生じ得る問題点をまとめると、以下のようになる。

(1) 画素サイズの小さい液晶表示装置では、バッファ容量  $C_b$  を安定して形成するのが困難であるため、表示むらが視認され易い。

(2) 画素サイズの大きい液晶表示装置では、バッファ容量電極 28、29 の電極面積が大きくなるため、画素の開口率を向上させるのが困難である。

#### 【0039】

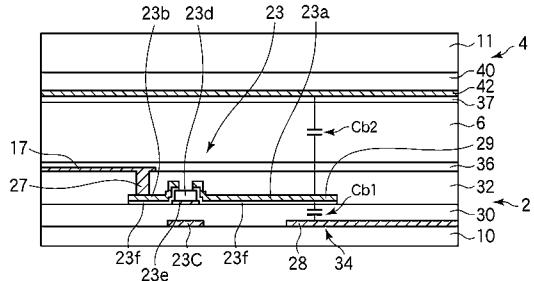

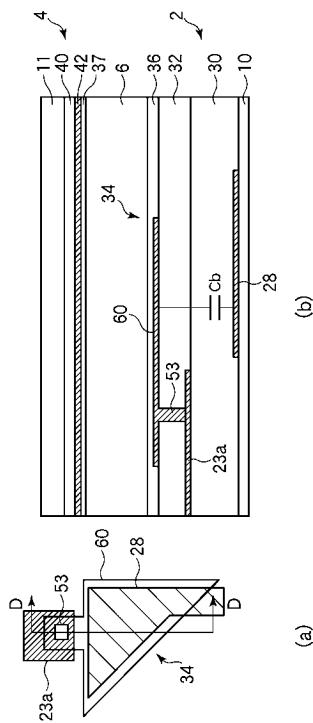

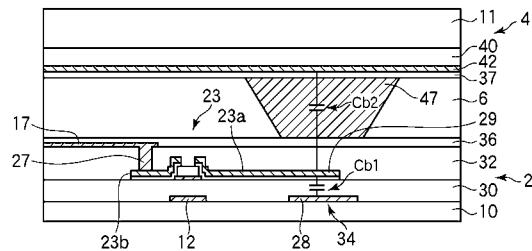

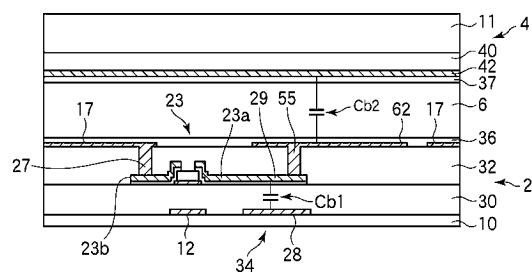

まず、上記の問題点(1)を解決する本実施の形態の第1乃至第3の原理について説明する。図8は、本実施の形態の第1の原理を示している。図8(a)はバッファ容量部34近傍の構成を示し、図8(b)は図8(a)のD-D線で切断した液晶表示装置の断面構成を示している。なお、この液晶表示装置は、バッファ容量部34の構成を除き、図6に示した液晶表示装置とほぼ同様の構成を有している。図8(a)、(b)に示すように、画素電極16、17と同層に形成され、コンタクトホール53を介して第3のTFT23のドレイン電極23aに電気的に接続されたバッファ容量電極60と、蓄積容量バスライン18と同層に形成されてバッファ容量電極60に重なって配置され、蓄積容量バスライン18に電気的に接続されたバッファ容量電極28と、それらの間に挟まれた絶縁膜30及び保護膜32によりバッファ容量  $C_b$  が形成されている。

20

#### 【0040】

この構成では、絶縁膜30及び保護膜32の2層がバッファ容量  $C_b$  の誘電体層となっている。したがって、誘電体層の厚さが厚くなるため、バッファ容量  $C_b$  の単位面積あたりの容量が小さくなる。これにより、バッファ容量  $C_b$  を形成するバッファ容量電極28、60の電極面積を大きくすることになる。電極面積が大きければ寸法のずれに対する許容誤差(マージン)が増加する。また、前述のようにTFTの特性を安定化するためには絶縁膜30(ゲート絶縁膜)の膜厚などを変えることは困難であるが、TFTのソース電極と画素電極との間に設けられる保護膜32は、層間絶縁が目的であるため膜厚や誘電率を比較的自由に調整できる。したがって、保護膜32の膜厚を必要なだけ厚くして、バッファ容量電極28、60の寸法ずれに対する許容誤差を大きくする設計が可能となる。

30

#### 【0041】

図9は、本実施の形態の第2の原理を示している。図9では、第3のTFT23及びバッファ容量部34近傍の断面構成を示している。図9に示すように、バッファ容量電極29の形成された領域には、液晶層6を排除するように所定の高さの樹脂層が設けられる。樹脂層として、例えばセル厚を規定するための柱状スペーサ47を形成するのが望ましい。バッファ容量電極29と、バッファ容量電極29に対向する領域の共通電極42と、柱状スペーサ47等の誘電体層とにより容量  $C_{b2}$  が形成される。

40

#### 【0042】

この構成では、バッファ容量部34の液晶層6が柱状スペーサ47によって排除されるため容量  $C_{b2}$  が変動せず、バッファ容量  $C_b$  (=  $C_{b1} + C_{b2}$ ) が安定化する。また、バッファ容量電極28、29が形成される領域に柱状スペーサ47を形成することによって、開口率の低下が抑えられる。

50

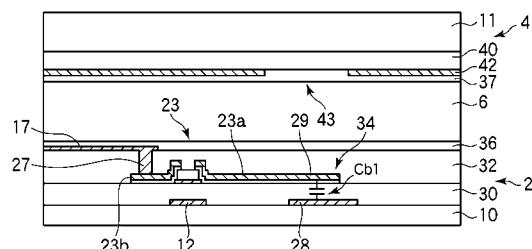

## 【0043】

図10は、本実施の形態の第3の原理を示している。図10に示すように、バッファ容量電極29の形成された領域の少なくとも一部には、共通電極42が部分的に除去された開口部43が形成されている。この構成では、バッファ容量電極29に対向する位置の共通電極42を除去することにより、液晶層6を介した容量Cb2がほとんど形成されなくなるため、バッファ容量Cb(Cb1)が安定化する。

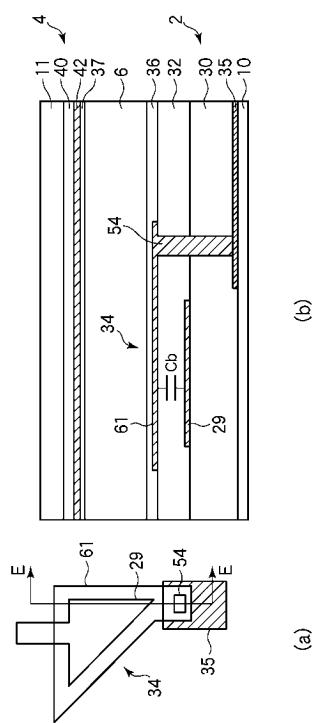

## 【0044】

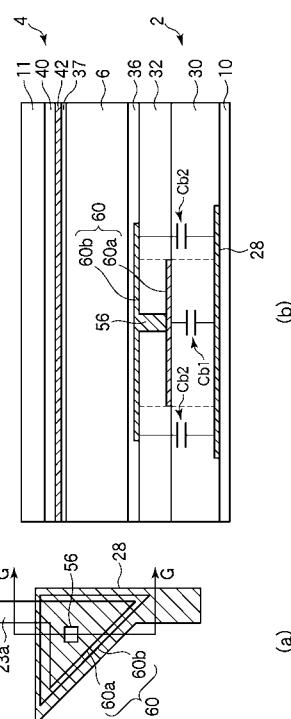

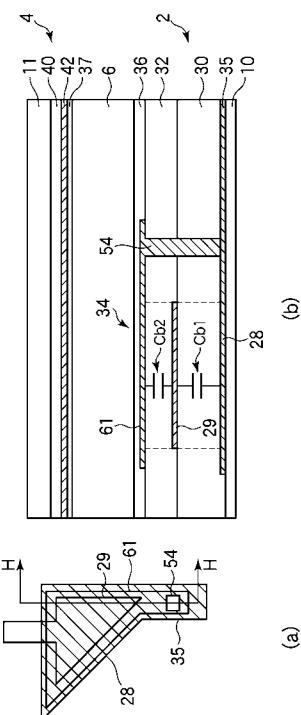

次に、上記の問題点(2)を解決する本実施の形態の第4及び第5の原理について説明する。図11は、本実施の形態の第4の原理を示している。図11(a)はバッファ容量部34近傍の構成を示し、図11(b)は図11(a)のE-E線で切断した液晶表示装置の断面構成を示している。図11(a)、(b)に示すように、画素電極16、17と同層に形成され、コンタクトホール54を介して接続電極35及び蓄積容量バスライン18に電気的に接続されたバッファ容量電極61と、TFT23のドレイン電極23aと同層に形成されてバッファ容量電極61に重なって配置され、ドレイン電極23aに電気的に接続されたバッファ容量電極29と、それらの間に挟まれた保護膜32とによりバッファ容量Cbが形成されている。

## 【0045】

この構成では、保護膜32がバッファ容量Cbの誘電体層となっている。前述のように、絶縁膜30に比較して保護膜32の膜厚を変えるのは容易である。したがって、保護膜32の膜厚を絶縁膜30より薄くすることができ、これによりバッファ容量電極29、61の電極面積が同一であってもバッファ容量Cbを大きくできる。また、バッファ容量Cbが同一であればバッファ容量電極29、61の電極面積を小さくできる。したがって、画素の開口率が向上する。

## 【0046】

図12及び図13は、本実施の形態の第5の原理を示している。図12は画素の構成を示し、図13は図12のF-F線で切断した液晶表示装置の断面構成を示している。図12及び図13に示すように、画素電極16、17と同層に形成され、コンタクトホール55を介してバッファ容量電極29に電気的に接続された画素電極62が形成されている。画素電極62の形成された領域は、副画素Cとして表示に寄与する。また画素電極62及びそれに対向する領域の共通電極42は、バッファ容量電極としても機能する。画素電極62、共通電極42、及びそれらの間に挟まれた液晶層6等により、容量Cb1に並列に接続される容量Cb2が形成される。

## 【0047】

この構成では、バッファ容量Cbの一部となる容量Cb2が液晶層6を誘電体層として形成される。液晶層6の厚さは絶縁膜30や保護膜32の膜厚の10倍程度であるため、電極面積を大きくする必要がある。しかしながら、画素電極62の形成された領域は副画素Cとして表示に寄与するため、画素の開口率が向上する。

以下、本実施の形態による液晶表示装置について、実施例を用いてより具体的に説明する。

## 【0048】

## (実施例1)

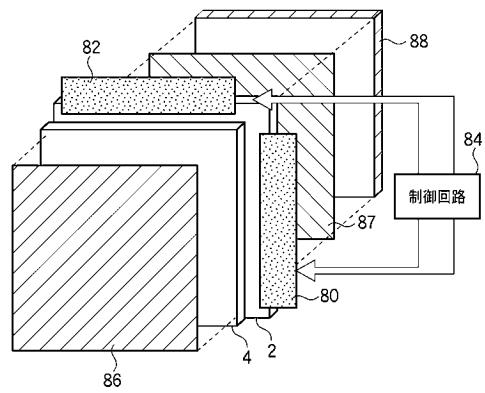

本実施の形態の実施例1による液晶表示装置について説明する。図14は、本実施の形態による液晶表示装置の概略構成を示している。図14に示すように、液晶表示装置は、TFT基板2と、対向基板4と、両基板2、4間に封止された液晶層6(図14では図示せず)とを有している。

## 【0049】

TFT基板2には、複数のゲートバスラインを駆動するドライバICが実装されたゲートバスライン駆動回路80と、複数のドレインバスラインを駆動するドライバICが実装されたドレインバスライン駆動回路82とが接続されている。これらの駆動回路80、82は、制御回路84から出力された所定の信号に基づいて、走査信号やデータ信号を所定

のゲートバスラインあるいはドレインバスラインに出力するようになっている。TFT基板2のTFT素子形成面と反対側の面には偏光板87が配置され、対向基板4の共通電極形成面と反対側の面には、偏光板87とクロスニコルに配置された偏光板86が配置されている。偏光板87のTFT基板2と反対側の面にはバックライトユニット88が配置されている。

#### 【0050】

本実施例では、図8に示した第1の原理に基づいて、絶縁膜30及び保護膜32の2層を誘電体層とするバッファ容量部34を形成した。絶縁膜30の膜厚を350nmとし、保護膜32の膜厚を350nmとした。単位面積あたりの容量は、絶縁膜30又は保護膜32のいずれか1層のみを誘電体層としたときと比べて約1/2となるため、バッファ容量電極の電極面積は約2倍となる。これにより、バッファ容量電極の寸法ずれに対する許容誤差が約2倍に拡大する。

#### 【0051】

図15(a)は本実施例による液晶表示装置のバッファ容量部34の構成の変形例を示し、図15(b)は図15(a)のG-G線で切断した液晶表示装置の断面構成を示している。図15(a)、(b)に示すように、バッファ容量電極60は、TFT23のドレイン電極23aに電気的に接続され、ドレイン電極23aと同層に形成されたサブ電極60aと、基板面に垂直に見てサブ電極60aに重なって配置され、コンタクトホール56を介してサブ電極60aに電気的に接続され、画素電極16、17と同層に形成されたサブ電極60bとを有している。サブ電極60a、60b、バッファ容量電極28を基板面に垂直に見ると、サブ電極60aが最も内側に配置され、バッファ容量電極28が最も外側に配置されている。サブ電極60a、60b、及びバッファ容量電極28が形成された領域では、サブ電極60a、バッファ容量電極28、及びそれらの間に挟まれた絶縁膜30により容量Cb1が形成される。サブ電極60aより外側であってサブ電極60b及びバッファ容量電極28だけが形成された領域では、サブ電極60bと、バッファ容量電極28と、それらの間に挟まれた絶縁膜30及び保護膜32により容量Cb2が形成される。容量Cb1、Cb2の和がバッファ容量Cbとなる。

#### 【0052】

パターニングの際に、サブ電極60a、60b、及びバッファ容量電極28に寸法ずれが生じた場合を考える。最も外側のバッファ容量電極28に寸法ずれが生じてもバッファ容量Cbは変動しない。最も内側のサブ電極60aが小さくパターニングされた場合、容量Cb1が減少するものの容量Cb2は増加する。逆に、サブ電極60aが大きくパターニングされた場合、容量Cb1が増加するものの容量Cb2は減少する。このため、バッファ容量Cbに対する影響は緩和される。

#### 【0053】

サブ電極60bに寸法ずれが生じた場合、容量Cb2が変動する。しかしながら、容量Cb2は絶縁膜30及び保護膜32の2層を誘電体として形成され、絶縁膜30及び保護膜32の2層の膜厚は当然に絶縁膜30の膜厚より厚い。つまり、サブ電極60bとバッファ容量電極28との間の間隔は、サブ電極60aとバッファ容量電極28との間隔より広い。このため、容量Cb2の変動は、絶縁膜30だけを誘電体として形成される容量Cb1の変動ほどの影響はない。サブ電極60a、60bが共に小さくパターニングされるか、又は共に大きくパターニングされた場合の影響は従来と変わらないが、プロセス的に同時に同方向の変動が起きる可能性は小さいので結果的にリスクが回避される。本変形例では、図8に示した構成のようにバッファ容量電極28、60を大きくする必要がないため、開口率の低下を抑制でき、かつ製造マージンを拡大することができる。なお、バッファ容量電極28ではなくサブ電極60bを最も外側に配置しても同様の効果が得られる。以上のように本実施例によれば、3TFTハーフトーン構造の液晶表示装置に生じ得る問題点(1)を解決することができる。

#### 【0054】

(実施例2)

10

20

30

40

50

本実施の形態の実施例2による液晶表示装置について説明する。本実施例では、既に図9に示したように、バッファ容量部34の形成領域に柱状スペーサ47を配置する。液晶の誘電率は配向状態や電圧印加状態によって変動するためバッファ容量Cb(Cb2)の変動要因となってしまうが、本実施例ではバッファ容量部34の液晶が柱状スペーサ47により排除されるため容量Cb2が安定化する。また、バッファ容量部34のバッファ容量電極28、29は、通常遮光性を有する金属により形成される。このためバッファ容量部34の形成領域は表示に寄与せず、開口率を低下させる要因となる。本実施例では、同様に開口率を低下させる要因となり得る柱状スペーサ47をバッファ容量部34の形成領域に重ねて形成することにより、開口率低下を抑えられる効果もある。

## 【0055】

10

図16は、本実施例による液晶表示装置の構成の変形例を示している。本変形例では、柱状スペーサ47ではなく、MVA方式で液晶の配向を規制する配向規制用構造物として用いられる絶縁性突起63の少なくとも一部をバッファ容量部34の形成領域の対向基板4側に配置する。本変形例ではバッファ容量部34の形成領域での液晶が完全に除かれるわけではないが、絶縁性突起63での電圧降下分だけ液晶層6への印加電圧が低下するため、容量Cbの変動を抑えることができる。

## 【0056】

20

図10に示した構成も本実施例の他の変形例として用いることができる。本変形例では、柱状スペーサ47ではなく、配向規制用構造物として用いられるスリット等の開口部43をバッファ容量部34の形成領域の対向基板4側に配置する。本変形例ではバッファ容量部34の形成領域での液晶の存在は変わらないが、共通電極42が除去されているため液晶層6に電圧が印加されなくなり、容量Cbの変動を抑えることができる。以上のように本実施例によれば、TFTハーフトーン構造の液晶表示装置に生じ得る問題点(1)を解決することができる。

## 【0057】

## (実施例3)

本実施例では、図11に示した第4の原理に基づいて、画素電極16、17と同層に形成され、コンタクトホール54を介して接続電極35及び蓄積容量バスライン18に電気的に接続されたバッファ容量電極61と、バッファ容量電極61に重なって配置され、TFT23のドレイン電極23aから引き出されたバッファ容量電極29と、それらの間に挟まれた保護膜32とによりバッファ容量Cbを形成した。絶縁膜30に比較して保護膜32の膜厚を変えるのは比較的容易であるため、本実施例では絶縁膜30の膜厚を350nmとし、保護膜32の膜厚をそれより薄い150nmとした。これにより、絶縁膜30を誘電体層として用いた場合と比較して、同一の電極面積で2.3倍( $=350/150$ )のバッファ容量Cbを形成することができた。

30

## 【0058】

40

図17は、本実施例による液晶表示装置のバッファ容量部34の構成の変形例を示している。図17(a)はバッファ容量部34の構成を示し、図17(b)は図17(a)のH-H線で切断した断面構成を示している。本変形例では、図11に示す構成と同様にバッファ容量電極29、61及び保護膜32により容量Cb2が形成されるのに加え、バッファ容量電極29と、蓄積容量バスライン18から引き出されてバッファ容量電極29に重なって配置されたバッファ容量電極28と、それらの間に挟まれた絶縁膜30により容量Cb1が容量Cb2に並列に形成される。互いに同電位の2つのバッファ容量電極(サブ電極)28、61で、それらの間の層に形成されたバッファ容量電極29を上下から挟むことによって、バッファ容量Cbが容量Cb1、Cb2の和になり、さらに効率的になる。絶縁膜30の膜厚を350nmとし、保護膜32の膜厚を150nmとすると、絶縁膜30のみを誘電体層として用いた場合と比較して、同一の電極面積で3.3倍( $=350/150+1$ )のバッファ容量Cbを形成することができた。

## 【0059】

バッファ容量電極28、29、61を基板面に垂直に見ると、バッファ容量電極29は

50

バッファ容量電極 28、61よりも内側に配置されている。これにより、バッファ容量電極 28、61に寸法ずれが生じても、バッファ容量  $C_b$  が変動しないようになっている。以上のように本実施例によれば、3 TFT ハーフトーン構造の液晶表示装置に生じ得る問題点(1)、(2)を解決することができる。

#### 【0060】

##### (実施例4)

図12及び図13に示した構成は、画素電極16、17と同層の画素電極(バッファ容量電極)62を大きく形成し、液晶層6を誘電体層としてバッファ容量  $C_b$  の一部となる容量  $C_{b2}$  を形成する。この構成は、構造的には図8に示した構成と類似している。液晶層6の厚さは絶縁膜30や保護膜32の膜厚の10倍程度であるため、同程度の容量を得るためににはおよそ10倍の電極面積が必要となるため効率的ではない。しかし本例では、画素電極62の形成された領域が副画素Cとして表示に寄与するため、画素の開口率が大幅に向上する。

#### 【0061】

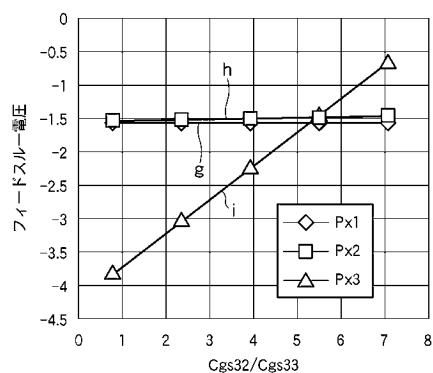

ただし、画素電極62の形成領域を副画素Cとして利用するためには、フィードスルー電圧を他の副画素A、Bと一致させる必要がある。フィードスルー電圧は、一般的にTFTのゲート電極-画素電極間の寄生容量  $C_{gs}$  と液晶容量  $C_{lc}$ との比で決まる。図18は、本実施例による液晶表示装置の1画素の等価回路図である。図18に示すように、4つの寄生容量  $C_{gs1}$ 、 $C_{gs2}$ 、 $C_{gs32}$ 、 $C_{gs33}$ が存在することが分かる。図19は、これらの寄生容量  $C_{gs}$  の値について検討した結果を示すグラフである。グラフの横軸は寄生容量  $C_{gs32}$ 、 $C_{gs33}$ の比( $C_{gs32}/C_{gs33}$ )を表し、縦軸はフィードスルー電圧を表している。線gは副画素A( $P \times 1$ )のフィードスルー電圧を示し、線hは副画素B( $P \times 2$ )のフィードスルー電圧を示し、線iは副画素C( $P \times 3$ )のフィードスルー電圧を示している。図19に示すように、副画素Cのフィードスルー電圧を他の副画素A、Bと一致させるには、TFT23の副画素B(画素電極17)に対する寄生容量  $C_{gs32}$ とTFT23の副画素C(画素電極62)に対する寄生容量  $C_{gs33}$ との比Y( $= C_{gs32}/C_{gs33}$ )を5~6程度にすればよいことが分かった。すなわち、寄生容量  $C_{gs32}$ 、 $C_{gs33}$ の比Yと、副画素Bの液晶容量  $C_{lc2}$ 及び蓄積容量  $C_{s2}$ の和とバッファ容量  $C_b$ との比X( $= (C_{lc2} + C_{s2})/C_b$ )とをほぼ等しくすればよいことになる( $C_{gs32}/C_{gs33} = (C_{lc2} + C_{s2})/C_b$ )。これにより、副画素A、B、Cの液晶層にそれぞれ印加される電圧(例えばフレーム毎に極性が反転する)の中心電圧の差はほぼ0.1V以下となる。

#### 【0062】

また他の手法として、副画素Bの画素電極17の電位と副画素Cの画素電極62の電位とが1フレーム期間内に等しくなるような十分なオフリーステート抵抗を介して両画素電極17、62を接続するリーカー抵抗部を設けてもよい。これにより、副画素A、B、Cの液晶層にそれぞれ印加される電圧の中心電圧の差はほぼ0.1V以下となり、画素電極62の形成領域を副画素Cとして利用できる。以上のように本実施例によれば、3 TFT ハーフトーン構造の液晶表示装置に生じ得る問題点(2)を解決することができる。

#### 【0063】

以上説明したように、本実施の形態によれば、従来の容量結合HT法を用いた構造とは異なる3 TFT ハーフトーン構造の液晶表示装置において、表示むらの原因となるバッファ容量  $C_b$  の変動を抑止でき、かつ開口率低下を防止できる。これにより、焼付きが生じ難く、表示むらのない表示特性を安定して得られる高輝度かつ広視野角の液晶表示装置を実現できる。なお、本実施の形態では基本的にMVA方式等のVAモードの液晶表示装置への適用を念頭に置いた画素構成となっているが、原理や効果はVAモードに限定されるものではなく、TN、IPS、OCB等のあらゆる液晶モードの液晶表示装置に適用可能である。

#### 【0064】

本発明は、上記実施の形態に限らず種々の变形が可能である。

10

20

30

40

50

例えば、上記実施の形態では透過型の液晶表示装置を例に挙げたが、本発明はこれに限らず、反射型や半透過型等の他の液晶表示装置にも適用できる。

【0065】

また上記実施の形態では、対向基板4上にCF樹脂層40が形成された液晶表示装置を例に挙げたが、本発明はこれに限らず、TFT基板2上にCF樹脂層が形成された、いわゆるCF-on-TFT構造の液晶表示装置にも適用できる。

【0066】

以上説明した実施の形態による液晶表示装置は、以下のようにまとめられる。

(付記1)

対向配置された一対の基板と、

前記基板間に封止された液晶層と、

一方の前記基板上に互いに並列して形成された複数のゲートバスラインと、

前記複数のゲートバスラインに絶縁膜を介して交差して形成された複数のドレインバスラインと、

前記ゲートバスラインに並列して形成された複数の蓄積容量バスラインと、

n本目の前記ゲートバスラインに電気的に接続されたゲート電極と、前記ドレインバスラインに電気的に接続されたドレイン電極とをそれぞれ備えた第1及び第2のトランジスタと、

前記第1のトランジスタのソース電極に電気的に接続された第1の画素電極と、

前記第2のトランジスタのソース電極に電気的に接続され、前記第1の画素電極から分離された第2の画素電極と、

前記第1の画素電極が形成された第1の副画素と、前記第2の画素電極が形成された第2の副画素とを少なくとも備えた画素領域と、

(n+1)本目の前記ゲートバスラインに電気的に接続されたゲート電極と、前記第2の画素電極に接続されたソース電極と、前記蓄積容量バスラインに接続されたドレイン電極とを備えた第3のトランジスタと、

前記第3のトランジスタのドレイン電極と前記蓄積容量バスラインとの間、又は前記第3のトランジスタのソース電極と前記第2の画素電極との間のいずれか一方を容量結合するバッファ容量部と

を有することを特徴とする液晶表示装置。

(付記2)

付記1記載の液晶表示装置において、

前記バッファ容量部は、前記第3のトランジスタのドレイン電極に電気的に接続された第1のバッファ容量電極と、前記第1のバッファ容量電極に対向して配置され、前記蓄積容量バスラインに電気的に接続された第2のバッファ容量電極と、前記第1及び第2のバッファ容量電極の間に配置された誘電体層とを有していること

を特徴とする液晶表示装置。

(付記3)

付記2記載の液晶表示装置において、

前記第1のバッファ容量電極は、前記第3のトランジスタのドレイン電極と同層に形成された第1のサブ電極と、前記第1又は第2の画素電極と同層に形成され、基板面に垂直に見て前記第1のサブ電極に重なって配置され、前記第1のサブ電極に電気的に接続された第2のサブ電極とを有し、

前記バッファ容量部は、前記第1のサブ電極と前記第2のバッファ容量電極との間に形成される容量Cb1と、前記第2のサブ電極と前記第2のバッファ容量電極との間に形成される容量Cb2とを有すること

を特徴とする液晶表示装置。

(付記4)

付記3記載の液晶表示装置において、

前記第2のバッファ容量電極は、前記蓄積容量バスラインと同層に形成されていること

10

20

30

40

50

を特徴とする液晶表示装置。

(付記 5 )

付記 3 又は 4 に記載の液晶表示装置において、

前記第 1 のサブ電極と前記第 2 のバッファ容量電極との間隔は、前記第 2 のサブ電極と前記第 2 のバッファ容量電極との間隔より狭く、

前記第 1 のサブ電極は、基板面に垂直に見て、前記第 2 のサブ電極及び前記第 2 のバッファ容量電極よりも内側に配置されていること

を特徴とする液晶表示装置。

(付記 6 )

付記 5 記載の液晶表示装置において、

前記第 2 のサブ電極は、基板面に垂直に見て、前記第 2 のバッファ容量電極よりも内側に配置されていること

を特徴とする液晶表示装置。

(付記 7 )

付記 2 記載の液晶表示装置において、

前記第 2 のバッファ容量電極は、前記蓄積容量バスラインと同層に形成された第 1 のサブ電極と、前記第 1 又は第 2 の画素電極と同層に形成され、基板面に垂直に見て前記第 1 のサブ電極に重なって配置され、前記第 1 のサブ電極に電気的に接続された第 2 のサブ電極とを有し、

前記バッファ容量部は、前記第 1 のサブ電極と前記第 1 のバッファ容量電極との間に形成される容量 C<sub>b</sub>1 と、前記第 2 のサブ電極と前記第 1 のバッファ容量電極との間に形成される容量 C<sub>b</sub>2 とを有すること

を特徴とする液晶表示装置。

(付記 8 )

付記 7 記載の液晶表示装置において、

前記第 1 のバッファ容量電極は、前記第 3 の薄膜トランジスタのドレイン電極と同層に形成されていること

を特徴とする液晶表示装置。

(付記 9 )

付記 7 又は 8 に記載の液晶表示装置において、

前記第 1 のバッファ容量電極は前記第 1 及び第 2 のサブ電極の間の層に形成され、基板面に垂直に見て、前記第 1 及び第 2 のサブ電極よりも内側に配置されていること

を特徴とする液晶表示装置。

(付記 10 )

付記 2 記載の液晶表示装置において、

他方の前記基板上に形成された共通電極と、前記一対の基板間の間隔を維持する柱状スペーサとをさらに有し、

前記第 1 のバッファ容量電極に対向する領域の前記共通電極は、前記第 2 のバッファ容量電極として機能し、

前記柱状スペーサは、前記第 1 のバッファ容量電極の形成領域に形成され、前記誘電体層として機能すること

を特徴とする液晶表示装置。

(付記 11 )

付記 2 記載の液晶表示装置において、

他方の前記基板上に形成された共通電極と、前記液晶を配向規制する絶縁性突起とをさらに有し、

前記第 1 のバッファ容量電極に対向する領域の前記共通電極は、前記第 2 のバッファ容量電極として機能し、

前記絶縁性突起の少なくとも一部は、前記第 1 のバッファ容量電極の形成領域に形成されていること

10

20

30

40

50

を特徴とする液晶表示装置。

(付記 1 2 )

付記 2 記載の液晶表示装置において、

他方の前記基板上に形成された共通電極をさらに有し、

前記共通電極は、前記第 1 のバッファ容量電極に対向する領域の少なくとも一部で除去されていること

を特徴とする液晶表示装置。

(付記 1 3 )

付記 2 記載の液晶表示装置において、

前記第 1 のバッファ容量電極は、前記第 1 又は第 2 の画素電極と同層に形成されている 10 こと

を特徴とする液晶表示装置。

(付記 1 4 )

付記 1 3 記載の液晶表示装置において、

前記第 2 のバッファ容量電極は、前記蓄積容量バスラインと同層に形成されていることを特徴とする液晶表示装置。

(付記 1 5 )

付記 2 記載の液晶表示装置において、

前記第 2 のバッファ容量電極は、前記第 1 又は第 2 の画素電極と同層に形成されている 20 こと

を特徴とする液晶表示装置。

(付記 1 6 )

付記 1 5 記載の液晶表示装置において、

前記第 1 のバッファ容量電極は、前記第 3 のトランジスタのドレイン電極と同層に形成されていること

を特徴とする液晶表示装置。

(付記 1 7 )

付記 2 記載の液晶表示装置において、

他方の前記基板上に形成された共通電極をさらに有し、

前記画素領域は、第 3 の画素電極が形成された第 3 の副画素をさらに有し、

前記第 3 の画素電極は、前記第 3 のトランジスタのドレイン電極に電気的に接続されて前記第 1 のバッファ容量電極としても機能し、

前記第 3 の画素電極に対向する領域の前記共通電極は、前記第 2 のバッファ容量電極としても機能すること

を特徴とする液晶表示装置。

(付記 1 8 )

付記 1 7 記載の液晶表示装置において、

前記第 1 乃至第 3 の副画素における前記液晶への印加電圧の中心電圧の差は 0 . 1 V 以下であること

を特徴とする液晶表示装置。

(付記 1 9 )

付記 1 7 又は 1 8 に記載の液晶表示装置において、

前記第 2 の副画素に形成される液晶容量  $C_{1c2}$  及び蓄積容量  $C_{s2}$  の和と、前記バッファ容量部に形成されるバッファ容量  $C_b$  との比  $X (= (C_{1c2} + C_{s2}) / C_b)$  と

、前記第 3 のトランジスタのゲート電極と前記第 2 の画素電極との間に形成される寄生容量  $C_{gs32}$  と、前記第 3 のトランジスタのゲート電極と前記第 3 の画素電極との間に形成される寄生容量  $C_{gs33}$  との比  $Y (= C_{gs32} / C_{gs33})$  とがほぼ等しいこと

を特徴とする液晶表示装置。

(付記 2 0 )

10

20

30

40

50

付記 17 又は 18 に記載の液晶表示装置において、

前記第 2 及び第 3 の画素電極の間を所定の抵抗を介して接続し、前記第 2 の画素電極の電位と前記第 3 の画素電極の電位とを 1 フレーム期間内にほぼ一致させるリーク抵抗部をさらに有すること

を特徴とする液晶表示装置。

【図面の簡単な説明】

【0067】

【図 1】本発明の一実施の形態の前提となる液晶表示装置の構成を示す図である。

【図 2】本発明の一実施の形態の前提となる液晶表示装置の構成を示す断面図である。

【図 3】本発明の一実施の形態の前提となる液晶表示装置の 1 画素の等価回路を示す図である。

10

【図 4】本発明の一実施の形態の前提となる液晶表示装置の構成の他の例を示す図である。

【図 5】本発明の一実施の形態の前提となる液晶表示装置の 1 画素の等価回路の他の例を示す図である。

【図 6】本発明の一実施の形態の前提となる液晶表示装置の構成のさらに他の例を示す図である。

【図 7】液晶表示装置における容量比の変化に対する電圧比の変化を示すグラフである。

【図 8】本発明の一実施の形態による液晶表示装置の第 1 の原理を示す図である。

【図 9】本発明の一実施の形態による液晶表示装置の第 2 の原理を示す図である。

20

【図 10】本発明の一実施の形態による液晶表示装置の第 3 の原理を示す図である。

【図 11】本発明の一実施の形態による液晶表示装置の第 4 の原理を示す図である。

【図 12】本発明の一実施の形態による液晶表示装置の第 5 の原理を示す図である。

【図 13】本発明の一実施の形態による液晶表示装置の第 5 の原理を示す図である。

【図 14】本発明の一実施の形態の実施例 1 による液晶表示装置の概略構成を示す図である。

【図 15】本発明の一実施の形態の実施例 1 による液晶表示装置の構成の変形例を示す図である。

【図 16】本発明の一実施の形態の実施例 2 による液晶表示装置の構成の変形例を示す図である。

30

【図 17】本発明の一実施の形態の実施例 3 による液晶表示装置の構成の変形例を示す図である。

【図 18】本発明の一実施の形態の実施例 4 による液晶表示装置の一画素の等価回路を示す図である。

【図 19】本発明の一実施の形態の実施例 4 による液晶表示装置を説明するグラフである。

【図 20】VA モードの液晶表示装置の T - V 特性を示すグラフである。

【図 21】表示画面に表示した画像の見え方の変化を示す図である。

【図 22】赤みがかった画像における R、G、B の階調ヒストグラムを示す図である。

40

【図 23】公知技術に基づく基本的な液晶表示装置の構成を示す図である。

【図 24】公知技術に基づく基本的な液晶表示装置の構成を示す断面図である。

【図 25】公知技術に基づく基本的な液晶表示装置の等価回路を示す図である。

【図 26】容量結合 HT 法を用いた従来の液晶表示装置に生じる焼付き現象を説明する図である。

【符号の説明】

【0068】

2 TFT 基板

4 対向基板

6 液晶層

10、11 ガラス基板

50

|                                             |               |    |

|---------------------------------------------|---------------|----|

| 1 2                                         | ゲートバスライン      |    |

| 1 4                                         | ドレインバスライン     |    |

| 1 6、1 7、6 2                                 | 画素電極          |    |

| 1 8                                         | 蓄積容量バスライン     |    |

| 1 9                                         | 蓄積容量電極        |    |

| 2 1、2 2、2 3                                 | T F T         |    |

| 2 1 a、2 2 a、2 3 a                           | ドレイン電極        |    |

| 2 1 b、2 2 b、2 3 b                           | ソース電極         |    |

| 2 1 d、2 2 d、2 3 d                           | チャネル保護膜       |    |

| 2 3 c                                       | ゲート電極         | 10 |

| 2 3 e                                       | 動作半導体層        |    |

| 2 3 f                                       | n型不純物半導体層     |    |

| 2 4、2 6、2 7、3 1、3 3、5 0、5 1、5 3、5 4、5 5、5 6 | コンタクトホール      |    |

| 2 5、3 5                                     | 接続電極          |    |

| 2 8、2 9、6 0、6 1                             | バッファ容量電極      |    |

| 3 0                                         | 絶縁膜           |    |

| 3 2                                         | 保護膜           |    |

| 3 4                                         | バッファ容量部       |    |

| 3 6、3 7                                     | 配向膜           | 20 |

| 4 0                                         | C F樹脂層        |    |

| 4 2                                         | 共通電極          |    |

| 4 3                                         | 開口部           |    |

| 4 4                                         | 線状突起          |    |

| 4 6                                         | スリット          |    |

| 4 7                                         | 柱状スペーサ        |    |

| 5 2                                         | 繋ぎ替え電極        |    |

| 6 0 a、6 0 b                                 | サブ電極          |    |

| 6 3                                         | 絶縁性突起         |    |

| 8 0                                         | ゲートバスライン駆動回路  | 30 |

| 8 2                                         | ドレインバスライン駆動回路 |    |

| 8 4                                         | 制御回路          |    |

| 8 6、8 7                                     | 偏光板           |    |

| 8 8                                         | バックライトユニット    |    |

【 図 1 】

【 図 2 】

【図3】

【図4】

【 図 5 】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図15】

【図14】

【図16】

【図17】

【図18】

【図20】

【図19】

【図22】

【図23】

【図24】

【図26】

【図25】

【図21】

---

フロントページの続き

(72)発明者 仲西 洋平

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

(72)発明者 吉田 秀史

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

(72)発明者 津田 英昭

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

(72)発明者 柴崎 正和

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

F ターム(参考) 2H092 GA11 JA24 JA34 JA37 JA41 JB31 NA01 PA01 PA03 PA12

5F110 AA30 BB01 CC07 DD02 FF03 HK08 HK21 NN02 NN12 NN24

NN72 NN73

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP2006276411A</a>                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2006-10-12 |

| 申请号            | JP2005094896                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2005-03-29 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 镰田豪<br>田坂泰俊<br>仲西洋平<br>吉田秀史<br>津田英昭<br>柴崎正和                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 发明人            | 镰田 豪<br>田坂 泰俊<br>仲西 洋平<br>吉田 秀史<br>津田 英昭<br>柴崎 正和                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/1368 H01L29/786 H01L21/336                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | G02F1/136213 H01L27/1255                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| FI分类号          | G02F1/1368 H01L29/78.612.Z                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 2H092/GA11 2H092/JA24 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JB31 2H092/NA01 2H092 /PA01 2H092/PA03 2H092/PA12 5F110/AA30 5F110/BB01 5F110/CC07 5F110/DD02 5F110/FF03 5F110/HK08 5F110/HK21 5F110/NN02 5F110/NN12 5F110/NN24 5F110/NN72 5F110/NN73 2H192 /AA24 2H192/BA16 2H192/BA25 2H192/BC26 2H192/BC42 2H192/CB05 2H192/CB12 2H192/DA12 2H192/DA13 2H192/DA42 2H192/DA43 2H192/DA65 2H192/EA43 2H192/GD14 2H192/GD23 2H192 /JA13 |         |            |

| 代理人(译)         | 盛冈正树                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 其他公开文献         | <a href="#">JP4438665B2</a>                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

**摘要(译)**

要解决的问题：提供一种能够获得优异显示特性的液晶显示装置。ŽSOLUTION：液晶显示装置具有第一和第二TFT，其栅极连接到第(n)栅极总线，漏极连接到漏极总线，第一像素电极连接到第一TFT的源极，第二像素电极，连接第二TFT的源极，第三TFT，其栅极连接第(n+1)栅极总线，源极连接第二像素电极，缓冲电容电极与第一和第二像素电极形成在同一层中并连接到第三TFT的漏电极23a的60，并连接到存储电容总线的缓冲电容电极28，并具有电容耦合的缓冲电容部分34漏电极23a和存储电容总线。Ž