(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-171749

(P2006-171749A)

(43) 公開日 平成18年6月29日(2006.6.29)

(51) Int.C1.

F 1

テーマコード(参考)

**G09G 3/36 (2006.01)**

**G02F 1/133 (2006.01)**

**G09G 3/20 (2006.01)**

G09G 3/36

G02F 1/133 550

G09G 3/20 660V

G09G 3/20 621F

G09G 3/20 650J

2H093

5C006

5C080

審査請求 未請求 請求項の数 33 O L (全 23 頁) 最終頁に続く

(21) 出願番号

特願2005-358295 (P2005-358295)

(22) 出願日

平成17年12月12日 (2005.12.12)

(31) 優先権主張番号

10-2004-0104572

(32) 優先日

平成16年12月11日 (2004.12.11)

(33) 優先権主張国

韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeongtong-gu, Suwon-si

Gyeonggi-do, Republic

of Korea

(74) 代理人 100072349

弁理士 八田 幹雄

(74) 代理人 100110995

弁理士 奈良 泰男

(74) 代理人 100114649

弁理士 宇谷 勝幸

最終頁に続く

(54) 【発明の名称】 液晶表示装置及び表示装置の駆動装置

## (57) 【要約】

【課題】画素の充電速度を増加させて表示装置の画質を改善する。

【解決手段】本発明は液晶表示装置に関し、行列形態に配列されている複数の画素と、第1周波数の入力映像データを第2周波数の複数の出力映像データに変換して出力する信号制御部と、前記信号制御部からの出力映像データ各々を相当するアナログデータ電圧に変換して前記画素に順次に印加するデータ駆動部とを含み、前記出力映像データのうちの前記画素に最大輝度を与える出力映像データは、前記入力映像データを直前フレームの入力映像データと比較して決められる。その結果、入力映像データを複数の出力映像データに変換する場合、液晶の応答速度が速くなつてフリッカー現象などの画質不良が防止される。

【選択図】図9

**【特許請求の範囲】****【請求項 1】**

行列形態に配列されている複数の画素を含む表示装置を駆動する装置であって、第1周波数の入力映像データを第2周波数の複数の出力映像データに変換して出力する信号制御部と、

前記信号制御部からの前記複数の出力映像データ各々をアナログデータ電圧に変換して前記画素に、順次に印加するデータ駆動部と、を含み、

前記複数の出力映像データのうちの前記画素に最大輝度を与える出力映像データである最大出力映像データは、前記入力映像データを直前フレームの入力映像データである直前入力映像データと比較して決められる表示装置の駆動装置。

**【請求項 2】**

前記最大出力映像データは、前記直前入力映像データと前記入力映像データとの大きさの差によって、前記複数の出力映像データに対応する複数の臨時映像データの中で前記最大映像データに対応する最大臨時映像データを基準に決められる請求項1に記載の表示装置の駆動装置。

**【請求項 3】**

前記最大出力映像データは、前記最大臨時映像データより大きい、または小さい請求項2に記載の表示装置の駆動装置。

**【請求項 4】**

前記最大出力映像データは、前記最大臨時映像データと同一である請求項2に記載の表示装置の駆動装置。

**【請求項 5】**

前記複数の臨時映像データのガンマ曲線の平均は、前記入力映像データのガンマ曲線と一致する請求項3に記載の表示装置の駆動装置。

**【請求項 6】**

前記複数の臨時映像データによる画素の光量の合計は、前記入力映像データによる画素の光量と同一である請求項3に記載の表示装置の駆動装置。

**【請求項 7】**

前記複数の出力映像データは、第1出力映像データと第2出力映像データと、を含み、前記第1出力映像データは、前記第2出力映像データより大きい請求項2に記載の表示装置の駆動装置。

**【請求項 8】**

前記第1出力映像データは、前記直前入力映像データと前記入力映像データとの大きさの差によって、前記第1出力映像データに対応する第1臨時映像データを基準に決められる請求項7に記載の表示装置の駆動装置。

**【請求項 9】**

前記入力映像データが前記直前入力映像データより大きい場合、前記第1出力映像データは、前記第1臨時映像データより大きい請求項8に記載の表示装置の駆動装置。

**【請求項 10】**

前記入力映像データが前記直前入力映像データより小さい場合、前記第1出力映像データは、前記第1臨時映像データより小さい請求項8に記載の表示装置の駆動装置。

**【請求項 11】**

前記入力映像データが前記直前入力映像データと同一である場合、前記第1出力映像データは、前記第1臨時映像データと同一である請求項8に記載の表示装置の駆動装置。

**【請求項 12】**

前記第1出力映像データは、前記第1臨時映像データと前記第2臨時映像データに相当するデータ電圧を画素に印加する時に得られる平衡状態の透過率曲線を基準に決められる請求項8に記載の表示装置の駆動装置。

**【請求項 13】**

前記信号制御部は、

10

20

30

40

50

前記入力映像データと前記直前入力映像データとを記憶するフレームメモリと、

前記フレームメモリからの前記入力映像データを前記直前入力映像データと比較して、

前記入力映像データを前記第1出力映像データ及び第2出力映像データに変換して出力する

映像信号補正部と、

を含む請求項7に記載の表示装置の駆動装置。

【請求項14】

前記映像信号補正部は、

前記第1出力映像データ及び第2出力映像データが記憶されているルックアップテーブルと、

制御信号によって前記ルックアップテーブルからの第1出力映像データ及び第2出力映像データのうちの一つを選択して出力するマルチプレクサーと、

を含む請求項13に記載の表示装置の駆動装置。

【請求項15】

前記映像信号補正部は、

前記第1出力映像データ及び第2出力映像データが、各々記憶されている第1ルックアップテーブル及び第2ルックアップテーブルと、

制御信号によって前記第1ルックアップテーブル及び第2ルックアップテーブルからの第1出力映像データ及び第2出力映像データのうちの一つを選択して出力するマルチプレクサーと、

前記マルチプレクサーからの第1出力映像データもしくは第2出力映像データを、前記入力映像データと前記直前入力映像データの関数で記憶し、前記入力映像データと前記直前入力映像データに対応する第1出力映像データもしくは第2出力映像データを出力する第3ルックアップテーブルと、

を含む請求項13に記載の表示装置の駆動装置。

【請求項16】

前記信号制御部は、

前記入力映像データと前記直前入力映像データとを記憶するフレームメモリと、

前記フレームメモリからの前記入力映像データと前記直前入力映像データとに基づいて前記入力映像データを前記複数の出力映像データに変換して出力する映像信号補正部と、

を含み、

前記映像信号補正部は、前記直前入力映像データと前記入力映像データとの一部対に対する出力映像データを記憶しているルックアップテーブルをさらに含み、残り直前入力映像データと残り入力映像データとの対に対する出力映像データは補間方式で求められる請求項1に記載の表示装置の駆動装置。

【請求項17】

前記複数の出力映像データは、第1出力映像データと第2出力映像データと、を含み、

前記第1出力映像データは、前記第2出力映像データより大きい請求項16に記載の表示装置の駆動装置。

【請求項18】

前記映像信号補正部は、

前記第1出力映像データ及び第2出力映像データに対する補正係数が記憶されているルックアップテーブルと、

制御信号によって前記ルックアップテーブルからの第1出力映像データ及び第2出力映像データに対する補正係数のうちの一つを選択して出力するマルチプレクサーと、

前記マルチプレクサーからの第1補正係数もしくは第2補正係数及び前記入力映像データと、前記直前入力映像データとによって補間を実施する演算部と、

を含む請求項17に記載の表示装置の駆動装置。

【請求項19】

前記映像信号補正部は、

前記第1出力映像データ及び第2出力映像データに対する第1補正係数及び第2補正係数

10

20

30

40

50

数が各々記憶されている第1ルックアップテーブル及び第2ルックアップテーブルと、制御信号によって前記第1ルックアップテーブル及び第2ルックアップテーブルからの第1補正係数及び第2補正係数のうちの一つを選択して出力するマルチプレクサーと、

前記マルチプレクサーからの第1補正係数もしくは第2補正係数を前記入力映像データと前記直前入力映像データの関数で記憶し、前記入力映像データと前記直前入力映像データに対応する第1補正係数もしくは第2補正係数を出力する第3ルックアップテーブルと、

前記第3ルックアップテーブルからの第1補正係数もしくは第2補正係数と前記入力映像データと前記直前入力映像データによって補間を実施する演算部と、

を含む請求項17に記載の表示装置の駆動装置。

10

【請求項20】

前記第2周波数は、前記第1周波数の2倍である請求項1に記載の表示装置の駆動装置。

【請求項21】

行列形態に配列されている複数の画素と、

第1周波数の入力映像データを第2周波数の複数の出力映像データに変換して出力する信号制御部と、

前記信号制御部からの出力映像データ各々をアナログデータ電圧に変換して前記画素に、順次に印加するデータ駆動部と、を含み、

前記複数の出力映像データの中で前記画素に最大輝度を与える出力映像データである最大出力映像データは、前記入力映像データを直前フレームの入力映像データである直前入力映像データと比較して決められる液晶表示装置。

20

【請求項22】

前記最大出力映像データは、前記直前入力映像データと前記入力映像データとの大きさの差によって、前記複数の出力映像データに対応する複数の臨時映像データの中で前記最大映像データに対応する最大臨時映像データを基準に決められる請求項21に記載の液晶表示装置。

【請求項23】

前記最大出力映像データは、前記最大臨時映像データより大きい、または小さい請求項22に記載の液晶表示装置。

30

【請求項24】

前記最大出力映像データは、前記最大臨時映像データと同一である請求項22に記載の液晶表示装置。

【請求項25】

前記複数の臨時映像データのガンマ曲線の平均は、前記入力映像データのガンマ曲線と一致する請求項23に記載の液晶表示装置。

【請求項26】

前記複数の臨時映像データによる画素の光量の合計は、前記入力映像データによる画素の光量と同一である請求項23に記載の液晶表示装置。

40

【請求項27】

前記複数の出力映像データは、第1出力映像データと第2出力映像データと、を含み、

前記第1出力映像データは、前記第2出力映像データより大きい請求項22に記載の液晶表示装置。

【請求項28】

前記第1出力映像データは、前記直前入力映像データと前記入力映像データとの大きさの差によって、前記第1出力映像データに対応する第1臨時映像データを基準に決められる請求項27に記載の液晶表示装置。

【請求項29】

前記入力映像データが前記直前入力映像データより大きい場合、前記第1出力映像データは前記第1臨時映像データより大きい請求項28に記載の液晶表示装置。

50

**【請求項 3 0】**

前記入力映像データが前記直前入力映像データより小さい場合、前記第1出力映像データは前記第1臨時映像データより小さい請求項28に記載の液晶表示装置。

**【請求項 3 1】**

前記入力映像データが前記直前入力映像データと同一である場合、前記第1出力映像データは前記第1臨時映像データと同一である請求項28に記載の液晶表示装置。

**【請求項 3 2】**

前記第1出力映像データは、前記第1臨時映像データと前記第2臨時映像データに相当するデータ電圧を画素に印加する時に得られる平衡状態の透過率曲線を基準に決められる請求項28に記載の液晶表示装置。

10

**【請求項 3 3】**

前記第2周波数は前記第1周波数の2倍である請求項21に記載の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶表示装置及び表示装置の駆動装置に関するものである。

**【背景技術】****【0002】**

一般的な液晶表示装置（LCD）は、画素電極及び共通電極が備えられた二枚の表示板と、その間にしている誘電率異方性を持つ液晶層を備える。画素電極は行列形態に配列されていて、薄膜トランジスタ（TFT）などスイッチング素子に連結されて一行ずつ順次にデータ電圧の印加を受ける。共通電極は、画素電極と異なる表示板または同一表示板に備えられ、共通電圧の印加を受ける。画素電極、共通電極、及びその間の液晶層は回路的にみると、液晶キャパシタを構成している。液晶キャパシタはこれに連結されたスイッチング素子と共に画素を構成する基本単位となる。

20

**【0003】**

このような液晶表示装置では、二つの電極に電圧を印加して液晶層に電界を生成し、この電界の強さを調節することで、液晶層を通過する光の透過率を調節して所望の画像を得る。

30

**【0004】**

この時、液晶層に一方向の電界が長時間印加されることによって発生する劣化現象を防止するために、フレーム別に、行別にもしくは画素別に共通電圧に対するデータ電圧の極性を反転させる。

**【0005】**

このようなTFT-LCDは、コンピュータの表示装置だけでなくテレビの表示画面としても広く使用されることによって、動画像を実現する必要が高まっている。しかし、従来のTFT-LCDは、液晶の応答速度が遅いために動画像を実現することが難しい。

**【0006】**

つまり、液晶分子の応答速度が遅いために液晶キャパシタに充電される電圧が目標電圧である所望の輝度が得られる電圧まで至るのにある程度の時間がかかり、この時間は、目標電圧と液晶キャパシタの直前に充電されていた電圧（直前電圧）との差によって変わる。したがって、目標電圧と直前電圧との差が大きい場合、最初から目標電圧のみを印加すると、スイッチング素子が導通している時間の間に目標電圧に至れないことがある。

40

**【発明の開示】****【発明が解決しようとする課題】****【0007】**

そこで、本発明が目的とする技術的課題は、画素の充電速度を上昇させて表示装置の画質を改善することにある。

**【課題を解決するための手段】****【0008】**

50

本発明の一つの特徴による駆動装置は、行列形態に配列されている複数の画素を含む表示装置を駆動する装置であって、第1周波数の入力映像データを第2周波数の複数の出力映像データに変換して出力する信号制御部と、前記信号制御部からの前記複数の出力映像データ各々を相当するアナログデータ電圧に変換して前記画素に順次に印加するデータ駆動部とを含み、前記複数の出力映像データのうちの前記画素に最大輝度を与える出力映像データである最大出力映像データは、前記入力映像データを直前フレームの入力映像データである直前入力映像データと比較して決められる。

【0009】

本発明の一つの特徴による液晶表示装置は、行列形態に配列されている複数の画素と、第1周波数の入力映像データを第2周波数の複数の出力映像データに変換して出力する信号制御部と、前記信号制御部からの出力映像データ各々を相当するアナログデータ電圧に変換して前記画素に順次に印加するデータ駆動部とを含み、前記複数の出力映像データの中で前記画素に最大輝度を与える出力映像データは前記入力映像データを直前フレームの入力映像データと比較して決められる。

【0010】

前記最大出力映像データは、前記直前入力映像データと前記入力映像データとの大きさの差によって、前記複数の出力映像データに対応する複数の臨時映像データの中で前記最大映像データに対応する最大臨時映像データを基準に決められるのが好ましい。

【0011】

前記最大出力映像データは、前記最大臨時映像データより大きい、または小さいのが好ましい。

【0012】

前記最大出力映像データは前記最大臨時映像データと同一であるのが好ましい。

【0013】

前記複数の臨時映像データのガンマ曲線の平均は、前記入力映像データのガンマ曲線と一致してもよい。

【0014】

前記複数の臨時映像データによる画素の光量の合計は前記入力映像データによる画素の光量と同一であってもよい。

【0015】

前記複数の出力映像データは、第1出力映像データと第2出力映像データと、を含み、前記第1出力映像データは、前記第2出力映像データより大きいのが好ましい。

【0016】

前記第1出力映像データは、前記直前入力映像データと前記入力映像データとの大きさの差によって、前記第1出力映像データに対応する第1臨時映像データを基準に決められるのが好ましい。

【0017】

前記入力映像データが前記直前入力映像データより大きい場合、前記第1出力映像データは前記第1臨時映像データより大きく、前記入力映像データが前記直前入力映像データより小さい場合、前記第1出力映像データは前記第1臨時映像データより小さく、または前記入力映像データが前記直前入力映像データと同一である場合、前記第1出力映像データは前記第1臨時映像データと同一であるのが好ましい。

【0018】

前記第1出力映像データは、前記第1臨時映像データと前記第2臨時映像データに相当するデータ電圧を引続き画素に印加する時に得られる最終的な平衡状態の透過率曲線を基準に決められるのが好ましい。

【0019】

前記信号制御部は、前記入力映像データと前記直前入力映像データとを記憶するフレームメモリと、前記フレームメモリからの前記入力映像データを前記直前入力映像データと比較して、前記入力映像データを前記第1出力映像データ及び第2出力映像データに変換

10

20

30

40

50

して出力する映像信号補正部を含むのが好ましい。

【0020】

前記映像信号補正部は、前記第1出力映像データ及び第2出力映像データが記憶されているルックアップテーブルと、制御信号によって前記ルックアップテーブルからの第1出力映像データ及び第2出力映像データのうちの一つを選択して出力するマルチブレクサーとを含むことができる。

【0021】

前記映像信号補正部は、前記第1出力映像データ及び第2出力映像データが各々記憶されている第1ルックアップテーブル及び第2ルックアップテーブルと、制御信号によって前記第1ルックアップテーブル及び第2ルックアップテーブルからの第1出力映像データ及び第2出力映像データのうちの一つを選択して出力するマルチブレクサーと、前記マルチブレクサーからの第1出力映像データもしくは第2出力映像データを前記入力映像データと前記直前入力映像データの関数で記憶し、前記入力映像データと前記直前入力映像データに応答して相当する第1出力映像データもしくは第2出力映像データを出力する第3ルックアップテーブルを含むことができる。

10

【0022】

前記信号制御部は、前記入力映像データと前記直前入力映像データとを記憶するフレームメモリと、前記フレームメモリからの前記入力映像データと前記直前入力映像データとに基づいて前記入力映像データを前記複数の出力映像データに変換して出力する映像信号補正部とを含み、前記映像信号補正部は、前記直前入力映像データと前記入力映像データの一部対に対する出力映像データを記憶しているルックアップテーブルをさらに含み、残り直前入力映像データと残り入力映像データとの対に対する出力映像データは補間方式で求められてもよい。

20

【0023】

前記複数の出力映像データは、第1出力映像データと第2出力映像データと、を含み、前記第1出力映像データは、前記第2出力映像データより大きいのが好ましい。

【0024】

前記映像信号補正部は、前記第1及び第2出力映像データに対する補正係数が記憶されているルックアップテーブルと、制御信号によって前記ルックアップテーブルからの第1出力映像データ及び第2出力映像データに対する補正係数のうちの一つを選択して出力するマルチブレクサーと、前記マルチブレクサーからの第1補正係数もしくは第2補正係数と前記入力映像データと前記直前入力映像データとによって補間を実施する演算部とを含むことができる。

30

【0025】

前記映像信号補正部は、前記第1出力映像データ及び第2出力映像データに対する第1補正係数及び第2補正係数が各々記憶されている第1及び第2ルックアップテーブルと、制御信号によって前記第1ルックアップテーブル及び第2ルックアップテーブルからの第1補正係数及び第2補正係数のうちの一つを選択して出力するマルチブレクサーと、前記マルチブレクサーからの第1補正係数もしくは第2補正係数を前記入力映像データと前記直前入力映像データの関数で記憶し、前記入力映像データと前記直前入力映像データに対応する第1補正係数もしくは第2補正係数を出力する第3ルックアップテーブルと、前記第3ルックアップテーブルからの第1補正係数もしくは第2補正係数と前記入力映像データと前記直前入力映像データによって補間を実施する演算部とを含むことができる。

40

【0026】

前記第2周波数は、前記第1周波数の2倍であってもよい。

【発明の効果】

【0027】

本発明によれば、入力映像データを複数の出力映像データに変換する場合、液晶の応答速度が速くなるため、フリッカー現象などのような画質不良が防止される。

【発明を実施するための最良の形態】

50

## 【0028】

以下、添付した図面を参照して、本発明の実施例について本発明が属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。しかし、本発明は多様で相異なる形態で実現することができ、以下に説明する実施例に限定されない。

## 【0029】

明細書に添付した図面では、複数の層及び領域を明確に表現するために、複数のそう及び領域の厚さを拡大して示しており、明細書全体にわたって類似な部分については同一図面符号を付けた。層、膜、領域、および板などの部分が他の部分の“上”にあるとする場合、他の部分の“直上”にある場合だけでなく、その中間に他の部分がある場合も含む。これに反し、ある部分が他の部分の“直上”にあるとする場合には、中間に他の部分がないことを意味する。

## 【0030】

次に、本発明の表示装置及び表示装置の駆動装置に対する一実施例である液晶表示装置及び液晶表示装置の駆動装置について、図面を参照して詳細に説明する。

## 【0031】

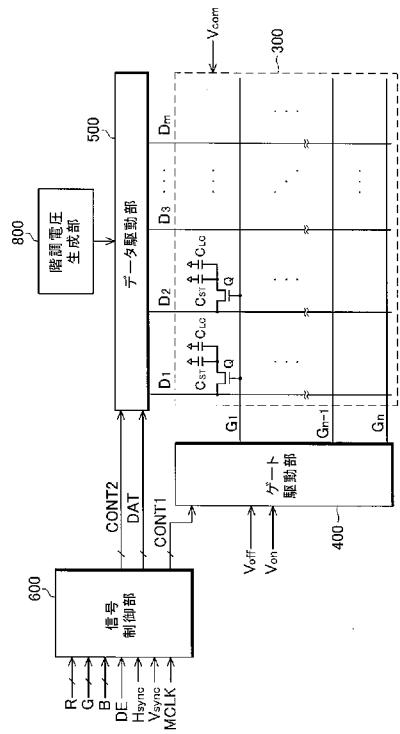

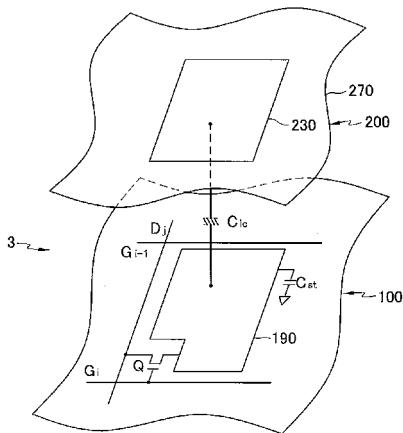

図1は、本発明の一実施例による液晶表示装置のブロック図である。図2は、本発明の一実施例による液晶表示装置の一つの画素に対する等価回路図である。また、図3は本発明の一実施例による液晶表示装置の構造図である。

## 【0032】

図1に示しているように、本発明の一実施例による液晶表示装置は、液晶表示板組立体300と、液晶表示板組立体300に連結されたゲート駆動部400とデータ駆動部500と、データ駆動部500に連結された階調電圧生成部800と、およびこれらを制御する信号制御部600を備える。

## 【0033】

液晶表示板組立体300は等価回路でみると複数の表示信号線 $G_1 \sim G_n$ 、 $D_1 \sim D_m$ 、および複数の表示信号線に連結されていてほぼ行列形態に配列された複数の画素を含む。また、液晶表示板組立体300は、互いに対向する下部表示板100及び上部表示板200と、両者の間に入っている液晶層3とを含む。

## 【0034】

表示信号線 $G_1 \sim G_n$ および $D_1 \sim D_m$ は、ゲート信号（“走査信号”とも言う）を伝達する複数のゲート線 $G_1 \sim G_n$ と、データ信号を伝達するデータ線 $D_1 \sim D_m$ である。ゲート線 $G_1 \sim G_n$ は、ほぼ行方向に延びていて、互いにほとんど平行する。データ線 $D_1 \sim D_m$ は、ほぼ列方向に延びていて、互いにほとんど平行する。

## 【0035】

各画素は、ゲート線 $G_1 \sim G_n$ 及びデータ線 $D_1 \sim D_m$ に連結されたスイッチング素子Qと、これに連結された液晶キャパシタ $C_{LC}$ と、ストレージキャパシタ $C_{ST}$ とを含む。ストレージキャパシタ $C_{ST}$ は、必要に応じて省略できる。

## 【0036】

各画素のスイッチング素子Qは、下部表示板100に備えられている薄膜トランジスタなどで構成され、ゲート線 $G_1 \sim G_n$ に連結されている制御端子と、データ線 $D_1 \sim D_m$ に連結されている入力端子と、液晶キャパシタ $C_{LC}$ 及びストレージキャパシタ $C_{ST}$ に連結されている出力端子とを有する三端子素子である。

## 【0037】

液晶キャパシタ $C_{LC}$ は、下部表示板100の画素電極190と上部表示板200の共通電極270を二つの端子とし、二つの電極190および270の間の液晶層3は誘電体として機能する。画素電極190は、スイッチング素子Qに連結され、共通電極270は上部表示板200の全面に形成されていて、共通電圧 $V_{com}$ の印加を受ける。図2とは異なって、共通電極270が下部表示板100に備えられる場合は、二つの電極190、270のうちの少なくとも一つが線状もしくは棒状に形成されてもよい。

## 【0038】

10

20

30

40

50

液晶キャパシタ  $C_{Lc}$  の補助的な役割を果たすストレージキャパシタ  $C_{ST}$  は、下部表示板 100 に備えられた別個の信号線（図示せず）と画素電極 190 が絶縁体を間に置いて重なって構成され、この別個の信号線には、共通電圧  $V_{com}$  などの決められた電圧が印加される。しかし、ストレージキャパシタ  $C_{ST}$  は、画素電極 190 が絶縁体を媒介として直上の前端のゲート線と重なって構成されてもよい。

#### 【0039】

一方、色表示を実現するために、各画素が原色のうちの一つを固有に表示（空間分割）し、各画素が時間によって交互に原色を表示（時間分割）する。これら原色の空間的、時間的な作用で所望の色相を認識させる。原色の例としては、赤色、緑色、及び青色がある。

10

#### 【0040】

図 2 は空間分割の一例であって、各画素が上部表示板 200 領域に原色のうちの一つを示す色フィルター 230 を備えることを示している。図 2 とは異なって、色フィルター 230 は下部表示板 100 の画素電極 190 の上、もしくは画素電極 190 の下に形成してもよい。

#### 【0041】

液晶表示板組立体 300 の二つの表示板 100、200 のうち少なくとも一つの外側の面には、光を偏光させる偏光子（図示せず）が付着されている。

#### 【0042】

階調電圧生成部 800 は、画素の透過率に関する二つの複数階調電圧を生成する。二つのうちの一つは共通電圧  $V_{com}$  に対して正の値を有し、他の一つは負の値を有する。

20

#### 【0043】

ゲート駆動部 400 は、液晶表示板組立体 300 のゲート線  $G_1 \sim G_n$  に連結されて、外部からのゲートオン電圧  $V_{on}$  とゲートオフ電圧  $V_{off}$  との組み合わせからなるゲート信号をゲート線  $G_1 \sim G_n$  に印加し、複数の集積回路で構成される。

#### 【0044】

データ駆動部 500 は、液晶表示板組立体 300 のデータ線  $D_1 \sim D_m$  に連結されて、階調電圧生成部 800 からの階調電圧を選択してデータ電圧として画素に印加する。

#### 【0045】

ゲート駆動部 400 もしくはデータ駆動部 500 は、複数の駆動集積回路チップ形態で液晶表示板組立体 300 上に直接装着され、または可撓性印刷回路膜（図示せず）上に装着されて T C P ( tape carrier package ) 形態で液晶表示板組立体 300 に付着されてもよい。また、ゲート駆動部 400 またはデータ駆動部 500 は、表示信号線  $G_1 \sim G_n$ 、 $D_1 \sim D_m$  と薄膜トランジスタスイッチング素子 Q と共に液晶表示板組立体 300 に集積されてもよい。

30

#### 【0046】

信号制御部 600 は、ゲート駆動部 400 及びデータ駆動部 500 などの動作を制御する。

#### 【0047】

以下に、このような液晶表示装置の動作について詳細に説明する。

40

#### 【0048】

信号制御部 600 は、外部のグラフィック制御機（図示せず）から入力映像信号 R、G、B、及びその表示を制御する入力制御信号の提供を受ける。入力制御信号は、例えば、垂直同期信号  $V_{sync}$ 、水平同期信号  $H_{sync}$ 、メインクロック  $MCLK$ 、およびデータイネーブル信号  $DE$  などの信号である。信号制御部 600 は、入力映像信号 R、G、B と入力制御信号に基づいて、入力映像信号 R、G、B を液晶表示板組立体 300 の動作条件に合わせて適切に処理する。また、信号制御部 600 は、ゲート制御信号  $CONT1$  及びデータ制御信号  $CONT2$  などの信号を生成した後、ゲート制御信号  $CONT1$  をゲート駆動部 400 に出力し、データ制御信号  $CONT2$  と処理した映像信号  $DAT$  をデータ駆動部 500 に出力する。信号制御部 600 のデータ処理は、所定周波数を有する入力

50

映像データ R、G、B を変換して、入力映像データ R、G、B と異なる周波数を有する複数の出力映像データを出力することを含む。信号制御部 600 のデータ処理については後述する。

【0049】

ゲート制御信号 C O N T 1 は、走査開始を指示する走査開始信号 S T V と、ゲートオン電圧 V o n の出力時間を制御する少なくとも一つのクロック信号を含む。ゲート制御信号 C O N T 1 は、ゲートオン電圧 V o n の持続時間を制限する出力イネーブル信号 O E を含むことができる。

【0050】

データ制御信号 C O N T 2 は、一束の画素に対するデータの伝送を知らせる水平同期開始信号 S T H 、データ線 D<sub>1</sub> ~ D<sub>m</sub> に当該データ電圧を印加することを命令するロード信号 L O A D 、及びデータクロック信号 H C L K を含む。また、データ制御信号 C O N T 2 は、共通電圧 V c o m に対するデータ電圧の極性（以下、共通電圧に対するデータ電圧の極性を「データ電圧の極性」と称する）を反転させる反転信号 R V S を含んでもよい。

【0051】

信号制御部 600 からのデータ制御信号 C O N T 2 によって、データ駆動部 500 は、一行の画素に対する映像データ D A T を受信し、階調電圧生成部 800 から各映像データ D A T に対応する階調電圧を選択することによって、映像データ D A T を当該データ電圧に変換した後、これを当該データ線 D<sub>1</sub> ~ D<sub>m</sub> に印加する。

【0052】

ゲート駆動部 400 は、信号制御部 600 からのゲート制御信号 C O N T 1 によって、ゲートオン電圧 V o n をゲート線 G<sub>1</sub> ~ G<sub>n</sub> に順次に印加して、このゲート線 G<sub>1</sub> ~ G<sub>n</sub> に連結されたスイッチング素子 Q を導通させ、その結果データ線 D<sub>1</sub> ~ D<sub>m</sub> に印加されたデータ電圧が導通したスイッチング素子 Q を通じて当該画素に印加される。

【0053】

画素に印加されたデータ電圧と共通電圧 V c o m の差は、液晶キャパシタ C<sub>Lc</sub> の充電電圧、つまり、画素電圧として示される。液晶分子は、画素電圧の大きさに応じてその配列が異なり、そのために液晶層 3 を通過する光の偏光が変化する。このような偏光の変化は、表示板 100、200 に付着された偏光子（図示せず）によって光の透過率変化で示され、光の透過率変化によって画素の輝度が決められる。

【0054】

1 水平周期（1 H：水平同期信号 H s y n c 及びゲートクロック C P V の一周期）を単位として、データ駆動部 500 とゲート駆動部 400 は同一動作を繰り返す。このような方式で、一つのフレームの間に、全てのゲート線 G<sub>1</sub> ~ G<sub>n</sub> に対して順次にゲートオン電圧 V o n を印加して、全ての画素にデータ電圧を印加する。一つのフレームが終わると、次のフレームが始まり、各画素に印加されるデータ電圧の極性が直前フレームにおける極性と反対になるようにデータ駆動部 500 に印加される反転信号 R V S の状態が制御される（フレーム反転）。この時、一つのフレーム内でも反転信号 R V S の特性によって、一つのデータ線を通じて流れるデータ電圧の極性が変わったり（例えば、行反転、ドット反転）、隣接データ線を通じて同時に流れるデータ電圧の極性も互いに異なることがある（例えば、列反転、ドット反転）。

【0055】

図 3 乃至図 5 を参照して、本発明の一実施例による信号制御部について詳細に説明する。

【0056】

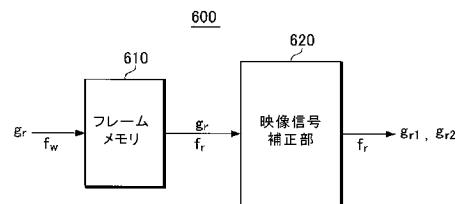

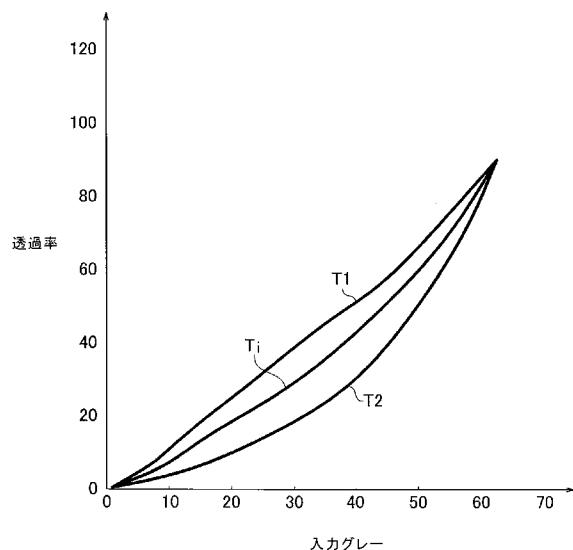

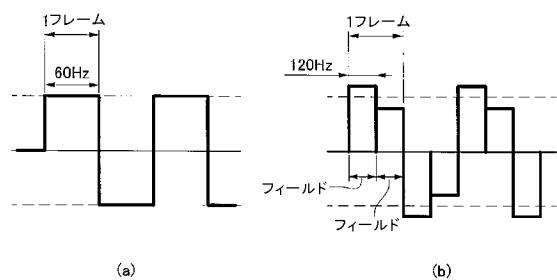

図 3 は、本発明の一実施例による信号制御部のブロック図である。図 4 は、図 3 に示した信号制御部 600 を含む液晶表示装置における映像データの補正前ガンマ曲線及び補正後ガンマ曲線を示したグラフである。図 5 は、図 3 に示した信号制御部 600 を含む液晶表示装置における映像データの補正前データ電圧と補正後データ電圧を示した波形図である。

10

20

30

40

50

## 【0057】

まず、図3に示されているように、信号制御部600はフレームメモリ610と、フレームメモリ610に連結されている映像信号補正部620を含む。

## 【0058】

フレームメモリ610は、入力される映像データをフレーム単位で記憶する。

## 【0059】

映像信号補正部620は、フレームメモリ610に記憶されている映像データ $g_r$ の入力を順次に受けて、映像データ $g_r$ を複数の出力映像データ、例えば、第1及び第2出力映像データ $g_{r1}$ 、 $g_{r2}$ に変換して順次に出力する。具体的に説明すると、映像信号補正部620は、映像データ $g_r$ を一回ずつ読み込んで、第1出力映像データ $g_{r1}$ に変換して順次に出力した後、映像データ $g_r$ を再び一回ずつ読み込んで第2出力映像データ $g_{r2}$ に変換して順次に出力する。その結果、データ駆動部500は、全ての画素に対して第1出力映像データ $g_{r1}$ に相当するデータ電圧をデータ線 $D_1 \sim D_m$ に印加した後、第2出力映像データ $g_{r2}$ に相当するデータ電圧をデータ線 $D_1 \sim D_m$ に印加する。以下、第1及び第2出力映像データ $g_{r1}$ 、 $g_{r2}$ が出力される期間及び第1及び第2出力映像データ $g_{r1}$ 、 $g_{r2}$ に相当するデータ電圧が印加される期間を「フィールド」と称する。

## 【0060】

一方、フレームメモリ610に記憶されている映像データを二回ずつ読み込むために、フレームメモリ610の読み取り周波数（出力周波数） $f_r$ は、書き取り周波数（入力周波数） $f_w$ の2倍である。その結果、フレームメモリ610の入力フレーム周波数 $f_w$ が60Hzであれば、映像信号補正部620の出力フィールド周波数及びデータ電圧の印加周波数は120Hzになる。

## 【0061】

一方、図4に示しているように、二つの出力映像データ $g_{r1}$ 、 $g_{r2}$ が示すガンマ曲線 $T_1$ 、 $T_2$ の平均は、補正前の入力映像データに対するガンマ曲線 $T_i$ と一致する。

## 【0062】

これを別の表現をすれば、第1及び第2出力映像データ $g_{r1}$ 、 $g_{r2}$ による画素の光量の合計が、補正前の入力映像データ $g_r$ による画素の光量と同一であると言える。ここで、光量とは、輝度と、その輝度を維持する時間とを乗算した値と同一である。

## 【0063】

したがって、入力映像データ $g_r$ に対応する輝度を $T(g_r)$ 、第1出力映像データ $g_{r1}$ に対応する輝度を $T(g_{r1})$ 、および第2出力映像データ $g_{r2}$ に対応する輝度を $T(g_{r2})$ とすると、以下の式(1)が成立する。

## 【0064】

$$2T(g_r) = T(g_{r1}) + T(g_{r2}) \cdots (1)$$

このように一つの入力映像データ $g_r$ を二つの出力映像データ $g_{r1}$ 、 $g_{r2}$ に変換する場合、二つの出力映像データ $g_{r1}$ 、 $g_{r2}$ のうちの一つは、他の一つより大きいか、または同一である。二つの出力映像データの中で大きいものを先に出力し、小さいものを後に出し、またはその反対にすることもできる。ノーマリーブラックモード液晶表示装置の場合、映像データが大きければ相当するデータ電圧もまた大きい。図5の(b)に、ノーマリーブラックモード液晶表示装置において、二つの出力映像データ $g_{r1}$ 、 $g_{r2}$ の中で大きいものを先に出力し、小さいものを後に出す場合のデータ電圧を示した。図5の(a)は、入力映像データを補正せずにそのまま出力した場合のデータ電圧を示す。

## 【0065】

二つの出力映像データ $g_{r1}$ 、 $g_{r2}$ のうち低い方を0、または0に近くすることで、インバルシブ駆動の効果を得ることができる。

## 【0066】

次に、図6を参照して、本発明の他の実施例による信号制御部について詳細に説明する

。

## 【0067】

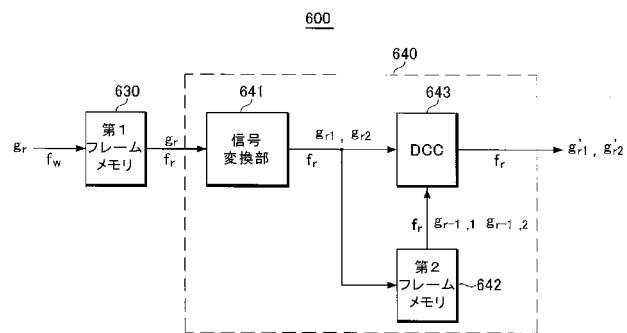

図6は、本発明の他の実施例による信号制御部のブロック図である。

## 【0068】

図6に示しているように、本実施例による信号制御部600は、第1フレームメモリ630と映像信号補正部640を含む。映像信号補正部640は、フレームメモリ630と連結されている信号変換部641、信号変換部641に連結されている第2フレームメモリ642、および信号変換部641及び第2フレームメモリ642に連結されているDCC処理部643を備える。

## 【0069】

第一フレームメモリ630及び信号変換部641の動作は、図3に示した信号制御部のフレームメモリ610及び映像信号補正部620の動作と同一である。

## 【0070】

つまり、第一フレームメモリ630は、第1周波数 $f_w$ で入力される映像データをフレーム単位で記憶する。信号変換部641は、第一フレームメモリ630に記憶されている映像データ $g_r$ を第1周波数 $f_w$ の2倍である第2周波数 $f_r$ で順次に読み込んで、映像データ $g_r$ 各々を第1及び第2臨時映像データ $g_{r1}, g_{r2}$ に変換して順次に出力する。変換の原理は、図4及び図5を参照して説明した通りである。

## 【0071】

第2フレームメモリ642は、信号変換部641からの臨時映像データ $g_{r1}, g_{r2}$ を二つのフィールド単位で記憶する。つまり、二つのフィールドの映像データを記憶する。

## 【0072】

DCC処理部643は、信号変換部641からの映像データと第2フレームメモリ642からの映像データを受信する。この時、第2フレームメモリ642から出力される映像データは、直前フレームの映像データ（以下「直前映像データ」と称し、 $g_{r-1}$ と表記する）である。直前映像データと区分するために、信号変換部641からの映像データを現在フレームの映像データ（以下、「現在映像データ」と称する。）とする。

## 【0073】

DCC処理部643は、現在映像データ $g_{r1}, g_{r2}$ 各々を直前映像データ $g_{r-1,1}, g_{r-1,2}$ と比較する。比較した結果によって、現在映像データ $g_{r1}, g_{r2}$ を出力映像データ $g_{r1'}, g_{r2'}$ に変換する。出力映像データは、現在映像データと直前映像データの大きさの差であり、これをDCCという。

## 【0074】

例えば、現在映像データ $g_{r1}, g_{r2}$ が直前映像データ $g_{r-1,1}, g_{r-1,2}$ より大きい場合、つまり、 $g_{r,p} > g_{r-1,p}$ （ $p = 1, 2$ ）である場合、出力映像データ $g_{r1'}, g_{r2'}$ は、現在映像データ $g_{r1}, g_{r2}$ より大きい。反対に、現在映像データ $g_{r1}, g_{r2}$ が直前映像データ $g_{r-1,1}, g_{r-1,2}$ より小さい場合、つまり、 $g_{r,p} < g_{r-1,p}$ である場合、出力映像データ $g_{r1'}, g_{r2'}$ は現在映像データ $g_{r1}, g_{r2}$ より小さい。また、現在映像データ $g_{r1}, g_{r2}$ が直前映像データ $g_{r-1,1}, g_{r-1,2}$ と同一である場合、つまり、 $g_{r,p} = g_{r-1,p}$ である場合、出力映像データ $g_{r1'}, g_{r2'}$ は、現在映像データ $g_{r1}, g_{r2}$ と同一である。

## 【0075】

現在映像データ $g_{r1}, g_{r2}$ が直前映像データ $g_{r-1,1}, g_{r-1,2}$ と異なる場合、出力映像データ $g_{r1'}, g_{r2'}$ を現在映像データ $g_{r1}, g_{r2}$ より大きく、または小さくするので、相当する画素が目標輝度に速かに接近することができる。

## 【0076】

図7乃至図9を参照して、本発明の他の実施例による信号制御部について詳細に説明する。

10

20

30

40

50

## 【0077】

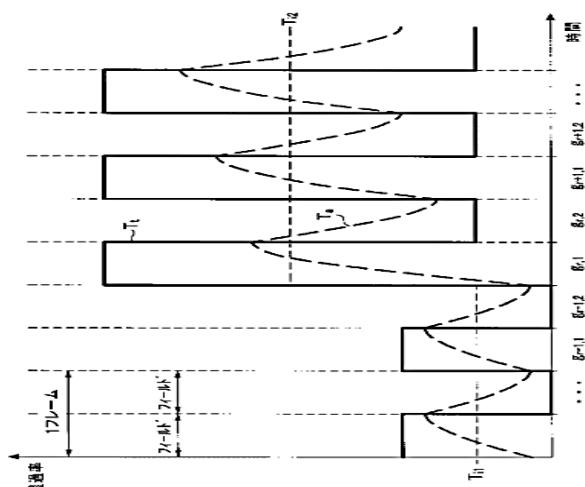

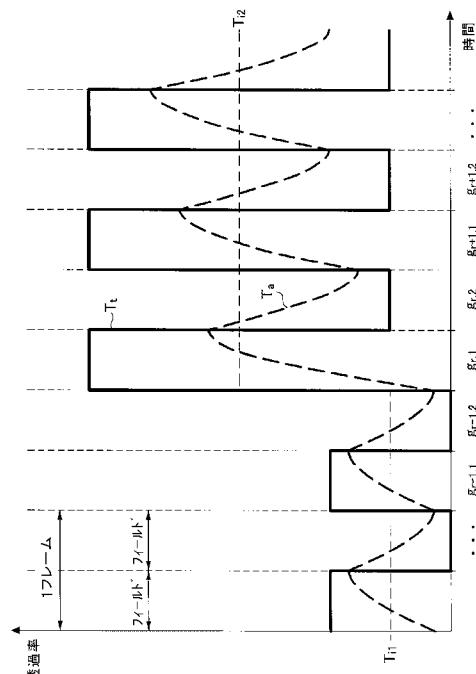

図7は、本発明の他の実施例による信号制御部のブロック図である。図8は、図7に示した信号制御部を含む液晶表示装置の時間に応じた透過率変化を示したグラフである。図9は、図3に示した信号制御部を含む液晶表示装置の時間に応じた透過率変化を示したグラフである。

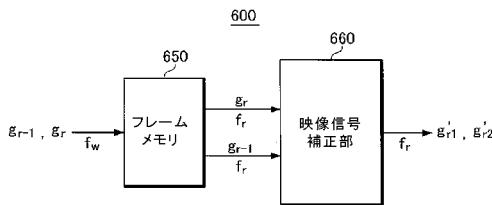

## 【0078】

まず、図7に示しているように、本実施例による信号制御部600はフレームメモリ650と、フレームメモリ650に連結されている映像信号補正部660とを含む。

## 【0079】

フレームメモリ650は、第1周波数 $f_w$ で入力される映像データを二つのフレームで記憶する。 10

## 【0080】

映像信号補正部660は、フレームメモリ650に記憶されている直前入力映像データ $g_{r-1}$ と現在入力映像データ $g_r$ とを第1周波数の2倍である第2周波数 $f_r$ で順次に読み込み、現在入力映像データ $g_r$ を直前入力映像データ $g_{r-1}$ と比較し、比較した結果によって、現在入力映像データ $g_r$ を第1及び第2出力映像データ $g_{r1}, g_{r2}$ に変換する。

## 【0081】

この時、第1出力映像データ $g_{r1}$ は、現在入力映像データ $g_r$ と直前入力映像データ $g_{r-1}$ との大きさの差によって、前記図6を参照して説明した第1臨時映像データ $g_{r1}$ （または、図3を参照して説明した映像信号補正部620の第1出力映像データ $g_{r1}$ ）より大きいか小さいか同一である。 20

## 【0082】

例えば、現在入力映像データ $g_r$ が直前入力映像データ $g_{r-1}$ より大きい場合、つまり、 $g_r > g_{r-1}$ である場合、第1出力映像データ $g_{r1}$ は第1臨時映像データ $g_{r1}$ より大きい。反対に、現在入力映像データ $g_r$ が直前入力映像データ $g_{r-1}$ より小さい場合、つまり、 $g_r < g_{r-1}$ である場合、第1出力映像データ $g_{r1}$ は第1臨時映像データ $g_{r1}$ より小さい。また、現在入力映像データ $g_{r1}, g_{r2}$ が直前入力映像データ $g_{r-1,1}, g_{r-1,2}$ と同一である場合、つまり、 $g_r = g_{r-1}$ である場合、第1出力映像データ $g_{r1}$ は第1臨時映像データ $g_{r1}$ と同一である。 30

## 【0083】

このように、現在入力映像データ $g_{r1}, g_{r2}$ が直前入力映像データ $g_{r-1,1}, g_{r-1,2}$ と異なる場合、第1出力映像データ $g_{r1}$ を第1臨時映像データ $g_{r1}$ より大きく、または小さくするので、相当する画素が目標輝度に速かに接近することができる。

## 【0084】

しかし、第2出力映像データ $g_{r2}$ を決める時には、第1出力映像データ $g_{r1}$ を求める方法であるDCCを適用しない。特に、第2出力映像データ $g_{r2}$ が0、または0に近い値であるとき、第2出力映像データ $g_{r2}$ が第2臨時映像データ $g_{r2}$ と同一であり得る。 40

## 【0085】

第2出力映像データ $g_{r2}$ は、実験などを通じて既に決められた値とするが、例えば、第1臨時映像データ $g_{r1}$ と第2臨時映像データ $g_{r2}$ とに相当するデータ電圧を、引続き画素に印加する時に得られる最終的な平衡状態の透過率曲線に、最も速く到達できる値に決める。具体的に説明すると、入力映像データが $r$ 番目フレームで、 $(r-1)$ 番目フレームから変わった後に、その次の $(r+1)$ 番目フレームからは変化しないと仮定する場合、最終的に示される平衡状態の透過率曲線が最も速い。可能であれば、 $(r+1)$ 番目フレームから示されるように第2出力映像データ $g_{r2}$ を決める。

## 【0086】

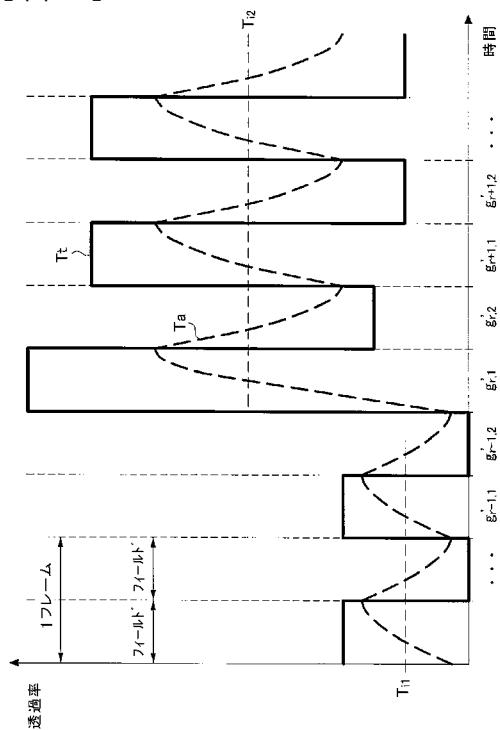

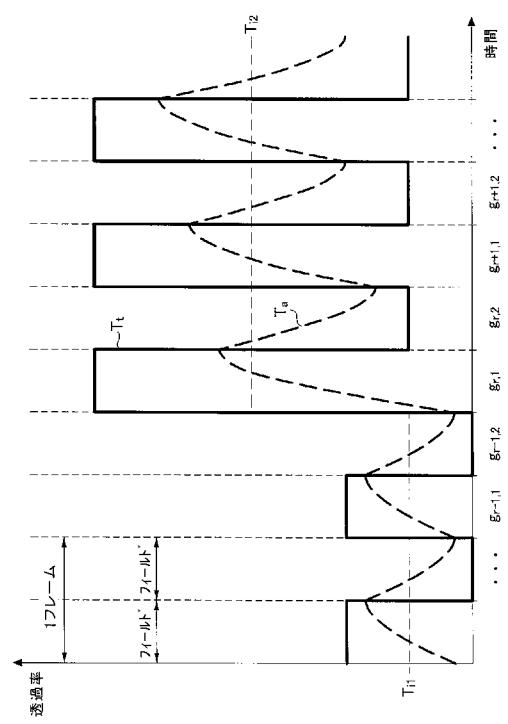

このように決められた第1及び第2出力映像データを適用した液晶表示装置の透過率が 50

図8に示した。図9は、図3を参照して説明した第1及び第2出力映像データを適用した液晶表示装置の透過率が示されている。

【0087】

図8及び図9において、 $T_{i_1}$ と $T_{i_2}$ は入力映像データを補正しなかった場合に現れる画素の予想透過率を示し、 $T_t$ は入力映像データを補正した場合に現れる画素の予想透過率を示し、 $T_a$ は入力映像データを補正した場合に現れる画素の実際透過率を示す。 $T_t$ と $T_a$ が異なることは、液晶の応答速度が遅いためである。したがって、DCC処理を行うわけである。

【0088】

図8に示しているように、第1出力映像データに対しては、DCCを適用し、第2出力映像データに対しては、DCCを適用せずに平衡状態に速く到達できるようにする値に決めた場合、入力映像データが変化した $r$ 番目フレームの直後フレームである( $r+1$ )番目フレームから透過率曲線 $T_a$ が平衡状態に到達する。

【0089】

これに反し、DCCを全く適用しなかった図9では、透過率曲線 $T_a$ はいくつものフレーム間で引続き変化する。

【0090】

一つの入力映像データを二つの出力映像データに変換する場合について、上述の通り説明したが、その他の場合にも上述した説明で適用できる。例えば、一つの映像データを三つの出力映像データに変換する場合、出力周波数は入力周波数の3倍になって、最大輝度を与える出力映像データのみにDCCを適用し、残りは実験やその他によって得たものであり得る。また、四つの入力映像データを3対の出力映像データに変換することもでき、この時にもDCCは最も大きい値に対してのみ適用できる。

【0091】

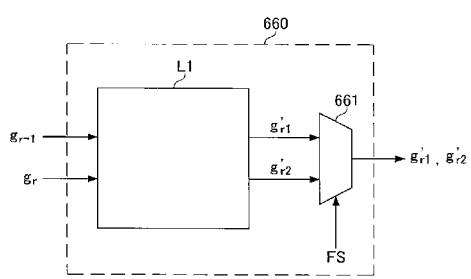

次に、図10及び図11を参照して、図7に示した映像信号補正部の例について詳細に説明する。

【0092】

図10及び図11は、図7に示した映像信号補正部のブロック図の例である。

【0093】

図10に示した映像信号補正部660は、ルックアップテーブルL1と、ルックアップテーブルL1と連結されていてフィールド選択信号FSの入力を受けるマルチブレクサー661とを含む。フィールド選択信号FSは、多様な方式で決めることができるが、単純にフィールドの奇数偶数で決める、またはカウンターなどを使って決めることもできる。また、このフィールド選択信号FSは、信号制御部600内部で生成されることもできるし、外部から提供されてもよい。

【0094】

ルックアップテーブルL1には、図7を参照して上述に説明した方法と同じ方法で求めた第1及び第2出力映像データ $g_{r_1}$ 、 $g_{r_2}$ が直前入力映像データ $g_{r-1}$ と現在入力映像データ $g_r$ の関数で記憶されている。したがって、ルックアップテーブルL1は直前入力映像データ $g_{r-1}$ と現在入力映像データ $g_r$ に対応する第1及び第2出力映像データ $g_{r_1}$ 、 $g_{r_2}$ をマルチブレクサー661に出力する。

【0095】

マルチブレクサー661は、フィールド選択信号FSの値によってルックアップテーブルL1からの第1及び第2出力映像データ $g_{r_1}$ 、 $g_{r_2}$ の中で一つを選択して出力する。

【0096】

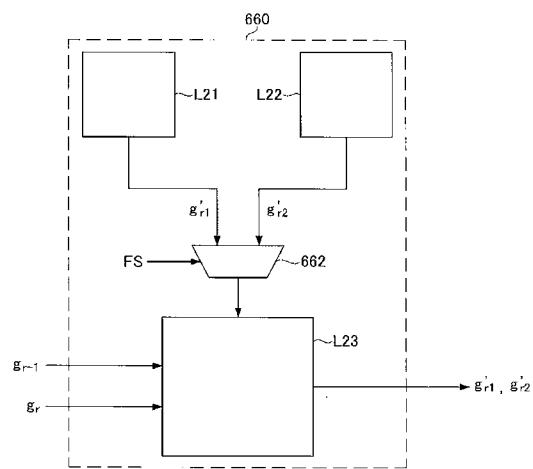

図11に示した映像信号補正部660は、第1ルックアップテーブルL21と、第2ルックアップテーブルL22と、ルックアップテーブルL21及びL22に連結されていてフィールド選択信号FSの入力を受けるマルチブレクサー662と、マルチブレクサー662に連結された第3ルックアップテーブルL23とを含む。

10

20

30

40

50

## 【0097】

第1ルックアップテーブルL21及び第2ルックアップテーブルL22には、図7を参照して上述に説明した方法と同じ方法で求めた第1及び第2出力データ $g_{r11}$ 、 $g_{r21}$ が各々記憶されている。

## 【0098】

マルチプレクサー662は、一つのフィールドが終わって次のフィールドが始まる前にフィールド選択信号FS値によって、第1ルックアップテーブルL1及び第2ルックアップテーブルL22からの第1及び第2出力映像データ $g_{r11}$ 、 $g_{r21}$ の中で一つを選択して出力する。

## 【0099】

第3ルックアップテーブルL23は、マルチプレクサー662からの第1及び第2出力映像データ $g_{r11}$ 、 $g_{r21}$ を直前入力映像データ $g_{r-11}$ と現在入力映像データ $g_r$ の関数で記憶し、入力された直前入力映像データ $g_{r-11}$ と現在入力映像データ $g_r$ に対応する第1もしくは第2出力映像データ $g_{r11}$ 、 $g_{r21}$ を出力する。

## 【0100】

この場合、原色、例えば赤色、緑色及び青色の三原色別に同ルックアップテーブルを使用し、これら三原色のDCC変換が同時に行われると、全ルックアップテーブルの大きさを縮小するのに有利である。

## 【0101】

以下に、図12及び図14を参照して、図7に示した信号制御部を含む液晶表示装置において、出力映像データを決める他の方法について詳細に説明する。

## 【0102】

本実施例では、ルックアップテーブルに直前映像データ及び現在映像データの一部値（または階調）に対して出力映像データと関する係数が記憶されており、映像信号補正部は、この係数を使用して出力映像データを求める。これについて詳細に説明する。

## 【0103】

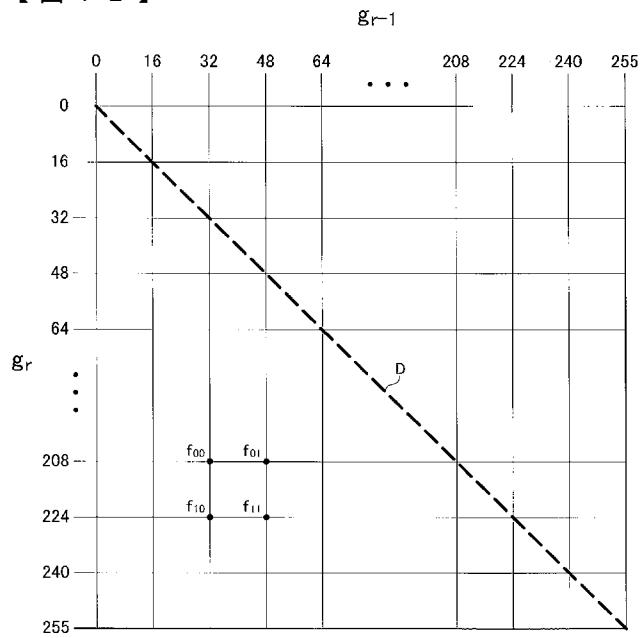

図12は、図7に示した信号制御部を含む液晶表示装置で出力映像データを決める他の方法を説明するための図面である。

## 【0104】

説明の便宜のために、入力映像データがxビットの上位ビット(MSB)とyビットの下位ビット(LSB)からなると仮定する。

## 【0105】

例えば、8ビット映像信号の場合、階調数が256個であるので、直前入力映像データ $g_{r-11}$ と現在入力映像データ $g_r$ の組み合わせは全て $256 \times 256 = 65,536$ 個となる。多くの数の組み合わせ各々に対して最終出力映像データ $g_{r11}$ 、 $g_{r21}$ をルックアップテーブルに記憶しておくことは、時間的、空間的に無理がある。したがって、直前入力映像データ及び現在入力映像データの一部対に対する出力映像データ $g_{r11}$ 、 $g_{r21}$ をルックアップテーブルに記憶しておき、これを基準に、残り対に対する出力映像データ $g_{r11}$ 、 $g_{r21}$ を求める方式を補間という。特に下位ビットが0である直前入力映像データ及び現在入力映像データの対に対する出力映像データ $g_{r11}$ 、 $g_{r21}$ を記憶しておいて、これを基準に他の入力映像データ対に対する出力映像データ $g_{r11}$ 、 $g_{r21}$ を求めるることは比較的に簡単である。

## 【0106】

8ビット映像データである場合、上位ビットのビット数は4または3とすることができるが、上位ビットのビット数が4である場合、 $17 \times 17$ の入力映像データ対、3である場合には $9 \times 9$ の入力データ対に対する出力映像データ $g_{r11}$ 、 $g_{r21}$ のみを記憶すればよい。

## 【0107】

上位ビットのビット数が4である場合に対して、図12に示したように、横軸と縦軸に各々直前入力映像データ $g_{r-11}$ と現在入力映像データ $g_r$ を配置してみる。

10

20

30

40

50

## 【0108】

図12における実線で区画された正方形領域は、直前入力映像データ $g_{r-1}$ と現在入力映像データ $g_r$ の上位ビットの値を基準に分けられたブロックである。ブロックの境界に存在する点は、直前入力映像データ $g_{r-1}$ または現在入力映像データ $g_r$ の下位ビットが0の点である。直前入力映像データ $g_{r-1}$ と現在入力映像データ $g_r$ 全てに対して各ブロック内に存在する点の上位ビットは全て同一であり、左側辺と上側辺上に位置する点もブロック内部の点と同一な上位ビットを有する。ただし、右側辺と下側辺上に存在する点の上位ビットは、ブロック内部点の上位ビットと相異なる。

## 【0109】

各ブロックの頂点に対しては、出力映像データが与えられ、これを基準データ $f$ と称する。例えば、図12は、一つのブロックを定義する四つの頂点に対する出力映像データを $f_{00}$ 、 $f_{01}$ 、 $f_{10}$ 、 $f_{11}$ で示している。頂点でない点に対する出力映像データは、これらと下位ビットの関数で与えられる演算を通じて求める。

## 【0110】

このような補間法の例を以下に説明する。

## 【0111】

現在入力映像データ $g_r$ の上位ビット及び下位ビットを各々 $g_r[x+y-1:y]$ 、 $g_r[y-1:0]$ とし、直前入力映像データ $g_{r-1}$ の上位ビット及び下位ビットを各々 $g_{r-1}[x+y-1:y]$ 、 $g_{r-1}[y-1:y]$ とすれば、基準データ $f$ は以下の数式(2)で示すことができる。

## 【0112】

$$f(g_r[x+y-1:y], g_{r-1}[x+y-1:y]) = g_r \cdot (g_r[x+y-1:y] \times 2^y + g_{r-1}[x+y-1:y] \times 2^y) \dots (2)$$

ここで、 $g_r \cdot$  は $g_{r-1} \cdot$  または $g_{r-2} \cdot$  である。

## 【0113】

上述した図12のブロック内点に対する出力映像データ $g_r \cdot$  は次の数式(3)のような補間法で与えられる。

## 【0114】

$$g = f_{00} + p \times g_{r-1}[y-1:0] / 2^y + q \times g_r[y-1:0] / 2^y + r \times g_{r-1}[y-1:0] \times g_r[y-1:0] / 2^{2y} \dots (3)$$

ここで、 $p$  と  $q$  は各々直前入力映像信号 $g_{r-1}$ と現在入力映像データ $g_r$ の下位ビットをブロック間隔 $2^y$ で分けた値である( $0 \leq p < 1$ 、 $0 \leq q < 1$ )。

## 【0115】

ここで、 $p$ 、 $q$ 、 $r$ は以下の数式(4)、(5)、(6)で示す。

## 【0116】

$$p(g_r[x+y-1:y], g_{r-1}[x+y-1:y]) = f_{01} - f_{00} = f(g_r[x+y-1:y], g_{r-1}[x+y-1:y] + 1) - f(g_r[x+y-1:y], g_{r-1}[x+y-1:y]) \dots (4)$$

$$q(g_r[x+y-1:y], g_{r-1}[x+y-1:y]) = f_{10} - f_{00} = f(g_r[x+y-1:y] + 1, g_{r-1}[x+y-1:y]) - f(g_r[x+y-1:y], g_{r-1}[x+y-1:y]) \dots (5)$$

$$r(g_r[x+y-1:y], g_{r-1}[x+y-1:y]) = f_{00} + f_{11} - f_{01} - f_{10} = f(g_r[x+y-1:y], g_{r-1}[x+y-1:y] + 1, g_{r-1}[x+y-1:y] + 1) - f(g_r[x+y-1:y], g_{r-1}[x+y-1:y] + 1) - f(g_r[x+y-1:y] + 1, g_{r-1}[x+y-1:y]) \dots (6)$$

ルックアップテーブルには、基準データ $f$ のみを記憶しておき、その他の $p$ 、 $q$ 、および $r$ などの係数は、演算を通じて求めることができる。しかし、演算時間が長くかかる短所があるため、基準データ $f$ の他にも $p$ 、 $q$ 、および $r$ などの係数を記憶しておけば演算時間が節約される。

## 【0117】

このような方式によって、入力映像データ  $g_r$  に対する第1出力映像データ  $g_{r_1}$  と第2出力映像データ  $g_{r_2}$  を求める。ただし、前記数式は一つの例に過ぎず、他の方法で補間を行ってもよい。

## 【0118】

図13と図14には、このような原理に基づいて補正を行う映像信号補正部の例が示されている。

## 【0119】

図13及び図14は、本発明の他の実施例による映像信号補正部のブロック図の例である。

10

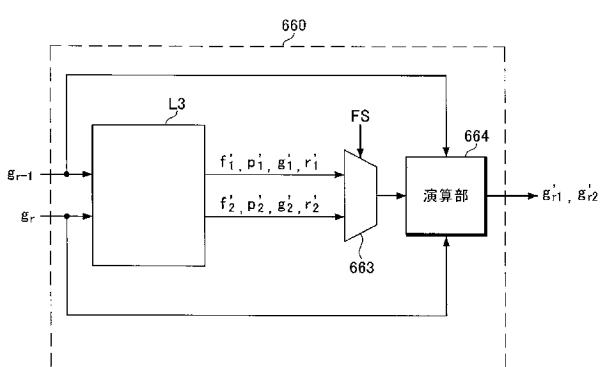

## 【0120】

図13に示した映像信号補正部660は、ルックアップテーブルL3と、これに連結されていてフィールド選択信号FSの入力を受けるマルチブレクサー663と、マルチブレクサー663に連結されていて直前映像データ  $g_{r-1}$  及び現在入力映像データ  $g_r$  の入力を受ける演算部664とを含む。

## 【0121】

ルックアップテーブルL3には、第1出力映像データ  $g_{r_1}$  に対する基準データ  $f_1$  及び係数  $p_1$ 、  $q_1$ 、  $r_1$  (以下、二つを合せて第1補正係数と言う)と、第2出力映像データ  $g_{r_2}$  に対する基準データ  $f_2$  及び係数  $p_2$ 、  $q_2$ 、  $r_2$  (以下、二つを合せて第2補正係数と言う)とが直前入力映像データ  $g_{r-1}$  と現在入力映像データ  $g_r$  の関数で記憶されている。したがって、ルックアップテーブルL3は、直前入力映像データ  $g_{r-1}$  と現在入力映像データ  $g_r$  に応答して、これに対応する第1補正係数  $f_1$ 、  $p_1$ 、  $q_1$ 、  $r_1$  と第2補正係数  $f_2$ 、  $p_2$ 、  $q_2$ 、  $r_2$  をマルチブレクサー663に出力する。

20

## 【0122】

マルチブレクサー663は、フィールド選択信号FS値によってルックアップテーブルL1からの第1補正係数  $f_1$ 、  $p_1$ 、  $q_1$ 、  $r_1$  と第2補正係数  $f_2$ 、  $p_2$ 、  $q_2$ 、  $r_2$  のうちの一つを選択して出力する。

## 【0123】

演算部664は、マルチブレクサー663からの第1または第2補正係数  $f_1$ 、  $p_1$ 、  $q_1$ 、  $r_1$ 、  $f_2$ 、  $p_2$ 、  $q_2$ 、  $r_2$  と直前及び現在入力映像データ  $g_{r-1}$ 、  $g_r$  の下位ビットの入力を受けて数式(3)の演算を行い、第1出力映像データ  $g_{r_1}$  や第2出力映像データ  $g_{r_2}$  を生成して出力する。

30

## 【0124】

このように補間法によって出力映像データ  $g_{r_1}$ 、  $g_{r_2}$  を生成すれば、ルックアップテーブルの大きさとデータ処理時間などを大きく縮小することができる。

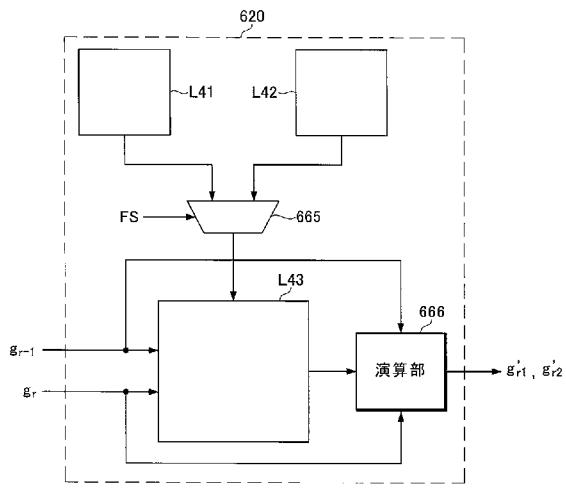

## 【0125】

図14に示した映像信号補正部660は、第1ルックアップテーブルL41と、第2ルックアップテーブルL42と、これらルックアップテーブルL41及びL42に各々連結されていてフィールド選択信号FSの入力を受けるマルチブレクサー665と、マルチブレクサー665に連結されていて直前入力映像データ  $g_{r-1}$  と現在入力映像データ  $g_r$  の入力を受ける第3ルックアップテーブルL43と、第3ルックアップテーブルL43に連結されていて直前入力映像データ  $g_{r-1}$  と現在入力映像データ  $g_r$  の入力を受ける演算部666と、を含む。

40

## 【0126】

第1ルックアップテーブルL41及び第2ルックアップテーブルL42には上述した第1及び第2補正係数が各々記憶されている。

## 【0127】

マルチブレクサー665は、一つのフィールドが終わって次のフィールドが始まる前にフィールド選択信号FS値によって第1ルックアップテーブルL41及び第2ルックアップテーブルL42からの第1及び第2補正係数の中で一つを選択して出力する。

50

## 【0128】

第3ルックアップテーブルL43は、マルチプレクサー663からの第1または第2補正係数を直前入力映像データ $g_{r-1}$ と現在入力映像データ $g_r$ の関数で記憶し、入力された直前入力映像データ $g_{r-1}$ と現在入力映像データ $g_r$ に応答して相当する第1または第2補正係数を出力する。

## 【0129】

演算部666は、マルチプレクサー665からの第1または第2補正係数 $f_1, p_1, q_1, r_1, f_2, p_2, q_2, r_2$ と直前及び現在入力映像データ $g_{r-1}, g_r$ の下位ビットの入力を受けて式(3)の演算を行い、第1出力映像データ $g_{r-1}$ 、または第2出力映像データ $g_{r-2}$ を生成して出力する。

10

## 【0130】

この場合にも、図11に示しているように、例えば、赤色、緑色及び青色の三原色別に同ルックアップテーブルを使用し、これら三原色のDCC変換が同時に行われる場合、全ルックアップテーブルの大きさを縮小するのに有利である。

## 【0131】

上述に、一つの入力映像データを二つの出力映像データに変換する場合について説明したが、その他の場合にも上述した説明で適用できる。例えば、一つの映像データを三つの出力映像データに変換することができ、この時出力周波数は入力周波数の3倍になり、最大輝度を与える出力映像データのみDCCを適用し得て、残りは実験やその他によって得られたものであってもよい。これとは異なって、四つの入力映像データを3対の出力映像データに変換することもでき、この時にもDCCは最も大きい値に対してのみ適用できる。

20

## 【0132】

以上、本発明の好ましい実施例について詳細に説明したが、本発明の権利範囲はこれに限定されず、請求範囲で定義している本発明の基本概念を利用した当業者の様々な変形及び改良形態もまた本発明の権利範囲に属する。

## 【図面の簡単な説明】

## 【0133】

【図1】本発明の一実施例による液晶表示装置のブロック図である。

30

【図2】本発明の一実施例による液晶表示装置の一つの画素に対する等価回路図である。

【図3】本発明の一実施例による液晶表示装置の構造図である。

【図4】図3に示した信号制御部を含む液晶表示装置における映像データの補正前ガンマ曲線及び補正後ガンマ曲線を示したグラフである。

【図5】図3に示した信号制御部を含む液晶表示装置における映像データを補正前データ電圧と補正後データ電圧を示した波形図である。

40

【図6】本発明の他の実施例による信号制御部のブロック図である。

【図7】本発明の他の実施例による信号制御部のブロック図である。

【図8】図7に示した信号制御部を含む液晶表示装置の時間に伴う透過率変化を示したグラフである。

【図9】図3に示した信号制御部を含む液晶表示装置の時間に伴う透過率変化を示したグラフである。

【図10】図7に示した映像信号補正部ブロック図の例である。

【図11】図7に示した映像信号補正部ブロック図の例である。

【図12】図7に示した信号制御部を含む液晶表示装置における出力映像データを決める他の方法を説明するための図面である。

【図13】本発明の他の実施例による映像信号補正部ブロック図の例である。

【図14】本発明の他の実施例による映像信号補正部ブロック図の例である。

## 【符号の説明】

## 【0134】

100、200 基板、

230 色フィルター、

270 共通電極、

300 液晶表示板組立体、

400 ゲート駆動部、

500 データ駆動部、

600 信号制御部、

800 階調電圧生成部、

G<sub>1</sub> - G<sub>n</sub> ゲート線、

D<sub>1</sub> - D<sub>m</sub> データ線、

Q スイッチング素子、

C<sub>L</sub> C 液晶キャパシタ、

C<sub>S</sub> T ストレージキャパシタ、

610 フレームメモリ、

620 映像補正部、

630、642、650 フレームメモリ、

640 映像信号補正部、

641 信号変換部、

643 DCC処理部、

660 映像信号補正部、

10 L21、L22、L23、L41、L42、L43 ルックアップテーブル、

662、663、665 マルチプレクサー、

664、666 演算部。

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【 図 1 4 】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 1 2 U |

| G 0 9 G | 3/20 | 6 4 1 P |

| G 0 9 G | 3/20 | 6 4 1 Q |

| G 0 9 G | 3/20 | 6 3 1 V |

| G 0 9 G | 3/20 | 6 1 1 E |

| G 0 9 G | 3/20 | 6 3 1 R |

(72)発明者 李 白 雲

大韓民国京畿道龍仁市新鳳洞 新エルジー 1次ビルレッジ 104棟 902号

F ターム(参考) 2H093 NC24 NC29 NC34 NC35 NC50 ND01 ND10 ND32

|       |      |      |      |      |      |      |      |      |      |      |

|-------|------|------|------|------|------|------|------|------|------|------|

| 5C006 | AA16 | AF03 | AF04 | AF05 | AF13 | AF44 | AF45 | AF46 | BB16 | BC16 |

| BF02  | BF08 | FA12 | FA14 | FA23 |      |      |      |      |      |      |

| 5C080 | AA10 | BB05 | DD06 | DD08 | EE19 | EE29 | FF07 | FF11 | GG09 | GG15 |

| GG17  | JJ02 | JJ04 | JJ05 |      |      |      |      |      |      |      |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置和显示装置的驱动装置                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 公开(公告)号        | <a href="#">JP2006171749A</a>                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2006-06-29 |

| 申请号            | JP2005358295                                                                                                                                                                                                                                                                                                                                                                                                                       | 申请日     | 2005-12-12 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 李白雲                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 李白雲                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G09G3/3648 G09G3/2025 G09G3/2081 G09G3/2092 G09G2320/0252 G09G2320/0285 G09G2340/16 G09G2360/16 G09G2360/18                                                                                                                                                                                                                                                                                                                        |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.660.V G09G3/20.621.F G09G3/20.650.J G09G3/20.612.U G09G3/20.641.P G09G3/20.641.Q G09G3/20.631.V G09G3/20.611.E G09G3/20.631.R                                                                                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 2H093/NC24 2H093/NC29 2H093/NC34 2H093/NC35 2H093/NC50 2H093/ND01 2H093/ND10 2H093/ND32 5C006/AA16 5C006/AF03 5C006/AF04 5C006/AF05 5C006/AF13 5C006/AF44 5C006/AF45 5C006/AF46 5C006/BB16 5C006/BC16 5C006/BF02 5C006/BF08 5C006/FA12 5C006/FA14 5C006/FA23 5C080/AA10 5C080/BB05 5C080/DD06 5C080/DD08 5C080/EE19 5C080/EE29 5C080/FF07 5C080/FF11 5C080/GG09 5C080/GG15 5C080/GG17 5C080/JJ02 5C080/JJ04 5C080/JJ05 2H193 /ZA04 |         |            |

| 代理人(译)         | 宇谷 胜幸                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 优先权            | 1020040104572 2004-12-11 KR                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

### 摘要(译)

通过增加像素的充电速度来改善显示装置的图像质量。液晶显示装置技术领域本发明涉及一种液晶显示装置，包括：以矩阵形式排列的多个像素；信号控制单元，用于将第一频率的输入图像数据转换为第二频率的多个输出图像数据，并输出转换后的图像数据；以及数据驱动器，用于将来自信号控制器的每个输出图像数据转换为与其对应的模拟数据电压，并顺序地将模拟数据电压施加到像素，其中，对输出图像数据中的像素给予最大亮度通过将输入视频数据与前一帧的输入视频数据进行比较来确定输出视频数据。结果，当将输入图像数据转换为多个输出图像数据时，液晶的响应速度增加，并且防止了诸如闪烁现象的图像质量缺陷。

9系统技术领域