(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-61552

(P2004-61552A)

(43) 公開日 平成16年2月26日(2004.2.26)

(51) Int. Cl. 7

**G09G 3/36**

**G02F 1/133**

**G09G 3/20**

F 1

G09G 3/36

G02F 1/133 550

G09G 3/20 612E

G09G 3/20 612T

G09G 3/20 621A

テーマコード(参考)

2H093

5C006

5C080

審査請求 未請求 請求項の数 2 O L (全 13 頁) 最終頁に続く

(21) 出願番号

特願2002-215736 (P2002-215736)

(22) 出願日

平成14年7月24日 (2002.7.24)

(71) 出願人 000004329

日本ビクター株式会社

神奈川県横浜市神奈川区守屋町3丁目12

番地

(74) 代理人 100085235

弁理士 松浦 兼行

(72) 発明者 古屋 正人

神奈川県横浜市神奈川区守屋町3丁目12

番地 日本ビクター株式会社内F ターム(参考) 2H093 NA16 NA33 NC09 NC11 NC16

NC22 NC34 NC41 ND08 ND20

ND60 NE03 NG02 NH15

最終頁に続く

(54) 【発明の名称】アクティブマトリクス型液晶表示装置

## (57) 【要約】

【課題】従来装置は、視覚上、前フレームの残像が時間的な干渉により、動きボケとして知覚され易く、動画像の解像度が劣化してしまうという問題や、液晶の印加電圧・時間応答の問題がある。

【解決手段】アクティブマトリクス型液晶表示装置は、1フレーム期間(1垂直走査期間)中に、第1のシフトレジスタSR1の出力パルスに基づく行選択パルス発生時の各画素回路に表示信号を書き込み保持する表示信号期間と、第2のシフトレジスタSR2の出力パルスに基づく、行選択パルス発生時の所定の基準電圧にリセットするリセット期間を設ける。表示信号期間とリセット期間の時間の割合は、SR1に入力する走査開始タイミング信号WTに対する、SR2に入力する走査開始タイミング信号Resetの遅延ライン期間数nを任意に変えることにより、水平走査時間を単位として任意に設定することができる。

【選択図】

図1

**【特許請求の範囲】****【請求項 1】**

互いに直交する複数の列信号電極及び複数の行走査電極と、前記複数の列信号電極に表示信号を順次サンプリングする列信号電極駆動回路と、前記複数の行走査電極に行選択パルスを供給する行走査電極駆動回路と、前記列信号電極および行走査電極の各交差部にそれぞれ設けられマトリクス状に配列された複数の表示画素とを備え、前記列信号電極駆動回路により、前記複数の表示画素への前記表示信号のサンプリングを1ライン期間内で行方向の表示画素に対して順次に行うと共に、前記行走査電極駆動回路により、前記複数の表示画素の選択をライン順次に行うアクティブマトリクス型液晶表示装置において、各行の前記表示画素に対して、1フレーム期間における前記表示信号を書き込み保持する表示信号期間と、所定の基準レベルにリセットするリセット期間を、任意の割合で設ける制御手段を有することを特徴とするアクティブマトリクス型液晶表示装置。10

**【請求項 2】**

前記制御手段は、前記表示信号の各水平期間のうち、画像情報を含まない水平ブランкиング期間の一部または全期間を前記所定の基準レベルに設定するレベル設定手段と、前記列信号電極駆動回路を構成するスイッチング回路群の全てを前記表示信号の画像情報を含まない前記リセット期間中にオン状態として、すべての前記複数の列信号電極に、前記レベル設定手段からの前記所定の基準レベルを出力させる基準レベル出力手段と、前記列信号電極駆動回路から前記複数の列信号電極に前記表示信号が順次に供給されている第1の期間に統いて、前記複数の列信号電極に前記基準レベル出力手段から前記所定の基準レベルが供給されている第2の期間の各々に対応して前記行走査電極駆動回路から出力する前記行選択パルスを前記複数の行走査電極に対して、1フレーム期間内で画像情報を含む総レベルが所定のレベル範囲内に收まるように行選択パルスを出力する行選択パルス出力手段とからなることを特徴とする請求項1記載のアクティブマトリクス型液晶表示装置。20

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明はアクティブマトリクス型液晶表示装置に係り、特に投射型液晶ディスプレイ等に適用して好適なアクティブマトリクス型液晶表示装置に関する。30

**【0002】****【従来の技術】**

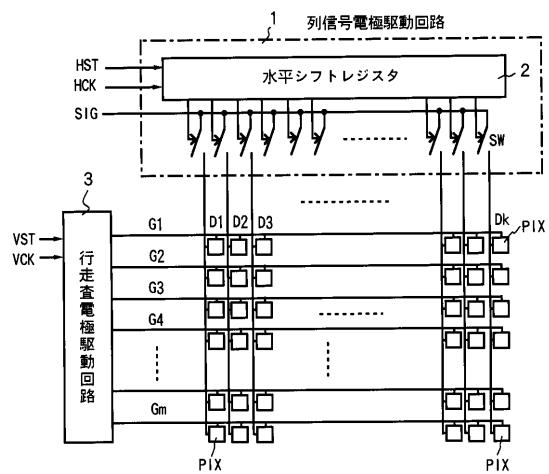

図8は従来のアクティブマトリクス型液晶表示装置の一例の構成図を示す。同図において、複数の列信号電極(D1、D2、・・・)および複数の行走査電極(G1、G2、・・・)が互いに直交する方向に形成されており、それらの各交差部には表示画素PIXが形成されている。すなわち、複数の表示画素PIXは二次元マトリクス状に配列されている。40

**【0003】**

列信号電極駆動回路1は水平シフトレジスタ2およびスイッチ回路群SWより構成されている。水平シフトレジスタ2の各出力段はスイッチ回路群SWの各制御端子に接続され、スイッチ回路群SWの各スイッチ入力側端子は表示信号SIG入力端子に共通接続され、スイッチ回路群SWの各スイッチ出力側端子は前記列信号電極(D1、D2、・・・)の各々に別々に接続されている。すなわち、列信号電極がk個あれば、スイッチ回路群SWはk個のスイッチ回路が設けられ、水平シフトレジスタ2の出力段がk段あることになる。50

**【0004】**

水平シフトレジスタ2には、図示しない駆動タイミング生成回路より水平スタート信号HST及び水平クロック信号HCKが供給される。水平シフトレジスタ2の各出力ビットからはスイッチ回路群SWの各制御端子に対し、順次オンパルスを送出し、スイッチ回路群SWの各スイッチ回路を順次オン状態とすることにより、表示信号SIG入力端子からの表示信号SIGを対応する列信号電極Dに順次サンプリングする。50

## 【0005】

行走査電極駆動回路3はシフトレジスタで構成され、そのシフトレジスタの各出力段が前記行走査電極(G1、G2、・・・)の各々に1対1に対応して接続されている。行走査電極駆動回路3を構成するシフトレジスタには、駆動タイミング生成回路(図示せず)より垂直スタート信号VST及び垂直クロック信号VCKを供給し、対応する行走査電極に順次行選択パルスを送出する。

## 【0006】

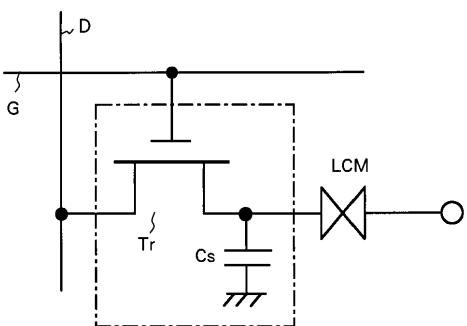

列信号電極と行走査電極の各交差部には、図9に示す構成の表示画素が接続されている。図9の表示画素は、スイッチングトランジスタTr、補助容量Cs、表示画素電極(図示せず)および液晶表示体LCMで構成されている。行走査電極Gの行選択パルスが供給されると、対応する行の表示画素のスイッチングトランジスタTrがオンとなり、列信号電極Dにサンプリングした表示信号がスイッチングトランジスタTrを介して補助容量Csに蓄積されると共に、液晶表示体LCMに供給されてこれを駆動する。補助容量CsはスイッチングトランジスタTrがオフの期間での液晶駆動電圧を保持し、高デューティ駆動を実現する目的で構成される。

## 【0007】

## 【発明が解決しようとする課題】

上記の従来のアクティブマトリクス型液晶表示装置においては、図9に示したように、画素回路毎にスイッチングトランジスタTrが形成され、各画素の表示信号電圧を補助容量Csに保持して表示を行う。このような信号電圧および表示情報を次フレームの書き換えまでほぼ完全に保持するホールド型表示方式では、原理的に以下の問題がある。

## (1) 人間の視覚特性に基づく動画解像度劣化

人間の視覚は一種の時間応答フィルタであり、刺激に対して応答するのにある時間遅れ特性をもつ。映像機器における動画像再生原理は、対象物の位置が空間的に異なる静止画像を走査またはコマで高速に切り換えて表示し、人間の視覚には結果的にそれらが連続した動きとして知覚される「残像効果」によっているが、アクティブマトリクス型液晶表示装置のようなホールド型ディスプレイでは、フレーム更新の直前まで前フレーム画像が表示されており、視覚上、前フレームの残像が時間的な干渉により、動きボケとして知覚され易く、動画像の解像度が劣化してしまうという問題がある。

## (2) 液晶の印加電圧・時間応答の問題

液晶の時間応答特性は液晶のセルギャップ、粘性係数および弾性定数等により決定されるが、特にしきい値電圧以上の中間調領域に相当する印加電圧の変化に対して応答時間が遅くなるという欠点があり、これが動画解像度を劣化させる要因となる。

## 【0008】

本発明は以上の点に鑑みなされたもので、線順次走査で書き込まれる各行の画素信号を、表示パネルの1フレーム書き込み期間より短い時間で基準電圧に順次リセットすることで、動画解像度劣化が小さいアクティブマトリクス型液晶表示装置を提供することを目的とする。

## 【0009】

また、本発明の他の目的は、各行の画素信号の信号電圧期間とリセット期間の割合を簡易な構成で任意に設定でき、明るさ優先、動画特性優先、といった異なるシステム要求や表示モードに対応可能なアクティブマトリクス型液晶表示装置を提供することにある。

## 【0010】

## 【課題を解決するための手段】

本発明は、上記の目的を達成するため、互いに直交する複数の列信号電極及び複数の行走査電極と、複数の列信号電極に表示信号を順次サンプリングする列信号電極駆動回路と、複数の行走査電極に行選択パルスを供給する行走査電極駆動回路と、列信号電極および行走査電極の各交差部にそれぞれ設けられマトリクス状に配列された複数の表示画素とを備え、列信号電極駆動回路により、複数の表示画素への表示信号のサンプリングを1ライン期間内で行方向の表示画素に対して順次に行うと共に、行走査電極駆動回路により、複数

10

20

30

40

50

の表示画素の選択をライン順次に行うアクティブマトリクス型液晶表示装置において、各行の表示画素に対して、1フレーム期間における表示信号を書き込み保持する表示信号期間と、所定の基準レベルにリセットするリセット期間を、任意の割合で設ける制御手段を有する構成としたものである。

【0011】

この発明では、各行の表示画素が1フレーム期間内で、表示信号を書き込み保持した後、所定の基準レベルにリセットされると共に、1フレーム期間内の表示信号期間とリセット期間との割合を任意の割合で設定することができる。

【0012】

また、上記の目的を達成するため、本発明は、上記の制御手段を、表示信号の各水平期間のうち、画像情報を含まない水平プランキング期間の一部または全期間を所定の基準レベルに設定するレベル設定手段と、列信号電極駆動回路を構成するスイッチング回路群の全てを表示信号の画像情報を含まないリセット期間中にオン状態として、すべての複数の列信号電極に、レベル設定手段からの所定の基準レベルを出力させる基準レベル出力手段と、列信号電極駆動回路から複数の列信号電極に表示信号が順次に供給されている第1の期間に統いて、複数の列信号電極に基準レベル出力手段から所定の基準レベルが供給されている第2の期間の各々に対応して行走査電極駆動回路から出力する行選択パルスを複数の行走査電極に対して、1フレーム期間内で画像情報を含む総レベルが所定のレベル範囲内に収まるように行選択パルスを出力する行選択パルス出力手段とから構成したものである。

10

20

【0013】

【発明の実施の形態】

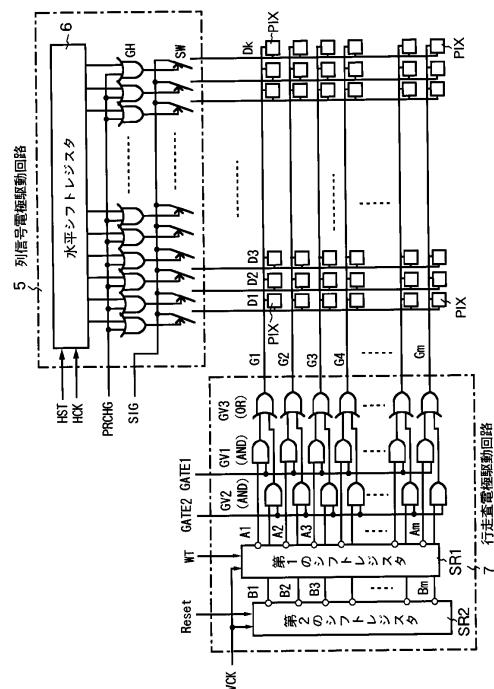

次に、本発明の実施の形態について図面と共に説明する。図1は本発明になるアクティブマトリクス型液晶表示装置の一実施の形態の回路構成図を示す。同図において、複数の列信号電極(D1、D2、…、Dk)及び複数の行走査電極(G1、G2、…、Gm)が互いに直交する方向に形成されており、それらの各交差部には表示画素PIXが形成されている。すなわち、複数の表示画素PIXは二次元マトリクス状に配列されている。

【0014】

列信号電極駆動回路5は水平シフトレジスタ6、スイッチ回路群SW、およびk個の2入力ORゲートからなるゲート回路群GHより構成されている。水平シフトレジスタ6のk個の各出力ビット端子は、ゲート回路群GHを構成する各2入力ORゲートのうち対応する一の2入力ORゲートの一方の入力端子に接続され、ゲート回路群GHを構成する全2入力ORゲートの他方の入力端子は共通にゲート信号PRCHG入力端子に接続され、更に、各2入力ORゲートの出力端子はスイッチ回路群SWを構成する対応する一のスイッチ回路の制御端子に別々に接続されている。

30

【0015】

スイッチ回路群SWを構成する全部でk個のスイッチ回路の入力側端子は表示信号SIG入力端子に共通接続され、各スイッチ回路の出力端子は前記列信号電極(D1、D2、…、Dk)の各々に1対1に対応して接続されている。

40

【0016】

水平シフトレジスタ6には、図示しない駆動タイミング生成回路より水平スタート信号HST及び水平クロック信号HCKが供給される。水平シフトレジスタ6はこれらの信号HST及びHCKに基づいて駆動され、これにより水平シフトレジスタの各出力ビット端子からは、ゲート回路群GH中の対応する2入力ORゲートの一方の入力端子に対し順次にパルスを供給する。

【0017】

ゲート回路群GHの各2入力ORゲートはこの入力を受け、スイッチ回路群SWの各スイッチ回路の制御端子に対し、順次にパルスを送出して順次にオン状態とする。このように、各スイッチ回路を順次オン状態とすることにより、表示信号SIG入力端子からの表示

50

信号 S I G が、スイッチ回路群 S W のオン状態とされたスイッチ回路を通して、対応する列信号電極 D に順次サンプリングする。

【 0 0 1 8 】

他方、行走査電極駆動回路 7 は、2 つのシフトレジスタ S R 1 及び S R 2 と、ゲート回路群 G V 1、G V 2 及び G V 3 より構成されている。第 1 のシフトレジスタ S R 1 の各出力ビット端子 A 1 ~ A m は、第 1 のゲート回路群 G V 1 を構成する m 個の 2 入力 A N D ゲートのうち対応する 2 入力 A N D ゲートの一方の入力端子に接続されている。第 1 のゲート回路群 G V 1 を構成する各 2 入力 A N D ゲートのもう一方の入力端子は、第 1 のゲート信号 G A T E 1 の入力端子に共通に接続されている。

【 0 0 1 9 】

第 2 のシフトレジスタ S R 2 の各出力ビット端子 B 1 ~ B m は、第 2 のゲート回路群 G V 2 を構成する m 個の 2 入力 A N D ゲートのうち対応する 2 入力 A N D ゲートの一方の入力端子に接続されている。第 2 のゲート回路群 G V 2 を構成する各 2 入力 A N D ゲートのもう一方の入力端子は、第 2 のゲート信号 G A T E 2 の入力端子に共通に接続されている。第 1 のゲート回路群 G V 1 と、第 2 のゲート回路群 G V 2 をそれぞれ構成する各 A N D ゲートの出力端子は、各々第 3 のゲート回路群 G V 3 を構成する m 個の 2 入力 O R ゲートのうち、対応する O R ゲートの入力端子にそれぞれ接続される。第 3 のゲート回路群 G V 3 を構成する m 個の O R ゲートの各出力端子は、各行の行走査電極 ( G 1、G 2、・・・、G m ) のうち、対応する 1 行の行走査電極に別々に接続されている。

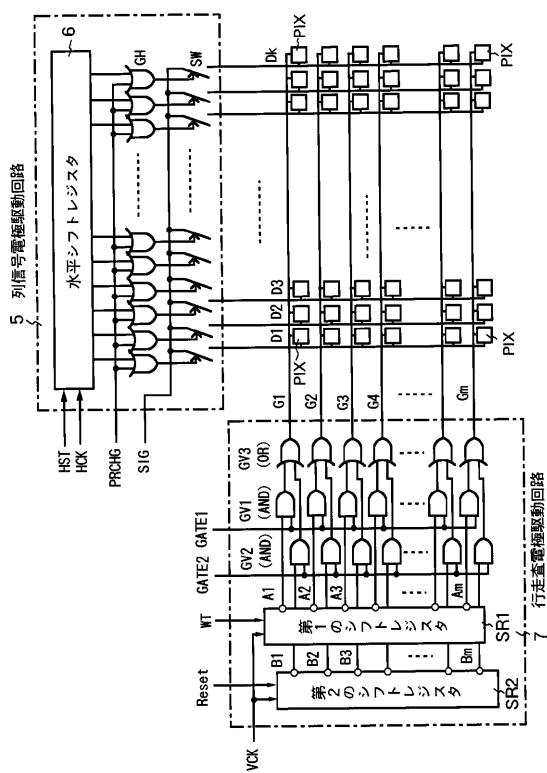

【 0 0 2 0 】

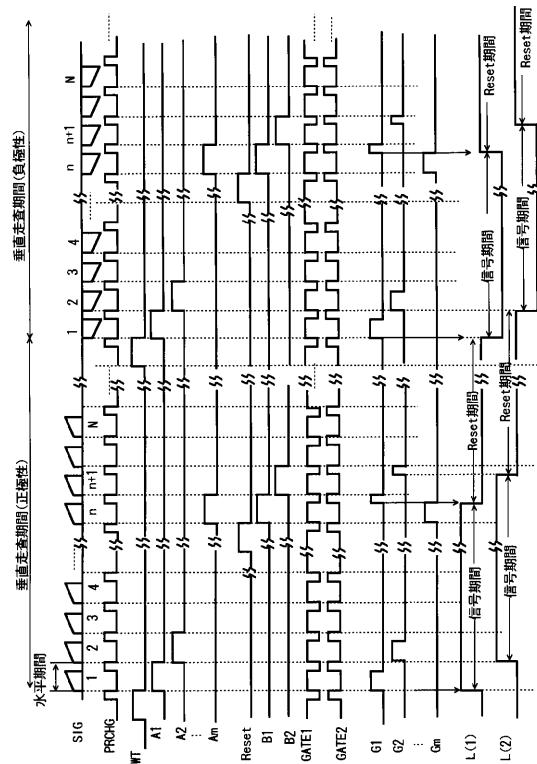

次に、図 2 および図 3 を用いて、図 1 のアクティブマトリクス型液晶表示装置の一実施の形態の駆動タイミングと動作について説明する。図 2 は図 1 の実施の形態における表示信号と各タイミング信号の関係について、各水平走査期間を基本単位に図示した模式図である。

【 0 0 2 1 】

図 2 において、表示信号 S I G は有効画像期間と画像情報を含まない水平プランキング期間より成り、水平プランキング期間の全てまたは少なくとも一部の期間には、リセット用の基準電圧レベルが重畠される。図 1 で説明した列信号電極駆動回路 5 のゲート回路群 G H ( O R 回路 ) のゲート信号 P R C H G は、上記表示信号 S I G の水平プランキング期間に重畠したリセット電圧レベル期間にて H レベルとなるようなタイミングとする。

【 0 0 2 2 】

これにより、水平プランキング期間に重畠したリセット電圧レベル期間においては、列信号電極駆動回路 5 の全てのゲート回路出力は H レベルとなり、スイッチ回路群 S W を構成する全てのスイッチ回路を同時にオン状態とする結果、全ての列信号電極 ( D 1、D 2、・・・、D k ) にリセット電圧レベルが同時に供給される。

【 0 0 2 3 】

行走査電極駆動回路 7 の第 1、第 2 のシフトレジスタ S R 1、S R 2 の各々に対して構成した第 1、第 2 のゲート回路群 G V 1、G V 2 ( A N D ゲート ) には、図 2 のタイミングで G A T E 1 信号、G A T E 2 信号を供給する。G A T E 1 信号は、上記列信号電極駆動回路 6 のゲート信号 P R C H G による列信号電極電圧のリセットより前のタイミングで立ち下がるようにタイミング設定されている。一方、G A T E 2 信号は、上記列信号電極駆動回路 6 のゲート信号 P R C H G によるリセットより後のタイミングで立ち下がるようにタイミング設定されている。

【 0 0 2 4 】

第 1 のシフトレジスタ S R 1 において、j 番目 ( j は 1 ~ m を満足する自然数 ) の出力ビット端子 A j の論理レベルが H レベルのとき、この出力ビット端子 A j の出力パルスを第 1 のゲート回路群 G V 1 の j 番目の A N D ゲートでゲート信号 G A T E 1 と論理積演算した出力が、ゲート回路群 G V 3 を通して、対応して設けられている行走査電極 G j に供給される。

【 0 0 2 5 】

10

20

30

40

50

また、第2のシフトレジスタSR2において、j番目の出力ビット端子Bjの論理レベルがHレベルのとき、この出力ビット端子Bjの出力パルスを第2のゲート回路群GV2のj番目のANDゲートでゲート信号GATE2と論理積演算した出力が、ゲート回路群GV3を通して、対応して設けられている行走査電極Gjに供給される。

【0026】

図3と共に後述するように、第1のシフトレジスタSR1には走査開始タイミング信号WTが供給され、これに基づき第1のシフトレジスタSR1の各ビット出力端子から順次シフトされて出力されたパルスのうち、出力ビット端子Ajの出力パルスが図2に示すように論理レベルがHレベルのとき、この出力ビット端子Ajの出力パルスを第1のゲート回路群GV1のj番目のANDゲートでゲート信号GATE1と論理積演算した出力が、ゲート回路群GV3を通して、対応して設けられている行走査電極Gjに供給され、表示信号の書き込みが行われる。

【0027】

次に、第1のシフトレジスタSR1への走査開始タイミング信号WTの入力後、後述するように、nライン期間後に第2のシフトレジスタSR2に走査開始タイミング信号Resetが供給され、これに基づき第2のシフトレジスタSR2の各ビット出力端子から順次シフトされて出力されたパルスのうち、出力ビット端子Bjの出力パルスが図2に示すように論理レベルがHレベルのとき、この出力ビット端子Bjの出力パルスを第2のゲート回路群GV2のj番目のANDゲートでゲート信号GATE2と論理積演算した出力が、ゲート回路群GV3を通して、対応して設けられている行走査電極Gjに供給され、表示信号SIGによらない一定電圧のReset信号の書き込みが行われる。

【0028】

このように、Ajにパルスが出力されて表示信号の書き込みが行われてからnライン期間後に、同一行jのBjにReset信号が出力されてリセットされる。従って、nラインの値は、表示信号書き込み後のリセットをかけるライン数を示しており、このnラインの値は、本実施の形態では任意の値に設定できる。

【0029】

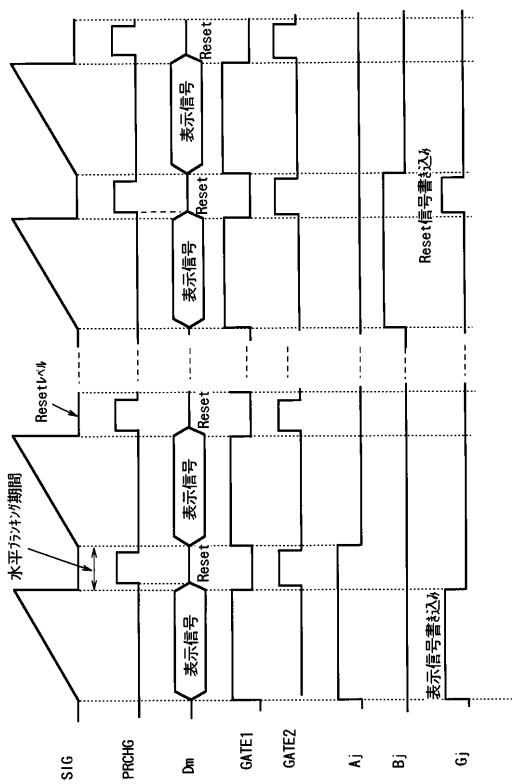

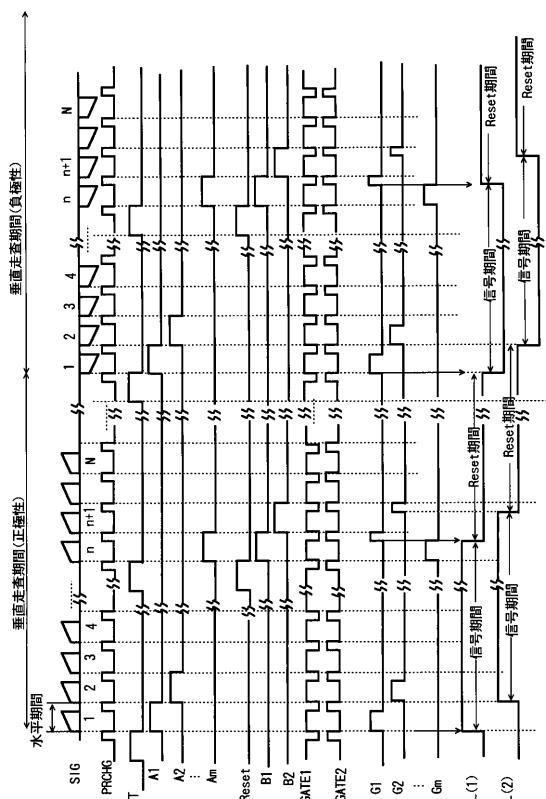

図3は本発明になるアクティブマトリクス型液晶表示装置の第1の実施の形態における表示信号と各タイミング信号の関係を、各垂直走査期間を含んだ時間軸で図示した模式図を示す。図3に示すように、表示信号SIGは表示画素PIX内の液晶の焼き付きや材料劣化を避けるために、垂直走査期間毎に極性反転するフレーム反転で入力され、これをサンプリングした各画素電圧も書き込み周期毎に極性反転した電圧となる。

【0030】

本実施の形態では、各極性で画素電圧（表示信号）を画素に書き込んで保持する期間（信号期間）と、所定の基準電圧にリセットするリセット期間を、各画素について1フレーム期間（1垂直走査期間）中に設けている。

【0031】

図1に示した行走査電極駆動回路7の第1のシフトレジスタSR1には、図3に示すように走査開始タイミング信号WTが表示信号フレームの先頭位置にパルス入力される。この走査開始タイミング信号WTは、図3に示すように第1のシフトレジスタSR1の各出力ビット端子A1, A2, ..., Amに順次シフトされると共に出力され、図2と共に説明したように、ゲート信号GATE1と論理積演算された行選択パルスが図1の行走査電極G1, G2, ..., Gmに出力される。これより、各行の画素回路が順次選択され、表示信号の書き込みが行われる。

【0032】

一方、図1に示した行走査電極駆動回路7の第2のシフトレジスタSR2には、図3に示すように走査開始タイミング信号Resetを、第1のシフトレジスタSR1の走査開始タイミング信号WTに対してnライン分遅れたタイミングで入力する。この走査開始タイミング信号Resetは、第2のシフトレジスタSR2の各出力ビット端子B1, B2, ..., Bmに順次シフトされると共に出力され、図2と共に説明したように、ゲート信

10

20

30

40

50

号 G A T E 2 と論理積演算された行選択パルスが図 1 の行走査電極 G 1 , G 2 , . . . , G m に出力される。

【 0 0 3 3 】

ゲート信号 G A T E 2 は、表示信号 S I G の水平プランキング期間に設けたりセット期間中、すなわち全ての列信号電極 ( D 1 , D 2 , . . . , D k ) にリセット電圧が供給されている期間に、各行に行選択がイネーブルとなるようにタイミング設定されており、その結果、対応する各行の画素回路には順次リセット電圧が書き込まれる。

【 0 0 3 4 】

以上により、各画素行の駆動画素電極の電圧、すなわち第 1 行の液晶駆動電圧は図 3 に L ( 1 ) で、第 2 行の液晶駆動電圧は同図に L ( 2 ) で示すように、信号期間とリセット期間が 1 フレーム ( 1 垂直走査期間 ) 内で切り替わる波形となる ( 第 3 行から第 m 行までの液晶駆動電圧も同様 ) 。

【 0 0 3 5 】

以上説明したように、本実施の形態のアクティブマトリクス型液晶表示装置によれば、1 フレーム期間 ( 1 垂直走査期間 ) 中に、各画素回路に表示信号を書き込み保持する表示信号期間と、所定の基準電圧にリセットするリセット期間を設けることができる。さらに、表示信号期間とリセット期間の時間の割合は、第 1 のシフトレジスタ S R 1 に入力する走査開始タイミング信号 W T に対する、第 2 のシフトレジスタ S R 2 に入力する走査開始タイミング信号 R e s e t の遅延ライン期間数 n ( ただし、n < m ) を任意に変えることにより、水平走査時間を単位として任意に設定することができる。

【 0 0 3 6 】

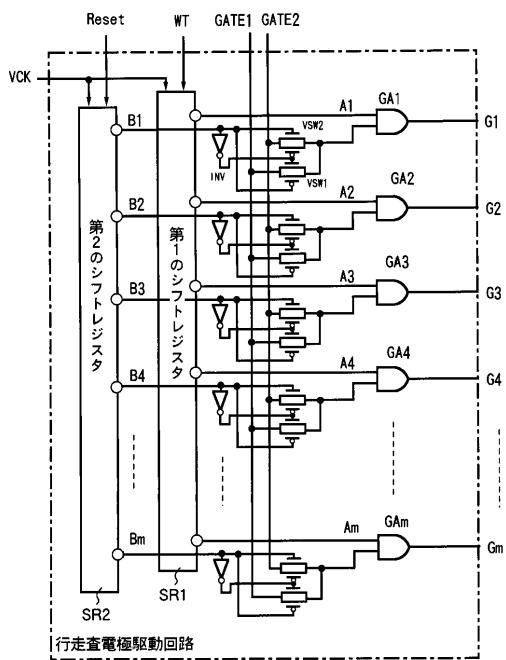

次に、本発明のアクティブマトリクス型液晶表示装置における行走査電極駆動回路の他の実施の形態の回路構成について説明する。図 4 は本発明のアクティブマトリクス型液晶表示装置における行走査電極駆動回路の他の実施の形態の回路構成図を示す。同図において、行走査電極駆動回路は 2 つのシフトレジスタ S R 1 及び S R 2 と、スイッチ回路 V S W 1 及び V S W 2 と、インバータ回路 I N V 、および A N D ゲート G A 1 ~ G A m で構成されている。第 1 及び第 2 のスイッチ回路 V S W 1 及び V S W 2 は、一方がオンの時には他方がオフとされる相補的に動作する一対のスイッチ回路で、第 2 のシフトレジスタ S R 2 の出力ビット端子 B 1 ~ B m に 1 対 1 に対応して m 対設けられている。

【 0 0 3 7 】

第 1 のシフトレジスタ S R 1 の各出力ビット端子 A 1 ~ A m は、2 入力 A N D ゲート G A 1 ~ G A m の一方の入力端子に別々に接続される。第 1 、第 2 のスイッチ回路 V S W 1 、 V S W 2 の制御入力端子には、第 2 のシフトレジスタ S R 2 の各ビット出力端子 B 1 ~ B m を、2 つのスイッチ回路 V S W 1 、 V S W 2 が相補的に動作するようにインバータ回路 I N V を含めて接続、構成する。

【 0 0 3 8 】

すなわち、第 2 のシフトレジスタ S R 2 のビット出力が L レベルの時はスイッチ回路 V S W 1 のみがオンとされ、このスイッチ回路 V S W 1 を通してゲート信号 G A T E 1 が出力側に伝達され、第 2 のシフトレジスタ S R 2 のビット出力が H レベルの時はスイッチ回路 V S W 2 のみがオンとされ、このスイッチ回路 V S W 2 を通してゲート信号 G A T E 2 が出力側に伝達される。これらのスイッチ回路 V S W 1 及び V S W 2 の出力は、2 入力 A N D ゲート G A 1 ~ G A m のもう一方の入力端子に別々に接続される。各 A N D ゲート G A 1 ~ G A m の出力端子は、各行の行走査電極 G 1 ~ G m に各々 1 対 1 に対応して接続されている。

【 0 0 3 9 】

図 5 は、図 4 図示の行走査電極駆動回路構成を適用した場合の表示信号と各タイミング信号の関係を、各垂直走査期間を含んだ時間軸で図示した模式図である。前記図 1 ~ 図 3 の実施の形態と本質的な動作は同じなので、詳細な説明は省略するが、図 4 に示す行走査電極駆動回路の構成では、第 1 のシフトレジスタ S R 1 に走査開始タイミング信号 W T のみをまず入力して、各行走査線の表示画素に順次に表示信号を書き込み、 W T 入力後リセッ

10

20

30

40

50

トをかけたい所望のライン期間 (n ライン時間) 経過時点で、今度は第 1 のシフトレジスタ S R 1 に走査開始タイミング信号 W T を入力すると同時に、第 2 のシフトレジスタ S R 2 にも走査開始タイミング信号 R e s e t を入力する点が前記図 1 ~ 図 3 に示した実施の形態と異なる。なお、図 5 では総有効ライン数を N と表記しているが、これは基本的には、シフトレジスタ S R 1 及び S R 2 の各段数 m と同じである。

【 0 0 4 0 】

以上説明した本発明のアクティブマトリクス型液晶表示装置は、各行の画素回路 (表示画素) の表示信号を 1 フレーム期間 (1 垂直走査期間) 内の任意の時間にリセットする手段を備えた点に特徴があり、具体手段である回路構成は以上に述べた実施の形態の構成に限定されるものではない。

10

【 0 0 4 1 】

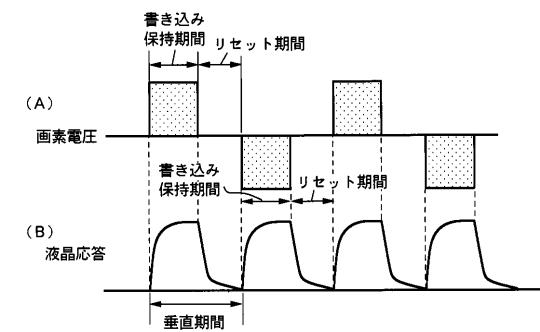

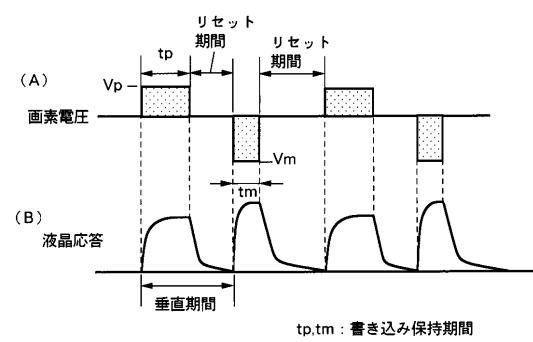

図 6 は本発明のアクティブマトリクス型液晶表示装置における画素電圧と、対応する画素の液晶の応答の一例を示す模式図である。図 6 (A) に示すように、画素電圧は液晶の焼き付きや材料劣化を避けるために垂直走査期間ごとに極性反転するフレーム反転で入力し、これをサンプリングした各画素電圧も書き込み周期毎に極性反転した電圧となる。

20

【 0 0 4 2 】

本発明のアクティブマトリクス型液晶表示装置の構成および駆動では、各極性で画素電圧 (表示信号) を画素に書き込んで保持する期間 (信号期間) と、所定の基準電圧にリセットするリセット期間を、各画素について 1 フレーム期間中に設けている。図 6 (A) に示すように、本発明装置における画素電圧 (交流) は、中心電圧にリセット電圧レベルが設定され、リセット期間の液晶駆動電圧がほぼゼロとなるようにされている。このようなりセット期間を有する駆動電圧を各画素の液晶に与える結果、液晶の応答波形は、図 6 (B) に示すように画像表示と黒表示を交互に繰り返す応答となる。これより、以下の効果が得られる。

20

【 0 0 4 3 】

(1) 各表示フレームの間に黒表示期間が挿入される結果、ホールド型ディスプレイの残像に起因する動画解像度劣化が改善できる。液晶の応答速度が遅く、リセット期間中に液晶が完全に黒レベルまでリセットされない場合においても、リセット期間で表示画像の輝度を減衰させる分、視覚特性上の残像による動画解像度劣化改善に有効に作用する。

30

【 0 0 4 4 】

(2) 各表示フレームの信号期間の間に液晶のしきい値電圧以下の駆動電圧期間が挿入され、液晶の中間調での応答速度低下の問題を改善できる。これにより、動画解像度を改善することができる。

30

【 0 0 4 5 】

(3) さらに、本実施の形態のアクティブマトリクス型液晶表示装置では、図 6 (A) に示す画素電圧の信号期間とリセット期間の時間の割合を、行走査電極駆動回路 7 の駆動信号に供給する制御信号 (W T, R e s e t) のタイミングにより任意に設定できる。

40

【 0 0 4 6 】

ここで、フレーム間で黒表示に対応したリセット期間を設けた場合、リセット期間の光出力が減衰するため、平均輝度は暗くなるが、本発明のアクティブマトリクス型液晶表示装置では、信号期間とリセット期間の時間の割合を任意に設定可能なため、明るさと動画応答のバランスをシステム要求により任意に設定できる。また、同一表示装置に「明るさ優先」と「動画持性優先」の複数のモードを持たせることも可能である。

【 0 0 4 7 】

図 7 は本発明のアクティブマトリクス型液晶表示装置における画素電圧と、対応する画素の液晶の応答の他の例を示す模式図である。図 7 においては、極性反転信号における正極性フレームと負極性フレーム各々に対して、信号期間とリセット期間の割合を異なる条件に設定している。液晶の焼き付きや材料劣化を避けるために、液晶駆動電圧は直流成分を極力無くす必要がある。

40

【 0 0 4 8 】

50

本発明によるアクティブマトリクス型液晶表示装置においては、各垂直走査期間（各フレーム）のリセット期間を任意に設定でき、フレーム毎にその期間を制御することも可能である。従って、図7（A）に示すように正極性の画素電圧の振幅 $V_p$ と、負極性の画素電圧の振幅 $V_m$ が基準電圧に対して異なる場合（ $V_p > V_m$ ）、すなわち正極性と負極性の対称性が崩れた画素電圧（表示信号）入力に対し、極性毎に時間の異なるリセット期間を与えるように駆動タイミングを制御し、

$V_p \times t_p \quad V_m \times t_m$

となるようにリセット期間の設定を行う。ここで、 $t_p$ は正極性の画素電圧を書き込み保持する表示信号期間、 $t_m$ は負極性の画素電圧を書き込み保持する表示信号期間である。

【0049】

これにより、液晶駆動電圧の平均直流成分を時間軸方向に調整することができ、液晶応答は、図7（B）に示すようになる。例えば、1フレームの総ライン数1000本の表示装置では電圧値方向で調整して残留する液晶直流成分を、さらに時間方向で1/1000精度で微調整でき、液晶駆動電圧の直流分を高精度で調整しそれぞれにできる。

【0050】

【発明の効果】

以上説明したように、本発明によれば、各行の表示画素に1フレーム期間内で、表示信号を書き込み保持した後、所定の基準レベルにリセットするようにしたため、各表示フレームの間に黒表示期間が挿入される結果、ホールド型ディスプレイの残像に起因する動画解像度劣化が改善でき、また、各表示フレームの信号期間の間に液晶のしきい値電圧以下の駆動電圧期間が挿入され、液晶の中間調での応答速度低下の問題を改善できる。

【0051】

また、本発明によれば、1フレーム期間内の表示信号期間とリセット期間との割合を任意の割合で設定するようにしたため、明るさと動画応答のバランスをシステム要求により任意に設定でき、また、同一表示装置に「明るさ優先」と「動画持性優先」の複数のモードを持たせることもできる。

【画面の簡単な説明】

【図1】本発明によるアクティブマトリクス型液晶表示装置の一実施の形態の回路構成図である。

【図2】図1の実施の形態における表示信号と各タイミング信号の関係について、各水平走査期間を基本単位に図示した模式図である。

【図3】図1の第1の実施の形態における表示信号と各タイミング信号の関係を、各垂直走査期間を含んだ時間軸で図示した模式図である。

【図4】本発明によるアクティブマトリクス型液晶表示装置における行走査電極駆動回路の他の実施の形態の回路構成図である。

【図5】図4図示の行走査電極駆動回路構成を適用した場合の表示信号と各タイミング信号の関係を、各垂直走査期間を含んだ時間軸で図示した模式図である。

【図6】本発明のアクティブマトリクス型液晶表示装置における画素電圧と、対応する画素の液晶の応答の一例を示す模式図である。

【図7】本発明のアクティブマトリクス型液晶表示装置における画素電圧と、対応する画素の液晶の応答の他の例を示す模式図である。

【図8】従来のアクティブマトリクス型液晶表示装置の一例の構成図である。

【図9】従来の液晶表示装置の表示画素を説明する回路構成図である。

【符号の説明】

5 列信号電極駆動回路

6 水平シフトレジスタ

7 行走査電極駆動回路

G H ゲート回路群（O R）

S W スイッチ回路群

S R 1 第1のシフトレジスタ

10

20

30

40

50

S R 2 第2のシフトレジスタ

G V 1、G V 2 ゲート回路群 (AND)

G V 3 ゲート回路群 (OR)

D 1 ~ D k 列信号電極

G 1 ~ G m 行走査電極

V S W 1、V S W 2 スイッチ回路

I N V インバータ回路

G A 1 ~ G A m ANDゲート

【 図 1 】

【 四 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 1 F |

| G 0 9 G | 3/20 | 6 2 2 P |

| G 0 9 G | 3/20 | 6 2 3 R |

| G 0 9 G | 3/20 | 6 4 1 R |

| G 0 9 G | 3/20 | 6 6 0 V |

F ターム(参考) 5C006 AA01 AA16 AC11 AC28 AF42 AF43 AF44 AF71 AF73 BB16

BC03 BC13 BF03 BF11 BF26 BF27 BF34 BF42 EC11 FA14

FA29 FA34 FA38 FA54

5C080 AA10 BB05 DD02 DD05 DD08 EE19 EE29 FF11 GG08 JJ03

JJ04 KK43

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵型液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2004061552A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2004-02-26 |

| 申请号            | JP2002215736                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2002-07-24 |

| [标]申请(专利权)人(译) | 日本胜利株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 日本有限公司Victor公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| [标]发明人         | 古屋正人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 古屋 正人                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| CPC分类号         | G09G3/3677 G09G3/2011 G09G3/3688 G09G2300/0842 G09G2310/0254 G09G2310/0267 G09G2310/0275 G09G2310/061 G09G2310/062 G09G2320/0252                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.612.E G09G3/20.612.T G09G3/20.621.A G09G3/20.621.F G09G3/20.622.P G09G3/20.623.R G09G3/20.641.R G09G3/20.660.V                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA33 2H093/NC09 2H093/NC11 2H093/NC16 2H093/NC22 2H093/NC34 2H093/NC41 2H093/ND08 2H093/ND20 2H093/ND60 2H093/NE03 2H093/NG02 2H093/NH15 5C006/AA01 5C006/AA16 5C006/AC11 5C006/AC28 5C006/AF42 5C006/AF43 5C006/AF44 5C006/AF71 5C006/AF73 5C006/BB16 5C006/BC03 5C006/BC13 5C006/BF03 5C006/BF11 5C006/BF26 5C006/BF27 5C006/BF34 5C006/BF42 5C006/EC11 5C006/FA14 5C006/FA29 5C006/FA34 5C006/FA38 5C006/FA54 5C080/AA10 5C080/BB05 5C080/DD02 5C080/DD05 5C080/DD08 5C080/EE19 5C080/EE29 5C080/FF11 5C080/GG08 5C080/JJ03 5C080/JJ04 5C080/KK43 2H193/ZA04 2H193/ZC15 2H193/ZP03 2H193/ZR02 |         |            |

| 其他公开文献         | JP3901048B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

### 摘要(译)

要解决的问题：解决传统设备由于前一帧残像的时间干扰而在视觉上容易被感知为运动模糊的问题，并且运动图像的分辨率下降，并且液晶的施加电压/时间响应变差。有。当在一个帧周期（一个垂直扫描周期）内产生基于第一移位寄存器SR1的输出脉冲的行选择脉冲时，有源矩阵液晶显示装置在每个像素电路中写入并保持显示信号。并且，基于第二移位寄存器SR2的输出脉冲，在产生行选择脉冲时，复位为预定的基准电压的复位期间。通过相对于输入到SR1的扫描开始定时信号WT任意地改变输入到SR2的扫描开始定时信号Reset的延迟线周期数n，显示信号周期和复位周期之间的时间比是水平扫描时间的单位。可以任意设定。

[选型图]图1