(19)日本国特許庁( J P )

(12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2002 - 156948

(P2002 - 156948A)

(43)公開日 平成14年5月31日(2002.5.31)

| (51) Int.CI <sup>7</sup> | 識別記号   | F I           | テ-マコード <sup>8</sup> (参考) |

|--------------------------|--------|---------------|--------------------------|

| G 0 9 G 3/36             |        | G 0 9 G 3/36  | 2 H 0 9 2                |

| G 0 2 F 1/133            | 510    | G 0 2 F 1/133 | 2 H 0 9 3                |

|                          | 575    |               | 5 C 0 0 6                |

|                          | 1/1345 | 1/1345        | 5 C 0 8 0                |

| G 0 9 G 3/20             | 621    | G 0 9 G 3/20  | 621 M                    |

審査請求 有 請求項の数 120 L (全 19数) 最終頁に続く

(21)出願番号 特願2000 - 353427(P2000 - 353427)

(71)出願人 000004237

日本電気株式会社

(22)出願日 平成12年11月20日(2000.11.20)

東京都港区芝五丁目7番1号

(72)発明者 奥苑 登

東京都港区芝五丁目7番1号 日本電気株式会社内

(74)代理人 100099830

弁理士 西村 征生

最終頁に続く

(54)【発明の名称】 カラー液晶ディスプレイの駆動回路、表示装置及びカラー液晶ディスプレイの駆動方法

(57)【要約】

【課題】 基板実装面積を削減し、カラー液晶ディスプレイの解像度や階調電圧の個数が異なっても共通の基板やT C Pを用いることができ、基板やT C P、表示装置を安価に構成できるようにする。

【解決手段】 開示されるカラー液晶ディスプレイの駆動回路は、データ電極駆動回路22において、制御回路21から供給される、階調情報A5～A0と階調電圧情報D7～D0とからなるシリアルデータS DATAに基づいて階調電圧特性に応じた階調電圧V<sub>R0</sub>～V<sub>R17</sub>、V<sub>G0</sub>～V<sub>G17</sub>、V<sub>B0</sub>～V<sub>B17</sub>を生成する。

**【特許請求の範囲】**

【請求項1】 複数個の階調電圧の中から映像信号に基づいて選択した階調電圧を用いてカラー液晶ディスプレイを駆動するデータ電極駆動回路を有するカラー液晶ディスプレイの駆動回路であって、

前記データ電極駆動回路は、供給されるデジタルの階調電圧設定データに基づいて階調電圧特性に応じた前記複数個の階調電圧を生成することを特徴とするカラー液晶ディスプレイの駆動回路。

【請求項2】 デジタル映像データの赤データ、緑データ、青データに対して、カラー液晶ディスプレイの印加電圧に対する赤、緑、青の透過率の特性に適合するよう補正するガンマ補正をそれぞれ独立に施すことにより得られたデータ赤信号、データ緑信号、データ青信号を用いて前記カラー液晶ディスプレイを駆動するカラー液晶ディスプレイの駆動回路であって、前記カラー液晶ディスプレイとは別個に設けられ、前記デジタル映像データの表示と関わらない無効期間中に、前記赤データ、緑データ、青データのガンマ補正に関する情報を出力する制御回路と、

前記カラー液晶ディスプレイの近傍に設けられ、前記赤データ、緑データ、青データのガンマ補正に関する情報に基づいて、前記赤データ、緑データ、青データに対して、前記ガンマ補正を施すことにより得られたデータ赤信号、データ緑信号、データ青信号を用いて前記カラー液晶ディスプレイを駆動するデータ電極駆動回路とを備えてなることを特徴とするカラー液晶ディスプレイの駆動回路。

【請求項3】 前記制御回路は、前記カラー液晶ディスプレイの裏面に取り付けられたバックライトの裏面上部に取り付けられたプリント基板上に搭載され、前記データ電極駆動回路は、前記赤データ、緑データ、青データのうち、前記カラー液晶ディスプレイのデータ電極に対応した前記赤データ、緑データ、青データに対して前記ガンマ補正を施すことにより階調性を付与するとともにアナログのデータ赤信号、データ緑信号、データ青信号に変換して出力する複数個のデータ電極駆動部から構成され、

前記複数個のデータ電極駆動部は、前記プリント基板と前記カラー液晶ディスプレイとを電気的に接続する対応するフィルムキャリアテープ上にそれぞれ搭載されていることを特徴とする請求項2記載のカラー液晶ディスプレイの駆動回路。

【請求項4】 前記赤データ、緑データ、青データのガンマ補正に関する情報は、前記赤データ、緑データ、青データのうちのいずれの階調電圧を設定するかを指示する階調情報と、複数個の階調電圧のいずれの値を選択するかを指示する階調電圧情報とからなることを特徴とする請求項2又は3記載のカラー液晶ディスプレイの駆動回路。

【請求項5】 前記制御回路は、前記階調情報及び前記階調電圧情報を、シリアルデータとして前記データ電極駆動回路に供給することを特徴とする請求項4記載のカラー液晶ディスプレイの駆動回路。

【請求項6】 各データ電極駆動部は、前記シリアルデータをパラレルの階調情報及び階調電圧情報に変換して出力するシフトレジスタと、前記赤データ、緑データ、青データの複数個の階調電圧として、いずれの値の階調電圧を選択するかを示す選択信号が予め記憶された記憶部と、

前記階調情報をデコードして、前記赤データ、緑データ、青データの複数個の階調電圧のうちのいずれを選択するかを指示する選択情報を出力するデコーダと、前記選択情報に従って前記記憶部から読み出された選択信号に基づいて、いずれかの値の階調電圧を選択して、複数個の赤階調電圧、緑階調電圧、青階調電圧として出力するマルチプレクサと、

前記複数個の赤階調電圧、緑階調電圧、青階調電圧に基づいて、前記赤データ、緑データ、青データに、ガンマ補正を施すことにより階調性を付与するとともにアナログのデータ赤信号、データ緑信号、データ青信号に変換して出力するデータ信号出力部とを備えてなることを特徴とする請求項5記載のカラー液晶ディスプレイの駆動回路。

【請求項7】 前記制御回路は、前記階調電圧情報を、前記赤データ、緑データ、青データを前記データ電極駆動回路に供給する配線を利用して供給することを特徴とする請求項4記載のカラー液晶ディスプレイの駆動回路。

【請求項8】 前記赤データ、緑データ、青データを前記データ電極駆動回路に取り込むために使用されるクロックが前記データ電極駆動回路内部でカウントされるカウント数と、前記赤データ、緑データ、青データの階調電圧情報が前記データ電極駆動回路に供給される順番とを一一に対応させるとともに、前記カウント数を前記階調情報とすることを特徴とする請求項4又は7記載のカラー液晶ディスプレイの駆動回路。

【請求項9】 各データ電極駆動部は、前記赤データの複数個の赤階調電圧として、いずれの値の階調電圧を選択するかを示す選択信号が予め記憶された赤階調電圧情報記憶部と、

前記緑データの複数個の緑階調電圧として、いずれの値の階調電圧を選択するかを示す選択信号が予め記憶された緑階調電圧情報記憶部と、

前記青データの複数個の青階調電圧として、いずれの値の階調電圧を選択するかを示す選択信号が予め記憶された青階調電圧情報記憶部と、

供給されるクロックの個数をカウントし、そのカウント数に応じて、複数個の階調電圧のうちのいずれを選択するかを指示する選択情報を出力する階調情報カウント部

と、

前記選択情報に従って前記赤階調電圧情報記憶部、緑階調電圧情報記憶部、青階調電圧情報記憶部から読み出された選択信号に基づいて、いずれかの値の階調電圧を選択して、複数個の赤階調電圧、緑階調電圧、青階調電圧として出力するマルチプレクサと、

前記複数個の赤階調電圧、緑階調電圧、青階調電圧に基づいて、前記赤データ、緑データ、青データに、ガンマ補正を施すことにより階調性を付与するとともにアナログのデータ赤信号、データ緑信号、データ青信号に変換して出力するデータ信号出力部とを備えてなることを特徴とする請求項8記載のカラー液晶ディスプレイの駆動回路。

【請求項10】前記ガンマ補正是、前記赤データ、緑データ、青データに対して、入力画像の輝度に対する再生画像の輝度の特性を任意に付与するために補正するガンマ補正をも含むことを特徴とする請求項2乃至9のいずれか1に記載のカラー液晶ディスプレイの駆動回路。

【請求項11】請求項1乃至10のいずれか1に記載のカラー液晶ディスプレイの駆動回路を備えてなることを特徴とする表示装置。

【請求項12】デジタル映像データの赤データ、緑データ、青データに対して、カラー液晶ディスプレイの印加電圧に対する赤、緑、青の透過率の特性に適合するように補正するガンマ補正をそれぞれ独立に施すことにより得られたデータ赤信号、データ緑信号、データ青信号を用いて前記カラー液晶ディスプレイを駆動するカラー液晶ディスプレイの駆動方法であって、

前記デジタル映像データの表示と関わらない無効期間中に、前記赤データ、緑データ、青データのガンマ補正に関する情報を、前記カラー液晶ディスプレイとは別個に設けられた制御回路から、前記カラー液晶ディスプレイの近傍に設けられ、前記赤データ、緑データ、青データのガンマ補正に関する情報に基づいて、前記赤データ、緑データ、青データに対して、前記ガンマ補正を施すことにより得られたデータ赤信号、データ緑信号、データ青信号を用いて前記カラー液晶ディスプレイを駆動するデータ電極駆動回路に供給することを特徴とするカラー液晶ディスプレイの駆動方法。

#### 【発明の詳細な説明】

##### 【0001】

【発明の属する技術分野】この発明は、カラー液晶ディスプレイの駆動回路、表示装置及びカラー液晶ディスプレイの駆動方法に関し、詳しくは、ガンマ補正を施したデジタル映像データに基づいてカラー液晶ディスプレイを駆動するカラー液晶ディスプレイの駆動回路、このようなカラー液晶ディスプレイの駆動回路を備えた表示装置及びカラー液晶ディスプレイの駆動方法に関する。

##### 【0002】

##### 【従来の技術】図17は、特願平11-316873号

10

に開示された従来のカラー液晶ディスプレイ1の駆動回路の構成例を示すブロック図である。この例のカラー液晶ディスプレイ1は、例えば、薄膜トランジスタ(TFT)をスイッチ素子に用いたアクティブマトリックス駆動方式のカラー液晶ディスプレイであり、行方向に所定間隔で設けられた複数本の走査電極(ゲート線)と列方向に所定間隔で設けられた複数本のデータ電極(ソース線)とで囲まれた領域を画素とし、各画素ごとに、等価的に容量性負荷である液晶セルと、対応する液晶セルを駆動するTFTと、データ電荷を1垂直同期期間の間蓄積するコンデンサとを配列し、デジタル映像データの赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>に基づいて生成されるデータ赤信号、データ緑信号、データ青信号がデータ電極に印加されるとともに、水平同期信号S<sub>H</sub>及び垂直同期信号S<sub>V</sub>に基づいて生成される走査信号が走査電極に印加されることにより、カラーの文字や画像等を表示するものである。また、この例のカラー液晶ディスプレイ1は、印加電圧を加えない状態においてその透過率が低い、いわゆるノーマリー・ブラック型である。

20

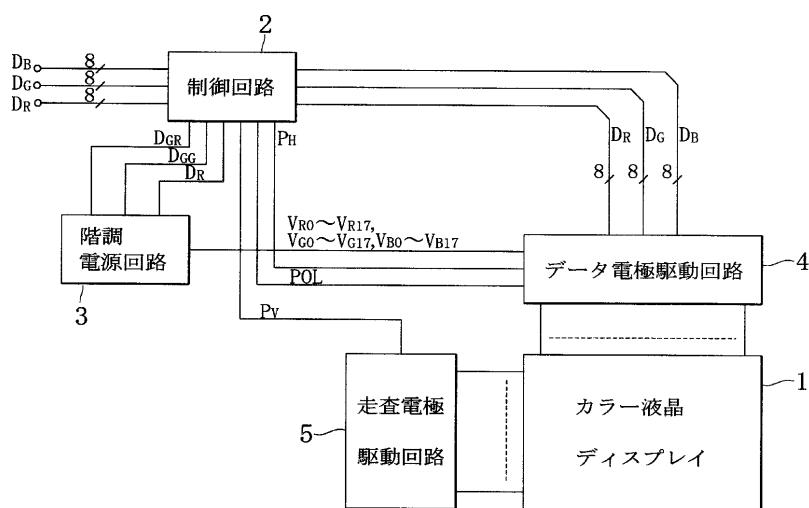

【0003】また、この例のカラー液晶ディスプレイ1の駆動回路は、制御回路2と、階調電源回路3と、データ電極駆動回路4と、走査電極駆動回路5とから概略構成されている。制御回路2は、例えば、ASIC(Application Specific Integrated Circuit)からなり、外部から供給されるそれぞれ8ビットの赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>をデータ電極駆動回路4に供給するとともに、外部から供給される水平同期信号S<sub>H</sub>及び垂直同期信号S<sub>V</sub>等に基づいて、水平走査パルスP<sub>H</sub>、垂直走査パルスP<sub>V</sub>及びカラー液晶ディスプレイ1を交流駆動するための極性反転パルスPOLを生成してデータ電極駆動回路4及び走査電極駆動回路5に供給する。また、制御回路2は、赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>にそれぞれ別個独立にガンマ補正を施すことにより階調性を付与するための赤階調電圧データD<sub>GR</sub>、緑階調電圧データD<sub>GG</sub>、青階調電圧データD<sub>GB</sub>を階調電源回路3に供給する。なお、この例におけるガンマ補正是、入力画像の輝度に対する再生画像の輝度の特性を任意に付与するために補正するガンマ補正(以下、第1のガンマ補正)と、カラー液晶ディスプレイ1の赤、緑、青のそれぞれの印加電圧Vに対する透過率Tの特性(V-T特性)に適合したガンマ補正(以下、第2のガンマ補正)とを含むものとする。

30

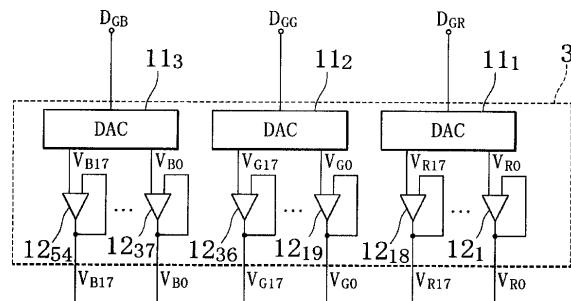

【0004】階調電源回路3は、図18に示すように、デジタル/アナログ変換器(DAC)11<sub>1</sub>~11<sub>3</sub>と、ボルテージフォロア12<sub>1</sub>~12<sub>54</sub>とから構成されている。DAC11<sub>1</sub>は、制御回路2から供給される赤階調電圧データD<sub>GR</sub>をアナログの赤階調電圧V<sub>R0</sub>~V<sub>R17</sub>に変換してそれぞれボルテージフォロア12<sub>1</sub>~12<sub>18</sub>に供給する。同様に、DAC11<sub>2</sub>は、制御回路2から供給される緑階調電圧データD<sub>GG</sub>

$V_{G0} \sim V_{G17}$  をアナログの緑階調電圧に変換し、それぞれボルテージフォロア  $12_{19} \sim 12_{36}$  に供給する。D A C  $11_3$  は、制御回路 2 から供給される青階調電圧データ  $D_{GB}$  をアナログの青階調電圧  $V_{B0} \sim V_{B17}$  に変換して、それぞれボルテージフォロア  $12_{37} \sim 12_{54}$  に供給する。ボルテージフォロア  $12_1 \sim 12_{54}$  は、ガンマ補正のための対応する赤階調電圧  $V_{R0} \sim V_{R17}$ 、緑階調電圧  $V_{G0} \sim V_{G17}$ 、青階調電圧  $V_{B0} \sim V_{B17}$  をそのままデータ電極駆動回路 4 に供給する。

【0005】データ電極駆動回路 4 は、 $k$  個 ( $k$  は自然数) のデータ電極駆動部  $4_1 \sim 4_k$  から構成されている。各データ電極駆動部  $4_1 \sim 4_k$  は、制御回路 2 から供給される赤データ  $D_R$ 、緑データ  $D_G$ 、青データ  $D_B$  のうち、カラー液晶ディスプレイ 1 の対応するデータ電極に対応した赤データ  $D_R$ 、緑データ  $D_G$ 、青データ  $D_B$  に対して、階調電源回路 3 から供給される赤階調電圧  $V_{R0} \sim V_{R17}$ 、緑階調電圧  $V_{G0} \sim V_{G17}$ 、青階調電圧  $V_{B0} \sim V_{B17}$  に基づいて、ガンマ補正を施すことにより階調性を付与するとともに、アナログの 384 個のデータ信号に変換して出力する。例えば、カラー液晶ディスプレイ 1 が S X G A (super extended graphics array) と呼ばれ、解像度が  $1280 \times 1024$  画素である場合には、1 画素が 3 個の赤 (R)、緑 (G)、青 (B) のドット画素により構成されているので、そのドット画素数は、 $3840 \times 1024$  画素である。したがって、この場合、データ電極駆動回路 4 は、(3840 画素  $\div$  384 個のデータ信号) であることから、10 個のデータ電極駆動部  $4_1 \sim 4_{10}$  から構成されることになる。データ電極駆動部  $4_1 \sim 4_{10}$  は、各構成要素の添え字が異なるとともに、入出力される信号の添え字が異なる以外は同一構成であるので、以下ではデータ電極駆動部  $4_1$  についてのみ説明する。

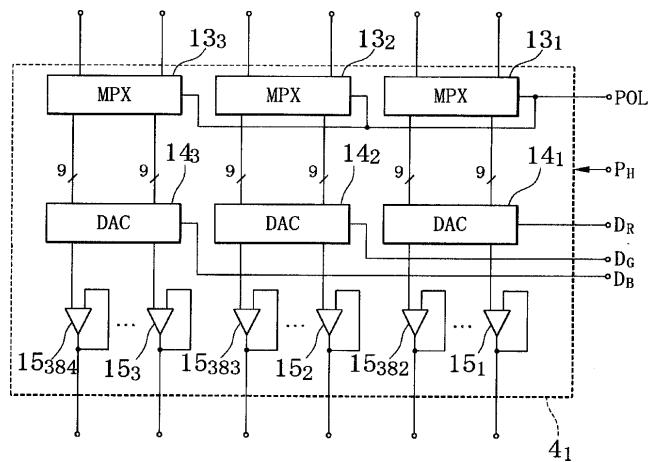

【0006】データ電極駆動部  $4_1$  は、図 19 に示すように、マルチプレクサ (M P X)  $13_1 \sim 13_3$  と、8 ビットの D A C  $14_1 \sim 14_3$  と、ボルテージフォロア  $15_1 \sim 15_{384}$  とから概略構成されている。M P X  $13_1$  は、階調電源回路 3 から供給される赤階調電圧  $V_{R0} \sim V_{R17}$  のうち、赤階調電圧  $V_{R0} \sim V_{R8}$  の組又は赤階調電圧  $V_{R9} \sim V_{R17}$  の組を、制御回路 2 から供給される極性反転パルス P O L に基づいて切り替えて D A C  $14_1$  に供給する。同様に、M P X  $13_2$  は、階調電源回路 3 から供給される緑階調電圧  $V_{G0} \sim V_{G17}$  のうち、緑階調電圧  $V_{G0} \sim V_{G8}$  の組又は緑階調電圧  $V_{G9} \sim V_{G17}$  の組を、制御回路 2 から供給される極性反転パルス P O L に基づいて切り替えて D A C  $14_2$  に供給する。M P X  $13_3$  は、階調電源回路 3 から供給される青階調電圧  $V_{B0} \sim V_{B17}$  のうち、青階調電圧  $V_{B0} \sim V_{B8}$  の組又は青階調電圧  $V_{B9} \sim V_{B17}$  の組を、制御回路 2 から供給される極性反転パルス

S P O L に基づいて切り替えて D A C  $14_3$  に供給する。

【0007】D A C  $14_1$  は、制御回路 2 から供給される 8 ビットの赤データ  $D_R$  に、M P X  $13_1$  から供給される赤階調電圧  $V_{R0} \sim V_{R8}$  の組又は赤階調電圧  $V_{R9} \sim V_{R17}$  の組に基づいて、ガンマ補正を施すことにより階調性を付与するとともに、アナログのデータ赤信号に変換して対応するボルテージフォロア  $15_1$ 、 $15_4$ 、 $15_7$ 、 $\dots$ 、 $15_{382}$  に供給する。同様に、D A C  $14_2$  は、制御回路 2 から供給される 8 ビットの緑データ  $D_G$  に、M P X  $13_2$  から供給される緑階調電圧  $V_{G0} \sim V_{G8}$  の組に基づいて、ガンマ補正を施すことにより階調性を付与するとともに、アナログのデータ緑信号に変換して対応するボルテージフォロア  $15_2$ 、 $15_5$ 、 $15_8$ 、 $\dots$ 、 $15_{383}$  に供給する。D A C  $14_3$  は、制御回路 2 から供給される 8 ビットの青データ  $D_B$  に、M P X  $13_3$  から供給される青階調電圧  $V_{B0} \sim V_{B8}$  の組又は青階調電圧  $V_{B9} \sim V_{B17}$  の組に基づいて、ガンマ補正を施すことにより階調性を付与するとともに、アナログのデータ青信号に変換して対応するボルテージフォロア  $15_3$ 、 $15_6$ 、 $15_9$ 、 $\dots$ 、 $15_{384}$  に供給する。ボルテージフォロア  $15_1 \sim 15_{384}$  は、D A C  $14_1 \sim 14_3$  から供給される対応するデータ赤信号、データ緑信号、データ青信号をそのままカラー液晶ディスプレイ 1 の対応するデータ電極に印加する。図 17 に示す走査電極駆動回路 5 は、制御回路 2 から供給される垂直走査パルス P v のタイミングで、走査信号を順次生成してカラー液晶ディスプレイ 1 の対応する走査電極に順次印加する。

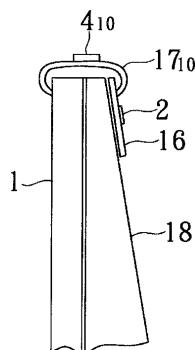

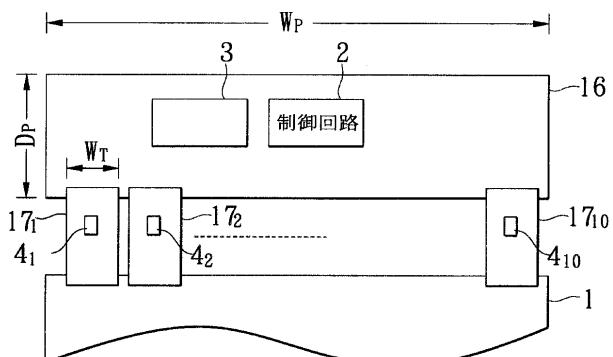

【0008】そして、上記構成のカラー液晶ディスプレイの駆動回路を備えた表示装置においては、図 20 に示すように、制御回路 2 及び階調電源回路 3 がプリント基板 16 上に搭載されるのに対し、データ電極駆動部  $4_1 \sim 4_{10}$  は、プリント基板 16 とカラー液晶ディスプレイ 1 とを電気的に接続する 10 個のフィルムキャリアテーブル上にそれぞれ搭載され、T C P (Tape Carrier Package)  $17_1 \sim 17_{10}$  として実装されている。プリント基板 16 は、図 21 に示すように、カラー液晶ディスプレイ 1 の裏面に取り付けられた断面略くさび型状のバックライト 18 の裏面上部に取り付けられる。このバックライト 18 は、白色電球等の点光源や蛍光ランプ等の線光源と、これらの光源から放射される光を拡散して面光源化する光拡散部材とからなり、非発光表示素子であるカラー液晶ディスプレイ 1 の裏面側からカラー液晶ディスプレイ 1 の裏面を均一に照明するものである。

【0009】

【発明が解決しようとする課題】上記したように、従来においては、階調電源回路 3 とデータ電極駆動部  $4_1 \sim 4_{10}$  とが別個独立に設けられていたために、階調電源

回路3から出力される54個の赤階調電圧 $V_{R0} \sim V_{R17}$ 、緑階調電圧 $V_{G0} \sim V_{G17}$ 、青階調電圧 $V_{B0} \sim V_{B17}$ を10個のデータ電極駆動部 $4_1 \sim 4_{10}$ にそれぞれ供給する必要がある。この階調電圧の供給方法として、以下に示す2つの方法が考えられるが、それぞれ以下に示す欠点がある。

【0010】まず、第1に、プリント基板16の表層に54本の配線を形成し、各TCP17<sub>1</sub>～17<sub>10</sub>に接続する方法がある。現在採用されている代表的な配線間ピッチは、3本の配線当たり1.27mmである。そこで、この配線ピッチで54本の配線をプリント基板16の表層に形成すると、54個の赤階調電圧 $V_{R0} \sim V_{R17}$ 、緑階調電圧 $V_{G0} \sim V_{G17}$ 、青階調電圧 $V_{B0} \sim V_{B17}$ を1本の配線でシリアル転送する場合に比べて2cm以上もプリント基板16の奥行き $D_p$ (図20参照)が長くなる。これにより、図21に示すように、プリント基板16がバックライト18の裏面上部に取り付けられる面積が広くなる。バックライト18は、単にカラー液晶ディスプレイの裏面を均一に照明するだけでなく、表示装置の裏面部分を平面に保つための役割も担っており、同一の画面サイズを有するカラー液晶ディスプレイを備えた表示装置において共通で用いられるのが一般である。ところが、上記したように、カラー液晶ディスプレイのタイプ、すなわち、解像度が異なるごとにプリント基板16の奥行き $D_p$ が異なることになれば、各タイプごとにバックライト18の形状を異ならせる必要があり、このことが表示装置のコストアップの要因となるおそれがある。

【0011】また、現在採用されている代表的なTCPの端子間のピッチは、外圧によりTCPの各端子とプリント基板16の各端子どうしを接触させて電気的導通を得る圧接技術の関係上、300μmが限界である。したがって、プリント基板16の表層に形成された54本の配線が接続された各端子と、TCP17<sub>1</sub>～17<sub>10</sub>の上部に設けられた各端子とを圧接技術により接続すると、1.6cm以上も各TCP17<sub>1</sub>～17<sub>10</sub>の幅 $W_T$ (図20参照)が広くなる。これにより、10個のデータ電極駆動部 $4_1 \sim 4_{10}$ を設ける必要があるSXGAタイプの18型カラー液晶ディスプレイの場合、16cm以上もTCP17<sub>1</sub>～17<sub>10</sub>の取付幅が広くなるため、プリント基板16の幅 $W_p$ 方向(図20参照)に10個のTCP17<sub>1</sub>～17<sub>10</sub>を並べて設けることが物理的に不可能になるおそれがある。

【0012】第2に、プリント基板16の内層に54本の配線を形成し、各TCP17<sub>1</sub>～17<sub>10</sub>に接続する方法がある。この場合、プリント基板16の内層に形成された54本の配線とTCP17<sub>1</sub>～17<sub>10</sub>の上部に設けられた各端子とを接続するために、プリント基板16の内層に形成された54本の配線を、スルーホールを介してプリント基板16の表層に形成され対応する54

個の端子に接続された54本の配線とを接続する必要がある。現在採用されている代表的なスルーホールの径は、0.8mmであるから、この径0.8mmのスルーホールを54個も並列してプリント基板16上に形成すれば、すべてのスルーホールを形成するのに要する面積もそれだけ広く必要になる。さらに、以上説明した第1及び第2の方法のいずれにおいても、階調電源回路3から供給される赤階調電圧 $V_{R0} \sim V_{R17}$ 、緑階調電圧 $V_{G0} \sim V_{G17}$ 、青階調電圧 $V_{B0} \sim V_{B17}$ の個数

10 が異なれば、配線間ピッチ、プリント基板16の奥行き $D_p$ 、各TCP17<sub>1</sub>～17<sub>10</sub>の幅 $W_T$ が異なってくるから、それに合わせてプリント基板16及びTCP17<sub>1</sub>～17<sub>10</sub>を作製する必要があり、このことがプリント基板16及びTCP17<sub>1</sub>～17<sub>10</sub>のコストアップ、ひいては表示装置のコストアップの要因となるおそれがある。

【0013】この発明は、上述の事情に鑑みてなされたもので、基板実装面積を削減することができるとともに、カラー液晶ディスプレイの解像度や階調電圧の個数が異なっている場合であっても、共通の基板やTCPを用いることができ、これにより、基板やTCP、ひいては表示装置を安価に構成することができるカラー液晶ディスプレイの駆動回路、表示装置及びカラー液晶ディスプレイの駆動方法を提供することを目的としている。

【0014】

【課題を解決するための手段】上記課題を解決するためには、請求項1記載の発明は、複数個の階調電圧の中から映像信号に基づいて選択した階調電圧を用いてカラー液晶ディスプレイを駆動するデータ電極駆動回路を有するカラー液晶ディスプレイの駆動回路に係り、上記データ電極駆動回路は、供給されるデジタルの階調電圧設定データに基づいて階調電圧特性に応じた上記複数個の階調電圧を生成することを特徴としている。

【0015】また、請求項2記載の発明は、デジタル映像データの赤データ、緑データ、青データに対して、カラー液晶ディスプレイの印加電圧に対する赤、緑、青の透過率の特性に適合するように補正するガンマ補正をそれぞれ独立に施すことにより得られたデータ赤信号、データ緑信号、データ青信号を用いて上記カラー液晶ディ

40 スプレイを駆動するカラー液晶ディスプレイの駆動回路に係り、上記カラー液晶ディスプレイとは別個に設けられ、上記デジタル映像データの表示と関わらない無効期間中に、上記赤データ、緑データ、青データのガンマ補正に関する情報を出力する制御回路と、上記カラー液晶ディスプレイの近傍に設けられ、上記赤データ、緑データ、青データのガンマ補正に関する情報に基づいて、上記赤データ、緑データ、青データに対して、上記ガンマ補正を施すことにより得られたデータ赤信号、データ緑信号、データ青信号を用いて上記カラー液晶ディスプレイを駆動するデータ電極駆動回路とを備えてなることを

特徴としている。

【0016】また、請求項3記載の発明は、請求項2記載のカラー液晶ディスプレイの駆動回路に係り、上記制御回路は、上記カラー液晶ディスプレイの裏面に取り付けられたバックライトの裏面上部に取り付けられたプリント基板上に搭載され、上記データ電極駆動回路は、上記赤データ、緑データ、青データのうち、上記カラー液晶ディスプレイのデータ電極に対応した上記赤データ、緑データ、青データに対して上記ガンマ補正を施すことにより階調性を付与するとともにアナログのデータ赤信号、データ緑信号、データ青信号に変換して出力する複数個のデータ電極駆動部から構成され、上記複数個のデータ電極駆動部は、上記プリント基板と上記カラー液晶ディスプレイとを電気的に接続する対応するフィルムキヤリアテープ上にそれぞれ搭載されていることを特徴としている。

【0017】また、請求項4記載の発明は、請求項2又は3記載のカラー液晶ディスプレイの駆動回路に係り、上記赤データ、緑データ、青データのガンマ補正に関する情報は、上記赤データ、緑データ、青データのうちのいずれの階調電圧を設定するかを指示する階調情報と、複数個の階調電圧のいずれの値を選択するかを指示する階調電圧情報をからなることを特徴としている。

【0018】また、請求項5記載の発明は、請求項4記載のカラー液晶ディスプレイの駆動回路に係り、上記制御回路は、上記階調情報及び上記階調電圧情報を、シリアルデータとして上記データ電極駆動回路に供給することを特徴としている。

【0019】また、請求項6記載の発明は、請求項5記載のカラー液晶ディスプレイの駆動回路に係り、各データ電極駆動部は、上記シリアルデータをパラレルの階調情報及び階調電圧情報に変換して出力するシフトレジスタと、上記赤データ、緑データ、青データの複数個の階調電圧として、いずれの値の階調電圧を選択するかを示す選択信号が予め記憶された記憶部と、上記階調情報をデコードして、上記赤データ、緑データ、青データの複数個の階調電圧のうちのいずれを選択するかを指示する選択情報を出力するデコーダと、上記選択情報に従って上記記憶部から読み出された選択信号に基づいて、いずれかの値の階調電圧を選択して、複数個の赤階調電圧、緑階調電圧、青階調電圧として出力するマルチブレクサと、上記複数個の赤階調電圧、緑階調電圧、青階調電圧に基づいて、上記赤データ、緑データ、青データに、ガンマ補正を施すことにより階調性を付与するとともにアナログのデータ赤信号、データ緑信号、データ青信号に変換して出力するデータ信号出力部とを備えてなることを特徴としている。

【0020】また、請求項7記載の発明は、請求項4記載のカラー液晶ディスプレイの駆動回路に係り、上記制御回路は、上記階調電圧情報を、上記赤データ、緑データ、青データ

10

タ、青データを上記データ電極駆動回路に供給する配線を利用して供給することを特徴としている。

【0021】また、請求項8記載の発明は、請求項4又は7記載のカラー液晶ディスプレイの駆動回路に係り、上記赤データ、緑データ、青データを上記データ電極駆動回路に取り込むために使用されるクロックが上記データ電極駆動回路内部でカウントされるカウント数と、上記赤データ、緑データ、青データの階調電圧情報が上記データ電極駆動回路に供給される順番とを一対一に対応させるとともに、上記カウント数を上記階調情報とすることを特徴としている。

【0022】また、請求項9記載の発明は、請求項8記載のカラー液晶ディスプレイの駆動回路に係り、各データ電極駆動部は、上記赤データの複数個の赤階調電圧として、いずれの値の階調電圧を選択するかを示す選択信号が予め記憶された赤階調電圧情報記憶部と、上記緑データの複数個の緑階調電圧として、いずれの値の階調電圧を選択するかを示す選択信号が予め記憶された緑階調電圧情報記憶部と、上記青データの複数個の青階調電圧として、いずれの値の階調電圧を選択するかを示す選択信号が予め記憶された青階調電圧情報記憶部と、供給されるクロックの個数をカウントし、そのカウント数に応じて、複数個の階調電圧のうちのいずれを選択するかを指示する選択情報を出力する階調情報カウント部と、上記選択情報に従って上記赤階調電圧情報記憶部、緑階調電圧情報記憶部、青階調電圧情報記憶部から読み出された選択信号に基づいて、いずれかの値の階調電圧を選択して、複数個の赤階調電圧、緑階調電圧、青階調電圧として出力するマルチブレクサと、上記複数個の赤階調電圧、緑階調電圧、青階調電圧に基づいて、上記赤データ、緑データ、青データに、ガンマ補正を施すことにより階調性を付与するとともにアナログのデータ赤信号、データ緑信号、データ青信号に変換して出力するデータ信号出力部とを備えてなることを特徴としている。

【0023】また、請求項10記載の発明は、請求項2乃至9のいずれか1に記載のカラー液晶ディスプレイの駆動回路に係り、上記ガンマ補正是、上記赤データ、緑データ、青データに対して、入力画像の輝度に対する再生画像の輝度の特性を任意に付与するために補正するガンマ補正をも含むことを特徴としている。

【0024】また、請求項11記載の発明に係る表示装置は、請求項1乃至10のいずれか1に記載のカラー液晶ディスプレイの駆動回路を備えてなることを特徴としている。

【0025】また、請求項12記載の発明は、デジタル映像データの赤データ、緑データ、青データに対して、カラー液晶ディスプレイの印加電圧に対する赤、緑、青の透過率の特性に適合するように補正するガンマ補正をそれぞれ独立に施すことにより得られたデータ赤信号、データ緑信号、データ青信号を用いて上記カラー液晶デ

ィスプレイを駆動するカラー液晶ディスプレイの駆動方法に係り、上記デジタル映像データの表示と関わらない無効期間中に、上記赤データ、緑データ、青データのガンマ補正に関する情報を、上記カラー液晶ディスプレイとは別個に設けられた制御回路から、上記カラー液晶ディスプレイの近傍に設けられ、上記赤データ、緑データ、青データのガンマ補正に関する情報に基づいて、上記赤データ、緑データ、青データに対して、上記ガンマ補正を施すことにより得られたデータ赤信号、データ緑信号、データ青信号を用いて上記カラー液晶ディスプレイを駆動するデータ電極駆動回路に供給することを特徴としている。

#### 【0026】

【作用】この発明の構成によれば、基板実装面積を削減することができるとともに、カラー液晶ディスプレイの解像度や階調電圧の個数が異なっている場合であっても、共通の基板やTCPを用いることができる。これにより、基板やTCP、ひいては表示装置を安価に構成することができる。

#### 【0027】

【発明の実施の形態】以下、図面を参照して、この発明の実施の形態について説明する。説明は、実施例を用いて具体的に行う。

##### A . 第1の実施例

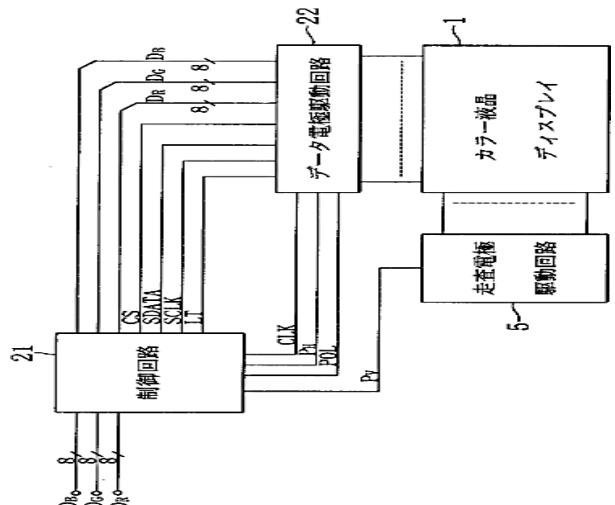

まず、この発明の第1の実施例について説明する。図1は、この発明の第1の実施例であるカラー液晶ディスプレイ1の駆動回路の構成を示すブロック図である。この図において、図17の各部に対応する部分には同一の符号を付け、その説明を省略する。この図に示すカラー液晶ディスプレイ1の駆動回路においては、図17に示す30制御回路2、階調電源回路3及びデータ電極駆動回路4に代えて、制御回路21及びデータ電極駆動回路22が新たに設けられている。

【0028】制御回路21は、例えば、ASICからなり、外部から供給されるそれぞれ8ビットの赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>をデータ電極駆動回路22に供給するとともに、外部から供給される水平同期信号S<sub>H</sub>及び垂直同期信号S<sub>V</sub>等に基づいて、水平走査パルスP<sub>H</sub>、垂直走査パルスP<sub>V</sub>、極性反転パルスP<sub>O</sub>L、クロックCLK、チップセレクト信号CS、シフトクロックSCLK、ラッチ信号LT及びシリアルデータSDATAを生成してデータ電極駆動回路22及び走査電極駆動回路5に供給する。

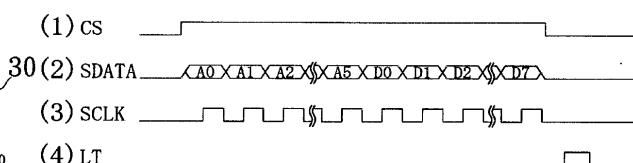

【0029】クロックCLKは、赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>をデータ電極駆動回路22を構成するデータレジスタに取り込むためなどに使用される。チップセレクト信号CSは、垂直帰線期間又は水平帰線期間等の画像表示と関わらない期間（以下、無効期間という）中に所定時間"H"レベルとなる信号である。シフトクロックSCLKは、クロックCLKとは非同期のク

ロックであり、シリアルデータSDATAをデータ電極駆動回路22に取り込むために使用される。ラッチ信号LTは、データ電極駆動回路22を構成するk個（kは自然数）のデータ電極駆動部22<sub>1</sub>～22<sub>k</sub>において、階調電圧情報記憶部28がシフトレジスタ27から供給されるパラレルの情報を取り込むタイミングを与える信号である（図5参照、詳細は後述）。

【0030】シリアルデータSDATAは、(n+1)ビット（nは自然数）の階調情報と(m+1)ビット（mは自然数）の階調電圧情報とから構成されており、チップセレクト信号CSが"H"レベルとなっている間に、シフトクロックSCLKに同期してデータ電極駆動回路22に供給される。階調情報は、赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>にそれぞれ別個独立にガンマ補正を施すことにより階調性を付与するために、赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>のうちのいずれのチャネルChR0～ChR17、ChG0～ChG17、ChB0～ChB17の階調電圧を設定するかを指示する情報である。ここで、図2にn=5である場合の20階調情報の各ビットA5～A0とチャネルChR0～ChR17、ChG0～ChG17、ChB0～ChB17との関係の一例を示す。

【0031】階調電圧情報は、赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>にそれぞれ別個独立にガンマ補正を施すことにより階調性を付与するために、データ電極駆動回路22を構成する各データ電極駆動部22<sub>1</sub>～22<sub>k</sub>において、階調電圧供給源29からマルチブレクサ（MPX）30（図5参照）に供給される256個の階調電圧V<sub>0</sub>（=V<sub>REF</sub>/255×0=0[V]）～V<sub>255</sub>（=V<sub>REF</sub>/255×255=V<sub>REF</sub>[V]）のいずれを選択するかを指示する情報である。V<sub>REF</sub>は、基準電圧である。ここで、図3にm=7である場合の階調電圧情報の各ビットD7～D0と階調電圧V<sub>0</sub>～V<sub>255</sub>との関係の一例を示す。なお、この例におけるガンマ補正是、上記した第1のガンマ補正と第2のガンマ補正とを含むものとする。

【0032】図1に示すデータ電極駆動回路22は、k個のデータ電極駆動部22<sub>1</sub>～22<sub>k</sub>から構成されている。各データ電極駆動部22<sub>1</sub>～22<sub>k</sub>は、制御回路21から供給される赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>のうち、カラー液晶ディスプレイ1のデータ電極に対応した赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>に対してガンマ補正を施すことにより階調性を付与するとともにアナログの384個のデータ信号S<sub>1</sub>～S<sub>384</sub>（図4参照）に変換して出力する。例えば、カラー液晶ディスプレイ1がSXGAタイプである場合には、データ電極駆動回路22は、10個のデータ電極駆動部22<sub>1</sub>～22<sub>10</sub>から構成されることになる。データ電極駆動部22<sub>1</sub>～22<sub>10</sub>は、各構成要素の添え字が異なるとともに、入出力される信号の添え字が異なる

以外は同一構成であるので、以下ではデータ電極駆動部22<sub>1</sub>についてのみ説明する。

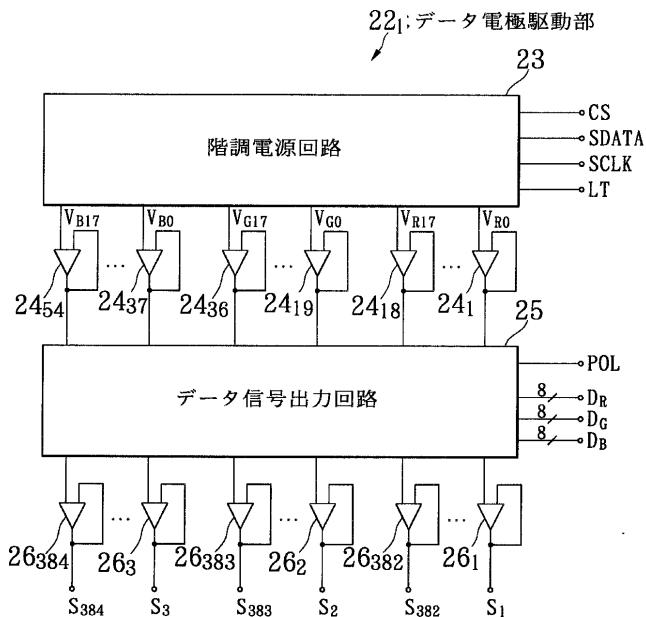

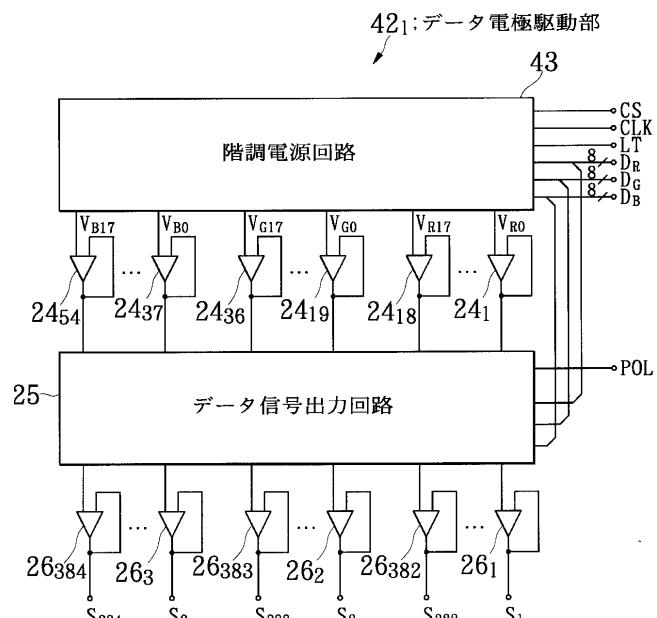

【0033】データ電極駆動部22<sub>1</sub>は、図4に示すように、階調電源回路23と、ボルテージフォロア24<sub>1</sub>～24<sub>54</sub>と、データ信号出力回路25と、ボルテージフォロア26<sub>1</sub>～26<sub>384</sub>とから概略構成されている。なお、実際のデータ電極駆動部においては、データ信号出力回路25の前段に、シフトレジスタ、データレジスタ、ラッチ、レベルシフタ等が設けられているが、これらの構成要素及びその動作は、この発明の特徴と直接関係ないので、この明細書においてはその説明を省略する。したがって、図4においては、水平走査パルスP<sub>H</sub>が供給される回路は図示されていない。

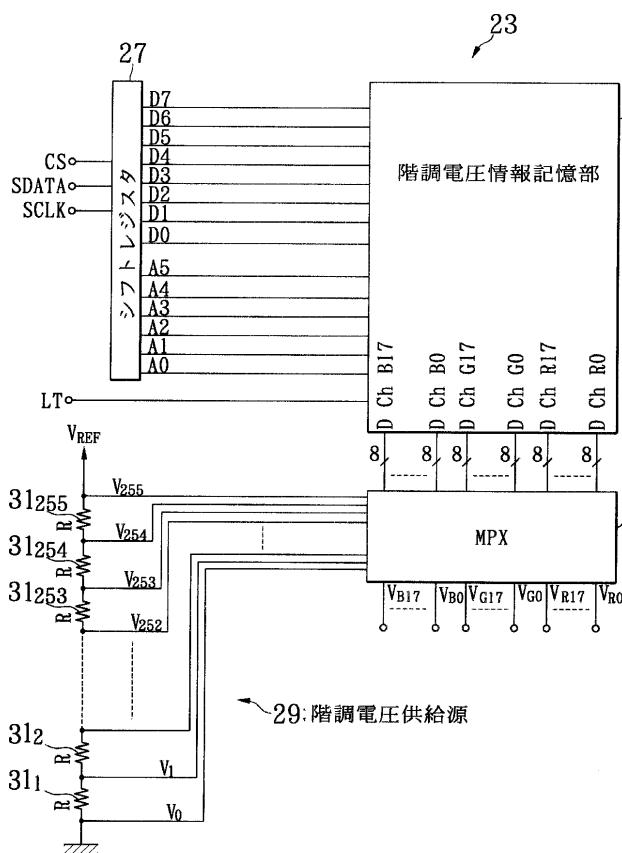

【0034】階調電源回路23は、図5に示すように、シフトレジスタ27と、階調電圧情報記憶部28と、階調電圧供給源29と、MPX30とから構成されている。シフトレジスタ27は、チップセレクト信号CSが"H"レベルである間に、シリアルデータSDATAをシフトクロックSCLKに同期して取り込み、パラレルの6ビットの階調情報A5～A0と8ビットの階調電圧情報D7～D0とを出力する。

【0035】階調電圧情報記憶部28は、ROM、RAM、あるいはフラッシュEEPROM等の不揮発性半導体メモリなどの半導体メモリからなり、チャネルChR0～ChR17、ChG0～ChG17、ChB0～ChB17ごとに、それぞれ8ビットの選択信号DChR0～DChR17、DChG0～DChG17、DChB0～DChB17が予め記憶されている記憶部と、シフトレジスタ27から供給される6ビットの階調情報A5～A0をデコードして、いずれのチャネルChR0～ChR17、ChG0～ChG17、ChB0～ChB17を選択するかを指示する選択情報SChR0～SChR17、SChG0～SChG17、SChB0～SChB17を出力するデコーダとから構成されている。この階調電圧情報記憶部28は、制御回路21から供給されるラッチ信号LTが"H"レベルとなるタイミングで、シフトレジスタ27から供給される6ビットの階調情報A5～A0及び8ビットの階調電圧情報D7～D0を内部に取り込み、階調情報A5～A0をデコードして得られた選択情報SChR0～SChR17、SChG0～SChG17、SChB0～SChB17に基づいて選択されたチャネルから、階調電圧情報D7～D0に基づいて選択された値の8ビットの選択信号DChR0～DChR17、DChG0～DChG17、DChB0～DChB17のいずれかを出し、MPX30に供給する。

【0036】階調電圧供給源29は、基準電圧V<sub>REF</sub>と接地との間に、同一抵抗値Rを有する255個の抵抗31<sub>1</sub>～31<sub>255</sub>が継続接続されて設けられ、256個の階調電圧V<sub>0</sub>(=V<sub>REF</sub>/255×0=0

[V]<sub>0</sub>)～V<sub>255</sub>(=V<sub>REF</sub>/255×255=V<sub>REF</sub>[V])をMPX30に供給する。MPX30は、階調電圧情報記憶部28から供給される8ビットの選択信号DChR0～DChR17、DChG0～DChG17、DChB0～DChB17に基づいて、階調電圧供給源29から供給される256個の階調電圧V<sub>0</sub>～V<sub>255</sub>のいずれかを選択して、アナログの赤階調電圧V<sub>R0</sub>～V<sub>R17</sub>、アナログの緑階調電圧V<sub>G0</sub>～V<sub>G17</sub>、アナログの青階調電圧V<sub>B0</sub>～V<sub>B17</sub>として出力する。

【0037】図4に示すボルテージフォロア24<sub>1</sub>～24<sub>54</sub>は、ガンマ補正のための対応する赤階調電圧V<sub>R0</sub>～V<sub>R17</sub>、緑階調電圧V<sub>G0</sub>～V<sub>G17</sub>、青階調電圧V<sub>B0</sub>～V<sub>B17</sub>をそのままデータ信号出力回路25に供給する。データ信号出力回路25は、ボルテージフォロア24<sub>1</sub>～24<sub>54</sub>から供給される赤階調電圧V<sub>R0</sub>～V<sub>R17</sub>、緑階調電圧V<sub>G0</sub>～V<sub>G17</sub>、青階調電圧V<sub>B0</sub>～V<sub>B17</sub>をそれぞれ256個の赤階調電圧V<sub>GR0</sub>～V<sub>GR255</sub>、緑階調電圧V<sub>GG0</sub>～V<sub>GG255</sub>、青階調電圧V<sub>GB0</sub>～V<sub>GB255</sub>に分割するとともに、これらそれぞれ256個の赤階調電圧V<sub>GR0</sub>～V<sub>GR255</sub>、緑階調電圧V<sub>GG0</sub>～V<sub>GG255</sub>、青階調電圧V<sub>GB0</sub>～V<sub>GB255</sub>のうち、制御回路21から供給される極性反転パルスPOLに基づいて切り替えられた、赤階調電圧V<sub>GR0</sub>～V<sub>GR127</sub>の組又は赤階調電圧V<sub>GR128</sub>～V<sub>GR255</sub>の組、緑階調電圧V<sub>GG0</sub>～V<sub>GG127</sub>の組又は緑階調電圧V<sub>GG128</sub>～V<sub>GG255</sub>の組、青階調電圧V<sub>GB0</sub>～V<sub>GB127</sub>の組又は青階調電圧V<sub>GB128</sub>～V<sub>GB255</sub>の組に基づいて、制御回路21から供給される8ビットの赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>に、ガンマ補正を施すことにより階調性を付与するとともにアナログのデータ赤信号S<sub>1</sub>、S<sub>4</sub>、S<sub>7</sub>、…、S<sub>382</sub>、データ緑信号S<sub>2</sub>、S<sub>5</sub>、S<sub>8</sub>、…、S<sub>383</sub>、データ青信号S<sub>3</sub>、S<sub>6</sub>、S<sub>9</sub>、…、S<sub>384</sub>に変換してボルテージフォロア26<sub>1</sub>～26<sub>384</sub>に供給する。ボルテージフォロア26<sub>1</sub>～26<sub>384</sub>は、データ信号出力回路25から供給されるデータ赤信号S<sub>1</sub>、S<sub>4</sub>、S<sub>7</sub>、…、S<sub>382</sub>、データ緑信号S<sub>2</sub>、S<sub>5</sub>、S<sub>8</sub>、…、S<sub>383</sub>、データ青信号S<sub>3</sub>、S<sub>6</sub>、S<sub>9</sub>、…、S<sub>384</sub>をそのままカラー液晶ディスプレイ1の対応するデータ電極に印加する。

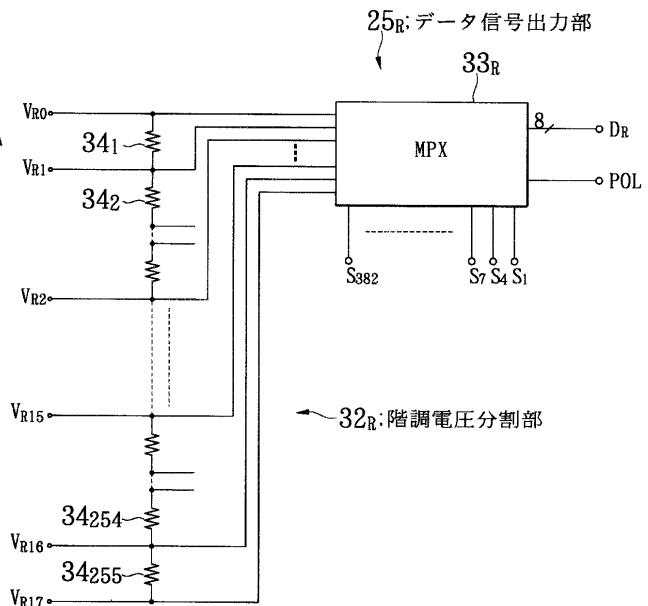

【0038】図4に示すデータ信号出力回路25は、赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>に対応して、3個のデータ信号出力部25<sub>R</sub>、25<sub>G</sub>、25<sub>B</sub>から構成されている。データ信号出力部25<sub>R</sub>、25<sub>G</sub>、25<sub>B</sub>は、各構成要素の添え字が異なるとともに、入出力される信号の種類が異なる以外は同一構成であるので、以下ではデータ信号出力部25<sub>R</sub>についてのみ説明する。

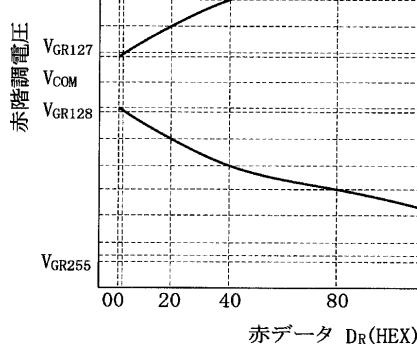

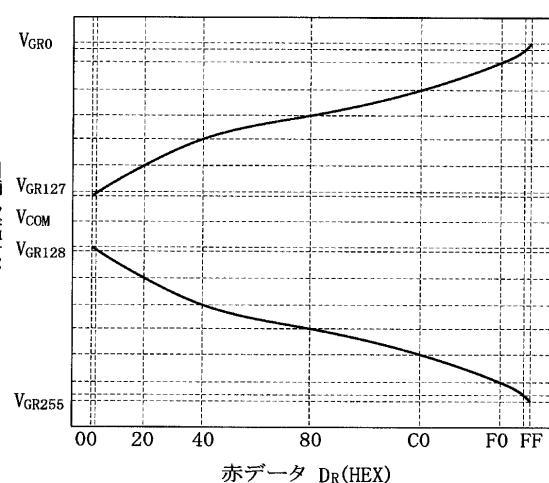

50 データ信号出力部25<sub>R</sub>は、図6に示すように、階調電

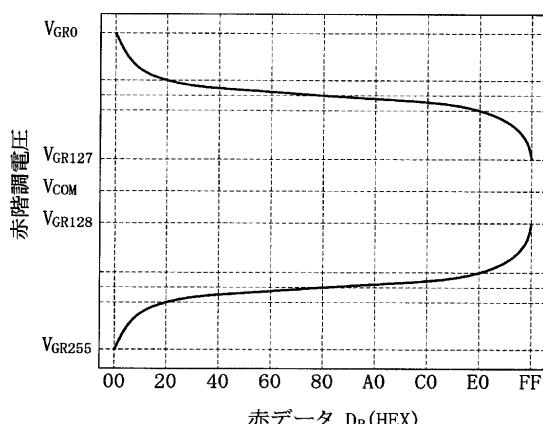

圧分割部32<sub>R</sub>と、MPX33<sub>R</sub>とから構成されている。階調電圧分割部32<sub>R</sub>は、255個のそれぞれ異なる抵抗値を有する抵抗34<sub>1</sub>～34<sub>255</sub>が継続接続されており、ボルテージフォロア24<sub>1</sub>～24<sub>18</sub>から供給される赤階調電圧V<sub>R0</sub>～V<sub>R17</sub>を256個の赤階調電圧V<sub>GR0</sub>～V<sub>GR255</sub>に分割してMPX33<sub>R</sub>に供給する。MPX33<sub>R</sub>は、階調電圧分割部32<sub>R</sub>から供給される256個の赤階調電圧V<sub>GR0</sub>～V<sub>GR255</sub>のうち、制御回路21から供給される極性反転パルスPOLに基づいて切り替えた、赤階調電圧V<sub>GR0</sub>～V<sub>GR127</sub>の組又は赤階調電圧V<sub>GR128</sub>～V<sub>GR255</sub>の組に基づいて、制御回路21から供給される8ビットの赤データD<sub>R</sub>に、ガンマ補正を施すことにより階調性を付与するとともにアナログのデータ赤信号S<sub>1</sub>、S<sub>4</sub>、S<sub>7</sub>、…、S<sub>382</sub>に変換してボルテージフォロア26<sub>1</sub>、26<sub>4</sub>、26<sub>7</sub>、…、26<sub>382</sub>に供給する。ここで、図7にデータ信号出力部25<sub>R</sub>に供給される8ビットの赤データD<sub>R</sub>(16進数(HEX)で表示)と赤階調電圧V<sub>GR0</sub>～V<sub>GR127</sub>及び赤階調電圧V<sub>GR128</sub>～V<sub>GR255</sub>との関係の一例を示す。図7から分かるように、データ信号出力部25<sub>R</sub>においては、第1のガンマ補正と第2のガンマ補正とを含むガンマ補正を赤データD<sub>R</sub>に施すことにより階調性を付与するために、赤データD<sub>R</sub>のデータ値に対して非線形的な電圧値をとる赤階調電圧V<sub>GR0</sub>～V<sub>GR127</sub>の組又は赤階調電圧V<sub>GR128</sub>～V<sub>GR255</sub>の組が階調電圧分割部32<sub>R</sub>からMPX33<sub>R</sub>に供給される。

【0039】そして、上記構成のカラー液晶ディスプレイの駆動回路を備えた表示装置においては、図20を例にとれば、制御回路21だけがプリント基板16上に搭載されるのに対し、データ電極駆動部22<sub>1</sub>～22<sub>10</sub>は、プリント基板16とカラー液晶ディスプレイ1とを電気的に接続する10個のフィルムキャリアテープ上にそれぞれ搭載され、TCP17<sub>1</sub>～17<sub>10</sub>として実装される。プリント基板16は、図21に示すように、カラー液晶ディスプレイ1の裏面に取り付けられた断面くさび型状のバックライト18の裏面上部に取り付けられる。

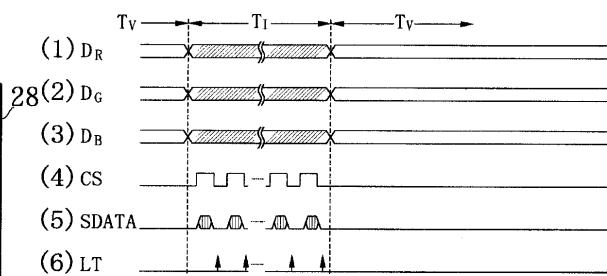

【0040】次に、上記構成のカラー液晶ディスプレイの駆動回路の動作のうち、この発明の特徴である制御回路21及びデータ電極駆動回路22の動作について、図8及び図9に示すタイミング・チャートを参照して説明する。制御回路21は、例えば、この例のカラー液晶ディスプレイの駆動回路を備えた表示装置に電源が投入された後、カラー映像信号の垂直帰線期間又は水平帰線期間等の画像表示と関わらない期間である無効期間T<sub>I</sub>中に、図8(4)～(6)に示すタイミング、より詳細には、図9(1)～(4)に示すタイミングで、チップセレクト信号CS、シリアルデータSDATA、シフトク

ロックSCLK及びラッチ信号LTをデータ電極駆動回路22に供給する。

【0041】すなわち、制御回路21は、無効期間T<sub>I</sub>中に、図9(1)に示すチップセレクト信号CSを所定時間"H"レベルとし、その間に、図9(3)に示すシフトクロックSCLKに同期して、図9(2)に示す、赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>のうちのいずれのチャネルChR0～ChR17、ChG0～ChG17、ChB0～ChB17の階調電圧を設定するかを指示する、6ビットの階調情報A5～A0(図2参照)と、256個の階調電圧V<sub>0</sub>～V<sub>255</sub>のいずれを選択するかを指示する、8ビットの階調電圧情報D7～D0(図3参照)とから構成されたシリアルデータSDATAをデータ電極駆動回路22に供給した後、図9(4)に示すラッチ信号LTを供給する。

【0042】これにより、データ電極駆動回路22を構成する各データ電極駆動部22<sub>1</sub>～22<sub>10</sub>においては、階調電源回路23を構成するシフトレジスタ27がチップセレクト信号CSが"H"レベルである間に、シリアルデータSDATAをシフトクロックSCLKに同期して取り込み、パラレルの6ビットの階調情報A5～A0と8ビットの階調電圧情報D7～D0とを出力し、階調電圧情報記憶部28に供給する。そして、階調電圧情報記憶部28は、制御回路21から供給されるラッチ信号LTが"H"レベルとなるタイミング(図9(4)参照)で、シフトレジスタ27から供給される6ビットの階調情報A5～A0及び8ビットの階調電圧情報D7～D0を内部に取り込み、デコーダが階調情報A5～A0をデコードして得られた選択情報SChR0～SChR17、SChG0～SChG17、SChB0～SChB17に基づいて選択されたチャネルから、階調電圧情報D7～D0に基づいて選択された値の8ビットの選択信号DChR0～DChR17、DChG0～DChG17、DChB0～DChB17のいずれかを出力し、MPX30に供給する。

【0043】次に、MPX30が階調電圧情報記憶部28から供給される8ビットの選択信号DChR0～DChR17、DChG0～DChG17、DChB0～DChB17に基づいて、階調電圧供給源29から供給される256個の階調電圧V<sub>0</sub>～V<sub>255</sub>のいずれかを選択して、アナログの赤階調電圧V<sub>R0</sub>～V<sub>R17</sub>、アナログの緑階調電圧V<sub>G0</sub>～V<sub>G17</sub>、アナログの青階調電圧V<sub>B0</sub>～V<sub>B17</sub>として出力するので、図4に示すボルテージフォロア24<sub>1</sub>～24<sub>54</sub>は、対応する赤階調電圧V<sub>GR0</sub>～V<sub>GR17</sub>、緑階調電圧V<sub>GG0</sub>～V<sub>GG17</sub>、青階調電圧V<sub>BB0</sub>～V<sub>BB17</sub>をそのままデータ信号出力回路25に供給する。これにより、データ信号出力回路25を構成する各データ信号出力部25<sub>R</sub>、25<sub>G</sub>、25<sub>B</sub>において、各階調電圧分割部33<sub>R</sub>、33<sub>G</sub>、33<sub>B</sub>は、ボルテージフォロア24<sub>1</sub>～24<sub>54</sub>

から供給される赤階調電圧  $V_{R0} \sim V_{R17}$ 、緑階調電圧  $V_{G0} \sim V_{G17}$ 、青階調電圧  $V_{B0} \sim V_{B17}$  をそれぞれ 256 個の赤階調電圧  $V_{GR0} \sim V_{GR255}$ 、緑階調電圧  $V_{GG0} \sim V_{GG255}$ 、青階調電圧  $V_{GB0} \sim V_{GB255}$  に分割して、MPX32<sub>R</sub>、32<sub>G</sub>、32<sub>B</sub> に供給する。以上説明した動作が図 8 に示す無効期間  $T_1$  中に順次繰り返されることにより、カラー液晶ディスプレイ 1 の赤、緑、青にそれぞれ対応する  $V - T$  特性の最低輝度から最高輝度までの範囲を充分に活用できるように考慮した赤階調電圧  $V_{GR0} \sim V_{GR255}$ 、緑階調電圧  $V_{GG0} \sim V_{GG255}$ 、青階調電圧  $V_{GB0} \sim V_{GB255}$  が MPX32<sub>R</sub>、32<sub>G</sub>、32<sub>B</sub> に設定される。

【0044】このような状態において、制御回路 21 は、図 8(1)～(3) に示すように、カラー映像信号の画像表示と関わる期間である有効期間  $T_v$  中に、外部から供給されたそれぞれ 8 ビットの赤データ  $D_R$ 、緑データ  $D_G$ 、青データ  $D_B$  をクロック CLK に同期してデータ電極駆動回路 22 に供給する。これにより、データ電極駆動回路 22 を構成する各データ電極駆動部 22<sub>1</sub>～22<sub>10</sub> は、設定されたそれぞれ 256 個の赤階調電圧  $V_{GR0} \sim V_{GR255}$ 、緑階調電圧  $V_{GG0} \sim V_{GG255}$ 、青階調電圧  $V_{GB0} \sim V_{GB255}$  のうち、制御回路 21 から供給される極性反転パルス POL に基づいて切り替えられた、赤階調電圧  $V_{GR0} \sim V_{GR127}$  の組又は赤階調電圧  $V_{GR128} \sim V_{GR255}$  の組、緑階調電圧  $V_{GG0} \sim V_{GG127}$  の組又は緑階調電圧  $V_{GG128} \sim V_{GG255}$  の組、青階調電圧  $V_{GB0} \sim V_{GB127}$  の組又は青階調電圧  $V_{GB128} \sim V_{GB255}$  の組に基づいて、制御回路 21 から供給される 8 ビットの赤データ  $D_R$ 、緑データ  $D_G$ 、青データ  $D_B$  に、ガンマ補正を施すことにより階調性を付与するとともにアナログのデータ赤信号、データ緑信号、データ青信号に変換した後、ボルテージフォア 26 においてそのままカラー液晶ディスプレイ 1 の対応するデータ電極に印加する。

【0045】このように、この例の構成によれば、階調電源回路 23 がデータ電極駆動部 22<sub>1</sub>～22<sub>10</sub> の内部に設けられているため、従来の第 1 の方法のように、プリント基板 16 の表層に配線を形成する場合には、チップセレクト信号 CS、シリアルデータ SDATA、シフトクロック SCLK 及びラッチ信号 LATCH を伝送するための 4 本の配線で済むので、50 本もの配線を削減することができ、プリント基板 16 の奥行き  $D_p$  (図 20 参照) が長くなることはなく、プリント基板 16 がバックライト 18 の裏面上部に取り付けられる面積 (図 20 参照) も広くなることはない。したがって、カラー液晶ディスプレイのタイプ、すなわち、解像度が異なっても、各タイプに共通のバックライト 18 を用いることができ、表示装置のコストがアップすることはない。また、

TCP17<sub>1</sub>～17<sub>10</sub> の幅  $W_T$  (図 20 参照) が広くなることがないので、プリント基板 16 の幅  $W_p$  方向 (図 20 参照) に 10 個の TCP17<sub>1</sub>～17<sub>10</sub> を容易に並べて設けることができる。

【0046】一方、従来の第 2 の方法のように、プリント基板 16 の内層に配線を形成する場合でも、4 本の配線で済むので、このプリント基板 16 の内層に形成された 4 本の配線を、スルーホールを介してプリント基板 16 の表層に形成され対応する 4 個の端子に接続された 4

- 10 本の配線と接続する場合であっても、すべてのスルーホールを形成するのに要する面積が広く必要となることはない。さらに、この例の構成によれば、階調電源回路 23 がデータ電極駆動部 22<sub>1</sub>～22<sub>10</sub> の内部に設けられているため、赤階調電圧  $V_{R0} \sim V_{R17}$ 、緑階調電圧  $V_{G0} \sim V_{G17}$ 、青階調電圧  $V_{B0} \sim V_{B17}$  の個数が異なっても、すべてのスルーホールの形成面積、プリント基板 16 の奥行き  $D_p$ 、各 TCP17<sub>1</sub>～17<sub>10</sub> の幅  $W_T$  が異なることはないから、カラー液晶ディスプレイのタイプ、すなわち、解像度が異なっても、各 20 タイプに共通のプリント基板 16 及び TCP17<sub>1</sub>～17<sub>10</sub> を用いることができ、プリント基板 16 及び TCP17<sub>1</sub>～17<sub>10</sub> のコストがアップすることではなく、当然に表示装置のコストがアップすることはない。以上のことから、この例の構成によれば、基板実装面積を削減することができるとともに、カラー液晶ディスプレイの解像度や階調電圧の個数が異なっている場合であっても、共通の基板や TCP を用いることができ、これにより、基板や TCP、ひいては表示装置を安価に構成することができる。もちろん、従来と同様、最適なガンマ補正を施すことにより階調性を付与することができ、良好な階調の再生画像を得ることができるとともに、高透過率の  $V - T$  特性を有するカラー液晶ディスプレイ 1 でも充分に使いこなすことができる。また、赤、緑、青のいずれか特定の色において階調つぶれが発生した場合には、制御回路 21 は、階調つぶれが発生している色の領域 (白レベル付近、灰色付近、黒レベル付近のいずれか) に対応した階調電圧 ( $V_{R0} \sim V_{R17}$ 、 $V_{G0} \sim V_{G17}$ 、 $V_{B0} \sim V_{B17}$  のいずれか) を変更するために変更された階調情報及び階調電圧情報をデータ電極駆動回路 22 に供給することにより、当該階調つぶれを取り除くことができる。

【0047】B. 第 2 の実施例

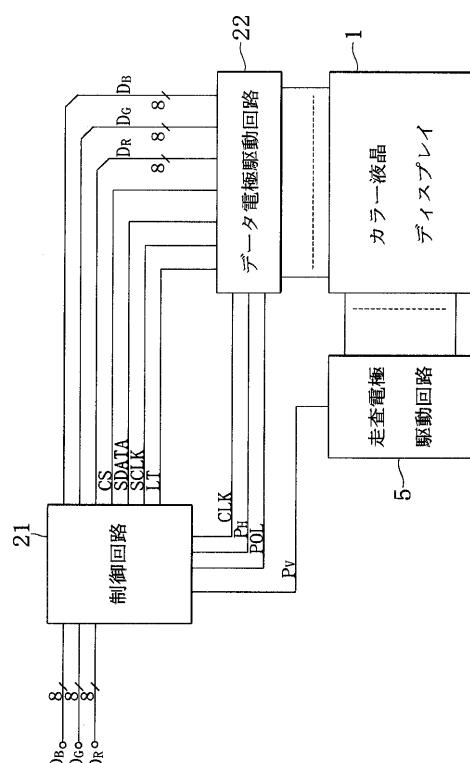

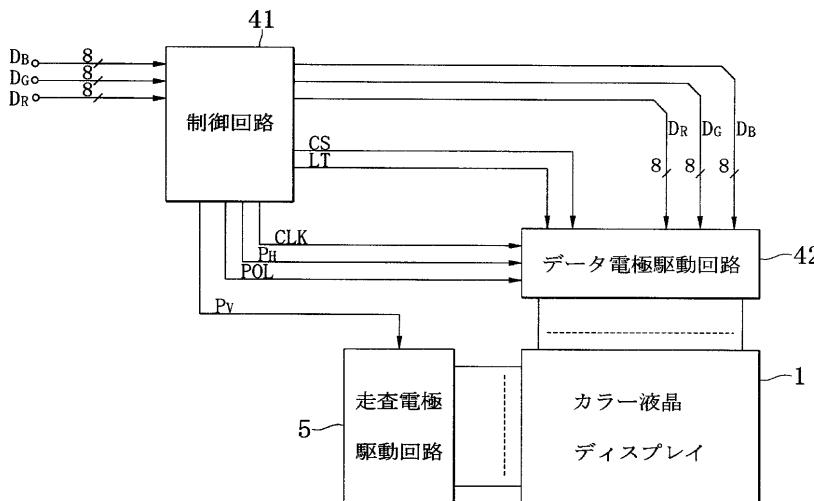

次に、この発明の第 2 の実施例について説明する。図 10 は、この発明の第 2 の実施例であるカラー液晶ディスプレイ 1 の駆動回路の構成を示すブロック図である。この図において、図 1 の各部に対応する部分には同一の符号を付け、その説明を省略する。この図に示すカラー液晶ディスプレイ 1 の駆動回路においては、図 1 に示す制御回路 21 及びデータ電極駆動回路 22 に代えて、制御回路 41 及びデータ電極駆動回路 42 が新たに設けられ

ている。

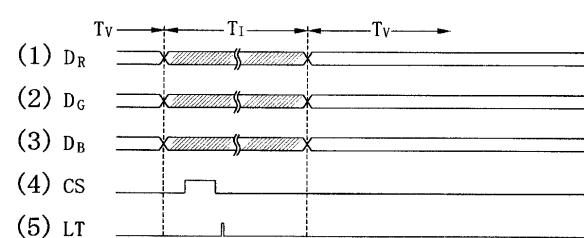

【0048】制御回路41は、例えば、ASICからなり、外部から供給されるそれぞれ8ビットの赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>をデータ電極駆動回路42に供給するとともに、外部から供給される水平同期信号S<sub>H</sub>及び垂直同期信号S<sub>V</sub>等に基づいて、水平走査パルスP<sub>H</sub>、垂直走査パルスP<sub>V</sub>、極性反転パルスP<sub>O</sub>L、クロックCLK、チップセレクト信号CS及びラッチ信号LTを生成してデータ電極駆動回路42及び走査電極駆動回路5に供給する。

【0049】クロックCLKは、赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>をデータ電極駆動回路42を構成するデータレジスタに取り込むためなどに使用される。チップセレクト信号CSは、垂直帰線期間又は水平帰線期間等の画像表示と関わらない無効期間中に所定時間"H"レベルとなる信号である。ラッチ信号LTは、データ電極駆動回路42を構成するk個(kは自然数)のデータ電極駆動部42<sub>1</sub>~42<sub>k</sub>において、階調電圧情報記憶部45<sub>R</sub>、45<sub>G</sub>、45<sub>B</sub>が制御回路41から8ビットでパラレルの赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>を供給する配線を利用して供給される、各チャネルChR0~ChR17、ChG0~ChG17、ChB0~ChB17ごとの赤階調電圧情報D<sub>R0</sub>~D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>~D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>~D<sub>B17</sub>を取り込むタイミングを与える信号である(図13参照、詳細は後述)。

【0050】赤階調電圧情報D<sub>R0</sub>~D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>~D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>~D<sub>B17</sub>は、赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>にそれぞれ別個独立にガンマ補正を施すことにより階調性を付与するために、データ電極駆動回路42を構成する各データ電極駆動部42<sub>1</sub>~42<sub>k</sub>において、階調電圧供給源29からMPX30(図13参照)に供給される256個の階調電圧V<sub>0</sub>(=V<sub>REF</sub>/255×0=0[V])~V<sub>255</sub>(=V<sub>REF</sub>/255×255=V<sub>REF</sub>[V])のいずれを選択するかを指示する情報である。V<sub>REF</sub>は、基準電圧である。ここで、図11に赤階調電圧情報D<sub>R0</sub>~D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>~D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>~D<sub>B17</sub>の各

ビットD7~D0と階調電圧V<sub>0</sub>~V<sub>255</sub>との関係の一例を示す。なお、この例においては、クロックCLKのカウント数が、赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>にそれぞれ別個独立にガンマ補正を施すことにより階調性を付与するために、赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>のうちのいずれのチャネルChR0~ChR17、ChG0~ChG17、ChB0~ChB17に対応しているかを指示する階調情報の役割を担っている。すなわち、チップセレクト信号CS(図15(1)参照)が"H"レベルとなっている間に供給される、クロックCLK(図15(5)参照)のカウント数

と、赤階調電圧情報D<sub>R0</sub>~D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>~D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>~D<sub>B17</sub>(図15(2)~(4)参照)とが一对一に対応しており、例えば、クロックCLKのカウント数が0の時に供給された赤階調電圧情報D<sub>R0</sub>、緑階調電圧情報D<sub>G0</sub>、青階調電圧情報D<sub>B0</sub>がチャネルChR0、ChG0、ChB0に対応していることになる。また、この例におけるガンマ補正是、上記した第1のガンマ補正と第2のガンマ補正とを含むものとする。

10 【0051】図10に示すデータ電極駆動回路42は、k個のデータ電極駆動部42<sub>1</sub>~42<sub>k</sub>から構成されている。各データ電極駆動部42<sub>1</sub>~42<sub>k</sub>は、制御回路41から供給される赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>のうち、カラー液晶ディスプレイ1の対応するデータ電極に対応した赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>に対してガンマ補正を施すことにより階調性を付与するとともにアナログの384個のデータ信号S<sub>1</sub>~S<sub>384</sub>に変換して出力する。例えば、カラー液晶ディスプレイ1がSXGAタイプである場合には、データ電極駆動回路42は、10個のデータ電極駆動部42<sub>1</sub>~42<sub>10</sub>から構成されることになる。データ電極駆動部42<sub>1</sub>~42<sub>10</sub>は、各構成要素の添え字が異なるとともに、入出力される信号の添え字が異なる以外は同一構成であるので、以下ではデータ電極駆動部42<sub>1</sub>についてのみ説明する。

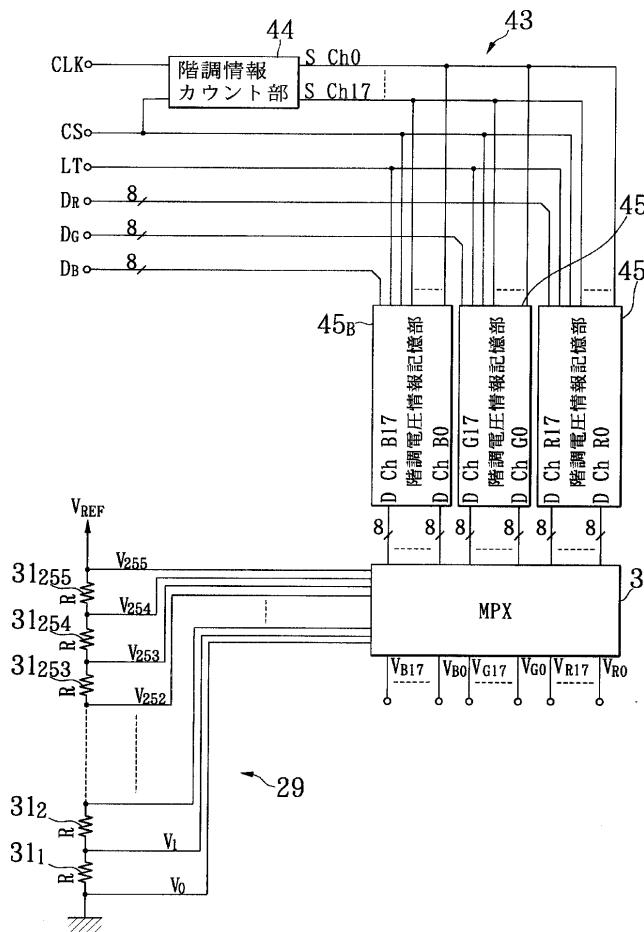

【0052】図12は、データ電極駆動部42<sub>1</sub>の構成を示すブロック図である。この図において、図4の各部に対応する部分には同一の符号を付け、その説明を省略する。この図に示すデータ電極駆動部42<sub>1</sub>においては、図4に示す階調電源回路23に代えて、階調電源回路43が新たに設けられている。図13は、階調電源回路43の構成を示すブロック図である。この図において、図5の各部に対応する部分には同一の符号を付け、その説明を省略する。この図に示す階調電源回路43においては、図5に示すシフトレジスタ27及び階調電圧情報記憶部28に代えて、階調情報カウント部44と、階調電圧情報記憶部45<sub>R</sub>、45<sub>G</sub>、45<sub>B</sub>とが新たに設けられている。

【0053】階調情報カウント部44は、チップセレクト信号CSが"H"レベルである間に供給されるクロックCLKの個数をカウントし、そのカウント数に応じて、いずれのチャネルChR0~ChR17、ChG0~ChG17、ChB0~ChB17を選択するかを指示する"H"レベルの選択情報SCh0~SCh17を順次出力する。階調電圧情報記憶部45<sub>R</sub>、45<sub>G</sub>、45<sub>B</sub>は、ROM、RAM、あるいはフラッシュEEPROM等の不揮発性半導体メモリなどの半導体メモリからなり、それぞれのチャネルChR0~ChR17、ChG0~ChG17、ChB0~ChB17に、それぞれ8ビットの選択信号DChR0~DChR17、DChG

0～DChG17、DChB0～DChB17が予め記憶されている。これらの階調電圧情報記憶部45<sub>R</sub>、45<sub>G</sub>、45<sub>B</sub>は、制御回路41から供給されるラッチ信号LTが"H"レベルとなるタイミングで、制御回路41から供給される8ビットの階調電圧情報である赤階調電圧情報D<sub>R0</sub>～D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>～D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>～D<sub>B17</sub>を内部に取り込み、階調情報カウント部44から供給される"H"レベルの選択情報SCh0～SCh17に基づいて選択されたチャネルから、赤階調電圧情報D<sub>R0</sub>～D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>～D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>～D<sub>B17</sub>に基づいて選択された値の8ビットの選択信号DChR0～DChR17、DChG0～DChG17、DChB0～DChB17のいずれかを出力し、MPX30に供給する。

【0054】そして、上記構成のカラー液晶ディスプレイの駆動回路を備えた表示装置においては、図20を例にとれば、制御回路41だけがプリント基板16上に搭載されるのに対し、データ電極駆動部42<sub>1</sub>～42<sub>10</sub>は、プリント基板16とカラー液晶ディスプレイ1とを電気的に接続する10個のフィルムキャリアテープ上にそれぞれ搭載され、TCP17<sub>1</sub>～17<sub>10</sub>として実装される。プリント基板16は、図21に示すように、カラー液晶ディスプレイ1の裏面に取り付けられた断面略くさび型状のバックライト18の裏面上部に取り付けられる。

【0055】次に、上記構成のカラー液晶ディスプレイの駆動回路の動作のうち、この発明の特徴である制御回路41及びデータ電極駆動回路42の動作について、図14及び図15に示すタイミング・チャートを参照して説明する。制御回路41は、例えば、この例のカラー液晶ディスプレイの駆動回路を備えた表示装置に電源が投入された後、カラー映像信号の垂直帰線期間又は水平帰線期間等の画像表示と関わらない期間である無効期間T<sub>I</sub>中に、図14(4)及び(5)に示すタイミング、より詳細には、図15(1)～(6)に示すタイミングで、チップセレクト信号CS、ラッチ信号LT及びクロックCLKを専用の配線を用いて、赤階調電圧情報D<sub>R0</sub>～D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>～D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>～D<sub>B17</sub>を赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>を供給する配線を利用して、データ電極駆動回路42に供給する。

【0056】すなわち、制御回路41は、無効期間T<sub>I</sub>中に、図15(1)に示すチップセレクト信号CSを所定時間"H"レベルとし、その間に、図15(5)に示すクロックCLKに同期して、図15(2)～(4)に示す、256個の階調電圧V<sub>0</sub>～V<sub>255</sub>のいずれを選択するかを指示する、それぞれ8ビットの赤階調電圧情報D<sub>R0</sub>～D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>～D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>～D<sub>B17</sub>(図11参照)をデータ電極駆動回路42に供給する。

タ電極駆動回路42に供給した後、図15(6)に示すラッチ信号LTを供給する。

【0057】これにより、データ電極駆動回路42を構成する各データ電極駆動部42<sub>1</sub>～42<sub>10</sub>においては、階調電源回路43を構成する階調情報カウント部44がチップセレクト信号CSが"H"レベルである間に供給されるクロックCLKの個数をカウントし、"H"レベルの選択情報SCh0～SCh17を順次出力する。そして、階調電圧情報記憶部45<sub>R</sub>、45<sub>G</sub>、45<sub>B</sub>は、10制御回路41から供給されるラッチ信号LTが"H"レベルとなるタイミング(図15(6)参照)で、制御回路41から供給される8ビットの階調電圧情報である赤階調電圧情報D<sub>R0</sub>～D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>～D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>～D<sub>B17</sub>を内部に取り込み、階調情報カウント部44から供給される"H"レベルの選択情報SCh0～SCh17に基づいて選択されたチャネルから、赤階調電圧情報D<sub>R0</sub>～D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>～D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>～D<sub>B17</sub>に基づいて選択された値の8ビットの選択信号DChR0～DChR17、DChG0～DChG17、DChB0～DChB17のいずれかを出力し、MPX30に供給する。

【0058】次に、MPX30が階調電圧情報記憶部28から供給される8ビットの選択信号DChR0～DChR17、DChG0～DChG17、DChB0～DChB17に基づいて、階調電圧供給源29から供給される256個の階調電圧V<sub>0</sub>～V<sub>255</sub>のいずれかを選択して、アナログの赤階調電圧V<sub>R0</sub>～V<sub>R17</sub>、アナログの緑階調電圧V<sub>G0</sub>～V<sub>G17</sub>、アナログの青階調電圧V<sub>B0</sub>～V<sub>B17</sub>として出力するので、図4に示すボルテージフォロア24<sub>1</sub>～24<sub>54</sub>は、対応する赤階調電圧V<sub>R0</sub>～V<sub>R17</sub>、緑階調電圧V<sub>G0</sub>～V<sub>G17</sub>、青階調電圧V<sub>B0</sub>～V<sub>B17</sub>をそのままデータ信号出力回路25に供給する。これにより、データ信号出力回路25を構成する各データ信号出力部25<sub>R</sub>、25<sub>G</sub>、25<sub>B</sub>において、各階調電圧分割部33<sub>R</sub>、31<sub>G</sub>、31<sub>B</sub>は、ボルテージフォロア24<sub>1</sub>～24<sub>54</sub>から供給される赤階調電圧V<sub>R0</sub>～V<sub>R17</sub>、緑階調電圧V<sub>G0</sub>～V<sub>G17</sub>、青階調電圧V<sub>B0</sub>～V<sub>B17</sub>をそれぞれ256個の赤階調電圧V<sub>GR0</sub>～V<sub>GR255</sub>、緑階調電圧V<sub>GG0</sub>～V<sub>GG255</sub>、青階調電圧V<sub>GB0</sub>～V<sub>GB255</sub>に分割して、MPX32<sub>R</sub>、32<sub>G</sub>、32<sub>B</sub>に供給する。以上説明した動作が1回行われることにより、カラー液晶ディスプレイ1の赤、緑、青にそれぞれ対応するV-T特性の最低輝度から最高輝度までの範囲を充分に活用できるように考慮した赤階調電圧V<sub>GR0</sub>～V<sub>GR255</sub>、緑階調電圧V<sub>GG0</sub>～V<sub>GG255</sub>、青階調電圧V<sub>GB0</sub>～V<sub>GB255</sub>がMPX32<sub>R</sub>、32<sub>G</sub>、32<sub>B</sub>に設定される。なお、これ以後の動作は、上記した第1の実施例の動作と略同様である。

るので、その説明を省略する。

【0059】このように、この例の構成によれば、階調電源回路43がデータ電極駆動部42<sub>1</sub>～42<sub>10</sub>の内部に設けられているため、従来の第1の方法のように、プリント基板16の表層に配線を形成する場合には、チップセレクト信号CS及びラッチ信号LTを伝送する2本の配線で済むので、52本もの配線を削減することができ、プリント基板16の奥行きD<sub>p</sub>(図20参照)が長くなることはなく、プリント基板16がバックライト18の裏面上部に取り付けられる面積(図20参照)も広くなることはない。したがって、カラー液晶ディスプレイのタイプ、すなわち、解像度が異なっても、各タイプに共通のバックライト18を用いることができ、表示装置のコストがアップすることはない。また、TCP17<sub>1</sub>～17<sub>10</sub>の幅W<sub>T</sub>(図20参照)が広くなることがないので、プリント基板16の幅W<sub>p</sub>方向(図20参照)に10個のTCP17<sub>1</sub>～17<sub>10</sub>を容易に並べて設けることができる。

【0060】一方、従来の第2の方法のように、プリント基板16の内層に配線を形成する場合でも、2本の配線で済むので、このプリント基板16の内層に形成された2本の配線を、スルーホールを介してプリント基板16の表層に形成され対応する2個の端子に接続された2本の配線と接続する場合であっても、すべてのスルーホールを形成するのに要する面積が広く必要になることはない。さらに、この例の構成によれば、階調電源回路43がデータ電極駆動部42<sub>1</sub>～42<sub>10</sub>の内部に設けられているため、赤階調電圧V<sub>R0</sub>～V<sub>R17</sub>、緑階調電圧V<sub>G0</sub>～V<sub>G17</sub>、青階調電圧V<sub>B0</sub>～V<sub>B17</sub>の個数が異なっても、すべてのスルーホールの形成面積、プリント基板16の奥行きD<sub>p</sub>、各TCP17<sub>1</sub>～17<sub>10</sub>の幅W<sub>T</sub>が異なることはないから、カラー液晶ディスプレイのタイプ、すなわち、解像度が異なっても、各タイプに共通のプリント基板16及びTCP17<sub>1</sub>～17<sub>10</sub>を用いることができ、プリント基板16及びTCP17<sub>1</sub>～17<sub>10</sub>のコストがアップすることはなく、当然に表示装置のコストがアップすることはない。以上のことから、この例の構成によれば、基板実装面積を削減することができるとともに、カラー液晶ディスプレイの解像度や階調電圧の個数が異なっている場合であっても、共通の基板やTCPを用いることができ、これにより、基板やTCP、ひいては表示装置を安価に構成することができる。さらに、この例の構成によれば、無効期間T<sub>I</sub>中に、赤階調電圧情報D<sub>R0</sub>～D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>～D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>～D<sub>B17</sub>を赤データD<sub>R</sub>、緑データD<sub>G</sub>、青データD<sub>B</sub>を供給する配線を利用して、データ電極駆動回路42に供給しているので、上記した第1の実施例よりもさらに配線数を削減することができるとともに、配線を有効利用することができる。また、1回の動作で、赤階調電圧V

<sub>G R 0</sub>～V<sub>G R 2 5 5</sub>、緑階調電圧V<sub>G G 0</sub>～V<sub>G G 2 5 5</sub>

<sub>G G 2 5 5</sub>、青階調電圧V<sub>G B 0</sub>～V<sub>G B 2 5 5</sub>がMP

X<sub>3 2 R</sub>、3<sub>2 G</sub>、3<sub>2 B</sub>に設定されるので、上記した第1の実施例と比べて、処理が簡単となるとともに、設定する時間を短縮することができる。

【0061】もちろん、従来と同様、最適なガンマ補正を施すことにより階調性を付与することができ、良好な階調の再生画像を得ることができるとともに、高透過率のV-T特性を有するカラー液晶ディスプレイ1でも充分に使いこなすことができる。また、赤、緑、青のいずれか特定の色において階調つぶれが発生した場合には、制御回路41は、階調つぶれが発生している色の領域(白レベル付近、灰色付近、黒レベル付近のいずれか)に対応した階調電圧(V<sub>R0</sub>～V<sub>R17</sub>、V<sub>G0</sub>～V<sub>G17</sub>、V<sub>B0</sub>～V<sub>B17</sub>のいずれか)を変更するため

に変更された階調情報及び階調電圧情報をデータ電極駆動回路42に供給することにより、当該階調つぶれを取り除くことができる。

【0062】以上、この発明の実施例を図面を参照して詳述してきたが、具体的な構成はこの実施例に限られるものではなく、この発明の要旨を逸脱しない範囲の設計の変更等があってもこの発明に含まれる。例えば、上述の各実施例においては、この発明をノーマリー・ラック型のカラー液晶ディスプレイ1に適用する例を示したが、これに限定されず、この発明は、印加電圧を加えない状態においてその透過率が高い、いわゆるノーマリー・ホワイト型のカラー液晶ディスプレイに適用しても良い。その場合、例えば、上記した第1及び第2の実施例において、データ信号出力部25<sub>R</sub>に供給される8ビットの赤データD<sub>R</sub>と赤階調電圧V<sub>R0</sub>～V<sub>R8</sub>及びV<sub>R9</sub>～V<sub>R17</sub>との関係は、図7に示すものではなく、図16に示すものとなる。また、上述の各実施例においては、この発明をTFTをスイッチ素子に用いたアクティブ・マトリックス駆動方式のカラー液晶ディスプレイ1に適用する例を示したが、これに限定されず、この発明は、どのような構成及び機能を有するカラー液晶ディスプレイにも適用することができる。

【0063】また、上述の各実施例において、第1のガンマ補正是、入力画像の輝度に対する再生画像の輝度の特性を任意に付与するために補正するガンマ補正を施すことを意味したが、この例としては、CRTディスプレイのガンマ特性(ガンマが約2.2)に適合したガンマ補正の他、CRTディスプレイのガンマ特性とは異なるガンマ特性に適合したガンマ補正を施すようにしても良い。例えば、テレビ放送やインターネットを介して各種商品を販売する場合、実際の商品の色柄とカラー液晶ディスプレイに表示された商品の色柄とが極力一致するよう第1のガンマ補正を施すことが考えられる。また、上述の各実施例においては、第1のガンマ補正をも施す例を示したが、これに限定されず、第2のガンマ補正だ

けを施すようにしても良い。また、上述の各実施例においては、デジタル映像データを処理する駆動回路の構成及び動作を示したが、これに限定されず、この発明は、アナログの映像信号を処理する駆動回路にも適用することができます。また、上述の第1の実施例の階調電源回路23においては、デコーダを階調電圧情報記憶部28の内部に設ける例を示したが、これに限定されず、デコーダを階調電圧情報記憶部28の外部に設けるように構成しても良い。また、この発明によるカラー液晶ディスプレイの駆動回路は、パーソナルコンピュータのモニタなどに用いられるカラー液晶ディスプレイを備えた表示装置にも適用することができる。

#### 【0064】

【発明の効果】以上説明したように、この発明の構成によれば、複数個の階調電圧の中から映像信号に基づいて選択した階調電圧を用いてカラー液晶ディスプレイを駆動するデータ電極駆動回路を有するカラー液晶ディスプレイの駆動回路において、データ電極駆動回路を、供給されるデジタルの階調電圧設定データに基づいて階調電圧特性に応じた複数個の階調電圧を生成するように構成したので、基板実装面積を削減することができるとともに、カラー液晶ディスプレイの解像度や階調電圧の個数が異なっている場合であっても、共通の基板やTCPを用いることができ、これにより、基板やTCP、ひいては表示装置を安価に構成することができる。また、この発明の別の構成によれば、デジタル映像データの表示と関わらない無効期間中に、赤データ、緑データ、青データのガンマ補正に関する情報を、カラー液晶ディスプレイとは別個に設けられた制御回路から、カラー液晶ディスプレイを駆動するデータ電極駆動回路へシリアル転送するようにしたので、制御回路とデータ電極駆動回路とを接続する配線数を減少させることができる。また、この発明の別の構成によれば、赤データ、緑データ、青データのガンマ補正に関する情報を、無効期間中に、赤データ、緑データ、青データをデータ電極駆動回路に供給する配線を利用して供給するようにしたので、さらに配線数を削減することができるとともに、配線を有効利用することができる。また、1回の動作で、赤階調電圧、緑階調電圧、青階調電圧が設定されるので、処理が簡単となるとともに、設定する時間を短縮することができる。

#### 【図面の簡単な説明】

【図1】この発明の第1の実施例であるカラー液晶ディスプレイの駆動回路の構成を示すブロック図である。

【図2】階調情報の各ビットA5～A0とチャネルChR0～ChR17、ChG0～ChG17、ChB0～ChB17との関係の一例を示す図である。

【図3】階調電圧情報の各ビットD7～D0と階調電圧V0～V255との関係の一例を示す図である。

【図4】同駆動回路を構成するデータ電極駆動回路22

50

の一部であるデータ電極駆動部22<sub>1</sub>の構成を示すブロック図である。

【図5】同データ電極駆動部22<sub>1</sub>を構成する階調電源回路23の構成を示すブロック図である。

【図6】同データ電極駆動部22<sub>1</sub>を構成するデータ信号出力回路25の一部であるデータ信号出力部25<sub>R</sub>の構成を示すブロック図である。

【図7】同データ信号出力部25<sub>R</sub>に供給される8ビットの赤データD<sub>R</sub>と赤階調電圧V<sub>GR0</sub>～V<sub>GR127</sub>及びV<sub>GR128</sub>～V<sub>GR255</sub>との関係の一例を示す図である。

【図8】同駆動回路の動作の一例を説明するためのタイミング・チャートである。

【図9】同駆動回路の動作の一例を説明するためのタイミング・チャートである。

【図10】この発明の第2の実施例であるカラー液晶ディスプレイの駆動回路の構成を示すブロック図である。

【図11】赤階調電圧情報D<sub>R0</sub>～D<sub>R17</sub>、緑階調電圧情報D<sub>G0</sub>～D<sub>G17</sub>、青階調電圧情報D<sub>B0</sub>～D<sub>B17</sub>の各ビットDR7～DR0、DG7～DG0、DB7～DB0と階調電圧V<sub>0</sub>～V<sub>255</sub>との関係の一例を示す図である。

【図12】同駆動回路を構成するデータ電極駆動回路42の一部であるデータ電極駆動部42<sub>1</sub>の構成を示すブロック図である。

【図13】同データ電極駆動部42<sub>1</sub>を構成する階調電源回路43の構成を示すブロック図である。

【図14】同駆動回路の動作の一例を説明するためのタイミング・チャートである。

【図15】同駆動回路の動作の一例を説明するためのタイミング・チャートである。

【図16】この発明の変形例であるカラー液晶ディスプレイの駆動回路を構成するデータ電極駆動回路22の一部であるデータ信号出力部25<sub>R</sub>に供給される8ビットの赤データD<sub>R</sub>と赤階調電圧V<sub>GR0</sub>～V<sub>GR127</sub>及びV<sub>GR128</sub>～V<sub>GR255</sub>との関係の一例を示す図である。

【図17】従来のカラー液晶ディスプレイの駆動回路の構成例を示すブロック図である。

【図18】同駆動回路を構成する階調電源回路3の構成例を示すブロック図である。

【図19】同駆動回路を構成するデータ電極駆動回路4の一部であるデータ電極駆動部4<sub>1</sub>の構成例を示すブロック図である。

【図20】同駆動回路の実装状態を説明するための図である。

【図21】同駆動回路の実装状態を説明するための図である。

#### 【符号の説明】

カラー液晶ディスプレイ

- 21, 41 制御回路

22, 42 データ電極駆動回路

$22_1 \sim 22_{10}, 42_1 \sim 42_{10}$  データ電極駆動部

部

23, 43 階調電源回路

25 データ信号出力回路

- \* 25<sub>R</sub>, 25<sub>G</sub>, 25<sub>B</sub> データ信号出力部

27 シフトレジスタ

28, 45<sub>R</sub>, 45<sub>G</sub>, 45<sub>B</sub> 階調電圧情報記憶部

\* 44 階調情報カウント部

【図1】

【図2】

| 階調情報 |    |    |    |    |    |   | チャネル   |

|------|----|----|----|----|----|---|--------|

| A5   | A4 | A3 | A2 | A1 | A0 |   |        |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R0  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R1  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R2  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R3  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R4  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R5  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R6  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R7  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R8  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R9  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R10 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R11 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R12 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R13 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R14 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R15 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch R16 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G0  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G1  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G2  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G3  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G4  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G5  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G6  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G7  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G8  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G9  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G10 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G11 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G12 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G13 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G14 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G15 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G16 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch G17 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B0  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B1  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B2  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B3  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B4  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B5  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B6  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B7  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B8  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B9  |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B10 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B11 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B12 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B13 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B14 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B15 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B16 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0 | Ch B17 |

【図3】

| 階調電圧情報 |     |     |     |     |     |     |     | 階調電圧             |

|--------|-----|-----|-----|-----|-----|-----|-----|------------------|

| D7     | D6  | D5  | D4  | D3  | D2  | D1  | D0  | V <sub>0</sub>   |

| 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | V <sub>0</sub>   |

| 0      | 0   | 0   | 0   | 0   | 0   | 0   | 1   | V <sub>1</sub>   |

| 0      | 0   | 0   | 0   | 0   | 0   | 1   | 0   | V <sub>2</sub>   |

| 0      | 0   | 0   | 0   | 0   | 0   | 1   | 1   | V <sub>3</sub>   |

| 0      | 0   | 0   | 0   | 0   | 1   | 0   | 0   | V <sub>4</sub>   |

| 0      | 0   | 0   | 0   | 0   | 1   | 0   | 1   | V <sub>5</sub>   |

| 0      | 0   | 0   | 0   | 0   | 1   | 1   | 0   | V <sub>6</sub>   |

| 0      | 0   | 0   | 0   | 0   | 1   | 1   | 1   | V <sub>7</sub>   |

| 0      | 0   | 0   | 0   | 1   | 0   | 0   | 0   | V <sub>8</sub>   |

| 0      | 0   | 0   | 0   | 1   | 0   | 0   | 1   | V <sub>9</sub>   |

| 0      | 0   | 0   | 0   | 1   | 0   | 1   | 0   | V <sub>10</sub>  |

| 0      | 0   | 0   | 0   | 1   | 0   | 1   | 1   | V <sub>11</sub>  |

| 0      | 0   | 0   | 0   | 1   | 1   | 0   | 0   | V <sub>12</sub>  |

| ...    | ... | ... | ... | ... | ... | ... | ... | ...              |

| 1      | 1   | 1   | 1   | 1   | 0   | 0   | 1   | V <sub>243</sub> |

| 1      | 1   | 1   | 1   | 1   | 0   | 1   | 0   | V <sub>244</sub> |

| 1      | 1   | 1   | 1   | 1   | 0   | 1   | 1   | V <sub>245</sub> |

| 1      | 1   | 1   | 1   | 1   | 1   | 0   | 0   | V <sub>246</sub> |

| 1      | 1   | 1   | 1   | 1   | 1   | 1   | 0   | V <sub>247</sub> |

| 1      | 1   | 1   | 1   | 1   | 1   | 0   | 0   | V <sub>248</sub> |

| 1      | 1   | 1   | 1   | 1   | 1   | 1   | 0   | V <sub>249</sub> |

| 1      | 1   | 1   | 1   | 1   | 1   | 1   | 1   | V <sub>250</sub> |

| 1      | 1   | 1   | 1   | 1   | 1   | 0   | 0   | V <sub>251</sub> |

| 1      | 1   | 1   | 1   | 1   | 1   | 0   | 1   | V <sub>252</sub> |

| 1      | 1   | 1   | 1   | 1   | 1   | 0   | 0   | V <sub>253</sub> |

| 1      | 1   | 1   | 1   | 1   | 1   | 1   | 0   | V <sub>254</sub> |

| 1      | 1   | 1   | 1   | 1   | 1   | 1   | 1   | V <sub>255</sub> |

【図15】

- (1) CS

(2) D<sub>R</sub>

(3) D<sub>G</sub>

(4) D<sub>B</sub>

(5) CLK

(6) LT

【図7】

【図4】

【図6】

【図5】

【図8】

【図9】

【図14】

【図10】

【図21】

【図11】

(1)

| 赤階調電圧情報 |     |     |     |     |     |     |     | 階調電圧      |

|---------|-----|-----|-----|-----|-----|-----|-----|-----------|

| DR7     | DR6 | DR5 | DR4 | DR3 | DR2 | DR1 | DR0 |           |

| 0       | 0   | 0   | 0   | 0   | 0   | 0   | 0   | $V_0$     |

| 0       | 0   | 0   | 0   | 0   | 0   | 0   | 1   | $V_1$     |

| 0       | 0   | 0   | 0   | 0   | 0   | 1   | 0   | $V_2$     |

| 0       | 0   | 0   | 0   | 0   | 0   | 1   | 1   | $V_3$     |

| 0       | 0   | 0   | 0   | 0   | 1   | 0   | 0   | $V_4$     |

| ...     | ... | ... | ... | ... | ... | ... | ... | ...       |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 0   | $V_{252}$ |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 0   | $V_{253}$ |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 0   | $V_{254}$ |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 1   | $V_{255}$ |

(2)

| 緑階調電圧情報 |     |     |     |     |     |     |     | 階調電圧      |

|---------|-----|-----|-----|-----|-----|-----|-----|-----------|

| DG7     | DG6 | DG5 | DG4 | DG3 | DG2 | DG1 | DG0 |           |

| 0       | 0   | 0   | 0   | 0   | 0   | 0   | 0   | $V_0$     |

| 0       | 0   | 0   | 0   | 0   | 0   | 0   | 1   | $V_1$     |

| 0       | 0   | 0   | 0   | 0   | 0   | 1   | 0   | $V_2$     |

| 0       | 0   | 0   | 0   | 0   | 0   | 1   | 1   | $V_3$     |

| 0       | 0   | 0   | 0   | 0   | 1   | 0   | 0   | $V_4$     |

| ...     | ... | ... | ... | ... | ... | ... | ... | ...       |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 0   | $V_{252}$ |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 0   | $V_{253}$ |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 0   | $V_{254}$ |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 1   | $V_{255}$ |

(3)

| 青階調電圧情報 |     |     |     |     |     |     |     | 階調電圧      |

|---------|-----|-----|-----|-----|-----|-----|-----|-----------|

| DB7     | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |           |

| 0       | 0   | 0   | 0   | 0   | 0   | 0   | 0   | $V_0$     |

| 0       | 0   | 0   | 0   | 0   | 0   | 0   | 1   | $V_1$     |

| 0       | 0   | 0   | 0   | 0   | 0   | 1   | 0   | $V_2$     |

| 0       | 0   | 0   | 0   | 0   | 0   | 1   | 1   | $V_3$     |

| 0       | 0   | 0   | 0   | 0   | 1   | 0   | 0   | $V_4$     |

| ...     | ... | ... | ... | ... | ... | ... | ... | ...       |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 0   | $V_{252}$ |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 0   | $V_{253}$ |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 0   | $V_{254}$ |

| 1       | 1   | 1   | 1   | 1   | 1   | 1   | 1   | $V_{255}$ |

【図12】

【図16】

【図13】

【図18】

【図20】

【図17】

【図19】

フロントページの続き

(51)Int.Cl.<sup>7</sup>

G 09 G 3/20識別記号

6 2 3

6 4 1

6 8 0F I

G 09 G 3/20テ-マコ-ド<sup>®</sup> (参考)

6 2 3 F

6 4 1 Q

6 8 0 G

F ターム(参考) 2H092 GA51 MA32 NA01 PA06 PA08

2H093 NA07 NA43 NA53 NA64 NC03

NC13 NC22 NC23 NC26 NC27

NC28 NC65 ND06 ND17 ND50

ND58 NE06

5C006 AA22 AF46 AF83 BB16 BC02

BC12 BF26 BF43 FA41 FA51

5C080 AA10 BB05 CC03 DD22 DD27

EE19 EE29 EE30 FF11 JJ02

JJ04 JJ05 JJ06

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 彩色液晶显示器的驱动电路，彩色液晶显示器的显示装置和驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号     | <a href="#">JP2002156948A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2002-05-31 |

| 申请号         | JP2000353427                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2000-11-20 |

| 申请(专利权)人(译) | NEC公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| [标]发明人      | 奥苑登                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人         | 奥苑 登                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号      | G02F1/1345 G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号      | G09G3/2011 G09G3/3611 G09G3/3688 G09G3/3696 G09G2320/0276                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| FI分类号       | G09G3/36 G02F1/133.510 G02F1/133.575 G02F1/1345 G09G3/20.621.M G09G3/20.623.F G09G3/20.641.Q G09G3/20.680.G                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号   | 2H092/GA51 2H092/MA32 2H092/NA01 2H092/PA06 2H092/PA08 2H093/NA07 2H093/NA43 2H093/NA53 2H093/NA64 2H093/NC03 2H093/NC13 2H093/NC22 2H093/NC23 2H093/NC26 2H093/NC27 2H093/NC28 2H093/NC65 2H093/ND06 2H093/ND17 2H093/ND50 2H093/ND58 2H093/NE06 5C006/AA22 5C006/AF46 5C006/AF83 5C006/BB16 5C006/BC02 5C006/BC12 5C006/BF26 5C006/BF43 5C006/FA41 5C006/FA51 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD22 5C080/DD27 5C080/EE19 5C080/EE29 5C080/EE30 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080/JJ05 5C080/JJ06 2H193/ZB43 2H193/ZD23 2H193/ZF03 2H193/ZH40 |         |            |

| 代理人(译)      | 西村 征生                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 其他公开文献      | <a href="#">JP3501751B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

解决的问题：即使彩色液晶显示器的分辨率和灰度电压的数量不同，也要减小电路板的安装面积并使用通用的基板或TCP，并可以廉价地配置基板，TCP和显示设备。用于公开的彩色液晶显示器的驱动电路是数据电极驱动电路，其中串行数据SDATA包括从控制电路提供的灰度信息A5至A0和灰度电压信息D7至D0。基于灰度电压特性，生成灰度电压V00至VR17，VG0至VG17以及VB0至VB17。