特開2001 - 100711

(P2001 - 100711A)

(43)公開日 平成13年4月13日(2001.4.13)

| (51) Int.Cl <sup>7</sup> | 識別記号 | 庁内整理番号 | F I           | 技術表示箇所 |

|--------------------------|------|--------|---------------|--------|

| G 0 9 G 3/36             |      |        | G 0 9 G 3/36  |        |

| G 0 2 F 1/133            | 575  |        | G 0 2 F 1/133 | 575    |

| G 0 9 G 3/20             | 611  |        | G 0 9 G 3/20  | 611 E  |

|                          | 612  |        |               | 612 F  |

|                          | 641  |        |               | 641 P  |

審査請求 未請求 請求項の数 50 L (全 14数) 最終頁に続く

(21)出願番号 特願2000 - 207015(P2000 - 207015)

(22)出願日 平成12年7月7日(2000.7.7)

(31)優先権主張番号 特願平11 - 210350

(32)優先日 平成11年7月26日(1999.7.26)

(33)優先権主張国 日本(JP)

(71)出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(72)発明者 西久保 圭志

大阪府大阪市阿倍野区長池町22番22号 シ

ヤープ株式会社内

(72)発明者 柳 俊洋

大阪府大阪市阿倍野区長池町22番22号 シ

ヤープ株式会社内

(74)代理人 100075557

弁理士 西教 圭一郎

(54)【発明の名称】ソースドライバ、ソースライン駆動回路およびそれを用いた液晶表示装置

## (57)【要約】

【課題】階調表示が滑らかで、かつフリッカなどの表示不具合のない、表示品位を格段に向上した液晶表示装置を提供する。

【解決手段】ソースラインを通して画素に階調電圧を印加するソースライン駆動回路8のソースドライバ2は、その内部に設けられている階調電圧作成用の抵抗分割比が階調表示特性に合わせ最適化されており、かつレベルシフト特性を考慮し正極性用と負極性用とで抵抗分割比が非対称に設定されている。

## 【特許請求の範囲】

【請求項1】 データ信号に従った階調電圧を、交流駆動が必要な画素に供給するソースドライバにおいて、

階調電圧作成のための抵抗分圧回路が設けられ、該抵抗分圧回路の抵抗分割比がレベルシフト特性に応じて正極性用と負極性用とで非対称に設定されていることを特徴とするソースドライバ。

【請求項2】 データ信号に従った階調電圧を、交流駆動が必要な画素に供給するソースドライバにおいて、内部に設けられた階調電圧作成のための抵抗分圧回路の抵抗分割比が階調表示特性に応じて最適化されていることを特徴とするソースドライバ。

【請求項3】 データ信号に従った階調電圧を、交流駆動が必要な画素に供給するソースライン駆動回路において、

請求項1または2記載のソースドライバと階調基準電圧発生回路とを備え、前記ソースドライバには複数の入力端子が設けられ、前記複数の入力端子には、各々電圧レベルの異なる階調基準電圧が供給されているとともに、前記複数の階調基準電圧に基づいて、正極性用の階調電圧と負極性用の階調電圧とを作成することを特徴とするソースライン駆動回路。

【請求項4】 データ信号に従った階調電圧を、交流駆動が必要な画素に供給するソースライン駆動回路において、

請求項1または2記載のソースドライバを備え、前記ソースドライバには入力端子が2つ設けられ、一方の入力端子には正極性用の最上位階調基準電圧が、他方の入力端子には負極性用の最下位階調基準電圧が供給されるとともに、前記最上位階調基準電圧および最下位階調基準電圧に基づいて、正極性用の階調電圧と負極性用の階調電圧とを作成することを特徴とするソースライン駆動回路。

【請求項5】 マトリクス状に配置された複数の画素と、画素の各列に対応して配置された複数のデータ信号線と、画素の各行に対応して配置された複数の走査信号線とを備えるとともに、各画素にスイッチング素子を有するアクティブマトリクス型液晶表示装置において、データ信号線を駆動するために、請求項3または4記載のソースライン駆動回路を備えたことを特徴とするアクティブマトリクス型液晶表示装置。

## 【発明の詳細な説明】

## 【0001】

【発明の属する技術分野】 本発明は、階調表示を行う表示装置において、データ信号に応じてソースラインに供給する階調電圧を作成するためのソースドライバ、それを用いたソースライン駆動回路、およびそれらを用いたマトリクス型表示装置に關し、特に液晶表示装置のように、表示画面を構成する画素に直流電圧が印加されると劣化あるいは破壊される恐れがあることから交流駆動を

必要とする表示装置に用いられるソースドライバ、それを用いたソースライン駆動回路、およびそれらを用いた表示装置に関する。

## 【0002】

【従来の技術】 近年、大画面にて高精細な表示が可能なアクティブマトリクス型液晶表示装置の開発が盛んである。上記アクティブマトリクス型液晶表示装置では、液晶を挟持する一対の基板の一方に、薄膜技術にて形成された薄膜トランジスタ (TFT : Thin Film Transistor) アレイを備えた構成が、広く採用されている。

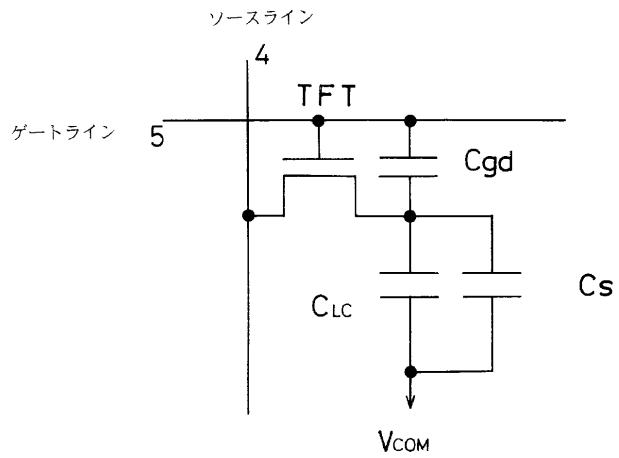

【0003】 図9は、従来のアクティブマトリクス型液晶表示装置における各画素の等価回路の一例を示す回路図である。各画素は、図9に示すように、互いに直交するように配置されたソースライン4およびゲートライン5の交点の各々に対応して設けられている。各画素にはたとえばアモルファスシリコンなどを用いて構成されるTFTが設けられ、TFTのゲート電極にゲートライン5が接続され、ソース電極にソースライン4が接続されている。TFTのドレイン電極には、液晶セル容量 $C_{LC}$ と、補助容量 $C_s$ と、寄生容量 $C_{gd}$ とが、負荷として接続されている。なお、上記の寄生容量 $C_{gd}$ は、ゲートライン5と表示電極を兼ねたドレイン電極とが容量結合していることによって生じる。液晶セル容量 $C_{LC}$ および補助容量 $C_s$ において、TFTのドレイン電極に接続されていない方の端子は、対向基板の共通電極(図示せず)に接続され、共通電極電圧 $V_{COM}$ が与えられる。上記した構成により、画素は液晶セル容量 $C_{LC}$ および補助容量 $C_s$ において、データ信号に応じた所定の電圧を一走査期間を通じて書込むことにより、所定の階調表示を実現する。

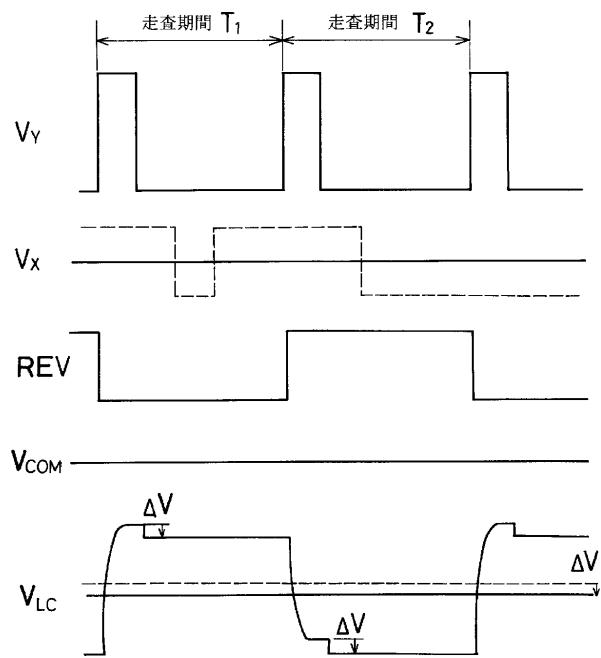

【0004】 液晶は電気化学的特性により、一定方向の電界を長時間印加し続けると劣化する。したがって、液晶に印加される電界の方向が一定周期毎に逆方向になるように駆動しなければならない。ドット反転方式ではソースドライバが outputする階調電圧 $V_x$ が、極性反転信号REVを基準として共通電極電圧 $V_{COM}$ を中心に反転し液晶セルを交流駆動する。

【0005】 階調電圧 $V_x$ が印加されたときに液晶セル容量 $C_{LC}$ に生じる液晶セル電圧 $V_{LC}$ は、寄生容量 $C_{gd}$ の影響を無視すれば、ソースライン4からTFTのソース電極およびドレイン電極を介して供給される階調電圧 $V_x$ と、共通電極電圧 $V_{COM}$ との差電圧であるが、実際の動作上は、上記寄生容量 $C_{gd}$ を無視することはできない。

【0006】 ここで、上記の寄生容量 $C_{gd}$ が画素の駆動に及ぼす影響について、図10を参照しながら説明する。図10は、ゲートライン5に供給される走査電圧 $V_y$ の波形、ソースドライバが outputする階調電圧 $V_x$ の波形、極性反転信号REVの波形、共通電極電圧 $V_{COM}$ の波形、およびこれらの電圧によって液晶セル容量 $C_{LC}$ に生じる液晶セル電圧 $V_{LC}$ の波形を表している。図10に

示すように、ゲートライン5を介して TFT のゲート電極に選択パルスが印加されると、TFTはオン状態となり、ソースライン4に印加されている階調電圧  $V_x$  がソース電極からドレイン電極を経て、TFTの負荷である液晶セル容量  $C_{LC}$  および補助容量  $C_s$  へ送られる。これにより、液晶セル電圧  $V_{LC}$  は、上記選択パルスに同期して立ち上がる。選択パルスが立下がった時点の電圧（以下、最終書き込み電圧と称する）は、液晶セル容量  $C_{LC}$  および補助容量  $C_s$  によって保持されるが、実際には最終書き込み電圧と TFT がオフした後の保持電圧との間に、寄生容量  $C_{gd}$  への電荷の再分配の影響によって、レベルシフト  $V$  が生じる。

【0007】前記のレベルシフト  $V$  は、図10に示す走査期間  $T_1$  のように液晶セル電圧  $V_{LC}$  が正極性の場合には、保持電圧を最終書き込み電圧より低下させるよう作用するが、走査期間  $T_2$  のように液晶セル電圧  $V_{LC}$  が負極性

$$V = (C_{gd} / (C_{gd} + C_{LC} + C_s)) \cdot V_G$$

【0010】ここで、液晶セル容量  $C_{LC}$  は、セルギャップを  $d$ 、表示電極の面積を  $A$ 、液晶材料の比誘電率を

$$C_{LC} = (C_{LC} \cdot A / d) \cdot A$$

【0011】なお、液晶材料の比誘電率  $\epsilon_{LC}$  は、液晶分子の配列状態すなわち液晶セル電圧  $V_{LC}$  に応じて変化するので、液晶セル容量  $C_{LC}$  は、下記の式3のように、液

$$C_{LC} = K_1 \cdot f_1 (V_{LC})$$

【0012】ゆえに、3レベルシフト  $V$  についても液晶セル電圧  $V_{LC}$  の関数  $f_2$  となり、下記の式4で与えられる

$$V = K_2 \cdot f_2 (V_{LC})$$

【0014】また、液晶の光透過率は、液晶セル電圧  $V_{LC}$  の大きさに対して非線形に変化する。つまり、階調表示を実現するときに、液晶セル電圧  $V_{LC}$  の実効値は各階調ごとに異なっているので、各階調におけるレベルシフト  $V$  の大きさも一定でないことが分かる。したがって、各階調ごとに、レベルシフト  $V$  の補正を行う必要がある。

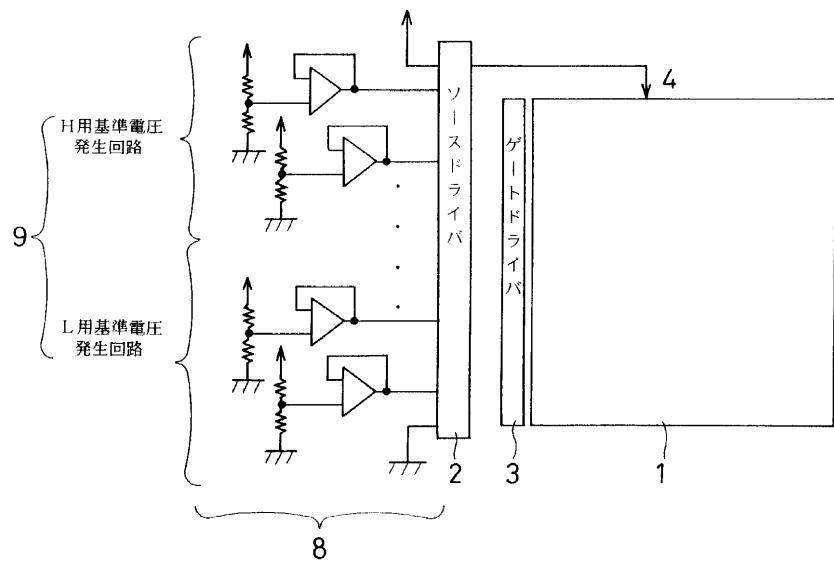

【0015】まず、従来のアクティブマトリクス型液晶表示装置の概略構成について説明する。図11に示すように、従来のアクティブマトリクス型液晶表示装置は、複数の画素がマトリックス状に配置された画素アレイ1と、互いに直交するように配置された複数のソースライン（図示せず）および複数のゲートライン（図示せず）からなる液晶パネルと、ソースラインを駆動するソースライン駆動回路8と、ゲートラインを駆動するゲートドライバ3とを備えている。

【0016】ソースライン駆動回路8には、ソースドライバ2とソースドライバ4に基準電圧を供給するための複数の基準電圧発生回路9（正極性と負極性用）とが設けられている。ソースドライバ2の出力電圧発生部は階調電圧作成回路、階調選択回路、出力バッファ（図示せず）からなり、正極性用（H用）基準電圧発生回路および負極性用（L用）基準電圧発生回路で作成した正極性

\*性の場合には、保持電圧を最終書き込み電圧より上昇させるように作用する。

【0008】この結果、走査期間  $T_1$  および走査期間  $T_2$  で液晶セル電圧  $V_{LC}$  の実効値が異なることとなり、液晶にDC電圧が印加されることとなり液晶が劣化する。また、正極性と負極性とで液晶に印加される電圧値が異なると、その電圧値に応じた輝度も異なることになり画像のちらつき（フリッカ）が発生してしまう。この問題を解決するために、従来、共通電極電圧  $V_{COM}$  を上記レベルシフト  $V$  と同じだけシフトさせることにより、正極性のときの液晶セル電圧  $V_{LC}$  の実効値と負極性のときの液晶セル電圧  $V_{LC}$  の実効値とを等しくすることが提案されている。

【0009】なお、レベルシフト  $V$  は、上述のように寄生容量  $C_{gd}$  が存在するために生じ、走査電圧  $V_Y$  の振幅を  $V_G$  とすると、下記の式1で与えられる。

... (

液晶セル電圧  $V_{LC}$  の関数  $f_1$  として与えられる。なお、  $K_1$  は定数である。

... (

る。

【0013】なお、  $K_2$  は定数である。

... ( 4

用基準電圧および負極性用基準電圧はソースドライバ2の階調電圧入力端子を通して出力階調電圧作成回路に供給される。

【0017】階調電圧作成回路は複数の抵抗を直列に接続した抵抗分圧回路が設けられ、正極性用基準電圧および負極性用基準電圧間を該抵抗分圧回路で当分割に分圧することにより、多数の出力階調電圧を作成している。作成された複数の階調電圧は出力階調データに応じて選択回路により選択され、出力バッファを介して液晶パネルのソースライン4に出力される。

【0018】このとき前述したようにレベルシフト  $V$  が存在するため、補正（以下  $V$  特性の補正という）をする必要がある。液晶への印加電圧に対するレベルシフト  $V$  の特性を理想的に補正するためには各階調電圧ごとに適正な階調電圧を与えればよいが全階調をソースドライバ2に入力するのは、回路規模が大きくなり実用的ではない。そのため、通常は正・負各5点程度の基準電圧をソースドライバ2の基準電圧入力端子に供給し、その間をソースドライバ2内部の階調電圧発生回路の直列抵抗で等分割することにより、  $V$  のずれを減らしている。

【0019】

【発明が解決しようとする課題】従来のソースドライバ

は内部の階調電圧発生回路につながる基準電圧入力端子を複数個備え、該入力端子間の抵抗値を等分割することでさらに多くの階調電圧を作成していた。また、内部の階調電圧発生用直列抵抗が正極性用と負極性用で対称に設定されていた。そのため、最上位および最下位の基準電圧入力端子にだけ最上位電圧と最下位電圧を供給した場合は、各々の階調における正極性の階調電圧と負極性の階調電圧とが上下対称になるように作成される。しかしながら、前述したように液晶駆動時には各階調ごとに異なるレベルシフト  $V$  が存在し、その  $V$  特性を補正しなければならない。そのため、通常は前記のようにソースドライバの正・負各 5 点程度の基準電圧入力端子に  $V$  を考慮した非対称な電圧値を供給し、その間をソースドライバ内部の階調電圧発生回路の直列抵抗で等分割することにより、 $V$  のずれを減らしている。

【0020】ソースドライバに外部から複数個の基準電圧を供給するには、大きく 2 つの理由がある。第 1 は滑らかな階調表示を実現するためであり、第 2 はレベルシフト  $V$  特性の補正を最適に近づけるためである。

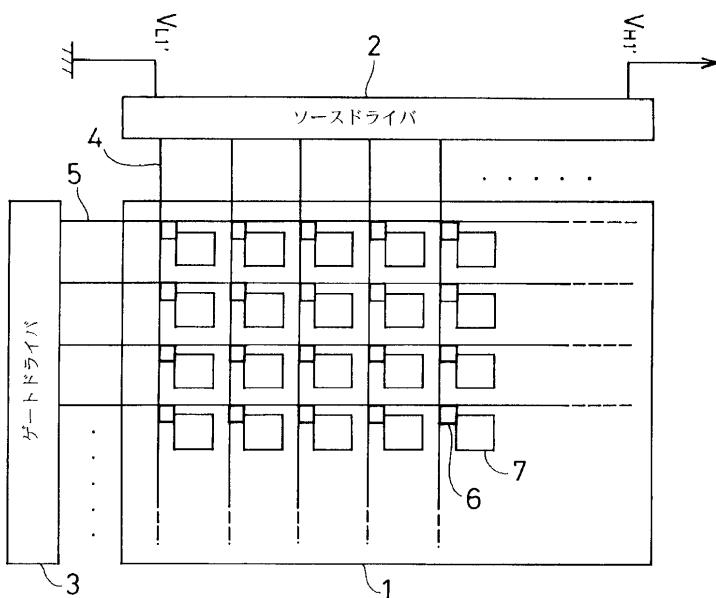

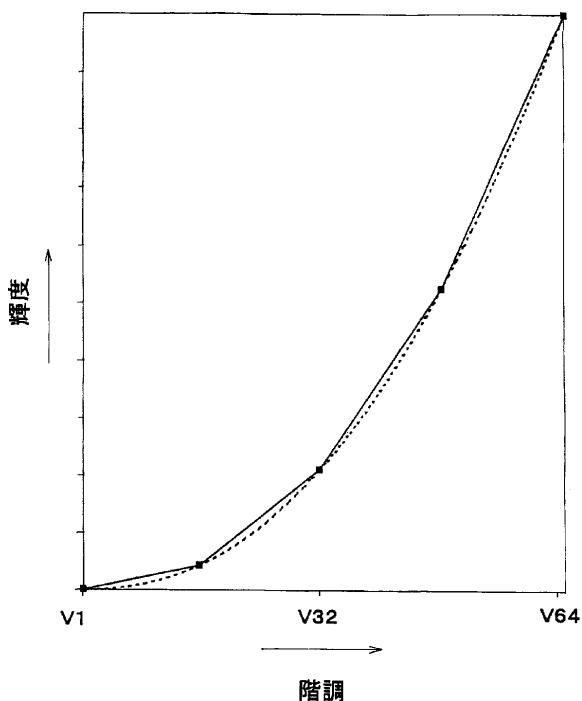

【0021】第 1 の理由について以下に述べる。ソースドライバ内部の階調電圧作成回路は等分割された直列抵抗からなり、通常は画像特性に合うように外部から電圧を供給するが、等分割されているがゆえに階調 - 輝度特性をとると、入力点が少ない場合には基準入力間の輝度変化が直線的な特性となり図 12 の実線で示すように輝度変化がスムーズに変化しない。図 12 の実線は、従来のソースドライバの階調 - 輝度特性で、各プロット点は、階調電圧が入力される点である。図 12 では、外部から 5 点の階調電圧が入力された場合を示す。また図 12 の点線は 64 階調の場合に全階調をスムーズに表示することを想定した場合の理想的な階調 - 輝度特性である。しかしながら、階調電圧の入力点が 5 点程度と入力点が少ない従来の場合では、図 12 に示す実線のように輝度が直線的に変化し理想的な階調 - 輝度特性は得られない。このような複数の基準点を設けて階調 - 輝度特性を改善する技術は、たとえば特開昭 61-4374 号公報に記載されている。

【0022】次に第 2 の理由について以下に述べる。図 13 は、ソースドライバ内部の抵抗値が基準電圧間で等分割されている従来のドライバの出力電圧のセンター値（正極性および負極性電圧の平均値）とレベルシフト  $V$  特性とを示している。横軸は階調を表し、縦軸は電圧を表す。図 13 の曲線 32 は各階調電圧におけるレベルシフト  $V$  特性を示す。破線 31 は、基準電圧間を等分割したときの各階調電圧におけるソースドライバ発生電圧のセンター値を示す。破線 31 と曲線 32 とが一致すると、液晶には DC 電圧は印加されず、適正に交流駆動されることになる。しかしながら、前述のように基準電圧が離散的に入力される場合には、レベルシフト  $V$  を考慮した最適な基準電圧が入力される階調以外の階調で

は、破線 31 に示すように等分割の抵抗から作成された電圧が出力される。このため、 $V$  特性の補正が充分になされず、適正な  $V$  特性からずれ  $V_a$  が生じる。このずれ量が大きいと、最適に交流駆動がされず液晶に DC 電圧がかかってしまい、液晶劣化の原因になってしまうだけでなくフリッカーまたは焼つけなどの不具合が生じる。

【0023】上記 2 つの不具合は表示装置としての性能を大きく損なう問題であり、表示品位を向上するためには多数の基準電圧入力点が必要になる。しかしながら、回路規模などの点で基準電圧を入力するポイントには限度があり、通常は多くとも正負各 5 点ずつくらいである。それでもソースドライバ内で基準電圧間の抵抗値を等分割しているため前記のとおり厳密に  $V$  特性を補正することができず、DC 電圧が液晶に印加される。また、基準電圧の入力点の前後で輝度の変化率が急激に変化するため階調のランプ表示（白から黒まで直線的に変化していく画像の表示）を行った場合などに不自然な輝度変化をするのがはっきりと確認される。

【0024】また  $V$  特性の補正をするために従来技術では、共通電極駆動回路に共通電極電位可変用の可変抵抗器を設け、各階調でのフリッカ評価パターンを目視または画像認識して、任意の何点かの階調でフリッカが少なくなるように可変抵抗器の抵抗値を調整することで共通電極電圧  $V_{COM}$  を適正に近付けていた。

【0025】しかしながら、ソースドライバ内部の抵抗分圧回路で外部基準電圧間を等分割して階調電圧を作成する従来技術では、図 13 に示すようにレベルシフト  $V$  の補正が全階調電圧で完全に合わないため、ある階調でフリッカが見えなくなるように共通電極電位  $V_{COM}$  を調整しても、その他の階調では正極性の液晶セル電圧  $V_{LC}$  と負極性の液晶セル電圧  $V_{LC}$  とが異なる値をとることになり、それらの階調電圧においてはフリッカが発生し、表示品位向上の妨げになっていた。また、共通電極電位  $V_{COM}$  の調整作業が非常に困難であり、時間もかかっていた。

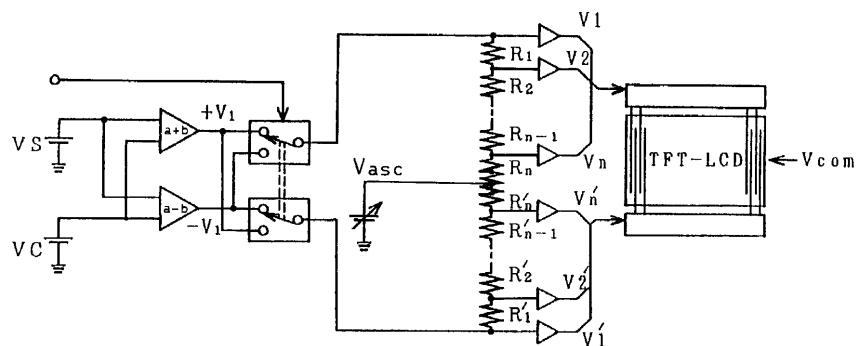

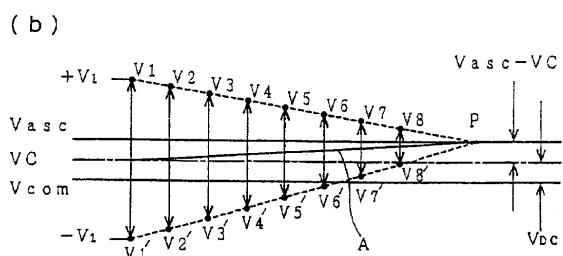

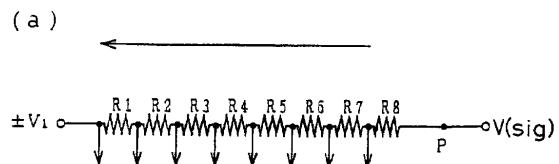

【0026】また、特開平 7-92937 号公報には、図 14 に示すようにソースドライバの外部にソースドライバに階調電圧を供給する階調電圧発生回路が設けられ、階調電圧発生回路内に形成された複数の階調電圧を形成する抵抗分圧回路の両端に、最大振幅電圧  $V_s$  と基準電圧  $V_c$  との加算電圧  $+V_1$  と減算電圧  $-V_1$  とが交流化信号により交互に供給されるとともに、図 15 の（a）および図 15 の（b）に示すように、抵抗分圧回路の中点に供給する中点電圧  $V_{as}$  を基準電圧  $V_c$  からずらすことにより、非対称にされた両極性の階調電圧を出力させ、共通電極の電圧に対して各階調電圧のセンター値をそれぞれに最適に設定し、多階調化を図りつつ残像現象を防止できる液晶表示装置の駆動方法が開示されている。

【0027】しかしながら、前記公報に開示されている駆動方法でN階調表示する場合、全ての階調電圧のセンター値を最適に設定するには、階調電圧発生回路中の抵抗分圧回路を正極性、負極性それぞれN個ずつ抵抗分割する必要があり、回路規模が増大し製造コストおよび消費電力を上昇させることとなり実用的でない。より詳細には、たとえば最上位基準電圧と最下位基準電圧との差が10Vで64階調表示を行うとき、正確な階調表示には最も高精度であるべき中間階調表示領域で5mV程度の電圧精度が要求される。これを実現するには、0.010%の抵抗値精度が要求され、ソースドライバ外部のディスクリート抵抗器として通常使用される抵抗値精度(1%)よりはるかに高性能な抵抗器が必要である。つまり、これをディスクリート抵抗器で実現することは実用的ではない。また、このような電圧精度が必要な回路を、ソースドライバ外部のディスクリート部品を使用して分圧すると、たとえばバックライトなどの外来ノイズにより分圧電圧値が安定しないなどの問題があり、電圧値精度が悪く正確な階調表示ができない。

【0028】本発明の目的は、階調表示が滑らかで、かつフリッカ、焼付けなどの表示不具合のない、表示品位を格段に向上した液晶表示装置を提供することである。

#### 【0029】

【課題を解決するための手段】本発明は、データ信号に従った階調電圧を交流駆動が必要な画素に供給するソースドライバにおいて、階調電圧作成のための抵抗分圧回路が設けられ、該抵抗分圧回路の抵抗分割比がレベルシフト特性に応じて正極性用と負極性用とで非対称に設定されていることを特徴とするソースドライバである。

【0030】本発明に従えば、ソースドライバに設けられている階調電圧作成用の抵抗分圧回路の複数の抵抗分割比が、液晶の誘電率異方性に起因するレベルシフトVの非線形な特性を考慮して正極性用と負極性用とで非対称となるように設定されているので、レベルシフトV特性の補正を各階調において行うことができ、各階調毎に正極性の液晶セル電圧 $V_{Lc}$ と負極性の液晶セル電圧 $V_{Lc}$ とを等しくすることができる。すなわち、液晶分子によけいなDC電圧がかかることがなくなるため、焼きが発生せず、フリッカなどの表示不具合を解消することができ、表示品位を格段に向上することが可能となる。また、全ての階調電圧がレベルシフトVを考慮して完全な補正がされているため、各階調のフリッカ評価パターンにて目視により共通電極電圧 $V_{COM}$ を調整する作業において、ある任意の1点の階調でフリッカが見えなくなるように共通電極電圧 $V_{COM}$ を調整するだけで、全階調でフリッカなどの表示不具合を完全に解消することができ、共通電極電圧 $V_{COM}$ の調整作業が非常に楽になり、作業時間を短縮することが可能となる。

【0031】また本発明は、データ信号に従った階調電圧を、交流駆動が必要な画素に供給するソースドライバ

において、内部に設けられた階調電圧作成のための抵抗分圧回路の抵抗分割比が階調表示特性に応じて最適化されていることを特徴とするソースドライバである。

【0032】本発明に従えば、ソースドライバ内に設けられる階調電圧作成用の抵抗分圧回路の複数の抵抗分割比をIC(Integrated Circuit:集積回路)化することにより高精度で目標とする特性(階調表示特性)に合わせ込むことが可能である。よって、本発明によるソースドライバは、理想的な特性を有する滑らかな階調表示を実現する液晶印加電圧を出力することができる。

【0033】また本発明は、データ信号に従った階調電圧を交流駆動が必要な画素に供給するソースライン駆動回路において、前記ソースドライバと階調基準電圧発生回路とを備え、ソースドライバには複数の入力端子が設けられ、前記複数の入力端子には、各々電圧レベルの異なる階調基準電圧が供給されているとともに、前記複数の階調基準電圧に基づいて、正極性用の階調電圧と負極性用の階調電圧とを作成することを特徴とするソースライン駆動回路である。

【0034】本発明のソースライン駆動回路は、階調電圧作成用の抵抗分圧回路の抵抗分割比が前述のように設定されているので、従来のように多数のレベルの階調基準電圧をソースドライバに供給しなくとも画素を最適に駆動することができる。したがって、ソースライン駆動回路のソースドライバ外部に設ける階調基準電圧発生回路を削減することができるので、全体としてソースライン駆動回路規模を縮小することができ、部品コストを低減できるとともに、低消費電力化を実現することが可能となる。

【0035】また本発明は、データ信号に従った階調電圧を、交流駆動が必要な画素に供給するソースライン駆動回路において、前述のソースドライバを備え、前記ソースドライバには入力端子が2つ設けられ、一方の入力端子には正極性用の最上位階調基準電圧が、他方の入力端子には負極性用の最下位階調基準電圧が供給されているとともに、前記最上位階調基準電圧および最下位階調基準電圧に基づいて、正極性用の階調電圧と負極性用の階調電圧とを作成することを特徴とするソースライン駆動回路である。

【0036】本発明に従えば、ソースライン駆動回路は、正極性の最上位階調基準電圧と負極性用の最下位階調基準電圧とをソースドライバに供給し、正極性用および負極性用の全ての階調電圧をソースドライバ内の抵抗分圧回路で高精度かつ適正に作成することが可能となるため、ソースドライバ外部に階調基準電圧発生回路を設ける必要がなく、ソースライン駆動回路規模を縮小することができ、部品コストを削減できるとともに、低消費電力化を実現することが可能となる。

【0037】また本発明は、マトリクス状に配置された複数の画素と、画素の各列に対応して配置された複数の

データ信号線と、画素の各行に対応して配置された複数の走査信号線とを備えるとともに、各画素にスイッチング素子を有するアクティブマトリクス型液晶表示装置において、データ信号線を駆動するために、前記ソースライン駆動回路を備えたことを特徴とするアクティブマトリクス型液晶表示装置である。

【0038】本発明によるアクティブマトリクス型液晶表示装置は、ソースドライバに設けられている階調電圧作成用の抵抗分圧回路の抵抗分割比が正極性用と負極性用とで非対称となるように設定されているため、各階調電圧によって異なるレベルシフト  $V$  を、ソースドライバ内の抵抗分圧回路の抵抗分割比に反映させて補正することができる。そのため、フリッカなどの表示不具合を解消することができ、表示品位を格段に向上したアクティブマトリクス型液晶表示装置を得ることが可能となる。

【0039】また、従来のように多数の外部階調基準電圧をソースドライバに供給することなく、目標の特性に合わせ込んだ理想的で高精度な階調電圧を作成することができる。したがって、ソースドライバ外部に設ける階調基準電圧発生回路を縮小することができ、全体としてソースライン駆動回路規模を縮小することができ、部品コストを削減できるとともに、低消費電力化を実現することができる。

#### 【0040】

【発明の実施の形態】以下に、本発明の実施の形態を説明する。

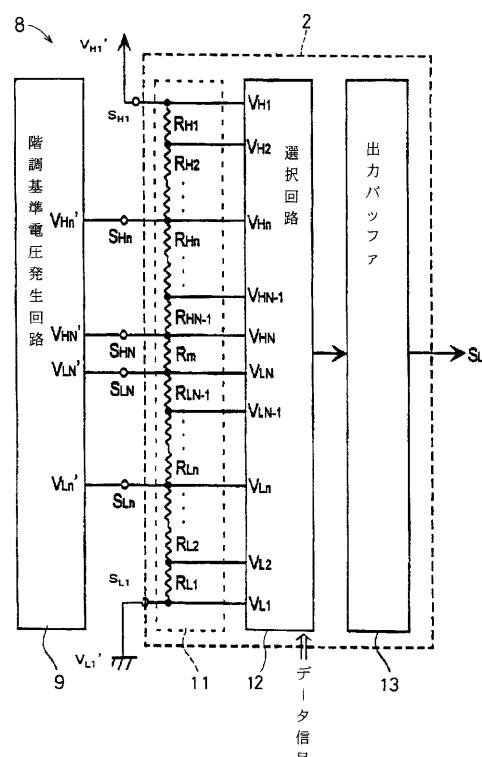

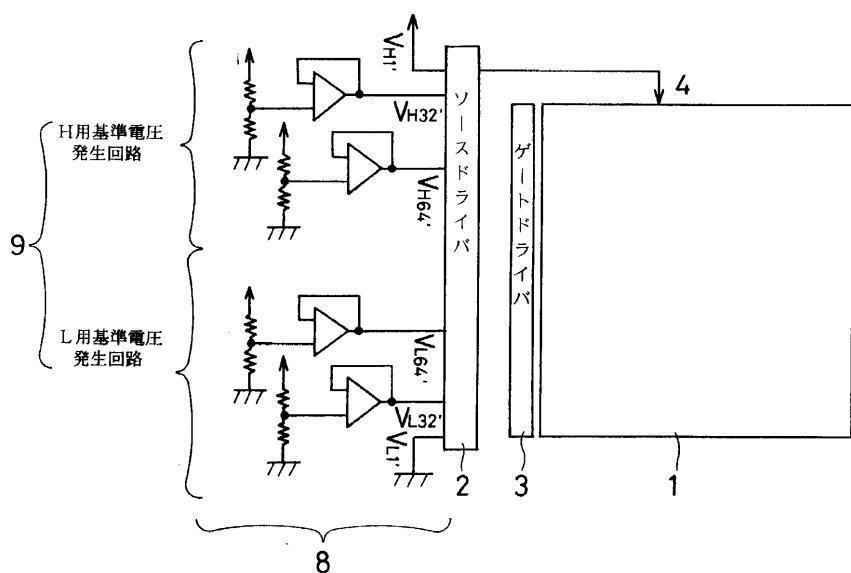

【0041】まず、本発明のアクティブマトリクス型液晶表示装置の概略構成について説明する。本アクティブマトリクス型液晶表示装置は、図1に示すように、互いに直交するように配置された複数のソースライン4(データ線)および複数のゲートライン5と、画素アレイ1と、ソースライン4を駆動するソースドライバ2と、ゲートライン5を駆動するゲートドライバ3とを備えている。図1では、ソースドライバ2として階調電圧を発生させる回路が中心に示されており、データ信号を入力する回路およびタイミング制御回路などは省略されている。

【0042】画素アレイ1は、隣接する2本のソースライン4と隣接する2本のゲートライン5とで囲まれた領域に1つずつ設けられた画素7によって形成されている。すなわち、画素7は全体としてマトリクス状に配列されて、画素アレイ1を形成している。

【0043】TFT6のドレイン電極には、液晶セル容量  $C_{LC}$  と、補助容量  $C_s$  と、寄生容量  $C_{gd}$  とが、負荷として接続されている。なお、上記の寄生容量  $C_{gd}$  は、ゲートライン5と表示電極を兼ねたドレイン電極とが容量結合していることによって生じる。液晶セル容量  $C_{LC}$  および補助容量  $C_s$  において、TFT6のドレイン電極に接続されていない方の端子は、対向基板の共通電極(図50

示せず)に接続され、共通電極電圧  $V_{COM}$  が与えられる。

【0044】上記した構成により、画素7は、液晶セル容量  $C_{LC}$  および補助容量  $C_s$  において、映像信号に応じた所定の電圧を一走査期間を通じて保持することにより、所定の階調表示を実現する。階調電圧  $V_x$  が印加されたときに液晶セル容量  $C_{LC}$  に生じる液晶セル電圧  $V_{LC}$  は、寄生容量  $C_{gd}$  の影響を無視すれば、ソースライン4からソースおよびドレインを介して供給される階調電圧  $V_x$  と、共通電極電圧  $V_{COM}$  との差電圧である。

【0045】(実施の形態1)図2に、64階調表示させる場合のアクティブマトリクス型液晶表示装置を示す。実施の形態1においては、図2に示すように、ソースライン駆動回路8は、ソースドライバ2を有し、ソースドライバ2の外部に階調基準電圧発生回路9が設けられている。

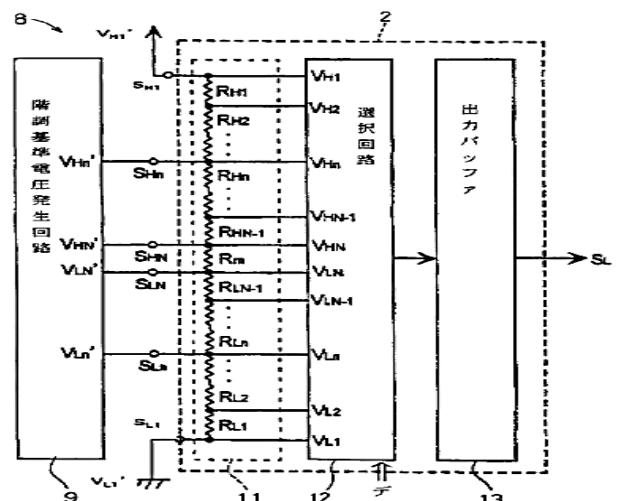

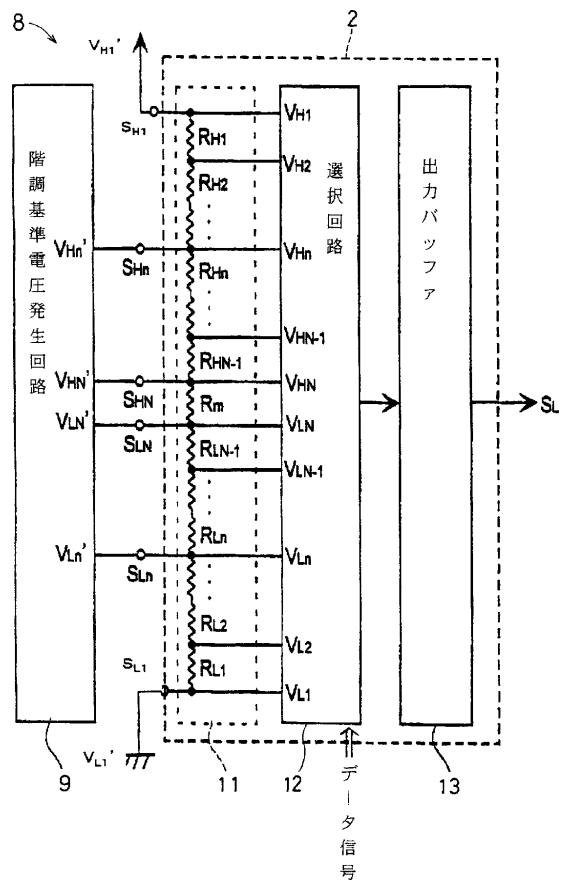

【0046】ソースドライバ2は、図3に示すように、複数の階調基準電圧入力端子  $S_{H1}, S_{Hn}, S_{HN}, S_{LN}, S_{L1}, S_{L2}$  を持ち、内部にIC(集積回路)化された階調電圧作成回路11、選択回路12、出力バッファ13を備えている。外部電源(図示せず)および階調基準電圧発生回路9により形成された階調基準電圧は、該ソースドライバの入力端子に供給され、階調電圧作成回路11で階調基準電圧が抵抗分割され、さらに複数の階調電圧が作成されて、選択回路12において、データ信号に応じたいずれかの階調電圧が選択され、出力バッファ13を介してソースライン4へ出力される。

【0047】ソースドライバ2の階調電圧作成回路11は、複数の抵抗が直列接続された抵抗分圧回路からなる。たとえば、N階調表示させる場合には、 $2N - 1$  個の抵抗が一方の入力端  $S_{H1}$  から他方の入力端  $S_{L1}$  の間に、 $R_{H1}, R_{H2}, \dots, R_{Hn}, \dots, R_{HN-1}, R_m, R_{LN-1}, \dots, R_{Ln}, \dots, R_{L1}$  の順に直列に設けられている。

【0048】入力端子  $S_{H1}$  には、外部電源により形成した正極性用最上位階調基準電圧  $V_{H1}'$  が供給され、入力端子  $S_{L1}$  には、外部電源により形成した負極性用最下位階調基準電圧  $V_{L1}'$  が供給される。入力端子  $S_{Hn}$  には階調基準電圧発生回路9により形成した正極性基準電圧  $V_{Hn}'$  が供給され、入力端子  $S_{HN}$  には階調基準電圧発生回路9により形成した正極性用基準電圧  $V_{HN}'$  が供給される。入力端子  $S_{Ln}$  には階調基準電圧発生回路9により形成した負極性用基準電圧  $V_{Ln}'$  が入力端子  $S_{LN}$  には階調基準電圧発生回路9により形成した負極性用基準電圧  $V_{LN}'$  が供給される。

【0049】入力端子  $S_{H1}$  に供給される正極性用最上位階調基準電圧  $V_{H1}'$  は正極性の第1の階調電圧  $V_{H1}$  として選択回路12に供給される。入力端子  $S_{L1}$  に供給される負極性用最下位階調基準電圧  $V_{L1}'$  は、負極性の第1の階調電圧  $V_{L1}$  として選択回路12に供給される。抵抗

$R_{H_1}$  と抵抗  $R_{H_2}$  の交点には、抵抗分圧回路の抵抗分割比によって、正極性の第 2 の階調電圧  $V_{H_2}$  が発生する。同様に、抵抗  $R_{H_{n-1}}$  と抵抗  $R_{H_n}$  の交点に正極性の  $n$  番目の階調電圧  $V_{H_n}$  が、抵抗  $R_{H_{N-1}}$  と抵抗  $R_m$  の交点に正極性の  $N$  番目の階調電圧  $V_{H_N}$  が発生する。同様に、抵抗  $R_{L_1}$  と抵抗  $R_{L_2}$  の交点に負極性の第 2 階調電圧  $V_{L_2}$  が、抵抗  $R_{L_{n-1}}$  と抵抗  $R_{L_n}$  の交点に負極性の  $n$  番目の階調電圧  $V_{L_n}$  が、抵抗  $R_{L_{N-1}}$  と抵抗  $R_m$  の交点に負極性の  $N$  番目の階調電圧  $V_{L_N}$  が発生する。

【0050】このとき、すべての階調においてレベルシフト  $V$  特性の補正が完全になされた階調電圧を作成するためには階調電圧作成回路 11 の抵抗分割比を適切に設定しなければならない。

【0051】全ての階調において正極性の液晶セル電圧  $V_{L_C}$  と負極性の液晶セル電圧  $V_{L_C}$  とを等しくするには、ソース出力電圧のセンター値  $(V_{H_n} + V_{L_n}) / 2$  が、各階調での  $V$  特性を考慮した共通電極電圧  $V_{COM}$  に等しくならなければならない。すなわち、レベルシフト  $V$  特性が各階調電圧によって一定でないことからソースドライバの出力電圧を各階調ごとに上下非対称になるよう 10 に設定しなくてはならない。ここで、上下非対称にするとは、正極性の  $n$  番目の階調電圧  $V_{H_n}$  と共通電極電圧  $V_{COM}$  との電位差と負極性の  $n$  番目の階調電圧  $V_{L_n}$  と共通電極電圧  $V_{COM}$  との電位差を異らせることを指す。

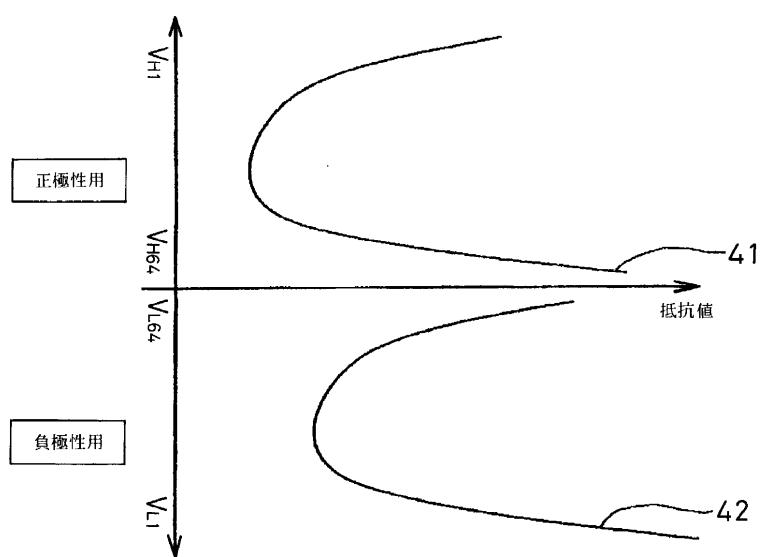

【0052】図 4 に 64 階調表示の場合のソースドライバ 2 内部の階調電圧発生回路 11 である抵抗分圧回路を 20 レベルシフト  $V$  特性の補正が完全になされるように、各個の直列抵抗の抵抗値の設定例を示す。曲線 41 は正極性用の階調電圧  $V_{H_1}, V_{H_2}, \dots, V_{H_{64}}$  を作成するための 63 個の直列抵抗  $R_{H_1}, R_{H_2}, \dots, R_{H_n}, \dots, R_{H_{63}}$  の抵抗値を表す。曲線 42 は負極性用の階調電圧  $V_{L_1}, V_{L_2}, \dots, V_{L_{64}}$  を作成するための 63 個の直列抵抗  $R_{L_1}, R_{L_2}, \dots, R_{L_n}, \dots, R_{L_{63}}$  の抵抗値を表す。図 4 から分かるように、正極性用の階調電圧を作成するための直列抵抗の抵抗値と負極性用の階調電圧を作成するための直列抵抗の抵抗値とは、レベルシフト  $V$  特性の補正を考慮して上下非対称の設定になっている。

【0053】実施の形態 1 では、64 階調表示させるため、図 2 で示すように 2 レベルの正極性の階調基準電圧  $V_{H_{32}}, V_{H_{64}}$  と、2 レベルの負極性の階調基準電圧  $V_{L_{32}}, V_{L_{64}}$  とが階調基準電圧発生回路で作成され、各々ソースドライバの入力端子  $S_{H_{32}}, S_{H_{64}}, S_{L_{32}}, S_{L_{64}}$  に供給される。

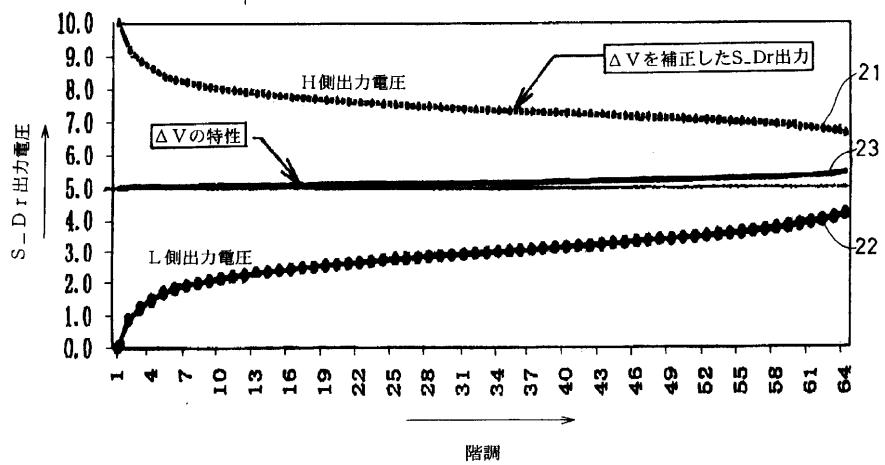

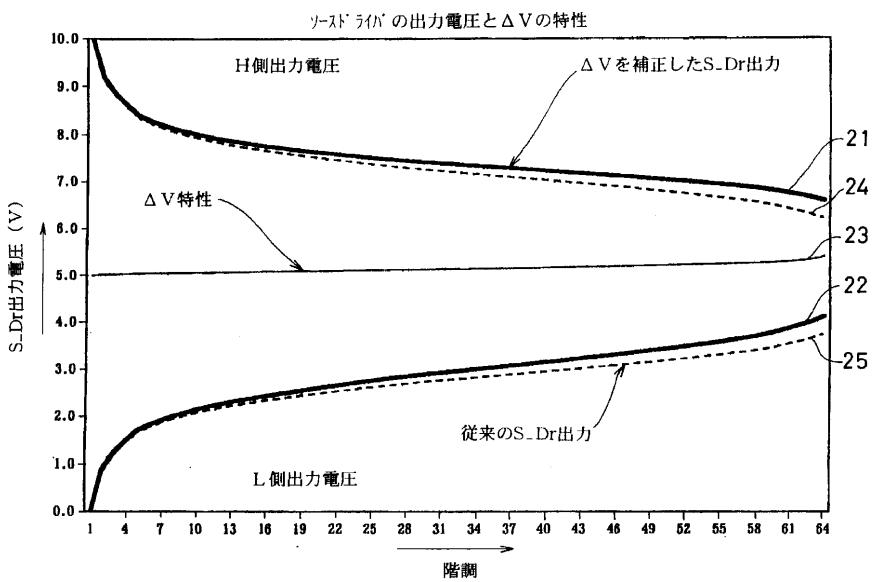

【0054】図 5 に、本実施の形態のソースドライバ 2 の抵抗分割回路で作成された正極性と負極性の各階調毎のソースラインへの出力電圧を示す。さらに図 5 の拡大図を図 6 に示す。図 5 および図 6 では、64 階調表示を行う場合を示しており、図 6 には、レベルシフト  $V$  の階調電圧依存性および従来のソースドライバを用いた場合のソースラインへの出力電圧も併せて示している。図 50

5 および図 6 の横軸は階調を表し、縦軸は出力電圧を表す。図 5 および図 6 の曲線 21 は、本実施の形態における正極性の各階調毎のソースラインへの出力電圧を、曲線 22 は、本実施の形態における負極性の各階調毎のソースラインへの出力電圧を、曲線 23 は、レベルシフト  $V$  の階調電圧依存性 ( $V$  特性) を表す。また、図 1 5 の曲線 24 は、従来の正極性の各階調毎のソースラインへの出力電圧を、曲線 25 は、従来の負極性の各階調毎のソースラインへの出力電圧を表す。図 5 および図 6 ではソースドライバの出力が階調 1 の正極性で  $+10$   $V$ 、階調 1 の負極性で  $0$   $V$ 、センター電圧が  $+5$   $V$  の場合を示す。

【0055】レベルシフト  $V$  は、階調が大きくなるにつれて上昇し、階調 1 から階調 64 までに、約  $+0.4$   $V$  上昇し、階調電圧によって非線形に変化することがわかる。本実施の形態では、ソースドライバの階調電圧は、各階調においてレベルシフト  $V$  の階調電圧依存性を考慮して作成されているため、正極性のソースラインへの出力電圧曲線 21 と負極性のソースラインへの出力電圧曲線 22 とはレベルシフト  $V$  特性曲線 23 に対して対称となっている。そのため、各々の階調における正極性の液晶セル電圧  $V_{L_C}$  と負極性の液晶セル電圧  $V_{L_C}$  とを等しくすることができ、フリッカなどの表示不具合は見られない。

【0056】これに対して、従来技術では曲線 24, 25 に示すように、出力電圧がセンター電圧  $+5$   $V$  に対してのみ各階調で対称となっており、液晶における DC 電圧がかかり、液晶の劣化またはフリッカが発生する。また、従来技術では、たとえば正極性用階調基準電圧と負極性用階調基準電圧を各々 5 点程度づつ、外部回路からソースドライバに供給し、レベルシフト  $V$  特性の補正のずれが少なくなるよう試みられてきたが、実際は、図 13 に示すように目標とする電圧からずれ  $V_a$  が生じ、 $V_a$  が大きくなるとフリッカが発生していた。

【0057】本実施の形態では、レベルシフト  $V$  の階調電圧依存性を考慮して、ソースドライバ内の抵抗分割回路の抵抗分割比が上下非対称に設定されており、これによって図 5 および図 6 の曲線 21, 22 のようにレベルシフト  $V$  特性に合った出力をすることができる。また、本実施の形態のソースドライバを備えるソースライン駆動回路は、上述のように抵抗分割比が設定されることにより、出力電圧のセンター値が図 13 の曲線 32 に示すような特性をもつ階調電圧を発生することができる。そのため、レベルシフト  $V$  特性の補正のずれがなく、フリッカなどの表示不具合を完全に解消できる。

【0058】また、ソースドライバ内部に抵抗分割比を最適に作りこむことで、IC 化したときの特徴である抵抗分割比精度がよいというメリットも得ることができる。仮に外部回路から全階調分の電圧を供給することは、前記課題で示したように最も高精度であるべき中間

調表示領域で5mV程度の電圧精度が要求されるため、実現できない。本実施の形態ではIC内にV特性の補正を考慮した特性を満たし、かつ特性に適合した階調電圧を作成できる電圧発生回路を設けた。一般にIC内での分圧精度は、約1mV以下の精度で設定することが可能であり、本願発明を実現することができる。ここで

特性とは表示装置へ入力される表示信号と該表示装置の出力である表示特性の関係を表す特性で、特性がその表示信号と表示装置に適合していないときは、表示される画像が白側または黒側に飽和し観察者に違和感を感じさせる。特性は表示信号または表示装置によって異なるため、その特性を考慮して階調電圧を決める必要がある。しかしながら、一般に使われる、たとえばTV信号またはVGA(Video Graphics Array)信号などの表示信号や、たとえばCRTなどの表示装置では、特性の値はほぼ一定であり、その値にあわせて階調電圧を決めることができる。またV特性は、液晶表示装置に使用される液晶材料の種類が支配的であるため、液晶材料が共通の表示装置であれば画面サイズにかかわらず本発明の駆動回路も共通に使用できる。

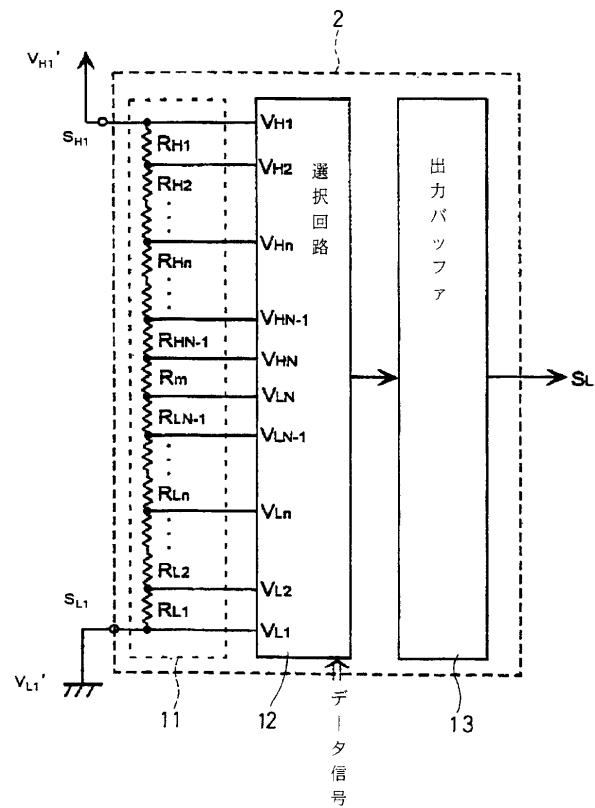

【0059】(実施の形態2)実施の形態2においては、ソースドライバの外部に階調基準電圧回路を設けていない。ソースドライバ2は、図7に示すように、IC(集積回路)化された階調電圧作製回路11、選択回路12、出力バッファ13および2つの入力端子S<sub>H1</sub>、S<sub>L1</sub>を備えており、一方の入力端子S<sub>H1</sub>には、外部電源により形成した正極性用の最上位階調基準電圧V<sub>H1</sub>’が供給され、他方の入力端子S<sub>L1</sub>には、外部電源により形成した負極性用最下位階調基準電圧V<sub>L1</sub>’が供給される。ソースドライバは外部から供給される階調基準電圧V<sub>H1</sub>’およびV<sub>L1</sub>’に基づいて、階調電圧作成回路11で複数の階調電圧を作成し、選択回路12においてデータ信号に応じたいずれかの階調電圧を選択し、出力バッファ13を介してソースライン4へ出力する。

【0060】ソースドライバ2の階調電圧作成回路11は、実施の形態1と同様に複数の抵抗が直列に接続された抵抗分圧回路からなる。たとえば、N階調表示されるには、2N-1個の抵抗が一方の入力端S<sub>H1</sub>から他方の入力端S<sub>L1</sub>の間に、R<sub>H1</sub>、R<sub>H2</sub>、…、R<sub>Hn</sub>、…、R<sub>HN-1</sub>、R<sub>m</sub>、R<sub>LN-1</sub>、…、R<sub>Ln</sub>、…、R<sub>L1</sub>の順に直列に設けられている。

【0061】実施の形態2では、階調電圧作成回路11中の2N-1個の直列抵抗を用いて正極性用最上位階調基準電圧V<sub>H1</sub>’と負極性用最下位階調基準電圧V<sub>L1</sub>’との間を抵抗分割し、正極性用のN個の階調電圧、および負極性用のN個の階調電圧、計2N個の所望の階調電圧を作成する。実施の形態1と同様に、ソースドライバ内部の抵抗分圧回路で階調表示が滑らかにかつ所望の特性になるように全ての階調を設定し、かつレベルシフトV特性の補正が完全になされるように、抵抗分割比を

正極性側と負極性側とで上下非対称になるように設定している。

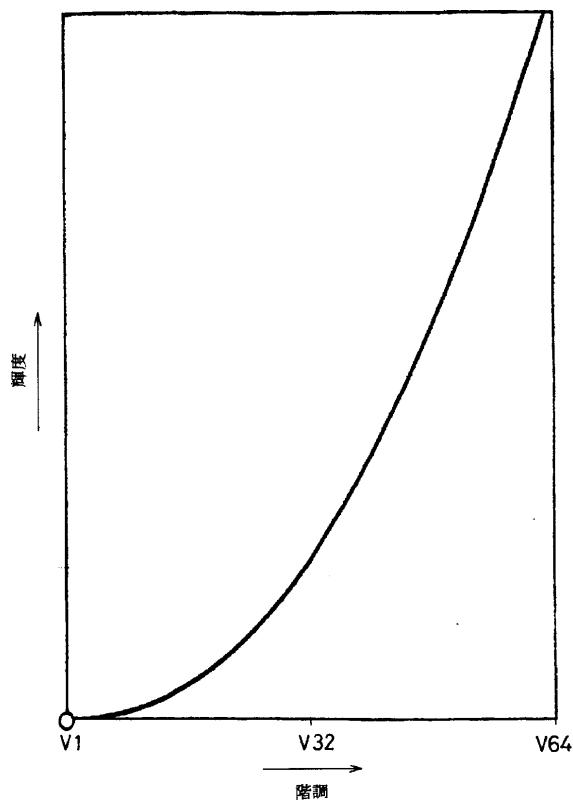

【0062】図8に、本実施の形態2のソースドライバの抵抗分圧回路で作成された階調電圧をソースラインへ出力し、液晶パネルの画素を駆動させたときの輝度を階調毎に示す。図8の横軸は階調を表し、縦軸は各階調ごとの液晶セル電圧V<sub>LC</sub>を液晶パネルの液晶層に印加したときの輝度を表す。第1階調電圧V<sub>1</sub>(黒表示)のところに○印が付してあるのは、正極性および負極性ともに、第1階調電圧V<sub>1</sub>として外部からソースドライバに階調基準電圧が供給されていることを表している。図8に示されるように、正極性用最上位階調基準電圧と負極性用最下位階調基準電圧とを入力するだけで、第1階調電圧V<sub>1</sub>から第64階調電圧V<sub>64</sub>まで、不自然な輝度変化をすることなく、かつレベルシフトV特性の補正がなされた表示が可能な液晶表示装置を実現できる。

【0063】また、本実施の形態2のソースドライバを有するソースライン駆動回路が備えられたアクティブマトリクス型液晶表示装置では、フリッカ評価パターンを用いての共通電極電圧の調整作業において、ある階調パターンに対してフリッカが生じないように共通電極電圧を最適化するだけで、他の全ての階調パターンについてもフリッカが生じなくすることができる。これにより、共通電極電圧を最適化する調整作業を非常に簡便に短時間に行なうことが可能となる。

【0064】上述したように、実施の形態2においては、ソースドライバの外部に階調基準電圧発生回路を設けずに、正極性用最上位階調基準電圧V<sub>H1</sub>’および負極性用最下位階調基準電圧V<sub>L1</sub>’のみをソースドライバに供給するだけで、上述のようにレベルシフトV特性の補正が完全になされるように、抵抗分圧回路の抵抗分割比が設定されているため、出力電圧のセンター値が図13の曲線32に示されるような特性を持つ階調電圧を出力可能である。そのため、レベルシフトV特性の補正のずれがなく、フリッカなどの表示不具合を完全に解消できる液晶表示装置を提供することができる。

【0065】

【発明の効果】本発明によれば、ソースドライバに設けられている階調電圧作成用の抵抗分圧回路の複数の抵抗分割比が、液晶の誘電率異方性に起因するレベルシフトVの非線形な特性を考慮して正極性用と負極性用とで非対称となるように設定されているので、レベルシフトV特性の補正を各階調において行なうことができ、各階調毎に正極性の液晶セル電圧V<sub>LC</sub>と負極性の液晶セル電圧V<sub>LC</sub>とを等しくすることができる。すなわち、液晶分子によけいなDC電圧がかかることがなくなるため、焼付きが発生せず、フリッカなどの表示不具合を解消することができ、表示品位を格段に向上することが可能となる。また全ての階調電圧がレベルシフトVを考慮して完全な補正がされるため、各階調のフリッカ評価パター

ンにて目視により共通電極電圧  $V_{COM}$  を調整する作業において、ある任意の1点の階調でフリッカが見えなくなるように共通電極電圧  $V_{COM}$  を調整するだけで、全階調でフリッカなどの表示不具合を完全に解消することができ、共通電極電圧  $V_{COM}$  の調整作業が非常に楽になり、作業時間を短縮することが可能となる。

【0066】また、本発明によれば、ソースドライバ内に設けられる階調電圧作成用の抵抗分圧回路の複数の抵抗分割比を I C (集積回路) 化することにより高精度で目標とする 特性 (階調表示特性) に合わせ込むことが可能である。よって、本発明によるソースドライバは、理想的な 特性を有する滑らかな階調表示を実現する液晶印加電圧を出力することができる。

【0067】また、本発明によるソースライン駆動回路は、階調電圧作成用の抵抗分割回路の抵抗分割比が前述のように設定されているので、従来のように多数のレベルの階調基準電圧をソースドライバに供給しなくとも画素を最適に駆動することができる。したがって、ソースライン駆動回路のソースドライバ外部に設ける階調基準電圧発生回路を削減することができるので、全体としてソースライン駆動回路規模を縮小することができ、部品コストを低減できるとともに、低消費電力化を実現することができる。

【0068】また、本発明によれば、ソースライン駆動回路は、正極性の最上位階調基準電圧と負極性用の最下位階調基準電圧とをソースドライバに供給し、正極性用および負極性用の全ての階調電圧をソースドライバ内の抵抗分圧回路で高精度かつ適正に作成することができるため、ソースドライバ外部に階調基準電圧発生回路を設ける必要がなく、ソースライン駆動回路規模を縮小することができ、部品コストを削減できるとともに、低消費電力化を実現することができる。

【0069】また、本発明によるアクティブマトリクス型液晶表示装置は、ソースドライバに設けられている階調電圧作成用の抵抗分圧回路の抵抗分割比が正極性用と負極性用とで非対称となるように設定されているため、各階調電圧によって異なるレベルシフト  $V$  を、ソースドライバ内の抵抗分圧回路の抵抗分割比に反映させて補正することができる。そのため、フリッカなどの表示不具合を解消することができ、表示品位を格段に向上したアクティブマトリクス型液晶表示装置を得ることができる。

【0070】また、従来のように多数の外部階調基準電圧をソースドライバに供給することなく、目標の 特性に合わせ込んだ理想的で高精度な階調電圧を作成することができる。したがって、ソースドライバ外部に設ける階調基準電圧発生回路を縮小することができ、全体としてソースライン駆動回路規模を縮小することができ、部品コストを削減できるとともに、低消費電力化を実現することができる。

#### 【図面の簡単な説明】

【図1】本発明に係るアクティブマトリクス型液晶表示装置の概略構成を示す図である。

【図2】本発明の実施の形態1に係るアクティブマトリクス型液晶表示装置の概略構成を示す図である。

【図3】本発明の実施の形態1に係るソースドライバの構成を示すブロック図である。

【図4】本発明の実施の形態1に係るソースドライバ内部の抵抗分圧回路の抵抗値を表す図である。

【図5】本発明の実施の形態1に係る各階調毎の正極性および負極性のソースラインへの出力電圧を表す図である。

【図6】本発明の実施の形態1に係る各階調毎の正極性および負極性のソースラインへの出力電圧を表す図である。

【図7】本発明の実施の形態2に係るソースドライバの構成を示すブロック図である。

【図8】本発明の実施の形態2に係る各階調毎の画素の輝度を表す図である。

【図9】スイッチング素子として TFT を使用したアクティブマトリクス型液晶表示装置における、1画素分の等価回路図である。

【図10】ゲートライン5に供給される走査電圧  $V_y$ 、ソースライン4に供給される階調電圧  $V_x$ 、極性反転信号  $R_E V$ 、共通電極電圧  $V_{COM}$  およびこれらの電圧によって液晶セル容量  $C_{LC}$  に生じる液晶セル電圧  $V_{LC}$  の波形をそれぞれ示す波形図である。

【図11】従来のアクティブマトリクス型液晶表示装置の概略構成を示す図である。

【図12】階調 - 輝度特性で基準電圧の入力が5点の場合を示す図である。

【図13】従来のアクティブマトリクス型液晶表示装置のソースドライバを用いたレベルシフト  $V$  および出力電圧のセンター値を示す図である。

【図14】従来の他のアクティブマトリクス型液晶表示装置の概略構成を示す図である。

【図15】従来の他のアクティブマトリクス型液晶表示装置の液晶駆動方法の電圧関係を説明するための図である。

#### 【符号の説明】

- 1 画素アレイ

- 2 ソースドライバ

- 3 ゲートドライバ

- 4 ソースライン

- 5 ゲートライン

- 6 TFT

- 7 画素

- 8 ソースライン駆動回路

- 9 階調基準電圧発生回路

- 1 2 選択回路

1 3 出力バッファ

2 1 本発明の正極性の各階調毎のソースラインへの出力電圧曲線

2 2 本発明の負極性の各階調毎のソースラインへの出力電圧曲線

2 3 各階調毎のレベルシフト  $V$  特性

2 4 従来における正極性の各段階毎のソースラインへ\*

- \*の出力電圧曲線

2 5 従来における負極性の各段階毎のソースラインへの出力電圧曲線

3 1 従来技術の駆動法で作成された階調電圧のセンタ一値

3 2 各階調毎のレベルシフト  $V$  特性

4 1 正極性の階調電圧作成用直列抵抗の抵抗値

4 2 負極性の階調電圧作成用直列抵抗の抵抗値

【図1】

【図13】

【図2】

【図3】

【図7】

【図4】

【図5】

【図6】

【図14】

【図8】

【図9】

【図10】

【図12】

【図11】

【図15】

フロントページの続き

(51)Int.CI.<sup>7</sup>G 0 9 G 3/20

H 0 4 N 5/66

識別記号

6 7 0

1 0 2

F I

G 0 9 G 3/20

H 0 4 N 5/66テ-マコ-ド<sup>®</sup> (参考)6 7 0 K

1 0 2 B

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 源极驱动器，源极线驱动电路和使用其的液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP2001100711A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2001-04-13 |

| 申请号            | JP2000207015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2000-07-07 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 西久保圭志<br>柳俊洋                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 西久保 圭志<br>柳 俊洋                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36 H04N5/66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| CPC分类号         | G09G3/3688 G09G3/3614 G09G3/3696 G09G2320/0204 G09G2320/0247 G09G2320/0257                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| FI分类号          | G09G3/36 G02F1/133.575 G09G3/20.611.E G09G3/20.612.F G09G3/20.641.P G09G3/20.670.K H04N5/66.102.B                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H093/NA36 2H093/NA53 2H093/NC03 2H093/NC11 2H093/ND06 2H093/ND10 2H093/ND12 2H093/ND35 2H193/ZC20 2H193/ZD23 2H193/ZF03 5C006/AC02 5C006/AC21 5C006/AF46 5C006/AF64 5C006/BB16 5C006/BC03 5C006/BC06 5C006/BC13 5C006/BC16 5C006/BF43 5C006/FA23 5C006/FA34 5C006/FA41 5C006/FA47 5C006/FA56 5C058/AA09 5C058/BA02 5C058/BA07 5C058/BA09 5C058/BA26 5C058/BB09 5C058/BB25 5C080/AA10 5C080/BB05 5C080/DD06 5C080/DD18 5C080/DD26 5C080/DD27 5C080/DD30 5C080/EE29 5C080/FF09 5C080/JJ02 5C080/JJ03 5C080/JJ05 5C080/KK02 5C080/KK43 |         |            |

| 优先权            | 1999210350 1999-07-26 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

### 摘要(译)

解决的问题：提供一种液晶显示装置，该液晶显示装置的灰度显示平滑并且没有诸如闪烁之类的显示缺陷，并且其显示质量显著提高。通过源极线向像素施加灰度级电压的源极线驱动电路8的源极驱动器2具有用于产生灰度级电压的电阻分压比，该电阻分压比根据灰度级显示特性而被优化。考虑到电平移动特性，将正极性和负极性的电阻分压比设定为不对称。