(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4245650号

(P4245650)

(45) 発行日 平成21年3月25日(2009.3.25)

(24) 登録日 平成21年1月16日(2009.1.16)

|                       |               |

|-----------------------|---------------|

| (51) Int.CI.          | F 1           |

| GO9F 9/30 (2006.01)   | GO9F 9/30 338 |

| GO9F 9/00 (2006.01)   | GO9F 9/00 352 |

| GO2F 1/1368 (2006.01) | GO2F 1/1368   |

請求項の数 12 (全 30 頁)

|              |                                                                      |           |                                              |

|--------------|----------------------------------------------------------------------|-----------|----------------------------------------------|

| (21) 出願番号    | 特願2008-125311 (P2008-125311)                                         | (73) 特許権者 | 000005049<br>シャープ株式会社<br>大阪府大阪市阿倍野区長池町22番22号 |

| (22) 出願日     | 平成20年5月12日 (2008.5.12)                                               | (74) 代理人  | 100077931<br>弁理士 前田 弘                        |

| (62) 分割の表示   | 特願2006-548873 (P2006-548873)<br>の分割<br>原出願日 平成17年12月14日 (2005.12.14) | (74) 代理人  | 100113262<br>弁理士 竹内 祐二                       |

| (65) 公開番号    | 特開2008-203889 (P2008-203889A)                                        | (72) 発明者  | 縁田 薫史<br>大阪府大阪市阿倍野区長池町22番22号<br>シャープ株式会社内    |

| (43) 公開日     | 平成20年9月4日 (2008.9.4)                                                 | (72) 発明者  | 八木 敏文<br>大阪府大阪市阿倍野区長池町22番22号<br>シャープ株式会社内    |

| 審査請求日        | 平成20年5月14日 (2008.5.14)                                               |           |                                              |

| (31) 優先権主張番号 | 特願2004-364498 (P2004-364498)                                         |           |                                              |

| (32) 優先日     | 平成16年12月16日 (2004.12.16)                                             |           |                                              |

| (33) 優先権主張国  | 日本国 (JP)                                                             |           |                                              |

| (31) 優先権主張番号 | 特願2005-295015 (P2005-295015)                                         |           |                                              |

| (32) 優先日     | 平成17年10月7日 (2005.10.7)                                               |           |                                              |

| (33) 優先権主張国  | 日本国 (JP)                                                             |           |                                              |

早期審査対象出願

最終頁に続く

(54) 【発明の名称】アクティブマトリクス基板、表示装置、液晶表示装置およびテレビジョン装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、前記基板上に形成された第1および第2アクティブ素子と、前記基板上に形成された第1および第2保持容量素子と、前記第1および第2保持容量素子を覆う層間絶縁膜と、前記層間絶縁膜上にそれぞれ形成され、かつ互いに隣接する第1および第2画素電極とを有しており、前記第1画素電極には前記第1アクティブ素子を介して第1データ信号が入力され、前記第2画素電極には前記第2アクティブ素子を介して前記第1データ信号と異なる第2データ信号が入力されるアクティブマトリクス基板であって、

前記第1および第2保持容量素子は、互いに共有する保持容量配線と、前記保持容量配線上に形成された絶縁膜と、前記絶縁膜を介して前記保持容量配線に対向配置され前記第1アクティブ素子のドレイン電極に接続された接続電極および前記第2アクティブ素子のドレイン電極に接続された接続電極にそれぞれ接続された互いに別個の保持容量電極とを有し、

前記第1保持容量素子の保持容量電極は、前記層間絶縁膜に形成されたコンタクトホールを介して前記第1画素電極と導通しており、

前記第2保持容量素子の保持容量電極は、前記層間絶縁膜に形成されたコンタクトホールを介して前記第2画素電極と導通しており、

前記第1および第2保持容量素子の各保持容量電極は、前記保持容量配線に沿って一列に配列され、

前記第1保持容量素子は、前記層間絶縁膜に形成されたコンタクトホールを介して前記

第1画素電極と導通していると共に、前記第1アクティブ素子のドレイン電極に接続された接続電極に接続されていない保持容量電極を有し、

前記第1画素電極と導通していると共に前記第1アクティブ素子のドレイン電極に接続された接続電極に接続されていない第1保持容量素子の保持容量電極は、前記第1画素電極と導通していると共に前記第1アクティブ素子のドレイン電極に接続された接続電極に接続された第1保持容量素子の保持容量電極と、前記第2画素電極と導通していると共に前記第2アクティブ素子のドレイン電極に接続された接続電極に接続された第2保持容量素子の保持容量電極との間に設けられているアクティブマトリクス基板。

【請求項2】

前記第2保持容量素子は、前記層間絶縁膜に形成されたコンタクトホールを介して前記第2画素電極と導通していると共に、前記第2アクティブ素子のドレイン電極に接続された接続電極に接続されていない保持容量電極を有し、

前記第2画素電極と導通していると共に前記第2アクティブ素子のドレイン電極に接続された接続電極に接続されていない第2保持容量素子の保持容量電極は、前記第2画素電極と導通していると共に前記第2アクティブ素子のドレイン電極に接続された接続電極に接続された第2保持容量素子の保持容量電極と、前記第1画素電極と導通していると共に前記第1アクティブ素子のドレイン電極に接続された接続電極に接続されていない第1保持容量の保持容量電極との間に設けられている請求項1に記載のアクティブマトリクス基板。

【請求項3】

請求項1又は2に記載のアクティブマトリクス基板と、前記アクティブマトリクス基板に対向する対向電極と、前記アクティブマトリクス基板および前記対向電極の間隙に介在する表示媒体層とを有する表示装置であって、

前記保持容量配線と前記対向電極とに同電位が与えられている表示装置。

【請求項4】

請求項1又は2に記載のアクティブマトリクス基板と、前記アクティブマトリクス基板に対向する対向電極が一方に形成された対向基板と、前記アクティブマトリクス基板および前記対向基板の間隙に介在する液晶層とを有する液晶表示装置。

【請求項5】

前記保持容量配線と前記対向電極とに同電位が与えられている請求項4に記載の液晶表示装置。

【請求項6】

前記液晶層が負の誘電異方性を有するネマチック液晶材料を含む垂直配向型液晶層である請求項5に記載の液晶表示装置。

【請求項7】

ノーマリー・ブラックモードで駆動する請求項6に記載の液晶表示装置。

【請求項8】

前記保持容量配線と前記対向電極とに異なる電位が与えられている請求項4に記載の液晶表示装置。

【請求項9】

前記液晶層が正の誘電異方性を有するネマチック液晶材料を含むツイスト配向型液晶層である請求項8に記載の液晶表示装置。

【請求項10】

ノーマリー・ホワイトモードで駆動する請求項9に記載の液晶表示装置。

【請求項11】

請求項3に記載の表示装置を備えるテレビジョン装置。

【請求項12】

請求項4乃至10のいずれか1つに記載の液晶表示装置を備えるテレビジョン装置。

【発明の詳細な説明】

【技術分野】

10

20

30

40

50

## 【0001】

本発明は、アクティブマトリクス基板、アクティブマトリクス基板の製造方法、表示装置、液晶表示装置およびテレビジョン装置に関する。例えば、液晶層を駆動するための薄膜トランジスタと保持容量素子とを各画素に配設したアクティブマトリクス（以下「AM」という）基板およびこのAM基板を備えたAM型液晶表示装置に関する。

## 【背景技術】

## 【0002】

AM基板は、液晶表示装置、EL（エレクトロルミネッセンス）表示装置などのAM型表示装置において幅広く用いられている。このようなAM基板を用いた従来のAM型液晶表示装置では、基板上に配置された複数本の走査信号線と、走査信号線と交差するように配置された複数本のデータ信号線と、両信号線の交点に配置された薄膜トランジスタ（以下「TFT」という）などを有しており、TFTのスイッチング機能により、各画素部に画像信号が伝達される。また、各画素部に保持容量素子を設けることもある（例えば、特許文献1を参照）。

## 【0003】

このような保持容量素子は、TFTがオフ期間中の液晶層の自己放電またはTFTのオフ電流による画像信号の劣化を防止している。また、保持容量素子は、TFTのオフ時間中の映像信号保持だけではなく、液晶駆動における各種変調信号の印加経路などにも使用され、保持容量素子を備えた液晶表示装置は、低消費電力と高画質とを実現することができる。

## 【0004】

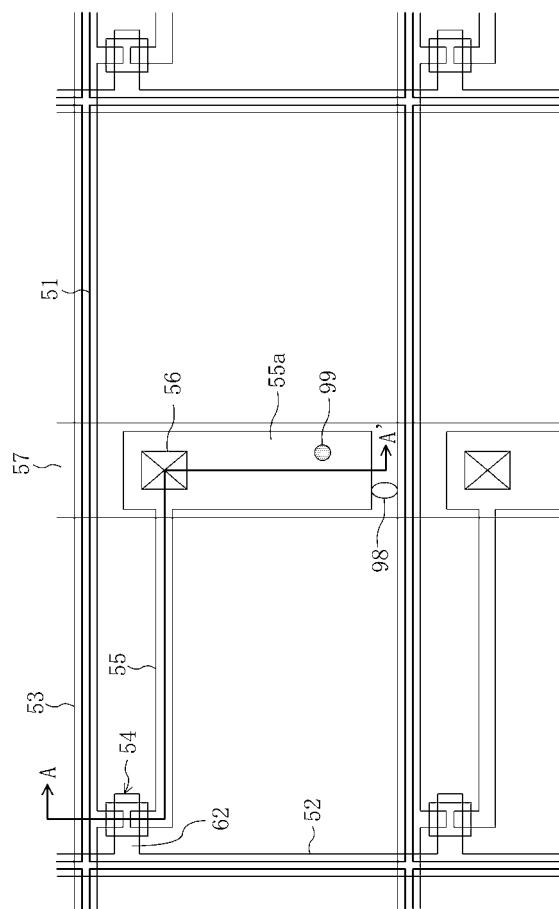

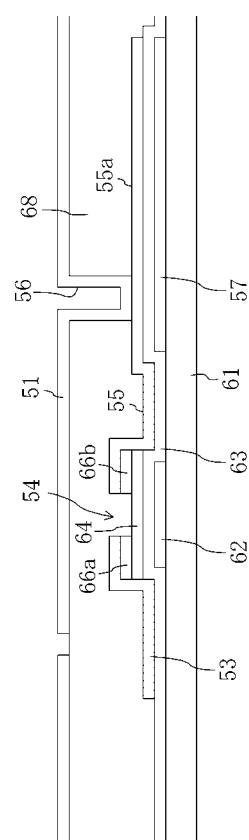

ここで、図面を参照しながら、従来のAM基板構造の一例を説明する。図24は、従来のAM型液晶表示装置に用いられる、保持容量素子を備えたAM基板の一画素の構成を示す平面模式図である。図25は、図24に示すAM基板を線分A-A'にて切断した断面を示す断面模式図である。

## 【0005】

図24および図25に示すように、AM基板には、複数の画素電極51がマトリクス状に設けられており、これらの画素電極51の周囲を通り、互いに交差するように、走査信号を供給するための走査信号線52と、データ信号を供給するためのデータ信号線53とが設けられている。また、これらの走査信号線52とデータ信号線53との交差部分において、画素電極51に接続されるスイッチング素子としてのTFT54が設けられている。このTFT54のゲート電極62には走査信号線52が接続され、ゲート電極62に入力される走査信号によってTFT54が駆動制御される。また、TFT54のソース電極66aにはデータ信号線53が接続され、TFT54のソース電極66aにデータ信号が入力される。さらに、ドレイン電極66bは、接続電極55を介して保持容量素子の一方の電極（上側保持容量電極）55aに接続され、さらに層間絶縁膜68に形成されたコンタクトホール56を介して画素電極51に接続されている。透明絶縁性基板（絶縁基板）61上には保持容量（共通）配線57が設けられ、この保持容量（共通）配線57が保持容量素子の他方の電極（下側保持容量電極）として機能する。

## 【0006】

図25に示すように、ガラスやプラスチックなどからなる透明絶縁性基板（絶縁基板）61上に、走査信号線52に接続されたゲート電極62が設けられている。走査信号線52やゲート電極62は、チタン、クロム、アルミニウム、モリブデンなどからなる金属膜や、それらの合金、積層膜で形成される。保持容量素子の他方の電極（下側保持容量電極）として機能する保持容量（共通）配線57は、走査信号線52やゲート電極62と同一材料により形成されている。これらを覆うゲート絶縁膜63は、窒化シリコンや酸化シリコンなどからなる絶縁膜により形成される。その上には、ゲート電極62と重畳するように、アモルファスシリコンやポリシリコンなどからなる高抵抗半導体層64と、さらにリンなどの不純物がドープされたn<sup>+</sup>アモルファスシリコンなどからなる低抵抗半導体層57とが設けられている。なお、低抵抗半導体層がソース電極66aおよびドレイン電極66b

10

20

30

40

50

bとなる。

【0007】

また、ソース電極66aと接続するように、データ信号線53が形成されている。さらに、ドレイン電極66bと接続するように、接続電極55が設けられ、接続電極55は保持容量素子の一方の電極である上側保持容量電極55aに接続されるように延びており、上側保持容量電極55aは画素電極51とコンタクトホール56を介して接続されている。データ信号線53、接続電極55および上側保持容量電極55aは、同一材料により形成され、チタン、クロム、アルミニウム、モリブデンなどの金属膜や、それらの合金、積層膜で形成される。

【0008】

画素電極51は、例えば、ITO(酸化インジウム錫)、IZO(酸化インジウム亜鉛)、酸化亜鉛、酸化スズなどの透明性を有する導電膜で形成される。コンタクトホール56は、TFT54、走査信号線52、データ信号線53および接続電極55の上部を覆う層間絶縁膜68を貫くように形成されている。層間絶縁膜68の材料としては、例えば、アクリル樹脂や、室化シリコン、酸化シリコンなどが挙げられる。図24および図25に示すような構造のAM基板については、例えば特許文献2に開示されている。

【0009】

このような構造のAM基板においては、製造プロセスの簡略化、製造コスト低減を目的として、保持容量(共通)配線(下側保持容量電極)57を走査信号線52と同一工程にて形成し、上側保持容量電極55aをデータ信号線53や接続電極55と同一工程にて形成している。また、図25に示すように、画素電極51を層間絶縁膜68の上に形成すると、画素電極51を各信号線52, 53と重畳させることができるので、高開口率化が図られるとともに、さらに画素電極51への各信号線52, 53からの電界をシールドできる効果もある。このとき、保持容量(共通)配線57または走査信号線52のパターン上の層間絶縁膜68にコンタクトホール56を形成して、画素電極51と上側保持容量電極55aとを接続し、接続電極55を介することで、画素電極51とドレイン電極66bとの接続が図られている。コンタクトホール56の形成位置は、上側保持容量電極55aの形成領域内に特に限定されるものではなく、接続電極55の形成領域内でも可能である。しかし、図24に示すように、保持容量(共通)配線57のパターン上の上側保持容量電極55aの形成領域内に形成すれば、開口率を低下させる新たな原因とならないので、好みしい。

【0010】

図24および図25に示すAM基板の保持容量素子においては、保持容量配線(下側保持容量電極)57と上側保持容量電極55aとの間のゲート絶縁膜63に導電性異物(ダストやパーティクル)やピンホール99が存在すると、保持容量配線(下側保持容量電極)57と上側保持容量電極55aとが短絡するので、短絡した画素が表示画像において点欠陥となってしまう点で改善の余地があった。また、エッチング不良やフォトリソ不良などによって、同一工程にて形成されるデータ信号線53と上側保持容量電極55aとが膜残り98の欠陥などにより短絡した場合にも、同様の点欠陥となり、修復できないという点で工夫の余地があった。

【0011】

例えば、MDA(Multi-domain Vertical Alignment)モードなどのVA(Vertically Alignment)液晶を用いた液晶表示パネルでは、電圧無印加状態において黒表示となるように設定される。データ信号線53と上側保持容量電極55aとが短絡した場合、TFT54を介さずにデータ信号が画素電極51に入力されることになるので、画素電極51に入力されるデータ信号を走査信号によって制御できなくなる。したがって、電圧無印加時においてその画素は黒表示とならず、輝点となる。なお、全面を黒表示にしたときに発生する輝点は、全面を白表示にしたときに発生する黒点や暗点よりも目立ち易いので、表示品位に与える影響が大きい。このような点欠陥を修正する技術が例えば特許文献3~5に開示されている。

10

20

30

40

50

## 【0012】

近年、薄型TVの大画面化が進むにつれて画素が大きくなり、欠陥画素が表示品位上無視できない大きさになってきている。画素欠陥の大きさを縮小するために、一画素を複数のサブピクセルに分割することにより、点欠陥の大きさ自体を小さくする技術が開発されている。しかし、一画素を複数のサブピクセルに分割することによってパターンが複雑化し、開口率が低下する問題がある。例えば、26インチ型のWXGA (Wide eXtended Graphics Array) ディスプレイでは開口率が4%～5%程度低下する。

## 【0013】

開口率を高めるために、隣接する画素が保持容量配線を共有する構造が例えば特許文献6および7に開示されている。具体的に述べると、画素を例えば2つのサブピクセルに分割した場合でも、保持容量配線（下側保持容量電極）と上側保持容量電極との間の絶縁層に導電性異物やピンホールが存在すると、保持容量配線（下側保持容量電極）と上側保持容量電極とが短絡し、短絡したサブピクセルが表示画像において点欠陥となってしまう。しかし、分割しない場合と比較すると、点欠陥の面積が1/2になるので、点欠陥が表示品位に与える影響が小さくなる。

## 【0014】

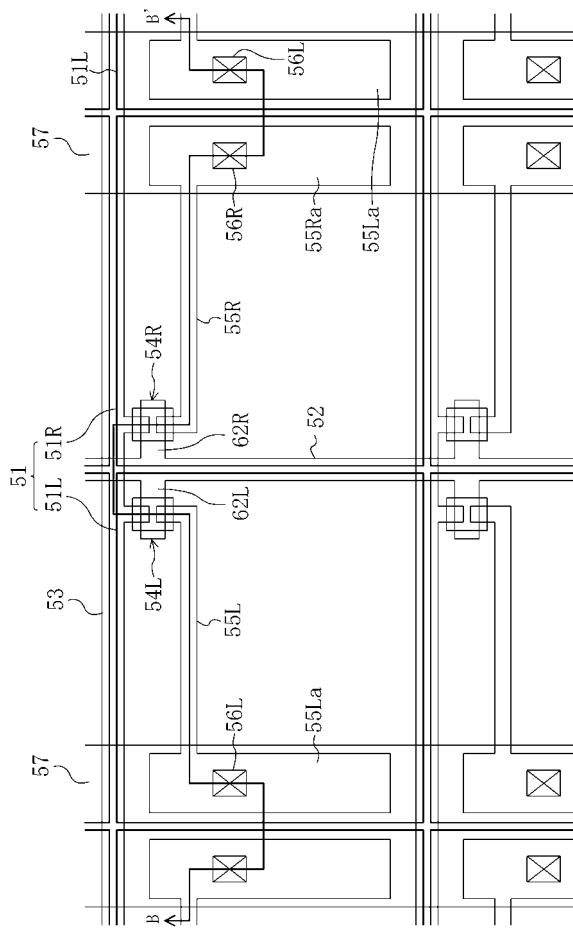

図26は、一画素を複数のサブピクセルに分割したAM基板における一画素の構成を示す平面模式図である。図27は、図26に示すAM基板を線分B-B'にて切断した断面を示す断面模式図である。なお、図26および図27において、図24および図25に示す構成要素と同一の構成要素には同一の参照符号を付している。

10

20

## 【0015】

図26および図27に示すように、画素電極51が2つのサブピクセル電極51L, 51Rに分割されており、これらのサブピクセル電極51L, 51Rの境界付近に走査信号を供給するための走査信号線52が設けられ、画素電極51の周囲にはデータ信号を供給するためのデータ信号線53が設けられている。また、走査信号線52とデータ信号線53との交差部分において、走査信号線52を平面視において挟んで配置され、サブピクセル電極51L, 51Rに接続されるスイッチング素子としてのTFT54L, 54Rが設けられている。TFT54L, 54Rのゲート電極62L, 62Rには走査信号線52が接続され、ゲート電極62L, 62Rに入力される走査信号によって、TFT54L, 54Rが駆動制御される。また、TFT54L, 54Rのソース電極66aにはデータ信号線53が接続され、TFT54L, 54Rのソース電極にデータ信号が入力される。さらに、ドレイン電極66bは、接続電極55L, 55Rを介して保持容量素子の一方の電極（上側保持容量電極）55La, 55Raに接続され、さらに層間絶縁膜68に形成されたコンタクトホール56L, 56Rを介してサブピクセル電極51L, 51Rに接続されている。透明絶縁性基板（絶縁基板）61上には保持容量（共通）配線57が設けられ、この保持容量（共通）配線57が保持容量素子の他方の電極（下側保持容量電極）として機能する。言い換えれば、互いに隣接する画素の上側保持容量電極55La, 55Raが、保持容量素子の他方の電極（下側保持容量電極）として、保持容量（共通）配線57を共有する。なお、図26および図27に示すAM基板は、図24および図25に示すAM基板を製造する工程と同様の工程を経て製造することができる。

30

40

## 【0016】

しかし、図26および図27に示すAM基板では、開口率の低下を抑えるために、互いに隣接する画素の境界付近に保持容量（共通）配線57が形成されている。保持容量（共通）配線57に対向して設けられた上側保持容量電極55La, 55Raは、十分な保持容量を確保するために、できる限り大面積にする必要がある。したがって、互いに隣接する画素の上側保持容量電極55La, 55Raが近接して形成されるので、互いに隣接する上側保持容量電極55La, 55Ra間でリーク不良が生じ易い。

## 【0017】

リーク不良が生じた場合、保持容量（共通）配線57を共有する2つのサブピクセル電極51L, 51Rが導通し、連結欠点になるという問題がある。これを回避するために、

50

隣接する画素のデータ信号が入力しないように修正する必要がある。例えば、互いに隣接する画素のうち一方の画素（第1画素）の上側保持容量電極55Laから第1画素に隣接する第2画素のサブピクセル電極51Rにデータ信号が入力されるのを防ぐために、第2画素におけるコンタクトホール56R内のサブピクセル電極51Rを除去することにより、サブピクセル電極51Rと上側保持容量電極55Raとを電気的に切り離す。また、第2画素のドレイン電極66bから上側保持容量電極55La, 55Raを介して第1画素のサブピクセル電極51Lにデータ信号が入力されるのを防ぐために、第2画素の接続電極55Rと上側保持容量電極55Raとを電気的に切り離す。したがって、互いに隣接する画素のうち1つの画素（第2画素）のサブピクセルが無通電状態になるので、点欠陥となる。

10

#### 【0018】

すなわち、一画素を複数のサブピクセルに分割したAM基板では、分割しないAM基板と比較すると、点欠陥が表示品位に与える影響が小さくなるが、互いに隣接する上側保持容量電極55La, 55Ra間でリーク不良が生じるおそれが付加されるので、点欠陥が生じる可能性が高くなるという点で改善の余地がある。

【特許文献1】特開平6-95157号公報（第1頁）

【特許文献2】特開平9-152625号公報（第8-11、19頁、第3、4図）

【特許文献3】特開平1-303415号公報

【特許文献4】特開平9-222615号公報

【特許文献5】特開平7-270824号公報

20

【特許文献6】特開2004-62146号公報

【特許文献7】特開2004-78157号公報

#### 【発明の開示】

【発明が解決しようとする課題】

#### 【0019】

本発明の目的の1つは、AM基板における点欠陥を修正することである。本発明の他の目的は、点欠陥を修正することにより、製造歩留りを向上させることである。

#### 【課題を解決するための手段】

#### 【0020】

本発明では、保持容量配線に対向配置された上側保持容量電極を2つ以上設け、各上側保持容量電極上の層間絶縁膜にコンタクトホールを形成し、コンタクトホールを介して層間絶縁膜上の画素電極を各上側保持容量電極と導通させることによって、上記課題を解決する。

30

#### 【0021】

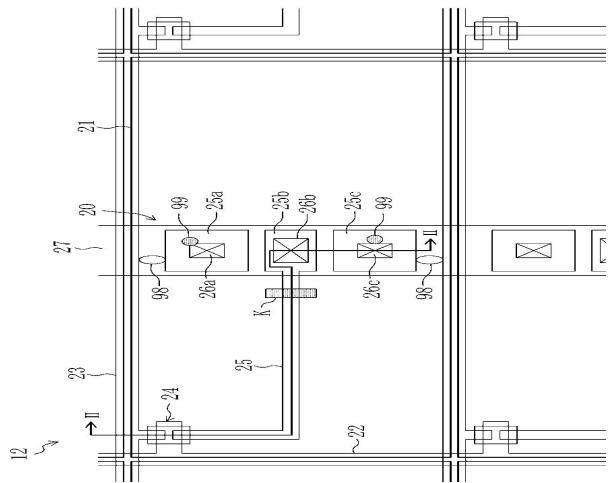

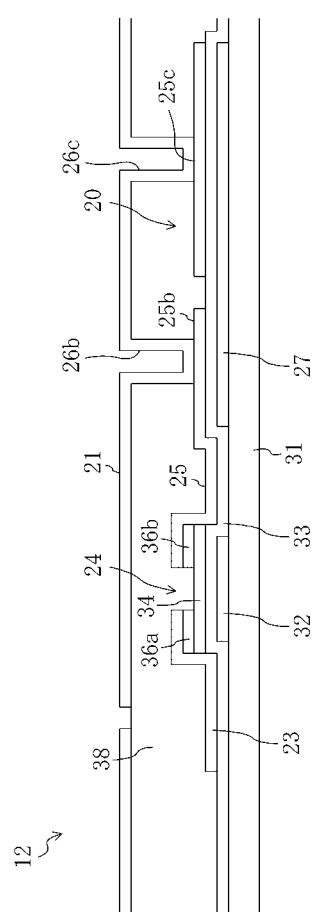

図面を参照しながら、本発明を具体的に説明する。図1は本発明のAM基板12の一態様を模式的に示す平面図であり、図2は図1中のII-II線断面図である。

#### 【0022】

本態様のAM基板12は、基板31と、基板31上に形成されたアクティブ素子（例えばTFT24）と、基板31上に形成された保持容量素子20と、保持容量素子20を覆う層間絶縁膜38と、層間絶縁膜38上に形成された画素電極21とを有する。保持容量素子20は、基板31上に形成された保持容量配線27と、保持容量配線27上に形成された絶縁膜（例えばゲート絶縁膜33）と、ゲート絶縁膜33を介して保持容量配線27に対向配置された3つの上側保持容量電極25a, 25b, 25cとを有する。TFT24は、列方向に延びる走査信号線22から行方向に延びたゲート電極32と、ゲート電極32を覆うゲート絶縁膜33と、ゲート絶縁膜33を介してゲート電極32上に形成された高抵抗半導体層34と、高抵抗半導体層34上に形成されたソース電極36aおよびドレイン電極36bとを有する。ソース電極36aは行方向に延びるデータ信号線23に接続され、ドレイン電極36bは接続電極25を介して上側保持容量電極25bに接続されている。

40

#### 【0023】

50

3つの上側保持容量電極 25a, 25b, 25c は、層間絶縁膜 38 にそれぞれ形成されたコンタクトホール 26a, 26b, 26c を介して、画素電極 21 と導通している。これにより、3つの上側保持容量電極 25a, 25b, 25c が画素電極 21 を介して導通するので、接続電極 25 を介して1つの上側保持容量電極 25b に入力されたデータ信号が画素電極 21 に入力されるとともに、2つの上側保持容量電極 25a, 25c にもデータ信号が入力される。すなわち、3つの上側保持容量電極 25a, 25b, 25c に同電位が与えられる。

#### 【0024】

次に、点欠陥を修正する工程について説明する。保持容量配線 27 と上側保持容量電極 25a, 25c とがゲート絶縁膜 33 中の導電性異物やピンホール 99 により短絡した場合は、保持容量配線 27 に供給された電位が上側保持容量電極 25a, 25c を介して画素電極 21 に与えられる。典型的には、画素電極 21 に対向配置された対向電極（不図示）と保持容量配線 27 とに同電位が与えられるので、画素電極 21 と対向電極とに電圧が印加されない状態となる。したがって、ノーマリー ホワイトモードの液晶表示装置では、その画素は輝点となり、ノーマリーブラックモードの液晶表示装置では、その画素は黒点となる。

#### 【0025】

また、データ信号線 23 と上側保持容量電極 25a, 25c とが膜残り 98 の欠陥などにより短絡した場合、TFT 24 を介さずにデータ信号が画素電極 21 に入力されることになるので、画素電極 21 に入力されるデータ信号を走査信号によって制御できなくなる。したがって、電圧無印加時において、ノーマリー ホワイトモードの液晶表示装置では、その画素は白表示とならず、ノーマリーブラックモードの液晶表示装置では、黒表示とならない。

#### 【0026】

これらの点欠陥を修正するために、短絡した上側保持容量電極 25a, 25c に形成されているコンタクトホール 26a, 26c 内の画素電極 21 をレーザなどにより取り除く。これにより、短絡した上側保持容量電極 25a, 25c を画素電極 21 から分離することができる。これにより、保持容量配線 27 からの電位が上側保持容量電極 25a, 25c を介して画素電極 21 に与えられるのを防ぐことができる。したがって、保持容量が正常の場合よりも低下するが、正常に近い画素駆動を行うことができる。

#### 【0027】

一方、接続電極 25 に接続された上側保持容量電極 25b と保持容量配線 27 とがゲート絶縁膜 33 中の導電性異物やピンホールにより短絡した場合は、短絡した上側保持容量電極 25b に形成されているコンタクトホール 26b 内の画素電極 21 をレーザなどにより取り除くことによって、短絡した上側保持容量電極 25b を画素電極 21 から分離することができる。さらに、レーザなどを用いて接続電極 25 を切断箇所 K で破壊分離すれば、データ信号線 23 と保持容量配線 27 とが TFT 24 を介して短絡するのを避けることができる。しかし、同時に画素電極 21 も TFT 24 から分離されるので、他の上側保持容量電極 25a, 25c (但し、コンタクトホール 26a, 26c の領域を除く) をレーザなどでメルトすることにより、画素電極 21 と保持容量配線 27 とを導通させる。これにより、画素電極 21 を保持容量配線 27 と同じ電位にすることができるので、例えばノーマリーブラックモードの液晶表示装置では、画素電極 21 の領域を黒表示にさせ、微小欠点として修正することができる。

#### 【0028】

本態様のAM基板 12 では、接続電極 25 に接続された上側保持容量電極 25b と保持容量配線 27 とが重なる領域の面積（第1面積）が、接続電極 25 に接続されていない上側保持容量電極 25a, 25c と保持容量配線 27 とが重なる領域の面積（第2面積）よりも小さい。しかし、上側保持容量電極 25a, 25b, 25c と画素電極 21 とのコンタクトの信頼性や、保持容量配線 27 と上側保持容量電極 25a, 25b, 25c が短絡する確率などに応じて、第1面積と第2面積との面積比を適宜選択することができる。

10

20

30

40

50

## 【0029】

例えば、コンタクトホール26bと比較して、コンタクトホール26a, 26cのほうが画素電極21をカバレージよく上側保持容量電極25a, 25cに接続することが難しい場合がある。あるいは上側保持容量電極のアルミニウムなどの金属膜と画素電極21のITOなどの膜との接触抵抗が大きい場合がある。これらの場合、上側保持容量電極25a, 25cが保持容量素子の電極としての機能を果たさないことがある。そこで、第1面積が第2面積よりも大きくなるように設定する。これにより、第1面積と第2面積とを足した総面積に対して第1面積の比率が高くなるので、第1面積の比率に応じた大きな保持容量を確保できる。

## 【0030】

本態様のAM基板12では、TFT24と上側保持容量電極とを接続する接続電極25の本数が1本である。これにより、接続電極25を全ての上側保持容量電極25a, 25b, 25cに接続した場合に比べて、開口率の低下を抑えることができる。

## 【0031】

また、図1に示すAM基板12では、接続電極25を介してTFT24と上側保持容量電極25bとが接続されているが、TFT24と上側保持容量電極とを接続する接続電極がなくてもよい。これにより、開口率の低下をさらに抑えることができる。例えば、TFT24のドレイン電極36b上の層間絶縁膜38にコンタクトホールを形成し、コンタクトホールを介して画素電極21とドレイン電極36bとを接続することにより、画素電極21を介して上側保持容量電極25a, 25b, 25cにデータ信号の電位を与えることができる。

## 【0032】

さらに、コンタクトホール26aの位置は、上側保持容量電極25bの領域内に特に限定されるものではなく、接続電極25の領域内でも可能である。但し、図1に示すように、保持容量配線27のパターン内であって、上側保持容量電極25bの領域内にコンタクトホール26aを形成すれば、開口率の低下を抑えることができる。

## 【0033】

他の局面において、本発明のAM基板12を動作モードがMVAの液晶表示装置に用いる場合には、スリット(電極層がない部分)の領域や対向基板に形成され、液晶層側に突出したリブ(凸部)の領域に接続電極25を配置することにより、接続電極25による開口率の低下を減らすことができる。

## 【0034】

本態様のAM基板12では、上側保持容量電極25a, 25b, 25cの平面視における形状が四辺形であるが、これに限定されず、三角形、半円形、台形などの形状であってもよい。3つの上側保持容量電極25a, 25b, 25cは、ゲート絶縁膜33の上に、保持容量配線27のパターンに重なるように設けられる。典型的には、上側保持容量電極はデータ信号線23と同一膜から形成されるので、膜残り98により上側保持容量電極がデータ信号線23と短絡し易い。そのため、図1に示すように、データ信号線23に近接する上側保持容量電極25a, 25cと、接続電極25に接続された上側保持容量電極25bとを分離することが好ましい。なお、上側保持容量電極は、図1に示すように、3分割されているが、分割数(N)はこれに限定されず、N=2であればよい。

## 【0035】

保持容量配線27は、典型的には、走査信号線22やゲート電極32と同一材料にて形成されるが、これに限定されるものではない。例えば、走査信号線22やゲート電極32の形成前または形成後に、他の材料(例えば、ITOなどの透明導電膜)を用いて、保持容量配線27を形成してもよい。

## 【0036】

また、本態様のAM基板12では、保持容量素子20を構成する絶縁膜は、図2に示すように、ゲート絶縁膜33のみであるが、これに限定されるものではない。例えば、保持容量配線27の上に、ゲート絶縁膜33以外の他の絶縁膜をゲート絶縁膜33の形成前ま

10

20

30

40

50

たは形成後に形成することにより、ゲート絶縁膜33を含む積層膜を形成してもよい。

【0037】

本発明のAM基板は、液晶表示装置や有機または無機EL表示装置などの表示装置に利用することができる。本発明は、他の局面において、表示装置を提供する。本発明の表示装置は、本発明のAM基板と、AM基板に対向する対向電極と、AM基板および対向電極の間隙に介在する表示媒体層とを有する。本明細書において「表示媒体層」とは、印加される電圧あるいは供給される電流に応じて光量が調整される層であり、光源からの光や外光（周囲光）の光透過率（または光反射率）が変調される層や自発光型の層を包括する。具体的な表示媒体層は、例えば液晶層、無機または有機EL層などである。

【0038】

また本明細書において「対向電極」は、AM基板の画素電極に対向して配置された電極であり、共通（全面）電極やストライプ電極を含む。例えば、有機EL表示装置においては、典型的には、陽極が画素電極に、陰極が対向電極にそれぞれ該当する。対向電極は、アルミニウムや銀などの光反射性を有する導電膜から形成されてもよく、ITO、IZO、酸化亜鉛、酸化スズなどの透明性を有する導電膜で形成されてもよい。

【0039】

本発明は、さらに他の局面において、液晶表示装置を提供する。本発明の液晶表示装置は、本発明のAM基板と、AM基板に対向する対向電極が一方に形成された対向基板と、AM基板および前記対向基板の間隙に介在する液晶層とを有する。なお、対向基板は、典型的には、ガラスやプラスチックなどからなる透明絶縁性基板である。

【0040】

本発明の表示装置および液晶表示装置においては、保持容量配線と対向電極とに同電位が与えられてもよい。有機EL表示装置において、AM基板の点欠陥を修正することにより、画素電極が保持容量配線に導通したとき、保持容量配線と対向電極とが同電位ならば、有機EL層（典型的には、電子輸送層、発光層および正孔輸送層を含む）に電流が流れないので、発光領域（画素）が発光しない。言い換えば、発光領域は黒点化されるので、点欠陥が目立ち難くなる。

【0041】

液晶表示装置において、AM基板の点欠陥を修正することにより、欠陥画素の画素電極が保持容量配線に導通したとき、保持容量配線と対向電極とが同電位ならば、液晶層に電圧が印加されない。液晶層が負の誘電異方性を有するネマチック液晶材料を含む垂直配向型液晶層である場合、典型的には、液晶表示装置はノーマリーブラックモードで駆動するので、修正された画素は黒表示となり、点欠陥が目立ち難くなる。

【0042】

一方、液晶層が正の誘電異方性を有するネマチック液晶材料を含むツイスト配向型液晶層である場合、典型的には、液晶表示装置はノーマリーホワイトモードで駆動する。この場合、欠陥画素の画素電極を保持容量配線に導通させ、かつ対向電極に供給された電位と異なる電位を保持容量配線に供給することにより、液晶層に所定電圧が印加される。例えば、画素が黒表示となるときの電位を保持容量配線に供給することにより、液晶層に所定電圧（画素が黒表示となるときの電圧）が印加されるので、修正された画素が黒点化されて、点欠陥が目立ち難くなる。

【発明の効果】

【0043】

本発明によれば、AM基板における点欠陥を修正することができる。これにより、製造歩留りを向上させることができる。

【発明を実施するための最良の形態】

【0044】

以下、図面を参照しながら本発明の実施形態を説明するが、本発明は以下の実施形態に限定されない。なお、同族的な構成要素を総括的に表すために、参照符号の英字を省略して、参照符号の数字のみを表記することがある。例えば、第1走査信号線22aおよび第

10

20

30

40

50

2走査信号線22bを総括的に走査信号線22と表記することがある。

【0045】

以下の実施形態に示すAM基板では、一画素を複数に分割した副画素（サブピクセル）が共通の走査信号線およびデータ信号線により駆動され、またデータ信号線が延びる方向に隣接する画素が同じ保持容量（共通）配線を共有する。保持容量（共通）配線上には、絶縁膜を介して、3つ以上に分割された上側保持容量電極が形成されている。2つ以上の上側保持容量電極は、それぞれの接続電極を介して、走査信号線とデータ信号線との交点付近に設けられたTFTに接続されている。また接続電極が接続されていない上側保持容量電極は、副画素を構成する副画素電極と接続されている。

【0046】

上側保持容量電極を複数に分割することにより、上側保持容量電極が保持容量配線、データ信号線または隣接する画素の上側保持容量電極とリークするなどの不良が生じた場合は、リークが生じた上側保持容量電極を電気的に切り離して修正する。また修正によってサブピクセルが無通電化した場合には、接続電極に接続されていない分割電極（上側保持容量電極）にレーザなどを照射することにより、副画素電極と保持容量（共通）配線とを導通させる。これにより、副画素電極に保持容量（共通）配線の電位を与えることができる。保持容量（共通）配線と対向電極とに同電位が与えられているときは、副画素電極と対向電極とに挟まれた液晶層に電圧が印加されない状態となる。ノーマリーブラックモードで駆動する垂直配向型液晶表示装置では、修正された画素は黒表示となり、点欠陥が目立ち難くなる。

10

【0047】

一方、ノーマリーホワイトモードで駆動するツイスト配向型液晶表示装置では、例えば、画素が黒表示となるときの電位を保持容量（共通）配線に供給することにより、液晶層に所定電圧（画素が黒表示となるときの電圧）が印加されるので、修正された画素が黒点化されて、点欠陥が目立ち難くなる。したがって、上記の修正を行うことにより、不良画素を表示品位上問題ないレベルの微小な点欠陥とすることができる、製造歩留りを向上させることができる。

20

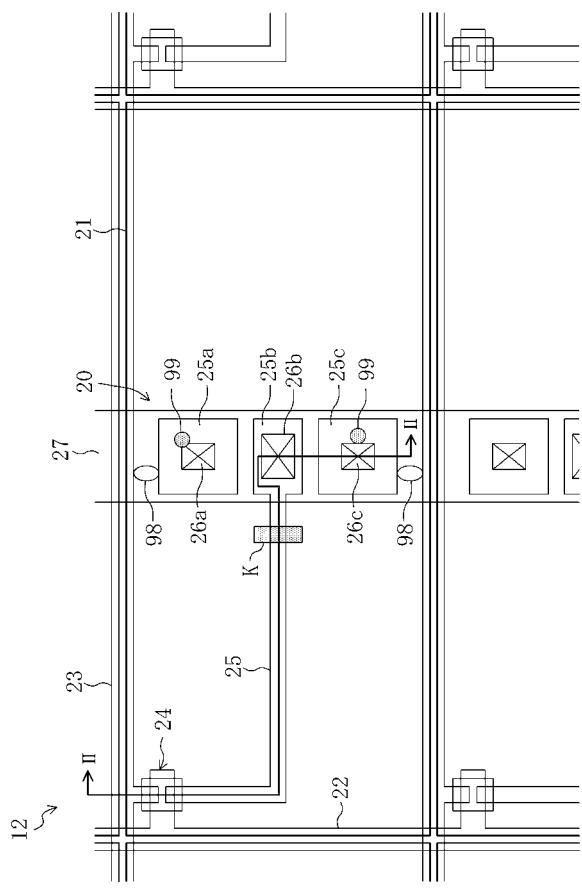

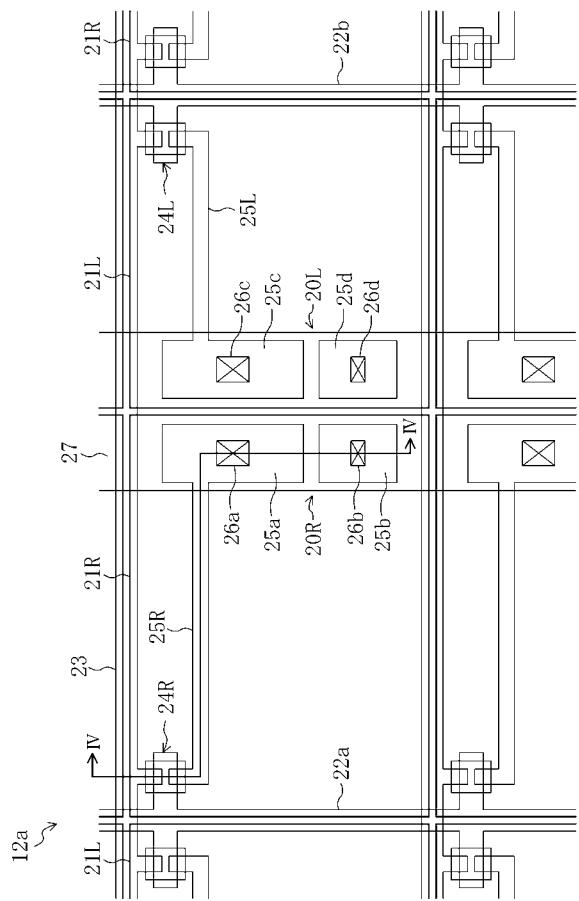

【0048】

（実施形態1）

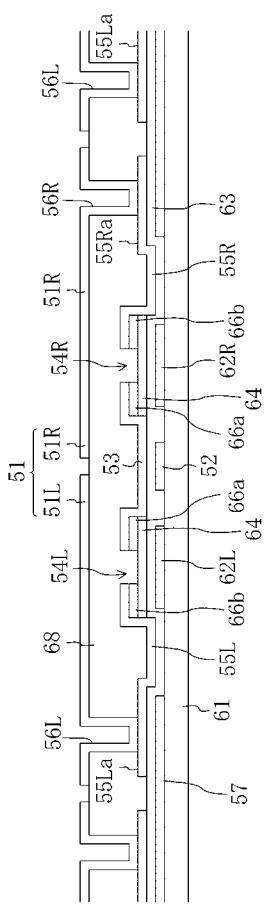

図3は本実施形態のAM基板12aを模式的に示す平面図であり、図4は図3中のIV-IV線断面図である。本実施形態のAM基板12aは、保持容量素子の下側電極として保持容量配線が形成されたCs-on-Common方式である。また本実施形態のAM基板12aは、一画素が2つの副画素に分割され、隣接する画素が保持容量配線を共有する構造を有する。

30

【0049】

本明細書において副画素（subpixel）は表示の最小単位であり、同じ走査信号線に供給される走査信号と、同じデータ信号線に供給されるデータ信号とによって選択され、同じデータ信号が入力される2以上の副画素から1つの画素（pixel）が構成される。さらに、例えばR, G, Bの3つの画素から1つの絵素（picture element）が構成される。画素（または副画素）の領域は、AM型液晶表示装置においては、画素電極（または副画素電極）と、画素電極（または副画素電極）に対向する対向電極とにより規定される。なお、ブラックマトリクスが設けられる構成においては、厳密には、表示すべき状態に応じて電圧が印加される領域のうち、ブラックマトリクスの開口部に対応する領域が画素（または副画素）の領域に対応することになる。

40

【0050】

本実施形態のAM基板12aは、マトリクス状に配列された複数の画素を有しており、行方向に配列された2つの副画素から一画素が構成されている。具体的には、図3に示すように、画素電極が2つの副画素電極21R（第1画素電極）、21L（第2画素電極）に分割されている。これらの副画素電極21R, 21Lの境界付近には、走査信号を供給するための走査信号線22が列方向（図中縦方向）に延びて設けられ、画素電極の周囲には、データ信号を供給するためのデータ信号線23が行方向（図中横方向）に延びて設け

50

られている。また、走査信号線 2 2 とデータ信号線 2 3 との交差部分において、走査信号線 2 2 を平面視において行方向に挟んで配置され、対応する副画素電極 2 1 R , 2 1 L に接続された 2 つのスイッチング素子としての TFT 2 4 R , 2 4 L が設けられている。

【 0 0 5 1 】

TFT 2 4 R , 2 4 L のゲート電極には走査信号線 2 2 が接続され、ゲート電極に入力される走査信号によって、TFT 2 4 R , 2 4 L が駆動制御される。また、TFT 2 4 R , 2 4 L のソース電極 3 6 a にはデータ信号線 2 3 が接続され、TFT 2 4 R , 2 4 L のソース電極 3 6 a にデータ信号が入力される。ドレイン電極 3 6 b は、接続電極 2 5 L , 2 5 R を介して保持容量素子の一方の電極（上側保持容量電極）2 5 a , 2 5 c に接続され、層間絶縁膜 3 8 に形成されたコンタクトホール 2 6 a , 2 6 c を介して副画素電極 2 1 R , 2 1 L に接続されている。 10

【 0 0 5 2 】

図 3 では、保持容量（共通）配線 2 7 の左側にある第 1 画素に含まれる右側の副画素電極 2 1 R と、第 1 画素に行方向（右側）に隣接する第 2 画素に含まれる左側の副画素電極 2 1 L とが示されている。第 1 画素に含まれる副画素電極 2 1 R は、第 1 走査信号線 2 2 a に供給される走査信号と、データ信号線 2 3 に供給されるデータ信号とによって選択される 2 つの副画素電極のうちの右側の副画素電極である。第 2 画素に含まれる副画素電極 2 1 L は、保持容量（共通）配線 2 7 を挟んで、第 1 走査信号線 2 2 a と行方向に隣接する第 2 走査信号線 2 2 b に供給される走査信号と、データ信号線 2 3 に供給されるデータ信号とによって選択される 2 つの副画素電極のうちの左側の副画素電極である。 20

【 0 0 5 3 】

2 つの副画素は、絶縁膜を挟む一対の電極をそれぞれ備えた第 1 保持容量素子 2 0 R および第 2 保持容量素子 2 0 L を有する。第 1 および第 2 保持容量素子 2 0 R , 2 0 L は、保持容量素子の一方の電極（下側保持容量電極）として、透明絶縁性基板（絶縁基板）3 1 上に設けられた保持容量（共通）配線 2 7 を共有する。保持容量（共通）配線 2 7 上には、ゲート絶縁膜 3 3 が形成され、ゲート絶縁膜 3 3 を介して保持容量（共通）配線 2 7 に対向配置された、保持容量素子の他方の電極（上側保持容量電極）が形成されている。保持容量（共通）配線 2 7 に対向する上側保持容量電極は、いうならば 4 分割され、第 1 保持容量素子 2 0 R の上側保持容量電極 2 5 a , 2 5 b および第 2 保持容量素子 2 0 L の上側保持容量電極 2 5 c , 2 5 d に分割されている。これらの上側保持容量電極 2 5 a , 2 5 b , 2 5 c , 2 5 d は保持容量（共通）配線 2 7 のパターンと重なるように配置されている。 30

【 0 0 5 4 】

本実施形態の AM 基板 1 2 a では、各保持容量素子 2 0 R , 2 0 L について 1 つの上側保持容量電極 2 5 a , 2 5 c に接続電極 2 5 R , 2 5 L が接続されている。接続電極 2 5 R , 2 5 L の材料として、典型的には、非透過性材料が用いられるので、接続電極 2 5 R , 2 5 L の形成領域が非透過領域となる。したがって、接続電極 2 5 R , 2 5 L を開口部として利用することが困難であるので、1 つの上側保持容量電極 2 5 a , 2 5 c のみに接続電極 2 5 R , 2 5 L を接続することにより、両方の上側保持容量電極に接続する場合よりも、開口率を高めることができる。但し、接続電極 2 5 R , 2 5 L の領域をリブやスリットなどの領域と重ねることができる場合には、両方の上側保持容量電極に接続電極を接続することが好ましい。 40

【 0 0 5 5 】

図 4 を参照しながら、第 1 画素に含まれる副画素電極 2 1 R の断面構造を説明する。ガラスやプラスチックなどからなる透明絶縁性基板（絶縁基板）3 1 上に、第 1 走査信号線 2 2 a に接続されたゲート電極 3 2 R が設けられている。第 1 走査信号線 2 2 a やゲート電極 3 2 R は、チタン、クロム、アルミニウム、モリブデンなどからなる金属膜や、それらの合金、積層膜から形成される。保持容量素子の下側保持容量電極として機能する保持容量（共通）配線 2 7 は、典型的には、第 1 走査信号線 2 2 a やゲート電極 3 2 R と同一材料から形成される。これらを覆うゲート絶縁膜 3 3 は、窒化シリコンや酸化シリコンな 50

どからなる絶縁膜により形成される。その上には、ゲート電極 32R と重畳するように、アモルファスシリコンやポリシリコンなどからなる高抵抗半導体層 34 と、さらにリンなどの不純物がドープされた  $n^+$  アモルファスシリコンなどからなる低抵抗半導体層とが設けられている。なお、低抵抗半導体層がソース電極 36a およびドレイン電極 36b となる。

#### 【0056】

また、ソース電極 36a と接続するように、データ信号線 23 が形成されている。さらに、ドレイン電極 36b と接続するように、接続電極 25R が設けられ、接続電極 25R は一方の上側保持容量電極 25a に接続されるように延びており、上側保持容量電極 25a は副画素電極 21R とコンタクトホール 26a を介して接続されている。

10

#### 【0057】

他方の上側保持容量電極 25b は、コンタクトホール 26b を介して副画素電極 21R と接続されている。すなわち、2つの上側保持容量電極 25a, 25b は、副画素電極 21R を介して互いに電気的に接続した構成となっている。データ信号線 23、接続電極 25、上側保持容量電極 25a, 25b は、典型的には同一材料から形成され、例えばチタン、クロム、アルミニウム、モリブデンなどからなる金属膜や、それらの合金、積層膜から形成される。画素電極 21R および 21L は、例えば、ITO、IZO、酸化亜鉛、酸化スズなどの透明性を有する導電膜から形成される。コンタクトホール 26a, 26b は、TFT 24R、走査信号線 22a、データ信号線 23 および接続電極 25 の上部を覆うように形成された層間絶縁膜 38 を貫くように形成されている。層間絶縁膜 38 の材料としては、例えば、アクリル樹脂や、窒化シリコン、酸化シリコンなどが挙げられる。

20

#### 【0058】

次に、本実施形態のAM基板 12a による点欠陥の修正工程について説明する。本実施形態のAM基板 12a において、保持容量(共通)配線 27 に対向して設けられた上側保持容量電極 25a ~ 25d は、十分な保持容量を確保するために、できる限り大面積にする必要がある。したがって、互いに行方向に隣接する副画素の上側保持容量電極が近接して形成されるので、互いに行方向に隣接する上側保持容量電極間でリーク不良が生じやすい。また、データ信号線 23 と上側保持容量電極 25a とが膜残りの欠陥などにより短絡するおそれもある。さらに、上側保持容量電極 25a と保持容量配線 27 とがゲート絶縁膜 33 中の導電性異物やピンホールにより短絡するおそれもある。

30

#### 【0059】

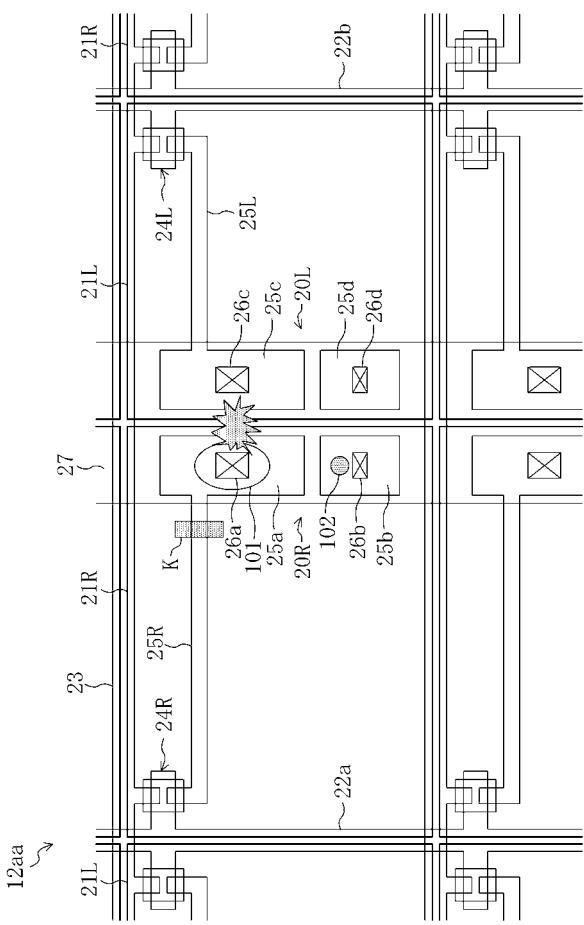

図 5 は、互いに隣接し、接続電極 25R, 25L にそれぞれ接続された上側保持容量電極 25a, 25c 間で短絡が生じた場合の修正工程を模式的に説明するための平面図である。修正前のAM基板 12a a では、上側保持容量電極 25a, 25c 間で、膜残りなどにより短絡が生じ、短絡した上側保持容量電極 25a, 25c およびコンタクトホール 26a, 26c を介して、互いに隣接する副画素電極 21R と副画素電極 21L とが導通しているので、連結欠点になっている。

#### 【0060】

図 6 は、接続電極 25R に接続された上側保持容量電極 25a とデータ信号線 23 とで短絡が生じた場合の修正工程を模式的に説明するための平面図である。修正前のAM基板 12a b では、データ信号線 23 と上側保持容量電極 25a とが膜残りの欠陥などにより短絡して、データ信号線 23 から上側保持容量電極 25a を介して副画素電極 21R にデータ信号が入力されている。

40

#### 【0061】

図 7 は、接続電極 25R に接続された上側保持容量電極 25a と保持容量配線 27 とが短絡した場合の修正工程を模式的に説明するための平面図である。修正前のAM基板 12a c では、上側保持容量電極 25a と保持容量配線 27 とがゲート絶縁膜 33 中の導電性異物やピンホールにより短絡して、短絡した画素が表示画像において点欠陥となっている。

#### 【0062】

50

接続電極 25R に接続された上側保持容量電極 25a が、隣接する上側保持容量電極 25c、データ信号線 23 または保持容量配線 27 に短絡した場合は、短絡した上側保持容量電極 25a に形成されているコンタクトホール 26a 内の電極部分 101 を取り除くことにより、副画素電極 21R および 21L における各短絡を解消することができる。さらに接続電極 25R を切断箇所 K にてレーザなどにより破壊分離すれば、短絡した上側保持容量電極 25a を分離することができるので、TFT24R がオンのときに、TFT24R を介してデータ信号線 23 と保持容量配線 27 がリークするのを防ぐことができる。

#### 【0063】

しかし、このとき、副画素電極 21R も TFT21R から電気的に分離され、無通電状態となるので、他方の上側保持容量電極 25b（但し、コンタクトホール 26b の領域を除く）をレーザ 102 などでメルトすることにより、上側保持容量電極 25b を介して副画素電極 21R と保持容量（共通）配線 27 を導通させる。これにより、副画素電極 21R を保持容量（共通）配線 27 と同じ電位にすることができる。したがって、修正されたこのAM基板 12a を有する液晶表示装置では、副画素電極 21R の領域を黒表示にさせ、微小欠点として修正することができる。

#### 【0064】

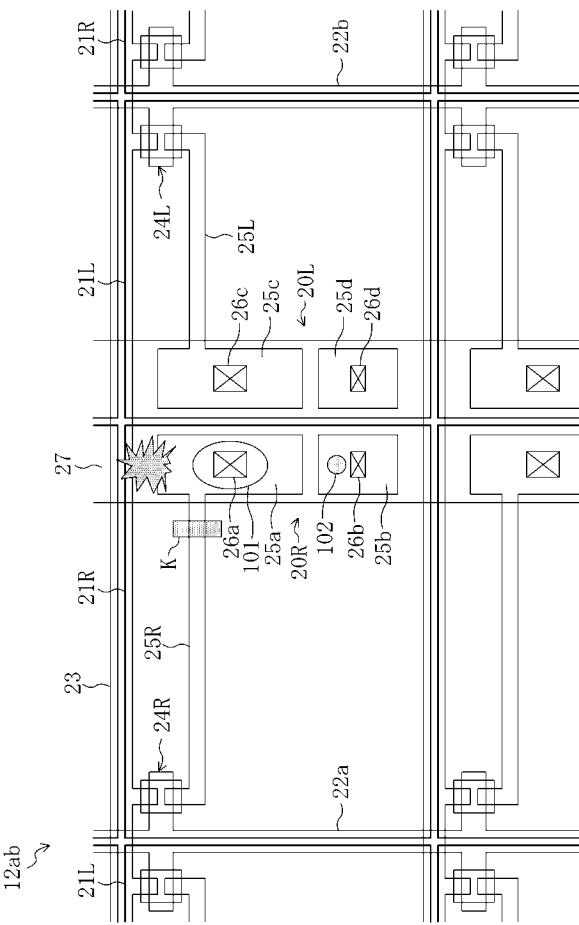

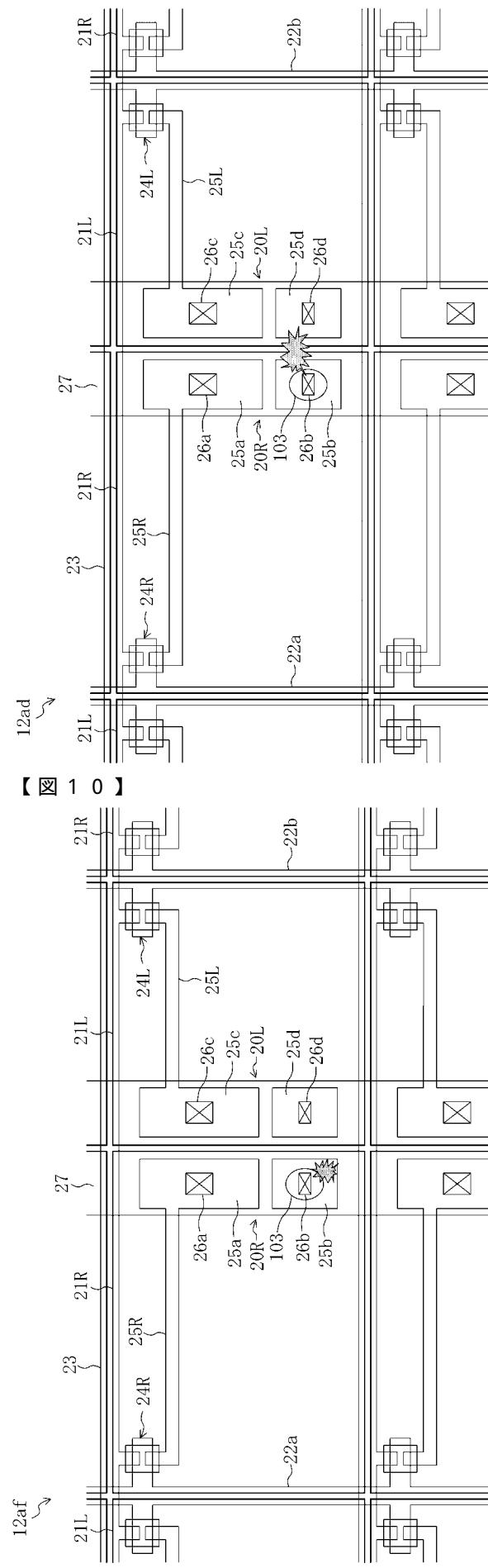

図 8 は、接続電極 25R に接続されていない上側保持容量電極 25b と、これに隣接する上側保持容量電極 25d との間で短絡が生じた場合の修正工程を模式的に説明するための平面図である。修正前のAM基板 12ad では、上側保持容量電極 25b, 25d 間で、膜残りなどにより短絡が生じ、短絡した上側保持容量電極 25b, 25d およびコンタクトホール 26b, 26d を介して、互いに隣接する副画素電極 21R と副画素電極 21L とが導通しているので、連結欠点になっている。

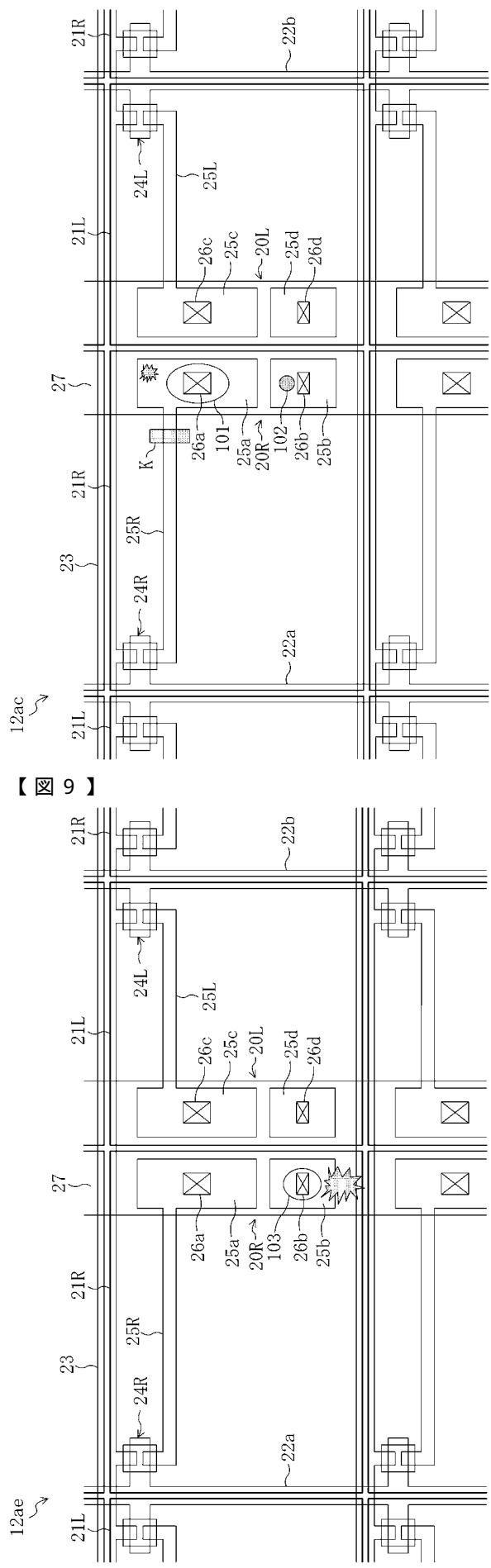

#### 【0065】

図 9 は、接続電極 25R に接続されていない上側保持容量電極 25b とデータ信号線 23 とで短絡が生じた場合の修正工程を模式的に説明するための平面図である。修正前のAM基板 12ae では、データ信号線 23 と上側保持容量電極 25b とが膜残りの欠陥などにより短絡して、データ信号線 23 から上側保持容量電極 25b を介して副画素電極 21R にデータ信号が入力されている。

#### 【0066】

図 10 は、接続電極 25R に接続されていない上側保持容量電極 25b と保持容量配線 27 とが短絡した場合の修正工程を模式的に説明するための平面図である。修正前のAM基板 12af では、上側保持容量電極 25b と保持容量配線 27 とがゲート絶縁膜 33 中の導電性異物やピンホールにより短絡して、短絡した画素が表示画像において点欠陥となっている。

#### 【0067】

接続電極 25R に接続されていない上側保持容量電極 25b が、隣接する上側保持容量電極 25d、データ信号線 23 または保持容量配線 27 に短絡した場合は、短絡した上側保持容量電極 25b に形成されているコンタクトホール 26b 内の電極部分 103 をレーザなどにより取り除く。これにより、短絡した上側保持容量電極 25b を副画素電極 21R から分離することができるので、保持容量配線 27 からの電位が上側保持容量電極 25b を介して副画素電極 21R に与えられるのを防ぐことができる。したがって、副画素を正常に近い状態で駆動させることができる。

#### 【0068】

##### （実施形態 2）

実施形態 1 のAM基板 12a では、接続電極 25R, 25L に接続された上側保持容量電極 25a, 25c と保持容量配線 27 が重なる領域の面積（第1面積）が、接続電極 25R, 25L に接続されていない上側保持容量電極 25b, 25d と保持容量配線 27 が重なる領域の面積（第2面積）よりも大きくなるように設定されている。

#### 【0069】

コンタクトホール 26a, 26c と比較して、コンタクトホール 26b, 26d のほう

10

20

30

40

50

が副画素電極 21R, 21L をカバーレージよく上側保持容量電極 25b, 25d に接続することが難しい場合がある。あるいは上側保持容量電極のアルミニウムなどを含む金属膜と副画素電極 21R, 21L のITOなどの膜との接触抵抗が大きい場合がある。これらの場合、上側保持容量電極 25b, 25d が保持容量素子の電極としての機能を果たさないことがある。そこで、第1面積が第2面積よりも大きくなるように設定することにより、第1面積と第2面積とを足した総面積に対して第1面積の比率が高くなるので、第1面積の比率に応じた大きな保持容量を確保できる。

#### 【0070】

しかし、接続電極 25R, 25L に接続された上側保持容量電極 25a, 25c の短絡 (例えば、保持容量配線 27 との間の短絡) がコンタクトの信頼性よりも懸念される場合は、第1面積を第2面積よりも小さくしてもよい。

10

#### 【0071】

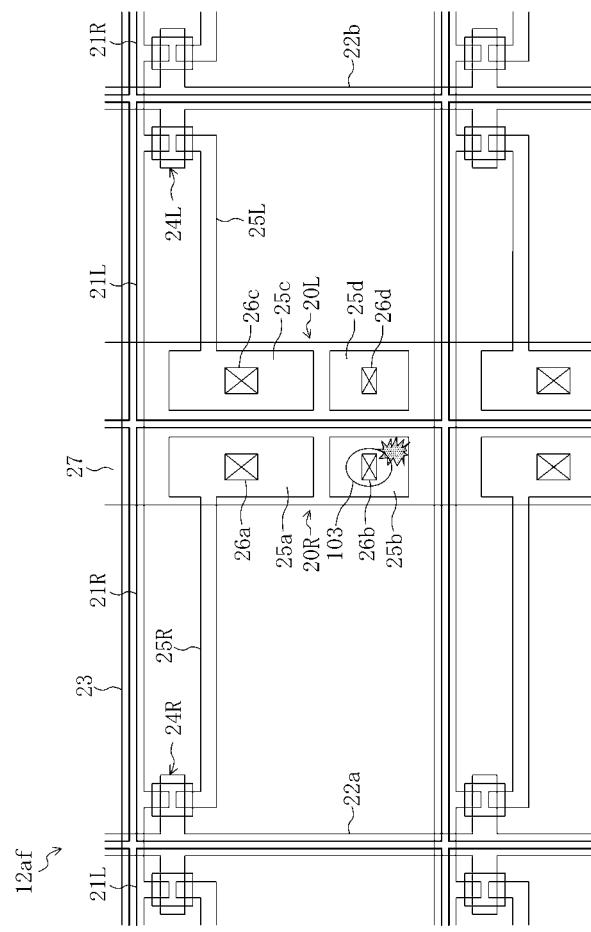

図 11 は、接続電極 25R, 25L に接続された上側保持容量電極 25a, 25c と保持容量配線 27 が重なる領域の面積が、接続電極 25R, 25L に接続されていない上側保持容量電極 25b, 25d と保持容量配線 27 が重なる領域の面積よりも小さくなるように設定された AM 基板 12b を模式的に示す平面図である。なお、実施形態 1 と同一の構成要素には同一の参照符号を付すことにより、同じ参照符号の構成要素についての説明を省略する。

#### 【0072】

本実施形態の AM 基板 12b では、接続電極 25R, 25L に接続された上側保持容量電極 25a, 25c と保持容量配線 27 が重なる領域の面積 (第1面積) が、接続電極 25R, 25L に接続されていない上側保持容量電極 25b, 25d と保持容量配線 27 が重なる領域の面積 (第2面積) よりも小さくなるように設定されているので、接続電極 25R, 25L に接続された上側保持容量電極 25a, 25c が短絡した場合に、第1面積と第2面積とを足した重なり総面積に対して第2面積の比率に応じた大きな保持容量を確保できる。

20

#### 【0073】

##### (実施形態 3)

実施形態 2 の AM 基板 12b では、図 11 に示すように、保持容量配線 27 の左側にある第1画素に含まれる2つの副画素 (左側の副画素は一部のみ図示) のうちの右側の副画素 (第1副画素) と、保持容量配線 27 の右側にある第2画素に含まれる2つの副画素 (右側の副画素は一部のみ図示) のうちの左側の副画素 (第2副画素) とで、上側保持容量電極 25a ~ 25d の配置が左右対称である。言い換えれば、第1副画素における接続電極 25R に接続された上側保持容量電極 25a と、第2副画素における接続電極 25L に接続された上側保持容量電極 25c とが保持容量配線 27 が延びる方向に対して交差する方向に隣接しており、かつ接続電極 25R に接続されていない上側保持容量電極 25c と、接続電極 25L に接続されていない上側保持容量電極 25d とが保持容量配線 27 が延びる方向に対して交差する方向に隣接している。

30

#### 【0074】

しかしながら、本発明において、上側保持容量電極 25a ~ 25d の配置は実施形態 2 に示すものに限定されず、第1副画素における接続電極 25R に接続された上側保持容量電極 25a と、第2副画素における接続電極 25L に接続された上側保持容量電極 25c とが保持容量配線 27 が延びる方向にずれて配置されていてもよい。

40

#### 【0075】

図 12 は、本実施形態の AM 基板 12c を模式的に示す平面図である。本実施形態の AM 基板 12c では、第1副画素における接続電極 25R に接続された上側保持容量電極 25a に対して、第2副画素における接続電極 25L に接続された上側保持容量電極 25c が図面の下側にずれて配置されている。また、第1副画素における接続電極 25R に接続されていない上側保持容量電極 25b に対して、第2副画素における接続電極 25L に接続されていない上側保持容量電極 25d が図面の上側にずれて配置されている。

50

## 【0076】

本実施形態のAM基板12cでは、上側保持容量電極25cが図面の下側にずれて配置されているので、TFT24Lのドレイン電極と上側保持容量電極25cとを接続する接続電極25Lが、第1副画素における接続電極25Rよりも長い。したがって、第1副画素の開口率よりも第2副画素の開口率が低くなるおそれがある。しかし、本実施形態のAM基板12cを動作モードがMVAの液晶表示装置に用いる場合には、スリット（電極層がない部分）の領域や対向基板に形成され、液晶層側に突出したリブ（凸部）の領域に接続電極25Lを配置することによって、接続電極25Lが長くなることによる開口率の低下を抑えることができる。

## 【0077】

10

実施形態2の場合は、図11に示すように、接続電極25R, 25Lに接続された上側保持容量電極25a, 25cが互いに近接しているので、上側保持容量電極25a, 25c間でリークが生じるおそれがある。接続電極25R, 25Lに接続された上側保持容量電極25a, 25cの短絡が生じた場合、どちらか一方の副画素を修正して、黒点化する必要がある。

## 【0078】

本実施形態のAM基板12cでは、接続電極25R, 25Lに接続された上側保持容量電極25a, 25cが、実施形態2の場合よりも、互いに離れているので、上側保持容量電極25a, 25c同士が短絡する可能性が低い。接続電極25R, 25Lに接続された上側保持容量電極25a, 25cが、接続電極25R, 25Lに接続されていない上側保持容量電極25b, 25dと短絡した場合には、接続電極25R, 25Lに接続されていない上側保持容量電極25b, 25dを分離することにより、上側保持容量電極25b, 25dによる保持容量が減少するものの、正常に近い駆動で副画素を表示することが可能となる。

20

## 【0079】

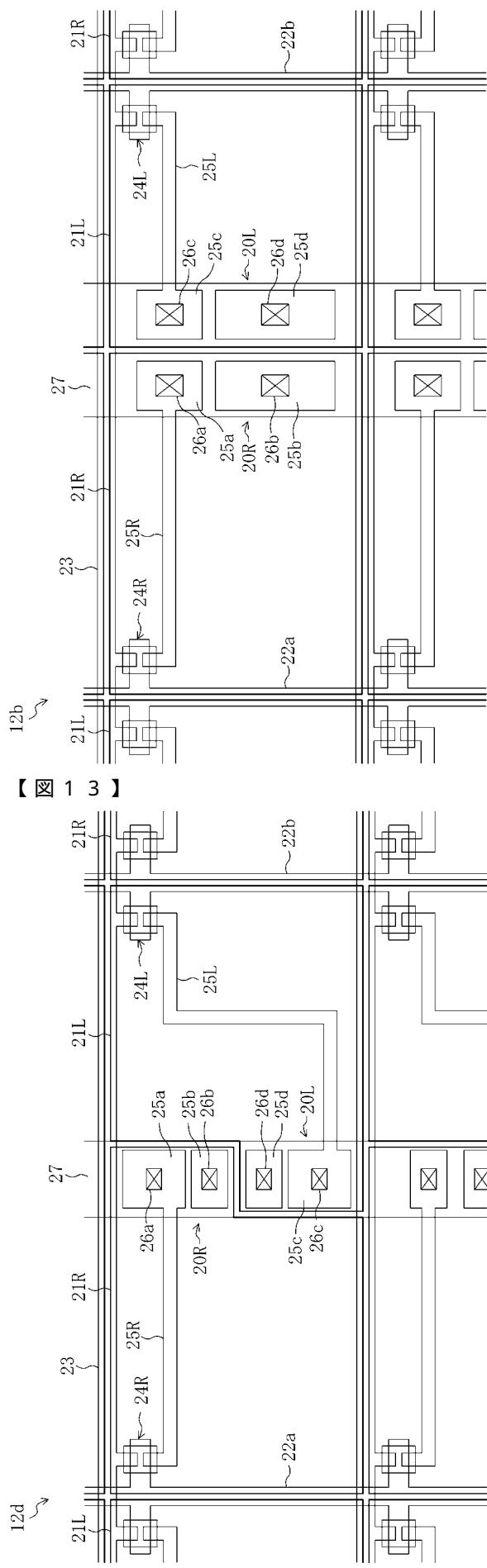

## (実施形態4)

実施形態1～3では、第1副画素における上側保持容量電極25a, 25bと、第2副画素における上側保持容量電極25c, 25dとが保持容量配線27が延びる方向に対して交差する方向に隣接しているが、本発明はこれに限定されない。例えば、保持容量配線27が延びる方向に上側保持容量電極25a～25dが配置されていてもよい。

30

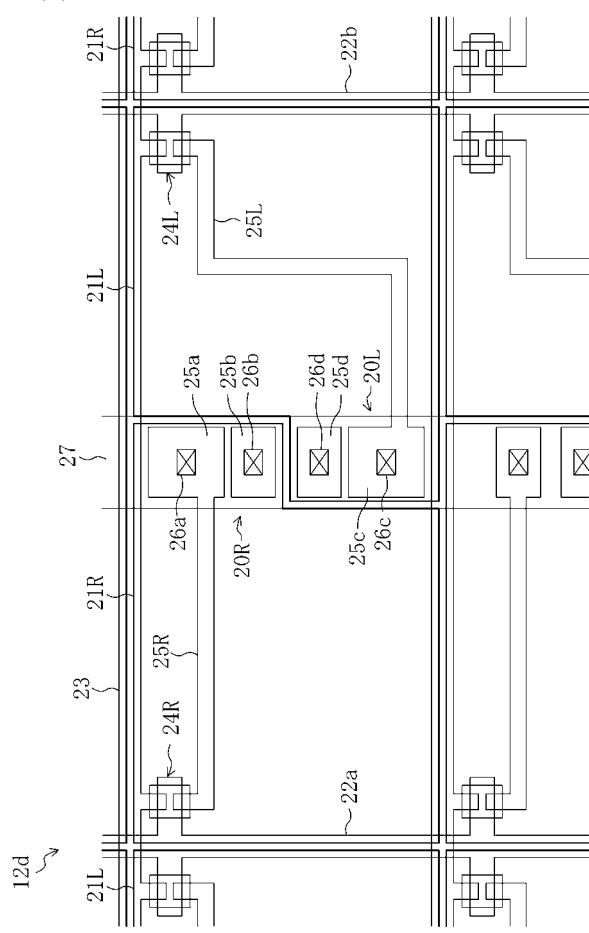

## 【0080】

図13は、本実施形態のAM基板12dを模式的に示す平面図である。本実施形態のAM基板12dでは、第1副画素に含まれる2つの上側保持容量電極25a, 25bが、第2副画素に含まれる2つの上側保持容量電極25c, 25dよりも、図面において上側に配置されている。また、第1副画素における接続電極25Rに接続された上側保持容量電極25aが、接続電極25Rに接続されていない上側保持容量電極25bよりも、図面において上側に配置されている。一方、第2副画素における接続電極25Lに接続された上側保持容量電極25cが、接続電極25Lに接続されていない上側保持容量電極25dよりも、図面において下側に配置されている。

## 【0081】

40

図12に示すように、上側保持容量電極25a～25dを保持容量配線27が延びる方向に配置することにより、保持容量配線27の幅を狭くすることができるので、副画素の開口率を向上させることができる。また、接続電極25Rに接続された上側保持容量電極25aと、接続電極25Lに接続された上側保持容量電極25cとの間に上側保持容量電極25b, 25dが介在しているので、両電極25a, 25c間の短絡を防ぐことができる。第1副画素の上側保持容量電極25bと第2副画素の上側保持容量電極25dとが短絡した場合には、一方の上側保持容量電極を分離することにより、副画素を正常に近い駆動で表示することが可能となる。

## 【0082】

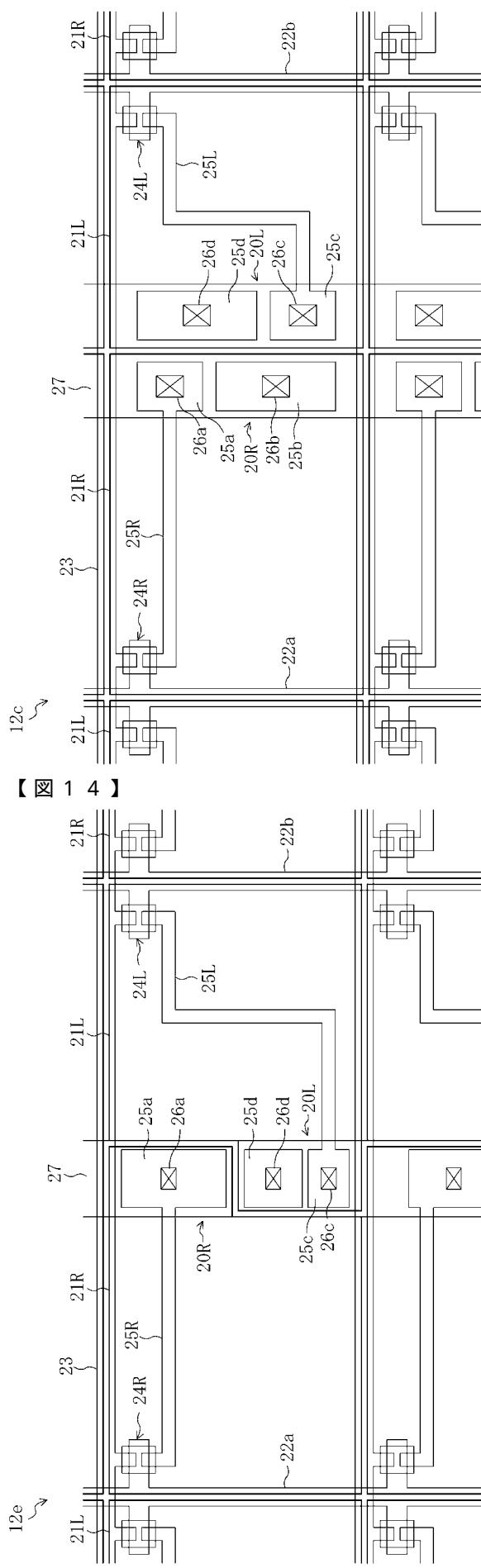

## (実施形態5)

50

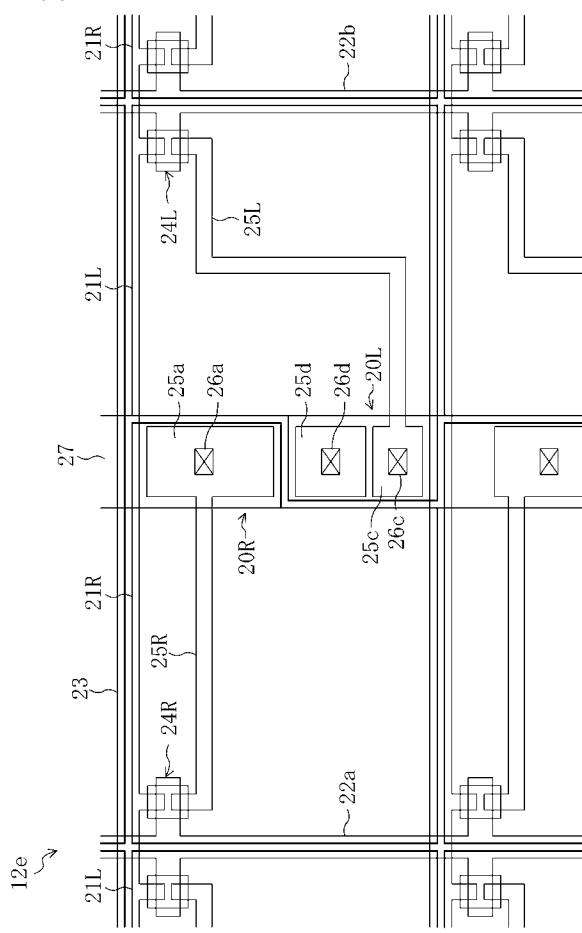

実施形態 1 ~ 4 では、第 1 副画素および第 2 副画素のそれぞれに 2 つの上側保持容量電極 25a ~ 25d が設けられているが、互いに隣接する 2 つの副画素のうち少なくとも一方の副画素について上側保持容量電極が 2 つ以上に分割されていてもよい。

【 0 0 8 3 】

図 14 は、本実施形態の AM 基板 12e を模式的に示す平面図である。本実施形態の AM 基板 12e は、第 2 副画素が 2 つの上側保持容量電極 25c, 25d を有しているが、第 1 副画素が接続電極 25R に接続された 1 つの上側保持容量電極 25a のみを有している。上側保持容量電極を 2 つ以上に分割すると、上側保持容量電極を分割しない場合に比して、その副画素の保持容量が低下する。したがって、上側保持容量電極の短絡が生じ易い副画素についてのみ上側保持容量電極を分割することにより、隣接する他方の副画素の保持容量が低下するのを抑えることができる。

【 0 0 8 4 】

( 実施形態 6 )

上記各実施形態では、上側保持容量電極同士が短絡した場合に、短絡した上側保持容量電極に形成されているコンタクトホール内の電極部分を取り除くことにより、短絡を解消するものなどを例示したが、本発明は、以下のような手段によって短絡した短絡部を除去することにより、短絡を解消してもよい。

【 0 0 8 5 】

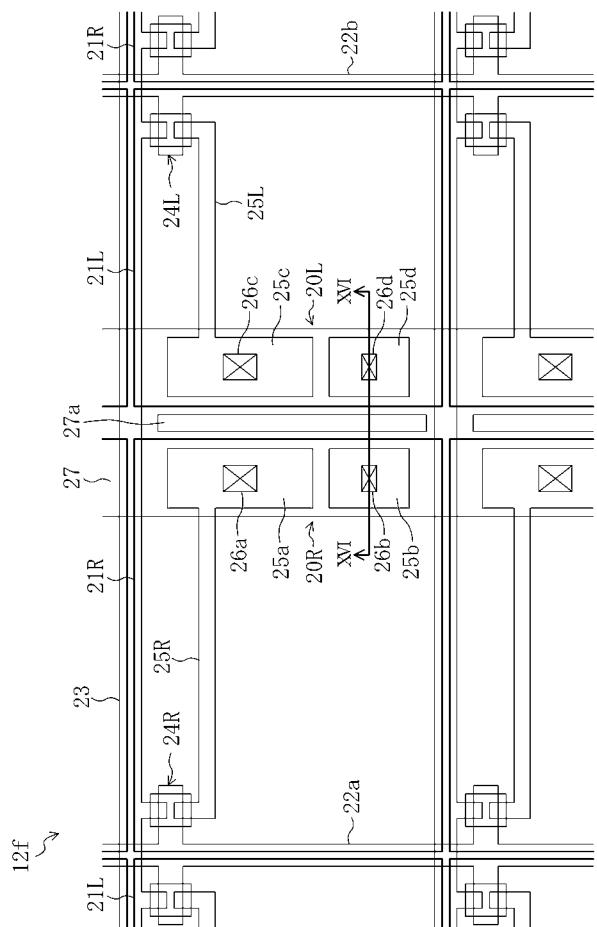

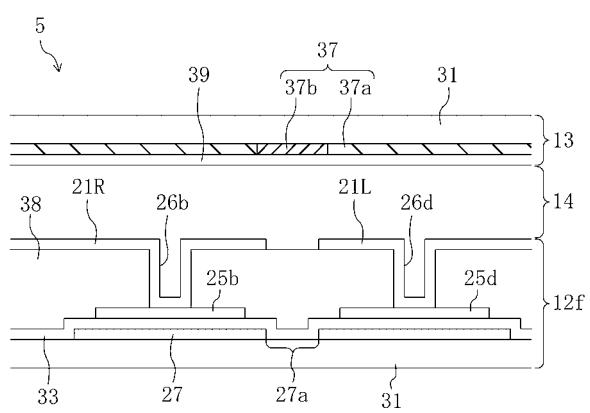

図 15 は、本実施形態の AM 基板 12f を模式的に示す平面図であり、図 16 は、図 15 中の XVI - XVI 線に沿った本実施形態の液晶表示パネル 5 を模式的に示す断面図である。

【 0 0 8 6 】

液晶表示パネル 5 は、図 16 に示すように、互いに対向して配置される AM 基板 12f および対向基板 13 と、それら両基板 12f および 13 の間に設けられた液晶層 14 とを備えている。

【 0 0 8 7 】

AM 基板 12f では、各保持容量配線 7 が、上側保持容量電極 25a および 25b と上側保持容量電極 25c および 25d との間で開口したスリット部 27a を有している。その他の構成および効果については、上記実施形態 1 で説明した AM 基板 12a と同様であるので、その説明を省略する。なお、スリット部 27a のパターン形状は、図 15 に示したものに特に限定されることなく、上側保持容量電極 25a ~ 25d や保持容量配線 27 の形状に応じて、適宜調整されるものである。

【 0 0 8 8 】

また、対向基板 13 は、基板 31 上に、カラーフィルタ層 37、対向電極 39 および配向膜（不図示）などが順に積層された多層積層構造になっている。

【 0 0 8 9 】

カラーフィルタ層 37 は、AM 基板 12f の各画素に対応してマトリクス状に設けられた R、G および B のうちのいずれか 1 つの着色層 37a と、各着色層 37a の間に設けられたブラックマトリクス 37b とを備えている。また、このブラックマトリクス 37b は、図 16 に示すように、AM 基板 12f に設けられたスリット部 27a と重なるように配置されている。これにより、ノーマリー ホワイトモードの液晶表示装置では、黒表示時にスリット部 27a からの光漏れを抑制することができる。

【 0 0 9 0 】

次に、上記構成の液晶表示パネル 5 の製造方法について説明する。液晶表示パネル 5 は、以下に説明する AM 基板作製工程、対向基板作製工程および液晶表示パネル作製工程を経て製造される。また、AM 基板作製工程および液晶表示パネル作製工程の少なくとも一方の後に検査工程を行い、検査工程で画素欠陥が検出された場合には、検査工程の後に画素欠陥を修正する工程が追加される。

【 0 0 9 1 】

以下に、AM 基板作製工程について、説明する。

【 0 0 9 2 】

10

20

30

40

50

まず、ガラス、プラスチックなどの基板31上の基板全体に、チタン、クロム、アルミニウム、モリブデン、タンタル、タンゲステン、銅などの金属膜、それらの合金膜、または、それらの積層膜（厚さ1000～3000）をスパッタリング法により成膜し、その後、フォトリソグラフィー技術（Photo Engraving Process、以下、「EEP技術」と称する）によりパターン形成して、走査信号線22、ゲート電極32Rおよび保持容量配線27を形成する。

【0093】

次いで、走査信号線22などが形成された基板全体に、CVD（Chemical Vapor Deposition）法により窒化シリコンや酸化シリコンなどの無機絶縁膜（厚さ3000～5000程度）を成膜し、ゲート絶縁膜33を形成する。

10

【0094】

続いて、ゲート絶縁膜33上の基板全体に、CVD法により真性アモルファスシリコン膜（厚さ1000～3000）と、リンがドープされたn+アモルファスシリコン膜（厚さ400～700）とを連続して成膜し、その後、EEP技術によりゲート電極32R上に島状にパターン形成して、真性アモルファスシリコン層とn+アモルファスシリコン層からなるシリコン積層体を形成する。

【0095】

続いて、シリコン積層体が形成された基板全体に、チタン、クロム、アルミニウム、モリブデン、タンタル、タンゲステン、銅などの金属膜、それらの合金膜、または、それらの積層膜（厚さ1000～3000）をスパッタリング法により成膜し、その後、EEP技術によりパターン形成して、データ信号線23、接続電極25Rおよび25L、並びに上側保持容量電極25a～25dを形成する（保持容量電極形成工程）。

20

【0096】

さらに、データ信号線23、接続電極25Rおよび25Lをマスクとして、シリコン積層体を構成するn+アモルファスシリコン層をエッチング除去して、チャネル部を形成して、ソース電極36aおよびドレイン電極36bを有する半導体層を形成する（チャネル部形成工程）。

【0097】

ここで、半導体層は、上記のようにアモルファスシリコン膜により形成させてもよいが、ポリシリコン膜を成膜させてもよく、また、アモルファスシリコン膜およびポリシリコン膜にレーザアニール処理を行って結晶性を向上させてもよい。これにより、半導体層内の電子の移動速度が速くなり、TFT24の特性を向上させることができる。

30

【0098】

次いで、データ信号線23などが形成された基板全体に、CVD法により窒化シリコンや酸化シリコンなどの無機絶縁膜（厚さ2000～5000）、またはダイコート（塗布）法により、感光性アクリル樹脂を（厚さ2μm～4μm）を成膜して、層間絶縁膜38を形成する。

【0099】

その後、層間絶縁膜38の上側保持容量電極25a～25dに対応する部分をそれぞれエッチング除去して、コンタクトホール26a～26dを形成する。

40

【0100】

続いて、コンタクトホール26a～26dが形成された層間絶縁膜38上の基板全体に、ITO（Indium Tin Oxide）、IZO（Indium Zinc Oxide）、酸化亜鉛、酸化スズなどからなる透明導電膜（厚さ1000～2000）をスパッタリング法により成膜し、その後、EEP技術によりパターン形成して、画素電極21Rおよび21Lを形成する。

【0101】

最後に、画素電極21Rおよび21L上の基板全体に、ポリイミド樹脂を厚さ500～1000で印刷し、その後、焼成して、回転布にて1方向にラビング処理を行って、配向膜を形成する。

50

## 【0102】

以上のようにして、AM基板12fが作製（製造）される。

## 【0103】

以下に、対向基板作製工程について、説明する。

## 【0104】

まず、ガラス、プラスチックなどの基板31上の基板全体に、クロム薄膜、または黒色顔料を含有する樹脂を成膜した後、EEP技術によりパターン形成して、ブラックマトリクス37bを形成する。

## 【0105】

次いで、ブラックマトリクスの間のそれぞれに、顔料分散法などを用いて、赤、緑および青のいずれの着色層37a（厚さ2μm程度）をパターン形成してカラーフィルタ層37を形成する。

## 【0106】

続いて、カラーフィルタ層37上の基板全体に、ITO、IZO、酸化亜鉛、酸化スズなどからなる透明導電膜（厚さ1000程度）を成膜して、対向電極39を形成する。

## 【0107】

最後に、対向電極39上の基板全体に、ポリイミド樹脂を厚さ500～1000で印刷し、その後、焼成して、回転布にて1方向にラビング処理を行って、配向膜を形成する。

## 【0108】

上記のようにして、対向基板13を作製することができる。

## 【0109】

<液晶表示パネル作製工程>

以下に、液晶表示パネル作製工程について、説明する。

## 【0110】

まず、上述のようにして作製されたAM基板12fおよび対向基板13のうちの一方に、スクリーン印刷により、熱硬化性エポキシ樹脂などからなるシール材料を液晶注入口の部分を欠いた棒状パターンに塗布し、他方の基板に液晶層14の厚さに相当する直径を持ち、プラスチックまたはシリカからなる球状のスペーサーを散布する。

## 【0111】

次いで、AM基板12fと対向基板13とを貼り合わせ、シール材料を硬化させて、空の液晶表示パネルを作製する。

## 【0112】

最後に、空の液晶表示パネルに、減圧法により液晶材料を注入した後、液晶注入口にUV硬化樹脂を塗布し、UV照射により、液晶材料を封止する。これによって、液晶層14が形成される。

## 【0113】

以上のようにして、液晶表示パネル5が作製（製造）される。

## 【0114】

以下に、検査工程および欠陥修正工程について、説明する。

## 【0115】

まず、AM基板作製工程の後（配向膜の形成前）に、検査工程（短絡部検出工程）を行う場合について、説明する。

## 【0116】

この短絡部検出工程では、AM基板作製工程で作製されたAM基板12fに対して、外観検査や電気光学検査などを行うことにより、短絡が発生した位置（短絡部）を検出する。ここで、外観検査とは、CCDカメラなどにより、配線パターンを光学的に検査するものであり、電気光学検査とは、アクティブマトリクス基板に対向するようにモジュレータ（電気光学素子）を設置した後、アクティブマトリクス基板とモジュレータとの間に電圧を印加させると共に光を入射させて、その光の輝度の変化をCCDカメラで捉えることで

10

20

30

40

50

配線パターンを電気光学的に検査するものである。

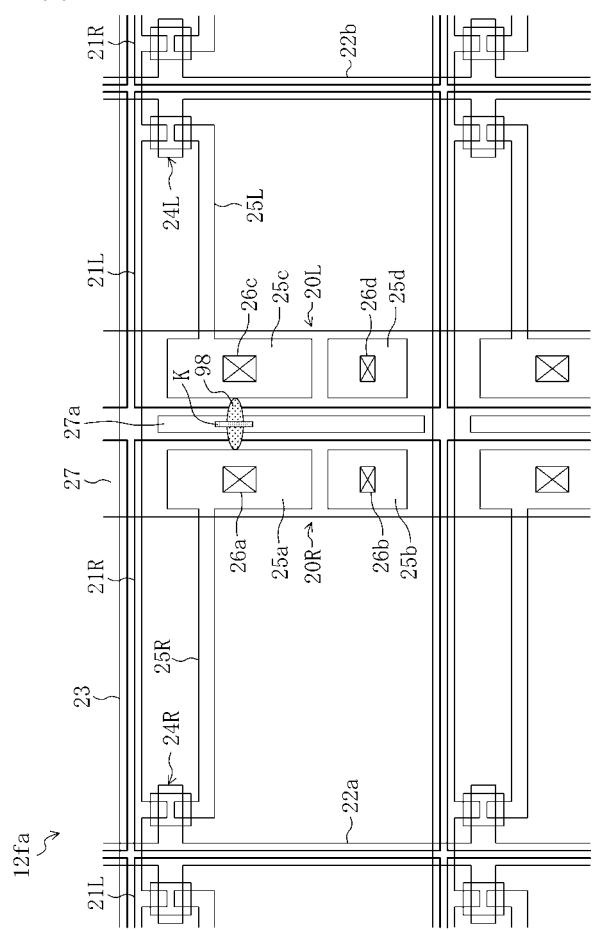

【0117】

続いて、短絡部が検出されたAM基板12fについて、短絡部を除去する欠陥修正を行う。本実施形態では、AM基板12faの上側保持容量電極25aおよび25cの間で短絡が発生した場合の短絡の修正方法について、図17を用いて説明する。

【0118】

具体的には、短絡部である膜残り98に対してスリット部27aを介してレーザを照射することにより、短絡した上側保持容量電極25aおよび25cを分離する。これにより、分離された上側保持容量電極25aおよび25cは、正常な画素における上側保持容量電極25aおよび25cと同等に機能することになる。

10

【0119】

ここで、膜残り98の切断には、例えば、YAG (Yttrium Aluminium Garnet) レーザの第4高調波 (波長266nm) が用いられる。これによれば、レーザ照射による短絡部の切断を精度よく行うことができる。

【0120】

また、スリット部27aの幅は、5μm以上であることが好ましく、スリット部27aの面積としては、25μm<sup>2</sup>以上であることが好ましい。なお、スリット部27aの幅とは、データ信号線23の延びる方向のスリット部27aの長さである。これにより、YAG レーザによって切断加工する場合のレーザ照射領域を確保することができる。さらに、レーザ照射時のYAG レーザの照射ビーム径の広がり、レーザ照射時のアライメントなどを考慮すると、スリット部27aの幅は、10μm以上であることが好ましく、スリット部27aの面積としては、100μm<sup>2</sup>以上であることが好ましい。

20

【0121】

なお、上記検査工程および欠陥修正工程は、画素電極21Rおよび21Lを形成した後の他に、上側保持容量電極25a～25dを形成する保持容量電極形成工程の後、または、チャネル部を形成するチャネル部形成工程の後に行ってもよい。これによれば、製造工程のより初期の段階で画素欠陥を修正することができ、AM基板および液晶表示パネルの製造歩留りをより向上させることができる

次に、液晶表示パネル作製工程の後に、検査工程（短絡部検出工程）を行う場合について、説明する。

30

【0122】

この短絡部検出工程では、液晶表示パネル作製工程で作製された液晶表示パネル5に対して、点灯検査を行うことにより、短絡部を検出する。具体的には、例えば、各走査信号線22にバイアス電圧-10V、周期16.7ms、パルス幅50μsecの+15Vのパルス電圧のゲート検査信号を入力して全てのTFT24をオン状態にする。さらに、各データ信号線23に16.7ms毎に極性が反転する±2Vの電位のソース検査信号を入力して、各TFT24のソース電極36aおよびドレイン電極36bを介して画素電極21に±2Vに対応した電荷を書き込む。同時に、対向電極39および保持容量配線27に直流で-1Vの電位の対向電極検査信号を入力する。このとき、画素電極21Rおよび21Lと対向電極39との間で構成される液晶容量、および保持容量配線27と上側保持容量電極25a～25dとの間で構成される保持容量素子に電圧が印加され、その画素電極21Rおよび21Lで構成する画素が点灯状態になる。そして、隣り合った画素の各上側保持容量電極の間（例えば、25aおよび25cの間）で短絡が発生した箇所では、その画素電極21Lおよび21Rが導通して、連結欠点となる。これにより、短絡部の位置が検出される。

40

【0123】

続いて、短絡部が検出されたAM基板12fについて、短絡部を除去する欠陥修正を行う。具体的な修正方法については、上述したAM基板12fでの修正方法と実質的に同じであるので詳細な説明を省略する。なお、AM基板12fでの修正の場合には、AM基板12fの表面および裏面の両方からレーザ照射が可能であったが、液晶表示パネル5での

50

修正の場合には、AM基板12fの基板側（裏面）からレーザ照射を行うことになる。

【0124】

以上説明したように、本実施形態のAM基板12fによれば、上側保持容量電極25aおよび25c、並びに上側保持容量電極25bおよび25dの各間において短絡が発生した場合には、スリット部27aを介して、短絡部である膜残り98に対してレーザ照射を行うことにより、画素欠陥を容易に修正することができ、AM基板および液晶表示パネルの製造歩留りを向上させることができる。

【0125】

また、上側保持容量電極25a～25d上の膜残り98が、アモルファスシリコン膜などの高抵抗半導体膜のみにより形成されている場合には、保持容量配線27にスリット部27aが設けられているので、保持容量配線27に与えられる電位により、その膜残り98がチャネル化し難くなり、上記のようなレーザ修正を行わずとも連結欠点の発生を抑制することができる。これとは反対に、保持容量配線27にスリット部27aが設けられない場合には、保持容量配線27がゲート電極として機能するとともに、各上側保持容量電極がソース電極およびドレイン電極としてそれぞれ機能することにより、高抵抗半導体膜の膜残り98がチャネル化し、各上側保持容量電極の間が導通することになる。

【0126】

（実施形態7）

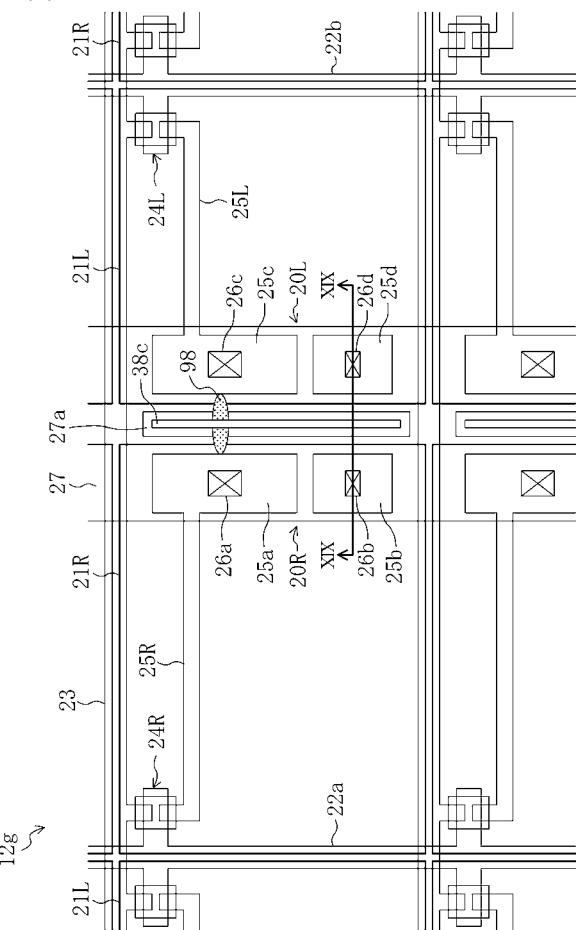

図18は、本実施形態のAM基板12gを模式的に示す平面図であり、図19は図18中のXIX-XIX線断面図である。

【0127】

このAM基板12gでは、図19に示すように、層間絶縁膜38が下層の第1層間絶縁膜38aと上層の第2層間絶縁膜38bとの2層構造となっており、その層間絶縁膜38が保持容量配線27のスリット部27aと重なるように開口したスリット部38cを有している。その他の構成および効果については、上記実施形態1で説明したAM基板12aと同様であるので、その説明を省略する。

【0128】

第1層間絶縁膜38aは、CVD法により窒化シリコンや酸化シリコンなどの無機絶縁膜（厚さ2000～5000）を成膜して形成され、第2層間絶縁膜は、ダイコート（塗布）法により、感光性アクリル樹脂を（厚さ2μm～4μm）を成膜して形成される。

【0129】

スリット部38cは、層間絶縁膜38に、上側保持容量電極25a～25dに対応するコンタクトホール26a～26dを形成する際に、同時に形成される。具体的には、まず、第2層間絶縁膜38を構成する感光性アクリル樹脂をパターニングして、続いて、そのパターニングされた感光性アクリル樹脂をマスクとして、第1層間絶縁膜を構成する無機絶縁膜をドライエッチングすることにより、コンタクトホール26a～26dおよびスリット部38cを有する層間絶縁膜38が形成される。

【0130】

また、コンタクトホール26a～26dなどを形成する上記エッチング工程において、上側保持容量電極25a～25dの間に発生した膜残り98を除去することもできる。これによれば、レーザ照射による短絡部の切断を行うことなく、通常のエッチングによって短絡部を除去することができる。

【0131】

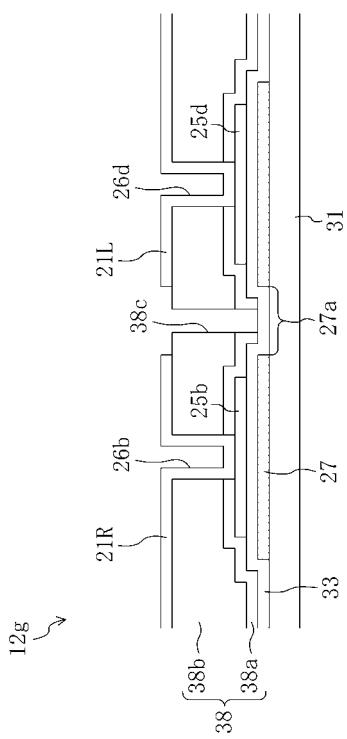

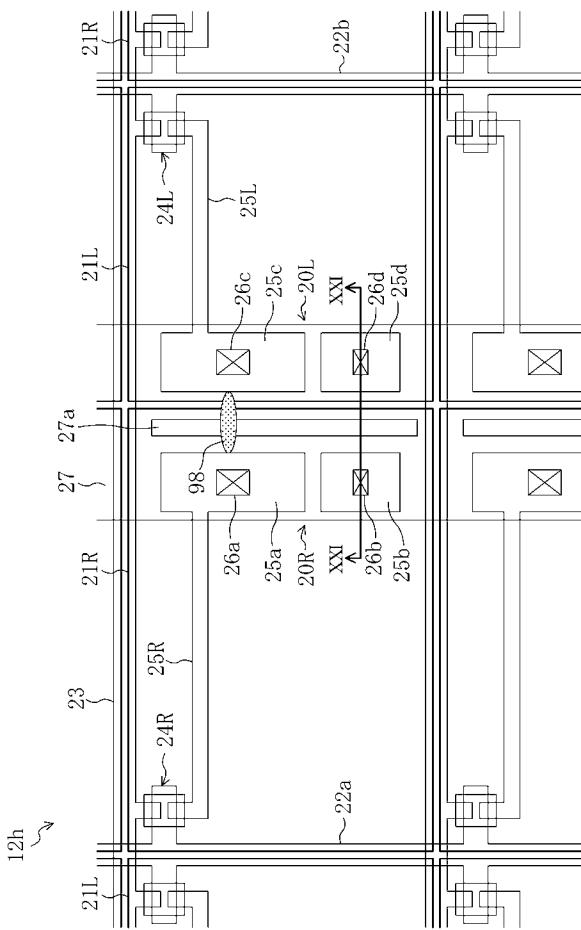

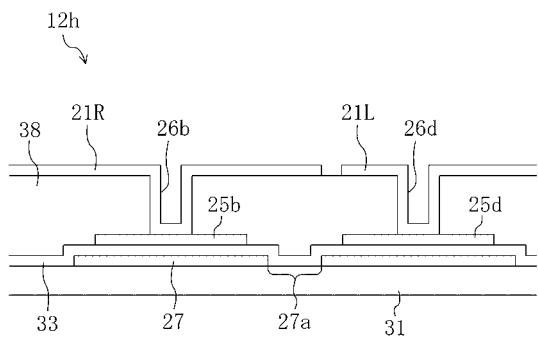

（実施形態8）

図20は、本実施形態のAM基板12hを模式的に示す平面図であり、図21は図20中のXXI-XXI線断面図である。

【0132】

このAM基板12hでは、図21に示すように、副画素電極21Rが保持容量配線27のスリット27aに重なるように配置されている。その他の構成および効果については、

10

20

30

40

50

上記実施形態 1 で説明した A M 基板 1 2 a と同様であるので、その説明を省略する。

【 0 1 3 3 】

この A M 基板 1 2 h によれば、副画素電極 2 1 R がスリット 2 7 a に重なっているので、レーザ照射を A M 基板 1 2 h の基板側（裏面）から行うことになる。また、ノーマリーホワイトモードの液晶表示装置に適用した場合に、黒表示時の光漏れを抑制することができるので、表示品位の低下を抑え、かつ開口率の低下を抑制することができる。

【 0 1 3 4 】

（実施形態 9 ）

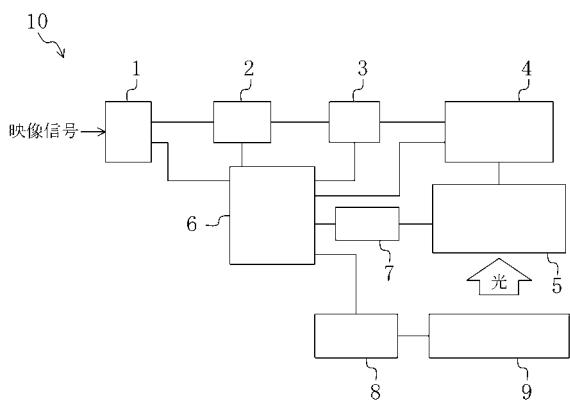

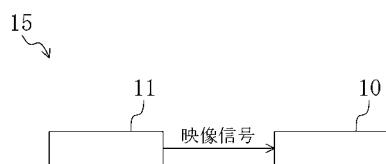

図 2 2 は、本実施形態のテレビジョン装置 1 5 を示すブロック図である。

【 0 1 3 5 】

テレビジョン装置 1 5 は、図 2 2 に示すように、テレビジョン放送を受信して映像信号を出力するチューナ部 1 1 と、チューナ部 1 1 から供給される映像信号に基づいて、画像を表示する液晶表示装置 1 0 とを備えている。

【 0 1 3 6 】

図 2 3 は、本実施形態の液晶表示装置 1 0 を示すブロック図である。

【 0 1 3 7 】

液晶表示装置 1 0 は、図 2 3 に示すように、チューナ部 1 1 などから供給される映像信号を輝度信号および色信号に分離するための Y / C 分離回路 1 と、輝度信号および色信号を光の 3 原色である R、G および B のアナログ R G B 信号に変換するためのビデオクロマ回路 2 と、アナログ R G B 信号をデジタル R G B 信号に変換するための A / D コンバータ 3 と、デジタル R G B 信号が入力される液晶コントローラ 4 と、液晶コントローラ 4 からのデジタル R G B 信号が所定のタイミングで入力され、実質的に画像を表示する上記各実施形態で説明した A M 基板 1 2 を備えた液晶表示パネル 5 と、液晶表示パネル 5 に階調電圧を供給するための階調回路 7 と、液晶表示パネル 5 に光を供給するためのバックライト 9 と、バックライト 9 を駆動させるためのバックライト駆動回路 8 と、上記構成のシステム全体を制御するためのマイコン 6 とを備えている。

【 0 1 3 8 】

なお、Y / C 分離回路 1 に供給される映像信号としては、上記のようなテレビジョン放送に基づく映像信号の他に、カメラにより撮像された映像信号、インターネット回線を介して供給される映像信号など、様々な映像信号を利用することができる。

【 0 1 3 9 】

上記構成のテレビジョン装置 1 5 および液晶表示装置 1 0 は、画素欠陥を容易に修正され A M 基板を備えているので、製造歩留りの向上を図ることができる。

【 0 1 4 0 】

以上、本発明の好ましい実施形態について説明したが、本発明の技術的範囲は上記実施形態に記載の範囲に限定されない。上記実施形態が例示であり、それらの各構成要素や各処理プロセスの組合せに、さらにいろいろな変形例が可能のこと、またこうした変形例も本発明の範囲にあることは当業者に理解されるところである。

【 産業上の利用可能性 】

【 0 1 4 1 】

本発明の A M 基板は、液晶表示装置、無機または有機 E L 表示装置などに利用することができる。また本発明の液晶表示装置は各種の電気機器に利用することができる。例えば、携帯電話機、P D A ( Personal Digital Assistance ) 、パーソナルコンピュータ、薄型テレビ、医療用ディスプレイ、カーナビゲーションシステム、アミューズメント機器などに利用することができる。

【 図面の簡単な説明 】

【 0 1 4 2 】

【 図 1 】本発明の A M 基板 1 2 の一態様を模式的に示す平面図である。

【 図 2 】図 1 中の II - II 線断面図である。

【 図 3 】実施形態 1 の A M 基板 1 2 a を模式的に示す平面図である。

10

20

30

40

50

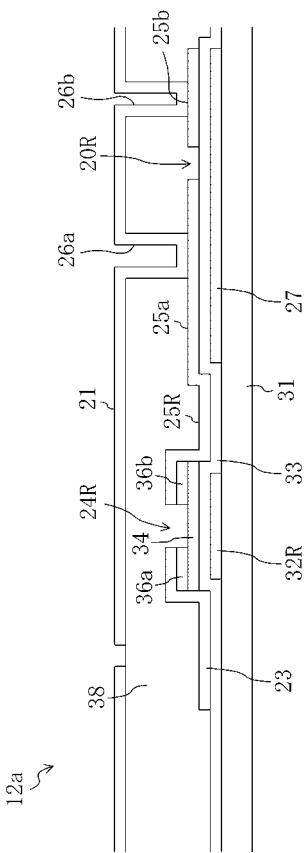

【図4】図3中のIV - IV線断面図である。

【図5】上側保持容量電極25a, 25c間で短絡が生じた場合の修正工程を模式的に説明するための平面図である。

【図6】上側保持容量電極25aとデータ信号線23とで短絡が生じた場合の修正工程を模式的に説明するための平面図である。

【図7】上側保持容量電極25aと保持容量配線27とが短絡した場合の修正工程を模式的に説明するための平面図である。

【図8】上側保持容量電極25bと上側保持容量電極25dとの間で短絡が生じた場合の修正工程を模式的に説明するための平面図である。

【図9】上側保持容量電極25bとデータ信号線23とで短絡が生じた場合の修正工程を模式的に説明するための平面図である。 10

【図10】上側保持容量電極25bと保持容量配線27とが短絡した場合の修正工程を模式的に説明するための平面図である。

【図11】上側保持容量電極25a, 25cと保持容量配線27が重なる領域の面積が、上側保持容量電極25b, 25dと保持容量配線27が重なる領域の面積よりも小さくなるように設定された実施形態2のAM基板12bを模式的に示す平面図である。

【図12】実施形態3のAM基板12cを模式的に示す平面図である。

【図13】実施形態4のAM基板12dを模式的に示す平面図である。

【図14】実施形態5のAM基板12eを模式的に示す平面図である。

【図15】実施形態6のAM基板12fを模式的に示す平面図である。 20

【図16】図15中のXVI - XVI線に沿った実施形態5の液晶表示パネルを模式的に示す断面図である。

【図17】実施形態6のAM基板12fにおいて、上側保持容量電極25a, 25c間で短絡が生じた場合の修正工程を模式的に説明するための平面図である。

【図18】実施形態7のAM基板12gを模式的に示す平面図である。

【図19】図18中のXIX - XIX線断面図である。

【図20】実施形態8のAM基板12hを模式的に示す平面図である。

【図21】図20中のXXI - XXI線断面図である。

【図22】実施形態9のテレビジョン装置15を示すブロック図である。

【図23】実施形態9の液晶表示装置10を示すブロック図である。 30

【図24】従来のAM型液晶表示装置に用いられる、保持容量素子を備えたAM基板の一画素の構成を示す平面模式図である。

【図25】図24に示すAM基板を線分A - A'にて切断した断面を示す断面模式図である。

【図26】一画素を複数のサブピクセルに分割したAM基板における一画素の構成を示す平面模式図である。

【図27】図26に示すAM基板を線分B - B'にて切断した断面を示す断面模式図である。

#### 【符号の説明】

##### 【0143】

- |       |            |

|-------|------------|

| 1 0   | 液晶表示装置     |

| 1 1   | チューナ部      |

| 1 2   | AM基板       |

| 1 3   | 対向基板       |

| 1 4   | 液晶層(表示媒体層) |

| 1 5   | テレビジョン装置   |

| 2 0   | 保持容量素子     |

| 2 0 R | 第1保持容量素子   |

| 2 0 L | 第2保持容量素子   |

| 2 1   | 画素電極       |

10

20

30

40

50

- |                               |               |    |

|-------------------------------|---------------|----|

| 2 1 R                         | 副画素電極（第1画素電極） | 10 |

| 2 1 L                         | 副画素電極（第2画素電極） |    |

| 2 2                           | 走査信号線         |    |

| 2 2 a                         | 第1走査信号線       |    |

| 2 2 b                         | 第2走査信号線       |    |

| 2 3                           | データ信号線        |    |

| 2 4 , 2 4 L , 2 4 R           | TFT（アクティブ素子）  |    |

| 2 5 L , 2 5 R                 | 接続電極          |    |

| 2 5 a , 2 5 b , 2 5 c , 2 5 d | 上側保持容量電極      |    |

| 2 6 a , 2 6 b , 2 6 c , 2 6 d | コンタクトホール      |    |

| 2 7                           | 保持容量（共通）配線    |    |

| 2 7 a , 3 8 c                 | スリット部         |    |

| 3 1                           | 基板            |    |

| 3 2 , 3 2 R                   | ゲート電極         |    |

| 3 3                           | ゲート絶縁膜        |    |

| 3 4                           | 高抵抗半導体層       |    |

| 3 6 a                         | ソース電極         |    |

| 3 6 b                         | ドレイン電極        |    |

| 3 7 b                         | ブラックマトリクス     |    |

| 3 8                           | 層間絶縁膜         |    |

| 3 9                           | 対向電極          |    |

| 9 8                           | 膜残り（短絡部）      |    |

〔 1 〕

〔 2 〕

【図3】

【図4】

## 【図5】

【図6】

【図7】

【 図 9 】

【図8】

【図 10】

【 図 1 1 】

【図12】

【図13】

【図14】

【図15】

### 【図17】

【図16】

【図18】

【図19】

【図20】

【図21】

【図23】

【図22】

【図24】

【図25】

【図26】

【図27】

---

フロントページの続き

前置審査

(72)発明者 野田 知希

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

(72)発明者 津幡 俊英

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

(72)発明者 武内 正典

大阪府大阪市阿倍野区長池町22番22号 シャープ株式会社内

審査官 渡邊 吉喜

(56)参考文献 國際公開第2006/064832 (WO, A1)

特開平09-090318 (JP, A)

特開2004-078157 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1/1343 - 1/1345、

1/135 - 1/1368、

G 09 F 9/00 - 9/46、

H 01 L 27/32

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有源矩阵基板，显示装置，液晶显示装置和电视装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">JP4245650B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2009-03-25 |

| 申请号            | JP2008125311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2008-05-12 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 縁田憲史<br>八木敏文<br>野田知希<br>津幡俊英<br>武内正典                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 縁田 憲史<br>八木 敏文<br>野田 知希<br>津幡 俊英<br>武内 正典                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G09F9/30 G09F9/00 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| CPC分类号         | G02F1/136213 G02F1/136259                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| FI分类号          | G09F9/30.338 G09F9/00.352 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| F-TERM分类号      | 2H092/JA26 2H092/JB42 2H092/JB65 2H092/JB66 2H092/JB69 2H092/JB71 2H092/MA52 2H092/NA12 2H092/NA13 2H092/NA27 2H092/NA30 2H092/QA07 2H092/QA09 2H192/AA24 2H192/BC24 2H192/BC31 2H192/CB05 2H192/DA12 2H192/DA14 2H192/DA43 2H192/DA65 2H192/HA36 2H192/HB03 2H192/HB05 2H192/HB38 2H192/HB48 2H192/HB64 2H192/JA02 5C094/AA31 5C094/AA41 5C094/AA42 5C094/BA03 5C094/BA43 5C094/CA19 5C094/DA13 5C094/EA10 5C094/FB12 5C094/HA08 5G435/AA14 5G435/AA17 5G435/AA19 5G435/BB12 5G435/CC09 5G435/KK05 5G435/LL04 |         |            |

| 代理人(译)         | 前田弘<br>竹内雄二                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 优先权            | 2004364498 2004-12-16 JP<br>2005295015 2005-10-07 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 其他公开文献         | JP2008203889A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

**摘要(译)**

要解决的问题：提供一种有源矩阵基板，显示装置，液晶显示装置和电视装置，能够通过修复有源矩阵基板中的点缺陷来提高产量。SOLUTION：有源矩阵基板12d包括TFT24R，24L，存储电容器元件20R，20L，以及第一像素电极21R和第二像素电极21L，其中存储电容器元件20R，20L包括存储电容器线27和存储电容器电极25a，25c设置成通过绝缘膜面对存储电容器线27，存储电容器电极25a与第一像素电极21R导电，同时与TFT的漏电极导电如图24R所示，存储电容器电极25c与第二像素电极21L导电，并且同时与TFT 24L的漏电极导电，并且存储电容器电极25a，25c沿存储电容器排成一行。第27行。Z

【図1】