(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-300948

(P2005-300948A)

(43) 公開日 平成17年10月27日(2005.10.27)

(51) Int.Cl.<sup>7</sup>

**G09G 3/36**

**G02F 1/133**

**G02F 1/1343**

**G02F 1/1345**

**G02F 1/1368**

F 1

GO9G 3/36

GO2F 1/133 550

GO2F 1/1343

GO2F 1/1345

GO2F 1/1368

テーマコード(参考)

2H092

2H093

5C006

5C080

審査請求 未請求 請求項の数 14 O L (全 22 頁) 最終頁に続く

(21) 出願番号

特願2004-117518 (P2004-117518)

(22) 出願日

平成16年4月13日 (2004.4.13)

(71) 出願人

502356528

株式会社 日立ディスプレイズ

千葉県茂原市早野3300番地

(72) 発明者

萬場 則夫

神奈川県横浜市戸塚区吉田町292番地

株式会社日立製作所

システム開発研究所内

(72) 発明者

工藤 泰幸

神奈川県横浜市戸塚区吉田町292番地

株式会社日立製作所

システム開発研究所内

(72) 発明者

庄司 孝志

神奈川県横浜市戸塚区吉田町292番地

株式会社日立アドバンストデジタル内

最終頁に続く

(54) 【発明の名称】表示装置及びその駆動方法

## (57) 【要約】

【課題】 液晶表示装置において、信号電圧保持後のプランギング期間でフレーム周期毎に対向電極信号を反転させると、輝度傾斜や縦スメアなどの表示むらが発生し画質を劣化させる。また、フレーム周波数が低い場合にはフリッカが発生する恐れがある。

【解決手段】 複数の走査線(G1, G2 ~ Gn)と交差する複数の信号線(D1, D2 ~ Dn)と、走査線と並行する複数の対向電極線(COM1, COM2 ~ COMn)と、交差部に配置された複数の画素(3)と、走査線に走査信号を印加する走査駆動回路(1)と、信号線に信号電圧を印加する信号駆動回路(2)とを有する表示装置において、正極性の対向電極電圧(VCOMA)と負極性の対向電極電圧(VCOMB)との反転信号である対向電極信号を生成する対向電極信号生成回路(5)と、対向電極電圧を対向電極線に印加する対向電極駆動回路(4)とを備え、対向電極駆動回路(4)は、走査駆動回路が输出する走査信号により制御されることを特徴とする。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数の走査線と交差する複数の信号線と、複数の走査線と並行する複数の対向電極線と、複数の走査線と複数の信号線との各々の交差部に配置された複数の画素と、複数の走査線に走査信号を印加する走査駆動回路と、複数の信号線に信号電圧を印加する信号駆動回路とを有する表示装置において、

前記対向電極線に対向電極電圧を印加する対向電極駆動回路と、

前記対向電極駆動回路に対向電極信号を供給する対向電極信号生成回路とを備え、

前記対向電極駆動回路は、走査信号が印加されると対向電極線に対向電極電圧を印加することを特徴とする表示装置。10

**【請求項 2】**

前記対向電極駆動回路は、複数の対向電極線に対応した複数のスイッチング素子で構成され、

前記スイッチング素子は、走査信号が印加されると対向電極線に対向電極電圧を印加することを特徴とする請求項 1 記載の表示装置。15

**【請求項 3】**

前記対向電極信号生成回路は、異なる 2 つの対向電極信号を対向電極駆動回路に供給し、

前記対向電極駆動回路は、複数の対向電極線に対応した複数のスイッチング素子で構成され、20

前記スイッチング素子は、2 つのグループに分割した対向電極線の一方のグループには、異なる 2 つの対向電極電圧の一方を印加し、他方のグループには、異なる 2 つの対向電極電圧の他方を印加し、走査信号が印加されると対向電極線に対向電極電圧を印加することを特徴とする請求項 1 記載の表示装置。25

**【請求項 4】**

複数の走査線と交差する複数の信号線と、複数の走査線と並行する複数の対向電極線と、複数の走査線と複数の信号線との各々の交差部に配置された複数の画素と、複数の走査線に走査信号を印加する走査駆動回路と、複数の信号線に信号電圧を印加する信号駆動回路とを有する表示装置において、30

前記走査駆動回路は、複数のセレクタブロックで構成され、

前記複数のセレクタブロックは、各々のセレクタブロックを選択するためのブロックセレクト信号と各々のセレクタブロックに対応する複数の水平ラインを順次走査するためのクロック信号とで制御され、

前記各々のセレクタブロックは、ブロックセレクト信号とクロック信号とが選択レベルとなると走査線に選択電圧を印加し、

前記各々のセレクタブロックにより走査される複数水平ライン毎に対向電極信号を各々生成する対向電極信号生成回路と、40

前記対向電極信号生成回路からの対向電極信号が供給される対向電極駆動回路とを備え、

前記対向電極駆動回路は、クロック信号が選択レベルとなると対向電極線に対向電極電圧を印加することを特徴とする表示装置。45

**【請求項 5】**

前記対向電極駆動回路は、複数の対向電極線に対応した複数のスイッチング素子で構成され、

前記スイッチング素子は、走査信号が印加されると対向電極線に対向電極電圧を印加することを特徴とする請求項 4 記載の表示装置。50

**【請求項 6】**

前記対向電極信号生成回路は、異なる 2 つの対向電極信号を対向電極駆動回路に供給し、

前記対向電極駆動回路は、複数の対向電極線に対応した複数のスイッチング素子で構成

され、

前記スイッチング素子は、前記セレクタブロックに対応する複数水平ライン毎に2つのグループに分割した対向電極線の一方のグループには、異なる2つの対向電極電圧の一方を印加し、他方のグループには、異なる2つの対向電極電圧の他方を印加し、走査信号を出力するためのクロック信号により制御されることを特徴とする請求項4記載の表示装置。

#### 【請求項7】

複数の走査線と交差する複数の信号線と、複数の走査線と並行する複数の対向電極線と、複数の走査線と複数の信号線との各々の交差部に配置された複数の画素と、複数の走査線に走査信号を印加する走査駆動回路と、複数の信号線に信号電圧を印加する信号駆動回路とを有する表示装置において、

前記複数の画素は、1水平ラインで1本の対向電極線を共有し、前記対向電極線と隣接する2つの走査線に分割して接続し、異なる2つの対向電極信号を生成する対向電極信号生成回路と、複数の対向電極線に対応した複数のスイッチング素子で構成される対向電極駆動回路とを備え、

前記複数の対向電極線を2つのグループに分割し、

前記グループの一方には、少なくとも2つのスイッチング素子を介して異なる2つの対向電極信号の一方を印加し、

前記グループの他方には、少なくとも2つのスイッチング素子を介して異なる2つの対向電極信号の他方を印加し、

前記2つのスイッチング素子は、該スイッチング素子と接続される対向電極線を含む水平ラインを駆動する2つの走査線に各々接続され、該走査線に選択電圧が印加されると該対向電極線に対向電極電圧を印加することを特徴とする表示装置。

#### 【請求項8】

前記走査駆動回路と前記対向電極駆動回路とを複数の画素を形成する基板と同一基板上に形成することを特徴とする請求項1ないし請求項7に記載の表示装置。

#### 【請求項9】

前記画素にIPS液晶を用いることを特徴とする請求項1ないし請求項7記載の表示装置。

#### 【請求項10】

複数の走査線と交差する複数の信号線と、複数の走査線と並行する複数の対向電極線と、複数の走査線と複数の信号線との各々の交差部に配置された複数の画素と、複数の走査線に走査信号を印加する走査駆動回路と、複数の信号線に信号電圧を印加する信号駆動回路とを有する表示装置の駆動方法において、

前記対向電極線に対向電極駆動回路からの異なる2つの対向電極電圧を印加し、

前記対向電極駆動回路に対向電極信号生成回路からの異なる2つの対向電極信号を供給し、

前記対向電極駆動回路は、複数の対向電極線に対応した複数のスイッチング素子で構成され、

前記スイッチング素子は、走査信号が印加されると対向電極線に対向電極電圧を印加することを特徴とする表示装置の駆動方法。

#### 【請求項11】

複数の走査線と交差する複数の信号線と、複数の走査線と並行する複数の対向電極線と、複数の走査線と複数の信号線との各々の交差部に配置された複数の画素と、複数の走査線に走査信号を印加する走査駆動回路と、複数の信号線に信号電圧を印加する信号駆動回路とを有する表示装置の駆動方法において、

前記走査駆動回路は、複数のセレクタブロックで構成され、

前記複数のセレクタブロックは、各々のセレクタブロックを選択するためのブロックセレクト信号と各々のセレクタブロックに対応する複数の水平ラインを順次走査するためのクロック信号とで制御され、

10

20

30

40

50

前記各々のセレクタブロックは、ブロックセレクト信号とクロック信号とが選択レベルとなると走査線に選択電圧を印加し、

前記各々のセレクタブロックにより走査される複数水平ライン毎に対向電極信号を対向電極信号生成回路が各々生成し、

前記対向電極信号生成回路からの対向電極信号を対向電極駆動回路に供給し、

前記対向電極駆動回路は、複数の対向電極線に対応した複数のスイッチング素子で構成され、

前記スイッチング素子は、クロック信号が選択レベルとなると対向電極線に対向電極電圧を印加することを特徴とする表示装置の駆動方法。

【請求項 1 2】

複数の走査線と交差する複数の信号線と、複数の走査線と並行する複数の対向電極線と、複数の走査線と複数の信号線との各々の交差部に配置された複数の画素と、複数の走査線に走査信号を印加する走査駆動回路と、複数の信号線に信号電圧を印加する信号駆動回路とを有する表示装置の駆動方法において、

前記複数の画素は、1水平ラインで1本の対向電極線を共有し、前記対向電極線と隣接する2つの走査線に分割して接続し、対向電極信号生成回路は異なる2つの対向電極信号を生成し、対向電極駆動回路は複数の対向電極線に対応した複数のスイッチング素子で構成され、

前記複数の対向電極線を2つのグループに分割し、

前記グループの一方には、少なくとも2つのスイッチング素子を介して異なる2つの対向電極信号の一方を印加し、

前記グループの他方には、少なくとも2つのスイッチング素子を介して異なる2つの対向電極信号の他方を印加し、

前記2つのスイッチング素子は、該スイッチング素子と接続される対向電極線を含む水平ラインを駆動する2つの走査線に各々接続され、該走査線に選択電圧が印加されると該対向電極線に対向電極電圧を印加することを特徴とする表示装置の駆動方法。

【請求項 1 3】

前記異なる2つの対向電極信号は、正極性の対向電極電圧と負極性の対向電極電圧とがフレーム周期毎に反転する反転信号であり、

前記正極性と負極性の対向電極電圧は、複数の画素への信号電圧の書換えが行われる期間は逆極性の対向電極電圧であり、

前記対向電極電圧が反転するタイミングは、複数の画素への表示信号に応じた信号電圧の書換えが行われないブランкиング期間であることを特徴とする請求項10ないし請求項12に記載の表示装置の駆動方法。

【請求項 1 4】

前記セレクタブロックに対応する異なる2つの対向電極信号は、正極性の対向電極電圧と負極性の対向電極電圧とがフレーム周期で反転する反転信号であり、

前記異なる2つの対向電極電圧は、複数の画素の表示信号に応じた信号電圧の書換えが行われる期間は逆極性の対向電極電圧であり、

前記異なる2つの対向電極信号が反転するタイミングは、選択されるセレクタブロックに対応する複数の水平ラインの表示信号に応じた信号電圧の書換えを行う期間前であることを特徴とする請求項11に記載の表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、アクディブマトリクス型である表示装置の対向電極に印加される信号電位を反転する表示装置及びその駆動方法に関する。

【背景技術】

【0002】

液晶表示装置は、画素アレイを形成した基板と、これに対向するもう一方の基板で液晶

を狭持し、画素アレイと同一基板上に設けた画素電極と、対向電極との間に表示信号に応じた信号電圧を印加することで、液晶の透過率を変調し多階調表示を行っている。

#### 【0003】

対向電極が設けられる場所が、画素アレイと同一基板上の場合はインプレーンスイッチング液晶と呼ばれ、横電界により制御される。一方、対向電極が画素アレイの形成された基板と対向する基板に設けられた場合は、ツイストネマティック液晶などと呼ばれ、縦電界で制御される。これらの液晶制御方式は、液晶にかかる電界方向が異なるが、駆動方法は共通である。

#### 【0004】

液晶表示装置では、対向電極の電位に対して高電位側（正極性）の信号電圧、又は低電位側（負極性）の信号電圧を画素電極に印加し続けると焼きつきと呼ばれる表示劣化が発生するため、ある周期で正極性と負極性を反転して印加する必要がある。

#### 【0005】

一般的に、上述した液晶表示装置の駆動方式は2つに分類できる。1つは対向電極の電位を一定とする方法であり、もう一方は、対向電極の電位を反転する方法（以下「対向電極反転駆動」という。）である。前者の駆動方法では、対向電極の電位が一定であるため、画素電極に印加する信号電位を正極性から負極性まで出力する信号駆動回路が必要になる。

#### 【0006】

それに対して、後者の対向電極反転駆動方式は、画素電極に正極性の信号電位を印加するために必要な低電位の対向電極電圧（以下「正極性の対向電極電圧」という。）と、画素電極に負極性の信号電位を印加するために必要な高電位の対向電極電圧（以下「負極性の対向電極電圧」という。）を、周期的に反転する。

#### 【0007】

そのため信号駆動回路の電圧出力範囲は前者に比べ半分近く小さくなり、信号駆動回路の耐圧を下げることが可能となるため、信号駆動回路をLSI化して構成する場合には部品コストを削減することができる。また、信号駆動回路が出力する電圧振幅が小さいことから、高速化に適した駆動方式でもある。

#### 【0008】

ただし、近年の液晶表示装置の高精細化（走査線数の増加）に伴う1水平期間の短縮や、液晶表示面積の大型化に伴う配線負荷の増大により、対向電極電圧の反転時に波形なまりが発生し、1水平期間内に目標とする電位に到達しないため表示ムラ等の画質劣化が発生する。この対向電極電圧の反転時の波形なまりを解決する方法として、下記特許文献1に記載の液晶表示装置がある。

#### 【0009】

この液晶表示装置においては、1水平ライン上にある画素の対向電極を共通化して水平方向の対向電極線とし、この対向電極線の奇数ライン同士と偶数ライン同士とを夫々端部で共通に接続して、第1の対向電極と第2の対向電極としている。

#### 【0010】

そして、第1、第2の対向電極に1フレーム期間で交互に反転する第1、第2の対向電極電圧を印加することで、1水平周期毎に画素電極に印加する信号電圧の極性が変化する対向電極反転駆動を行う。

#### 【0011】

さらに、第1、第2の対向電極電圧が反転するタイミングを、画素電極信号のプランキング期間中としている。これにより1水平周期毎に対向電極電圧が反転せず、この反転による波形なまりも発生しないために表示ムラ等の画質劣化をなくし、高品位な液晶表示装置としている。

#### 【0012】

また、共通電極線（対向電極線）を夫々独立に駆動する表示装置が、下記特許文献2に記載されている。

10

20

30

40

50

【特許文献 1】特開 2001-356356 号公報

【特許文献 2】特開 2003-255907 号公報

【発明の開示】

【発明が解決しようとする課題】

【0013】

上記特許文献 1 に記載の液晶表示装置は、各水平ラインの画素に信号電圧を保持させた（書込んだ）後、プランキング期間で対向電極電圧が反転するため、画素電極電位が変動する。この際に、フレームの前半で電圧保持した画素と、後半で電圧保持した画素とでは、書き込み後に対向電極電圧が反転する期間が異なるため、輝度傾斜や縦スメアと呼ばれる表示ムラが発生し画質が劣化する恐れがある。

10

【0014】

さらに、プランキング期間で対向電極電圧が反転することで全画素の画素電極電位が一斉に変動するため、フレーム周波数が低い場合にはフリッカが発生する恐れがある。

【0015】

また、上記特許文献 2 に記載の表示装置では、共通電極駆動回路が必要になるため回路規模が増大する。

【0016】

本発明の目的は、回路規模の増大を抑制しつつ、表示ムラやフリッカなどの画質劣化を抑制した高品位な表示装置及びその駆動方法を提供することにある。

20

【課題を解決するための手段】

【0017】

本発明は、複数本の走査線と前記走査線と交差する複数本の信号線と前記走査線と並行する複数本の対向電極線と前記走査線と前記信号線との交差部に対応して配置された画素を有する複数の画素と、前記走査線に走査信号を印加する走査駆動回路と、前記走査信号により選択電圧が印加された前記走査線に接続される画素に対応する信号電圧を前記信号線に印加する信号駆動回路とを有する表示装置において、正極性の対向電極電圧と負極性の対向電極電圧との反転信号である対向電極信号を生成する対向電極信号生成回路と、前記対向電極電圧を前記対向電極線に印加する対向電極駆動回路とを備え、前記対向電極駆動回路は前記走査駆動回路が出力する前記走査信号により制御されることを特徴とする。

30

【0018】

また、本発明は、複数本の走査線と前記走査線と交差する複数本の信号線と前記走査線と並行する複数本の対向電極線と前記走査線と前記信号線との交差部に対応して配置された画素を有する複数の画素と、前記走査線に走査信号を印加する走査駆動回路と、前記走査信号により選択電圧が印加された前記走査線に接続される画素に対応する信号電圧を前記信号線に印加する信号駆動回路とを有する表示装置において、前記走査駆動回路は複数のセレクタブロックで構成され、ブロックセレクト信号とクロック信号で制御されるセレクタ方式であり、前記走査駆動回路の前記セレクタブロックにより走査される水平ラインのグループ毎に正極性の対向電極電圧と負極性の対向電極電圧との反転信号である対向電極信号を夫々生成する対向電極信号生成回路と、前記水平ラインのグループ毎に生成された前記対向電極電圧を該水平ラインのグループの前記対向電極線に印加する対向電極駆動回路とを備え、前記対向電極駆動回路は前記走査駆動回路の前記クロック信号により制御されることを特徴とする。

40

【発明の効果】

【0019】

本発明によれば、特に、次に示す(1)ないし(7)の効果を奏する。

【0020】

(1)各水平ラインの画素に信号電圧を保持させてから、次のフレーム期間で各水平ラインの書き込みを行うまで対向電極電圧の極性が反転しないため、輝度傾斜や縦スメアと呼ばれる表示ムラが抑制された高品位な表示装置を得ることができる。

50

【0021】

(2) 対向電極電圧の極性反転がフレーム期間内の1ライン単位で分散して発生するため、フレーム周波数が低い場合でも、フリッカが起こりにくい高品位な表示装置を得ることができる。

【0022】

(3) 各水平ラインの画素に信号電圧を保持させてから、次のフレーム期間で各水平ラインの書き込みを行うまで対向電極電圧の極性が反転しないため、従来に比べ走査信号の電圧振幅を小さくすることが可能となり、素子の耐圧を下げることが可能となる。また、走査信号の電圧振幅を小さくすることで素子の劣化を軽減できるため、高品位な表示装置を得ることができる。

【0023】

(4) 各水平ラインにおいて、非選択期間は対向電極線がハイインピーダンス状態であるため、対向電極線との間に寄生容量を持つ信号線の負荷が見かけ上は軽くなり、信号線に印加する信号電圧の目標電位までの収束時間が改善されるため、高速化に適した表示装置を得ることができる。

【0024】

(5) 対向電極反転駆動を適用する高画質で低消費電力な表示装置に適用できる。

【0025】

(6) 走査信号に基づいて対向電極線を駆動することにより、他の制御信号や端子が不要となるため、回路規模の増大を抑制できる。

【0026】

(7) 対向電極線がフロー ティングになるため、信号線の収束が改善し、画質を向上することができる。

【発明を実施するための最良の形態】

【0027】

以下、図面を用いて、本発明の実施例を説明する。

【実施例1】

【0028】

以下の実施例の説明では、画素部分に液晶材料を用いた液晶表示装置の例を示すが、その基本的な構造や駆動方法は画素部にエレクトロルミネッセンス材料や発光ダイオード素子を用いた表示装置にも適用できる。

【0029】

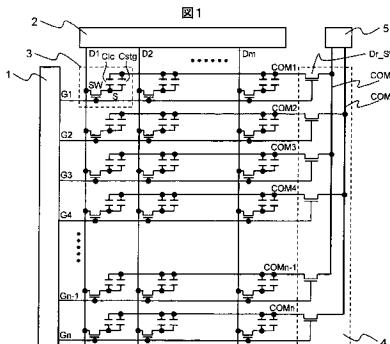

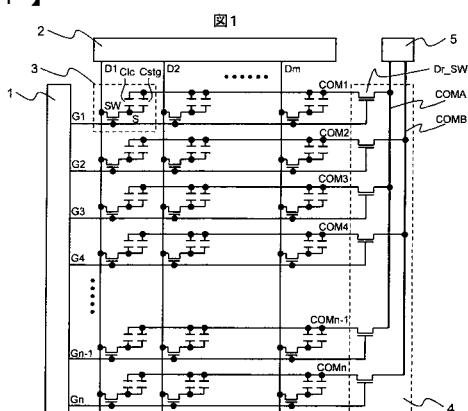

まず、本発明に係る表示装置及びその駆動方法の実施例1について、図1から図3を参照して説明する。

【0030】

図1は、本発明の実施例1としての液晶表示装置の構成を示す概略図である。以下、実施例1における液晶表示装置の構成を説明する。ここで示す液晶表示装置は、例えば、水平方向のドット数がm個、垂直方向のライン数がn本として説明を行う。液晶表示装置には、走査線G1、G2、G3、G4、・・・、Gn-1、Gnがn本配置される。この走査線Gは、走査駆動回路1が出力する走査信号が印加される。また、走査線Gと交わる方向に信号線D1、D2、・・・、Dmがm本配置される。この信号線Dには、信号駆動回路2が出力する表示信号に応じた信号電圧が印加される。

【0031】

走査線Gと同じ方向に対向電極線COM1、COM2、COM3、COM4、・・・、COMn-1、COMnがn本配置される。この対向電極線COMは、対向電極駆動回路4が出力する対向電極信号が印加される。

【0032】

走査線Gと信号線Dが交差する付近には、スイッチング素子を含む画素3が夫々配置される。したがって、液晶表示装置には、水平方向にm個、垂直方向にn個の画素3がマトリクス状に配置される。この画素3は、スイッチング素子SWと、液晶容量C1cと、必要な場合には保持容量Cstgと、各容量を形成するための画素電極Sと対向電極とで構成

10

20

30

40

50

される。

【0033】

スイッチング素子SWは、薄膜トランジスタ（以下「TFT」という。）などの3端子素子が用いられ、このTFTはアモルファスSiや多結晶Siや単結晶Siなどで形成される。スイッチング素子SWは、そのゲート端子が走査線Gに接続されており、走査線Gに印加される走査信号によりオンオフ制御される。

【0034】

この実施例1の液晶表示装置では、1水平ライン上に並ぶ画素3のスイッチング素子SWのゲート端子が、その水平ラインに対応する1本の走査線Gに接続される。また、スイッチング素子SWのドレイン端子は信号線Dに接続されており、走査線に印加される走査信号によりスイッチング素子SWがオン状態に制御された場合には、スイッチング素子SWのソース端子に接続されている画素電極Sに信号線に印加される信号電圧を伝播する。さらに、1垂直ライン上に並ぶ画素3のスイッチング素子WSのドレイン端子が1本の信号線Dに接続され、1水平ライン上に並ぶ画素3に含まれる対向電極は、その水平ラインに対応する1本の対向電極線COMに接続される。

【0035】

対向電極信号生成回路5は、対向電極反転駆動に必要な正極性の対向電極電圧Vcom#hiと負極性の対向電極電圧Vcom#lowとの反転信号を生成し、第1の対向電極信号線COMAと第2の対向電極信号線COMBに出力する。

【0036】

対向電極駆動回路4は、n個のスイッチング素子Dr#SWで構成される。このスイッチング素子Dr#SWは、TFTなどの3端子素子が用いられ、このTFTは、アモルファスSiや多結晶Siや単結晶Siで形成される。

【0037】

スイッチング素子Dr#SWのソース端子は、各対向電極線COMに接続される。一方、ドレイン端子は、第1の対向電極信号線COMAと第2の対向電極信号線COMBに、例えば、1水平ライン毎に交互に接続される。

【0038】

図1の液晶表示装置の場合には、奇数ラインは第1の対向電極信号線COMAに接続され、偶数ラインは第2の対向電極信号線COMBに接続されている。またDr#SWのゲート端子は、該Dr#SWのソース端子に接続される対向電極線を共有する画素を制御する走査線に接続される。

【0039】

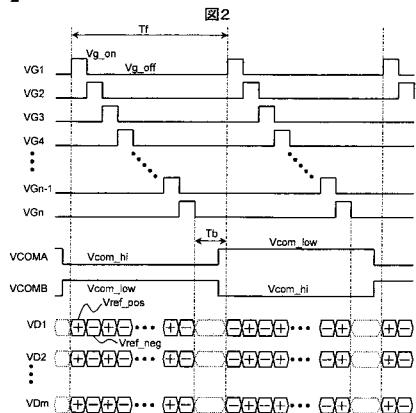

次に、図2と図3を参照して、実施例1の液晶表示装置の駆動方法を説明する。以下の説明では、スイッチング素子SW及びDr#SWのTFTとして、例えば、n型TFTを用いた場合について説明する。また、以下の説明では、例えば、信号駆動回路2が出力する信号電圧の極性が1水平周期毎に反転する対向電極反転駆動について説明する。

【0040】

図2は、走査駆動回路1と信号駆動回路2と対向電極信号生成回路5とが出力する信号のタイミングを示す図である。VG1、VG2、VG3、VG4、・・・、VGn-1、VGnは、走査線G1、G2、G3、G4、・・・、Gn-1、Gnに印加される走査信号を表している。Vg#onはスイッチング素子SWをオン状態とするための選択信号レベルであり、Vg#offはスイッチング素子SWをオフ状態とするための非選択信号レベルである。ここで、画素3に含まれるスイッチング素子SWをn型TFTとしているため、Hiレベルの電圧信号を選択レベルとし、Lowレベルの電圧信号を非選択信号レベルとしている。

【0041】

図2においては、第1水平ラインから第n水平ラインまで順次Vg#onを印加した様子を示している。走査駆動回路1は、少なくとも1フレーム期間Tfに1回は各水平ラインの走査線にVg#onを印加する。走査駆動回路1は、この動作を毎フレーム繰り返す。VCOMAとVCOMBは、対向電極信号生成回路5が生成して第1の対向電極信号線COMAと第2の対向電極

10

20

30

40

50

信号線COMBと共に夫々出力する対向電極信号である。

【0042】

VCOMAとVCOMBは、Vcom#hiとVcom#lowとの反転信号であり、1フレームの中のブランкиング期間Tb(通常は、表示信号がなく表示装置に信号の書換えを行わない期間)で極性を反転する。したがって、VCOMAとVCOMBは交流周波数が、フレーム周波数の1/2となる。また、VCOMAとVCOMBは、少なくとも画素に信号電圧を書込む期間は逆極性の対向電極電圧を出力する。

【0043】

VD1、VD2、・・・、VDmは、信号駆動回路2が信号線D1、D2、・・・、Dmに印加する信号電圧を示している。ここで、Vref#posは正極性の信号電圧を示しており、Vref#negは負極性の信号電圧を示している。

【0044】

信号駆動回路2は、選択信号Vg#onにより選択された各画素に対応する表示信号に応じた信号電圧を、各画素に対応する信号線Dに出力する。その際の信号電圧の極性は、その画素の対向電極に印加される対向電極信号の極性に依存し、Vcom#hiが印加される場合には、正極性の信号電圧Vref#posが outputされ、Vcom#lowが印加される場合には、負極性の信号電圧Vref#negが outputされる。

【0045】

図2の前半に示すフレーム期間においては、奇数ラインの対向電極線が対向電極駆動回路4内のDr#SWを介してCOMAに接続されており、このCOMAの信号がVcom#hiであるため、奇数ラインの画素が選択される期間には、正極性の信号電圧Vref#posが outputされる。

【0046】

一方、偶数ラインの対向電極線がDr#SWを介してCOMBに接続されており、このCOMBの信号がVcom#lowであるため、偶数ラインの画素が選択される期間には、負極性の信号電圧Vref#negが outputされる。

【0047】

次のフレーム期間では、VCOMAとVCOMBの信号極性が反転するため、各水平ラインの画素に出力される信号電圧の極性も反転する。

【0048】

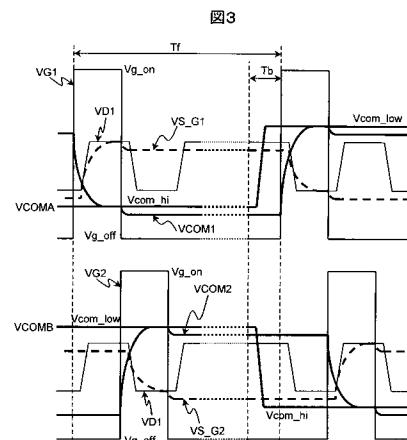

図3は、図2に示す各信号が画素に印加された場合の、各画素の電圧波形を示した図である。図3では、例えば、信号線D1に接続される画素のうち走査線G1とG2に接続される画素の電圧波形を示している。

【0049】

図3において、VS#G1は走査線G1に接続される画素の画素電極Sの電圧信号を示し、VS#G2は走査線G2に接続される画素の画素電極Sの電圧信号を示している。また、VCOM1は第1水平ラインの対向電極線の電圧信号を示し、VCOM2は第2水平ラインの対向電極線の電圧信号を示す。

【0050】

まず、1フレーム期間において、第1水平ラインの画素が、走査信号VG1により選択されると、対向電極COM1には対向電極駆動回路4内のDr#SWを介してVCOMAが印加される。よって、対向電極COM1の電圧VCOM1はVcom#hiに収束していく。

【0051】

一方、画素電極Sには、スイッチング素子SWを介して、信号線D1により伝播される該画素の表示信号に応じた正極性の信号電圧VD1が印加され、VS#G1は信号電圧であるVD1に収束する。

【0052】

第1水平ラインの選択期間終了後は、スイッチング素子SW及びDr#SWが共にオフ状態となるため、画素電極Sと対向電極COM1はフローティング状態となるが、選択期間で印加された正極性の信号電圧は液晶容量C1cと保持容量Cstgに保持される。保持期間中では、COM1はフローティング状態であるために、VCOMAの極性が反転しても対向電極COM1

10

20

30

40

50

の信号極性が反転することはない。すなわち、VCOMAの極性を反転しても保持された信号電圧に影響を及ぼさない。

【0053】

次に、第2水平ラインの画素が走査信号VG2により選択されると、対向電極COM2にはDr#SWを介してVCOMBが印加される。よって、COM2の電圧VCOM2はVcom#lowに収束していく。

【0054】

一方、画素電極Sには、スイッチング素子SWを介して信号線D1により伝播される該画素の表示信号に応じた負極性の信号電圧VD1が印加され、VS#G2は信号電圧VD1に収束する。

【0055】

第2水平ラインの選択期間終了後は、スイッチング素子SW及びDr#SWが共にオフ状態となるため、画素電極Sと対向電極COM2はフローティング状態となるが、選択期間で印加された負極性の信号電圧は液晶容量C1cと保持容量Cstgに保持される。保持期間中では、COM2はフローティング状態であるために、VCOMBの極性が反転しても対向電極COM2の信号極性が反転することはない。すなわち、VCOMBの極性を反転しても保持された信号電圧に影響を及ぼさない。

【0056】

以上の動作を順次繰り返すことにより、1フレーム分の表示信号に対応し、かつ1水平ライン毎に極性を反転した信号電圧を、全水平ラインの画素に保持させることができる。

【0057】

図2の後半に示す1フレーム期間では、各水平ラインにおいて対向電極電圧の極性が反転し、信号駆動回路2から各画素に出力される信号電圧も逆極性となり、同様の駆動が行われることによって、1フレーム分の表示信号に対応した信号電圧を、全水平ラインの画素に保持させることができる。上記駆動をフレーム毎に繰り返すことで、1水平ライン毎に信号電圧の極性を反転させる対向電極反転駆動を実現することができる。

【0058】

本発明に係る実施例1の液晶表示装置及びその駆動方法を用いることにより、本発明は、次に示す(1)ないし(6)の特徴を有する。

【0059】

(1)各水平ラインの画素に信号電圧を保持させてから、次のフレーム期間で各水平ラインの信号電圧の書換えを行うまで対向電極電圧の極性が反転しないため、輝度傾斜や縦スメアと呼ばれる表示ムラが抑制された高品位な表示を実現できる。

【0060】

(2)各水平ラインの対向電極に印加される対向電極電圧の極性反転が、フレーム期間内において1ライン単位で分散して発生するため、フレーム周波数が低い場合でもフリッカが起こりにくい高品位な液晶表示装置を得ることができる。

【0061】

(3)各水平ラインの画素に信号電圧を保持させてから、次のフレーム期間で信号電圧の書換えを行うまで対向電極電圧の極性が反転しないため、従来に比べ走査信号の電圧振幅を小さくすることが可能となり、素子の耐圧を下げることができる。また、走査信号の電圧振幅を小さくすることで素子の劣化を軽減できるため、高品位な液晶表示装置を得ることができる。

【0062】

(4)各水平ラインにおいて、非選択期間は対向電極線がフローティング状態であるため、対向電極線との間に寄生容量を持つ信号線の負荷が軽くなり、信号線に印加する信号電圧の目標電位までの収束時間が改善されるため、高速化に適した表示装置を得ることができる。

【0063】

(5)対向電極駆動回路4の回路規模が小さいため、画素3のスイッチング素子SWが形成される同一基板上に、対向電極駆動回路4を形成することが可能になる。

10

20

30

40

50

## 【0064】

(6) 対向電極駆動回路4の制御を走査駆動回路1の走査信号で行えるため、対向電極駆動回路4の制御信号を新たに設ける必要がない。

## 【0065】

なお、図1の構成図において、対向電極信号生成回路5が出力する対向電極信号線を2つとしているが、これを1つとして対向電極駆動回路4内のDr#SWのドレイン端子を全てこの1つの対向電極信号に接続し、この対向電極信号線に印加する信号を1水平周期毎に極性反転することにより、上述と同様に信号電圧の極性を1水平周期毎に反転する対向電極反転駆動を実現することができる。

## 【0066】

また、上述の説明では対向電極反転駆動における信号電圧の極性反転周期を1水平周期として説明したが、この極性反転周期は任意に設定してもよい。これは、VCOMAとVCOMBの極性と交流周期を適宜設定することで実現できる。

## 【0067】

また、画素電極電圧や対向電極電圧の目標電圧への収束を向上させるため、表示信号に対応する信号電圧を書込む前に、一旦同じ極性の信号電圧を書込むダブルゲート駆動と組み合わせることも可能である。

## 【0068】

また、図1の構成図において、アモルファスSiや多結晶Siを用いることで画素マトリクスと対向電極駆動回路、又は画素マトリクスと対向電極駆動回路と走査駆動回路とを同一基板上に形成し、その他の回路を基板周辺に配置することも可能である。

## 【実施例2】

## 【0069】

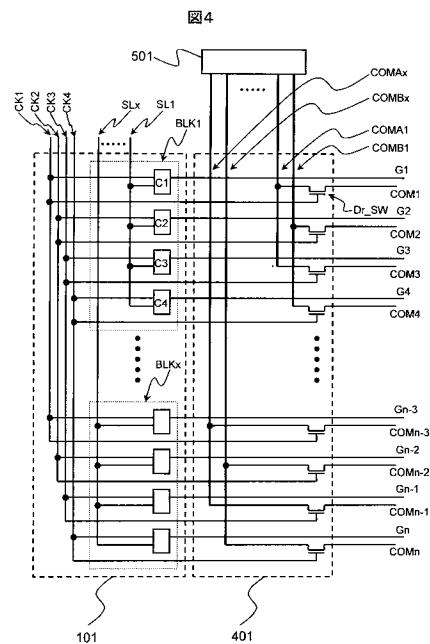

次に、本発明に係る表示装置及びその駆動方法の実施例2について、図4から図6を参照して説明する。図4は、本発明の実施例2としての液晶表示装置の構成を示す概略図である。

## 【0070】

以下、図4を用いて、実施例2における液晶表示装置の構成を説明する。信号駆動回路2と画素3からなる画素マトリクスと信号供給のための信号線Dと走査線Gと対向電極線C0Mは、実施例1の図1と同じため図4では省略する。

## 【0071】

本発明に係る実施例2は、走査駆動回路101がセレクタ方式で構成されており、この走査駆動回路101の制御信号で対向電極駆動回路401を制御する構成である。走査駆動回路101は複数のセレクタブロックBLKで構成され、各セレクタブロックBLKは複数本の走査線を駆動する。例えば、1つのセレクタブロックが4本の走査線を駆動する場合の構成図である。

## 【0072】

図4に示すように、全水平ライン数nが4×本である場合には、BLK1からBLKxまでのx個のBLKで構成される。この構成は、水平ライン数nが、セレクタブロックBLKの構成単位のライン数(4本)で割り切れる場合であるが、割り切れない場合には最終のセレクタブロックに余りの水平ラインの走査線を割当てればよい。

## 【0073】

各セレクタブロックBLKは、そのセレクタブロックが駆動する走査線の数と等しいセルで構成され、4つのセルC1、C2、C3、C4で構成される。このセルは、各セレクタブロックBLKが駆動する走査線に夫々接続される。また、C1、C2、C3、C4のセルは、クロック信号CK1、CK2、CK3、CK4が夫々入力される。したがって、クロック信号CKはセレクタブロックのセル数に相当する数が必要となる。

## 【0074】

また、各セルには、そのセルが含まれるセレクタブロックBLKを選択するためのブロックセレクト信号SLも夫々入力される。セレクタブロックBLKがx個ある場合には、ブロック

セレクト信号はSL1からSL<sub>x</sub>までx本必要となる。

【0075】

対向電極駆動回路401は、対向電極線の数に相当する数のスイッチング素子Dr#SWで構成される。このスイッチング素子は、実施例1と同様にTFT等の3端子素子であり、アモルファスSiや多結晶Siや単結晶Siで形成される。

【0076】

各スイッチング素子Dr#SWのソース端子は、対向電極線COM1、COM2、…、COM<sub>n</sub>に夫々接続される。また、ゲート端子は、該スイッチング素子と接続する対向電極線を含む水平ラインの走査線を駆動するセルCと同じクロック信号CKが接続される。また、対向電極信号線COMAとCOMBは、セレクタブロックBLK毎に設けられる。したがって、1番目のセレクタブロックBLK1が駆動する水平ライン群には、COMA1とCOMB1が設けられ、最終のセレクタブロックBLK<sub>x</sub>が駆動する水平ライン群には、COMAxとCOMB<sub>x</sub>が設けられる。

10

【0077】

対向電極駆動回路401においては、例えば、1水平周期毎に信号電圧の極性を反転させる対向電極反転駆動を行うために、各セレクタブロックが駆動する水平ライン群のうち、奇数ラインの対向電極線が接続されるスイッチング素子Dr#SWのドレイン端子には、COMAが接続され、偶数ラインの対向電極線が接続されるスイッチング素子Dr#SWのドレイン端子には、COMBが接続される。

20

【0078】

また、対向電極信号線COMA1、COMB1、…、COMAx、COMB<sub>x</sub>に印加される信号は、正極性の対向電極信号Vcom#hiと負極性の対向電極信号Vcom#lowとの交流信号であり、これらの信号は、対向電極信号生成回路501が生成して出力する。

20

【0079】

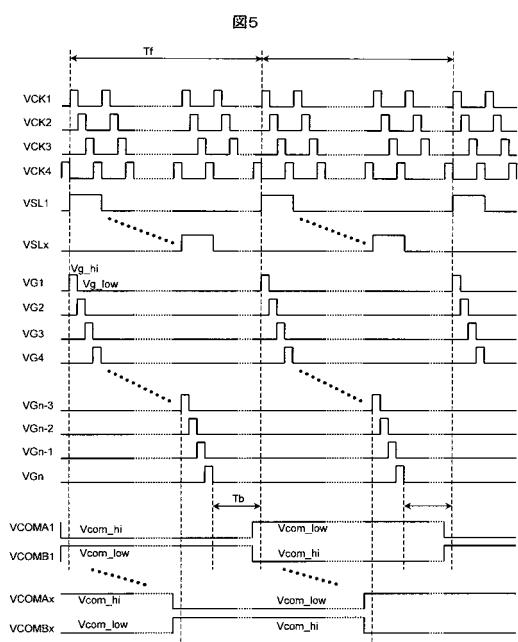

次に図5及び図6を用いて実施例2の液晶表示装置の動作及びその駆動方法について説明する。

【0080】

図5は、走査駆動回路101を制御するブロックセレクト信号VSLとクロック信号VCKと、走査信号VG、対向電極信号生成回路501が出力する対向電極信号VCOMAとVCOMBのタイミングを示した図である。

30

【0081】

1つのセレクタブロックBLKに割当てられる水平ライン数が4本の場合には、クロック信号VCK1、VCK2、VCK3、VCK4は4水平周期に、少なくとも1回の割合で選択レベルの信号(Hiレベル)を出力する。各クロック信号VCKの位相を約1水平周期ずらすことで、4水平周期内にセレクタブロックを構成するC1からC4の4つのセルに、クロック信号の選択レベルを順次印加することができる。

30

【0082】

ロックセレクト信号VSLは、例えば、1フレーム期間で少なくとも1回の割合で4水平周期間の選択レベル(Hiレベル)の信号を出力する。したがって、このロックセレクト信号VSLが選択レベルの期間中に、前述したクロック信号VCKは、夫々少なくとも1回は選択レベルの信号を出力する。各ロックセレクト信号は、例えば、位相を4水平周期程度ずらして出力されることで、順次各セレクタブロックに選択信号を印加し、全てのセレクタブロックに1フレーム期間中少なくとも1回は選択レベルの信号を印加することができる。

40

【0083】

各セレクタブロックBLKに含まれるセルCは、ロックセレクト信号VSLとクロック信号VCKが共に選択レベルの信号になると、接続されている走査線に選択レベルの走査信号Vg#onを出力する。したがって、前述のようにクロック信号VCKとロックセレクト信号VSLを印加することで、1フレーム期間で全走査線に選択レベルの走査信号Vg#onを順次印加することができる。

【0084】

50

対向電極信号は各セレクタブロックBLKに対応しており、夫々が正極性の対向電極信号Vcom#hiと負極性の対向電極信号Vcom#lowとの反転信号である。例えば、セレクタブロックBLK1に対応する対向電極信号はVCOMA1とVCOMB1であり、セレクタブロックBLKxに対応する対向電極信号はVCOMAxとVCOMBxである。各対向電極信号は、対応するセレクタブロックのブロックセレクタ信号に選択レベルの信号が印加される前の4水平周期以内に極性を反転することが望ましい。また、対向電極信号VCOMAとVCOMBは、少なくとも走査線に選択レベルが印加される期間は逆極性である。

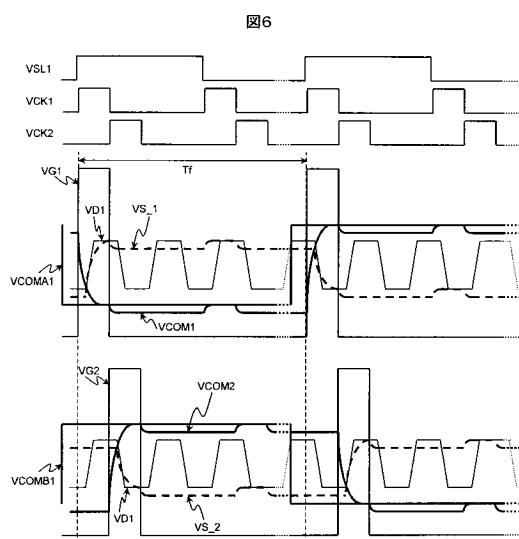

#### 【0085】

図6は、セレクタブロックBLK1で駆動される第1水平ラインと第2水平ラインの画素のうち、信号線D1に接続される画素の駆動電圧波形を示している。図中のVCOM1とVCOM2は、第1水平ライン及び第2水平ラインの対向電極線の電位である。また、第1水平ラインで信号線D1に接続する画素の画素電極の電圧をVS#1とし、第2水平ラインで信号線D1に接続する画素の画素電極の電圧をVS#2とする。

#### 【0086】

まず、第1水平ラインにおいて、ブロックセレクト信号VSL1とクロック信号VCK1が共に選択レベルになると、走査駆動回路101は走査線G1に選択信号Vg#onを出力する。同時に、クロック信号VCK1の選択レベルにより対向電極駆動回路401のCOM1に接続されるDr#SWがオン状態となり、COM1に対向電極信号VCOMA1を印加する。

#### 【0087】

図6の前半に示す1フレーム期間でVCOMA1はVcom#hiであるため、信号駆動回路2は正極性の信号電圧を信号線D1に印加する。したがって、第1水平ライン上の信号線D1に接続される画素は、対向電極電圧がVcom#hiに収束し、画素電極電圧VS#1は正極性の信号電圧VD1に収束する。

#### 【0088】

ここでクロック信号VCK1がLowレベルとなることで、画素のSWと対向電極駆動回路内のDr#SWがオフ状態となり、第1水平ラインの画素は正極性の信号電圧を保持する。

#### 【0089】

次に、ブロックセレクト信号VSL1とクロック信号VCK2が両方とも選択レベルとなり、走査線G2に選択信号が印加される。また、クロック信号VCK2が選択レベルであるため対向電極駆動回路401のCOM2に接続されるDr#SWがオン状態となり、COM2に対向電極信号VCOMB1を印加する。

#### 【0090】

例えば、VCOMB1はVcom#lowであるため、信号駆動回路2は負極性の信号電圧を信号線D1に印加する。したがって、第2水平ライン上の信号線D1に接続される画素は、対向電極電圧がVcom#lowに収束し、画素電極電圧VS#2は負極性の信号電圧VD1に収束する。

#### 【0091】

ここで、クロック信号VCK2がLowレベルとなると、第2水平ライン上の画素は負極性の信号電圧を保持する。その後、ブロックセレクト信号VSL1は次のフレームで書き込みが行われるまでLowレベルとなる。VSL1がLowレベルの状態において、VCK1は4水平周期に1回の割合で選択レベルとなる。この時、対向電極駆動回路401のCOM1に接続されるDr#SWはオン状態となり、保持期間中においてもCOM1にVCOMA1の電圧信号を印加する。

#### 【0092】

一方、VCK2も4水平周期に1回の割合で選択レベルとなるり、この時に対向電極駆動回路401のCOM2に接続されるDr#SWはオン状態となるため、COM2には保持期間中でもVCOMB1の信号電圧が印加される。

#### 【0093】

この保持期間中はVCOMAとVCOMBの電圧極性が変化しないため、対向電極電圧の極性は、次の信号電圧の書換えまで変化しない。

#### 【0094】

図6の後半に示すフレームでは、同様にVG1とVG2により第1水平ラインと第2水平ライ

10

20

30

40

50

ンの信号電圧の書換え動作が行われるが、このとき対向電極信号生成回路501が出力する対向電極信号VCOMA1とVCOMB1は極性を反転しているため、信号駆動回路2が信号線D1に出力する信号電圧の極性も反転しており、各画素には前半に示すフレームとは逆極性の信号電圧が保持されることになる。

#### 【0095】

上記駆動をフレーム毎に繰り返すことで、1水平ライン毎に信号電圧の極性を反転させる対向電極反転駆動を実現することができる。

#### 【0096】

本発明に係る実施例2の液晶表示装置及びその駆動方法を用いることにより、本発明は、次に示す(1)ないし(7)の特徴を有する。

#### 【0097】

(1)各水平ラインの画素に信号電圧を保持させてから、次のフレーム期間で各水平ラインの信号電圧を書換えるまで対向電極電圧の極性が反転しないため、輝度傾斜や縦スメアと呼ばれる表示ムラが抑制された高品位な表示を実現できる。

#### 【0098】

(2)書き込み後の保持期間中であっても、各水平ラインの対向電極線に、ある一定周期で対向電極信号を印加することができる。

#### 【0099】

(3)各水平ラインの対向電極に印加される対向電極電圧の極性反転が、フレーム期間内において1ライン単位で分散して発生するため、フレーム周波数が低い場合でもフリッカが起こりにくい高品位な液晶表示装置を得ることができる。

#### 【0100】

(4)各水平ラインの画素に信号電圧を保持させてから、次のフレーム期間で信号電圧を書換えるまで対向電極電圧の極性が反転しないため、従来に比べ走査信号の電圧振幅を小さくすることが可能となり、素子の耐圧を下げることができる。また、走査信号の電圧振幅を小さくすることで素子の劣化を軽減できるため、高品位な液晶表示装置を得ることができる。

#### 【0101】

(5)各水平ラインにおいて、非選択期間は対向電極線がフローティング状態であるため、対向電極線との間に寄生容量を持つ信号線の負荷が軽くなり、信号線に印加する信号電圧の目標電位までの収束時間が改善されるため、高速化に適した表示装置を得ることができる。

#### 【0102】

(6)対向電極駆動回路401の回路規模が小さいため、画素のスイッチング素子SWが形成される同一基板上に、対向電極駆動回路401を形成することが可能になる。

#### 【0103】

(7)対向電極駆動回路401の制御を走査駆動回路101の走査信号で行うことができるため、対向電極駆動回路401の制御信号を新たに設ける必要がない。

#### 【0104】

なお、図4の構成図において、対向電極信号生成回路501が出力する対向電極信号線を各セレクタブロックに対してCOMAとCOMBの2本1組としているが、これを各セレクタブロックで1本として対向電極駆動回路401内のDr#SWのドレイン端子を対応する対向電極信号線に接続し、この対向電極信号線に印加する信号を1水平周期毎に極性反転することにより、上述と同様に信号電圧の極性を1水平周期毎に反転する対向電極反転駆動を実現することができる。

#### 【0105】

また、上述の説明では対向電極反転駆動における信号電圧の極性反転周期を1水平周期として説明したが、この極性反転周期は任意に設定してもよい。これは、VCOMAとVCOMBの極性と交流周期を適宜設定することで実現できる。

#### 【0106】

10

20

30

40

50

また、画素電極や対向電極への書き込みを向上するために、一旦同じ極性の信号電圧を書き込むダブルゲート駆動と組み合わせることも可能である。

【0107】

また、図4の構成図において、アモルファスSiや多結晶Siを用いることで画素マトリクスと対向電極駆動回路、又は画素マトリクスと対向電極駆動回路と走査駆動回路とを同一基板上に形成し、その他の回路を基板周辺に配置することも可能である。

【実施例3】

【0108】

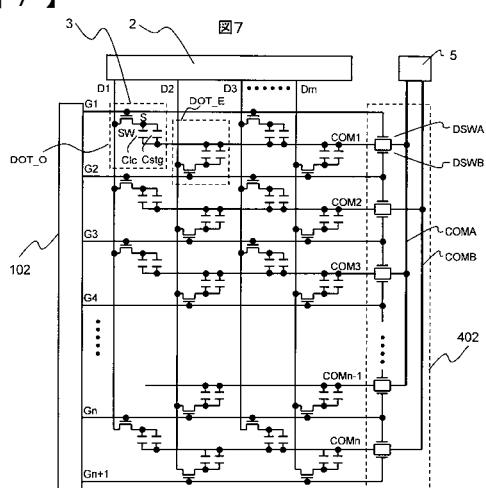

まず、本発明に係る表示装置及びその駆動方法の実施例3について、図7から図9を参考して説明する。

10

【0109】

図7は、実施例3における液晶表示装置の構成を示す概略図である。以下、実施例3における液晶表示装置の構成を説明する。ここで、信号駆動回路2と対向電極信号生成回路5及び画素3からなる画素マトリクスの構成は、本発明に係る実施例1と共に通であるため説明を省略する。

【0110】

図7に示す液晶表示装置は、水平方向のドット数がm個、垂直方向のライン数をn本として説明を行う。この液晶表示装置には、走査駆動回路102が outputする走査信号を各画素3に印加するための走査線G1、G2、G3、G4、・・・、Gn、Gn+1がn+1本配置される。また、信号駆動回路2が outputする信号電圧を各画素に印加するために、走査線と交わる方向に信号線D1、D2、・・・、Dmがm本配置される。

20

【0111】

対向電極駆動回路402が outputする対向電極信号を、各画素の対向電極に印加するために、走査線と同じ方向に対向電極線COM1、COM2、COM3、COM4、・・・、COMn-1、COMnがn本配置される。この対向電極線と信号線の交差する付近には、スイッチング素子SWを含む画素3が夫々配置される。したがって、表示装置には水平方向にm個、垂直方向にn個の画素がマトリクス型に配置される。

【0112】

1本の対向電極線に接続される1水平ライン分の画素は、その対向電極線と隣接する2本の走査線により駆動される。例えば、第1水平ラインのCOM1に隣接する走査線はG1とG2である。この時、例えば、第1水平ラインのCOM1に接続される画素のうち、奇数番目の信号線に接続される画素DOT#0のスイッチング素子SWのゲート端子は、走査線G1に接続され、偶数番目の信号線に接続される画素DOT#Eのスイッチング素子SWのゲート端子は、走査線G2に接続される。ここでは、1画素づつ交互にG1とG2に接続したが、この周期は任意に設定してよい。

30

【0113】

第2水平ライン以降も同様に接続されるため、走査線Gは垂直方向の画素数より1本多く必要となる。また、各画素3のスイッチング素子SWのドレイン端子は、対応する信号線Dに接続され、各画素3の対向電極は対応する対向電極線COMに接続される。

40

【0114】

対向電極駆動回路402は、DSWAとDSWBの2個1組のスイッチング回路n個で構成される。このDSWAとDSWBは、TFTなどの3端子素子が用いられ、このTFTはアモルファスSiや多結晶Siや単結晶Siなどで形成される。DSWAとDSWBのソース端子は、共に対応する対向電極線COMに接続される。一方、ドレイン端子は、第1の対向電極信号線COMAと第2の対向電極信号線COMBに、例えば、1水平ライン毎に交互に接続されている。

【0115】

図7の液晶表示装置の場合には、奇数ラインはCOMAに接続されており、偶数ラインはCOMBに接続されている。また、DSWAとDSWBのゲート端子は、このソース端子に接続される対向電極線を共有する画素を制御する2本の走査線に各々接続される。

【0116】

50

次に、図8と図9を参照して、実施例3の液晶表示装置の駆動方法を説明する。以下の説明では、スイッチング素子SWとスイッチング素子DSWA及びDSWBのTFTとして、例えば、n型TFTを用いた場合について説明する。また、以下の説明では、例えば、信号駆動回路2が出力する信号電圧の極性が1水平周期毎に反転する対向電極反転駆動について説明する。

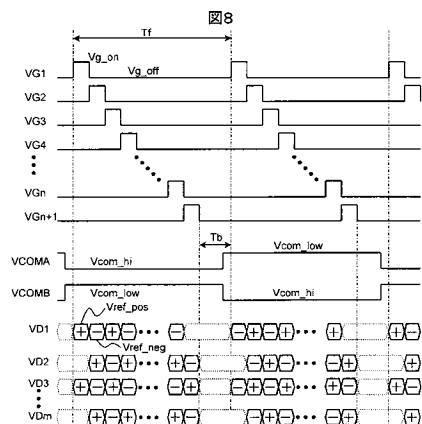

#### 【0117】

図8は、走査駆動回路102と信号駆動回路2と対向電極信号生成回路5が出力する各信号のタイミングを示す図である。VG1、VG2、VG3、VG4、・・・、VGn、VGn+1は、走査線G1、G2、G3、G4、・・・、Gn、Gn+1に印加される走査信号を表している。

#### 【0118】

走査駆動回路102は、少なくとも1フレーム期間Tfに1回は各走査線にVg#onを印加する。同図においては、G1からGn+1まで順次Vg#onを印加した様子を示している。走査駆動回路102は、この動作を毎フレーム繰り返す。

#### 【0119】

VCOMAとVCOMBは、対向電極信号生成回路5が生成してCOMAとCOMBに夫々出力する対向電極信号である。VCOMAとVCOMBは、正極性の対向電極電圧であるVcom#hiと負極性の対向電極電圧であるVcom#lowとの反転信号である。このVCOMAとVCOMBは、1フレーム期間の中のプランギング期間Tbで極性を反転する。したがって、VCOMAとVCOMBは交流周波数が、フレーム周波数の1/2となる。また、VCOMAとVCOMBは、少なくとも画素に信号電圧を書込む期間は逆極性の対向電極電圧である。

#### 【0120】

また、VD1、VD2、・・・、VDmは、信号駆動回路2が信号線D1、D2、・・・、Dmに印加する信号電圧を示している。ここで、Vref#posは正極性の信号電圧を示しており、Vref#negは負極性の信号電圧を示している。この信号駆動回路2は、走査駆動回路102が選択した画素に対応する表示信号に応じた信号電圧を、該画素が選択されている期間に合わせて出力する。その際の信号電圧の極性は、その画素の対向電極に印加される対向電極信号の極性に依存し、Vcom#hiが印加される画素には、正極性の信号電圧Vref#posが出力され、Vcom#lowが印加される画素には、負極性の信号電圧Vref#negが出力される。

#### 【0121】

図8の前半に示される1フレーム期間においては、奇数ラインの対向電極線がDSWAとDSWBを介してCOMAに接続されており、COMAの信号がVcom#hiであるため、奇数ラインの対向電極線に接続されている画素が選択されている期間、この画素に接続する信号線には正極性の信号電圧Vref#posが出力される。

#### 【0122】

一方、偶数ラインの対向電極線は、DSWAとDSWBを介してCOMBに接続されており、COMBの信号がVcom#lowであるため、偶数ラインの対向電極線に接続されている画素が選択されている期間には、この画素に接続する信号線に負極性の信号電圧Vref#negが出力される。次のフレーム期間では、VCOMAとVCOMBの信号極性が反転するため、各画素に出力される信号電圧の極性も反転する。

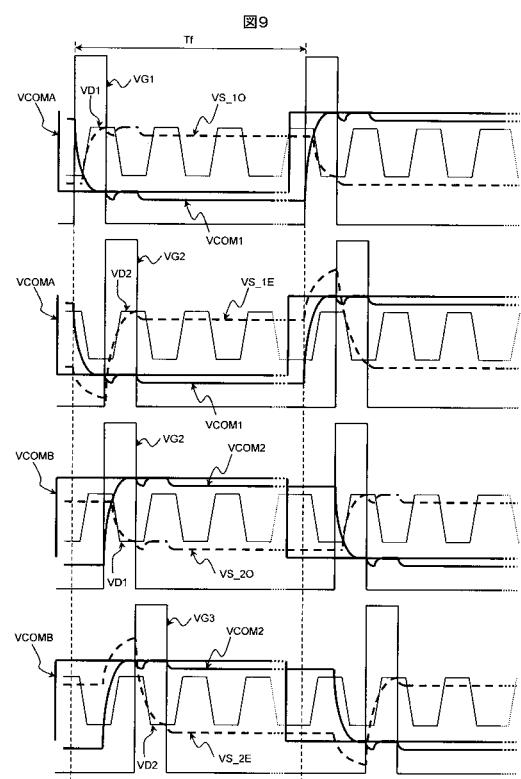

#### 【0123】

図9は、図8に示す各信号が、画素に印加された場合の、各画素の電圧波形を示した図である。図9は、例えば、信号線D1とD2に接続される画素のうち、対向電極線COM1に接続される画素と、対向電極線COM2に接続される画素の電圧波形を示した。

#### 【0124】

ここで、VS#1Oは信号線D1と対向電極線COM1とが接続される画素の画素電極電圧を示し、VS#1Eは信号線D2と対向電極線COM1とが接続される画素の画素電極電圧を示し、VS#2Oは信号線D1と対向電極線COM2とが接続される画素の画素電極電圧を示し、VS#2Eは信号線D2と対向電極線COM2とが接続される画素の画素電極電圧を示している。また、VCOM1は第1水平ラインの対向電極線COM1の電圧信号を示し、VCOM2は第2水平ラインの対向電極線COM2の電圧信号を示す。

10

20

30

40

50

## 【0125】

まず、図9の前半に示すフレーム期間において、第1水平ラインの奇数番目の信号線に接続される画素が走査信号VG1により選択されると、対向電極COM1には対向電極駆動回路402内のDSWAを介してVCOMAが印加される。よって、対向電極COM1の電圧VCOM1はVcom#hiに収束していく。

## 【0126】

画素電極は、スイッチング素子SWを介して信号線D1により該画素の表示信号に応じた正極性の信号電圧VD1が印加され、VS#10はVD1に収束する。そして、VG1の選択期間終了後は、スイッチング素子SW及びCOM1に接続されるDSWAが共にオフ状態となるため、画素電極と対向電極COM1はフローティング状態となるが、選択期間で印加された正極性の信号電圧は液晶容量C1cと保持容量Cstgに保持される。

10

## 【0127】

次に、走査信号VG2によりG2に選択信号が印加されると、第1水平ラインの偶数番目の信号線に接続される画素と、第2水平ラインの奇数番目の信号線に接続される画素とが選択状態となる。

## 【0128】

まず、第1水平ラインの対向電極線COM1と偶数番目の信号線D2に接続される画素において、COM1には対向電極駆動回路402内のDSWBを介してVCOMAが印加されるためVcom#hiに収束する。画素電極は、スイッチング素子SWを介して信号線D2により該画素の表示信号に応じた正極性の信号電圧VD2が印加され、VS#1Eは信号電圧であるVD2に収束する。

20

## 【0129】

一方、第2水平ラインの対向電極線COM2と奇数番目の信号線D1に接続される画素において、COM2は対向電極駆動回路402内のDSWAを介してVCOMBが印加されるためVcom#lowに収束する。画素電極は、スイッチング素子SWを介して信号線D1により該画素の表示信号に応じた負極性の信号電圧VD1が印加され、VS#20は信号電圧であるVD1に収束する。

30

## 【0130】

そして、VG2の選択期間終了後は、画素のスイッチング素子SWとCOM1に接続されるDSWBと、COM2に接続されるDSWAが共にオフ状態となるため、画素電極と対向電極はフローティング状態となるが、選択期間で印加された正極性の信号電圧、又は負極性の信号電圧は液晶容量C1cと保持容量Cstgに保持される。

30

## 【0131】

次に、走査信号VG3によりG3に選択信号が印加されると、第2水平ラインの対向電極COM2と偶数番目の信号線D2に接続される画素が選択され、また、第3水平ラインの対向電極線COM3と奇数番目の信号線D1に接続される画素が選択される。

40

## 【0132】

まず、COM2とD2に接続される画素においては、対向電極COM2には対向電極駆動回路402内のDSWBを介してVCOMBが印加されるため、VCOM2はVcom#lowに収束する。画素電極は、スイッチング素子SWを介して信号線D2により該画素の表示信号に応じた負極性の信号電圧VD2が印加され、VS#2Eは信号電圧であるVD2に収束する。

40

## 【0133】

一方、波形は図示していないがCOM3とD1に接続される画素においては、対向電極COM3に対向電極駆動回路402内のDSWAを介してVCOMAが印加されるため、VCOM3はVcom#hiに収束する。画素電極は、スイッチング素子SWを介して信号線D1により該画素の表示信号に応じた正極性の信号電圧VD1が印加されて収束する。

50

## 【0134】

そして、VG3の選択期間終了後は、画素のスイッチング素子SWとCOM2に接続されるDSWBとCOM3に接続されるDSWAとが共にオフ状態となるため、画素電極と対向電極はフローティング状態となるが、選択期間で印加された正極性の信号電圧、又は負極性の信号電圧は液晶容量C1cと保持容量Cstgに保持される。保持期間中では、対向電極線と画素電極はフローティング状態であるために、VCOMAやVCOMBの極性が反転しても対向電極線の信

号極性が反転することはない。

【0135】

以上の動作を順次繰り返すことにより、1フレーム分の表示信号に対応し、かつ1水平ライン毎に極性を反転した信号電圧を、全水平ラインの画素に保持させることができる。図の後半に示すフレームでは、各水平ラインにおいて、対向電極信号の極性が反転し、信号駆動回路2から各画素に出力される信号電圧も逆極性となり、同様の駆動が行われることによって、1フレーム分の表示信号に対応した前フレームと逆極性の信号電圧を、全水平ラインの画素に保持させることができる。上記駆動をフレーム毎に繰り返すことで、1水平ライン毎に信号電圧の極性を反転させる対向電極反転駆動を実現することができる。

【0136】

本発明に係る実施例3の液晶表示装置及びその駆動方法を用いることにより、本発明は、次に示す(1)ないし(7)の特徴を有する。

【0137】

(1)各水平ラインの画素に信号電圧を保持させてから、次のフレーム期間で各水平ラインの信号電圧の書換えを行うまで対向電極電圧の極性が反転しないため、輝度傾斜や縦スマearerと呼ばれる表示ムラが抑制された高品位な表示を実現できる。

【0138】

(2)各水平ラインの対向電極に印加される対向電極電圧の極性反転が、フレーム期間内において1ライン単位で分散して発生するため、フレーム周波数が低い場合でもフリッカが起こりにくい高品位な液晶表示装置を得ることができる。

【0139】

(3)各水平ラインの画素に信号電圧を保持させてから、次のフレーム期間で信号電圧の書換えを行うまで対向電極電圧の極性が反転しないため、従来に比べ走査信号の電圧振幅を小さくすることが可能となり、素子の耐圧を下げることができる。また、走査信号の電圧振幅を小さくすることで素子の劣化を軽減できるため、高品位な液晶表示装置を得ることができる。

【0140】

(4)各水平ラインにおいて、非選択期間は対向電極線がフローティング状態であるため、対向電極線との間に寄生容量を持つ信号線の負荷が軽くなり、信号線に印加する信号電圧の目標電位までの収束時間が改善されるため、高速化に適した表示装置を得ることができる。

【0141】

(5)1本の走査線により選択される画素は、隣接する2本の対向電極線に分散して接続されているため、対向電極線の負荷が従来に比べ軽くなり、対向電極電圧の収束時間が改善されるため、高速化に適した表示装置を得ることができる。

【0142】

(6)対向電極駆動回路402の回路規模が小さいため、画素のスイッチング素子SWが形成される同一基板上に、対向電極駆動回路402を形成することが可能になる。

【0143】

(7)対向電極駆動回路402の制御を走査駆動回路102の走査信号で行うことができるため、対向電極駆動回路402の制御信号を新たに設ける必要がない。

【0144】

なお、以上の説明では対向電極反転駆動における信号電圧の極性反転周期を1水平周期として説明したが、この極性反転周期は任意に設定してもよい。これは、VCOMAとVCOMBの極性と交流周期を適宜設定することで実現できる。また、画素電極や対向電極における目標電圧への収束を向上するためにダブルゲート駆動と組み合わせることも可能である。

【0145】

また、図7の構成図において、アモルファスSiや多結晶Siを用いることで画素マトリクスと対向電極駆動回路、又は画素マトリクスと対向電極駆動回路と走査駆動回路とを同一基板上に形成し、その他の回路を基板周辺に配置することも可能である。

10

20

30

40

50

## 【0146】

また、本発明に係る実施例2で説明したセレクタ方式の走査駆動回路と、本発明に係る実施例3で説明した画素構成と対向電極駆動回路とを組み合わせても、上記実施例1から実施例3と同様の効果が得られる。

## 【図面の簡単な説明】

## 【0147】

【図1】実施例1における液晶表示装置の概略図

【図2】実施例1における駆動回路が出力する信号のタイミングチャート

【図3】実施例1における画素の各電極の電圧波形図

10

【図4】実施例2における液晶表示装置の概略図

【図5】実施例2における駆動回路が出力する信号のタイミングチャート

【図6】実施例2における画素の各電極の電圧波形図

【図7】実施例3における液晶表示装置の概略図

【図8】実施例3における駆動回路が出力する信号のタイミングチャート

【図9】実施例3における画素の各電極の電圧波形図

## 【符号の説明】

## 【0148】

1、101、102…走査駆動回路、2…信号駆動回路、3…画素、4、401、402…対向電極駆動回路、5、501…対向電極信号生成回路

## 【図1】

## 【図3】

## 【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

## フロントページの続き

|                          |              |            |

|--------------------------|--------------|------------|

| (51)Int.Cl. <sup>7</sup> | F I          | テーマコード(参考) |

| G 0 9 G 3/20             | G 0 9 G 3/20 | 6 1 1 E    |

|                          | G 0 9 G 3/20 | 6 1 2 T    |

|                          | G 0 9 G 3/20 | 6 2 1 B    |

|                          | G 0 9 G 3/20 | 6 2 2 G    |

|                          | G 0 9 G 3/20 | 6 2 2 K    |

|                          | G 0 9 G 3/20 | 6 2 4 C    |

|                          | G 0 9 G 3/20 | 6 2 4 E    |

|                          | G 0 9 G 3/20 | 6 8 0 F    |

F ターム(参考) 2H092 GA14 GA59 JA24 JB14 NA01 PA06

2H093 NA16 NA33 NA43 NC09 NC34 ND09 ND10 ND15 ND49 NE03

5C006 AC11 AC25 AC26 AF42 AF50 AF71 AF73 BA19 BB16 BC03

BC06 BC20 FA14 FA23 FA41 FA46

5C080 AA10 BB05 DD06 DD22 FF01 FF11 JJ02 JJ04

## 【要約の続き】

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP2005300948A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2005-10-27 |

| 申请号            | JP2004117518                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 申请日     | 2004-04-13 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 日立显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| [标]发明人         | 萬場則夫<br>工藤泰幸<br>庄司孝志                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 发明人            | 萬場 則夫<br>工藤 泰幸<br>庄司 孝志                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G02F1/1343 G02F1/133 G02F1/1345 G02F1/1368 G09G3/20 G09G3/36 G09G5/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| CPC分类号         | G09G3/3614 G09G2320/0233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/1343 G02F1/1345 G02F1/1368 G09G3/20.611.E G09G3/20.612.T<br>G09G3/20.621.B G09G3/20.622.G G09G3/20.622.K G09G3/20.624.C G09G3/20.624.E G09G3/20.680.F                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/GA59 2H092/JA24 2H092/JB14 2H092/NA01 2H092/PA06 2H093/NA16 2H093/NA33 2H093/NA43 2H093/NC09 2H093/NC34 2H093/ND09 2H093/ND10 2H093/ND15 2H093/ND49 2H093/NE03 5C006/AC11 5C006/AC25 5C006/AC26 5C006/AF42 5C006/AF50 5C006/AF71 5C006/AF73 5C006/BA19 5C006/BB16 5C006/BC03 5C006/BC06 5C006/BC20 5C006/FA14 5C006/FA23 5C006/FA41 5C006/FA46 5C080/AA10 5C080/BB05 5C080/DD06 5C080/DD22 5C080/FF01 5C080/FF11 5C080/JJ02 5C080/JJ04 2H192/AA24 2H192/DA12 2H192/GD61 2H193/ZA04 2H193/ZA07 2H193/ZA09 2H193/ZB08 2H193/ZB09 2H193/ZB14 2H193/ZC04 2H193/ZC15 2H193/ZD32 2H193/ZF44 2H193/ZF59 2H193/ZF60 2H193/ZP03 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

### 摘要(译)

在液晶显示装置中，在保持信号电压后的消隐期间中，在每一帧期间使对置电极信号反转时，会产生亮度不均，垂直拖尾等显示不均，图像品质下降。此外，如果帧频率低，则可能会发生闪烁。与多条扫描线(G1, G2至Gn)相交的多条信号线(D1, D2至Dn)，与扫描线平行的多条对电极线(COM1, COM2至COMn)，在具有布置在交叉点处的多个像素(3)的显示装置中，用于将扫描信号施加到扫描线的扫描驱动电路(1)和用于将信号电压施加到信号线的信号驱动电路(2)，对电极信号产生电路(5)，其产生对电极信号，该对电极信号是正对电极电压(VCOMA)和负对电极电压(VCOMB)以及对电极线的对电极电压的反相信号。提供用于施加电压的对电极驱动电路(4)，并且由从扫描驱动电路输出的扫描信号来控制对电极驱动电路(4)。[选型图]图