(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-173592

(P2005-173592A)

(43) 公開日 平成17年6月30日(2005.6.30)

(51) Int.Cl.<sup>7</sup>**G09G 3/36**

**G02F 1/133**

**G09G 3/20**

F 1

G09G 3/36

G02F 1/133 550

G09G 3/20 611F

G09G 3/20 612J

G09G 3/20 612R

テーマコード(参考)

2H093

5C006

5C080

審査請求 有 請求項の数 63 O L (全 36 頁) 最終頁に続く

(21) 出願番号 特願2004-349838 (P2004-349838)

(22) 出願日 平成16年12月2日 (2004.12.2)

(31) 優先権主張番号 2003-090301

(32) 優先日 平成15年12月11日 (2003.12.11)

(33) 優先権主張国 韓国(KR)

(31) 優先権主張番号 2004-029611

(32) 優先日 平成16年4月28日 (2004.4.28)

(33) 優先権主張国 韓国(KR)

(31) 優先権主張番号 2004-029612

(32) 優先日 平成16年4月28日 (2004.4.28)

(33) 優先権主張国 韓国(KR)

(71) 出願人 501426046

エルジー・フィリップス エルシーテー

カンパニー、リミテッド

大韓民国 ソウル、ヨンドゥンポーク、ヨ

イドードン 20

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100085176

弁理士 加藤 伸晃

(74) 代理人 100106703

弁理士 産形 和央

(74) 代理人 100094112

弁理士 岡部 謙

(74) 代理人 100096943

弁理士 白井 伸一

最終頁に続く

(54) 【発明の名称】データ駆動集積回路及びその駆動方法とそれを利用した表示装置

## (57) 【要約】

【課題】本発明はデータ駆動集積回路及びその駆動方法とそれを利用した液晶表示装置を提供する。

【解決手段】この液晶表示装置はデータラインなどに画素データを供給するデータ出力チャンネル群を含んでダミー・データ出力チャンネル群を有するデータ集積回路と、前記ダミー・データ出力チャンネル群の出力チャンネルを選択するためのチャンネル選択部とを具備して；前記チャンネル選択部によって選択される前記ダミー・データ出力チャンネルを通して前記画素データが前記データラインなどに供給する。

【選択図】図4

**【特許請求の範囲】****【請求項 1】**

データ駆動集積回路を持つ表示装置において、前記データ駆動集積回路が、前記表示装置で要求される解像度に従ってデータラインの数に対応して画素データを供給するデータ出力チャンネルを含んで、少なくとも2個の領域を持つデータ出力チャンネルグループと、画素データが供給されない他の出力チャンネルを含む出力チャンネルと、前記データ出力チャンネルを選択する選択部とを具備することを特徴とする表示装置。

**【請求項 2】**

前記データ出力チャンネルの数は前記データ駆動集積回路にプログラム化されたことを特徴とする請求項1記載の表示装置。 10

**【請求項 3】**

前記データ出力チャンネルを選択するためのチャンネル選択信号を発生して供給する選択信号発生部と、前記データ駆動集積回路を制御して前記画素データを供給するタイミング制御部をさらに具備することを特徴とする請求項1記載の表示装置。

**【請求項 4】**

前記選択信号発生部は第1及び第2電圧源のそれぞれと接続されて前記チャンネル選択信号を発生する第1及び第2選択端子を含むことを特徴とする請求項3記載の表示装置。 20

**【請求項 5】**

前記データ駆動集積回路はサンプリング信号を順次的に供給するシフトレジスタ部と、前記シフトレジスタ部からのサンプリング信号に従って画素データをラッチするためのラッチと、前記ラッチからの前記画素データをアナログ画素データに変換するデジタル-アナログ変換部と、前記デジタル-アナログ変換部からの前記画素データをバッファリングして前記多数のデータラインに出力するためのバッファ部をもっと具備することを特徴とする請求項1記載の表示装置。 20

**【請求項 6】**

前記第1及び第2選択端子は第1及び第2論理値を発生して、前記第1論理値であれば前記出力チャンネルの総数N(Nは定数)より小さな1個の出力チャンネルを、前記第2論理値であれば前記1個より小さなJ個の出力チャンネルを前記データ出力チャンネルで選択することを特徴とする請求項4記載の表示装置。 30

**【請求項 7】**

前記第1及び第2選択端子は第1乃至第4論理値を発生して、前記第4論理値であれば前記出力チャンネルの総数N(Nは定数)より小さな1個を、前記第3論理値であれば前記Iより小さなJ個を、前記第2論理値であれば前記Jより小さなK個を、前記第1論理値であれば前記Kより小さなL個を前記データ出力チャンネルで選択することを特徴とする請求項4記載の表示装置。 30

**【請求項 8】**

前記データ出力チャンネルグループは一番目の出力チャンネルからI、J、K、L番目の中からいざれか一つまでの出力チャンネルを含むことを特徴とする請求項7記載の表示装置。

**【請求項 9】**

前記選択信号発生部は前記データラインの数、前記要求される解像度に対応するデータ集積回路の個数、前記データ集積回路が実装されたテープキャリアパッケージの幅、前記タイミング制御部と前記データ駆動集積回路の間のデータ送信ラインの数の中から少なくとも一つの条件に沿って前記チャンネル選択信号を発生することを特徴とする請求項3記載の表示装置。 40

**【請求項 10】**

前記選択信号発生部は前記チャンネル選択信号を発生するスイッチング素子を具備することを特徴とする請求項3記載の表示装置。

**【請求項 11】**

前記選択信号発生部は前記チャンネル選択信号を発生するディープスイッチを具備する 50

ことを特徴とする請求項 3 記載の表示装置。

【請求項 1 2】

前記他の出力チャンネルはダミーチャンネルであることを特徴とする請求項 1 記載の表示装置。

【請求項 1 3】

前記ダミーチャンネルはフロー・ティングされることを特徴とする請求項 1 2 記載の表示装置。

【請求項 1 4】

前記ダミーチャンネルは一定常数の電圧に設定されたことを特徴とする請求項 1 2 記載の表示装置。

【請求項 1 5】

前記他の出力チャンネルは前記データ出力チャンネルグループの少なくとも 2 個領域の間に位することを特徴とする請求項 1 記載の表示装置。

【請求項 1 6】

前記データ出力チャンネルグループの少なくとも 2 個領域は同一な数のデータ出力チャンネルを持つことを特徴とする請求項 1 記載の表示装置。

【請求項 1 7】

表示装置の多数のデータラインと接続されたデータ駆動集積回路において、前記表示装置で要求される解像度に沿ってデータラインの数に対応して画素データを供給する M (M は N 以下の定数) 個のデータ出力チャンネルを含んで、少なくとも 2 個の領域を持つデータ出力チャンネルグループと、画素データが供給されない (N-M) 個の出力チャンネルを含む N 個の出力チャンネルを具備することを特徴とするデータ駆動集積回路。

【請求項 1 8】

前記 M 個のデータ出力チャンネルを選択するためのチャンネル選択信号を発生する選択信号発生部をさらに具備することを特徴とする請求項 1 7 記載のデータ駆動集積回路。

【請求項 1 9】

前記チャンネル選択部は前記チャンネル選択信号に沿って前記データ出力チャンネルグループに含まれるデータ出力チャンネルの数を可変させることを特徴とする請求項 1 8 記載のデータ駆動集積回路。

【請求項 2 0】

前記選択信号発生部は前記データラインの数、前記データ集積回路の個数、前記データ集積回路が実装されるテープキャリアパッケージの幅、前記画素データの入力ライン数の中から少なくとも一つの条件に沿って前記チャンネル選択信号を発生することを特徴とする請求項 1 8 記載のデータ駆動集積回路。

【請求項 2 1】

前記チャンネル選択部は第 1 及び第 2 論理値を発生して、前記第 1 論理値であれば前記 N より小さな I 個の出力チャンネルを、前記第 2 論理値であれば前記 I 個より小さな J 個の出力チャンネルを前記データ出力チャンネルで選択することを特徴とする請求項 1 8 記載のデータ駆動集積回路。

【請求項 2 2】

前記チャンネル選択部は第 1 乃至第 4 論理値を発生して、前記第 4 論理値であれば前記 N より小さな I 個を、前記第 3 論理値であれば前記 I より小さな J 個を、前記第 2 論理値であれば前記 J より小さな K 個を、前記第 1 論理値であれば前記 K より小さな L 個を前記データ出力チャンネルで選択することを特徴とする請求項 1 8 記載のデータ駆動集積回路。

【請求項 2 3】

前記データ出力チャンネルグループは一番目のデータ出力チャンネルから I、J、K、L 番目の中からいづれか一つまでのデータ出力チャンネルを含むことを特徴とする請求項 2 記載のデータ駆動集積回路。

【請求項 2 4】

10

20

30

40

50

前記(N-M)個の出力チャンネルは前記データ出力チャンネルグループの少なくとも2個の領域の間に位することを特徴とする請求項17記載のデータ駆動集積回路。

【請求項25】

前記データ出力チャンネルグループの少なくとも2個領域は同一な数のデータ出力チャンネルを持つことを請求項17記載のデータ駆動集積回路。

【請求項26】

前記(N-M)個の出力チャンネルはフローディングされることを特徴とする請求項17記載のデータ駆動集積回路。

【請求項27】

前記(N-M)個の出力チャンネルは一定常数の電圧に設定されたことを特徴とする請求項17記載のデータ駆動集積回路。 10

【請求項28】

前記選択信号発生部は第1及び第2電圧源のそれぞれと接続されて前記チャンネル選択信号を発生する第1及び第2選択端子を含むことを特徴とする請求項18記載のデータ駆動集積回路。

【請求項29】

前記選択信号発生部は前記チャンネル選択信号を発生するスイッチを具備することを特徴とする請求項18記載のデータ駆動集積回路。

【請求項30】

前記選択信号発生部は前記チャンネル選択信号を発生するディープスイッチを具備することを特徴とする請求項18記載のデータ駆動集積回路。 20

【請求項31】

サンプリング信号を順次的に供給するシフトレジスタ部と、前記シフトレジスタ部からのサンプリング信号に従って画素データをラッチするためのラッチと、前記ラッチからの前記画素データをアナログ画素データに変換するデジタル-アナログ変換部と、前記デジタル-アナログ変換部からの前記画素データをバッファリングして前記多数のデータラインに出力するためのバッファ部をもっと具備することを特徴とする請求項17記載のデータ駆動集積回路。

【請求項32】

第1乃至第3出力チャンネルグループを含むN(Nは定数)個の出力チャンネルと、表示装置で要求される解像度に従って画素データが供給される多数のデータラインに対応する第1及び第3出力チャンネルグループと、ダミー出力チャンネルにデ-セイブルされる第2出力チャンネルグループを選択するチャンネル選択部を具備して、前記第2出力チャンネルグループは前記第1及び第3出力チャンネルグループの間に位することを特徴とするデータ駆動集積回路。 30

【請求項33】

前記第2出力チャンネルグループは前記N個の出力チャンネルの中からいずれか一つの出力チャンネルを含むことを特徴とする請求項32記載のデータ駆動集積回路。

【請求項34】

前記第2出力チャンネルグループは前記N個の出力チャンネル中(N/2)個の出力チャンネルを含むことを特徴とする請求項32記載のデータ駆動集積回路。 40

【請求項35】

前記第2出力チャンネルグループは前記N個の出力チャンネルの中でN番目の出力チャンネルを含むことを特徴とする請求項32記載のデータ駆動集積回路。

【請求項36】

前記出力チャンネル選択のためのチャンネル選択信号を発生する選択信号発生部をさらに具備することを特徴とする請求項32記載のデータ駆動集積回路。

【請求項37】

サンプリング信号を順次的に供給するシフトレジスタ部と、前記シフトレジスタ部からのサンプリング信号に従って画素データをラッチするためのラッチと、前記ラッチからの50

前記画素データをアナログ画素データに変換するデジタル-アナログ変換部と、前記デジタル-アナログ変換部からの前記画素データをバッファリングして前記多数のデータラインに出力するためのバッファ部とをもつと具備することを特徴とする請求項32記載のデータ駆動集積回路。

【請求項38】

前記選択信号発生部は前記データラインの数、前記データ集積回路の個数、前記データ集積回路が実装されるテープキャリアパッケージの幅、前記画素データの入力ライン数の中から少なくとも一つの条件に沿って前記チャンネル選択信号を発生することを特徴とする請求項36記載のデータ駆動集積回路。

【請求項39】

前記選択信号発生部は第1及び第2電圧源のそれぞれと接続されて前記チャンネル選択信号を発生する第1及び第2選択端子を含むことを特徴とする請求項36記載のデータ駆動集積回路。

【請求項40】

前記第1及び第2出力チャンネルグループは同一な数の出力パネルを持つことを特徴とする請求項32記載のデータ駆動集積回路。

【請求項41】

前記第1出力チャンネルグループは一番目からI1番目、I2番目、I3番目(ただ、 $1 < I1 < I2 < I3 < N$ )中からいざれかまでの出力チャンネルを含むことを特徴とする請求項32記載のデータ駆動集積回路。

【請求項42】

前記第3出力チャンネルグループはN番目からJ1番目、J2番目、J3番目(ただ、 $I3 < J1 < J2 < J3 < N$ )中からいざれかまでの出力チャンネルを含むことを特徴とする請求項41記載のデータ駆動集積回路。

【請求項43】

前記出力チャンネルの中でI1+1番目からJ3-1番目まで、I2+1番目からJ2-1番目まで、I3+1番目からJ1-1番目の中である一グループは前記ダミー出力チャンネルであることを特徴とする請求項42記載のデータ駆動集積回路。

【請求項44】

前記ダミー出力チャンネルはフローティングされることを特徴とする請求項43記載のデータ駆動集積回路。

【請求項45】

前記ダミー出力チャンネルは一定常数の電圧に設定されたことを特徴とする請求項43記載のデータ駆動集積回路。

【請求項46】

前記選択信号発生部は前記選択制御信号を発生するスイッチを具備することを特徴とする請求項36記載のデータ駆動集積回路。

【請求項47】

前記選択信号発生部は前記選択制御信号を発生するディープスイッチを具備することを特徴とする請求項36記載のデータ駆動集積回路。

【請求項48】

前記出力チャンネルの数はプログラム化されたことを特徴とする請求項32記載のデータ駆動集積回路。

【請求項49】

スタートパルスをシフトさせてサンプリング信号を発生するためのN(ただ、Nは陽の定数)個のシフトレジスタから構成されたシフトレジスタ部を含むデータ駆動集積回路において、第1及び第2出力チャンネル群から構成された出力チャンネル部と、前記シフトレジスタ部で前記第1出力チャンネル群と対応される第1群のシフトレジスタからの出力信号を選択して前記第1出力チャンネル群の中、一部のデータラインと接続されられる第1データ出力チャンネル群を選択する第1選択部と、前記第1選択部からの出力信号を前記

10

20

30

40

50

第2出力チャンネル群と対応される第2群のシフトレジスタに供給して前記第2出力チャンネル群の中、他のデータラインと接続される第2データ出力チャンネル群を選択する第2選択部とを具備することを特徴とするデータ駆動集積回路。

【請求項50】

前記第1及び第2データ出力チャンネル群の選択のためのチャンネル選択信号を発生する選択信号発生部をさらに具備することを特徴とする請求項49記載のデータ駆動集積回路。

【請求項51】

前記選択信号発生部は前記データラインの数、前記データ集積回路の個数、前記データ集積回路が実装されるテーブキャリアパッケージの幅、前記データ集積回路のデータ入力欄である数の中から少なくとも一つの条件に沿って前記チャンネル選択信号を発生することを特徴とする請求項50記載のデータ駆動集積回路。

【請求項52】

前記選択信号発生部は電圧源及び基底電圧源に接続されて前記チャンネル選択信号を発生する選択端子を具備することを特徴とする請求項50記載のデータ駆動集積回路。

【請求項53】

前記選択信号発生部は前記チャンネル選択信号を発生するスイッチを具備することを特徴とする請求項50記載のデータ駆動集積回路。

【請求項54】

前記選択信号発生部は前記チャンネル選択信号を発生するディープスイッチを具備することを特徴とする請求項50記載のデータ駆動集積回路。

【請求項55】

前記第1及び第2データ出力チャンネルは同一な出力チャンネルを持つことを特徴とする請求項49記載のデータ駆動集積回路。

【請求項56】

前記第1選択部は前記チャンネル選択信号に沿って前記N個のシフトレジスタの第I1(ただし、I1は1より大きい陽の定数)番目、I2(ただし、I2はI1より大きい陽の定数)番目及びI3(ただし、I3はI2より大きくてNより小さな陽の定数)番目シフトレジスタの出力信号の中からいずれかを選択する第1マルチフレクサーを具備することを特徴とする請求項49記載のデータ駆動集積回路。

【請求項57】

前記第2選択部は、前記チャンネル選択信号に沿って第1マルチフレクサーからの出力信号を出力するデマルチプレクサーと、前記チャンネル選択信号に沿って前記デマルチプレクサーからの出力信号と前記N個のシフトレジスタの第J1-1(ただし、J1はI3より大きい陽の定数)番目シフトレジスタの出力信号の中からいずれかを選択して第J1番目シフトレジスタに供給する第2マルチフレクサーと、前記チャンネル選択信号に沿って前記デマルチプレクサーからの出力信号と前記N個のシフトレジスタの第J2-1(ただし、J2はJ1より大きい陽の定数)番目シフトレジスタの出力信号の中からいずれかを選択して第J2番目シフトレジスタに供給する第3マルチフレクサーと、前記チャンネル選択信号に沿って前記デマルチプレクサーからの出力信号と前記N個のシフトレジスタの第J3-1(ただし、J3はJ2より大きくてNより小さな陽の定数)番目シフトレジスタの出力信号の中からいずれかを選択して第J3番目シフトレジスタに供給する第4マルチフレクサーとを具備することを特徴とする請求項56記載のデータ駆動集積回路。

【請求項58】

前記チャンネル選択部は前記チャンネル選択信号に応答して前記第1出力チャンネル群の中、一番目からI1番目、I2番目、I3番目(ただし、 $1 < I1 < I2 < I3 < N$ )出力チャンネルの中からいずれか一つまでを第1データ出力チャンネル群で選択することを特徴とする請求項57記載のデータ駆動集積回路。

【請求項59】

前記チャンネル選択部は前記チャンネル選択信号に応答して前記第2出力チャンネル群

10

20

30

40

50

の中、N番目からJ1番目、J2番目、J3番目(ただし、 $I_3 < J_1 < J_2 < J_3 < N$ )中からいずれか一つまでを第2データ出力チャンネル群で選択することを特徴とする請求項58記載のデータ駆動集積回路。

**【請求項60】**

前記出力チャンネルの中で $I_1 + 1$ 番目から $J_3 - 1$ 番目まで、 $I_2 + 1$ 番目から $J_2 - 1$ 番目まで、 $I_3 + 1$ 番目から $J_1 - 1$ 番目の中である一群は前記ダミー出力チャンネルであることを請求項59記載のデータ駆動集積回路。

**【請求項61】**

前記ダミー出力チャンネルはフローティングされたことを特徴とする請求項60記載のデータ駆動集積回路。

10

**【請求項62】**

前記ダミー出力チャンネルは一定常数の電圧に設定されたことを特徴とする請求項60記載のデータ駆動集積回路。

**【請求項63】**

表示装置で要求される解像度を決める段階と、多数の出力チャンネルの中で前記要求される解像度に対応して画素データが供給されられるデータ出力チャンネルを含んで、少なくとも2個の領域を持つデータ出力チャンネルグループを選択する段階と、前記選択されたデータ出力チャンネルグループを通じてデータラインで画素データを供給して、非選択された出力チャンネルでは画素データを供給しない段階とを含むことを特徴とする表示装置に含まれたデータ駆動集積回路の駆動方法。

20

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明はデータ駆動集積回路を利用する表示装置に関することで、特に作業性の向上及び製造費用を節減することができるようとしたデータ駆動集積回路及びその駆動方法とそれを利用した表示装置に関するものである。

**【背景技術】**

**【0002】**

通常の液晶表示装置は電界を利用して液晶の光透過率を調節することで画像を表示する。

30

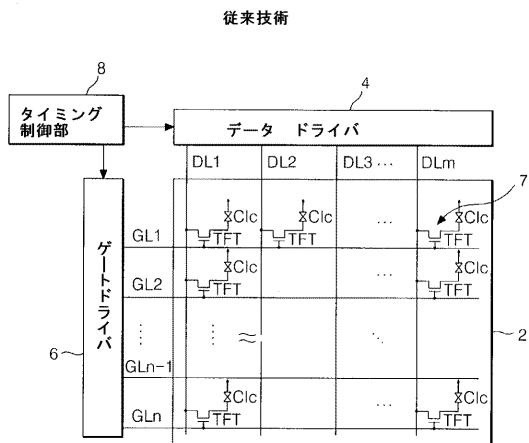

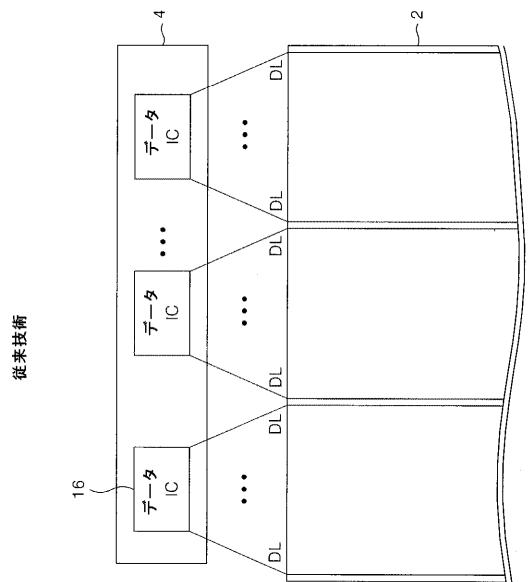

このために、液晶表示装置は図1に示したように液晶セルなどがマトリックス形態で配列された液晶パネル(2)と、液晶パネル(2)のゲートラインなど(GL1乃至GLn)を駆動するためのゲート・ドライバ(6)と、液晶パネル(2)のデータラインなど(DL1乃至DLm)を駆動するためのデータ・ドライバ(4)と、ゲート・ドライバ(6)とデータ・ドライバ(4)を制御するためのタイミング制御部(8)とを具備する。

**【0003】**

液晶パネル(2)はゲートラインなど(GL1乃至GLn)とデータラインなど(DL1乃至DLm)の交差部毎に形成された薄膜トランジスタ(TFT)と、薄膜トランジスタ(TFT)と接続された液晶セル(7)とを具備する。薄膜トランジスタ(TFT)はゲートライン(GL)からのスキャン信号、即ちゲート・ハイ電圧(VGH)が供給される場合、ターン・オンされてデータライン(DL)からの画素信号を液晶セル(7)に供給する。そして、薄膜トランジスタ(TFT)はゲートライン(GL)からゲート・ロー電圧(VGL)が供給される場合、ターン・オフされて液晶セル(7)に充電された画素信号が維持されるようにする。

40

**【0004】**

液晶セル(7)は等価的に液晶容量のキャパシティで表現されて、液晶を間に置いて対面する共通電極と薄膜トランジスタ(TFT)に接続された画素電極を含む。そして、液晶セル(7)は充電された画素信号が次の画素信号が充電される際まで安定的に維持されるようにするためにストリッジ・キャパシティとを更に具備する。このストリッジ・キャパシティは画素電極と以前段のゲートラインの間に形成される。このような液晶セル(

50

7) は薄膜トランジスタ ( TFT ) を通して充電される画素信号につれて誘電異方性を有する液晶の配列状態が可変して光透過率を調節することでグラデーションを具現するようになる。

#### 【 0 0 0 5 】

タイミング制御部 ( 8 ) は図示されないビデオ・カードから供給される同期信号 ( V , H ) を利用してゲート制御信号など ( GSP , GSC , GOE ) 及びデータ制御信号など ( SSP , SSC , SOE , POL ) を発生する。ゲート制御信号など ( GSP , GSC , GOE ) はゲート・ドライバ ( 6 ) に供給されてゲート・ドライバを制御するようになり、データ制御信号など ( SSP , SSC , SOE , POL ) はデータ・ドライバ ( 4 ) に供給されてデータ・ドライバを除去するようになる。共に、タイミング制御部 ( 8 ) は赤色 ( R ) 、緑色 ( G ) 及び青色 ( B ) の画素データ ( VD ) を整列してデータ・ドライバ ( 4 ) に供給する。

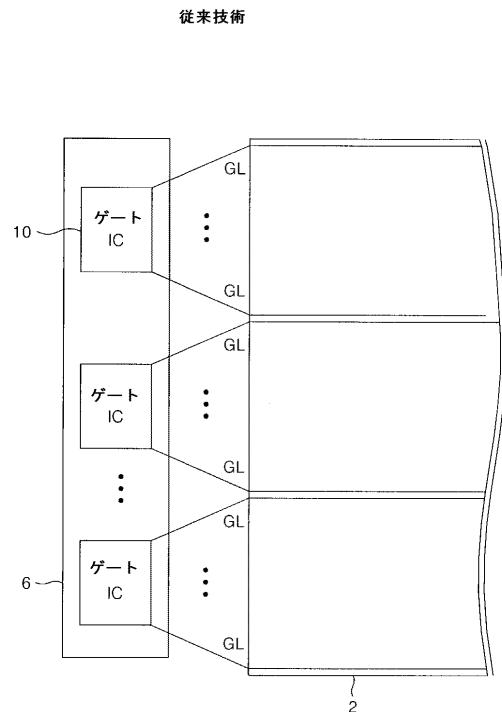

#### 【 0 0 0 6 】

ゲート・ドライバ ( 6 ) はゲートラインなど ( GL1 乃至 GLn ) を順次に駆動させる。このために、ゲート・ドライバ ( 6 ) は図 2 a のように多数のゲート集積回路 ( 以下、" I C " という ) ( 10 ) とを具備する。ゲート I C ( 10 ) などは自分に接続されたゲートラインなど ( GL1 乃至 GLn ) をタイミング制御部 ( 8 ) からの制御によって順次に駆動させる。もう一度言って、ゲート I C ( 10 ) などはタイミング制御部 ( 8 ) から供給されるゲート制御信号など ( GSP , GSC , GOE ) に応答してゲートラインなど ( GL1 乃至 GLn ) に順次にゲート・ハイ電圧 ( VGH ) を順次に供給する。

#### 【 0 0 0 7 】

具体的に、ゲート・ドライバ ( 6 ) はゲート・スタート・パルス ( GSP ) をゲート・シフト・クラック ( GSC ) につれてシフトさせてシフトパルスを発生する。そして、ゲート・ドライバ ( 6 ) はシフト・パルスに応答して水平期間毎に当たるゲートライン ( GL ) にゲート・ハイ電圧 ( VGH ) を供給するようになる。もう一度言って、シフトパルスは水平期間毎に一ラインずつシフトされて、ゲート I C ( 10 ) などの中のいずれか一つはシフトパルスに対応されて当たるゲートライン ( GL ) にゲート・ハイ電圧 ( VGH ) を供給する。この場合、ゲート I C ( 10 ) などはゲートラインなど ( GL1 乃至 GLn ) にゲート・ハイ電圧 ( VGH ) が供給されない残りの期間ではゲート・ロー電圧 ( VGL ) を供給する。

#### 【 0 0 0 8 】

データ・ドライバ ( 4 ) は水平期間毎に 1 ライン分ずつの画素信号をデータラインなど ( DL1 乃至 DLM ) に供給する。このために、データ・ドライバ ( 4 ) は図 2 b のように多数のデータ I C ( 16 ) などを具備する。データ I C ( 16 ) などはタイミング制御部 ( 8 ) から供給されるデータ制御信号など ( SSP , SSC , SOE , POL ) に応答してデータラインなど ( DL1 乃至 DLM ) に画素信号を供給する。この際、データ I C ( 16 ) などはタイミング制御部 ( 8 ) からの画素データ ( VD ) をガンマ電圧発生部 ( 図示しない ) からのガンマ電圧を利用してアナログ画素信号に変換して出力する。

#### 【 0 0 0 9 】

具体的に、データ I C ( 16 ) などはソース・スタート・パルス ( SSP ) をソース・シフト・クラック ( SSC ) につれてシフトさせてサンプリング信号を発生する。続いて、データ I C ( 16 ) などはサンプリング信号に応答して画素データ ( VD ) を一定の単位ずつ順次にラッチする。以後、ラッチされた 1 ライン分の画素データ ( VD ) をアナログ画素信号に変換してソース出力エナーブル信号 ( SOE ) のエナーブル期間にデータラインなど ( DL1 乃至 DLM ) に供給するようになる。この場合、データ I C ( 16 ) などは画素データ ( VD ) を極性制御信号 ( POL ) に応答して正極性または負極性の画素信号に変換するようになる。

#### 【 0 0 1 0 】

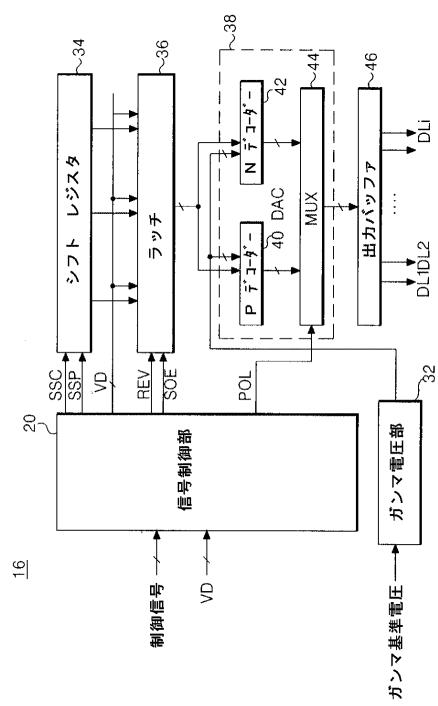

このために、データ I C ( 16 ) などのそれぞれは図 3 に示したように順次のサンプリング信号を供給するシフト・レジスタ部 ( 34 ) と、サンプリング信号に応答して画素デ

10

20

30

40

50

ータ ( V D ) を順次にラッチして同時に出力するラッチ部 ( 3 6 ) と、ラッチ部 ( 3 6 ) からの画素データ ( V D ) を画素電圧信号に変換するデジタル・アナログ変換部 ( 以下、" D A C 部" という ) ( 3 8 ) と、 D A C ( 3 8 ) からの画素電圧信号を緩衝して出力する出力バッパ部 ( 4 6 ) とを具備する。また、データ I C ( 1 6 ) などはタイミング制御部 ( 8 ) から供給される各種の制御信号など ( S S P , S S C , S O E , R E V , P O L など ) と画素データ ( V D ) を中継する信号制御部 ( 2 0 ) と、 D A C 部 ( 3 8 ) で必要とする正極性及び負極性のガンマ電圧などを供給するガンマ電圧部 ( 3 2 ) とを更に具備する。

#### 【 0 0 1 1 】

信号制御部 ( 2 0 ) はタイミング制御部 ( 図示しない ) からの各種の制御信号など ( S S P , S S C , S O E , R E V , P O L など ) と画素データ ( V D ) が当たる構成要素などで出力されるように制御する。

#### 【 0 0 1 2 】

ガンマ電圧部 ( 3 2 ) はガンマ基準電圧の発生部 ( 図示しない ) から入力される多数このガンマ基準電圧をグレイ別に細分化して出力する。

#### 【 0 0 1 3 】

シフト・レジスタ部 ( 3 4 ) に含まれたシフト・レジスタなどは信号制御部 ( 2 0 ) からのソース・スタート・パルス ( S S P ) をソース・シフト・クラック ( S S C ) につれてシフトさせてサンプリング信号に出力する。

#### 【 0 0 1 4 】

ラッチ部 ( 3 6 ) はシフト・レジスタ部 ( 3 4 ) からのサンプリング信号に応答して信号制御部 ( 2 0 ) からの画素データ ( V D ) を一定単位ずつ順次にサンプリングしてラッチするようになる。このために、ラッチ部 ( 3 6 ) は  $i$  (  $i$  は自然数 ) 個の画素データ ( V D ) をラッチするために  $i$  個のラッチなどで構成されて、ラッチなどのそれぞれは画素データ ( V D ) のビット数に対応する大きさを有する。特に、タイミング制御部 ( 8 ) は伝送周波数を減らすために画素データ ( V D ) をイーブン画素データとオード画素データに分けてそれぞれの伝送ラインを通して同時に出力するようになる。ここで、イーブン画素データとオード画素データのそれぞれは赤 ( R ) , 緑 ( G ) , 青 ( B ) 画素データを含む。これについてラッチ部 ( 3 6 ) はサンプリング信号毎に信号制御部 ( 2 0 ) を経由して供給されるイーブン画素データとオード画素データを同時にラッチするようになる。続いて、ラッチ部 ( 3 6 ) は信号制御部 ( 2 0 ) からのソース出力エナーブル信号 ( S O E ) に応答してラッチされた  $i$  個の画素データ ( V D ) を同時に出力する。この場合、ラッチ部 ( 3 6 ) はデータ反転選択信号 ( R E V ) に応答してトランジーション・ビット数が減らすように変造された画素データ ( V D ) などを復元させて出力するようになる。これはタイミング制御部 ( 8 ) でデータ伝送の際に電磁気的な干渉 ( E M I ) を最小化するためにトランジーションされるビット数が基準値を越す画素データ ( V D ) などはトランジーション・ビット数が減るように変造して供給するためである。

#### 【 0 0 1 5 】

D A C 部 ( 3 8 ) はラッチ部 ( 3 6 ) からの画素データ ( V D ) を同時に正極性及び負極性の画素電圧信号に変換して出力するようになる。このために、 D A C 部 ( 3 8 ) はラッチ部 ( 3 6 ) に共通接続された P ( P o s i t i v e ) デコーディング部 ( 4 0 ) 及び N ( N e g a t i v e ) デコーディング部 ( 4 2 ) と、 P デコーディング部 ( 4 0 ) オヨビ N デコーディング部 ( 4 2 ) の出力信号を選択するためのマルチプレクサ ( M U X ; 4 4 ) とを具備する。

#### 【 0 0 1 6 】

P デコーディング部 ( 4 0 ) に含まれる  $n$  個の P デコーダーなどはラッチ部 ( 3 6 ) から同時に入力される  $n$  個の画素データなどをガンマ電圧部 ( 3 2 ) からの正極性のガンマ電圧などを利用して正極性画素電圧信号に変換するようになる。N デコーディング部 ( 4 2 ) に含まれる  $i$  個の N デコーダーなどはラッチ部 ( 3 6 ) から同時に入力される  $i$  個の画素データなどをガンマ電圧部 ( 3 2 ) からの負極性ガンマ電圧などを利用して負極性の

10

20

30

40

50

画素電圧信号に変換するようになる。マルチブレクサ部(44)に含まれるi個のマルチブレクサなどは信号制御部(20)からの極性制御信号(POL)に応答してPデコーダー(40)からの正極性の画素電圧信号またはNデコーダー(42)からの負極性の画素電圧信号を選択して出力するようになる。

#### 【0017】

出力バッパ部(46)に含まれるi個の出力バッパなどはi個のデータラインなど(DL1乃至DLi)などに直列にそれぞれ接続された電圧ホロワーなどで構成される。このような出力バッパなどはDAC部(138)の画素電圧信号などを信号緩衝してデータラインなど(DL1乃至DLi)に供給するようになる。

#### 【0018】

このような従来の液晶表示装置は液晶パネル(2)の解像図についてデータ・ドライバ(4)が具備するデータI C(16)の出力チャンネルが違ってくる。これは、液晶パネル(2)の解像図別にデータライン(DL)に接続されることができる一定のチャンネルを有するデータI C(16)などが違ってくるためである。これについて、液晶パネル(2)の解像図別に相互異なる出力チャンネルを有する相互異なる数のデータI C(16)などを使用することで作業性の低下及び製造費用が浪費される短所がある。

#### 【0019】

これを詳細に説明すると、液晶パネル(2)の解像図がXGA級(1024×3)である液晶表示装置は3072個のデータライン(DL)数を有することで768個のデータ出力チャンネルを有する四つのデータI C(16)が必要になる。また、液晶パネル(2)の解像図がSXGA+級(1400×3)である液晶表示装置は4200個のデータライン(DL)数を有するので702個のデータ出力チャンネルを有する六つのデータI C(16)が必要にするようになる。この際、残りの12個のデータ出力チャンネルはダミーラインに処理される。また、液晶パネル(2)の解像図がWXGA級(1290×3)である液晶表示装置は3840個のデータライン(DL)の数を有するので642個のデータ出力チャンネルを有する六つのデータI C(16)が必要になる。この際、残る12個のデータ出力チャンネルはダミーラインに処理される。このように、液晶パネル(2)の解像図別に相互異なる出力チャンネルを有する異なるデータI C(16)などを使用すべきである。これについて、従来の液晶表示装置では作業性の低下及び製造比率の浪費される短所がある。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0020】

従って、本発明の目的は作業性の向上及び製造費用を節減することができるようになしたデータ駆動集積回路及びその駆動方法とそれを利用した表示装置に関するものである。

#### 【0021】

本発明の異なる目的は液晶パネルの解像図についてデータ駆動集積回路の出力チャンネルを制御することができるようにしたデータ駆動集積回路及びその駆動方法とそれを利用した表示装置に関するものである。

#### 【課題を解決するための手段】

#### 【0022】

前記目的を達成するために、本発明の実施例によるデータ駆動集積回路を持つ表示装置は前記データ駆動集積回路が、前記表示装置で要求される解像度に沿ってデータラインの数に対応して画素データを供給するデータ出力チャンネルを含んで、少なくとも2個の領域を持つデータ出力チャンネルグループと、画素データが供給されない他の出力チャンネルを含む出力チャンネルと、前記データ出力チャンネルを選択する選択部とを具備する。

前記データ出力チャンネルの数は前記データ駆動集積回路にプログラム化される。

#### 【0023】

及び、本発明の表示装置は前記データ出力チャンネルを選択するためのチャンネル選択信号を発生して供給する選択信号発生部と、前記データ駆動集積回路を制御して前記画素

10

20

30

40

50

データを供給するタイミング制御部をさらに具備する。

前記選択信号発生部は第1及び第2電圧源のそれぞれと接続されて前記チャンネル選択信号を発生する第1及び第2選択端子を含む。

【0024】

前記データ駆動集積回路はサンプリング信号を順次的に供給するシフトレジスタ部と、前記シフトレジスタ部からのサンプリング信号に沿って画素データをラッチするためのラッチと、前記ラッチからの前記画素データをアナログ画素データに変換するデジタル-アナログ変換部と、前記デジタル-アナログ変換部からの前記画素データをバッファリングして前記多数のデータラインに出力するためのバッファ部をもっと具備する。

【0025】

前記第1及び第2選択端子は第1及び第2論理値を発生して、前記第1論理値であれば前記出力チャンネルの総数N(Nは定数)より小さな1個の出力チャンネルを、前記第2論理値であれば前記1個より小さなJ個の出力チャンネルを前記データ出力チャンネルで選択する。

【0026】

前記第1及び第2選択端子は第1乃至第4論理値を発生して、前記第4論理値であれば前記出力チャンネルの総数N(Nは定数)より小さな1個を、前記第3論理値であれば前記Iより小さなJ個を、前記第2論理値であれば前記Jより小さなK個を、前記第1論理値であれば前記Kより小さなL個を前記データ出力チャンネルで選択する。

前記データ出力チャンネルグループは一番目の出力チャンネルからI、J、K、L番目の中からいざれか一つまでの出力チャンネルを含む。

【0027】

前記選択信号発生部は前記データラインの数、前記要求される解像度に対応するデータ集積回路の個数、前記データ集積回路が実装されたテープキャリアパッケージの幅、前記タイミング制御部と前記データ駆動集積回路の間のデータ送信ラインの数の中から少なくとも一つの条件に沿って前記チャンネル選択信号を発生する。

【0028】

前記選択信号発生部は前記チャンネル選択信号を発生するスイッチング素子を具備する。

前記選択信号発生部は前記チャンネル選択信号を発生するディープスイッチを具備する。

前記他の出力チャンネルはダミーチャンネルである。

前記ダミーチャンネルはフロータイミングされる。

前記ダミーチャンネルは一定常数の電圧に設定される。

前記他の出力チャンネルは前記データ出力チャンネルグループの少なくとも2個領域の間に位する。

前記データ出力チャンネルグループの少なくとも2個領域は同一な数のデータ出力チャンネルを持つ。

【0029】

本発明の実施例によるデータ駆動集積回路は表示装置の多数のデータラインと接続されたデータ駆動集積回路において、前記表示装置で要求される解像度に沿ってデータラインの数に対応して画素データを供給するM(MはN以下の定数)個のデータ出力チャンネルを含んで、少なくとも2個の領域を持つデータ出力チャンネルグループと、画素データが供給されない(N-M)個の出力チャンネルを含むN個の出力チャンネルを具備する。

【0030】

及び、本発明のデータ駆動集積回路は前記M個のデータ出力チャンネルを選択するためのチャンネル選択信号を発生する選択信号発生部をさらに具備する。

前記チャンネル選択部は前記チャンネル選択信号に沿って前記データ出力チャンネルグループに含まれるデータ出力チャンネルの数を可変させる。

前記選択信号発生部は前記データラインの数、前記データ集積回路の個数、前記データ

10

20

30

40

50

集積回路が実装されるテープキャリアパッケージの幅、前記画素データの入力ライン数の中から少なくとも一つの条件に沿って前記チャンネル選択信号を発生する。

【0031】

前記チャンネル選択部は第1及び第2論理値を発生して、前記第1論理値であれば前記Nより小さなI個の出力チャンネルを、前記第2論理値であれば前記I個より小さなJ個の出力チャンネルを前記データ出力チャンネルで選択する。

【0032】

前記チャンネル選択部は第1乃至第4論理値を発生して、前記第4論理値であれば前記Nより小さなI個を、前記第3論理値であれば前記Iより小さなJ個を、前記第2論理値であれば前記Jより小さなK個を、前記第1論理値であれば前記Kより小さなL個を前記データ出力チャンネルで選択する。

【0033】

前記データ出力チャンネルグループは一番目のデータ出力チャンネルからI、J、K、L番目の中からいずれか一つまでのデータ出力チャンネルを含む。

前記(N-M)個の出力チャンネルは前記データ出力チャンネルグループの少なくとも2個の領域の間に位する。

【0034】

前記データ出力チャンネルグループの少なくとも2個領域は同一な数のデータ出力チャンネルを持つ。

前記(N-M)個の出力チャンネルはフロー・ティングされる。前記(N-M)個の出力チャンネルは一定常数の電圧に設定される。

【0035】

前記選択信号発生部は第1及び第2電圧源のそれぞれと接続されて前記チャンネル選択信号を発生する第1及び第2選択端子を含む。

前記選択信号発生部は前記チャンネル選択信号を発生するスイッチを具備する。

前記選択信号発生部は前記チャンネル選択信号を発生するディープスイッチを具備する。

【0036】

及び、本発明のデータ駆動集積回路はサンプリング信号を順次的に供給するシフトレジスタ部と、前記シフトレジスタ部からのサンプリング信号に沿って画素データをラッチするためのラッチと、前記ラッチからの前記画素データをアナログ画素データに変換するデジタル-アナログ変換部と、前記デジタル-アナログ変換部からの前記画素データをバッファリングして前記多数のデータラインに出力するためのバッファ部をもっと具備する。

【0037】

本発明の実施例によるデータ駆動集積回路は第1乃至第3出力チャンネルグループを含むN(Nは定数)個の出力チャンネルと、表示装置で要求される解像度に沿って画素データが供給される多数のデータラインに対応する第1及び第3出力チャンネルグループと、ダミー出力チャンネルにデ・セイブルされる第2出力チャンネルグループを選択するチャンネル選択部を具備して、前記第2出力チャンネルグループは前記第1及び第3出力チャンネルグループの間に位する。

【0038】

前記第2出力チャンネルグループは前記N個の出力チャンネルの中からいずれか一つの出力チャンネルを含む。

前記第2出力チャンネルグループは前記N個の出力チャンネル中(N/2)個の出力チャンネルを含む。

前記第2出力チャンネルグループは前記N個の出力チャンネルの中でN番目の出力チャンネルを含む。

【0039】

前記出力チャンネル選択のためのチャンネル選択信号を発生する選択信号発生部をさらに具備する。

10

20

30

40

50

前記選択信号発生部は前記データラインの数、前記データ集積回路の個数、前記データ集積回路が実装されるテープキャリアパッケージの幅、前記画素データの入力ライン数の中から少なくとも一つの条件に沿って前記チャンネル選択信号を発生する。前記選択信号発生部は第1及び第2電圧源のそれぞれと接続されて前記チャンネル選択信号を発生する第1及び第2選択端子を含む。

## 【0040】

前記第1及び第2出力チャンネルグループは同一な数の出力パネルを持つ。

前記第1出力チャンネルグループは一番目から $I_1$ 番目、 $I_2$ 番目、 $I_3$ 番目(ただ、 $1 < I_1 < I_2 < I_3 < N$ )中からいざれかまでの出力チャンネルを含む。

前記第3出力チャンネルグループは $N$ 番目から $J_1$ 番目、 $J_2$ 番目、 $J_3$ 番目(ただ、 $I_3 < J_1 < J_2 < J_3 < N$ )中からいざれかまでの出力チャンネルを含む。 10

## 【0041】

前記出力チャンネルの中で $I_1 + 1$ 番目から $J_3 - 1$ 番目まで、 $I_2 + 1$ 番目から $J_2 - 1$ 番目まで、 $I_3 + 1$ 番目から $J_1 - 1$ 番目の中である一グループは前記ダミー出力チャンネルである。

前記ダミー出力チャンネルはフローティングされる。

前記ダミー出力チャンネルは一定常数の電圧に設定される。

## 【0042】

前記選択信号発生部は前記選択制御信号を発生するスイッチを具備する。

前記選択信号発生部は前記選択制御信号を発生するディープスイッチを具備する。 20

前記出力チャンネルの数はプログラム化される。

## 【0043】

本発明の他の実施例によるデータ駆動集積回路はスタートパルスをシフトさせてサンプリング信号を発生するための $N$ (ただ、 $N$ は陽の定数)個のシフトレジスタから構成されたシフトレジスタ部を含むデータ駆動集積回路において、第1及び第2出力チャンネル群から構成された出力チャンネル部と、前記シフトレジスタ部で前記第1出力チャンネル群と対応される第1群のシフトレジスタからの出力信号を選択して前記第1出力チャンネル群の中、一部のデータラインと接続されられる第1データ出力チャンネル群を選択する第1選択部と、前記第1選択部からの出力信号を前記第2出力チャンネル群と対応される第2群のシフトレジスタに供給して前記第2出力チャンネル群の中、他のデータラインと接続される第2データ出力チャンネル群を選択する第2選択部とを具備する。 30

## 【0044】

及び、本発明のデータ駆動集積回路は前記第1及び第2データ出力チャンネル群の選択のためのチャンネル選択信号を発生する選択信号発生部をさらに具備する。

## 【0045】

前記選択信号発生部は前記データラインの数、前記データ集積回路の個数、前記データ集積回路が実装されるテープキャリアパッケージの幅、前記データ集積回路のデータ入力欄である数の中から少なくとも一つの条件に沿って前記チャンネル選択信号を発生する。

## 【0046】

前記選択信号発生部は電圧源及び基底電圧源に接続されて前記チャンネル選択信号を発生する選択端子を具備する。 40

前記選択信号発生部は前記チャンネル選択信号を発生するスイッチを具備する。

前記選択信号発生部は前記チャンネル選択信号を発生するディープスイッチを具備する

。

## 【0047】

前記第1及び第2データ出力チャンネルは同一な出力チャンネルを持つ。

前記第1選択部は前記チャンネル選択信号に沿って前記 $N$ 個のシフトレジスタの第 $I_1$ (ただ、 $I_1$ は1より大きい陽の定数)番目、 $I_2$ (ただ、 $I_2$ は $I_1$ より大きい陽の定数)番目及び $I_3$ (ただ、 $I_3$ は $I_2$ より大きくて $N$ より小さな陽の定数)番目シフトレジスタの出

力信号の中からいずれかを選択する第1マルチフレクサーを具備する。

【0048】

前記第2選択部は、前記チャンネル選択信号に沿って第1マルチフレクサーからの出力信号を出力するデマルチフレクサーと、前記チャンネル選択信号に沿って前記デマルチフレクサーからの出力信号と前記N個のシフトレジスタの第J1-1(ただし、J1は13より大きい陽の定数)番目シフトレジスタの出力信号の中からいずれかを選択して第J1番目シフトレジスタに供給する第2マルチフレクサーと、前記チャンネル選択信号に沿って前記デマルチフレクサーからの出力信号と前記N個のシフトレジスタの第J2-1(ただし、J2はJ1より大きい陽の定数)番目シフトレジスタの出力信号の中からいずれかを選択して第J2番目シフトレジスタに供給する第3マルチフレクサーと、前記チャンネル選択信号に沿って前記デマルチフレクサーからの出力信号と前記N個のシフトレジスタの第J3-1(ただし、J3はJ2より大きくてNより小さな陽の定数)番目シフトレジスタの出力信号の中からいずれかを選択して第J3番目シフトレジスタに供給する第4マルチフレクサーとを具備する。

10

【0049】

前記チャンネル選択部は前記チャンネル選択信号に応答して前記第1出力チャンネル群の中、一番目からI1番目、I2番目、I3番目(ただし、 $1 < I1 < I2 < I3 < N$ )出力チャンネルの中からいずれか一つまでを第1データ出力チャンネル群で選択する。

20

【0050】

前記チャンネル選択部は前記チャンネル選択信号に応答して前記第2出力チャンネル群の中、N番目からJ1番目、J2番目、J3番目(ただし、 $I3 < J1 < J2 < J3 < N$ )中からいずれか一つまでを第2データ出力チャンネル群で選択する。

20

【0051】

前記出力チャンネルの中でI1+1番目からJ3-1番目まで、I2+1番目からJ2-1番目まで、I3+、1番目からJ1-1番目の中であるーグループは前記ダミー出力チャンネルである。

前記ダミー出力チャンネルはフローティングされる。

前記ダミー出力チャンネルは一定常数の電圧に設定される。

30

【0052】

本発明の実施例によるデータ駆動集積回路の駆動方法は表示装置で要求される解像度を決める段階と、多数の出力チャンネルの中で前記要求される解像度に対応して画素データが供給されられるデータ出力チャンネルを含んで、少なくとも2個の領域を持つデータ出力チャンネルグループを選択する段階と、前記選択されたデータ出力チャンネルグループを通じてデータラインで画素データを供給して、非選択された出力チャンネルでは画素データを供給しない段階とを含む。

30

【発明を実施するための最良の形態】

【0053】

[実施例]

以下、本発明の実施例を添付した図4乃至図17を参照して詳細に説明する。

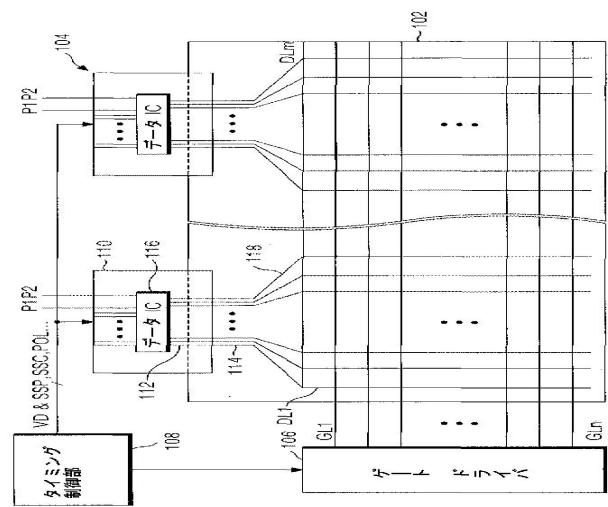

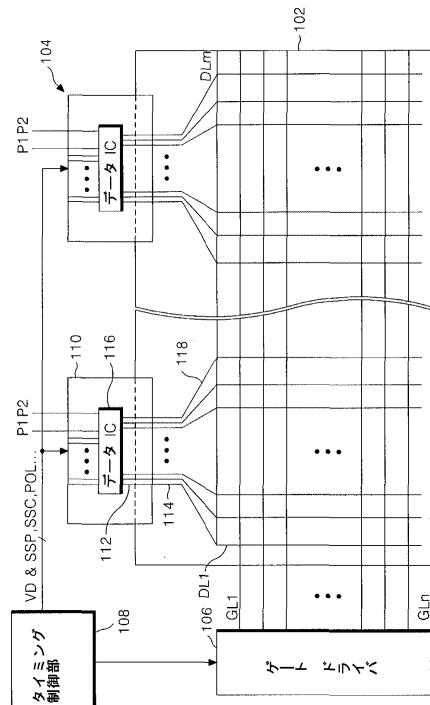

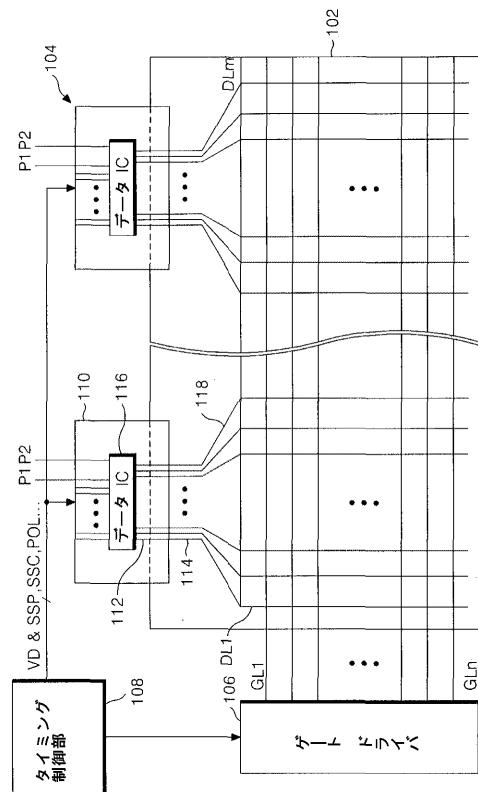

図4を参照すると、本発明の第1実施例による液晶表示装置は液晶セルなどがマトリックス形態で配列された液晶パネル(102)と、液晶パネル(102)のゲートラインなど(GL1乃至GLn)を駆動するためのゲートドライバ(106)と、液晶パネル(102)のデータラインなど(DL1乃至DLm)を駆動するためのデータドライバ(104)と、ゲートドライバ(106)とデータドライバ(104)を制御するためのタイミング制御部(108)とを具備する。

40

【0054】

液晶パネル(102)はゲートラインなど(GL1乃至GLn)とデータラインなど(DL1乃至DLm)の交差部毎に形成された薄膜トランジスタ(TFT)と、薄膜トランジスタ(TFT)と接続された液晶セル(図示しない)とを具備する。薄膜トランジスタ(TFT)はゲートライン(GL)からのスキャン信号、即ちゲート・ハイ電圧(VGH)

50

) が供給される場合、ターン・オンされてデータライン (D L) からの画素信号を液晶セルに供給する。そして、薄膜トランジスタ (TFT) はゲートライン (G L) からゲート・ロー電圧 (V GL) が供給される場合、ターン・オフされて液晶セルに充電された画素信号が維持されるようとする。

【0055】

液晶セルは等価的に液晶容量のキャパシティで表現されて、液晶を間に置いて対面する共通電極と 薄膜トランジスタ (TFT) に接続された画素電極を含む。そして、液晶セルは充電された画素信号が次の画素信号が充電される際まで安定的に維持されるようするためストリッジ・キャパシティとを更に具備する。このストリッジ・キャパシティは画素電極と以前段のゲートラインの間に形成される。このような液晶セル (7) は薄膜トランジスタ (TFT) を通して充電される画素信号につれて誘電異方性を有する液晶の配列状態が可変して光透過率を調節することでグラデーションを具現するようになる。

10

【0056】

タイミング制御部 (108) は図示されないビデオ・カードから供給される同期信号 (V, H) を利用してゲート制御信号など (GSP, GSC, GOE) 及びデータ制御信号など (SSP, SSC, SOE, POL) を発生する。ゲート制御信号など (GSP, GSC, GOE) はゲート・ドライバ (106) に供給されてゲート・ドライバを制御するようになり、データ制御信号など (SSP, SSC, SOE, POL) はデータ・ドライバ (104) に供給されてデータ・ドライバを除去するようになる。共に、タイミング制御部 (108) は赤色 (R)、緑色 (G) 及び青色 (B) の画素データ (VD) を整列してデータ・ドライバ (104) に供給する。

20

【0057】

ゲート・ドライバ (106) はゲートラインなど (GL1 乃至 GLn) を順次に駆動させる。このために、ゲート・ドライバ (106) は多数のゲートIC (図示しない) とを具備する。ゲートICなどは自分に接続されたゲートラインなど (GL1 乃至 GLn) をタイミング制御部 (108) からの制御によって順次に駆動させる。もう一度言って、ゲートICなどはタイミング制御部 (108) から供給されるゲート制御信号など (GSP, GSC, GOE) に応答してゲートラインなど (GL1 乃至 GLn) に順次にゲート・ハイ電圧 (VGH) を順次に供給する。

30

【0058】

具体的に、ゲート・ドライバ (106) はゲート・スタート・パルス (GSP) をゲート・シフト・クラック (GSC) につれてシフトさせてシフトパルスを発生する。そして、ゲート・ドライバ (106) はシフト・パルスに応答して水平期間毎に当たるゲートライン (GL) にゲート・ハイ電圧 (VGH) を供給するようになる。もう一度言って、シフトパルスは水平期間毎に一ラインずつシフトされて、ゲートICなどの中のいずれか一つはシフトパルスに対応されて当たるゲートライン (GL) にゲート・ハイ電圧 (VGH) を供給する。この場合、ゲートIC (10) などはゲートラインなど (GL1 乃至 GLn) にゲート・ハイ電圧 (VGH) が供給されない残りの期間ではゲート・ロー電圧 (VGL) を供給する。

40

【0059】

データ・ドライバ (104) は水平期間毎に 1 ライン分ずつの画素信号をデータラインなど (DL1 乃至 DLm) に供給する。このために、データ・ドライバ (104) は多数のデータIC (116) などを具備する。データIC (116) などのそれぞれはテープ・キャリアー・パッケージ (以下、"データTCP" という) (110) の上に実装される。このような、データIC (116) などは電気的に接続される。そして、データIC (116) などはタイミング制御部 (108) から供給されるデータ制御信号など (SSP, SSC, SOE, POL) に応答してデータラインなど (DL1 乃至 DLm) に画素信号を供給する。この際、データIC (116) などはタイミング制御部 (108) からの画素データ (VD) をガンマ電圧発生部 (図示しない) からのガンマ電圧を利用してアナログ画素信号に変換して出力する。

50

## 【0060】

具体的に、データIC(116)などはソース・スタート・パルス(SSP)をソース・シフト・クラック(SSC)についてシフトさせてサンプリング信号を発生する。続いて、データIC(116)などはサンプリング信号に応答して画素データ(VD)を一定の単位ずつ順次にラッチする。以後、ラッチされた1ライン分の画素データ(VD)をアナログ画素信号に変換してソース出力エナーブル信号(SOE)のエナーブル期間にデータラインなど(DL1乃至DLm)に供給するようになる。この場合、データIC(116)などは画素データ(VD)を極性制御信号(POL)に応答して正極性または負極性の画素信号に変換するようになる。

## 【0061】

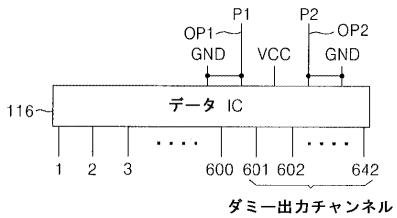

一方、本発明の第1実施例による液晶表示装置のデータIC(116)などのそれぞれは外部から入力される第1及び第2チャンネル選択信号(P1, P2)に応答してデータラインなど(DL1乃至DLm)に画素信号を供給するための出力チャンネルを変更するようになる。このために、データIC(116)などのそれぞれは第1及び第2チャンネル選択信号(P1, P2)が供給される第1及び第2オプションピン(OP1, OP2)とを具備する。

## 【0062】

第1及び第2オプションピン(OP1, OP2)のそれぞれは電圧源(VCC)及び基底電圧源(GND)に選択的に接続されて2ビット2進論理値を有するようになる。これについて、第1及び第2オプションピン(OP1, OP2)を通してデータIC(116)に供給される第1及び第2チャンネル選択信号(P1, P2)は"00"、"01"、"10"及び"11"の値を有するようになる。

## 【0063】

これについて、データIC(116)などのそれぞれは第1及び第2オプションピン(OP1, OP2)を通して供給される第1及び第2チャンネル選択信号(P1, P2)について液晶パネル(102)の解像図についてすでに設定された出力チャンネルを有するようになる。

## 【0064】

このような液晶パネル(102)の解像図についてデータIC(116)の出力チャンネルによるデータIC(116)の個数を表1に表した。

## 【表1】

| 解像図   | ピクセル数  |        | データIC出力チャンネルによるデータIC個数 |       |       |       |

|-------|--------|--------|------------------------|-------|-------|-------|

|       | データライン | ゲートライン | 600CH                  | 618CH | 630CH | 642CH |

| XGA   | 3072   | 768    | 5.12                   | 4.97  | 4.88  | 4.79  |

| SXGA+ | 4200   | 1050   | 7.00                   | 6.80  | 6.67  | 6.54  |

| UXGA  | 4800   | 1200   | 8.00                   | 7.77  | 7.62  | 7.48  |

| WXGA  | 3840   | 800    | 6.40                   | 6.21  | 6.10  | 5.98  |

| WSGA- | 4320   | 900    | 7.20                   | 6.99  | 6.86  | 6.73  |

| WSXGA | 5040   | 1050   | 8.40                   | 8.16  | 8.00  | 7.85  |

| WUXGA | 5760   | 1200   | 9.60                   | 9.32  | 9.14  | 8.97  |

## 【0065】

表1を参照すると、四つチャンネルですべての解像図を表現することができる。即ち、XGA級の解像図を有する液晶パネル(102)では618個のデータ出力チャンネルを有する五つのデータIC(116)が必要となる。この際、残る18個のデータ出力チャンネルはダミーラインを処理する。また、SXGA+級の解像図を有する液晶パネル(102)では600個のデータ出力チャンネルを有する七つのデータIC(116)が必要となる。また、UXGA+級の解像図を有する液晶パネル(102)では6

10

20

30

40

50

00個のデータ出力チャンネルを有する八つのデータI C (116)が必要となる。そして、WXGA+級の解像図を有する液晶パネル(102)では642個のデータ出力チャンネルを有する六つのデータI C (116)が必要となる。また、WSXGA級の解像図を有する液晶パネル(102)では618個のデータ出力チャンネルを有する七つのデータI C (116)が必要となる。また、WSXGA級の解像図を有する液晶パネル(102)では630個のデータ出力チャンネルを有する八つのデータI C (116)が必要となる。また、WUXGA級の解像図を有する液晶パネル(102)では642個のデータ出力チャンネルを有する九つのデータI C (116)が必要となる。

【0066】

これについて、本発明の第1実施例による液晶表示装置は第1及び第2チャンネル選択信号(P1, P2)についてデータI C (116)の出力チャンネルを600チャンネル、618チャンネル、630チャンネル及び642チャンネルの中のいずれか一つで設定することで液晶パネル(102)のすべての解像図を表現することができる。もう一度言って、本発明の第1実施例による液晶表示装置のデータI C (116)は642個のデータ出力チャンネルを有するように製造して、第1及び第2オプションピン(OP1, OP2)からの第1及び第2チャンネル選択信号(P1, P2)についてデータI C (116)の出力チャンネルを設定することで液晶パネル(102)のすべての解像図に共用に使用することができる。

【0067】

これを詳細に説明すると、本発明の第1実施例による液晶表示装置のデータI C (116)は642個のデータ出力チャンネルを有するように製造される。

【0068】

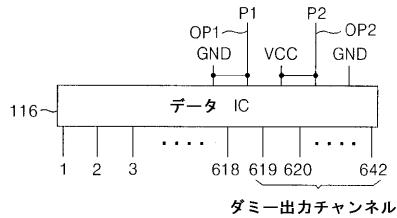

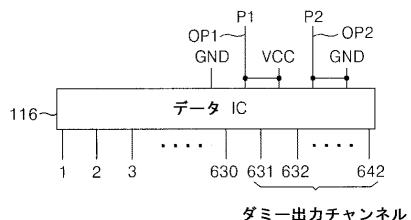

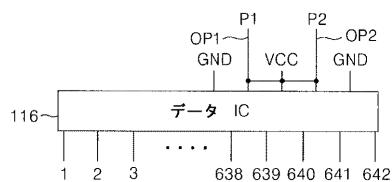

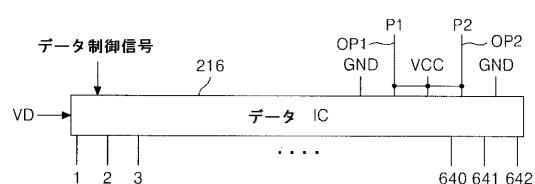

第1及び第2オプションピン(OP1, OP2)のそれぞれが基底電圧源(GND)に接続されてデータI C (116)に供給される第1及び第2チャンネル選択信号(P1, P2)の値が"00"である場合にデータI C (116)は図5に示したように642個のデータ出力チャンネルの中の第1乃至第600データ出力チャンネルを通して画素電圧信号を出力するようになる。この際、第601乃至第642出力チャンネルはダミー出力チャンネルになる。また、第1オプションピン(OP1)が基底電圧源(GND)に接続されると共に第2オプションピン(OP2)が電圧源(VCC)に接続されてデータI C (116)に供給される第1及び第2チャンネル選択信号(P1, P2)の値が"01"である場合にデータI C (116)は図6に示したように642個のデータ出力チャンネルの中の第1乃至第618データ出力チャンネルを通して画素電圧信号を出力するようになる。この際、第619乃至第642出力チャンネルはダミー出力チャンネルになる。そして、第1オプションピン(OP1)が電圧源(VCC)に接続されると共に第2オプションピン(OP2)が基底電圧源(GND)に接続されてデータI C (116)に供給される第1及び第2チャンネル選択信号(P1, P2)の値が"10"である場合にデータI C (116)は図7に示したように642個のデータ出力チャンネルの中の第1乃至第630データ出力チャンネルを通して画素電圧信号を出力するようになる。この際、第631乃至第642出力チャンネルはダミー出力チャンネルになる。最後に、第1及び第2オプションピン(OP1, OP2)のそれぞれが電圧源(VCC)に接続されてデータI C (116)に供給される第1及び第2チャンネル選択信号(P1, P2)の値が"11"である場合にデータI C (116)は図8に示したように第1乃至第642データ出力チャンネルを通して画素電圧信号を出力するようになる。

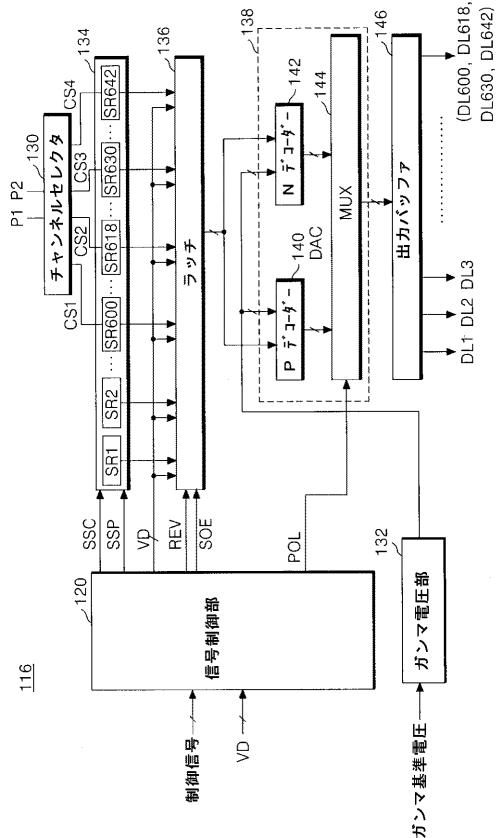

【0069】

これについて、本発明の第1実施例による液晶表示装置のデータI C (116)は図9に示したように第1及び第2オプションピン(OP1, OP2)に供給される第1及び第2チャンネル選択信号(P1, P2)についてデータI C (116)の出力チャンネルを設定するためのチャンネル選択部(130)と、順次的であるサンプリング信号を供給するためのシフト・レジスタ部(134)と、サンプリング信号に応答して画素データ(VD)を順次にラッチして同時に出力するラッチ部(136)と、ラッチ部(136)から

の画素データ（V D）を画素電圧信号に変換するデジタル・アナログ変換部（以下、”D A C部”という）（138）と、D A C（138）からの画素電圧信号を緩衝して出力する出力バッパ部（146）とを具備する。

【0070】

また、データI C（116）などはタイミング制御部（108）から供給される各種の制御信号などと画素データ（V D）を中継する信号制御部（120）と、D A C部（138）で必要とする正極性及び負極性のガンマ電圧などを供給するガンマ電圧部（132）とを更に具備する。

【0071】

信号制御部（120）はタイミング制御部（108）からの各種の制御信号など（S S P, S S C, S O E, R E V, P O Lなど）と画素データ（V D）が当たる構成要素などで出力されるように制御する。 10

【0072】

ガンマ電圧部（132）はガンマ基準電圧の発生部（図示しない）から入力される多数このガンマ基準電圧をグレイ別に細分化して出力する。

【0073】

チャンネル選択部（130）は第1及び第2オプションピン（O P 1、O P 2）を通して第1及び第2チャンネル選択信号（P 1, P 2）につれて第1乃至第4チャンネル制御信号（C S 1乃至C S 4）をシフト・レジスタ部（134）に供給するようになる。即ち、チャンネル選択部（130）は”00”の値を有する第1及び第2チャンネル選択信号（P 1, P 2）に対応される第1チャンネル制御信号（C S 1）と、”01”の値を有する第1及び第2チャンネル選択信号（P 1, P 2）に対応される第2チャンネル制御信号（C S 2）と、”10”の値を有する第1及び第2チャンネル選択信号（P 1, P 2）に対応される第3チャンネル制御信号（C S 3）と、”11”の値を有する第1及び第2チャンネル選択信号（P 1, P 2）に対応される第4チャンネル制御信号（C S 4）を発生する。 20

【0074】

シフト・レジスタ部（134）に含まれたシフト・レジスタなどは信号制御部（120）からのソース・スタート・パルス（S S P）をソース・シフト・クラック（S S C）につれてシフトさせてサンプリング信号に出力する。この際、シフト・レジスタ部（134）は642個のシフト・レジスタなど（S R 1乃至S R 642）で構成される。 30

【0075】

このような、シフト・レジスタ部（134）はチャンネル選択部（130）からの第1乃至第4チャンネル制御信号（C S 1乃至C S 4）につれて第600、第618、第630及び第642シフト・レジスタ（S R 600、S R 628、S R 630、S R 642）のそれぞれの出力信号を次の段データI C（116）に供給するようになる。

【0076】

具体的に、チャンネル選択部（130）から第1チャンネル制御信号（C S 1）に供給される場合にシフト・レジスタ部（134）は第1乃至第600番目のシフト・レジスタなど（S R 1乃至S R 600）を利用して信号制御部（120）からのソース・スタート・パルス（S S P）をソース・サンプリング・クラック信号（S S C）につれて順次にシフトさせてサンプリング信号に出力するようになる。この際、第600番目のシフト・レジスタなど（S R 600）の出力信号（キャリ信号）を次の段のデータI C（116）の一番目のシフト・レジスタ（S R 1）に供給するようになる。これにつれて、第601乃至第642シフト・レジスタ（S R 601乃至S R 642）はサンプリング信号を出力しなくなる。ここで、シフト・レジスタが陽の方向に駆動される場合に中間の42個のチャンネルを使用しなくてダミー処理して構造の上、もっと有利に使用することができる。 40

【0077】

一方、チャンネル選択部（130）から第2チャンネル制御信号（C S 2）に供給される場合にシフト・レジスタ部（134）は第1乃至第618番目のシフト・レジスタなど 50

(S R 1 乃至 S R 6 1 8) を利用して信号制御部 (1 2 0) からのソース・スタート・パルス (S S P) をソース・サンプリング・クラック信号 (S S C) につれて順次にシフトさせてサンプリング信号に出力するようになる。この際、第 6 1 8 番目のシフト・レジスタなど (S R 6 0 0) の出力信号 (キャリ信号) を次の段のデータ I C (1 1 6) の一番目のシフト・レジスタ (S R 1) に供給するようになる。これについて、第 6 1 9 乃至 第 6 4 2 シフト・レジスタ (S R 6 1 9 乃至 S R 6 4 2) はサンプリング信号を出力しなくなる。ここで、シフト・レジスタが陽の方向に駆動される場合、中間の 2 4 個のチャンネルを使用しなくてダミー処理して構造の上、もっと有利に使用することができる。

## 【0 0 7 8】

一方、チャンネル選択部 (1 3 0) から第 3 チャンネル制御信号 (C S 3) に供給される場合にシフト・レジスタ部 (1 3 4) は第 1 乃至 第 6 3 0 番目のシフト・レジスタなど (S R 1 乃至 S R 6 3 0) を利用して信号制御部 (1 2 0) からのソース・スタート・パルス (S S P) をソース・サンプリング・クラック信号 (S S C) につれて順次にシフトさせてサンプリング信号に出力するようになる。この際、第 6 3 0 番目のシフト・レジスタなど (S R 6 0 0) の出力信号 (キャリ信号) を次の段のデータ I C (1 1 6) の一番目のシフト・レジスタ (S R 1) に供給するようになる。これについて、第 6 3 1 乃至 第 6 4 2 シフト・レジスタ (S R 6 3 1 乃至 S R 6 4 2) はサンプリング信号を出力しなくなる。ここで、シフト・レジスタが陽の方向に駆動される場合に中間の 1 2 個のチャンネルを使用しなくてダミー処理して構造の上、もっと有利に使用することができる。

## 【0 0 7 9】

一方、チャンネル選択部 (1 3 0) から第 4 チャンネル制御信号 (C S 4) に供給される場合にシフト・レジスタ部 (1 3 4) は第 1 乃至 第 6 4 2 番目のシフト・レジスタなど (S R 1 乃至 S R 6 4 2) を利用して信号制御部 (1 2 0) からのソース・スタート・パルス (S S P) をソース・サンプリング・クラック信号 (S S C) につれて順次にシフトさせてサンプリング信号に出力するようになる。この際、第 6 4 2 番目のシフト・レジスタなど (S R 6 0 0) の出力信号 (キャリ信号) を次の段のデータ I C (1 1 6) の一番目のシフト・レジスタ (S R 1) に供給するようになる。

## 【0 0 8 0】

ラッチ部 (1 3 6) はシフト・レジスタ部 (1 3 4) からのサンプリング信号に応答して信号制御部 (1 2 0) からの画素データ (V D) を一定単位ずつ順次にサンプリングしてラッチするようになる。このために、ラッチ部 (1 3 6) は 6 4 2 個の画素データ (V D) をラッチするために 6 4 2 個のラッチなどで構成されて、ラッチなどのそれぞれは画素データ (V D) のビット数に対応する大きさを有する。特に、タイミング制御部 (1 0 8) は伝送周波数を減らすために画素データ (V D) をイーブン画素データとオード画素データに分けてそれぞれの伝送ラインを通して同時に出力するようになる。ここで、イーブン画素データ (V D e v e n) とオード画素データ (V D o d d) のそれぞれは赤 (R) , 緑 (G) , 青 (B) 画素データを含む。

## 【0 0 8 1】

これについてラッチ部 (1 3 6) はサンプリング信号毎に信号制御部 (1 2 0) を経由して供給されるイーブン画素データとオード画素データを同時にラッチするようになる。続いて、ラッチ部 (1 3 6) は信号制御部 (1 2 0) からのソース出力エナーブル信号 (S O E) に応答してラッチされた 6 3 0 個、6 3 0 個及び 6 4 2 個の中のいずれか一つのデータ出力チャンネルを通して画素データ (V D) を同時に出力する。この場合、ラッチ部 (1 3 6) はデータ反転選択信号 (R E V) に応答してトランジーション・ビット数が減らすように変造された画素データ (V D) などを復元させて出力するようになる。これはタイミング制御部 (1 0 8) でデータ伝送の際に電磁気的な干渉 (E M I) を最小化するためにトランジーションされるビット数が基準値を越す画素データ (V D) などはトランジーション・ビット数が減るように変造して供給するためである。

## 【0 0 8 2】

D A C 部 (1 3 8) はラッチ部 (1 3 6) からの画素データ (V D) を同時に正極性及

10

20

30

40

50

び負極性の画素電圧信号に変換して出力するようになる。このために、D A C部(138)はラッチ部(136)に共通接続されたP(P o s i t i v e)デコーディング部(140)及びN(N e g a t i v e)デコーディング部(142)ト、Pデコーディング部(140)オヨビNデコーディング部(142)の出力信号を選択するためのマルチプレクサ(M U X ; 144)とを具備する。

## 【0083】

Pデコーディング部(140)に含まれるn個のPデコーダーなどはラッチ部(136)から同時に入力されるn個の画素データなどをガンマ電圧部(132)からの正極性のガンマ電圧などを利用して正極性画素電圧信号に変換するようになる。Nデコーディング部(142)に含まれるn個のNデコーダーなどはラッチ部(136)から同時に入力されるn個の画素データなどをガンマ電圧部(32)からの負極性ガンマ電圧などを利用して負極性の画素電圧信号に変換するようになる。マルチプレクサ部(144)に含まれる最大642個のマルチプレクサなどは信号制御部(120)からの極性制御信号(P O L)に応答してPデコーダー(140)からの正極性の画素電圧信号またはNデコーダー(142)からの負極性の画素電圧信号を選択して出力するようになる。

## 【0084】

出力バッパ部(146)に含まれる最大642個の出力バッパなどは最大642個のデータラインなど(D L 1乃至D L 642)などに直列にそれぞれ接続された電圧ホロワー(V o l t a g e f o l l o w e r)などで構成される。このような出力バッパなどはD A C部(138)からの画素電圧信号などを信号緩衝してデータラインなど(D L 1乃至D L 642)に供給するようになる。

## 【0085】

このような本発明の第1実施例による液晶表示装置で600個のデータ出力チャンネルを有するデータI C(116)は表1に表したようにS X G A +級及びU X G A急の解像図を有する液晶パネル(102)に使用されて、618個のデータ出力チャンネルを有するデータI C(116)はW S X G A級の解像図を有する液晶パネル(102)に使用されて、642個のデータ出力チャンネルを有するデータI C(116)はW X G A級とW U X G A級の解像図を有する液晶パネル(102)に使用される。

## 【0086】

一方、本発明の第1実施例による液晶表示装置は上述のところのように第1及び第2出力選択信号(P 1, P 2)につれて変更されるデータI C(116)の出力チャンネルに対応されるようにT C Pパッド(112)、液晶パネル(102)のデータパッド(114)及びリンク部(118)を設計するようになる。

## 【0087】

このような、本発明の第1実施例による液晶表示装置とその駆動方法のデータI C(116)は第1及び第2オプションピン(O P 1、O P 2)に供給される第1及び第2出力選択信号(P 1, P 2)につれて表1に表したように液晶パネル(102)の解像図につれてデータI C(116)の出力チャンネルを設定することで一種類のデータI C(116)だけでもすべての解像図を表現することができるようになる。これにつれて、本発明の第1実施例による液晶表示装置は作業性の向上及び製造費用を減少させることができる。

## 【0088】

図10は本発明の第2実施例による液晶表示装置でデータI Cを表すブロック図である。

図10を参照すると、本発明の第2実施例による液晶表示装置はデータI C(216)を除いてはすべての構成要素は本発明の第1実施例による液晶表示装置と同一になる。これにつれて、本発明の第2実施例による液晶表示装置では図10を図4と結びつけてデータI C(216)だけを説明することにし、異なる構成要素などに対する説明は省略する。この際、図4に示されたデータI Cの図面符号”116”は図10に示された”216”に代えることにする。

## 【0089】

10

20

30

40

50

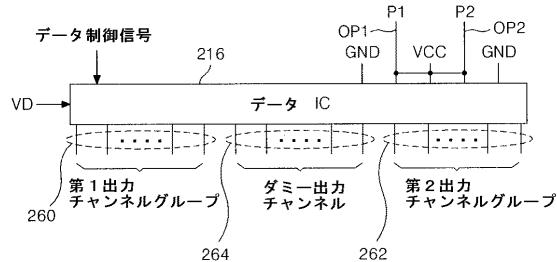

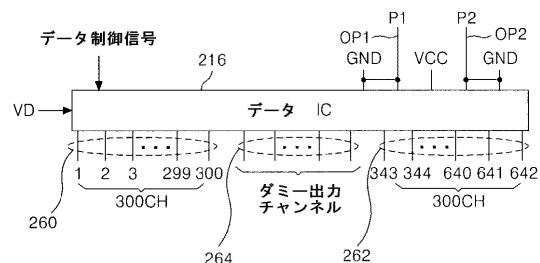

本発明の第2実施例による液晶表示装置でデータI C (216)はデータラインなど(DL乃至LDM)に画素データを供給する第1データ出力チャンネル群(260)及び第2データ出力チャンネル群(262)と、第1及び第2データ出力チャンネル群(260, 262)の間のダミー・データ出力チャンネル群(264)とを具備する。

【0090】

このような、データI C (216)はデータラインなど(DL乃至LDM)の数につれてダミー・データ出力チャンネル群(264)を通してデータラインなど(DL乃至LDM)に供給されるがそデータの出力可否を決定するための第1及び第2チャンネル選択信号(P1, P2)が供給される第1及び第2オプションピン(OP1, OP2)とを更に具備する。

10

【0091】

第1及び第2オプションピン(OP1, OP2)のそれぞれは電圧源(VCC)及び基底電圧源(GND)に選択的に接続されて2ビット2進論理値を有するようになる。これについて、第1及び第2オプションピン(OP1, OP2)を通してデータI C (216)に供給される第1及び第2チャンネル選択信号(P1, P2)は"00"、"01"、"10"及び"11"の値を有するようになる。

【0092】

これについて、データI C (216)などのそれぞれは第1及び第2オプションピン(OP1, OP2)を通して供給される第1及び第2チャンネル選択信号(P1, P2)につれて液晶パネル(102)の解像図についてすでに設定された出力チャンネルを有するようになる。

20

【0093】

このような液晶パネル(102)の解像図についてデータI C (216)の出力チャンネルによるデータI C (216)の個数を表1のようである。

【0094】

これについて、本発明の第2実施例による液晶表示装置は第1及び第2チャンネル選択信号(P1, P2)についてデータI C (216)の出力チャンネルを600チャンネル、618チャンネル、630チャンネル及び642チャンネルの中のいずれか一つで設定することで液晶パネル(102)のすべての解像図を表現することができる。もう一度言って、本発明の第3実施例による液晶表示装置のデータI C (216)は642個の出力チャンネルを有するように製造して、第1及び第2オプションピン(OP1, OP2)からの第1及び第2チャンネル選択信号(P1, P2)についてデータI C (216)の出力チャンネルを設定することで液晶パネル(102)のすべての解像図に共用に使用することができる。

30

【0095】

また、本発明の第2実施例による液晶表示装置は出力チャンネルの決定によるデータI C (216)のダミー・データ出力群(264)をデータI C (216)のデータ出力チャンネルなどの中の中間部分に配置するようになる。即ち、データI C (216)の第1及び第2データ出力チャンネル群(260, 262)はダミー・データ出力群(264)の間に置いて同一の出力チャンネルを有するようになる。これについて、本発明の第2実施例による液晶表示装置はデータI C (216)の第1及び第2データ出力チャンネル群(260, 262)のそれぞれの出力チャンネルを同一にすることで画素データの出力の際に電気的な干渉を減少させることができる。

40

【0096】

これを詳細に説明すると、本発明の第2実施例による液晶表示装置のデータI C (216)は642個の出力チャンネルを有するように製造される。

【0097】

第1及び第2オプションピン(OP1, OP2)のそれぞれが基底電圧源(GND)に接続されてデータI C (216)に供給される第1及び第2チャンネル選択信号(P1, P2)の値が"00"である場合にデータI C (216)は図11に示したように642

50

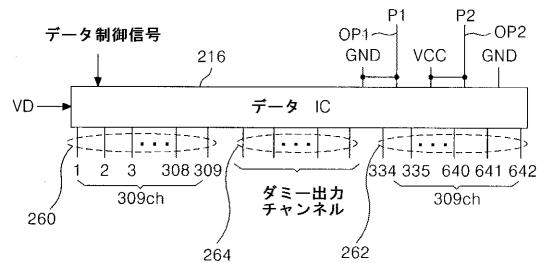

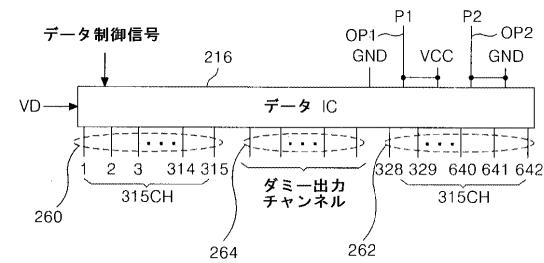

個のデータ出力チャンネルの中の第1乃至第300出力チャンネルを有する第1データ出力チャンネル群(260)及び第343乃至第642出力チャンネルを有する第2データ出力チャンネル群(262)を通して画素電圧信号を出力するようになる。この際、ダミー・データ出力チャンネル群(264)は第301乃至第342出力チャンネルを有してダミーラインに処理されて画素データが出力されたり出力されない。また、第1オプションピン(OP1)が基底電圧源(GND)に接続されると共に第2オプションピン(OP2)が電圧源(VCC)に接続されてデータIC(216)に供給される第1及び第2チャンネル選択信号(P1, P2)の値が"01"である場合にデータIC(216)は図12に示したように642個のデータ出力チャンネルの中の第1乃至第309出力チャンネルを有する第1データ出力チャンネル群(260)及び第334乃至第642出力チャンネルを有する第2データ出力チャンネル群(262)を通して画素電圧信号を出力するようになる。この際、ダミー・データ出力チャンネル群(264)は第310乃至第333出力チャンネルを有してダミーラインに処理されて画素データが出力されたり出力されない。そして、第1オプションピン(OP1)が電圧源(VCC)に接続されると共に第2オプションピン(OP2)が基底電圧源(GND)に接続されてデータIC(1016)に供給される第1及び第2チャンネル選択信号(P1, P2)の値が"10"である場合にデータIC(116)は図13に示したように642個のデータ出力チャンネルの中の第1乃至第315出力チャンネルを有する第1データ出力チャンネル群(260)及び第328乃至第642出力チャンネルを有する第2データ出力チャンネル群(262)を通して画素データを出力するようになる。この際、ダミー・データ出力チャンネル群(264)は第316乃至第327出力チャンネルを有してダミーラインに処理されて画素データが出力されたり出力されない。最後に、第1及び第2オプションピン(OP1, OP2)のそれぞれが電圧源(VCC)に接続されてデータIC(1016)に供給される第1及び第2チャンネル選択信号(P1, P2)の値が"11"である場合にデータIC(1016)は図14に示したように第1データ出力チャンネル群(260)、ダミー・データ出力チャンネル群(264)及び第2データ出力チャンネル群(262)、即ち、第1乃至第642出力チャンネルを通して画素データを出力するようになる。

#### 【0098】

このために、本発明の第2実施例による液晶表示装置のデータIC(216)は図9に示したように第1及び第2オプションピン(OP1, OP2)に供給される第1及び第2チャンネル選択信号(P1, P2)につれてデータIC(216)の出力チャンネルを設定するためのチャンネル選択部(130)と、順次的であるサンプリング信号を供給するためのシフト・レジスタ部(134)と、サンプリング信号に応答して画素データ(VD)を順次にラッチして同時に出力するラッチ部(136)と、ラッチ部(136)からの画素データ(VD)を画素電圧信号に変換するデジタル・アナログ変換部(以下、"DAC部"という)(138)と、DAC(138)からの画素電圧信号を緩衝して出力する出力バッパ部(146)とを具備する。

#### 【0099】

また、データIC(216)などはタイミング制御部(108)から供給される各種の制御信号などと画素データ(VD)を中継する信号制御部(120)と、DAC部(138)で必要とする正極性及び負極性のガンマ電圧などを供給するガンマ電圧部(132)とを更に具備する。

#### 【0100】

このような、チャンネル選択部(130)及びシフト・レジスタ部(134)を除いてはラッチ部(136)、DAC部(138)、出力バッパ部(146)、信号制御部(120)及びガンマ電圧部(132)を含むデータIC(216)は上述した本発明の第1実施例による液晶表示装置のデータICと同一のために上述した説明に代えることとする。

#### 【0101】

このような、本発明の第2実施例による液晶表示装置のデータIC(216)は第1及

10

20

30

40

50

び第2オプションピン( O P 1、 O P 2 )に供給される第1及び第2出力選択信号( P 1、 P 2 )について表1に表したように液晶パネル( 1 0 2 )の解像図についてデータI C( 2 1 6 )の出力チャンネルを設定することで一種類のデータI C( 1 1 6 )だけでもすべての解像図を表現することができるようになる。これについて、本発明の第2実施例による液晶表示装置は作業性の向上及び製造費用を減少させることができる。

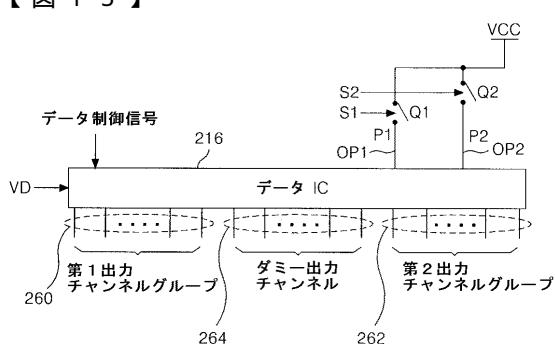

#### 【 0 1 0 2 】

一方、本発明の第1及び第2実施例による液晶表示装置でデータI C( 1 1 6、 2 1 6 )の第1及び第2オプションピン( O P 1、 O P 2 )に供給される第1及び第2チャンネル選択信号( P 1、 P 2 )は図15に示したように第1及び第2スイッチ( Q 1、 Q 2 )の選択的なスイッチングによって発生することができる。

10

#### 【 0 1 0 3 】

第1スイッチ( Q 1 )は電圧源( V C C )と第1オプションピン( O P 1 )の間に接続されて、第2スイッチ( Q 2 )は電圧源( V C C )と第2オプションピン( O P 2 )の間に接続される。このような、第1及び第2スイッチ( Q 1、 Q 2 )のそれぞれはタイミング制御部( 1 0 8 )からのスイッチング信号( S 1、 S 2 )によってスイッチングされるか液晶パネル( 1 0 2 )の解像図について設定されたスイッチング信号( S 1、 S 2 )によってスイッチングされる。

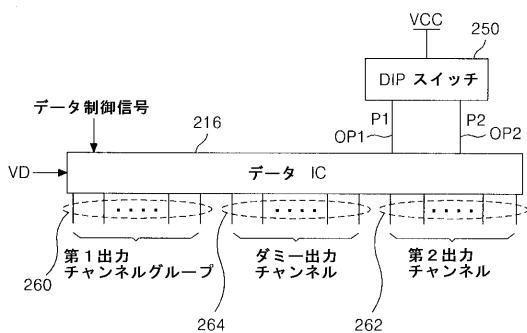

#### 【 0 1 0 4 】

また一方で、本発明の第1及び第2実施例による液晶表示装置でデータI C( 1 1 6、 2 1 6 )の第1及び第2オプションピン( O P 1、 O P 2 )に供給される第1及び第2チャンネル選択信号( P 1、 P 2 )は図16に示したように電圧源( V C C )に接続されると共に第1及び第2オプションピン( O P 1、 O P 2 )のそれぞれに供給されたディップスイッチ( 2 5 0 )のスイッチング操作によって発生されることがある。

20

#### 【 0 1 0 5 】

ディップスイッチ( 2 5 0 )は液晶パネル( 1 0 2 )の解像図についてシステム・エンジニアによってスイッチのそれぞれの位置が設定されることで第1及び第2チャンネル選択信号( P 1、 P 2 )を発生して第1及び第2オプションピン( O P 1、 O P 2 )のそれぞれに供給する。

#### 【 0 1 0 6 】

図17は本発明の第3実施例による液晶表示装置でデータI Cを表すブロック図である。

30

図17を参照すると、本発明の第3実施例による液晶表示装置はデータI C( 2 1 6 )を除いてはすべての構成要素は本発明の第1実施例による液晶表示装置と同一になる。これについて、本発明の第3実施例による液晶表示装置では図17を図4に結び付けてデータI C( 2 1 6 )だけを説明することにし、異なる構成要素などに対する説明は省略する。この際、図4に示されたデータI Cの図面符号" 1 1 6 "は図17に示された" 2 1 6 "に代えることにする。

#### 【 0 1 0 7 】

本発明の第3実施例による液晶表示装置でデータI C( 2 1 6 )はデータラインなど( D L 乃至 L D m )に画素データを供給する第1データ出力チャンネル群( 2 6 0 )及び第2データ出力チャンネル群( 2 6 2 )と、第1及び第2データ出力チャンネル群( 2 6 0、 2 6 2 )の間のダミー・データ出力チャンネル群( 2 6 4 )とを具備する。

40

#### 【 0 1 0 8 】

このような、データI C( 2 1 6 )はデータラインなど( D L 乃至 L D m )の数についてダミー・データ出力チャンネル群( 2 6 4 )を通してデータラインなど( D L 乃至 L D m )に供給されるがそのデータの出力可否を決定するための第1及び第2チャンネル選択信号( P 1、 P 2 )が供給される第1及び第2オプションピン( O P 1、 O P 2 )とを更に具備する。

#### 【 0 1 0 9 】

第1及び第2オプションピン( O P 1、 O P 2 )のそれぞれは電圧源( V C C )及び基

50

底電圧源 (GND) に選択的に接続されて 2 ビット 2 進論理値を有するようになる。これについて、第 1 及び第 2 オプションピン (OP1, OP2) を通してデータ I C (216) に供給される第 1 及び第 2 チャンネル選択信号 (P1, P2) は "00"、"01"、"10" 及び "11" の値を有するようになる。

## 【0110】

これについて、データ I C (216) などのそれぞれは第 1 及び第 2 オプションピン (OP1, OP2) を通して供給される第 1 及び第 2 チャンネル選択信号 (P1, P2) につれて液晶パネル (102) の解像図についてすでに設定された出力チャンネルを有するようになる。

## 【0111】

このような液晶パネル (102) の解像図についてデータ I C (216) の出力チャンネルによるデータ I C (216) の個数を表 1 のようである。

## 【0112】

これについて、本発明の第 3 実施例による液晶表示装置は第 1 及び第 2 チャンネル選択信号 (P1, P2) についてデータ I C (216) の出力チャンネルを 600 チャンネル、618 チャンネル、630 チャンネル及び 642 チャンネルの中のいずれか一つで設定することで液晶パネル (102) のすべての解像図を表現することができる。もう一度言って、本発明の第 3 実施例による液晶表示装置のデータ I C (216) は 642 個の出力チャンネルを有するように製造して、第 1 及び第 2 オプションピン (OP1, OP2) からの第 1 及び第 2 チャンネル選択信号 (P1, P2) についてデータ I C (216) の出力チャンネルを設定することで液晶パネル (102) のすべての解像図に共用に使用することができる。

## 【0113】

また、本発明の第 3 実施例による液晶表示装置は出力チャンネルの決定によるデータ I C (216) のダミー・データ出力群 (264) をデータ I C (216) のデータ出力チャンネルなどの中の中間部分に配置するようになる。即ち、データ I C (216) の第 1 及び第 2 データ出力チャンネル群 (260, 262) はダミー・データ出力群 (264) の間に置いて同一の出力チャンネルを有するようになる。これについて、本発明の第 3 実施例による液晶表示装置はデータ I C (216) の第 1 及び第 2 データ出力チャンネル群 (260, 262) のそれぞれの出力チャンネルを同一にすることで画素データの出力の際に電気的な干渉を減少させることができる。

## 【0114】

これを詳細に説明すると、本発明の第 2 実施例による液晶表示装置のデータ I C (216) は 642 個の出力チャンネルを有するように製造される。

## 【0115】

第 1 及び第 2 オプションピン (OP1, OP2) のそれぞれが基底電圧源 (GND) に接続されてデータ I C (216) に供給される第 1 及び第 2 チャンネル選択信号 (P1, P2) の値が "00" である場合にデータ I C (216) は図 11 に示したように 642 個のデータ出力チャンネルの中の第 1 乃至第 300 出力チャンネルを有する第 1 データ出力チャンネル群 (260) 及び第 343 乃至第 642 出力チャンネルを有する第 2 データ出力チャンネル群 (262) を通して画素電圧信号を出力するようになる。この際、ダミー・データ出力チャンネル群 (264) は第 301 乃至第 342 出力チャンネルを有してダミーラインに処理されて画素データが出力されたり出力されない。また、第 1 オプションピン (OP1) が基底電圧源 (GND) に接続されると共に第 2 オプションピン (OP2) が電圧源 (VCC) に接続されてデータ I C (216) に供給される第 1 及び第 2 チャンネル選択信号 (P1, P2) の値が "01" である場合にデータ I C (216) は図 12 に示したように 642 個のデータ出力チャンネルの中の第 1 乃至第 309 出力チャンネルを有する第 1 データ出力チャンネル群 (260) 及び第 334 乃至第 642 出力チャンネルを有する第 2 データ出力チャンネル群 (262) を通して画素電圧信号を出力するようになる。この際、ダミー・データ出力チャンネル群 (264) は第 310 乃至第 33

10

20

30

40

50

3出力チャンネルを有してダミーラインに処理されて画素データが出力されたり出力されない。そして、第1オプションピン( O P 1 )が電圧源( V C C )に接続されると共に第2オプションピン( O P 2 )が基底電圧源( G N D )に接続されてデータI C ( 2 1 6 )に供給される第1及び第2チャンネル選択信号( P 1 , P 2 )の値が”10”である場合にデータI C ( 2 1 6 )は図13に示したように642個のデータ出力チャンネルの中の第1乃至第315出力チャンネルを有する第1データ出力チャンネル群( 2 6 0 )及び第328乃至第642出力チャンネルを有する第2データ出力チャンネル群( 2 6 2 )を通して画素データを出力するようになる。この際、ダミー・データ出力チャンネル群( 2 6 4 )は第316乃至第327出力チャンネルを有してダミーラインに処理されて画素データが出力されたり出力されない。最後に、第1及び第2オプションピン( O P 1 , O P 2 )のそれぞれが電圧源( V C C )に接続されてデータI C ( 1 0 1 6 )に供給される第1及び第2チャンネル選択信号( P 1 , P 2 )の値が”00”である場合にデータI C ( 1 0 1 6 )は図14に示したように第1データ出力チャンネル群( 2 6 0 )、ダミー・データ出力チャンネル群( 2 6 4 )及び第2データ出力チャンネル群( 2 6 2 )、即ち、第1乃至第642出力チャンネルを通して画素データを出力するようになる。

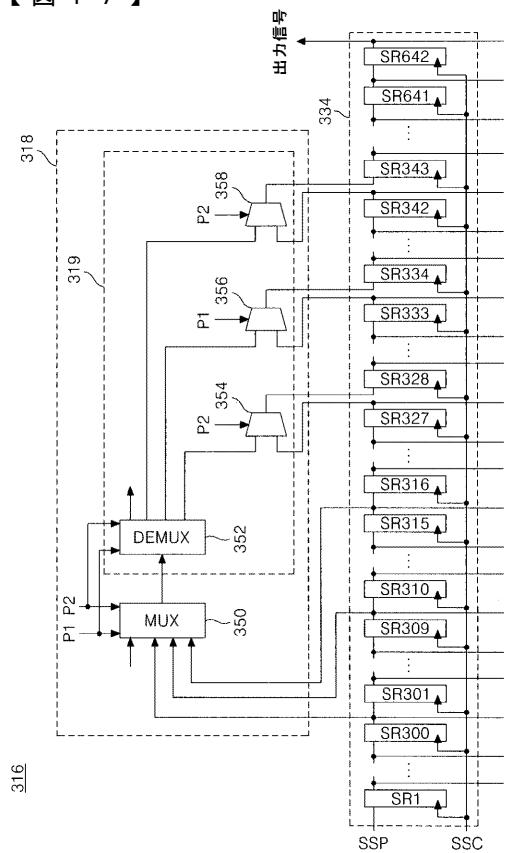

#### 【 0 1 1 6 】

このために、本発明の第3実施例による液晶表示装置のデータI C ( 2 1 6 )は図17に示したように第1及び第2オプションピン( O P 1 , O P 2 )に供給される第1及び第2チャンネル選択信号( P 1 , P 2 )につれてデータI C ( 2 1 6 )の出力チャンネルを設定するためのチャンネル選択部( 3 1 8 )と、順次的であるサンプリング信号を供給するためのシフト・レジスタ部( 3 3 4 )と、サンプリング信号に応答して画素データ( V D )を順次にラッチして同時に出力するラッチ部と、ラッチ部からの画素データ( V D )を画素電圧信号に変換するデジタル・アナログ変換部( 以下、”D A C 部”という )と、D A C からの画素電圧信号を緩衝して出力する出力バッパ部とを具備する。

#### 【 0 1 1 7 】

また、データI C ( 2 1 6 )などはタイミング制御部( 1 0 8 )から供給される各種の制御信号などと画素データ( V D )を中継する信号制御部( 1 2 0 )と、D A C 部( 1 3 8 )で必要とする正極性及び負極性のガンマ電圧などを供給するガンマ電圧部( 1 3 2 )とを更に具備する。

#### 【 0 1 1 8 】

このような、チャンネル選択部( 3 1 8 )及びシフト・レジスタ部( 3 3 4 )を除いてはラッチ部、D A C 部、出力バッパ部、信号制御部及びガンマ電圧部を含むデータI C ( 2 1 6 )は上述した本発明の第1実施例による液晶表示装置のデータI C と同一のために上述した説明に代えることとする。

#### 【 0 1 1 9 】

本発明の第3実施例による液晶表示装置のデータI C ( 2 1 6 )でデータI C ( 2 1 6 )のシフト・レジスタ部( 3 3 4 )はN個のシフト・レジスタなど( S R 1 乃至 S R n )で構成される。シフト・レジスタ部( 3 3 4 )に含まれたシフト・レジスタなどは信号制御部からのソース・スタート・パルス( S S P )をソース・スタート・パルス( S S P )につれてシフトさせてサンプリング信号に出力する。このような、シフト・レジスタ部( 3 3 4 )の第N番目のシフト・レジスタ( S R n )の出力信号( C a r r y )は次の段のデータI C ( 2 1 6 )の第1番目のシフト・レジスタ( S R 1 )に供給される。この際、シフト・レジスタ部( 3 3 4 )は一例で642個のシフト・レジスタなど( S R 1 乃至 S R 6 4 2 )で構成されたことと仮定して説明する。

#### 【 0 1 2 0 】

チャンネル選択部( 3 1 8 )は第1及び第2チャンネル選択信号( P 1 , P 2 )につれて第I 1 ( ただし、I 1 は1より大きい陽の正数 )番目のシフト・レジスタ( S R I 1 )の出力信号、第I 2 ( ただし、I 2 はI 1 より大きい陽の正数 )番目のシフト・レジスタ( S R I 2 )の出力信号及び第I 3 ( ただし、I 3 はI 2 より大きてNより小さい陽の正数 )番目のシフト・レジスタ( S R I 3 )の出力信号の中のいずれか一つを選択して出力する第

10

20

30

40

50

1マルチプレクサ(350)と、第1及び第2チャンネル選択信号(P1, P2)につれて第1マルチプレクサ(350)の出力信号を第J1(ただ、J1はI3より大きい陽の正数)番目のシフト・レジスタ(SRJ1)の出力信号、第J2(ただ、J2はJ1より大きい陽の正数)番目のシフト・レジスタ(SRJ2)の出力信号及び第J3(ただ、J3はJ2より大きてNより小さい陽の正数)番目のシフト・レジスタ(SRJ3)の出力信号の中のいずれか一つで供給するディマルチプレクサ(352)と、第2チャンネル選択信号(P2)につれて第J1-1番目のシフト・レジスタ(SRJ1-1)の出力信号及びディマルチプレクサ(352)の出力信号の中のいずれか一つをJ1番目のシフト・レジスタ(SRJ1)へ供給する第2マルチプレクサ(354)と、第1チャンネル選択信号(P1)につれて第J2-1番目のシフト・レジスタ(SRJ2-1)の出力信号及びディマルチプレクサ(352)の出力信号の中のいずれか一つを第J2番目のシフト・レジスタ(SRJ2)へ供給する第3マルチプレクサ(356)と、第2チャンネル選択信号(P2)につれて第J3-1番目のシフト・レジスタ(SRJ3-1)の出力信号及びディマルチプレクサ(352)の出力信号の中のいずれか一つを第J3-1番目のシフト・レジスタ(SRJ3-1)の出力信号及びディマルチプレクサ(352)の出力信号の中のいずれか一つを第J3番目のシフト・レジスタ(SRJ3)へ供給する第4マルチプレクサ(358)とを具備する。ここで、以下、I1は第300番目のシフト・レジスタ(SR300)とし、I2は第309番目のシフト・レジスタ(SR309)とし、I3は第315番目のシフト・レジスタ(SR315)とする。また、J1は第328番目のシフト・レジスタ(SR328)とし、J2は第334番目のシフト・レジスタ(SR334)とし、J3は第343番目のシフト・レジスタ(SR343)とする。ここで、第1マルチプレクサ(350)は第1選択部になり、ディマルチプレクサ(352)、第2乃至第4マルチプレクサ(354, 356, 358)は第2選択部(319)になる。

10

20

20

### 【0121】

このような、第1マルチプレクサ(350)は第1及び第2チャンネル選択信号(P1, P2)の論理値が”00”である場合に第300番目のシフト・レジスタ(SR300)から供給される出力信号を選択してディマルチプレクサ(352)に供給する。また、第1マルチプレクサ(350)は第1及び第2チャンネル選択信号(P1, P2)の論理値が”01”である場合に第309番目のシフト・レジスタ(SR309)から供給される出力信号を選択してディマルチプレクサ(352)に供給する。そして、第1マルチプレクサ(350)は第1及び第2チャンネル選択信号(P1, P2)の論理値が”10”である場合に第315番目のシフト・レジスタ(SR315)から供給される出力信号を選択してディマルチプレクサ(352)に供給する。半面に、第1マルチプレクサ(350)は第1及び第2チャンネル選択信号(P1, P2)の論理値が”11”である場合に無対処条件(Do not Care Conditions)になる。

30

### 【0122】

ディマルチプレクサ(352)は第1及び第2チャンネル選択信号(P1, P2)の論理値が”00”である場合に第1マルチプレクサ(350)から供給される出力信号を第4マルチプレクサ(358)に供給する。また、ディマルチプレクサ(352)は第1及び第2チャンネル選択信号(P1, P2)の論理値が”01”である場合に第1マルチプレクサ(350)から供給される出力信号を第3マルチプレクサ(356)に供給する。そして、ディマルチプレクサ(352)は第1及び第2チャンネル選択信号(P1, P2)の論理値が”10”である場合に第1マルチプレクサ(350)から供給される出力信号を第2マルチプレクサ(354)に供給する。半面に、ディマルチプレクサ(352)は第1及び第2チャンネル選択信号(P1, P2)の論理値が”11”である場合に無情の条件になる。

40

### 【0123】

第2マルチプレクサ(354)は第2チャンネル選択信号(P2)の論理値が”0”である場合にディマルチプレクサ(352)からの出力信号を第328番目のシフトレジス

50

タ ( S R 3 2 8 ) に供給する。また、第 2 マルチブレクサ ( 3 5 4 ) は第 2 チャンネル選択信号 ( P 2 ) の論理値が " 1 " である場合に第 3 2 7 番目のシフトレジスタ ( S R 3 2 7 ) からの出力信号を第 3 2 8 番目のシフト・レジスタ ( S R 3 2 8 ) に供給する。

【 0 1 2 4 】

第 3 マルチブレクサ ( 3 5 6 ) は第 1 チャンネル選択信号 ( P 1 ) の論理値が " 0 " である場合にディマルチブレクサ ( 3 5 2 ) からの出力信号を第 3 3 4 番目のシフトレジスタ ( S R 3 3 4 ) に供給する。また、第 3 マルチブレクサ ( 3 5 6 ) は第 1 チャンネル選択信号 ( P 1 ) の論理値が " 1 " である場合に第 3 3 3 番目のシフトレジスタ ( S R 3 3 3 ) からの出力信号を第 3 3 4 番目のシフト・レジスタ ( S R 3 3 4 ) に供給する。

【 0 1 2 5 】

第 4 マルチブレクサ ( 3 5 8 ) は第 2 チャンネル選択信号 ( P 2 ) の論理値が " 0 " である場合にディマルチブレクサ ( 3 5 2 ) からの出力信号を第 3 4 3 番目のシフトレジスタ ( S R 3 4 3 ) に供給する。また、第 4 マルチブレクサ ( 3 5 8 ) は第 2 チャンネル選択信号 ( P 2 ) の論理値が " 1 " である場合に第 3 4 2 番目のシフトレジスタ ( S R 3 4 2 ) からの出力信号を第 3 4 3 番目のシフト・レジスタ ( S R 3 4 3 ) に供給する。

【 0 1 2 6 】

このような、第 1 及び第 2 チャンネル選択信号 ( P 1 , P 2 ) によるチャンネル選択部 ( 3 1 8 ) 及びシフト・レジスタ部 ( 3 3 4 ) の動作を説明すると次のようである。

【 0 1 2 7 】

まず、図 1 1 に示したようにデータ I C ( 2 1 6 ) の出力チャンネルなどの中の第 1 乃至 3 0 0 番目の出力チャンネルなどを第 1 出力チャンネル群 ( 2 6 0 ) で選択して、第 3 0 1 乃至 3 4 2 番目の出力チャンネルなどをダミー出力チャンネル群 ( 2 6 4 ) に選択して、第 3 4 3 乃至 第 6 4 2 番目の出力チャンネルなどを第 2 出力チャンネル群 ( 2 6 2 ) に選択する場合に、データ I C ( 2 1 6 ) のチャンネル選択部 ( 3 1 8 ) には " 0 0 " の論理値を有する 1 及び第 2 チャンネル選択信号 ( P 1 , P 2 ) が供給される。これにつれて、シフト・レジスタ部 ( 3 3 4 ) は第 1 乃至 第 6 0 0 番目のシフト・レジスタなど ( S R 1 乃至 S R 6 0 0 ) を利用してソース・スタート・パルス ( S S P ) をソース・サンプリング・クラック信号 ( S S C ) につれて順次にシフトさせてサンプリング信号に出力するようになる。この際、第 3 0 0 番目のシフト・レジスタ ( S R 3 0 0 ) の出力信号は第 1 マルチブレクサ ( 3 5 0 ) 、ディマルチブレクサ ( 3 5 2 ) 及び第 4 マルチブレクサ ( 3 5 8 ) を経由して第 3 4 3 番目のシフト・レジスタ ( S R 3 4 3 ) に供給される。ここで、第 6 4 2 番目のシフト・レジスタ ( S R 6 4 2 ) の出力信号は次の段のデータ I C ( 2 1 6 ) の第 1 シフト・レジスタ ( S R 1 ) に供給される。これにつれて、第 1 乃至 第 3 0 0 番目のシフト・レジスタ ( S R 1 乃至 S R 3 0 0 ) と第 3 4 3 乃至 第 6 4 2 番目のシフト・レジスタ ( S R 3 4 3 乃至 S R 6 4 2 ) はサンプリング信号をラッチ部に供給する。この際、実質的に第 3 0 1 乃至 第 3 4 2 番目のシフト・レジスタ ( S R 3 0 1 乃至 S R 3 4 2 ) もまたサンプリング信号をラッチ部に供給するようになる。

【 0 1 2 8 】

一方、図 1 2 に示したようにデータ I C ( 2 1 6 ) の出力チャンネルなどの中の第 1 乃至 第 3 0 9 番目の出力チャンネルなどを第 1 出力チャンネル群 ( 2 6 0 ) に選択して、第 3 1 0 乃至 3 3 3 番目の出力チャンネルなどをダミー出力チャンネル群 ( 2 6 4 ) に選択して、第 3 3 4 乃至 第 6 4 2 番目の出力チャンネルなどを第 2 出力チャンネル群 ( 2 6 2 ) に選択する場合に、データ I C ( 2 1 6 ) のチャンネル選択部 ( 3 1 8 ) には " 0 1 " の論理値を有する 1 及び第 2 チャンネル選択信号 ( P 1 , P 2 ) が供給される。これにつれて、シフト・レジスタ部 ( 3 3 4 ) は第 1 乃至 第 6 0 0 番目のシフト・レジスタなど ( S R 1 乃至 S R 6 0 0 ) を利用してソース・スタート・パルス ( S S P ) をソース・サンプリング・クラック信号 ( S S C ) につれて順次にシフトさせてサンプリング信号に出力するようになる。この際、第 3 0 9 番目のシフト・レジスタ ( S R 3 0 9 ) の出力信号は第 1 マルチブレクサ ( 3 5 0 ) 、ディマルチブレクサ ( 3 5 2 ) 及び第 3 マルチブレクサ ( 3 5 6 ) を経由して第 3 3 4 番目のシフト・レジスタ ( S R 3 3 4 ) に供給される。こ

10

20

30

40

50

こで、第642番目のシフト・レジスタ(SR642)の出力信号は次の段のデータIC(216)の第1シフト・レジスタ(SR1)に供給される。これにつれて、第1乃至第309番目のシフト・レジスタ(SR1乃至SR309)と第334乃至第642番目のシフト・レジスタ(SR334乃至SR642)はサンプリング信号をラッチ部に供給する。この際、実質的に第310乃至第333番目のシフト・レジスタ(SR310乃至SR333)もまたサンプリング信号をラッチ部に供給するようになる。

#### 【0129】

また一方、図13に示したようにデータIC(216)の出力チャンネルなどの中の第1乃至第315番目の出力チャンネルなどを第1出力チャンネル群(260)に選択して、第316乃至327番目の出力チャンネルなどをダミー出力チャンネル群(264)に選択して、第328乃至第642番目の出力チャンネルなどを第2出力チャンネル群(262)に選択する場合に、データIC(216)のチャンネル選択部(318)には"10"の論理値を有する1及び第2チャンネル選択信号(P1, P2)が供給される。これにつれて、シフト・レジスタ部(334)は第1乃至第600番目のシフト・レジスタなど(SR1乃至SR600)を利用してソース・スタート・パルス(SSP)をソース・サンプリング・クラック信号(SSC)につれて順次にシフトさせてサンプリング信号に出力するようになる。この際、第315番目のシフト・レジスタ(SR315)の出力信号は第1マルチブレクサ(350)、ディマルチブレクサ(352)及び第2マルチブレクサ(354)を経由して第328番目のシフト・レジスタ(SR328)に供給される。ここで、第642番目のシフト・レジスタ(SR642)の出力信号(Carry)は次の段のデータIC(216)の第1シフト・レジスタ(SR1)に供給される。これにつれて、第1乃至第315番目のシフト・レジスタ(SR1乃至SR315)と第328乃至第642番目のシフト・レジスタ(SR328乃至SR642)はサンプリング信号をラッチ部に供給する。この際、実質的に第316乃至第327番目のシフト・レジスタ(SR316乃至SR327)もまたサンプリング信号をラッチ部に供給するようになる。

#### 【0130】

また異なる一方で、図14に示したようにデータIC(216)の出力チャンネルなどの中の第1乃至第321番目の出力チャンネルなどを第1出力チャンネル群(260)に選択して、第322乃至第642番目の出力チャンネルなどを第2出力チャンネル群(262)に選択する場合に、データIC(216)のチャンネル選択部(318)には"11"の論理値を有する1及び第2チャンネル選択信号(P1, P2)が供給される。これにつれて、シフト・レジスタ部(334)は第1乃至第642番目のシフト・レジスタなど(SR1乃至SR642)を利用してソース・スタート・パルス(SSP)をソース・サンプリング・クラック信号(SSC)につれて順次にシフトさせてサンプリング信号に出力するようになる。この際、第1マルチブレクサ(350)、ディマルチブレクサ(352)のそれぞれは無常の条件になる。そして、第327番目のシフト・レジスタ(SR327)の出力信号は第2マルチブレクサ(354)を経由して第328番目のシフト・レジスタ(SR328)に供給されて、第333番目のシフト・レジスタ(SR333)の出力信号は第3ディマルチブレクサ(356)を経由して第334番目のシフト・レジスタ(SR334)に供給されて、第342番目のシフト・レジスタ(SR342)の出力信号は第4ディマルチブレクサ(358)を経由して第343番目のシフト・レジスタ(SR343)に供給される。これにつれて、シフト・レジスタ部(334)の第1乃至第642番目のシフト・レジスタ(SR1乃至SR642)のそれぞれはサンプリング信号をラッチ部に供給するようになる。ここで、第642番目のシフト・レジスタ(SR642)の出力信号は次の段のデータIC(216)の第1シフト・レジスタ(SR1)に供給される。

#### 【0131】

このような、本発明の第3実施例による液晶表示装置のデータIC(216)は上述した本発明の第1実施例による液晶表示装置のデータIC(216)の動作についてシフト

10

20

30

40

50

・レジスタ部(334)から出力されるサンプリング信号を利用してタイミング制御部(108)から供給されるデータ(VD)を画素データに変換して第1及び第2出力チャンネル群(260, 262)及びダミー出力チャンネル群(264)の一部を通して液晶パネル(102)のデータラインなど(DL)に供給する。

【0132】

このような、本発明の第3実施例による液晶表示装置のデータIC(216)は第1及び第2オプションピン(OP1、OP2)に供給される第1及び第2チャンネル選択信号(P1, P2)について表1に表したように液晶パネル(102)の解像図についてデータIC(216)の出力チャンネルを設定することで一種類のデータIC(216)だけでもすべての解像図を表現することができるようになる。これについて、本発明の第1実施例による液晶表示装置は作業性の向上及び製造費用を減少させることができる。

10

【0133】

一方、本発明の第3実施例による液晶表示装置のデータIC(216)は第1及び第2オプションピン(OP1、OP2)に供給される第1及び第2チャンネル選択信号(P1, P2)は図15に示したように第1及び第2スイッチ(Q1, Q2)に対する選択的なスイッチングによって発生することができる。第1及び第2スイッチ(Q1, Q2)に対する詳細な説明は上述した本発明の第2実施例による液晶表示装置の説明に代えることとする。

【0134】

もう一方で、本発明の第3実施例による液晶表示装置のデータIC(216)の第1及び第2オプションピン(OP1、OP2)に供給される第1及び第2チャンネル選択信号(P1, P2)は図15に示したように電圧源(VCC)に接続されると共に第1及び第2オプションピン(OP1、OP2)のそれぞれに接続されたディップ・スイッチ(250)のスイッチング操作によって発生されることができる。ディップ・スイッチ(250)に対する詳細な説明は上述した本発明の第2実施例による液晶表示装置の説明に代えることとする。

20

【0135】

上述したところのように、本発明の第1乃至第3実施例による液晶表示装置では第1及び第2チャンネル選択信号(P1, P2)について642個の出力チャンネルを有するデータIC(116, 216)の出力チャンネルを変更することに対して限り限定されることではなく、642個以下及び以上の出力チャンネルを有するデータIC(116, 216)に同一に適用されることができる。

30

【0136】

また、第1及び第2チャンネル選択信号(P1, P2)について設定されるデータIC(116, 216)の出力チャンネルは600, 618, 630及び642個の出力チャンネルにだけ限定されることではなく、どんな場合にも適用することができる。

【0137】

もう一度言って、第1及び第2チャンネル選択信号(P1, P2)について設定されるデータIC(116, 216)の出力チャンネルは液晶パネル(102)の解像図、TCPの個数、TCPの幅、タイミング制御部(108)からデータIC(116, 216)に画素データ(VD)を伝送するためのタイミング制御部(108)とデータIC(116, 216)の間のデータ伝送ラインの数の中の少なくともいずれか一つの条件によって設定される。これについて、第1及び第2チャンネル選択信号(P1, P2)について設定されるデータIC(116, 216)の出力チャンネルは600, 618, 624, 630, 642, 645, 684, 696, 702, 720などになれる。

40

【0138】

そして、データIC(116, 216)の出力チャンネルを設定するためのチャンネル選択信号(P1, P2)もまた2ビットの2進論理値に限定されることではなく、2ビット以上の2進論理値を有することができる。

【0139】

また異なる一方で、本発明の第1乃至第3実施例による液晶表示装置のデータIC(116, 216)は上述した液晶表示装置を含む平板表示装置に使用されることができる。

【0140】

上述したところのように、本発明による液晶表示装置の駆動装置はチャンネル選択信号を利用して液晶パネルの解像図についてデータ集積回路のチャンネルを変更することで一種類のデータ集積回路を利用して液晶パネルのすべての解像図を駆動させることができるようになる。

【0141】

また、本発明はデータラインなどに一つのデータを供給する第1出力チャンネル群れと第2データ出力チャンネル群の間にダミー・データ出力チャンネル群が形成されたデータ集積回路とを具備して、チャンネル選択信号を利用して液晶パネルの解像図についてデータ集積回路のチャンネルを変更することで一種類のデータ集積回路を利用して液晶パネルのすべての解像を駆動させることができるようになる。

【0142】

従って、本発明は液晶パネルの解像図に関係なく、データ集積回路を共通に使用することができる所以データ集積回路の個数を減少させることができる。結果的に、本発明の実施例による液晶表示装置は作業性の向上及び製造費用を節減することができる。

【0143】

以上説明した内容を通して当業者であると、本発明の技術思想を逸脱しない範囲で多様な変更及び修正が可能であることがわかる。従って、本発明の技術的範囲は詳細な説明に記載された内容に限らず特許請求の範囲により定めなければならない。

【図面の簡単な説明】

【0144】

【図1】従来の液晶表示装置を概略的に表す図面である。

【図2a】従来のゲート・ドライバに含まれているゲート集積回路を表す図面である。

【図2b】従来のデータ・ドライバに含まれているデータ集積回路を表す図面である。

【図3】図2bに示されたデータ集積回路の内部の構造を詳細に表す図面である。

【図4】本発明の第1実施例による液晶表示装置を表す図面である。

【図5】図4に示された第1及び第2チャンネルの選択信号について600個のデータ出力チャンネルを有するように設定したデータ集積回路を表す図面である。

【図6】図4に示された第1及び第2チャンネルの選択信号について618個のデータ出力チャンネルを有するように設定したデータ集積回路を表す図面である。

【図7】図4に示された第1及び第2チャンネルの選択信号について630個のデータ出力チャンネルを有するように設定したデータ集積回路を表す図面である。

【図8】図4に示された第1及び第2チャンネルの選択信号について642個のデータ出力チャンネルを有するように設定したデータ集積回路を表す図面である。

【図9】図4に示されたデータ集積回路の内部の構造を詳細に表す図面である。

【図10】本発明の第2実施例による液晶表示装置のデータ集積回路を表すブロック図である。

【図11】図10に示された第1及び第2チャンネルの選択信号について600個のデータ出力チャンネルを有するように設定したデータ集積回路を表す図面である。

【図12】図10に示された第1及び第2チャンネルの選択信号について618個のデータ出力チャンネルを有するように設定したデータ集積回路を表す図面である。

【図13】図10に示された第1及び第2チャンネルの選択信号について630個のデータ出力チャンネルを有するように設定したデータ集積回路を表す図面である。

【図14】図10に示された第1及び第2チャンネルの選択信号について642個のデータ出力チャンネルを有するように設定したデータ集積回路を表す図面である。

【図15】図10に示された第1及び第2チャンネルの選択信号を発生するためのスイッチング素子などを表す図面である。

【図16】図10に示された第1及び第2チャンネルの選択信号を発生するためのディッ

10

20

30

40

50

プ・スイッチを表す図面である。

【図17】本発明の第3実施例によるデータ集積回路のチャンネル選択部及びシフト・レジスタ部を表すブロック図である。

【符号の説明】

【0145】

2, 102: 液晶パネル

7: 液晶セル

4, 104: データドライバ

6, 106: ゲートドライバ

8, 108: タイミング制御部

10 10: ゲートI C

16, 116, 416: データI C

20, 120: 信号制御部

32, 132: ガンマ電圧部

34, 134: シフト・レジスタ部

36, 136: ラッチ部

38, 138: D A C部

40: Pディコーディング部

42: Nディコーディング部

46, 146: 出力バッパ部

44, 144: マルチプレクサ

110, 610: データT C P

130, 318: チャンネル選択部

184: ダミー・データ入力パッド群

260, 660: 第1データ出力チャンネル群

262, 662: 第2データ出力チャンネル群

264, 664: ダミー・データ出力チャンネル群

350: 第1マルチプレクサ

352: ディマルチプレクサ

354: 第2マルチプレクサ

356: 第3マルチプレクサ

358: 第4マルチプレクサ

10

20

30

【図1】

【図2 a】

【図2 b】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図14】

【図15】

【図12】

【図13】

【図16】

【図17】

## フロントページの続き

(51) Int.CI.<sup>7</sup>

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 3 B |

| G 0 9 G | 3/20 | 6 2 3 F |

| G 0 9 G | 3/20 | 6 2 3 G |

| G 0 9 G | 3/20 | 6 2 3 H |

| G 0 9 G | 3/20 | 6 2 3 R |

| G 0 9 G | 3/20 | 6 2 3 V |

| G 0 9 G | 3/20 | 6 5 0 C |

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100096688

弁理士 本宮 照久

(74)代理人 100104352

弁理士 朝日 伸光

(74)代理人 100128657

弁理士 三山 勝巳

(72)発明者 宋 鴻 聲

大韓民国 慶尚北道 龜尾市 九坪洞 474-7 富榮 アパート 803-706号

(72)発明者 姜 信 浩

大韓民国 京畿道 水原市 八達區 仁溪洞 住公 アパート 112-105号

(72)発明者 洪 鎮 鉄

大韓民国 慶尚北道 龜尾市 呉太洞 テドン3次 アパート 102-1105号

F ターム(参考) 2H093 NA16 NC11 NC34 ND49 ND50

5C006 AA16 AB01 AF23 AF25 AF43 AF45 AF47 AF51 AF59 AF71

AF82 BB16 BC02 BC23 BF03 BF04 FA03 FA51

5C080 AA10 BB05 DD21 EE29 FF11 GG02 JJ02 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 数据驱动集成电路及其驱动方法和使用该集成电路的显示装置                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2005173592A</a>                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2005-06-30 |

| 申请号            | JP2004349838                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2004-12-02 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | Eruji. 菲利普斯杜天公司，有限公司                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 宋鴻聲<br>姜信浩<br>洪鎮鉄                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 发明人            | 宋 鴻 聲<br>姜 信 浩<br>洪 鎮 鉄                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G02F1/133 G02F1/136 G09F9/35 G09G3/20 G09G3/32 G09G3/36                                                                                                                                                                                                                                                                                                                                           |         |            |

| CPC分类号         | G09G3/20 G09G3/3688 G09G2300/0426 G09G2310/027 G09G2340/0421 G02F1/136 G09G3/32<br>A47J17/02 B26D3/02 B26D3/283 B26D2003/285 B26D2003/288                                                                                                                                                                                                                                                         |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.611.F G09G3/20.612.J G09G3/20.612.R G09G3/20.623.B<br>G09G3/20.623.F G09G3/20.623.G G09G3/20.623.H G09G3/20.623.R G09G3/20.623.V G09G3/20.650.C<br>G09G3/20.611.C G09G3/20.621.B G09G3/20.621.M G09G3/20.641.Q                                                                                                                                                    |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NC11 2H093/NC34 2H093/ND49 2H093/ND50 5C006/AA16 5C006/AB01 5C006/AF23<br>5C006/AF25 5C006/AF43 5C006/AF45 5C006/AF47 5C006/AF51 5C006/AF59 5C006/AF71<br>5C006/AF82 5C006/BB16 5C006/BC02 5C006/BC23 5C006/BF03 5C006/BF04 5C006/FA03 5C006/FA51<br>5C080/AA10 5C080/BB05 5C080/DD21 5C080/EE29 5C080/FF11 5C080/GG02 5C080/JJ02<br>5C080/JJ06 2H093/NC12 2H193/ZA04 2H193/ZF36 |         |            |

| 代理人(译)         | 臼井伸一<br>朝日 伸光                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 优先权            | 1020030090301 2003-12-11 KR<br>1020040029611 2004-04-28 KR<br>1020040029612 2004-04-28 KR                                                                                                                                                                                                                                                                                                         |         |            |

| 其他公开文献         | JP4979888B2                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                         |         |            |

**摘要(译)**

要解决的问题：提供一种数据驱动集成电路及其驱动方法，以及使用该电路的液晶显示装置。解决方案：液晶显示装置包括数据集成电路，该数据集成电路具有伪数据输出通道组，该伪数据输出通道组包括用于将像素数据提供给数据线等的数据输出通道组，以及用于选择伪数据输出的输出通道的通道选择器渠道组。通过由通道选择器选择的伪数据输出通道将像素数据提供给数据线等。ž