|                          |      |               |                          |

|--------------------------|------|---------------|--------------------------|

| (51) Int.Cl <sup>7</sup> | 識別記号 | F I           | マークコード <sup>8</sup> (参考) |

| G 0 9 G 3/36             |      | G 0 9 G 3/36  | 2 H 0 9 3                |

| G 0 2 F 1/133            | 550  | G 0 2 F 1/133 | 5 C 0 0 6                |

| G 0 9 G 3/20             | 621  | G 0 9 G 3/20  | 5 C 0 8 0                |

|                          | 623  | 623           | C                        |

|                          | 641  | 641           | C                        |

審査請求 未請求 請求項の数 280 件 (全 15 数)

|             |                                 |         |                                              |

|-------------|---------------------------------|---------|----------------------------------------------|

| (21)出願番号    | 特願2001 - 146858(P2001 - 146858) | (71)出願人 | 390019839<br>三星電子株式会社<br>大韓民国京畿道水原市八達区梅灘洞416 |

| (22)出願日     | 平成13年5月16日(2001.5.16)           | (72)発明者 | 延允模<br>大韓民国ソウル市瑞草区良在洞94 - 16番地               |

| (31)優先権主張番号 | 2000 - 79698                    | (72)発明者 | 李建斌<br>大韓民国ソウル市影登浦区唐山洞サンガアパート3棟411号          |

| (32)優先日     | 平成12年12月21日(2000.12.21)         | (74)代理人 | 100094145<br>弁理士 小野 由己男 (外1名)                |

| (33)優先権主張国  | 韓国(KR)                          |         |                                              |

最終頁に続く

(54)【発明の名称】 液晶ディスプレイ装置及びそのための階調電圧発生回路

(57) 【要約】

【課題】 少費用かつ低電力の液晶ディスプレイ装置の駆動速度を向上させ得る階調電圧発生回路を提供することである。

【解決手段】 ソース駆動回路3は、階調電圧発生回路5から出力される階調電圧に応じて、駆動の極性により、ゲートクロック信号がハイレベルの区間では既存の液晶駆動電圧に比べて高レベルの液晶駆動電圧を発生させ、ローレベルのゲートクロック信号が印加されると、既存の液晶駆動電圧と同一なレベルの液晶駆動電圧を発生させる。

## 【特許請求の範囲】

【請求項1】液晶ディスプレイ装置において、多数の画素を備えた液晶パネルと、ゲートクロック信号及び多数の制御信号を発生させるためのタイミング制御回路と、前記ゲートクロック信号に応じて前記液晶パネルにディスプレイされるデータに対応する多数の階調電圧を発生させるための階調電圧発生回路と、前記ゲートクロック信号に応じて前記液晶パネルの前記画素を1列ずつ順次にスキャニングするためのゲート駆動回路と、前記階調電圧及び前記制御信号に応じて前記液晶パネルにディスプレイされるデータに対応する液晶駆動電圧を発生させ、発生された前記液晶駆動電圧をスキャニング毎に前記液晶パネルに印加するためのソース駆動回路とを含み、前記ソース駆動回路は、前記階調電圧に応じて、前記ゲートクロック信号のハイレベル区間とローレベル区間毎に各々異なる値を有する液晶駆動電圧を発生させる、液晶ディスプレイ装置。

【請求項2】前記ソース駆動回路は、前記液晶パネルの正極性駆動の時、前記ゲートクロック信号のハイレベル区間の間、第1電圧レベルの液晶駆動電圧を発生させ、前記ゲートクロック信号のローレベル区間の間、前記第1電圧よりも低電位である第2電圧レベルの液晶駆動電圧を発生させる、請求項1に記載の液晶ディスプレイ装置。

【請求項3】前記ソース駆動回路は、前記液晶パネルの負極性駆動の時、前記ゲートクロック信号のハイレベル区間の間、第3電圧レベルの液晶駆動電圧を発生させ、前記ゲートクロック信号のローレベル区間の間、前記第3電圧よりも高電位の第4電圧レベルの液晶駆動電圧を発生させる、請求項2に記載の液晶ディスプレイ装置。

【請求項4】前記階調電圧発生回路は、前記ゲートクロック信号に応じて前記ゲートクロック信号と同一な周期を有する多数のクロック信号を発生させるためのクロック発生部と、前記ソース駆動回路の電源電圧を所定比率で分圧して、前記階調電圧を発生させるのに基準になる多数の電圧を発生させるための電圧発生部と、前記クロック発生部及び前記電圧発生部から発生された前記クロック信号及び前記電圧に応じて多数の前記階調電圧を前記ソース駆動回路に出力させるための階調電圧発生部とを含む、請求項1に記載の液晶ディスプレイ装置。

【請求項5】前記クロック発生部は、前記ゲートクロック信号を取る込むための入力端子と、前記入力端子に並列に連結されたn個のクロック発生ユニットと、

10

20

30

40

50

前記n個のクロック発生ユニット各々に連結されたn個の出力端子とを含む、請求項4に記載の液晶ディスプレイ装置。

【請求項6】前記電圧発生部は、前記電源電圧を所定比率で分圧して各々異なる電圧レベルのn個の前記電圧を発生させるためのn個の電圧発生ユニットを含み、

前記各々の電圧発生ユニットは、前記電源電圧と接地電圧の間に連結された少なくとも2つ以上の抵抗と、前記抵抗の間の接点のうちいずれか1つに連結された出力端子を含む請求項4に記載の液晶ディスプレイ装置。

【請求項7】前記階調電圧発生部は、前記液晶パネルの正極性駆動のために、前記ゲートクロック信号と同一な極性及び各々異なるレベルのm/2個の階調電圧を発生させる第1階調電圧発生ユニットと、前記液晶パネルの負極性駆動のために、前記ゲートクロック信号と反対の極性及び各々異なるレベルのm/2個の階調電圧を発生させる第2階調電圧発生ユニットを含む、請求項4に記載の液晶ディスプレイ装置。

【請求項8】前記第1階調電圧発生ユニットは、前記クロック発生部から入力される前記n個のクロック信号のうちいずれか1つと、前記電圧発生部から入力される前記n個の基準電圧のうちいずれか1つを取り込むための第1入力端子と、抵抗を通じて接地された第2入力端子と、フィードバック抵抗を通じて前記第2入力端子と接続された出力端子と、を備えた少なくとも1つ以上の増幅回路を含む、請求項7に記載の液晶ディスプレイ装置。

【請求項9】前記増幅回路は、前記クロック信号と前記基準電圧を加算した後、これを所定比率で増幅して前記階調電圧を発生させる、請求項8に記載の液晶ディスプレイ装置。

【請求項10】前記増幅回路は、前記階調電圧を分圧するための少なくとも1つ以上の抵抗と、前記抵抗の接点に連結されて前記分圧された階調電圧を出力するための少なくとも1つ以上の出力端子と、を含む、請求項8に記載の液晶ディスプレイ装置。

【請求項11】前記第2階調電圧発生ユニットは、前記電圧発生部から入力される前記n個の基準電圧のうちいずれか1つを取り込むための第1入力端子と、抵抗を通じて前記クロック発生部から入力される前記n個のクロック信号のうちいずれか1つを取り込むための第2入力端子と、

フィードバック抵抗を通じて前記第2入力端子に接続された出力端子と、を備えた少なくとも1つ以上の増幅回路を含む、請求項7に記載の液晶ディスプレイ装置。

【請求項12】前記増幅回路は、前記基準電圧から前記クロック信号を減算した後、これを所定比率で増幅して前記階調電圧を発生させる、請求項11に記載の液晶デ

ィスプレイ装置。

【請求項13】前記增幅回路は、前記階調電圧を分圧するための少なくとも1つ以上の抵抗と、前記抵抗の接点に連結されて前記分圧された階調電圧を出力するための少なくとも1つ以上の出力端子を含む、請求項11に記載の液晶ディスプレイ装置。

【請求項14】多数の画素を備えた液晶パネルと、前記液晶パネルにディスプレイされるデータに対応する多数の階調電圧を発生させるための階調電圧発生回路と、ゲートクロック信号及び多数の制御信号を発生させるためのタイミング制御回路と、前記ゲートクロック信号に応じて前記液晶パネルの前記画素を1列ずつ順次にスキャニングするためのゲート駆動回路と、前記階調電圧及び前記制御信号に応じて前記液晶パネルにディスプレイされるデータに対応する液晶駆動電圧を発生させ、発生された前記液晶駆動電圧をスキャニング毎に前記液晶パネルに印加するためのソース駆動回路とを備えた液晶ディスプレイ装置の階調電圧発生回路において、

前記ゲートクロック信号に応じて前記ゲートクロック信号と同一な周期を有する多数のクロック信号を発生させるためのクロック信号発生部と、

前記ソース駆動回路の電源電圧を所定比率で分圧して、前記階調電圧を発生させるのに基準になる多数の電圧を発生させるための電圧発生部と、

前記クロック発生部及び前記電圧発生部から発生された前記クロック信号及び前記電圧に応じて多数の前記階調電圧を前記ソース駆動回路に出力させるための階調電圧発生部とを含む、液晶ディスプレイ装置のための階調電圧発生回路。

【請求項15】前記クロック発生部は、前記ゲートクロック信号を取り込むための入力端子と、前記入力端子に並列に連結されたn個のクロック発生ユニットと、

前記n個のクロック発生ユニット各々に連結されたn個の出力端子とを含む、請求項14に記載の液晶ディスプレイ装置のための階調電圧発生回路。

【請求項16】前記電圧発生部は、前記電源電圧を所定比率で分圧して、各々異なる電圧レベルのn個の前記電圧を発生させるためのn個の電圧発生ユニットを含み、

前記各々の電圧発生ユニットは、前記電源電圧と接地電圧の間に連結された少なくとも2つ以上の抵抗と、前記抵抗の間の接点のうちいずれか1つに連結された出力端子を含む、請求項14に記載の液晶ディスプレイ装置のための階調電圧発生回路。

【請求項17】前記階調電圧発生部は、前記液晶パネルの正極性駆動のために、前記ゲートクロック信号と同一な極性及び各々異なるレベルのm/2個の階調電圧を発生させる第1階調電圧発生ユニットと、前記液晶パネルの負極性駆動のために、前記ゲートクロ

ック信号と反対される極性及び各々異なるレベルのm/2個の階調電圧を発生させる第2階調電圧発生ユニットを含む、請求項14に記載の液晶ディスプレイ装置のための階調電圧発生回路。

【請求項18】前記第1階調電圧発生ユニットは、前記クロック発生部から入力される前記n個のクロック信号のうちいずれか1つと、前記電圧発生部から入力される前記n個の基準電圧のうちいずれか1つを取り込むための第1入力端子と、

10 抵抗を通じて接地された第2入力端子と、フィードバック抵抗を通じて前記第2入力端子に接続された出力端子と、を備えた少なくとも1つ以上の增幅回路とを含む、請求項17に記載の液晶ディスプレイ装置のための階調電圧発生回路。

【請求項19】前記增幅回路は、前記クロック信号と前記基準電圧を加算した後、これを所定比率で増幅して前記階調電圧を発生させる、請求項18に記載の液晶ディスプレイ装置のための階調電圧発生回路。

【請求項20】前記增幅回路は、前記階調電圧を分圧するための少なくとも1つ以上の抵抗と、前記抵抗の接点に連結されて前記分圧された階調電圧を出力するための少なくとも1つ以上の出力端子と、を含む請求項18に記載の液晶ディスプレイ装置のための階調電圧発生回路。

【請求項21】前記第2階調電圧発生ユニットは、前記電圧発生部から入力される前記基準電圧のうちいずれか1つを取り込むための第1入力端子と、抵抗を通じて前記クロック発生部から入力される前記n個のクロック信号のうちいずれか1つを取り込むための第2入力端子と、フィードバック抵抗を通じて前記第2入力端子と接続された出力端子と、を備えた少なくとも1つ以上の增幅回路とを含む請求項17に記載の液晶ディスプレイ装置のための階調電圧発生回路。

【請求項22】前記增幅回路は、前記基準電圧から前記クロック信号を減加算した後、これを所定比率で増幅して前記階調電圧を発生させる、請求項21に記載の液晶ディスプレイ装置のための階調電圧発生回路。

40 【請求項23】前記增幅回路は、前記階調電圧を分圧するための少なくとも1つ以上の抵抗と、前記抵抗の接点に連結されて前記分圧された階調電圧を出力するための少なくとも1つ以上の出力端子を含む、請求項21記載の液晶ディスプレイ装置のための階調電圧発生回路。

【請求項24】多数の画素を備えた液晶パネルと、前記液晶パネルにディスプレイされるデータに対応する多数の階調電圧を発生させるための階調電圧発生回路と、ゲートクロック信号及び多数の制御信号を発生させるためのタイミング制御回路と、前記ゲートクロック信号に応じて前記液晶パネルの前記画素を1列ずつ順次にスキャ

ニングするためのゲート駆動回路と、前記階調電圧及び前記制御信号に応じて前記液晶パネルにディスプレイされるデータに対応する液晶駆動電圧を発生させ、発生された前記液晶駆動電圧をスキャニング毎に前記液晶パネルに印加するためのソース駆動回路とを備えた液晶ディスプレイ装置の階調電圧発生回路において、前記ソース駆動回路は、前記階調電圧に応じて、前記ゲートクロック信号のハイレベル区間とローレベル区間毎に各々異なる値を有する液晶駆動電圧を発生させる、液晶ディスプレイ装置のための階調電圧発生回路。

【請求項25】前記ソース駆動回路が、前記液晶パネルの正極性駆動の時、前記ゲートクロック信号のハイレベル区間の間、第1電圧レベルの液晶駆動電圧を発生させ、前記ゲートクロック信号のローレベル区間の間、前記第1電圧よりも低電位である第2電圧レベルの液晶駆動電圧を発生させるように、前記ソース駆動回路に前記階調電圧を出力する、請求項24に記載の液晶ディスプレイ装置のための階調電圧発生回路。

【請求項26】前記ソース駆動回路が、前記液晶パネルの負極性駆動の時、前記ゲートクロック信号のハイレベル区間の間、第3電圧レベルの液晶駆動電圧を発生させ、前記ゲートクロック信号のローレベル区間の間、前記第3電圧よりも高電位の第4電圧レベルの液晶駆動電圧を発生させるように、前記ソース駆動回路に前記階調電圧を出力する、請求項25に記載の液晶ディスプレイ装置。

【請求項27】前記各々のクロック発生ユニットは、前記入力端子と前記出力端子の間に直列に連結されたキャパシタと抵抗を備え、前記ゲートクロック信号と同一な周期を有するクロック信号を発生させる、請求項5に記載の液晶ディスプレイ装置。

【請求項28】前記各々のクロック発生ユニットは、前記入力端子と前記出力端子の間に直列に連結されたキャパシタと抵抗を備え、前記ゲートクロック信号と同一な周期を有するクロック信号を発生させる、請求項15に記載の液晶ディスプレイ装置。

#### 【発明の詳細な説明】

##### 【0001】

【発明の属する技術分野】本発明は、液晶ディスプレイ装置に関し、さらには高速に駆動される液晶ディスプレイ装置に関する。

【0002】また本発明は、その液晶ディスプレイ装置のための階調電圧発生回路に関する。

##### 【0003】

【従来の技術】一般的に、液晶(Liquid Crystal)は或る温度の範囲で液体と結晶の中間性質を有する有機化合物であり、電圧又は温度に従って色又は透明度が変わる。液晶を利用して情報を表現するLCD(Liquid Crystal Display)は従来のディスプレイ装置に比べて、小型で、小電力であ

るので新たなディスプレイ装置として脚光を浴びている。

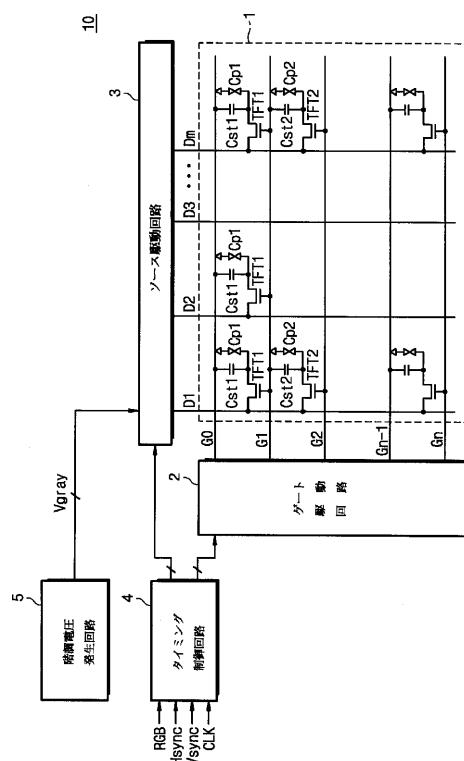

【0004】図1は一般的な液晶ディスプレイ装置10の構成を示すための構成図である。図1を参照すると、液晶ディスプレイ装置10は、液晶パネル1、液晶パネル1に連結されたゲート駆動回路2、ソース駆動回路3、タイミング制御回路4、そして、階調電圧発生回路(gray voltage generating circuit)又はガンマ基準電圧発生器(gamma reference generating circuit)5を含む。

【0005】液晶パネル1は、多数のゲートライン(G0-Gn)とゲートライン(G0-Gn)各々に垂直に交差する多数のデータライン(D1-Dm)で構成される。各々のゲートライン(G0-Gn)にはゲート駆動回路2が連結され、各々のデータライン(D1-Dm)にはソース駆動回路3が連結される。液晶パネル1の各ゲートラインとデータラインが交差する各々の領域には1つの画素(pixel)が構成され、各々の画素は1つの薄膜トランジスタ(Thin Film Transistor:TFT)、1つの維持キャパシタ(storing capacitor:Cst)、そして1つの液晶キャパシタ(liquid crystal capacitor:Cp)で構成される。液晶パネル1を構成する各々の画素は、赤(red:R)、緑(green:G)、青(blue:B)に対応する3つの付属画素(subpixels)をさらに含む。液晶パネル1を通じてディスプレイされる画像は、R,G,B3種類の色フィルタの組合によって得られ、これらの組合によって液晶ディスプレイ装置10は色画像だけでなく純粋な赤、緑、青と、グレースケール(gray scales)をディスプレイできる。

【0006】タイミング制御信号4は、色信号(R,G,B)、水平及び垂直同期信号(HSync, VSync)、そして、クロック信号(CLK))に応じてゲート駆動回路2及びソース駆動回路3に必要な制御信号(例えば、ゲートクロック(Gate Clock)、ゲートオン信号(Gate On Signal)等)を発生させる。そして、階調電圧発生回路5はソース駆動回路3に連結されて、液晶駆動電圧(Vdrive)を発生させるのに基準になる電圧(階調電圧(gray voltage:Vgray)又はガンマ基準電圧(gamma reference voltage))を発生させる。階調電圧発生回路5の一例は2000年5月23日、Kim等による米国特許第6,067,063号に“LIQUID CRYSTAL DISPLAY HAVING A WIDEVIEW ANGLE AND METHOD FOR DRIVING THE SAME”的名称で開示されている。ここに開示されている階調電圧発生回路5は、電源電圧

(VCC) と接地 (GND) の間に直列連結された多数の抵抗 (R1 ~ Rn+1) を含み、各抵抗 (R1 ~ Rn+1) は電源電圧 (VCC) を所定比率で分配して、n 個の階調電圧 (VG1 ~ VGn) を発生させる。

【0007】前記のような構造を有する液晶ディスプレイ装置 10 の動作は次のとおりである。先ず、ゲート駆動回路 2 が液晶パネル 1 の画素を 1 列ずつ順次にスキャニングすると、ソース駆動回路 3 は、階調電圧発生回路 5 から出力される基準電圧 (Vgray) に応じてタイミング制御回路 4 を通じて入力される色信号 (R, G, B) による液晶駆動電圧 (Vdrive) を発生させ、発生された液晶駆動電圧 (Vdrive) をスキャニング毎に液晶パネル 1 に印加する動作を遂行する。

【0008】このような動作を遂行することにおいて、薄膜トランジスタ (TFT) はスイッチとして作用する。例えば、トランジスタがターンオンである場合、ソース駆動回路 3 から発生された液晶駆動電圧 (Vdrive) によって液晶キャパシタ (Cp) が充填され、トランジスタがターンオフである場合、液晶キャパシタ (Cp) に充填された電圧が漏洩されるのを防止する。従って、液晶パネル 1 を構成する各々の薄膜トランジスタ (TFT) を駆動させるのに、ソース駆動回路 3 から印加される液晶駆動電圧 (Vdrive) が重要な影響を与える。

【0009】産業の発達に従って、高速化されつつある液晶ディスプレイ装置の技術分野の特性において、液晶キャパシタ (Cp) の充填の時、ソース駆動回路 3 から印加される液晶駆動電圧 (Vdrive) が高い値を有すると、液晶キャパシタ (Cp) は低い液晶駆動電圧 (Vdrive) が印加される時に比べて、より速く充填され、液晶キャパシタ (Cp) の速い充填は液晶ディスプレイ装置の全体駆動速度を向上させ得るので、液晶キャパシタ (Cp) の充填速度の改善は液晶ディスプレイ装置の駆動速度を改善させ得る。

【0010】液晶ディスプレイ装置の駆動速度を向上させるためにソース駆動回路 3 から印加される液晶駆動電圧 (Vdrive) を高める方法は様々である。例えば、高レベルの液晶駆動電圧 (Vdrive) を発生するようにゲート駆動回路 2 又はソース駆動回路 3 自体の設計を変更したり、この駆動回路 2, 3 に制御信号を発生させるタイミング制御回路 4 の設計を変更させたりする方法がある。しかし、このような比較的に高価の回路に対する設計の変更は、液晶ディスプレイ装置の生産単価を高める問題点がある。そして、液晶駆動電圧 (Vdrive) の電位を一律的に高めると、高い液晶駆動電圧 (Vdrive) ほど液晶ディスプレイ装置の電力消耗が増加する問題点がある。従って、少費用かつ低電力の液晶ディスプレイ装置の駆動速度を向上させ得る方法が要求される。

【0011】

【発明が解決しようとする課題】本発明の目的は、少費用かつ低電力の液晶ディスプレイ装置の駆動速度を向上させ得る階調電圧発生回路を提供することである。

#### 【0012】

【課題を解決するための手段】前述の目的を達成するための本発明に係る液晶ディスプレイ装置は、多数の画素を備えた液晶パネルと、液晶パネルにディスプレイされるデータに対応する多数の階調電圧を発生させる階調電圧発生回路と、ゲートクロック信号及び多数の制御信号を発生させるためのタイミング制御信号と、ゲートクロック信号に応じて液晶パネルの画素を 1 列ずつ順次にスキャニングするためのゲート駆動回路と、階調電圧及び制御信号に応じて液晶パネルにディスプレイされるデータに対応する液晶駆動電圧を発生させ、発生された液晶駆動電圧をスキャニング毎に液晶パネルに印加するためのソース駆動回路とを含む。そしてソース駆動回路は、階調電圧に応じて、ゲートクロック信号のハイレベル区間とローレベル区間毎に各々異なる値を有する液晶駆動電圧を発生させる。

【0013】ここで、ソース駆動回路は、以下のように液晶駆動電圧を発生させる。液晶パネルは、ソース電極からドレイン電極を介して液晶駆動電圧を受ける画素電極と、画素電極に対向するように形成され共通電圧が印加される共通電極と、画素電極と共通電極との間に配置される液晶とを備えている。そして、共通電極に印加される共通電圧と画素電極に印加される液晶駆動電圧との電位差により、液晶が駆動される。

##### ・液晶パネルの正極性駆動の時

(a) ゲートクロック信号のハイレベル区間の間、共通電圧よりも高い第 1 電圧レベルの液晶駆動電圧を発生させる。

(b) ゲートクロック信号のローレベル区間の間、共通電圧よりも高くかつ第 1 電圧よりも低電位である第 2 電圧レベルの液晶駆動電圧を発生させる。

##### ・液晶パネルの負極性駆動の時

(c) ゲートクロック信号のハイレベル区間の間、共通電圧よりも低い第 3 電圧レベルの液晶駆動電圧を発生させる。

(d) ゲートクロック信号のローレベル区間の間、共通電圧よりも低く第 3 電圧よりも高電位の第 4 電圧レベルの液晶駆動電圧を発生させる。

【0014】階調電圧発生回路は、クロック発生部と電圧発生部とソース駆動回路部とを備えている。ここで、クロック発生部は、ゲートクロック信号に応じてゲートクロック信号と同一な周期を有する多数のクロック信号を発生させる。電圧発生部は、ソース駆動回路の電源電圧を所定比率で分圧して、階調電圧を発生させるのに基準になる多数の電圧を発生させる。階調電圧発生部は、クロック発生部及び電圧発生部から発生されたクロック信号及び電圧に応じて、多数の階調電圧をソース駆動回

路に出力させる。

【0015】クロック発生部は、ゲートクロック信号を取る込むための入力端子と、入力端子に並列に連結されたn個のクロック発生ユニットと、n個のクロック発生ユニット各々に連結されたn個の出力端子とを含んでいる。そして、クロック発生ユニットは、入力端子と出力端子の間に直列に連結されたキャパシタと抵抗を備えており、ゲートクロック信号と同一な周期を有するクロック信号を発生させる。

【0016】電圧発生部は、電源電圧を所定比率で分圧して各々異なる電圧レベルのn個の電圧を発生させるためのn個の電圧発生ユニットを含んでいる。そして、各々の電圧発生ユニットは、電源電圧と接地電圧の間に連結された少なくとも2つ以上の抵抗と、抵抗の間の接点のうちいずれか1つに連結された出力端子を含んでいる。

【0017】階調電圧発生部は、第1階調電圧発生ユニットと第2階調電圧発生ユニットとを備えている。ここで、第1階調電圧発生ユニットは、液晶パネルの正極性駆動のために、ゲートクロック信号と同一な極性及び各々異なるレベルのm/2個の階調電圧を発生させる。一方、第2階調電圧発生ユニットは、液晶パネルの負極性駆動のために、ゲートクロック信号と反対の極性及び各々異なるレベルのm/2個の階調電圧を発生させる。

【0018】第1階調電圧発生ユニットは、第1入力端子と第2入力端子出力端子を備えた少なくとも1つ以上の增幅回路を有している。第1入力端子は、クロック発生部から入力されるn個のクロック信号のうちいずれか1つと、電圧発生部から入力されるn個の基準電圧のうちいずれか1つを取り込む。第2入力端子は、抵抗を通じて接地されている。出力端子は、フィードバック抵抗を通じて第2入力端子と接続されている。第1階調電圧発生ユニットの增幅回路は、クロック信号と基準電圧を加算した後、これを所定比率で増幅して、階調電圧を発生させる。

【0019】第2階調電圧発生ユニットも、第1階調電圧発生ユニットと同様に、第1入力端子と第2入力端子と出力端子とを備えている。但し、第2入力端子は、抵抗を通じてクロック発生部から入力されるn個のクロック信号のうちいずれか1つを取り込む点において、第1階調電圧発生ユニットと異なる。第2階調電圧発生ユニットの増幅回路は、基準電圧からクロック信号を減算した後、これを所定比率で増幅して階調電圧を発生させる。

【0020】また第1及び第2階調電圧発生ユニット増幅回路は、階調電圧を分圧するための少なくとも1つ以上の抵抗と、抵抗の接点に連結されて分圧された階調電圧を出力するための少なくとも1つ以上の出力端子とを含んでいる。

【0021】

【発明の実施の形態】以下、本発明による実施形態を添付した図2乃至図13を参照して詳細に説明する。

【0022】本発明の新規な液晶ディスプレイ装置の階調電圧発生回路は、ソース駆動回路が液晶キャパシタを短時間に充填させ得るよう、所定区間の間、高電位の液晶駆動電圧を発生させ、前記区間の以降には一般的な液晶駆動電圧を発生させるように、階調電圧を変形させて出力する。その結果、低電力消耗で液晶ディスプレイ装置の駆動速度が向上される。

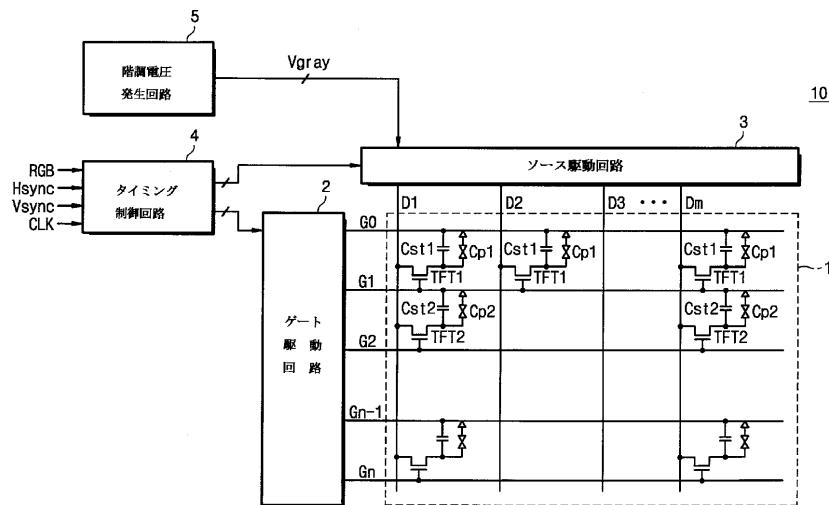

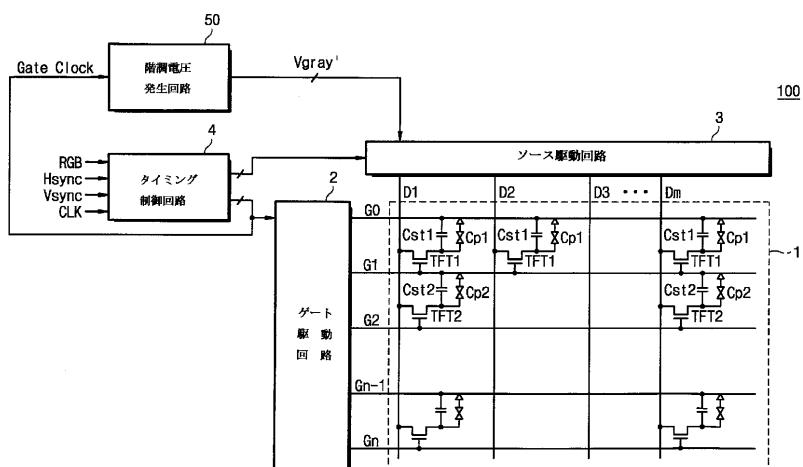

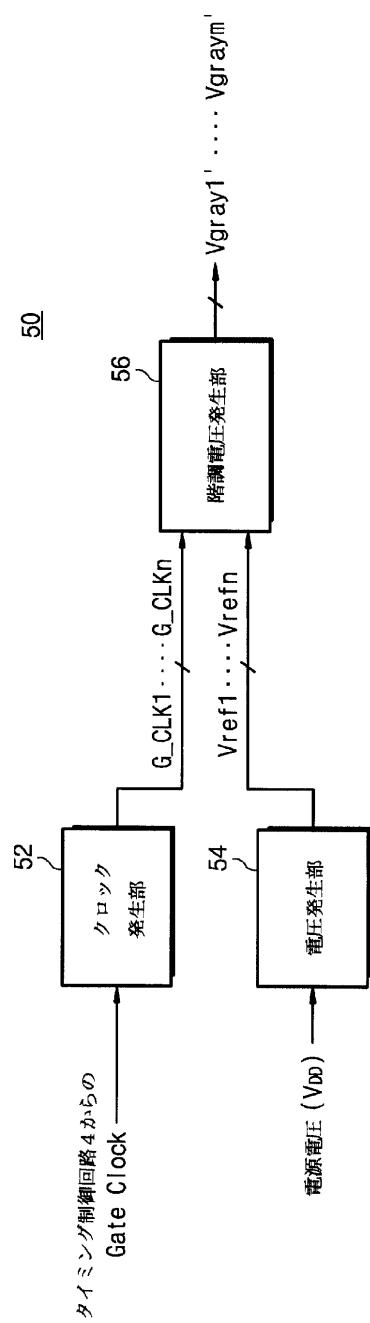

【0023】図2は本発明による液晶ディスプレイ装置100の構成を概略的に示す構成図である。図2を参照すると、液晶ディスプレイ装置100は液晶パネル1、液晶パネル1に連結された多数のゲート駆動回路2、多数のソース駆動回路3、タイミング制御回路4、そして、階調電圧発生回路50を含む。このような構成は、図1に示された一般的な液晶ディスプレイ装置10の構成と比較すると、タイミング制御回路4から発生されるゲートクロック信号(Gate Clock)に応じて階調電圧(Vgray')を発生させる階調電圧発生回路50を除くと、図1に示された液晶ディスプレイ装置10と同一な構成を有する。従って、同一な構成を有し、同一な動作を遂行する機能ブロックに対しては、図1で使用された参照番号を使用し、これに関する詳細な説明は省略する。

【0024】周知のように、色信号(R, G, B)に従って多数の階調電圧のうち1つを選択し、これに応じて液晶駆動電圧(Vdrive)を液晶パネルに印加するソース駆動回路3の機能は、液晶パネル1に備えられた液晶キャパシタ(Cp)の充填速度と密接な関係である。ところで、液晶キャパシタ(Cp)を充填させる液晶駆動電圧(Vdrive)は、階調電圧発生回路50から発生される階調電圧(Vgray')に依存する。従って、本発明による液晶ディスプレイ装置100は、ゲート駆動回路2、ソース駆動回路3及びタイミング制御回路4のように高価で、複雑な回路的な構成を有する回路に対する設計変更なしに、液晶パネル1に備えられた液晶キャパシタ(Cp)の充填速度が速まるようにソース駆動回路3から発生される液晶駆動電圧(Vdrive)を変化させる。ゲート駆動回路2、ソース駆動回路3及びタイミング制御回路4を設計変更する場合に比べて、より低価の階調電圧発生回路50の開発によって、液晶ディスプレイ装置100の駆動速度を向上させる。

【0025】図3は、本発明による階調電圧発生回路50の構成を概略的に示す構成図である。図3を参照すると、本発明による階調電圧発生回路50は、クロック発生部52、電圧発生部54、そして、階調電圧発生部56で構成される。クロック発生部52は、タイミング制御回路4から発生されるゲートクロック信号(Gate Clock)に応じて互いに重ならないn個のクロック

ク信号( $G_{CLK1}, \dots, G_{CLKn}$ )を発生させ。電圧発生部54は、電源電圧( $V_{DD}$ )に応じて電圧レベルが各々異なるn個の基準電圧( $V_{ref1}, \dots, V_{refn}$ )を発生させる。ここで、電源電圧( $V_{DD}$ )はアナログ電圧であり、ソース駆動回路3の電源電圧として使用される。

【0026】クロック発生部52及び電圧発生部54から発生されたn個のクロック信号( $G_{CLK1}, \dots, G_{CLKn}$ )とn個の基準電圧( $V_{ref1}, \dots, V_{refn}$ )が階調電圧発生部56に入力されると、階調電圧発生部56はクロック信号( $G_{CLK1}, \dots, G_{CLKn}$ )に同期されて基準電圧( $V_{ref1}, \dots, V_{refn}$ )のレベルに従って各々異なる電位を有するm個の階調電圧( $V_{gray1'}, \dots, V_{graym'}$ )を発生させる。階調電圧( $V_{gray1'}, \dots, V_{graym'}$ )はソース駆動回路3が1つのゲートクロック(Gate Clock)周期(clock period)の間、ゲートクロック信号のハイ区間とロー区間毎に各々異なる値を有する液晶駆動電圧( $V_{drive'}$ )を発生させるようにする。このような特性を有するソース駆動回路3の液晶駆動電圧( $V_{drive'}$ )によって液晶パネル1に備えられた液晶キャパシタ(Cp)の充填速度が速まり、液晶ディスプレイ装置100の駆動速度が向上される。

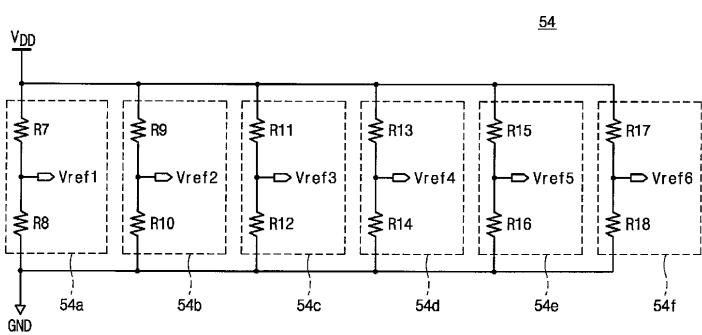

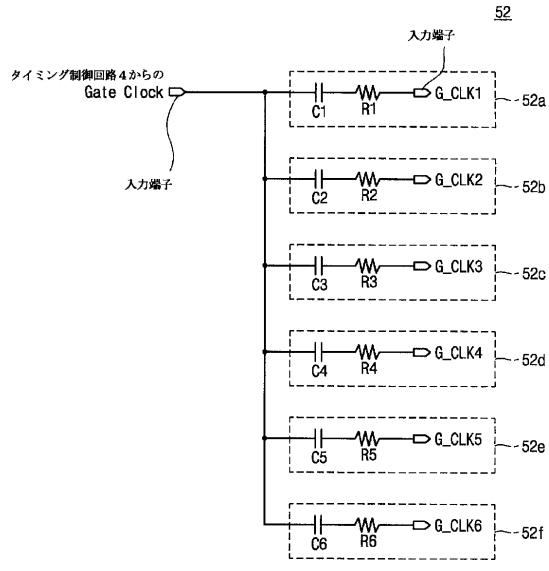

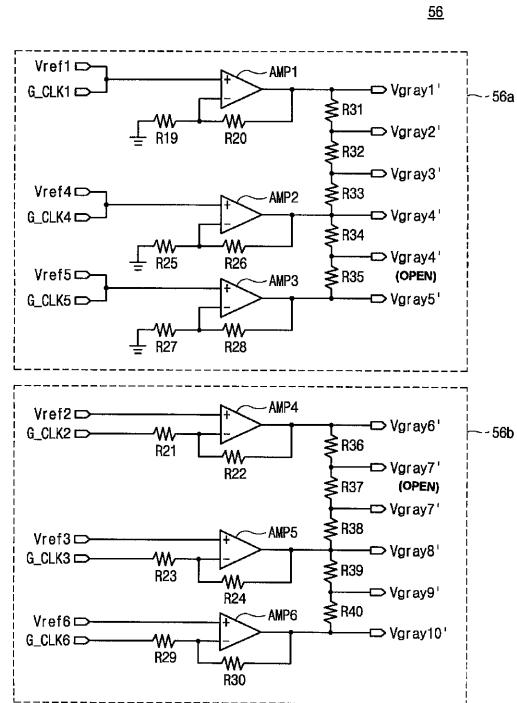

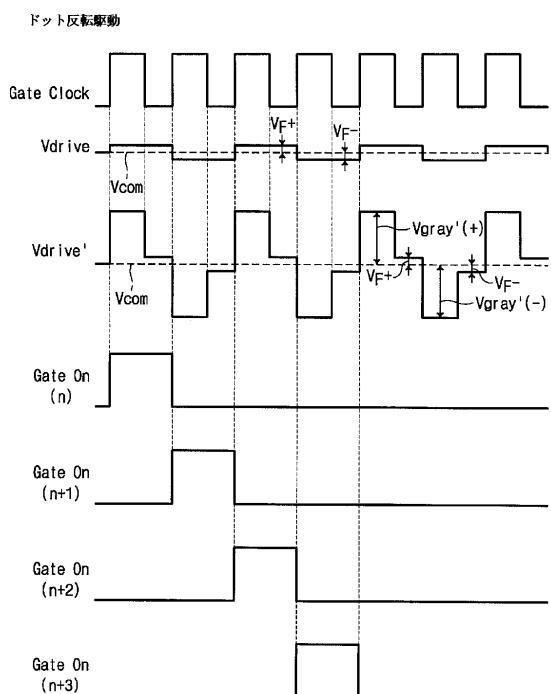

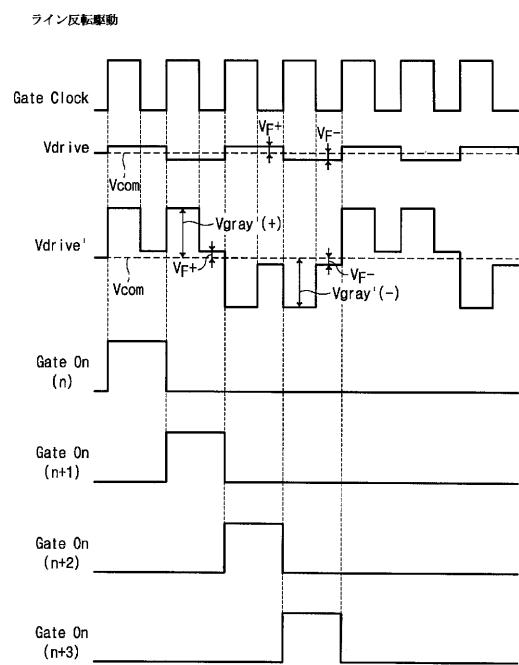

【0027】図4は、図3に示されたクロック発生部52の回路図であり、図5は、図3に示された電圧発生部54の回路図である。そして、図6は、図3に示された階調電圧発生部56の回路図である。図4及び図5に示されたクロック発生部52及び電圧発生部54は各々6つのクロック信号( $G_{CLK1}, \dots, G_{CLK6}$ )と6つの基準電圧( $V_{ref1}, \dots, V_{ref6}$ )を発生させる。図6に示された階調電圧発生部56は6つのクロック信号( $G_{CLK1}, \dots, G_{CLK6}$ )と6つの基準電圧( $V_{ref1}, \dots, V_{ref6}$ )に応じて10つの階調電圧( $V_{gray1'}, \dots, V_{gray10'}$ )を発生させる。ここで、回路によって発生される信号の個数は回路の構成によって様々であり、図に示された回路は回路構成の一例にすぎない。

【0028】図4を参照すると、クロック発生部52はタイミング制御回路4から発生されるゲートクロック信号を取り込むための入力端子と、入力端子に並列に連結された第1乃至第6クロック発生ユニット(52a-52f)、そして、クロック発生ユニット(52a-52f)各々に連結された第1乃至第6出力端子で構成される。各々のクロック発生ユニット(52a-52f)は入力端子と出力端子の間に直列に連結されたキャパシタ(C1, ..., 又はC6)と抵抗(R1, ..., 又はR6)を備えて、タイミング制御回路4から発生されるゲートクロック信号と同一な周期を有する第1乃至第6クロック信号( $G_{CLK1}, \dots, G_{CLK6}$ )を出力端子を50

通じて互いに重ならないように出力する。

【0029】図5を参照すると、電圧発生部54は電源電圧( $V_{DD}$ )を所定比率で分けて各々異なる電圧レベルの6つの基準電圧( $V_{ref1}, \dots, V_{ref6}$ )を発生させるための第1乃至第6電圧発生ユニット(54a-54f)で構成される。第1乃至第6電圧発生ユニット(54a-54f)は電源電圧( $V_{DD}$ )と接地電圧(GND)の間に並列に連結されている。電圧発生ユニット(54a-54f)は各々、電源電圧( $V_{DD}$ )と接地電圧(GND)の間に直列に連結された2つの抵抗と、これらの抵抗の間の接点に連結された出力端子を含む。

【0030】図6を参照すると、階調電圧発生部56は液晶の正極性駆動に使用するための第1乃至第5階調電圧( $V_{gray1'}, \dots, V_{gray5'}$ )を発生させる第1階調電圧発生ユニット(56a)と液晶の負極性駆動に使用するための第6乃至第10階調電圧( $V_{gray6'}, \dots, V_{gray10'}$ )を発生させる第2階調電圧発生ユニット(56b)で構成される。

【0031】第1階調電圧発生ユニット(56a)はクロック発生部52から発生されるクロック信号( $G_{CLK1}, G_{CLK4}, G_{CLK5}$ )と電圧発生部54から発生される基準電圧( $V_{ref1}, V_{ref4}, V_{ref5}$ )を取り込むための第1乃至第6入力端子と、入力端子を通じて入力されるクロック信号( $G_{CLK1}, G_{CLK4}, G_{CLK5}$ )と基準電圧( $V_{ref1}, V_{ref4}, V_{ref5}$ )を加算した後、これを所定比率で増幅して階調電圧( $V_{gray1'}, V_{gray4'}, V_{gray5'}$ )を発生させるための第1乃至第3增幅回路(AMP1-AMP3)と、増幅回路(AMP1-AMP3)から発生される階調電圧( $V_{gray1'}, V_{gray4'}, V_{gray5'}$ )を出力するための出力端子とを含む。ここで、第1增幅回路(AMP1)は、第1クロック信号( $G_{CLK1}$ )と第1基準電圧( $V_{ref1}$ )を加算した後、これを所定比率で増幅して第1階調電圧( $V_{gray1'}$ )を発生させ、第2增幅回路(AMP2)は、第4クロック信号( $G_{CLK4}$ )と第4基準電圧( $V_{ref4}$ )を加算した後、これを所定比率で増幅して第4階調電圧( $V_{gray4'}$ )を発生させる。そして、第3增幅回路(AMP3)は、第5クロック信号( $G_{CLK5}$ )と第5基準電圧( $V_{ref5}$ )を加算した後、これを所定比率で増幅して第5階調電圧( $V_{gray5'}$ )を発生させる。ここで、第1階調電圧発生ユニット(56a)に備えられた第1乃至第3增幅回路(AMP1-AMP3)から発生される階調電圧( $V_{gray1'}, V_{gray4'}, V_{gray5'}$ )を数学式で表すと、次のとおりである。

$$(数1) V_{gray1'} = (R19 + R20) / R19 [V_{ref1} + R1 / (R1 + R19) V_{G_{CLK}}]$$

(数2)  $V_{gray4'} = (R25 + R26) / R25$

$[V_{ref1} + R4 / (R4 + R25) V_{G_{CLK}}]$

(数3)  $V_{gray5'} = (R27 + R28) / R27$

$[V_{ref5} + R5 / (R5 + R27) V_{G_{CLK}}]$

ここで、 $V_{G_{CLK}}$ はゲートクロック信号の交流成分を示す。

【0032】第1階調電圧発生ユニット(56a)は、このような階調電圧( $V_{gray1'}$ ,  $V_{gray4'}$ ,  $V_{gray5'}$ )の他にも第2及び第3階調電圧( $V_{gray2'}$ ,  $V_{gray3'}$ )をさらに発生させる。この階調電圧( $V_{gray2'}$ ,  $V_{gray3'}$ )は、第1及び第2增幅回路(AMP1, AMP2)の出力端の間に直列に連結された抵抗(R31, R32, R33)によって、 $V_{gray1'}$ と $V_{gray4'}$ とが分圧された電圧レベルを有する。

【0033】第2階調電圧発生ユニット(56b)は、クロック発生部52から発生されるクロック信号( $G_{CLK2}$ ,  $G_{CLK3}$ ,  $G_{CLK6}$ )と電圧発生部54から発生される基準電圧( $V_{ref2}$ ,  $V_{ref3}$ ,  $V_{ref6}$ )を取り込むための第7乃至第12入力端子と、入力端子を通じて入力される基準電圧( $V_{ref2}$ ,  $V_{ref43}$ ,  $V_{ref6}$ )からクロック信号( $G_{CLK2}$ ,  $G_{CLK3}$ ,  $G_{CLK6}$ )を減算して、階調電圧( $V_{gray6'}$ ,  $V_{gray7'}$ ,  $V_{gray10'}$ )を発生させるための第4乃至第6增幅回路(AMP4 - AMP6)と、增幅回路(AMP4 - AMP6)から発生される階調電圧( $V_{gray6'}$ ,  $V_{gray8'}$ ,  $V_{gray10'}$ )を出力するための出力端子とを含む。ここで、第4增幅回路(AMP4)は、第2基準電圧( $V_{ref2}$ )から第2クロック信号( $G_{CLK2}$ )を減算した後、これを所定比率で増幅して第6階調電圧( $V_{gray6'}$ )を発生させ、第5增幅回路(AMP5)は、第3基準電圧( $V_{ref3}$ )から第3クロック信号( $G_{CLK3}$ )を減算した後、これを所定比率で増幅して第8階調電圧( $V_{gray8'}$ )を発生させる。そして、第6增幅回路(AMP6)は、第6基準電圧( $V_{ref6}$ )から第6クロック信号( $G_{CLK6}$ )を減算した後、これを所定比率で増幅して第10階調電圧( $V_{gray10'}$ )を発生させる。ここで、第2階調電圧発生ユニット(56b)に備えられた第4乃至第6增幅回路(AMP4 - AMP6)から発生される階調電圧( $V_{gray6'}$ ,  $V_{gray8'}$ ,  $V_{gray10'}$ )を数学式で表すと、次のとおりである。

(数4)  $V_{gray6'} = (R2 + R21 + R22) / R22 \times [V_{ref2} - R22 / (R2 + R21) V_{G_{CLK}}]$

(数5)  $V_{gray8'} = (R3 + R23 + R24) / R24 \times [V_{ref3} - R24 / (R3 + R23) V_{G_{CLK}}]$

(数6)  $V_{gray10'} = (R6 + R29 + R30) / R30 \times [V_{ref6} - R30 / (R6 + R29) V_{G_{CLK}}]$

ここで、 $V_{G_{CLK}}$ はゲートクロック信号の交流成分を示す。

【0034】第2階調電圧発生ユニット(56b)は、このような階調電圧( $V_{gray6'}$ ,  $V_{gray8'}$ ,  $V_{gray10'}$ )の他にも第7及び第9階調電圧( $V_{gray7'}$ ,  $V_{gray9'}$ )をさらに発生させる。第7階調電圧 $V_{gray7'}$ は、第4及び第5增幅回路(AMP4, AMP5)の出力端の間に直列に連結された抵抗(R36, R37, R38)によって、 $V_{gray6'}$ と $V_{gray8'}$ とが分圧された電圧レベルを有する。第9階調電圧 $V_{gray9'}$ は、第5及び第6增幅回路(AMP5, AMP6)の出力端の間に直列に連結された抵抗(R39, R40)によって、 $V_{gray8'}$ と $V_{gray10'}$ とが分圧された電圧レベルを有する。

【0035】図6で、第4階調電圧( $V_{gray4'}$ )と第7階調電圧( $V_{gray7'}$ )は1つ又は2つの出力端子を通じて出力できる。例えば、4番目出力端子を通じて出力される第4階調電圧( $V_{gray4'}$ )は第2增幅回路(AMP2)の出力をそのままに使用することを示し、5番目出力端子を通じて出力される第4階調電圧( $V_{gray4'}$ )は第2增幅回路(AMP2)の出力を抵抗を通じて所定比率で分圧して出力することを示す。このように、階調電圧発生部56から発生される階調電圧( $V_{ref1'}$ , ...,  $V_{ref10'}$ )は、回路の構成によって増幅回路の出力をそのままに使用することもできるし、所定比率で分圧して使用することもできる。

【0036】図6では、第4及び第7階調電圧( $V_{gray4'}$ ,  $V_{gray7'}$ )に関して示しているが、第4及び第7階調電圧( $V_{gray4'}$ ,  $V_{gray7'}$ )を除いた他の階調電圧にも同様に適用され得る。

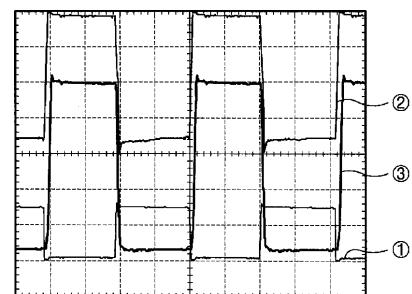

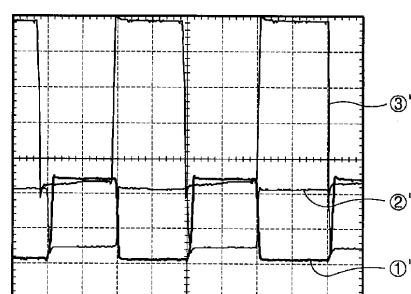

【0037】図7A及び図7Bは、本発明による階調電圧発生回路から発生される階調電圧波形の一例を示すための波形図である。図7Aは正極性の階調電圧を示し、図7Bは負極性の階調電圧を示す。

【0038】図7で、 $V_{ref1'}$ 及び $V_{ref2'}$ で示された波形は、タイミング制御回路4から発生されたゲートクロック信号を、 $V_{ref3'}$ 及び $V_{ref4'}$ で示された波形は48階調の階調電圧を、 $V_{ref5'}$ 及び $V_{ref6'}$ で示された波形は64階調の階調電圧を各々示す。

【0039】図8及び図9は、図7A及び図7Bに示された階調電圧( $V_{ref1'}$ , ...,  $V_{ref10'}$ )が印加されて、出力されるソース駆動回路3の出力波形の一例を示すための波形図である。図8はドット反転(dot inversion)駆動の時の波形であり、図9は2-ライン反転(2-line inversion)駆動の時の波形である。

n ) 駆動の時の波形として、電源が印加されない時、白色を表す白色モード (N o r m a l l y W h i t e M o d e ) 時の波形を示す。

【0040】図8及び図9には、タイミング制御回路4から出力されるゲートクロック信号と、従来技術による液晶ディスプレイ装置のソース駆動回路の出力信号 (V d r i v e ) と、本発明による液晶ディスプレイ装置100のソース駆動回路3の出力信号 (V d r i v e ' ) と、n乃至n+3番目ラインを駆動させるためにタイミング制御回路4から出力されるゲートオン信号 (G a t e O n (n) - G a t e O n (n+3) ) とが示されている。

【0041】図8及び図9を参照すると、従来技術による液晶ディスプレイ装置のソース駆動回路はゲートクロック信号の周期毎にV<sub>F+</sub>及びV<sub>F-</sub>の電圧レベルを有する液晶駆動電圧 (V d r i v e ) を発生させる。液晶駆動電圧は駆動電圧 (V c o m ) を基準にして、プラス方向とマイナス方向に対称をなす。

【0042】しかし、本発明による液晶ディスプレイ装置100のソース駆動回路3はゲートクロック信号の周期毎に階調電圧に従って変わる液晶駆動電圧 (V d r i v e ' = V g r a y (t) ) を発生させる。この液晶駆動電圧 (V d r i v e ' ) はゲートクロック信号の周期におけるハイレベル区間とローレベル区間毎に、各々異なるレベルの液晶駆動電圧 (V d r i v e ' ) を発生させる。即ち、液晶駆動電圧 (V d r i v e ' = V g r a y (t) ) は、液晶パネル1に備えられた液晶キャパシタ (C p ) を高速で充填させるのに十分なプラス高電圧及びマイナス高電圧を発生させる。しかし、持続的に高電圧を発生させないで、所定区間だけで高電圧を発生させて、高電圧発生に従う電力消耗を防止する。

【0043】図8を参照すると、例えば、ドット反転駆動の時、n番目ラインを駆動させるためのゲートオン信号 (G a t e O n (n) ) が印加される場合の正極性駆動をみると、ソース駆動回路3はゲートクロック信号がハイレベルの時、既存の液晶駆動電圧 (V d r i v e ) に比べて高電圧の第1電圧レベルの液晶駆動電圧 (V d r i v e ' ) を発生させ、ゲートクロック信号がローレベルの時、既存の液晶駆動電圧 (V d r i v e ) と同一なV<sub>F+</sub>の電圧レベルの第2電圧レベルの液晶駆動電圧 (V d r i v e ' ) を発生させる。ここで、液晶駆動電圧 (V d r i v e ' ) が有する第1及び第2電圧レベルは両方とも共通電圧 (V c o m ) より高い値を有し、第1電圧レベルは第2電圧レベルに比べてより高い値を有する。

【0044】n+1番目ラインを駆動させるためのゲートオン信号 (G a t e O n (n) ) が印加される場合の負極性駆動をみると、ソース駆動回路3はゲートクロック信号がハイレベルの時、既存の液晶駆動電圧 (V d r i v e ) に比べて低電圧 (より大きな負の電圧) の第

3電圧レベルの液晶駆動電圧 (V d r i v e ' ) を発生させ、ゲートクロック信号がローレベルの時、既存の液晶駆動電圧 (V d r i v e ) と同一なV<sub>F-</sub>の電圧レベルの第4電圧レベルの液晶駆動電圧 (V d r i v e ' ) を発生させる。ここで、液晶駆動電圧 (V d r i v e ' ) が有する第3及び第4電圧レベルは両方とも共通電圧 (V c o m ) より低い値を有し、第3電圧レベルは第4電圧レベルに比べてより低い値を有する。

【0045】図9を参照すると、例えば、2-ライン反転 (2-line inversion) 駆動の時、n及びn+1番目ラインを駆動させるためのゲートオン信号 (G a t e O n (n) ) が印加される場合の正極性駆動をみると、ソース駆動回路3はゲートクロック信号がハイレベルの時、既存の液晶駆動電圧 (V d r i v e ) に比べて高電圧の液晶駆動電圧 (V d r i v e ' ) を発生させ、ゲートクロック信号がローレベルの時、既存の液晶駆動電圧 (V d r i v e ) と同一なV<sub>F+</sub>の電圧レベルの液晶駆動電圧 (V d r i v e ' ) を発生させる。そして、n+2及びn+3番目ラインを駆動させるゲートオン信号 (G a t e O n (n) ) が印加される場合の負極性駆動をみると、ソース駆動回路3はゲートクロック信号がハイレベルの時、既存の液晶駆動電圧 (V d r i v e ) に比べて低電圧の液晶駆動電圧 (V d r i v e ' ) を発生させ、ゲートクロック信号がローレベルの時、既存の液晶駆動電圧 (V d r i v e ) と同一なV<sub>F-</sub>の電圧レベルの液晶駆動電圧 (V d r i v e ' ) を発生させる。図7及び図8に示されたソース駆動回路3の出力波形はライン駆動方法の種類に従って変わり、様々な種類のライン駆動方法 (例えば、n-ライン反転 (n-line inversion) 駆動方法) にも適用できる。

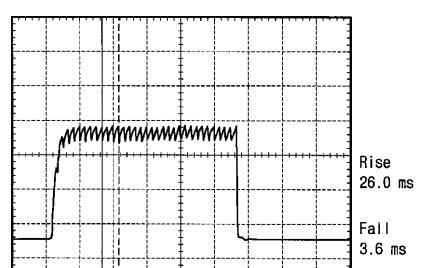

【0046】図10A乃至図13Bは、図7A及び図7Bに示された階調電圧によるソース駆動回路3の0-32, 0-48, 0-64, そして32-64階調の応答速度の測定結果を示すための図である。

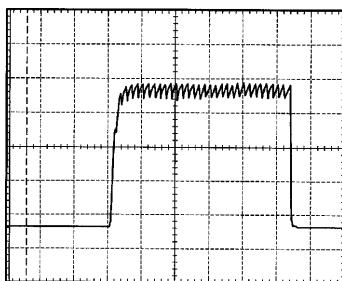

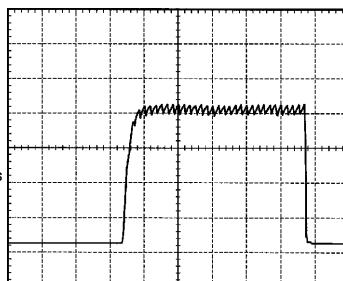

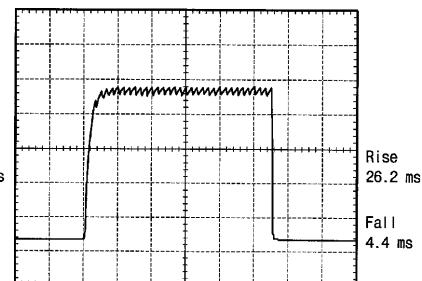

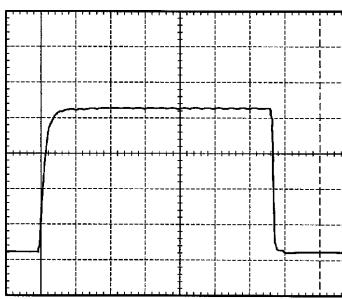

【0047】詳細には、図10Aは従来技術によるソース駆動回路の0-32階調の応答速度を、図10Bは本発明によるソース駆動回路の0-32階調の応答速度を示している。また、図11Aは従来技術によるソース駆動回路の0-48階調の応答速度を、図11Bは本発明によるソース駆動回路の0-48階調の応答速度を示している。また、図12Aは従来技術によるソース駆動回路の0-64階調の応答速度を、図12Bは本発明によるソース駆動回路の0-64階調の応答速度を示している。また、図13Aは従来技術によるソース駆動回路の32-64階調の応答速度を、図13Bは本発明によるソース駆動回路の32-64階調の応答速度を示している。

【0048】測定結果は、各々正極性と負極性を有する5つのソース駆動回路に対して図7A及び図7Bに示さ

れた48階調の階調電圧( )及び64階調の階調電圧( )を変更して印加して測定したものを示す。ここで、各波形のライジングタイム(rising time)は輝度基準である。この輝度基準のライジングタイムは、液晶の動きを基準にする時、液晶のフォーリングタイム(falling time)に該当する。

【0049】図10A及び図10Bを参照すると、0-32階調に対するソース駆動回路の応答速度において、従来技術によるライジングタイム(即ち、液晶のフォーリングタイム)は26.0msであり、フォーリングタイム(即ち、液晶のライジングタイム)は3.6msである。しかし、本発明によるライジングタイム(即ち、液晶のフォーリングタイム)は24.2msであり、フォーリングタイム(即ち、液晶のライジングタイム)は3.6msである。このような場合、輝度基準のフォーリングタイムには変化がないが、輝度基準のライジングタイムは26msから24.2msに1.8ms減少される。

【0050】図11A及び図11Bを参照すると、0-48階調に対するソース駆動回路の応答速度において、従来技術によるライジングタイム(即ち、液晶のフォーリングタイム)は36.8msであり、フォーリングタイム(即ち、液晶のライジングタイム)は3.6msである。しかし、本発明によるライジングタイム(即ち、液晶のフォーリングタイム)は26.2msであり、フォーリングタイム(即ち、液晶のライジングタイム)は4.4msである。このような場合、輝度基準のフォーリングタイムは0.8ms増加されるが、輝度基準のライジングタイムは36.8msから26.2msに10.6ms減少される。

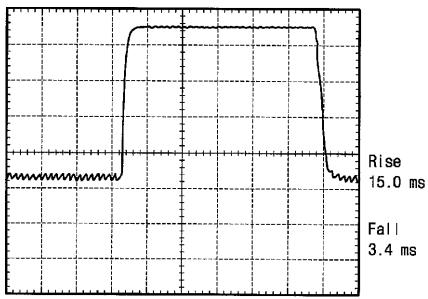

【0051】図12A及び図12Bを参照すると、0-64階調に対するソース駆動回路の応答速度において、\*

\*従来技術によるライジングタイム(即ち、液晶のフォーリングタイム)は22.6msであり、フォーリングタイム(即ち、液晶のライジングタイム)は4.7msである。しかし、本発明によるライジングタイム(即ち、液晶のフォーリングタイム)は15.1msであり、フォーリングタイム(即ち、液晶のライジングタイム)は4.6msである。このような場合、輝度基準のフォーリングタイムは0.1ms減少されるが、輝度基準のライジングタイムは22.6msから15.1msに7.5ms減少される。

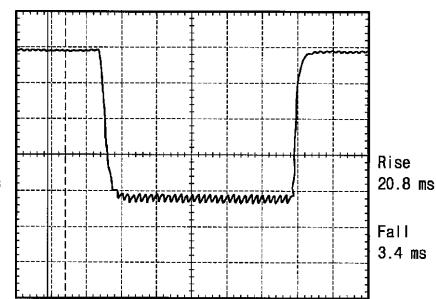

【0052】図13A及び図13Bを参照すると、32-64階調に対するソース駆動回路の応答速度において、従来技術によるライジングタイム(即ち、液晶のフォーリングタイム)は20.8msであり、フォーリングタイム(即ち、液晶のライジングタイム)は3.4msである。しかし、本発明によるライジングタイム(即ち、液晶のフォーリングタイム)は15.0msであり、フォーリングタイム(即ち、液晶のライジングタイム)は3.4msである。このような場合、輝度基準のフォーリングタイムには変化がないが、輝度基準のライジングタイムは20.8msから15.0msに5.8ms減少される。

【0053】図10A乃至図13Bを参照すると、本発明によるソース駆動回路3の応答速度は、0-32階調の場合、26msから24.2msに1.8ms減少され、0-48階調の場合、36.8msから26.2msに10.6ms減少され、0-64階調の場合、22.6msから15.1msに7.5ms減少され、32-64階調の場合、20.8msから15.0msに5.8ms減少される。これを表で示すと次のとおりである。

#### 【0054】

【表1】

| 液晶のフォーリングタイム |               |               |

|--------------|---------------|---------------|

|              | 従来技術          | 本発明           |

| 0-32階調       | 26.0 ms(1.00) | 24.2 ms(0.93) |

| 0-48階調       | 36.8 ms(1.00) | 26.2 ms(0.71) |

| 0-64階調       | 22.6 ms(1.00) | 15.1 ms(0.67) |

| 32-64階調      | 20.8 ms(1.00) | 15.0 ms(0.72) |

前記表1で、示している液晶のフォーリングタイムは同一条件で遂行された模擬実験の結果であり、( )内に表示された数は従来技術による液晶のフォーリングタイムを基準にして、定規化(normalization)した結果を各々示す。

【0055】表1を参照すると、液晶のフォーリングタイムは0-32階調の場合、26.0msから24.2msに1.8ms減少され、0-48階調の場合、36.8msから26.2msに10.6ms減少され、0-64階調の場合、22.6msから15.1msに7.5ms減少され、32-64階調の場合、20.8ms

msから15.0msに5.8ms減少された。これを定規化した結果で比較すると、液晶のフォーリングタイムは0-32階調の場合、7%改善され、0-48階調の場合、29%改善され、0-64階調の場合、33%改善され、32-64階調の場合、27%改善された。表1から分かるように、液晶のフォーリングタイムの速度、即ち、液晶ディスプレイ装置の駆動速度は、表示しようとする階調値が多くなるほど、改善される。

【0056】前述のように、本発明による階調電圧発生回路50は、ソース駆動回路3が図7及び図8に示されたような電圧レベルの液晶駆動電圧(Vdrive')

を発生させるように階調電圧( $V_{gray'}$ )を変形させて出力する。その結果、ソース駆動回路3はゲートクロック信号の周期毎に階調電圧に従って変わる液晶駆動電圧( $V_{drive'} = V_{gray'}(t)$ )を発生させる。そして、液晶パネル1に備えられた液晶キャパシタ(Cp)は、ソース駆動回路3から印加される液晶駆動電圧( $V_{drive'}$ )によって高速で充填される。その結果、液晶のフォーリングタイムは短縮され、液晶ディスプレイ装置の駆動速度が向上される。

【0057】以上、本発明による回路の構成及び動作を説明したが、これは一例に過ぎない。本発明の思想の範囲内で様々な変化及び変更が可能である。

【まとめ】本実施形態による階調電圧発生回路50は、ゲートクロック信号が高電位の区間には大きい階調電圧を出力し、ソース駆動回路3から大きい液晶駆動電圧 $V_{drive}$ を出力させ、ゲートクロック信号が低電位の区間にはより小さい階調電圧を出力し、ソース駆動回路3から小さい液晶駆動電圧 $V_{drive}$ を出力させることにより、液晶キャパシタCpを短時間に充填させることができるようになる。

【0058】ゲートクロック信号が低電位の区間では、液晶駆動電圧 $V_{drive}$ を従来と同程度の小さい電位にするため、液晶ディスプレイ装置を低消耗電力で駆動することができる。

【0059】また、ゲートクロック信号の周期に合わせて、液晶駆動電圧 $V_{drive}$ の大きさを変化させることのみで良いので、液晶ディスプレイ装置の高価格化を防止できる。

#### 【0060】

【発明の効果】本発明による階調電圧発生回路はソース駆動回路が液晶キャパシタを短時間に充填させ得るよう、所定区間の間、高電位の液晶駆動電圧を発生させ、前記区間の以降には一般的な液晶駆動電圧を発生させるように階調駆動電圧を変形させて出力する。これにより、低電力消耗で液晶ディスプレイ装置の駆動速度を向上させ得る。

#### 【図面の簡単な説明】

【図1】一般的な液晶ディスプレイ装置の構成を概略的に示す構成図。

【図2】本発明の一実施形態による液晶ディスプレイ装置の構成を概略的に示す構成図。

【図3】本発明の一実施形態による階調電圧発生回路の構成を概略的に示す構成図。

【図4】図3に示されたクロック発生部のより詳細な構成を示す回路図。

【図5】図3に示された電圧発生部のより詳細な構成を示す回路図。

【図6】図3に示された階調電圧発生部のより詳細な構成を示す回路図。

【図7A】本発明の一実施形態による階調電圧発生部から発生される正極性の階調電圧波形の一例を示す図。

【図7B】本発明の一実施形態による階調電圧発生部から発生される負極性の階調電圧波形の一例を示す図。

【図8】図7に示された階調電圧が印加されて出力されるソース駆動回路の出力波形の一例を示す図(ドット反転駆動時)。

【図9】図7に示された階調電圧が印加されて出力されるソース駆動回路の出力波形の一例を示す図(ライン反転駆動時)。

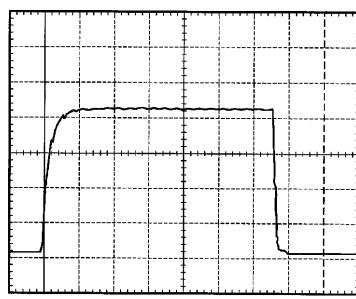

【図10A】図7に示された階調電圧によるソース駆動回路の0-32階調の応答速度の測定結果を示す図(従来)。

【図10B】図7に示された階調電圧によるソース駆動回路の0-32階調の応答速度の測定結果を示す図(本実施形態)。

【図11A】図7に示された階調電圧によるソース駆動回路の0-48階調の応答速度の測定結果を示す図(従来)。

【図11B】図7に示された階調電圧によるソース駆動回路の0-48階調の応答速度の測定結果を示す図(本実施形態)。

【図12A】図7に示された階調電圧によるソース駆動回路の0-64階調の応答速度の測定結果を示す図(従来)。

【図12B】図7に示された階調電圧によるソース駆動回路の0-64階調の応答速度の測定結果を示す図(本実施形態)。

【図13A】図7に示された階調電圧によるソース駆動回路の32-64階調の応答速度の測定結果を示す図(従来)。

【図13B】図7に示された階調電圧によるソース駆動回路の32-64階調の応答速度の測定結果を示す図(本実施形態)。

#### 【符号の説明】

- 1 液晶パネル

- 2 ゲート駆動回路

- 3 ソース駆動回路

- 4 タイミング制御回路

- 5, 50 階調電圧発生回路

- 53 クロック発生部

- 54 電圧発生部

- 56 階調電圧発生部

- 100 液晶ディスプレイ装置

【図1】

【図7 A】

【図2】

【図7 B】

【図5】

【図10 A】

【図3】

【図4】

【図6】

【図8】

【図9】

【図10B】

【図11A】

【図11B】

【図12A】

【図12B】

【図13A】

【図13B】

フロントページの続き

F ターム(参考) 2H093 NA16 NC34 ND39 ND60

5C006 AC21 BB16 BC06 BC16 BF43

FA04 FA14 FA47 FA56

5C080 AA10 BB05 DD08 DD26 EE29

JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                   |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | <无法获取翻译>                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP2002221949A5</a>                                                                                                                                                                                                                    | 公开(公告)日 | 2008-04-17 |

| 申请号            | JP2001146858                                                                                                                                                                                                                                      | 申请日     | 2001-05-16 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                          |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                          |         |            |

| [标]发明人         | YEON YEUN MO<br>LEE KUN BIN<br>延允模<br>李建斌                                                                                                                                                                                                         |         |            |

| 发明人            | 延允模<br>李建斌                                                                                                                                                                                                                                        |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                       |         |            |

| CPC分类号         | G09G2310/0251 G09G3/3648 G09G3/3696                                                                                                                                                                                                               |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.621.F G09G3/20.623.C G09G3/20.641.C                                                                                                                                                                               |         |            |

| F-TERM分类号      | 5C006/BC06 2H093/NC34 2H093/ND39 5C080/EE29 5C080/DD26 5C006/FA04 5C080/JJ03 5C080/AA10 5C006/FA14 2H093/ND60 5C006/BB16 5C080/JJ02 5C080/BB05 5C006/BF43 5C006/FA56 5C006/FA47 5C080/JJ04 5C080/DD08 2H093/NA16 5C006/AC21 5C006/BC16 2H193/ZA04 |         |            |

| 优先权            | 1020000079698 2000-12-21 KR                                                                                                                                                                                                                       |         |            |

| 其他公开文献         | JP4963758B2<br>JP2002221949A                                                                                                                                                                                                                      |         |            |

### 摘要(译)

解决的问题：提供一种灰度电压发生电路，其能够提高低成本低功耗的液晶显示装置的驱动速度。根据从灰度级电压产生电路5输出的灰度级电压，源极驱动电路3在栅极时钟信号的高电平部分中具有高于常规液晶驱动电压的电压，这取决于驱动极性。当产生该电平的液晶驱动电压并且施加低电平栅极时钟信号时，产生与现有的液晶驱动电压相同电平的液晶驱动电压。