(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4743837号

(P4743837)

(45) 発行日 平成23年8月10日(2011.8.10)

(24) 登録日 平成23年5月20日(2011.5.20)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G09G 3/36

G02F 1/133 (2006.01)

G02F 1/133 575

G09G 3/20 (2006.01)

G09G 3/20 612U

G09G 3/20 621F

G09G 3/20 631R

請求項の数 16 (全 19 頁) 最終頁に続く

(21) 出願番号

特願2005-6288 (P2005-6288)

(22) 出願日

平成17年1月13日(2005.1.13)

(65) 公開番号

特開2006-195151 (P2006-195151A)

(43) 公開日

平成18年7月27日(2006.7.27)

審査請求日

平成19年9月14日(2007.9.14)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100103894

弁理士 家入 健

(72) 発明者 降旗 弘史

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

(72) 発明者 能勢 崇

神奈川県川崎市中原区下沼部1753番地

NECエレクトロニクス株式会社内

審査官 武田 悟

最終頁に続く

(54) 【発明の名称】コントローラ・ドライバ及びそれを用いる液晶表示装置並びに液晶駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

受信画像データのビット数を圧縮して第1の圧縮画像データ及び第2の圧縮画像データを生成する圧縮手段と、

少なくとも1フレーム分の前記第2の圧縮画像データを蓄積可能な画像メモリと、

前記第1の圧縮画像データを入力するとともに、前記画像メモリから前記第1の圧縮画像データよりも1フレーム前の第2の圧縮画像データを入力し、これらのデータに基づいて前記受信画像データの階調値を補正した補正画像データを生成するオーバードライブ演算回路と、

前記補正画像データに基づいて液晶パネルを駆動するための駆動電圧を生成するデータ線駆動回路とを備え、

前記圧縮手段は、前記第1の圧縮画像データ及び前記第2の圧縮画像データを生成する際に適用する圧縮処理を時間経過とともに変更するものであり、

前記圧縮手段において前記第1の圧縮画像データを生成する際に適用する圧縮処理は、前記受信画像データより1フレーム前の画像データのビット数を圧縮して前記第2の圧縮画像データを生成する際に適用する圧縮処理と同一であるコントローラ・ドライバ。

## 【請求項 2】

前記圧縮手段は、

前記受信画像データのビット数を圧縮して前記第1の圧縮画像データを生成する第1の圧縮回路と、

10

20

前記受信画像データのビット数を圧縮して前記第2の圧縮画像データを生成する第2の圧縮回路とを備え、

前記第1の圧縮回路及び前記第2の圧縮回路は、それぞれ前記第1の圧縮画像データ及び前記第2の圧縮画像データを生成する際に適用する圧縮処理を時間経過とともに変更するものであり、

前記第1の圧縮回路で行う圧縮処理は、前記受信画像データより1フレーム前の画像データのビット数を圧縮する際に前記第2の圧縮回路で行う圧縮処理と同一である請求項1に記載のコントローラ・ドライバ。

【請求項3】

前記第1の圧縮回路及び前記第2の圧縮回路はディザ法により画像データのビット数を圧縮するものであって、 10

前記受信画像データのビット数を圧縮する際に前記第1の圧縮回路に適用するディザマトリクスは、前記受信画像データより1フレーム前の画像データのビット数を圧縮する際に前記第2の圧縮回路に適用されるディザマトリクスと同一であることを特徴とする請求項2に記載のコントローラ・ドライバ。

【請求項4】

前記第2の圧縮回路に適用するディザマトリクスを、前記第2の圧縮回路において1フレーム前に適用したディザマトリクスとは異なるものに変更する請求項3に記載のコントローラ・ドライバ。

【請求項5】 20

前記第2の圧縮回路に適用するディザマトリクスが $n \times n$ のディザマトリクス( $n$ は2以上の整数)の場合には、前記 $n \times n$ のディザマトリクスのディザ係数を置換して得られる $n^2$ 通りのディザマトリクスの間で、前記第2の圧縮回路に適用するディザマトリクスを1フレーム毎に変更する請求項4に記載のコントローラ・ドライバ。

【請求項6】

受信画像データのビット数を圧縮して第1の圧縮画像データ及び第2の圧縮画像データを生成する圧縮手段と、

少なくとも1フレーム分の前記第2の圧縮画像データを蓄積可能な画像メモリと、

前記第1の圧縮画像データのビット数を伸張した画像データを入力するとともに、前記画像メモリから前記第1の圧縮画像データよりも1フレーム前の第2の圧縮画像データのビット数を伸張した画像データを入力し、これらのデータに基づいて前記受信画像データの階調値を補正した補正画像データを生成するオーバードライブ演算回路と、 30

前記補正画像データに基づいて液晶パネルを駆動するための駆動電圧を生成するデータ線駆動回路とを備え、

前記圧縮手段は、前記第1の圧縮画像データ及び前記第2の圧縮画像データを生成する際に適用する圧縮処理を時間経過とともに変更するものであり、

前記圧縮手段において前記第1の圧縮画像データを生成する際に適用する圧縮処理は、前記受信画像データより1フレーム前の画像データのビット数を圧縮して前記第2の圧縮画像データを生成する際に適用する圧縮処理と同一であるコントローラ・ドライバ。

【請求項7】 40

前記圧縮手段は、

前記受信画像データのビット数を圧縮して前記第1の圧縮画像データを生成する第1の圧縮回路と、

前記受信画像データのビット数を圧縮して前記第2の圧縮画像データを生成する第2の圧縮回路とを備え、

前記第1の圧縮回路及び前記第2の圧縮回路は、それぞれ前記第1の圧縮画像データ及び前記第2の圧縮画像データを生成する際に適用する圧縮処理を時間経過とともに変更するものであり、

前記第1の圧縮回路で行う圧縮処理は、前記受信画像データより1フレーム前の画像データのビット数を圧縮する際に前記第2の圧縮回路で行う圧縮処理と同一である請求項6 50

に記載のコントローラ・ドライバ。

【請求項 8】

前記画像メモリから取得した前記第2の圧縮画像データのビット数を伸張する伸張回路と、

前記第2の圧縮回路が出力する前記第2の圧縮画像データを保持可能であり、前記画像メモリからアクセス可能な第1の一時データ保持回路と、

前記画像メモリが出力する前記第2の圧縮画像データを保持可能であり、前記伸張回路からアクセス可能な第2の一時データ保持回路とを備える請求項7に記載のコントローラ・ドライバ。

【請求項 9】

前記第2の圧縮画像データのビット数を伸張可能な伸張回路と、

前記補正画像データを格納するシフトレジスタ部を備え、

前記シフトレジスタ部は、前記画像メモリから1ライン分の前記第2の圧縮画像データを一括して取得できるよう前記画像メモリと接続され、

さらに前記シフトレジスタ部は、保持しているデータをシフト動作によって前記伸張回路に出力できるよう前記伸張回路と接続されていることを特徴とする請求項7に記載のコントローラ・ドライバ。

【請求項 10】

前記第2の圧縮画像データのビット数を1ライン単位で伸張可能な伸張回路と、

前記補正画像データを格納するシフトレジスタ部を備え、

前記伸張回路は、前記画像メモリから1ライン分の前記第2の圧縮画像データを一括して取得できるよう前記画像メモリと接続され、

前記シフトレジスタ部は、前記伸張回路から前記第2の圧縮画像データのビット数を伸張した1ライン分の画像データを一括して取得できるよう前記伸張回路と接続され、

さらに前記シフトレジスタ部は、保持しているデータをシフト動作によって前記オーバードライブ演算回路に出力できるよう前記オーバードライブ演算回路と接続されていることを特徴とする請求項7に記載のコントローラ・ドライバ。

【請求項 11】

請求項1乃至10のいずれかに記載のコントローラ・ドライバと、

前記コントローラ・ドライバにより駆動される液晶表示部とを備える液晶表示装置。

【請求項 12】

少なくとも2フレームの連続する受信画像データに含まれる各受信画像データのビット数を圧縮することで、第1及び第2の圧縮画像データを各受信画像データについて生成し、

ある受信画像データのビット数を圧縮して得られた前記第1の圧縮画像データ及び前記ある受信画像データよりも1フレーム前の受信画像データのビット数を圧縮して得られた前記第2の圧縮画像データに基づいて、前記ある受信画像データの階調値を補正した補正画像データを生成する液晶駆動方法であって、

前記第1の圧縮画像データ及び前記第2の圧縮画像データを生成する際に適用する圧縮処理を時間経過とともに変更し、

前記ある受信画像データのビット数を圧縮して前記第1の圧縮画像データを生成する際に適用する圧縮処理は、前記ある受信画像データより1フレーム前の受信画像データのビット数を圧縮して前記第2の圧縮画像データを生成する際に適用する圧縮処理と同一であることを特徴とする液晶駆動方法。

【請求項 13】

前記第1の圧縮画像データ及び前記第2の圧縮画像データはディザ法により生成されるものであり、

前記ある受信画像データのビット数を圧縮して前記第1の圧縮画像データ生成する際に適用するディザマトリクスは、前記ある受信画像データより1フレーム前の受信画像データのビット数を圧縮して前記第2の圧縮画像データを生成する際に適用するディザマトリ

10

20

30

40

50

クスと同一であることを特徴とする請求項 1 2 に記載の液晶駆動方法。

【請求項 1 4】

前記ある受信画像データから前記第 2 の圧縮画像データを生成する際に適用するディザマトリクスを、前記ある受信画像データよりも 1 フレーム前の受信画像データから前記第 2 の圧縮画像データを生成する際に適用したディザマトリクスとは異なるものに変更する請求項 1 3 に記載の液晶駆動方法。

【請求項 1 5】

前記第 2 の圧縮画像データを生成する際に適用するディザマトリクスが、 $n \times n$  のディザマトリクス ( $n$  は 2 以上の整数) の場合には、前記第 2 の圧縮画像データを生成する際に適用するディザマトリクスを、ディザ係数を置換して得られる  $n^2$  通りのディザマトリクスの間で、1 フレーム毎に変更する請求項 1 4 に記載の液晶駆動方法。

10

【請求項 1 6】

少なくとも 2 フレームの連続する受信画像データに含まれる各受信画像データのビット数を圧縮することで、第 1 及び第 2 の圧縮画像データを各受信画像データについて生成し

ある受信画像データのビット数を圧縮して得られた前記第 1 の圧縮画像データのビット数を伸張した画像データ、及び前記ある受信画像データよりも 1 フレーム前の受信画像データのビット数を圧縮して得られた前記第 2 の圧縮画像データのビット数を伸張した画像データに基づいて、前記ある受信画像データの階調値を補正した補正画像データを生成する液晶駆動方法であって、

20

前記第 1 の圧縮画像データ及び前記第 2 の圧縮画像データを生成する際に適用する圧縮処理を時間経過とともに変更し、

前記ある受信画像データのビット数を圧縮して前記第 1 の圧縮画像データを生成する際に適用する圧縮処理は、前記ある受信画像データよりも 1 フレーム前の受信画像データのビット数を圧縮して前記第 2 の圧縮画像データを生成する際に適用する圧縮処理と同一であることを特徴とする液晶駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶パネルを駆動するコントローラ・ドライバ、表示装置及び液晶パネルの駆動方法に関する。

30

【背景技術】

【0002】

携帯電話端末や PDA 等の携帯情報機器が液晶パネルを駆動するために備えているコントローラ・ドライバには、1 フレーム分の画像データを蓄積可能な画像メモリと、画像メモリに保存した画像データの表示タイミングを指示する同期信号を生成する簡単な制御回路を備えるよう構成されたものがある。このような構成によれば、静止画表示等の表示画像を切り替える必要がない場合は、CPU 等の外部の処理装置から画像データを受信することなく、画像メモリに保存した画像データを液晶パネルに表示することで静止画の表示が可能であり、消費電力の削減に有効である。

40

【0003】

このようなメモリ内蔵コントローラ・ドライバを備えた従来の液晶表示装置の一例を図 1 4 に示す。従来の液晶表示装置は、液晶パネル 7、液晶パネル 7 のゲート線を駆動するゲート線駆動回路 6、CPU 等の処理装置 5 から画像データ  $D_n$  を受信して携帯電話端末等が備える液晶パネル 7 に表示を行うコントローラ・ドライバ 8 を備えている。コントローラ・ドライバ 8 は、少なくとも 1 フレーム分の画像データを蓄積可能な画像メモリ 8 3、階調化された電圧を発生する階調電圧発生回路 1 7、液晶パネル 7 のデータ線を駆動するデータ線駆動回路 8 9、データ線駆動回路 8 9 及びゲート線駆動回路 6 に表示タイミングを指示するタイミング制御回路 1 8、及び、階調電圧発生回路 1 7 に対する階調電圧の設定指示やタイミング制御回路 1 8 に対する画像表示タイミングの指示等を行う命令制御

50

回路 8 0 を備えている。なお、コントローラ・ドライバ 8 の構成は一例であり、コントローラ・ドライバにゲート線駆動回路を含んで構成される場合もあり、さらに、電源を含んで構成されることもある。

#### 【 0 0 0 4 】

上述したように、コントローラ・ドライバ 8 が少なくとも1フレーム分の画像データを蓄積可能な画像メモリ 8 3 を備えることにより、静止画の表示を行う際には、画像メモリ 8 3 に保存した画像を液晶パネル 7 に表示することで、外部の処理装置 5 から画像データを転送することなく画像表示が可能となる。具体的には、命令制御回路 8 0 が、画像データを画像メモリ 8 3 からデータ線駆動回路 8 9 へ転送するよう指示し、さらに、データ線駆動回路 8 9 及びゲート線駆動回路 6 に表示タイミングを指示する。このような構成により、静止画表示中に外部の処理装置 5 の動作を停止して消費電力を低減することができるという利点がある。

10

#### 【 0 0 0 5 】

また一方では、携帯電話端末等の高機能化に伴って、携帯情報機器でも動画の表示を行うことが求められている。しかし、液晶パネルは表示画像の変化に対する応答速度が遅く、動画を表示する際に画像ボケが発生する性質がある。そこで従来から、大型液晶パネル等においては液晶の応答速度を改善するためにオーバードライブ処理が行われている。オーバードライブ処理とは、現在の画像データと1フレーム前の画像データとを比較し、階調値が増加、つまり輝度が高くなっている場合には、通常の値より高い液晶駆動電圧によって液晶パネルを駆動し、階調値が減少（輝度が低下）している場合には、通常より低い駆動電圧で液晶パネルを駆動するものである。これによって、液晶パネルの応答速度を高めることができる。このようなオーバードライブ処理の詳細は、例えば特許文献 1 乃至 3 に記載されている。

20

【特許文献 1】特許 2 6 1 6 6 5 2 号公報

【特許文献 2】特開平 4 - 3 6 5 0 9 4 号公報

【特許文献 3】特開 2 0 0 3 - 2 0 2 8 4 5 号公報

【特許文献 4】特開 2 0 0 3 - 1 6 2 2 7 2 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【 0 0 0 6 】

30

従来のメモリ内蔵コントローラ・ドライバ 8 にオーバードライブ処理回路を付加することによって、液晶の応答速度の改善が期待できる。しかし、携帯電話端末等の携帯情報機器は機器サイズ及び消費電力の制約が大きい。このため、これらの機器に使用するメモリ内蔵コントローラ・ドライバ 8 も、チップサイズが小さくかつ消費電力が小さいことが望ましいが、コントローラ・ドライバ 8 にオーバードライブ処理回路を単純に付加したのでは、コントローラ・ドライバ 8 のチップサイズ及び消費電力が増大することが問題となる。

#### 【 0 0 0 7 】

このうち、チップサイズを減少するための手段として、画像データを圧縮した後に画像メモリに保存することにより、チップ面積を占める割合の大きい画像メモリの容量を小さくすることが有効である。しかしながら、画像メモリに保存された圧縮画像データ又はこれを伸張した画像データを使用してオーバードライブ処理を行う場合は、液晶パネルに印加する電圧を正確に制御できないという課題がある。

40

#### 【 0 0 0 8 】

例えば、従来から知られている組織的ディザ法によって画像データの圧縮を行う場合に、ディザ処理によって空間的に配置された誤差がオーバードライブ処理によってさらに強調され、液晶パネルに表示される画像の粒状感が増した表示となる可能性がある。具体的に説明すると、 $2 \times 2$  ディザマトリクスを用いて、画像データを 2 ビット圧縮した場合、入力画像が同じ階調の画像データであっても、ディザマトリクスとの演算処理により、4 階

50

調差を持つ画像が生じる。ここで、表示画像の全体が同じ色から別の色に変わったとき、オーバードライブ処理を行ったとする。その場合、4階調分の余分なオーバードライブがかかる場所が存在する。さらに、ディザ処理の場合は、特定の場所にこの余分なオーバードライブがかかることになる。そのため、粒状感の増した表示となってしまう。

#### 【0009】

本発明は、上述の課題を考慮してなされたものであり、圧縮画像データを用いてオーバードライブ処理を行う場合に、液晶パネルに印加する電圧を正確に制御できるコントローラ・ドライバを提供するものである。

#### 【課題を解決するための手段】

#### 【0010】

本発明にかかるコントローラ・ドライバは、受信画像データを圧縮して第1の圧縮画像データ及び第2の圧縮画像データを生成する圧縮手段と、少なくとも1フレーム分の前記第2の圧縮画像データを蓄積可能な画像メモリと、前記第1の圧縮画像データ又はこれを伸張した画像データを入力するとともに、前記画像メモリから前記第1の圧縮画像データよりも1フレーム前の第2の圧縮画像データ又はこれを伸張した画像データを入力し、これらのデータに基づいて前記受信画像データの階調値を補正した補正画像データを生成するオーバードライブ演算回路とを備えるものである。さらに、前記圧縮手段は、前記第1の圧縮画像データ及び前記第2の圧縮画像データを生成する際に適用する圧縮処理を時間経過とともに変更するものであり、前記圧縮手段において前記第1の圧縮画像データを生成する際に適用する圧縮処理は、前記受信画像データより1フレーム前の画像データを圧縮して前記第2の圧縮画像データを生成する際に適用する圧縮処理と同一であることを特徴とする。

10

#### 【0011】

また、本発明にかかる液晶表示装置は、上記の本発明にかかるコントローラ・ドライバと、前記コントローラ・ドライバによって駆動される液晶表示部とを備えるものである。

#### 【0012】

このように構成することにより、オーバードライブ演算回路で比較される2つの画像データに含まれる圧縮誤差を時間経過と共に変更でき、さらに、2つの画像データが同一の圧縮誤差を用いて圧縮・伸張されたものとなる。このため、コントローラ・ドライバの回路規模を小さくしながら、オーバードライブと圧縮誤差による粒状感やブロックノイズを軽減でき、圧縮誤差の違いに起因する不要な電圧が液晶パネルに印加されることはなく、適切なオーバードライブ処理を行うことができる。

20

#### 【0013】

さらに、本発明にかかる液晶駆動方法は、画像データを受信し、受信画像データを圧縮して第1の圧縮画像データを生成し、前記第1の圧縮画像データ又はこれを伸張した画像データ、及び、前記第1の圧縮画像データよりも1フレーム前の第2の圧縮画像データ又はこれを伸張した画像データに基づいて、前記受信画像データの階調値を補正した補正画像データを生成する液晶駆動方法であって、前記第1の圧縮画像データ及び前記第2の圧縮画像データを生成する際に適用する圧縮処理は、前記受信画像データより1フレーム前の画像データを圧縮して前記第2の圧縮画像データを生成する際に適用する圧縮処理と同一であることを特徴としている。

30

#### 【0014】

このような方法によれば、オーバードライブ演算時に比較される2つの画像データに含まれる圧縮誤差を時間経過と共に変更でき、さらに、2つの画像データが同一の圧縮誤差を用いて圧縮・伸張されたものとなる。このため、コントローラ・ドライバの回路規模を小さくしながら、オーバードライブと圧縮誤差による粒状感やブロックノイズを軽減でき、圧縮誤差の違いに起因する不要な電圧が液晶パネルに印加されることはなく、適切なオーバードライブ処理を行うことができる。

40

#### 【発明の効果】

50

## 【0015】

本発明により、コントローラ・ドライバの回路規模を小さくしながら、オーバードライブと圧縮誤差による粒状感やブロックノイズを軽減でき、液晶パネルに印加する電圧を正確に制御することが可能なコントローラ・ドライバ及びそれを用いる液晶表示装置並びに液晶駆動方法を提供することができる。

## 【発明を実施するための最良の形態】

## 【0016】

発明の実施の形態1.

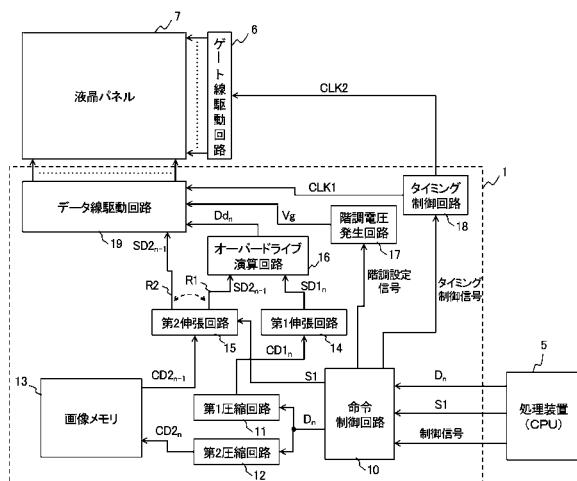

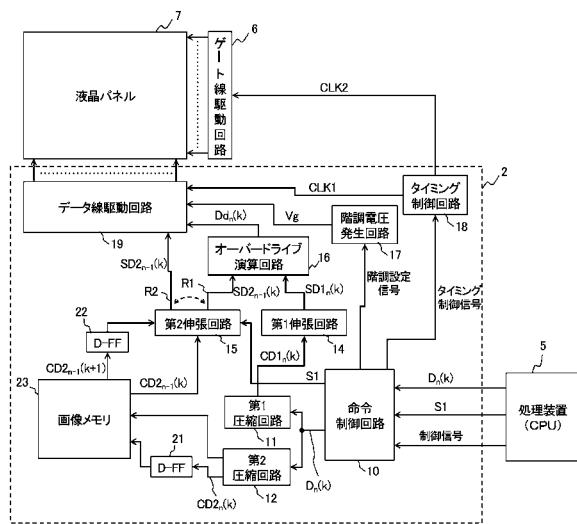

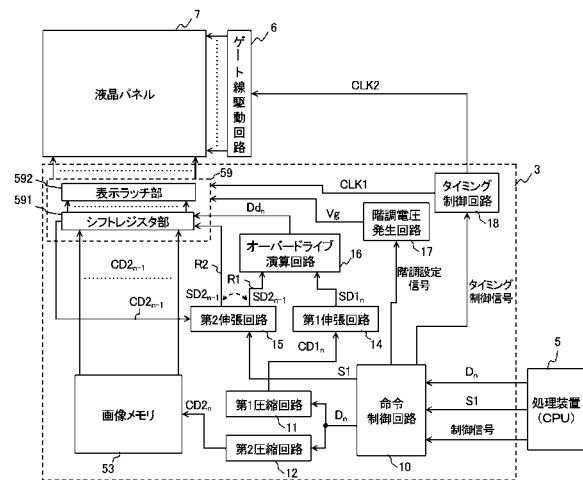

本実施の形態にかかるコントローラ・ドライバ1を備える液晶表示装置の構成を図1に示す。コントローラ・ドライバ1は、(1)第1圧縮回路11及び第2圧縮回路12の2つの圧縮回路を備えて個別に圧縮処理を行うことにより、第1圧縮回路11に転送される圧縮画像データに含まれる圧縮誤差と画像メモリ13に保存される圧縮画像データに含まれる圧縮誤差を変更できること、及び(2)命令制御回路10が外部の処理装置5から動画・静止画切り替え信号S1を受信し、受信した信号S1に応じて第2伸張回路15が伸張後の画像データの出力先を切り替えることを特徴としている。以下、コントローラ・ドライバ1について詳細に説明する。なお、図14に示した従来の構成と同一の機能を有するものについては、同一の番号を付して詳細な説明を省略する。

10

## 【0017】

命令制御回路10は、処理装置5から画像データD<sub>n</sub>、制御信号及び動画・静止画切り替え信号S1を受信する。制御信号には、画像データD<sub>n</sub>が動画である場合に表示タイミングを制御するタイミング制御信号を含む、処理装置5からコントローラ・ドライバ1の制御を行うための信号である。命令制御回路10は、受信した画像データD<sub>n</sub>を第1圧縮回路11及び第2圧縮回路12に出力する。さらに、命令制御回路10は、動画・静止画切り替え信号S1を第2伸張回路15に出力する。

20

## 【0018】

第1圧縮回路11は、入力された1画素単位の画像データD<sub>n</sub>を圧縮し、圧縮後の画像データCD1<sub>n</sub>を第1伸張回路14に対して出力する。一方、第2圧縮回路12は、画像データD<sub>n</sub>を圧縮して圧縮後の画像データCD2<sub>n</sub>を画像メモリ13に保存する。画像メモリ13は、少なくとも1フレーム分の圧縮画像データを蓄積可能なメモリである。なお、第1圧縮回路11と第2圧縮回路12は、画像データD<sub>n</sub>に対して別々の圧縮処理を行うことができる。第1圧縮回路11及び第2圧縮回路12で行う圧縮処理の詳細については後述する。

30

## 【0019】

第1伸張回路14は、圧縮画像データCD1<sub>n</sub>を伸張し、伸張後の画像データSD1<sub>n</sub>をオーバードライブ演算回路16に転送する。第2伸張回路15は、圧縮画像データCD1<sub>n</sub>より1フレーム前であって、第2圧縮回路12で圧縮された画像データCD2<sub>n-1</sub>を画像メモリ13から読み出して伸張処理を行う。

## 【0020】

第2伸張回路15は、動画・静止画切り替え信号S1に応じて、伸張後の画像データSD2<sub>n-1</sub>をオーバードライブ演算回路16に出力するか、オーバードライブ演算回路16をバイパスしてデータ線駆動回路19に直接出力するかを選択する。このような動作は様々な具体的構成により実現可能であるが、要するに動画・静止画切り替え信号S1に応じて第2伸張回路15の接続先を変更できればよく、具体的な構成は特に限定されるものではない。一例としては、第2伸張回路15の出力端子に動画・静止画切り替え信号S1に応じて動作するセレクタを備えることとし、動画を表示する際にはオーバードライブ演算回路16に接続される経路R1を選択し、静止画を表示する際にはオーバードライブ演算回路を迂回してデータ線駆動回路19に接続される迂回経路R2を選択するよう構成すればよい。

40

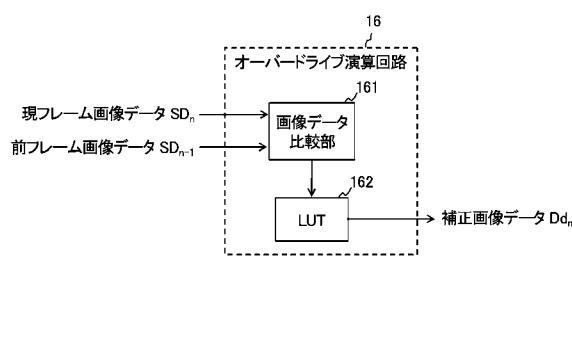

## 【0021】

次に、オーバードライブ演算回路16の構成例を、図2を用いて説明する。オーバード

50

ライブ演算回路 16 が備える画像データ比較部 161 では、第 1 伸張回路 14 から入力される現フレーム画像データ  $SD_n$  と、第 2 伸張回路 15 から入力される前フレーム画像データ  $SD_{n-1}$  との比較を行って、両画像データ間での階調変化を検出する。さらに、画像データ比較部 161 は、ルックアップテーブル (LUT) 162 を参照して、入力画像データ  $SD_n$  及び  $SD_{n-1}$  間の階調変化に応じた補正画像データを選択し、補正画像データ  $Dd_n$  としてデータ線駆動回路 19 に出力する。

【0022】

ここで、LUT 162 は、現フレーム画像データ  $SD_n$  と前フレーム画像データ  $SD_{n-1}$  との組合せに対応して予め定められた補正画像データ  $Dd_n$  を格納したテーブルである。補正画像データは、入力画像データ  $SD_n$  及び  $SD_{n-1}$  間の階調変化を強調するよう定めされており、補正画像データに基づいてデータ線駆動回路 19 が液晶パネル 7 を駆動することによって、液晶パネル 7 の応答速度の改善が図られる。10

【0023】

なお、画像データ比較部 161 は、現フレーム画像データ  $SD_n$  と前フレーム画像データ  $SD_{n-1}$  とを比較した結果、両者が同一であった場合は、現フレーム画像データ  $SD_n$  あるいは前フレーム画像データ  $SD_{n-1}$  をそのまま補正画像データ  $Dd_n$  として出力する。オーバードライブ処理を行う必要がないためである。

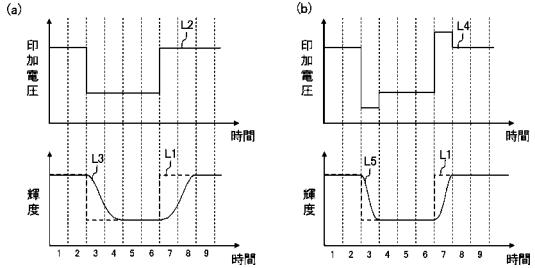

【0024】

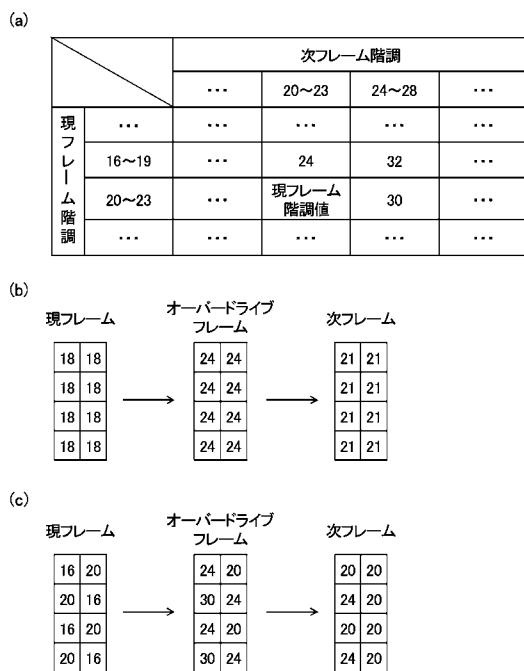

オーバードライブ処理の効果を、図 3 (a) を用いて説明する。図 3 (a) は、オーバードライブ処理を行わない場合における液晶パネル 7 に対する印加電圧と、当該印加電圧に応じた液晶パネル 7 の輝度変化の様子を示したものである。グラフの横軸は、時間を画像フレーム単位で表している。液晶パネルに表示する画像データが L1 で示す破線のように変化した場合、液晶パネル 7 に対する印加電圧は、画像データの輝度変化に応じて L2 のように変化する。このとき、液晶の応答速度が遅いために、液晶パネルの表示輝度の変化は、L3 で示すように画像データ及び印加電圧の変化から遅れてしまう。20

【0025】

一方、図 3 (b) は、オーバードライブ処理を行った場合の様子を、図 3 (a) と対応させて示したものである。図 3 (a) と同様に、L1 のように画像データが変化した場合には、オーバードライブ演算回路 16 が、画像データの階調変化を強調するような補正画像データをデータ線駆動回路 19 に出力することにより、液晶パネル 7 に対する印加電圧は L4 に示すように変化する。オーバードライブ処理を行った場合の液晶パネルの表示輝度 L5 は、オーバードライブ処理を行わない場合の表示輝度 L3 より速く所望の表示輝度に達することになり、液晶の応答速度が改善される。30

【0026】

図 1 に戻り、データ線駆動回路 19 は、オーバードライブ演算回路 16 から出力される補正画像データ  $Dd_n$ 、又は、オーバードライブ演算回路 16 をバイパスして第 2 伸張回路 15 から入力される伸張後の画像データ  $SD_{2n-1}$  を順次受信して 1 ライン分の画像データをラッチし、タイミング制御回路 18 から指示されるタイミング信号  $CLK_1$  に従って、階調電圧発生回路 17 の生成する階調電圧  $Vg$  から画像データに応じて選択した電圧を液晶パネル 7 に印加する。他方、ゲート線駆動回路 6 は、タイミング制御回路 18 から指示されるタイミング信号  $CLK_2$  に従って液晶パネル 7 にゲートパルスを印加し、液晶パネル 7 を駆動する。40

【0027】

このように構成することにより、静止画を表示する際に、データ線駆動回路 19 が、第 2 伸張回路 15 が output する伸張後の画像データ  $SD_{2n-1}$  をラッチして液晶パネル 7 を駆動することができるため、オーバードライブ演算回路 16 を経由せずに画像表示を行うことができる。

【0028】

従来のコントローラ・ドライバ 8 にオーバードライブ処理回路を単純に内蔵した構成では、静止画表示を行う場合もオーバードライブ処理回路に対する入力を必要とするため、50

入力のための電力を必要とする。さらに画像メモリに対するアクセス電力も必要となる。これは、コントローラ・ドライバ8が動画・静止画切り替え信号S1を用いていないために、常に動画表示として動作するためである。このように、従来のコントローラ・ドライバ8にオーバードライブ処理回路を単純に内蔵した構成では、消費電力を低減できないという問題が発生する。さらに、このような構成において静止画表示を行うと、オーバードライブ処理回路に対して入力する画像データが存在しないために、オーバードライブ処理回路は、最後に入力された画像データとの比較によるオーバードライブ演算を実行し続けることとなる。したがって、オーバードライブ処理回路は、静止画表示になる前に最後に表示される画像データと画像メモリに残っている画像データを比較して、補正画像データを選択して出力することになるため、正しい静止画表示を行うことができないという問題もある。

10

### 【0029】

これに対して、本実施の形態にかかるコントローラ・ドライバ1は、迂回経路R2を設け、画像種別に応じて第2伸張回路15の出力先を選択するよう構成することにより、静止画表示する際にオーバードライブ演算回路16を迂回して画像表示を行うことができる。このような構成により、オーバードライブ演算回路16を動作させることなく静止画表示を行うことができるため、静止画表示を行う際の消費電力を低減することができる。さらに、静止画表示の際にオーバードライブ演算回路16から誤った補正画像データが出力されることはため、正しい静止画表示を行うことができる。

### 【0030】

20

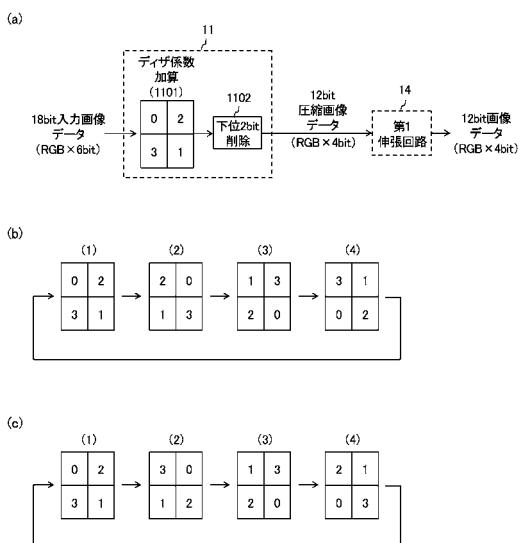

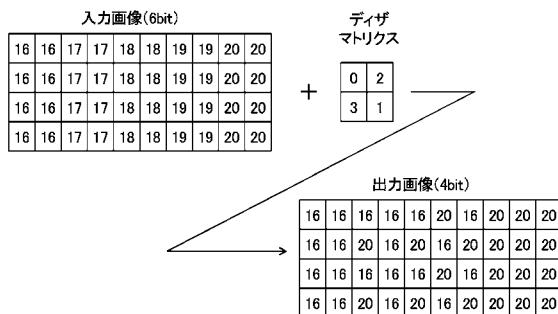

続いて、第1圧縮回路11及び第2圧縮回路12が行う圧縮処理について説明する。第1圧縮回路11及び第2圧縮回路12における画像データの圧縮方法には、例えば組織的ディザ法を適用できる。組織的ディザ法は、画像圧縮により生じる誤差を空間的に分散させて擬似的な表示を行う方法であり、隣接する複数の画素を1組とするディザマトリクスを使用して、画像圧縮で損なわれた階調に相当する中間階調を擬似的に表現する。以下、図4及び図5を用いて具体的に説明する。

### 【0031】

図4(a)は、入力される画像データが18ビット(6ビット×RGB)である場合に、2×2画素のディザマトリクスを適用して、12ビット(4ビット×RGB)の圧縮画像データを得る例を示したものである。第1圧縮回路11に18ビットの画像データが入力されると、ディザ係数加算処理(1101)と、ディザ係数を加算したRGBの各副画素から下位2ビットを削除する処理(1102)が行われ、12ビット(4ビット×RGB)の画像データが出力される。第1圧縮回路11から出力される圧縮後の12ビット画像データは、第1伸張回路14に転送されが、組織的ディザ法では伸張処理を行うことはできないため、この場合の第1伸張回路14は単なるスルーリーク路あるいは配線のみが存在することになる。

30

### 【0032】

組織的ディザ法による画像圧縮の例を図5に示す。図5は、1画素当たり6ビットの画像データで構成される10画素×4画素の入力画像と、入力画像に対して図に示す2×2ディザマトリクスを適用して、1画素当たり4ビットにまで圧縮した出力画像を表している。なお、入力画像及び出力画像の数値は、各画素の階調数を10進数で示したものである。図5の入力画像に対するディザ係数加算処理(1101)では、入力画像の奇数ラインに対してラインの先頭画素から順にディザ係数0, 2, 0, 2, ...が加算され、偶数ラインに対してラインの先頭画素から順にディザ係数3, 1, 3, 1, ...が加算される。ディザ係数を加算した画像データから下位2ビットを削除する処理(1102)を行うと、階調16から20の4階調を含む入力画像から中間階調(17, 18, 19)が失われ、階調16及び20のみの画像に圧縮された出力画像が得られる。出力画像は1画素当たり4ビットにまで圧縮されるものの、視覚の積分効果によって、見かけ上は6ビット相当の階調数を表現することができる点が組織的ディザ法の特徴である。

40

### 【0033】

50

なお、上述したように、1つのディザマトリクスを固定的に使用したのでは、ディザ処理によって空間的に配置された誤差がオーバードライブ処理によってさらに強調され、液晶パネルに表示される画像の粒状感が増した表示となる可能性がある。図6を用いて具体的に説明する。図6は、8画素の画像全体が18階調で表示されている画像が、全体が21階調の画像に変化する際のオーバードライブ処理を示すものである。図6(a)は、ルックアップテーブル162の例であり、例えば、18階調の画像から21階調の画像に変化する場合には、24階調の画像に相当する印加電圧によってオーバードライブを行うことを示している。

#### 【0034】

図6(b)は、ディザ処理を行わない画像に対するオーバードライブ処理を示している。現フレーム画像が18階調、変化後のフレーム画像が21階調であるから、変化時のフレーム(オーバードライブフレーム)では、24階調の画像に相当する電圧が液晶に印加される。その後のフレーム(次フレーム)では、21階調の電圧を液晶に印加することによって、図3を用いて説明したように、応答速度の向上が図られる。

10

#### 【0035】

一方、図6(c)は、図5に示したものと同様の $2 \times 2$ ディザマトリクスによって2ビット圧縮を行った画像に対するオーバードライブ処理を示している。このような組織的ディザ法を適用した場合は、図6(c)に示すように、18階調であった圧縮前の画像は、16階調と20階調の画素が混在した画像として表される。また、21階調の変化後の画像は、20階調と24階調の画素が混在した画像として表され、変化前のフレーム(現フレーム)と比較すると、16階調から20階調に変化する画素、20階調のまま変化しない画素、20階調から24階調に変化する画素の3種類が混在することになる。

20

#### 【0036】

このような画像変化に対して、図6(a)に示したLUT162に従ってオーバードライブ処理を適用すると、20階調のまま変化しない画素にはオーバードライブが行われず、他の画素にはオーバードライブが行われることになるため、画素によってオーバードライブの強弱が生じてしまう。この結果、図6(c)のオーバードライブフレームでは、20階調の画素と30階調の間で10階調の差が生じることになり、組織的ディザ法による4階調の誤差がさらに強調されて、表示画像の粒状感を増すことになる。

30

#### 【0037】

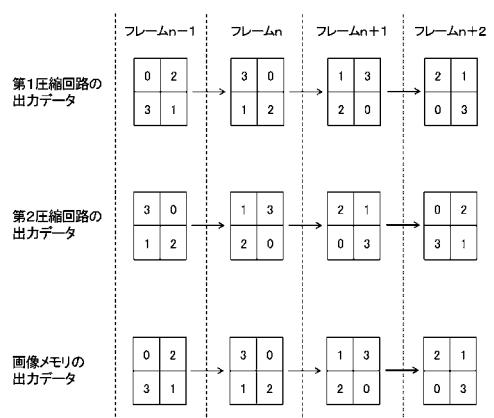

そこで本発明では、画像データに適用するディザマトリクスを時間経過に応じて変更することで、誤差を時間的に分散し、表示画像の粒状感を抑制したオーバードライブ処理を行う。例えば、図4(b)に示すように、4フレームを一周期としてディザマトリクスを変更することにより、フレーム毎に適用する圧縮処理を変更する。また、図4(c)に示すように、1フレーム毎にディザ係数を時計回りに回転させ、4フレームを一周期としてディザマトリクスを変更してもよい。

#### 【0038】

このような処理を行った場合、入力画像に変化がなければ、ディザ処理後の画像が出力されることになる。一方、入力画像が変化した場合は、ディザ処理された画像に対してオーバードライブ処理が行われることになる。このため、上述したように、表示画像中の場所によってはオーバードライブの強弱に際が生じてディザ処理による誤差が強調され、粒状感が増した画像となる可能性がある。しかしながら、本発明では、フレーム毎にディザマトリクスを回転することにより誤差を時間的に分散しているため、出力画像の粒状感を抑制することができる。

40

#### 【0039】

また、一般的には、 $n \times n$ ディザマトリクス( $n$ は2以上の整数)を用いて画像データの圧縮を行う場合、ディザ係数を置換して得られる $n^2$ 通りのディザマトリクスを用い、 $n^2$ フレームを一周期としてディザマトリクスを順次変更することとすればよい。例えば、画像データの下位4ビットを削減する場合には、ディザ係数に0~15を用いた $4 \times 4$ のディザマトリクスを使用して、16通りのディザマトリクスを1フレーム毎に順次変更

50

して適用することにより、ディザ処理による誤差を時間的に分散し、表示画像の粒状感を抑制したオーバードライブ処理を行うことができる。

#### 【0040】

しかし、画像データの圧縮処理を時間経過に応じて変更すると、圧縮された画像データ若しくは伸張後の画像データに含まれる圧縮誤差が刻々と変化することになるため、新たな問題が生じる。組織的ディザ法の場合を例にとると、同一階調である現在の画像データと1フレーム前の画像データが異なるディザマトリクスを用いて圧縮された場合は、これらの画像に含まれる圧縮誤差が異なるため、オーバードライブ演算回路で比較する際に両画像が階調の異なった画像として認識され、誤ったオーバードライブ処理が行われることになる。

10

#### 【0041】

この新たな問題を解消するため、本発明では、第1圧縮回路11及び第2圧縮回路12に適用する圧縮処理を、画像データD<sub>n</sub>を第1圧縮回路11で圧縮する際に圧縮後の画像データに含まれることになる圧縮誤差と、画像データD<sub>n</sub>より1フレーム前の画像データD<sub>n-1</sub>を第2圧縮回路12で圧縮する際に圧縮後の画像データに含まれることになる圧縮誤差とが同一となるよう決定する。例えば、組織的ディザ法であれば、第1圧縮回路11において画像データD<sub>n</sub>に適用するディザマトリクスを、第2圧縮回路12において1フレーム前の画像データD<sub>n-1</sub>に適用したディザマトリクスと同一とすればよい。換言すれば、第2圧縮回路12で用いるディザマトリクスを、1フレーム後の画像データを圧縮する際に第1圧縮回路11で用いるディザマトリクスと同一とすればよいことになる。

20

#### 【0042】

図7を用いて具体的に説明する。図7は、第1圧縮回路11、第2圧縮回路12及び画像メモリ13の出力データに対して適用されるディザマトリクスを示している。図のように、ある時刻のフレームnに対して第1圧縮回路11に適用されるディザマトリクスは、1フレーム前のフレームn-1に対して第2圧縮回路12で適用されるディザマトリクスと共通である。このように、第1圧縮回路11に適用されるディザマトリクスは、第2圧縮回路12に適用されるディザマトリクスから1フレーム分遅延した関係にある。一方、画像メモリ13の出力データは、1フレーム前に第2圧縮回路12において圧縮された画像データであるから、図のように、ある時刻（例えばフレームn）に第1圧縮回路11で適用されるディザマトリクスと、当該時刻に画像メモリ13から出力される画像データに適用されたディザマトリクスは一致している。オーバードライブ演算回路16では、第1圧縮回路11の出力データと画像メモリ13の出力データの比較が行われるが、両者に適用されたディザマトリクス、つまり圧縮誤差は共通したものとなる。

30

#### 【0043】

このような構成によって、オーバードライブ演算回路16において比較される圧縮画像データSD1<sub>n</sub>に含まれる圧縮誤差と1フレーム前の圧縮画像データSD2<sub>n-1</sub>に含まれる圧縮誤差と同一にすることができる。

#### 【0044】

以上に説明したように、本実施の形態にかかるコントローラ・ドライバ1は、第1圧縮回路11及び第2圧縮回路12に適用する圧縮処理を時間と共に変更すると共に、オーバードライブ演算回路16で比較される2つの画像データに含まれる圧縮誤差を同一とするものである。このような構成により、コントローラ・ドライバの回路規模を小さくしながら、オーバードライブと圧縮誤差による粒状感やブロックノイズを軽減でき、圧縮誤差の違いに起因する不要な電圧が液晶パネル7に印加されることはなく、適切なオーバードライブ処理を行うことができる。

40

#### 【0045】

なお、上述した効果を得るために、要するにオーバードライブ演算回路16において比較される画像データSD1<sub>n</sub>と1フレーム前の画像データSD2<sub>n-1</sub>に含まれる圧縮誤差が同一となるよう構成することが重要である。したがって、第1圧縮回路11及び第2圧縮回路12の2つの圧縮回路を備えるコントローラ・ドライバ1の構成は一例にすぎ

50

ない。例えば、1つの圧縮回路における時分割処理によって、1つの画像データ  $D_n$  を異なる圧縮誤差で圧縮するよう構成してもよい。

【0046】

また、第1圧縮回路11及び第2圧縮回路12において適用される画像圧縮方法は組織的ディザ法に限られず、その他の非可逆圧縮方法を適用する場合であっても、上述したように第1圧縮回路11において現在の画像データに適用される圧縮処理を、第2圧縮回路12において前フレームの画像データに対して適用された圧縮処理に合わせることによって、適切なオーバードライブ処理を行うことができる。例えば、特許文献4に開示された、ディザ処理によって圧縮されたデータを圧縮時のディザ処理に対する逆処理によって伸張することにより、誤差を最小限に抑える圧縮伸張処理を行うこととしてもよい。

10

【0047】

発明の実施の形態2.

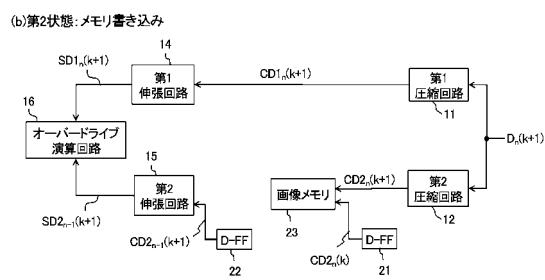

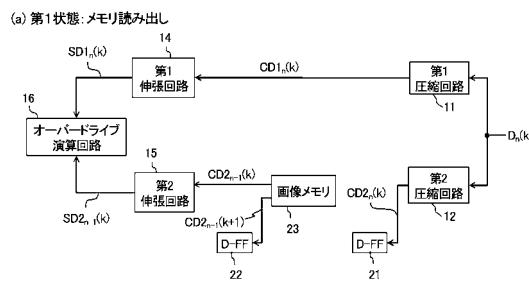

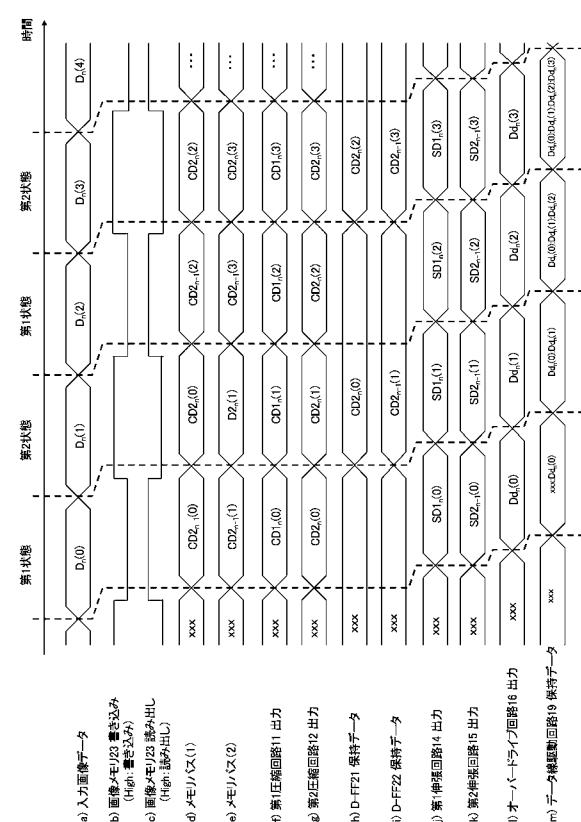

本実施の形態にかかるコントローラ・ドライバ2を備える液晶表示装置の構成を図8に示す。コントローラ・ドライバ2は、発明の実施の形態1に示したコントローラ・ドライバ1と比較して、第2圧縮回路12と画像メモリ23との間にD型フリップフロップ回路(D-F-F)21を備え、画像メモリ23と第2伸張回路15との間にD-F-F22を備えていることを特徴としている。なお、他の構成はコントローラ・ドライバ1と同じであるため、同一の番号を付して詳細な説明を省略する。以下では、D-F-F21及び22を備えたことによるコントローラ・ドライバ2の動作の特徴を説明する。

【0048】

20

図9は、第1圧縮回路11及び第2圧縮回路12からオーバードライブ演算回路16に至るまでの画像データの流れを示す図である。図9(a)と(b)は、連続する2画素の画像データに対する処理を示している。なお、図9(a)での入力画像データを  $D_n(k)$  と表し、図9(b)での入力画像データを  $D_n(k+1)$  と表す。ここで、nはフレームに付与した番号、kは画素に付与した番号である。

【0049】

図9(a)に示す第一状態では、まず、第1圧縮回路11及び第2圧縮回路12に画像データ  $D_n(k)$  が入力される。第1圧縮回路11は画像データ  $D_n(k)$  を前述した組織的ディザ法等によって圧縮し、圧縮画像データ  $CD1_n(k)$  を第1伸張回路14に出力する。一方、第2圧縮回路12は圧縮画像データ  $CD2_n(k)$  を  $D-F-F21$  に出力し、画像メモリ23には書き込みを行わない。第2伸張回路15は、画像メモリ23から1フレーム前の圧縮画像データ  $CD2_{n-1}(k)$  を取得し、伸張後の画像データ  $SD2_{n-1}(k)$  をオーバードライブ演算回路16に出力する。なおこのとき、 $D-F-F22$  には、 $CD2_{n-1}(k)$  に連続する  $k+1$  番目の画素の圧縮画像データ  $CD2_{n-1}(k+1)$  を画像メモリ23から読み出して保持する。このように、図9(a)に示す処理では、画像メモリ23からの読み込みだけを行い、画像メモリ23に対する書き込みは行われない。

30

【0050】

図9(b)に示す第2状態では、画像データ  $D_n(k+1)$  が入力される。第1圧縮回路11は画像データ  $D_n(k+1)$  を圧縮し、圧縮画像データ  $CD1_n(k)$  を第1伸張回路14に出力する。第2圧縮回路12は圧縮画像データ  $CD2_n(k+1)$  を画像メモリ23に書き込み、これとともに  $D-F-F21$  に保持されている  $CD2_n(k)$  も画像メモリ23に書き込まれる。一方、第2伸張回路15は、 $D-F-F22$  に保持されている  $CD2_{n-1}(k+1)$  を読み込み、画像メモリ23からの画像データの読み込みは行われない。このように、図9(b)に示す処理では、画像メモリ23に対する書き込みだけを行い、画像メモリ23からの読み込みは行われない。

40

【0051】

図10は、コントローラ・ドライバ2における画像データの入出力タイミングを示す図である。図10(b)及び(c)に示すように、第一状態と第二状態とで画像メモリ23の読み出し及び書き込みを交互に行う。ここで、図10に示すメモリバス(1)は、第一

50

状態では画像メモリ 2 3 から第 2 伸張回路 1 5 に入力されるデータを示し、第二状態では D - F F 2 1 から画像メモリ 2 3 に入力されるデータを示している。またメモリバス ( 2 ) は、第一状態では画像メモリ 2 3 から D - F F 2 2 に入力されるデータを示し、第二状態では第 2 圧縮回路 1 2 から画像メモリ 2 3 に入力されるデータを示している。

【 0 0 5 2 】

上述したように、コントローラ・ドライバ 2 は、2 画素を単位に画像メモリ 2 3 への書き込み又は読み出しを行うことを特徴とする。発明の実施の形態 1 に示したコントローラ・ドライバ 1 では、1 画素の画像データを出力する間（画像表示クロックと呼ぶ）に、コントローラ・ドライバ 1 が備える画像メモリ 1 3 への C D 2 <sub>n</sub> の書き込みと C D 2 <sub>n+1</sub> の読み出しを実行する必要がある。このため、画像表示クロックを倍化した動作クロックによって画像メモリ 1 3 へのアクセスを行うか、画像メモリ 1 3 を 2 ポートメモリとする必要がある。これに対して、本実施の形態にかかるコントローラ・ドライバ 2 は、1 画素の画像データを出力する間は、画像メモリ 2 3 への書き込みと読み出しのいずれか一方しか行わないため、画像表示クロックを倍化した動作クロックを必要とせず、画像メモリ 2 3 は 1 ポートメモリによって構成することができる。

【 0 0 5 3 】

なお、本実施の形態では、D - F F 2 1 及び 2 2 を備えることとしたが、要するに、1 画素の画像データを出力する間、一時的に圧縮画像データを保持することができる回路であればよい。したがって、D - F F 2 1 及び 2 2 に代えてラッチ回路等の一時データ保持回路を用いることとしてもよい。

【 0 0 5 4 】

また、本実施の形態にかかるコントローラ・ドライバ 2 は、発明の実施の形態 1 にかかるコントローラ・ドライバ 1 と同様に、迂回経路 R 2 を設け、命令制御回路 1 0 が output する動画・静止画切り替え信号 S 1 に応じて第 2 伸張回路 1 5 の出力先を選択するよう構成することにより、静止画を表示する際にオーバードライブ演算回路 1 6 を迂回して画像表示を行うことができる。このような構成により、オーバードライブ演算回路 1 6 を動作させることなく静止画表示を行うことができるため、静止画表示を行う際の消費電力を低減することができる。さらに、静止画表示の際にオーバードライブ演算回路 1 6 から誤った補正画像データが出力されないため、正しい静止画表示を行うことができる。

【 0 0 5 5 】

発明の実施の形態 3 。

本実施の形態にかかるコントローラ・ドライバ 3 を備える液晶表示装置の構成を図 1 1 に示す。コントローラ・ドライバ 3 は、発明の実施の形態 1 に示したコントローラ・ドライバ 1 と比較して、画像メモリ 5 3 からデータ線駆動回路 5 9 が備えるシフトレジスタ部 5 9 1 に対して 1 ライン分の圧縮画像データを一括転送した後に、圧縮画像データをシフトレジスタ部 5 9 1 から第 2 伸張回路 1 5 に入力して伸張処理を行うことを特徴としている。以下では、このシフトレジスタ部 5 9 1 を介した伸張処理について説明する。

【 0 0 5 6 】

まず始めに、データ線駆動回路 5 9 が備えるシフトレジスタ部 5 9 1 に対して、画像メモリ 5 3 から 1 ライン分の圧縮画像データが一括して転送される。次に、シフトレジスタ部 5 9 1 が保持する圧縮データが第 2 伸張回路 1 5 に転送されて、伸張処理が行われる。

【 0 0 5 7 】

シフトレジスタ部 5 9 1 と第 2 伸張回路 1 5 の間でのデータ転送動作を、図 1 2 を用いて説明する。なお、図では一例として、圧縮画像データが 12 ビットであり、伸張後の画像データが 18 ビットである場合を示している。まず図 1 2 ( a ) に示すように、画像メモリ 5 3 からシフトレジスタ部 5 9 1 に 1 ライン分の圧縮画像データが一括して転送される。ここで、画像メモリ 5 3 は、少なくとも 1 フレーム分の圧縮画像データを保存可能なメモリである。

【 0 0 5 8 】

次に、図 1 2 ( b ) に示すように、シフト動作によってフリップフロップ ( F F ) 回路

10

20

30

40

50

591Aが保持している圧縮画像データから順に第2伸張回路15に転送される。同時に、FF回路591B及び591Cは、保持する画像データを図の左方向に順次シフトする。さらに、オーバードライブ演算回路15から出力される18ビットの補正画像データ、又は第2伸張回路15から出力される伸張後の18ビット画像データがFF回路591Cに保持される。このシフト動作を1ライン分の画像データについて繰り返すことにより、シフトレジスタ部591が表示用の画像データによって書き換えられることになる。

#### 【0059】

最後に図12(c)に示すように、画像データを表示ラッチ部592に転送して、液晶パネル4を駆動する。また、この表示ラッチ部592に転送するラッチ動作に合わせて、画像メモリ53からシフトレジスタ部591に次の1ライン分の圧縮画像データが一括して転送され、上記の処理が繰り返し実行される。10

#### 【0060】

このように、コントローラ・ドライバ3では、シフトレジスタ部591に1ライン分の圧縮画像データを一括して転送した後に伸張処理を行うため、画像メモリ53に対するメモリアクセスを1ラインの画像データに対して1回に抑えることができる。これにより、1画素毎にメモリアクセスを行う発明の実施の形態1に示したコントローラ・ドライバ1に比べてメモリアクセス回数を減少できるため、メモリアクセスに要する消費電力を低減することができる。

#### 【0061】

なお、本実施の形態にかかるコントローラ・ドライバ3は、発明の実施の形態1にかかるコントローラ・ドライバ1と同様に、迂回経路R2を設け、命令制御回路10が outputする動画・静止画切り替え信号S1に応じて第2伸張回路15の出力先を選択する構成することにより、静止画を表示する際にオーバードライブ演算回路16を迂回して画像表示を行うことができる。このような構成により、オーバードライブ演算回路16を動作させることなく静止画表示を行うことができるため、静止画表示を行う際の消費電力を低減することができる。さらに、静止画表示の際にオーバードライブ演算回路16から誤った補正画像データが出力されないため、正しい静止画表示を行うことができる。20

#### 【0062】

発明の実施の形態4.

本実施の形態にかかるコントローラ・ドライバ4を備える液晶表示装置の構成を図13に示す。コントローラ・ドライバ4ではまず、画像メモリ53から第2伸張回路75に1ライン分の圧縮画像データが一括して転送される。第2伸張回路75は、1ライン分の圧縮画像データの伸張処理を並行して実施可能な伸張回路である。第2伸張回路75は、例えば、従来の第2伸張回路15を1ラインの画素分だけ並列に配置して構成すればよい。第2伸張回路75で伸張された画像データSD<sub>2n-1</sub>は、データ線駆動回路79が備えるシフトレジスタ部791に転送される。30

#### 【0063】

オーバードライブ処理を行う場合は、シフトレジスタ部791のシフト動作によって伸張画像データSD<sub>2n-1</sub>をオーバードライブ演算回路16に順次出力し、オーバードライブ演算回路16において伸張後の現在の画像データSD<sub>1n</sub>との比較を行う。オーバードライブ演算回路16が outputする補正画像データDd<sub>n</sub>は、シフトレジスタ部791に保持される。つまり、シフトレジスタ部791から1フレーム前の画像データSD<sub>2n-1</sub>をオーバードライブ演算回路16に出力する度に、オーバードライブ演算回路16から補正画像データDd<sub>n</sub>がシフトレジスタ部791に入力されることになる。これを1ライン分繰り返すことにより、シフトレジスタ部791が表示用の画像データによって書き換えられることになる。このように1ライン分の表示用の画像データが得られると、画像データを表示ラッチ部592に転送して、液晶パネル4を駆動する。40

#### 【0064】

一方、静止画表示を行う場合など、オーバードライブ処理を行わない場合は、第2伸張回路75からシフトレジスタ部791に伸張後の画像データSD<sub>2n-1</sub>を転送し、この50

画像データ S D 2<sub>n-1</sub> をシフトレジスタ部 791 から表示ラッチ部 592 に転送して、液晶パネル 4 を駆動する。なお、動画と静止画でのシフトレジスタ部 791 の出力先の切り替えは、命令制御回路 10 から出力される動画・静止画切り替え信号 S 1 をデータ線駆動回路 79 に入力し、静止画の場合にはシフトレジスタ部 791 をオーバードライブ演算回路 16 に接続しないよう構成すればよい。

【0065】

このように構成することにより、発明の実施の形態 3 に示したコントローラ・ドライバ 3 と同様に、メモリアクセス回数を抑えることにより消費電力を低減でき、さらに、静止画表示を行う場合には、シフトレジスタ部 791 のシフト動作も必要ないことから、コントローラ・ドライバ 3 に比べて静止画表示を行う際の消費電力をさらに低減することができる。さらに、オーバードライブ演算回路 16 を動作させることなく静止画表示を行うことができるため、静止画表示を行う際の消費電力を低減することができる。また、静止画表示の際にオーバードライブ演算回路 16 から誤った補正画像データが出力されないため、正しい静止画表示を行うことができる。

10

【0066】

なお、上述した発明の実施の形態 1 乃至 4 では、コントローラ・ドライバ 1 乃至 4 にゲート線駆動回路 6 を含まないものとして説明したが、このような構成は一例である。コントローラ・ドライバ 1 乃至 4 にゲート線駆動回路 6 を含んで構成される場合もあり、さらに、電源回路等を含んで構成されることもあるが、このように構成されたコントローラ・ドライバであっても、本発明の作用、効果を達成可能である。

20

【図面の簡単な説明】

【0067】

【図 1】発明の実施の形態 1 にかかるコントローラ・ドライバ 1 の構成図である。

【図 2】オーバードライブ演算回路 16 の構成図である。

【図 3】オーバードライブ演算回路 16 の動作を説明する図である。

【図 4】画像圧縮方法の一例を説明する図である。

【図 5】画像圧縮方法の一例を説明する図である。

【図 6】本発明の課題を説明する図である。

【図 7】発明の実施の形態 1 における圧縮誤差の関係を説明する図である。

【図 8】発明の実施の形態 2 にかかるコントローラ・ドライバ 2 の構成図である。

30

【図 9】コントローラ・ドライバ 2 における画像データの流れを示す図である。

【図 10】コントローラ・ドライバ 2 のタイミングチャートである。

【図 11】発明の実施の形態 3 にかかるコントローラ・ドライバ 3 の構成図である。

【図 12】コントローラ・ドライバ 3 の動作を説明する図である。

【図 13】発明の実施の形態 4 にかかるコントローラ・ドライバ 4 の構成図である。

【図 14】従来のコントローラ・ドライバ 8 の構成図である。

【符号の説明】

【0068】

1、2、3、4 コントローラ・ドライバ

10 命令制御回路

40

11 第 1 圧縮回路

12 第 2 圧縮回路

13、23、53 画像メモリ

14 第 1 伸張回路

15 第 2 伸張回路

16 オーバードライブ演算回路

19、59、79 データ線駆動回路

591、791 シフトレジスタ部

R2 迂回経路

【図1】

【図2】

【図3】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(51)Int.Cl.

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 3 2 B |

| G 0 9 G | 3/20 | 6 4 1 G |

| G 0 9 G | 3/20 | 6 4 1 P |

(56)参考文献 特開2003-202845 (JP, A)

特開2003-167555 (JP, A)

特開2001-346131 (JP, A)

特開2005-242026 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |           |   |         |

|---------|-----------|---|---------|

| G 0 9 G | 3 / 0 0   | - | 3 / 3 8 |

| G 0 2 F | 1 / 1 3 3 |   |         |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 控制器驱动器，使用该液晶显示器的液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP4743837B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 公开(公告)日 | 2011-08-10 |

| 申请号            | JP2005006288                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2005-01-13 |

| [标]申请(专利权)人(译) | NEC电子股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 申请(专利权)人(译)    | NEC电子公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 瑞萨电子公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 降旗弘史<br>能勢崇                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 降旗 弘史<br>能勢 崇                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| CPC分类号         | G09G3/3648 G09G3/2055 G09G2320/0252 G09G2320/0261 G09G2320/0285 G09G2320/0613<br>G09G2340/02 G09G2340/16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号          | G09G3/36 G02F1/133.575 G09G3/20.612.U G09G3/20.621.F G09G3/20.631.R G09G3/20.632.B<br>G09G3/20.641.G G09G3/20.641.P H04N5/70.A                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 2H093/NA53 2H093/NA58 2H093/NC13 2H093/NC15 2H093/NC29 2H093/NC50 2H093/NC59 2H093<br>/NC62 2H093/ND03 2H093/ND06 2H093/ND32 2H093/ND39 2H193/ZD23 2H193/ZD29 5C006/AA12<br>5C006/AA16 5C006/AA17 5C006/AC11 5C006/AC21 5C006/AF03 5C006/AF04 5C006/AF26 5C006<br>/AF44 5C006/AF45 5C006/AF46 5C006/BB16 5C006/BC16 5C006/BF02 5C006/BF08 5C006/FA12<br>5C006/FA44 5C058/AA12 5C058/BA07 5C058/BB03 5C080/AA10 5C080/BB05 5C080/DD02 5C080<br>/DD08 5C080/DD25 5C080/EE19 5C080/EE29 5C080/FF11 5C080/GG10 5C080/GG11 5C080/GG15<br>5C080/GG17 5C080/JJ01 5C080/JJ02 5C080/JJ04 5C080/KK07 5C080/KK47 |         |            |

| 审查员(译)         | 武田 悟                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | JP2006195151A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

## 摘要(译)

要解决的问题：提供一种控制器驱动器，当使用压缩图像数据进行过驱动处理时，该控制器驱动器可以精确地控制施加到液晶面板上的电压。

解决方案：控制器驱动器1设置有压缩图像数据D <SB> n </SB>；以产生压缩图像数据CD1 <SB> n </SB>；的第一压缩电路11，产生压缩的第二压缩电路12图像数据CD2 <SB> n </SB>；和图像存储器13，其可以存储相当于至少一帧的压缩图像数据CD2 <SB> n </SB>。此外，控制器驱动器1设置有过驱动计算电路16，其产生校正图像数据Dd <SB> n </SB>，其中校正图像数据D <SB> n </SB>；或数据CD1 <SB> n </SB>；的灰度值，来自压缩图像数据CD1 <SB> n </SB>；或数据CD2 <SB> n </SB>；的扩展数据和压缩图像数据CD2 <SB> n </SB>；或数据CD1 <SB> n </SB>；的扩展数据。由第一压缩电路11进行的压缩处理是由第二压缩电路12进行的相同的压缩处理，而图像数据是比接收的图像数据D <SB> n </SB>；之前的一帧并且这些压缩过程随着时间的推移而改变。Z

|                                 |       | 次フレーム階調 |              |       |     |

|---------------------------------|-------|---------|--------------|-------|-----|

|                                 |       | ...     | 20~23        | 24~28 | ... |

| 現<br>フ<br>レ<br>ー<br>ム<br>階<br>調 | ...   | ...     | ...          | ...   | ... |

|                                 | 16~19 | ...     | 24           | 32    | ... |

|                                 | 20~23 | ...     | 現フレーム<br>階調値 | 30    | ... |

|                                 | ...   | ...     | ...          | ...   | ... |