(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4014895号

(P4014895)

(45) 発行日 平成19年11月28日(2007.11.28)

(24) 登録日 平成19年9月21日(2007.9.21)

(51) Int.CI.

F 1

|             |              |                  |             |              |

|-------------|--------------|------------------|-------------|--------------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/36</b>  |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | <b>G02F</b> | <b>1/133</b> |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  |

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  |

**G09G** 3/20 6 1 1 A**G09G** 3/20 6 1 2 U**G09G** 3/20 6 2 1 A

請求項の数 6 (全 24 頁) 最終頁に続く

(21) 出願番号

特願2002-57701 (P2002-57701)

(22) 出願日

平成14年3月4日(2002.3.4)

(65) 公開番号

特開2003-228347 (P2003-228347A)

(43) 公開日

平成15年8月15日(2003.8.15)

審査請求日 平成17年3月1日(2005.3.1)

(31) 優先権主張番号

特願2001-362175 (P2001-362175)

(32) 優先日

平成13年11月28日(2001.11.28)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 302020207

東芝松下ディスプレイテクノロジー株式会社

東京都港区港南4-1-8

(74) 代理人 100075812

弁理士 吉武 賢次

(74) 代理人 100088889

弁理士 橋谷 英俊

(74) 代理人 100082991

弁理士 佐藤 泰和

(74) 代理人 100096921

弁理士 吉元 弘

(74) 代理人 100103263

弁理士 川崎 康

最終頁に続く

(54) 【発明の名称】表示装置およびその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

縦横に配置された信号線および走査線と、

前記信号線および走査線に接続される複数の表示画素部と、を備えた表示装置において

、

前記複数の表示画素部に画素データを供給する表示制御部と、を備え、

前記表示画素部は、

対応する信号線に供給されるアナログ画素データまたはデジタル画素データに応じた表示を行う複数の副表示画素と、

対応する信号線にデジタル画素データが供給された場合に、該データを格納する複数の1ビットメモリと、を有し、

前記表示制御部は、前記アナログ画素データに基づいて前記複数の副表示画素に表示を行わせる場合には、画素データを色ごとに奇数画素および偶数画素に分けて順に、対応する信号線に順に供給し、前記デジタル画素データに基づいて前記複数の副表示画素に表示を行う場合には、前記デジタル画素データをビットごとに、対応する信号線に供給することを特徴とする表示装置。

## 【請求項 2】

前記表示制御部は、一つの前記表示画素ごとに、

デジタル画素データをラッチする複数のラッチ部と、

前記複数のラッチ部でラッチされたデータをアナログ画素データに変換するD/Aコン

10

20

バータと、

前記複数のラッチ部の出力のいずれか、または前記D/Aコンバータの出力を選択するマルチプレクサと、

前記マルチプレクサの出力を電流増幅するアンプと、

前記アンプの出力を対応する信号線に供給するセレクタと、を有することを特徴とする請求項1に記載の表示装置。

#### 【請求項3】

前記複数のラッチ部は、前記アナログ画素データに基づいて前記複数の副表示画素に表示を行う場合には、1本の信号線に供給されるアナログ画素データに対応するデジタル画素データの全ビットを同時にラッチし、

前記マルチプレクサは、前記D/Aコンバータから出力されたアナログ画素データを選択して前記アンプに供給することを特徴とする請求項2に記載の表示装置。

#### 【請求項4】

前記複数のラッチ部は、前記デジタル画素データに基づいて前記複数の副表示画素に表示を行う場合には、異なる複数の信号線に対応する複数のデジタル画素データの特定ビットをそれぞれラッチし、

前記マルチプレクサは、前記複数のラッチ部でラッチされたデジタル画素データを順に選択して前記アンプに供給することを特徴とする請求項2または3に記載の表示装置。

#### 【請求項5】

前記表示画素部は、

前記複数の1ビットメモリに格納されたデータのリフレッシュ動作を行うリフレッシュ部を有し、

前記表示画素部は、表示画面の画像に変更がない場合には、前記複数の1ビットメモリに格納されているデータを読み出して前記複数の副表示画素の表示を行うとともに、前記リフレッシュ部により周期的に前記複数の1ビットメモリをリフレッシュすることを特徴とする請求項1～4のいずれかに記載の表示装置。

#### 【請求項6】

前記表示制御部は、表示画面に表示される画像の一部のみに変更がある場合には、変更のある部分を含む部分的な前記アナログ画素データを対応する信号線に供給し、

前記表示画素部は、前記部分的なアナログ画素データに基づいて、対応する前記複数の副表示画素の表示を更新し、その他の表示領域については、前期複数の1ビットメモリに格納されているデータに基づいて前記複数の副表示画素の表示を行うことを特徴とする請求項1～5のいずれかに記載の表示装置。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、駆動回路を画素部と同一の絶縁基板上に一体形成する液晶表示装置に関し、特に、各画素ごとに画素データを格納するための複数の1ビットメモリを設ける液晶表示装置に関する。

##### 【0002】

##### 【従来の技術】

各画素ごとに、画素データを格納するメモリを設ける表示装置が提案されている。例えば、特開平9-258168には、メモリ内のキャパシタ素子により画素電圧を保持する構成が開示されている。

##### 【0003】

##### 【発明が解決しようとする課題】

メモリに画素データを格納しておけば、画面の書き換えを行わないときは、メモリに格納されたデータを読み出して表示すればよく、信号線駆動回路内のラッチ回路、D/Aコンバータおよびアナログバッファ等を動作させる必要がなくなるため、消費電力の低減を図ることができる。

10

20

30

40

50

**【0004】**

しかしながら、画素ごとにメモリを設けると、動画を表示するときに、頻繁にメモリの内容を更新しなければならず、消費電力が増えてしまう。また、メモリは対向電極や画素電極の下方に形成されるため、メモリ内のキャパシタ素子が対向電極や画素電極と容量結合を起こし、キャパシタ素子の両端電圧が対向電極や画素電極の電位変動の影響を受けやすくなる。

**【0005】**

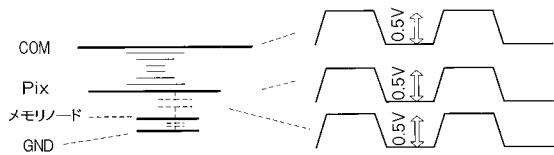

図28は対向電極および画素電極とメモリを構成するキャパシタ素子の両端電極との位置関係を概略的に示す図である。図示のように、対向電極の電位が変動すると、その影響で画素電極の電位も変動し、それに応じてメモリを構成するキャパシタ素子の上側電極の電位も変動してしまう。10

**【0006】**

キャパシタ素子の下側電極は接地されているため、キャパシタ素子の上側電極の電位が変動すると、キャパシタ素子の両端電圧が変化してしまい、この変化が色の変化となって現れる。すなわち、色むら等の不具合の要因になる。

**【0007】**

このような問題を回避する手法として、図29に示すように、キャパシタ素子の接地電極を他の電極よりも上方に配置することが考えられる。ところが、このようにしても、対向電極や画素電極の電位変動に伴って接地端子の電位が変動してしまい、結果としてキャパシタ素子の両端電極が変化してしまう。20

**【0008】**

本発明は、このような点に鑑みてなされたものであり、その目的は、消費電力を低減できる表示装置を提供することにある。

**【0009】**

また、本発明の他の目的は、画素ごとに設けられる1ビットメモリの両端電圧の変動を抑制することができる液晶表示装置を提供することにある。

**【0010】**

また、本発明のほかの目的は、制御配線、電源線、TFT素子および容量素子を効果的効率的に集積するための、画素内回路構成を提供することにある。

**【0011】**

本発明の一態様によれば、縦横に配置された信号線および走査線と、前記信号線および走査線に接続される複数の表示画素部と、を備えた表示装置において、前記複数の表示画素部に画素データを供給する表示制御部と、を備え、前記表示画素部は、対応する信号線に供給されるアナログ画素データまたはデジタル画素データに応じた表示を行う複数の副表示画素と、対応する信号線にデジタル画素データが供給された場合に、該データを格納する複数の1ビットメモリと、を有し、前記表示制御部は、前記アナログ画素データに基づいて前記複数の副表示画素に表示を行わせる場合には、画素データを色ごとに奇数画素および偶数画素に分けて順に、対応する信号線に順に供給し、前記デジタル画素データに基づいて前記複数の副表示画素に表示を行う場合には、前記デジタル画素データをビットごとに、対応する信号線に供給することを特徴とする表示装置が提供される。3040

**【0014】****【発明の実施の形態】**

以下、本発明に係る表示装置について、図面を参照しながら具体的に説明する。

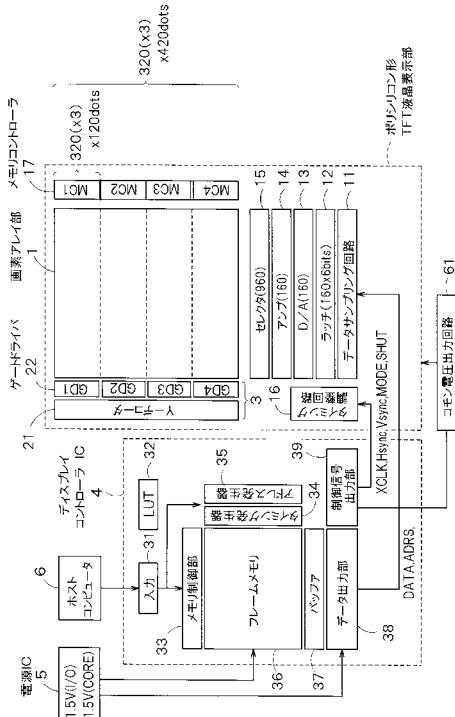

**(第1の実施形態)**

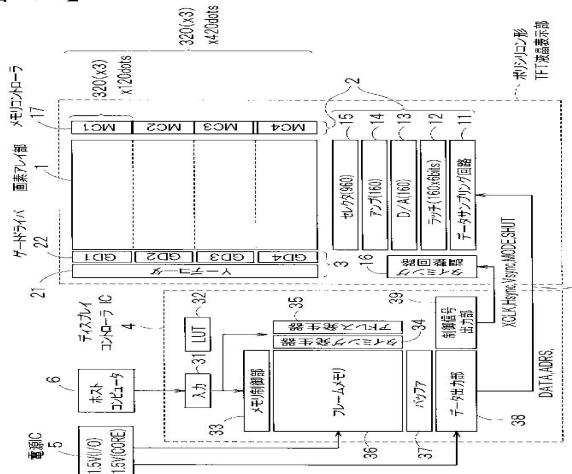

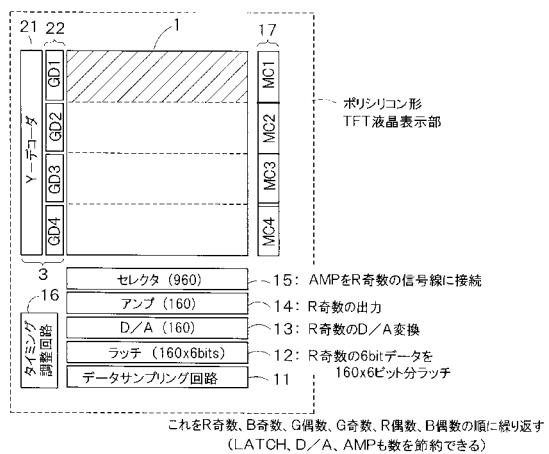

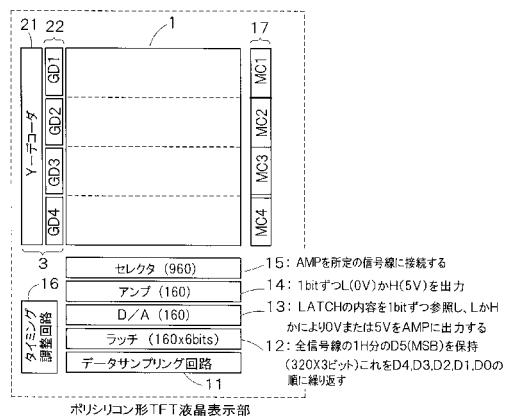

図1は本発明に係る表示装置の第1の実施形態である液晶表示装置の概略構成を示すブロック図である。図1の液晶表示装置は、信号線および走査線が縦横に配置され複数の画素が形成された画素アレイ部1と、信号線を駆動する信号線駆動回路2と、走査線を駆動する走査線駆動回路3と、ディスプレイ・コントローラIC4と、電源IC5等により構成され、ホストコンピュータ6から供給された画素データの表示を行う。

**【0015】**

画素アレイ部1、信号線駆動回路2および走査線駆動回路3からなる液晶表示部7は、絶縁基板上に例えばポリシリコン形TFTを用いて形成され、ディスプレイ・コントローラIC4と電源IC5は同一の絶縁基板上にCOG(Chip On Glass)により実装されている。なお、ディスプレイ・コントローラIC4に内蔵された回路を絶縁基板上にポリシリコン形TFTを用いて形成してもよい。

#### 【0016】

信号線駆動回路2は、ディスプレイ・コントローラIC4からビデオバスL1を介して供給される画素データをサンプリングするデータサンプリング回路11と、データサンプリング回路11でサンプリングしたデータをラッチするラッチ回路12と、ラッチされたデータをアナログ電圧に変換するD/Aコンバータ(D/A)13と、D/A13の出力を増幅するアンプ14と、アンプ14の出力を信号線に振り分けるセレクタ15と、信号線駆動回路2内の各部のタイミング制御を行うタイミング調整回路16と、画素アレイ部1へのデータの書き込み制御を行うメモリコントローラ17とを有する。10

#### 【0017】

走査線駆動回路3は、Y-デコーダ21と、4つのゲートドライバ22とを有する。画素アレイ部1は例えば、総画素数 $320(\times 3) \times 480$ であり、表示領域は上下で四分割され、各ブロックは $320(\times 3) \times 120$ 画素を有する。各ブロック内の走査線はそれぞれ対応するゲートドライバ22が駆動する。

#### 【0018】

ディスプレイ・コントローラIC4は、入力部31と、ルックアップテーブル(LUT)32と、メモリ制御部33と、タイミング発生器34と、アドレス発生器35と、フレームメモリ36と、バッファ37と、データ出力部38と、制御信号出力部39とを有する。20

#### 【0019】

電源IC5は、DC/DCコンバータや対向電極駆動回路などを内蔵する。電源IC5は、不図示の外部電源から3Vの駆動電圧VDDと接地電圧VSSの供給を受ける。

#### 【0020】

画素アレイ部1を構成する各表示画素は、6つの副表示画素部42を有し、各副表示画素部42の面積比率は、32:16:8:4:2:1である。このように、面積の異なる6つの副表示画素部42を設けることにより、 $2^6 = 64$ 階調表示が実現される。30

#### 【0021】

副表示画素部42と対向電極との間には、液晶層が封止されて液晶容量C1が形成されている。液晶層の材料である液晶は、高速応答のものではなく、通常のTN液晶が用いられる。

#### 【0022】

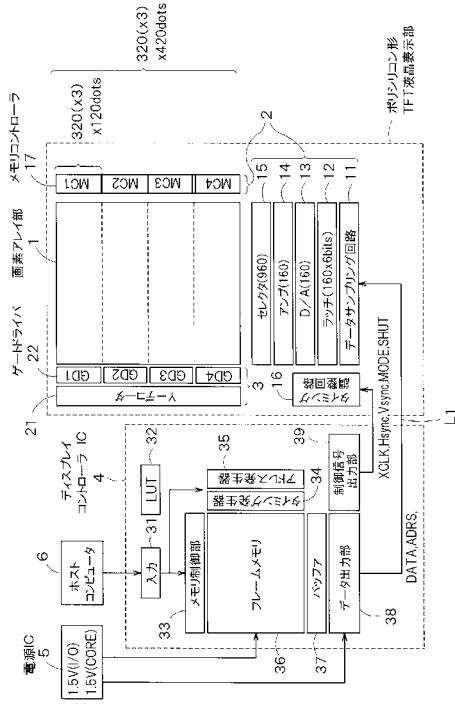

図2は画素アレイ部1内の1表示画素の詳細構成を示す回路図である。図示のように、1表示画素には、信号線に接続される画素TFT41と、6つの副表示画素部42と、6つの1ビットメモリ(DRAM)43と、これらDRAM43に対してリフレッシュ動作を行うリフレッシュ回路44と、副表示画素部42とリフレッシュ回路44の間に接続される極性反転回路45とが設けられている。40

#### 【0023】

副表示画素部42のそれぞれは、それぞれ異なる面積比率の副表示画素電極と対向電極との間に形成される液晶容量C1と、補助容量C2と、転送用TFT46とを有する。

#### 【0024】

DRAM43はそれぞれ、読み書き制御トランジスタ47とキャパシタ素子C3とを有する。リフレッシュ回路44は、直列接続される2つのインバータIV1, IV2と、初段のインバータIV1の入力端子と後段のインバータIV2の出力端子との間に接続される帰還TFT48とを有する。初段のインバータIV1の出力端子と後段のインバータIV2の入力端子は極性反転回路45に接続されている。リフレッシュ回路44は、電源電圧Vdd(5V)と接地電圧Vss(0V)を用いて、DRAM43に格納されているデータをリフレッシュ50

シユする。

**【 0 0 2 5 】**

極性反転回路 4 5 は、リフレッシュ回路 4 4 内のインバータ I V 1 , I V 2 のいずれか一方の出力を選択する選択トランジスタ 4 9 , 5 0 を有する。これら選択トランジスタ 4 9 , 5 0 は、図 1 のメモリコントローラ 1 7 からの極性制御信号 SPOLA, SPOLB に基づいて、オン・オフ制御される。

**【 0 0 2 6 】**

本実施形態の液晶表示装置は、面積階調方式により、 $2^6 = 64$  階調の表示を行うことができ、かつ、アナログ画素データに基づく表示とデジタル画素データに基づく表示とを切り替えて行うことができる。具体的には、動画を表示する場合には、アナログ画素データに基づく表示を行い、静止画を表示する場合には、デジタル画素データに基づく表示を行う。10

**【 0 0 2 7 】**

以下では、アナログ画素データによる書き込みをアナログ書き込みと呼び、デジタル画素データによる書き込みをデジタル書き込みと呼ぶ。

**【 0 0 2 8 】**

アナログ書き込みを行うか、デジタル書き込みを行うかは、ディスプレイ・コントローラ I C 4 が判断する。ディスプレイ・コントローラ I C 4 は、C P U 6 からのフレームメモリ 3 6 への書き込みを監視しており、一定期間にわたってフレームメモリ 3 6 の内容が変化しなければ、静止画表示と判断して、次の 1 フレームではデジタル書き込みを行う。その後、ディスプレイ・コントローラ I C 4 からのデータ出力は停止される。フレームメモリ 3 6 の内容が変化すると、次のフレームから再びディスプレイ・コントローラ I C 4 からのデータ出力が再開され、アナログ書き込みを行う。20

**【 0 0 2 9 】**

静止画を表示する場合、各画素のDRAM 4 3 に格納されたデータに基づいて表示更新を行うため、信号線駆動回路 2 等の周辺回路を駆動させる必要がなく、消費電力の低減が図れる。。

**【 0 0 3 0 】**

従来の液晶表示装置では、ディスプレイ・コントローラ I C 4 に映像データ D / A 1 3 が入力されない場合でも、ディスプレイ・コントローラ I C 4 は常に 1 フレーム分の画素データを出力していた。これに対して、本実施形態では、各画素がメモリを内蔵しているため、ディスプレイ・コントローラ I C 4 からの一切の映像データ D / A 1 3 の出力を停止し、かつ信号線駆動回路 2 の動作を停止させても、表示を継続できる。30

**【 0 0 3 1 】**

また、本実施形態の液晶表示装置は、表示画面の一部の領域のみアナログ書き込みを行い、その他の領域はデジタル書き込みを行うことができる。あるいは、各画素内のメモリに基づく画素電極の極性反転動作のみで表示を継続保持できる。したがって、表示画面の部分的な書き換えが可能になる。これにより、無駄に信号線駆動回路 2 等を駆動する必要がなくなり、消費電力のさらなる低減が図れる。

**【 0 0 3 2 】**

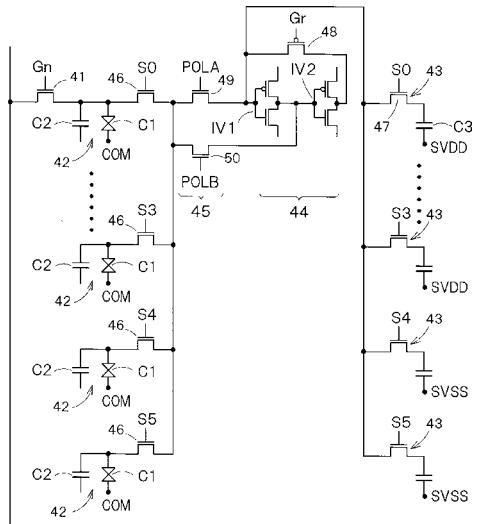

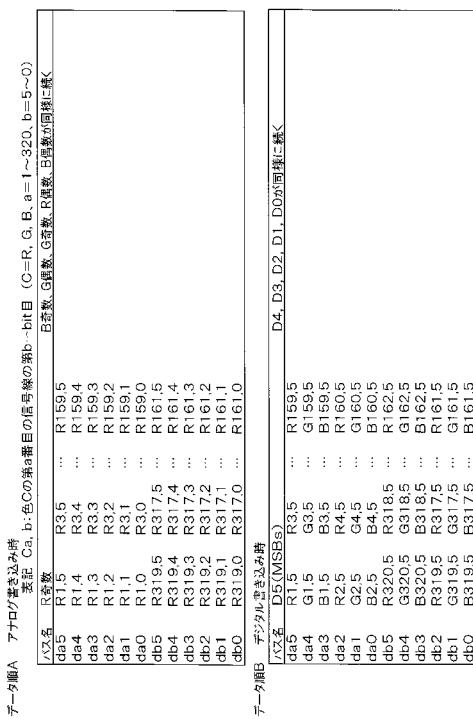

本実施形態では、アナログ書き込み時とデジタル書き込み時で、信号線駆動回路 2 の動作が異なっている。図 3 はラッチ回路 1 2 と D / A ( DAC ) 1 3 の詳細な接続関係を示す図である。実際には、図 3 の回路が 1 6 0 個設けられている。40

**【 0 0 3 3 】**

アナログ書き込み時は、1 本の信号線に供給されるデジタル画素データの 6 ビットがそれぞれ 6 個のラッチ回路 1 2 でラッチされる。D / A 1 3 は、これら 6 個のラッチ回路 1 2 でラッチされた 6 ビット分のデータをアナログ画素電圧に変換する。D / A 1 3 の後段に配置されるマルチプレクサ 5 1 は、D / A 1 3 から出力されたアナログ画素電圧をアンプ 1 4 に供給する。アンプ 1 4 は、D / A 1 3 からのアナログ画素電圧を電流增幅して、セレクタ 1 5 を介して、対応する信号線に供給する。50

**【0034】**

一方、デジタル書き込み時は、6本の信号線に供給される6種類のデジタル画素データの特定ビット（例えば、まず最初は最上位ビット）がそれぞれ6個のラッチ回路12でラッチされる。マルチプレクサ51は、これら6個のラッチ回路12でラッチされた6種類のデータを1種類ずつ選択してアンプ14に供給する。セレクタ15は、アンプ14の出力を対応する信号線に供給する。この動作を順に繰り返す。

**【0035】**

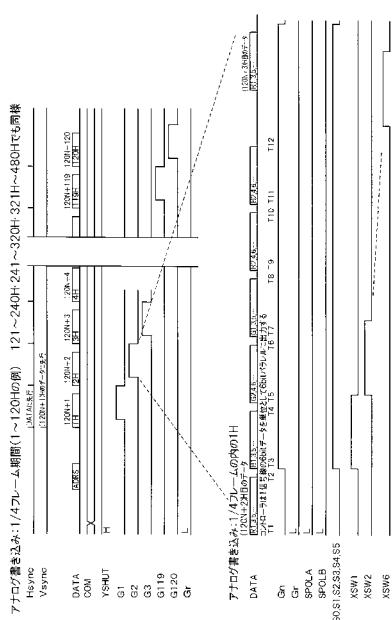

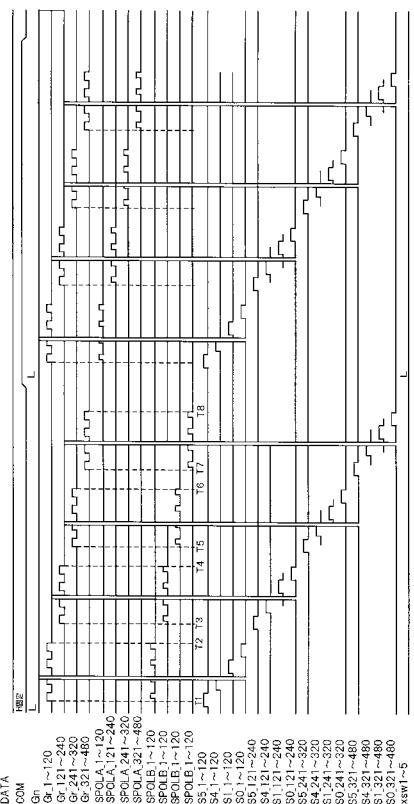

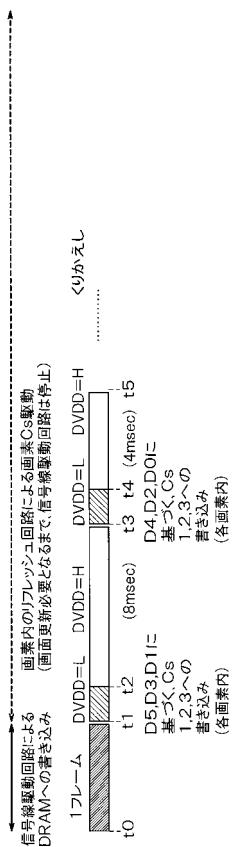

次に、図1の液晶表示装置の動作を説明する。図4はアナログ書き込み時のタイミング図、図5はアナログ書き込み時の液晶表示装置の動作を説明する図である。

**【0036】**

図4のタイミング図は、図5の斜線部で示す1/4フレーム期間の動作タイミングを示している。図示のように、1水平ラインごとに順に書き込みが行われる。図4の下部には、2番目の水平ラインの詳細な書き込みタイミングが図示されている。

**【0037】**

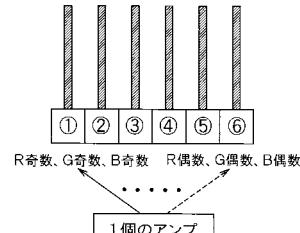

アナログ書き込み時は、図4に示すように、1赤色の1水平ライン分の奇数画素データ（時刻T1～T2）、2青色の1水平ライン分の奇数画素データ（時刻T3～T4）、3緑色の1水平ライン分の偶数画素データ（時刻T5～T6）、4緑色の1水平ライン分の奇数画素データ（時刻T7～T8）、5赤色の1水平ライン分の偶数画素データ（時刻T9～T10）、6青色の1水平ライン分の偶数画素データ（時刻T11～T12）の順に書き込みが行われる。

**【0038】**

上記の1～6が書き込み終わると、次の水平ラインについて、同様の処理が繰り返される。

**【0039】**

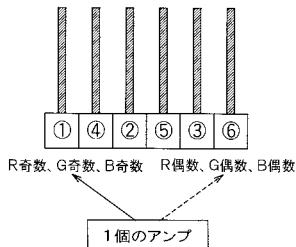

アナログ書き込みの場合、図2の極性反転回路45内の2つの選択トランジスタ49,50はいずれもオフに設定される。したがって、DRAM43にはデータは書き込まれない。また、アナログ書き込み時は、図2の信号S0～S5は常にハイレベルに設定され、すべての転送用TFT46がオンに設定される。この状態で、信号線に上述した1～6のアナログ画素データが順に供給されると、図2に図示されたすべての液晶容量C1と補助容量C2に、アナログ画素電圧に応じた電荷が蓄積される。各色とも64階調の表示が実現される。

**【0040】**

図1の液晶表示装置は、6本の信号線に対して1個の割合でD/A13とアンプ14を有する。したがって、アナログ書き込みの場合には、アンプ14の後段のセレクタ15は図6の1～6の順に選択を切り替える。セレクタ15の選択を切り替える信号XSW1～XSW6のタイミングは図5のようになる。

**【0041】**

このように、アンプ14の後段にセレクタ15を設けることにより、アンプ14とD/A13コンバータを複数の信号線で共用でき、回路規模の削減と消費電力の低減が図れる。

**【0042】**

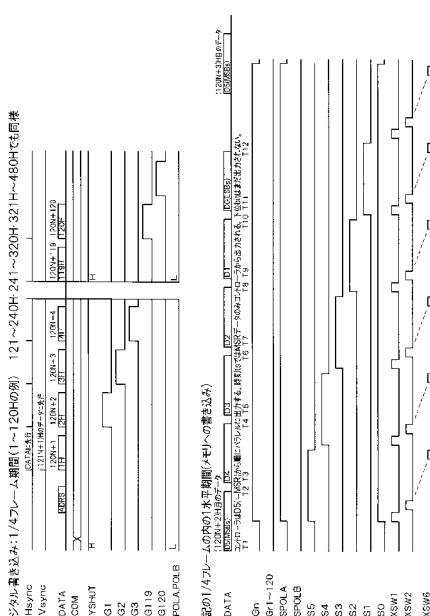

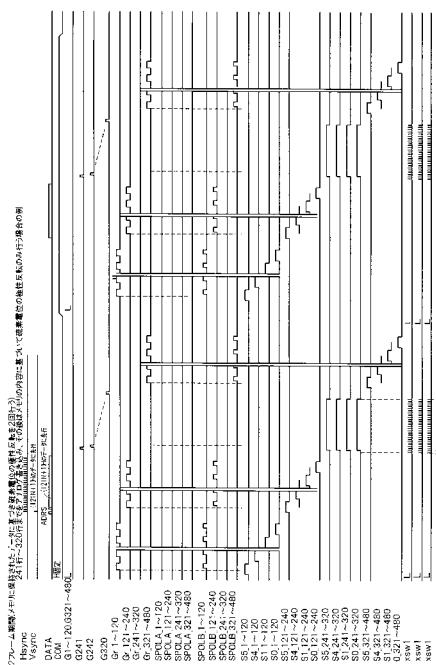

次に、デジタル書き込みについて説明する。図7はデジタル書き込み時のタイミング図、図8はデジタル書き込み時の液晶表示装置の動作を説明する図である。

**【0043】**

図7は1/4フレーム期間のタイミングを示し、そのうちの1水平ラインの書き込みタイミングが同図の下部に示されている。

**【0044】**

デジタル書き込み時は、図7に示すように、(1)1水平ライン分の全画素データの最上位ビットD5（時刻T1～T2）、(2)1水平ライン分の全画素データのビットD4（時刻T3～T4）、(3)1水平ライン分の全画素データのビットD3（時刻T5～T6）、(4)1水平ライン分の全画素データのビットD2（時刻T7～T8）、(5)1水平ライン分の

10

20

30

40

50

全画素データのビットD1(時刻T9～T10)、(6)1水平ライン分の全画素データのビットD0(時刻T11～T12)の順に書き込みが行われる。

#### 【0045】

上記の(1)～(6)のいずれにおいても、図9に示すように、赤色の奇数画素、緑の奇数画素、青の奇数画素、赤色の偶数画素、緑の偶数画素および青の偶数画素の順に書き込みが行われる。

#### 【0046】

デジタル書き込み時は、図7に示すように、信号S0は常にハイレベルに設定されるので、転送用TFT46は常にオン状態である。この状態で、信号S5～S1が順にオンに設定される。

10

#### 【0047】

まず、信号S5がオンに設定される。これにより、信号S0およびS5が入力される転送用TFT46と、同じく信号S0およびS5が入力されるDRAM43内の読み書き制御トランジスタ47がオンする。このとき、信号線には赤色奇数画素データの最上位ビットデータD5が供給され、このデータは対応するDRAM43に格納されるとともに、対応する副表示画素の液晶容量C1に電荷が蓄積される。

#### 【0048】

続いて、信号S5はオンのままで、隣接する信号線に、緑色奇数画素データの最上位ビットデータD5が供給される。これにより、この信号線に対応したDRAM43にこのデータが格納されるとともに、対応する副表示画素の液晶容量C1に対応する電荷が蓄積される。

20

#### 【0049】

同様に、信号S5をオンのままにして、青の奇数画素、赤色の偶数画素、緑の偶数画素および青の偶数画素の各データの最上位ビットデータD5が順に対応する信号線に供給される。

#### 【0050】

次に、信号S5の代わりに信号S4がオンに設定される。これにより、信号S0およびS4が入力される転送用TFT46と、同じく信号S0およびS4が入力されるDRAM43内の読み書き制御トランジスタ47がオンする。このとき、信号線には赤色奇数画素データのビットデータD4が供給され、このデータは対応するDRAM43に格納されるとともに、対応する液晶容量C1に対応する電荷が蓄積される。

30

#### 【0051】

続いて、信号S4はオンのままで、緑色奇数画素、青の奇数画素、赤色の偶数画素、緑の偶数画素および青の偶数画素の各データのビットデータD4が順に対応する信号線に供給される。

#### 【0052】

次に、同様にして、信号S3～S1が順にオンに設定され、画素データのビットデータD3～D1が順に書き込まれる。

#### 【0053】

次に、信号S0だけがオンに設定され、信号S0が入力されるDRAM43に最下位ビットデータD0が書き込まれ、かつ対応する電荷が液晶容量C1に蓄積される。

40

#### 【0054】

上述したように、本実施形態では、アナログ書き込みとデジタル書き込みで、画素データの書き込み順序を変えている。その理由は、例えばデジタル書き込み時に、アナログ書き込みと同じ順序で書き込むと、転送用TFT46を頻繁にオン・オフさせなければならず、消費電力が増えるためである。これに対して、上述した手法でデジタル書き込みを行えば、デジタル画素データの特定のビットについて、すべての色を連続して書き込むため、その間は転送用TFT46をオン・オフさせなくて済み、転送用TFT46のオン・オフ回数を減らすことができ、消費電力の低減が図れる。

#### 【0055】

アナログ書き込みとデジタル書き込みでのデータの書き込み順序をまとめると、図10の

50

ようになる。

**【0056】**

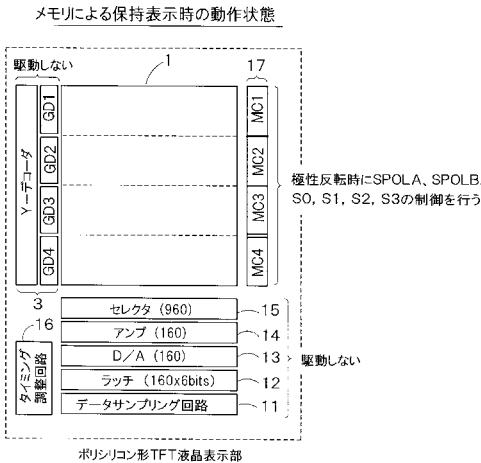

次に、DRAM43に格納されたデータの保持表示、すなわち静止画表示を行う場合について説明する。図11は静止画表示時のタイミング図、図12は静止画表示時の液晶表示装置の動作を説明する図である。

**【0057】**

静止画表示の場合、図12に示すように、信号線駆動回路2の一部、具体的にはデータサンプリング回路11、ラッチ回路12、D/A13、アンプ14およびセレクタ15は動作しない。静止画表示の場合、図10に示すように、信号S5～S0が順に一定期間ずつハイレベルになる。信号S5～S0がハイレベルの間に、リフレッシュ回路44が動作してリフレッシュ動作が行われる。

10

**【0058】**

詳しく説明すると、信号S5をハイレベルにした状態でこの信号線に対応するDRAM43のデータがリフレッシュ回路44に導かれる。そして信号Grがハイレベルになると2つのインバータIV1とIV2とがループ上に接続され、このDRAM43をリフレッシュする。また、極性反転回路45を構成する2つのトランジスタ49,50のいずれか一方がオンし、DRAM43に格納されているデータまたはその反転データに応じた電荷が信号S5に対応する液晶容量C1に蓄積される。

**【0059】**

次に、信号S4をハイレベルにした状態でこの信号線に対応するDRAM43のデータがリフレッシュ回路44に導かれる。そして信号Grがハイレベルになると2つのインバータIV1とIV2とがループ上に接続され、前記DRAMをリフレッシュする。また、極性反転回路45を構成する2つのトランジスタのいずれか一方がオンし、DRAM43に格納されているデータまたはその反転データに応じた電荷が信号S4に対応する液晶容量C1に蓄積される。

20

**【0060】**

これと同じ動作をS3, S2, S1, S0と繰り返すことにより、全ての液晶容量の極性反転が完了する。

**【0061】**

静止画表示は、図12に示すように、表示画面を上下方向に4分割した各画素ブロックごとに行われる。具体的には、図11に示すように、まず1～120ラインの静止画表示が行われた(時刻T1～T2)後、121～240ラインの静止画表示(時刻T3～T4)、次に241～360ラインの静止画表示(時刻T5～T6)、最後に361～480ラインの静止画表示(時刻T7～T8)が行われる。

30

**【0062】**

その後、次のフレームでは、コモン電圧を反転させて、同様の処理が行われる。

**【0063】**

このように、静止画表示の場合、DRAM43に格納されたデータを読み出して表示処理を行うため、データサンプリング回路11、ラッチ回路12、D/A13、アンプ14およびセレクタ15を動作させなくて済み、消費電力の低減が図れる。

40

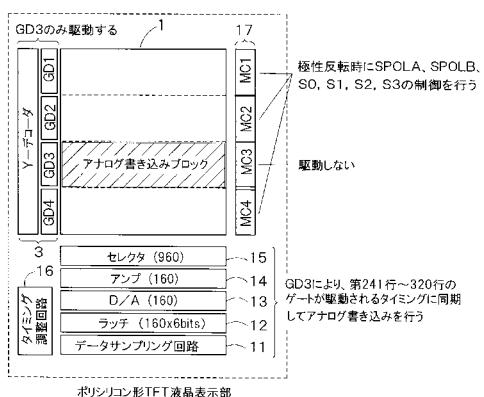

**【0064】**

次に、表示画面の一部の領域のみアナログ書き込みを行う例を説明する。図13はこの場合のタイミング図、図14は一部の領域のみアナログ書き込みを行う場合の液晶表示装置の動作を説明する図である。図13は図14の斜線部で示すように241～320ラインについてのみアナログ書き込みを行い、その他はDRAM43の内容を読み出して極性反転動作を行う例を示している。

**【0065】**

この場合、走査線駆動回路3が241～320ラインの画素TFT41のゲートを駆動するタイミングに同期させてアナログ書き込みを行う(図13の時刻T1～T2)。それ以外の期間は、静止画表示と同様に、DRAM43に格納されたデータを120ライン単位で読

50

み出して液晶容量 C 1 に再書き込みを行う。

**【 0 0 6 6 】**

このように、本実施形態では、アナログ書き込みとデジタル書き込みを切り替えて行えるようにし、表示画面の一部領域のみアナログ書き込みを行い、他の領域はデジタル書き込みを行えるようにしたため、信号線駆動回路 2 内の D / A 1 3 等を無駄に動作なくて済み、消費電力の低減が図れる。

**【 0 0 6 7 】**

(第 2 の実施形態)

第 2 の実施形態は、DRAM 4 3 を構成するキャパシタ素子の両端電圧が画素電極の電圧やコモン電圧の変動を受けないようにしたものである。

10

**【 0 0 6 8 】**

図 1 5 は本発明に係る表示装置の概略構成を示すプロック図である。図 1 5 では、図 1 と共に通する構成部分には同一符号を付しており、以下では相違点を中心に説明する。

**【 0 0 6 9 】**

図 1 5 の液晶表示装置は、図 1 の構成に加えて、コモン電圧の波形整形を行うコモン電圧出力回路 6 1 を備えている。このコモン電圧出力回路 6 1 は、液晶表示部 6 やディスプレイ・コントローラ I C 4 とは別個の I C に内蔵される。

**【 0 0 7 0 】**

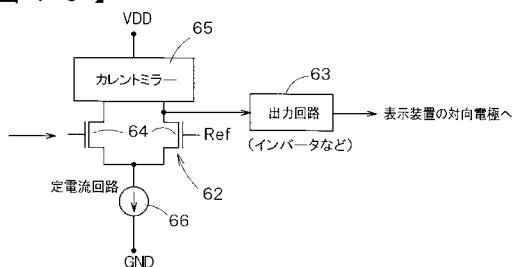

図 1 6 はコモン電圧出力回路 6 1 の詳細構成を示す回路図である。図示のように、コモン電圧出力回路 6 1 は、ディスプレイ・コントローラ I C 4 から供給される中間電圧と基準電圧 R e f との電位差に応じた信号を出力するオペアンプ 6 2 と出力回路 6 3 を有する。このオペアンプ 6 2 は、トランジスタ対 6 4 と、カレントミラー回路 6 5 と、定電流回路 6 6 とを有する。

20

**【 0 0 7 1 】**

定電流回路 6 6 は、ディスプレイ・コントローラ I C 4 からのバイアス信号に基づいて、電流を可変調整する。具体的には、アナログ書き込みの際は、定電流回路 6 6 に流れる電流を多くする。これにより、コモン電圧波形は急峻になる。また、DRAM 4 3 の内容に基づく保持表示の場合は、定電流回路 6 6 に流れる電流を少なくする。これにより、コモン電圧波形はなまる。

**【 0 0 7 2 】**

30

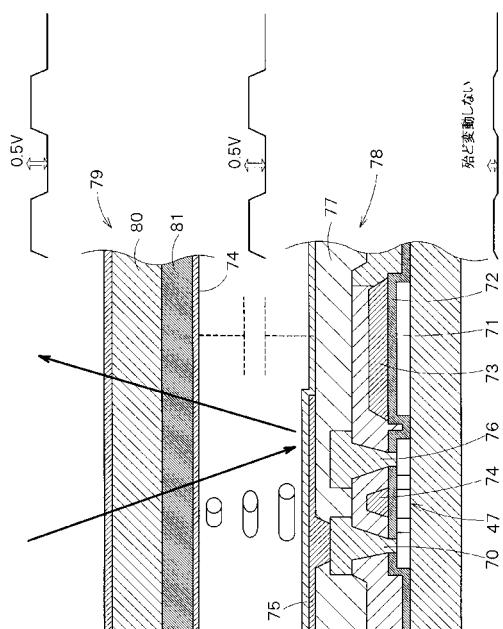

図 1 7 は第 2 の実施形態の液晶表示装置の断面構造を示す図である。図 1 7 の液晶表示装置は、第 1 の実施形態と同様に、各画素ごとに面積比率の異なる複数の副表示画素電極と DRAM 4 3 を有し、面積階調表示を行う。

**【 0 0 7 3 】**

DRAM 4 3 は、図 2 と同様に、読み書き制御トランジスタ 4 7 とキャパシタ素子 C 3 とで構成される。DRAM 4 3 を構成する一方の電極 7 1 は、読み書き制御トランジスタ 4 7 の活性層の材料と同じポリシリコンで形成され、その上面に酸化シリコンからなる絶縁層 7 2 を介して他方の電極 7 3 が形成されている。この他方の電極 7 3 は、接地レベルに設定される。

**【 0 0 7 4 】**

40

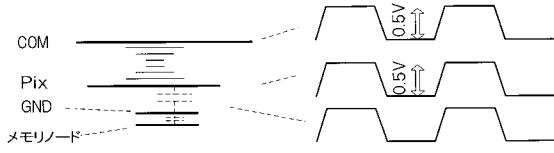

このように、接地レベルに設定される他方の電極 7 3 を対向電極 7 4 や画素電極 7 5 に近い側に配置する理由は、接地レベルに設定される電極の方が対向電極 7 4 や画素電極 7 5 の電位変動の影響を受けにくいためである。

**【 0 0 7 5 】**

読み書き制御トランジスタ 4 7 は、ガラス等の絶縁基板上にポリシリコンを活性層 7 1 として形成されている、活性層 7 1 の上面には酸化シリコンからなるゲート絶縁膜 7 2 が形成され、その上面に M o W 合金等からなるゲート電極 7 4 が形成されている。ゲート電極 7 4 の左右には酸化シリコンからなる層間絶縁膜を介してソースおよびドレイン電極 7 0 , 7 6 が形成されている。ソースおよびドレイン電極 7 0 , 7 6 の上面には、アクリル樹脂等からなる層間絶縁膜 7 7 が形成され、この上に A 1 からなる画素電極 7 5 が形成され

50

ている。

**【 0 0 7 6 】**

このような構造のアレイ基板 7 8 に対向配置される対向基板 7 9 は、ガラス基板 8 0 上に赤、青、緑のカラーフィルタ 8 1 が配置され、この上に I T O 等の透明電極からなる対向電極 7 4 が配置されて構成されている。

**【 0 0 7 7 】**

対向電極 7 4 に供給されるコモン電圧は、極性反転駆動のために、周期的に 0 V または 5 V になる。コモン電圧が 0 V から 5 V に、あるいは 5 V から 0 V に急激に変化すると、その影響で、DRAM 4 3 のキャパシタ素子の上側電極（接地電極）の電圧が変動するおそれがある。

10

**【 0 0 7 8 】**

そこで、本実施形態では、図 1 5 に示すコモン電圧出力回路 6 1 により、図 1 8 のようにコモン電圧の電圧波形をなまらせている。これにより、キャパシタ素子の上側電極の電圧変動が抑制され、キャパシタ素子の両端電圧も変動しなくなる。どのくらい鈍らせるかは表示装置の画面寸法や画素数、液晶材料、上側電極に電圧を供給する電源の電荷供給能力などに依存して異なるが、おおむね、コモン反転時の前記上側電極の電位変動ピーク値が、リフレッシュ回路のインバータのノイズマージン以下であるように設計するべきである。この条件のもとでは、キャパシタ素子の両端電圧が仮に変動したとしても、リフレッシュ回路により、論理レベルを誤ることなく、DRAM の記憶電圧をリフレッシュできるからである。

20

**【 0 0 7 9 】**

このように、第 2 の実施形態では、DRAM 4 3 のキャパシタ素子の接地電極を対向電極 7 4 に近い側に配置するとともに、対向電極 7 4 に供給されるコモン電圧の電圧波形をなまらせるようにしたため、キャパシタ素子の両端電圧が対向電極 7 4 や画素電極の電圧変動の影響を受けにくくなり、表示品質が向上する。

**【 0 0 8 0 】**

**( 第 3 の実施形態 )**

第 3 の実施形態は、デジタル画素データの複数ビットで一つの副画素を共用するものである。

**【 0 0 8 1 】**

30

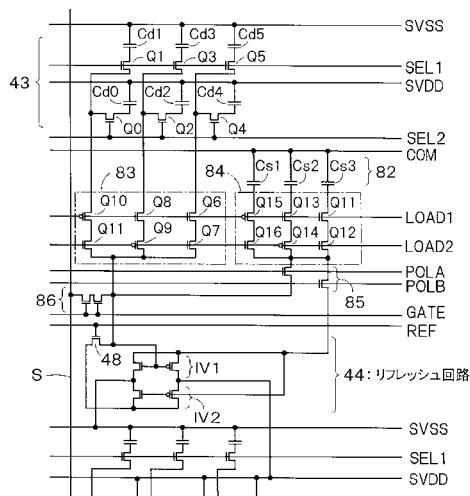

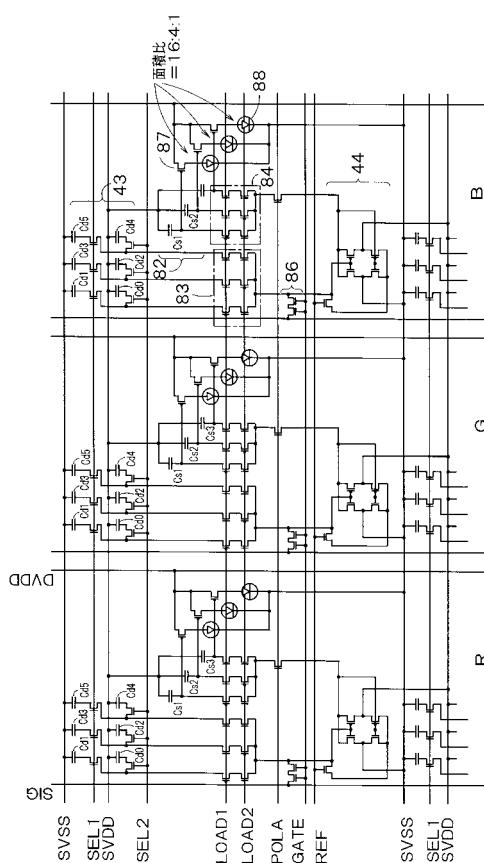

図 1 9 は本発明に係る表示装置の第 3 の実施形態における信号線駆動回路内の 1 画素分の回路構成を示す回路図であり、デジタル画素データのビット数が 6 ビットで、各画素が面積比 16:4:1 の 3 つの副表示画素を有する例を示している。実際には、図 1 9 の回路が R G B の各色ごとに一つずつ設けられ、これら 3 つの回路で 1 画素が構成される。なお、図 1 9 では、信号線駆動回路の特徴的でない部分は省略している。

**【 0 0 8 2 】**

図 1 9 の液晶表示装置は、デジタル画素データの各ビットに対応して設けられる 6 つの容量 C d0 , C d1 , C d2 , C d3 , C d4 , C d5 と各容量に接続されるトランジスタ Q 0 ~ Q 5 とを有する DRAM 4 3 と、DRAM 4 3 に記憶されたデジタル画素データを 1 ビットずつ順に保持するリフレッシュ回路 4 4 と、3 つの副表示画素のそれぞれに対応して設けられる 3 個の容量素子からなりリフレッシュ回路 4 4 で保持されたデータを記憶する蓄積容量部 8 2 と、DRAM 4 3 に記憶されたデジタル画素データをリフレッシュ回路 4 4 に伝送するか否かを切り替える第 1 の切替部 8 3 と、リフレッシュ回路 4 4 で保持されたデータを蓄積容量部 8 2 に伝送するか否かを切り替える第 2 の切替部 8 4 と、極性切替回路 8 5 と、信号線 S 上のデータを取り込むか否かを制御するデータ取込制御回路 8 6 と、を備えている。

40

**【 0 0 8 3 】**

蓄積容量部 8 2 は、DRAM 4 3 に記憶された 6 ビットのデジタル画素データを 2 回に分けてそれぞれ異なるタイミングで異なる期間ずつ記憶し、3 つの副表示画素は、対応する蓄積容量部 8 2 に記憶されたデータに応じた表示を行う。

**【 0 0 8 4 】**

50

リフレッシュ回路 4 4 は、縦続接続された 2 つのインバータ IV1, IV2 と、後段のインバータ IV2 の出力端子と前段のインバータ IV1 の入力端子との間に接続されるトランジスタスイッチ 4 8 とを有する。

#### 【 0 0 8 5 】

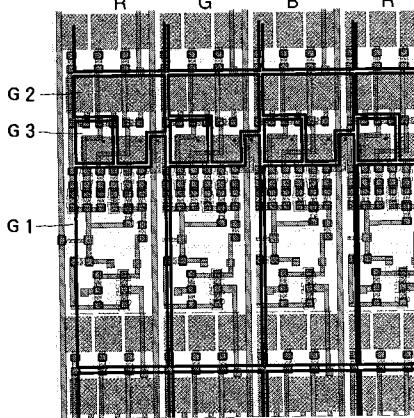

図 2 0 は本発明に係る表示装置の第 3 の実施形態における 1 画素分の平面レイアウト図である。図 2 0 では、画素電極 G1, G2, G3 を太線枠で表示している。図示のように、RGB の各色ごとに、16:4:1 の面積比の画素電極 G1, G2, G3 が設けられ、各画素電極 G1, G2, G3 は蓄積容量部 8 2 に接続されている。

#### 【 0 0 8 6 】

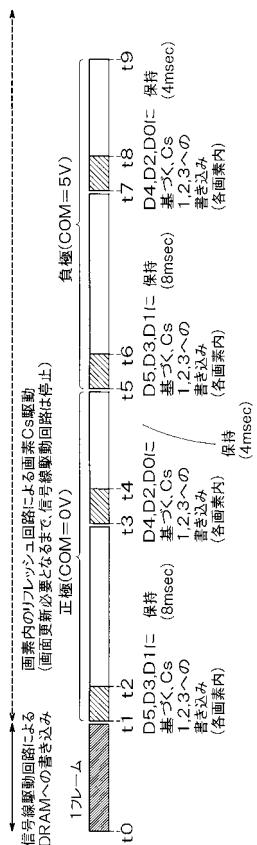

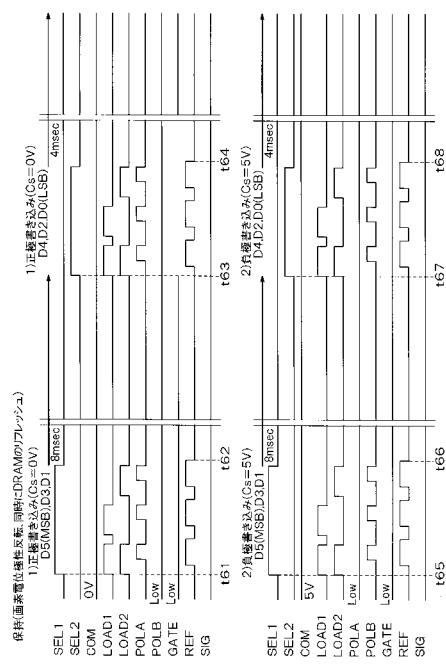

図 2 1 は本発明に係る表示装置の第 3 の実施形態における表示タイミング図である。図示のように、まず時刻 t 0 ~ t 1 では、1 フレーム分のデジタル画素データを DRAM 4 3 に記憶する。

10

#### 【 0 0 8 7 】

その後、時刻 t 1 ~ t 5 では、DRAM 4 3 に記憶されたデジタル画素データに基づく正極性データを奇数ビットと偶数ビットに分けて順に蓄積容量部 8 2 に記憶する。その後、時刻 t 5 ~ t 9 では、DRAM 4 3 に記憶したデータに基づく負極性データを奇数ビットと偶数ビットに分けて順に蓄積容量部 8 2 に記憶する。

#### 【 0 0 8 8 】

以降、画面に表示されるデータに変更がない限り、時刻 t 1 ~ t 9 の処理を繰り返して行う。

20

#### 【 0 0 8 9 】

以下では、時刻 t 1 ~ t 9 の処理を詳細に説明する。まず、時刻 t 1 ~ t 2 では、DRAM 4 3 に記憶された 1 フレーム分のデジタル画素データのうち、奇数ビット D5, D3, D1 のデータに対応する正極性データを蓄積容量部 8 2 に記憶する。

#### 【 0 0 9 0 】

その後、時刻 t 2 ~ t 3 では、蓄積容量部 8 2 に記憶されたデータを保持する。この期間は、奇数ビット D5, D3, D1 に応じた表示が行われる。なお、時刻 t 2 ~ t 3 の期間は、例えば 8 msec である。

#### 【 0 0 9 1 】

その後、時刻 t 3 ~ t 4 では、DRAM 4 3 に記憶された 1 フレーム分のデジタル画素データのうち、偶数ビット D4, D2, D0 のデータに対応する正極性データを蓄積容量部 8 2 に記憶する。その後、時刻 t 4 ~ t 5 では、蓄積容量部 8 2 に記憶されたデータを保持する。この期間は、偶数ビット D4, D2, D0 に応じた表示が行われる。なお、時刻 t 3 ~ t 4 の期間は、例えば 4 msec である。

30

#### 【 0 0 9 2 】

その後、時刻 t 5 ~ t 7 では、デジタル画素データの奇数ビット D5, D3, D1 に対応する負極性データを蓄積容量部 8 2 に記憶して表示を行い、時刻 t 7 ~ t 9 では、デジタル画素データの偶数ビット D4, D2, D0 に対応する負極性データを蓄積容量部 8 2 に記憶して表示を行う。

#### 【 0 0 9 3 】

このように、本実施形態では、1 フレーム分の 6 ビットデジタル画素データを奇数ビットと偶数ビットに分け、前半では奇数ビットの値に基づいて 8 msec の間表示を行い、後半では偶数ビットの値に基づいて 4 msec の間表示を行う。1 画素内の 3 つの画素電極の面積比は 16:4:1 なので、前半の面積 × 時間はそれぞれ  $16 \times 8$ 、 $4 \times 8$ 、 $1 \times 8$  になり、後半の面積 × 時間はそれぞれ、 $16 \times 4$ 、 $4 \times 4$ 、 $1 \times 4$  になり、これら計 6 組の比は順に、32:8:2:16:4:1 になる。これにより、 $2^6 = 64$  階調表示が実現される。

40

#### 【 0 0 9 4 】

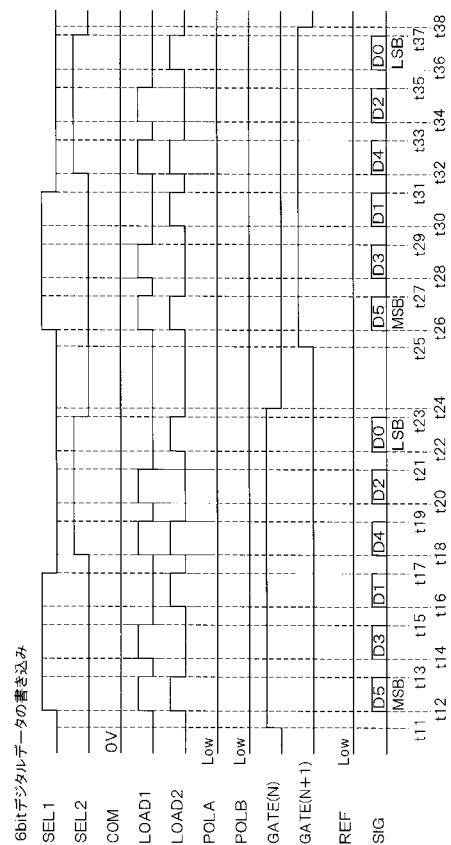

図 2 2 は、図 2 1 の時刻 t 0 ~ t 1 に行われる、DRAM 4 3 へのデジタル画素データの書き込み処理を示す詳細タイミング図である。図 2 2 の時刻 t 11 ~ t 24 では、1 水平ライン分のデジタル画素データを DRAM 4 3 に書き込み、時刻 t 25 ~ t 38 では、次の 1 水平ライン分

50

のデジタル画素データをDRAM4 3に書き込む。

**【0095】**

以下では、時刻t11～t24の間の処理を詳述する。時刻t12～t17では、制御信号SEL1がハイレベルになり、デジタル画素データの奇数ビットD1,D3,D5が容量Cd1,Cd3,Cd5にそれぞれ記憶される。より詳細には、時刻t12～t13のときに、第1の切替部83内のトランジスタQ6,Q7がともにオンして、信号線に供給された5ビット目のデジタル画素データが容量Cd5に書き込まれる。その後、時刻t14～t15のときに、第1の切替部83内のトランジスタQ8,Q9がともにオンして、信号線に供給された3ビット目のデジタル画素データが容量Cd3に書き込まれる。その後、時刻t16～t17のときに、第1の切替部83内のトランジスタQ10,Q11がともにオンして、信号線に供給された1ビット目のデジタル画素データが容量Cd1に書き込まれる。10

**【0096】**

その後、時刻t18～t23では、制御信号SEL2がハイレベルになり、奇数ビットのデジタル画素データD0,D2,D4が容量Cd0,Cd2,Cd4にそれぞれ記憶される。より詳細には、時刻t18～t19のときに、第1の切替部83内のトランジスタQ6,Q7がともにオンして、信号線に供給された4ビット目のデジタル画素データが容量Cd4に書き込まれる。その後、時刻t20～t21のときに、第1の切替部83内のトランジスタQ8,Q9がともにオンして、信号線に供給された2ビット目のデジタル画素データが容量Cd2に書き込まれる。その後、時刻t22～t23のときに、第1の切替部83内のトランジスタQ10,Q11がともにオンして、信号線に供給された0ビット目のデジタル画素データが容量Cd0に書き込まれる。20

**【0097】**

時刻t25～t38では、次の水平ラインについて、時刻t11～t24と同様の処理を行う。

**【0098】**

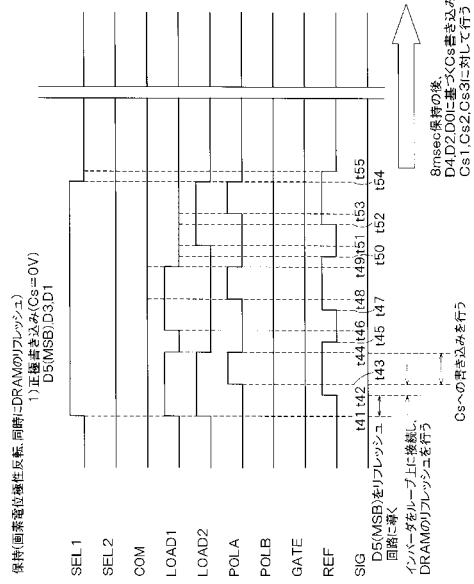

図23は蓄積容量部82への書き込み動作の詳細を示すタイミング図であり、デジタル画素データの奇数ビットD5,D3,D1を蓄積容量部82に書き込む例を示している。図23の時刻t41において、信号SEL1がハイレベルで、信号LOAD1,LOAD2がともにハイレベルになると、容量Cd5に記憶されているデータがリフレッシュ回路44に伝送される。

**【0099】**

その後、時刻t42になると、信号REFがハイレベルになり、リフレッシュ回路44内の2つのインバータIV1,IV2がリング状に接続され、リフレッシュ回路44は保持動作を行う。30

**【0100】**

その後、時刻t43になると、信号POLAがハイレベルになり、リフレッシュ回路44内のインバータIV2の出力が蓄積容量部82内の容量Cs3に書き込まれる(時刻t43～t44)。

**【0101】**

その後、時刻t46になると、信号LOAD1がハイレベルで、信号LOAD2がローレベルになり、今度はDRAM43内の容量Cd3に記憶されているデータが蓄積容量部82内の容量Cs2に記憶される(時刻t48～t49)。40

**【0102】**

その後、時刻t51になると、信号LOAD1がローレベルで、信号LOAD2がハイレベルになり、今度はDRAM43内の容量Cd1に記憶されているデータが蓄積容量部82内の容量Cs1に記憶される(時刻t53～t54)。

**【0103】**

以上の動作が終了して、所定期間(例えば8msec)が経過すると、今度はデジタル画素データの偶数ビットD4,D2,D0に対応するデータが蓄積容量部82に書き込まれる。

**【0104】**

図24は1フレーム分の蓄積容量部82への書き込み処理の詳細を示すタイミング図である。図示のように、図23と同様の処理が所定期間(8msecまたは4msec)を隔てて4回50

に分けて行われる。具体的には、デジタル画素データの奇数ビットD5,D3,D1に対応する正極性データが蓄積容量部82に記憶され(時刻t61～t62)、8msec経過後に、デジタル画素データの偶数ビットD4,D2,D0に対応する正極性データが蓄積容量部82に記憶される(時刻t63～t64)。その後、デジタル画素データの奇数ビットD5,D3,D1に対応する負極性データが蓄積容量部82に記憶され(時刻t65～t66)、8msec経過後に、デジタル画素データの偶数ビットD4,D2,D0に対応する負極性データが蓄積容量部82に記憶される(時刻t67～t68)。

#### 【0105】

このように、第3の実施形態では、デジタル画素データを奇数ビットと偶数ビットに分けて、タイミングをずらして同じ蓄積容量部82に記憶するようにしたため、蓄積容量部82内の容量の数がDRAM43内の容量の数の半分だけで済む。したがって、容量の数と第2の切替部84内のアナログスイッチの数を削減できる。

10

#### 【0106】

また、DRAM43からリフレッシュ回路44へのデータ伝送を切替制御する第1の切替部83と、リフレッシュ回路44から蓄積容量部82へのデータ伝送を切替制御する第2の切替部84とを共通の制御信号LOAD1,LOAD2で切替制御するようにしたため、配線数を削減できる。これらの効果により、本実施形態によれば、面積をそれほど増やさずに1画素あたりの面積階調のビット数を増やすことができ、高階調表示が実現できる。

#### 【0107】

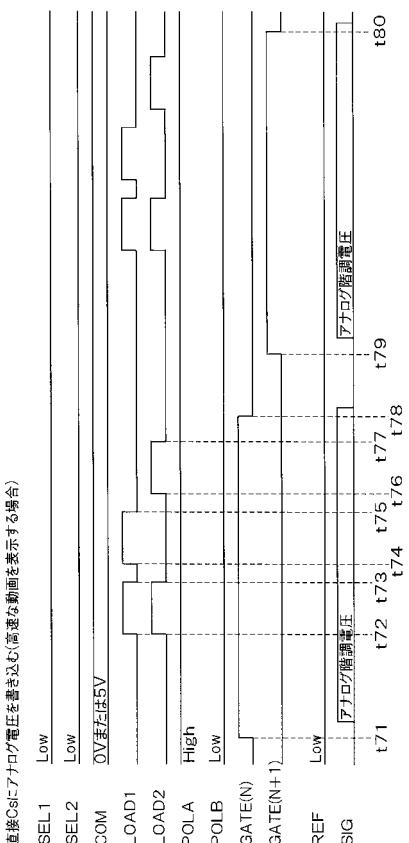

上述した第3の実施形態の説明では、デジタル画素データに基づく表示を行う例を説明したが、図19の回路を用いれば、アナログ階調電圧に基づく表示も可能である。この場合のタイミング図は図25のようになる。

20

#### 【0108】

図25の場合、信号線に供給されるアナログ階調電圧を直接、蓄積容量部82に書き込む。すなわち、DRAM43と第1の切替部83は使用しない。

#### 【0109】

図25の時刻t71～t78の間に1水平ライン分の表示が行われ、時刻t79～t80の間に次の水平ライン分の表示が行われる。

#### 【0110】

以下では、時刻t71～t78の表示動作を詳しく説明する。まず、時刻t72～t73では、信号信号LOAD1,LOAD2がともにハイレベルになり、信号線から供給されたアナログ階調電圧に応じたデータが蓄積容量部82内の容量Cs3に蓄積される。

30

#### 【0111】

次に、時刻t74～t75では、信号LOAD1ハイレベルで、信号LOAD2がローレベルになり、信号線から供給されたアナログ階調電圧に応じたデータが蓄積容量部82内の容量Cs2に蓄積される。

#### 【0112】

次に、時刻t76～t77では、信号LOAD1ローレベルで、信号LOAD2がハイレベルになり、信号線から供給されたアナログ階調電圧に応じたデータが蓄積容量部82内の容量Cs1に蓄積される。

40

#### 【0113】

このように、アナログ書き込みを行う場合は、同じアナログ階調電圧に基づいて3つの容量Cs3,Cs2,Cs1への書き込みを行う。アナログ書き込みは、DRAM43も第1の切替部83も使用しないため、上述したデジタル書き込みよりも動作が単純であり、動画表示などのように高速に画面を切り替える必要がある場合に適している。

#### 【0114】

本実施の形態では、時分割を2とし、画素部の分割を3とし、これら組み合わせにより、6bitの階調表示を行う例を示したが、時分割の数と画素部の分割はこれに限定されない。例えば、時分割を3とし、画素部の分割を2とする別の例も可能である。その場合は、時分割を16:4:1の比とし、画素部の分割を2:1とすればよい。要は、面積×時

50

間の積が  $2^n$  ( $n = 0, 1, \dots, 5$ ) となればよいのである。

**【0115】**

本実施の形態では、2つの時分割の期間を 8 msec および 4 msec としたが、時間の長さはこれに限定されない。6 msec および 3 msec などとすることも可能である。消費電力を低減するためにはできるだけこの時間を長くすることが有効だが、あまり長くしすぎると液晶への実効電圧が劣化することにより、フリッカ（表示のちらつき）が発生して視認性を損なう恐れがある。したがって、時間はフリッカが視認されない範囲でできるだけ長めに設定するのがよい。

**【0116】**

（第4の実施形態）

10

上述した第1～第3の実施形態では、本発明を液晶表示装置に適用した例を説明したが、本発明は、EL（electroluminescence）表示装置にも適用可能である。

**【0117】**

図26は本発明に係る表示装置の第4の実施形態における信号線駆動回路内の1画素分の回路構成を示す回路図である。図26の表示装置はEL表示装置であり、デジタル画素データのビット数が6ビットで、各画素がRGBの各色ごとに面積比16:4:1の3つの副表示EL発光部を有する例を示している。

**【0118】**

図26のEL表示装置は、図19と同じ構成のDRAM43、リフレッシュ回路44、蓄積容量部82、第1の切替部83、第2の切替部84およびデータ取込制御回路86を備えている。

20

**【0119】**

EL表示装置では、極性反転駆動を行う必要はないため、極性反転回路は持たない。

**【0120】**

蓄積容量部82のそれぞれには点灯制御TFT87のゲート端子が接続され、このTFT87のドレイン端子にはEL表示素子88が接続され、ソース端子には電源線DVDDが接続されている。

**【0121】**

点灯制御TFT87がオン状態のときに、電源線DVDDがハイレベル電圧になると、EL表示素子88は点灯する。電源線DVDDがハイレベル電圧であっても、点灯制御TFT87がオフ状態であればEL表示素子88は点灯しない。

30

**【0122】**

図27は図26のEL表示装置の駆動タイミングを示す図である。図21と対比すればわかるように、本実施形態は極性反転駆動を行わないため、図21よりもタイミング制御が容易である。

**【0123】**

まず、時刻t0～t1では、1フレーム分のデジタル画素データをDRAM43に記憶する。その後、時刻t1～t5では、DRAM43に記憶されたデジタル画素データに基づく奇数ビットと偶数ビットに分けて順に蓄積容量部82に記憶する。その後、時刻t1～t5の処理を繰り返す。

40

**【0124】**

デジタル画素データの奇数ビットに基づいてEL表示素子88を駆動する期間（時刻t2～t3 = 8 msec）は、偶数ビットに基づいてEL表示素子88を駆動する期間（時刻t4～t5 = 4 msec）の2倍の長さであるため、時刻t2～t3の面積×時間はそれぞれ $16 \times 8$ 、 $4 \times 8$ 、 $1 \times 8$ になり、時刻t4～t5の面積×時間はそれぞれ、 $16 \times 4$ 、 $4 \times 4$ 、 $1 \times 4$ になり、これら計6組の比は順に、32:8:2:16:4:1になる。これにより、 $2^6 = 64$ 階調表示が実現される。

**【0125】**

このように、本発明をEL表示装置に適用した場合でも、デジタル画素データのビット数nの半分の数の蓄積容量部82とEL表示素子88で $2^n$ 階調表示が可能になり、画素の

50

構成を簡易化できる。

**【0126】**

本実施の形態では、D V D DがHレベルとなる期間を8 msecおよび4 msecとしたが、この時間の長さはこれに限定されない。消費電力の観点からは、この時間の長さは長いほど低消費電力になると考えられる。

**【0127】**

一方、D R A Mのリフレッシュの観点からは、あまり時間を長くすると、一つのD R A Mがリフレッシュされる時間間隔が長くなりすぎ、D R A Mの電圧レベルが劣化しすぎ、リフレッシュ回路で補正しきれないレベルに劣化してしまい正しい点灯制御ができなくなる恐れがある。D R A Mの電圧レベルの劣化は、切替えスイッチのリーク電流が小さいほど緩和される。点灯期間の長さはこれらの観点から最適化されるべきである。10

**【0128】**

本実施の形態では、リフレッシュ回路として、2つのインバータをループ状に接続して構成するものを用いたが、リフレッシュ回路の構成はこれに限られない。第1に、D R A M 4 3の論理レベルを補正できること、第2に点灯制御T F T 8 7に十分なオン・オフ電圧を供給できる構成であればよい。例えばD R A M 4 3の論理レベル補正是0ボルトまたは5ボルトで行い、他方、前記蓄積容量への点灯制御電圧供給は、-2ボルトまたは8ボルトで行うようにしてもよい。この構成は図26のリフレッシュ回路44と切替え回路84との間に任意の構成のレベルシフタを挿入配置すればよい。

**【0129】**

本実施の形態では、時分割を2とし、点灯部の分割を3とし、これら組み合わせにより、6 b i tの階調表示を行う例を示したが、時分割の数と点灯部の分割はこれに限定されない。例えば、時分割を3とし、点灯部の分割を2とする別の例も可能である。その場合は、時分割を16 : 4 : 1の比とし、点灯部の分割を2 : 1とすればよい。要は、面積 × 時間の積が $2^n$  ( $n = 0, 1, \dots, 5$ )となればよい。20

**【0130】**

本実施の形態では、面積 × 時間の積が $2^n$  ( $n = 0, 1, \dots, 5$ )となるように説明したが、実際のE L素子の特性によっては、人間の目の感じ方に対応させるため、 $2^n$ から少しずれた値にするような補正も有効であると考えられる。面積、時間、D V D D電圧レベルを色に応じて少しずつ補正しても良い。30

**【0131】**

以上の第1～第4の実施形態に示したように構成された表示装置は、静止画を表示するために、1画面分のデータを各画素のメモリに書き込んだ後は、信号線駆動回路を停止することができ消費電力を大幅に節約できる。画素内での表示制御動作は、信号線駆動回路を動作させることに比べて、十分小さいからである。

**【0132】**

**【発明の効果】**

以上詳細に説明したように、本発明によれば、アナログ画素データに基づく信号線書き込みとデジタル画素データに基づく信号線書き込みとを切り替えて行えるようにし、かつ信号線にアナログ画素データを供給する場合の該データの並びとデジタル画素データを供給する場合の該データの並びとを互いに相違させるため、消費電力の低減が図れる。40

**【0133】**

また、本発明によれば、デジタル画素データを2回に分けて蓄積容量部に記憶するようにしたため、蓄積容量部内の容量素子の数が画素記憶部内の容量素子の数の半分だけで済む。したがって、面積をそれほど増やさずに画素あたりの面積階調のビット数を増やすことができる。

**【図面の簡単な説明】**

**【図1】**本発明に係る表示装置の第1の実施形態である液晶表示装置の概略構成を示すブロック図。

**【図2】**画素アレイ部1内の1表示画素の詳細構成を示す回路図。

10

20

30

40

50

【図3】ラッチ回路12とD/A(DAC)13の詳細な接続関係を示す図。

【図4】アナログ書き込み時のタイミング図。

【図5】アナログ書き込み時の液晶表示装置の動作を説明する図。

【図6】アナログ書き込み時に信号線に供給される信号の種類を示す図。

【図7】デジタル書き込み時のタイミング図。

【図8】デジタル書き込み時の液晶表示装置の動作を説明する図。

【図9】デジタル書き込み時に信号線に供給される信号の種類を示す図。

【図10】アナログ書き込みとデジタル書き込みでのデータの書き込み順序を比較した図

。

【図11】静止画表示時のタイミング図。

10

【図12】静止画表示時の液晶表示装置の動作を説明する図。

【図13】表示画面の一部の領域のみアナログ書き込みを行う場合のタイミング図。

【図14】一部の領域のみアナログ書き込みを行う場合の液晶表示装置の動作を説明する図。

【図15】本発明に係る表示装置の概略構成を示すプロック図。

【図16】コモン電圧出力回路の詳細構成を示す回路図。

【図17】第2の実施形態の液晶表示装置の断面構造を示す図。

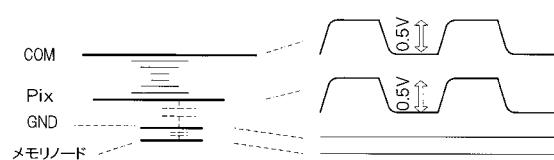

【図18】第2の実施形態におけるコモン電圧波形を示す図。

【図19】本発明に係る表示装置の第3の実施形態における信号線駆動回路内の1画素分の回路構成を示す回路図。

20

【図20】本発明に係る表示装置の第3の実施形態における1画素分の平面レイアウト図

。

【図21】本発明に係る表示装置の第3の実施形態における表示タイミング図。

【図22】DRAMへのデジタル画素データの書き込み処理を示す詳細タイミング図。

【図23】蓄積容量部への書き込み動作の詳細を示すタイミング図。

【図24】1フレーム分の蓄積容量部への書き込み処理の詳細を示すタイミング図。

【図25】アナログ階調電圧に基づく表示を行う例を示すタイミング図。

【図26】本発明に係る表示装置の第4の実施形態における信号線駆動回路内の1画素分の回路構成を示す回路図。

【図27】図26のEL表示装置の駆動タイミングを示す図。

30

【図28】対向電極および画素電極とメモリを構成するキャパシタ素子の両端電極との位置関係を概略的に示す図。

【図29】キャパシタ素子の接地電極を他の電極よりも上方に配置した例を示す図。

#### 【符号の説明】

1 画素アレイ部

2 信号線駆動回路

3 走査線駆動回路

11 データサンプリング回路

12 ラッチ回路

13 D/A

40

14 アンプ

15 セレクタ

16 タイミング調整回路

17 メモリコントローラ

21 Y-デコーダ

22 ゲートドライバ

31 入力部

32 ルックアップテーブル(LUT)

33 メモリ制御部

34 タイミング発生器

50

- 3 5 アドレス発生器

3 6 フレームメモリ

3 7 バッファ

3 8 データ出力部

3 9 制御信号出力部

4 1 画素 TFT

4 2 副表示画素部

4 3 DRAM 4 3

4 4 リフレッシュ回路 4 4

4 5 極性反転回路

4 6 転送 TFT

4 7 読み書き制御トランジスタ

4 8 キャパシタ素子

5 1 マルチブレクサ

6 1 コモン電圧出力回路

【 図 1 】

【図2】

【 义 3 】

【図4】

【図5】

アナログ書き込み時の信号線駆動回路の動作状態

【図6】

【図7】

【図8】

デジタル書き込み時の信号線駆動回路の動作状態

【図9】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

【図14】

メモリによる保持表示時と、部分的なアナログ書き込みの混在

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図 2 3】

【図 2 4】

【図 2 5】

【図 2 6】

【図27】

【図28】

【図29】

---

フロントページの続き

(51) Int.CI.

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 1 M |

| G 0 9 G | 3/20 | 6 2 3 F |

| G 0 9 G | 3/20 | 6 2 3 G |

| G 0 9 G | 3/20 | 6 2 4 B |

| G 0 9 G | 3/20 | 6 2 4 D |

| G 0 9 G | 3/20 | 6 4 1 G |

| G 0 9 G | 3/30 | J       |

(74)代理人 100107582

弁理士 関根 毅

(74)代理人 100108785

弁理士 箱崎 幸雄

(74)代理人 100112793

弁理士 高橋 佳大

(74)代理人 100118843

弁理士 赤岡 明

(74)代理人 100118876

弁理士 岡澤 順生

(74)代理人 100137523

弁理士 出口 智也

(72)発明者 中 村 卓

埼玉県深谷市幡羅町一丁目9番地2 株式会社東芝 深谷工場内

(72)発明者 林 宏 宜

埼玉県深谷市幡羅町一丁目9番地2 株式会社東芝 深谷工場内

審査官 濱本 祐広

(56)参考文献 特開2001-264814 (JP, A)

国際公開第01/073738 (WO, A1)

特開2001-290467 (JP, A)

特開2000-338918 (JP, A)

特開2001-306038 (JP, A)

特開平09-331490 (JP, A)

特開平10-026945 (JP, A)

特開2001-331153 (JP, A)

(58)調査した分野(Int.CI., DB名)

G09G 3/00-3/38

G02F 1/133

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号        | <a href="#">JP4014895B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 公开(公告)日 | 2007-11-28 |

| 申请号            | JP2002057701                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2002-03-04 |

| [标]申请(专利权)人(译) | 株式会社东芝                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 东芝公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | 东芝松下显示技术有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 中村卓<br>林宏宜                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 中村卓<br>林宏宜                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20 G09G3/30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| CPC分类号         | G09G3/3685 G09G3/2074 G09G3/3607 G09G3/3614 G09G3/3648 G09G3/3655 G09G3/3666<br>G09G2300/0408 G09G2300/0842 G09G2300/0876 G09G2310/027 G09G2310/04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.611.A G09G3/20.612.U G09G3/20.621.A G09G3/20.621.M<br>G09G3/20.623.F G09G3/20.623.G G09G3/20.624.B G09G3/20.624.D G09G3/20.641.G G09G3/30.J<br>G09G3/3233 G09G3/3266 G09G3/3275 G09G3/3291                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 2H093/NA11 2H093/NA16 2H093/NA31 2H093/NA54 2H093/NA61 2H093/NB01 2H093/NB07 2H093<br>/NB11 2H093/NC41 2H093/NC71 2H093/ND01 2H093/ND39 2H193/ZD24 5C006/AA12 5C006/AA22<br>5C006/AC24 5C006/AC25 5C006/AF46 5C006/AF82 5C006/BB16 5C006/BC03 5C006/BC06 5C006<br>/BC12 5C006/BF01 5C006/BF04 5C006/BF24 5C006/BF26 5C006/BF27 5C006/BF34 5C006/BF37<br>5C006/EB05 5C006/FA22 5C006/FA47 5C080/AA06 5C080/AA10 5C080/BB05 5C080/CC03 5C080<br>/DD05 5C080/DD25 5C080/DD26 5C080/EE28 5C080/FF11 5C080/GG12 5C080/JJ02 5C080/JJ03<br>5C080/JJ04 5C080/JJ06 5C380/AA01 5C380/AB06 5C380/AB15 5C380/AB18 5C380/AB23 5C380<br>/AB34 5C380/AB42 5C380/BA01 5C380/BA06 5C380/BA08 5C380/BA10 5C380/BA13 5C380/BA40<br>5C380/BA47 5C380/BB06 5C380/CA04 5C380/CA06 5C380/CA09 5C380/CA12 5C380/CA14 5C380<br>/CA26 5C380/CA32 5C380/CA53 5C380/CB01 5C380/CB27 5C380/CC23 5C380/CC24 5C380/CC26<br>5C380/CC33 5C380/CC45 5C380/CC49 5C380/CC53 5C380/CC58 5C380/CC66 5C380/CD049 5C380<br>/CE01 5C380/CE03 5C380/CE13 5C380/CE19 5C380/CF02 5C380/CF09 5C380/CF13 5C380/CF21<br>5C380/CF23 5C380/CF24 5C380/CF26 5C380/CF48 5C380/CF51 5C380/CF52 5C380/CF53 5C380<br>/CF64 5C380/DA02 5C380/DA07 5C380/DA11 5C380/DA16 5C380/DA31 5C380/DA32 5C380/DA33<br>5C380/DA41 5C380/DA42 5C380/DA56 5C380/DA58 5C380/HA02 5C380/HA05 |         |            |

| 代理人(译)         | 耀希达凯贤治<br>弘吉<br>川崎靖<br>智也Ideguchi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 优先权            | 2001362175 2001-11-28 JP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 其他公开文献         | <a href="#">JP2003228347A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

## 摘要(译)

要解决的问题：提供能够降低功耗的显示设备。解决方案：本发明的液晶显示装置中的信号线驱动电路2具有数据采样电路11，锁存电路12，D / A转换器13，放大器14，选择器15，定时调整电路16，液晶显示装置能够通过区域灰度系统进行2 &lt;SP&gt; 6 &lt;/SP&gt; /

SP&gt; = 64灰度的显示，并且还能够在基于模拟像素数据的显示和显示之间切换基于数字像素数据。具体地，当显示动画时，设备基于模拟像素数据显示动画，并且当显示静止图像时，设备基于数字像素数据显示动画。因此，可以避免信号线驱动电路2中的D/A转换器13等的浪费操作，并且可以降低功耗。 ↗

图 1