**【特許請求の範囲】****【請求項 1】**

複数の信号線および複数の走査線を有する液晶パネルと、各信号線を駆動する信号線駆動部と、各走査線を駆動する走査線駆動部と、電源電圧が入力され各電圧を出力する電源部と、外部信号が入力される制御部とを備え、前記制御部は前記外部信号の入力開始を検知し、時間経過した後に、前記電源部を介して、前記走査線駆動部に対し、非選択時電圧を立ち上げさせ、その立ち上がり時点から第1所定時間が経過した後に、垂直同期信号の所定個数目の立ち上がりに実質的に同期して、前記電源部を介して、前記走査線駆動部に対し、選択時電圧を立ち上げらせる事を特徴とする液晶表示装置。

**【請求項 2】**

前記制御部は、前記選択時電圧の立ち上がりよりも早い時点において、前記電源部を介して、前記信号線駆動部を構成する非ロジック部に対し、印加電圧を立ち上げらせる事を特徴とする請求項1の液晶表示装置。

**【請求項 3】**

前記制御部は前記外部信号の入力停止を検知し、時間経過した後に、前記電源部を介して前記走査線駆動部に対し、前記選択時電圧を立ち下がらせる事を特徴とする請求項1の液晶表示装置。

**【請求項 4】**

前記制御部は、前記選択時電圧の立ち下がり時点から第2所定時間が経過した時、前記電源部を介して、前記走査線駆動部に対し、前記非選択時電圧を立ち下がらせる事を特徴とする請求項3の液晶表示装置。

**【請求項 5】**

前記制御部は、前記選択時電圧の立ち上がり時点よりも遅れた時点において、前記電源部を介して、前記非ロジック部に対し、前記印加電圧を立ち下がらせる事を特徴とする請求項2の液晶表示装置。

**【請求項 6】**

前記制御部には信号生成部が設けられ、前記信号生成部はシフトレジスタと論理回路により構成され、前記シフトレジスタには、前記外部信号が入力されたことを検知する検知信号と、外部クロック信号と、前記垂直同期信号が入力され、前記論理回路には、前記シフトレジスタの各出力と、前記検知信号が入力されることにより、前記各電圧を出力させるための各制御信号を出力する事を特徴とする請求項1の液晶表示装置。

**【請求項 7】**

前記外部信号は、データイネーブル信号またはドットクロック信号または垂直同期信号または水平同期信号の中の少なくとも1つの信号である事を特徴とする請求項1の液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は液晶表示装置に関する。

**【背景技術】****【0002】**

従来、この種の装置は例えば、特許文献1に示されている。特許文献1によると液晶パネル11と、ゲートドライバ12と、ソースドライバ13と、コントロールIC14と、電源IC15とからなる液晶表示装置が示されている。

**【0003】**

電源IC15は、ソースドライバ13に対し、駆動用電圧3.3ボルトおよび第1電圧5ボルトを出力している。電源IC15は、ゲートドライバ12に対し、駆動電圧3.3ボルトおよび第2電圧1.5ボルトおよび第3電圧-1.5ボルトを出力している。また、コントロールIC14は、画像データが入力され、ソースドライバ13に対し、表示データ等を出力している。そして、電源IC15には、電源電圧の電圧が供給されている。

10

20

30

40

50

【特許文献 1】特開 2004-45748 号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかし上記装置では、ソースドライバ 13 に対し、駆動電圧の入力前に、表示データや第 1 電圧が入力される事がある。また、ゲートドライバ 12 に対し、駆動電圧の入力前に第 2 電圧が入力される事がある。そのため、各部品が誤動作したり、故障する、第 1 の欠点がある。

【0005】

本発明者は、この欠点を解消するために、コントローラ I C 14 が出力する垂直クロック信号が入力され、制御信号を出力するアナログ I C を設けた。なお、この制御信号は、駆動電圧と、表示データと、第 1 電圧と、第 2 電圧の出力順序を定めるものである。しかし、デジタル信号を取り扱うコントローラ I C 14 の出力側にアナログ I C を設けるのでノイズが発生し易い、第 2 の欠点がある。更に、アナログ I C を新たに設けるので、コストが高くなる、第 3 の欠点がある。

【0006】

そこで、本発明は、この様な従来の欠点を考慮し、各電圧が所定の順番で立ち上がり、各部品が誤動作しにくい、ノイズが発生しにくい、コストが安い液晶表示装置を提供するものである。

【課題を解決するための手段】

【0007】

上記課題を解決するために、請求項 1 の本発明では、複数の信号線および複数の走査線を有する液晶パネルと、各信号線を駆動する信号線駆動部と、各走査線を駆動する走査線駆動部と、電源電圧が入力され各電圧を出力する電源部と、外部信号が入力される制御部とを備え、前記制御部は前記外部信号の入力開始を検知し、時間経過した後に、前記電源部を介して、前記走査線駆動部に対し、非選択時電圧を立ち上げさせ、その立ち上がり時点から第 1 所定時間が経過した後に、垂直同期信号の所定個数の立ち上がりに実質的に同期して、前記電源部を介して、前記走査線駆動部に対し、選択時電圧を立ち上げせるものである。

【0008】

請求項 2 の本発明では、前記制御部は、前記選択時電圧の立ち上がりよりも早い時点において、前記電源部を介して、前記信号線駆動部を構成する非ロジック部に対し、印加電圧を立ち上げさせる。

【0009】

請求項 3 の本発明では、前記制御部は前記外部信号の入力停止を検知し、時間経過した後に、前記電源部を介して前記走査線駆動部に対し、前記選択時電圧を立ち下がらせる。

【0010】

請求項 4 の本発明では、前記制御部は、前記選択時電圧の立ち下がり時点から第 2 所定時間が経過した時、前記電源部を介して、前記走査線駆動部に対し、前記非選択時電圧を立ち下がらせる。

【0011】

請求項 5 の本発明では、前記制御部は、前記選択時電圧の立ち上がり時点よりも遅れた時点において、前記電源部を介して、前記非ロジック部に対し、前記印加電圧を立ち下がらせる。

【0012】

請求項 6 の本発明では、前記制御部には信号生成部が設けられ、前記信号生成部はシフトレジスタと論理回路により構成され、前記シフトレジスタには、前記外部信号が入力されたことを検知する検知信号と、外部クロック信号と、前記垂直同期信号が入力され、前記論理回路には、前記シフトレジスタの各出力と、前記検知信号が入力されることにより、前記各電圧を出力させるための各制御信号を出力する。

10

20

30

40

50

**【0013】**

請求項7の本発明では、前記外部信号は、データイネーブル信号またはドットクロック信号または垂直同期信号または水平同期信号の中の少なくとも1つの信号である。

**【発明の効果】****【0014】**

請求項1の様に、非選択時電圧の立ち上がり時点から第1所定時間が経過した後に、垂直同期信号の所定個数目の立ち上がりに実質的に同期して、選択時電圧を立ち上げるので、その間に、走査線駆動部が走査され、走査線駆動部のロジック部やレジスタ部に残っている不確定なデータが初期化される。

**【0015】**

請求項2の様に、選択時電圧の立ち上がり時点よりも早めに、信号線駆動部の非ロジック部に対し、印加電圧を立ち上げることにより、走査動作前に、信号線駆動部の出力を整えることができる。

**【0016】**

請求項3の様に、外部信号の入力停止を検知し、時間経過した後に、選択時電圧を立ち下げる所以、仮に、検知信号が何らかの異常により瞬間的に停止した場合は、選択時電圧は維持される所以、正常な表示を続行できる。

**【0017】**

請求項4の様に、選択時電圧の立ち下がり時点から、第2所定時間が経過した時に、非選択時電圧を立ち下げる所以、走査線駆動部内の過電流による破壊を防止できる。

**【0018】**

請求項5の様に、選択時電圧の立ち下がり時点から遅れて、信号線駆動部の非ロジック部に対し、印加電圧を立ち下げる所以、異常表示を防止できる。

**【0019】**

請求項6の様に、構成することにより、制御部はデジタル処理できる所以、従来の様にノイズが発生しにくい。また、制御部内に設けられた信号生成部により、複数の制御信号を生成する所以、従来の様に、別々の部品を設ける必要がなく、コストが安くなる。

**【0020】**

請求項7の様に、外部信号は、データイネーブル信号またはドットクロック信号または垂直同期信号または水平同期信号の中の少なくとも1つの信号である。従って、画像データが入力される時には、必ず前記信号のいずれかが入力される。その結果、画像データが入力されると、必ず、前記各電圧は立ち上がり、正常な表示ができる。

**【発明を実施するための最良の形態】****【0021】**

以下に、図面と実施例により、本発明を実施するための最良の形態を詳細に説明する。

**【実施例】****【0022】**

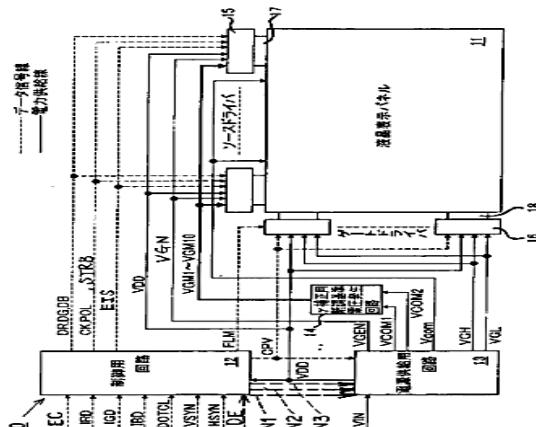

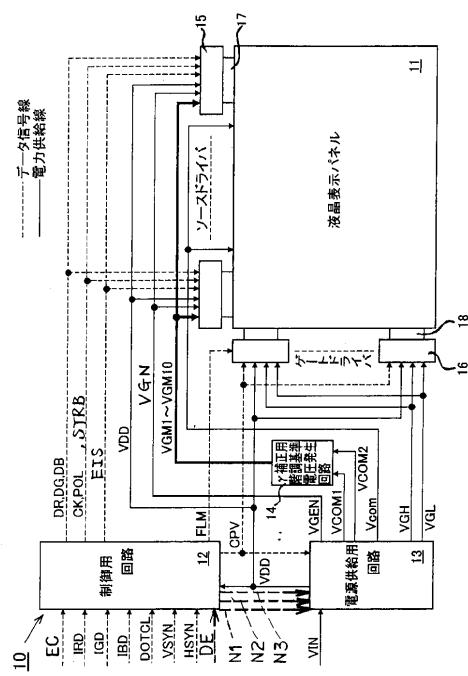

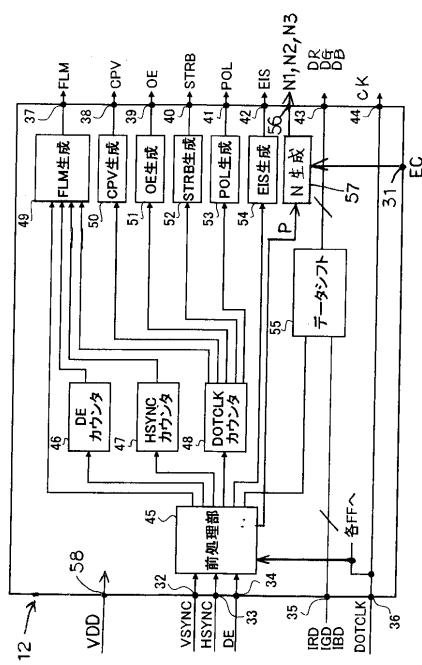

以下、図1ないし図5に従い、実施例に係る液晶表示装置10を説明する。図1は液晶表示装置10を示すブロック図、図2は液晶表示装置10に用いられる制御部12のブロック図、図3は制御部12に用いられる信号生成部57のシフトレジスタのブロック図、図4は信号生成部57の論理回路のブロック図、図5は液晶表示装置10に用いられる電源部13のブロック図である。

**【0023】**

図1において、液晶表示装置10は、液晶パネル11と、制御部12と、電源部13と、ガンマ補正部14と、複数個の信号線駆動部15と、複数個の走査線駆動部16等からなる。

**【0024】**

液晶パネル11は例えば、下ガラス基板上に、複数個設けられた信号線17と、複数個の走査線18と、それらの交点近傍に設けられたTFTと、TFTに接続された画素電極などを有する。液晶パネル11は、上ガラス基板に設けられたカラーフルタおよび共通電

極と、下ガラス基板および上ガラス基板との間に設けられた液晶（共に図示せず）等を有する。

【0025】

信号線駆動部15は各信号線17を駆動するドライバである。走査線駆動部16は各走査線18を駆動するドライバである。

【0026】

図1と図2において、制御部12は、図示しない入力インターフェースを介し、コンピュータ、テレビジョン装置、ビデオ再生装置、DVD再生装置、ナビゲーション本体等から送られた、例えばRGB各6ビットのデジタル画像データIRD, IGD, IBDと、外部クロック信号EC、データイネーブル信号DE、ドットクロック信号DOTCLK、垂直同期信号VSYNC、水平同期信号HSYNC等を取り込む。10

【0027】

外部信号V, H, C, Dは、データイネーブル信号DEまたはドットクロック信号DOTCLKまたは垂直同期信号VSYNCまたは水平同期信号HSYNCの中の、少なくとも1つの信号である。この様に、外部信号V, H, C, Dは制御部12に入力される。

【0028】

そして、制御部12は、上記各信号をデジタル的に信号処理し、デジタルRGB表示データDR, DG, DB、水平クロック信号CK、ストローブ信号STRB、極性反転信号POL、およびスタートパルス信号EISを、それぞれ信号線駆動部15へ供給する。

【0029】

制御部12は、走査線駆動部16に対し、スタートパルスFLM、垂直クロック信号CPV、ゲートイネーブル信号OEを供給する。

【0030】

制御部12の一具体例を、図2に従い、説明する。制御部12は、外部クロック信号ECの入力端子31と、データイネーブル信号DE入力端子34と、RGB各6ビットのデジタル画像データIRD, IGD, IBDの入力端子35と、クロック信号DOTCLK入力端子36と、垂直同期信号VSYNC入力端子32と、水平同期信号HSYNC入力端子33等を有している。

【0031】

そして、制御部12は、デジタルRGB表示データDR, DG, DBの出力端子43と水平クロック信号CK出力端子44と、ストローブ信号STRB出力端子40と、極性反転信号POL出力端子41と、スタートパルス信号EIS出力端子42と、制御信号N1と、N2, N3の出力端子56等を有している。30

【0032】

制御部12の内部には、大きく分けて前処理部45と、データイネーブル信号DEカウンタ46と、水平同期信号HSYNCカウンタ47と、ドットクロック信号DOTCLKカウンタ48を備えている。前処理部45からの出力信号と、DEカウンタ46の出力信号と、HSYNCカウンタ47の出力信号と、DOTCLKカウンタ48の出力信号により、スタートパルス出力手段（FLM生成回路49）において、スタートパルスFLM信号が生成され、DOTCLKカウンタ48の出力信号により、CPV生成回路50において、垂直クロック信号CPVが生成される。40

【0033】

また、DOTCLKカウンタ48の出力信号により、OE生成回路51によりゲートイネーブル信号OEが、ストローブ生成回路52によりストローブ信号STRBが生成される。POL生成回路53により極性反転信号POLが生成され、EIS生成回路54によりスタートパルス信号EISが生成される。更に、デジタル画像データIRD, IGD, IBDは、データシフト回路55において処理されて、デジタルRGB表示データDR, DG, DBとして出力される。

【0034】

前処理部45は、外部信号V, H, C, Dが入力されたことを検知する検知信号Pを出

10

20

30

40

50

力する。信号生成部 57 は、検知信号 P と外部クロック信号 EC が入力され、制御信号 N1, N2, N3 を出力する。また、外部クロック信号 EC は、液晶表示装置 10 内で生成される。

#### 【0035】

これらの前処理部 45 と、DE カウンタ 46 と、H Sync カウンタ 47 と、DOTC LK カウンタ 48 と、OE 生成回路 51 と、ストローブ生成回路 52 と、POL 生成回路 53 と、EIS 生成回路 54 と、データシフト回路 55 等の構成は、従来の制御部における構成と実質的に相違はなく、動作原理も同様であるので、詳細な説明は省略する。

#### 【0036】

但し、外部信号 V, H, C, D と、外部クロック信号 EC が、信号生成部 57 に入力されている点が、従来の制御部との相違点である。10

#### 【0037】

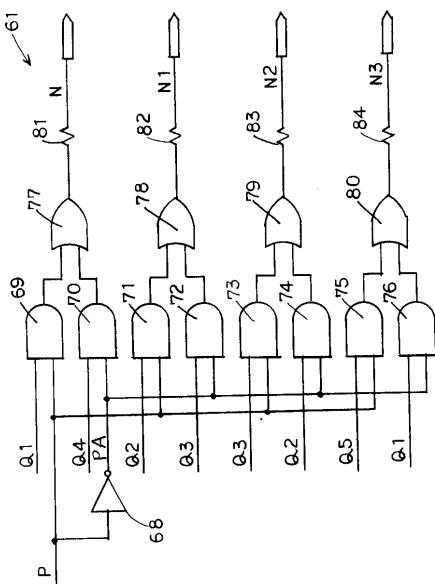

次に、主に図 3 と図 4 に従い、信号生成部 57 を説明する。信号生成部 57 は、シフトレジスタ 60 と、論理回路 61 により構成されている。

#### 【0038】

図 3において、シフトレジスタ 60 は、6 個のフリップフロップ（以下に、FF と記す）62, 63, 64, 65, 66, 67 からなる。10

#### 【0039】

FF 62 の D 端子は、検知信号 P が入力され、プリセット端子 p は一定電圧が入力されクロック端子 C は、外部クロック信号 EC が入力される。FF 62 のクリア端子 L はリセット信号 RESET の反転信号が入力され、端子 Q は出力 Q1 を出力する。20

#### 【0040】

FF 63 の D 端子は、出力 Q1 が入力され、プリセット端子 p は一定電圧が入力され、クロック端子 C は、外部クロック信号 EC が入力される。FF 63 のクリア端子 L はリセット信号 RESET の反転信号が入力され、端子 Q は出力 Q2 を出力する。

#### 【0041】

FF 64 の D 端子は、出力 Q2 が入力され、プリセット端子 p は一定電圧が入力され、クロック端子 C は、外部クロック信号 EC が入力される。FF 64 のクリア端子 L はリセット信号 RESET の反転信号が入力され、端子 Q は出力 Q3 を出力する。

#### 【0042】

FF 65 の D 端子は、出力 Q3 が入力され、プリセット端子 p は一定電圧が入力され、クロック端子 C は、外部クロック信号 EC が入力される。FF 65 のクリア端子 L はリセット信号 RESET の反転信号が入力され、端子 Q は出力 Q4 を出力する。30

#### 【0043】

FF 66 の D 端子は、出力 Q4 が入力され、プリセット端子 p は一定電圧が入力され、クロック端子 C は、垂直同期信号 V Sync が入力される。FF 66 のクリア端子 L は検知信号 P の反転信号が入力され、端子 Q は次の FF 66 の D 端子に接続されている。

#### 【0044】

FF 67 のプリセット端子 p は一定電圧が入力され、クロック端子 C は、垂直同期信号 V Sync が入力される。FF 67 のクリア端子 L は検知信号 P の反転信号が入力され、端子 Q は出力 Q5 を出力する。以上の部品にて、シフトレジスタ 60 は構成されている。40

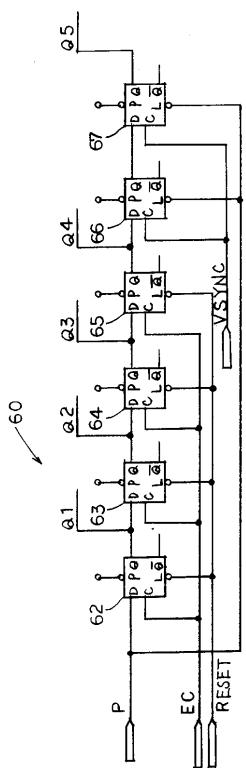

#### 【0045】

図 4において、論理回路 61 は、ノット回路 68 と、アンドゲート 69 ~ 76 と、オアゲート 77 ~ 81 と、抵抗 81 ~ 84 とから構成されている。ノット回路 68 は検知信号 P の反転信号 PA を出力する。

#### 【0046】

アンドゲート 69 の 1 つの入力側は、出力 Q1 が入力され、他の入力側は検知信号 P が入力される。

#### 【0047】

アンドゲート 70 の 1 つの入力側は、出力 Q4 が入力され、他の入力側は反転信号 PA 50

が入力される。

【0048】

アンドゲート71の1つの入力側は、出力Q2が入力され、他の入力側は検知信号Pが入力される。

【0049】

アンドゲート72の1つの入力側は、出力Q3が入力され、他の入力側は反転信号PAが入力される。

【0050】

アンドゲート73の1つの入力側は、出力Q3が入力され、他の入力側は検知信号Pが入力される。

10

【0051】

アンドゲート74の1つの入力側は、出力Q2が入力され、他の入力側は反転信号PAが入力される。

【0052】

アンドゲート75の1つの入力側は、出力Q5が入力され、他の入力側は検知信号Pが入力される。

【0053】

アンドゲート76の1つの入力側は、出力Q1が入力され、他の入力側は反転信号PAが入力される。

【0054】

オアゲート77の1つの入力側は、アンドゲート69の出力が入力され、他の入力側はアンドゲート70の出力が入力される。オアゲート77の出力側は抵抗81を介して、遅延信号Nを出力する。但し、この液晶表示装置10では、遅延信号Nは用いられない。

20

【0055】

オアゲート78の1つの入力側は、アンドゲート71の出力が入力され、他の入力側はアンドゲート72の出力が入力される。オアゲート78の出力側は抵抗82を介して、制御信号N1を出力する。

【0056】

オアゲート79の1つの入力側は、アンドゲート73の出力が入力され、他の入力側はアンドゲート74の出力が入力される。オアゲート79の出力側は抵抗83を介して、制御信号N2を出力する。

30

【0057】

オアゲート81の1つの入力側は、アンドゲート75の出力が入力され、他の入力側はアンドゲート76の出力が入力される。オアゲート81の出力側は抵抗84を介して、制御信号N3を出力する。以上の部品により、信号生成部57は構成されている。

【0058】

上述した様に、シフトレジスタ60には、外部信号V, H, C, Dが入力された事を検知する検知信号Pと、外部クロック信号ECと、垂直同期信号VSYNCが入力される。

【0059】

論理回路61には、シフトレジスタ60の各出力Q1, Q2, Q3, Q4, Q5と、検知信号Pが入力される。その結果、信号生成部57は、各電圧を出力させるための各制御信号N1, N2, N3を出力する。

40

【0060】

次に、図1に示す様に、電源電圧VINは電源部13に入力されている。電源部13は供給された電源電圧VIN(例えば12ボルト)を基に、液晶表示装置10内で使用される各種の電圧を生成する。例えば、制御部12のロジック部と、信号線駆動部15のロジック部と、走査線駆動部16のロジック部に対して、駆動用電圧VDDを生成する。

【0061】

また、電源部13は、ガンマ補正部14に対して、基準電圧VCOM1およびVCOM2と、共通電圧VCOMを生成する。

50

## 【0062】

更に、電源部13は、信号線駆動部15の非ロジック部（例えば出力部）に対して、所定の印加電圧VGNを出力する。電源部13は、走査線駆動部16の非ロジック部（例えば出力部）に対して、選択時電圧VGHおよび非選択時電圧VGLを出力する。電源部13は、液晶パネル11の共通電極に印加するための共通電圧VCOMを出力する。

## 【0063】

ガンマ補正部14は、電源部13から供給された基準電圧VCOM1およびVCOM2を抵抗分圧することにより、階調基準電圧VGM1～VGM10を生成し、信号線駆動部15へ供給する。

## 【0064】

信号線駆動部15は、18ビットラッチ、シフトレジスタ、サンプリングメモリ、ホールドメモリ、レベルシフタ、分圧回路、DA変換器、出力部（いずれも図示せず）を備えている。

## 【0065】

制御部12から信号線駆動部15へ入力された表示データを構成する各6ビットのデータDR, DG, DBは、信号線駆動部15内のラッチにおいて時分割で、内部にラッチされる。

## 【0066】

そして、信号線駆動部15内のサンプリングメモリ、ホールドメモリ、レベルシフタを経て、水平同期信号HSYNCに同期して発生されるスタートパルスEISに基づいて、分圧回路からの基準電圧を基に、DA変換器により、DA変換が行われる。

## 【0067】

このことにより、ガンマ補正されたアナログ電圧（階調電圧）が発生され、出力バッファ（出力部）を経て、液晶パネル11のY1～Yn（図示せず）からなるn本の信号線17に供給される。

## 【0068】

また、制御部12から走査線駆動部16へ供給された垂直同期信号VSYNCに同期し発生されるクロック信号CPVと、スタートパルスFLMは、走査線駆動部16により処理される。そして走査信号は、液晶パネル11のX1～Xm（図示せず）からなるm本の走査線18に供給される。

## 【0069】

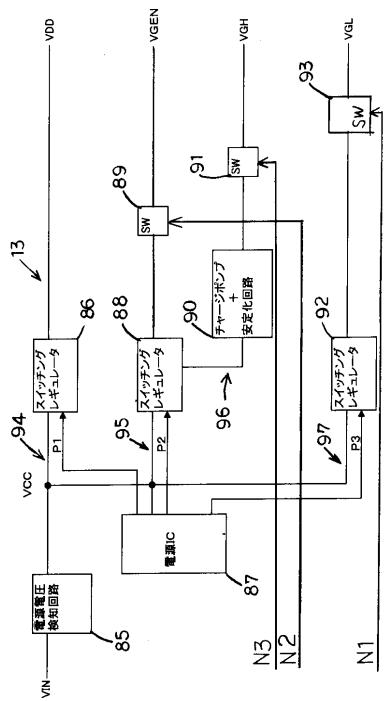

次に、図5に従い、電源部13を説明する。図5において、電源部13は電源電圧検知回路85と、スイッチングレギュレータ86と、電源IC87とを有している。更に電源部13は、スイッチングレギュレータ88と、スイッチ部89と、変換回路90と、スイッチ部91と、スイッチングレギュレータ92と、スイッチ部93を有している。

## 【0070】

電源電圧検知回路85は、電源電圧VINが所定値（例えば、直流12ボルト）以上になると、電圧VCC（例えば、直流14ボルト）を出力する。そして、電源電圧検知回路85は、電源電圧VINが所定値未満になると、電圧VCCの出力を停止する。

## 【0071】

スイッチングレギュレータ86は電源電圧検知回路85に接続され、電圧VCCが入力される。スイッチングレギュレータ86は電源IC87に接続され、PWM制御信号P1が入力される。スイッチングレギュレータ86は上記信号P1により、駆動電圧VDD(3.3ボルト)を出力する。

## 【0072】

これらの電源電圧検知回路85と、電源IC87と、スイッチングレギュレータ86により、駆動電圧変換部94が構成されている。駆動電圧変換部94は、駆動電圧VDDを出力するものである。

## 【0073】

また、図示していないが、発振器は、駆動電圧変換部94の出力側に接続され、駆動電

10

20

30

40

50

圧 V D D が供給されている。この様に、発振器が発振する外部クロック信号 E C は電源部 1 3 が出力する駆動電圧 V D D と、殆ど同時に立ち上がり、駆動電圧 V D D と、殆ど同時に立ち下がる様に、構成されている。

#### 【 0 0 7 4 】

スイッチングレギュレータ 8 8 は電源電圧検知回路 8 5 に接続され、電圧 V C C が入力される。スイッチングレギュレータ 8 8 は電源 I C 8 7 に接続され、P W M 制御信号 P 2 が入力される。スイッチングレギュレータ 8 8 は上記信号 P 2 により、例えば 1 0 ボルトを出力する。

#### 【 0 0 7 5 】

これらの電源電圧検知回路 8 5 と、電源 I C 8 7 と、スイッチングレギュレータ 8 8 により、電圧（例えば 1 0 ボルト）を出力するための電圧変換部 9 5 が構成されている。10

#### 【 0 0 7 6 】

スイッチ部 8 9 は例えば M O S F E T 等からなる。スイッチ部 8 9 は、電圧変換部 9 5 の出力側に接続されている。スイッチ部 8 9 の制御端子は、制御信号 N 2 が入力される。

#### 【 0 0 7 7 】

制御信号 N 2 がロウレベルの時、スイッチ部 8 9 は開成し、電圧変換部 9 5 は電圧を出力しない。制御信号 N 2 がハイレベルの時、スイッチ部 8 9 は閉成し、電圧変換部 9 5 は、所定の電圧 V G N ( 1 0 ボルト ) を出力する。

#### 【 0 0 7 8 】

変換回路 9 0 は例えば、チャージポンプと安定化回路等からなり、スイッチングレギュレータ 8 8 に接続されている。20

#### 【 0 0 7 9 】

上記電源電圧検知回路 8 5 と、電源 I C 8 7 と、スイッチングレギュレータ 8 8 と、変換回路 9 0 とにより、選択時電圧（例えば 1 5 ボルト）を出力するための電圧変換部 9 6 が構成されている。

#### 【 0 0 8 0 】

スイッチ部 9 1 は例えば M O S F E T 等からなる。スイッチ部 9 1 は、電圧変換部 9 6 の出力側に接続されている。スイッチ部 9 1 の制御端子は、制御信号 N 3 が入力される。

#### 【 0 0 8 1 】

制御信号 N 3 がロウレベルの時、スイッチ部 9 1 は開成し、電圧変換部 9 6 は電圧を出力しない。制御信号 N 3 がハイレベルの時、スイッチ部 9 1 は閉成し、電圧変換部 9 6 は、選択時電圧 V G H ( 1 5 ボルト ) を出力する。30

#### 【 0 0 8 2 】

スイッチングレギュレータ 9 2 は電源電圧検知回路 8 5 に接続され、電圧 V C C が入力される。スイッチングレギュレータ 9 2 は電源 I C 8 7 に接続され、P W M 制御信号 P 3 が入力される。スイッチングレギュレータ 9 2 は上記信号 P 3 により、例えば、- 1 5 ボルトを出力する。

#### 【 0 0 8 3 】

上記電源電圧検知回路 8 5 と、電源 I C 8 7 と、スイッチングレギュレータ 9 2 とにより、非選択時電圧（例えば - 1 5 ボルト）を出力するための電圧変換部 9 7 が構成されている。40

#### 【 0 0 8 4 】

スイッチ部 9 3 は例えば M O S F E T 等からなる。スイッチ部 9 3 は、電圧変換部 9 7 の出力側に接続されている。スイッチ部 9 3 の制御端子は、制御信号 N 1 が入力される。

#### 【 0 0 8 5 】

制御信号 N 1 がロウレベルの時、スイッチ部 9 3 は開成し、電圧変換部 9 7 は電圧を出力しない。制御信号 N 1 がハイレベルの時、スイッチ部 9 3 は閉成し、電圧変換部 9 7 は非選択時電圧 V G L ( - 1 5 ボルト ) を出力する。以上の部品により、電源部 1 3 は構成されている。

#### 【 0 0 8 6 】

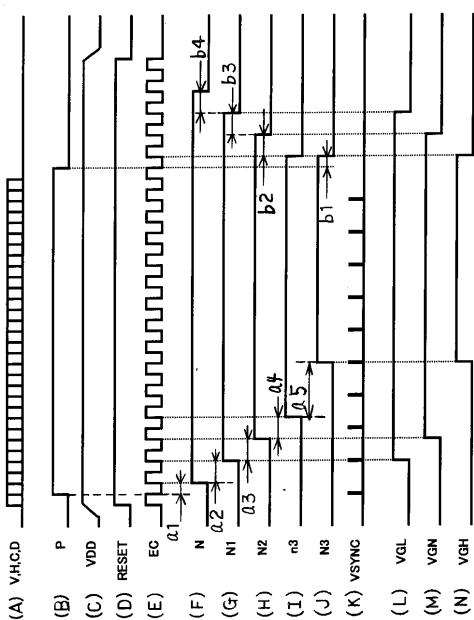

次に、図1ないし図6に従い、液晶表示装置10の動作を説明する。図6は、液晶表示装置10に用いられる各種信号等のタイミングチャートである。

#### 【0087】

最初に、使用者は例えば、ナビゲーション本体に設けられたスタートボタン(図示をせず)を押したものとする。

#### 【0088】

スタートボタンが設けられた入力部は、電源回路(共に図示せず)に接続されている。電源回路は所定の電源を直流12ボルトに変換するものである。その結果、電源部13に対して、電源電圧VIN(直流12ボルト)の入力が始まる。

#### 【0089】

電源部13において、電圧VCC(14ボルト)が生成され、駆動電圧変換部94により、駆動電圧VDDは立ち上がり、ハイレベルとなる(図6(C)参照)。

#### 【0090】

この時、電源部13は、信号線駆動部15と、走査線駆動部16と、制御部12に対し駆動電圧VDDを出力する。

#### 【0091】

また、駆動電圧VDDの立ち上がりと殆ど同時に、外部信号V,H,C,Dが制御部12に入力される(図6(A)参照)。

#### 【0092】

更に、この時、リセット信号RESETが立ち上がり(図6(D)参照)、外部クロック信号ECも立ち上がる(図6(E)参照)。外部クロック信号ECの周波数は例えば100ヘルツであり、1周期が10msである。

#### 【0093】

制御部12は外部信号V,H,C,Dが入力されると(図6(A)参照)、少し遅れて(例えば、5ms)、外部信号V,H,C,Dの入力開始を検知し、ハイレベルの検知信号Pを出力する(図6(B)参照)。この時、画像データIRD,IGD,IBDが制御部12に入力される。

#### 【0094】

制御部12の信号生成部57には、ハイレベルの検知信号Pと、ハイレベルのリセット信号RESETと、外部クロック信号ECが入力される。

#### 【0095】

その後、a1時間(例えば5ms)経過して、外部クロック信号ECが立ち上ると、遅延信号Nは立ち上がる(図6(F)参照)。

#### 【0096】

そして、a2時間(例えば10ms)経過して、外部クロック信号ECが立ち上ると、制御信号N1は立ち上がる(図6(G)参照)。

#### 【0097】

電源部12は、制御信号N1の立ち上がり(ハイレベルになる)に応じて、スイッチ部93を閉成し、走査線駆動部16に対し、非選択時電圧VGL(-15ボルト)を出力する(図6(L)参照)。

#### 【0098】

その後、a3時間(10ms)経過して、外部クロック信号ECが立ち上ると、制御信号N2は立ち上がる(図6(H)参照)。

#### 【0099】

電源部13は、制御信号N2の立ち上がり(ハイレベルになる)に応じて、スイッチ部89を閉成し、信号線駆動部15の非ロジック部に対し、印加電圧VGN(10ボルト)を立ち上がらせる(図6(M)参照)。

#### 【0100】

この時、制御部12は走査線駆動部16に対し、スタートパルスFLM、垂直クロック信号CPV、ゲートイネーブル信号DEを出力する。

10

20

30

40

50

## 【0101】

そして、 $a_4$ 時間(10ms)経過し、外部クロック信号ECが立ち上ると、遅延信号n3は立ち上がる(図6(I)参照)。

## 【0102】

制御部12は、遅延信号n3が立ち上がった後に、所定個数目(例えば2個目)の垂直同期信号VSYNCの立ち上がり(図6(K)参照)に実質的に同期して、制御信号N3を立ち上げる(図6(J)参照)。

## 【0103】

電源部13は、制御信号N3の立ち上がり(ハイレベルになる)に応じて、スイッチ部91を開成し、走査線駆動部16に対し、選択時電圧VGH(例えば15ボルト)を出力する(図6(N)参照)。その結果、液晶パネル11において、表示データDR, DG, DBによる表示が開始される。10

## 【0104】

なお、遅延信号n3の立ち上がり時点と、垂直同期信号VSYNCの立ち上がり時点が一致した場合は、制御部12は、その時点から、所定個数目(例えば、1個目であり、次の)垂直同期信号VSYNCの立ち上がりに実質的に同期して、制御信号N3を立ち上げる。

## 【0105】

上記内容をまとめると、制御部12は、非選択時電圧VGLの立ち上がり時点から、第1所定時間( $a_3 + a_4 = 20\text{ms}$ )が経過した後に、垂直同期信号VSYNCの所定個数の立ち上がり(図6(J)参照)に実質的に同期して、電源部13を介して、走査線駆動部16に対し、選択時電圧VGHを立ち上がらせる。20

## 【0106】

また、制御部12は、選択時電圧VGHの立ち上がり(図6(N)参照)よりも早い時点で、電源部13を介して、信号線駆動部15を構成する非ロジック部に対し、印加電圧VGNを立ち上がらせる(図6(M)参照)。

## 【0107】

次に、液晶表示装置10が表示終了するまでの動作を説明する。最初に、制御部12に対する外部信号V, H, C, Dの入力が停止する(図6(A)参照)。

## 【0108】

制御部12は、少し遅れて、入力停止を検知し、ロウレベルの検知信号Pを出力する(図6(B)参照)。30

## 【0109】

上記検知時点からb1(例えば5ms)の時間経過した後に、制御部12は、制御信号N3を立ち下げる(図6(J)参照)。b1は10ms以内に設定されている。

## 【0110】

電源部13は制御信号N3の立ち下がり(ロウレベルになる)に応じて、スイッチ部91を開成し、走査線駆動部16に対し、選択時電圧VGHを立ち下がらせる(図6(N)参照)。

## 【0111】

選択時電圧VGHの立ち下がり時点からb2時間(10ms)経過後に、外部クロック信号ECの立ち上がりに応じて、制御部12は、制御信号N2を立ち下げる(図6(H)参照)。40

## 【0112】

電源部13は、制御信号N2の立ち下がりに応じて、スイッチ部89を開成し、信号線駆動部15の非ロジック部に対し、印加電圧VGNを立ち下がらせる(図6(M)参照)。

## 【0113】

上記立ち下がり時点からb3時間(10ms)経過後に、外部クロック信号ECの立ち上がりに応じて、制御部12は、制御信号N1を立ち下げる(図6(G)参照)。50

## 【0114】

電源部13は、制御信号N1の立ち下がりに応じて、スイッチ部93を開成し、走査線駆動部16に対し、非選択時電圧VGLを立ち下げる(図6(L)参照)。この様にして表示が終了する。

## 【0115】

その後、外部クロック信号ECは立ち下げる(図6(E)参照)。また、リセット信号RESETも立ち下がり(図6(D)参照)。駆動電圧VDDも立ち下がる(図6(C)を参照)。以上にて、動作を終了する。

## 【0116】

上記内容をまとめ。制御部12は、選択時電圧VGHの立ち下がり時点から、第2所定時間( $b_2 + b_3 = 10\text{ ms}$ )が経過した時に(図6(G)参照)、電源部13を介して走査線駆動部16に対し、非選択時電圧VGLを立ち下がらせる。

## 【0117】

更に、制御部12は、選択時電圧VGHの立ち下がり時点(図6(N)参照)よりも遅れた時点において、電源部13を介して、信号線駆動部15の非ロジック部に対し、印加電圧VGNを立ち下がらせる(図6(M)参照)。

## 【図面の簡単な説明】

## 【0118】

【図1】本発明の実施例に係る液晶表示装置10のブロック図である。

10

【図2】上記装置10に用いられる制御部12のブロック図である。

20

【図3】信号生成部57のシフトレジスタ62のブロック図である。

【図4】信号生成部57の論理回路61のブロック図である。

【図5】上記装置10に用いられる電源部13のブロック図である。

【図6】上記装置10に用いられる各種信号等のタイミングチャートである。

## 【符号の説明】

## 【0119】

11 液晶パネル

30

12 制御部

13 電源部

15 信号線駆動部

16 走査線駆動部

17 信号線

18 走査線

【図1】

【図2】

【図3】

【図4】

【 図 5 】

【 図 6 】

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

G 0 9 G 3/20 6 7 0 D

G 0 9 G 3/20 6 1 2 G

F ターム(参考) 2H093 NA16 NA21 NA41 NC09 NC11 NC21 NC22 NC41 NC52 NC58

NC59 ND34 ND37 ND48

5C006 AC24 AC25 AF44 AF51 AF53 AF64 AF67 BB11 BF03 BF22

BF26 BF27 BF42 FA00

5C080 AA10 BB05 DD09 DD17 EE25 FF09 JJ02 JJ03 JJ04

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP2007199546A</a>                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2007-08-09 |

| 申请号            | JP2006020091                                                                                                                                                                                                                                                                                                                                                                                                                                        | 申请日     | 2006-01-30 |

| [标]申请(专利权)人(译) | 爱普生映像元器件有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 爱普生影像设备公司                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 堀部啓二<br>中山勝仁                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 堀部 啓二<br>中山 勝仁                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| F1分类号          | G09G3/36 G02F1/133.550 G09G3/20.623.A G09G3/20.622.A G09G3/20.612.R G09G3/20.670.D<br>G09G3/20.612.G                                                                                                                                                                                                                                                                                                                                                |         |            |

| F-Term分类号      | 2H093/NA16 2H093/NA21 2H093/NA41 2H093/NC09 2H093/NC11 2H093/NC21 2H093/NC22 2H093<br>/NC41 2H093/NC52 2H093/NC58 2H093/NC59 2H093/ND34 2H093/ND37 2H093/ND48 5C006/AC24<br>5C006/AC25 5C006/AF44 5C006/AF51 5C006/AF53 5C006/AF64 5C006/AF67 5C006/BB11 5C006<br>/BF03 5C006/BF22 5C006/BF26 5C006/BF27 5C006/BF42 5C006/FA00 5C080/AA10 5C080/BB05<br>5C080/DD09 5C080/DD17 5C080/EE25 5C080/FF09 5C080/JJ02 5C080/JJ03 5C080/JJ04 2H193<br>/ZH21 |         |            |

| 代理人(译)         | 须泽 修                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

### 摘要(译)

要解决的问题：提供一种廉价的液晶显示装置，其中各个电压按预定顺序上升，并且各个部件不易发生故障并产生噪声。 ŽSOLUTION：液晶显示装置包括具有多条信号线17和多条扫描线18的液晶面板11，驱动各条线17的信号线驱动器15，驱动相应扫描的扫描线驱动器16线18，输入源电压并输出各个电压的电源单元13，以及输入外部信号的控制器12。控制器12检测开始输入的外部信号，使扫描线驱动器16在一段时间后通过电源单元13升高非选择时间信号，然后使扫描线驱动器16升高选择时间电压通过电源单元13在上升之后的第一预定时间基本上与垂直同步信号的上升同步，该垂直同步信号被计数为预定的。 Ž