(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-10520

(P2005-10520A)

(43) 公開日 平成17年1月13日(2005.1.13)

(51) Int.Cl.<sup>7</sup>

**G09G 3/36**

**G02F 1/133**

**G09G 3/20**

**H04N 5/66**

F 1

GO9G 3/36

GO2F 1/133 550

GO2F 1/133 575

GO9G 3/20 611E

GO9G 3/20 621B

テーマコード(参考)

2H093

5C006

5C058

5C080

審査請求 未請求 請求項の数 7 O L (全 16 頁) 最終頁に続く

(21) 出願番号

(22) 出願日

特願2003-175251 (P2003-175251)

平成15年6月19日 (2003.6.19)

(71) 出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100104695

弁理士 島田 明宏

(72) 発明者 井上 明彦

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

F ターム(参考) 2H093 NA16 NA33 NA55 NC03 NC16

NC28 NC34 ND06 ND10

5C006 AA14 AA16 AC21 AC28 AF44

AF46 AF51 AF53 AF71 BB16

BC11 BC16 BF14 BF24 FA22

FA23 FA56

5C058 AA06 BA01 BA07 BB11 BB14

最終頁に続く

(54) 【発明の名称】 液晶中間調表示方法及びその方法を用いた液晶表示装置

## (57) 【要約】

【課題】 F R C 方式によっても画素の輝度差が生じず、さらに空間的にフリッカ成分を除去しようとする場合にも、スジ状の輝度ムラが生じない中間調表示方法およびその方法を用いた表示装置を提供する。

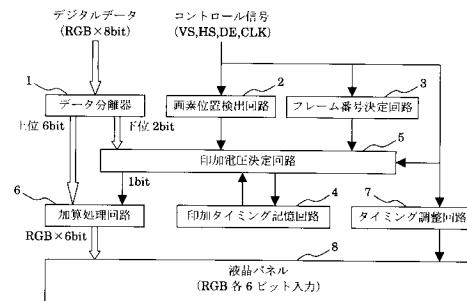

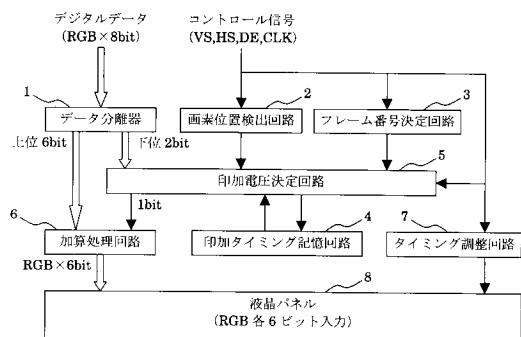

【解決手段】 本液晶表示装置は、R G B 各色毎に、データ分離器 1、画素位置検出回路 2、フレーム番号決定回路 3、印加タイミング記憶回路 4、印加電圧決定回路 5、加算処理回路 6、およびタイミング調整回路 7 を備えており、これらにより (1 + N) 階調の多階調表示を行う場合の単位周期を 2 N フレームとし、この 2 N フレーム内で高電圧または低電圧の正極電圧と負極電圧との印加回数が等しくなるように駆動電圧を設定する。このことにより、液晶素子を含む画素回路をマトリクス状に複数配置してなる液晶パネル 8 に表示される同一輝度であるべき各画素の平均輝度が均一となるため、表示品位が向上する。

【選択図】

図 1

## 【特許請求の範囲】

## 【請求項 1】

予め定められた複数の駆動電圧から所定の単位周期毎に選ばれる第1および第2の駆動電圧のいずれかの駆動電圧であって、前記単位周期に含まれる1つ以上のフレーム毎に極性を反転しフレーム毎に設定した駆動電圧に基づき、当該単位周期で(1+N)階調(Nは2以上の自然数)の多階調表示を行う液晶中間調表示方法において、

前記単位周期を2Nフレームとして、当該単位周期のうち、正の極性を有する第1の駆動電圧が設定されるフレーム数と負の極性を有する第1の駆動電圧が設定されるフレーム数とを同数とし、正の極性を有する第2の駆動電圧が設定されるフレーム数と負の極性を有する第2の駆動電圧が設定されるフレーム数とを同数とすることを特徴とする液晶中間調表示方法。10

## 【請求項 2】

前記単位周期の前半Nフレームのうち前記第1の駆動電圧が設定されるフレーム数と、前記単位周期の後半Nフレームのうち前記第1の駆動電圧が設定されるフレーム数とを同数とし、

前記前半Nフレームのうち前記第2の駆動電圧が設定されるフレーム数と、前記後半Nフレームのうち前記第2の駆動電圧が設定されるフレーム数とを同数とすることを特徴とする、請求項1に記載の液晶中間調表示方法。

## 【請求項 3】

Nが偶数の場合、k番目のフレーム(kはN未満の奇数とする)および(N+k+1)番目のフレームに設定される駆動電圧を等しくするとともに、(k+1)番目のフレームおよび(N+k)番目のフレームに設定される駆動電圧を等しくし、Nが奇数の場合、m番目のフレーム(mはN以下の自然数とする)および(m+N)番目のフレームに設定される駆動電圧を等しくすることを特徴とする、請求項2に記載の液晶中間表示方法。20

## 【請求項 4】

複数の画素からなる表示単位で多階調表示を行うため、前記表示単位に含まれる画素毎に所定の階調を表示させる第1または第2の駆動電圧を設定することを特徴とする、請求項1から請求項3までのいずれか1項に記載の液晶中間調表示方法。

## 【請求項 5】

装置外部から与えられる表示データに応じて、予め定められた複数の駆動電圧から所定の単位周期毎に選ばれる第1および第2の駆動電圧のいずれかの駆動電圧であって、前記単位周期に含まれる1つ以上のフレーム毎に極性を反転しフレーム毎に設定した駆動電圧に基づき、当該単位周期で(1+N)階調(Nは2以上の自然数)の多階調表示を行う液晶表示装置において。30

前記単位周期を2Nフレームとして、当該単位周期のうち、正の極性を有する第1の駆動電圧が設定されるフレーム数と負の極性を有する第1の駆動電圧が設定されるフレーム数とを同数とし、正の極性を有する第2の駆動電圧が設定されるフレーム数と負の極性を有する第2の駆動電圧が設定されるフレーム数とを同数とする電圧決定手段と、

前記電圧決定手段により設定された駆動電圧に基づき、多階調表示を行う表示手段とを備える液晶表示装置。40

## 【請求項 6】

前記電圧決定手段は、

前記単位周期である2Nフレームのうち前記表示データに対応するフレームを決定するフレーム決定手段と、

前記単位周期に設定される駆動電圧を当該単位周期に含まれるフレームに関連させて記憶するタイミング記憶手段と、

前記フレーム決定手段により決定されるフレームに基づき、前記タイミング記憶手段に記憶される、当該決定されるフレームに関連する駆動電圧を、前記表示手段に与える印加電圧決定手段と、

を含むことを特徴とする、請求項5に記載の液晶表示装置。50

**【請求項 7】**

前記電圧決定手段は、複数の画素からなる表示単位で多階調表示を行うため、前記表示単位に含まれる画素毎に所定の階調を表示させる第1または第2の駆動電圧を設定し、前記表示手段は、前記駆動電圧に基づき、前記表示単位で多階調表示を行うことを特徴とする、請求項5または請求項6に記載の液晶表示装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、液晶表示方法およびその方法を使用した液晶表示装置に関し、より詳しくは2つの異なる駆動電圧を周期的に印加することにより中間調を表示する多階調表示方法の液晶表示方法およびその方法を使用した液晶表示装置に関する。 10

**【0002】****【従来の技術】**

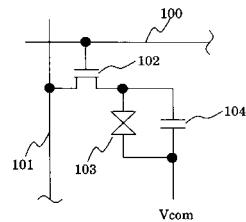

通常、液晶表示装置は、液晶素子を含む画素回路がマトリクス状に複数配置してなる表示パネルと、所定の画素回路に所定のデータ信号を表示パネルに与える液晶駆動用ドライバと、所定の画素回路を選択するための所定の走査信号を表示パネルに与える選択用ドライバとを備える。図20は、この液晶表示装置に含まれる画素回路の等価回路を示す図である。図示されるように、この画素回路は、液晶駆動用ドライバからのデータ信号を与えるデータ信号線101と、選択用ドライバからの走査信号を与える走査信号線100と、走査信号に応じてスイッチング素子として機能する電界効果トランジスタ102と、画素の表示光量を調節するための液晶素子103と、所定の容量を有する補助容量素子104とを備える。電界効果トランジスタ102は、そのゲートに走査信号線100が接続され、そのドレインにデータ信号線が接続される。また、液晶素子および補助容量素子の一端は電界効果トランジスタ102のソースに接続され、これらの他端は全画素回路に共通の電極である共通電極Vcomに接続される。この画素回路では、走査信号が与えられるとき、すなわち走査信号線100が選択されるとき、上記電界効果トランジスタ102は導通状態になるため、データ信号線に印加される(データ信号の)電圧は補助容量素子104に印加される。その後、走査信号線100の選択期間が終了するとき、電界効果トランジスタ102が遮断状態となるが、補助容量素子104に蓄積(保持)された電荷により遮断時の電圧が保持され続ける。ここで、液晶素子103の光透過率または光反射率は、印加される電圧により変化するため、走査信号線100が選択されるとき、データ信号線101に対して画像データに応じた電圧を印加すれば、画素の表示輝度(表示階調)を画像データに合わせて変化させることができる。 20

**【0003】**

ここで、デジタル方式の液晶駆動用ドライバは、外部から与えられたデジタルデータに基づき予め定められた複数の基準電圧のうちの1つを選択して所定の画素回路の液晶素子に印加する。このデジタル方式の液晶駆動用ドライバは、表示階調数が増えるに従って内部の素子数が増えるため、表示階調数が増えるに従って製造コストが高くなる。そこで、デジタル方式の液晶駆動用ドライバを使用しながら、その内部素子数を増やすことなく表示階調を増やすことができる制御方式として、従来よりフレームレートコントロール方式(以下「FRC方式」と略称する)がある。 40

**【0004】**

このFRC方式は、複数のフレーム間で異なる2つの駆動電圧を所定の液晶素子に印加することにより視感上の擬似的な中間輝度を得る方式である。図21は、このFRC方式により3階調の多階調表示を行う例を示す図である。ここでは、連続するフレーム1とフレーム2との間で異なる2つの駆動電圧(高電圧と低電圧)が所定の液晶素子に印加されることにより、3階調の多階調表示が行われる。なお、ここでのフレーム周波数は60Hzであるものとし、各フレーム毎に印加電圧の極性が反転されるフレーム反転方式の交流化駆動が行われるものとする。 50

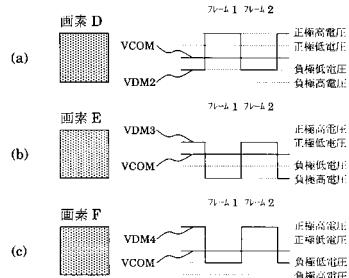

**【0005】**

図21をより詳しく説明すると、図21(a)は、輝度が最も低い画素Aを表示するための各フレームにおける駆動電圧を示し、図21(b)は、輝度が最も高い画素Bを表示するための各フレームにおける駆動電圧を示し、図21(c)は、中間輝度の画素Cを表示するための各フレームにおける駆動電圧を示す。図21(a)に示すように、共通電極の電位V<sub>COM</sub>を基準として、フレーム1, 2ともに低電圧が印加されるので画素の輝度は最も低い。また、図21(b)に示すように、フレーム1, 2ともに高電圧が印加されるので画素の輝度は最も高い。さらに、図21(c)に示すように、フレーム1では正極性の低電圧が印加され、フレーム2では負極性の高電圧が印加されるので、画素の輝度は、図21(a)に示す画素の輝度と図21(b)に示す画素の輝度との中間輝度となる。

## 【0006】

10

このFR<sub>C</sub>方式によって図21(c)に示す中間輝度を得る場合、フレーム1では低い輝度の画素が表示され、フレーム2では高い輝度の画素が表示されるので、連続するフレーム間で異なる輝度の画素が交互に表示されることになる。そのため、表示される画素C(の輝度変化)にはフレーム周波数の2分の1倍の周波数30Hzのフリッカ成分が含まれることになる。ここで一般的に、周波数50Hz以下のフリッカ成分は視感上目立つとされているので、例えば表示画面内の全ての画素が同位相で図21(c)に示す中間輝度で表示されると、表示画面全面でフリッカ成分が目立つようになる。そのため、表示装置の表示品位が低下する。

## 【0007】

20

そこで、従来より、図21(c)に示す中間輝度を得るために、所定の画素を形成する画素回路には図21(c)に示す駆動電圧を印加するほか、他の画素を形成する画素回路に對してはこの駆動電圧とは異なる駆動電圧を印加し、これらの画素回路により表示される画素が表示画面内に散らばるように混在させることにより、空間的に上記フリッカ成分を除去する手法がある。

## 【0008】

30

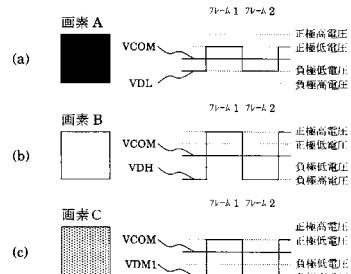

例えば、図21(c)に示す場合とは異なる駆動電圧を印加する場合としては、以下の3つの場合が考えられる。すなわち、フレーム1において正極性の高電圧が印加され、フレーム2において負極性の低電圧が印加される第1の場合、フレーム1において負極性の高電圧が印加され、フレーム2において正極性の低電圧が印加される第2の場合、およびフレーム1において負極性の低電圧が印加され、フレーム2において正極性の高電圧が印加される第3の場合である。図22は、これらの駆動電圧が印加される場合を示しており、より詳しくは、図22(a)は、第1の場合の駆動電圧と当該駆動電圧が印加されることにより形成される画素Dとを示し、図22(b)は、第2の場合の駆動電圧と当該駆動電圧が印加されることにより形成される画素Eとを示し、図22(c)は、第3の場合の駆動電圧と当該駆動電圧が印加されることにより形成される画素Fとを示す。これらの画素D, E, Fおよび図21(c)に示す画素Cは、空間的に散在するように、すなわち表示画面上の位置が散らばるように配置される。図23は、これらの画素C, D, E, Fの配置例を示す図である。この図23は、列1から列4までの各列の4行分の画素を示しており、図に示すC, D, E, Fの記号が上記画素C, D, E, Fに対応している。このように各画素を配置すれば、或るフレームにおいて同一の駆動電圧が印加されることにより表示される画素が表示画面上に均等に散らばるため、空間的に上記フリッカ成分が除去される。

40

## 【0009】

## 【特許文献1】

特開平8-43795号公報

## 【特許文献2】

特開平6-138846号公報

## 【特許文献3】

特開2001-34239号公報

## 【0010】

50

## 【発明が解決しようとする課題】

以上のような従来の F R C 方式では、同一の組み合わせの駆動電圧が印加されることにより形成される画素、例えば図 2 3 に示す画素 C , D , E , F の輝度は全て同じであることが前提となる。しかし、図 2 0 に示される電界効果トランジスタ 1 0 2 を含む等価回路には寄生容量が存在する。そのため、同一の駆動電圧（高電圧または低電圧）である正極性および負極性の電圧が印加される場合を比較すると、図 2 1 および図 2 2 に示す共通電極の電位 V C O M は、理想値からずれることがある。そのため、同一の組み合わせの駆動電圧が印加されることにより形成される画素、例えば画素 C , E と画素 D , F との中間輝度は同一であるべきにもかかわらず、差が生じることがある。

## 【0011】

10

特に、上記の輝度差は空間的にフリッカ成分を除去しようとする場合に視感上目立つことがある。すなわち、図 2 3 に示す列 1 および列 3 の画素 C , E は、図 2 1 ( c ) および図 2 2 ( b ) に示すように、正極性および負極性の高電圧のみで駆動されることにより形成され、図 2 3 に示す列 2 および列 4 の画素 D , F は、図 2 2 ( a ) および図 2 2 ( c ) に示すように、正極性の高電圧と負極性の低電圧のみで駆動されることにより形成されるため、一列おきでは同一輝度となるが、隣り合う列同士では輝度差が生じる。そのため列方向に延びるスジ状の輝度ムラが視感上目立つという問題がある。そして、このことは、例えば図 2 3 に示す画素 C と画素 F を入れ替えたとしても同様であり、この場合には行方向に延びるスジ状の輝度ムラが目立つことになる。

## 【0012】

20

そこで、本発明の目的は、F R C 方式による中間調表示方法であっても上記の輝度差が生じない中間調表示方法およびその方法を用いた表示装置を提供することである。また、さらなる本発明の目的は、F R C 方式による中間調表示方法であって空間的にフリッカ成分を除去しようとする場合にも、スジ状の輝度ムラが生じない中間調表示方法およびその方法を用いた表示装置を提供することである。

## 【0013】

## 【課題を解決するための手段】

第 1 の発明は、予め定められた複数の駆動電圧から所定の単位周期毎に選ばれる第 1 および第 2 の駆動電圧のいずれかの駆動電圧であって、前記単位周期に含まれる 1 つ以上のフレーム毎に極性を反転しフレーム毎に設定した駆動電圧に基づき、当該単位周期で ( 1 + N ) 階調 ( N は 2 以上の自然数 ) の多階調表示を行う液晶中間調表示方法において、前記単位周期を 2 N フレームとして、当該単位周期のうち、正の極性を有する第 1 の駆動電圧が設定されるフレーム数と負の極性を有する第 1 の駆動電圧が設定されるフレーム数とを同数とし、正の極性を有する第 2 の駆動電圧が設定されるフレーム数と負の極性を有する第 2 の駆動電圧が設定されるフレーム数とを同数とすることを特徴とする。

## 【0014】

30

このような第 1 の発明によれば、( 1 + N ) 階調の多階調表示を行う場合の単位周期を 2 N フレームとし、この 2 N フレーム内で高電圧または低電圧の正極性および負極性の電圧の印加回数が等しくなる。そのため、同一輝度であるべき各画素の平均輝度が均一となる。

## 【0015】

40

第 2 の発明は、第 1 の発明において、

前記単位周期の前半 N フレームのうち前記第 1 の駆動電圧が設定されるフレーム数と、前記単位周期の後半 N フレームのうち前記第 1 の駆動電圧が設定されるフレーム数とを同数とし、

前記前半 N フレームのうち前記第 2 の駆動電圧が設定されるフレーム数と、前記後半 N フレームのうち前記第 2 の駆動電圧が設定されるフレーム数とを同数とすることを特徴とする。

## 【0016】

このような第 2 の発明によれば、単位周期である 2 N フレームを前半と後半とに 2 等分し

50

た各 N フレーム内で、異なる 2 つの駆動電圧の印加回数が等しくなるように設定される。そのため、前半と後半との各 N フレーム間の平均輝度がほぼ等しくなるので、フリッカの発生が抑えられる。

【 0 0 1 7 】

第 3 の発明は、第 2 の発明において、

N が偶数の場合、k 番目のフレーム (k は N 未満の奇数とする) および (N + k + 1) 番目のフレームに設定される駆動電圧を等しくするとともに、(k + 1) 番目のフレームおよび (N + k) 番目のフレームに設定される駆動電圧を等しくし、N が奇数の場合、m 番目のフレーム (m は N 以下の自然数とする) および (m + N) 番目のフレームに設定される駆動電圧を等しくすることを特徴とする。

10

【 0 0 1 8 】

このような第 3 の発明によれば、例えば単位周期を 8 フレームとするとき、1 番目のフレームおよび 6 番目のフレームの駆動電圧と、2 番目のフレームおよび 5 番目のフレームの駆動電圧と、3 番目のフレームおよび 8 番目のフレームの駆動電圧と、4 番目のフレームおよび 7 番目のフレームの駆動電圧とがそれぞれ等しくなるように設定される。そのため、隣接するフレーム間で同一の駆動電圧が連續して印加される回数が最小となり、単位周期の前半部と後半部とを同じ駆動電圧の順番に設定する場合に比べ、さらに表示品位が向上する。

【 0 0 1 9 】

第 4 の発明は、第 1 から第 3 までのいずれか 1 つの発明において、

20

複数の画素からなる表示単位で多階調表示を行うため、前記表示単位に含まれる画素毎に所定の階調を表示させる第 1 または第 2 の駆動電圧を設定することを特徴とする。

【 0 0 2 0 】

このような第 4 の発明によれば、複数の画素からなる表示単位で多階調表示を行うため、表示階調数が向上するとともに、空間的にフリッカ成分が除去される。

【 0 0 2 1 】

第 5 の発明は、装置外部から与えられる表示データに応じて、予め定められた複数の駆動電圧から所定の単位周期毎に選ばれる第 1 および第 2 の駆動電圧のいずれかの駆動電圧であって、前記単位周期に含まれる 1 つ以上のフレーム毎に極性を反転しフレーム毎に設定した駆動電圧に基づき、当該単位周期で (1 + N) 階調 (N は 2 以上の自然数) の多階調表示を行う液晶表示装置において、

前記単位周期を 2 N フレームとして、当該単位周期のうち、正の極性を有する第 1 の駆動電圧が設定されるフレーム数と負の極性を有する第 1 の駆動電圧が設定されるフレーム数とを同数とし、正の極性を有する第 2 の駆動電圧が設定されるフレーム数と負の極性を有する第 2 の駆動電圧が設定されるフレーム数とを同数とする電圧決定手段と、

30

前記電圧決定手段により設定された駆動電圧に基づき、多階調表示を行う表示手段とを備える。

【 0 0 2 2 】

第 6 の発明は、第 5 の発明において、

40

前記電圧決定手段は、

前記単位周期である 2 N フレームのうち前記表示データに対応するフレームを決定するフレーム決定手段と、

前記単位周期に設定される駆動電圧を当該単位周期に含まれるフレームに関連させて記憶するタイミング記憶手段と

前記フレーム決定手段により決定されるフレームに基づき、前記タイミング記憶手段に記憶される、当該決定されるフレームに関連する駆動電圧を決定し、前記表示手段に与える印加電圧決定手段と

を含むことを特徴とする。

【 0 0 2 3 】

第 7 の発明は、第 5 または第 6 の発明において、

50

前記電圧決定手段は、複数の画素からなる表示単位で多階調表示を行うため、前記表示単位に含まれる画素毎に所定の階調を表示させる第1または第2の駆動電圧を設定し、前記表示手段は、前記駆動電圧に基づき、前記表示単位で多階調表示を行うことを特徴とする。

【0024】

【発明の実施の形態】

以下、本発明の一実施形態につき添付図面を参照して説明する。

本実施形態に係る液晶表示装置は、デジタル24ビット（RGB各8ビット）で入力される映像信号に対し、以下に詳述する中間調（多階調）表示方法に基づく演算処理を行う。この処理により、本液晶表示装置の液晶パネルがデジタル18ビット（RGB各6ビット）入力の構成であるにもかかわらず、デジタル24ビット相当の画質品位で表示が可能となる。

【0025】

図1は、この液晶表示装置の構成を示すブロック図である。この液晶表示装置は、RGB各色成分を処理するため、RGB各色毎に、データ分離器1、画素位置検出回路2、フレーム番号決定回路3、印加タイミング記憶回路4、印加電圧決定回路5、加算処理回路6、およびタイミング調整回路7を備えており、これらにより所定のデジタル信号処理が施されたデジタル信号を生成する。本液晶表示装置は、液晶素子を含む画素回路をマトリクス状に複数配置してなる液晶パネル8をさらに備えており、上記デジタル信号に基づき、デジタル24ビット相当の画質品位で表示を行う。なお、液晶パネル8は、所定の画素回路に所定のデータ信号を与える液晶駆動用ドライバと、所定の画素回路を選択するための所定の走査信号を与える選択用ドライバとを含むものとする。また、上記画素回路は、図20に示す従来の画素回路と同様の構成であるのでここでは説明を省略する。この液晶表示装置に与えられる映像信号は、RGBの各色別にそれぞれ8ビットのデジタルデータからなる。また、本液晶表示装置には、上記映像信号とともに、垂直同期信号（VS）、水平同期信号（HS）、データイネーブル信号（DE）、およびクロック信号（CLK）からなる一般的なデジタルコントロール信号が与えられる。

【0026】

ここで、本液晶表示装置の各構成要素の動作につき詳述する前に、FRC方式により中間調表示を得る方法について説明する。本液晶表示装置は、2つの異なる駆動電圧（低電圧および高電圧）を所定の画素回路に印加する構成である。この構成で、所定の中間調表示を得るための単位周期（以下「フレーム周期」という）を2フレームとした中間調表示を行う方法では、図21に示すように3階調の中間調表示が可能である。すなわち、フレーム周期をNフレーム（Nは2以上の自然数）とすれば、（N+1）階調の中間調表示が可能である。以下では、フレーム周期を4フレームとして5階調の中間調表示を行う場合を応用することにより、フレーム周期をその2倍の8フレームとし、駆動電圧の組み合わせを複数設定することにより253階調の中間調表示が行われる。すなわち、本液晶表示装置では、与えられる8ビットのデジタルデータのうちの下位2ビットに基づき上記FRC方式が使用され、上記デジタルデータのうちの上位6ビットで $2^6$ 個の駆動電圧が定められる。これらの $2^6$ 個の駆動電圧のうち互いの電圧差が最小となる2つの駆動電圧、すなわち隣接する2つの駆動電圧を組み合わせることにより、下表に示すような表示階調0から252までの253階調の中間調表示を得ている。

【表1】

| 上位 6 ビットで決定される駆動電圧 (8 ビットデジタル表現) |   |   |    |   |     |     |     |     | 表示階調<br>(8 ビットデジタル表現) |

|----------------------------------|---|---|----|---|-----|-----|-----|-----|-----------------------|

| 0                                | 4 | 8 | 12 | ~ | 240 | 244 | 248 | 252 |                       |

| 8                                | 0 |   |    |   |     |     |     |     | 0                     |

| 6                                | 2 |   |    |   |     |     |     |     | 1                     |

| 4                                | 4 |   |    |   |     |     |     |     | 2                     |

| 2                                | 6 |   |    |   |     |     |     |     | 3                     |

|                                  | 8 | 0 |    |   |     |     |     |     | 4                     |

|                                  | 6 | 2 |    |   |     |     |     |     | 5                     |

|                                  | 4 | 4 |    |   |     |     |     |     | 6                     |

|                                  | 2 | 6 |    |   |     |     |     |     | 7                     |

|                                  | 8 | 0 |    |   |     |     |     |     | 8                     |

|                                  | 6 | 2 |    |   |     |     |     |     | 9                     |

|                                  | 4 | 4 |    |   |     |     |     |     | 10                    |

|                                  | 2 | 6 |    |   |     |     |     |     | 11                    |

|                                  |   |   |    |   |     |     |     |     | ~                     |

|                                  |   |   |    | 8 | 0   |     |     |     | 240                   |

|                                  |   |   |    | 6 | 2   |     |     |     | 241                   |

|                                  |   |   |    | 4 | 4   |     |     |     | 242                   |

|                                  |   |   |    | 2 | 6   |     |     |     | 243                   |

|                                  |   |   |    |   | 8   | 0   |     |     | 244                   |

|                                  |   |   |    |   | 6   | 2   |     |     | 245                   |

|                                  |   |   |    |   | 4   | 4   |     |     | 246                   |

|                                  |   |   |    |   | 2   | 6   |     |     | 247                   |

|                                  |   |   |    |   |     | 8   | 0   |     | 248                   |

|                                  |   |   |    |   |     | 6   | 2   |     | 249                   |

|                                  |   |   |    |   |     | 4   | 4   |     | 250                   |

|                                  |   |   |    |   |     | 2   | 6   |     | 251                   |

|                                  |   |   |    |   |     | 0   | 8   |     | 252                   |

10

20

30

## 【0027】

この表では、フレーム周期（8 フレーム）で印加される隣接する 2 つの駆動電圧と、これらの駆動電圧により得られる表示階調との関係が示されており、それぞれの値は、8 ビットデジタル表現で示されている。なお、上記駆動電圧は、8 ビットのデジタルデータのうち上位 6 ビットにより決定される離散値となる。また、上表の各行内に記載される一連の 2 つの数値は、当該列に対応する駆動電圧が印加されるフレームの数を示している。さらに、上表の表示階調は、フレーム周期内に表示される画素の表示階調を積算して得られる値をフレーム周期数で割ることにより、単位時間内の平均的な輝度として得られる値である。

## 【0028】

例えば、上表の 2 行目を参照すると、駆動電圧 0 を印加されるフレーム数が 6 であり、駆動電圧 4 (8 ビットデジタル表現) を印加されるフレーム数が 2 であるとき、得られる表示階調は  $(0 \times 6 + 4 \times 2) / 8 = 1$  (8 ビットデジタル表現) であることがわかる。

## 【0029】

なお、上記映像信号は、典型的には、各フレーム周期内で全画素の輝度が変化しない静止画像を示す信号であるが、上記映像信号が動画像を示す信号であったとしても、全画素の輝度はフレーム周期内ではそれほど大きく変化しないため、特に問題とはならない。

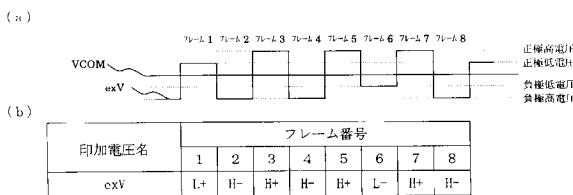

## 【0030】

次に、上記のような 8 フレームをフレーム周期とするときに印加される電圧波形および極性について説明する。図 2 は、上記電圧波形および極性を例示する図である。より詳しく

40

50

は、図2(a)では、所定の液晶素子に高電圧または低電圧の2つの異なる駆動電圧が極性変化を伴って印加されるときの波形例が示されており、図2(b)は、図2(a)に示される波形例が極性を付した記号の形で表形式により示されている。図では、上記波形例がe×Vとして示されており、図2(b)に示す記号であるH+は正極性の高電圧(正極高電圧)を、H-は負極性の高電圧(負極高電圧)を、L+は正極性の低電圧(正極低電圧)を、L-は負極性の低電圧(負極低電圧)をそれぞれ示している。

#### 【0031】

図2に示されるように、液晶パネル8の各液晶素子は、液晶の性質上交流化駆動することが必要であるため、印加電圧の極性がフレーム毎に反転されるフレーム反転方式の交流化駆動が行われる。さらに、この液晶パネル8は、各行毎に交互に印加電圧の極性を反転駆動するライン反転方式の交流化駆動を行うものとする。ここで、8フレームとも高電圧が印加されたときの画素の表示階調を100%とし、8フレームとも低電圧が印加されたときの画素の表示階調を0%とすると、上記波形例e×Vにより表示される画素の表示階調は、8フレームのうちの6フレームにおいて高電圧が印加され、残りの2フレームにおいて低電圧が印加されているので、75%の中間調となる。

#### 【0032】

さらに、本液晶表示装置では、4つの画素からなる画素パターンを表示単位とする空間的な中間調表示方法が併用される。図3は、上記表示単位である2×2の画素からなる画素パターンを示す図である。この表示単位を以下では「2×2画素パターン」または「画素パターン」という。なお、図に示すa～dの記号は画素a～dを示している。ここで、上記隣接する2つの駆動電圧のうちの高電圧が印加されることにより形成される画素を明るい画素と呼び、低電圧が印加されることにより形成される画素を暗い画素と呼ぶものとするとき、上記画素パターンは、明るい画素と暗い画素との組み合わせにより5つの階調を表示することができる。図4は、4つの画素の組み合わせにより得られる画素パターンと、当該画素パターンにより得られる表示階調とを示す図である。この図4に示される白いマス目は明るい画素を示し、黒いマス目は暗い画素を示す。

#### 【0033】

本液晶表示装置は、図3に示す画素パターンにより図4に示す5つの階調を表示し、この画素パターンを液晶パネルの画面内に複数配置する。図5は、この液晶パネルにおける画素の配置例を示す図である。本液晶表示装置は、図5に示すように同一の駆動電圧が印加されることにより形成される画素が表示画面内に散らばるように混在させることにより、空間的に上記フリッカ成分を除去する。さらに、本液晶表示装置では、後述するように、画素a, b, c, dを形成するための各駆動電圧の位相ができる限り同一にならないよう設定することにより、さらにフリッカが軽減されている。なお、上記2×2画素パターンは一例であって、組み合わせる画素の数や画素パターンの形状には様々な態様を適用することができる。

#### 【0034】

次に、本液晶表示装置の図1に示す各構成要素の動作につき説明する。前述したように、本液晶表示装置は、RGB各色成分を処理するためRGB各色毎に各構成要素が設けられており、映像信号を処理する際には、RGB各色成分毎に各構成要素が同じ動作を行う。したがって、ここでは説明の便宜のため、緑色成分に関連する処理動作のみについて、図1を参照して説明する。

#### 【0035】

データ分離器1は、外部から映像信号として与えられる8ビットのデジタルデータを上位6ビットと下位2ビットとに分離する。画素位置検出回路2は、上記デジタルデータとともに受け取ったコントロール信号に基づき、現在のデジタルデータにより示される画素の位置が、図3に示す2×2画素パターンにおける画素a, b, c, dのいずれになるのかを検出し、画素位置情報として出力する。フレーム番号決定回路3は、フレーム周期に含まれる各フレームに対して順番にフレーム番号が付されるようにカウントすることにより、受け取った上記コントロール信号に基づき、現在のフレームが当該フレーム周期のうち

10

20

30

40

50

の何番目のフレームであるかを決定し、フレーム番号情報として出力する。印加タイミング記憶回路4は、 $2 \times 2$ 画素パターンを形成する各画素回路に対して印加される電圧であって、上記デジタルデータの下位2ビットにより決定される駆動電圧の高低（高電圧であるか低電圧であるか）およびその極性をフレーム順に記憶している。以下、この印加タイミング記憶回路4に記憶された駆動電圧の印加順序について説明する。

【0036】

図6は、上記デジタルデータの下位2ビットが‘00’のときの各フレームにおける画素a、b、c、dの駆動電圧を示し、以下、図7は、上記下位2ビットが‘01’のとき、図8は、上記下位2ビットが‘10’のとき、図9は、上記下位2ビットが‘11’のときの、各フレームにおける駆動電圧をそれぞれ示している。これらの図に示す記号は図2に示す記号と同義であり、画素パターンも図4に示すパターンと同じである。また、階調名は、最も暗い階調を階調1として表示階調を5段階で示した名称であり、印加電圧名は、上記下位2ビットの数字と表示画素名とを結合させた名称である。なお、最も明るい階調である階調5のときの各フレームにおける駆動電圧は示されていないが、このときには図6に示す各フレームにおける画素a、b、c、dの駆動電圧が全て高電圧とされるわけではなく、上記の表に示されるように、当該隣接する2つの駆動電圧がそれぞれ1段階上昇したときの隣接する2つの駆動電圧が全て低電圧とされる場合に等しくなる。

【0037】

ここで、図7から図9までを参照すると、画素a、b、c、dの駆動電圧の位相が同一にならないように設定されているため、或るフレームでは隣接する2つの画素の輝度が異なる場合がある反面、他のフレームでは上記隣接する2つの画素の輝度が同じ場合があり、結果的に単位フレーム全体ではフリッカが軽減されることになる。なお、これらの図に示す駆動電圧の印加順序は一例であって、他の様々な印加順序が適用可能である。

【0038】

また、図7から図9までを参照すると、フレーム周期において、高電圧または低電圧のそれぞれの駆動電圧につき、正極性および負極性の電圧の印加回数が等しくなる。そのため、同一輝度（同一階調）であるべき各画素の平均輝度が均一となるため、表示品位が向上する。

【0039】

さらに、図6から図9までを参照すると、フレーム周期である8フレームのうちの前半の4フレーム（フレーム番号1～4）における各駆動電圧（高電圧および低電圧）の印加回数と、後半の4フレーム（フレーム番号5～8）における上記印加回数とは等しく設定されている。そのため、前半のフレームでの平均輝度と後半のフレームでの平均輝度がほぼ等しくなるためフリッカの発生が抑えられ、高品位の表示が可能となるので好適である。このように、フレーム周期を2Nフレームとするとき、当該フレーム周期を前半部と後半部とに2等分した各Nフレームで異なる2つの駆動電圧の印加回数がそれぞれ等しくなるように設定すれば、フレーム周期の前半部および後半部を構成する各Nフレーム間の平均輝度がほぼ等しくなる。そのため、フレーム周期内でのフリッカの発生が抑えられた高品位の表示が可能となる。

【0040】

さらにまた、図6から図9までに示すように、フレーム番号1およびフレーム番号6の駆動電圧と、フレーム番号2およびフレーム番号5の駆動電圧と、フレーム番号3およびフレーム番号8の駆動電圧と、フレーム番号4およびフレーム番号7の駆動電圧とがそれぞれ等しくなるように設定する。すなわち、フレーム周期を2Nフレームとするとき、Nが偶数の場合はk番目のフレーム（ここでkはN未満の奇数とする）および（N+k+1）番目のフレームの駆動電圧と、（k+1）番目のフレームおよび（N+k）番目のフレームの駆動電圧とがそれぞれ等しくなるように設定する。なお、Nが奇数の場合、m番目のフレーム（mはN以下の自然数とする）および（m+N）番目のフレームに設定される駆動電圧を等しくする。そうすれば、フレーム周期において高電圧または低電圧のそれぞれの駆動電圧につき、正極性および負極性の電圧の印加回数を等しくしながら、隣接するフ

10

20

30

40

50

フレーム間で同一の駆動電圧が連續して印加される回数が最小となる。そのため、フレーム周期内で同じ駆動電圧（高電圧または低電圧）が設定されるフレームが適宜に離れる（ばらつく）ため、さらに表示品位が向上する。なお、これに対して、Nが偶数の場合にフレーム周期の前半部と後半部とを同じ順番になるように駆動電圧を設定すると、フレーム周期において高電圧または低電圧の印加回数は等しくなるが、正極性および負極性の電圧の印加回数は等しくならないため、好適とはならない。

【0041】

印加電圧決定回路5は、上記デジタルデータの下位2ビットと、画素位置検出回路2から出力される画素位置情報と、フレーム番号決定回路3から出力されるフレーム番号情報とを受け取り、以上のような印加タイミング記憶回路4に記憶されている印加順序に従って、各画素回路に印加すべき駆動電圧を決定し、この決定された駆動電圧が高電圧であるときには‘1’とし、低電圧であるときには‘0’とする1ビットの高低情報を加算処理回路6に与える。

【0042】

加算処理回路6は、データ分離器1から与えられたデジタルデータの上位6ビットに対して、印加電圧決定回路5から与えられた上記高低情報の1ビットを加算して得られる6ビットのデータを液晶パネル8に送出する。なお、この加算処理では、デジタルデータが‘1111111’であって高低情報が‘1’の場合に出力データがオーバフローする。このことを防ぐため、上記場合にのみ処理結果が‘1111111’とされるものとする。

【0043】

タイミング調整回路7は、上記コントロール信号を演算処理に必要な時間だけ遅延させることにより、表示タイミングを適宜に調整する。液晶パネル8は、加算処理回路6からのR B G各色成分別の6ビットのデジタルデータと、タイミング調整回路7からのコントロール信号とに基づいて、所定の画像を表示する。

【0044】

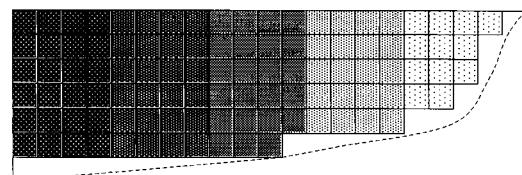

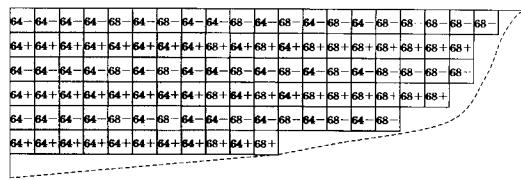

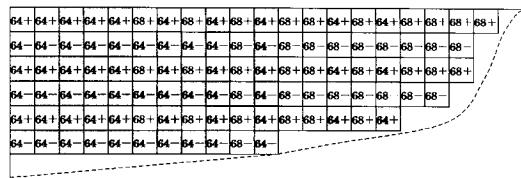

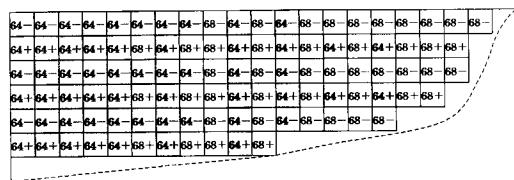

次に、実際の映像信号を本液晶表示装置に与えて演算処理した場合について説明する。図10は、本液晶表示装置に与えられる映像信号により表わされる画像の左上部分を示す図である。この画像は静止画であって水平方向（右方向）へ4画素おきに階調が1づつ増えしていくグレースケール画像である。図11は、図10に示す画像の各画素の階調（および極性）を8ビットのデジタルデータに置き換えて示した図である。この図11に示すデジタルデータを本液晶表示装置で演算処理した結果を各フレーム毎に図12から図19までに示す。すなわち、図12は、フレーム番号1における各画素の階調をデジタルデータで示した図であり、以下、図13はフレーム番号2、図14はフレーム番号3、図15はフレーム番号4、図16はフレーム番号5、図17はフレーム番号6、図18はフレーム番号7、図19はフレーム番号8における、それぞれの画素の階調をデジタルデータで示した図である。なお、これらの図に示す階調は、本液晶表示装置で用いられるライン反転方式の液晶パネル画面上における階調数とその極性を示しており、この階調数は、駆動電圧を示す6ビットデータの下位に2ビットのデータ‘00’を付加して拡張した8ビットのデジタルデータが8ビット表現で示されている。また、本液晶表示装置のリフレッシュレートは60Hzであり、フレーム番号1からフレーム番号8までの各フレーム画像は、フレーム番号順に16.67ms毎に順次繰り返して表示される。このような中間調表示方式により、FRC方式によっても視感上の画素の輝度差が生じず、またスジ状の輝度ムラも生じない。

【0045】

なお、本液晶表示装置では、交流化駆動方式として行毎に反転駆動するライン反転方式である水平ライン反転方式が使用されるが、列毎に反転駆動する垂直ライン方式や、画素毎に反転駆動するドット反転方式が使用されてもよい。

【0046】

また、本液晶表示装置では、図3に示す画素パターンによる空間的な中間調表示方法が併用されるが、併用されない構成であってもよい。併用されない構成であっても、同一の駆

10

20

30

40

50

動電圧（高電圧または低電圧）の正極性および負極性の電圧がフレーム周期で同数に設定されることにより、同一輝度であるべき画素のフレーム周期での平均輝度が等しくなるため、液晶表示装置の表示品位が向上する。

【0047】

【発明の効果】

本発明の液晶中間調表示方法では、 $(1 + N)$ 階調の多階調表示を行う場合の単位周期を $2N$ フレームとし、この $2N$ フレーム内で高電圧または低電圧の正極性および負極性の電圧の印加回数が等しくなる。そのため、同一輝度であるべき各画素の平均輝度が均一となるため、表示品位が向上する。

【0048】

さらに、本発明の液晶中間調表示方法では、単位周期である $2N$ フレームを前半と後半とに $2$ 等分した各 $N$ フレーム内で、異なる $2$ つの駆動電圧の印加回数が等しくなるように設定される。そのため、前半と後半との各 $N$ フレーム間の平均輝度がほぼ等しくなるので、フリッカの発生が抑えられた高品位の表示が可能となる。

【0049】

さらにまた、本発明の液晶中間調表示方法では、単位周期を $2N$ フレームとするとき、 $N$ が偶数の場合は、 $k$ 番目のフレームおよび $(N + k + 1)$ 番目のフレームの駆動電圧と、 $(k + 1)$ 番目のフレームおよび $(N + k)$ 番目のフレームの駆動電圧とがそれぞれ等しくなるように設定される。また、 $N$ が奇数の場合は、 $m$ 番目のフレームおよび $(m + N)$ 番目のフレームに設定される駆動電圧を等しくする。そのため、隣接するフレーム間で同一の駆動電圧が連續して印加される回数が最小となり、単位周期の前半部と後半部とを同じ駆動電圧の順番に設定する場合に比べ、さらに表示品位が向上する。

【0050】

さらにまた、本発明の液晶中間調表示方法では、複数の画素からなる表示単位で多階調表示を行うため、表示階調数が向上するとともに、空間的にフリッカ成分が除去される。

【図面の簡単な説明】

【図1】本発明の一実施形態に係る液晶表示装置の構成を示すブロック図である。

【図2】上記一実施形態における駆動電圧の波形および極性を例示する図である。

【図3】上記一実施形態における $2 \times 2$ 画素パターンを示す図である。

【図4】上記一実施形態における画素パターンと、当該画素パターンにより得られる表示階調とを示す図である。

【図5】上記一実施形態における液晶パネルにおける画素の配置例を示す図である。

【図6】上記一実施形態におけるデジタルデータの下位2ビットが‘00’のときの各フレームにおける画素の駆動電圧を示す図である。

【図7】上記一実施形態におけるデジタルデータの下位2ビットが‘01’のときの各フレームにおける画素の駆動電圧を示す図である。

【図8】上記一実施形態におけるデジタルデータの下位2ビットが‘10’のときの各フレームにおける画素の駆動電圧を示す図である。

【図9】上記一実施形態におけるデジタルデータの下位2ビットが‘11’のときの各フレームにおける画素の駆動電圧を示す図である。

【図10】上記一実施形態に係る液晶表示装置に与えられる映像信号により表わされる画像の左上部分を示す図である。

【図11】図10に示す画像の各画素の階調（および極性）を8ビットのデジタルデータに置き換えて示した図である。

【図12】上記一実施形態におけるフレーム番号1の各画素の階調をデジタルデータで示した図である。

【図13】上記一実施形態におけるフレーム番号2の各画素の階調をデジタルデータで示した図である。

【図14】上記一実施形態におけるフレーム番号3の各画素の階調をデジタルデータで示した図である。

10

20

30

40

50

【図15】上記一実施形態におけるフレーム番号4の各画素の階調をデジタルデータで示した図である。

【図16】上記一実施形態におけるフレーム番号5の各画素の階調をデジタルデータで示した図である。

【図17】上記一実施形態におけるフレーム番号6の各画素の階調をデジタルデータで示した図である。

【図18】上記一実施形態におけるフレーム番号7の各画素の階調をデジタルデータで示した図である。

【図19】上記一実施形態におけるフレーム番号8の各画素の階調をデジタルデータで示した図である。

【図20】従来の液晶表示装置に含まれる画素回路の等価回路を示す図である。

【図21】従来のFRC方式により3階調の多階調表示を行う例を示す図である。

【図22】図21(c)に示す場合とは異なる駆動電圧が印加する場合を示す図である。

【図23】図22に示す画素C, D, E, Fの配置例を示す図である。

## 【 符号の説明 】

- 1 ... データ分離器

- 2 ... 画素位置検出回路

- 3 ... フレーム番号決定回路

- 4 ... 印加タイミング記憶回路

- 5 ... 印加電圧決定回路

- 6 ... 加算処理回路

- 7 ... タイミング調整回路

- 8 ... 液晶パネル

10

20

【 図 1 】

【 図 2 】

【 図 3 】

〔 図 4 〕

| 階調        | 画素パターン例 |

|-----------|---------|

| 表示階調：0%   |         |

| 表示階調：25%  |         |

| 表示階調：50%  |         |

| 表示階調：75%  |         |

| 表示階調：100% |         |

## □ …明るい要素

【 図 5 】

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| a | b | a | b | a | b | a | b |

| d | c | d | c | d | c | d |   |

| a | b | a | b | a | b | a |   |

| d | c | d | c | d | c | d |   |

| a | b | a | b | a | b | a |   |

| d | c | d | c | d | c |   |   |

| a | b | a | b | a | b | a |   |

| d | c |   |   |   |   |   |   |

| a | b | a | b | a |   |   |   |

| d | c |   |   |   |   |   |   |

【 図 6 】

【 図 7 】

| <端子記号> |      | フレーム番号 |    |    |    |    |    |    |    |

|--------|------|--------|----|----|----|----|----|----|----|

| 印加電圧名  | 印加電圧 | 1      | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

| 01a    | H+   | L-     | L+ | L- | L+ | H- | L+ | L- |    |

| 01b    | L+   | L-     | L+ | H- | L+ | H- | L+ | H+ | L- |

| 01c    | L-   | L+     | H+ | L- | L+ | L- | L+ | H+ |    |

| 01d    | L-   | H+     | L- | L+ | H- | L+ | L- | L+ |    |

【 図 1 1 】

【 四 1 2 】

【 四 13 】

〔 図 8 〕

| <階調3> |     | フレーム番号 |    |    |    |    |    |    |    |

|-------|-----|--------|----|----|----|----|----|----|----|

|       |     | 1      | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

| 印加電圧名 | 10a | L+     | H- | H+ | L- | H+ | L- | L+ | H- |

|       | 10b | H+     | L- | L+ | H- | L+ | H- | H+ | L- |

|       | 10c | L-     | H+ | L- | H+ | H- | L+ | H- | L+ |

|       | 10d | H-     | L+ | H- | L+ | L- | H+ | L- | H+ |

【 図 9 】

| <階調4> |  | フレーム番号 |    |    |    |    |    |    |    |

|-------|--|--------|----|----|----|----|----|----|----|

| 印加電圧名 |  | 1      | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

| 11a   |  | L+     | H+ | H+ | H- | H+ | L- | H+ | H- |

| 11b   |  | H+     | H- | H+ | L- | H+ | H- | L+ | H- |

| 11c   |  | H-     | H+ | L- | H+ | H- | H+ | H- | L+ |

| 11d   |  | H+     | L+ | H- | H+ | L- | H+ | H- | H+ |

【 図 1 0 】

【図14】

【 図 15 】

【 16 】

【 図 17 】

【 図 1 8 】

〔 19 〕

【 図 2 2 】

【 図 2 3 】

| 列 1 | 列 2 | 列 3 | 列 4 |  |

|-----|-----|-----|-----|--|

| C   | D   | C   | D   |  |

| E   | F   | E   | F   |  |

| C   | D   | C   | D   |  |

| E   | F   | E   | F   |  |

|     |     |     |     |  |

【 図 2 0 】

【 図 2 1 】

【図23】

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 4 1 C |

| G 0 9 G | 3/20 | 6 4 1 E |

| G 0 9 G | 3/20 | 6 4 1 K |

| G 0 9 G | 3/20 | 6 4 2 A |

| H 0 4 N | 5/66 | 1 0 2 B |

F ターム(参考) 5C080 AA10 BB05 DD05 DD06 EE29 FF11 JJ02 JJ04 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶半色调显示方法和使用该方法的液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP2005010520A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 公开(公告)日 | 2005-01-13 |

| 申请号            | JP2003175251                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 申请日     | 2003-06-19 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| [标]发明人         | 井上明彦                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 发明人            | 井上 明彦                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36 H04N5/66                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| CPC分类号         | G09G3/3648 G09G3/2025 G09G3/2051 G09G3/2055 G09G3/3614 G09G2310/06 G09G2320/0247                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/133.575 G09G3/20.611.E G09G3/20.621.B G09G3/20.641.C G09G3/20.641.E G09G3/20.641.K G09G3/20.642.A H04N5/66.102.B                                                                                                                                                                                                                                                                                                                                                       |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA33 2H093/NA55 2H093/NC03 2H093/NC16 2H093/NC28 2H093/NC34 2H093/ND06 2H093/ND10 5C006/AA14 5C006/AA16 5C006/AC21 5C006/AC28 5C006/AF44 5C006/AF46 5C006/AF51 5C006/AF53 5C006/AF71 5C006/BB16 5C006/BC11 5C006/BC16 5C006/BF14 5C006/BF24 5C006/FA22 5C006/FA23 5C006/FA56 5C058/AA06 5C058/BA01 5C058/BA07 5C058/BB11 5C058/BB14 5C080/AA10 5C080/BB05 5C080/DD05 5C080/DD06 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080/JJ05 2H193/ZA04 2H193/ZC15 2H193/ZD25 2H193/ZF03 |         |            |

| 代理人(译)         | 岛田彰                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 其他公开文献         | <a href="#">JP4390483B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

### 摘要(译)

解决的问题：提供一种半色调显示方法和使用该方法的显示装置，其中即使通过FRC方法，甚至在试图在空间上去除闪烁成分时，像素亮度也不发生差异。提供。液晶显示装置包括用于每种RGB颜色的数据分离器，像素位置检测电路，帧数确定电路，施加定时存储电路，施加电压确定电路，加法处理电路和加法处理电路。提供定时调整电路7，将(1+N)个灰度的多灰度显示时的单位周期设为2N帧，在该2N帧内，将高电压或低电压正电压和负电压进行设定。设置驱动电压，以使施加次数相等。结果，在以矩阵状排列包括液晶元件的多个像素电路的液晶面板8上显示的每个像素的平均亮度变得均匀，从而提高了显示质量。[选型图]图1