(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-3802

(P2005-3802A)

(43) 公開日 平成17年1月6日(2005.1.6)

(51) Int.Cl.<sup>7</sup>

G02F 1/1343

G02F 1/1368

F 1

G02F 1/1343

G02F 1/1368

テーマコード(参考)

2 H 0 9 2

審査請求 未請求 請求項の数 5 O L (全 11 頁)

(21) 出願番号

特願2003-165305 (P2003-165305)

(22) 出願日

平成15年6月10日 (2003.6.10)

(71) 出願人 302020207

東芝松下ディスプレイテクノロジー株式会社

東京都港区港南4-1-8

100058479

弁理士 鈴江 武彦

100091351

弁理士 河野 哲

100088683

弁理士 中村 誠

100108855

弁理士 蔵田 昌俊

100084618

弁理士 村松 貞男

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】広い視野角特性を有するとともに、表示品位を向上することが可能な液晶表示装置を提供することを目的とする。

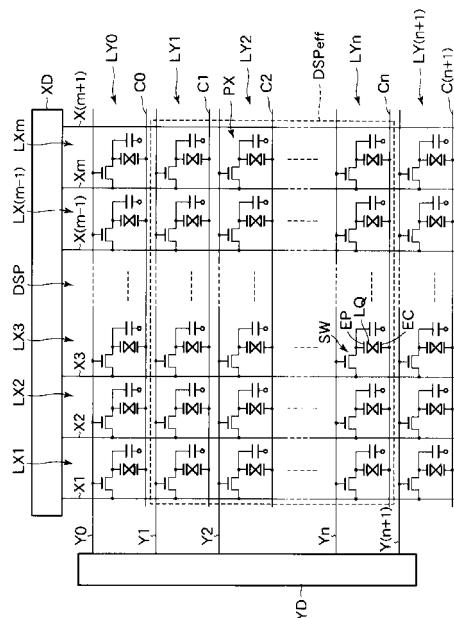

【解決手段】液晶表示パネルは、マトリクス状に配置された複数の画素P Xからなる有効表示部D S P<sub>e f f</sub>を備えている。アレイ基板は、行方向に延出した複数の走査配線Yと、各走査配線Yに交差するよう列方向に延出した複数の信号配線Xと、走査配線Y間に配置された共通配線Cと、走査配線Yと信号配線Xとの交差部に設けられたスイッチング素子S Wと、スイッチング素子S Wに電気的に接続された画素電極E Pと、共通配線Cに電気的に接続され画素電極E Pとの間で液晶層L Qに含まれる液晶分子をスイッチングするための電界を形成する共通電極E Cと、を備えている。有効表示部D S P<sub>e f f</sub>において、列方向に配列された複数の画素からなる画素列L Xは、隣接する2本の信号配線間に配置されている。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

一対の基板間に液晶層を挟持して構成され、マトリクス状に配置された複数の画素からなる有効表示部を備えた液晶表示装置であって、

一方の基板は、

行方向に延出された複数の走査配線と、

前記各走査配線に交差するよう列方向に延出された複数の信号配線と、

前記走査配線間に配置された共通配線と、

前記走査配線と前記信号配線との交差部に設けられたスイッチング素子と、

前記スイッチング素子に電気的に接続された画素電極と、

前記共通配線に電気的に接続され前記画素電極との間で前記液晶層に含まれる液晶分子をスイッチングするための電界を形成する共通電極と、を備え、

前記有効表示部において、列方向に配列された複数の画素からなる画素列は、隣接する2本の信号配線間に配置されたことを特徴とする液晶表示装置。

**【請求項 2】**

前記有効表示部がm列の画素列を備え、前記信号配線が(m+1)本配置されたことを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

前記信号配線は、m列の画素列にそれぞれ映像信号を供給するためのm本の映像信号線と、固定電圧が供給された1本の副信号線と、からなることを特徴とする請求項2に記載の液晶表示装置。

**【請求項 4】**

前記有効表示部の端部に配置された画素列は、この画素列に映像信号を供給するための前記映像信号線と、前記副信号線との間に配置されたことを特徴とする請求項3に記載の液晶表示装置。

**【請求項 5】**

前記有効表示部の両端部に配置された画素列を構成する各画素の外側に配置され前記共通配線に電気的に接続された副共通電極を備えたことを特徴とする請求項1に記載の液晶表示装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

この発明は、液晶表示装置に係り、特に、アレイ基板の主面にほぼ平行な水平電界によって液晶分子をスイッチングするIPS(In-Plane Switching)モードの液晶表示装置に関する。

**【0002】****【従来の技術】**

近年、CRTディスプレイに代わる平面表示装置が盛んに開発されており、中でも液晶表示装置は、軽量、薄型、低消費電力等の利点から特に注目を集めている。特に、各画素にスイッチング素子を組み込んだアクティブマトリクス型液晶表示装置においては、IPS(In-Plane Switching)モードが注目されている。

**【0003】**

このIPSモードの液晶表示装置は、液晶層を挟持する基板間で液晶分子が捻れていないホモジニアス構造をとる液晶表示パネルを備えている。この液晶表示パネルは、同一基板上に形成された画素電極と共通電極とを備え、基板の主面に対してほぼ平行な水平電界で液晶分子をスイッチングする。また、液晶表示パネルは、それぞれの外面に互いに偏光板方向が直交するように配置された偏光板を備えている。一方の偏光板は、その偏光軸が一方の基板に接している液晶分子の長軸方向と平行または直交するように配置されている。

**【0004】**

IPSモード液晶表示装置は、このような偏光板の配置により、電圧無印加時に黒色画面

10

20

30

40

50

を表示し、映像信号に対応した電圧を画素電極に印加することにより徐々に光透過率が増加して白色画面を表示する。このような表示特性が得られるのは、以下のような原理に基づく。すなわち、画素電極と共通電極との間に形成される水平電界により、液晶分子が水平電界の向きに配列しようとして基板正面とほぼ平行な平面内で回転する。このような液晶分子の配列状態により、液晶パネルを通過する光の偏光状態が変わる。これにより、偏光板を通過するすなわち液晶表示パネルを透過する光の透過率が変調される。

#### 【0005】

液晶表示パネル内において、液晶分子の配列状態が同じであっても、液晶表示パネルに入射する光の入射方向によって透過光の偏光状態は変化する。このため、入射方向に対応して光の透過率が異なる。しかしながら、IPSモード液晶表示装置では、液晶分子が基板正面とほぼ平行な平面内で回転するため、透過光の入射方向に対して偏光状態が大きく影響しないので、視野角依存性は小さく、広い視野角特性を有するといった特徴がある（例えば、特許文献1及び特許文献2参照。）。

#### 【0006】

##### 【特許文献1】

特公昭63-021907号公報

#### 【0007】

##### 【特許文献2】

特開平6-160878号公報

#### 【0008】

##### 【発明が解決しようとする課題】

上述したIPSモード液晶表示装置は、通常、列方向に配列された複数の画素からなる画素列は、その画素列に映像信号を供給するための信号線と、隣接する画素列に映像信号を供給するための信号線との間に挟まれるように配置される。しかしながら、有効表示部の端部に配置された画素列は、2本の信号線の間に挟まれるように配置されていない。つまり、有効表示部の外側に隣接する画素列が存在しないため、隣接する画素列に映像信号を供給するための信号線が存在しない。

#### 【0009】

IPSモード液晶表示装置は、各画素に付帯する液晶容量が非常に小さいため、僅かな寄生容量の差または電界の差の影響を強く受ける。つまり、有効表示部の端部に配置された画素と、有効表示部内の他の画素とでは、信号線とこれに隣接する電極との間の寄生容量や電界の条件が異なってしまう。このため、有効表示部内すべての画素について同一条件で駆動しているにもかかわらず、有効表示部端部に配置された画素のみが異なる表示となり、表示品位の劣化を招く。

#### 【0010】

そこで、この発明は、上記問題点を解決するためになされたものであり、広い視野角特性を有するとともに、表示品位を向上することが可能な液晶表示装置を提供することを目的とする。

#### 【0011】

##### 【課題を解決するための手段】

この発明の様態による液晶表示装置は、

一対の基板間に液晶層を挟持して構成され、マトリクス状に配置された複数の画素からなる有効表示部を備えた液晶表示装置であって、

一方の基板は、

行方向に延出された複数の走査配線と、

前記各走査配線に交差するよう列方向に延出された複数の信号配線と、

前記走査配線間に配置された共通配線と、

前記走査配線と前記信号配線との交差部に設けられたスイッチング素子と、

前記スイッチング素子に電気的に接続された画素電極と、

前記共通配線に電気的に接続され前記画素電極との間で前記液晶層に含まれる液晶分子を

10

20

30

40

50

スイッチングするための電界を形成する共通電極と、を備え、前記有効表示部において、列方向に配列された複数の画素からなる画素列は、隣接する2本の信号配線間に配置されたことを特徴とする。

#### 【0012】

##### 【発明の実施の形態】

以下、図面を参照してこの発明の一実施の形態に係る液晶表示装置について詳細に説明する。

#### 【0013】

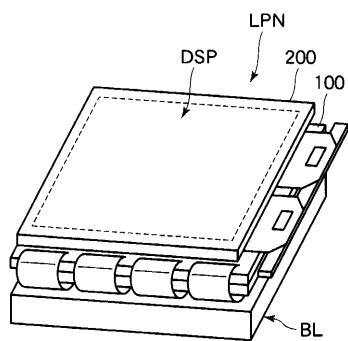

図1及び図2に示すように、液晶表示装置は、アクティブマトリクス駆動型のIPSモード液晶表示装置であって、液晶表示パネルLPN、液晶表示パネルLPNを背面から照明するバックライトユニットBLなどを備えて構成される。 10

#### 【0014】

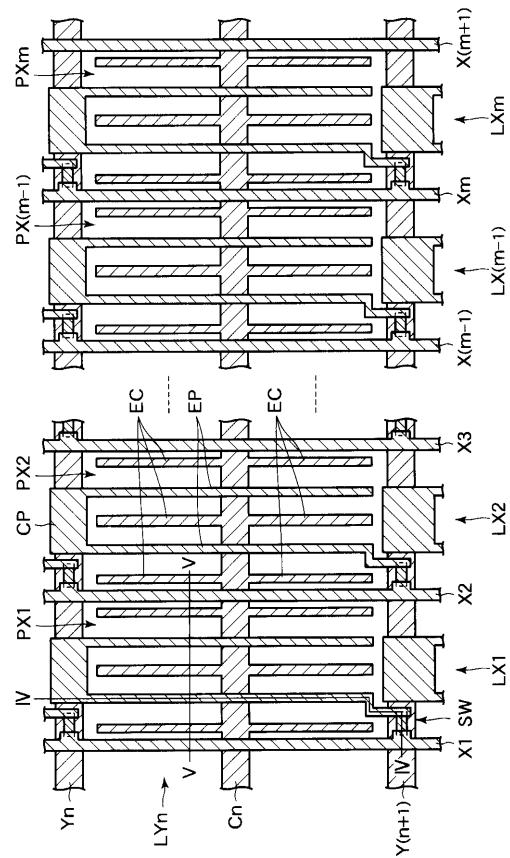

液晶表示パネルLPNは、アレイ基板100と、アレイ基板100と互いに対向して配置された対向基板200と、これらアレイ基板100と対向基板200との間に挟持された液晶層LQと、を備えて構成されている。この液晶表示パネルLPNは、 $m \times (n + 2)$ 個のマトリクス状に配置された複数の画素PXからなる表示領域DSPを備えている。

#### 【0015】

アレイ基板100は、表示領域DSPにおいて、複数の走査配線Y、複数の共通配線C、複数の信号配線Xを備えている。例えば( $n + 2$ )本の走査配線Y(Y0、Y1、...Yn、Y(n+1))は、それぞれ行方向に延出され、互いに所定間隔をおいて列方向に配列されている。例えば( $n + 2$ )本の共通配線C(C0、C1、...Cn、C(n+1))は、それぞれ行方向に延出され、互いに所定間隔をおいて列方向に配列されている。各共通配線Cは、走査配線Yとほぼ平行に、しかも、隣接する2本の走査配線Yの間に配置されている。少なくとも( $m + 1$ )本の信号配線X(X1、...Xm、X(m+1))は、それぞれ列方向に延出され、互いに所定間隔をおいて行方向に配列されている。すなわち、各信号配線Xは、走査配線Y及び共通配線Cに交差する(ほぼ直交する)ように配置されている。 20

#### 【0016】

また、アレイ基板100は、表示領域DSPの画素PX毎に設けられたスイッチング素子SW及び画素電極EP、複数の画素PXに共通に設けられた共通電極ECなどを備えている。スイッチング素子すなわち薄膜トランジスタSWは、各走査配線Yと各信号配線Xとの交差部に設けられている。画素電極EPは、各スイッチング素子SWに電気的に接続されている。共通電極ECは、共通配線Cに電気的に接続されている。この共通電極ECは、画素電極EPとの間で液晶層LQに含まれる液晶分子をスイッチングするための電界(アレイ基板100の正面にほぼ平行な水平電界)を形成する。 30

#### 【0017】

液晶表示パネルLPNは、( $n + 2$ )本の走査配線Yに接続された走査線駆動回路YD、及び、( $m + 1$ )本の信号配線Xに接続された信号線駆動回路XDを備えている。走査線駆動回路YDは、同一走査配線Yに接続された各スイッチング素子SWを駆動するための駆動信号を生成し、各走査配線Yに順次駆動信号を出力する。信号線駆動回路XDは、各画素に供給する映像信号を生成し、各行のスイッチング素子SWが駆動信号によってオンするタイミングで対応する信号配線Xに順次映像信号を出力する。これにより、各画素PXの画素電極EPは、対応するスイッチング素子SWを介して供給される映像信号に応じた画素電位にそれぞれ設定される。 40

#### 【0018】

このような構成により、表示領域DSPにおいては、同一の走査配線Yにm個のスイッチング素子SWが接続され、画素ラインLYが形成される。ここでは、( $n + 2$ )本の走査配線Yに対応して( $n + 2$ )本の画素ラインLY(LY0、LY1、...LYn、LY(n+1))が形成されている。また、同一の信号配線Xに( $n + 2$ )個のスイッチング素子SWが接続され、画素列LXが形成される。ここでは、m本の信号配線Xに対応してm本 50

の画素列  $L_X (L_X 1, \dots L_X m)$  が形成されている。

#### 【0019】

実質的に画像を表示する有効表示部  $DSP_{eff}$  は、 $m \times n$  個の画素  $P_X$  によって構成されている。すなわち、 $n$  本の走査配線  $Y (1 \sim n)$  には、それぞれ  $m$  個のスイッチング素子  $SW$  が接続されており、行方向に配列された  $m$  個の画素  $P_X$  からなる画素ライン  $LY (1 \sim n)$  によって有効表示部  $DSP_{eff}$  が構成される。換言すると、 $m$  本の信号配線  $X (1 \sim m)$  には、それぞれ  $n$  個のスイッチング素子  $SW$  が接続されており、列方向に配列された  $n$  個の画素  $P_X$  からなる画素列  $LX (1 \sim m)$  によって有効表示部  $DSP_{eff}$  が構成される。

#### 【0020】

この有効表示部  $DSP_{eff}$ においては、すべての画素列  $LX (1 \sim m)$  は、隣接する 2 本の信号配線間に配置されている。すなわち、各画素列  $LX$  は、その画素列に映像信号を供給するための信号配線と、他の信号配線との間に配置されている。これにより、有効表示部  $DSP_{eff}$  を構成するすべての画素列  $LX (1 \sim m)$  は、等価な構造を有することになる。このため、有効表示部  $DSP_{eff}$  内におけるすべての画素  $P_X$ について、信号配線  $X$  とこれに隣接する共通電極  $EC$  との間の寄生容量や電界の条件をほぼ同一とすることができ、同一条件で駆動した際には均一な表示品位が得られる。

#### 【0021】

このような構造は、有効表示部  $DSP_{eff}$  に  $m$  列の画素列  $LX (1 \sim m)$  を備えている場合に、 $(m + 1)$  本の信号線を配置することによって実現できる。すなわち、 $(m + 1)$  本の信号配線のうち、 $m$  本の信号配線  $X (1 \sim m)$  は、対応する  $m$  列の画素列  $LX (1 \sim m)$  にそれぞれ映像信号を供給するための映像信号線として機能し、1 本の信号配線（例えば信号線  $X (m + 1)$ ）は、副信号線として機能する。

#### 【0022】

この副信号線  $X (m + 1)$  には、表示領域  $DSP$  内においてスイッチング素子が接続されず、対応する画素列は形成されない。このため、副信号線  $X (m + 1)$  には、映像信号とは別の信号に対応した電圧が供給されればよく、望ましくは固定電圧が供給される。

#### 【0023】

例えば図 2 に示した例では、有効表示部  $DSP_{eff}$  の一端部に配置された第 1 画素列  $LX_1$  は、この第 1 画素列  $LX_1$  に映像信号を供給するための映像信号線  $X_1$  と、第 1 画素列  $LX_1$  に隣接する第 2 画素列  $LX_2$  に映像信号を供給するための映像信号線  $X_2$  との間に配置される。また、有効表示部  $DSP_{eff}$  の他端部に配置された第  $m$  画素列  $LX_m$  は、この第  $m$  画素列  $LX_m$  に映像信号を供給するための映像信号線  $X_m$  と、副信号線  $X (m + 1)$  との間に配置される。このように、すべての画素列  $LX (1 \sim m)$  は、隣接する 2 本の信号配線間に配置されることになる。

#### 【0024】

また、表示領域  $DSP$ において、走査配線  $Y_0$  及び  $Y (n + 1)$  にも有効表示部  $DSP_{eff}$  と同様に  $m$  個のスイッチング素子  $SW$  が接続されており、それぞれ画素ライン  $LY_0$  及び  $LY (n + 1)$  を形成する。これら画素ライン  $LY_0$  及び  $LY (n + 1)$  は、有効表示部  $DSP_{eff}$  外に配置され、実質的に画像表示に寄与しないダミー画素ラインとなる。ダミー画素ライン  $LY_0$  及び  $LY (n + 1)$  に接続された画素  $P_X$  は、実質的に有効表示部  $DSP_{eff}$  内の画素  $P_X$  と同一構造であることが望ましい。

#### 【0025】

これにより、有効表示部  $DSP_{eff}$  を構成するすべての画素  $P_X$  は、2 本の隣接する信号配線間に配置されるとともに 2 本の隣接する走査配線間に配置され、等価な構造を有することになり、より好ましい。つまり、各画素に付帯する液晶容量が非常に小さい IPS モード液晶表示装置においては、寄生容量や電界の僅かな差が各画素の表示品位に大きな影響を及ぼす。したがって、有効表示部  $DSP_{eff}$  内のすべての画素  $P_X$  で等価な構造を形成することで、表示品位をさらに向上することができる。

#### 【0026】

10

20

30

40

50

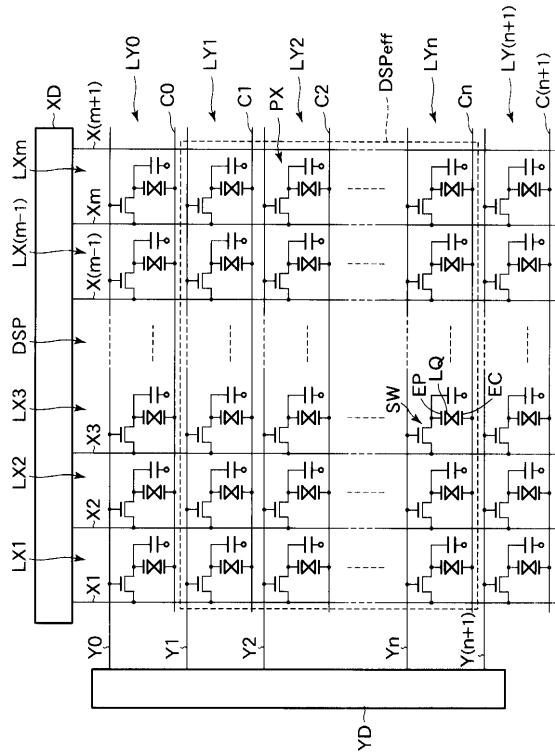

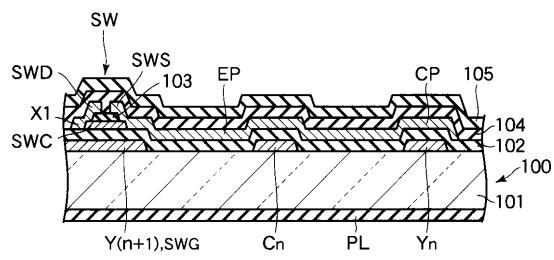

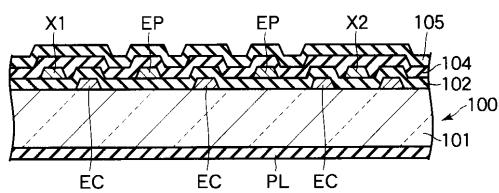

次に、図3乃至図5を参照して第1実施形態について説明する。なお、図3は、有効表示部D S P<sub>e f f</sub>の画素ラインL Y nにおける両端部の画素の平面構造を示しており、また、図4は、図3におけるI V - I V線で切断したアレイ基板の断面構造を示しており、さらに、図5は、図3におけるV - V線で切断したアレイ基板の断面構造を示している。

## 【0027】

すなわち、アレイ基板100は、光透過性を有する絶縁性基板としてのガラス基板101を用いて構成される。走査配線Y、共通配線C、及び、共通電極E Cは、ガラス基板101上に成膜されたアルミニウム(A1)などの金属材料をフォトリソグラフィ法によってパターニングすることで形成される。走査配線Yの一部は、スイッチング素子S Wのゲート電極S W Gとして機能する。共通電極E Cは、列方向に延出されたストライプ状に形成され、1画素あたり複数本配置(図3では3本)されることが望ましい。これらの共通電極E Cは、共通配線Cと一緒に形成されている。

## 【0028】

これら走査配線Y、共通配線C、及び、共通電極E Cは、窒化シリコン膜(SiNx)やシリコン酸化膜(SiO<sub>2</sub>)などのゲート絶縁膜102によって覆われている。スイッチング素子S Wのスイッチ機能を司る半導体層S W Cは、ゲート絶縁膜102上に成膜されたアモルファスシリコン(a-Si)をパターニングすることで形成される。つまり、この半導体層S W Cは、ゲート絶縁膜102を介して、走査配線Y(ゲート電極S W G)とオーバラップする部分に配置される。

## 【0029】

この半導体層S W C上には、窒化シリコン膜(SiNx)やシリコン酸化膜(SiO<sub>2</sub>)などのチャネル保護膜103が積層されている。信号線及び副信号線を含む信号配線X、画素電極E P、及び、蓄積容量部C Pは、ゲート絶縁膜102及びチャネル保護膜103上にn型不純物を含有するアモルファスシリコン(n+a-Si)、チタン(Ti)、及び、アルミニウム(A1)の3層を連続堆積し、一括してパターニングすることで形成される。

## 【0030】

n型不純物を含有するアモルファスシリコン(n+a-Si)は、半導体層S W Cと信号配線X及び画素電極E Pとのオーミックコンタクトをとるために設けられている。チタン(Ti)は、アルミニウム(A1)がアモルファスシリコン(a-Si)の半導体層S W Cに拡散するのを防止するために設けられている。

## 【0031】

信号配線Xの一部は、半導体層S W Cにコンタクトし、スイッチング素子S Wのドレイン電極S W Dとして機能する。画素電極E Pの一部は、半導体層S W Cにコンタクトし、スイッチング素子S Wのソース電極S W Sとして機能する。また、画素電極E Pは、共通電極E Cとオーバラップしないよう列方向に延出されたストライプ状に形成され、1画素あたり複数本配置(図3では2本)されることが望ましい。図3に示したレイアウトでは、信号配線Xと画素電極E Pとの間、及び、隣接する2本の画素電極E P間にそれぞれ共通電極E Cが配置されている。

## 【0032】

複数の画素電極E Pは、蓄積容量部C Pと一緒に形成されている。この蓄積容量部C Pは、ゲート絶縁膜102を介して、走査配線Yとオーバラップする部分に配置される。この蓄積容量部C Pは、画素P Xに供給された映像信号を保持するために設けられている。

## 【0033】

これら信号配線X、画素電極E P、及び、蓄積容量部C Pは、窒化シリコン膜(SiNx)やシリコン酸化膜(SiO<sub>2</sub>)などの保護膜104によって覆われている。さらに、アレイ基板100の表面は、ラビング処理を施された配向膜105によって覆われている。

## 【0034】

一方で、対向基板200も同様に、光透過性を有する絶縁性基板としてのガラス基板を用いて構成される。この対向基板200は、走査配線Y及び信号配線Xに対向するように格

10

20

30

40

50

子状に配置された遮光性を有するブラックマトリクスを備えている。また、この対向基板 200 の表面は、ラビング処理を施された配向膜によって覆われている。

#### 【0035】

上述したような構成のアレイ基板 100 と対向基板 200 とを所定のギャップ（例えば 3  $\mu\text{m}$ ）を隔てて貼り合わせ、これら一対の基板間に液晶組成物を封入することで液晶層 LQ を形成する。このとき、配向膜の作用により、液晶層 LQ に含まれる液晶分子の長軸は所定方向に配向される。

#### 【0036】

さらに、アレイ基板 100 及び対向基板 200 は、それぞれの外面に互いに偏光軸方向が直交するように配置された偏光板 PL を備えている。一方の偏光板は、その偏光軸が一方の基板に接している液晶分子の長軸方向と平行または直交するように配置されている。10

#### 【0037】

このようなIPSモード液晶表示装置では、2枚の偏光板 PL の配置により、電圧無印加時には黒色画面を表示する。また、信号配線 X からスイッチング素子 SW を介して画素電極 EP に映像信号を供給することにより、共通電極 EC との間の電位差によって基板にほぼ平行な水平電界が形成される。液晶分子は、この水平電界の向きに配列しようとして基板正面とほぼ平行な平面内で回転する。

#### 【0038】

一方で、バックライトユニット BL から出射された光は、入射側偏光板（すなわちアレイ基板外面の偏光板）PL を介して液晶表示パネル LPN に入射する。液晶表示パネル LPN に入射した光の偏光状態は、液晶層 LQ を通過する際に液晶分子の配列状態によって変わる。液晶表示パネル LPN を通過した光は、出射側偏光板（すなわち対向基板外面の偏光板）PL の偏光軸方向の成分のみが透過する。これにより、液晶表示パネル LPN を透過する光の透過率が変調される。20

#### 【0039】

このような液晶表示装置によれば、例えば図3に示すように、画素ライン LYn は、m 個の画素 PX (1 ~ m) によって構成され、しかも、画素列 LX1 ~ LX (m - 1) のそれぞれの画素 PX1 ~ PX (m - 1) は、隣接する2本の信号線の間に配置され、また、画素列 LXm の画素 PXm は、1本の信号線 Xm と副信号線 X (m + 1) との間に配置されている。このため、いずれの画素 PX もほぼ同じ容量となる。したがって、信号線及び副信号線にすべて同じ電位を供給して液晶表示装置の点灯画像検査を行ったところ、有効表示部全域の画素について均一な表示品位を得られることが確認できた。30

#### 【0040】

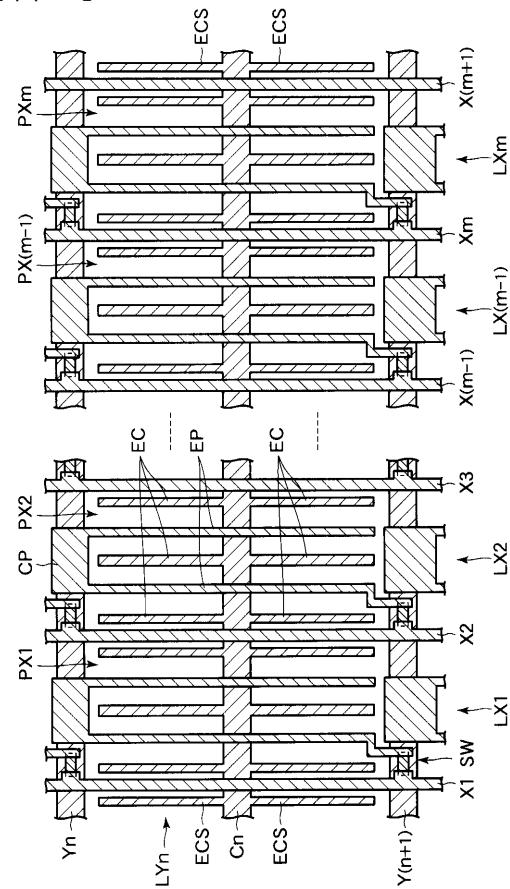

次に、図6を参照して第2実施形態について説明する。なお、図6は、有効表示部 DSPef 的画素ライン LYn における両端部の画素の平面構造を示している。この第2実施形態における有効表示部 DSPef の構造は、基本的に第1実施形態と同様である。

#### 【0041】

すなわち、第2実施形態では、アレイ基板 100 は、共通電極 EC の他にさらに共通配線 C に電気的に接続された副共通電極 ECS を備えている。この副共通電極 ECS は、有効表示部 DSPef の両端部に配置された画素列 LX1 及び LXm を構成する各画素 PX1 及び PXm の外側に配置されている。また、この副共通電極 ECS は、共通電極 EC と同一材料により列方向に延出されたストライプ状に形成され、共通配線 C と一緒に形成されている。40

#### 【0042】

通常、IPSモード液晶表示装置では、1画素について、2本の信号配線間に配置された共通電極 EC と画素電極 EP（または信号配線 X）との間に形成される電界により液晶分子をスイッチングする。しかしながら、僅かな電界の差の影響を強く受けるIPSモードでは、隣接する画素（特に行方向に隣接する画素）内に配置された共通電極 EC との間に形成される電界の影響が全くないとは言い難い。つまり、隣接する画素からの電界の影響を完全にはシールドできていない。50

**【 0 0 4 3 】**

有効表示部  $DSP_{eff}$  では、その中央部の画素  $P_X$  については必ず隣接する画素が存在するのに対して、有効表示部  $DSP_{eff}$  の両端部の画素  $P_X$  については隣接する画素が存在しない。このため、有効表示部  $DSP_{eff}$  の両端部画素  $P_X$  は、その他の画素  $P_X$  と電界の条件が若干ながら異なるおそれがある。

**【 0 0 4 4 】**

そこで、この第2実施形態では、両端部画素  $P_X$  の外側に、少なくとも1本の副共通電極  $ECS$  を配置したことにより、他の画素  $P_X$  と電界及び画素容量の条件を同一とすることができる。

**【 0 0 4 5 】**

このような液晶表示装置によれば、信号線及び副信号線にすべて同じ電位を供給して液晶表示装置の点灯画像検査を行ったところ、有効表示部全域の画素について、上述した第1実施形態よりもさらに均一な表示品位を得られることが確認できた。

**【 0 0 4 6 】**

なお、有効表示部  $DSP_{eff}$  の両端部に位置する第1画素列  $LX_1$  及び第m画素列  $LX_m$  の外側に、副信号線  $X(m+1)$  や副共通電極  $ECS$  だけでなく有効表示部  $DSP_{eff}$  内の画素  $P_X$  と実質的に同一な構造のダミー画素を配置しても良い。但し、副信号線  $X(m+1)$  や副共通電極  $ECS$  のみですべての画素  $P_X$  を等価な条件に構成できるのであれば、狭額縁化に有利であり、望ましい。

**【 0 0 4 7 】**

また、この発明は、画素容量の小さい構造の表示装置全般に適用可能であり、例えば、超高精細のTN方式のアクティブマトリクス型液晶表示装置などにも有効である。

**【 0 0 4 8 】**

以上説明した液晶表示装置によれば、同一基板上に画素電極及び共通電極を備えて基板正面と平行な平面内で液晶分子をスイッチングするIPSモードを採用したことにより、広い視野角特性を実現できる。また、有効表示部を構成するすべての画素について等価な構造とし、各画素での電界及び液晶容量の条件をほぼ同一とすることにより、局所的、特に有効表示部両端部に位置する画素の表示品位を他の画素と揃えることができ、均一な表示品位の画像を表示可能である。このため、良好な多階調表示を実現でき、表示品位を向上することができる。

**【 0 0 4 9 】**

なお、この発明は、上記実施形態そのままに限定されるものではなく、その実施の段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組み合せてよい。

**【 0 0 5 0 】****【 発明の効果 】**

以上説明したように、この発明によれば、広い視野角特性を有するとともに、表示品位を向上することが可能な液晶表示装置を提供することができる。

**【 図面の簡単な説明 】**

【図1】図1は、この発明の一実施の形態に係る液晶表示装置の構造を概略的に示す図である。

【図2】図2は、図1に示した液晶表示装置に備えられた液晶表示パネルの構成を概略的に示す等価回路である。

【図3】図3は、図2に示した液晶表示パネルに適用可能な第1実施形態に係るアレイ基板の平面構造を概略的に示す図である。

【図4】図4は、図3に示したIV-IV線で切断したアレイ基板の断面構造を概略的に示す図である。

【図5】図5は、図3に示したV-V線で切断したアレイ基板の断面構造を概略的に示す

10

20

30

40

50

図である。

【図6】図6は、図2に示した液晶表示パネルに適用可能な第2実施形態に係るアレイ基板の平面構造を概略的に示す図である。

【符号の説明】

100...アレイ基板、200...対向基板、LQ...液晶層、DSP<sub>eff</sub>...有効表示部、Y...走査配線、X...信号配線、X(m+1)...副信号線、C...共通配線、LY...画素ライン、LX...画素列、PX...画素、SW...スイッチング素子、EP...画素電極、EC...共通電極、ECS...副共通電極

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 浅田 智

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

F ターム(参考) 2H092 GA14 JA24 JB02 JB11 JB32 NA01

|                |                                                                                                                                                                                                                   |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2005003802A</a>                                                                                                                                                                                     | 公开(公告)日 | 2005-01-06 |

| 申请号            | JP2003165305                                                                                                                                                                                                      | 申请日     | 2003-06-10 |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                                                                                                                                                    |         |            |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                                                                                                                                                      |         |            |

| [标]发明人         | 浅田智                                                                                                                                                                                                               |         |            |

| 发明人            | 浅田 智                                                                                                                                                                                                              |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368                                                                                                                                                                                             |         |            |

| FI分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                             |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/JA24 2H092/JB02 2H092/JB11 2H092/JB32 2H092/NA01 2H192/AA24 2H192 /BB02 2H192/BB72 2H192/BB82 2H192/CB05 2H192/CB46 2H192/CB71 2H192/CC04 2H192/CC72 2H192/DA02 2H192/EA22 2H192/FA02 2H192/JA33 |         |            |

| 代理人(译)         | 河野 哲<br>中村诚                                                                                                                                                                                                       |         |            |

| 其他公开文献         | JP2005003802A5                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                         |         |            |

### 摘要(译)

本发明的目的是提供一种具有宽视角特性并能够改善显示质量的液晶显示装置。液晶显示面板包括有效显示部分DSP效，该有效显示部分DSP包括以矩阵布置的多个像素PX。阵列基板具有在行方向上延伸的多个扫描布线Y，在列方向上延伸以与每个扫描布线Y相交的多个信号布线X，以及布置在扫描布线Y之间的公共布线。C，设置在扫描配线Y和信号配线X的交点处的开关元件SW，电连接至开关元件SW的像素电极EP，以及电连接至公共配线C的像素电极EP。并且，公共电极EC形成用于切换液晶层LQ中包含的液晶分子的电场。在有效显示部分DSP效中，包括在列方向上排列的多个像素的像素列LX布置在两条相邻的信号线之间。

[选择图]图2