(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-287087

(P2004-287087A)

(43) 公開日 平成16年10月14日(2004.10.14)

(51) Int.Cl.<sup>7</sup>**G09G 3/36**

**G02F 1/133**

**G09G 3/20**

F 1

G09G 3/36

G02F 1/133 550

G09G 3/20 611A

G09G 3/20 611E

G09G 3/20 621B

テーマコード(参考)

2H093

5C006

5C080

審査請求 未請求 請求項の数 7 O L (全 24 頁) 最終頁に続く

(21) 出願番号

特願2003-78981 (P2003-78981)

(22) 出願日

平成15年3月20日 (2003.3.20)

(71) 出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100104695

弁理士 島田 明宏

(72) 発明者 大和 朝日

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(72) 発明者 中野 武俊

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

(72) 発明者 柳 俊洋

大阪府大阪市阿倍野区長池町22番22号

シャープ株式会社内

最終頁に続く

(54) 【発明の名称】 液晶表示装置およびその駆動方法

## (57) 【要約】

【課題】携帯電話機等における低消費電力化の強い要求に応えつつフリッカやシャドーを低減して表示品位向上させた液晶表示装置を提供する。

【解決手段】第nフレームの前半期間では、多数の画素形成部からなる画素マトリクスにおける奇数番目の行に対応する走査信号G(1)、G(3)、G(5)を順にアクティブとすることで第1の飛び越し走査を行い、画素マトリクスの奇数行の各画素形成部に書き込むべき画素値に相当する電圧を、正極性の映像信号として各映像信号線に印加する。第nフレームの後半期間では、画素マトリクスの偶数番目の行に対応する走査信号G(2)、G(4)、G(6)を順にアクティブとすることで第2の飛び越し走査を行い、画素マトリクスの偶数行の各画素形成部に書き込むべき画素値に相当する電圧を、負極性の映像信号として各映像信号線に印加する。以上によりライン反転駆動を実現する。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

表示すべき画像を形成するための複数の画素形成部と、前記表示すべき画像を示す映像信号を前記複数の画素形成部に伝達するための複数の映像信号線と、前記複数の映像信号線と交差する複数の走査信号線とを備え、前記複数の画素形成部が前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置されたアクティブラーマトリクス型の液晶表示装置であって、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路と、

前記映像信号を前記複数の映像信号線に印加する映像信号線駆動回路とを備え、

前記各画素形成部は、対応する交差点を通過する走査信号線が前記走査信号線駆動回路によって選択されているときに、当該対応する交差点を通過する映像信号線に前記映像信号線駆動回路によって印加される映像信号を画素値として取り込み、

前記走査信号線駆動回路は、前記複数の走査信号線を1本または所定本数おきに所定順に選択して駆動する第1の飛び越し走査と、前記複数の走査信号線のうち前記第1の飛び越し走査で選択されない走査信号線を所定順に選択して駆動する第2の飛び越し走査とを交互に繰り返し、

前記映像信号線駆動回路は、前記第1および第2の飛び越し走査のそれぞれにおいて前記映像信号としての電圧を同一極性で前記複数の映像信号線に印加すると共に、前記走査信号線駆動回路による走査信号線の駆動が前記第1の飛び越し走査から前記第2飛び越し走査へと切り替わる時に前記複数の映像信号線への印加電圧の極性を反転させることを特徴とする液晶表示装置。

**【請求項 2】**

前記走査信号線駆動回路は、前記第1の飛び越し走査において走査信号線が選択される順序に基づく走査方向と前記第2の飛び越し走査において走査信号線が選択される順序に基づく走査方向とが互いに逆となるように、前記複数の走査信号線を選択的に駆動することを特徴とする、請求項1に記載の液晶表示装置。

**【請求項 3】**

前記走査信号線駆動回路は、前記第2の飛び越し走査の後に所定期間だけ前記複数の走査信号線を非選択状態とすることを特徴とする、請求項1または2に記載の液晶表示装置。

**【請求項 4】**

前記各画素形成部は、

対応する交差点を通過する走査信号線である対応走査信号線が選択されているときにオンされ、当該対応走査信号線が選択されていないときにオフされるスイッチング素子と、対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成部に共通的に設けられ、前記画素電極との間に所定容量が形成されるように配置された共通電極とを含み、

同一走査信号線によってオンおよびオフされるスイッチング素子に接続される画素電極である同時選択画素電極は、前記複数の画素形成部からなるマトリクスにおいて上下に隣接する2行に分散的に配置されていることを特徴とする、請求項1から3までのいずれか1項に記載の液晶表示装置。

**【請求項 5】**

表示すべき画像を形成するための複数の画素形成部と、前記表示すべき画像を示す映像信号を前記複数の画素形成部に伝達するための複数の映像信号線と、前記複数の映像信号線と交差する複数の走査信号線とを備え、前記複数の画素形成部が前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置されたアクティブラーマトリクス型の液晶表示装置の駆動方法であって、

前記複数の走査信号線を選択的に駆動する走査信号線駆動ステップと、

前記映像信号を前記複数の映像信号線に印加する映像信号線駆動ステップとを備え、

前記走査信号線駆動ステップでは、前記複数の走査信号線を1本または所定本数おきに所

10

20

30

40

50

定順に選択して駆動する第1の飛び越し走査と、前記複数の走査信号線のうち前記第1の飛び越し走査で選択されない走査信号線を所定順に選択して駆動する第2の飛び越し走査とが交互に繰り返され、

前記映像信号線駆動ステップでは、前記第1および第2の飛び越し走査のそれぞれにおいて同一極性で前記映像信号としての電圧が前記複数の映像信号線に印加されると共に、前記走査信号線駆動ステップでの走査信号線の駆動が前記第1の飛び越し走査から前記第2飛び越し走査へと切り替わる時に前記複数の映像信号線への印加電圧の極性が反転することを特徴とする駆動方法。

#### 【請求項6】

前記走査信号線駆動ステップでは、前記第1の飛び越し走査において走査信号線が選択される順序に基づく走査方向と前記第2の飛び越し走査において走査信号線が選択される順序に基づく走査方向とが互いに逆となるように、前記複数の走査信号線が選択的に駆動されることを特徴とする、請求項5に記載の駆動方法。 10

#### 【請求項7】

前記走査信号線駆動ステップでは、前記第2の飛び越し走査の後に所定期間だけ前記複数の走査信号線が非選択状態とされることを特徴とする、請求項5または6に記載の駆動方法。 20

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、液晶表示装置およびその駆動方法に関するものであり、更に詳しくは、アクティブマトリクス型の液晶表示装置における交流化駆動に関する。 20

##### 【0002】

##### 【従来の技術】

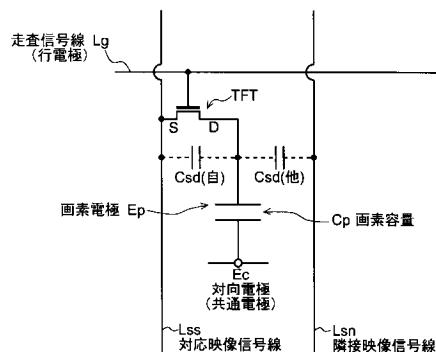

一般に液晶表示装置では、液晶の劣化を抑えると共に表示品位を維持するために交流化駆動が行われている。しかし、アクティブ型の液晶表示装置においては、画素毎に設けられたTFT (Thin Film Transistor) 等のスイッチング素子の特性が十分でないために、液晶パネルの映像信号線(列電極)に電圧を印加する映像信号線駆動回路(「列電極駆動回路」または「データ線駆動回路」とも呼ばれる)から出力される映像信号の正負すなわち共通電極の電位を基準とする印加電圧の正負が対称であっても、液晶層の透過率は正負のデータ電圧に対して完全に対称とはならない。このため、1フレーム毎に液晶への印加電圧の極性を反転させる駆動方式(1フレーム反転駆動方式)では、液晶パネルによる表示においてフリッカが発生する。また、図9に示すように、映像信号線L<sub>ss</sub>, L<sub>sn</sub>と画素電極E<sub>p</sub>との間に存在する寄生容量C<sub>sd</sub>(自), C<sub>sd</sub>(他)により、各画素電極E<sub>p</sub>と共通電極E<sub>c</sub>との間の電圧に対応する各画素値が映像信号線L<sub>ss</sub>, L<sub>sn</sub>の電位の影響を受け、画面に縦シャドーと呼ばれる縦方向に延びる縞状の模様等が現れることがある。 30

##### 【0003】

携帯電話機等のように消費電力の削減に対する要求が特に強い携帯用情報機器で使用される液晶モジュールにおいては、交流化駆動の方式として、その要求に応えるべくフレーム反転駆動方式が採用されていた。しかし、近年、携帯電話機等においても、処理性能の向上と利用の高度化などによって高品位の表示能力が要求されるようになり、それに伴い、フリッカや縦シャドーが問題視されるようになってきている。 40

##### 【0004】

##### 【特許文献1】

特開平8-320674号公報

##### 【0005】

##### 【発明が解決しようとする課題】

上記のような問題を解決するために、交流化駆動方式として、1水平走査線毎に印加電圧の正負極性を反転させつつ1フレーム毎にも正負極性を反転させる駆動方式(「ライン反 50

転駆動方式」と呼ばれる)が採用されている。しかし、フレーム反転駆動方式に代えてライン反転駆動方式を採用すると、液晶パネルに印加すべき映像信号における極性反転の頻度(反転周波数)が高くなり、また、駆動用IC(Integrated Circuit)に必要な耐圧の低減のために共通電極の電位の切換周波数も高くなる。その結果、消費電力が増大する。また、ライン反転駆動方式を採用しただけでは、フリッカを十分に抑えることはできない。

#### 【0006】

そこで本発明では、携帯電話機等における低消費電力化の強い要求に応えつつフリッカやシャドーを低減して表示品位を向上させた液晶表示装置を提供することを目的とする。

#### 【0007】

##### 【課題を解決するための手段】

第1の発明は、表示すべき画像を形成するための複数の画素形成部と、前記表示すべき画像を示す映像信号を前記複数の画素形成部に伝達するための複数の映像信号線と、前記複数の映像信号線と交差する複数の走査信号線とを備え、前記複数の画素形成部が前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置されたアクティブマトリクス型の液晶表示装置であって、

前記複数の走査信号線を選択的に駆動する走査信号線駆動回路と、

前記映像信号を前記複数の映像信号線に印加する映像信号線駆動回路とを備え、

各画素形成部は、対応する交差点を通過する走査信号線が前記走査信号線駆動回路によって選択されているときに、当該対応する交差点を通過する映像信号線に前記映像信号線駆動回路によって印加される映像信号を画素値として取り込み、

前記走査信号線駆動回路は、前記複数の走査信号線を1本または所定本数おきに所定順に選択して駆動する第1の飛び越し走査と、前記複数の走査信号線のうち前記第1の飛び越し走査で選択されない走査信号線を所定順に選択して駆動する第2の飛び越し走査とを交互に繰り返し、

前記映像信号線駆動回路は、前記第1および第2の飛び越し走査のそれぞれにおいて前記映像信号としての電圧を同一極性で前記複数の映像信号線に印加すると共に、前記走査信号線駆動回路による走査信号線の駆動が前記第1の飛び越し走査から前記第2飛び越し走査へと切り替わる時に前記複数の映像信号線への印加電圧の極性を反転させることを特徴とする。

#### 【0008】

第2の発明は、第1の発明において、

前記走査信号線駆動回路は、前記第1の飛び越し走査において走査信号線が選択される順序に基づく走査方向と前記第2の飛び越し走査において走査信号線が選択される順序に基づく走査方向とが互いに逆となるように、前記複数の走査信号線を選択的に駆動することを特徴とする。

#### 【0009】

第3の発明は、第1または第2の発明において、

前記走査信号線駆動回路は、前記第2の飛び越し走査の後に所定期間だけ前記複数の走査信号線を非選択状態とすることを特徴とする。

#### 【0010】

第4の発明は、第1から第3までの発明のいずれかにおいて、

前記各画素形成部は、

対応する交差点を通過する走査信号線である対応走査信号線が選択されているときにオンされ、当該対応走査信号線が選択されていないときにオフされるスイッチング素子と、対応する交差点を通過する映像信号線に前記スイッチング素子を介して接続される画素電極と、

前記複数の画素形成部に共通的に設けられ、前記画素電極との間に所定容量が形成されるように配置された共通電極とを含み、

同一走査信号線によってオンおよびオフされるスイッチング素子に接続される画素電極で

10

20

30

40

50

ある同時選択画素電極は、前記複数の画素形成部からなるマトリクスにおいて上下に隣接する2行に分散的に配置されていることを特徴とする。

#### 【0011】

第5の発明は、表示すべき画像を形成するための複数の画素形成部と、前記表示すべき画像を示す映像信号を前記複数の画素形成部に伝達するための複数の映像信号線と、前記複数の映像信号線と交差する複数の走査信号線とを備え、前記複数の画素形成部が前記複数の映像信号線と前記複数の走査信号線との交差点にそれぞれ対応してマトリクス状に配置されたアクティブマトリクス型の液晶表示装置の駆動方法であって、

前記複数の走査信号線を選択的に駆動する走査信号線駆動ステップと、

前記映像信号を前記複数の映像信号線に印加する映像信号線駆動ステップとを備え、

10

前記走査信号線駆動ステップでは、前記複数の走査信号線を1本または所定本数おきに所定順に選択して駆動する第1の飛び越し走査と、前記複数の走査信号線のうち前記第1の飛び越し走査で選択されない走査信号線を所定順に選択して駆動する第2の飛び越し走査とが交互に繰り返され、

前記映像信号線駆動ステップでは、前記第1および第2の飛び越し走査のそれれにおいて同一極性で前記映像信号としての電圧が前記複数の映像信号線に印加されると共に、前記走査信号線駆動ステップでの走査信号線の駆動が前記第1の飛び越し走査から前記第2飛び越し走査へと切り替わる時に前記複数の映像信号線への印加電圧の極性が反転することを特徴とする。

#### 【0012】

20

第6の発明は、第5の発明において、

前記走査信号線駆動ステップでは、前記第1の飛び越し走査において走査信号線が選択される順序に基づく走査方向と前記第2の飛び越し走査において走査信号線が選択される順序に基づく走査方向とが互いに逆となるように、前記複数の走査信号線が選択的に駆動されることを特徴とする。

#### 【0013】

30

第7の発明は、第5または第6の発明において、

前記走査信号線駆動ステップでは、前記第2の飛び越し走査の後に所定期間だけ前記複数の走査信号線が非選択状態とされることを特徴とする。

#### 【0014】

##### 【発明の実施の形態】

以下、本発明の実施形態について添付図面を参照して説明する。

##### <1. 第1の実施形態>

##### <1.1 全体の構成および動作>

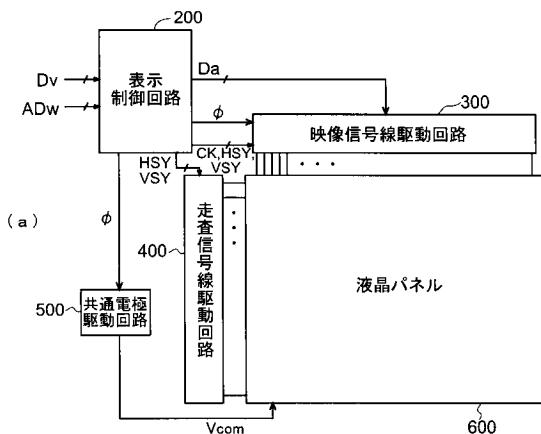

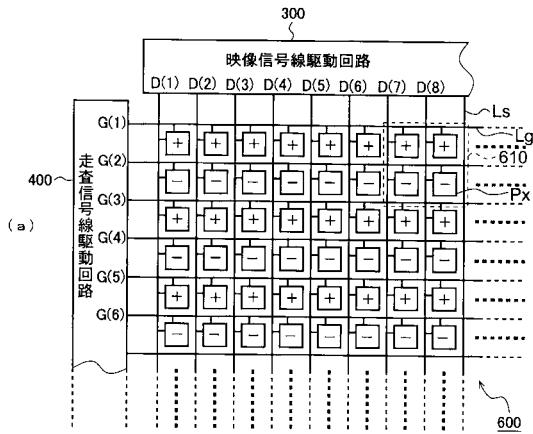

図1(a)は、本発明の第1の実施形態に係る液晶表示装置の構成を示すブロック図である。この液晶表示装置は、表示制御回路200と、映像信号線駆動回路300(「列電極駆動回路」または「データ線駆動回路」とも呼ばれる)と、走査信号線駆動回路(「行電極駆動回路」または「ゲート線駆動回路」とも呼ばれる)400と、共通電極駆動回路500と、アクティブマトリクス型の液晶パネル600とを備えている。

#### 【0015】

40

この液晶表示装置における表示部としての液晶パネル600は、外部のコンピュータにおけるCPU等から受け取る画像データDVの表す画像における水平走査線にそれぞれが対応する複数本の走査信号線(行電極)と、それら複数本の走査信号線のそれぞれと交差する複数本の映像信号線(列電極)と、それら複数本の走査信号線と複数本の映像信号線との交差点にそれぞれ対応して設けられた複数の画素形成部とを含む。各画素形成部の構成は、基本的には従来のアクティブマトリクス型液晶パネルにおける構成と同様である(詳細は後述)。また、この液晶パネル600は、各画素形成部に含まれる画素電極に共通的に設けられかつ液晶層を挟んで各画素電極と対向するように配置された共通電極を備えている。

#### 【0016】

50

本実施形態では、液晶パネル600に表示すべき画像を表す（狭義の）画像データおよび表示動作のタイミング等を決めるデータ（例えば表示用クロックの周波数を示すデータ）（以下「表示制御データ」という）は、外部のコンピュータにおけるCPU等から表示制御回路200に送られる（以下、外部から送られるこれらのデータDvを「広義の画像データ」という）。すなわち、外部のCPU等は、広義の画像データDvを構成する（狭義の）画像データおよび表示制御データを、アドレス信号ADwを表示制御回路200に供給して、表示制御回路200内の後述の表示メモリおよびレジスタにそれぞれ書き込む。

## 【0017】

表示制御回路200は、レジスタに書き込まれた表示制御データに基づき、表示用のクロック信号CKや、水平同期信号HSY、垂直同期信号VSY等を生成する。また、表示制御回路200は、外部のCPU等によって表示メモリに書き込まれた（狭義の）画像データを表示メモリから読み出して、デジタル画像信号Daとして出力する。さらに、表示制御回路200は、水平同期信号HSYおよび垂直同期信号VSYに基づき、液晶パネル600の交流化駆動のための極性切換制御信号を生成する。このようにして、表示制御回路200によって生成される信号のうち、クロック信号CKは映像信号線駆動回路300に、水平同期信号HSYおよび垂直同期信号VSYは映像信号線駆動回路300および走査信号線駆動回路400に、デジタル画像信号Daは映像信号線駆動回路300に、極性切換制御信号は、映像信号線駆動回路300および共通電極駆動回路500に、それぞれ供給される。

## 【0018】

映像信号線駆動回路300には、上記のように、液晶パネル600に表示すべき画像を表示データが画素単位でデジタル画像信号Daとして供給されると共に、タイミングを示す信号としてクロック信号CK、水平同期信号HSY、垂直同期信号VSY、および極性切換制御信号が供給される。映像信号線駆動回路300は、これらの信号Da、CK、HSY、VSY、にに基づき、液晶パネル600を駆動するための映像信号（以下「駆動用映像信号」ともいう）D(1), D(2), D(3), ...を生成し、これを液晶パネル600の各映像信号線に印加する。この駆動用映像信号D(1), D(2), D(3), ...は、液晶パネル600の交流化駆動のために、極性切換制御信号に応じてその極性が反転する。

## 【0019】

走査信号線駆動回路400は、水平同期信号HSYおよび垂直同期信号VSYに基づき、液晶パネル600における走査信号線を1水平走査期間ずつ後述の所定順に選択するために各走査信号線に印加すべき走査信号G(1), G(2)、G(3), ...を生成し、全走査信号線のそれを所定順で選択するためのアクティブな走査信号の各走査信号線への印加を1垂直走査期間を周期として繰り返す。

## 【0020】

共通電極駆動回路500は、液晶パネル600の共通電極に与えるべき電圧である共通電圧Vcomを生成する。本実施形態では、映像信号線の電圧の振幅を抑えるために、交流化駆動に応じて共通電極の電位をも変化させている。すなわち、共通電極駆動回路500は、表示制御回路200からの極性切換制御信号に応じて、1フレーム（1垂直走査期間）において2種類の基準電圧の間で切り換わる電圧を生成し、これを共通電圧Vcomとして液晶パネル600の共通電極に供給する。

## 【0021】

液晶パネル600では、上記のようにして映像信号線に、映像信号線駆動回路300によってデジタル画像信号Daに基づく駆動用の映像信号D(1), D(2), D(3), ...が印加され、走査信号線には、走査信号線駆動回路400によって走査信号G(1), G(2)、G(3), ...が印加され、共通電極には、共通電極駆動回路500によって共通電圧Vcomが印加される。これにより液晶パネル600は、外部のCPU等から受け取った画像データDvの表す画像を表示する。

## 【0022】

10

20

30

40

50

## &lt; 1 . 2 表示制御回路 &gt;

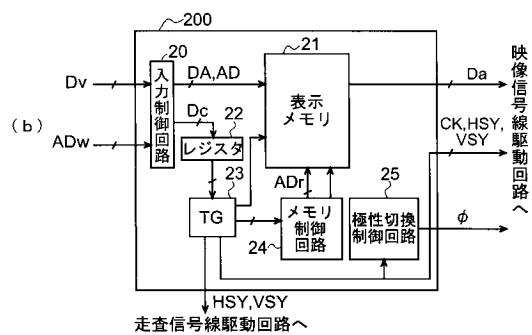

図1( b )は、上記の液晶表示装置における表示制御回路200の構成を示すブロック図である。この表示制御回路200は、入力制御回路20と表示メモリ21とレジスタ22とタイミング発生回路23とメモリ制御回路24と極性切換制御回路25とを備えている。

## 【 0 0 2 3 】

この表示制御回路200が外部のCPU等から受け取る広義の画像データDVを示す信号(以下、この信号も符号“DV”で表すものとする)およびアドレス信号ADwは、入力制御回路20に入力される。入力制御回路20は、アドレス信号ADwに基づき、広義の画像データDVを、画像データDAと表示制御データDcとに振り分ける。そして、画像データDAを表す信号(以下、これらの信号も符号“DA”で表すものとする)をアドレス信号ADwに基づくアドレス信号ADと共に表示メモリ21に供給することで画像データDAを表示メモリ21に書き込むと共に、表示制御データDcをレジスタ22に書き込む。表示制御データDcは、クロック信号CKの周波数や画像データDVの表す画像を表示するための水平走査期間および垂直走査期間を指定するタイミング情報を含んでいる。

## 【 0 0 2 4 】

タイミング発生回路(以下「TG」と略記する)23は、レジスタ22の保持する上記表示制御データに基づき、クロック信号CK、水平同期信号HSYおよび垂直同期信号VSYを生成する。また、TG23は、表示メモリ21およびメモリ制御回路24をクロック信号CKに同期させて動作させるためのタイミング信号を生成する。

## 【 0 0 2 5 】

メモリ制御回路24は、外部から入力されて入力制御回路20を介して表示メモリ21に格納された画像データDAのうち、液晶パネル600に表示すべき画像を表すデータを読み出すためのアドレス信号ADRと、表示メモリ21の動作を制御するための信号とを生成する。これらのアドレス信号ADRおよび制御信号は表示メモリ21に与えられ、これにより、液晶パネル600に表示すべき画像を表すデータがデジタル画像信号Daとして表示メモリ21から読み出され、表示制御回路200から出力される。このデジタル画像信号Daは、既述のように映像信号線駆動回路300に供給される。

## 【 0 0 2 6 】

極性切換制御回路25は、TG23によって生成された水平同期信号HSYおよび垂直同期信号VSYに基づき、上記の極性切換制御信号を生成する。この極性切換制御信号は、液晶パネル600の交流化駆動のための極性反転のタイミングを決定する制御信号であって、既述のように映像信号線駆動回路300および共通電極駆動回路500に供給される。

## 【 0 0 2 7 】

## &lt; 1 . 3 液晶パネル &gt;

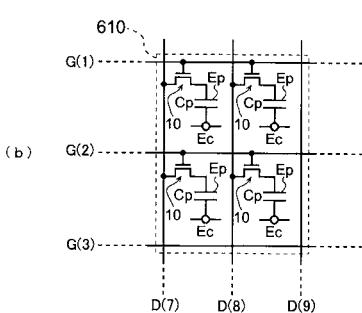

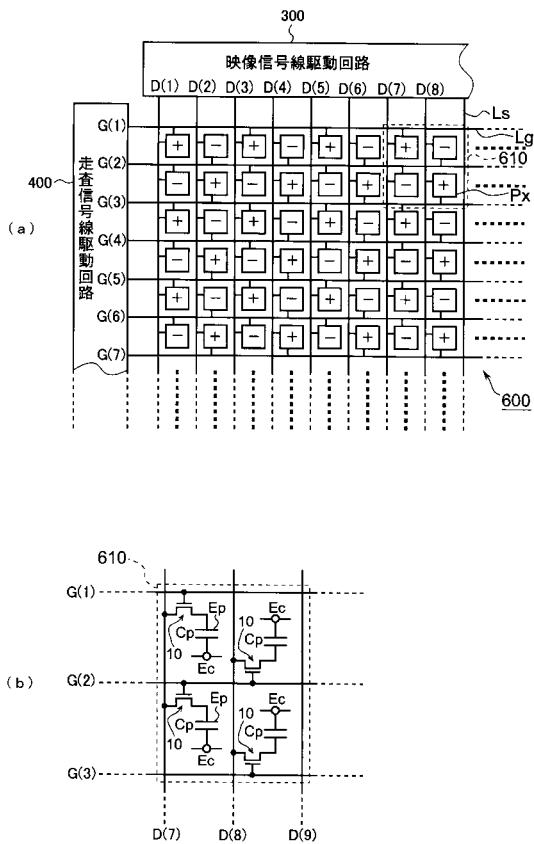

図2( a )は、本実施形態における液晶パネル600の構成を示す模式図であり、図2( b )は、この液晶パネルの一部(4画素に相当する部分)610の等価回路図である。

## 【 0 0 2 8 】

この液晶パネル600は、映像信号線駆動回路300に接続される複数の映像信号線Lsと、走査信号線駆動回路400に接続される複数の走査信号線Lgとを備え、当該複数の映像信号線Lsと当該複数の走査信号線Lgとは、各映像信号線Lsと各走査信号線Lgとが交差するように格子状に配設されている。そして、当該複数の映像信号線Lsと当該複数の走査信号線Lgとの交差点に対応して複数の画素形成部Pxがそれぞれ設けられている。各画素形成部Pxは、図2( b )に示すように、対応する交差点を通過する映像信号線Lsにソース端子が接続されたTFT10と、そのTFT10のドレイン端子に接続された画素電極Epと、上記複数の画素形成部Pxに共通的に設けられた共通電極(「対向電極」ともいう)Ecと、上記複数の画素形成部Pxに共通的に設けられ画素電極Epと共通電極Ecとの間に挟持された液晶層とからなる。そして、画素電極Epと共通電極Ecとそれらの間に挟持された液晶層により画素容量Cpが形成される。このような画

素形成部  $P_x$  の構成は、以下に述べる本発明の各実施形態においても同様である。なお、上記構成からわかるように、いずれかの走査信号線  $L_g$  に印加される走査信号  $G(k)$  がアクティブになると、その走査信号線が選択されて、その走査信号線に接続される（各画素形成部  $P_x$  の） $TFT10$  が導通状態となり、その  $TFT10$  に接続される画素電極  $E_p$  には、駆動用映像信号  $D(j)$  が映像信号線  $L_s$  を介して印加される。これにより、その印加された駆動用映像信号  $D(j)$  の電圧（共通電極  $E_c$  の電位を基準とする電圧）が、その画素電極  $E_p$  を含む画素形成部  $P_x$  に画素値として書き込まれる。

### 【0029】

上記のような画素形成部  $P_x$  は、マトリクス状に配置されて画素形成マトリクスを構成し、これに伴い、画素形成部  $P_x$  に含まれる画素電極  $E_p$  も、マトリクス状に配置されて画素電極マトリクスを構成する。ところで、画素形成部  $P_x$  の主要部である画素電極  $E_p$  は、液晶パネルに表示される画像の画素と 1 対 1 に対応し同一視できる。そこで、以下では、説明の便宜上、画素形成部  $P_x$  または画素電極  $E_p$  と画素とを同一視するものとし、「画素形成マトリクス」または「画素電極マトリクス」を「画素マトリクス」ともいう。

### 【0030】

図 2 (a)において、各画素形成部  $P_x$  に付されている“+”は、或るフレームにおいて当該画素形成部  $P_x$  を構成する画素液晶に（もしくは共通電極  $E_c$  を基準として画素電極  $E_p$  に）正の電圧が印加されることを意味し、“-”は、当該フレームにおいて当該画素形成部  $P_x$  を構成する画素液晶に（もしくは共通電極  $E_c$  を基準として画素電極  $E_p$  に）負の電圧が印加されることを意味し、これら各画素形成部  $P_x$  に付された“+”と“-”により、画素マトリクスにおける極性パターンが示される。このような極性パターンの表現方法は、以下に述べる本発明の他の実施形態においても同様である。なお図 2 (a)に示すように本実施形態では、画素液晶への印加電圧の正負極性を画素マトリクスにおける各行毎に反転させ且つ 1 フレーム毎にも反転させる駆動方式であるライン反転駆動方式が採用されている。

### 【0031】

#### <1.4 駆動方法>

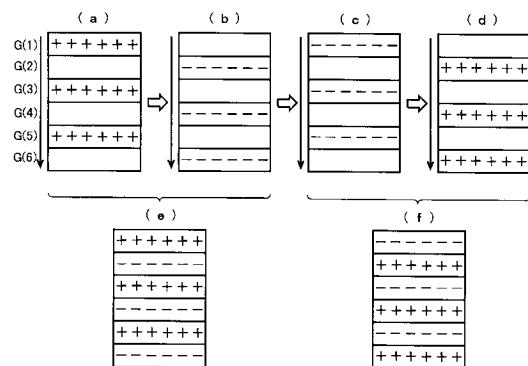

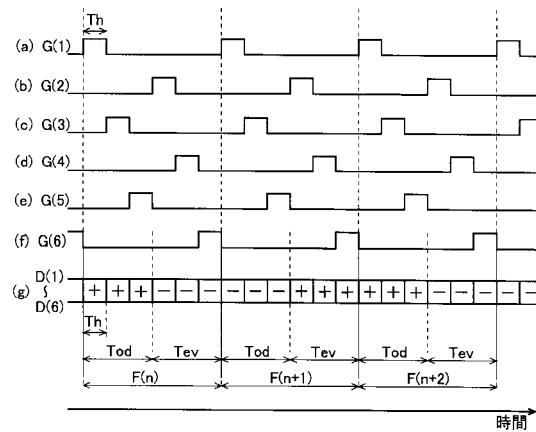

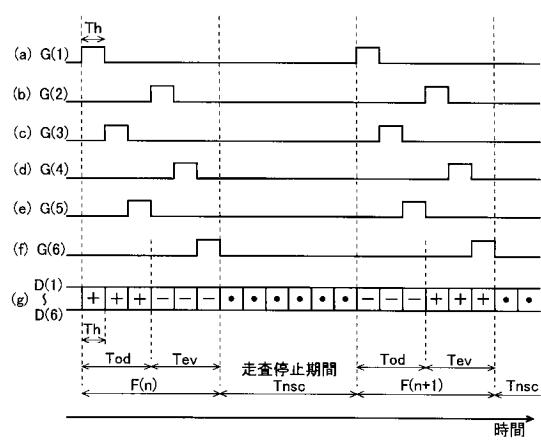

次に、図 3 および図 4 を参照しつつ、上記構成の液晶パネル 600 を備えた本実施形態に係る液晶表示装置の駆動方法を説明する。なお以下では、説明の便宜上、液晶パネル 600 における走査信号線  $L_g$  の本数を 6、映像信号線  $L_s$  の本数を 6 とし、6 本の走査信号線  $L_g$  には走査信号線駆動回路 400 により走査信号  $G(1) \sim G(6)$  がそれぞれ印加され、6 本の映像信号線  $L_s$  には映像信号線駆動回路 300 により駆動用映像信号  $D(1) \sim D(6)$  がそれぞれ印加されるものとする。

### 【0032】

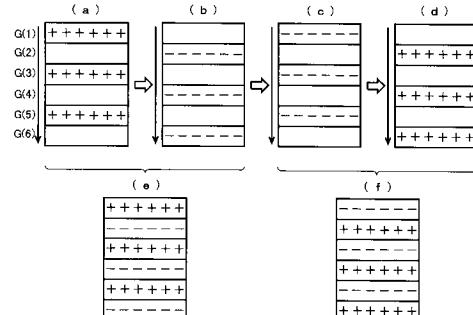

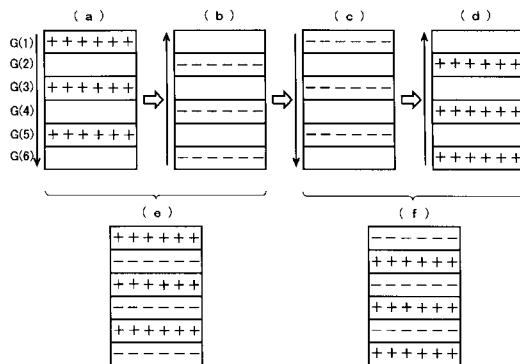

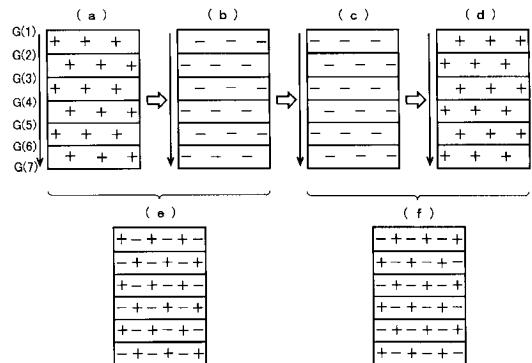

図 3 は、本実施形態に係る液晶表示装置の駆動方法を説明するための概念図であり、6 行からなる各矩形は画素マトリクスを示しており、この画素マトリクスに付された記号“+”または“-”は、画素液晶に印加される電圧すなわち共通電極  $E_c$  を基準とする画素電極  $E_p$  の電圧（以下「画素電圧」という）の極性を示しており、画素マトリクスを示す各矩形に沿って描かれた矢印は、走査方向（行番号の昇順に走査するか降順に走査するか）を示している。また、図 4 は、本駆動方法を説明するためのタイミングチャートである。すなわち図 4 (a) ~ (f) は走査信号  $G(1) \sim G(6)$  を示しており、走査信号  $G(k)$  が H レベルのとき、当該走査信号  $G(k)$  の印加される走査信号線  $L_g$  が選択され、走査信号  $G(k)$  が L レベルのとき、当該走査信号  $G(k)$  の印加される走査信号線  $L_g$  は非選択状態となる ( $k = 1 \sim 6$ )。また、図 4 (g) は、映像信号線  $L_s$  に印加される駆動用の映像信号  $D(1) \sim D(6)$  の（共通電極  $E_c$  を基準とする）電圧極性を 1 水平走査期間  $T_h$  毎に示している。

### 【0033】

図 3 (a) は、或るフレーム（以下では、これを第  $n$  フレームとし、記号“ $F(n)$ ”で表すものとする）の前半期間に映像信号  $D(1) \sim D(6)$  によって書き換えられる画素値に相当する画素電圧の極性を示している。本駆動方法では、図 4 (a) ~ (f) に示す

10

20

30

40

50

ように第 n フレーム F ( n ) の前半期間 T o d において、画素マトリクスにおける奇数番目の行に対応する走査信号 G ( 1 ) 、 G ( 3 ) 、 G ( 5 ) がこの順にアクティブとなることで、すなわち奇数番目の走査信号線 L g が昇順に選択されることで、飛び越し走査が行われる（以下、この走査を「第 1 の飛び越し走査」といい、この走査の期間 T o d を「奇数フィールド」という）。そして、画素マトリクスにおける第 1 行、第 3 行、第 5 行の各画素形成部 P x に書き込むべき画素値に相当する電圧が、それぞれ走査信号 G ( 1 ) 、 G ( 3 ) 、 G ( 5 ) のアクティブ期間において、図 4 ( g ) に示すように正極性の映像信号 D ( 1 ) ~ D ( 6 ) として各映像信号線 L s に印加される。なお、この奇数フィールド T o d では、偶数番目の走査信号 G ( 2 ) 、 G ( 4 ) 、 G ( 6 ) は非アクティブであるので、画素マトリクスにおける偶数行の画素形成部 P x には、当該奇数フィールド T o d 以前に印加された画素電圧が画素値として保持されている。このことを示すために、図 3 ( a ) では、画素マトリクスにおける偶数行には極性を示す記号“ + ”や“ - ”はいずれも付されていない。このような表記方法は、他の実施形態においても同様である。

10

#### 【 0 0 3 4 】

図 3 ( b ) は、第 n フレームの後半期間に映像信号 D ( 1 ) ~ D ( 6 ) によって書き換える画素値に相当する画素電圧の極性を示している。本駆動方法では、図 4 ( a ) ~ ( f ) に示すように第 n フレーム F ( n ) の後半期間 T e v において、画素マトリクスにおける偶数番目の行に対応する走査信号 G ( 2 ) 、 G ( 4 ) 、 G ( 6 ) がこの順にアクティブとなることで、すなわち偶数番目の走査信号線 L g が昇順に選択されることで、飛び越し走査が行われる（以下、この走査を「第 2 の飛び越し走査」といい、この走査の期間 T e v を「偶数フィールド」という）。そして、画素マトリクスにおける第 2 行、第 4 行、第 6 行の各画素形成部 P x に書き込むべき画素値に相当する電圧が、それぞれ走査信号 G ( 2 ) 、 G ( 4 ) 、 G ( 6 ) のアクティブ期間において、図 4 ( g ) に示すように負極性の映像信号 D ( 1 ) ~ D ( 6 ) として各映像信号線 L s に印加される。なお、この偶数フィールド T e v では、奇数番目の走査信号 G ( 1 ) 、 G ( 3 ) 、 G ( 5 ) は非アクティブであるので、画素マトリクスにおける奇数行の画素形成部 P x には、当該偶数フィールド T e v 以前（すなわち第 n フレーム F ( n ) の奇数フィールド T o d の期間）に印加された画素電圧が画素値として保持されている。

20

#### 【 0 0 3 5 】

図 3 ( c ) は、次の第 n + 1 フレームの前半期間に映像信号 D ( 1 ) ~ D ( 6 ) によって書き換える画素値に相当する画素電圧の極性を示している。本駆動方法では、第 n + 1 フレーム F ( n + 1 ) の前半期間である奇数フィールド T o d において、画素マトリクスにおける奇数番目の行に対応する走査信号 G ( 1 ) 、 G ( 3 ) 、 G ( 5 ) がこの順にアクティブとなることで第 1 の飛び越し走査が行われ（図 4 ( a ) ~ ( f ) ）、画素マトリクスにおける第 1 行、第 3 行、第 5 行の各画素形成部 P x に書き込むべき画素値に相当する電圧が、負極性の映像信号 D ( 1 ) ~ D ( 6 ) として各映像信号線 L s に印加される（図 4 ( g ) ）。なお、この奇数フィールド T o d では、偶数番目の走査信号 G ( 2 ) 、 G ( 4 ) 、 G ( 6 ) は非アクティブであるので、画素マトリクスにおける偶数行の画素形成部 P x には、当該奇数フィールド T o d 以前（すなわち第 n フレーム F ( n ) の偶数フィールド T e v の期間）に印加された画素電圧が画素値として保持されている。

30

#### 【 0 0 3 6 】

図 3 ( d ) は、第 n + 1 フレームの後半期間に映像信号 D ( 1 ) ~ D ( 6 ) によって書き換える画素値に相当する画素電圧の極性を示している。本駆動方法では、第 n + 1 フレーム F ( n + 1 ) の後半期間である偶数フィールド T e v において、画素マトリクスにおける偶数番目の行に対応する走査信号 G ( 2 ) 、 G ( 4 ) 、 G ( 6 ) がこの順にアクティブとなることで第 2 の飛び越し走査が行われ（図 4 ( a ) ~ ( f ) ）、画素マトリクスにおける第 2 行、第 4 行、第 6 行の各画素形成部 P x に書き込むべき画素値に相当する電圧が、正極性の映像信号 D ( 1 ) ~ D ( 6 ) として各映像信号線 L s に印加される（図 4 ( g ) ）。なお、この偶数フィールド T e v では、奇数番目の走査信号 G ( 1 ) 、 G ( 3 ) 、 G ( 5 ) は非アクティブであるので、画素マトリクスにおける奇数行の画素形成部 P

40

x には、当該偶数フィールド T e v 以前（すなわち第 n + 1 フレーム F ( n + 1 ) の奇数フィールド T o d の期間）に印加された画素電圧が画素値として保持されている。

#### 【 0 0 3 7 】

上記のような駆動方法によれば、画素マトリクスの極性パターンは、第 n フレーム F ( n ) の終了時点では、図 3 ( e ) に示すパターンとなり、第 n + 1 フレーム F ( n + 1 ) の終了時点では、図 3 ( f ) に示すパターンとなる。このようにして上記駆動方法により、ライン反転駆動を行うことができる。

#### 【 0 0 3 8 】

##### < 1 . 5 効果 >

本実施形態では、上記のようにしてライン反転駆動が行われるが、従来のライン反転駆動に比べ、消費電力を大幅に低減することができる。以下、この点につき図 5 および図 6 を参照して説明する。

#### 【 0 0 3 9 】

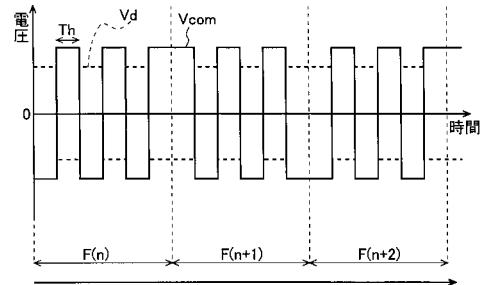

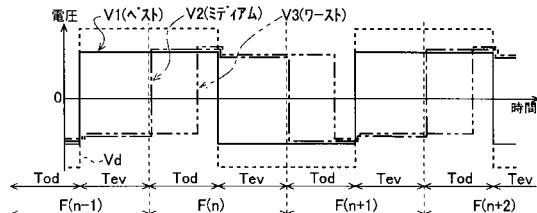

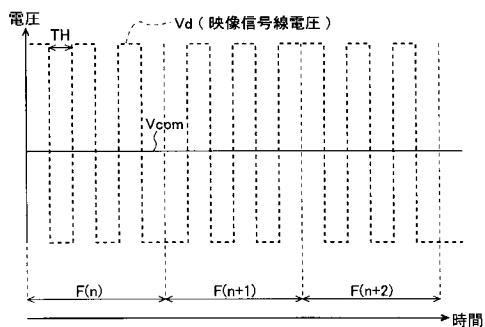

図 5 は、本実施形態において映像信号線 L s に印加される映像信号 D ( 1 ) ~ D ( 6 ) の電圧（以下「映像信号電圧」といい、各映像信号線 L s 每の電圧値を区別する必要がないときには記号 “ V d ” で表すものとする）、および、共通電極 E c に印加される共通電圧 V c o m の電圧波形を、走査信号 G ( 1 ) ~ G ( 6 ) の波形と共に示している。一方、図 6 は、ライン反転駆動方式を採用した従来の液晶表示装置（以下「従来例」という）における映像信号電圧 V d および共通電圧 V c o m の波形を示している。両図を比較すればわかるように、走査線数を Y とした場合、本実施形態では、反転周波数が従来例の  $1 / ( Y - 1 )$  となる（図 5 、図 6 に示した例では  $Y = 6$  であるので、反転周波数が従来例の  $1 / 5$  となる）。ところで、一般に液晶パネルを駆動するための消費電力は反転周波数に比例する。したがって、本実施形態によれば、液晶パネル駆動のための消費電力が従来例に比べてほぼ  $1 / ( Y - 1 )$  となる。

#### 【 0 0 4 0 】

このように本実施形態によれば、図 3 および図 4 に示したようなライン反転駆動により、フレーム反転駆動に比べてフリッカの発生を抑えつつ、従来のライン反転駆動に比べて消費電力を大幅に低減することができる。

#### 【 0 0 4 1 】

なお、上記実施形態では、画素マトリクスにおける 1 行毎に画素電圧の極性を反転させるライン反転駆動を前提として、各フレームにおいて前半期間では奇数ラインのみが走査され、後半期間では偶数ラインのみが走査される構成となっている。すなわち、反転周波数を削減するために、走査信号線 L g を 1 本おきに選択する飛び越し走査を行う構成となっている。しかし、各フレームの期間が、正極性の電圧を印加すべきラインを走査する期間と、負極性電圧を印加すべきラインを飛び越し走査する期間とに分かれるような構成であれば、すなわち、各フレーム内で同一極性の電圧を印加すべきラインが連続的に走査されるような構成であれば、走査信号線 L g を複数本おきに選択する飛び越し走査を行うようにしてもよい。例えば、画素マトリクスにおける 2 ライン毎に画素電圧の極性を反転させる 2 ライン反転駆動を前提として、各フレームにおいて前半期間では走査信号線 L g を 2 本おきに 2 本ずつを選択することで第 1 の飛び越し走査を行い、各フレームの後半期間では同一フレームの前半期間で選択されなかった走査信号線 L g を 2 本おきに 2 本ずつを選択することで第 2 の飛び越し走査を行うという構成にしてもよい。このような構成によつても反転周波数が大幅に低下するので、それに応じて消費電力が大幅に削減される。

#### 【 0 0 4 2 】

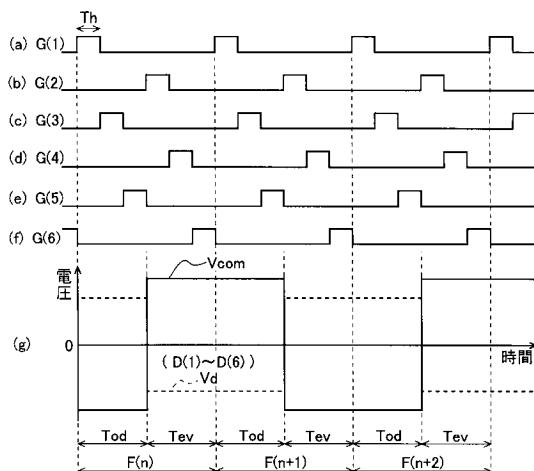

##### < 2 . 第 2 の実施形態 >

次に、本発明の第 2 の実施形態に係る液晶表示装置について説明する。本実施形態は、図 3 および図 4 に示した駆動方法に代えて図 7 および図 8 に示す駆動法を採用している点で、第 1 の実施形態と相違する。本実施形態における全体構成および液晶パネルの構成は第 1 の実施形態と同様であるので、同一または対応する部分に同一の参照符号を付して説明を省略する。

10

20

30

40

50

## 【 0 0 4 3 】

## &lt; 2 . 1 駆動方法 &gt;

以下、図7および図8を参照しつつ本実施形態に係る液晶表示装置の駆動方法を説明する。なお本実施形態においても、説明の便宜上、液晶パネル600における走査信号線Lgの本数を6、映像信号線Lsの本数を6とし、6本の走査信号線Lgには走査信号線駆動回路400により走査信号G(1)～G(6)がそれぞれ印加され、6本の映像信号線Lsには映像信号線駆動回路300により駆動用映像信号D(1)～D(6)がそれぞれ印加されるものとする。

## 【 0 0 4 4 】

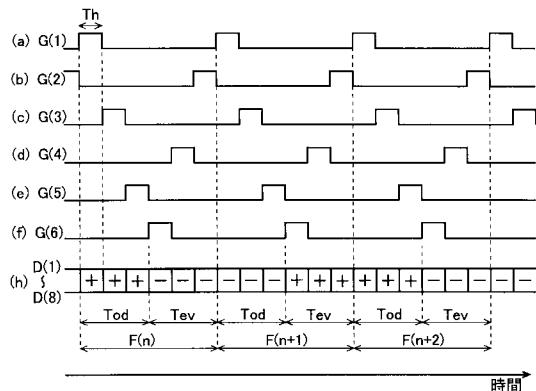

図7は、本実施形態に係る液晶表示装置の駆動方法を説明するための概念図であり、この図における表現方法は図3で採用したものと同様である。また、図8は、本駆動方法を説明するためのタイミングチャートであり、この図における表現方法は図4で採用したものと同様である。

## 【 0 0 4 5 】

図7(a)は、第nフレームの前半期間に映像信号D(1)～D(6)によって書き換える画素値に相当する画素電圧の極性を示している。本駆動方法では、図8(a)～(f)に示すように、第nフレームF(n)の前半期間である奇数フィールドToddにおいて、画素マトリクスにおける奇数番目の行に対応する走査信号G(1)、G(3)、G(5)がこの順にアクティブとなることで、すなわち奇数番目の走査信号線Lgが昇順に選択されることで、第1の飛び越し走査が行われる。そして、画素マトリクスにおける第1行、第3行、第5行の各画素形成部Pxに書き込むべき画素値に相当する電圧が、それぞれ走査信号G(1)、G(3)、G(5)のアクティブ期間において、図8(g)に示すように正極性の映像信号D(1)～D(6)として各映像信号線Lsに印加される。なお、この奇数フィールドToddでは、偶数番目の走査信号G(2)、G(4)、G(6)は非アクティブであるので、画素マトリクスにおける偶数行の画素形成部Pxには、当該奇数フィールドTodd以前に印加された画素電圧が画素値として保持されている。

## 【 0 0 4 6 】

図7(b)は、第nフレームの後半期間に映像信号D(1)～D(6)によって書き換える画素値に相当する画素電圧の極性を示している。本駆動方法では、図8(a)～(f)に示すように第nフレームF(n)の後半期間Tevにおいて、画素マトリクスにおける偶数番目の行に対応する走査信号G(2)、G(4)、G(6)が逆順にアクティブとなることで、すなわち偶数番目の走査信号線Lgが降順に選択されることで、第2の飛び越し走査が行われる。そして、画素マトリクスにおける第6行、第4行、第2行の各画素形成部Pxに書き込むべき画素値に相当する電圧が、それぞれ走査信号G(6)、G(4)、G(2)のアクティブ期間において、図8(g)に示すように負極性の映像信号D(1)～D(6)として各映像信号線Lsに印加される。ここで、図7(b)における上向きの矢印は、偶数フィールドTevにおける第2の飛び越し走査では、従来例や第1の実施形態とは逆向きに走査が行われることを示している。なお、この偶数フィールドTevでは、奇数番目の走査信号G(1)、G(3)、G(5)は非アクティブであるので、画素マトリクスにおける奇数行の画素形成部Pxには、当該偶数フィールドTev以前(すなわち第nフレームF(n)の奇数フィールドToddの期間)に印加された画素電圧が画素値として保持されている。

## 【 0 0 4 7 】

図7(c)は、次の第n+1フレームの前半期間に映像信号D(1)～D(6)によって書き換える画素値に相当する画素電圧の極性を示している。本駆動方法では、第n+1フレームF(n+1)の前半期間である奇数フィールドToddにおいて、画素マトリクスにおける奇数番目の行に対応する走査信号G(1)、G(3)、G(5)がこの順にアクティブとなることで第1の飛び越し走査が行われ(図8(a)～(f))、画素マトリクスにおける第1行、第3行、第5行の各画素形成部Pxに書き込むべき画素値に相当する電圧が、負極性の映像信号D(1)～D(6)として各映像信号線Lsに印加される(

10

20

30

40

50

図 8 ( g ) )。なお、この奇数フィールド T o d では、偶数番目の走査信号 G ( 2 )、G ( 4 )、G ( 6 ) は非アクティブであるので、画素マトリクスにおける偶数行の画素形成部 P x には、当該奇数フィールド T o d 以前 ( すなわち第 n フレーム F ( n ) の偶数フィールド T e v の期間 ) に印加された画素電圧が画素値として保持されている。

#### 【 0 0 4 8 】

図 7 ( d ) は、第 n + 1 フレームの後半期間に映像信号 D ( 1 ) ~ D ( 6 ) によって書き換えられる画素値に相当する画素電圧の極性を示している。本駆動方法では、第 n + 1 フレーム F ( n + 1 ) の後半期間である偶数フィールド T e v において、画素マトリクスにおける偶数番目の行に対応する走査信号 G ( 2 )、G ( 4 )、G ( 6 ) が逆順にアクティブとなることで第 2 の飛び越し走査が行われ ( 図 8 ( a ) ~ ( f ) )、画素マトリクスにおける第 6 行、第 4 行、第 2 行の各画素形成部 P x に書き込むべき画素値に相当する電圧が、それぞれ走査信号 G ( 6 )、G ( 4 )、G ( 2 ) のアクティブ期間において正極性の映像信号 D ( 1 ) ~ D ( 6 ) として各映像信号線 L s に印加される ( 図 8 ( g ) )。なお、この偶数フィールド T e v では、奇数番目の走査信号 G ( 1 )、G ( 3 )、G ( 5 ) は非アクティブであるので、画素マトリクスにおける奇数行の画素形成部 P x には、当該偶数フィールド T e v 以前 ( すなわち第 n + 1 フレーム F ( n + 1 ) の奇数フィールド T o d の期間 ) に印加された画素電圧が画素値として保持されている。

#### 【 0 0 4 9 】

上記のような駆動方法によれば、画素マトリクスの極性パターンは、第 n フレーム F ( n ) の終了時点では、図 7 ( e ) に示すパターンとなり、第 n + 1 フレーム F ( n + 1 ) の終了時点では、図 7 ( f ) に示すパターンとなる。このようにして上記駆動方法により、第 1 の実施形態と同様にライン反転駆動を行うことができる。

#### 【 0 0 5 0 】

##### < 2 . 2 作用および効果 >

上記のように本実施形態によれば、第 1 の実施形態と同様に反転周波数を大幅低下させつつライン反転駆動を行うことができるので、消費電力の削減について第 1 の実施形態と同様の効果を得ることができる。

#### 【 0 0 5 1 】

また、本実施形態では、図 7 ( a ) ~ ( d ) に示すように、第 1 の飛び越し走査の方向と第 2 の飛び越し走査の方向とは互いに逆となっている。すなわち、昇順の飛び越し走査と降順の飛び越し走査とが交互に行われるよう走査信号線 L g に走査信号 G ( 1 ) ~ G ( 6 ) が印加される ( 図 8 ( a ) ~ ( f ) )。これにより、シャドーの発生が抑制される。以下、この点につき図 9 ~ 図 12 を参照して説明する。

#### 【 0 0 5 2 】

図 9 は、本発明が対象とするアクティブマトリクス型液晶表示装置における画素形成部 P x の等価回路を示している。この図に示すように、画素電極 E p を挟む 2 本の映像信号線のうち画素形成部 ( 詳しくは画素容量 C p ) にデータを書き込むための映像信号線 L s である対応映像信号線 L s s と画素電極 E p との間に寄生容量 ( 以下 ' C s d ( 自 ) ' という ) が存在すると共に、それら 2 本の映像信号線のうちの他方の映像信号線 ( 以下 ' 隣接映像信号線 ' という ) L s n と画素電極 E p との間に寄生容量 ( 以下 ' C s d ( 他 ) ' という ) が存在する。このため、各画素値に相当する画素電圧は、当該画素を形成する画素形成部 P x に当該画素値が書き込まれた後 ( TFT がオフの状態 ) において、C s d ( 自 ) を介して対応映像信号線 L s s の電位変化 ( 映像信号電圧 V d の変化 ) の影響を受けると共に、C s d ( 他 ) を介して隣接映像信号線 L s n の電位変化 ( 映像信号電圧 V d の変化 ) の影響を受ける。そして、このような対応映像信号線 L s s および隣接映像信号線 L s n における映像信号電圧 V d の変化に基づく影響によって、縦シャドー等のように本来の表示内容には含まれない表示としての ' シャドー ' が発生する。

#### 【 0 0 5 3 】

図 10 は、このような寄生容量 C s d ( 自 )、C s d ( 他 ) を介しての映像信号電圧 V d の変化の影響によるシャドーの低減を検討するための電圧波形図である。この図において

10

20

30

40

50

、（太い）点線は、映像信号電圧  $V_d$  を示しており（ここでは説明の便宜上、全ての映像信号線の電圧は同一値  $V_d$  としている）、実線、1点鎖線および2点鎖線は、画面上の異なる位置における画素電極への印加電圧（以下、これも便宜上「画素電圧」という）を示している。実線で示される画素電圧  $V_1$  は、映像信号電圧  $V_d$  とほぼ同じタイミングで変化し、1点鎖線で示される画素電圧  $V_2$  は、映像信号電圧  $V_d$  の変化に対して1/4周期ずれて変化し、2点鎖線で示される画素電圧  $V_3$  は、映像信号電圧  $V_d$  の変化に対して略1/2周期ずれて変化している。これら3つの画素電圧  $V_1$ ,  $V_2$ ,  $V_3$  のうち実線で示される画素電圧  $V_1$  は、映像信号電圧  $V_d$  の変化の影響が最も小さく、2点鎖線で示される画素電圧  $V_3$  は、映像信号電圧  $V_d$  の変化の影響が最も大きく、1点鎖線で示される画素電圧  $V_2$  は、映像信号電圧  $V_d$  の変化の影響の程度はそれらの中間となる。したがって、シャドー低減の観点からすると、画素電圧  $V_1$  に対応する画素は「ベスト条件」にあり、画素電圧  $V_2$  に対応する画素は「ミディアム条件」にあり、画素電圧  $V_3$  に対応する画素は「ワースト条件」にあると考えることができる。なお、上記より、一般に、第1の実施形態のように走査方向が固定されている場合、画素マトリクスのうち走査開始時近傍で走査される行と走査終了時近傍に走査される行とでは、表示すべき内容が同一であっても画素電圧の実効値が相違し、それによって両行の画素の間に輝度差が生じることになる。この輝度差はシャドーの発生を意味する。

10

20

30

40

#### 【0054】

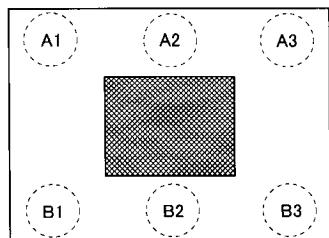

図11は、このようなシャドーの低減の観点から、画面の上部Aにおける画素に対する条件と画面の下部Bにおける画素に対する条件とを整理したものであり、図11(b)は、第1の実施形態のように常に昇順に飛び越し走査を行ってライン反転駆動を行う場合における各位置の画素の条件を示しており、図11(c)は、本実施形態のように昇順の飛び越し走査と降順の飛び越し走査とを交互に繰り返してライン反転駆動を行う場合における各位置の画素の条件を示している。

#### 【0055】

第1の実施形態のように常に昇順に走査する場合、図11(b)より、画面上部Aでは奇数ラインの画素はミディアム条件、偶数ラインの画素はベスト条件にあり、一方、画面下部Bでは奇数ラインの画素はワースト条件、偶数ラインの画素はミディアム条件にある。したがって、この場合には、画面下部Bにおける条件が画面上部Aに比べて悪いので、画面下部Bにおいて映像信号電圧  $V_d$  の変化の影響を受け、シャドーが発生しやすい。そして、例えば図12に示すように塗りつぶされた矩形を画面の中央部に表示すると、このシャドーが目立ちやすくなる。すなわち、図12に示す表示の場合、画面の左側および右側における下方部B1およびB3には上記作用によりシャドーが発生するが、この矩形の下方部B2におけるシャドーの発生はこの矩形表示の影響で抑制される。その結果、画面の左側における上方部A1と下方部B1との輝度差、および、右側における上方部A3と下方部B3との輝度差が、シャドーとして人間に認識されやすくなる。

30

#### 【0056】

これに対し、本実施形態のように昇順の飛び越し走査と降順の飛び越し走査とを交互に繰り返すという走査（以下「方向反転走査」という）の場合には、図11(c)より、画面上部Aにおける奇数ラインおよび偶数ラインの画素は共にミディアム条件にあり、一方、画面下部Bでは奇数ラインの画素はワースト条件、偶数ラインの画素はベスト条件にある。したがって、この場合、画面下部Bにおいてはワースト条件とベスト条件とが相殺され、その結果、画面下部Bにおける条件は、画面上部Aにおける条件と実質的に同一となる。したがって、本実施形態のように方向反転走査が行われると、シャドーの発生が抑制されることになる。

40

#### 【0057】

以上のように本実施形態によれば、第1の実施形態と同様の効果を得つつ、シャドーの発生を抑制することができる。

#### 【0058】

<3. 第3の実施形態>

50

次に、本発明の第3の実施形態に係る液晶表示装置について説明する。本実施形態は、図4に示した駆動方法に代えて図13に示すような駆動方法を採用している点で、第1の実施形態と相違する。本実施形態における全体構成および液晶パネルの構成は第1の実施形態と同様であるので、同一または対応する部分に同一の参照符号を付して説明を省略する。なお、本実施形態における画素マトリクスの極性パターンは、第1の実施形態と同様、液晶パネル600の駆動に伴って図3(a)～(d)に示すように変化するが、図3(b)の極性パターンから図3(c)の極性パターンへと変化する間に後述の走査停止期間が存在し、この点で第1の実施形態と相違する。

#### 【0059】

##### <3.1 駆動方法>

10

以下、図3および図13を参照して本実施形態に係る液晶表示装置の駆動方法を説明する。なお本実施形態においても、説明の便宜上、液晶パネル600における走査信号線Lgの本数を6、映像信号線Lsの本数を6とし、6本の走査信号線Lgには走査信号線駆動回路400により走査信号G(1)～G(6)がそれぞれ印加され、6本の映像信号線Lsには映像信号線駆動回路300により駆動用映像信号D(1)～D(6)がそれぞれ印加されるものとする。

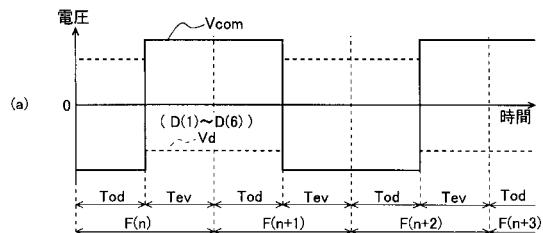

#### 【0060】

本実施形態では、第nフレームF(n)において、図13(a)～(g)に示すように、第1の実施形態における第nフレームF(n)と同様の走査信号G(1)～G(6)および映像信号D(1)～D(6)が液晶パネル600(の走査信号線Lgおよび映像信号線Ls)に印加され、第1の実施形態における第nフレームF(n)と同様の駆動が行われる。すなわち、第nフレームF(n)において、図3(a)(b)に示すような反転駆動が行われ、この第nフレームF(n)の終了時点において、画素マトリクスの極性パターンが図3(e)に示すようになる。

20

#### 【0061】

本実施形態では、図13(a)～(f)に示すように、第nフレームF(n)の終了後、所定期間Tnsc(例えば1フレームの期間)だけ全ての走査信号G(1)～G(6)が非アクティブとなって走査が停止する。この走査停止期間Tnscでは、画素マトリクスの極性パターンが図3(e)に示すパターンである状態が継続する。

30

#### 【0062】

上記の走査停止期間Tnscが終了すると、本実施形態における第n+1フレームF(n+1)が開始する。この第n+1フレームF(n+1)では、図13(a)～(g)に示すように、第1の実施形態における第n+1フレームF(n+1)と同様の走査信号G(1)～G(6)および映像信号D(1)～D(6)が液晶パネル600に印加され、第1の実施形態における第n+1フレームF(n+1)と同様の駆動が行われる。すなわち、第n+1フレームF(n+1)において、図3(c)(d)に示すような反転駆動が行われ、この第n+1フレームF(n+1)の終了時点において、画素マトリクスの極性パターンが図3(f)に示すようになる。

#### 【0063】

上記の第n+1フレームF(n)が終了すると、第n+2フレームF(n+2)へ移行する前に上記と同様の走査停止期間Tnscが挿入される。この走査停止期間Tnscでは、画素マトリクスの極性パターンが図3(f)に示すパターンである状態が継続する。

40

#### 【0064】

このようにして本実施形態では、1フレームが終了する毎に走査停止期間Tnscが挿入される。すなわち同一極性の映像信号D(1)～D(6)が印加される第1の飛び越し走査が行われ、続けて、第1の飛び越し走査のときと異なる極性の映像信号D(1)～D(6)が印加される第2の飛び越し走査が行われた後に、所定期間Tnscだけ走査が停止し、この期間Tnscの経過後に次のフレームが開始する。なお、走査停止期間Tnscにおける映像信号D(1)～D(6)の電圧レベルは、特に限定されない。例えば走査停止期間Tnscの直前の電圧を維持してもよいし、適宜の周期で変化する電圧値としても

50

よいし、また、映像信号線駆動回路 300 における映像信号 D(1) ~ D(6) の出力端子を高インピーダンス状態としてもよい。

### 【0065】

#### <3.2 作用および効果>

上記のような本実施形態によれば、第1の実施形態と同様の効果に加えて、走査停止期間 T<sub>ns</sub>c の挿入により、フリッカおよびシャドーの発生を低減することができる。以下、これらにつき説明する。

### 【0066】

#### <3.2.1 フリッカの低減>

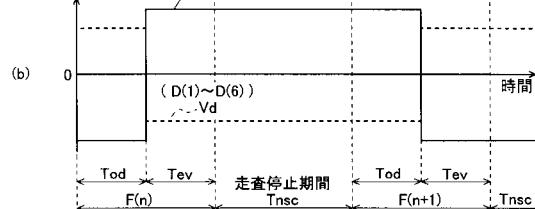

図14(a)は、第1の実施形態における映像信号電圧 V<sub>d</sub> および共通電圧 V<sub>com</sub> の波形を示している。第1の実施形態では、各フレーム内で、画素マトリクスのうち同一極性の画素電圧を印加すべき行の走査が連続的に行われることから、映像信号電圧 V<sub>d</sub> および共通電圧 V<sub>com</sub> の極性反転の直前には、画素マトリクスの全画素電圧が同一極性となる。すなわち、図14(a)に示した例では、第nフレーム F(n)において奇数フィールド T<sub>od</sub> から偶数フィールド T<sub>ev</sub> へ切り替わる直前(第1の飛び越し走査から第2の飛び越し走査へと移行する直前)に、画素マトリクスの全画素電圧が正極性となり、第n+1フレーム F(n+1)において奇数フィールド T<sub>od</sub> から偶数フィールド T<sub>ev</sub> へ切り替わる直前には、画素マトリクスの全画素電圧が負極性となる。このように、画素マトリクスにおいてほぼ全ての画素電圧が同一極性となる期間が繰り返し現れるため、フリッカの発生が問題となる。

10

20

### 【0067】

これに対し、本実施形態における映像信号電圧 V<sub>d</sub> および共通電圧 V<sub>com</sub> は、図14(b)に示す波形となり、走査停止期間 T<sub>ns</sub>c では、画素電圧の極性が画素マトリクスにおいて行毎に異なる状態、すなわち、画素電圧の極性の異なる画素形成部が画素マトリクスにおいて均等に分散した状態となる。図14(b)に示した例では、例えば、第nフレーム F(n)の後の走査停止期間 T<sub>ns</sub>c では、画素マトリクスの極性パターンが図3(e)に示すパターンである状態が継続する。その結果、本実施形態によれば、画素マトリクスにおいてほぼ全ての画素電圧が同一極性となる期間が繰り返し現れるものの、画素電圧の極性の異なる画素形成部が画素マトリクスにおいて均等に分散した状態の期間が走査停止期間 T<sub>ns</sub>c として挿入されることで、フリッカの発生しうる期間の占める割合が小さくなる。これにより、第1の実施例に比べフリッカが低減される。

30

### 【0068】

#### <3.2.2 シャドーの低減>

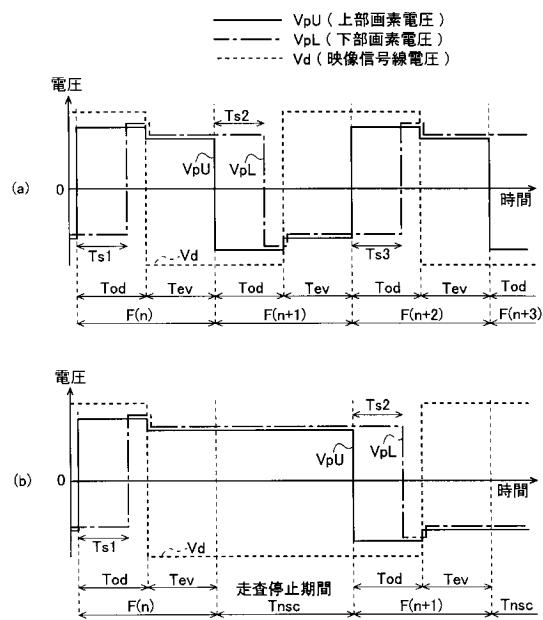

図15(a)は、第1の実施形態における映像信号電圧 V<sub>d</sub>、ならびに、画面上部における画素電極への印加電圧(以下、便宜上「上部画素電圧」という) V<sub>pU</sub> および画面下部における画素電極への印加電圧(以下、便宜上「下部画素電圧」という) V<sub>pL</sub> の波形を示しており、図15(b)は、本実施形態における映像信号電圧 V<sub>d</sub> ならびに上部画素電圧 V<sub>pU</sub> および下部画素電圧 V<sub>pL</sub> の波形を示している。そして、これら図15(a)(b)において、映像信号電圧 V<sub>d</sub> は(太い)点線で、上部画素電圧 V<sub>pU</sub> は実線で、下部画素電圧 V<sub>pL</sub> は1点鎖線で、それぞれ示されている。なお、ここでは、説明の便宜上、画面の全領域において同一輝度で表示されるものとする。

40

### 【0069】

第1の実施形態では、図15(a)に示すように、例えば第nフレーム F(n)で奇数フィールド T<sub>od</sub> から偶数フィールド T<sub>ev</sub> へと切り替わるときに映像信号電圧 V<sub>d</sub> の極性が反転し、上部画素電圧 V<sub>pU</sub> および下部画素電圧 V<sub>pL</sub> は、寄生容量 C<sub>sd</sub>(自), C<sub>sd</sub>(他) を介して当該反転の影響を受けて共に若干低下する。しかし、この極性反転後も第nフレーム F(n)内では上部画素電圧 V<sub>pU</sub> と下部画素電圧 V<sub>pL</sub> とは略同一であるので、画面の上部と下部とで輝度差はほとんど見られない。これに対し、次の第n+1フレーム F(n+1)に入ると、上部画素電圧 V<sub>pU</sub> の極性が反転し、所定期間 T<sub>s2</sub> は上部画素電圧 V<sub>pU</sub> の極性と下部画素電圧 V<sub>pL</sub> の極性とが相違し、その所定期間 T<sub>s2</sub>

50

の経過後に下部画素電圧  $V_{pL}$  の極性も反転する。そして、この所定期間  $T_{s2}$  では、下部画素電圧  $V_{pL}$  は映像信号電圧  $V_d$  の影響を受けた値となっているが、上部画素電圧  $V_{pU}$  は映像信号電圧  $V_d$  の影響をほとんど受けないので、上部画素電圧  $V_{pU}$  と下部画素電圧  $V_{pL}$  とでは実効値（絶対値）が相違し、その結果、画面における上部と下部とで輝度差が生じる。同様にして、第  $n$  フレーム  $F(n)$  の開始時点から下部画素電圧  $V_{pL}$  の極性が反転するまでの期間  $T_{s1}$ 、および、第  $n+1$  フレーム  $F(n+2)$  の開始時点から下部画素電圧  $V_{pL}$  の極性が反転するまでの期間  $T_{s3}$  においても、画面における上部と下部とで輝度差が生じる。よって、このような期間  $T_{s1}$ ,  $T_{s2}$ ,  $T_{s3}$  の存在により、第 1 の実施形態ではシャドーの発生が問題となる。

## 【0070】

10

これに対し本実施形態では、上記と同様、画面における上部と下部とで輝度差が生じる期間  $T_{s1}$ ,  $T_{s2}$  が存在するが、走査停止期間  $T_{nsc}$  が挿入され、この走査停止期間  $T_{nsc}$  では、上部画素電圧  $V_{pU}$  と下部画素電圧  $V_{pL}$  とは略同一となって、画面における上部と下部とで輝度差は見られない。このように本実施形態によれば、輝度差の見られない期間である走査停止期間  $T_{nsc}$  の挿入によって、輝度差の生じるうる期間の割合が小さくなる。これにより、第 1 の実施例に比べシャドーが低減される。

## 【0071】

20

## &lt;3.3 变形例&gt;

上記第 4 の実施形態では、第 1 の実施形態のように常に昇順に飛び越し走査を行いつつ走査停止期間  $T_{nsc}$  を挿入する構成となっているが、第 2 の実施形態のように昇順の飛び越し走査と降順の飛び越し走査とを交互に繰り返す方向反転走査を行いつつ走査停止期間  $T_{nsc}$  を挿入する構成としてもよい。

## 【0072】

20

## &lt;4.第4の実施形態&gt;

次に、本発明の第 4 の実施形態に係る液晶表示装置について説明する。本実施形態では、全体構成が第 1 の実施形態と同様であるので、同一または対応する部分に同一の参照符号を付して詳しい説明を省略する。一方、本実施形態における液晶パネル 600 の具体的構成および画素マトリクスにおける極性パターンは、第 1 の実施形態と相違する。以下では、これらを中心に説明する。

## 【0073】

30

## &lt;4.1 構成および駆動方法&gt;

図 16 (a) は、本実施形態における液晶パネル 600 の構成を示す模式図であり、図 16 (b) は、この液晶パネル 600 の一部（4 画素に相当する部分）610 の等価回路図である。これらの図に示すように、この液晶パネル 600 は、いわゆる千鳥構造のパネルである。すなわち、同一の走査信号線  $L_g$  に TFT10 を介して接続される画素電極（以下「同時選択画素電極」という）が、画素マトリクスにおける同一行に配置されるのではなく、上下にずらして、隣接する 2 行に分散的に配置されている。すなわち、画素マトリクスにおける同一行の各画素電極に接続される TFT10 のゲート端子は、同一の走査信号線  $L_g$  に全て接続されるのではなく、その画素行を挟む 2 本の走査信号線  $L_g$  に分散的に接続される。なお、図 16 (a) (b) に示した例は、典型例であって、同時選択画素電極が画素マトリクスにおける隣接 2 行に交互に配置されているが、同時選択画素電極が隣接 2 行に分散的に配置されていればよく、このような交互に配置さえる構成に限定されない。ただし以下では、同時選択画素電極が画素マトリクスにおける隣接 2 行に交互に配置されているものとして説明を進める。

## 【0074】

40

本実施形態では、上記のような同時選択画素電極の分散配置（千鳥構造）に応じて、映像信号線駆動回路 300 から各画素値に対応する映像信号  $D(j)$  ( $j = 1, 2, 3, \dots$ ) が output される。このためには、例えば、偶数番目の映像信号  $D(2)$ ,  $D(4)$ ,  $D(6)$ , ... が奇数番目の映像信号  $D(1)$ ,  $D(3)$ ,  $D(5)$ , ... よりも 1 水平走査期間だけ遅れて出力されるように、映像信号線駆動回路 300 に遅延回路を設けた構成とすれば

50

よい。また、これに代えて、表示すべき画像の画素データを、上記のような同時選択画素電極の分散配置に応じた順序でデジタル画像信号D<sub>a</sub>として映像信号線駆動回路300に供給するように、表示制御回路200の構成を変更してもよい。

#### 【0075】

一方、走査信号G(k)(k=1, 2, 3, ...)、および映像信号D(j)(j=1, 2, 3, ...)の極性については、第1の実施形態と同様、図4に示すような信号および極性となっている。また、共通電圧V<sub>com</sub>も、第1の実施形態と同様、図5(g)に示す波形となっており、これにより共通電極E<sub>c</sub>も交流化駆動される。

#### 【0076】

上記のような構成および駆動方法によれば、画素マトリクスの極性パターンは図17に示すパターンとなる。ただし図17では、説明の便宜上、液晶パネル600における走査信号線L<sub>g</sub>の本数を6、映像信号線L<sub>s</sub>の本数を6とし、6本の走査信号線L<sub>g</sub>には走査信号線駆動回路400により走査信号G(1)～G(6)がそれぞれ印加され、6本の映像信号線L<sub>s</sub>には映像信号線駆動回路300により駆動用映像信号D(1)～D(6)がそれぞれ印加されるものとしている。10

#### 【0077】

図17(a)は、第nフレームF(n)の前半期間である奇数フィールドT<sub>od</sub>で映像信号D(1)～D(6)によって書き換えられる画素値に相当する画素電圧の極性を示している。本駆動方法では、このフレームの奇数フィールドT<sub>od</sub>において、奇数番目の走査信号G(1)、G(3)、G(5)がこの順にアクティブとなることで、すなわち奇数番目の走査信号線L<sub>g</sub>が昇順に選択されることで、第1の飛び越し走査が行われ、図17(a)に示す画素マトリクスにおいて“+”を付した部分の画素形成部P<sub>x</sub>に書き込むべき画素値に相当する電圧が、正極性の映像信号D(1)～D(6)として映像信号線L<sub>s</sub>に印加される。なお、図17(a)に示す画素マトリクスにおいて、空白部分(“+”と“-”のいずれも付されていない部分)の画素形成部P<sub>x</sub>には、当該奇数フィールドT<sub>od</sub>以前に印加された画素電圧が画素値として保持されている(この点は、図17(b)～(d)においても同様)。20

#### 【0078】

図17(b)は、第nフレームの後半期間である偶数フィールドに映像信号D(1)～D(6)によって書き換えられる画素値に相当する画素電圧の極性を示している。本駆動方法では、このフレームの偶数フィールドT<sub>ev</sub>において、偶数番目の走査信号G(2)、G(4)、G(6)がこの順にアクティブとなることで、すなわち偶数番目の走査信号線L<sub>g</sub>が昇順に選択されることで、第2の飛び越し走査が行われ、図17(b)に示す画素マトリクスにおいて“-”を付した部分の画素形成部P<sub>x</sub>に書き込むべき画素値に相当する電圧が、負極性の映像信号D(1)～D(6)として映像信号線L<sub>s</sub>に印加される。30

#### 【0079】

図17(c)は、第n+1フレームF(n+1)の前半期間である奇数フィールドT<sub>od</sub>で映像信号D(1)～D(6)によって書き換えられる画素値に相当する画素電圧の極性を示している。本駆動方法では、このフレームの奇数フィールドT<sub>od</sub>において、奇数番目の走査信号G(1)、G(3)、G(5)がこの順にアクティブとなることで第1の飛び越し走査が行われ、図17(c)に示す画素マトリクスにおいて“-”を付した部分の画素形成部P<sub>x</sub>に書き込むべき画素値に相当する電圧が、負極性の映像信号D(1)～D(6)として映像信号線L<sub>s</sub>に印加される。40

#### 【0080】

図17(d)は、第n+1フレームの後半期間である偶数フィールドに映像信号D(1)～D(6)によって書き換えられる画素値に相当する画素電圧の極性を示している。本駆動方法では、このフレームの偶数フィールドT<sub>ev</sub>において、偶数番目の走査信号G(2)、G(4)、G(6)がこの順にアクティブとなることで第2の飛び越し走査が行われ、図17(d)に示す画素マトリクスにおいて“+”を付した部分の画素形成部P<sub>x</sub>に書き込むべき画素値に相当する電圧が、正極性の映像信号D(1)～D(6)として映像信50

号線 L s に印加される。

#### 【 0 0 8 1 】

上記のような駆動方法によれば、画素マトリクスの極性パターンは、第 n フレーム F ( n ) の終了時点では、図 17 ( e ) に示すパターンとなり、第 n + 1 フレーム F ( n + 1 ) の終了時点では、図 17 ( f ) に示すパターンとなる。このようにして上記駆動方法により、第 1 の実施形態と同様のライン反転駆動を行いつつ、いわゆるドット反転駆動を擬似的に実現することができる。

#### 【 0 0 8 2 】

##### < 4 . 2 効果 >

上記のように本実施形態によれば、第 1 の実施形態と同様のライン反転駆動による消費電力の大幅な低減という効果に加えて、図 17 ( e ) ( f ) に示すように擬似的にドット反転駆動が実現されるので、フリッカを軽減することができる。また、本実施形態では、第 1 の実施形態と同様、共通電圧 V c o m も図 5 ( g ) に示すように交流化されているので、通常のドット反転駆動を行った場合に比べ、映像信号電圧 V d ( D ( 1 ) , D ( 2 ) , D ( 3 ) , ... ) の振幅がほぼ半分となる。ところで、消費電力は一般に電圧振幅の 2 乗に比例する。したがって、本実施形態における映像信号線 L s の駆動のための消費電力は、図 18 に示すように共通電圧 V c o m が固定される通常のドット反転駆動を行った場合に比べ、略 1 / 4 となる。すなわち、通常のドット反転駆動を採用した従来の液晶表示装置と比較すると、本実施形態によれば、各フレーム内で画素マトリクスにおいて同一極性の電圧を印加すべき行を連続的に走査することにより大幅に消費電力が削減されることに加えて、共通電圧 V c o m の交流化により更に消費電力が低減されることになる。

#### 【 0 0 8 3 】

##### < 4 . 3 変形例 >

上記第 4 の実施形態では、基本的には第 1 の実施形態と同様の走査信号 G ( k ) および映像信号 D ( j ) ( 図 4 ) が使用されているが、これに代えて、第 2 の実施形態と同様の走査信号 G ( k ) および映像信号 D ( j ) ( 図 8 ) を使用してもよい。このようにすれば、方向反転走査が行われるので、上記第 4 の実施形態の効果に加えて、第 2 の実施形態と同様の効果 ( シャドー低減効果 ) も得られる。さらに、これに代えて、第 3 の実施形態と同様の走査信号 G ( k ) および映像信号 D ( j ) ( 図 13 ) を使用してもよく、この場合には、上記第 4 の実施形態の効果に加えて、走査停止期間の挿入により第 3 の実施形態と同様の効果 ( シャドー低減効果およびフリッカ低減効果 ) も得られる。

#### 【 0 0 8 4 】

##### 【 発明の効果 】

第 1 の発明によれば、第 1 の飛び越し走査における映像信号線への印加電圧の極性と、第 2 の飛び越し走査における映像信号線への印加電圧の極性とは異なっているが、各飛び越し走査内における映像信号線への印加電圧は同一極性であるので、従来に比べて反転周波数を大幅に低減しつつライン反転駆動を行うことができる。したがって、このようなライン反転駆動により ( フレーム反転駆動に比べ ) 良好的な表示品位を確保しつつ、消費電力を大幅に削減することができる。

#### 【 0 0 8 5 】

第 2 の発明によれば、第 1 の飛び越し走査と第 2 の飛び越し走査とで走査方向が互いに逆となることで、画素形成部に保持される画素値 ( 画素電圧 ) に対する映像信号線の電圧変化の影響が実質的に相殺され、その結果、本来の表示内容とは関係しない画面内の輝度差の発生が低減される。すなわち、シャドーの発生が抑制される。

#### 【 0 0 8 6 】

第 3 の発明によれば、第 2 の飛び越し走査の後に所定期間だけ複数の走査信号線が非選択状態となることで、走査停止期間が挿入される。このような走査停止期間の挿入により、フリッカの発生しうる期間の占める割合が小さくなるので、フリッカの発生が低減される。また、このような走査停止期間の挿入により、表示内容とは関係しない輝度差の生じうる期間の占める割合も小さくなるので、シャドーの発生も低減される。

10

20

30

40

50

## 【0087】

第4の発明によれば、同時選択画素電極が画素形成部のマトリクスにおいて上下に隣接する2行に分散的に配置されているので、ライン反転駆動を行いつつ擬似的にドット反転駆動を実現することができる。このため、通常のドット反転駆動に比べて消費電力を大幅に削減しつつ、フリッカの発生を低減することができる。

## 【0088】

第5の発明によれば、第1の発明と同様の効果を奏する。

第6の発明によれば、第2の発明と同様の効果を奏する。

第7の発明によれば、第3の発明と同様の効果を奏する。

## 【図面の簡単な説明】

10

【図1】本発明の第1の実施形態に係る液晶表示装置の構成を示すブロック図である。

【図2】第1の実施形態における液晶パネルの構成を示す模式図(a)および等価回路図(b)である。

【図3】第1の実施形態に係る液晶表示装置の駆動方法を説明するための概念図である。

【図4】第1の実施形態に係る液晶表示装置の駆動方法を説明するためのタイミングチャートである。

【図5】第1の実施形態による消費電力の低減を説明するためのタイミングチャートである。

【図6】ライン反転駆動方式を採用した従来の液晶表示装置における消費電力を説明するためのタイミングチャートである。

20

【図7】本発明の第2の実施形態に係る液晶表示装置の駆動方法を説明するための概念図である。

【図8】第2の実施形態に係る液晶表示装置の駆動方法を説明するためのタイミングチャートである。

【図9】液晶パネルにおける画素形成部の構成を示す等価回路図である。

【図10】第2の実施形態によるシャドーの低減を説明するための電圧波形図である。

【図11】第2の実施形態によるシャドーの低減を説明するための図である。

【図12】第2の実施形態によるシャドーの低減を説明するための表示例を示す図である。

【図13】本発明の第3の実施形態に係る液晶表示装置の駆動方法を説明するためのタイミングチャートである。

30

【図14】第3の実施形態によるフリッカの低減を説明するための電圧波形図である。

【図15】第3の実施形態によるシャドーの低減を説明するための電圧波形図である。

【図16】本発明の第4の実施形態における液晶パネルの構成を説明するための模式図(a)および等価回路図(b)である。

【図17】第4の実施形態における液晶表示装置の動作および極性パターンを説明するための概念図である。

【図18】通常のドット反転駆動における共通電圧および映像信号電圧を示す電圧波形図である。

40

## 【符号の説明】

|       |                    |

|-------|--------------------|

| 1 0   | ... TFT (薄膜トランジスタ) |

| 2 0 0 | ... 表示制御回路         |

| 3 0 0 | ... 映像信号線駆動回路      |

| 4 0 0 | ... 走査信号線駆動回路      |

| 5 0 0 | ... 共通電極駆動回路       |

| 6 0 0 | ... 液晶パネル          |

| L s   | ... 映像信号線(列電極)     |

| L g   | ... 走査信号線(行電極)     |

| P x   | ... 画素形成部(画素)      |

| C p   | ... 画素容量           |

50

|         |                                |

|---------|--------------------------------|

| E p     | …画素電極                          |

| E c     | …共通電極（対向電極）                    |

| C K     | …クロック信号                        |

| H S Y   | …水平同期信号                        |

| V S Y   | …垂直同期信号                        |

| D a     | …デジタル画像信号                      |

| G ( k ) | …走査信号 ( $k = 1, 2, 3, \dots$ ) |

| D ( j ) | …映像信号 ( $j = 1, 2, 3, \dots$ ) |

| V d     | …映像信号電圧                        |

| V c o m | …共通電圧                          |

| F ( n ) | …第 n フレーム                      |

| T o d   | …奇数フィールド ( 第 1 の飛び越し走査の期間 )    |

| T e v   | …偶数フィールド ( 第 2 の飛び越し走査の期間 )    |

| T h     | …水平走査期間                        |

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図12】

【図13】

【図10】

【図11】

| 画面上の位置 | A     |       | B  |      |

|--------|-------|-------|----|------|

|        | 奇数ライン | 偶数ライン | 条件 | ミ'アム |

| G(1)   | +     | +     | A  |      |

| G(2)   | -     | -     |    |      |

| G(3)   | +     | +     | +  |      |

| G(4)   | -     | -     |    |      |

| G(5)   | +     | +     | +  |      |

| G(6)   | -     | -     | B  |      |

| 画面上の位置 | A     |       | B    |      |

|--------|-------|-------|------|------|

|        | 奇数ライン | 偶数ライン | 条件   | ミ'アム |

| (c)    | A     | B     | A    | B    |

|        | ミ'アム  | ワ'スト  | ミ'アム | ベ'スト |

【図14】

【図15】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

G 0 9 G 3/20 6 2 2 N

G 0 9 G 3/20 6 4 2 A

F ターム(参考) 2H093 NA32 NA33 NA34 NA45 NC16 NC34 ND10 ND39

5C006 AC27 AC29 AF42 AF44 BB16 BC03 BC12 FA22 FA23 FA47

5C080 AA10 BB05 DD05 DD06 DD26 FF11 JJ01 JJ02 JJ03 JJ04

KK47

|                |                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | <无法获取翻译>                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2004287087A5</a>                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2007-02-08 |

| 申请号            | JP2003078981                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2003-03-20 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 大和朝日<br>中野武俊<br>柳俊洋                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 大和 朝日<br>中野 武俊<br>柳 俊洋                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| CPC分类号         | G09G3/3614 G09G2300/0809 G09G2310/0224 G09G2320/0247 G09G2330/021 E05Y2800/428 E06B3 /301 E06B3/4609 E06B7/14 E06B7/2307                                                                                                                                                                                                                                                                                       |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.611.A G09G3/20.611.E G09G3/20.621.B G09G3/20.622.N G09G3/20.642.A                                                                                                                                                                                                                                                                                                              |         |            |

| F-TERM分类号      | 2H093/NA32 2H093/NA33 2H093/NA34 2H093/NA45 2H093/NC16 2H093/NC34 2H093/ND10 2H093 /ND39 5C006/AC27 5C006/AC29 5C006/AF42 5C006/AF44 5C006/BB16 5C006/BC03 5C006/BC12 5C006/FA22 5C006/FA23 5C006/FA47 5C080/AA10 5C080/BB05 5C080/DD05 5C080/DD06 5C080 /DD26 5C080/FF11 5C080/JJ01 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/KK47 2H193/ZA04 2H193 /ZC02 2H193/ZC04 2H193/ZC13 2H193/ZC15 2H193/ZC20 2H193/ZC26 |         |            |

| 代理人(译)         | 岛田彰                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 其他公开文献         | JP2004287087A<br>JP3904524B2                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

**摘要(译)**

解决的问题：提供一种液晶显示装置，该液晶显示装置通过减少闪烁和阴影同时满足对移动电话等的低功耗的强烈需求而具有改善的显示质量。在第n帧的前半周期中，与包括大量像素形成部分的像素矩阵中的奇数行相对应的扫描信号G(1)，G(3)和G(5)被依次激活。因此，执行第一隔行扫描，并且将与要写入像素矩阵的奇数行的每个像素形成部分中的像素值相对应的电压施加到每个视频信号线作为正视频信号。在第n帧的后半周期中，通过依次激活与像素矩阵的偶数行相对应的扫描信号G(2)，G(4)和G(6)来执行第二次隔行扫描，将与要写入矩阵的偶数行中的每个像素形成部分中的像素值相对应的电压作为负视频信号施加到每个视频信号线。通过以上实现了线路反转驱动。

[选择图]图3