(19)日本国特許庁( J P )

## 12) 公開特許公報 ( A ) (11)特許出願公開番号

特開2003 - 302955

(P2003 - 302955A)

(43)公開日 平成15年10月24日(2003.10.24)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I           | テマコード(参考) |

|--------------------------|------|---------------|-----------|

| G 0 9 G 3/36             |      | G 0 9 G 3/36  | 2 H 0 9 3 |

| G 0 2 F 1/133            | 575  | G 0 2 F 1/133 | 5 C 0 0 6 |

| G 0 9 G 3/20             | 611  | G 0 9 G 3/20  | 5 C 0 8 0 |

|                          | 612  |               | 612 F     |

|                          | 621  |               | 621 C     |

審査請求 未請求 請求項の数 220L(全 17数) 最終頁に続く

(21)出願番号 特願2003 - 98589(P2003 - 98589)

(22)出願日 平成15年4月1日(2003.4.1)

(31)優先権主張番号 2002 - 017793

(32)優先日 平成14年4月1日(2002.4.1)

(33)優先権主張国 韓国(KR)

(31)優先権主張番号 2002 - 026218

(32)優先日 平成14年5月13日(2002.5.13)

(33)優先権主張国 韓国(KR)

(71)出願人 390019839

三星電子株式会社

大韓民国京畿道水原市八達区梅灘洞416

(72)発明者 李昇祐

大韓民国ソウル市衿川区禿山1洞293 - 10番

地禿山現代アパート102棟1008号

(74)代理人 100094145

弁理士 小野由己男(外1名)

最終頁に続く

(54)【発明の名称】フレームレート制御方法及びそのための液晶表示装置

## (57)【要約】

【課題】 表現可能な全階調の中で上位階調のガンマ歪曲が除去できる第1のフレームレート制御方法、RGBデータの入力ビット数で表現できる色数を全て表示できる第2のフレームレート制御方法、第1及び第2のフレームレート制御方法が適用できる液晶表示装置を提供する。

【解決手段】 フレームレート制御方法は、液晶表示装置外部のグラフィックソースからnビットのRGBデータを受信する第1段階と、RGBデータが示す階調値を利用してeビットにRGBデータを拡張する第2段階と、拡張されたRGBデータの下位dビットを抽出して、連続する2d個のフレーム内に拡張されたRGBデータの下位dビットによって拡張RGBデータの下位dビットを除いた(e-d)ビットが示す階調とその直上位階調の発生頻度が調整されるようにフレームデータを変換させる第3段階とを含む。

| 従来FRC |            |            |      | Hi-FRC I |     |            |            |      |

|-------|------------|------------|------|----------|-----|------------|------------|------|

| 入力    | 上位<br>6ビット | 下位<br>2ビット | 評価   | 入力       | 変換  | 上位<br>6ビット | 下位<br>2ビット | 評価   |

| 255   | 111111     | 11         | 同一輝度 | 255      | 252 | 111111     | 00         | ▲    |

| 254   | 111111     | 10         |      | 254      | 251 | 111110     | 11         | ▲    |

| 253   | 111111     | 01         |      | 253      | 250 | 111110     | 10         | ▲    |

| 252   | 111111     | 00         |      | 252      | 249 | 111110     | 01         | ▲    |

| 251   | 111110     | 11         | ▲    | 251      | 248 | 111110     | 00         | ▲    |

| 250   | 111110     | 10         | ▲    | 250      | 247 | 111101     | 11         | ▲    |

| 6     | *          | *          | *    | 6        | 3   | 000000     | 11         | ▲    |

| 5     | 000001     | 01         | ▲    | 5        | 2   | 000000     | 10         | ▲    |

| 4     | 000001     | 00         | ▲    | 4        | 1   | 000000     | 01         | ▲    |

| 3     | 000000     | 11         | ▲    | 3        | 0   | 000000     | 00         |      |

| 2     | 000000     | 10         | ▲    | 2        | 0   | 000000     | 00         | 同一輝度 |

| 1     | 000000     | 01         | ▲    | 1        | 0   | 000000     | 00         |      |

| 0     | 000000     | 00         |      | 0        | 0   | 000000     | 00         |      |

## 【特許請求の範囲】

【請求項1】外部のグラフィックソースからそれぞれ2進nビットの階調値で構成されるRGBデータを受信する第1段階と、

前記入力されたRGBデータ中の階調値から(2<sup>d</sup>-1)を減算し、最下位から所定数の階調データが同一輝度に設定されるようにデータを変換する第2段階と、

連続する2<sup>d</sup>個のフレーム内に、前記RGBデータの各階調値の下位dビットによって前記RGBデータの各階調値の上位(n-d)ビットが示す階調データとその直上位階調データの発生頻度が調整されるようにフレームデータを変換する第3段階と、

を含むことを特徴とする液晶表示装置のフレームレート制御方法。

【請求項2】前記nは8であり、dは2であることを特徴とする、請求項1に記載の液晶表示装置のフレームレート制御方法。

【請求項3】前記最下位から4つの階調データを'0'に設定することを特徴とする、請求項2に記載の液晶表示装置のフレームレート制御方法。

【請求項4】液晶表示装置外部のグラフィックソースからそれぞれ2進nビットの階調値で構成されるRGBデータを受信する第1段階と、

前記RGBデータ中の各階調値を利用してeビット(e+n+1)にRGBデータを拡張する第2段階と、

前記拡張されたRGBデータの下位dビットを抽出し、連続する2<sup>d</sup>個のフレーム内に、前記拡張されたRGBデータの下位dビットによって前記拡張RGBデータの下位dビットを除いた上位(e-d)ビットが示す階調データとその直上位階調データの発生頻度が調整される

ようにフレームデータを変換させる第3段階を含み、

前記第1乃至第3段階は所定の数の単位画素ブロックに對して行われ、各単位画素ブロックでは前記RGBデータ

$$\left(\frac{63G}{255} \times 8\right) \text{四捨五入}$$

(Gは入力される8ビットRGBデータが示す10進数で表現された階調値であり、"()四捨五入"は括弧内の数を小数点以下四捨五入するという意味である。)

によって遂行されることを特徴とする、請求項4に記載の液晶表示装置のフレームレート制御方法。

【請求項10】前記nが8ビットである時、

$$if G=255, G_{Hi-FRC}=504,$$

$$else G_{Hi-FRC}=\left(\frac{63G}{256} \times 8\right) \text{四捨五入}=\left(\frac{63G}{32}\right) \text{四捨五入}$$

(Gは入力される8ビットRGBデータが示す10進数で表現された階調値であり、"()四捨五入"は括弧内の数を小数点以下四捨五入するという意味であり、前記式でG<sub>Hi-FRC</sub>は9ビットに変換されたデータである。)

によって遂行されることを特徴とする、請求項4に記載の液晶表示装置のフレームレート制御方法。

\*タの下位dビットを除いた上位(e-d)ビットが示す階調データと、その直上位階調データの発生頻度が空間的に調整されるように配置されることを特徴とする液晶表示装置のフレームレート制御方法。

【請求項5】前記nは8ビット、dは3ビット、eは9ビットであることを特徴とする、請求項4に記載の液晶表示装置のフレームレート制御方法。

【請求項6】前記nは10ビット、12ビットまたはそれ以上のビットであることを特徴とする、請求項4に記載の液晶表示装置のフレームレート制御方法。

【請求項7】前記所定の数の画素ブロックは4×2画素ブロックであることを特徴とする、請求項4に記載の液晶表示装置のフレームレート制御方法。

【請求項8】前記nが8ビット、dが3ビット、eが9ビットである時、

前記dビットの最下位ビットが'0'であれば、8個のフレーム内に前記dビットの残りのビットによって前記RGBデータの上位(e-d)ビットが示す階調データとその直上位階調データの発生頻度が調整されるようにフレームデータを変換させ、

前記dビットの最下位ビットが'1'であれば、最初4フレーム間には前記dビットの残りのビットによって前記RGBデータの上位(e-d)ビットが示す階調上位とその直上位階調上位の発生頻度が調整されるようにフレームデータを変換させ、残り4フレーム内には前記dビットの残りのビットに'1'を足した値によって前記RGBデータの(e-d)ビットが示す階調とその直上位階調の発生頻度が調整されるようにフレームデータを変換させることを特徴とする、請求項4に記載の液晶表示装置のフレームレート制御方法。

【請求項9】前記nが8ビットである時、前記第2段階は、

【数1】

前記第2段階は

40 【数2】

前記第2段階は

40 【数2】

【請求項11】前記nが8ビットである時、

50 前記第2段階は、

3

【数3】 *if*  $G \leq 6$ ,  $G_{Hi-FRC} = G$ ,

4

$$\text{else } G_{Hi-FRC} = \left( \frac{64 \times (G+1)}{256} - 1 \right) \times 8 = 2G - 6$$

(Gは入力される8ビットRGBデータが示す10進数で表現された階調値であり、"()四捨五入"は括弧内の数を小数点以下四捨五入するという意味であり、前記数式で $G_{Hi-FRC}$ は9ビットに変換されたデータである。)

によって遂行されることを特徴とする、請求項4に記載10\*前記第2段階は、液晶表示装置のフレームレート制御方法。

【数4】

【請求項12】前記nが8ビットである時。

*if*  $G = 255$ ,  $G_{Hi-FRC} = 504$ ,

\*

$$\text{else } G_{Hi-FRC} = \left( \left( \frac{63 \times (G+1)}{256} - \frac{1}{8} \right) \times 8 \right) \text{四捨五入} \left( \frac{63 \times (G+1)}{32} - 1 \right) \text{四捨五入}$$

(Gは入力される8ビットRGBデータが示す10進数で表現された階調値であり、"()四捨五入"は括弧内の数を小数点以下四捨五入するという意味であり、前記数式で $G_{Hi-FRC}$ は9ビットに変換されたデータである。)

によって遂行されることを特徴とする、請求項4に記載の液晶表示装置のフレームレート制御方法。

前記第2段階は、

【数5】

【請求項13】前記nが8ビットである時。

*if*  $G \leq 8$ ,  $G_{Hi-FRC} = G$ ,

*if*  $9 < G < 255$ ,  $G_{Hi-FRC} = 2G - 8$ ,

*if*  $G = 255$ ,  $G_{Hi-FRC} = 504$

(Gは入力される8ビットRGBデータが示す10進数で表現した階調値であり、 $G_{Hi-FRC}$ は9ビットに変換されたデータである。)

にしたがって行われることを特徴とする、請求項4に記載の液晶表示装置のフレームレート制御方法。

ータの発生頻度が調整されるようにフレームデータを変換し、前記変換されたRGBデータを前記ソース駆動部に出力させるタイミング制御部を含む液晶表示装置。

【請求項14】複数のゲートラインとデータラインが交差する領域に形成された画素を有する液晶パネルと、前記液晶パネルのゲートラインを順次に走査するための信号を印加するゲート駆動部と、RGBデータによって前記液晶パネルの各画素に印加するための階調電圧を選択して出力させるソース駆動部と、

【請求項15】前記タイミング制御部のフレームデータ変換は所定の数の単位画素ブロックに対して遂行され、各単位画素ブロックでは前記RGBデータの下位dビットを除いた上位(e-d)ビットが示す階調データとその直上位階調データの発生頻度が空間的に調整されるように配置されることを特徴とする、請求項14に記載の液晶表示装置。

前記ゲート駆動部の走査のためのゲート電圧を生成して40出力し、前記ソース駆動部に必要な階調電圧を生成して出力させる電圧発生部と、グラフィックソースからそれぞれ2進nビットの階調値で構成されるRGBデータを受けて、前記RGBデータが示す階調値を利用してeビット(e-n+1)に拡張されたRGBデータを算出し、前記拡張されたRGBデータの下位dビットを抽出して、連続する2^d個のフレーム内に、前記抽出されたRGBデータの下位dビットによって前記RGBデータの下位dビットを除いた上位(e-d)ビットが示す階調データとその直上位階調データ

【請求項16】前記nは8ビット、dは3ビット、eは9ビットであることを特徴とする、請求項14に記載の液晶表示装置。

【請求項17】前記nは10ビット、12ビットまたはそれ以上のビットであることを特徴とする、請求項14に記載の液晶表示装置。

【請求項18】前記所定の数の画素ブロックは4×2画素ブロックであることを特徴とする、請求項14に記載の液晶表示装置。

【請求項19】液晶表示装置外部のグラフィックソース

からそれぞれ2進nビットの階調値で構成されるRGBデータの入力を受ける第1段階と、前記RGBデータが示す階調値を利用してeビット( $e = n + 1$ )にRGBデータを拡張する第2段階と、

前記拡張されたRGBデータの下位dビットを抽出し、連続する $2^d$ 個のフレーム内に、前記拡張されたRGBデータの下位dビットによって前記拡張RGBデータの下位dビットを除いた上位( $e - d$ )ビットが示す階調データとその直上位階調データの発生頻度が調整されるようにフレームデータを変換する第3段階と、

前記第3段階で得られた $2^d$ 個のフレームデータの中で最初半分のフレームをノーマルフレーム、残り半分のフレームをプラスフレームと定義し、前記プラスフレームは各フレームの画素配置を垂直方向に変えて得られ、前記ノーマルフレームとプラスフレームは毎フレームごとに互いに交互に表示されるようにフレームデータを再配置する第4段階とを含み、

前記第1乃至第4段階は所定数の単位画素ブロックに対して行われ、各単位画素ブロック内では前記RGBデータの下位dビットを除いた上位( $e - d$ )ビットが示す階調データとその直上位階調データの発生頻度が空間的に調整されるように配置されることを特徴とする液晶表示装置のフレームレート制御方法。

【請求項20】前記所定数の画素ブロックは $4 \times 2$ 画素ブロックであることを特徴とする、請求項19に記載の液晶表示装置のフレームレート制御方法。

【請求項21】一つのフレームを構成しようとする表示画面において、所定の画素ブロック単位にノーマルフレーム又はプラスフレームの中の一つが表示されると同時に、前記画素ブロック単位に隣接した周辺の画素ブロックではノーマルフレーム又はプラスフレームの中の他の一つが表示されるように画素パターンを空間的に再配置する第5段階をさらに含むことを特徴とする、請求項19に記載の液晶表示装置のフレームレート制御方法。

【請求項22】前記所定の画素ブロック単位は $4 \times 4$ 画素ブロックであることを特徴とする、請求項21に記載の液晶表示装置のフレームレート制御方法。

#### 【発明の詳細な説明】

##### 【0001】

【発明の属する技術分野】本発明はフレームレート制御(FRC:frame rate control)のための液晶表示装置及びその駆動方法に関し、さらに詳しくはグラフィックソースから入力されるRGBデータ(RGB各色の画素データを言う)の構成ビット数より少いビット処理能力しか持たないRGBデータ伝送系を使用する場合にも最高階調値近辺での色再現性低下を防止できる液晶表示装置及びその駆動方法に関する。

##### 【0002】

【従来の技術】最近、パソコン(personal computer)やテレビなどの軽量化及び薄形化によって表示装置分野

にも軽量化及び薄形化が要求されており、このような要求を充足させるために陰極線管(CRT:cathode-ray tube)の代りに液晶表示装置(LCD:liquid crystal display)のようなフラットパネル表示装置(flat panel display)が開発されて様々な分野において実用化されている。液晶表示装置では二枚の基板の間に注入されている異方性誘電率を有する液晶物質に電界が印加され、この電界の強さを調節することによって基板を透過する光の量が制御されて所望の画像(image)に対する表示が行われる。

【0003】このような液晶表示装置には外部のグラフィックソース(graphic source)からレッド(red:赤)、グリーン(green:緑)、ブルー(blue:青)の各nビットRGBデータが入力される。前記RGBデータは液晶表示装置のRGBデータ伝送系、特にタイミング制御部でデータフォーマットを変換した後、駆動IC(integrated circuit)でRGBデータに相当するアナログ階調電圧(gray voltage)が選択され、前記選択された階調電圧を液晶パネルに伝送し、各画素に印加することによって表示動作が行われる。

【0004】一般に、前記グラフィックソースからタイミング制御部に入力されるRGBデータの構成ビット数と前記駆動ICで処理可能なビット数とは同一である。現在、市場に発表されている液晶表示装置ではn=8ビットの製品が普通である。しかし、8ビットのRGBデータを処理できる駆動ICが高価であるため、それより少いビット処理能力しか持っていない駆動ICを用いて、下位ビットを切り捨てるような液晶表示装置を設計することができれば、製品の原価を低くできる可能性がある。この場合、切り捨てた下位ビットが表現していた微細な階調は、複数フレームの当該画素データを1群として、群の中の少なくとも1個のフレームの画素階調を、少なくとも駆動ICが取り扱える最小階調段階だけ変化させて、フレーム群の平均画素階調を入力画素データの平均階調に近づける技術である。

【0005】このような技術的必要に応じて提案された方法がフレームレート制御(FRC:frame rate control)である。前記フレームレート制御はタイミング制御部に適用されることの多い技術であり、入力されたnビット構成のRGBデータの中から駆動ICで処理可能なビット数である( $n - d$ )ビットだけを取り出して表示できるようにフレームデータを再構成する技術である。ここで、dは切り捨てビット数を示す整数であり、入力RGBデータの最下位所定ビット数を示す。前記フレームレート制御方法によると、連続する $2^d$ 個(‘2のd乗個’と記すこともある)のフレーム内に、各フレームでRGBデータの下位dビットを利用してRGBデータの( $n - d$ )ビットが示す階調値‘A’(以下、“A”とする)とその直上位階調である‘A+1’のフレーム別発生頻度が調整されるようにフレームデータを変換する。

これとともに、フレーム内の所定の画素単位、例えば、 $4 \times 2$  の画素単位でも前記二つの階調‘A’と‘A+1’のフレーム別発生頻度が空間的に調整されるように配置することによって、時間的及び空間的に画面表示を平均した時、nビットのRGBデータによって表示が行われたように認識されることがある。つまり、階調‘A’と‘A+1’の間で $2^d$ 個の微差階調を追加的に表示することができ、これは( $n-d$ )ビットのRGBデータにdビットを追加してnビットRGBデータによって表示することと同一な動作といえる。

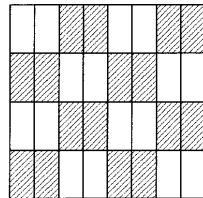

【0006】図1にはnが8であり、dが2の場合のフレームレート制御を説明する図表が示されている。この場合、1群のフレーム数は、 $2^2 = 4$  (フレーム)である。図1には、近接した8画素のバランスを考慮しながら、同じ入力画面が4フレーム続いたと仮定した時の微差階調の表現例を示している。これは、4フレーム期間中の下位2ビットの状態によって、 $4 \times 2$  画素ブロックでの各画素の表示状態が示されている。前記画素ブロックのうち、斜線のある画素はRGBデータの上位6ビットが示す階調値を再現表示し、斜線のない画素は前記6ビットが示す階調値に‘1’を足した値、つまり、その直上位階調の値を再現表示している。 $4 \times 2$  画素ブロックの上方に記した‘o’は‘odd’の略語であって、奇数番目列(column)を示し、‘e’は‘even’の略語で偶数番目列を示す。

【0007】図1によれば、下位2ビットの4種類の状態は各々二つの階調値‘A’と‘A+1’の間の4種類の階調値を示し、‘00’は‘A’、‘01’は‘A+1/4’、‘10’は‘A+2/4’、‘11’は‘A+3/4’の階調値を各々示す。下位2ビットが‘11’である場合について例を挙げて説明する。まず、空間的な観点から見る時、下位2ビットが‘11’であれば、8個の画素を有する $4 \times 2$  画素ブロックでは階調値‘A+1’が常に6個の画素で発生するようデータが構成されている。また、時間的な観点から見る時、下位2ビットが‘11’であれば、例えば、‘o’列‘1’行の画素では階調値‘A+1’が4フレーム内に3回発生するようデータが構成されている。したがって、時間的及び空間的に平均すれば、 $4 \times 2$  画素ブロックでは下位2ビットが‘11’である場合に、階調‘A’に‘3/4’を足した階調が平均的に表示されたように認識することができる。

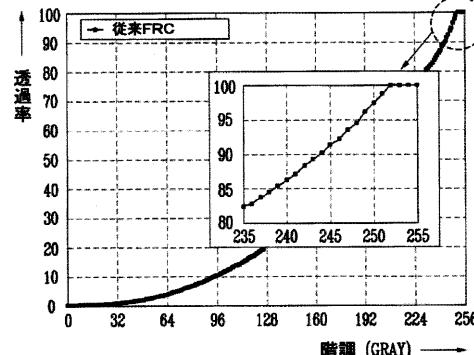

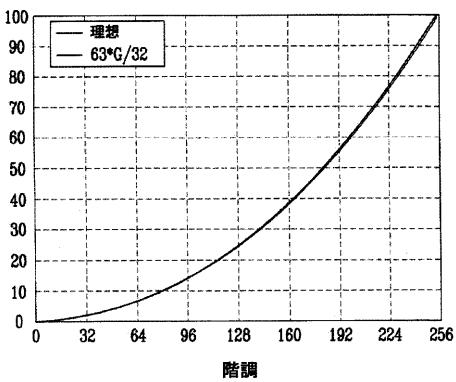

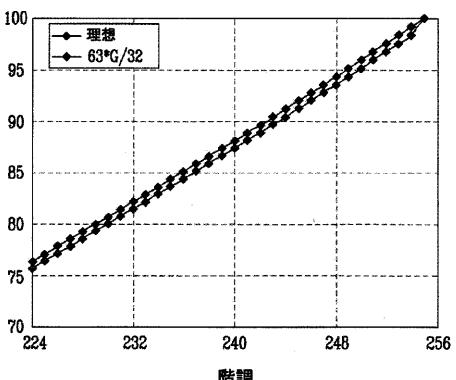

【0008】図2に、図1のフレームレート制御が適用される時の階調(gray)に対する透過率(transmittance)の関係を示す。階調に対する透過率の曲線を通常ガンマ曲線と呼ぶ。しかし、前記従来のフレームレート制御方法では、図2に拡大して示したように、上位4つの階調でガンマの歪曲が存在し、これによって表示可能な色の数が減少する問題点がある。より詳細に説明すれば、入力RGBデータが8ビットでありながら出力データ

タが6ビットに圧縮される場合、表示すべき全体階調数は $2^8 = 256$ 個である。しかし、上位6ビットを利用してフレームレート制御をするので上位4つの階調ではRGBデータの上位6ビットが‘111111 = 63’になる。つまり、最高階調値が $4 * 63 = 252$ で飽和し、どの画素も、どの時点も、前記の‘A+1’を実現できない。フレームレート制御では任意の階調‘A’とその上位階調‘A+1’の発生頻度を調節してRGBデータが拡張されているように表現されるが、上記の場合には‘111111’の上位階調を実現できない。従ってフレームレート制御を適用することができず、表示すべき全体階調数のうち、上位4つの階調(252、253、254、255)は、共通の透過率を生じるように予め設定せざるを得ない。この結果、最上位3階調が失われて図2のようになる。これが上位階調でガンマ歪曲を起こす原因である。また、各原色の色R、G、Bが253個の階調を表現するので、RGB合成によって表現できる全体色の数は $253 \times 253 \times 253 = 16,194,277$ であり、これは理想的に表現可能な色の数 $256 \times 256 \times 256 = 16,777,216$ より60万余個足りない。このような現象は最高階調値近辺での色再現性低下をもたらすので、好ましくないものである。

【0009】一方、フレームレート制御が適用される液晶表示装置では画質劣化という問題点がある。たとえば、表示画面の下側は黒であり、上側は赤、緑、青、白の各々の最大明るさが出るように階調レベルを垂直に配置した画面を構成する場合、4個の階調間隔で横線が表示される現象が発生する。このような画質劣化現象は、前記フレームレート制御と共に、1フレーム単位に液晶印加極性を反転させる反転駆動方法が同時に適用されたために起こる。

#### 【0010】

【発明が解決しようとする課題】本発明は以上のような技術的背景から行われたものであって、表現可能な全階調の中で上位階調のガンマ歪曲が除去できる第1のフレームレート制御方法を提供することに第1目的がある。本発明の第2目的は、RGBデータの所定数の下位ビットを拡張した後、これをを利用してフレームを再構成することによって、RGBデータの入力ビット数で表現できる色数を全て表示できる第2のフレームレート制御方法を提供することにある。

【0011】本発明の第3目的は、画素のパターンを時間的及び空間的に適切に配置することにより、画質劣化及びフリッカーを減少させることができる第3のフレームレート制御方法を提供することにある。本発明の第4目的は、前記第1及び第2のフレームレート制御方法が適用できる液晶表示装置を提供することにある。

#### 【0012】

【課題を解決するための手段】前記目的を達成するため

の本発明によるフレームレート制御方法は、グラフィックソースからそれぞれ2進nビットの階調値で構成されるRGBデータを受信する第1段階と、前記RGBデータa階調値から‘(2のd乗)-1’を減算し、最下位から所定数の階調データが同一輝度を表示するようにRGBデータを変換する第2段階と、上位(n-d)ビットが示す階調データとその直上位階調データの発生頻度が調整されるようにフレームデータを変換する第3段階とを含む。

【0013】前記目的を達成するための本発明によるフレームレート制御方法は、液晶表示装置外部のグラフィックソースからそれぞれ2進nビットの階調値で構成されるRGBデータを受信する第1段階と、前記RGBデータの各階調値を利用してeビットに拡張されたRGBデータを算出する第2段階と、前記拡張されたRGBデータの下位dビットを抽出して、連続する $2^d$ 個のフレーム期間中、前記抽出されたRGBデータの下位dビットによって前記RGBデータの下位dビットを除いた上位(e-d)ビットが示す階調データとその直上位階調データの発生頻度が調整されるようにフレームデータを変換させる第3段階とを含み、前記第1乃至第3段階は所定数の単位画素ブロックに対して遂行され、各単位画素ブロックでは前記拡張されたRGBデータの下位dビットを除いた上位(e-d)ビットが示す階調データとその直上位階調データの発生頻度が空間的に調整されるように配置されることを特徴とする。

【0014】前記本発明によるフレームレート制御方法では、液晶表示装置のタイミング制御部に入力されるnビットのRGBデータをeビットに拡張した後、これをを利用してフレームレート制御を行うことにより、フレームレート制御することによって発生する表現可能な色数の減少を防止することができる。前記説明された本発明の目的、技術的構成及びその効果は次の実施例に関する説明を通じてより明白になる。

### 【0015】

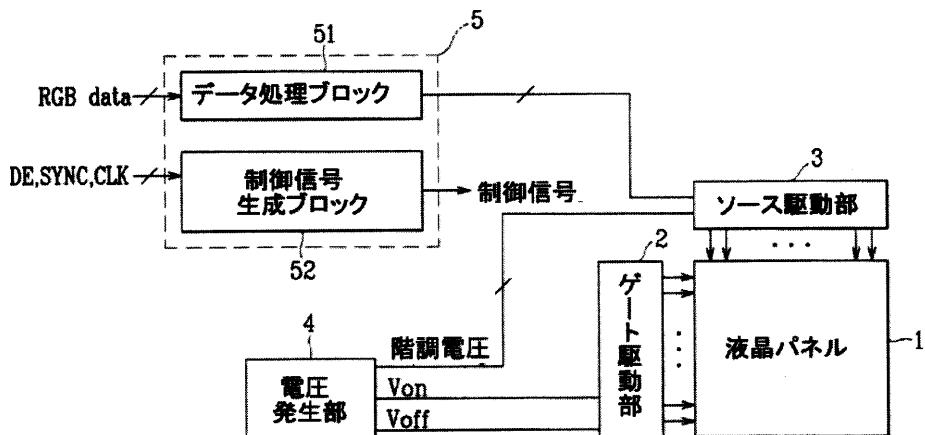

【発明の実施の形態】以下、添付した図面を参照して本発明の好ましい実施例を詳細に説明する。図3には本発明による液晶表示装置の概略的な構成が示されている。図3に示されているように、本発明による液晶表示装置は液晶パネル1、ゲート駆動部2、ソース駆動部3、電圧発生部4及びタイミング制御部5からなる。前記液晶パネル1は互いに交差する複数のゲートライン及びデータラインと、各ゲートラインとデータラインが交差する領域に形成された画素で構成され、ゲートラインが順次に走査(scanning)されるたびにアナログ階調電圧がデータラインを経て対応する画素に印加される。前記タイミング制御部5には外部のグラフィックソース(graphic source)からRGBデータ、フレームの時点を示すデータタイナーブル信号(DE)、同期信号(SYNC)、及びクロック信号(CLK)が入力される。前記RGBデータは

タイミング制御部5のデータ処理ブロック51によってフレームレート制御とRGBデータのタイミング再分配などのデータ処理が行われた後、ソース駆動部3に伝送される。また、前記タイミング制御部5の制御信号生成ブロック52は、前記データタイナーブル信号(DE)、同期信号(SYNC)及びクロック信号(CLK)を利用して表示動作を制御するための多様な制御信号を生成し各構成要素に伝送する。前記電圧発生部4はゲートラインを走査するためのゲートオン/オフ電圧を生成して前記ゲート駆動部2に出力すると同時に、画素印加電圧であるアナログ階調電圧を生成して前記ソース駆動部3に出力する。前記ソース駆動部3ではタイミング制御部5から伝送されたRGBデータによってそれに適したアナログ階調電圧を選択して前記液晶パネル1に印加する。

【0016】次に、前記のように構成される液晶表示装置のタイミング制御部に適用される第1及び第2のフレームレート制御方法について説明する。図4には第1のフレームレート制御方法を説明するための図表を示す。本発明による第1のフレームレート制御方法は、従来のフレームレート制御を適用する時、図2のガンマ曲線を下方にシフトさせて、所定数の最下位階調に対して同一な輝度を適用することによって最上位階調でのガンマ歪曲補正のための余地を作る。言い換えれば、任意のnビットRGBデータの下位dビット削除圧縮するフレームレート制御が行われる時、前記第1のフレームレート制御方法では、表現可能な $2^d$ 個の階調の中で最上位所定数の階調(高輝度部分)に対して同一の輝度を適用するのではなく、最下位所定数の階調(低輝度部分)に対して同一の輝度を適用する。つまり、上位階調では輝度が高くガンマ曲線の歪曲が容易に視認されるので、この領域のガンマ歪を正し、輝度が低くガンマ曲線の歪曲を認めにくい最下位階調に対しては同一輝度を適用する。これにより、全体としてのガンマ曲線歪曲が従来に比べて視覚的かつ相対的に低減できる。このような方法はsRGB支援モニターに特に有利である。

【0017】図4の図表は、8ビット入力RGBデータによる0乃至255の階調に対する輝度状況を示し、左半分は従来の方法、右は本発明の第1方法のデータである。備考欄の黒三角は輝度表示が正常であることを示す。右側、本発明のデータでは、各画素毎に入力データから‘3’を差し引いて負値を‘0’に変換する。つまり、最下位4つの階調を‘0’に変換し、残りの階調では全体的に正常な輝度となるように変換したデータが示されている。本発明の方法では同じ画面が4フレーム続くと仮定して、次に、連続する4つのフレームに‘A+1’階調を分配する方法を決定する。つまり、変換されたデータの下位2ビットを利用して上位6ビットが示す階調とその直上位階調(上位6ビットが示す階調に‘1’を加えた値、つまり、256階調のグレーでは‘4’を加えた値)の発生頻度を調整するようにRGB

データを変換させる。前記発生頻度の調整は従来のフレームレート制御方法と同様に行なわれる。ここで、下位4つの階調に対しては同一の輝度が現れるようするために、下位4つの各階調に対しては‘000000’でだけ4つのフレームを構成する。

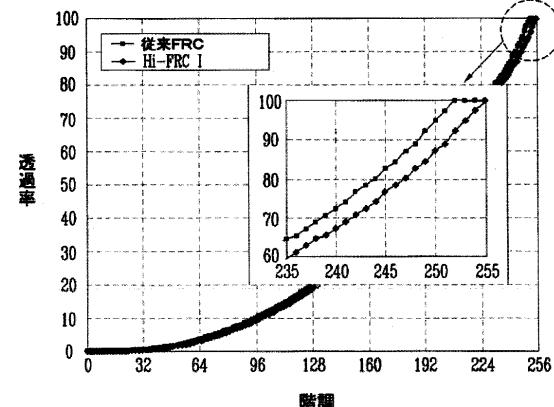

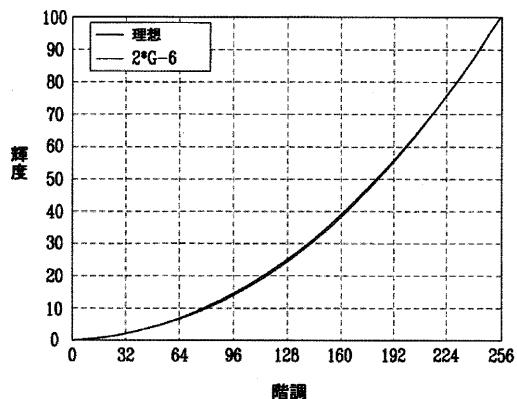

【0018】図5には前記第1のフレームレート制御方法が適用される時のグレー(gray)に対する透過率の関係がグラフに示されている。前記図5に示されているように、上位階調でのガンマ歪曲が除去されており、下位階調でのガンマ歪曲は許容できる程度になる。しかし、このような第1のフレームレート制御方法においても、下位階調でのガンマ歪曲は存在し、これは表現可能な色数の減少につながる。本発明による第2のフレームレート制御方法は表現可能な色数の増加をその目的とする。

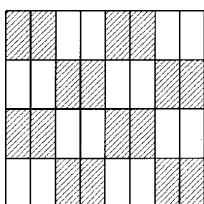

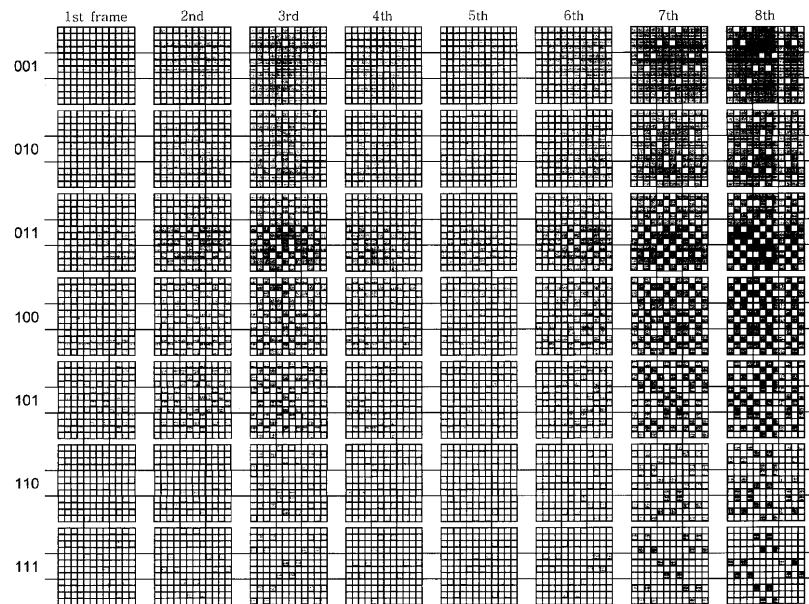

【0019】図6には本発明による第2のフレームレート制御方法を説明するための図表が示されている。本発明による第2のフレームレート制御方法はnビットのRGBデータをeビットデータに拡張して、下位dビットによってRGBデータを変換させる方法である。例えば、n=8ビットのRGBデータが液晶表示装置のタイミング制御部に入力される場合、e=9ビットにデータを拡張して、下位3ビットによってRGBフレームデータを変換させる。ここで、8ビットRGBデータで構成される1フレームは6ビットRGBデータによって2<sup>d</sup>フレーム内の平均階調データで表現される。空間的には4×2画素ブロックを使用する。現在の技術状況では前記nが8ビットである場合が一般的であるが、10ビット、12ビットまたはそれ以上に拡張でき、前記dは3以上の整数、前記eは(n+1)以上の整数である。

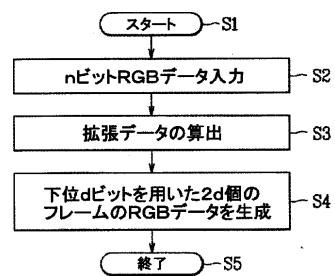

【0020】まず、図7のフローチャートを参照して本発明による第2のフレームレート制御方法の全体的な処理流れを説明する。動作が始まると(S1)、外部のグラフィックソースから液晶表示装置のタイミング制御部にnビットのRGBデータが入力される(S2)。次に、前記RGBデータが示す階調値を利用した所定の数式によって拡張データが算出される(S3)。前記拡張データ算出のための数式については後記する。その後、前記拡張されたeビットの下位dビットデータを利用して上位(e-d)ビットデータを変換させて出力する(S4)。より具体的には、前記拡張されたRGBデータの下位dビットが抽出されて、連続する2<sup>d</sup>個のフレーム内に、前記抽出されたRGBデータの下位dビットによって前記RGBデータの下位dビットを除いた(e-d)ビットが示す階調とその直上位階調の発生頻度が調整されるようにフレームデータが変換される。この時、前記過程が行われる各フレームの単位画素ブロックは4×2である。各単位画素ブロックでは前記拡張されたRGBデータの下位dビットを除いた(e-d)ビットが示す階調とその直上位階調の発生頻度が空間的に調整されるように配置される。

【0021】このような過程によってフレームデータの生成が終了し(S5)、前記S2乃至S4段階の過程は入力される全てのフレームのRGBデータに対して行われる。図6の図表はnが8ビット、dが3ビット、eが9ビットである時の第2のフレームレート制御方法を説明する。前記図6に示すように、dビット、つまり、拡張されたRGBデータの下位3ビットによって連続する2<sup>d</sup>個のフレーム内にフレームレート制御が行われる。図6で斜線で表示した画素はRGBデータの(e-d)ビット、つまり、上位6ビットが示す階調を表示し、斜線で表示されていない画素はRGBデータの(e-d)ビットが示す階調の直上位階調を表示する。つまり、(e-d)ビットが示す階調を‘A’とする時、斜線で表示されていない画素が表示する階調は‘A+1’である。

【0022】図6で、下位3ビットは階調‘A’以上‘A+1’未満の2<sup>d</sup>個の階調、つまり、2<sup>3</sup>個の階調を示し、より具体的に、‘000’は‘A+0/8’、‘001’は‘A+1/8’、‘010’は‘A+2/8’、‘011’は‘A+3/8’、‘100’は‘A+4/8’、‘101’は‘A+5/8’、‘110’は‘A+6/8’、‘111’は‘A+7/8’を各々示す。前記下位3ビットの状態によって、6ビットで表現できる階調‘A’と‘A+1’の発生頻度を調整することによって、8フレーム間の表示を時間的に平均すれば前記のように‘A’と‘A+1’の間の8段階の階調が表現できるようにしたことに本発明の特徴がある。

【0023】より具体的に、下位3ビットの中で最下位ビットが‘0’である場合には、残り2ビットで従来のフレームレート制御と同様に8フレームを再構成する。下位3ビットの中で最下位ビットが‘1’である場合には、最初の4フレーム内には残り2ビットで従来のフレームレート制御と同様の4フレームを再構成し、その次の4フレーム内には残り2ビットに‘1’を足して従来のフレームレート制御と同様の4フレームを再構成する。例えば、下位3ビットの情報が‘101’であると仮定する。最初4フレームは既存のフレームレート制御と同様にフレームを再構成し、この時には‘10’の2ビット情報を利用する。その次の4フレーム間には‘101’の下位ビットが‘1’であるので‘10’に‘1’を足した値、つまり、‘11’を利用して従来のフレームレート制御と同様にフレームを再構成する。もし、下位3ビットの中で最下位ビットが‘0’であれば既存のフレームレート制御と同様にフレーム再構成が行われる。

【0024】次に、nが8であり、eが9である時、前記第2のフレームレート制御方法で拡張ビットを算出する過程について説明する。まず、次の数式1は8ビットのRGBデータを9ビットに拡張するためのものである。

【数6】

$$\left(\frac{63G}{255} \times 8\right) \text{ 四捨五入}$$

前記式1でGは入力される8ビットRGデータが示す10進数で表現された階調値であり、"( )四捨五入"は括弧内の数の小数点以下を四捨五入するという意味である。入力RGデータに対して前記式1を適用すれば、計算結果の整数部として9ビットで示される数が算出される。このように算出された9ビットデータは先に説明した第2のフレームレート制御方法に利用される。前記式1で、255で割り算する過程は、ハードウェア・ロジックで実現する場合に計算量を増加させる問題があるが、逆数をかける方法で実現したり、ロジック内部にルックアップテーブル(look-up table)を備えることによって簡単に解決できる。もし若干の誤差を許せば、分母=256、分子=64として(2G)で近似でき、現実の操作はレジスターで1ビットだけシフトするだけよいが、これでは高輝度部の飽和現象が残るから、(2G-6)で計算する方がよい。また、分母=256、分子=63つまり( $63G / 32$ )としてもよい。要は、9ビットのデータを使って、高輝度部に飽和現象や跳躍現象がなく、低輝度部の飽和現象が最小(または所定段階)になるような、カーブがなだらかで輝度反転が無く、計算時間の短い変換法を見出せばよいことである。

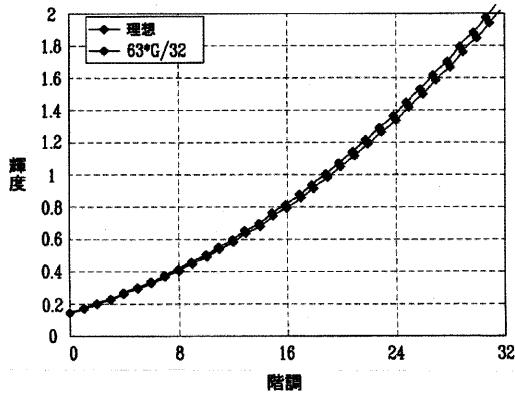

【0026】次に、8ビットのRGBデータを9ビットに拡張するための式2を説明する。

【0027】

**【数 7】** if  $G=255$ ,  $G_{Hi-FRC}=504$ ,

$$\text{else } G_{Hi-FRC} = \left(\frac{63G}{256} \times 8\right) \text{四捨五入} = \left(\frac{63G}{32}\right) \text{四捨五入}$$

if  $G \leq 6$ ,  $G_{Hi-FRC} = G$ ,

$$\text{if } 7 < G < 255, \quad G_{Hi-FRC} = \left( \frac{64 \times (G+1)}{256} - 1 \right) \times 8 = 2G - 6,$$

if  $G=255$ ,  $G_{Hi-FRC}=504$

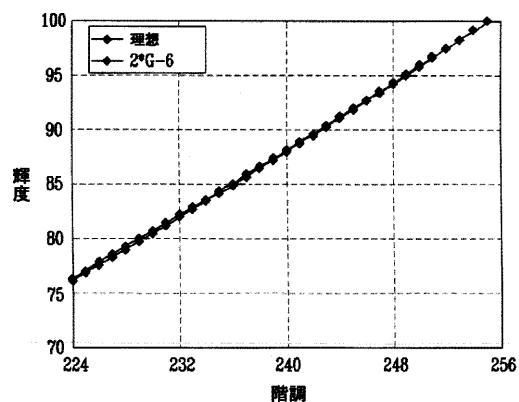

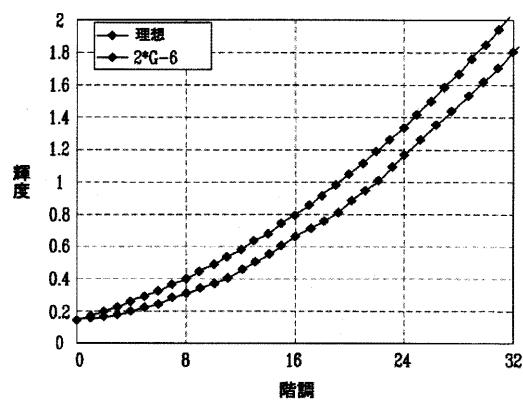

前記式3は割算演算が含まれていない簡単な式である。図9aには全体階調と輝度との関係に対して式3を適用した場合(2G-6)と理想的な場合(Ideal)が示されており、図9bには上位階調に対して前記二つの場合が示されており、図9cには下位階調に対して前記二つの場合が示されている。前記図9cに示されているように、下位階調で式3を適用した場合と理想的な

$$\text{else } G_{Hi-FRC} = \left( \left( \frac{63 \times (G+1)}{256} - \frac{1}{8} \right) \times 8 \right) \text{ 四捨五入} = \left( \frac{63 \times (G+1)}{32} - 1 \right) \text{ 四捨五入}$$

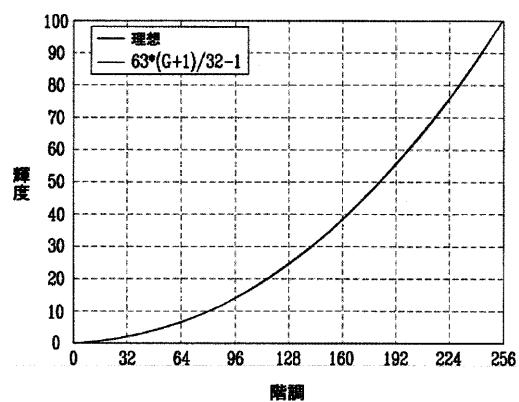

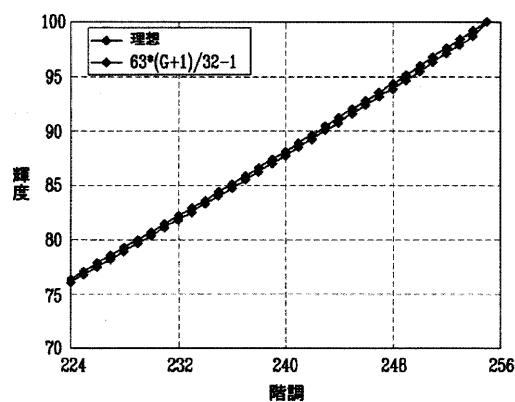

図10aには全体階調と輝度との関係に対して数式4を50適用した場合(63(G+1)/32-1)と理想的な場合

合(Ideal)が示されており、図10bには上位階調に対して前記二つの場合が示されており、図10cには下位階調に対して前記二つの場合が示されている。前記数式4を適用した図10a乃至図10cから分かるように、数式4を適用すれば、全体的に誤差が少なく変換できるという長所がある。

【0032】次に、8ビットのRGBデータを9ビットに拡張するための数式5を説明する。

【0033】

$$\begin{aligned} \text{【数式5】} & \text{if } G \leq 8, \quad G_{Hi-FRC} = G, \\ & \text{if } 9 < G < 255, \quad G_{Hi-FRC} = 2G - 8, \\ & \text{if } G = 255, \quad G_{Hi-FRC} = 504 \end{aligned}$$

前記数式5は前記数式1、2及び3と類似しており、タイミング制御部に入力される8ビットのRGBデータを9ビットに拡張するためのものである。次に、図11乃至16を参照して本発明による第3のフレームレート制御方法を説明する。本発明による第3のフレームレート制御方法は、画質劣化を減少させることをその目的とする。

【0034】図11乃至14には本発明による第3のフレームレート制御方法を説明するための図表が示されている。本発明による第3のフレームレート制御方法は前述した第2のフレームレート制御方法により再構成された画素パターンに対して追加的に画素パターンを配置することに関する。基本的に、前記第3のフレームレート制御方法は前記図6に示した画素パターンを得るために過程をすべて含み、前記第2のフレームレート制御方法を遂行した結果に対する本発明の第3のフレームレート制御方法が適用される。また、図6に示された画素パターンは空間的な観点では $4 \times 2$ 画素ブロック、時間的な観点では8フレーム期間の画素パターンであって、第2のフレームレート制御方法によって既に画素パターンが再構成されたものであるので、前記第3フレームレート制御方法にもこののような前提条件が適用されていると仮定する。ここで、本発明が適用される基本画素単位を $4 \times 2$ 画素ブロックにしたことと、8フレーム画素パターンにしたことは本発明の原理から逸脱しない限度内で変更することができ、このことは当該技術分野で通常の知識を有する者であれば容易に行うことができる。前記第3フレームレート制御方法では、時間的な観点又は空間的な観点での第2フレームレート制御方法によって得られた画素パターンを、また、再配置することにより画質劣化を減少させることができる。

【0035】図11に示した画素パターンでは“ノーマルフレーム”と“プラスフレーム”という概念が導入される。この概念は本発明で提案された用語であって、ノーマルフレームとは、本発明による第2のフレームレート制御方法が適用された画素パターンを有するフレーム

を表示するための画素データであり、プラスフレームとは、前記第2のフレームレート制御方法が適用された画素パターンにおいて上下方向に各画素の配置を変えたフレームを表示するための画素データのことである。つまり、図6の画素パターンに対して最初4個のフレームはノーマルフレームに構成し、その後の4個のフレームはプラスフレームに構成することによって、図11の画素パターンが得られる。単純に図6の画素パターンを前記4個のノーマルフレームと4個のプラスフレームが連続的に表示されることだけでも、4個の階調レベル単位に横線が表示される画質劣化現象はある程度減少できる。

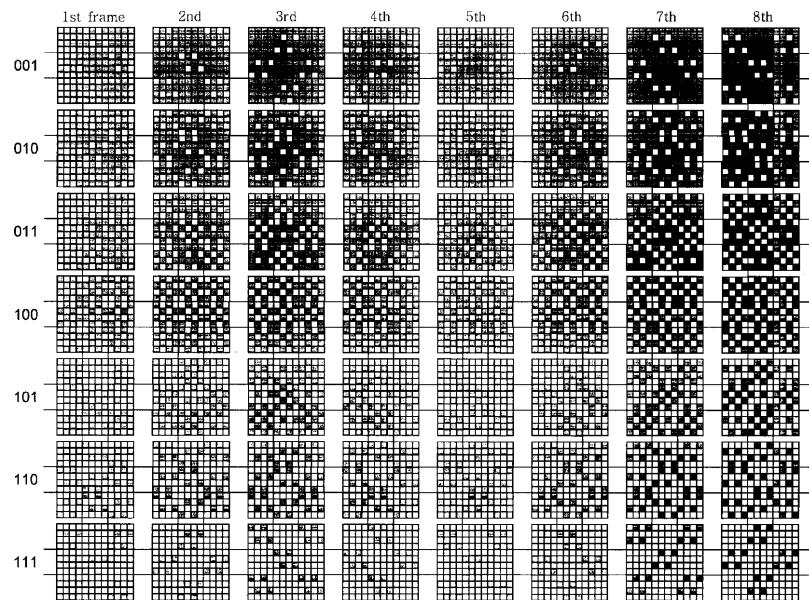

【0036】しかし、本発明者は、画質を改善するための方法をさらに研究した結果、前記ノーマルフレームとプラスフレームが1フレーム単位につづつ交互に表示されるように8フレームを構成することが画質劣化を改善するのに一層効果的であるということを知った。図12にはノーマルフレームとプラスフレームが交互に表示されるように構成された画素パターンが示されている。しかし、前記図12に示された画素パターンによってもフリッカーを完全に解決することはできない。したがって、空間的にもノーマルフレームとプラスフレームを混用する方法を考えるようになった。つまり、1フレームを構成する表示画面で所定の画素ブロック単位にノーマルフレーム又はプラスフレームのうちのいずれかが表示されるようにし、その単位画素ブロックに隣接する画素ブロックではノーマルフレーム又はプラスフレームのうちの他のものを表示するようにする。例えば、任意の一つの単位画素ブロックでは図12の画素パターンの中でノーマルフレームが先に始まるようにし、それに隣接した他の単位画素ブロックではプラスフレームが先に始まるようすれば、前記ノーマルフレームとプラスフレームの空間的な配置を行える。このようにする場合、1フレーム内でも空間的に前記ノーマルフレームとプラスフレームが混用されて表示されるので、フリッカー問題を完全に解決できる。

【0037】図13a及び13bには空間的な観点でノーマルフレームとプラスフレームを配置する一つの例が示されている。前記図13a及び13bの例において、一つのブロックは $4 \times 2$ 画素ブロックであり、斜線のブロックはプラスフレーム、斜線部分のないブロックはノーマルフレームである。図13aにはn番目フレームのための画素パターンが示されており、 $4 \times 4$ 画素ブロック単位にノーマルフレーム又はプラスフレームのうちの一つが該当画素ブロックでは同一に表示され、各単位画素ブロックとそれに隣接する単位画素ブロックにはノーマルフレーム又はプラスフレームが各々表示される。一方、図13bには(n+1)番目フレームのための画素パターンが示されており、前記図13aに示された画素パターンとは反対である。つまり、n番目フレームでノ

ーマルフレームが表示されていた単位画素ブロックは( $n+1$ )番目フレームでプラスフレームを表示し、 $n$ 番目フレームでプラスフレームが表示されていた単位画素ブロックは( $n+1$ )番目フレームでノーマルフレームを表示する。そして、図13bに示したように、( $n+1$ )番目フレームでは $n$ 番目フレームでとは反対にノーマルフレームとプラスフレームが配置されるように画素パターンが構成される。このように画素パターンを構成することにより、フリッカーと画質劣化の問題点を完全に解決することができる。

【0038】図14の画素パターンはノーマルフレームとプラスフレームが交互に表示されるように画素パターンが構成されるという点では図12の画素パターンと類似しているが、プラスフレームとノーマルフレームの発生順序が図12の画素パターンとは反対である。つまり、時間的に1番目フレームではプラスフレームが表示され、その次のフレームではノーマルフレームが表示される。図15及び16には前記第3のフレームレート制御方法によって時間的及び空間的な観点で再配置された画素パターンが示されている。より具体的に、図15は特に赤及び緑色に対して時間的及び空間的な観点から再配置した画素パターンを示しており、図16は青色に対して時間的及び空間的な観点から再配置した画素パターンを示している。前記図15及び図16では $4 \times 4$ 画素ブロックが単位画素ブロックとなり、この単位画素ブロックはプラスフレームとノーマルフレームを交互に空間的に表示し、同様に時間的にもプラスフレームとノーマルフレームを交互に表示することを詳細に示している。既述のように、垂直方向に階調レベルを配置する時、横線が表示されることは反転駆動と深く関連する。緑色では下に階調が暗くなる方向である時、横線がよく見え、赤及び青色では上に階調が暗くなる方向である時よく見えることは反転の極性に影響があることが分かる反証である。したがって、将来どのような反転駆動方法が適用されても、それによる影響を少なくするためにもう一つの方法を追加することができる。図15に示したものは赤／緑色に対する反転駆動方法であるとすれば、青色に対するものをこれと反対に $4 \times 4$ 画素ブロック内で上下を変えた形態で画素パターンを有するようにする。RG Bが同一なFRC画素パターンを有するものより、異なるFRC画素パターンを有する方が画質が向上する。

### 【0039】

【発明の効果】以上説明したように本発明によるフレームレート制御方法は、下位階調に対して共通の輝度を適用することによって、視覚的によく識別できる上位階調でのガンマ歪曲を除去することができ、高輝度部の色相歪みを軽減するので、好ましい色再現が可能になる。また、本発明による第2のフレームレート制御方法は液晶表示装置のタイミング制御部に入力されるRGBデータの所定の数の下位ビットを拡張した後、これを利用して

18

フレームを再構成することによって、RGBデータの入力ビット数で表現できる色の数を増加させることができる。

【0040】本発明による第3のフレームレート制御方法は前記第2のフレームレート制御方法によって再構成された画素パターンに対してノーマルフレームとプラスフレームを定義し、これらノーマルフレームとプラスフレームを時間的及び空間的に再配置することにより画質の劣化を減少させることができる。

### 10 【図面の簡単な説明】

【図1】 従来の液晶表示装置でのフレームレート制御を説明するための図面である。

【図2】 従来のフレームレート制御が適用される時のグレーに対する透過率の関係を示した図面である。

【図3】 本発明による液晶表示装置の概略的な構成を示した図面である。

【図4】 本発明の液晶表示装置のための第1のフレームレート制御方法を説明するための図面である。

【図5】 図4に示す第1のフレームレート制御方法が適用される時のグレーに対する透過率の関係を示した図面である。

【図6】 本発明の液晶表示装置のための第2のフレームレート制御方法を説明するための図面である。

【図7】 図6に示す第2のフレームレート制御方法を実行するフローチャートである。

【図8a】 前記図7のフローチャートにおいて拡張ビット算出のための式2が適用される場合のガンマ特性を示したグラフである。

【図8b】 前記図7のフローチャートにおいて拡張ビット算出のための式2が適用される場合のガンマ特性を示したグラフである。

【図8c】 前記図7のフローチャートにおいて拡張ビット算出のための式2が適用される場合のガンマ特性を示したグラフである。

【図9a】 前記図7のフローチャートにおいて拡張ビット算出のための式3が適用される場合のガンマ特性を示したグラフである。

【図9b】 前記図7のフローチャートにおいて拡張ビット算出のための式3が適用される場合のガンマ特性を示したグラフである。

【図9c】 前記図7のフローチャートにおいて拡張ビット算出のための式3が適用される場合のガンマ特性を示したグラフである。

【図10a】 前記図7のフローチャートにおいて拡張ビット算出のための式4が適用される場合のガンマ特性を示したグラフである。

【図10b】 前記図7のフローチャートにおいて拡張ビット算出のための式4が適用される場合のガンマ特性を示したグラフである。

【図10c】 前記図7のフローチャートにおいて拡張

ビット算出のための式4が適用される場合のガンマ特性を示したグラフである。

【図11】 本発明による第3のフレームレート制御方法においてノーマルフレームとプラスフレームの概念を説明するための図面である。

【図12】 本発明による第3のフレームレート制御方法においてノーマルフレームとプラスフレームが1フレーム毎に交互に表示されるように構成した画素パターンを示した図面である。

【図13a】 連続する二つのフレームで空間的に $4 \times 10$ 4画素ブロック単位にノーマルフレームとプラスフレームを混用して構成した画素パターンを示した図面である。

【図13b】 連続する二つのフレームで空間的に $4 \times 4$ 4画素ブロック単位にノーマルフレームとプラスフレームを混用して構成した画素パターンを示した図面である。

【図14】 本発明による第3のフレームレート制御方法において、プラスフレームとノーマルフレームが1フレーム毎に交互に表示されるように構成した画素パターンを示した図面である。

\* レーム毎に交互に表示されるように構成した画素パターンを示した図面である。

【図15】 本発明の第3のフレームレート制御方法によって赤及び緑色に対して時間的及び空間的にノーマルフレームとプラスフレームを配置した画素パターンを示した図面である。

【図16】 本発明の第3のフレームレート制御方法によって青色に対して時間的及び空間的にノーマルフレームとプラスフレームを配置した画素パターンを示した図面である。

#### 【符号の説明】

- 1 : 液晶パネル

- 2 : ゲート駆動部

- 3 : ソース駆動部

- 4 : 電圧発生部

- 5 : タイミング制御部

- 5 1 : データ処理ブロック

- 5 2 : 制御信号生成ブロック

【図1】

| 下位<br>2ビット | フレーム番号                  |                         |                         |                         |

|------------|-------------------------|-------------------------|-------------------------|-------------------------|

|            | 1                       | 2                       | 3                       | 4                       |

| 00         | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

| 01         | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

| 10         | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

| 11         | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

|            | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 | o e<br>1<br>2<br>3<br>4 |

■ 上位6ビットの階調データ

□ 上位6ビットの直上階調データ

【図4】

| 従来FRC |            |            | Hi-FRC I |     |     |            |            |    |

|-------|------------|------------|----------|-----|-----|------------|------------|----|

| 入力    | 上位<br>6ビット | 下位<br>2ビット | 評価       | 入力  | 変換  | 上位<br>6ビット | 下位<br>2ビット | 評価 |

| 255   | 111111     | 11         | 同一輝度     | 255 | 252 | 111111     | 00         | ▲  |

| 254   | 111111     | 10         |          | 254 | 251 | 111110     | 11         | ▲  |

| 253   | 111111     | 01         |          | 253 | 250 | 111110     | 10         | ▲  |

| 252   | 111111     | 00         |          | 252 | 249 | 111110     | 01         | ▲  |

| 251   | 111110     | 11         | ▲        | 251 | 248 | 111110     | 00         | ▲  |

| 250   | 111110     | 10         | ▲        | 250 | 247 | 111101     | 11         | ▲  |

| *     | *          | *          | *        | *   | *   | *          | *          |    |

| 6     | 000001     | 10         | ▲        | 6   | 3   | 000000     | 11         | ▲  |

| 5     | 000001     | 01         | ▲        | 5   | 2   | 000000     | 10         | ▲  |

| 4     | 000001     | 00         | ▲        | 4   | 1   | 000000     | 01         | ▲  |

| 3     | 000000     | 11         | ▲        | 3   | 0   | 000000     | 00         |    |

| 2     | 000000     | 10         | ▲        | 2   | 0   | 000000     | 00         |    |

| 1     | 000000     | 01         | ▲        | 1   | 0   | 000000     | 00         |    |

| 0     | 000000     | 00         |          | 0   | 0   | 000000     | 00         |    |

【図2】

【図7】

【図5】

【図3】

【図13a】

【図6】

| 下位3ビット | フレーム番号                 |                        |                        |                        |                        |                        |                        |                        |

|--------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

|        | 1                      | 2                      | 3                      | 4                      | 5                      | 6                      | 7                      | 8                      |

| 000    | oe<br>1<br>2<br>3<br>4 |

| 010    | oe<br>1<br>2<br>3<br>4 |

| 100    | oe<br>1<br>2<br>3<br>4 |

| 110    | oe<br>1<br>2<br>3<br>4 |

| 001    | oe<br>1<br>2<br>3<br>4 |

| 011    | oe<br>1<br>2<br>3<br>4 |

| 101    | oe<br>1<br>2<br>3<br>4 |

| 111    | oe<br>1<br>2<br>3<br>4 |

【図8a】

【図8b】

【図13b】

【図8c】

【図9a】

【図9b】

【図9c】

【図10a】

【図10b】

【図10c】

【図11】

【図12】

【図14】

【図15】

【図16】

## 【手続補正書】

【提出日】平成15年4月3日(2003.4.3)

## 【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】0025

【補正方法】変更

【補正内容】

【0025】

【数6】

$$\left(\frac{63G}{255} \times 8\right) \text{四捨五入} \quad \cdots (1)$$

前記式(1)でGは入力される8ビットR G Bデータが示す10進数で表現された階調値であり、"( )四捨五入"は括弧内の数の小数点以下を四捨五入するという意味である。入力R G Bデータに対して前記式1を適用すれば、計算結果の整数部として9ビットで示される

数が算出される。このように算出された9ビットデータは先に説明した第2のフレームレート制御方法に利用される。前記数式1で、255で割り算する過程は、ハードウェア・ロジックで実現する場合に計算量を増加させる問題があるが、逆数をかける方法で実現したり、ロジック内部にルックアップテーブル(look-up table)を備えることによって簡単に解決できる。もし若干の誤差を許せば、分母=256、分子=64として(2G)で近似でき、現実の操作はレジスターで1ビットだけシフトするだけでよいが、これでは高輝度部の飽和現象が残るから、(2G-6)で計算する方がよい。また、分母=256、分子=63つまり( $63G/32$ )としてもよい。要は、9\*

$$\text{if } G=255, \quad G_{Hi-FRC}=504,$$

$$\text{else } G_{Hi-FRC}=\left(\frac{63G}{256}\times 8\right) \text{四捨五入}=\left(\frac{63G}{32}\right) \text{四捨五入}$$

前記数式(2)で $G_{Hi-FRC}$ は9ビットに変換されたデータである。前記数式(1)には割算演算が含まれているので、実現するのには計算量が多い。数式をロジックで実現する時、8の倍数で割ることが便利なので、数式(2)を適用することができる。前記数式(2)によれば、入力されるRGBデータの階調値が255であれば、 $G_{Hi-FRC}$ は、 $504 = 63 \times 8$ となるため、上位6ビットが"63(十進数)"であり、下位3ビットが'000'の値となる。この階調値255が、6ビットドライバーICで出力できる最大の入力値となる。その他の階調では入力RGBデータに63だけをかけて、その結果を5ビットだけ下位ビットだけ方向にシフトすれば容易に得られる。図8a乃至図8cのグラフには前記数式(2)を適用した場合の階調に対する輝度曲線と理想的な輝度曲線が比較して示されている。

#### 【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0028

【補正方法】変更

$$\text{if } G \leq 6, \quad G_{Hi-FRC}=G,$$

$$\text{if } 7 < G < 255, \quad G_{Hi-FRC}=\left(\frac{64 \times (G+1)}{256}-1\right) \times 8 = 2G-6,$$

$$\text{if } G=255, \quad G_{Hi-FRC}=504$$

前記数式(3)は割算演算が含まれていない簡単な数式である。図9aには全体階調と輝度との関係に対して数式(3)を適用した場合(2G-6)と理想的な場合(Ideal)が示されており、図9bには上位階調に対して前記二つの場合が示されており、図9cには下位階調に対して前記二つの場合が示されている。前記図9cに示されているように、下位階調で数式(3)を適用した

\*ビットのデータを使って、高輝度部に飽和現象や跳躍現象がなく、低輝度部の飽和現象が最小(または所定段階)になるような、カーブがなだらかで輝度反転が無く、計算時間の短い変換法を見出せばよいことである。

#### 【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0027

【補正方法】変更

【補正内容】

【0027】

【数7】

} ... (2)

\*【補正内容】

【0028】図8aには全体階調と輝度との関係に対して数式(2)を適用した場合( $63^*G/32$ )と理想的な場合(Ideal)が示されており、図8bには上位階調に対して前記二つの場合が示されており、図8cには下位階調に対して前記二つの場合が示されている。前記図8a乃至図8cのグラフを見てみると、上位階調で理想的な場合と多少の差があるが、その他の階調ではほとんど理想的な場合に近接することが分かる。次に、8ビットのRGBデータを9ビットに拡張するための数式3を説明する。

#### 【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0029

【補正方法】変更

【補正内容】

【0029】

【数8】

} ... (3)

場合と理想的な場合の差が大きいように見られるが、これはグラフのスケーリング(scaling)差によるもので、実際には大きな誤差がない。

#### 【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0031

【補正方法】変更

## 【補正内容】

## 【0031】

*if G=255, G<sub>Hi-FRC</sub>=504,*

*else G<sub>Hi-FRC</sub>=((63×(G+1)/256-1/8)×8) 四捨五入=(63×(G+1)/32-1) 四捨五入*

## \* 【数9】

\*

... (4)

図10aには全体階調と輝度との関係に対して数式(4)を適用した場合(63(G+1)/32-1)と理想的な場合(Ideal)が示されており、図10bには上位階調に対して前記二つの場合が示されており、図10cには下位階調に対して前記二つの場合が示されている。前記数式(4)を適用した図10a乃至図10cから分かるように、数式(4)を適用すれば、全体的に誤差が少なく変換できるという長所がある。

*if G≤8, G<sub>Hi-FRC</sub>=G,*

*if 9<G<255, G<sub>Hi-FRC</sub>=2G-8,*

*if G=255, G<sub>Hi-FRC</sub>=504*

## \* 【手続補正6】

【補正対象書類名】明細書

【補正対象項目名】0033

【補正方法】変更

【補正内容】

【0033】

【数10】

*if G≤8, G<sub>Hi-FRC</sub>=G,*

*if 9<G<255, G<sub>Hi-FRC</sub>=2G-8,*

*if G=255, G<sub>Hi-FRC</sub>=504*

... (5)

前記数式(5)は前記数式(1)、(2)及び(3)と類似しており、タイミング制御部に入力される8ビットのRGBデータを9ビットに拡張するためのものである。次に、図11乃至16を参照して本発明による第3\*

\*のフレームレート制御方法を説明する。本発明による第3のフレームレート制御方法は、画質劣化を減少させることをその目的とする。

## フロントページの続き

(51) Int.CI.<sup>7</sup>

G 0 9 G 3/20

識別記号

6 4 1

F I

G 0 9 G 3/20

テ-マコド<sup>®</sup> (参考)

6 4 1 C

6 4 1 E

6 4 1 F

6 4 1 G

6 4 1 K

6 4 1 P

6 4 2 J

6 5 0 M

6 4 2

6 5 0

F ターム(参考) 2H093 NA16 NA31 NA43 NA55 NA61

NC09 NC11 ND10

5C006 AA12 AA14 AA16 AA17 AA22

AC26 AF04 AF44 AF45 AF46

AF51 AF52 AF71 AF83 BB16

BC12 BC16 BF14 BF24 BF28

BF43 FA16 FA23 FA25 FA29

FA56 GA02

5C080 AA10 BB05 CC03 DD05 DD06

EE17 EE29 EE30 FF11 GG17

JJ01 JJ02 JJ05

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 帧率控制方法及其液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| 公开(公告)号        | <a href="#">JP2003302955A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2003-10-24 |

| 申请号            | JP2003098589                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2003-04-01 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| [标]发明人         | 李昇祐                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 李昇祐                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| CPC分类号         | G09G3/3611 G09G3/2022 G09G3/2055 G09G2320/0271 G09G2340/0428                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| FI分类号          | G09G3/36 G02F1/133.575 G09G3/20.611.E G09G3/20.612.F G09G3/20.621.C G09G3/20.641.C<br>G09G3/20.641.E G09G3/20.641.F G09G3/20.641.G G09G3/20.641.K G09G3/20.641.P G09G3/20.642.<br>J G09G3/20.650.M                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA31 2H093/NA43 2H093/NA55 2H093/NA61 2H093/NC09 2H093/NC11 2H093/<br>/ND10 5C006/AA12 5C006/AA14 5C006/AA16 5C006/AA17 5C006/AA22 5C006/AC26 5C006/AF04<br>5C006/AF44 5C006/AF45 5C006/AF46 5C006/AF51 5C006/AF52 5C006/AF71 5C006/AF83 5C006<br>/BB16 5C006/BC12 5C006/BC16 5C006/BF14 5C006/BF24 5C006/BF28 5C006/BF43 5C006/FA16<br>5C006/FA23 5C006/FA25 5C006/FA29 5C006/FA56 5C006/GA02 5C080/AA10 5C080/BB05 5C080<br>/CC03 5C080/DD05 5C080/DD06 5C080/EE17 5C080/EE29 5C080/EE30 5C080/FF11 5C080/GG17<br>5C080/JJ01 5C080/JJ02 5C080/JJ05 2H193/ZD25 |         |            |

| 优先权            | 1020020017793 2002-04-01 KR<br>1020020026218 2002-05-13 KR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 其他公开文献         | <a href="#">JP4772276B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

### 摘要(译)

解决的问题：提供一种第一帧速率控制方法，该方法能够去除所有可表示灰度之间的较高灰度的伽马失真，以及第二帧速率控制，其能够显示可以由RGB数据的输入位数表示的所有颜色。提供一种液晶显示装置，该液晶显示装置可以应用该方法以及第一和第二帧频控制方法。帧速率控制方法包括以下步骤：从液晶显示设备外部的图形源接收n位RGB数据，并通过使用RGB数据指示的灰度值将RGB数据扩展为e位。提取第二步和扩展RGB数据的低d位，并在连续2d帧(ed)中用扩展RGB数据的低d位除去扩展RGB数据的低d位。它包括由比特指示的灰度级和转换帧数据的第三步骤，从而调整紧接在该灰度级之上的灰度级的出现频率。

| 第1-帧速率 |                              |      |                              | 第2-帧速率 |                              |        |                              |

|--------|------------------------------|------|------------------------------|--------|------------------------------|--------|------------------------------|

| 入力     | 上位n<br>位数データ<br>下位d<br>位数データ | 出力   | 上位e<br>位数データ<br>下位d<br>位数データ | 入力     | 上位n<br>位数データ<br>下位d<br>位数データ | 出力     | 上位e<br>位数データ<br>下位d<br>位数データ |

| 000000 | 0000                         | 0000 | 0000                         | 000000 | 000000                       | 000000 | 000000                       |

| 000001 | 0000                         | 0000 | 0000                         | 000001 | 000001                       | 000001 | 000001                       |

| 000010 | 0000                         | 0000 | 0000                         | 000010 | 000010                       | 000010 | 000010                       |

| 000011 | 0000                         | 0000 | 0000                         | 000011 | 000011                       | 000011 | 000011                       |

| 000100 | 0000                         | 0000 | 0000                         | 000100 | 000100                       | 000100 | 000100                       |

| 000101 | 0000                         | 0000 | 0000                         | 000101 | 000101                       | 000101 | 000101                       |

| 000110 | 0000                         | 0000 | 0000                         | 000110 | 000110                       | 000110 | 000110                       |

| 000111 | 0000                         | 0000 | 0000                         | 000111 | 000111                       | 000111 | 000111                       |

| 001000 | 0000                         | 0000 | 0000                         | 001000 | 001000                       | 001000 | 001000                       |

| 001001 | 0000                         | 0000 | 0000                         | 001001 | 001001                       | 001001 | 001001                       |

| 001010 | 0000                         | 0000 | 0000                         | 001010 | 001010                       | 001010 | 001010                       |

| 001011 | 0000                         | 0000 | 0000                         | 001011 | 001011                       | 001011 | 001011                       |

| 001100 | 0000                         | 0000 | 0000                         | 001100 | 001100                       | 001100 | 001100                       |

| 001101 | 0000                         | 0000 | 0000                         | 001101 | 001101                       | 001101 | 001101                       |

| 001110 | 0000                         | 0000 | 0000                         | 001110 | 001110                       | 001110 | 001110                       |

| 001111 | 0000                         | 0000 | 0000                         | 001111 | 001111                       | 001111 | 001111                       |

| 010000 | 0000                         | 0000 | 0000                         | 010000 | 010000                       | 010000 | 010000                       |

| 010001 | 0000                         | 0000 | 0000                         | 010001 | 010001                       | 010001 | 010001                       |

| 010010 | 0000                         | 0000 | 0000                         | 010010 | 010010                       | 010010 | 010010                       |

| 010011 | 0000                         | 0000 | 0000                         | 010011 | 010011                       | 010011 | 010011                       |

| 010100 | 0000                         | 0000 | 0000                         | 010100 | 010100                       | 010100 | 010100                       |

| 010101 | 0000                         | 0000 | 0000                         | 010101 | 010101                       | 010101 | 010101                       |

| 010110 | 0000                         | 0000 | 0000                         | 010110 | 010110                       | 010110 | 010110                       |

| 010111 | 0000                         | 0000 | 0000                         | 010111 | 010111                       | 010111 | 010111                       |

| 011000 | 0000                         | 0000 | 0000                         | 011000 | 011000                       | 011000 | 011000                       |

| 011001 | 0000                         | 0000 | 0000                         | 011001 | 011001                       | 011001 | 011001                       |

| 011010 | 0000                         | 0000 | 0000                         | 011010 | 011010                       | 011010 | 011010                       |

| 011011 | 0000                         | 0000 | 0000                         | 011011 | 011011                       | 011011 | 011011                       |

| 011100 | 0000                         | 0000 | 0000                         | 011100 | 011100                       | 011100 | 011100                       |

| 011101 | 0000                         | 0000 | 0000                         | 011101 | 011101                       | 011101 | 011101                       |

| 011110 | 0000                         | 0000 | 0000                         | 011110 | 011110                       | 011110 | 011110                       |

| 011111 | 0000                         | 0000 | 0000                         | 011111 | 011111                       | 011111 | 011111                       |