(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4851696号

(P4851696)

(45) 発行日 平成24年1月11日(2012.1.11)

(24) 登録日 平成23年10月28日(2011.10.28)

(51) Int.CI.

G02F 1/1335 (2006.01)

F 1

G02F 1/1335 515

請求項の数 7 (全 26 頁)

(21) 出願番号 特願2004-264847 (P2004-264847)

(22) 出願日 平成16年9月13日 (2004.9.13)

(65) 公開番号 特開2005-99797 (P2005-99797A)

(43) 公開日 平成17年4月14日 (2005.4.14)

審査請求日 平成19年9月13日 (2007.9.13)

(31) 優先権主張番号 2003-066483

(32) 優先日 平成15年9月25日 (2003.9.25)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 503447036

サムスン エレクトロニクス カンパニー

リミテッド

大韓民国キョンギード、スウォンーシ、ヨ

ントン-ク、マエタンードン 416

(74) 代理人 110000051

特許業務法人共生国際特許事務所

(72) 発明者 シン・キヨン-ジュ

大韓民国京畿道龍仁市器興邑甫羅里289

-12番地 サムジョンソンビマウル10

2棟504号

(72) 発明者 蔡鍾哲

大韓民国ソウル市麻浦区新孔德洞 三星ア

パート102棟2001号

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項1】

絶縁基板、

前記絶縁基板上に行方向に形成されている複数個のゲート線、

前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、

前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び

前記スイッチング素子に接続されている複数個の画素電極

を含み、

前記画素電極に対応される赤色画素、緑色画素、青色画素及び白色画素からなるドットが連続配列されており、 10

赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、青色画素及び白色画素に対応し、

前記ドット内の各画素の液晶容量と保持容量の和である全体容量が、全てのドットで同一であり、

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電極と白色画素電極の面積が等しく、

前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする液晶表示装置。

## 【請求項2】

前記ドット内の赤色画素及び緑色画素の液晶容量と前記ドット内の青色画素及び白色画素の液晶容量の比率が  $a : b$ 、前記ドット内の赤色画素及び緑色画素の保持容量と前記ドット内の青色画素及び白色画素の保持容量の比率が  $c : d$  である場合、 $a + c = b + d$ 、 $1 / 2 < c / d < 1$  であることを特徴とする請求項1に記載の液晶表示装置。

【請求項3】

絶縁基板、

前記絶縁基板上に行方向に形成されている複数個のゲート線、

前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、

前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び

前記スイッチング素子に接続されている複数個の画素電極

を含み、

前記画素電極に対応される赤色画素、緑色画素、青色画素及び白色画素からなるドットが連続配列されており、

赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、青色画素及び白色画素に対応し、

前記ドット内の赤色画素及び緑色画素の液晶容量が青色画素及び白色画素の液晶容量よりも大きく、赤色画素及び緑色画素の寄生容量が青色画素及び白色画素の寄生容量よりも大きく、赤色画素及び緑色画素のキックバック電圧と青色画素及び白色画素のキックバック電圧が同一であり、

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電極と白色画素電極の面積が等しく、

前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする液晶表示装置。

【請求項4】

絶縁基板、

前記絶縁基板上に行方向に形成されている複数個のゲート線、

前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、

前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び

前記スイッチング素子に接続されている複数個の画素電極

を含み、

前記画素電極に対応される赤色画素、緑色画素、青色画素及び白色画素からなるドットが連続配列されており、

赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、青色画素及び白色画素に対応し、

前記ドット内の赤色画素及び緑色画素と青色画素及び白色画素の間の液晶容量の比率、保持容量の比率、及び寄生容量の比率が、全てのドットで同一であり、

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電極と白色画素電極の面積が等しく、

前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする液晶表示装置。

【請求項5】

絶縁基板、

前記絶縁基板上に行方向に形成されている複数個のゲート線、

前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、

前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び

前記スイッチング素子に接続されている複数個の画素電極

を含み、

10

20

30

40

50

前記画素電極に対応される赤色画素、緑色画素、青色画素及び白色画素からなるドットが連続配列されており、

赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、青色画素及び白色画素に対応し、

各画素のチャンネルの幅と長さの比率をW/Lとする時、前記ドット内の赤色画素及び緑色画素と青色画素及び白色画素の間の全体容量の比率、寄生容量の比率、及びW/Lの比率が、全てのドットで同一であり、

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電極と白色画素電極の面積が等しく、

前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする液晶表示装置。 10

【請求項6】

絶縁基板、

前記絶縁基板上に行方向に形成されている複数個のゲート線、

前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、

前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び

前記スイッチング素子に接続されている複数個の画素電極

を含み、

前記画素電極に対応される赤色画素、緑色画素、青色画素及び白色画素からなるドットが連続配列されており、 20

赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、青色画素及び白色画素に対応し、

各画素のチャンネルの幅と長さの比率をW/Lとする時、前記ドット内の赤色画素及び緑色画素と青色画素及び白色画素の間の全体容量の比率、液晶容量の比率、保持容量の比率、寄生容量の比率、及びW/Lの比率が、全てのドットで同一であり、

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電極と白色画素電極の面積が等しく、

前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする液晶表示装置。 30

【請求項7】

絶縁基板、

前記絶縁基板上に行方向に形成されている複数個のゲート線、

前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、

前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び

前記スイッチング素子に接続されている複数個の画素電極

を含み、

赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、青色画素及び白色画素に対応し、二つの赤色画素電極、二つの緑色画素電極、一つの青色画素電極及び一つの白色画素電極にて一つのドットがなり、前記一つのドットで行方向に前記赤色画素電極及び前記緑色画素電極が交互に配列されており、列方向に前記赤色画素電極及び前記緑色画素電極が交互に配列されており、前記青色画素電極及び前記白色画素電極は二つの画素行にかけて一つの菱形状を形成し、隣り合う二つの行で菱形状を中心に対角線方向に前記赤色画素電極及び前記緑色画素電極が対向して配置され、 40

前記青色画素電極及び前記白色画素電極は前記データ線を基準として分離され、前記青色画素電極及び前記白色画素電極の各々に前記スイッチング素子が接続されており、

各画素のチャンネルの幅と長さの比率をW/Lとする時、前記ドット内の赤色画素及び緑色画素と青色画素及び白色画素の間の全体容量の比率、液晶容量の比率、保持容量の比率、寄生容量の比率及びW/Lの比率が、全てのドットで同一であり、 50

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電極と白色画素電極の面積が等しく、

前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする液晶表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は液晶表示装置に関し、特にRGBW液晶表示装置に関する。

【背景技術】

【0002】

液晶表示装置は、現在最も広く用いられている平板表示装置の一つであって、電界生成電極が形成されている2枚の表示板とその間に挿入されている液晶層からなり、電極に電圧を印加して液晶層の液晶分子を再配列させることによって、液晶層を通過する光の透過率を調節する表示装置である。

液晶表示装置の中でも、電界生成電極が二つの表示板に各々備えられているものが現在主に用いられている。そのうち、一方の表示板には複数の画素電極が行列状に配列されており、他方の表示板には一つの共通電極が表示板全面を覆っている構造の液晶表示装置が主流である。

【0003】

このような液晶表示装置は、画素電極と赤色、緑色、青色の色フィルタが形成されている複数の画素を有し、配線を通じて印加される信号によって各画素などが駆動されて表示動作が行われる。配線には、走査信号を伝達する走査信号線すなわちゲート線、画像信号を伝達する画像信号線すなわちデータ線があり、各画素は一つのゲート線及び一つのデータ線と接続されている薄膜トランジスタが形成されており、これを通じて画素に形成されている画素電極に伝達される画像信号が制御される。

【0004】

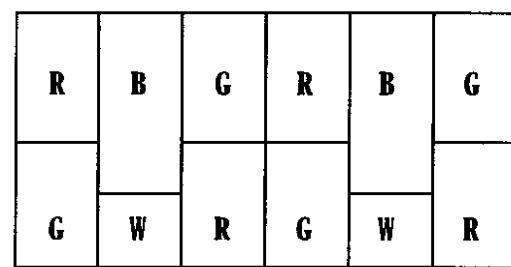

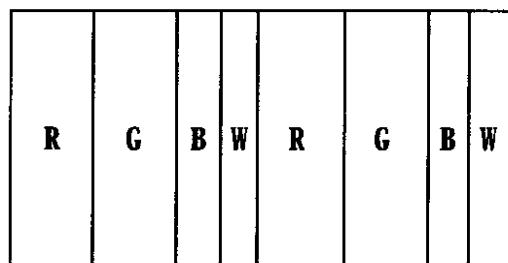

この時、それぞれの画素に赤色(R)、緑色(G)、青色(B)の色フィルタを多様に配列して様々なカラーを表示することができる。配列方法としては、同一色の色フィルタが画素列に沿って配列され、画素行ごとに異なる色の色フィルタが配列されるストライプ(stripe)型、画素列方向及び行方向に赤色(R)、緑色(G)、青色(B)の色フィルタを順次に配列するモザイク(mosaic)型、画素列方向に画素などが交差するようジグザグ状に配置し、赤色(R)、緑色(G)、青色(B)の色フィルタを順次に配列するデルタ(delta)型などがある。

【0005】

また、画像表示の際により有利な高解像度の表現能力を有すると同時に、設計コストを最少化できる“*The PenTile Matrix* (登録商標) color pixel arrangement”という画素配列構造が提案された。このようなペントイルマトリクス(PenTile Matrix)の画素配列構造において、菱形状の青色の単位画素は二つのドットの表示時に共有され、隣り合う青色の単位画素は一つのデータ駆動集積回路によってデータ信号が伝達され、各々異なるゲート駆動集積回路によって駆動される。このようなペントイルマトリクス画素構造を利用すれば、SVGA級の表示装置によってUXGA級の解像度を実現することができ、低価格のゲート駆動集積回路の数は増加するが、高価格のデータ駆動集積回路の数を減らすことができるので、表示装置の設計コストを最少化することができる。

【発明の開示】

【発明が解決しようとする課題】

【0006】

ところが、このようなペントイルマトリクス画素構造は、データ線とゲート線の配置が難しく、データ線とゲート線が画素電極と重なる部分が多い場合には開口率が低下する問題点がある。そして、赤色画素及び緑色画素に対応する画素電極と青色画素に対応する画素電極との面積が等しくないため、赤色画素及び緑色画素と青色画素との間の画素パラメ

10

20

30

40

50

タ、例えば保持容量 (Cst) 、液晶容量 (Clc) などが各々異なり、フリッカー等の画質不良のおそれがある。

【0007】

一方、前記のような赤色 (R) 、緑色 (G) 及び青色 (B) の 3 色から構成された液晶表示装置とは異なって、赤色 (R) 、緑色 (G) 及び青色 (B) に白色 (W) を追加して輝度を改善する RGBW 方式も公知の技術である。このような RGBW 配列方式には、ストライプ型配列方式とモザイク型配列方式がある。ストライプ型配列方式の場合、R 、 G 、 B 及び W の 4 つの画素からなる一つのドットは、データ線の数が 25 % 増加し、モザイク型配列方式の場合は、データ線の数は 30 % 減少するがゲート線の数が 2 倍増加する短所がある。RGBW 配列方式のこのような問題を解消するために、ペンタイルマトリクス画素構造における特定画素 ( 例えば青色画素 ) の面積を分けて、白色画素の面積として活用することもある。

しかし、このような RGBW 配列方式の場合、赤色、緑色、青色及び白色の比率を 1 : 1 : 1 : 1 にすることもできるが、その場合白色が強調されすぎて彩度が低下する問題がある。

【0008】

本発明は上記した問題に鑑みてなされたものであり、その技術的課題は、画質の向上された液晶表示装置を提供することにある。

【課題を解決するための手段】

【0009】

本発明による液晶表示装置は、絶縁基板、前記絶縁基板上に行方向に形成されている複数個のゲート線、前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び前記スイッチング素子に接続されている複数個の画素電極を含み、前記画素電極に対応される赤色画素、緑色画素、青色画素及び白色画素からなるドットが連続配列されており、赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、青色画素及び白色画素に対応し、

前記ドット内の各画素の液晶容量と保持容量の和である全体容量が、全てのドットで同一であり、

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電極と白色画素電極の面積が等しく、前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする。

【0010】

また、前記ドット内の赤色画素及び緑色画素の液晶容量と前記ドット内の青色画素及び白色画素の液晶容量の比率が  $a : b$  、前記ドット内の赤色画素及び緑色画素の保持容量と前記ドット内の青色画素及び白色画素の保持容量の比率が  $c : d$  である場合、  $a + c = b + d$  、  $1 / 2 < c / d < 1$  であることが好ましい。

【0011】

本発明による液晶表示装置は、絶縁基板、前記絶縁基板上に行方向に形成されている複数個のゲート線、前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び前記スイッチング素子に接続されている複数個の画素電極を含み、前記画素電極に対応される赤色画素、緑色画素、青色画素及び白色画素からなるドットが連続配列されており、赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、青色画素及び白色画素に対応し、

前記ドット内の赤色画素及び緑色画素の液晶容量が青色画素及び白色画素の液晶容量よりも大きく、赤色画素及び緑色画素の寄生容量が青色画素及び白色画素の寄生容量よりも大きく、赤色画素及び緑色画素のキックバック電圧と青色画素及び白色画素のキックバック電圧が同一であり、

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電

10

20

30

40

50

極と白色画素電極の面積が等しく、前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする。

【0012】

本発明による液晶表示装置は、絶縁基板、前記絶縁基板上に行方向に形成されている複数個のゲート線、前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び前記スイッチング素子に接続されている複数個の画素電極を含み、前記画素電極に対応される赤色画素、緑色画素、青色画素及び白色画素からなるドットが連続配列されており、赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、青色画素及び白色画素に対応し、

10

前記ドット内の赤色画素及び緑色画素と青色画素及び白色画素の間の液晶容量の比率、保持容量の比率、及び寄生容量の比率が、全てのドットで同一であり、

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電極と白色画素電極の面積が等しく、前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする。

【0013】

本発明による液晶表示装置は、絶縁基板、前記絶縁基板上に行方向に形成されている複数個のゲート線、前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び前記スイッチング素子に接続されている複数個の画素電極を含み、前記画素電極に対応される赤色画素、緑色画素、青色画素及び白色画素からなるドットが連続配列されており、赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、青色画素及び白色画素に対応し、

20

各画素のチャンネルの幅と長さの比率をW/Lとする時、前記ドット内の赤色画素及び緑色画素と青色画素及び白色画素の間の全体容量の比率、寄生容量の比率、及びW/Lの比率が、全てのドットで同一であり、

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電極と白色画素電極の面積が等しく、前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする。

30

【0014】

本発明による液晶表示装置は、絶縁基板、前記絶縁基板上に行方向に形成されている複数個のゲート線、前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び前記スイッチング素子に接続されている複数個の画素電極を含み、前記画素電極に対応される赤色画素、緑色画素、青色画素及び白色画素からなるドットが連続配列されており、赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、青色画素及び白色画素に対応し、

各画素のチャンネルの幅と長さの比率をW/Lとする時、前記ドット内の赤色画素及び緑色画素と青色画素及び白色画素の間の全体容量の比率、液晶容量の比率、保持容量の比率、寄生容量の比率、及びW/Lの比率が、全てのドットで同一であり、

40

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電極と白色画素電極の面積が等しく、前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする。

【0015】

本発明による液晶表示装置は、絶縁基板、前記絶縁基板上に行方向に形成されている複数個のゲート線、前記絶縁基板上に列方向に形成され、前記ゲート線と絶縁されて交差している複数個のデータ線、前記ゲート線及びデータ線に接続されている複数個のスイッチング素子、及び前記スイッチング素子に接続されている複数個の画素電極を含み、赤色画素電極、緑色画素電極、青色画素電極及び白色画素電極は、各々、赤色画素、緑色画素、

50

青色画素及び白色画素に対応し、二つの赤色画素電極、二つの緑色画素電極、一つの青色画素電極及び一つの白色画素電極にて一つのドットがなり、前記一つのドットで行方向に前記赤色画素電極及び前記緑色画素電極が交互に配列されており、列方向に前記赤色画素電極及び前記緑色画素電極が交互に配列されており、前記青色画素電極及び前記白色画素電極は二つの画素行にかけて一つの菱形状を形成し、隣り合う二つの行で菱形状を中心に対角線方向に前記赤色画素電極及び前記緑色画素電極が対向して配置され、前記青色画素電極及び前記白色画素電極は前記データ線を基準として分離され、前記青色画素電極及び前記白色画素電極の各々に前記スイッチング素子が接続されており、

各画素のチャンネルの幅と長さの比率をW/Lとする時、前記ドット内の赤色画素及び緑色画素と青色画素及び白色画素の間の全体容量の比率、液晶容量の比率、保持容量の比率、寄生容量の比率及びW/Lの比率が、全てのドットで同一であり、

前記ドット内の赤色画素電極と緑色画素電極の面積が等しく、前記ドット内の青色画素電極と白色画素電極の面積が等しく、

前記ドット内の赤色画素電極と青色画素電極の面積は互いに異なることを特徴とする液晶表示装置。

10

### 【発明の効果】

#### 【0016】

本発明による液晶表示装置は、各画素電極の面積が異なる場合、各画素間の全体容量、液晶容量、保持容量、寄生容量及びTFTのW/Lの比率が同一になるように形成することによって、フリッカー発生を防止することができる。

20

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、添付した図面を参照して、本発明の実施例に対して、本発明が属する技術分野における通常の知識を有する者が容易に実施することができるよう詳細に説明する。しかし、本発明は多様な形態で実現することができ、ここで説明する実施例に限定されない。

図面は、各種層及び領域を明確に表現するために、厚さを拡大して示している。明細書全体を通じて類似した部分については同一な図面符号を付けている。層、膜、領域、板などの部分が他の部分の“上に”あるとする時、これは他の部分の“すぐ上に”ある場合に限らず、その中間に更に他の部分がある場合も含む。逆に、ある部分が他の部分の“すぐ上に”あるとする時、これは中間に他の部分がない場合を意味する。

30

#### 【0018】

本発明の実施例による液晶表示装置について図面を参照して詳細に説明する。

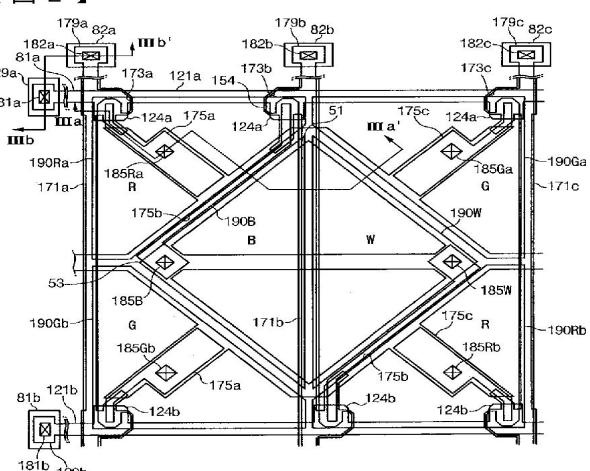

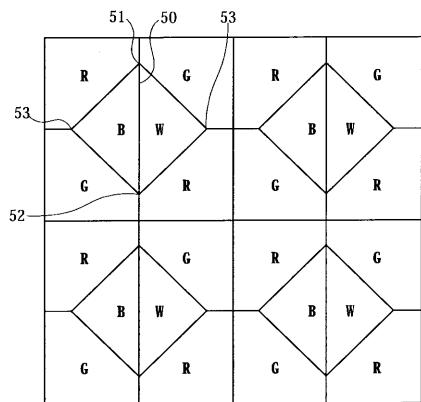

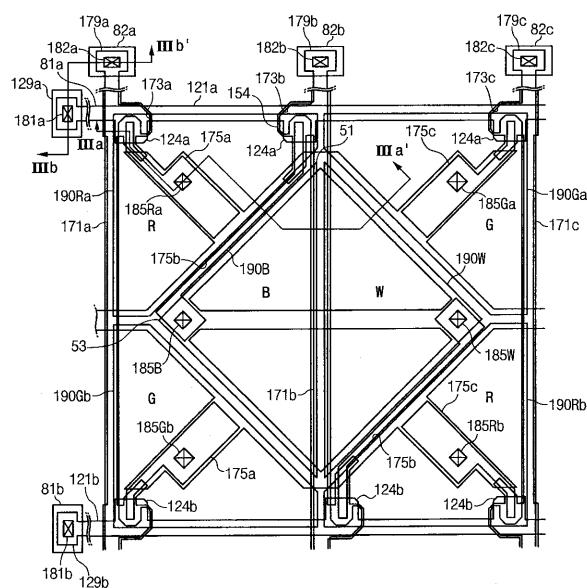

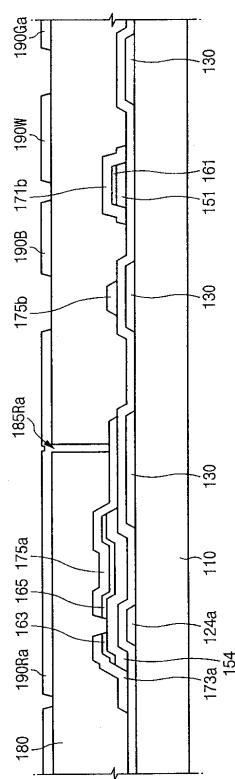

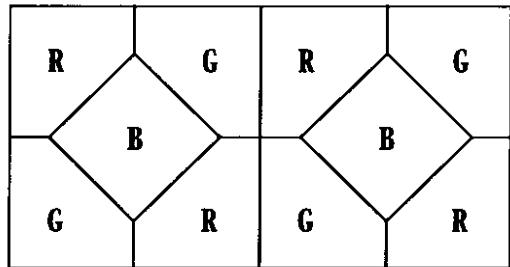

まず、図1～図3bを参照して本発明の好ましい第1実施例による液晶表示装置について詳細に説明する。

図1は本発明の第1実施例による液晶表示装置の画素配置図であり、図2は本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板の配置図であり、図3a及び図3bは図2に示す薄膜トランジスタ表示板の各々IIIa-IIIa'線とIIIb-IIIb'線による断面図である。

40

#### 【0019】

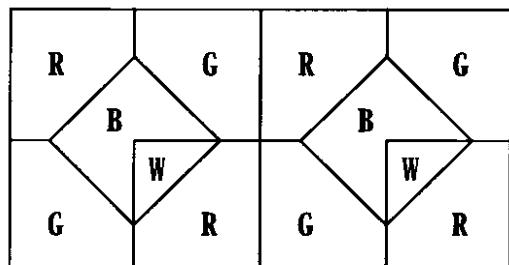

図1に示すように、一つの列方向には、赤色画素(R)、青色画素(B)、緑色画素(G)、赤色画素(R)、青色画素(B)及び緑色画素(G)が順次配列されており、隣接するもう一つの列方向には、緑色画素(G)、白色画素(W)、赤色画素(R)、緑色画素(G)、白色画素(W)、赤色画素(R)が順次配列されている。そして、一つの行方向には、赤色画素(R)及び緑色画素(G)が交互に配置されており、もう一つの行方向には、三角形状の青色画素(B)及び白色画素(W)からなる菱形状が交互に配置されている。

一つの列方向に配列されている赤色画素(R)、青色画素(B)及び緑色画素(G)と、隣接してもう一つの列方向に配列されている緑色画素(G)、白色画素(W)及び赤色画素(R)が一つのドットを構成する。即ち、一つのドット内には、赤色画素(R)が二つ、緑

50

色画素 (G) が二つ、青色画素 (B) が一つ、白色画素 (W) が一つが形成されている。

【0020】

ここで、三角形状の青色画素 (B) 及び白色画素 (W) は、一辺が対向しており、二つの画素列にかけて一つの菱形状を形成し、このような菱形状は一つのドットの中心に位置している。

そして、赤色画素 (R) 及び緑色画素 (G) は、隣接する二つの行で菱形状を中心に対角線方向に対向するように配置されている。即ち、三角形状の青色画素 (B) 及び白色画素 (W) は、辺 50 の左右に位置する辺の頂点 51、52 がデータ線と平行な線上に位置し、辺 50 に直交する位置にある 2 つの頂点 53 がゲート線と平行な線上に位置している。そして、このような三角形状の青色画素 (B) と白色画素 (W) は、互いの辺 50 が対向し、全体的に菱形を形成している。

【0021】

このような画素配置を有する本発明の第 1 実施例による液晶表示装置の薄膜トランジスタ表示板の構造について図 2、図 3a 及び図 3b を参照してより詳細に説明する。

赤色画素、緑色画素、青色画素及び白色画素の各々に、赤色画素電極 190Ra、190Rb、緑色画素電極 190Ga、190Gb、青色画素電極 190B 及び白色画素電極 190W が対応し、このような二つの赤色画素電極 190Ra、190Rb、二つの緑色画素電極 190Ga、190Gb、一つの青色画素電極 190B 及び一つの白色画素電極 190W により、一つのドットが形成される。

この時、図 2 に示すように、四角形状の一つのドット内には、横方向に二つのゲート線が形成されている。即ち、第 1 赤色画素電極 190Ra、第 1 緑色画素電極 190Ga 及び青色画素電極 190B にゲート信号を伝達する第 1 ゲート線 121a と、第 2 赤色画素電極 190Rb、第 2 緑色画素電極 190Gb 及び白色画素電極 190W にゲート信号を伝達する第 2 ゲート線 121b が、一つのドット内に形成されている。

【0022】

四角形状の一つのドット内には、縦方向に 3 つのデータ線が形成されている。即ち、第 1 赤色画素電極 190Ra 及び第 2 緑色画素電極 190Gb にデータ信号を伝達する第 1 データ線 171a、青色画素電極 190B 及び白色画素電極 190W にデータ信号を伝達する第 2 データ線 171b、第 2 赤色画素電極 190Rb 及び第 1 緑色画素電極 190Ga にデータ信号を伝達する第 3 データ線 171c が、ゲート線 121a、121b と絶縁されて交差しながら一つのドット内に形成されている。

ここで、ゲート線 121a、121b とデータ線 171a、171b、171c が交差する部分には、ゲート線 121a、121b と接続されているゲート電極 124a、124b、データ線 171a、171b、171c と接続されているソース電極 173a、173b、173c、ゲート電極 124a、124b に対してソース電極 173a、173b、173c と対向側に形成されているドレイン電極 175a、175b、175c 及び半導体層 154 を含む 6 つの薄膜トランジスタが形成されており、それぞれの画素には、画素電極 190Ra、190Rb、190Ga、190Gb、190B、190W が 6 つの薄膜トランジスタを通じてゲート線 121a、121b 及びデータ線 171a、171b、171c と電気的に接続されている。

【0023】

このように、青色画素電極 190B 及び白色画素電極 190W に接続されたデータ線 171b を直線化し、即ち青色画素電極 190B 及び白色画素電極 190W をデータ線を基準として分離することによって、データ線 171b の抵抗増加を防止することができる。

これと共に、青色画素電極 190B 及び白色画素電極 190W に接続されたデータ線 171b を直線化し、青色画素電極 190B 及び白色画素電極 190W に薄膜トランジスタを各々形成することによって、独立的な駆動を可能にする。

【0024】

一方、ゲート線 121a、121b の端部 129a、129b は、外部から走査信号の伝達を受けてゲート線 121a、121b に伝達するために幅が拡張されており、データ線 17

10

20

30

40

50

1a、171b、171cの端部179a、179b、179cは、外部から映像信号の伝達を受けてデータ線171a、171b、171cに伝達するために幅が拡張されている。

また、ゲート線121a、121bと同一層で、画素電極190Ra、190Rb、190Ga、190Gb、190B、190Wと重なって保持容量を形成する維持電極配線130が形成されている。維持電極配線130は、隣り合う画素電極190Ra、190Rb、190Ga、190Gb、190B、190Wの一部と全て重なるように画素電極が分離されている領域、即ち画素電極間の境界線に形成されている。

#### 【0025】

この場合、維持電極配線130の一部は、赤色画素電極190Ra、190Rb、緑色画素電極190Ga、190Gb、青色画素電極190B及び白色画素電極190Wと共有できるよう、ゲート線121a、121bと平行に、そしてゲート線121a、121bの間の中心部に形成されている。したがって、三角形状の青色画素電極190B及び白色画素電極190Wの頂点に該当する部分53と維持電極配線130は、重畳して保持容量(保持容量)を構成する。

#### 【0026】

より詳細に、本発明の第1実施例による液晶表示装置用薄膜トランジスタ表示板の構造を見ると、透明な絶縁基板110上にゲート信号を伝達する複数のゲート線121a、121bと維持電極配線130が形成されている。ゲート線121a、121bは横方向にのびており、各ゲート線121a、121bの一部は上または下に突出して複数のゲート電極124a、124bを構成し、ゲート線の端部129a、129bは幅が拡張されている。

#### 【0027】

ゲート線121a、121bは、本発明の一実施例のように、単一層から形成されたり、二重層や三重層から形成されることもできる。言いかえれば、ゲート線121a、121bは、物理的な性質の異なる二つの膜、即ち下部膜とその上の上部膜を含むことができる。上部膜は、ゲート信号の遅延や電圧降下を低減させるように低い比抵抗(resistivity)の金属、例えばアルミニウム(AI)やアルミニウム合金などアルミニウム系列の金属で形成できる。これとは異なって、下部膜は、他の物質特にITO(indium tin oxide)またはIZO(indium zinc oxide)との物理的、化学的、電気的な接触特性が優れた物質、例えばモリブデン(Mo)、モリブデン合金(例:モリブデン-タンクスチル(MoW)合金)、クロム(Cr)などで形成できる。下部膜と上部膜の組み合わせの好ましい例としては、Cr/AI、Cr/AI-Nd合金などのように、各々異なるエッチング条件でエッチングされる二つの層が挙げられる。

#### 【0028】

維持電極配線130は、画素電極190Ra、190Rb、190Ga、190Gb、190B、190Wの一部と各々重なって、画素の電荷保存能力を向上させるための保持容量すなわち維持容量を構成する。

ゲート線121a、121b上には、窒化ケイ素(SiNx)などからなるゲート絶縁膜140が形成されている。ゲート絶縁膜140の上部には、水素化非晶質シリコン(非晶質シリコンはa-Siと略称する)などからなる複数の線状半導体151が形成されている。線状半導体151は主に縦方向にのびており、ここから複数の突出部154がゲート電極124a、124bを向いてのびている。

#### 【0029】

半導体151、154の上部には、シリサイドまたはn型不純物が高濃度にドーピングされているn+水素化非晶質シリコンなどの物質からなる複数の線状及び島状抵抗性接触部材161、165が形成されている。線状接触部材161は複数の突出部163を有しており、この突出部163と島状接触部材165が対をなして半導体151の突出部154上に位置している。半導体151、154と抵抗性接触部材161、165の側面も傾斜しており、傾斜角は約30~80度である。

ゲート線121a、121b及び維持電極配線130を覆うゲート絶縁膜140及び抵抗性接触部材161、163、165上には、低抵抗の導電物質からなるデータ線171a

10

20

30

40

50

～cが形成されている。

【0030】

データ線171a、171b、171cは、主に縦方向にのびてゲート線121a、121bと交差し、データ電圧を伝達する。各データ線171a、171b、171cからドレイン電極175a、175b、175cの両側にのびた複数の枝がソース電極173a、173b、173cをなす。1対のソース電極173a、173b、173cとドレイン電極175a、175b、175cは各々分離されている。ゲート電極124a、124b、124c、ソース電極173a、173b、173c及びドレイン電極175a、175b、175cは、半導体151の突出部154と共に薄膜トランジスタ(TFT)を構成し、薄膜トランジスタのチャンネルは、ソース電極173a、173b、173cとドレイン電極175a、175b、175cの間の突出部154に形成されている。また、データ線の一端部179a、179b、179cは、外部からの画像信号の印加が受けられるように幅が拡張されている。

【0031】

なお、データ線171a、171b、171cも、ゲート線121a、121bと同様に単一層で形成されたり、二重層や三重層で形成されることができる。即ち、データ線171a、171b、171c及びドレイン電極175a、175b、175cもまた、下部膜とその上に位置する上部膜からなることができる。ゲート線121a、121bの場合と同様に、下部膜と上部膜の組み合わせの好ましい例としては、Cr/Al、Cr/Al-Nd合金などのように、各々異なるエッチング条件でエッチングされる二つの層が挙げられる。

データ線171a、171b、171c及びドレイン電極175a、175b、175cの下部膜及び上部膜も、ゲート線121a、121bと同様に、その側面が約30～80度各々傾斜している。

【0032】

抵抗性接触部材161、165は、その下部の半導体151とその上部のデータ線171a、171b、171c及びドレイン電極175a、175b、175cの間にのみ存在し、これらの間の接触抵抗を低くする役割をする。半導体151は、薄膜トランジスタが位置する突出部154を除いて、その上部の抵抗性接触部材161、165と実質的に同一平面形状を有している。

データ線171a、171b、171c及びドレイン電極175a、175b、175cの上部には、平坦化特性が優れて感光性を有する有機物質、プラズマ化学気相蒸着(PECVD)法によって形成されるa-Si:C:O、a-Si:O:Fなどの低誘電率絶縁物質、または無機物質である窒化ケイ素などからなる保護膜180が形成されている。

【0033】

保護膜180には、データ線171a、171b、171cの端部179a、179b、179c及びドレイン電極175a、175b、175cを各々露出する複数の接触孔182a、182b、182c、185Ra、185Ga、185B、185Rb、185Gb、185Wが設けられており、ゲート絶縁膜140と共にゲート線121a、121bの端部129a、129bを露出する複数の接触孔181a、181bが設けられている。

接触孔181a、181b、182a、182bは、ゲート線121a、121b及びデータ線171a、171b、171cの端部129a、129b、179a、179b、179cを露出する。そして、接触孔185Ra、185Ga、185B、185Rb、185Gb、185Wは、ドレイン電極175a、175b、175cの一部を露出する。ここで、接触孔185Ra、185B、185Gaは、第1赤色画素電極190Ra、青色画素電極190B及び第1緑色画素電極190Gaに各々接続されているドレイン電極175a、175b、175cの一部を露出し、接触孔185Gb、185W、185Rbは、第2緑色画素電極190Gb、白色画素電極190W及び第2赤色画素電極190Rbに各々接続されているドレイン電極175a、175b、175cの一部を露出する。

【0034】

保護膜180上には、複数の画素電極190Ra、190Rb、190Ga、190Gb、190Wが設けられ、各々接続されている。

0B、190W及び複数の接触補助部材81a、81b、82a、82bが形成され、これらはIZO、ITOなどの透明な導電物質からなる。このような画素電極190Ra、190Rb、190Ga、190Gb、190B、190Wは、それぞれの画素R、B、G、Wに画素形状に沿って形成されている。

画素電極190Ra、190Rb、190Ga、190Gb、190B、190Wは、接触孔185Ra、185Ga、185B、185Rb、185Gb、185Wを通じてドレイン電極175a、175b、175cと物理的・電気的に接続されて、ドレイン電極175a、175b、175cからデータ電圧の印加を受ける。データ電圧が印加された画素電極190Ra、190Rb、190Ga、190Gb、190B、190Wは、共通電圧の印加を受ける他の表示板(図示せず)の共通電極(図示せず)と共に電場を生成することによって、二つの電極間の液晶分子を再配列させる。

#### 【0035】

また、画素電極190Ra、190Rb、190Ga、190Gb、190B、190W及び共通電極の間には、容量(以下、“液晶容量”と言う)が形成されて、薄膜トランジスタがターンオフされた後にも印加された電圧を維持しており、電圧維持能力を強化するために液晶容量と並列に接続された別の容量を設けるが、これを維持容量と言う。維持容量は、画素電極190Ra、190Rb、190Ga、190Gb、190B、190Wとこれに隣接する他のゲート線121a、121b(これを前段ゲート線(previous gate line)と言う)や別途形成された維持電極配線などの重畳などで形成される。維持電極配線130は、ゲート線121a、121bと同一層で形成され、ゲート線121a、121bと分離され共通電圧などの電圧の印加を受ける。維持容量の静電容量、即ち保持容量を増やすために、重畳部分の面積を増加させたり、画素電極190Ra、190Rb、190Ga、190Gb、190B、190Wと接続され、前段ゲート線若しくは維持電極配線と重なる導電体を保護膜180の下に設けて、両者間の距離を短くすることができる。

#### 【0036】

青色画素電極190Bと接続されるドレイン電極175bの一部は、第1赤色画素電極190Raと青色画素電極190Bの境界線に沿って長くのびてあり、第1赤色画素電極190Raと青色画素電極190Bが分離される領域の下部に形成されている。このようにのびているドレイン電極175bの一部は、接触孔185Bを通じて青色画素電極190Bと接続され、この接触孔185Bは、維持電極配線130上に位置することによって、接触孔185Bによる開口率の減少を最少化した。

そして、青色画素電極190Bと接続されるドレイン電極175bの一部は、その下に設けられている維持電極配線130と重畳している。したがって、維持電極配線130と青色画素電極190Bの重畳による保持容量Cstbは、維持電極配線130と青色画素電極190Bの間に介在するドレイン電極175bが維持電極配線130とより近いので、維持電極配線130とドレイン電極175bの重畳による保持容量に代替することができる。そして、このように維持電極配線130とドレイン電極175bを重畳させることによって、開口率が増大する。

#### 【0037】

同様に、白色画素電極190Wと接続されるドレイン電極175bの一部は、第2赤色画素電極190Rbと白色画素電極190Wの境界線に沿って長く延長され、第2赤色画素電極190Rbと白色画素電極190Wが分離される領域の下部に形成されている。このようにのびているドレイン電極175bの一部は、接触孔185Wを通じて白色画素電極190Wと接続され、この接触孔185Bbは、維持電極配線130上に位置することによって、接触孔185Wによる開口率の減少を最少化した。

また、白色画素電極190Wと接続されるドレイン電極175bの一部は、その下に形成されている維持電極配線130と重畳している。したがって、維持電極配線130と白色画素電極190Wの重畳による保持容量Cstwは、維持電極配線130と白色画素電極190Wの間に介在しているドレイン電極175bが維持電極配線130とより近いので、維持電極配線130とドレイン電極175bの重畳による保持容量に代替することができる。

10

20

30

40

50

そして、このように維持電極配線 130 とドレイン電極 175b を重畳させることによって、開口率が増加する。

【0038】

そして、青色画素電極 190B と第2緑色画素電極 190Gb が分離されている領域の下部には維持電極配線 130 が形成されており、白色画素電極 190W と第1緑色画素電極 190Ga が分離されている領域の下部にも、維持電極配線 130 が形成されて保持容量を構成する。

第1赤色画素電極 190Ra と青色画素電極 190B が分離される領域の下部、第2赤色画素電極 190Rb と白色画素電極 190W が分離される領域の下部、青色画素電極 190B と第2緑色画素電極 190Gb が分離されている領域の下部、及び白色画素電極 190W と第1緑色画素電極 190Ga が分離されている領域の下部に形成されている維持電極配線 130 は、バックライトの透過を防止するためのブラックマトリクスの役割をする。これにより、共通電圧の印加を受ける他の表示板（図示せず）と薄膜トランジスタ表示板の結合時ににおける結合位置の調整不良による開口率の減少を防止する。

【0039】

そして、このような画素配置の液晶表示装置では、解像度改善のためにレンダリング駆動を行うことが好ましい。特定形状の画像を表示するために特定画素を駆動する際に、特定画素のみを駆動するのではなく、駆動しようとする特定画素周辺の周辺画素を駆動することで特定画素が駆動される効果があり、該当特定画像を自然に表示できるのがレンダリング駆動である。

【0040】

ここで、赤色画素電極 190Ra、190Rb と共通電極の間で形成される液晶容量を  $C_{lcr}$ 、赤色画素電極 190Ra、190Rb と維持電極配線 130 の間で形成される保持容量を  $C_{str}$ 、緑色画素電極 190Ga、190Gb と共通電極の間で形成される液晶容量を  $C_{lcg}$ 、緑色画素電極 190Ga、190Gb と維持電極配線 130 の間で形成される保持容量を  $C_{stg}$ 、青色画素電極 190B と共通電極の間で形成される液晶容量を  $C_{lcb}$ 、青色画素電極 190B と維持電極配線 130 の間で形成される保持容量を  $C_{stb}$ 、白色画素電極 190W と共通電極の間で形成される液晶容量を  $C_{lcw}$ 、及び白色画素電極 190W と維持電極配線の間で形成される保持容量を  $C_{stw}$  で表すこととする。

【0041】

本発明の第1実施例において、液晶表示装置の画素配置は P2 型 R G B W 画素構造であって、赤色画素電極 190Ra、190Rb と緑色画素電極 190Ga、190Gb の面積が等しく、青色画素電極 190B と白色画素電極 190W の面積が等しく、赤色画素電極 190Ra、190Rb 及び緑色画素電極 190Ga、190Gb の面積の和と青色画素電極 190B 及び白色画素電極 190W の面積の和の比率が 2:1 である場合について説明する。したがって、 $C_{lcr}$  及び  $C_{lcg}$  の和と  $C_{lcb}$  及び  $C_{lcw}$  の和の比率は 2:1 である。画素の全体容量は液晶容量と保持容量の和であるので、画素間の液晶容量が各々異なる場合画素の全体容量が変わってくる。この場合、画素間のキックバック電圧の偏差によってフリッカーのような画質不良を起こす。

即ち、キックバック電圧を  $V_{kb}$ 、画素電極と共通電極の間で形成される液晶容量を  $C_{lc}$ 、維持電極配線と画素電極の間で形成される保持容量を  $C_{st}$ 、ゲート電極とドレイン電極の間で形成される寄生容量を  $C_{gd}$ 、ゲート線に印加される電圧を  $V_g$  とする時、キックバック電圧は次の式 1 の通りである。

$$V_{kb} = \{C_{gd} / (C_{gd} + C_{lc} + C_{st})\} V_g \quad (1)$$

【0042】

式 1 のように、 $C_{lc}$  が各々異なる画素の場合、 $V_{kb}$  が異なってくるので、各画素間でキックバック電圧 ( $V_{kb}$ ) の偏差が生ずる。したがって、これを防止するために、本発明の第1実施例では、画素の全体容量が同一になるように保持容量を調整する。即ち、 $C_{lcr}$  と  $C_{str}$  の和、 $C_{lcg}$  と  $C_{stg}$  の和、 $C_{lcb}$  と  $C_{stb}$  の和、及び  $C_{lcw}$  と前記  $C_{stw}$  の和が同一になるように、保持容量を設定する。そのために、維持電極配線 130 と画素電極が重なる面積を調整

10

20

30

40

50

する。

即ち、赤色画素電極 190Ra、190Rb（または緑色画素電極 190Ga、190Gb）の面積が一つの青色画素電極 190B（または一つの白色画素電極 190W）の面積よりも大きくて、Clcr（またはClcg）がClcb（またはClcw）よりも大きい場合には、赤色画素電極 190Ra、190Rb（または緑色画素電極 190Ga、190Gb）と維持電極配線 130 が重なる面積が一つの青色画素電極 190B（または一つの白色画素電極 190W）と維持電極配線 130 が重なる面積よりも小さくするために、Cstr（またはCstg）がCstb（またはClcw）よりも小さくなるように維持電極配線 130 を形成する。

#### 【0043】

詳細には、本発明の第1実施例において、赤色画素電極 190Ra、190Rbと緑色画素電極 190Ga、190Gbの面積が等しく、青色画素電極 190Bと白色画素電極 190Wの面積が等しく、赤色画素電極 190Ra、190Rb及び緑色画素電極 190Ga、190Gbの面積の和と青色画素電極 190B及び白色画素電極 190Wの面積の和の比率が 2:1 であり、Clcr及びClcgの和とClcb及びClcwの和の比率が 2:1 である場合、即ちClcr（またはClcg）とClcb（またはClcw）の比率が 2:1 である場合に対して説明する。

したがって、 $2Clcr$ （または $2Clcg$ ）+ $Cstr$ （または $Cstg$ ）=Clcb（またはClcw）+ $2Cstb$ （または $2Cstw$ ）となるように、Cstb（またはCstw）を 2 倍増加させ、Cstb（またはCstw）が $2Clcr$ （または $2Clcg$ ）よりも 2 倍小さい分だけ補償する。

ここで、液晶容量Clcr、Clcg、Clcb、Clcwは、液晶に印加される画素電圧に応じて変わるため、低階調の電圧を印加したり高階調の電圧を印加する場合、即ち階調電圧の変動時に全体容量の差が生じことがある。

#### 【0044】

階調変化時、Clcr（またはClcg）が Clcb（またはClow）よりも大きくなり、赤色画素電極 190Ra、190Rb（または緑色画素電極 190Ga、190Gb）の全体容量 $2Clcr$ （または $2Clcg$ ）+ $Cstr$ （または $Cstg$ ）と青色画素電極 190B（または一つの白色画素電極 190W）の全体容量Clcb（またはClcw）+ $2Cstb$ （または $2Cstw$ ）の間には差が生じて、各画素間Vkbの偏差が発生するおそれがある。したがって、階調変化にも変わらない保持容量Cstr、Cstg、Cstb、Cstwを、より大きく形成することが好ましい。

#### 【0045】

本発明の第2実施例では、 $2Clcr$ （または $2Clcg$ ）+ $2Cstr$ （または $2Cstg$ ）=Clcb（またはClcw）+ $3Cstb$ （または $3Cstw$ ）になるように、維持電極配線と画素電極が重なる面積を増加させて液晶表示装置を製造する。即ち、ドット内の赤色画素及び緑色画素の液晶容量とドット内の青色画素及び白色画素の液晶容量の比率が a : b、ドット内の赤色画素及び緑色画素の保持容量とドット内の青色画素及び白色画素の保持容量の比率が c : d である場合、 $a + c = b + d$  であり、 $1 / 2 < c / d < 1$  になるように、第1実施例よりも保持容量を増加させることが好ましい。

より詳細に説明するために、実際数値を導入して設計した液晶表示装置を示す図 4a～図 5bを参照して説明する。

#### 【0046】

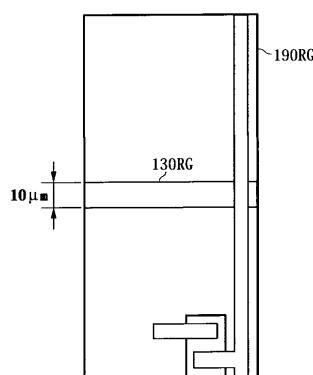

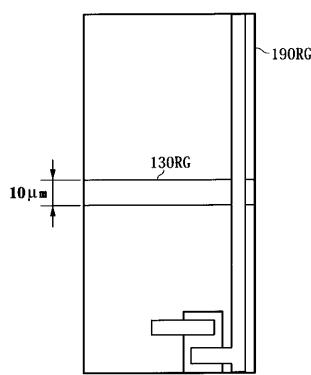

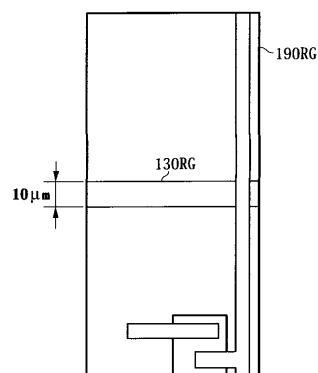

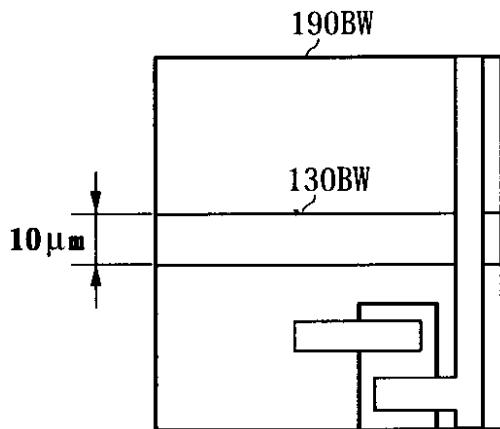

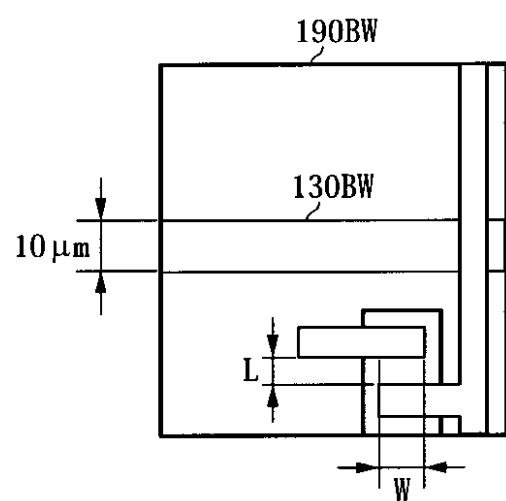

図 4aは従来の液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示したものであり、図 4bは従来の液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示したものである。

図 4aに示すように、Clcr（またはClcg）は $2 \pm 10\%$ 、Cstr（またはCstg）は 1、Cgdr（またはCgdg）は 0.1、及び画素電極 190RG と重畳する維持電極配線 130RG の幅は $10 \mu\text{m}$ である。ここで、Clcr（またはClcg）、Cstr（またはCstg）、Cgdr（またはCgdg）は比率を示すための値であるので、単位は省略する。

図 4bに示すように、Clcb（またはClcw）は $1 \pm 10\%$ 、Cstb（またはCstw）は 1、Cgdb（またはCgdw）は 0.1、及び画素電極 190BW と重畳する維持電極配線 130BW の幅は $10 \mu\text{m}$ である。ここで、Clcb（またはClcw）、Cstb（またはCstw）、Cgdb（またはCgdw）は比率を示すための値であるので、単位は省略する。

## 【0047】

そして、図4a及び図4bに示すように、赤色画素電極（または緑色画素電極）190RGの面積と青色画素電極（または白色画素電極）190BWの面積比率は2:1である。したがって、Clcr（またはClcg）とClcb（またはClcw）の比率は2:1である。この場合、中間階調の画素電圧、即ち20Vを印加した場合、赤色画素または緑色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$\begin{aligned}V_{kbr} \text{ (または } V_{kbg} \text{ )} &= (0.1 \times 20) / (0.1 + 1 + 2) \\&= 0.645\end{aligned}$$

中間階調の画素電圧、即ち20Vを印加した場合、青色画素または白色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$\begin{aligned}V_{kbb} \text{ (または } V_{kbw} \text{ )} &= (0.1 \times 20) / (0.1 + 1 + 1) \\&= 0.952\end{aligned}$$

したがって、赤色画素（または緑色画素）と青色画素（または白色画素）の間Vkbの偏差であるVkbは0.307であり、フリッカーのような画質不良が発生する。

## 【0048】

また、階調変化によって液晶容量Clcr、Clcg、Clcb、Clcwが10%増加する場合、赤色画素または緑色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$\begin{aligned}V_{kb} \text{ (または } V_{kbg} \text{ )} &= (0.1 \times 20) / (0.1 + 1 + 2 + 2) \\&= 0.606\end{aligned}$$

そして、青色画素または白色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$\begin{aligned}V_{kbb} \text{ (または } V_{kbw} \text{ )} &= (0.1 \times 20) / (0.1 + 1 + 1 + 1) \\&= 0.909\end{aligned}$$

したがって、赤色画素（または緑色画素）と青色画素（または白色画素）の間Vkbの偏差であるVkbは0.303であり、フリッカーのような画質不良が発生する。

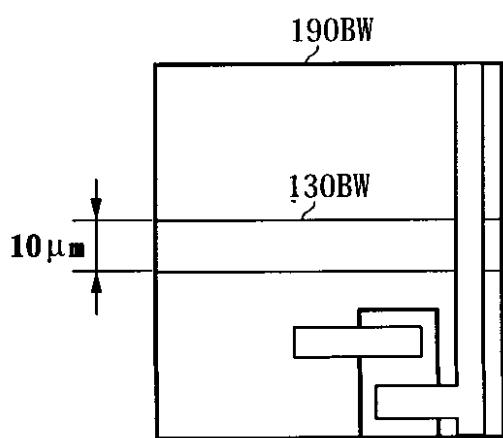

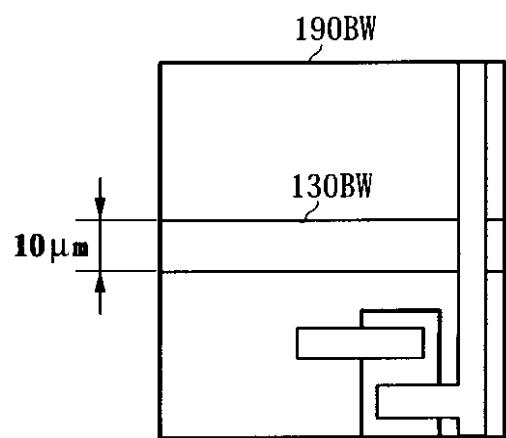

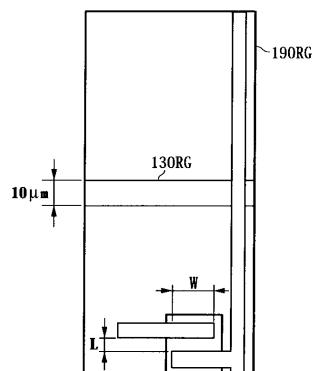

## 【0049】

赤色画素（または緑色画素）と青色画素（または白色画素）との間のキックバック電圧の差によってフリッカーのような画質不良を発生させる図4a及び図4bに示す液晶表示装置とは異なって、図5a及び図5bでは、青色画素（または白色画素）の保持容量を増加させて全体容量を同一に設計した液晶表示装置が示されている。

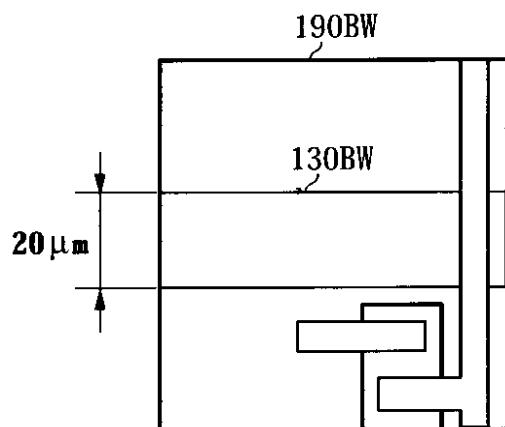

図5aは本発明の第1実施例による液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示しており、図5bは本発明の第1実施例による液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示すものである。

## 【0050】

図5aに示すように、Clcr（またはClcg）は $2 \pm 10\%$ 、Cstr（またはCstg）は1、Cgdr（またはCgdr）は0.1、及び画素電極190RGと重畳する維持電極配線130RGの幅は $10 \mu\text{m}$ である。

図5bに示すように、Clcb（またはClcw）は $1 \pm 10\%$ 、Cstb（またはCstw）は2、Cgdb（またはCgdb）は0.1、及び画素電極190BWと重畳する維持電極配線130BWの幅は $20 \mu\text{m}$ である。

そして、図5a及び図5bに示すように、赤色画素電極（または緑色画素電極）190RGの面積と青色画素電極（または白色画素電極）190BWの面積比率は2:1であり、したがってClcr（またはClcg）とClcb（またはClcw）の比率は2:1である。この場合、中間階調の画素電圧、即ち20Vを印加した場合、赤色画素または緑色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$\begin{aligned}V_{kbr} \text{ (または } V_{kbg} \text{ )} &= (0.1 \times 20) / (0.1 + 1 + 2) \\&= 0.645\end{aligned}$$

そして、中間階調の画素電圧、即ち20Vを印加した場合、青色画素または白色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$V_{kbb} \text{ (または } V_{kbw} \text{ )} = (0.1 \times 20) / (0.1 + 2 + 1)$$

10

20

30

40

50

$$= 0.645$$

したがって、赤色画素（または緑色画素）と青色画素（または白色画素）の間Vkbの偏差であるVkbは0であり、フリッカー現象が防止される。

#### 【0051】

ところで、階調変化によって液晶容量C1cr、C1cg、C1cb、C1cwが10%増加する場合、赤色画素または緑色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$Vkb\text{ (または}Vkb_g\text{)} = (0.1 \times 20 / (0.1 + 1 + 2 + 2)) \\ = 0.606$$

そして、青色画素または白色画素のキックバック電圧は、式1を参照すれば次の通りである。 10

$$Vkb_b\text{ (または}Vkb_w\text{)} = (0.1 \times 20 / (0.1 + 2 + 1 + 1)) \\ = 0.625$$

したがって、赤色画素（または緑色画素）と青色画素（または白色画素）の間のVkbの偏差であるVkbは0.019であり、フリッカーのような画質不良が解消乃至激減する。

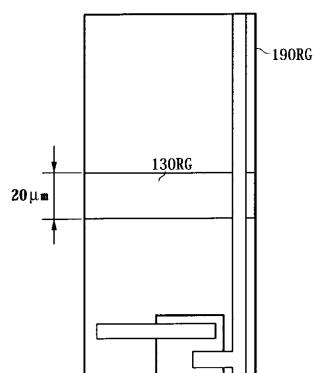

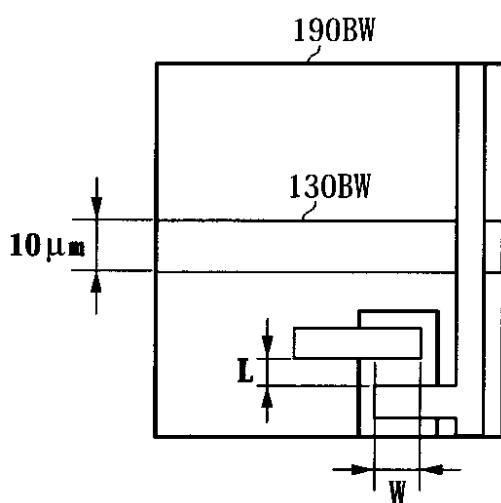

#### 【0052】

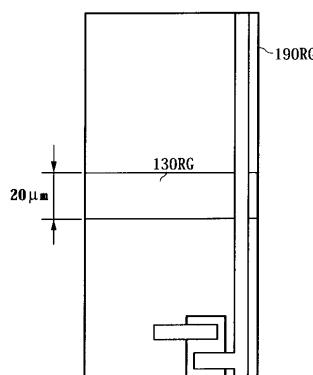

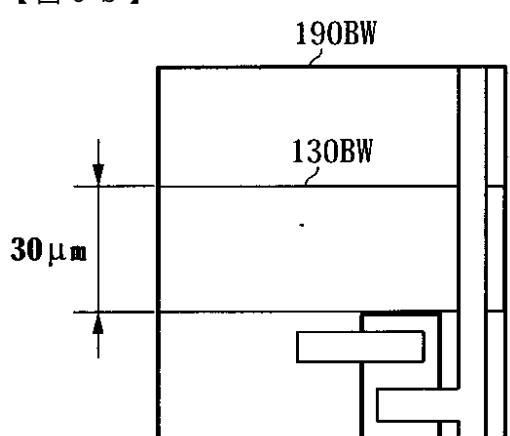

このような階調変化時のVkbの発生を防止するために、保持容量を全て増加させて全体容量を同一に設計した液晶表示装置の実施例を図6a及び図6bに示した。

図6aは本発明の第2実施例による液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示すものであり、図6bは本発明の第2実施例による液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示すものである。 20

図6aに示すように、Clcr（またはClcg）は $2 \pm 10\%$ 、Cstr（またはCstg）は2、Cgdr（またはCgdg）は0.1及び画素電極190RGと重畳する維持電極配線130RGの幅は $20\mu\text{m}$ である。

図6bに示すように、Clcb（またはClcw）は $1 \pm 10\%$ 、Cstb（またはCstw）は3、Cgdb（またはCgdw）は0.1及び画素電極190BWと重畳する維持電極配線130BWの幅は $30\mu\text{m}$ である。

#### 【0053】

そして、図6a及び図6bに示すように、赤色画素電極（または緑色画素電極）190RGの面積と青色画素電極（または白色画素電極）190BWの面積比率は2:1であり、したがってClcr（またはClcg）とClcb（またはClcw）の比率は2:1である。この場合、中間階調の画素電圧、即ち20Vを印加した場合、赤色画素または緑色画素のキックバック電圧は、式1を参照すれば次の通りである。 30

$$Vkb_r\text{ (または}Vkb_g\text{)} = (0.1 \times 20 / (0.1 + 2 + 2)) \\ = 0.488$$

中間階調の画素電圧、即ち20Vを印加した場合、青色画素または白色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$Vkb_b\text{ (または}Vkb_w\text{)} = (0.1 \times 20 / (0.1 + 3 + 1)) \\ = 0.488$$

したがって、赤色画素（または緑色画素）と青色画素（または白色画素）の間Vkbの偏差であるVkbは0であり、フリッカー現象が防止される。 40

#### 【0054】

そして、階調変化によって液晶容量Clcr、Clcg、Clcb、Clcwが10%増加する場合、赤色画素または緑色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$Vkb\text{ (または}Vkb_g\text{)} = (0.1 \times 20 / (0.1 + 2 + 2 + 2)) \\ = 0.465$$

青色画素または白色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$Vkb_b\text{ (または}Vkb_w\text{)} = (0.1 \times 20 / (0.1 + 3 + 1 + 1)) \\ = 0.476$$

10

20

30

40

50

したがって、赤色画素（または緑色画素）と青色画素（または白色画素）の間Vkbの偏差であるVkbは階調変化にもかかわらず0.011であり、フリッカー現象が目立たない。

#### 【0055】

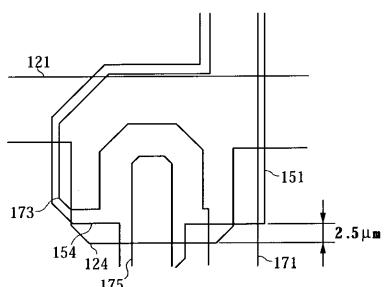

一方、キックバック現象を防止するためには、式1のように、ゲート電極124とドレイン電極の間で形成される寄生容量を調整するのも良い。これについて第3実施例及び第4実施例で説明する。

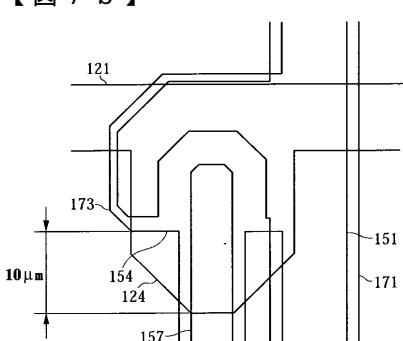

図7aは本発明による第3実施例の液晶表示装置におけるトランジスタ部分を拡大したものであって、青色画素（または白色画素）のゲート電極とドレイン電極が重なって形成される寄生容量Cgdb（またはCgdw）を示すものであり、図7bは本発明による第3実施例の液晶表示装置におけるトランジスタ部分を拡大したものであって、赤色画素（または緑色画素）のゲート電極とドレイン電極が重なって形成される寄生容量Cgdr（またはCgdg）を示すものである。

#### 【0056】

従来液晶表示装置では、赤色画素（または緑色画素）と青色画素（または白色画素）の間にVkbの偏差が発生したため、それを減らすために本発明の第3実施例では、Cgdr（またはCgdg）をCgdb（またはCgdw）よりも大きくすることによって赤色画素（または緑色画素）のVkbと青色画素（または白色画素）のVkbを一致させる。そのために、図7bのように、赤色画素（または緑色画素）のゲート電極124とドレイン電極175が重なる面積を増加させる。以下で詳細に説明する。

図7aに示すように、バックライトによる光漏れ電流（Photo Leakage Current）を防止するために、ゲート電極124はドレイン電極方向のチャンネル形成部分の外側へ2.5μm拡張されている。

このような拡張部は、青色画素（または白色画素）では2.5μmであり、図7bに示すように、赤色画素（または緑色画素）では10μmに増加して形成されているので、ゲート電極124とドレイン電極175が重なる面積が増加し、赤色画素（または緑色画素）のCgdr（またはCgdg）が増加するので、赤色画素（または緑色画素）のVkbと青色画素（または白色画素）のVkbを一致させることでキックバック現象を防止する。

#### 【0057】

より詳細に説明するために、実際数値を導入して設計した液晶表示装置を図8a及び図8bを参照して説明する。

図8aは本発明の第3実施例による液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示したものであり、図8bは本発明の第3実施例による液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示したものである。

図8aに示すように、Clcr（またはClcg）は $2 \pm 10\%$ 、Cstr（またはCstg）は1、Cgdr（またはCgdg）は0.15、及び画素電極190RGと重畳する維持電極配線130RGの幅は10μmである。

図8bに示すように、Clcb（またはClcw）は $1 \pm 10\%$ 、Cstb（またはCstw）は1、Cgdb（またはCgdw）は0.1、及び画素電極190BWと重畳する維持電極配線130BWの幅は10μmである。

#### 【0058】

そして、図8a及び図8bに示すように、赤色画素電極（または緑色画素電極）190RGの面積と青色画素電極（または白色画素電極）190BWの面積比率は2:1であり、したがってClcr（またはClcg）とClcb（またはClcw）の比率は2:1となる。この場合、中間階調の画素電圧、即ち20Vを印加した場合、赤色画素または緑色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$\begin{aligned} V_{kbr} \text{ (または} V_{kbg} \text{)} &= (0.15 \times 20) / (0.15 + 1 + 2) \\ &= 0.952 \end{aligned}$$

中間階調の画素電圧、即ち20Vを印加した場合、青色画素または白色画素のキックバック電圧は、式1を参照すれば、次の通りである。

10

20

30

40

50

$$V_{kbb} \text{ (または} V_{kbw} \text{) } = (0.1 \times 20 / (0.1 + 1 + 1)) \\ = 0.952$$

したがって、赤色画素（または緑色画素）と青色画素（または白色画素）の間 $V_{kb}$ の偏差である $V_{kb}$ は0であり、フリッカーのような現象が発生しない。

【0059】

しかしながら、階調変化によって液晶容量 $C_{lcr}$ 、 $C_{lcg}$ 、 $C_{lcb}$ 、 $C_{lcw}$ が10%増加する場合、赤色画素または緑色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$V_{kb} \text{ (または} V_{kbw} \text{) } = (0.15 \times 20 / (0.15 + 1 + 2.2)) \\ = 0.896$$

10

そして、青色画素または白色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$V_{kb} \text{ (または} V_{kbw} \text{) } = (0.1 \times 20 / (0.1 + 1 + 1.1)) \\ = 0.909$$

したがって、赤色画素（または緑色画素）と青色画素（または白色画素）の間 $V_{kb}$ の偏差である $V_{kb}$ は0.013であり、階調変化によって $V_{kb}$ が発生してフリッカーのような画質不良が解消乃至激減する。

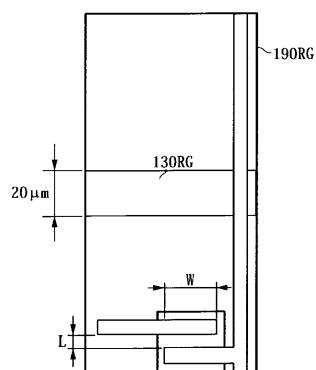

【0060】

このような階調変化時の $V_{kb}$ の発生を防止するために、赤色画素（または緑色画素）と青色画素（または白色画素）の間の液晶容量、保持容量、寄生容量の比率が同一になるように形成した液晶表示装置の実施例を図9a及び図9bに示した。

20

図9aは本発明による第4実施例の液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示したものであり、図9bは本発明による第4実施例の液晶表示装置であって青色画素電極または白色画素電極を有する画素を示したものである。

図9aに示すように、 $C_{lcr}$ （または $C_{lcg}$ ）は $2 \pm 10\%$ 、 $C_{str}$ （または $C_{stg}$ ）は2、 $C_{gdr}$ （または $C_{gdg}$ ）は0.2、及び画素電極190RGと重畳する維持電極配線130RGの幅は $20 \mu m$ である。

図9bに示すように、 $C_{lcb}$ （または $C_{lcw}$ ）は $1 \pm 10\%$ 、 $C_{stb}$ （または $C_{stw}$ ）は1、 $C_{gdb}$ （または $C_{gdw}$ ）は0.1、及び画素電極190BWと重畳する維持電極配線130BWの幅は $10 \mu m$ である。

30

【0061】

そして、図9a及び図9bに示すように、赤色画素電極（または緑色画素電極）190RGの面積と青色画素電極（または白色画素電極）190BWの面積比率は2:1である。したがって、 $C_{lcr}$ （または $C_{lcg}$ ）と $C_{lcb}$ （または $C_{lcw}$ ）の比率は2:1であり、 $C_{str}$ （または $C_{stg}$ ）と $C_{stb}$ （または $C_{stw}$ ）の比率は2:1であり、 $C_{gdr}$ （または $C_{gdg}$ ）と $C_{gdb}$ （または $C_{gdw}$ ）の比率も2:1となり、赤色画素（または緑色画素）と青色画素（または白色画素）の間の液晶容量、保持容量、寄生容量の比率が同一になるように形成されている。

この場合、中間階調の画素電圧、即ち20Vを印加した場合、赤色画素または緑色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$V_{kbr} \text{ (または} V_{kbw} \text{) } = (0.2 \times 20 / (0.2 + 2 + 2)) \\ = 0.952$$

40

そして、中間階調の画素電圧、即ち20Vを印加した場合、青色画素または白色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$V_{kbb} \text{ (または} V_{kbw} \text{) } = (0.1 \times 20 / (0.1 + 1 + 1)) \\ = 0.952$$

したがって、赤色画素（または緑色画素）と青色画素（または白色画素）の間 $V_{kb}$ の偏差である $V_{kb}$ は0であり、フリッカーのような現象が発生しない。

【0062】

そして、階調変化によって液晶容量 $C_{lcr}$ 、 $C_{lcg}$ 、 $C_{lcb}$ 、 $C_{lcw}$ が10%増加する場合には、赤色画素または緑色画素のキックバック電圧は、式1を参照すれば次の通りである。

50

$$V_{kb} (\text{または} V_{kbg}) = (0.2 \times 20 / (0.2 + 2 + 2 \cdot 2)) \\ = 0.909$$

そして、青色画素または白色画素のキックバック電圧は、式1を参照すれば次の通りである。

$$V_{kbb} (\text{または} V_{kbw}) = (0.1 \times 20 / (0.1 + 1 + 1 \cdot 1)) \\ = 0.909$$

したがって、赤色画素（または緑色画素）と青色画素（または白色画素）の間 $V_{kb}$ の偏差である $V_{kb}$ は階調変化にもかかわらず0であり、フリッカー現象が発生しない。即ち、本発明の第4実施例による液晶表示装置は、全階調に渡って安定的にフリッカー現象を防止できるという長所がある。

10

#### 【0063】

しかし、本発明の第1実施例及び第2実施例のように、赤色画素（または緑色画素）と青色画素（または白色画素）の間の全体容量が同一である場合とは異なって、本発明の第3実施例及び第4実施例のように、赤色画素（または緑色画素）と青色画素（または白色画素）の間の全体容量が各々異なる場合には、赤色画素（または緑色画素）と青色画素（または白色画素）の間で充電率の差が発生する。

即ち、オン電流 $I_{on}$ によって充電されるべき画素の全体容量が各々異なるので、 $= RC$ における（充電時間）の差を齎してゲートオンタイムの短い大型パネルの液晶表示装置では充電率の差が発生する。これを防止するための液晶表示装置について第5及び第6実施例として以下で説明する。

20

#### 【0064】

赤色画素（または緑色画素）と青色画素（または白色画素）の間の全体容量、寄生容量及びTFTのW/Lの比率が同一になるように形成した液晶表示装置を、実際数値を導入して第5実施例として図10a及び図10bに示した。

図10aは本発明による第5実施例の液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示したものであり、図10bは本発明による第5実施例の液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示したものである。

#### 【0065】

赤色画素（または緑色画素）の全体容量を $C_{rg}$ 、青色画素（または白色画素）の全体容量を $C_{bw}$ 、赤色画素（または緑色画素）のTFTに電流が流れる時の抵抗を $R_{rg}$ 、青色画素（または白色画素）のTFTに電流が流れる時の抵抗を $R_{bw}$ とする時、赤色画素（または緑色画素）の充電時間は $= R_{rg} \times C_{rg}$ 、青色画素（または白色画素）の充電時間は $= R_{bw} \times C_{bw}$ であり、赤色画素（または緑色画素）の充電時間と青色画素（または白色画素）の充電時間を同一にすべきであるので、次の式2のように示されなければならない。

30

$$R_{rg} \times C_{rg} = R_{bw} \times C_{bw}$$

$$(V / I_{rg}) C_{rg} = (V / I_{bw}) C_{bw}$$

$$C_{rg} / C_{bw} = I_{rg} / I_{bw} \quad (2)$$

ここで、 $I_{rg}$ は赤色画素（または緑色画素）のTFTに電圧が印加された時のTFTに流れる電流 $I_{on}$ であり、 $I_{bw}$ は青色画素（または白色画素）のTFTに電圧が印加された時のTFTに流れる電流 $I_{on}$ である。したがって、赤色画素（または緑色画素）と青色画素（または白色画素）の間の全体容量の比率ほど赤色画素（または緑色画素）と青色画素（または白色画素）の間の $I_{on}$ の比率も同一であるとき、充電時間が同一になる。

40

#### 【0066】

この時、TFTに電圧が印加された時のTFTに流れる電流 $I_{on}$ は、式3の通りである。

$$I_{on} = (W / L) \mu C_{ox} (V_{gd} - V_{th})^2 \quad (3)$$

ここで、Wはソース電極からドレイン電極に電流が移動するチャンネルの幅であり、Lはソース電極からドレイン電極に電流が移動するチャンネルの長さであり、 $\mu$ はチャンネルの電子移動度であり、 $C_{ox}$ はチャンネルを形成する半導体層とゲート電極の間の容量であり、 $V_{th}$ はしきい電圧である。従って、式3を式2に適用すれば、

50

$C_{rg} / C_{bw} = I_{rg} / I_{bw} = (W / L)_{rg} / (W / L)_{bw}$

となる。

ここで、 $(W / L)_{rg}$ は赤色画素（または緑色画素）の TFT のチャンネルの幅と長さの比率であり、 $(W / L)_{bw}$ は青色画素（または白色画素）の TFT のチャンネルの幅と長さの比率である。

#### 【0067】

したがって、赤色画素電極（または緑色画素電極）の面積と青色画素電極（または白色画素電極）の面積が各々異なる液晶表示装置において、赤色画素（または緑色画素）と青色画素（または白色画素）の間の全体容量、寄生容量及び TFT の  $W / L$  の比率が同一になるように形成する場合、 $V_{kb}$ の偏差は 0 であり、充電時間が各画素間で同一であるので、フリッカーのような現象が発生しない。10

#### 【0068】

赤色画素（または緑色画素）と青色画素（または白色画素）の間の全体容量、寄生容量及び TFT の  $W / L$  の比率が同一になるように形成した液晶表示装置を、実際数値を導入して第 5 実施例として図 10a 及び図 10b に示した。

図 10a は本発明による第 5 実施例の液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示したものであり、図 10b は本発明による第 5 実施例の液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示したものである。

#### 【0069】

図 10a に示すように、 $C_{lcr}$ （または  $C_{lcg}$ ）は  $2 \pm 10\%$ 、 $C_{str}$ （または  $C_{stg}$ ）は 1、 $C_{gdr}$ （または  $C_{gdg}$ ）は 0.15、及び画素電極 190RG と重畳する維持電極配線 130RG の幅は  $10 \mu\text{m}$ 、 $(W / L)_{rg}$  は  $30 / 4 \mu\text{m}$  である。20

図 10b に示すように、 $C_{lcb}$ （または  $C_{lcw}$ ）は  $1 \pm 10\%$ 、 $C_{stb}$ （または  $C_{stw}$ ）は 1、 $C_{gdb}$ （または  $C_{gdw}$ ）は 0.1、及び画素電極 190BW と重畳する維持電極配線 130BW の幅は  $10 \mu\text{m}$ 、 $(W / L)_{bw}$  は  $20 / 4 \mu\text{m}$  である。

そして、図 10a 及び図 10b に示すように、赤色画素電極（または緑色画素電極）190RG の面積と青色画素電極（または白色画素電極）190BW の面積比率は 2:1 である。

したがって、 $C_{rg}$  と  $C_{bw}$  間の比率、 $C_{gdr}$ （または  $C_{gdg}$ ）と  $C_{gdb}$ （または  $C_{gdw}$ ）間の比率、及び  $(W / L)_{rg}$  と  $(W / L)_{bw}$  間の比率は 3:2 で同一であって  $V_{kb}$  の偏差は 0 であり、充電時間が各画素間で同一であるので、フリッカーのような現象が発生しない。即ち、第 5 実施例は、第 3 実施例における充電時間が各々異なるという問題点を解消した発明である。30

#### 【0070】

そして、赤色画素（または緑色画素）と青色画素（または白色画素）の間の全体容量、液晶容量、寄生容量、及び TFT の  $W / L$  の比率が同一になるように形成した液晶表示装置を実際数値を導入して第 6 実施例として図 11a 及び図 11b に示した。

図 11a は本発明による第 6 実施例の液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示したものであり、図 11b は本発明による第 6 実施例の液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示したものである。

図 11a に示すように、 $C_{lcr}$ （または  $C_{lcg}$ ）は  $2 \pm 10\%$ 、 $C_{str}$ （または  $C_{stg}$ ）は 2、 $C_{gdr}$ （または  $C_{gdg}$ ）は 0.2、及び画素電極 190RG と重畳する維持電極配線 130RG の幅は  $20 \mu\text{m}$ 、 $(W / L)_{rg}$  は  $40 / 4 \mu\text{m}$  である。40

図 11b に示すように、 $C_{lcb}$ （または  $C_{lcw}$ ）は  $1 \pm 10\%$ 、 $C_{stb}$ （または  $C_{stw}$ ）は 1、 $C_{gdb}$ （または  $C_{gdw}$ ）は 0.1、及び画素電極 190BW と重畳する維持電極配線 130BW の幅は  $10 \mu\text{m}$ 、 $(W / L)_{bw}$  は  $20 / 4 \mu\text{m}$  である。

#### 【0071】

そして、図 11a 及び図 11b に示すように、赤色画素電極（または緑色画素電極）190RG の面積と青色画素電極（または白色画素電極）190BW の面積比率は 2:1 である。したがって、赤色画素電極（または緑色画素電極）190RG と青色画素電極（または白色画素電極）190BW の面積比率、 $C_{rg}$  と  $C_{bw}$  間の比率、 $C_{lcr}$ （または  $C_{lcg}$ ）と  $C_{lcb}$ （または  $C_{lcw}$ ）間の比率、 $C_{str}$ （または  $C_{stg}$ ）と  $C_{stb}$ （または  $C_{stw}$ ）間の比率、 $C_{gdr}$ （または  $C_{gdg}$ ）50

) と  $C_{gdb}$  ( または  $C_{gdw}$  ) 間の比率、及び  $(W/L)_{rg}$  と  $(W/L)_{bw}$  間の比率は 2 : 1 と同一であって、 $V_{kb}$  の偏差は 0 であり、充電時間も各画素間で同一であるので、フリッカーのような現象が発生しない。即ち、第 6 実施例は第 4 実施例における充電時間が各々異なる問題点を解消した発明である。

【 0 0 7 2 】

本発明の実施例では、赤色画素 ( または緑色画素 ) と青色画素 ( または白色画素 ) の間の液晶容量の比率が 2 : 1 である場合に関連して、様々な方法で  $V_{kb}$  偏差を減少させる方法を説明したが、赤色画素 ( または緑色画素 ) と青色画素 ( または白色画素 ) の間の液晶容量の比率が 2 : 1 でない場合にも適用することができる。

また、本発明の実施例では P 2 型 R G B W 画素構造を実施例として説明したが、青色画素電極の面積を増加させたペントイルマトリクス型画素構造 ( 図 12 a 参照 ) 、青色及び白色画素電極の面積を減らした P 1 型 R G B W 画素構造 ( 図 12 b 参照 ) 、青色及び白色画素電極の面積を減らしたストライプ型配列方式の R G B W 画素構造 ( 図 12 c 参照 ) 、白色画素電極の面積を減らした P 2 型 R G B W 画素構造 ( 図 12 d 参照 ) の場合にも、青色画素電極または白色画素電極の面積が赤色画素電極または白色画素電極の面積と異なるので、本発明が適用できる。

【 0 0 7 3 】

以上、添付した図面に示された実施例を参考にして説明したが、これは例示的なものに過ぎず、該当技術分野における通常の知識を有する者であれば、本発明に基づいて様々な変形及び均等な他の実施例が可能であることが理解できるであろう。よって、本発明の真の技術的保護範囲は添付された特許請求の範囲によって決められなければならない。

【 図面の簡単な説明 】

【 0 0 7 4 】

【 図 1 】本発明の第 1 実施例による液晶表示装置の画素配置図である。

【 図 2 】本発明の第 1 実施例による液晶表示装置用薄膜トランジスタ表示板の配置図である。

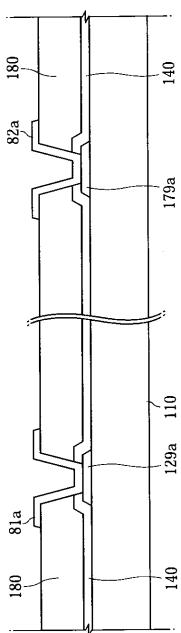

【 図 3 a 】図 2 の薄膜トランジスタ表示板の IIIa-IIIa' 線による断面図である。

【 図 3 b 】図 2 の薄膜トランジスタ表示板の IIIb-IIIb' 線による断面図である。

【 図 4 a 】従来液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示した図である。

【 図 4 b 】従来液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示した図である。

【 図 5 a 】本発明の第 1 実施例による液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示した図である。

【 図 5 b 】本発明の第 1 実施例による液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示した図である。

【 図 6 a 】本発明の第 2 実施例による液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示した図である。

【 図 6 b 】本発明の第 2 実施例による液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示した図である。

【 図 7 a 】本発明による第 3 実施例の液晶表示装置におけるトランジスタ部分を拡大示したもので、青色画素 ( または白色画素 ) のゲート電極とドレイン電極が重なって形成される寄生容量  $C_{gdb}$  ( または  $C_{gdw}$  ) を表示した図である。

【 図 7 b 】本発明による第 3 実施例の液晶表示装置におけるトランジスタ部分を拡大示したもので、赤色画素 ( または緑色画素 ) のゲート電極とドレイン電極が重なって形成される寄生容量  $C_{gdr}$  ( または  $C_{gdg}$  ) を表示した図である。

【 図 8 a 】本発明による第 3 実施例の液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示した図である。

【 図 8 b 】従来液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示した図である。

10

20

30

40

50

【図9a】本発明による第4実施例の液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示した図である。

【図9b】本発明による第4実施例の液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示した図である。

【図10a】本発明による第5実施例の液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示した図である。

【図10b】本発明による第5実施例の液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示した図である。

【図11a】本発明による第6実施例の液晶表示装置であって、赤色画素電極または緑色画素電極を有する画素を示した図である。

【図11b】本発明による第6実施例の液晶表示装置であって、青色画素電極または白色画素電極を有する画素を示した図である。

【図12a】青色画素電極の面積を増加させたペンタイルマトリクス型画素構造を示した図である。

【図12b】青色及び白色画素電極の面積を減らしたP1型RGBW画素構造を示した図である。

【図12c】青色及び白色画素電極の面積を減らしたストライプ型配列方式のRGBW画素構造を示した図である。

【図12d】白色画素電極の面積を減らしたP2型RGBW画素構造を示した図である。

【符号の説明】

【0075】

110 基板

121a、121b、129a、129b ゲート線

124a、124b ゲート電極

140 ゲート絶縁膜

151、154 半導体

161、163、165 抵抗性接触部材

171a、171b、171c、179a、179b、179c データ線

173a、173b、173c ソース電極

175a、175b、175c ドレイン電極

180 保護膜

130 維持電極配線

181a、181b、182a、182b、182c、185Ra、185Ga、185B、185Rb、185Gb、185W 接触孔

190Ra、190Rb、190Ga、190Gb、190B、190W 画素電極

81a、81b、82a、82b、82c 接触補助部材

10

20

30

【図1】

【 図 2 】

### 【図3a】

【図3b】

【図4 a】

【図4 b】

【図5 a】

【図5 b】

【図6 a】

【図6 b】

【図7 a】

【図7 b】

【図 8 a】

【図 8 b】

【図 9 a】

【図 9 b】

【図 10 a】

【図 10 b】

【図 1 1 a】

【図 1 1 b】

【図 1 2 a】

【図 1 2 a】

【図 1 2 b】

【図 1 2 c】

【図 1 2 d】

---

フロントページの続き

審査官 吉田 英一

(56)参考文献 特開平10-054959 (JP, A)

特開2002-328386 (JP, A)

特開2001-296523 (JP, A)

特開2003-029667 (JP, A)

特開2004-078218 (JP, A)

特表2004-507773 (JP, A)

特開2002-006303 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1335

|                |                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                               |         |            |

| 公开(公告)号        | <a href="#">JP4851696B2</a>                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2012-01-11 |

| 申请号            | JP2004264847                                                                                                                                                                                                                                                                                                                         | 申请日     | 2004-09-13 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                                                                                                                                                                                                                                                                                             |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | シンキヨンジュ<br>蔡鍾哲                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | シン・キヨン-ジュ<br>蔡鍾哲                                                                                                                                                                                                                                                                                                                     |         |            |

| IPC分类号         | G02F1/1335 G02F1/1343 G02F1/1345                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | G02F1/133514 G02F2201/52 G09G2300/0452                                                                                                                                                                                                                                                                                               |         |            |

| FI分类号          | G02F1/1335.515 G02F1/1343 G02F1/1345                                                                                                                                                                                                                                                                                                 |         |            |

| F-TERM分类号      | 2H091/FA02Y 2H091/FA50Y 2H091/FD01 2H091/FD04 2H091/GA03 2H091/LA15 2H091/LA20 2H092/GA12 2H092/GA23 2H092/JA42 2H092/JB61 2H092/JB62 2H092/NA01 2H092/NA07 2H092/PA08 2H191/FA02Y 2H191/FA96Y 2H191/FD01 2H191/FD04 2H191/GA05 2H191/LA19 2H191/LA27 2H291/FA02Y 2H291/FA96Y 2H291/FD01 2H291/FD04 2H291/GA05 2H291/LA19 2H291/LA27 |         |            |

| 审查员(译)         | 吉田栄一                                                                                                                                                                                                                                                                                                                                 |         |            |

| 优先权            | 1020030066483 2003-09-25 KR                                                                                                                                                                                                                                                                                                          |         |            |

| 其他公开文献         | JP2005099797A                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                            |         |            |

## 摘要(译)

要解决的问题：通过防止闪烁等来提高图像质量。多条数据线在列方向上形成在绝缘基板上并与栅极线绝缘并与栅极线交叉;的多个开关连接到栅极线和数据线的元件，其包括多个连接到该开关元件的像素电极，一个红色像素组成，绿色像素，蓝色像素和对应于该像素电极的点为白像素按顺序排列。通过调整像素电极190RG和维持电极130RG宽度(重叠区域)等，总电容的红色像素和绿色像素，蓝色像素和在所述存储电容器的液晶电容比的点为白像素之间的比率比，寄生电容的比是所有的点是相同的，并且每个像素的通道的宽度W和长度L的比W / L是所有的点是相同的。背景技术

〔 図 2 〕