(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-292397

(P2005-292397A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>G02F 1/1343

G02F 1/1337

G02F 1/1368

F 1

G02F 1/1343

G02F 1/1337 505

G02F 1/1368

テーマコード(参考)

2H090

2H092

審査請求 未請求 請求項の数 9 O L (全 32 頁)

(21) 出願番号

(22) 出願日特願2004-106138 (P2004-106138)

平成16年3月31日 (2004.3.31)(71) 出願人 302036002

富士通ディスプレイテクノロジーズ株式会

社

神奈川県川崎市中原区上小田中4丁目1番

1号

(71) 出願人 501358079

友達光電股▼ふん▲有限公司

台灣新竹科学工業園区新竹市力行二路1号

(74) 代理人 100091672

弁理士 岡本 啓三

(72) 発明者 鎌田 豪

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通ディスプレイテクノロジーズ

株式会社内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】白茶けを防止できて表示品質が良好であり、開口率が高くて明るい表示が可能であるとともに、製造が容易な液晶表示装置を提供する。

【解決手段】画素電極を、斜め方向に延びるスリット117aにより副画素電極116a～116dに分割する。また、補助容量バスライン112の上方に制御電極113を形成する。副画素電極116b, 116cは制御電極113と重なり、制御電極113と容量結合する。制御電極113とTFT141のソース電極114sとは接続配線115aを介して接続する。副画素電極116aは接続配線115aに電気的に接続する。また副画素電極116dは、制御電極113から延びる接続配線115bに電気的に接続する。

【選択図】図11

111:ゲートバスライン 116a～116d:副画素電極

112:補助容量バスライン 117a:スリット

113:制御電極 124:突起

114s:ソース電極 115:データバスライン

**【特許請求の範囲】****【請求項 1】**

相互に対向して配置された第1基板及び第2の基板と、

前記第1の基板及び前記第2の基板の間に封入された垂直配向型液晶と、

前記第1の基板に設けられて走査信号が供給されるゲートバスラインと、

前記第1の基板に設けられて表示信号が供給されるデータバスラインと、

前記ゲートバスライン及び前記データバスラインにより画定される画素領域毎に形成されたスイッチング素子及び画素電極と、

前記第1の基板の画素領域に設けられて前記スイッチング素子と接続された制御電極と、

、

前記第2の基板に設けられたコモン電極とを有し、

前記画素電極が複数の副画素電極に分割され、前記複数の副画素電極の少なくとも一部の副画素電極が前記制御電極と容量結合し、前記制御電極に電圧が印加されると、前記制御電極に容量結合した副画素電極に、前記制御電極との間で形成される容量と前記液晶を介して前記コモン電極との間で形成される容量との比に応じた電圧が印加されることを特徴とする液晶表示装置。

**【請求項 2】**

前記複数の副画素電極のうち前記スイッチング素子に接続された副画素電極の面積の総和  $S_1$  と、前記制御電極との間に形成された容量を介して駆動される副画素電極の面積の総和  $S_2$  との比 ( $S_1 : S_2$ ) が、1 : 9 乃至 6 : 4 の範囲内であることを特徴とする請求項 1 に記載の液晶表示装置。

**【請求項 3】**

前記複数の副画素電極のうち前記スイッチング素子に接続された副画素電極の電圧  $V_1$  と、前記制御電極との間に形成された容量を介して駆動される副画素電極の電圧  $V_2$  との比 ( $V_2 / V_1$ ) が、0.8 乃至 0.59 の範囲内であることを特徴とする請求項 1 に記載の液晶表示装置。

**【請求項 4】**

相互に対向して配置された第1の基板及び第2の基板と、

前記第1の基板及び前記第2の基板の間に封入された液晶と、

前記第1の基板に設けられて走査信号が供給されるゲートバスラインと、

前記第1の基板に設けられて表示信号が供給されるデータバスラインと、

前記ゲートバスライン及び前記データバスラインにより画定される画素領域内に配置され、スリットにより複数の副画素電極に分割された画素電極と、

前記ゲートバスライン及び前記データバスラインに接続されたスイッチング素子と、

前記スイッチング素子に接続されて前記複数の副画素電極の少なくとも1つと容量結合する制御電極と、

前記第2の基板に設けられたコモン電極とを有し、

前記画素電極を分割するスリットの少なくとも一部が、電圧印加時の液晶分子の配向方向を規定するドメイン規制用構造物を構成することを特徴とする液晶表示装置。

**【請求項 5】**

前記データバスラインに前記表示信号を供給し、前記ゲートバスラインに前記走査信号を供給したときに、前記複数の副画素電極の一部に第1の電圧が印加され、残りの副画素電極には前記第1の電圧と異なる第2の電圧が印加されることを特徴とする請求項 4 に記載の液晶表示装置。

**【請求項 6】**

前記制御電極と容量結合をしている副画素電極以外の副画素電極が、前記スイッチング素子と接続していることを特徴とする請求項 4 に記載の液晶表示装置。

**【請求項 7】**

前記第2の基板に、電圧印加時の液晶分子の配向方向を規定する第2のドメイン規制用構造物が形成されていることを特徴とする請求項 4 に記載の液晶表示装置。

## 【請求項 8】

前記スリットと前記第2のドメイン規制用構造物との間隔が、各副画素電極毎に設定されていることを特徴とする請求項7に記載の液晶表示装置。

## 【請求項 9】

前記スイッチング素子と前記制御電極との間を接続する配線が、前記第2の基板の第2のドメイン規制用構造物に沿って配置されていることを特徴とする請求項7に記載の液晶表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、液晶分子の配向方向が相互に異なる複数の領域（ドメイン）を有するMVA（Multi-domain Vertical Alignment）型液晶表示装置に関し、特に画素電極が複数の副画素電極に分割されている液晶表示装置に関する。

## 【背景技術】

## 【0002】

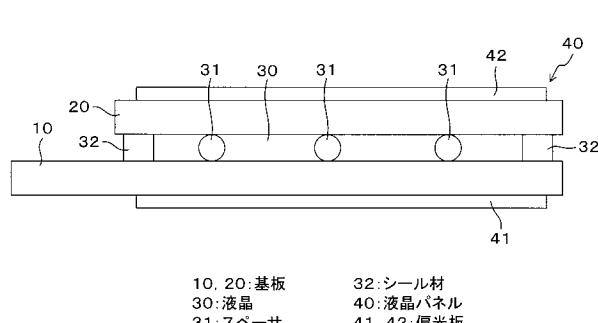

液晶表示装置は、CRT（Cathode Ray Tube）に比べて薄くて軽量であり、低電圧で駆動できて消費電力が小さいという利点がある。そのため、液晶表示装置は、テレビ、ノート型PC（パーソナルコンピュータ）、ディスクトップ型PC、PDA（携帯端末）及び携帯電話など、種々の電子機器に使用されている。特に、各画素（サブピクセル）毎にスイッチング素子としてTFT（Thin Film Transistor：薄膜トランジスタ）を設けたアクティブマトリクス型液晶表示装置は、その駆動能力の高さからCRTにも匹敵する優れた表示特性を示し、ディスクトップ型PCやテレビなど従来CRTが使用されていた分野にも広く使用されるようになった。

## 【0003】

一般的に、液晶表示装置は、図1に示すように、スペーサ31を挟んで配置されてシール材32により接合された2枚の透明基板10,20と、これらの基板10,20間に封入された液晶30とにより構成されている。一方の基板10には、画素毎に画素電極及びTFT等が形成され、他方の基板20には画素電極に対向するカラーフィルタと、各画素共通のコモン（共通）電極とが形成されている。カラーフィルタには赤色（R）、緑色（G）及び青色（B）の3種類があり、画素毎にいずれか1色のカラーフィルタが配置されている。隣接して配置された赤色（R）、緑色（G）及び青色（B）の3つの画素で1つのピクセル（Pixel）を構成する。

## 【0004】

以下、画素電極及びTFTが形成された基板をTFT基板と呼び、TFT基板に対向して配置される基板を対向基板と呼ぶ。また、TFT基板と対向基板との間に液晶を封入してなる構造物を液晶パネルという。

## 【0005】

TFT基板10は、接続端子の分だけ対向基板20よりも大きく形成されている。TFT基板10及び対向基板20により構成される液晶パネル40の両側には、それぞれ偏光板41,42が配置されている。また、液晶パネル40の下方にはバックライト（図示せず）が配置されている。

## 【0006】

従来は、2枚の基板10,20間に水平配向型液晶（誘電率異方性が正の液晶）を封入し、液晶分子をツイスト配向させるTN（Twisted Nematic）型液晶表示装置が広く使用されていた。しかし、TN型液晶表示装置には視野角特性が悪く、画面を斜め方向から見たときにコントラストや色調が大きく変化するという欠点がある。このため、視野角特性が良好なVA（Vertical Alignment）型液晶表示装置及びMVA（Multi-domain Vertical Alignment）型液晶表示装置が開発され、実用化されている。

## 【0007】

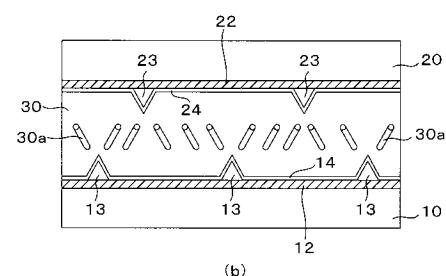

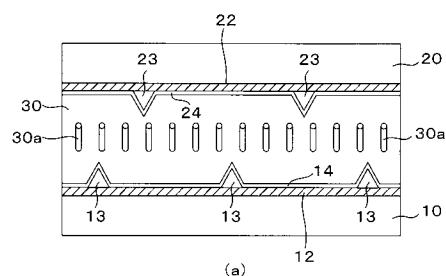

図2（a）,（b）は、MVA型液晶表示装置の一例を示す模式断面図である。TFT

10

20

30

40

50

基板 10 及び対向基板 20 はスペーサ ( 図示せず ) を挟んで配置されており、これらの基板 10, 20 の間には垂直配向型液晶 ( 誘電率異方性が負の液晶 ) 30 が封入されている。対向基板 10 の画素電極 12 の上には、ドメイン規制用構造物として複数の土手状の突起 13 が形成されている。画素電極 12 及び突起 13 の表面は、例えばポリイミドからなる垂直配向膜 14 に覆われている。

【 0 0 0 8 】

対向基板 20 のコモン電極 22 の下にも、ドメイン規制用構造物として複数の土手状の突起 23 が形成されている。これらの突起 23 は、基板 10 側の突起 13 に対し斜め方向にずれた位置に配置されている。コモン電極 22 及び突起 23 の表面も、例えばポリイミドからなる垂直配向膜 24 に覆われている。

10

【 0 0 0 9 】

MVA 型液晶表示装置においては、画素電極 12 とコモン電極 22 との間に電圧を印加しない状態では、図 2 ( a ) に示すように、殆どの液晶分子 30a は基板面に対し垂直に配向する。但し、突起 13, 23 の近傍の液晶分子 30a は、突起 13, 23 の傾斜面に垂直な方向に配向する。

【 0 0 1 0 】

画素電極 12 とコモン電極 22 との間に所定の電圧を印加すると、電界の影響により液晶分子 30a は基板面に対し斜めに配向する。この場合に、図 2 ( b ) に示すように、突起 13, 23 の両側では液晶分子 30a の傾斜方向が異なり、いわゆる配向分割 ( マルチドメイン ) が達成される。

20

【 0 0 1 1 】

この図 2 ( b ) に示すように、MVA 型液晶表示装置では電圧を印加したときの液晶分子 30a の傾斜方向が突起 13, 23 の両側で異なるので、斜め方向への光の漏れが抑制され、優れた視野角特性が得られる。

【 0 0 1 2 】

上記の例ではドメイン規制用構造物が突起の場合について説明したが、電極に設けたスリットや、基板表面の窪み ( 溝 ) をドメイン規制用構造物とすることもある。また、図 2 ( a ), ( b ) では TFT 基板 10 及び対向基板 20 の両方にドメイン規制用構造物を設けた例について説明したが、TFT 基板 10 及び対向基板 20 のうちのいずれか一方のみにドメイン規制用構造物を形成してもよい。

30

【 0 0 1 3 】

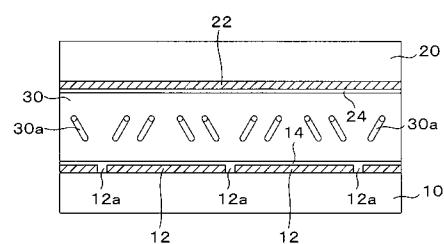

図 3 は、TFT 基板 10 側の画素電極 12 に、ドメイン規制用構造物としてスリット 12a を形成した例を示している。スリット 12a の縁部付近では電気力線が斜め方向に発生するので、スリット 12a の両側で液晶分子 30a の傾斜方向が異なる。これにより配向分割が達成され、視野角特性が向上する。

【 0 0 1 4 】

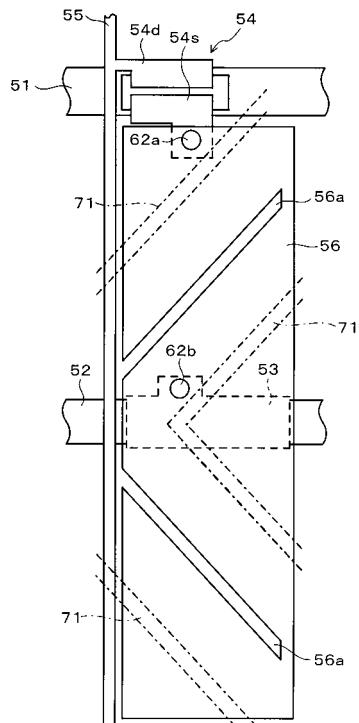

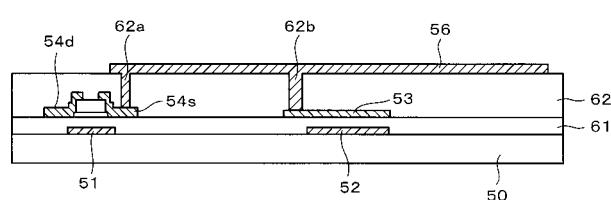

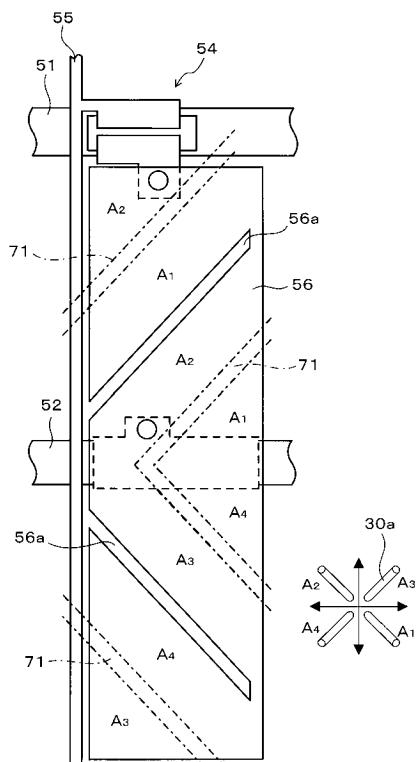

図 4 は実際の MVA 型液晶表示装置の 1 画素を示す平面図、図 5 は同じくその液晶表示装置の TFT 基板の模式断面図である。

【 0 0 1 5 】

TFT 基板 50 には、水平方向に延びる複数のゲートバスライン 51 と、垂直方向に延びる複数のデータバスライン 55 とがそれぞれ所定のピッチで配置されている。これらのゲートバスライン 51 及びデータバスライン 55 により区画される矩形の領域がそれぞれ画素領域である。また、TFT 基板 50 には、ゲートバスライン 51 と平行に配置されて画素領域の中央を横断する補助容量バスライン 52 が形成されている。ゲートバスライン 51 及び補助容量バスライン 52 とデータバスライン 55 との間には第 1 の絶縁膜 61 が形成されており、この第 1 の絶縁膜 61 によりゲートバスライン 51 とデータバスライン 55 及び補助容量バスライン 52 とデータバスライン 55 との間が電気的に分離されている。

40

【 0 0 1 6 】

各画素領域毎に、TFT 54 、画素電極 56 及び補助容量電極 53 が形成されている。

50

TFT54は、ゲートバスライン51の一部をゲート電極としている。また、TFT54のドレイン電極54dはデータバスライン55に接続しており、ソース電極54sはゲートバスライン51を挟んでドレイン電極54dに対向する位置に形成されている。更に、補助容量電極53は、第1の絶縁膜61を挟んで補助容量バスライン52に対向する位置に形成されている。

## 【0017】

補助容量電極53、TFT54及びデータバスライン55は第2の絶縁膜62に覆われており、画素電極56はこの第2の絶縁膜62の上に配置される。画素電極56はITO(Indium-Tin Oxide)等の透明導電体からなり、第2の絶縁膜62に形成されたコンタクトホール62a, 62bを介してTFT54のソース電極54s及び補助容量電極53に電気的に接続している。また、画素電極56には、斜め方向に延びる2本のスリット56aが上下対称に形成されている。この画素電極56の表面は、例えばポリイミドからなる垂直配向膜(図示せず)により覆われている。

## 【0018】

TFT基板50に対向して配置される対向基板には、ブラックマトリクス(遮光膜)、カラーフィルタ及びコモン電極が形成されている。コモン電極の上には、図4に一点鎖線で示すように、ゲートバスライン51及び補助容量バスライン52の上方で屈曲する複数の土手状の突起71が形成されている。画素電極56のスリット56aは、これらの突起71の列間に配置されている。

## 【0019】

このように形成された液晶表示装置において、画素電極56とコモン電極との間に所定の電圧を印加すると、図6に示すように、液晶分子30の配向方向が相互に異なる4つのドメインA1, A2, A3, A4が形成される。これらのドメインA1, A2, A3, A4は突起71及びスリット56aを境界としている。これらのドメインA1, A2, A3, A4の面積がほぼ等しくなるようにスリット56a及び突起71を形成すると、視野角特性の方向依存性が小さくなる。

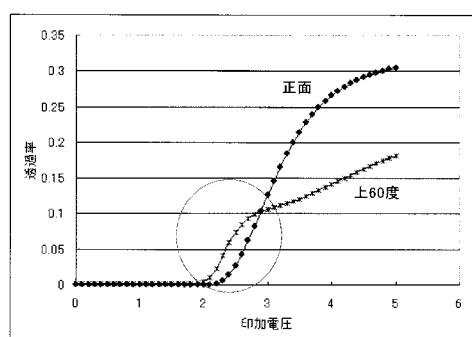

## 【0020】

ところで、従来のMVA型液晶表示装置では、画面を斜め方向から見たときに白っぽくなる現象が発生する。図7は、横軸に印加電圧(V)をとり、縦軸に透過率をとって、画面を正面から見たときのT-V(透過率-電圧)特性と上60°の方向から見たときのT-V特性とを示す図である。この図7に示すように、しきい値電圧よりも若干高い電圧を画素電極に印加したとき(図中丸で囲んだ部分)には、斜め方向から見たときの透過率が正面から見たときの透過率よりも高くなる。また、印加電圧がある程度高くなると、斜め方向から見たときの透過率は、正面から見たときの透過率よりも低くなる。このため、斜め方向から見たときには赤色画素、緑色画素及び青色画素の輝度差が小さくなり、その結果前述したように画面が白っぽくなる現象が発生する。この現象は、白茶け(discolor)と呼ばれている。白茶けは、MVA型液晶表示装置だけでなく、TN型液晶表示装置でも発生する。

## 【0021】

米国特許第4840460号の明細書には、1つの画素を複数の副画素に分割して、それらの副画素を容量結合することが提案されている。このような液晶表示装置では、各副画素の容量比によって電位が分割されるため、各副画素に相互に異なる電圧を印加することができる。従って、見かけ上、1つの画素にT-V特性のしきい値が異なる複数の領域が存在することになる。このように1つの画素にT-V特性のしきい値が異なる複数の領域が存在すると、図7に示すように正面から見たときの透過率よりも斜め方向から見たときの透過率が高くなる現象が抑制され、その結果画面が白っぽくなる現象(白茶け)も抑制される。このように1つの画素を容量結合した複数の副画素に分割して表示特性を改善する方法は、容量結合によるHT(ハーフトーングレースケール)法と呼ばれる。

## 【0022】

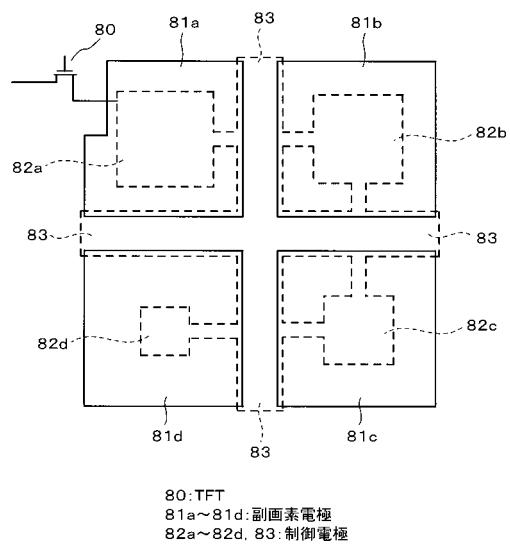

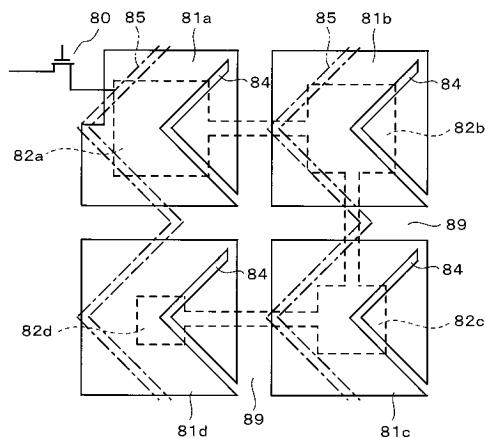

特許第3076938号の明細書(特開平5-66412号公報)には、図8に示すよ

10

20

30

40

50

うに、画素電極を複数（図8では4つ）の副画素電極81a～81dに分割し、各副画素電極81a～81dの下方に絶縁膜を介して制御電極82a～82dをそれぞれ配置した液晶表示装置が開示されている。この液晶表示装置では、制御電極82a～82dの大きさがそれぞれ異なっており、TFT80を介して制御電極82a～82dに表示電圧が印加されるようになっている。また、副画素電極81a～81dの間から光が漏れることを防止するために、副画素電極81a～81dの間にも制御電極83を配置している。

#### 【0023】

特許第3401049号の明細書（特開平6-332009号公報）にも、1つの画素を複数の副画素に分割した液晶表示装置が開示されている。この液晶表示装置では、例えば副画素毎にラビング処理条件を変化させて、副画素の表面の液晶分子のプレチルト角を相互に異なるものとしている。

#### 【0024】

これらの従来の技術は、いずれもTN型液晶表示装置に関するものである。

#### 【特許文献1】米国特許第4840460号の明細書

#### 【特許文献2】特許第3076938号の明細書（特開平5-66412号公報）

#### 【特許文献3】特許第3401049号の明細書（特開平6-332009号公報）

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0025】

ところで、容量結合によるHT法では、1つの画素を複数の副画素に分割することで副画素間に隙間が発生し、開口率が大きく減少する。一般的なノーマリー・ホワイトモードのTN型液晶表示装置では、副画素間の隙間は透過率が高い部分となる。従って、対向基板には、副画素間の隙間を遮光するブラックマトリクスを形成することが必要となる。しかしながら、TFT基板と対向基板との貼合せずれや斜め方向への光の漏れを防止することを考慮すると、ブラックマトリクスの幅を副画素間の隙間の幅よりも20μm程度（片側10μm程度）大きくする必要があり、開口率の著しい減少を招く。

#### 【0026】

特許第3076938号の明細書に記載されているように、副画素間の隙間にも制御電極を形成して透過率を制御することも可能ではある。しかし、この場合は制御電極及び副画素電極をいずれもITO等の透明導電体で形成することが必要であり、透明導電体膜の成膜工程及びフォトリソグラフィ工程がそれぞれ2回必要となって製造コストの上昇を招く。

#### 【0027】

特許第3401049号の明細書に記載された液晶表示装置では、例えば副画素毎にラビング処理条件を変えて副画素毎に液晶分子のプレチルト角を相互に異なるものとしている。しかしながら、ラビング処理により発生した塵が液晶に混入して表示品質を低下せることがあり、ラビング処理が不要であるというMVA型液晶表示装置の利点を失うことになる。

#### 【0028】

また、MVA型液晶表示装置では、配向分割を実現するために液晶分子のプレチルト角を約88～89°の極めて狭い範囲に安定して配向させることが必要である。例えば液晶分子のプレチルト角が86°以下になると電圧無印加時に光が透過してコントラストが低下し、プレチルト角が89.5°以上になると電圧を印加したときに液晶分子が所定の方向に倒れにくくなる。しかしながら、ラビング処理により液晶分子のプレチルト角を約88～89°の範囲で高精度に制御することは極めて困難である。また、垂直配向膜へのラビング処理後の液晶分子のプレチルト角は極めて安定性が悪く、水洗処理やその後の加熱処理で容易に変化してしまう。

#### 【0029】

以上から、本発明の目的は、白茶けを防止できて表示品質が良好であり、開口率が高く明るい表示が可能であるとともに、製造が容易な液晶表示装置を提供することにある。

## 【課題を解決するための手段】

## 【0030】

本願第1発明の液晶表示装置は、相互に対向して配置された第1基板及び第2の基板と、前記第1の基板及び前記第2の基板の間に封入された垂直配向型液晶と、前記第1の基板に設けられて走査信号が供給されるゲートバスラインと、前記第1の基板に設けられて表示信号が供給されるデータバスラインと、前記ゲートバスライン及び前記データバスラインにより画定される画素領域毎に形成されたスイッチング素子及び画素電極と、前記第1の基板の画素領域に設けられて前記スイッチング素子と接続された制御電極と、前記第2の基板に設けられたコモン電極とを有し、前記画素電極が複数の副画素電極に分割され、前記複数の副画素電極のうちの少なくとも一部の副画素電極が前記制御電極と容量結合し、前記制御電極に電圧が印加されると、前記制御電極に容量結合した副画素電極に、前記制御電極との間で形成される容量と前記液晶を介して前記コモン電極との間で形成される容量との比に応じた電圧が印加される。

## 【0031】

本発明の液晶表示装置は、垂直配向型液晶（誘電率異方性が負の液晶）を使用するVAモードの液晶表示装置（VA型液晶表示装置及びMVA型液晶表示装置）と容量結合構造とを組み合わせることで、単独では得られない高い性能を得ることができる。

## 【0032】

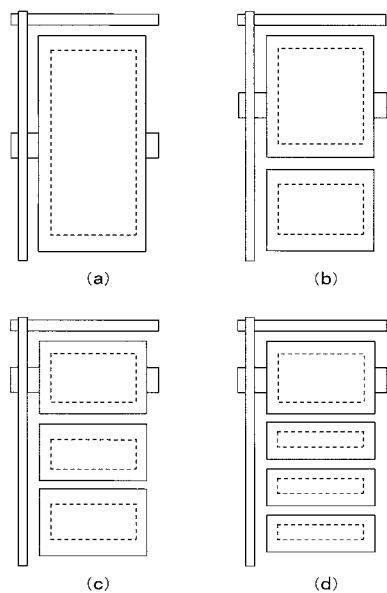

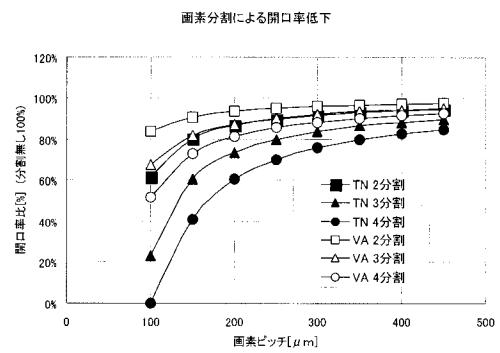

図9(a)は画素電極が分割されていない液晶表示装置の1画素を示す模式図、図9(b)は画素電極が2つに分割された液晶表示装置の1画素を示す模式図、図9(c)は画素電極が3つに分割された液晶表示装置の1画素を示す模式図、図9(d)は画素電極が4つに分割された液晶表示装置の1画素を示す模式図である。また、図10は、横軸に画素ピッチをとり、縦軸に開口率比をとって、TN型液晶表示装置及びVA型液晶表示装置における画素電極の分割数と画素ピッチ及び開口率比との関係を示す図である。なお、開口率比は、画素電極が分割されていない液晶表示装置の開口率と、画素電極が分割されている液晶表示装置の開口率との比を示している。

## 【0033】

TN型液晶表示装置では、画素電極の周囲の領域では光を透過するため、ブラックマトリクス（遮光膜）を形成する必要がある。通常、ブラックマトリクスは対向基板側に形成されるため、 TFT基板と対向基板との貼り合わせ精度が問題となる。そのため、貼り合せずれに対するマージンが設計上必須となる。つまり、図9(a)～(d)に破線で示すように、ブラックマトリクスを画素電極の内側まで形成することが必要となる。一般的に、貼り合せずれに対するマージンは5～7μmである。図10では、貼り合せずれに対するマージンを5μmとして開口率比を計算している。

## 【0034】

図10からわかるように、分割数が増えるにしたがって副画素電極間のギャップの影響及び貼り合せずれに対するマージンの影響が大きくなるが、n分割のときに副画素電極間のギャップは(n-1)箇所なのに対し、貼り合せずれに対するマージンは(n+1)×2箇所と多いために、開口率に大きな影響を与えてしまう。また、副画素電極間のギャップと貼り合せずれに対するマージンとは製造ラインの実力などを反映した固定値であるため、TN型液晶表示装置では画素ピッチが小さくなると開口率比が急激に低くなる。

## 【0035】

一方、VAモードの液晶表示装置の場合は、画素電極の周囲の領域は光を通さないため、遮光が不要である。従って、画素電極を分割しても、貼り合せずれに対するマージンは不要であり、開口率の低下が少ない。図10からわかるように、TN型液晶表示装置では画素ピッチが小さくなるにしたがって画素電極を分割したときの開口率は急激に低下する。また、分割数が多いほどその傾向は大きくなる。一方、VAモードの液晶表示装置では、画素ピッチが小さくなても、TN型液晶表示装置に比べて開口率の低下が少ない。

## 【0036】

しかも、後述するように、画素電極を分割するスリットを、MVA型液晶表示装置のド

メイン規制用構造物として使用することにより、開口率の低下を実質的にゼロとすることが可能である。すなわち、容量結合とMVA型液晶表示装置との組み合わせは相性が極めてよく、容量結合の輝度低下を最小限にしながら視野角特性を改善することができる。

【0037】

本願第2発明の液晶表示装置は、相互に対向して配置された第1の基板及び第2の基板と、前記第1の基板及び前記第2の基板の間に封入された液晶と、前記第1の基板に設けられて走査信号が供給されるゲートバスラインと、前記第1の基板に設けられて表示信号が供給されるデータバスラインと、前記ゲートバスライン及び前記データバスラインにより画定される画素領域内に配置され、スリットにより複数の副画素電極に分割された画素電極と、前記ゲートバスライン及び前記データバスラインに接続されたスイッチング素子と、前記スイッチング素子に接続されて前記複数の副画素電極の少なくとも1つと容量結合する制御電極と、前記第2の基板に設けられたコモン電極とを有しており、前記画素電極を分割するスリットの少なくとも一部が、電圧印加時の液晶分子の配向方向を規定するドメイン規制用構造物を構成する。

【0038】

すなわち、本発明においては、副画素電極を分離するスリットを用いて液晶分子の配向方向を規定するので、副画素電極を分離するスリットと液晶分子の配向方向を規定するスリットとを別個に設ける場合に比べて、配向が乱れる部分が少なく、明るい表示が可能になる。

【0039】

また、本発明においては、例えば複数の副画素電極の一部を制御電極と容量結合し、他の副画素電極をスイッチング素子と接続することにより、表示電圧を供給したときに、副画素電極の一部に印加される電圧と他の副画素電極に印加される電圧とが異なり、見かけ上、1画素内にT-V特性のしきい値が異なる複数の領域が存在することになる。これにより、斜め方向から見たときに画面が白っぽくなる現象（白茶け）が抑制され、表示品質が向上する。

【0040】

他の副画素電極をスイッチング素子に接続する替わりに、制御電極と容量結合させてもよい。この場合、副画素電極の大きさと制御電極との重なり量とを調整することにより、表示電圧供給時における副画素電極の電圧を制御することができる。

【0041】

液晶分子の配向方向をより確実に制御するために、第2の基板にもドメイン規制用構造物（第2のドメイン規制用構造物）を形成することが好ましい。この場合、スイッチング素子と制御電極との間を接続する配線を第2の基板のドメイン規制用構造物に沿って形成することにより、透過率の減少を抑制することができる。

【0042】

また、制御電極を補助容量バスラインの上に絶縁膜を介して形成すると、制御電極と補助容量バスラインとの間の容量により、スイッチング素子を介して供給された表示電圧をより確実に保持することができる上、平面的に同一領域で容量を形成できるため、開口率のロスがない。更に、制御電極と容量結合する副画素電極が複数ある場合に、一方の副画素電極に容量結合する部分と他方の副画素電極に容量結合する部分との間を、補助容量バスラインよりも狭い幅の配線で接続すると、制御電極とスリットとの交差部における透過率の減少を抑制することができる。

【0043】

また、スイッチング素子と制御電極との間を接続する配線の下方に補助容量バスラインと接続した導電パターンを形成することにより、配線とスリットとの交差部における透過率の減少を抑制することができる。更に、スリットの下方に補助容量バスラインと接続した導電パターンを形成することにより、スリットの部分における光の漏れをより確実に防止することができる。

【発明を実施するための最良の形態】

10

20

30

40

50

## 【0044】

以下に、本発明の実施形態を図面に基づいて説明する。

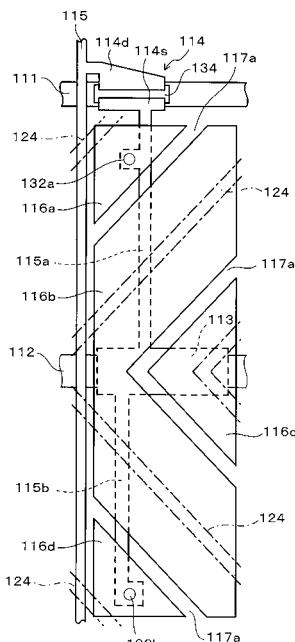

## 【0045】

(第1の実施形態)

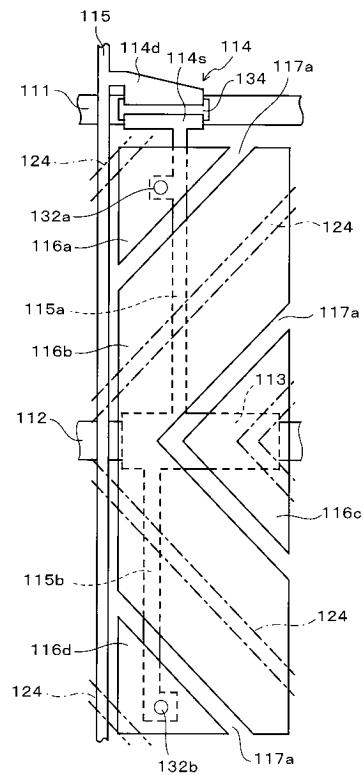

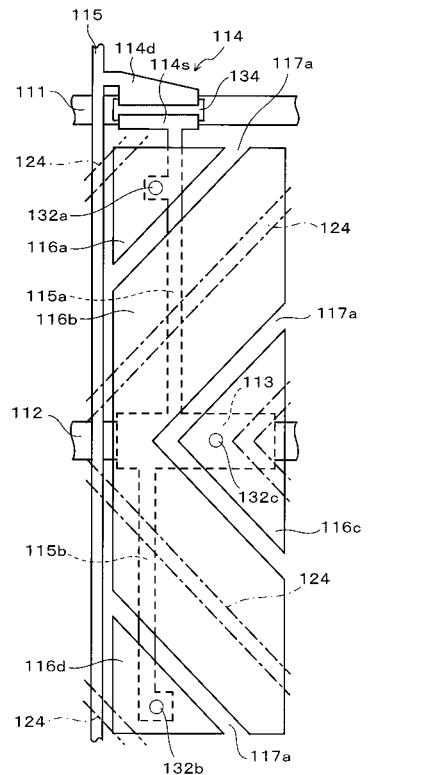

図11は本発明の第1の実施形態の液晶表示装置を示す平面図、図12は同じくその模式断面図である。

## 【0046】

本実施形態の液晶表示装置は、図12に示すように、ガラス板等の透明薄板からなる2枚の基板110, 120と、これらの基板110, 120間に封入された垂直配向型液晶(誘電率異方性が負の液晶)130により構成されている。基板110には、図11に示すように水平方向に延びる複数のゲートバスライン111と、垂直方向に延びる複数のデータバスライン115とが形成されている。ゲートバスライン111のピッチは例えば約300μm、データバスライン115のピッチは例えば約100μmである。ゲートバスライン111とデータバスライン115とにより区画される矩形の領域がそれぞれ画素領域である。

10

【0047】

基板110には、ゲートバスライン111と平行に配置されて画素領域の中央を横断する補助容量バスライン112が形成されている。ゲートバスライン111及び補助容量バスライン112とデータバスライン115との間には第1の絶縁膜131が形成されており、この第1の絶縁膜131によりゲートバスライン111とデータバスライン115との間、及び補助容量バスライン112とデータバスライン115との間が電気的に分離されている。

20

【0048】

基板110には各画素領域毎に、TFT114、制御電極113及び画素電極が形成されている。本実施形態においては、図11に示すように、画素電極が、斜め方向に延びる上下対称のスリット117aにより4つの副画素電極116a～116dに分割されている。

【0049】

TFT114は、ゲートバスライン111の一部をゲート電極としている。また、TFT114のドレイン電極114dはデータバスライン115に接続され、ソース電極114sはゲートバスライン111を挟んでドレイン電極114dに対向する位置に配置されている。

30

【0050】

制御電極113は、第1の絶縁膜131を挟んで補助容量バスライン112と対向する位置に配置されている。この制御電極113は、接続配線115aを介してTFT114のソース電極114sと接続されている。

【0051】

副画素電極116a～116dはITO等の透明導電体からなる。これらの副画素電極116a～116dを分離するスリット117aの幅は例えば10μmである。

【0052】

副画素電極116aは、コンタクトホール132aを介して接続配線115aと電気的に接続されており、副画素電極116dはコンタクトホール132bを介して制御電極113から延びる接続配線115bと電気的に接続されている。副画素電極116b, 116cは、それぞれ第2の絶縁膜132を介して制御電極113と容量結合している。これらの副画素電極116a～116dは、例えばポリイミドからなる垂直配向膜118に覆われている。

【0053】

一方、対向基板120の面上(図12では下側)には、ブラックマトリクス(遮光膜)121及びカラーフィルタ122が形成されている。ブラックマトリクス121は例えばCr(クロム)等の金属からなり、TFT基板110側のゲートバスライン111、補助

40

50

容量バスライン 112、データバスライン 115 及び TFT 114 に対向する位置に配置されている。

【0054】

カラーフィルタ 122 には赤色、緑色及び青色の 3 種類があり、各画素毎に赤色、緑色及び青色のいずれか一色のカラーフィルタが配置される。

【0055】

カラーフィルタ 122 の下側には、ITO 等の透明導電体からなるコモン電極（共通電極）123 が形成されている。このコモン電極 123 の下側にはドメイン規制用の土手状の突起 124 が形成されている。この突起 124 は、図 11 に示すように、ゲートバスライン 111 及び補助容量バスライン 112 の上で屈曲しており、TFT 基板 110 のスリット 117a に対し水平方向にずれた位置に配置される。コモン電極 123 及び突起 124 の表面は、例えばポリイミドからなる垂直配向膜 125 に覆われている。

【0056】

以下、上述のように構成された本実施形態の液晶表示装置の動作について説明する。

【0057】

データバスライン 115 に所定の表示電圧を供給し、ゲートバスライン 111 に走査信号を供給すると、TFT 114 がオンになってソース電極 145s に接続している副画素電極 116a, 116d 及び制御電極 113 に表示電圧が書き込まれる。また、副画素電極 116b, 116c は制御電極 113 と容量結合しているので、副画素電極 116b, 116c にも電圧が印加される。

【0058】

但し、本実施形態では、図 11 に示すように、副画素電極 116c が副画素電極 116b よりも面積が小さく、且つ制御電極 113 との重なり量が大きいので、副画素電極 116c の電圧のほうが副画素電極 116b の電圧よりも高くなる。副画素電極 116a の電圧を A、副画素電極 116b の電圧を B、副画素電極 116c の電圧を C、副画素電極 116d の電圧を D とすると、A = D > C > B となる。

【0059】

このようにして副画素電極 116a ~ 116d に電圧が印加されると、液晶分子は突起 124 及びスリット 117a の延びる方向に対し直角な方向に傾斜する。このとき、液晶分子の傾斜方向は突起 124 及びスリット 117a の両側で反対方向となる。本実施形態においても、図 4 に示す従来の液晶表示装置と同様に、液晶分子の配向方向が相互に異なる 4 つのドメインが形成される。

【0060】

ところで、ドメインの境界部分では液晶分子の乱れが生じるため、透過率が低くなる。また、画素電極をスリットにより複数の副画素電極に分割した場合、スリットの部分には電圧が印加されないため、スリット部分の透過率が低くなる。

【0061】

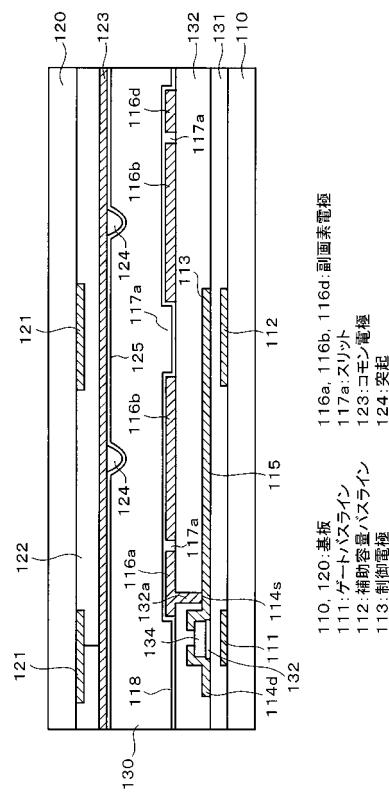

図 13 は、副画素電極 81a ~ 81d を分離するスリット 89 とは別に、ドメイン規制用構造物としてスリット 84 及び突起 85 を設けた MVA 型液晶表示装置の例を示す模式図である。この図 13 において、スリット 84 は副画素電極 81a ~ 81d にそれぞれ形成されており、突起 85 は対向基板側に形成されている。また、副画素電極 81a ~ 81d の下方には、TFT 80 と接続された制御電極 82a ~ 82d がそれぞれ形成されている。

【0062】

図 11, 図 12 に示す本実施形態の液晶表示装置では、各副画素電極 116a ~ 116d を分離するスリット 117a がドメイン規制用構造物として機能するので、図 13 に示すように副画素電極 81a ~ 81d を分離するスリット 89 と配向規制用スリット 84 を個別に形成する場合に比べて透過率の低下が少なく、明るい表示が可能となる。

【0063】

また、本実施形態においては、副画素電極 116a, 116d、副画素電極 116b 及

10

20

30

40

50

び副画素電極 116c にそれぞれ異なる電圧が印加されるので、見かけ上、1つの画素内に T-V 特性のしきい値が相互に異なる3つの領域が存在することになる。これにより、画面を斜め方向から見たときに画面が白っぽくなる現象（白茶け）が抑制され、良好な表示品質が得られる。

#### 【0064】

次に、本実施形態の液晶表示装置の製造方法について説明する。まず、TFT 基板の製造方法について、図 12 を参照して説明する。

#### 【0065】

まず、ガラス板等からなる基板 110 の上に、例えば PVD (Physical Vapor Deposition) 法により Cr (クロム) からなる金属膜、又は Al (アルミニウム) と Ti (チタン) との積層構造を有する金属膜を形成する。その後、この金属膜をフォトリソグラフィによりパターニングして、ゲートバスライン 111 及び補助容量バスライン 112 を形成する。なお、基板 110 からの不純物の拡散を防止するために、基板 110 の表面を絶縁膜で覆ってから金属膜を形成してもよい。

#### 【0066】

次に、基板 110 の上に、例えば CVD (Chemical Vapor Deposition) 法により酸化シリコン又は窒化シリコンを堆積させて、ゲートバスライン 111 及び補助容量バスライン 112 を覆う第 1 の絶縁膜 131 を形成する。

#### 【0067】

次に、第 1 の絶縁膜 131 の上に、例えば CVD 法により厚さが 20 ~ 100 nm のアモルファスシリコン膜（又はポリシリコン膜）と、窒化シリコン膜とを順次形成する。その後、フォトリソグラフィ法により窒化シリコン膜をパターニングすることにより、TFT 114 のチャネルを保護するチャネル保護膜 134 を形成する。

#### 【0068】

次に、基板 110 の上側全面に、不純物が高濃度に導入されたアモルファスシリコンからなるオーミックコンタクト層を形成し、その上に Ti - Al - Ti の積層構造を有する金属膜を形成する。そして、フォトリソグラフィ法により金属膜、オーミックコンタクト層及びアモルファスシリコン膜をパターニングして、TFT 114 の活性層となる半導体層 111 の形状を確定するとともに、データバスライン 115、ソース電極 114s、ドレイン電極 114d、制御電極 113 及び接続配線 115a, 115b を形成する。

#### 【0069】

次に、基板 110 の上側全面に、例えば CVD 法により窒化シリコンを堆積させて第 2 の絶縁膜 132 を形成する。そして、フォトリソグラフィ法により第 2 の絶縁膜 132 の所定位置に、接続配線 115a に通じるコンタクトホール 132a と、接続配線 115b に通じるコンタクトホール 132b とを形成する。

#### 【0070】

次いで、基板 110 の上側全面に、スパッタ法等により ITO 膜を形成する。この ITO 膜は、コンタクトホール 132a, 132b を介して接続配線 115a, 115b に電気的に接続される。その後、フォトリソグラフィ法により ITO 膜をパターニングして、副画素電極 116a ~ 116d を形成する。次に、副画素電極 116a ~ 116d の表面にポリイミドを塗布して垂直配向膜 118 を形成する。このようにして TFT 基板が完成する。

#### 【0071】

次に、対向基板の製造方法について、図 12 を参照して説明する。

#### 【0072】

まず、基板 120 の上に、例えば Cr 等の金属膜を形成し、この金属膜をパターニングして、TFT 基板 110 側のゲートバスライン 111、補助容量バスライン 112、データバスライン 115 及び TFT 114 に対向する位置にブラックマトリクス 121 を形成する。

#### 【0073】

10

20

30

40

50

次に、基板 120 の上に、例えば赤色感光樹脂、緑色感光樹脂及び青色感光樹脂を使用して、赤色、緑色及び青色のカラーフィルタ 122 を形成する。各画素毎に赤色、緑色及び青色のいずれか 1 色のカラーフィルタが配置されるようにする。

【0074】

次に、カラーフィルタ 122 の上に ITO 膜をスパッタ法により形成してコモン電極 123 を形成する。そして、例えばフォトトレジストを使用して、コモン電極 123 の上に誘電体からなる土手状の突起 124 を形成する。

【0075】

次いで、コモン電極 123 及び突起 124 の表面にポリイミドを塗布して、垂直配向膜 125 を形成する。このようにして対向基板が完成する。

10

【0076】

このようにして形成した TFT 基板と対向基板とを、スペーサを挟んで貼合わせ、TFT 基板と対向基板との間に垂直配向型液晶（誘電率異方性が負の液晶）を封入する。このようにして、本実施形態の液晶表示装置が完成する。

【0077】

本実施形態の液晶表示装置は、上述したように、制御電極 113 及び接続配線 115a, 115b をデータバスライン 115、ソース電極 114s 及びドレイン電極 114d と同時に形成することができるので、従来に比べて製造工程が増加することなく、製造が容易である。

【0078】

（第 2 の実施形態）

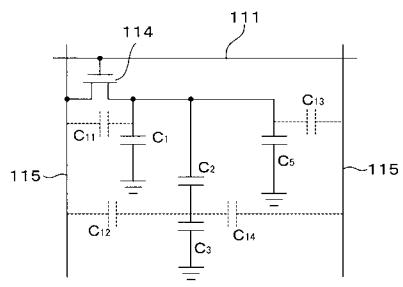

図 14 は、本発明の第 2 の実施形態の液晶表示装置の 1 画素を示す平面図である。図 14 において、図 11 と同一物には同一符号を付してその詳しい説明は省略する。

20

【0079】

本実施形態においては、図 14 に示すように、制御電極 113 と副画素電極 116c とが、第 2 の絶縁膜に形成されたコンタクトホール 132c を介して電気的に接続されている。従って、TFT 114 を介して表示電圧が供給されたときの副画素電極 116a の電圧を A、副画素電極 116b の電圧を B、副画素電極 116c の電圧を C、副画素電極 116d の電圧を D とすると、A = C = D > B となる。

30

【0080】

図 11 に示す第 1 の実施形態では、表示電圧として十分に高い電圧が印加されたときには、副画素電極 116a ~ 116d により規定される各副画素領域で液晶分子がそれぞれ所定の方向に配向し、液晶分子の配向方向が相互に異なる 4 つの領域（4 ドメイン）が形成されて、良好な視野角特性が得られる。しかし、表示信号の電圧（表示電圧）が低い場合、例えば画素電極 116a, 116b には T-V 特性のしきい値よりも若干高い電圧が印加され、画素電極 116b, 116c には T-V 特性のしきい値電圧よりも低い電圧しか印加されないときには、液晶分子の配向方向が 2 つ（2 ドメイン）となって、視野角特性が悪くなることが考えられる。

【0081】

一方、本実施の形態では、副画素電極 116c には副画素電極 116a, 116d と同じ電圧が印加されるので、表示電圧が低い場合であっても液晶分子の配向方向が相互に異なる 4 つの領域（4 ドメイン）が形成され、第 1 の実施形態に比べて、輝度が低いときの視野角特性の劣化が回避される。

40

【0082】

また、図 11 に示す第 1 の実施形態では、副画素電極 116a, 116c, 116d とデータバスライン 115 との間の寄生容量により副画素電極 116a, 116c, 116d の電圧が変化するという欠点があるのに対し、本実施形態ではそのような欠点が解消されるという利点がある。以下にその理由を説明する。

【0083】

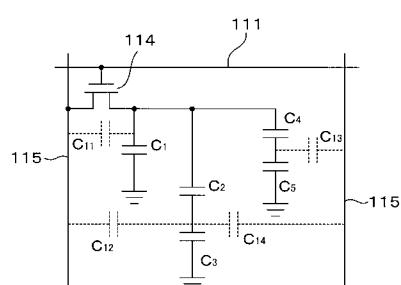

図 15 は、第 1 の実施形態の液晶表示装置の画素部の等価回路図である。この図 15 に

50

において、 $C_1$  は副画素電極 116a, 116d とコモン電極とにより構成される容量、 $C_2$  は制御電極 113 と副画素電極 116b とにより構成される容量、 $C_3$  は副画素電極 116b とコモン電極とにより構成される容量、 $C_4$  は制御電極 113 と副画素電極 116c とにより構成される容量、 $C_5$  は副画素電極 116c とコモン電極とにより構成される容量を示している。また、 $C_{11}$  は左側のデータバスライン 115 と副画素電極 116a, 116d との間の寄生容量、 $C_{12}$  は左側のデータバスライン 115 と副画素電極 116b との間の寄生容量、 $C_{13}$  は右側のデータバスライン 115 と副画素電極 116c との間の寄生容量、 $C_{14}$  は右側のデータバスライン 115 と副画素電極 116b との間の寄生容量を示している。

## 【0084】

10

第 1 の実施形態の液晶表示装置では、副画素電極 116a, 116d の左側の辺が右側のデータバスライン 115 に対向しており、副画素電極 116a, 116d と右側のデータバスライン 115 との間に寄生容量  $C_{11}$  が発生する。また、副画素電極 116c の右側の辺が左側のデータバスライン 115 に対向しており、副画素電極 116c と左側のデータバスライン 115 との間に寄生容量  $C_{13}$  が発生する。

## 【0085】

一般に、液晶表示装置では奇数番目のデータバスラインに供給する表示電圧の極性と偶数番目のデータバスラインに供給する表示電圧の極性とを逆にしている。また、1フレーム毎に各データバスラインに供給する表示電圧の極性を逆にしている。このようにして液晶表示装置を駆動した場合、第 1 の実施形態の液晶表示装置では、データバスライン 115 に供給された表示電圧が寄生容量  $C_{11}$ ,  $C_{13}$  を介して副画素電極 116a, 116c, 116d の電圧に影響を与え、副画素電極 116a, 116d, 116c の電圧が変化してしまう。

20

## 【0086】

なお、副画素電極 116c は、左側のデータバスライン 115 に対向する辺の長さと右側のデータバスライン 115 に対向する辺の長さがほぼ等しいため、左側のデータバスライン 115 と右側のデータバスライン 115 とに相互に逆極性の表示電圧を印加した場合、左側のデータバスライン 115 の影響による電圧の変化が右側のデータバスラインの影響による電圧の変化によって相殺される。従って、副画素電極 116c の電圧は殆ど変化しない。

30

## 【0087】

図 16 は、第 2 の実施形態の液晶表示装置の画素部の等価回路図である。この図 16 において、 $C_1$  は副画素電極 116a, 116d とコモン電極とにより構成される容量、 $C_2$  は制御電極 113 と副画素電極 116b とにより構成される容量、 $C_3$  は副画素電極 116b とコモン電極とにより構成される容量、 $C_5$  は副画素電極 116c とコモン電極とにより構成される容量を示している。また、 $C_{11}$  は左側のデータバスライン 115 と副画素電極 116a, 116d との間の寄生容量、 $C_{12}$  は左側のデータバスライン 115 と副画素電極 116b との間の寄生容量、 $C_{13}$  は右側のデータバスライン 115 と副画素電極 116c との間の寄生容量、 $C_{14}$  は右側のデータバスライン 115 と副画素電極 116b との間の寄生容量を示している。

40

## 【0088】

この図 16 に示すように、本実施形態では副画素電極 116a, 116c, 116d が電気的に接続されており、図 14 に示すように、左側のデータバスラインに対向する副画素電極 116a, 116d の右側の辺の長さと、右側のデータバスラインに対向する副画素電極 116c の左側の辺の長さとがほぼ等しい。このため、左側のデータバスラインと右側のデータバスラインとに相互に逆極性の表示電圧を印加した場合、左側のデータバスラインの影響による副画素電極 116a, 116c, 116d の電圧の変化が右側のデータバスラインの影響による副画素電極 116a, 116c, 116d の電圧の変化によって相殺され、その結果、副画素電極 116a, 116c, 116d の電圧は殆ど変化しない。これにより、本実施形態の液晶表示装置は、第 1 の実施形態と同様の効果を得ること

50

ができるのに加えて、第1の実施形態に比べてより一層良好な表示品質が得られるという効果を奏する。

【0089】

なお、本実施形態において、TFT114に接続された副画素電極116a, 116c, 116dの面積の総和（低しきい値領域の面積）をS1、これらの副画素電極116a, 116c, 116dに印加される電圧をV1とし、制御電極113に容量結合した副画素電極116bの面積（高しきい値領域の面積）をS2、副画素電極116bに印加される電圧をV2としたときに、例えばS1:S2を、1:9~6:4の範囲内とし、V2/V1を0.8~0.59の範囲内とすることが好ましい。例えば、S1:S2=4:6とし、V2/V1=0.72とする。

10

【0090】

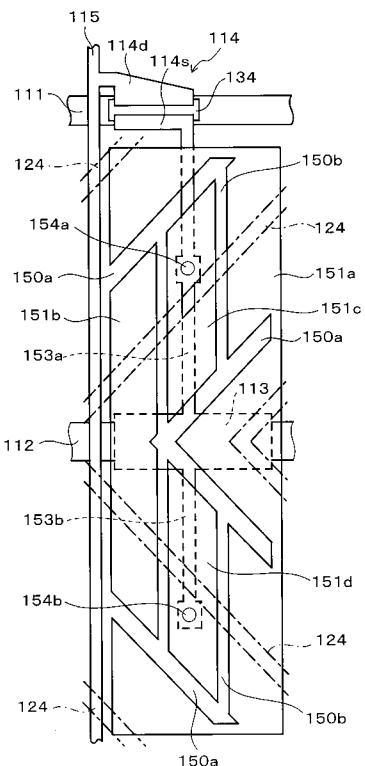

（第3の実施形態）

図17は、本発明の第3の実施形態の液晶表示装置の1画素を示す平面図である。本実施形態が第1の実施形態と異なる点は、スリットにより画定される副画素電極の形状が異なることになり、その他の構成は基本的に第1の実施形態と同様であるので、図17において図11と同一物には同一符号を付してその詳しい説明は省略する。

【0091】

本実施形態においては、図17に示すように、画素電極が、斜め方向に延在するスリット150aと垂直方向に延在するスリット150bとにより4つの副画素電極151a, 151b, 151c, 151dに分割されている。副画素電極151aは上下対称形であり、電圧印加時に液晶分子の配向方向が相互に異なる4つの領域（4ドメイン）が形成されるように、且つそれらの領域がほぼ同じ大きさとなるように、形状及び突起124に対する位置が決められている。また、副画素電極151aは、第2の絶縁膜を介して制御電極113と容量結合している。

20

【0092】

副画素電極151bも上下対称形に形成されており、電圧印加時に液晶分子の配向方向が相互に異なる4つの領域（4ドメイン）が形成されるように、且つそれらの領域がほぼ同じ大きさとなるように、形状及び突起124に対する位置が決められている。また、副画素電極151bも、第2の絶縁膜を介して制御電極113と容量結合している。但し、本実施形態においては、制御電極113に電圧が印加されたときに、副画素電極151bの電圧のほうが副画素電極151aの電圧よりも高くなるように、副画素電極151a, 151bの大きさ及び制御電極113との重なり量が設定されている。

30

【0093】

副画素電極151c, 151dは、補助容量バスライン112を挟んで上下対称に配置されている。これらの副画素電極151c, 151dの下方にはTFT114のソース電極114s及び制御電極113に接続した接続配線153a, 153bが形成されている。副画素電極151cはコンタクトホール154aを介して接続配線153aに接続され、副画素電極151dはコンタクトホール154bを介して接続配線153bに接続されている。これらの副画素電極151c, 151dも、電圧印加時に液晶分子の配向方向が相互に異なる4つの領域（副画素電極151c, 151dにそれぞれ2つの領域）となるように、且つそれらの領域がほぼ同じ大きさとなるように、形状及び突起124に対する位置が決められている。

40

【0094】

本実施形態の液晶表示装置は、図14に示す第2の実施形態の液晶表示装置に比べて以下に示す利点がある。すなわち、第2の実施形態では、表示電圧が供給されたときに、4つの副画素電極116a~116dのうちの3つ（副画素電極116a, 116c, 116d）の電圧が同一となる。そのため、第2の実施形態の液晶表示装置では1画素内にT-V特性のしきい値が相互に異なる領域が2つしか存在しないことになり、第1の実施形態に比べて白茶けを抑制する効果が小さくなる。一方、本実施の形態では、表示電圧が供給されたときに、副画素電極151aの電圧と、副画素電極151bの電圧と、副画素電

50

極 151c, 151d の電圧とが相互に異なる。すなわち、本実施形態においては、1画素内に T-V 特性のしきい値が相互に異なる 3 つの領域が存在することになる。従って本実施形態の液晶表示装置は、第 1 の実施形態と同様に白茶けを抑制する効果が大きい。

#### 【0095】

また、本実施形態では、副画素電極 151a、副画素電極 151b 及び副画素電極 151c, 151d のそれぞれにおいて、電圧印加時の液晶分子の配向方向が相互に異なる 4 つの領域が形成されるように副画素電極 151a ~ 151d の形状及び突起 124 に対する位置が決められているので、表示電圧が低くても第 1 の実施形態のように視野角特性が劣化することがない。

#### 【0096】

なお、本実施形態においては、副画素電極 151c, 151d の面積の総和（低しきい値領域の面積）を S1、副画素電極 151b の面積（中しきい値領域の面積）を S2、副画素電極 151a の面積（高しきい値領域の面積）を S3 としたときに、これらの面積比を例えば、S1 : S2 : S3 = 1 : 2 : 7 又は 2 : 2 : 6 等に設定することが好ましい。

#### 【0097】

##### （第 4 の実施形態）

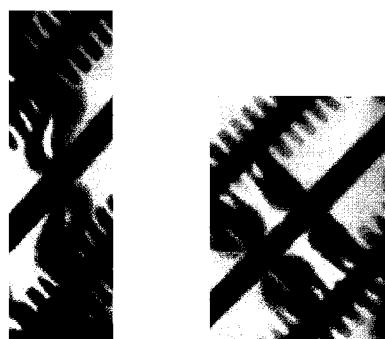

図 18 は、本発明の第 4 の実施形態の液晶表示装置の 1 画素を示す平面図である。本実施形態が図 17 に示す第 3 の実施形態と異なる点は、スリットにより画定される副画素電極の形状が異なることにあり、その他の構成は基本的に第 3 の実施形態と同様であるので、図 18 において図 17 と同一物には同一符号を付してその詳しい説明は省略する。

#### 【0098】

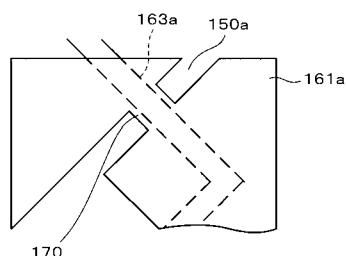

本実施形態においては、図 18 に示すように、斜め方向に延在するスリット 150a, 150c により画素電極が 4 つの副画素電極 161a, 161b, 161c, 161d に分割されている。副画素電極 161a 及び副画素電極 161b はいずれも上下対称形であり、電圧印加時に液晶分子の配向方向が相互に異なる 4 つの領域（4 ドメイン）が形成されるように、且つこれらの領域がほぼ同じ大きさとなるように、形状及び突起 124 に対する位置が決められている。また、これらの副画素電極 161a, 161b は、第 2 の絶縁膜を介して制御電極 113 と容量結合している。

#### 【0099】

副画素電極 161c, 161d は、補助容量バスライン 112 を挟んで上下対称に配置されている。これらの副画素電極 161c, 161d の下方には TFT114 のソース電極 114s 及び制御電極 113 に接続した接続配線 153a, 153b が形成されている。副画素電極 161c はコンタクトホール 154a を介して接続配線 153a に接続され、副画素電極 161d はコンタクトホール 154b を介して接続配線 153b に接続されている。これらの副画素電極 161c, 161d も、電圧印加時に液晶分子の配向方向が相互に異なる 4 つの領域（副画素電極 161c, 161d にそれぞれ 2 つの領域）が形成されるように、且つこれらの領域がほぼ同じ大きさとなるように、形状及び突起 124 に対する位置が決められている。

#### 【0100】

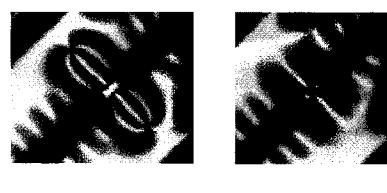

本実施形態は、図 17 に示す第 3 の実施形態の液晶表示装置に比べて以下に示す利点がある。すなわち、第 3 の実施形態の液晶表示装置では、スリット 150b がドメイン規制用構造物であるスリット 150a 及び突起 124 に対しほぼ 45° の角度で交差している。このようなスリットがあると液晶分子の配向の乱れが生じ、図 19 (a) の光の透過図に示すように透過率が低い部分が発生する。

#### 【0101】

一方、本実施形態では、ドメイン規制用構造物であるスリット 150a 及び突起 124 に対しほぼ 45° の角度に交差するスリットをなくし、スリット 150a に対しほぼ垂直にスリット 150c を形成している。この場合、図 19 (b) の光の透過図に示すように、液晶分子の乱れが小さくなつて透過率の減少が抑制される。これにより、本実施形態の液晶表示装置は、第 3 の実施形態と同様の効果が得られるのに加えて、第 3 の実施形態の

10

20

30

40

50

液晶表示装置に比べてより一層明るい表示が可能になるという効果を奏する。

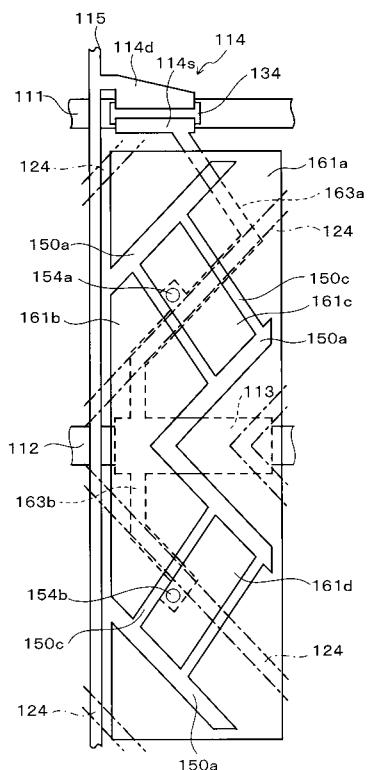

【0102】

(第5の実施形態)

図20は、本発明の第5の実施形態の液晶表示装置の1画素を示す平面図である。本実施形態が図18に示す第4の実施形態と異なる点は、接続配線のパターン形状が異なることにあり、その他の構成は基本的に第4の実施形態と同様であるので、図20において図18と同一物には同一符号を付して、その詳しい説明は省略する。

【0103】

接続配線163aは、ソース電極114sから突起124に向って斜め方向(突起124に対しほぼ垂直な方向)に延びる部分と、突起124に沿って延びる部分と、制御電極113に向ってデータバスライン115と平行に延びる部分とにより構成されている。そして、接続配線163aは、突起124に沿って延びる部分でコンタクトホール154aを介して副画素電極161cに電気的に接続している。また、接続配線163bは、制御電極113から突起124に向ってデータバスライン115と平行に延びる部分と、突起124に沿って延びる部分とにより構成されている。そして、突起124に沿って延びる部分の先端でコンタクトホール154bを介して副画素電極161dと電気的に接続している。

【0104】

図18に示す第4の実施形態の液晶表示装置では、スリット150a, 150bから接続配線153a, 153bが露出する部分で、接続配線153a, 153bから発生する電気力線の影響により液晶分子の配向の乱れが発生して、透過率の低い部分が発生する。

【0105】

一方、本実施形態においては、上述したように接続配線163a, 163bを突起124に沿って配置している。突起124はドメインの境界となり、もともと透過率が低い部分である。従って、図20に示すように、接続配線163a, 163bを突起124に沿って配置することにより、接続配線163a, 163bがスリット150cから露出する部分での透過率の低下が回避される。これにより、本実施形態の液晶表示装置は、第4の実施形態と同様の効果を得ることができるように加えて、第4の実施形態に比べてより一層明るい表示が可能になるという効果を奏する。

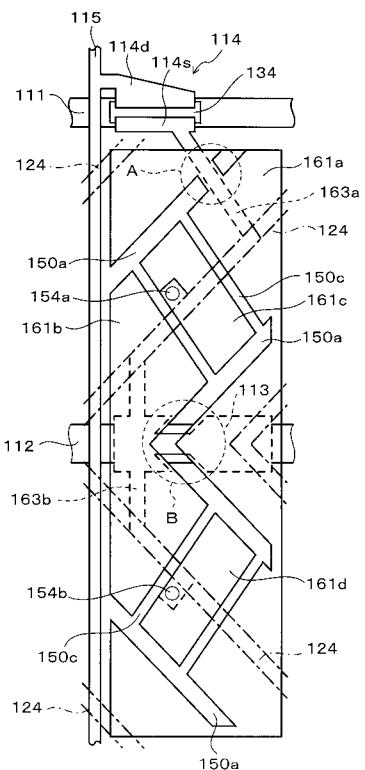

【0106】

(第6の実施形態)

図21は本発明の第6の実施形態の液晶表示装置の1画素を示す平面図、図22は図21中に破線の円Aで囲んだ部分を拡大して示す模式図、図23は図21中に破線の円Bで囲んだ部分を拡大して示す模式図である。なお、図21において、図20と同一物には同一符号を付して、その詳しい説明は省略する。

【0107】

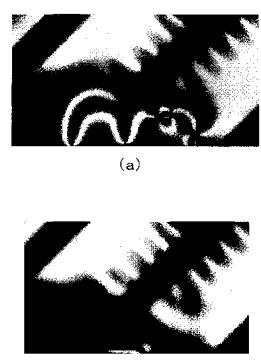

本実施形態においては、図22に示すように、スリット150aと接続配線163aとが交差する部分に、接続配線163aを覆うITO膜170が形成されている。このITO膜170は副画素電極161aの一部を構成するものである。このように、接続配線163aの露出部をITO膜170で覆うことにより、接続配線163aから発生する電気力線を遮蔽して液晶分子の乱れを防止することができる。図24(a)に第5の実施形態の液晶表示装置(ITO膜170がないとき)のスリット150aと接続配線163aとの交差部の光の透過図を示し、図24(b)に本実施形態(ITO膜170があるとき)のスリット150aと接続配線163aとの交差部の光の透過図を示す。この図24(a), (b)から、本実施形態では第5の実施形態に比べて、スリット150aと接続配線163aとの交差部の光の透過率が向上することがわかる。

【0108】

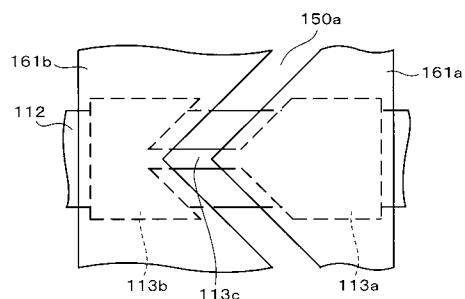

また、本実施形態では、図23に示すように、副画素電極161aと容量結合する制御電極113aと、副画素電極161bと容量結合する制御電極113bとの間を補助容量バスライン112よりも細い配線113cにより接続している。図20に示すような制御

10

20

30

40

50

電極 113 では、スリット 150a から制御電極 113 が露出しているため、制御電極 113 から発生する電気力線が液晶分子の配向を乱し、図 25 (a) の光の透過図に示すように、透過率が減少してしまう。

【0109】

一方、本実施形態では、制御電極 113a, 113b を接続する配線 113c のエッジが補助容量バスライン 112 の上に配置されている。補助容量バスライン 112 は、通常接地電位に保持されるので、配線 113c から発生する電気力線が補助容量バスライン 112 に吸収され、液晶分子の配向の乱れが抑制される。図 25 (b) に、本実施形態における制御電極 113 とスリット 150a との交差部の光の透過図を示す。この図 25 (a), (b) から、本実施形態では第 5 の実施形態に比べて制御電極 113 の近傍の光の透過率が向上することがわかる。

【0110】

(第 7 の実施形態)

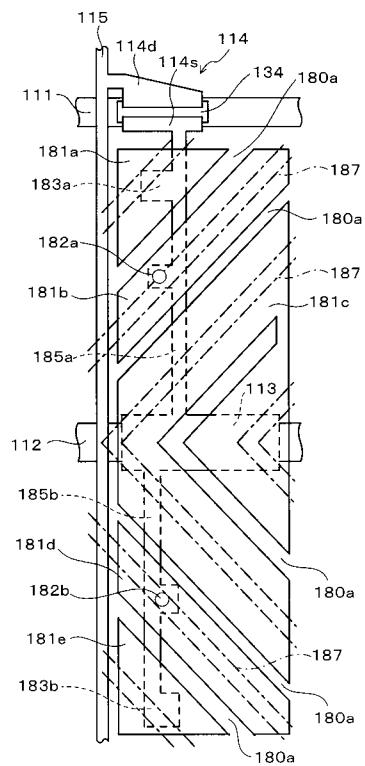

図 26 は本発明の第 7 の実施形態の液晶表示装置の 1 画素を示す平面図である。本実施形態が図 11 に示す第 1 の実施形態と異なる点は、スリットにより画定される副画素電極の形状と対向基板側に形成される突起のパターン形状とが異なることにあり、その他の構成は基本的に第 1 の実施形態と同様であるので、図 26 において図 11 と同一物には同一符号を付してその詳しい説明は省略する。

【0111】

本実施形態においては、画素電極が、斜め方向に延びるスリット 180a により、5 つの副画素電極 181a ~ 181e に分割されている。副画素電極 181a, 181e は、補助容量バスライン 112 を挟んで上下対称に配置されている。副画素電極 181a の下方には第 2 の絶縁膜を介して矩形の制御電極 183a が形成されており、副画素電極 181a は制御電極 183a と容量結合している。この制御電極 183a は、ソース電極 114s から制御電極 113 まで延びる接続配線 185a と電気的に接続されている。

【0112】

また、副画素電極 181e の下方には第 2 の絶縁膜を介して矩形の制御電極 183b が形成されており、副画素電極 181e は制御電極 183b と容量結合している。この制御電極 183b は、制御電極 113 から延びる接続配線 185b と電気的に接続されている。これらの副画素電極 181a, 181e は、電圧印加時に液晶分子の配向方向が相互に異なる 4 つの領域 (副画素電極 181a, 181e にそれぞれ 2 つの領域) が形成されるように、且つこれらの領域がほぼ同じ大きさとなるように、形状及び突起 187 の位置が決められている。

【0113】

副画素電極 181b, 181d も、補助容量バスライン 112 を挟んで上下対称に配置されている。副画素電極 181b は、コンタクトホール 182b を介して接続配線 185a と電気的に接続されている。また、副画素電極 181d は、コンタクトホール 182c を介して接続配線 185b と電気的に接続されている。これらの副画素電極 181, 181d も、電圧印加時に液晶分子の配向方向が相互に異なる 4 つの領域 (副画素電極 181b, 181d にそれぞれ 2 つの領域) が形成されるように、且つこれらの領域がほぼ同じ大きさとなるように、形状及び突起 187 の位置が決められている。

【0114】

副画素電極 181c は制御電極 113 と容量結合している。この副画素電極 181c も、電圧印加時に液晶分子の配向方向が相互に異なる 4 つの領域が形成されるように、且つこれらの領域がほぼ同じ大きさとなるように、形状及び突起 187 の位置が決められている。

【0115】

本実施形態において、表示電圧を供給したときの副画素電極 181a の電圧を A、副画素電極 181b の電圧を B、副画素電極 181c の電圧を C、副画素電極 181d の電圧を D、副画素電極 181e の電圧を E とすると、 $B = D > A = E > C$  となる。

10

20

30

40

50

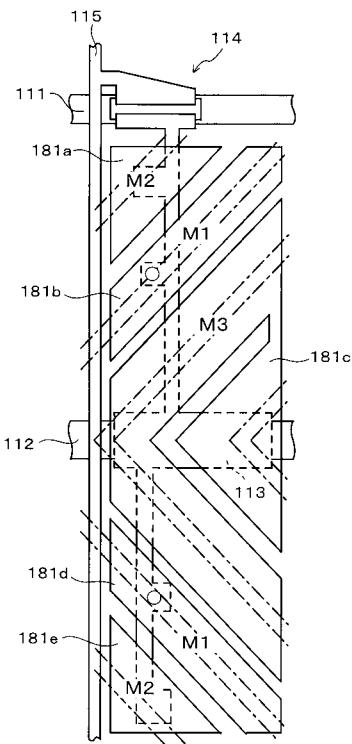

## 【0116】

本実施形態においては、T-V特性のしきい値が異なる3つの領域の面積比を容易に最適化することができる。例えば図27に示すように、副画素電極181bと副画素電極181dとの合計の面積をM1、副画素電極181aと副画素電極181eとの合計の面積をM2、副画素電極181cの面積をM3とする。ある大きさの液晶表示装置では、これらの面積比M1:M2:M3が1:2:7(M1:M2:M3=1:2:7)のときに白茶けが最も少なくなることが実験から判明している。この場合、突起187の幅を10μm、スリット180aの幅を10μmとし、突起とスリットの間隔を、副画素電極181b, 181dでは3μm、副画素電極181a, 181eでは7μm、副画素電極181cでは25μmとすると、面積比M1:M2:M3が概ね1:2:7となる。このように、本実施形態では、突起187とスリット180aとの間隔を設定するだけで、副画素電極181a~181eの面積比を容易に所望の値とすることができます。10

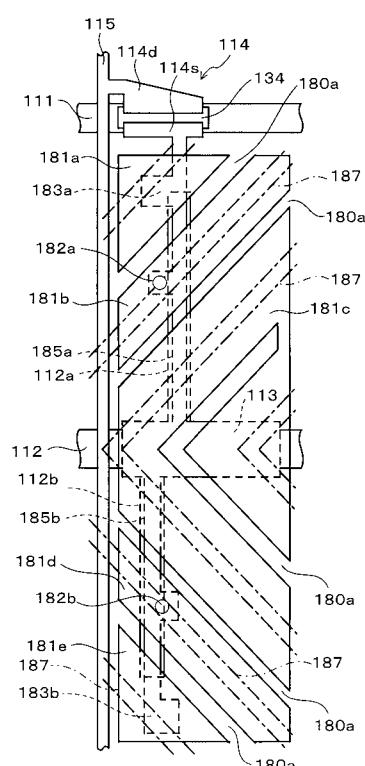

## 【0117】

図28は第7の実施形態の変形例1の液晶表示装置の1画素を示す平面図である。この変形例1においては、接続配線185a, 185bの下方に、補助容量バスライン112から延びる導電パターン112a, 112bを設けている。この導電パターン112a, 112bにより接続配線112a, 112bから発生する電気力線が吸収され、スリット180aから接続配線112a, 112bが露出する部分での液晶分子の配向の乱れを抑制することができる。

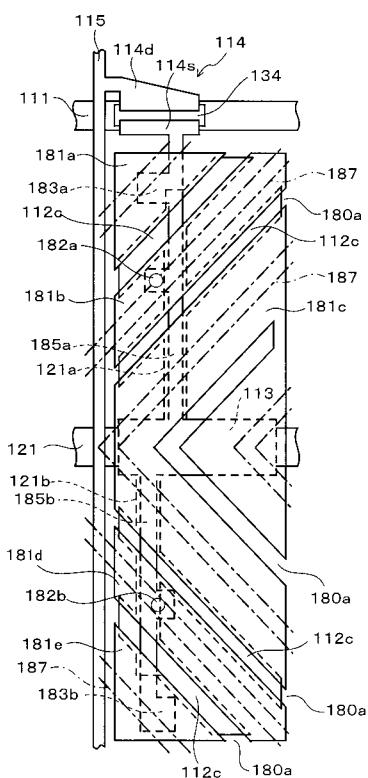

## 【0118】

図29は第7の実施形態の変形例2の液晶表示装置の1画素を示す平面図である。この変形例2においては、更にスリット180aの下方に、補助容量バスライン112と接続した導電パターン112cを形成している。この導電パターン112cによりスリット180aの下方の部分が接地電位に保持されるので、スリット180aの部分での光の透過をより確実に防止することができる。20

## 【0119】

## (その他の実施形態)

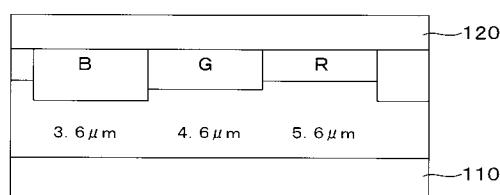

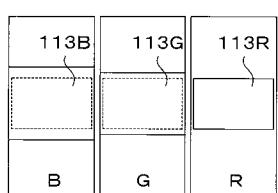

図30に示すように、赤色(R)画素、緑色(G)画素及び青色(B)画素のセルギャップが相互に異なるマルチギャップ構造の液晶表示装置では、画素電極とコモン電極との間の容量(液晶容量)が各色画素毎に異なる。例えば図30に示すように、青色画素Bのセルギャップが3.6μm、緑色画素Gのセルギャップが4.6μm、赤色画素Rのセルギャップが5.6μmであるとすると、青色画素Bの液晶容量は緑色画素Gの液晶容量の(4.6/3.6)倍となる。第1~第7の実施形態に示したように、容量結合による電圧降下を赤色画素、緑色画素及び青色画素で等しくするためには、液晶容量と制御電極との容量比が一定であることが必要である。従って、制御電極と副画素電極の重なり量をセルギャップの逆比にすることが必要である。すなわち、図31に示すように、緑色画素Gの制御電極113Gの面積を赤色画素Rの制御電極113Rの(5.6/4.6)倍とする。また、青色画素Bの制御電極113Bを緑色画素Gの制御電極113Gの(4.6/3.6)倍とする。30

## 【0120】

このように赤色画素R、緑色画素G及び青色画素Bで制御電極の大きさを変えることにより、容量結合による電圧降下が等しくなり、良好な表示品質が得られる。なお、制御電極の面積を変える替わりに、制御電極と副画素電極との間の絶縁膜の厚さを各色画素毎に変化させてもよい。しかしながら、制御電極と副画素電極との間の絶縁膜の厚さを各色画素毎に変化させる場合は製造工程が増加するため、上述の如く制御電極の面積を変えたほうが簡単である。40

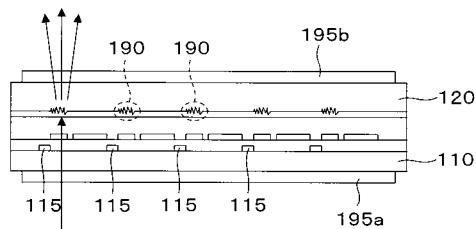

## 【0121】

図32は、第1~第7の実施形態において、T-V特性のしきい値が最も低い副画素の部分に散乱層190を設けた例を示している。なお、図32において、195a, 195bは液晶パネルの両面にそれぞれ配置された偏光板を示している。50

## 【0122】

表示電圧が低い場合は、1画素内的一部の副画素のみが光を透過し、他の副画素の部分では光を透過しない。このため、画素サイズが大きい場合は画面がざらついた印象を与えてしまう。そこで、図32に示すように、T-V特性のしきい値が最も低い副画素の部分に散乱層190を形成する。この散乱層190は、例えば基板120の表面をエッチングで荒らすなどの方法により形成される。これにより、光が散乱されて、輝度が低いときの画面のざらつきが抑制される。また、散乱によって輝度が低いときの視野角特性が改善されるという効果もある。

## 【0123】

なお、偏光板195aと偏光板195bとの間に光を散乱させる層を配置すると、偏光が乱れるため、コントラストが低下する。しかし、この図32に示す例のように、画素の一部のみに散乱層190を配置した場合はコントラストの低下が少なく、実用上問題は発生しない。

## 【0124】

上記第1～第7の実施形態においてはいずれも本発明を透過型液晶表示装置に適用した場合について説明したが、本発明は反射型液晶表示装置及び半透過型液晶表示装置に適用することもできる。

## 【0125】

## (面積比及び電圧比)

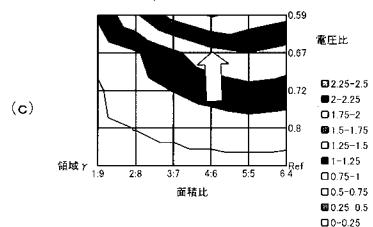

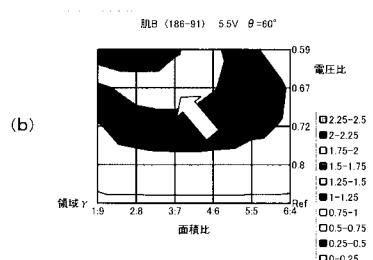

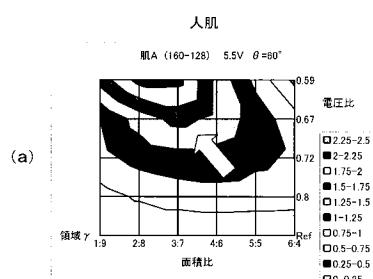

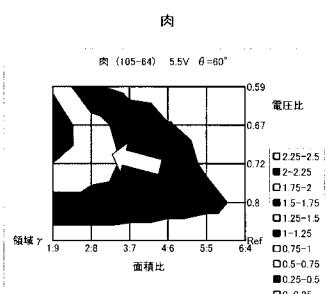

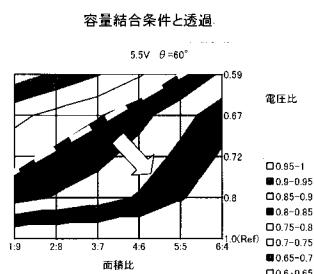

本願発明のように容量結合とVAモードの液晶表示装置とを組み合わせた場合、副画素電極の面積の比率と電圧の比率には最適な値の範囲が存在する。図33～図35はそのパラメータの組み合わせについて調べた結果を示す図である。これらの図33～図35において、横軸は副画素電極の面積比を示している。すなわち、TFTに直結した副画素電極の面積（低しきい値領域の面積）と、制御電極に容量結合した副画素電極の面積（高しきい値領域の面積）との比を示している。また、縦軸は電圧比、すなわち制御電極に容量結合された副画素電極の電圧/TFTに直結した副画素電極の電圧を示す。容量結合された副画素電極の電圧は、容量の分圧で決定される。

## 【0126】

この組み合わせに対して、VAモードの液晶表示装置において白茶けの影響を受けやすい代表的な画像を選び、そのピーク階調における係数をもって等高線グラフを作成した。なお、グラフには係数が高い組み合わせ、すなわち白茶けの改善効果がより大きな組み合わせの方向を矢印で示している。

## 【0127】

図33(a), (b), (c)はいずれも人肌の画像の階調値である。人肌は人間が記憶している色であり、画像の人物に対する印象を色で判断する場合が多く且つ重要であるため、白茶け改善が重要である代表的画像といえる。また、図34は食材である肉の画像の階調値である。食欲を引き出せるかという点で画像の再現性が重要であり、人肌よりも暗い低階調側の画像である。

## 【0128】

図33(a)～(c)及び図34から、電圧比が0.8以上では白茶けを改善する効果が殆どなく、電圧比は0.8以下でなければならないことは明らかである。

## 【0129】

また、面積比は、低階調の肉の画像は面積比が1:9などの比率のときに白茶け改善の効果が良好であるが、人肌の画像では面積比が2:8～5:5のときに白茶け改善の効果が良好であり、面積比が6:4では効果が落ち始める。また、面積比が6:4では低階調の肉の画像では白茶けの改善効果が全く得られない。

## 【0130】

図35は容量結合のパラメータと透過率との関係を示す図である。高しきい値領域の副画素電極には十分な電圧が印加されないため透過率は低下する傾向にあるが、高しきい値領域の副画素電極の面積割合が小さいほど、また電圧比が大きくしきい値のずれが小さい

10

20

30

40

50

ほど、透過率の低下は小さく抑えられる。図中矢印の方向が透過率が高い良好なパラメータの方向性となる。

【0131】

図33(a)～(c)及び図34と図35とを比較すると、互いにパラメータは反する方向に最適解があることがわかる。肌、肉、透過率でバランスが取れる条件としては4:6分割で電圧比0.72付近が理想的である。

【0132】

なお、3分割については更に組み合わせが複雑になるが、傾向は2分割と同様である。しかしながら、実験から低しきい値領域、中しきい値領域及び高しきい値領域の3つの画素において(低しきい値領域+中しきい値領域)と高しきい値領域、又は低しきい値領域と(中しきい値領域+高しきい値領域)との二つに組み合わせた場合の条件が2分割の条件範囲に入ってくれば大きな差はなくなることがわかっている。なお、画素電極を低しきい値領域、中しきい値領域及び高しきい値領域の3つに分割する場合、1:2:7、1:3:6、2:2:6等が理想的な条件となる。

【0133】

以下、本発明の諸態様を、付記としてまとめて記載する。

【0134】

(付記1) 相互に対向して配置された第1基板及び第2の基板と、前記第1の基板及び前記第2の基板の間に封入された垂直配向型液晶と、前記第1の基板に設けられて走査信号が供給されるゲートバスラインと、前記第1の基板に設けられて表示信号が供給されるデータバスラインと、前記ゲートバスライン及び前記データバスラインにより画定される画素領域毎に形成されたスイッチング素子及び画素電極と、

前記第1の基板の画素領域に設けられて前記スイッチング素子と接続された制御電極と、

前記第2の基板に設けられたコモン電極とを有し、

前記画素電極が複数の副画素電極に分割され、前記複数の副画素電極のうちの少なくとも一部の副画素電極が前記制御電極と容量結合し、前記制御電極に電圧が印加されると、前記制御電極に容量結合した副画素電極に、前記制御電極との間で形成される容量と前記液晶を介して前記コモン電極との間で形成される容量との比に応じた電圧が印加されることを特徴とする液晶表示装置。

【0135】

(付記2) 前記複数の副画素電極のうち前記スイッチング素子に接続された副画素電極の面積の総和S1と、前記制御電極との間に形成された容量を介して駆動される副画素電極の面積の総和S2との比(S1:S2)が、1:9乃至6:4の範囲内であることを特徴とする付記1に記載の液晶表示装置。

【0136】

(付記3) 前記複数の副画素電極のうち前記スイッチング素子に接続された副画素電極の電圧V1と、前記制御電極との間に形成された容量を介して駆動される副画素電極の電圧V2との比(V2/V1)が、0.8乃至0.59の範囲内であることを特徴とする付記1に記載の液晶表示装置。

【0137】

(付記4) 相互に対向して配置された第1の基板及び第2の基板と、前記第1の基板及び前記第2の基板の間に封入された液晶と、前記第1の基板に設けられて走査信号が供給されるゲートバスラインと、前記第1の基板に設けられて表示信号が供給されるデータバスラインと、前記ゲートバスライン及び前記データバスラインにより画定される画素領域内に配置され、スリットにより複数の副画素電極に分割された画素電極と、前記ゲートバスライン及び前記データバスラインに接続されたスイッチング素子と、前記スイッチング素子に接続されて前記複数の副画素電極の少なくとも1つと容量結合

10

20

30

40

50

する制御電極と、

前記第2の基板に設けられたコモン電極とを有し、

前記画素電極を分割するスリットの少なくとも一部が、電圧印加時の液晶分子の配向方向を規定するドメイン規制用構造物を構成することを特徴とする液晶表示装置。

【0138】

(付記5) 前記データバスラインに前記表示信号を供給し、前記ゲートバスラインに前記走査信号を供給したときに、前記複数の副画素電極の一部に第1の電圧が印加され、残りの副画素電極には前記第1の電圧と異なる第2の電圧が印加されることを特徴とする付記4に記載の液晶表示装置。

【0139】

(付記6) 前記制御電極と容量結合をしている副画素電極以外の副画素電極が、前記スイッチング素子と接続していることを特徴とする付記4に記載の液晶表示装置。

【0140】

(付記7) 前記第1の基板には、前記スリット以外のドメイン規制用構造物を有しないことを特徴とする付記4に記載の液晶表示装置。

【0141】

(付記8) 前記第2の基板に、電圧印加時の液晶分子の配向方向を規定する第2のドメイン規制用構造物が形成されていることを特徴とする付記4に記載の液晶表示装置。

【0142】

(付記9) 前記スリットと前記第2のドメイン規制用構造物との間隔が、各副画素電極毎に設定されていることを特徴とする付記8に記載の液晶表示装置。

【0143】

(付記10) 前記スイッチング素子と前記制御電極との間を接続する配線が、前記第2の基板の第2のドメイン規制用構造物に沿って配置されていることを特徴とする付記8に記載の液晶表示装置。

【0144】

(付記11) 前記ドメイン規制用構造物を構成するスリット以外のスリットが、前記ドメイン規制用構造物を構成するスリットに対しほぼ垂直に配置されていることを特徴とする付記4に記載の液晶表示装置。

【0145】

(付記12) 前記画素領域に隣接する2つのデータバスラインのうちの一方のデータバスラインとの間に第1の寄生容量が発生する副画素電極と、他方のデータバスラインとの間に前記第1の寄生容量とほぼ同じ大きさの第2の寄生容量が発生する副画素電極とが、相互に電気的に接続されていることを特徴とする付記4に記載の液晶表示装置。

【0146】

(付記13) 前記スイッチング素子と前記制御電極とを接続する配線と前記スリットとが交差する部分に、前記配線を覆う導電体膜が形成されていることを特徴とする付記4に記載の液晶表示装置。

【0147】

(付記14) 前記制御電極が、前記画素領域の中央を横断する補助容量バスラインの上に絶縁膜を介して形成されていることを特徴とする付記4に記載の液晶表示装置。

【0148】

(付記15) 前記複数の副画素電極のうち前記制御電極と容量結合する第1の副画素電極及び第2の副画素電極を有し、

前記制御電極のうち前記第1の副画素電極に容量結合する部分と前記第2の副画素電極に容量結合する部分との間が、前記補助容量バスラインよりも細い配線で接続されていることを特徴とする付記14に記載の液晶表示装置。

【0149】

(付記16) 前記スイッチング素子と前記制御電極とを接続する配線の下方に、前記補助容量バスラインに接続した導体パターンが形成されていることを特徴とする付記14

10

20

30

40

50

に記載の液晶表示装置。

【0150】

(付記17) 前記スリットの下方に、前記補助容量バスラインに接続した導体パターンが形成されていることを特徴とする付記14に記載の液晶表示装置。

【0151】

(付記18) 前記第1の基板及び前記第2の基板のいずれか一方に設けられたカラーフィルタを有し、カラーフィルタの色毎に前記第1の基板と前記第2の基板との間の液晶層の厚さが異なることを特徴とする付記4に記載の液晶表示装置。

【0152】

(付記19) 前記液晶層の厚さが厚い画素ほど前記制御電極の大きさが小さいことを特徴とする付記18に記載の液晶表示装置。 10

【0153】

(付記20) 前記第1の基板及び第2の基板のうちの少なくとも一方の基板の前記複数の副画素電極の一部に対向する部分に、光を散乱する散乱層が形成されていることを特徴とする付記4に記載の液晶表示装置。

【図面の簡単な説明】

【0154】

【図1】従来の液晶表示装置の構造を示す模式断面図である。

【図2】図2(a), (b)は、従来のMVA型液晶表示装置の一例を示す模式断面図である。 20

【図3】図3は、TFT基板側の画素電極にドメイン規制用構造物としてスリットを形成した従来のMVA型液晶表示装置を示す模式断面図である。

【図4】図4は実際のMVA型液晶表示装置の1画素を示す平面図である。

【図5】図5は同じくその液晶表示装置のTFT基板の模式断面図である。

【図6】図6は、従来のMVA型液晶表示装置における4つのドメインを示す模式図である。

【図7】図7は、画面を正面から見たときのT-V特性と上60°の方向から見たときのT-V特性とを示す図である。

【図8】図8は、容量結合によるHT(ハーフトーングレースケール)法を使用した従来の液晶表示装置の1画素を示す平面図である。 30

【図9】図9(a)は画素電極が分割されていない液晶表示装置の1画素を示す模式図、図9(b)は画素電極が2つに分割された液晶表示装置の1画素を示す模式図、図9(c)は画素電極が3つに分割された液晶表示装置の1画素を示す模式図、図9(d)は画素電極が4つに分割された液晶表示装置の1画素を示す模式図である。

【図10】図10は、TN型液晶表示装置及びVA型液晶表示装置における画素電極の分割数と画素ピッチ及び開口率比との関係を示す図である。

【図11】図11は、本発明の第1の実施形態の液晶表示装置を示す平面図である。

【図12】図12は、同じくその模式断面図である。

【図13】図13は、副画素電極を分離するスリットとは別に、ドメイン規制用構造物としてスリット及び突起を設けたMVA型液晶表示装置の例を示す模式図である。 40

【図14】図14は、本発明の第2の実施形態の液晶表示装置の1画素を示す平面図である。

【図15】図15は、第1の実施形態の液晶表示装置の画素部の等価回路図である。

【図16】図16は、第2の実施形態の液晶表示装置の画素部の等価回路図である。

【図17】図17は、本発明の第3の実施形態の液晶表示装置の1画素を示す平面図である。

【図18】図18は、本発明の第4の実施形態の液晶表示装置の1画素を示す平面図である。

【図19】図19(a)は第3の実施形態の液晶表示装置の一部分の光の透過状態を示す光透過図、図19(b)は第4の実施形態の液晶表示装置の図19(a)に対応する部分 50

の光の透過状態を示す光透過図である。

【図20】図20は、本発明の第5の実施形態の液晶表示装置の1画素を示す平面図である。

【図21】図21は、本発明の第6の実施形態の液晶表示装置の1画素を示す平面図である。

【図22】図22は、図21中に破線の円Aで囲んだ部分を拡大して示す模式図である。

【図23】図23は、図21中に破線の円Bで囲んだ部分を拡大して示す模式図である。

【図24】図24(a)は第5の実施形態の液晶表示装置の一部分の光の透過状態を示す光透過図、図24(b)は第6の本実施形態の図24(a)に対応する部分の光の透過状態を示す光透過図である。

【図25】図25(a)は第5の実施形態の液晶表示装置の他の部分の光の透過状態を示す光透過図、図25(b)は第6の本実施形態の図25(a)に対応する部分の光の透過状態を示す光透過図である。

【図26】図26は、本発明の第7の実施形態の液晶表示装置の1画素を示す平面図である。

【図27】図27は、副画素電極の面積比を説明する平面図である。

【図28】図28は、第7の実施形態の変形例1の液晶表示装置の1画素を示す平面図である。

【図29】図29は、第7の実施形態の変形例2の液晶表示装置の1画素を示す平面図である。

【図30】図30は、赤色(R)画素、緑色(G)画素及び青色(B)画素のセルギャップが相互に異なるマルチギャップ構造の液晶表示装置を示す模式図である。

【図31】図31は、セルギャップに応じて制御電極の大きさを設定した液晶表示装置を示す模式図である。

【図32】図32は、T-V特性のしきい値が最も低い副画素の部分に散乱層を設けた液晶表示装置の例を示す模式図である。

【図33】図33(a), (b), (c)はいずれも人肌の画像における面積比及び電圧比の最適範囲を示す図である。

【図34】図34は肉の画像における面積比及び電圧比の最適範囲を示す図である。

【図35】図35は容量結合のパラメータと透過率との関係を示す図である。

#### 【符号の説明】

##### 【0155】

10, 20, 50, 110, 120...基板、

12, 56...画素電極、

12a, 56a, 84, 117a, 150a, 150b, 150c, 180a...スリット、

13, 23, 71, 85, 124, 187...突起、

14, 24, 118, 125...配向膜、

22, 123...コモン電極

30, 130...液晶

40...液晶パネル、

41, 42...偏光板、

51, 111...ゲートバスライン、

52, 112...補助容量バスライン、

53...補助容量電極、

54, 114...TFT

55, 115...データバスライン、

61, 62, 131, 132...絶縁膜、

81a~81d, 116a~116d, 151a~151d, 161a~161d, 1

81a~181e...副画素電極、

10

20

30

40

50

8 2 a ~ 8 2 d , 8 3 , 1 1 3 , 1 8 3 a , 1 8 3 b , 1 1 3 R , 1 1 3 G , 1 1 3 B

... 制御電極、

1 1 5 a , 1 1 5 b , 1 5 3 a , 1 5 3 b , 1 6 3 a , 1 6 3 b , 1 8 5 a , 1 8 5 b

... 接続配線、

1 2 1 ... ブラックマトリクス、

1 2 2 ... カラーフィルタ、

1 7 0 ... I T O 膜、

1 9 0 ... 散乱層。

【図 1】

【図 2】

10, 20: 基板

12: 画素電極

13, 23: 突起

22: コモン電極

30a: 液晶分子

24: 配向膜

【図3】

10, 20:基板

12:画素電極

13a:スリット

14, 24:配向膜

22:コモン電極

30a:液晶分子

【図4】

51:ゲートバスライン

52:補助容量バスライン

55:データバスライン

56:画素電極

56a:スリット

71:突起

【図5】

50:基板

51:ゲートバスライン

52:補助容量バスライン

53:補助容量電極

55:データバスライン

56:画素電極

61, 62:絶縁膜

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

111:ゲートバスライン 116a~116d:副画素電極

112:補助容量バスライン 117a:スリット

115:データバスライン 124:突起

【 図 1 2 】

110: 110, 120-基板

111: ディート容バスライン

112: ディート容バスライン

113: 制御電極

114: 116a, 116b, 116d 副系電極

115: リリット

123: コモン電極

124: 突起

【図13】

80:TFT 84:スリット

81a~81d:副画素電極 85:突起

82a~82d:制御電極

【 図 1 4 】

111: ゲートバスライン 116a～116d: 副画素電極

112: 助容量バスライン 117a: スリット

115: データバスライン 124: 突起

【図15】

【図16】

【 図 17 】

111: ゲートバスライン 124: 突起

112: 補助容量バスライン 150a, 150b: スリット

115: データバスライン 151a~151d: 副画素電極

【 四 1 8 】

111: ゲートバスライン 124: 突起

112: 補助容量バスライン 150a, 150b: スリット

115: データバスライン 161a~161d: 副画素電極

【 図 1 9 】

(a) (b)

【図20】

111:ゲートバスライン

112:補助容量バスライン

115:データバスライン

124:突起

161a~161d:副画素電極

163a, 163b:接続配線

【図21】

111:ゲートバスライン

112:補助容量バスライン

115:データバスライン

124:突起

161a~161d:副画素電極

163a, 163b:接続配線

【図22】

【図23】

【図24】

(a) (b)

【図25】

(a) (b)

【図26】

111:ゲートバスライン

112:補助容量バスライン

115:データバスライン

180a:スリット

181a～181e:副画素電極

187:突起

【図27】

【図28】

111:ゲートバスライン

112:補助容量バスライン

115:データバスライン

180a:スリット

181a～181e:副画素電極

112a, 112b:導電パターン

187:突起

【図29】

111:ゲートバスライン

112:補助容量バスライン

115:データバスライン

180a:スリット

181a～181e:副画素電極

112a～112c:導電パターン

187:突起

【図30】

【図31】

【図32】

110, 120:基板

115:データバスライン

190:散乱層

【図33】

【図34】

【図35】

---

フロントページの続き

(72)発明者 笹林 貴

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

(72)発明者 上田 一也

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

(72)発明者 吉田 秀史

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

F ターム(参考) 2H090 HB08Y KA04 LA01 LA04 MA01 MA07 MA13 MA14

2H092 GA13 GA14 GA29 JA26 JA46 JB05 JB63 JB64 JB69 KA04

KA05 KA11 KB01 KB04 KB25 MA03 MA13 NA01 NA07 NA27

PA01 PA02 PA06 QA06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2005292397A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 公开(公告)日 | 2005-10-20 |

| 申请号            | JP2004106138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2004-03-31 |

| [标]申请(专利权)人(译) | 富士通显示技术股份有限公司<br>友达光电股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | 富士通显示器科技公司<br>友达光电股▼ふん▲有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| [标]发明人         | 鎌田豪<br>笠林貴<br>上田一也<br>吉田秀史                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 发明人            | 鎌田 豪<br>笠林 貴<br>上田 一也<br>吉田 秀史                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| IPC分类号         | G02F1/1337 G02F1/133 G02F1/1343 G02F1/136 G02F1/1368 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| CPC分类号         | G02F1/134336 G02F2001/134345 G02F2001/134354 G09G3/3607 G09G3/3614 G09G3/3648<br>G09G2300/0443 G09G2320/0209 G09G2320/0242 G09G2320/028                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| FI分类号          | G02F1/1343 G02F1/1337.505 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| F-TERM分类号      | 2H090/HB08Y 2H090/KA04 2H090/LA01 2H090/LA04 2H090/MA01 2H090/MA07 2H090/MA13 2H090<br>/MA14 2H092/GA13 2H092/GA14 2H092/GA29 2H092/JA26 2H092/JA46 2H092/JB05 2H092/JB63<br>2H092/JB64 2H092/JB69 2H092/KA04 2H092/KA05 2H092/KA11 2H092/KB01 2H092/KB04 2H092<br>/KB25 2H092/MA03 2H092/MA13 2H092/NA01 2H092/NA07 2H092/NA27 2H092/PA01 2H092/PA02<br>2H092/PA06 2H092/QA06 2H192/AA24 2H192/AA46 2H192/BA13 2H192/BA25 2H192/BC23 2H192<br>/BC31 2H192/CB05 2H192/CC04 2H192/DA12 2H192/DA71 2H192/EA22 2H192/EA43 2H192/GA03<br>2H192/GD14 2H192/GD44 2H192/JA13 2H290/AA34 2H290/BA04 2H290/BA05 2H290/BB24 2H290<br>/BB44 2H290/BB73 2H290/BC01 2H290/CA46 |         |            |

| 代理人(译)         | 冈本圭造                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 其他公开文献         | JP4459685B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

**摘要(译)**

要解决的问题：提供一种可以防止变色的液晶显示装置，具有高显示质量和高孔径比，并且可以提供明亮的显示。解决方案：通过倾斜延伸的狭缝117a将像素电极分成子像素电极116a至116d。控制电极113形成在辅助电容总线112上方。子像素电极116b和116c与控制电极113重叠并与控制电极113电容耦合。控制电极113和TFT 141的源电极114s通过连接线115a连接。子像素电极116a电连接到连接线115a。此外，子像素电极116d电连接到从控制电极113延伸的连接线115b