**【特許請求の範囲】****【請求項 1】**

液晶表示パネル用画像データ処理装置であって、

前記液晶表示パネルに表示すべき動画面の各画素を与えるラスターデータとしての各画像データを順次に受信する入力端と、前記受信画像データを現画像データとして順次に出力する出力端とを有する受信回路と、

前記受信回路の前記出力端に接続された入力端及び出力端を有し、前記現画像データを符号化して符号化画像データを前記出力端より出力する符号化回路と、

前記符号化回路の前記出力端に接続された入力端及び出力端を有し、前記符号化画像データを復号化して前記現画像データに対応する第1復号化画像データを前記出力端より出力する第1復号化回路と、10

前記符号化回路の前記出力端に接続された入力端及び出力端を有し、前記入力端で受信した前記符号化画像データを前記動画面の1フレーム期間だけ遅延した上で遅延後の前記符号化画像データを遅延符号化画像データとして前記出力端より出力する遅延回路と、

前記遅延回路の前記出力端に接続された入力端及び出力端を有し、前記現画像データの出力時に対して前記1フレーム期間だけ前の時点において前記受信回路が前記現画像データとして出力した1フレーム前画像データの符号化画像データを前記入力端で受信し、前記受信符号化画像データを復号化して前記1フレーム前画像データに対応する第2復号化画像データを前記出力端より出力する第2復号化回路と、20

前記第1復号化回路の前記出力端及び前記第2復号化回路の前記出力端に接続された入力端及び出力端を有し、前記第1復号化画像データ及び前記第2復号化画像データに基づいて、前記現画像データと前記1フレーム前画像データ間の輝度値の変化量を算出し、得られた変化量データを前記出力端より出力する変化量算出回路と、

前記受信回路の前記出力端及び前記変化量算出回路の前記出力端に接続された入力端及び出力端を有し、前記現画像データ及び前記変化量データに基づいて前記1フレーム前画像データを再生し、得られた1フレーム前再生画像データを前記出力端より出力する1フレーム前画像再生回路と、

少なくとも一つの基準温度データ及び出力端を有しており、前記液晶表示パネル又はその近傍雰囲気の一方の温度データと前記少なくとも一つの基準温度データとを比較し、その比較結果に基づき制御信号を前記出力端より出力する温度制御部と、30

前記受信回路の前記出力端、前記1フレーム前画像再生回路の前記出力端及び前記温度制御部の前記出力端に接続された入力端及び前記液晶表示パネルに接続された出力端を有し、(1)前記現画像データの第1輝度値と前記1フレーム前再生画像データの第2輝度値とが相違するか否かを検出し、(2)前記第1及び第2輝度値が互いに相違する場合には、前記現画像データ、前記1フレーム前再生画像データ及び前記制御信号に基づいて前記第1輝度値を補正し、補正済み輝度値を与える補正現画像データを前記出力端より出力し、(3)前記第1及び第2輝度値が互いに一致する場合には、前記現画像データを前記補正現画像データとして前記出力端より出力する画像データ補正回路とを備え、

前記補正現画像データは、前記補正現画像データに基づき前記液晶表示パネルが生成する液晶印加電圧により実現される液晶の透過率が、前記1フレーム期間の経過時に前記第1輝度値に相当する第1透過率に到達する様に、決定されることを特徴とする、40

液晶表示パネル用画像データ処理装置。

**【請求項 2】**

請求項1記載の液晶表示パネル用画像データ処理装置であって、

前記画像データ補正回路は、

前記受信回路の前記出力端及び前記1フレーム前画像再生回路の前記出力端に接続された入力端と、出力端とを有する、少なくとも2個のルックアップテーブル保有回路と、

前記少なくとも2個のルックアップテーブル保有回路の前記出力端、及び前記温度制御部の前記出力端に接続された入力端と、前記液晶表示パネルに接続された出力端とを有する補正量制御回路とを備え、50

前記補正量制御回路は、前記少なくとも2個のルックアップテーブル保有回路が出力する少なくとも2個の補正候補現画像データの内から前記制御信号の指令に基づいて1個の補正候補現画像データを選択し、被選択補正候補現画像データを前記補正現画像データとして前記出力端から出力し、

前記少なくとも2個のルックアップテーブル保有回路は、第1温度における第1ルックアップテーブル保有回路は、第1温度における第1ルックアップテーブルを保有しており、

前記第1ルックアップテーブルは、前記液晶表示パネル又はその近傍雰囲気の温度が前記第1温度にある状況下で、前記液晶の前記透過率が前記1フレーム期間の経過時に前記第1透過率となる様に、 $n$ ビット信号である前記現画像データの前記第1輝度値と、前記 $n$ ビット信号である前記1フレーム前再生画像データの前記第2輝度値との組合せ毎に予め求められた、 $2^n \times 2^n$ 個の、第1候補値を与える第1補正画像データを有しており、

前記第1輝度値と前記第2輝度値とが互いに等しい場合における前記第1候補値は前記第1輝度値であり、

前記第1ルックアップテーブル保有回路は、前記第1ルックアップテーブルにおける前記 $2^n \times 2^n$ 個の第1補正画像データの中から、入力した前記現画像データの前記第1輝度値と、入力した前記1フレーム前再生画像データの前記第2輝度値との前記組合せに対応する第1候補値を有する第1補正画像データを、前記少なくとも2個の補正候補現画像データの一方である第1補正候補現画像データとして出力し、

前記少なくとも2個のルックアップテーブル保有回路の他方である第2ルックアップテーブル保有回路は、前記第1温度とは異なる第2温度における第2ルックアップテーブルを保有しており、

前記第2ルックアップテーブルは、前記液晶表示パネル又はその近傍雰囲気の温度が前記第2温度にある状況下で、前記液晶の前記透過率が前記1フレーム期間の経過時に前記第1透過率となる様に、前記現画像データの前記第1輝度値と前記1フレーム前再生画像データの前記第2輝度値との組合せ毎に予め求められた、 $2^n \times 2^n$ 個の、第2候補値を与える第2補正画像データを有しており、

前記第1輝度値と前記第2輝度値とが互いに等しい場合における前記第2候補値は前記第1輝度値であり、

前記第2ルックアップテーブル保有回路は、前記第2ルックアップテーブルにおける前記 $2^n \times 2^n$ 個の第2補正画像データの中から、入力した前記現画像データの前記第1輝度値と、入力した前記1フレーム前再生画像データの前記第2輝度値との前記組合せに対応する第2候補値を有する第2補正画像データを、前記少なくとも2個の補正候補現画像データの他方である第2補正候補現画像データとして出力することを特徴とする、

液晶表示パネル用画像データ処理装置。

### 【請求項3】

請求項1記載の液晶表示パネル用画像データ処理装置であって、

前記温度制御部は一つの基準温度のデータを有しており、

前記画像データ補正回路は、

前記受信回路の前記出力端及び前記1フレーム前画像再生回路の前記出力端に接続された入力端と、出力端とを有するルックアップテーブル保有回路と、

前記受信回路の前記出力端に接続された第1入力端と、前記ルックアップテーブル保有回路の前記出力端に接続された第2入力端と、出力端とを有する減算回路と、

前記減算回路の前記出力端及び前記温度制御部の前記出力端に接続された入力端と、出力端とを有する補正量制御回路と、

前記受信回路の前記出力端に接続された第1入力端と、前記補正量制御回路の前記出力端に接続された第2入力端と、前記液晶表示パネルに接続された出力端とを有する加算回路とを備えており、

前記ルックアップテーブル保有回路は、前記基準温度におけるルックアップテーブルを保有しており、

前記ルックアップテーブルは、前記液晶表示パネル又はその近傍雰囲気の温度が前記基準

10

20

30

40

50

温度にある状況下で、前記液晶の前記透過率が前記1フレーム期間の経過時に前記第1透過率となる様に、前記現画像データの前記第1輝度値と前記1フレーム前再生画像データの前記第2輝度値との組合せ毎に予め求められた、 $2^n \times 2^n$ 個の、候補値を与える補正画像データを有しており、

前記第1輝度値と前記第2輝度値とが互いに等しい場合における前記候補値は前記第1輝度値であり、

前記ルックアップテーブル保有回路は、前記ルックアップテーブルにおける前記 $2^n \times 2^n$ 個の補正画像データの中から、入力した前記現画像データの前記第1輝度値と、入力した前記1フレーム前再生画像データの前記第2輝度値との前記組合せに対応する候補値を有する補正画像データを、補正候補現画像データとして出力し、

前記補正量制御回路は、(A)前記減算回路の出力データが0値を示すときには前記減算回路の前記出力データをそのまま出力し、(B)前記減算回路の出力データが0値でないときには、前記減算回路の前記出力データ及び前記制御信号に基づいて、前記補正済み輝度値と前記第1輝度値との差分に相当する補正量データを生成し、前記補正量データをその出力端より出力することを特徴とする、液晶表示パネル用画像データ処理装置。

#### 【請求項4】

液晶表示パネル用画像データ処理装置であつて、

前記液晶表示パネルに表示すべき動画面の各画素を与えるラスターデータとしての各画像データを順次に受信する入力端と、前記受信画像データを現画像データとして順次に出力する出力端とを有する受信回路と、

前記受信回路の前記出力端に接続された入力端及び出力端を有し、前記現画像データを符号化して符号化画像データを前記出力端より出力する符号化回路と、

前記符号化回路の前記出力端に接続された入力端及び出力端を有し、前記符号化画像データを復号化して前記現画像データに対応する第1復号化画像データを前記出力端より出力する第1復号化回路と、

前記符号化回路の前記出力端に接続された入力端及び出力端を有し、前記入力端で受信した前記符号化画像データを前記動画面の1フレーム期間だけ遅延した上で遅延後の前記符号化画像データを遅延符号化画像データとして前記出力端より出力する遅延回路と、

前記遅延回路の前記出力端に接続された入力端及び出力端を有し、前記現画像データの出力時に対して前記1フレーム期間だけ前の時点において前記受信回路が前記現画像データとして出力した1フレーム前画像データの符号化画像データを前記入力端で受信し、前記受信符号化画像データを復号化して前記1フレーム前画像データに対応する第2復号化画像データを前記出力端より出力する第2復号化回路と、

前記第1復号化回路の前記出力端及び前記第2復号化回路の前記出力端に接続された入力端並びに出力端を有し、前記第1復号化画像データ及び前記第2復号化画像データに基づいて、前記現画像データと前記1フレーム前画像データ間の輝度値の変化量を算出し、得られた変化量データを前記出力端より出力する変化量算出回路と、

前記受信回路の前記出力端及び前記変化量算出回路の前記出力端に接続された入力端並びに出力端を有し、前記現画像データ及び前記変化量データに基づいて前記1フレーム前画像データを再生し、得られた1フレーム前再生画像データを前記出力端より出力する1フレーム前画像再生回路と、

前記受信回路の前記出力端及び前記1フレーム前画像再生回路の前記出力端に接続された入力端並びに前記液晶表示パネルに接続された出力端を有し、(1)前記現画像データの第1輝度値と前記1フレーム前再生画像データの第2輝度値とが相違するか否かを検出し、(2)前記第1及び第2輝度値が互いに相違する場合には、前記現画像データ及び前記1フレーム前再生画像データに基づいて前記第1輝度値を補正し、補正済み輝度値を与える補正現画像データを前記出力端より出力し、(3)前記第1及び第2輝度値が互いに一致する場合には、前記現画像データを前記補正現画像データとして前記出力端より出力する画像データ補正回路とを備え、

前記補正現画像データは、前記補正現画像データに基づき前記液晶表示パネルが生成する

10

20

30

40

50

液晶印加電圧により実現される液晶の透過率が、前記 1 フレーム期間の経過時に前記第 1 輝度値に相当する第 1 透過率に到達する様に、決定されることを特徴とする、液晶表示パネル用画像データ処理装置。

#### 【請求項 5】

請求項 4 記載の液晶表示パネル用画像データ処理装置であって、

前記画像データ補正回路は、

前記受信回路の前記出力端及び前記 1 フレーム前画像再生回路の前記出力端に接続された入力端と、前記液晶表示パネルに接続された出力端とを有すると共に、ルックアップテーブルを保有するルックアップテーブル保有回路を備えており、

前記ルックアップテーブルは、前記液晶の前記透過率が前記 1 フレーム期間の経過時に前記第 1 透過率となる様に、 $n$  ビット信号である前記現画像データの前記第 1 輝度値と、前記  $n$  ビット信号である前記 1 フレーム前再生画像データの前記第 2 載度値との組合せ毎に予め求められた、 $2^n \times 2^n$  個の補正画像データを有しており、

前記第 1 載度値と前記第 2 載度値とが互いに等しい場合における前記補正画像データの値は前記第 1 載度値であり、

前記ルックアップテーブル保有回路は、前記ルックアップテーブルにおける前記  $2^n \times 2^n$  個の補正画像データの中から、入力した前記現画像データの前記第 1 載度値と、入力した前記 1 フレーム前再生画像データの前記第 2 載度値との前記組合せに対応する第 1 補正画像データを抽出し、抽出された前記第 1 補正画像データに基づき前記補正現画像データを設定することを特徴とする、

液晶表示パネル用画像データ処理装置。

#### 【請求項 6】

請求項 4 記載の液晶表示パネル用画像データ処理装置であって、

前記画像データ補正回路は、

前記受信回路の前記出力端に接続された入力端と、第 1 及び第 2 出力端とを有し、第 1 量子化処理によって、量子化ビット数  $n$  の前記現画像データを量子化ビット数  $m$  ( $m < n$ ) の削減された現画像データに変換し且つ第 1 補間係数を算出すると共に、前記削減された現画像データ及び前記第 1 補間係数を与える第 1 補間係数信号をそれぞれ前記第 1 及び第 2 出力端から出力する第 1 データ変換回路と、

前記 1 フレーム前画像再生回路の前記出力端に接続された入力端と、第 1 及び第 2 出力端とを有し、第 2 量子化処理によって、前記量子化ビット数  $n$  の前記 1 フレーム前再生画像データを量子化ビット数  $q$  ( $q < n$ ) の削減された 1 フレーム前再生画像データに変換し且つ第 2 補間係数を算出すると共に、前記削減された 1 フレーム前再生画像データ及び前記第 2 補間係数を与える第 2 補間係数信号をそれぞれ前記第 1 及び第 2 出力端から出力する第 2 データ変換回路と、

前記第 1 データ変換回路の前記第 1 出力端及び第 2 データ変換回路の前記第 1 出力端に接続された入力端と、出力端とを有すると共に、ルックアップテーブルを保有するルックアップテーブル保有回路と、

前記ルックアップテーブル保有回路の前記出力端に接続された第 1 入力端と、前記第 1 データ変換回路の前記第 2 出力端に接続された第 2 入力端と、前記第 2 データ変換回路の前記第 2 出力端に接続された第 3 入力端と、前記液晶表示パネルに接続された出力端とを有する補間回路とを備えており、

前記ルックアップテーブルは、前記液晶の前記透過率が前記 1 フレーム期間の経過時に前記第 1 透過率となる様に、 $m$  ビット信号である前記削減された現画像データの輝度値と、 $q$  ビット信号である前記削減された 1 フレーム前再生画像データの輝度値との組合せ毎に予め求められた、 $(2^m + 1) \times (2^q + 1)$  個の補正画像データを有しており、

前記削減された現画像データの前記輝度値と前記削減された 1 フレーム前再生画像データの前記輝度値とが互いに等しい場合における前記補正画像データの値は、前記削減された現画像データの前記輝度値であり、

前記ルックアップテーブル保有回路は、前記ルックアップテーブルにおける前記  $(2^m + 1) \times (2^q + 1)$  個の補正画像データを有しており、

$1) \times (2^q + 1)$  個の補正画像データの中から、入力した前記削減された現画像データの前記輝度値と、入力した前記削減された 1 フレーム前再生画像データの前記輝度値との前記組合せに対応する第 1 補正画像データと、前記組合せに隣接する 3 個の先行する格子点における第 2 ないし第 4 補正画像データとを、前記出力端から出力し、

前記補間回路は、前記第 1 及び第 2 補間係数信号並びに前記第 1 ないし第 4 補正画像データに基づき、n ビット信号の補間された補正画像データを生成し、前記補間された補正画像データに基づき前記補正現画像データを設定することを特徴とする、

液晶表示パネル用画像データ処理装置。

#### 【請求項 7】

請求項 6 記載の液晶表示パネル用画像データ処理装置であって、

10

前記画像データ補正回路は、

前記補間回路の前記出力端、前記受信回路の前記出力端及び前記 1 フレーム前画像再生回路の前記出力端に接続された入力端と、前記液晶表示パネルに接続された出力端とを有しており、(A) 前記現画像データと前記 1 フレーム前再生画像データとが互いに等しいか否かを判断し、(B) 前記現画像データと前記 1 フレーム前再生画像データとが互いに等しい場合には、前記補間された補正画像データに代えて、前記現画像データを前記補正現画像データとして出力し、(C) 前記現画像データと前記 1 フレーム前再生画像データとが互いに相違する場合には、前記補間された補正画像データを前記補正現画像データとして出力する補正データ制限回路を更に備えることを特徴とする、

液晶表示パネル用画像データ処理装置。

20

#### 【請求項 8】

液晶表示パネル用画像データ処理装置であって、

前記液晶表示パネルに表示すべき動画面の各画素を与えるラスターデータとしての各画像データを順次に受信する入力端と、前記受信画像データを現画像データとして順次に出力する出力端とを有する受信回路と、

前記受信回路の前記出力端に接続された入力端、出力端及び圧縮符号化パラメータを有し、前記圧縮符号化パラメータに基づいて前記現画像データを符号化して符号化画像データを前記出力端より出力する符号化回路と、

前記符号化回路の前記出力端に接続された入力端及び出力端を有し、前記符号化画像データを復号化して前記現画像データに対応する第 1 復号化画像データを前記出力端より出力する第 1 復号化回路と、

30

前記符号化回路の前記出力端に接続された入力端及び出力端を有し、前記入力端で受信した前記符号化画像データを前記動画面の 1 フレーム期間だけ遅延した上で遅延後の前記符号化画像データを遅延符号化画像データとして前記出力端より出力する遅延回路と、

前記遅延回路の前記出力端に接続された入力端及び出力端を有し、前記現画像データの出力時に対して前記 1 フレーム期間だけ前の時点において前記受信回路が前記現画像データとして出力した 1 フレーム前画像データの符号化画像データを前記入力端で受信し、前記受信符号化画像データを復号化して前記 1 フレーム前画像データに対応する第 2 復号化画像データを前記出力端より出力する第 2 復号化回路と、

前記第 1 復号化回路の前記出力端及び前記第 2 復号化回路の前記出力端に接続された入力端、並びに出力端を有し、前記第 1 復号化画像データ及び前記第 2 復号化画像データに基づいて、前記現画像データの階調変化に対応する補正データを生成し、前記補正データを前記出力端より出力する補正データ生成回路と、

40

前記受信回路の前記出力端及び前記補正データ生成回路の前記出力端に接続された入力端、並びに前記液晶表示パネルに接続された出力端を有し、前記現画像データ及び前記補正データに基づいて補正現画像データを生成し、前記補正現画像データを前記出力端より前記液晶表示パネルへ出力する補正回路とを備え、

前記補正データ生成回路は、(1) 前記第 1 復号化画像データが与える第 1 階調数と前記第 2 復号化画像データが与える第 2 階調数とが相違するか否かを検出し、(2) 前記第 1 階調数が第 2 階調数よりも大きい場合には、前記現画像データの階調数をより一層増加さ

50

せる第1補正量を与える前記補正データを生成し、他方、前記第1階調数が第2階調数よりも小さい場合には、前記現画像データの前記階調数をより一層減少させる第2補正量を与える前記補正データを生成し、(3)前記第1及び第2階調数が互いに一致する場合には、前記現画像データの前記階調数の増減を行わない旨を指令する前記補正データを生成し、

前記補正現画像データは、前記補正現画像データに基づき前記液晶表示パネルが生成する液晶印加電圧により実現される液晶の透過率が、前記1フレーム期間の経過時に前記第1階調数に相当する第1透過率に到達する様に、決定されており、

前記圧縮符号化パラメータは、前記現画像データの第1容量及び前記現画像データを符号化して得られる前記符号化画像データの第2容量に基づいて、設定されていることを特徴とする、

液晶表示パネル用画像データ処理装置。

【請求項9】

請求項8記載の液晶表示パネル用画像データ処理装置であって、

前記符号化回路は、前記第1容量の1/2以下の前記第2容量を有する前記符号化画像データを生成することを特徴とする、

液晶表示パネル用画像データ処理装置。

【請求項10】

請求項9記載の液晶表示パネル用画像データ処理装置であって、

前記符号化回路は、前記第1容量の1/3以下の前記第2容量を有する前記符号化画像データを生成することを特徴とする、

液晶表示パネル用画像データ処理装置。

【請求項11】

請求項8乃至10の何れかに記載の液晶表示パネル用画像データ処理装置であって、

前記受信回路の前記出力端に接続された入力端及び前記符号化回路の前記入力端に接続された出力端を有し、第1三原色データを有する前記現画像データを輝度データ及び色差データを有する第1画像データに変換して前記第1画像データを前記出力端から出力する第1色空間変換回路と、

前記第1復号化回路の前記出力端に接続された入力端及び前記補正データ生成回路の前記入力端に接続された出力端を有し、前記第1復号化画像データを、第2三原色データを有する第2画像データに変換して前記第2画像データを前記出力端から出力する第2色空間変換回路と、

前記第2復号化回路の前記出力端に接続された入力端及び前記補正データ生成回路の前記入力端に接続された出力端を有し、前記第2復号化画像データを、第3三原色データを有する第3画像データに変換して前記第3画像データを前記出力端から出力する第3色空間変換回路とを更に備えており、

前記圧縮符号化パラメータは、前記輝度データの容量及び前記輝度データを符号化して得られる符号化輝度データの容量に基づいて設定される第1圧縮符号化パラメータと、前記色差データの容量及び前記色差データを符号化して得られる符号化色差データの容量に基づいて設定される第2圧縮符号化パラメータとを有しており、

前記符号化回路は、前記第1及び第2圧縮符号化パラメータのそれぞれに基づいて、前記輝度データ及び前記色差データを符号化して前記符号化輝度データ及び前記符号化色差データを生成すると共に、前記符号化輝度データ及び前記符号化色差データを前記符号化画像データとして前記出力端より出力することを特徴とする、

液晶表示パネル用画像データ処理装置。

【請求項12】

請求項11記載の液晶表示パネル用画像データ処理装置であって、

前記第1及び第2圧縮符号化パラメータは互いに相違しており、

前記輝度データに対する第1圧縮率は前記色差データに対する第2圧縮率よりも小さいことを特徴とする、

10

20

30

40

50

液晶表示パネル用画像データ処理装置。

【請求項 1 3】

請求項 1 1 又は 1 2 に記載の液晶表示パネル用画像データ処理装置であつて、

前記符号化回路は、

前記色差データの第 2 符号化処理を行う前の段階において、前記色差データに対してのみ間引き処理を行う色差データ間引き処理部を備えており、

前記第 1 及び第 2 復号化回路は、共に、

間引かれた画素の前記色差データを得るための補間処理を行う補間回路を備えることを特徴とする、

液晶表示パネル用画像データ処理装置。

10

【請求項 1 4】

請求項 1 1 又は 1 2 に記載の液晶表示パネル用画像データ処理装置であつて、

前記符号化回路は、

前記色差データの第 2 符号化処理を行う前の段階において、前記色差データに対してのみ平滑化処理を行う色差データ平滑化処理部を備えており、

前記第 1 及び第 2 復号化回路は、共に、

平滑化された画素の前記色差データを得るための補間処理を行う補間回路を備えることを特徴とする、

液晶表示パネル用画像データ処理装置。

【請求項 1 5】

請求項 1 乃至 1 4 の何れかに記載の前記液晶表示パネル用画像データ処理装置と、

前記液晶表示パネル用画像データ処理装置に接続された液晶表示パネルとを備えることを特徴とする、

液晶表示装置。

20

【請求項 1 6】

動画像の画像データから、液晶に印加される電圧を決定する補正画像データを生成する画像データ処理方法であつて、

前記画像データの輝度値の時間的な変化に応じて前記液晶の応答速度が速くなる様な印加電圧を与え得る、前記画像データを補正するための少なくとも 2 個の補正候補画像データを生成し、

前記液晶の周囲温度の測定結果に応じて、前記少なくとも 2 個の補正候補画像データの中から、前記周囲温度の下でより最適な応答速度を与え得る 1 個の最適補正候補画像データを前記補正画像データとして決定することを特徴とする、

30

画像データ処理方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は、1 バックライト、液晶（液晶パネル）、及びそのドライバを備える液晶表示パネル（以下、LCD パネルとも称す）と、2 外部から入力するラスターデータの画像データから同パネルの液晶に印加する電圧を決定する補正画像データを生成する画像データ処理装置とを備えた液晶表示装置に関するものであり、特に、入力する動画像の輝度変化に応じて液晶の応答速度（単位時間当たりにおける液晶の透過率の変化量に相当）を最適化するための LCD パネル用画像データの処理技術に関する。

40

【0002】

【従来の技術】

液晶の透過率は累積応答効果により変化するため、LCD パネルは、液晶の応答速度よりも相対的に速い輝度変化を呈する入力動画像に適切に対応出来ないという問題点を内包している。こうした問題点を解決するために、入力動画像の輝度変化時の液晶駆動電圧を通常の駆動電圧よりも意図的に大きく設定することにより、液晶の応答速度を改善する方法が提案されている。

50

## 【0003】

上記方法を適用した液晶駆動により、入力動画像の輝度変化に応じて液晶の応答速度が速くなる様に同応答速度を制御可能にした液晶表示装置の一例の詳細が、日本国特許第2616652号の特許公報（特許文献1）に記載されている。即ち、同文献1に記載された液晶表示装置は、動画面の各画面における各画素を与えるラスター画像データを順次にA/D変換するA/D変換回路、入力動画面の1フレーム分の画像データを保持する画像メモリ（フレームメモリ）、ある画素における現在の画像データと当該画素における1フレーム前の画像データとを比較して輝度変化信号を出力する比較回路、液晶パネルの駆動回路、及び液晶パネルを備えている。

## 【0004】

次に、当該装置の動作について記載する。A/D変換回路は、所定の周波数を有するサンプリングクロックでアナログ形式のラスター画像データをサンプリングした上で、デジタル形式の画像データに変換し、変換後の画像データを画像メモリ及び比較回路に出力する。画像メモリは、各画素の画像データの入力に応じて、当該画素に対応するアドレスに既に格納されている1フレーム前の画像データを読み出して比較回路に出力すると共に、入力した現在の画像データを上記アドレスに上書き保存する。この様に、画像メモリは、入力した各画素の現在画像データを1フレームに相当する期間だけ遅延する遅延回路として機能する。比較回路は、A/D変換回路が出力する現在の画像データと、画像メモリが出力する1フレーム前の画像データとを比較し、両データ間の画像の輝度変化を与える輝度変化信号を、現在の画像データと共に、駆動回路に出力する。駆動回路は、輝度変化信号に基づいて、輝度値が増加した画素に対しては通常の液晶駆動電圧よりも高い駆動電圧を液晶パネルに印加して同パネルの表示画素を駆動し、他方、輝度値が減少した画素に対しては通常値よりも低い駆動電圧を以って同パネルの表示画素を駆動する。

## 【0005】

しかしながら、上記文献1に示された液晶表示装置においては、液晶パネルの表示画素数が多くなると、それに応じて画像メモリに書き込まれる1フレーム分の画像データ数が増加するため、画像メモリとして必要なメモリ容量が大きくならざるを得ないという問題点がある。

## 【0006】

そこで、上記画像メモリの容量削減化を図ると言う観点から、日本国特許第3041951号の特許公報（特許文献2）に記載の液晶表示装置は、4つの画素に対して上記画像メモリの1アドレスを割り当てると言う間引き処理方法を提案している。即ち、同先行文献2は、縦横1画素おきに画素データを間引いて残った各画素データを上記画像メモリに記憶しておくと共に、上記画像メモリの読み出し動作の際には、間引いた隣接する3個の画素に対しては、対応する記憶済み画素の画像データと同じ画像データを3回読み出すことで被間引き画素用画像データを割り当てることで、上記画像メモリの容量の削減化を実現している。例えば、座標（a, A）に位置する画素の画像データが上記画像メモリのアドレス0の領域に格納されているものとすると、（a, B）, (b, A), (b, B)の3個の被間引き画素に対しては、アドレス0の画像データが読み出されて割り当たられる。

## 【0007】

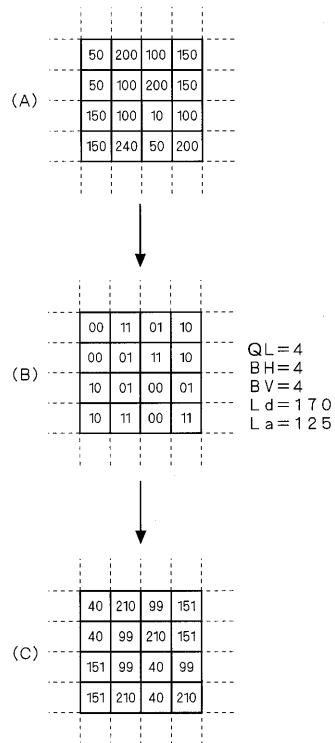

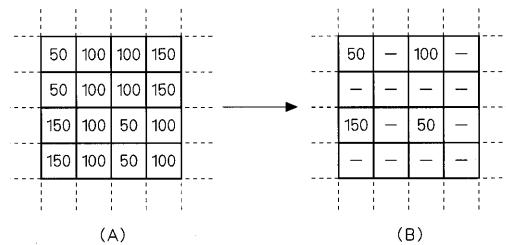

しかしながら、日本国特許第3041951号の特許発明が提案する方法を用いる場合には、却って、次の様な問題点が惹起される。この点を図46(A)～図46(D)に例示する。

## 【0008】

図46(A)はn番目のフレームにおける各画像データを、図46(B)は図46(A)に示すn番目のフレームの画像に対して間引き処理を行った後の各画像データを、図46(C)は間引き処理を行った各画像データを上記読み出し処理によって補間した後の各画像データを、図46(D)は1フレーム後の(n+1)番目のフレームにおける各画像データを、それぞれ表している。図46(A)及び図46(D)に示す様に、n番目のフレームの画像と、(n+1)番目のフレームの画像とは、互いに同じである。

**【 0 0 0 9 】**

間引き処理を行った場合には、図46(C)に示す様に、(B,a)、(B,b)の画素データとして(A,a)の画素データが読み出され、(B,c)、(B,d)の画素データとして(A,c)の画素データが読み出される。つまり、実際は輝度値150の画素データが、輝度値50の画素データとして読み出されることになる。このため、現フレームとその1フレーム前との間では画像が変化していないにも拘わらず、n番目のフレームのアドレス(B,a)、(B,b)、(B,c)、及び(B,d)に対応する各表示画素は、通常よりも高い駆動電圧で駆動されることになる。

**【 0 0 1 0 】**

この様に、間引き処理を行った場合には、画素データが間引かれた部分では電圧の制御が正しく行われなくなり、その結果、不要な電圧が印加されることによる画質劣化が生じ得る。

**【 0 0 1 1 】****【特許文献1】**

特許第2616652号公報

**【特許文献2】**

特許第3041951号公報

**【 0 0 1 2 】****【発明が解決しようとする課題】**

既述の通り、両先行特許発明によれば、現フレームとその1フレーム前との間で輝度値が変化する場合であっても、液晶駆動電圧を通常の液晶駆動電圧よりも大きく設定することにより、液晶の応答速度を改善することが可能である。

**【 0 0 1 3 】**

しかしながら、前者の先行特許発明(特許文献1)は、遅延機能を有する画像メモリの容量の増大化を招くと言う問題点を有しており、後者の先行特許発明(特許文献2)においては、メモリ容量の削減化に伴って画質の劣化を引き起こすと言う問題点を有しており、両者共に一長一短であると言わざるを得ない。

**【 0 0 1 4 】**

加えて、両先行特許発明は、入力動画面の輝度値の変化量と液晶の応答速度との関係のみを考慮するのみであって、液晶パネル及びその近傍の温度と液晶の応答速度との関係については何等の考慮・検討も成されていない。これでは、より実用性に適した液晶表示装置を提供することにはならないと言える。

**【 0 0 1 5 】**

本発明はこの様な懸案事項を解決すべく成されたものであり、その目的は、間引き処理に伴う画質劣化を発生させること無くメモリ容量の削減化を実現しつつ、入力動画面の輝度値の時間的な変化及び液晶表示パネルの周囲温度の変化に応じて、液晶に印加される電圧を適切に制御することにより、液晶の応答速度を正確に制御することが可能な液晶表示パネル用画像データ処理技術を提供することにある。

**【 0 0 1 6 】**

更に、本発明の第2目的は、間引き処理に伴う画質劣化を発生させること無くメモリ容量の削減化を実現しつつ、入力動画面の輝度値の時間的な変化に応じて、液晶に印加される電圧を適切に制御することにより、液晶の応答速度を正確に制御することが可能な液晶表示パネル用画像データ処理技術を提供する点にある。

**【 0 0 1 7 】****【課題を解決するための手段】**

本発明の主題は、液晶表示パネル用画像データ処理装置であって、前記液晶表示パネルに表示すべき動画面の各画素を与えるラスターデータとしての各画像データを順次に受信する入力端と、前記受信画像データを現画像データとして順次に出力する出力端とを有する受信回路と、前記受信回路の前記出力端に接続された入力端及び出力端を有し、前記現画像データを符号化して符号化画像データを前記出力端より出力する符号化回路と、前記符

10

20

30

40

50

号化回路の前記出力端に接続された入力端及び出力端を有し、前記符号化画像データを復号化して前記現画像データに対応する第1復号化画像データを前記出力端より出力する第1復号化回路と、前記符号化回路の前記出力端に接続された入力端及び出力端を有し、前記入力端で受信した前記符号化画像データを前記動画面の1フレーム期間だけ遅延した上で遅延後の前記符号化画像データを遅延符号化画像データとして前記出力端より出力する遅延回路と、前記遅延回路の前記出力端に接続された入力端及び出力端を有し、前記現画像データの出力時に対して前記1フレーム期間だけ前の時点において前記受信回路が前記現画像データとして出力した1フレーム前画像データの符号化画像データを前記入力端で受信し、前記受信符号化画像データを復号化して前記1フレーム前画像データに対応する第2復号化画像データを前記出力端より出力する第2復号化回路と、前記第1復号化回路の前記出力端及び前記第2復号化回路の前記出力端に接続された入力端及び出力端を有し、前記第1復号化画像データ及び前記第2復号化画像データに基づいて、前記現画像データと前記1フレーム前画像データ間の輝度値の変化量を算出し、得られた変化量データを前記出力端より出力する変化量算出回路と、前記受信回路の前記出力端及び前記変化量算出回路の前記出力端に接続された入力端及び出力端を有し、前記現画像データ及び前記変化量データに基づいて前記1フレーム前画像データを再生し、得られた1フレーム前再生画像データを前記出力端より出力する1フレーム前画像再生回路と、少なくとも一つの基準温度データ及び出力端を有しており、前記液晶表示パネル又はその近傍雰囲気の一方の温度データと前記少なくとも一つの基準温度データとを比較し、その比較結果に基づき制御信号を前記出力端より出力する温度制御部と、前記受信回路の前記出力端、前記1フレーム前画像再生回路の前記出力端及び前記温度制御部の前記出力端に接続された入力端及び前記液晶表示パネルに接続された出力端を有し、(1)前記現画像データの第1輝度値と前記1フレーム前再生画像データの第2輝度値とが相違するか否かを検出し、(2)前記第1及び第2輝度値が互いに相違する場合には、前記現画像データ、前記1フレーム前再生画像データ及び前記制御信号に基づいて前記第1輝度値を補正し、補正済み輝度値を与える補正現画像データを前記出力端より出力し、(3)前記第1及び第2輝度値が互いに一致する場合には、前記現画像データを前記補正現画像データとして前記出力端より出力する画像データ補正回路とを備え、前記補正現画像データは、前記補正現画像データに基づき前記液晶表示パネルが生成する液晶印加電圧により実現される液晶の透過率が、前記1フレーム期間の経過時に前記第1輝度値に相当する第1透過率に到達する様に、決定されることを特徴とする。

## 【0018】

## 【発明の実施の形態】

<実施の形態1及び2における着眼点>

ある温度（例えば常温）において、入力動画面における各画素の画像データの輝度値変化に対応して液晶パネルの各表示画素に印加される電圧を最適化しても、少なくとも液晶パネルを含む同パネルの周囲温度が上記ある温度よりも高い場合には、適切な電圧よりも高い電圧が液晶に印加され、その結果、画質の劣化が生じる。即ち、周囲温度が常温よりも高い場合には、液晶の応答速度が常温時のそれよりも速くなり、液晶の透過率がある値から目標値に到達するまでの時間が相対的に短くなる。そのため、補正電圧が常温時のそれと同じままのときには過補正となってしまう。即ち、1フレーム期間に相当する時間の経過時点での透過率は目標値よりも大きな値となり、そのため、表示画面中の明るく変化する部分は過度に明るい部分となり、逆に表示画面中の暗く変化する部分は過度に暗い部分となってしまう。これに対して、周囲温度が上記ある温度よりも低い場合には、逆に補正不足となる。

## 【0019】

本発明の実施の形態1及び2は、この様な周囲温度変化と液晶の応答速度との関係に着目し、この観点を基礎として、入力動画面における画像データの輝度値の時間的变化に応じて液晶の応答速度を最適値に制御するものである（上記輝度値の時間的变化に応じて液晶の応答速度を速くする）。

10

20

30

40

50

**【 0 0 2 0 】**

以下、図面を参照しつつ、実施の形態 1 及び 2 を詳述する。

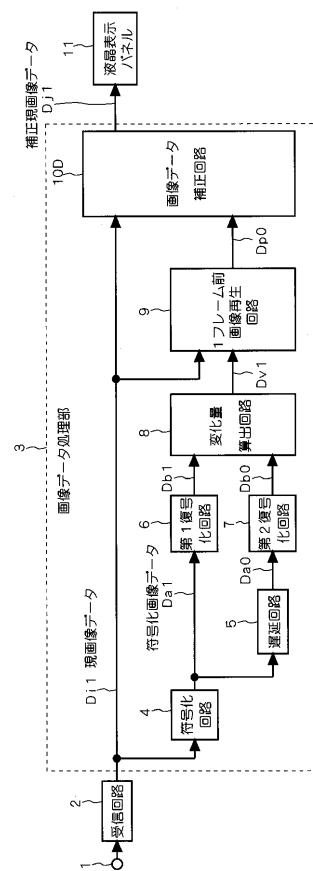

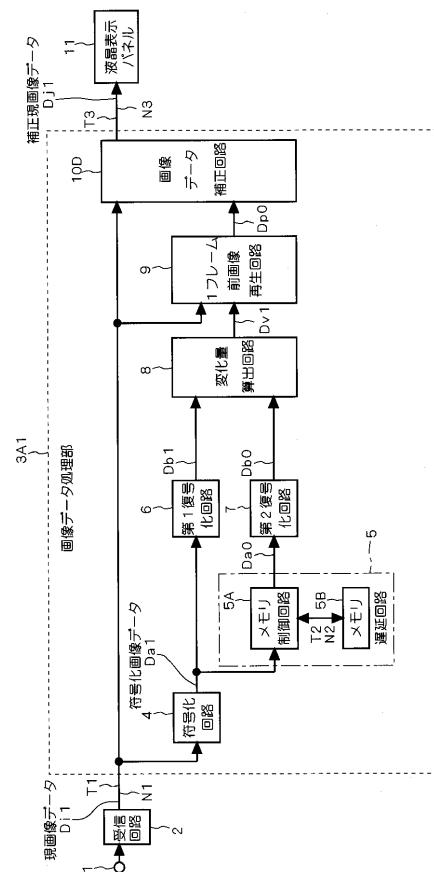

**【 0 0 2 1 】****( 実施の形態 1 )**

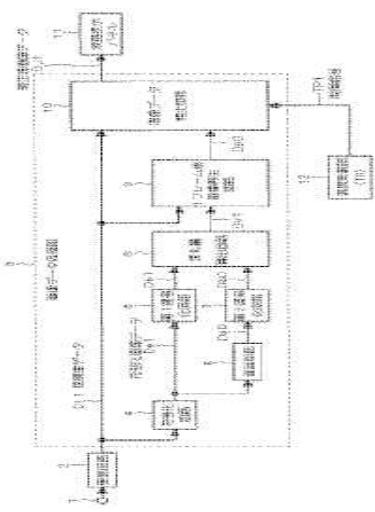

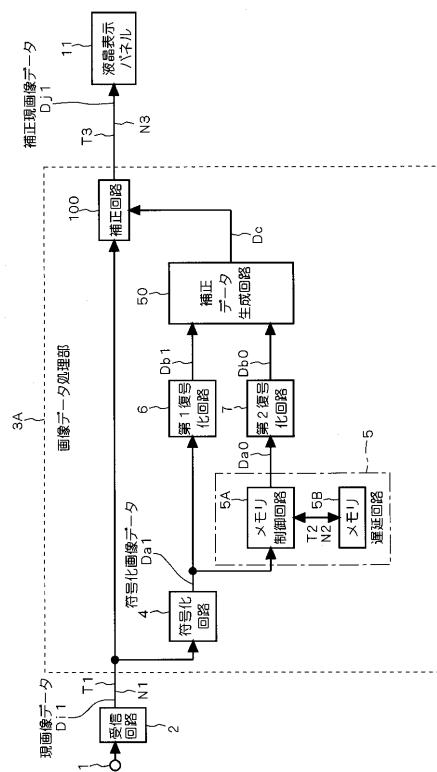

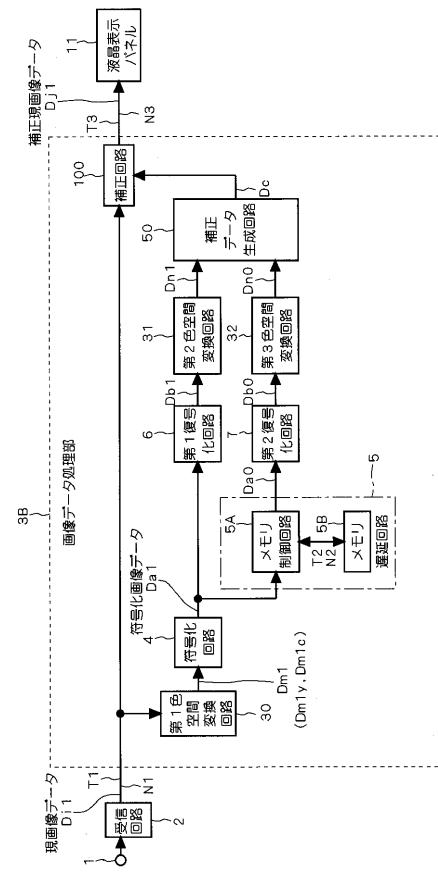

図 1 は、本実施の形態に係る液晶表示装置を示すブロック図である。同装置は、大別して、本装置の中核部分である画像データ処理装置と、当該画像データ処理装置に接続された液晶表示パネル 1 1 とから成る。そして、画像データ処理装置は、受信回路 2 と、画像データ処理部 3 と、温度制御部 1 2 とから構成される。他方、液晶表示パネル 1 1 は、液晶及びその駆動電極等を含む液晶パネル、バックライト及び駆動回路等より成り、画像の輝度または濃度を表す補正画像データ（補正現画像データとも称す）D j 1 を受信し、受信補正画像データ D j 1 に対応する電圧を生成した上で当該電圧を液晶に印加することにより、表示動作を行う。10

**【 0 0 2 2 】**

ここで、画像データ処理装置は、入力する動画像の画像データから、液晶に印加される電圧を決定する補正画像データ D j 1 を生成する部分であるが、その機能を概略的に記載すれば、次の通りである。即ち、本装置は、( I ) 画像データの輝度値の時間的な変化に応じて液晶の応答速度が速くなる様な印加電圧を与える、少なくとも 2 個の、異なる温度下での、補正画像データの候補を生成しておき、( II ) 液晶の周囲温度の測定結果に応じて、少なくとも 2 個の補正画像データの候補中から、周囲温度の下でより最適な応答速度を与える 1 個の候補を最適な補正画像データとして決定する。20

**【 0 0 2 3 】**

以下、この様な機能を実現し得る画像データ処理装置の各部の構成について記載する。

**【 0 0 2 4 】**

先ず、受信回路 2 は、液晶表示パネル 1 1 に表示すべき画面（動画面）（以下、同画面を現画像と称す）の各画素を与える各画像データ（ラスターデータ）を順次に受信する入力端子 1 と、受信した各画像データを現画像データ D i 1 として順次に出力する出力端とを有する。

**【 0 0 2 5 】**

次に、本体たる画像データ処理部 3 は、符号化回路 4 、遅延回路 5 、第 1 復号化回路 6 、第 2 復号化回路 7 、変化量算出回路 8 、1 フレーム前画像再生回路 9 、及び画像データ補正回路 1 0 から成り、現画像データ D i 1 に対応する補正現画像データ D j 1 を生成する。30

**【 0 0 2 6 】**

先ず、符号化回路 4 は、受信回路 2 の出力端に接続された入力端及び出力端を有し、入力する現画像データ D i 1 を符号化して符号化画像データ D a 1 をその出力端より出力する。ここで、同回路 4 における現画像データ D i 1 の符号化方法としては、例えば F B T C 又は G B T C 等のブロック符号化（ B T C ）を用いることができる。あるいは、 J P E G における 2 次元離散コサイン変換符号化、 J P E G - L S における予測符号化、又は J P E G 2 0 0 0 におけるウェーブレット変換等の、任意の静止画用符号化方式を用いることも可能である。尚、こうした静止画用の符号化方法については、符号化前の画像データと復号化された画像データとが完全に一致しない非可逆符号化方式のものであっても適用可能である。40

**【 0 0 2 7 】**

又、第 1 復号化回路 6 は、符号化回路 4 の上記出力端に接続された入力端及び出力端を有しており、受信した符号化画像データ D a 1 を復号化して現画像データ D i 1 に対応する第 1 復号化画像データ D b 1 をその出力端より出力する。

**【 0 0 2 8 】**

又、遅延回路 5 は、符号化回路 4 の上記出力端に接続された入力端及び後述する第 2 復号化回路 7 に接続された出力端を有し、当該入力端で受信した符号化画像データ D a 1 を端子 1 で受信する動画面の 1 フレーム期間だけ遅延した上で、遅延後の符号化画像データ D

10

20

30

40

50

a<sub>1</sub>を遅延符号化画像データD<sub>a</sub>0として上記出力端より出力する。従って、遅延回路5は、符号化画像データD<sub>a</sub>1の受信タイミングに応じて、符号化画像データD<sub>a</sub>1から見て1フレーム期間だけ前の符号化画像データを、遅延符号化画像データD<sub>a</sub>0として出力することになる。

#### 【0029】

ここで、「1フレーム期間」とは、「ある画素のデータを受信して、そのデータに対応する電圧が当該画素に対応する表示画素を成す液晶部分に印加されてから、次のフレームにおける同じ位置の画素のデータを受信して、そのデータに対応する電圧が上記液晶部分に印加されるまでの時間」である。

#### 【0030】

この様な遅延機能を有する同回路5は、例えば、1データの読み出し及び書き込みの両機能を兼ね備えた1個のメモリ(例えばRAM)(図示せず)と、2当該メモリのアドレスを指定する読み出し・書き込み指令信号(アドレス信号)を入力端子1で受信する上記動画面の同期信号(図示せず)に同期させて生成するタイミング回路(図示せず)とから構成される(1メモリ構成)。この構成例の場合には、本回路5は、現在の符号化画像データD<sub>a</sub>1の受信タイミングに応じて、(i)上記1メモリのアドレス(データ格納領域)の内で、当該符号化画像データD<sub>a</sub>1の受信時点から遡って1フレーム期間分だけ前の時点における符号化画像データが格納されている対象アドレスから、上記の1フレーム期間分だけ前の符号化画像データを読み出して当該読み出しデータを遅延符号化画像データD<sub>a</sub>0として出力し、(ii)その直後に、現在の符号化画像データD<sub>a</sub>1を上記対象アドレス内に書き込む。この様な動作によって、本回路5は、現在の符号化画像データD<sub>a</sub>1に対する遅延機能を実現する。本画像データ処理部3においては、メモリに書き込むデータの数とメモリから読み出すデータの数と同じであり、しかも、1画面の左上位置の画素に相当するメモリ領域に格納されている画像データから順番に読み出すだけであり、上記の一例の様に、既に記憶されている画像データの読み出しと新しい画像データの書き込みとを一つのメモリで実現し得るのである。

#### 【0031】

又、遅延回路5の他の構成例として、上記タイミング回路によって同時にアドレス指定される2個のメモリを利用したものが適用可能である(2メモリ構成)。即ち、同回路5は、現在の符号化画像データD<sub>a</sub>1の受信タイミングに応じて、一方のメモリに現在の符号化画像データD<sub>a</sub>1を書き込むと同時に、他方のメモリから、1フレーム期間前に既に書き込み済みの上記1フレーム期間分だけ前の符号化画像データを読み出して当該読み出しデータを遅延符号化画像データD<sub>a</sub>0として出力するのである。

#### 【0032】

以上の通り、遅延回路5は、符号化画像データD<sub>a</sub>1を1フレームに相当する期間だけ遅延する処理を通じて、現画像データD<sub>i</sub>1の1フレーム前の画像データを符号化した遅延符号化画像データD<sub>a</sub>0を出力する。

#### 【0033】

この様に、遅延回路5は、現画像データD<sub>i</sub>1を直接にメモリ内に格納するのではなくて、一旦データ圧縮した後の符号化画像データD<sub>a</sub>1をその構成要素たるメモリ内に格納しているので、同回路5のメモリ容量の削減化を容易に達成出来る。しかも、現画像データD<sub>i</sub>1の符号化率(データ圧縮率)を高くする程に、遅延回路5を構成するメモリの容量を飛躍的に少なくすることが可能である。この点は、既述した2件の先行特許発明には無い利点である。

#### 【0034】

更に、第2復号化回路7は、遅延回路5の上記出力端に接続された入力端、及び出力端を有しており、遅延回路5が出力する遅延符号化画像データD<sub>a</sub>0を復号化する。即ち、第2復号化回路7は、受信回路2からの現画像データD<sub>i</sub>1の出力時に対して1フレーム期間だけ前の時点において受信回路2が現画像データD<sub>i</sub>1として既に出力していた1フレーム前画像データの符号化画像データD<sub>a</sub>0をその入力端で受信し、受信符号化画像データ

10

20

30

40

50

タ D a 0 を復号化して上記 1 フレーム前画像データに対応する第 2 復号化画像データ D b 0 をその出力端より出力する。

#### 【 0 0 3 5 】

更に、変化量算出回路 8 は、第 1 復号化回路 6 の出力端及び第 2 復号化回路 7 の出力端に接続された入力端、並びに出力端を有しており、第 1 復号化画像データ D b 1 及び第 2 復号化画像データ D b 0 に基づいて、現画像データ D i 1 と上記 1 フレーム前画像データ間の輝度値の変化量を算出し、得られた変化量データ D v 1 をその出力端より出力する。一例として、同回路 8 は、減算回路より構成されており、現画像の 1 フレーム前の画像に対応する第 2 復号化画像データ D b 0 から現画像に対応する第 1 復号化画像データ D b 1 を減算することで、画素毎の変化量データ D v 1 を算出する。

10

#### 【 0 0 3 6 】

更に、1 フレーム前画像再生回路 9 は、受信回路 2 の出力端及び変化量算出回路 8 の出力端に接続された入力端、並びに出力端を有しており、現画像データ D i 1 及び変化量データ D v 1 に基づいて 1 フレーム前画像データ D p 0 を再生し、得られた 1 フレーム前再生画像データ D p 0 をその出力端より出力する。具体的には、同回路 9 は、加算回路より構成されており、現画像データ D i 1 に変化量データ D v 1 を加算することで、現画像データ D i 1 から見て 1 フレーム期間だけ前に対応する 1 フレーム前再生画像データ D p 0 を再生する。

20

#### 【 0 0 3 7 】

画像データ補正回路 10 は、画像データ処理部 3 の中核部分を成す回路であり、次の温度制御部 12との関係で、その回路配線及び回路機能が明らかとなる。そこで、画像データ補正回路 10 の詳細に先立ち、温度制御部 12 の構成を記載する。

20

#### 【 0 0 3 8 】

温度制御部 12 は、少なくとも一つの基準温度 (T 0) のデータを保有しており、制御信号 T P 1 を出力するための出力端を有している。そして、同部 12 は、液晶表示パネル 1 1 あるいはその近傍雰囲気の一方の温度データ（この温度データを「周囲温度データ」と定義する）と、少なくとも一つの基準温度データとを比較し、その比較結果に基づき制御信号 T P 1 をその出力端より出力する。一例として、温度制御部 12 は、1 上記周囲温度データを測定し得る温度センサ（尚、温度センサは温度制御部 12 とは別個の外付け部品であっても良い）と、2 当該温度センサの出力端に接続された第 1 入力端と基準温度 (T 0) のデータを与えるレベルが印加された第 2 入力端とを有する比較器とから成り、周囲温度 (T) が基準温度 (T 0) 以下のときには同比較器は第 1 レベル（例えば“1”レベル）の信号として制御信号 T P 1 を出力し、逆に周囲温度 (T) が基準温度 (T 0) よりも高いときには同比較器は第 2 レベル（例えば“0”レベル）の信号として制御信号 T P 1 を出力する。

30

#### 【 0 0 3 9 】

ここで、留意事項として、上記周囲温度について一言する。即ち、温度を測定すべき場所としては、理想的には液晶そのものが対象となるべきところであるが、現実的にはその様な温度を測定出来ないため、その代わりとして、液晶パネルの表面温度、あるいは、液晶パネル近傍の雰囲気の温度が用いられる。そして、液晶パネルは LCD パネル 1 1 内に配設されているので、「周囲温度」とは、結局の所、「液晶表示パネル 1 1 あるいはその近傍雰囲気の一方の温度」と定義されることになる。

40

#### 【 0 0 4 0 】

以上の温度制御部 12 の構成・機能の記載を踏まえて、次に、画像データ補正回路 10 の構成・機能を記載する。即ち、同回路 10 は、受信回路 2 の出力端、1 フレーム前画像再生回路 9 の出力端及び温度制御部 12 の出力端に接続された入力端、並びに、液晶表示パネル 1 1 に接続された出力端を有している。そして、画像データ補正回路 10 は、(1) 現画像データ D i 1 が示す第 1 輝度値と 1 フレーム前再生画像データ D p 1 が示す第 2 輝度値とが互いに相違するか否かを検出し、(2) 第 1 及び第 2 輝度値が互いに相違する場合には、現画像データ D i 1 、1 フレーム前再生画像データ D p 1 及び制御信号 T P 1 に

50

基づいて第1輝度値を補正し、補正済み輝度値を与える補正現画像データDj1をその出力端より出力する。これに対して、同回路10は、(3)第1及び第2輝度値が互いに一致する場合には、現画像データDi1を、補正することなく、補正現画像データDj1としてその出力端より出力する。この場合、補正現画像データDj1は、補正現画像データDj1に基づき液晶表示パネル11が生成する液晶印加電圧により実現される液晶の透過率が、現画像データDi1の受信時から1フレーム期間だけ経過した時点において、第1輝度値に相当する第1透過率に到達する様に、決定される。

#### 【0041】

再度述べると、画像データ補正回路10は、温度制御部12が出力する制御信号TP1に基づいて、補正候補の画像データの補正量が周囲温度に対して適切な補正量となる様に、制御動作を実行する。例えば、液晶の応答速度は温度によって変化するので、温度が比較的高い場合には、同回路10は、補正量を比較的小さな値に設定し、逆に温度が比較的低い場合には、同回路10は補正量を比較的大きな値に設定することで、液晶の応答速度が適切な値となる様に同速度を制御する。

#### 【0042】

最後に、LCDパネル11は、補正現画像データDj1に基づいて作成した電圧を液晶に印加することにより、表示動作を行う。

#### 【0043】

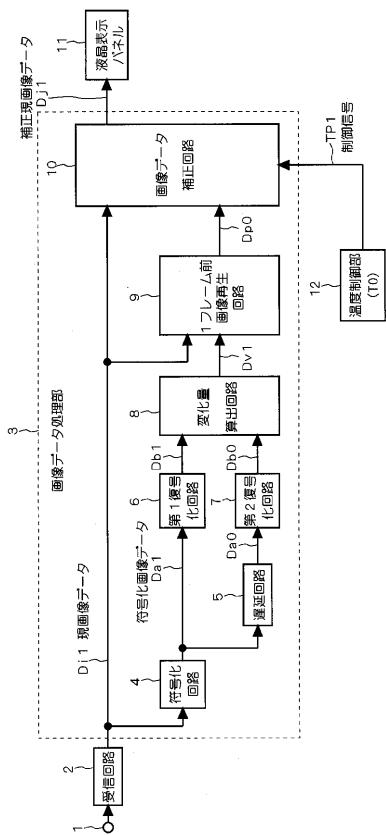

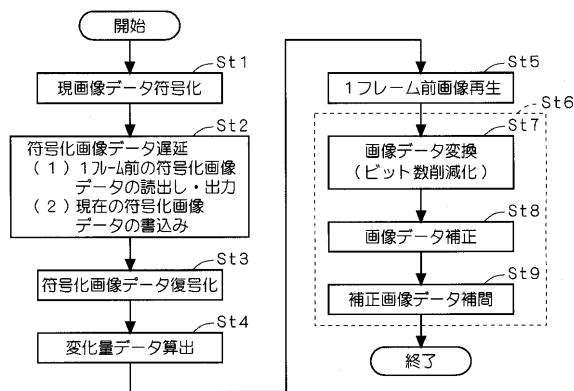

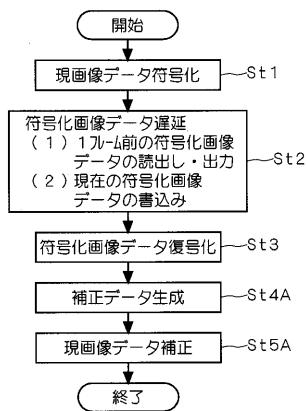

ここで、図2は、以上に記載した図1の画像データ処理装置における一連の動作を、整理する観点から、示すフローチャートである。尚、図2における処理の流れは、1動画面中のある画素についての現画像データが補正現画像データに補正されるまでの工程を模式的に示しており、他の全ての画素データも順次に同様の工程を経て補正される。

#### 【0044】

先ず、現画像データ符号化工程(St1)においては、符号化回路4により、ある1画面内の画素に関する現画像データDi1が符号化され、その符号化画像データDa1が生成される。

#### 【0045】

次の符号化画像データ遅延工程(St2)においては、遅延回路5により、現在の符号化画像データDa1が1フレームに相当する期間だけ遅延される。従って、現時点においては、遅延回路5からは、現画像データDi1の1フレーム前の画像データを符号化した符号化画像データDa0が出力される。本工程における、より具体的な処理としては、現画像データDi1の1フレーム前の画像データを符号化した符号化画像データDa0を遅延回路5内のメモリ(あるいは一方のメモリ)における所定のアドレスから読み出し、且つ、現在の符号化画像データDa1を、現時点から1フレーム後の将来の符号化画像データDa0として、当該メモリ(あるいは他方のメモリ)における上記所定のアドレス(あるいは対応するアドレス)に上書きする(あるいは読み出しと同時並行的に書込む)。

#### 【0046】

更に、符号化画像データ復号化工程(St3)においては、両復号化回路6,7により、両符号化画像データDa1,Da0が同期して復号化され、両復号化画像データDb1,Db0が生成される。

#### 【0047】

次の変化量データ算出工程(St4)においては、変化量算出回路8により、変化量データDv1が生成される。

#### 【0048】

その次の1フレーム前画像再生工程(St5)においては、1フレーム前画像再生回路9により、1フレーム前再生画像データDp0が生成される。

#### 【0049】

更に、現画像データ補正工程(St6)においては、画像データ補正回路10の動作により、現画像データDi1に対応する補正現画像データDj1が生成される。

#### 【0050】

10

20

30

40

50

そして、以上の各工程 S t 1 ~ S t 6 の動作が、現画像データ D i 1 に対して 1 フレーム毎に実行される。

【 0 0 5 1 】

次に、本実施形態の核心を成す画像データ補正回路 1 0 のより具体的な構成・機能について、言及する。

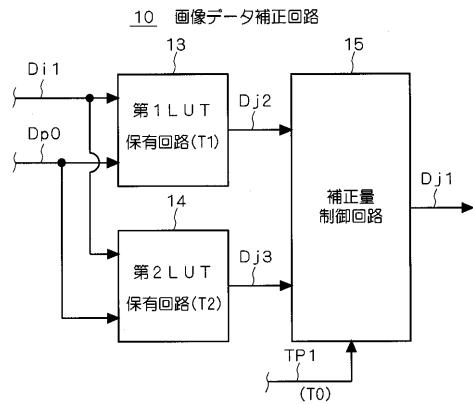

【 0 0 5 2 】

画像データ補正回路 1 0 は、一般的には、( A ) 受信回路 2 の出力端及び 1 フレーム前画像再生回路 9 の出力端に接続された入力端と、出力端とを有する、「少なくとも 2 個のルックアップテーブル保有回路」と、( B ) 少なくとも 2 個のルックアップテーブル保有回路の出力端、及び温度制御部 1 2 の出力端に接続された入力端と、液晶表示パネル 1 1 10 に接続された出力端とを有する「補正量制御回路」とより構成される。

【 0 0 5 3 】

そして、( B ) 補正量制御回路は、少なくとも 2 個のルックアップテーブル保有回路が出力する少なくとも 2 個の補正候補現画像データの内から、制御信号 T P 1 の指令に基づいて、1 個の補正候補現画像データを選択し、被選択補正候補現画像データを補正現画像データ D j 1 として、その出力端から出力する。

【 0 0 5 4 】

これに対して、( A - 1 ) 少なくとも 2 個のルックアップテーブル保有回路の一方である「第 1 ルックアップテーブル保有回路」は、第 1 温度 ( T 1 ) における「第 1 ルックアップテーブル」を保有している。この第 1 ルックアップテーブルは、「液晶表示パネル 1 1 20 又はその近傍雰囲気の温度が第 1 温度 ( T 1 ) にある状況下で、液晶の透過率が 1 フレーム期間内に第 1 輝度値に相当する第 1 透過率に到達し得る様に、n ビット信号である現画像データ D i 1 の第 1 輝度値と、同じく n ビット信号である 1 フレーム前再生画像データ D p 1 の第 2 輝度値との組合せ毎に予め求められた、 $2^n \times 2^n$  個の、第 1 候補値を与える第 1 補正画像データ」を有している。そして、第 1 ルックアップテーブル保有回路は、第 1 ルックアップテーブルにおける $2^n \times 2^n$  個の第 1 補正画像データの中から、現画像データ D i 1 の第 1 輝度値と、1 フレーム前再生画像データ D p 1 の第 2 輝度値との組合せに対応する第 1 候補値を有する第 1 補正画像データを、少なくとも 2 個の補正候補現画像データの一方である第 1 補正候補現画像データとして出力する。

【 0 0 5 5 】

又、( A - 2 ) 少なくとも 2 個のルックアップテーブル保有回路の他方である「第 2 ルックアップテーブル保有回路」は、第 1 温度 ( T 1 ) とは異なる第 2 温度 ( T 2 ) における「第 2 ルックアップテーブル」を保有している。ここで、第 2 ルックアップテーブルは、「液晶表示パネル 1 1 又はその近傍雰囲気の温度が第 2 温度 ( T 2 ) にある状況下で、液晶の透過率が 1 フレーム期間内に第 1 透過率に到達し得る様に、現画像データ D i 1 の第 1 輝度値と 1 フレーム前再生画像データ D p 1 の第 2 輝度値との組合せ毎に予め求められた、 $2^n \times 2^n$  個の、第 2 候補値を与える第 2 補正画像データ」を有している。そして、第 2 ルックアップテーブル保有回路は、第 2 ルックアップテーブルにおける $2^n \times 2^n$  個の第 2 補正画像データの中から、現画像データ D i 1 の第 1 輝度値と、1 フレーム前再生画像データ D p 1 の第 2 輝度値との組合せに対応する第 2 候補値を有する第 2 補正画像データを、少なくとも 2 個の補正候補現画像データの他方である第 2 補正候補現画像データとして出力する。

【 0 0 5 6 】

次に、上記の一般的構成の内で、温度制御部 1 2 が 1 個の基準温度 ( T 0 ) のデータを有しており、且つ、画像データ補正回路 1 0 が 2 個のルックアップテーブル保有回路を有している場合における、画像データ補正回路 1 0 の構成・機能について記載する。又、記載の便宜上、n ビットとは 8 ビットであるものとする。勿論、n ビット信号とは 8 ビット信号に限定される概念ではなく、ビット数が 2 以上の任意の整数値を採り得る信号である。即ち、n ビット信号は、画像データ処理により実質的に補正データを生成することが可能なビット数を有する信号であれば良い。

10

20

30

40

50

## 【0057】

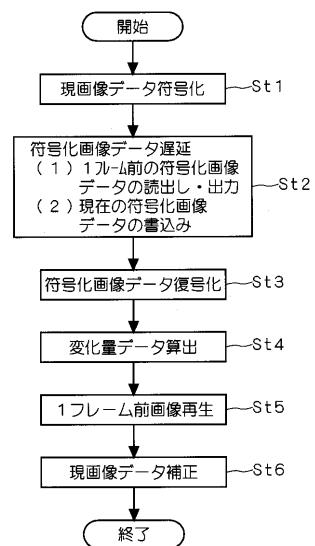

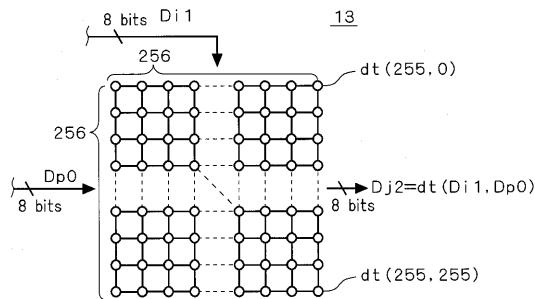

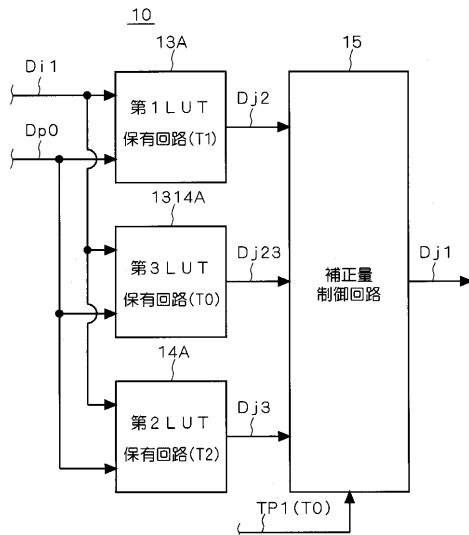

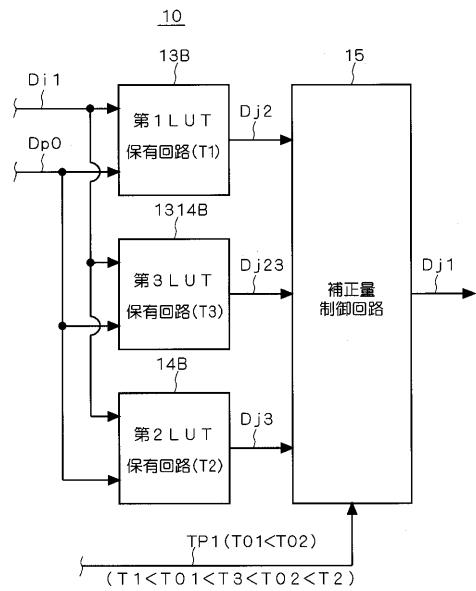

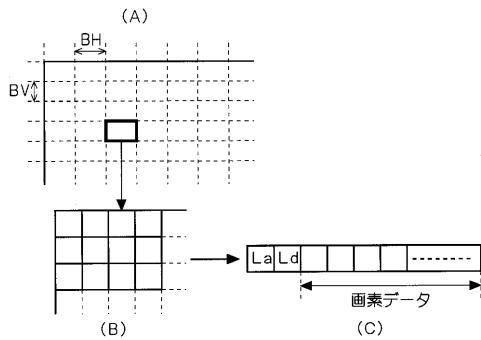

図3は、画像データ補正回路10の内部構成の一例を示すブロック図である。図3に示す様に、同回路10は、1受信回路2の出力端及び1フレーム前画像再生回路9の出力端に接続された入力端を共に有する第1及び第2ルックアップテーブル(以後、ルックアップテーブルを端にLUTと称す)保有回路13,14と、2両回路13,14の出力端に接続された入力端を有する補正量制御回路15とから成る。これらの内で、補正量制御回路15は、第1LUT保有回路13が出力する第1補正候補現画像データDj2と第2LUT保有回路14が出力する第2補正候補現画像データDj3との一方を、制御信号TP1の指令内容に応じて、被選択補正候補現画像データ、即ち、補正現画像データDj1として、選択・出力する。従って、補正量制御回路15はセレクタとしての構成・機能を有する。

## 【0058】

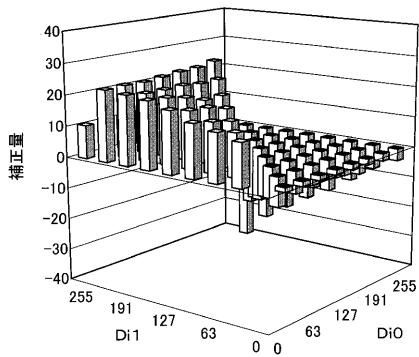

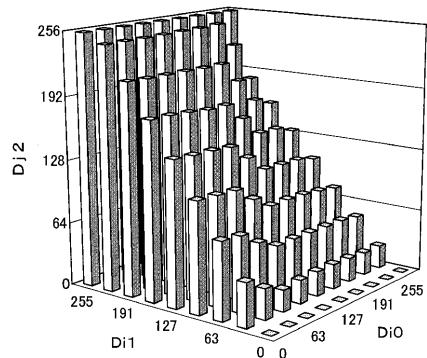

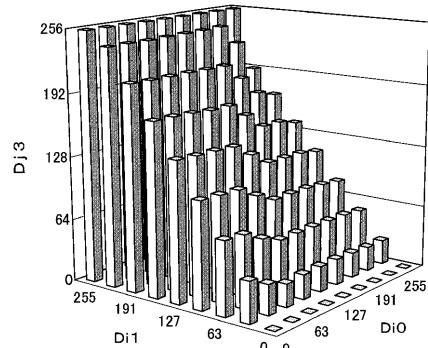

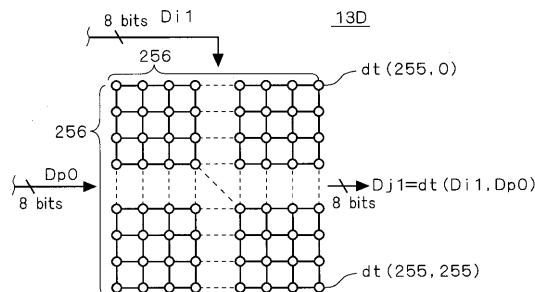

これに対して、第1LUT保有回路13は、基準温度(T0)以下のある温度、即ち、第1温度(T1)におけるLUTデータを第1LUTとして保有ないしは記憶している。例えば、同回路13は、メモリあるいはディスク等の記憶装置より成る。ここで、第1LUTは、液晶表示パネル11又はその近傍雰囲気の温度が上記第1温度(T1)に該当する状況下において、液晶の透過率が1フレーム期間内に第1透過率に到達し得る様に、8ビット信号の現画像データDi1が示す第1輝度値と、同じく8ビット信号の1フレーム前再生画像データDp1が示す第2輝度値との組合せ毎に予め求められた、 $256 \times 256$ 個の第1候補値データ(第1補正画像データ)を有するマトリックス状テーブルである。この様な $256 \times 256$ 個の第1補正画像データを有する第1LUTの構成を模式的に示す図が、図4である。図4に示す様に、現画像データDi1及び1フレーム前再生画像データDp0は、共に8ビット画像データであり、“0”～“255”までの範囲に属する値を取り得る。そして、第1LUTは、2次元に配列される $256 \times 256$ 個の第1候補値データを有している。その結果、第1LUT保有回路13は、現画像データDi1(第1入力信号)の第1輝度値と1フレーム前再生画像データDp0(第2入力信号)の第2輝度値との組合せに対応する第1候補値(換言すれば、上記組合せで指定される格納領域(アドレス)に格納されている第1候補値)を有する第1補正画像データdt(Di1,Dp0)を、第1補正候補現画像データDj2として出力する。尚、第1輝度値と第2輝度値とが互いに等しい場合、つまり、1画面内のある画素における輝度変化が無い場合には、第1LUT保有回路13が出力する第1補正画像データdt(Di1,Dp0)は、現画像データDi1の第1輝度値(=第2輝度値)を与えるデータである。即ち、この場合には、同回路13は、現画像データDi1の輝度値を補正しない。

## 【0059】

又、他方の第2LUT保有回路14は、基準温度(T0)よりも高いある温度、即ち、第2温度(T2)におけるLUTデータを第2LUTとして保有ないしは記憶している。例えば、同回路14は、メモリあるいはディスク等の記憶装置より成る。そして、第2LUTは、液晶表示パネル11又はその近傍雰囲気の温度が上記第2温度(T2)に該当する状況下において、液晶の透過率が1フレーム期間内に第1透過率に到達し得る様に、8ビット信号の現画像データDi1が示す第1輝度値と、8ビット信号の1フレーム前再生画像データDp1が示す第2輝度値との組合せ毎に予め求められた、 $256 \times 256$ 個の第2候補値データ(第2補正画像データ)を有するマトリックス状テーブルである。この様な $256 \times 256$ 個の第2補正画像データを有する第2LUTの構造もまた、基本的に、図4に示したものと同様である。従って、第2LUT保有回路14は、現画像データDi1(第1入力信号)の第1輝度値と1フレーム前再生画像データDp0(第2入力信号)の第2輝度値との組合せに対応する第2候補値(換言すれば、上記組合せで指定される格納領域(アドレス)に格納されている第2候補値)を有する第2補正画像データdt(Di1,Dp0)を、第2補正候補現画像データDj3として出力する。そして、第2温度(T2)下において第1輝度値と第2輝度値とが互いに等しい場合、つまり、1画面内のある画素における輝度変化が無い場合には、第2LUT保有回路14が出力する第2補正

10

20

30

40

50

画像データ  $D_{i1}, D_{p0}$  は、第2温度 ( $T_2$ ) 下における現画像データ  $D_{i1}$  の第1輝度値 (= 第2輝度値) を与えるデータである。即ち、この場合には、同回路 14 は、現画像データ  $D_{i1}$  の輝度値を補正しない。

#### 【0060】

以上の通り、第1LUT保有回路 13 及び第2LUT保有回路 14 が出力する第1補正候補現画像データ  $D_{j2}$  及び第2補正候補現画像データ  $D_{j3}$  は共に、対応するある温度下において、現画像データ  $D_{i1}$  が与える第1輝度値及び1フレーム前再生画像データ  $D_{p0}$  が与える第2輝度値に基づいて、入力画面内の当該画素の表示画素に該当する液晶の部分が1フレーム期間内に当該現画像データ  $D_{i1}$  の第1輝度値に対応する透過率 (第1透過率) となる様に決定された、補正現画像データ  $D_{j1}$  の候補データである。

10

#### 【0061】

そして、図3の補正量制御回路 15 は、温度制御部 12 から出力される制御信号  $TP_1$  に基づいて、補正現画像データ  $D_{j1}$  の両候補データ  $D_{j2}, D_{j3}$  の内から、その一方の補正候補データを、現在の周囲温度下において最適と評価される補正現画像データとして選択し、選択された補正現画像データ  $D_{j1}$  を出力する。例えば、温度制御部 12 が、検出された周囲温度 ( $T$ ) が同部 12 の基準温度 ( $T_0$ ) 以下であることを検出する場合には、同部 12 は、第1補正候補現画像データ  $D_{j2}$  の選択を指令する第1レベル (例えば “1”) の制御信号  $TP_1$  を出力し、この制御信号  $TP_1$  の入力に応じて、補正量制御回路 15 は、第1補正候補現画像データ  $D_{j2}$  を当該周囲温度 ( $T$ ) における最適化された補正現画像データ  $D_{j1}$  として選択する。他方、温度制御部 12 が、検出された周囲温度 ( $T$ ) が同部 12 の基準温度 ( $T_0$ ) よりも高いことを検出する場合には、同部 12 は、第2補正候補現画像データ  $D_{j3}$  の選択を指令する第2レベル (例えば “0”) の制御信号  $TP_1$  を出力し、この制御信号  $TP_1$  の入力に応じて、補正量制御回路 15 は、第2補正候補現画像データ  $D_{j3}$  を当該周囲温度 ( $T$ ) における最適化された補正現画像データ  $D_{j1}$  として選択する。

20

#### 【0062】

尚、第1輝度値と第2輝度値とが等しい場合には、補正量制限回路 15 が第1及び第2補正候補現画像データ  $D_{j2}, D_{j3}$  の何れを選択しようとも、選択後の補正現画像データ  $D_{j1}$  の輝度値は現画像データ  $D_{i1}$  の第1輝度値に等しい。従って、動画面内のある画面中の画素データが与える輝度値と次の画面中の当該画素データが与える輝度値との間に変化が無い場合には、周囲温度 ( $T$ ) の如何に拘わらず、画像データ補正回路 10 は現画像データ  $D_{i1}$  の補正を一切行わない。

30

#### 【0063】

次に、図3の各LUT保有回路 13, 14 におけるLUT内の  $2^n \times 2^n$  個の候補値を与える補正画像データの求め方ないしは決定方法について、図面を参照しつつ言及する。尚、第1及び第2候補値の決定方法は、そのときの周囲温度が異なる点を除いて、基本的に同じであるので、以下の記載では、便宜上、第1候補値を与える第1補正画像データ  $D_{j2}$  を代表例に取上げて記載する。

#### 【0064】

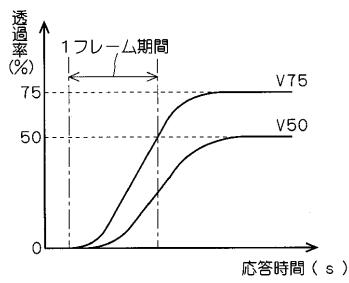

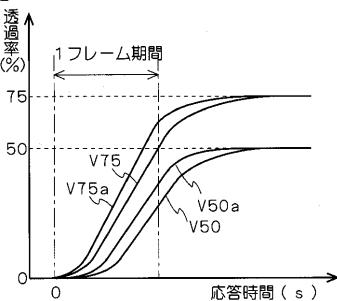

現画像データ  $D_{i1}$  の輝度 (第1輝度) を 8 ビット (0 ~ 255) の情報量として表す場合を考える。このとき、現画像データ  $D_{i1} = 127$  の場合には、当該輝度値に対応する液晶の透過率は 50 % である。この様な透過率 50 % を実現し得る印加電圧を電圧  $V_{50}$  とする。同様に、現画像データ  $D_{i1} = 191$  の場合には、当該輝度値に対応する液晶の透過率は 75 % であり、この様な透過率 75 % を実現し得る印加電圧を電圧  $V_{75}$  とする。ここで、図5は、透過率 0 % の液晶に対して上記電圧  $V_{50}, V_{75}$  を印加した場合の、液晶の応答速度を示す (prior art)。図5に示す様に、電圧  $V_{50}$  及び電圧  $V_{75}$  の何れの場合にも、液晶の透過率が所定の透過率 (50 % 及び 75 %) に到達するには、1フレーム期間よりも長い応答時間をする。従って、入力動画面中のある画素の画像データの輝度値が1フレーム期間経過後に (時間的に) 変化する場合には、「1フレーム期間経過時点における、当該画素に対応する表示画素を成す液晶部分の透過率」が、「現画像

40

10

20

30

40

50

データ D<sub>i</sub>1 が与える第 1 輝度値に対応する所望の透過率」となる様な電圧を、当該液晶部分に印加することにより、液晶の応答速度を向上させることが出来る。

#### 【 0 0 6 5 】

今、現画像データ D<sub>i</sub>1 の輝度値が “0” から “127” に変化する場合を考える。この場合、図 5 に示す様に、電圧 V<sub>50</sub> を液晶に印加したのでは、1 フレーム期間経過時点における液晶の透過率は 50 % に到達し得ないが、電圧 V<sub>75</sub> を液晶に印加するときには、1 フレーム期間経過時点における液晶の透過率は 50 % となる。よって、目標とする透過率が 50 % の場合には、輝度変化に応じて、液晶に印加する電圧を電圧 V<sub>75</sub> に設定することにより、1 フレーム期間内に液晶の透過率を所望の透過率とすることが可能となる。つまり、現画像データ D<sub>i</sub>1 が “0” から “127” に変化する場合、当該現画像データ D<sub>i</sub>1 を補正された現画像データ D<sub>j</sub>2 = 191 として液晶表示パネル 11 に出力することにより、当該現画像データ D<sub>i</sub>1 の受信時から 1 フレーム期間経過時点において液晶の透過率が所望の透過率となる様な電圧が液晶に印加される。10

#### 【 0 0 6 6 】

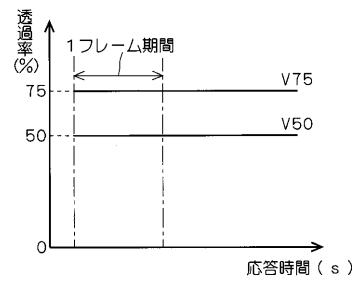

尚、ある画面内における 1 画素のデータが与える輝度値が次の 1 フレーム期間経過後においても変化しないときには、当該画素に対応する表示画素を成す液晶部分は既に当該輝度値を実現し得る透過率を有しているので、液晶の応答速度に変化は無く、補正量は 0 値である。この点を、念の為に、図 6 の応答速度図に示しておく。

#### 【 0 0 6 7 】

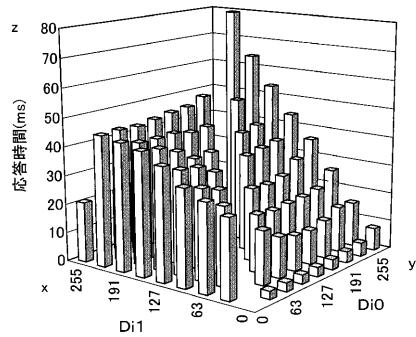

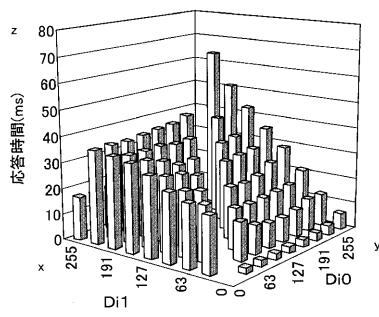

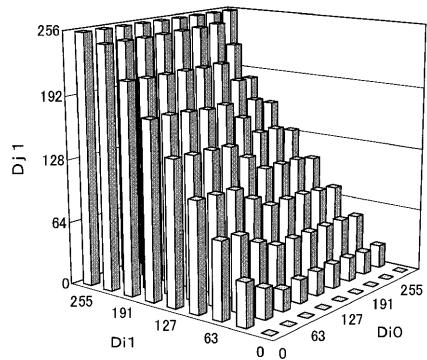

図 7 は、液晶の応答速度の一例を示す図である (prior art)。図 7 において、x 軸は現画像データ D<sub>i</sub>1 の値 (現画像における輝度値) を、y 軸は現画像データ D<sub>i</sub>1 から見て 1 フレーム前の画像データ D<sub>i</sub>0 の値 (1 フレーム前の画像における輝度値) を、z 軸は、液晶が 1 フレーム前の輝度値に対応する透過率から現画像データ D<sub>i</sub>1 の輝度値に対応する透過率を有するまでに要する応答時間を、各々示している。ここで、画像の輝度値が 8 ビットで与えられる場合には、現画像における輝度値、及び、1 フレーム前の画像における輝度値の組み合わせは  $256 \times 256$  通り存在するので、液晶の応答速度の値も  $256 \times 256$  通り存在する。但し、図 7 では、図示の都合上、輝度値の組み合わせに対応する応答速度を  $8 \times 8$  通りの数に簡略化している。20

#### 【 0 0 6 8 】

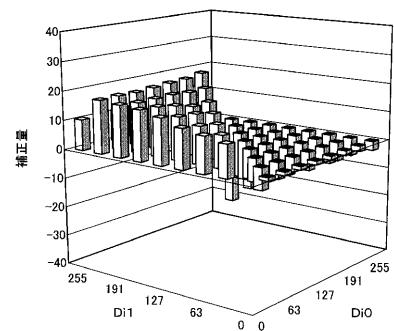

図 8 は、液晶の透過率が 1 フレーム期間経過時点において現画像データ D<sub>i</sub>1 の輝度値に対応する透過率となるために必要な現画像データ D<sub>i</sub>1 の補正量 (輝度補正量： 8 ビット値) を示している (prior art)。現画像データ D<sub>i</sub>1 の輝度値が 8 ビットで与えられる場合、現画像の輝度値及び 1 フレーム前の画像における輝度値の組み合わせに対応して、補正量は  $256 \times 256$  通りの数だけ存在する。但し、ここでも、図示の都合上、図 8 は、 $8 \times 8$  通りに簡略化された補正量を示している。30

#### 【 0 0 6 9 】

図 7 に示す様に、液晶の応答速度は、現画像における輝度値及び 1 フレーム前の画像における輝度値の組合せ毎に異なり、しかも、液晶の材料及び駆動電極の形状等にも依存するので、輝度値の変化に応じて液晶の応答速度を速めるために必要な画像データの補正量を簡単な計算式によって求めることは出来ない。しかしながら、その様な計算式を定立すること自体は困難であるものの、図 9 (prior art) に示す様な補正画像データを作成することは出来る。即ち、各現画像データ D<sub>i</sub>1 に、図 8 に示す  $256 \times 256$  通りの補正量を、1 フレーム前の画像データ D<sub>i</sub>0 の各輝度値に対応させながら加算していくことで、図 9 の補正画像データ D<sub>j</sub>2 が得られる。そこで、図 1 の液晶表示パネル 11 において用いられている液晶について、ある温度 (第 1 温度 T<sub>1</sub>) 下において実際に得られる図 8 のデータを用いて上記の様な加算処理を実際に逐一実行していくことにより得られた、図 9 に相当の補正画像データ D<sub>j</sub>2 を、 $256 \times 256$  個の第 1 時候補値データとして、図 3 の第 1 LUT 保有回路 13 に格納する。その際、第 1 補正画像データ D<sub>j</sub>2 は、液晶表示パネル 11 が表示可能な輝度範囲を超えない様に設定される。40

#### 【 0 0 7 0 】

10

20

30

40

50

この様に、ある温度（第1温度T1）下において実際に得られた補正量データを以って第1LUTデータを構成しているので、液晶の材料及び電極形状等の使用条件に対応した第1補正画像データDj2を有する第1LUT保有回路13を構築することが出来、液晶の特性に応じた応答速度の制御が可能となる。

#### 【0071】

又、図8においては、液晶の応答速度が比較的遅くなる階調変化に対しては補正量が比較的大きくなる様に、補正量が設定されている。即ち、一般的に、液晶の応答速度は階調毎に異なり、例えば、白から黒への階調変化に対しては液晶の応答速度は比較的速いが、暗いグレーから明るいグレーへの階調変化に対しては液晶の応答速度は比較的遅い。そのため、液晶の応答速度が比較的速くなる階調変化については補正量が比較的小さくなる様に、逆に液晶の応答速度が比較的遅くなる階調変化については補正量が比較的大きくなる様に、補正量は設定されている。特に、中間輝度（グレー）から高輝度（白）に階調が変化する際の応答速度は遅い。従って、図8の補正量を定めるに当って、中間輝度を表す1フレーム前再生画像データDp0と、高輝度を表す現画像データDi1との間の差に対応する階調変化量を、正の方向（グレーから白への階調変化の場合）あるいは負の方向（白からグレーへの階調変化の場合）により大きな値に設定することにより、液晶の応答速度を効果的に向上させることが出来、以って、液晶の応答速度が特に遅くなる様な上記輝度変化（階調変化）の場合に対しても適切且つ確実に対応することが可能となる。

#### 【0072】

又、液晶の応答特性は当該液晶の温度によっても変化するので、既述した通り、図3の第2LUT保有回路14には、第1LUTの場合とは異なる第2温度（T2(>T1)）下において液晶の応答速度を効果的に向上させ得る様な補正データが、第2LUTデータとして、書き込まれている。

#### 【0073】

ここで、図10乃至図13(prior arts)は、図5、図7乃至図9に示した液晶の応答速度、補正量、及び補正画像データにおける第1温度(T1)とは異なる第2温度(T2)下における、応答速度、補正量、及び補正画像データの一例を示す図である。図10中、電圧V50及び電圧V75はそれぞれ図5に示す電圧V50,V75に相当しており、参考として描かれている。図10に示す様に、第1温度(T1)よりも高い第2温度(T2)においては、液晶の応答速度は第1温度(T1)のときのそれよりも速くなるので、目標透過率50%を1フレーム期間経過時点において達成するために必要な印加電圧は、電圧V75aよりも小さく且つ電圧V50aよりも大きな値に設定される。尚、図10乃至図13の各図は周囲温度が異なる以外は図5、図7乃至図9の各図と同様の内容を有するので、それらの図面の詳細な説明は割愛する。

#### 【0074】

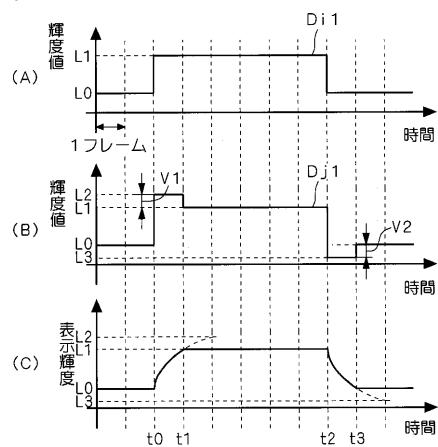

ここで、図14(A)、図14(B)及び図14(C)は、本実施の形態における画像データ処理方法の要点を示すタイミングチャートである。即ち、図14(A)は、時刻t0において輝度値L0からより明るい輝度値L1に変化し、その後は時刻t2直前まで輝度値の变化の無い現画像データDi1を示している。又、図14(B)は補正現画像データDj1の輝度値を示しており、更に図14(C)は、補正現画像データDj1に基づく電圧を液晶に印加したときの表示輝度の変化を示している。

#### 【0075】

補正現画像データDj1は、時刻t0において輝度値L0からより一層明るい輝度値L2(>L1)に変化し、1フレーム期間経過時点の時刻t1において輝度値L1に減少変化する。この様な補正現画像データDj1の設定により、時刻t0から時刻t1までの1フレーム期間内においてのみ、液晶の応答速度は、現画像データDi1に相当する電圧が液晶に印加される場合のそれよりも速くなり、時刻t1において、液晶の透過率は確実に表示輝度L1を実現し得る値に到達する。そして、時刻t1から時刻t2直前までの期間においては液晶の応答速度を速める必要性は無くなっているので、同期間中における補正現画像データDj1は輝度値L1のレベルを維持し続ける。時刻t2において現画像データ

10

20

30

40

50

D<sub>i</sub>1が輝度値L0に戻る場合においても、同様に、より一層速い応答速度を実現する必要性があるため、補正現画像データD<sub>j</sub>1は輝度値L1から輝度値L0よりも暗い輝度値L3へと変化し、その後、時刻t3までの1フレーム期間内、当該輝度値L3を維持する。これにより、表示輝度は、1フレーム期間経過後の時刻t3において、確実に輝度値L0に到達する。

## 【0076】

尚、図14(C)中の破線により示される表示輝度の変化は、時刻t1以降及び時刻t3以降においても、現画像データD<sub>i</sub>1を補正量V1及びV2で補正し続けた場合の表示輝度の変化である。

## 【0077】

次に、図1の画像データ処理部3における符号化処理及び復号化処理時に発生する誤差が補正画像データD<sub>j</sub>1に与える影響について言及する。

## 【0078】

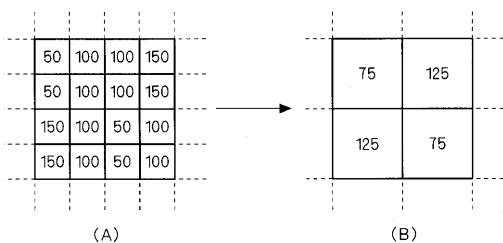

図15(D)は現画像を表す現画像データD<sub>i</sub>1の値を模式的に示す図であり、図15(A)は現画像の1フレーム前の画像を表す画像データD<sub>i</sub>0の値を模式的に示す図である。図15(D)及び図15(A)に示す様に、各現画像データD<sub>i</sub>1とそれに対応する1フレーム前の画像データD<sub>i</sub>0間では、変化はない。

## 【0079】

これに対して、図15(E)及び図15(B)は、それぞれ、図15(D)及び図15(A)に示す現画像データD<sub>i</sub>1及び1フレーム前の画像データD<sub>i</sub>0に対応する符号化画像データを模式的に示す図である。ここでは、図15(E)及び図15(B)は、共にFTBC符号化によって得られる符号化画像データを示しており、代表値(L<sub>a</sub>, L<sub>b</sub>)を8ビットデータとして表し、各画素に1ビットのデータを割り当てている。

## 【0080】

図15(F)及び図15(C)は、それぞれ、図15(E)及び図15(B)に示す符号化画像データを復号化した後の第1及び第2復号化画像データD<sub>b</sub>1及びD<sub>b</sub>0を示している。

## 【0081】

又、図15(G)は、図15(F)及び図15(C)に示す両復号化画像データD<sub>b</sub>1及びD<sub>b</sub>0に基づいて生成される変化量データD<sub>v</sub>1の値を示しており、図15(H)は、図1の1フレーム前画像再生回路9から画像データ補正回路14に出力される、再生された1フレーム前画像データD<sub>p</sub>0の値を示している。

## 【0082】

図15(D)及び図15(F)並びに図15(A)及び図15(C)に示す様に、両復号化画像データD<sub>b</sub>1及びD<sub>b</sub>0に、符号化及び復号化処理に伴う誤差が生じている。しかしながら、図15(F)及び図15(C)に示す両復号化画像データD<sub>b</sub>1及びD<sub>b</sub>0に基づいて変化量データD<sub>v</sub>1を生成することにより、図15(G)に示す通り、各変化量データD<sub>v</sub>1値は何れも0値となる。このため、図15(H)に示す様に、1フレーム前再生画像データD<sub>p</sub>0は、符号化及び復号化により生じる誤差の影響を一切受けることなく、図15(A)の1フレーム前の画像データD<sub>i</sub>0を忠実に再生し得る。従って、最終的に得られる1フレーム前の再生画像データは、符号化及び復号化処理に伴う誤差の影響を受けていないことが、理解される。

## 【0083】

他方、図1の画像データ補正回路10に入力される現画像データD<sub>i</sub>1は画像の符号化処理を施されてはいないので、画像データ補正回路10は、現画像データD<sub>i</sub>1と、誤差の影響を受ける事無く正しく再生された1フレーム前再生画像データD<sub>p</sub>0とに基づき、正しい補正画像データD<sub>j</sub>1を液晶表示パネル11に出力することが出来る。

## 【0084】

尚、上記記載では、画像データ補正回路10が図3に示す2個のLUT保有回路13, 14を有する場合について開示しているが、同回路10の構成がこの形態に限定されるもの

ではないことは明らかである。即ち、3個以上のLUT保有回路を画像データ補正回路10内に設け、周囲温度と基準温度との比較結果を与える制御信号TP1のレベルに応じて、補正量制御回路15がこれらのLUT保有回路を適宜に切り替えることとしても良い。この場合、LUT保有回路の数と基準温度の数とを増やす毎に、各周囲温度における画像データの補正量をより精細に且つ適切に制御することが可能となる。その様な変形例の数例を以下に示す。

#### 【0085】

図16は、温度制御部12が1個の基準温度(T0)のデータを有しており、且つ、画像データ補正回路10が3個のLUT保有回路13A, 1314A, 14Aを有している場合における、画像データ補正回路10の構成を示すブロック図である。これらの構成要素の内で、第1及び第2LUT保有回路13A、14Aは、それぞれ、図3における第1及び第2LUT保有回路13、14に相当しており、第3LUT保有回路1314Aは、温度制御部12が有する基準温度(T0)と同じ周囲温度における、 $256 \times 256$ 個の第3候補値データから成る第3LUTをその格納部分に保有している。そして、補正量制御回路15は、(A)制御信号TP1が $T < T_0$ を示すレベルを有するときには、第1補正候補現画像データDj2を選択し、(B)制御信号TP1が $T = T_0$ を示すレベルを有するときには、第3補正候補現画像データDj23を選択し、(C)制御信号TP1が $T > T_0$ を示すレベルを有するときには、第2補正候補現画像データDj3を選択する。

#### 【0086】

次に、図17は、温度制御部12が2個の基準温度( $T_{01}$ 、 $T_{02}(>T_{01})$ )のデータを有しており、且つ、画像データ補正回路10が3個のLUT保有回路13B, 1314B, 14Bを有している場合における、画像データ補正回路10の構成を示すブロック図である。これらの構成要素の内で、第1及び第2LUT保有回路13B、14Bは、それぞれ、図3における第1及び第2LUT保有回路13、14に相当しており、 $T_1 < T_{01} < T_3 < T_{02} < T_2$ の関係が成立する。そして、第3LUT保有回路1314Bは、温度制御部12が有する第1基準温度( $T_{01}$ )よりも高く且つ第2基準温度( $T_{02}$ )よりも低い第3温度T3における、 $256 \times 256$ 個の第3候補値データから成る第3LUTを、その格納部分に保有している。そして、補正量制御回路15は、(A)制御信号TP1が $T < T_{01}$ を示すレベルを有するときには、第1補正候補現画像データDj2を選択し、(B)制御信号TP1が $T_{01} < T < T_{02}$ を示すレベルを有するときには、第3補正候補現画像データDj23を選択し、(C)制御信号TP1が $T > T_{02}$ を示すレベルを有するときには、第2補正候補現画像データDj3を選択する。この様に、基準温度とLUT保有回路との数が共に図3の場合よりも増えることにより、より一層木目細やかな現画像データDi1の補正が可能となる。

#### 【0087】

本実施の形態によれば、以下の複数の利点が得られる。

#### 【0088】

(I) 符号化回路4により現画像データDi1を符号化してデータ量を圧縮した上で、この圧縮された現画像データを遅延回路5内のメモリに1フレーム期間格納するので、現画像データDi1を1フレーム期間遅延するために必要なメモリの容量を格段に削減することが出来る。しかも、現画像データDi1の画素情報を一切間引かずに現画像データDi1の符号化及び復号化を行うので、ある周囲温度下での、正確な値の補正候補現画像データを発生させることが出来る。

#### 【0089】

(II) 画像データ補正回路10の各LUT保有回路は、現画像データDi1と1フレーム前再生画像データDp0とに基づいて、ある周囲温度下での補正候補現画像データを生成するので、補正候補画像データは、符号化及び復号化処理時に生じる誤差の影響を一切受けない。

#### 【0090】

(III) 画像データ補正回路10は、補正現画像データDj1を生成する際に、周囲温

10

20

30

40

50

度情報を与える制御信号 T P 1 の指令に応じて、複数の補正候補現画像データの中から最適な補正候補現画像データを補正現画像データ D j 1 として選択するので、周囲温度が変化した場合であっても、現画像データ D i 1 を正しく補正することが出来、常に液晶の応答速度を正確に制御することが可能となる。

#### 【 0 0 9 1 】

##### ( 実施の形態 2 )

本実施の形態は、実施の形態 1 における図 1 の画像データ補正回路 1 0 の変形例を提案するものであり、図 1 の液晶表示装置におけるその他の構成要素については何らの変更もない。従って、本実施の形態の記載においては、図 1 の回路構成を援用する。

#### 【 0 0 9 2 】

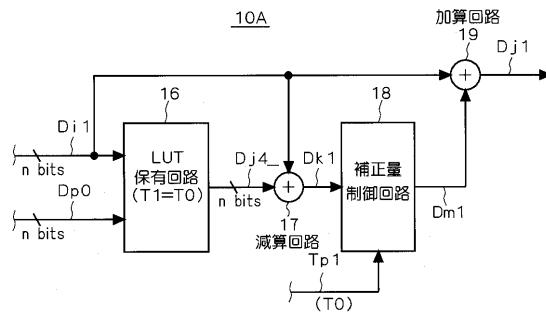

本実施の形態の特徴点は、次の点にある。即ち、本実施の形態では、温度制御部 1 2 は一つの基準温度 T 0 のデータを有しており、画像データ補正回路は、( 1 ) 受信回路 2 の出力端及び 1 フレーム前画像再生回路 9 の出力端に接続された入力端と、出力端とを有し、上記基準温度 T 0 に等しい所定の温度 T 1 における L U T データを保有する 1 つの L U T 保有回路を有し、( 2 ) L U T 保有回路が出力する補正画像データと現画像データ D i 1 との減算処理を行って補正量データを算出し、( 3 ) 補正量データを制御信号 T P 1 の指令に応じて補正して新たな補正量データを生成した上で、( 4 ) 現画像データ D i 1 と新たな補正量データとの加算処理を行って補正現画像データ D j 1 を生成する。以下、図面に基づき、その特徴点を詳述する。

#### 【 0 0 9 3 】

図 1 8 は、本実施の形態に係る画像データ補正回路 1 0 A の構成例を示すブロック図である。L U T 保有回路 1 6 は、基準温度 T 0 (= T 1 ) における L U T を保有しており、当該 L U T は、「液晶表示パネル 1 1 又はその近傍雰囲気の温度（周囲温度）T が基準温度 T 0 にある状況下で、液晶の透過率が 1 フレーム期間内に現画像データ D i 1 の第 1 輝度値に対応した第 1 透過率となる様に、n ビット信号である現画像データ D i 1 の第 1 載度値と n ビット信号である 1 フレーム前再生画像データ D p 0 の第 2 載度値との組合せ毎に予め求められた、 $2^n \times 2^n$  個の、候補値を与える補正画像データ」を有している。ここで、当該 L U T の右下がり対角線上のデータ、即ち、第 1 載度値と第 2 載度値とが互いに等しい輝度変化無しの場合における候補値データは、当該第 1 載度値である（即ち、この場合には補正なし）。この L U T データの求め方は、実施の形態 1 で記載した方法による。

#### 【 0 0 9 4 】

又、減算回路 1 7 は、受信回路 2 の出力端に接続された第 1 入力端と、L U T 保有回路 1 6 の出力端に接続された第 2 入力端と、出力端とを有する。

#### 【 0 0 9 5 】

又、補正量制御回路 1 8 は、減算回路 2 の出力端に接続された第 1 入力端と、温度制御部 1 2 の出力端に接続された第 2 入力端と、出力端とを有する。

#### 【 0 0 9 6 】

更に、加算回路 1 9 は、受信回路 2 の出力端に接続された第 1 入力端と、補正量制御回路 1 8 の出力端に接続された第 2 入力端と、液晶表示パネル 1 1 に接続された出力端とを有する。

#### 【 0 0 9 7 】

次に、画像データ補正回路 1 0 A が有する現画像データ補正機能について記載する。尚、画像データ補正回路 1 0 A 以外の各部分の動作については、実施の形態 1 における対応部分の動作と同様であるので、その記載を割愛する。

#### 【 0 0 9 8 】

L U T 保有回路 1 6 は、上記の通り、予め決められた温度 T 1 (= T 0 ) における、 $2^n \times 2^n$  個の候補値データないしは補正画像データを、L U T データとして、その記憶領域内に格納している。そして、同回路 1 6 は、L U T 内における $2^n \times 2^n$  個の補正画像データの中から、入力した現画像データ D i 1 の第 1 載度値と、入力した 1 フレーム前再生画像データ D p 0 の第 2 載度値との組合せに対応する（換言すれば、当該組合せで定められ

10

20

30

40

50

るアドレス内に格納されている)候補値を有する補正画像データ(  $n$  ビット信号)を、補正候補現画像データ  $D_{j4}$  として出力する。

#### 【0099】

その後、減算回路17は、LUT保有回路16が出力する補正候補現画像データ  $D_{j4}$  から現画像データ  $D_{i1}$  を減算して、現画像データ  $D_{i1}$  に対する補正量データ  $D_{k1}$  を決定・出力する。

#### 【0100】

次に、補正量制御回路18は、(A)減算回路17の出力データ  $D_{k1}$  が0値を示すときには減算回路17の出力データ  $D_{k1}$  をそのまま出力し、(B)減算回路17の出力データが0値でないときには、減算回路17の出力データ及び制御信号TP1に基づいて、補正済み輝度値と第1輝度値との差分に相当する補正量データ  $D_{m1}$  を生成し、補正量データ  $D_{m1}$  をその出力端より出力する。

10

#### 【0101】

ここで、上記(B)の機能をより具体的に記載するならば、次の通りである。即ち、補正量制御回路18は、温度制御部12が出力する制御信号TP1に基づいて、補正量データ  $D_{k1}$  が適切値になる様に補正量データ  $D_{k1}$  を補正(制御)して、新たな補正量データ  $D_{m1}$  を生成・出力する。その際の補正方法は、次の通りである。

#### 【0102】

(B-1) 第1制御：検出された周囲温度Tが上記基準温度  $T_0$  (=  $T_1$ ) よりも高い場合には、温度制御部12は、その状況を示す第1レベルを有する制御信号TP1を、補正量制御回路18に出力し、制御信号TP1の当該指令内容に応じて、補正量制御回路18は、補正量データ  $D_{k1}$  の値が小さくなる様に、同データ  $D_{k1}$  の値を制御する。その際の補正方法としては、例えば、正の定数  $\alpha$  を用いて、 $D_{m1} = D_{k1} - \alpha$  で与えられる関係式を利用して、新たな補正量データ  $D_{m1}$  を生成しても良く、あるいは、 $D_{m1} = D_{k1} + \beta \times (T_0 - T)$  で与えられる関係式を利用して、新たな補正量データ  $D_{m1}$  を生成しても良い。

20

#### 【0103】

(B-2) 第2制御：逆に周囲温度Tが上記基準温度  $T_0$  (=  $T_1$ ) よりも低い場合には、温度制御部12は、その状況を示す第2レベルを有する制御信号TP1を、補正量制御回路18に出力し、制御信号TP1の当該指令内容に応じて、補正量制御回路18は、補正量データ  $D_{k1}$  の値が大きくなる様に、同データ  $D_{k1}$  の値を制御する。その際の補正方法としては、例えば、正の定数  $\alpha$  を用いて、 $D_{m1} = D_{k1} + \alpha$  で与えられる関係式を利用して、新たな補正量データ  $D_{m1}$  を生成しても良く、あるいは、 $D_{m1} = D_{k1} + \beta \times (T_0 - T)$  で与えられる関係式を利用して、新たな補正量データ  $D_{m1}$  を生成しても良い。

30

#### 【0104】

勿論、補正量制御回路18は、周囲温度が高い場合の第1制御(B-1)と、周囲温度が低い場合の第2制御(B-2)の何れか一方だけの制御によって、新たな補正量データ  $D_{m1}$  を生成・出力することとしても良い。

#### 【0105】

(B-3) 第3制御：周囲温度Tが上記基準温度  $T_0$  (=  $T_1$ ) (例えば常温)に等しい場合には、温度制御部12は、その状況を示す第3レベルを有する制御信号TP1を、補正量制御回路18に出力し、制御信号TP1の当該指令内容に応じて、補正量制御回路18は、入力した補正量データ  $D_{k1}$  の値を新たな補正量データ  $D_{m1}$  として出力する。即ち、この場合には、補正量制御回路18は、補正量データ  $D_{k1}$  に対する補正を行わない。

40

#### 【0106】

最後に、加算回路19は、新たな補正量データ  $D_{m1}$  を現画像データ  $D_{i1}$  に加算して、加算後のデータを補正現画像データ  $D_{j1}$  として液晶表示パネル11に出力する。

#### 【0107】

本実施の形態によっても、実施の形態1において記載した利点(III)と同様の利点が得られる。

#### 【0108】

##### (実施の形態2の変形例1)

本変形例は、実施の形態2におけるLUT保有回路16を変更する点に、その特徴点を有しており、図18中の他の構成要素に変更は無い。以下、図面に基づき、本変形例の特徴点を詳述する。

#### 【0109】

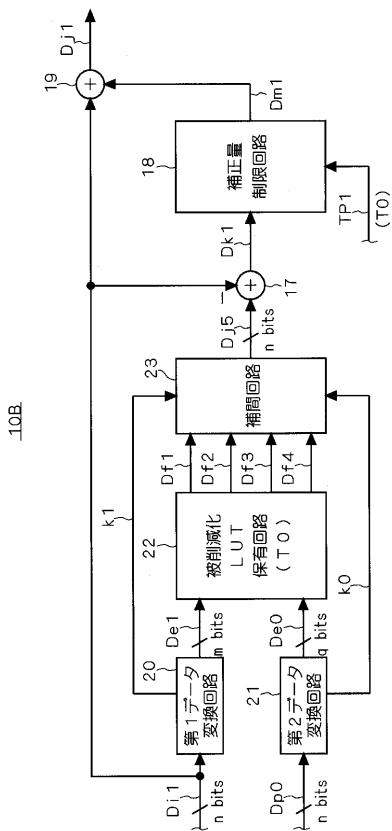

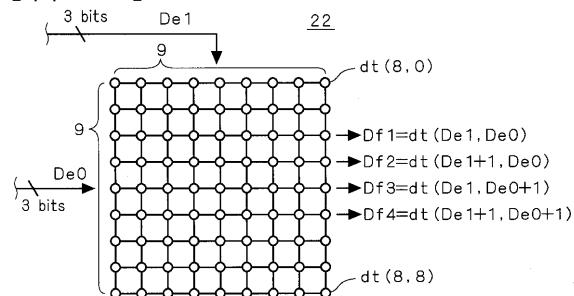

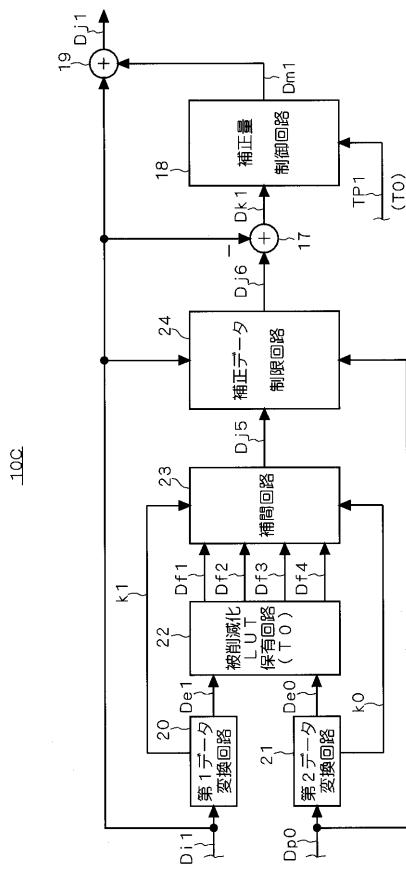

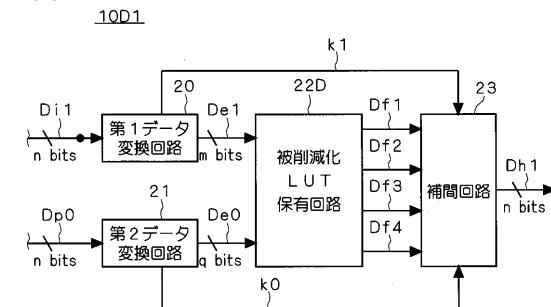

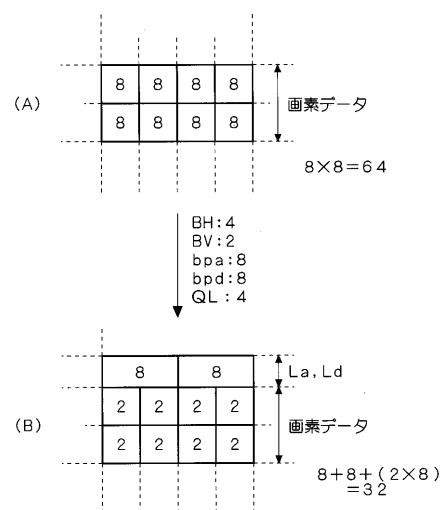

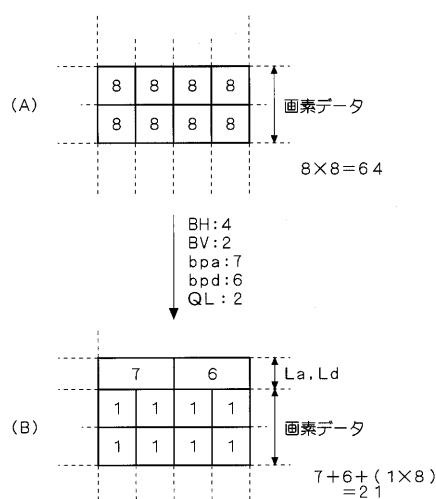

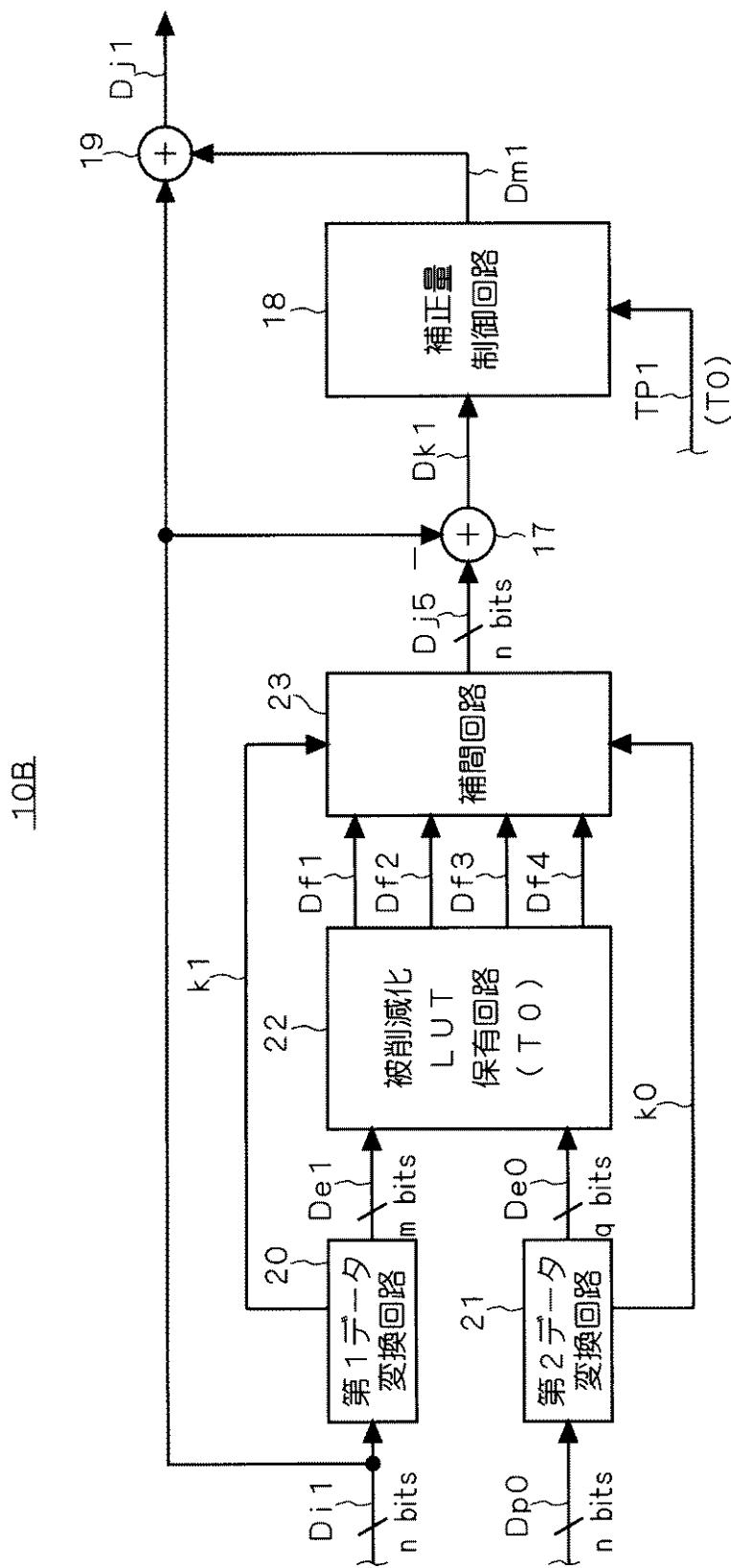

図19は、本変形例に係る画像データ補正回路10Bの構成を示すブロック図である。図19中、図18中の構成要素と同一のものには、同一の参照符号が付されている。図19において、第1データ変換回路20は、線形量子化あるいは非線形量子化等の量子化処理によって、入力した現画像データDi1のビット数nをビット数m(m < n)に削減する。同様に、第2データ変換回路21は、線形量子化あるいは非線形量子化等の量子化処理によって、入力した1フレーム前再生画像データDp0のビット数nをビット数q(q < n)に削減する。被削減化LUT保有回路22は、実施の形態1で記載した決定方法と同様の方法に基づいて予め決定された基準温度T0における被削減化LUTデータを、その記憶部内に保有している。この被削減化LUTは、 $(2^m + 1) \times (2^q + 1)$ 個の、候補値を与える補正画像データから成る。そして、各候補値は、液晶表示パネル11又はその近傍雰囲気の温度(周囲温度)Tが基準温度T0にある状況下で、液晶の透過率が1フレーム期間内に現画像データDi1の第1輝度値に対応した第1透過率となる様に、mビット信号である削減化された現画像データDe1の輝度値とqビット信号である削減化された1フレーム前再生画像データDe0の輝度値との組合せ毎に求められている。ここでも、削減化された現画像データDe1の輝度値と削減化された1フレーム前再生画像データDe0の輝度値とが等しい場合には、補正不要であり、被削減化LUTの右下がり対角線上の候補値データは、削減化された現画像データDe1の輝度値に等しい。そして、被削減化LUT保有回路22は、入力した両データDe1、De0に応じて、両データDe1、De0の輝度値の組合せに対応する候補値データと、当該候補値データに隣接する3個の隣接候補値データとを出力する。補間回路23は、2個の補間係数に基づき、入力した4個の被削減化画像補正データの補間処理を行って、図18のデータDj4に対応するnビットの補正候補現画像データDj5を生成する。以下では、記載の便宜上、n = 8及びm = q = 3の場合について、図19の回路10Bの動作を記載する。

#### 【0110】

第1及び第2データ変換回路20、21は、それぞれ、現画像データDi1及び1フレーム前再生画像データDp0の量子化ビット数を、8ビットから3ビットに削減した上で、削減化された現画像データDe1及び削減化された1フレーム前再生画像データDe0を生成・出力する。と同時に、両データ変換回路20及び21は、それぞれ、第1及び第2補間係数k0及びk1を算出し、これらの補間係数を与える信号を補間回路23へ出力する。

#### 【0111】

被削減化LUT保有回路22は、3ビット現画像データDe1及び3ビット1フレーム前再生画像データDe0の入力タイミングに応じて、4個の補正画像データDf1～Df4を出力する。

#### 【0112】

補間回路23は、補正画像データDf1～Df4及び補間係数k0、k1に基づいて、補間された8ビットの補正候補現画像データDj5を生成・出力する。

#### 【0113】

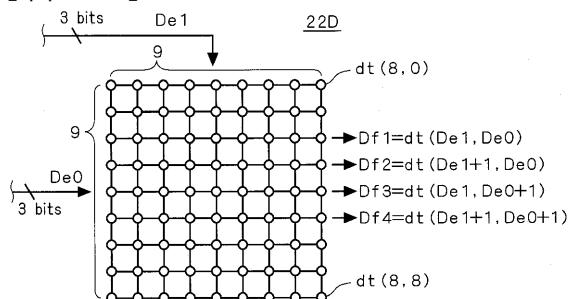

図20は、図19に示す被削減化LUT保有回路22が有するLUTの構成を模式的に示す図である。ここでは、ビット数変換された現画像データDe1及びビット数変換された1フレーム前再生画像データDe0は、共に3ビットのデータであり、0～7の範囲内の値を取り得る。図20に示す様に、被削減化LUTは、2次元に配列される9×9個の候

10

20

30

40

50

補値データから成り、被削減化 LUT 保有回路 22 は、3 ビットの現画像データ D e 1 の輝度値、及び、3 ビットの 1 フレーム前再生画像データ D b 0 の輝度値に対応するアドレスに格納されている補正画像データ d t ( D e 1 , D e 0 ) を第 1 候補値を与える第 1 補正画像データ D f 1 として出力し、更に、第 1 補正画像データ D f 1 に隣接する 3 つの補正画像データ d t ( D e 1 + 1 , D e 0 ) , d t ( D e 1 , D e 0 + 1 ) , d t ( D e 1 + 1 , D e 0 + 1 ) を、それぞれ第 2 、第 3 及び第 4 補正画像データ D f 2 , D f 3 , D f 4 として、出力する。

## 【0114】

次に、補間回路 23 における補間処理の詳細について記載する。

## 【0115】

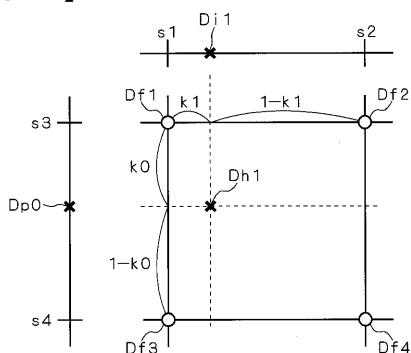

補間回路 23 は、第 1 ~ 第 4 補正画像データ D f 1 ~ D f 4 、及び、第 1 及び第 2 補間係数 k 1 , k 0 を用いて、以下の式(1)により、補間された補正画像データ(補正候補現画像データ) D j 5 を生成する。

## 【0116】

## 【数 1】

$$D j 5 = (1 - k 0) \times \{ (1 - k 1) \times D f 1 + k 1 \times D f 2 \} \\ + k 0 \times \{ (1 - k 1) \times D f 3 + k 1 \times D f 4 \} \quad \cdots (1)$$

## 【0117】

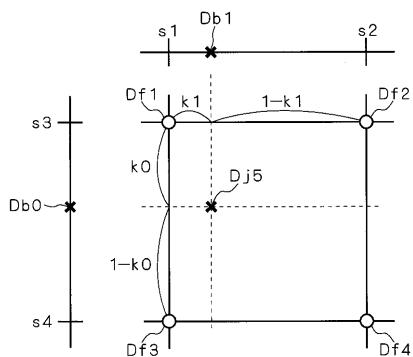

図 21 は、上記式(1)により表される補間後の補正画像データ D j 5 の算出方法を示す図である。図 21において、s 1 , s 2 は、第 1 データ変換回路 20 が現画像データ D i 1 の量子化ビット数を変換する際に用いられる閾値であり、s 3 , s 4 は、第 2 データ変換回路 21 が 1 フレーム前再生画像データ D p 0 の量子化ビット数を変換する際に用いられる閾値である。しかも、s 1 は、ビット数変換された現画像データ D e 1 に対応する閾値であり、s 2 は、ビット数変換された現画像データ D e 1 よりも 1 だけ大きい現画像データ( D e 1 + 1 )に対応する閾値である。又、s 3 は、ビット数変換された 1 フレーム前再生画像データ D e 0 に対応する閾値であり、s 4 は、ビット数変換された 1 フレーム前再生画像データ D e 0 よりも 1 だけ大きい 1 フレーム前再生画像データ( D e 0 + 1 )に対応する閾値である。

## 【0118】

このとき、第 1 及び第 2 補間係数 k 1 及び k 0 は、それぞれ、以下の式(2)及び式(3)により決定される。

## 【0119】

## 【数 2】

$$k 1 = (D b 1 - s 1) / (s 2 - s 1) \quad \cdots (2)$$

但し、 $s 1 < D b 1 \leq s 2$

## 【0120】

## 【数 3】

$$k 0 = (D b 0 - s 3) / (s 4 - s 3) \quad \cdots (3)$$

但し、 $s 3 < D b 0 \leq s 4$

## 【0121】

上記式(1)に示す補間演算処理により補間された補正候補現画像データ D j 5 は、減算回路 17 に出力される。以降の動作は、図 18 に関して記載した動作と同じである。

## 【0122】

以上の通り、本回路 10B は、現画像データ D i 1 及び 1 フレーム前再生画像データ D p 0 のビット数を変換する際に算出される第 1 及び第 2 補間係数 k 0 , k 1 を用いて、ビット数変換された 4 つのデータ( D e 1 , D e 0 )、( D e 1 + 1 , D e 0 )、( D e 1 ,

10

20

30

40

50

$D_{e0+1}$  )、及び(  $D_{e1+1}$  ,  $D_{e0+1}$  )に対応する4つの補正画像データ  $D_f1$  ,  $D_f2$  ,  $D_f3$  ,  $D_f4$  から、その補間値  $D_j5$  を決定している。従って、第1及び第2データ変換回路20及び21の動作時に生じ得る量子化誤差が補間値たる補正候補現画像データ  $D_j5$  に与える影響を低減することが出来る。即ち、補間を行わない場合には、LUT上の格子点以外のデータを選択しようとしても一番近い格子点のデータが用いられるので、そのことにより誤差が生じるが、補間する場合には、格子点間のデータを演算することが出来るため、格子内のデータの連続性が保たれている限り、誤差が減少するのである。

#### 【0123】

尚、第1及び第2データ変換回路20及び21は、線形量子化以外の非線形量子化によって、入力データのビット数削減を行うことも出来る。例えば、非線形量子化によりビット数を変換する際に、補正画像データの変化(隣接する補正画像データ間の差)が大きい領域では量子化密度を相対的に高く設定することにより、ビット数削減に伴う補正候補現画像データ  $D_j5$  の誤差を低減することが出来る。10

#### 【0124】

既述した通り、両データ変換回路20及び21によるデータ変換処理後のデータのビット数は、3ビットに限られるものではなく、補間回路23によって補間することで実質的に使用可能な補正候補現画像データ  $D_j5$  を求め得るビット数であれば良い。その限りで、任意のビット数をデータ変換処理後のデータビット数として選択することが出来る。勿論、量子化ビット数の値に応じて、被削減化LUT保有回路22が有する補正画像データの個数もまた変化する。20

#### 【0125】

更に、両データ変換回路20及び21によるデータ変換後の各データ  $D_{e1}$  及び  $D_{e0}$  のビット数  $m$  及び  $q$  が、互いに異なっていても良い。

#### 【0126】

又、両データ変換回路20及び21における第1及び第2データ変換の内の何れか一方を実施しない様にすることも可能である。この様な変形として、例えば第1データ変換回路20を図19の回路構成から除去するときには、被削減化LUT保有回路22には8ビット及び3ビットのデータが入力することとなり、同回路22は、 $257 \times 9$  個あるいは $256 \times 9$  個の補正画像データを被削減化LUTとして有する。この場合、第1補間係数  $k_1$  は0値となるので、補間値  $D_j5$  は、 $k_1 = 0$  を式(1)に代入することで、求められる。その際に被削減化LUTから抽出されて補間に利用される補正画像データは、第1及び第3補正画像データ  $D_f1$  ,  $D_f3$  の2つである。逆に、第2データ変換回路21を用いない場合には、同回路22は $9 \times 257$  個あるいは $9 \times 256$  個の補正画像データを被削減化LUTとして有し、且つ、 $k_0 = 0$  を式(1)に代入することで補間値  $D_j5$  は決定される。その際に被削減化LUTから抽出されて補間に利用される補正画像データは、第1及び第2補正画像データ  $D_f1$  ,  $D_f2$  の2つである。30

#### 【0127】

又、補間回路23を、線形補間以外の補間演算を用いて、例えば高次の関数を用いた補間演算を用いて、補正候補現画像データ  $D_j5$  を決定する様に、構成しても良い。40

#### 【0128】

##### (実施の形態2の変形例2)

本変形例は、実施の形態2の変形例1を改良するものである。

#### 【0129】

図22は、本変形例に係る画像データ補正回路10Cの構成を示すブロック図であり、図22の回路が図19の回路と唯一相違する点は、新たに補正データ制限回路24を追加した点にある。

#### 【0130】

補正データ制限回路24は、(1)先ず、現画像データ  $D_{i1}$  及び1フレーム前再生画像データ  $D_{p0}$  に基づいて、両データ  $D_{i1}$  及び  $D_{p0}$  が互いに等しいか否かを検出し、( 50

2) 両データ  $D_{i1}$  及び  $D_{p0}$  が互いに等しくない場合には、補正候補現画像データ  $D_{j5}$  をそのまま補正候補現画像データ  $D_{j6}$  として出力し（補正データの制限なし）（ $D_{j6} = D_{j5}$ ）、（3）現画像データ  $D_{i1}$  と 1 フレーム前再生画像データ  $D_{p0}$  とが互いに等しい時には、補間回路 23 が output する補正候補現画像データ  $D_{j5}$  の代わりに、現画像データ  $D_{i1}$  を補正候補現画像データ  $D_{j6}$  として出力する（補正データの制限有り）（ $D_{j6} = D_{i1}$ ）。

#### 【0131】

この様な機能を有する補正データ制限回路 24 を且回路 23 及び 17 間に介在させることにより、次の様な利点が得られる。即ち、現画像データ  $D_{i1}$  と 1 フレーム前再生画像データ  $D_{p0}$  とが互いに等しい場合、つまり、動画面中のある画素の画像データ（輝度）に変化が無い場合において、第 1 及び第 2 データ変換回路 20 及び 21 によるビット数削減と、補間回路 23 による補間演算との実行に伴い発生し得る画像データの補正誤差が、減算回路 17 に入力される補正候補現画像データ内に含まれてしまう事態を確実に回避することが可能となる。

#### 【0132】

尚、現画像データ  $D_{i1}$  と 1 フレーム前再生画像データ  $D_{p0}$  との差が比較的少ない場合においても、補正データ制限回路 24 が、（A）補間回路 23 が output する補正候補現画像データ  $D_{j5}$  の代わりに、現画像データ  $D_{i1}$  を最終的な補正候補現画像データ  $D_{j6}$  として出力する様にしても良い。あるいは、補正データ制限回路 24 が、（B）補正量が少なくなる様に補間回路 23 が output する補正候補現画像データ  $D_{j5}$  を制限する様にしても良い。より具体的には、補正データ制限回路 24 が、現画像データ  $D_{i1}$  と 1 フレーム前再生画像データ  $D_{p0}$  との差分値の絶対値が、予め決められた値（ $S_h$ ）よりも小さいことを検出した場合には、同回路 24 は、以下の式（4）及び式（5）により定められるデータ処理に基づいて、補間回路 23 が output する補正候補現画像データ  $D_{j5}$  を制限することが出来る。

#### 【0133】

#### 【数4】

$$D_{j6} = D_{i1} + m \times (D_{j5} - D_{i1}) \quad \dots (4)$$

$$m = f(S_h - |D_{i1} - D_{p0}|) \quad \dots (5)$$

但し、 $f(S_h - |D_{i1} - D_{p0}|)$  は、 $S_h - |D_{i1} - D_{p0}|$  における任意の関数である。

#### 【0134】

この様な制限処理により、補間時に生じる誤差を補正することが可能となる。即ち、両データ  $D_{i1}$  及び  $D_{p0}$  が互いに等しい場合には、補間の際に用いられる LUT 内の対角線上の格子点（2 点）におけるデータの補正量は共に 0 値であるが、逆向きの対角上における 2 点の補正量が 0 値ではない。そのため、その分の補正量が補間処理により誤差として発生してしまうところ、上記の様な制限処理を施すことにより、この誤差を低減化する方向で補正することが出来る。特に、対角線に近い部分の誤差を少なくすることが出来る。

#### 【0135】

#### （実施の形態 3）

本実施の形態は、既述した第 2 目的を達成するための構成例を提案するものである。即ち、本実施の形態においては、実施の形態 1 及び 2 とは異なり、液晶表示パネルの周囲温度の変化と言う点は考慮外である。従って、本実施の形態を以下に詳述するに際しては、実施の形態 1 及び 2 の記載と重複する箇所が多々生じることとなる。このため、その様な重複箇所の記載に関しては、適宜、実施の形態 1 及び 2 の記載及び対応図面を援用することとする。

#### 【0136】

但し、本実施の形態の詳述に先だって、以下の指摘（問題認識）が本実施の形態における

10

20

30

40

50

思考の出発点を成しているので、再度、既述した日本国特許第2616652号（特許文献1）の先行発明に内在する問題点を指摘する。即ち、同文献1に記載の先行発明は、輝度値の大小関係の変化のみに基づいて液晶駆動電圧を増減させると言う発想に依拠している。このため、現画像の輝度値がその1フレーム前の画像の輝度値よりも増加する場合には、その増加量の値如何に拘わらず、現画像の輝度値に対応する液晶駆動電圧よりも高い駆動電圧が一律に液晶駆動電極に印加される。その結果、輝度値の変化が僅かな場合には、液晶に過電圧が印加されることになり、画質の劣化が生じる。逆に、現画像の輝度値が1フレーム前の画像の輝度値よりも減少する場合においても、その減少量の値如何に拘わらず、現画像の輝度値に対応する液晶駆動電圧よりも低い駆動電圧が一律に液晶駆動電極に印加されるため、同様な画質劣化が生じ得る。この様な本質的な問題点が顕出する原因は、輝度値の単純な比較処理に基づいて駆動電圧の増減量を一律に設定している点にあるものと、本願発明者は考える。そこで、斯かる観点を踏まえて、本願発明者は本実施の形態の主題を創作している。

10

20

30

40

## 【0137】

図23は、本実施の形態に係る液晶表示装置の構成を示すブロック図である。図23中、図1中の参照符号と同一の参照符号が付された各構成要素は、図1中の対応する構成要素と同一である。即ち、図23の装置が図1の装置と相違する点は、(i)温度制御部12の不存在、及び、(ii)本装置の中核部たる画像データ補正回路10Dの構成にあり、その他の構成要素1, 2, 4, 5, 6, 7, 8, 9は同一回路構成及び同一機能を有する。従って、これらの構成要素1, 2, 4, 5, 6, 7, 8, 9の記載に関しては、実施の形態1における対応部分の記載を基本的に援用する。

20

30

## 【0138】

図23における各部の概要は以下の通りである。先ず、受信回路2は、入力端子1を介して映像信号を受信し、1フレーム分の入力動画像（現画像）に対応するラスター画像データ（現画像データ）Di1を順次出力する。画像データ処理部3は、現画像データDi1に対して所定の処理を施すことにより、現画像データDi1の補正信号である補正現画像データDj1を生成する。画像データ処理部3は、符号化回路4、遅延回路5、第1復号化回路6、第2復号化回路7、変化量算出回路8、1フレーム前画像再生回路9、及び画像データ補正回路10Dを備える。

30

## 【0139】

符号化回路4は、現画像データDi1を符号化・圧縮することにより、現画像に対応する符号化画像データDa1を生成・出力する。現画像データDi1の符号化には、FBTC（Fixed Block Truncation Coding）又はGBT（Generalized Block Truncation Coding）等のブロック符号化を用いることが出来る。又、JPEG（Joint Photographic Experts Group）の様な2次元離散コサイン変換符号化、JPEG-LS（Joint Photographic Experts Group-Lossless）の様な予測符号化、あるいはJPEG2000の様なウェーブレット変換といった様な、任意の静止画用符号化方式を、上記符号化に適用することも可能である。尚、静止画用符号化方法が、符号化前の現画像データDi1と復号化後の復号化画像データDb1とが完全に一致しない非可逆符号化方法であっても、その様な静止画用符号化方法を適用することは可能である。

40

## 【0140】

遅延回路5は、符号化回路4より出力される符号化画像データDa1を1フレームに相当する期間だけ遅延することにより、現画像データDi1の1フレーム前の画像データに対応する符号化画像データDa0を出力する。遅延回路5は、符号化画像データDa1を1フレーム期間記憶するメモリ（図示せず）と、当該メモリを制御するメモリ制御部（図示せず）とを備える。よって、現画像データDi1の符号化率（データ圧縮率）を高くする程に、遅延回路5が有するメモリの容量を少なくすることが出来る。

50

## 【0141】

第1復号化回路6は、符号化画像データDa1を復号化（伸長化）することにより、現画像データDi1に対応する第1復号化画像データDb1を出力する。同時に、第2復号化

回路 7 は、符号化画像データ D a 0 を復号化することにより、現画像データ D i 1 の 1 フレーム期間分だけ前の画像データに対応する第 2 復号化画像データ D b 0 を出力する。

【 0 1 4 2 】

変化量算出回路 8 は、両復号化画像データ D b 1 及び D b 0 に基づいて、第 2 復号化画像データ D b 0 から第 1 復号化画像データ D b 1 を減算することにより、各画素における、1 フレーム期間分だけ前の画像の輝度値と現画像の輝度値との変化量データ D v 1 を算出・出力する。

【 0 1 4 3 】

1 フレーム前画像再生回路 9 は、現画像データ D i 1 に輝度値変化量データ D v 1 を加算することにより、1 フレーム前の画像データ D p 0 を再生する。

10

【 0 1 4 4 】

画像データ補正回路 10 D は、現画像データ D i 1 と 1 フレーム前再生画像データ D p 0 とに基づいて現画像データ D i 1 を補正することにより、補正現画像データ D j 1 を出力する。具体的には、同回路 10 D は、現画像データ D i 1 の値、従って現画像の輝度値が、1 フレーム前再生画像データ D p 0 が与える輝度値と比較して変化する場合にのみ、液晶の表示画素部分の透過率が 1 フレーム期間以内に現画像の輝度値に対応する透過率となる様に、現画像データ D i 1 を補正する。

【 0 1 4 5 】

液晶表示パネル 11 は、ある画素の補正現画像データ D j 1 に基づいて駆動電圧を決定した上で、当該駆動電圧を当該画素に対応する液晶の表示画素用の駆動電極に印加して、表示動作を行う。

20

【 0 1 4 6 】

ここで、図 2 3 に示す画像データ処理部 3 の動作を示すフローチャートとして、既述した図 2 を援用する。図 2 中の各ステップに関して、本実施の形態が実施の形態 1 と相違する唯一の点は、ステップ S t 6 にある。

【 0 1 4 7 】

現画像データ符号化工程 ( S t 1 ) においては、符号化回路 4 は現画像データ D i 1 を符号化し、現画像に対応する符号化画像データ D a 1 を出力する。被遅延符号化画像データ読出し工程 ( S t 2 ) においては、遅延回路 5 は、現画像の 1 フレーム前の画像に対応する符号化画像データ D a 0 を出力すると共に、符号化画像データ D a 1 を 1 フレームに相当する期間だけ遅延させる動作を実行する。符号化画像データ復号化工程 ( S t 3 ) においては、第 1 復号化回路 6 及び第 2 復号化回路 7 は、それぞれ、対応する符号化画像データ D a 1 及び D a 0 を復号化し、現画像及び 1 フレーム前の画像に対応する第 1 及び第 2 復号化画像データ D b 1 及び D b 0 を出力する。変化量データ算出工程 ( S t 4 ) においては、変化量算出回路 8 は、両復号化画像データ D b 1 及び D b 0 に基づいて、輝度値の変化量データ D v 1 を生成・出力する。1 フレーム前画像再生工程 ( S t 5 ) においては、1 フレーム前画像再生回路 9 は、輝度値の変化量データ D v 1 及び現画像データ D i 1 に基づいて、1 フレーム前の画像に対応する再生画像データ D p 0 を出力する。核心部たる現画像データ補正工程 ( S t 6 ) においては、画像データ補正回路 10 D は、両データ D i 1 及び D p 0 に基づいて現画像データ D i 1 を補正し、補正現画像データ D j 1 を出力する。以上のステップ S t 1 ~ S t 6 における一連の動作が、1 画面内の各画素の現画像データ D i 1 に対して実行される。

30

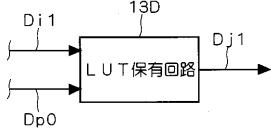

【 0 1 4 8 】

図 2 4 は、図 2 3 に示された画像データ補正回路 10 D の内部構成の一例を示すブロック図である。同回路 10 D は、ルックアップテーブル ( L U T ) 保有回路 13 D を備える。そして、L U T 保有回路 13 D は、現画像データ D i 1 及び 1 フレーム前再生画像データ D p 0 に基づいて、液晶中の対応する表示画素部分の透過率が 1 フレーム期間内に当該画素の現画像の輝度値に対応する透過率となる様な補正データ ( L U T データ ) を、L U T の中から抽出し、その様に抽出された L U T データを、現画像データ D i 1 を補正するための補正現画像データ D j 1 に設定・出力する。

40

50

## 【0149】

図25は、LUT保有回路13Dが有するルックアップテーブルの構成を模式的に示す図であり、実施の形態1において既述した図4に対応する図面である。ここでは、現画像データDi1及び1フレーム前再生画像データDp0は共に8ビットの画像データであり、それらのデータが与える輝度値は0～255の範囲内の値となる。図25に示すルックアップテーブルは、2次元に配列される $256 \times 256$ 個のデータを有し、現画像データDi1及び1フレーム前再生画像データDp0の両値に対応する補正現画像データDj1 = dt(Di1, Dp0)を出力する。

## 【0150】

以下、補正現画像データDj1の決定方法について記載する。但し、本実施の形態における補正現画像データDj1の決定方法は、実施の形態1において図5、図7、図8及び図9を参照して記載した決定方法と基本的に同一である。そのため、それらの記載を基本的に援用すると共に、図5、図7及び図8の各図面を以下の記載においても援用する。本実施の形態における補正現画像データDj1の決定方法を重ねて記載すれば、次の通りである。

## 【0151】

現画像の輝度値を8ビット(0～255)で以って与えるものとすると、例えば現画像データDi1 = 127の場合、当該画素に対応する液晶の表示画素部分には透過率が50%となる様な電圧V50が印加される。同様に、現画像データDi1 = 191の場合には、透過率が75%となる様な電圧V75が印加される。図5に示す様に、現画像データDi1に基づいた電圧V50及びV75を対応する表示画素部分にそれぞれ印加する場合、液晶の表示画素部分の透過率がそれぞれ50%及び75%と言う所定の透過率に到達するには、1フレーム期間よりも長い応答時間を要する。よって、現画像の輝度値が1フレーム前の画像の輝度値と比較して変化する場合には、液晶の表示画素部分の透過率が1フレーム期間内に現画像の輝度値に対応する透過率となる様な補正現画像データDj1を回路3において生成・出力し、この補正現画像データDj1に基づいて生成される駆動電圧を対応する表示画素部分の電極に印加することにより、液晶の応答速度を向上させることが可能である。

## 【0152】

図5に例示する様な応答速度の場合には、電圧V75を印加すると、1フレーム期間経過時の液晶の透過率は50%となる。よって、目標とする透過率が50%の場合には、液晶の駆動電圧を電圧V75に設定することにより、1フレーム期間内に液晶の透過率を50%とすることが出来る。つまり、現画像データDi1の輝度値が0から127に変化する場合には、現画像データDi1の輝度値を修正して、輝度値191を有する補正後の現画像データDj1を液晶表示パネル11に出力するならば、液晶内の対応する表示画素部分が1フレーム期間内に所望の透過率を有することとなる様な駆動電圧が上記表示画素部分に印加される。

## 【0153】

図7において、現画像の輝度値及び1フレーム前画像の輝度値との組み合わせは $256 \times 256$ 通り存在するので、応答速度も $256 \times 256$ 通り存在する。又、図8において、現画像データDi1に対する補正量は、現画像の輝度値及び1フレーム前画像の輝度値との組み合わせに対応して、 $256 \times 256$ 通り存在する。図7に示す様に、液晶の応答速度は現画像の輝度値及び1フレーム前画像の輝度値との組合せ毎に異なり、補正量は簡単な計算式によって一般的に求めることが出来ない。そのため、図24のLUT保有回路13Dのルックアップテーブルには、図26に示す様に、図8に示した $256 \times 256$ 通りの補正量をそれぞれの現画像データDi1に加算して得られた補正現画像データDj1が格納される。ここで、補正現画像データDj1の値は、当然のことではあるが、液晶表示パネル11にとって表示可能な透過率の範囲を超えない様に、即ち、現画像及び1フレーム前画像の輝度値が共に8ビットの場合であれば、0～255の範囲内の値に、設定される。補正現画像データDj1がこの範囲以外の値に設定される場合には、液晶パネルを駆

10

20

30

40

50

動させるセグメント電極駆動回路として従来から一般的に使用されている回路を使用することが出来ない。

#### 【0154】

既述の通り、液晶の応答特性は、液晶の材料、電極形状、あるいは温度等の様々な要因によって変化する。従って、こうした個々の使用条件に対応する補正現画像データD<sub>j</sub>1を有するルックアップテーブルを採用することにより、使用条件の変更に応じて、ルックアップテーブル内の補正現画像データD<sub>j</sub>1を書き換えるか、又は、十分な容量を有するルックアップテーブルを用意しておいて複数の異なる組み合わせの中から当該使用条件に適した補正現画像データD<sub>j</sub>1に切り替えることで以って、液晶の特性に応じた臨機応変な応答速度の制御を実現することが出来る。

10

#### 【0155】

又、図8に示す様に、補正量は、液晶の応答速度に応じて設定されており、液晶の応答速度が遅い輝度値の組み合わせに対する補正量が大となる様に、補正量は設定される。特に、中間輝度（グレー）から高輝度（白）に変化する際の液晶の応答速度は遅い。従って、中間輝度を表す1フレーム前再生画像データD<sub>p</sub>0と高輝度を表す現画像データD<sub>i</sub>1との組み合わせに対応する補正現画像データD<sub>j</sub>1の値を、現画像データD<sub>i</sub>1の値と比べてより大きな値に設定することにより、液晶の応答速度を効果的に向上させることが出来る。

20

#### 【0156】

図25に例示されるルックアップテーブルより出力される補正現画像データD<sub>j</sub>1は、液晶表示パネル11に出力される。同パネル11内のドライバ（図示せず）は、補正現画像データD<sub>j</sub>1に基づいて駆動電圧を生成し、その駆動電圧を液晶の対応するセグメント電極に印加することにより、最適な階調表示を実現する。

20

#### 【0157】

本実施の形態に係る画像データ処理部3（図23）の動作を模式的に記載するタイミングチャートとして、図14（A）、図14（B）及び図14（C）の図面をここでも援用すると共に、これらの図面に関する実施の形態1における記載部分をも援用する。

30

#### 【0158】

以上の通り、本実施の形態に係る画像データ処理部3は、現画像データD<sub>i</sub>1を一旦符号化してデータ量を圧縮した上で現画像データの符号化データを遅延しているので、現画像データD<sub>i</sub>1を1フレーム期間だけ遅延するために必要なメモリ容量を削減することができると言う利点を呈する。しかも、画素データを間引かずに、1画面内の全画素の現画像データD<sub>i</sub>1について符号化・復号化処理を実行しているので、本実施の形態は、画質の劣化をもたらさない、適切な値を有する補正現画像データD<sub>j</sub>1を発生することが出来、その結果、液晶の応答速度を適正に制御することができると言う利点をも奏する。

30

#### 【0159】

又、画像データ補正回路10Dは、現画像データD<sub>i</sub>1と1フレーム前再生画像データD<sub>p</sub>0とに基づいて補正現画像データD<sub>j</sub>1を生成・出力するので、実施の形態1と同様に、符号化・復号化処理時に発生し得る誤差の影響を受けない補正現画像データD<sub>j</sub>1を実現することができると言う利点をも兼ね備えている。この点を、以下に記載する。

40

#### 【0160】

図27（A）～図27（F）は、符号化及び復号化処理に起因して発生する誤差が補正現画像データD<sub>j</sub>1に与える影響について記載するための説明図である。即ち、図27（A）は、現画像の1フレーム前である（n-1）番目のフレームにおける実際の画像例を表す画像データD<sub>i</sub>0を、図27（D）は、現画像であるn番目のフレームにおける画像を表す現画像データD<sub>i</sub>1の値を、それぞれ模式的に示す図である。図27（A）及び図27（D）に示す様に、現画像データD<sub>i</sub>1は、実際の1フレーム前の画像データD<sub>i</sub>0と比較して、変化していない。図27（E）及び図27（B）は、それぞれ、図27（D）及び図27（A）に示す現画像データD<sub>i</sub>1及び1フレーム前の画像データD<sub>i</sub>0に対応する符号化データを模式的に示す図である。ここで、図27（E）及び図27（B）は、

50

F T B C 符号化によって得られる符号化データを示しており、代表値 (L a , L b) を 8 ビットとして、各画素に 1 ビットを割り当てている。図 27 (F) 及び図 27 (C) は、それぞれ、図 27 (E) 及び図 27 (B) に示す符号化データを復号化して得られる復号化画像データ D b 0 及び D b 1 を示している。図 27 (G) は、図 27 (F) 及び図 27 (C) に示す復号化画像データ D b 1 及び D b 0 に基づいて生成される輝度値の変化量データ D v 1 の値を示しており、図 27 (H) は、1 フレーム前再生画像データ D p 0 の値を示している。図 27 (D)、図 27 (F)、図 27 (A) 及び図 27 (C) に示す様に、現画像データ D i 1 及び 1 フレーム前の画像データ D i 0 と比べて、復号化画像データ D b 1 及び D b 0 に符号化・復号化に伴う誤差が生じた場合においても、図 27 (F) 及び図 27 (C) に示す復号化画像データ D b 1 及び D b 0 に基づいて変化量データ D v 1 が算出され、この変化量データ D v 1 値は、図 27 (G) に示す通り、0 である。これにより、図 27 (H) に示す様に、符号化・復号化により生じる誤差の影響を受けることなく、1 フレーム前再生画像データ D p 0 として、図 27 (A) に示す 1 フレーム前の画像データ D i 0 と同じデータが再生されており、その様な誤差を含まない当該データ D p 0 が画像データ補正回路 10 D へ出力される。

10

#### 【0161】

画像データ補正回路 10 D の入力信号の一方である現画像データ D i 1 に対しては、画像データの符号化処理が施されていないので、画像データ補正回路 10 D は、現画像データ D i 1 及び誤差無く適正に再生された 1 フレーム前再生画像データ D p 0 に基づき、適正な補正現画像データ D j 1 を液晶表示パネル 11 に出力することが出来る。

20

#### 【0162】

上記の記載においては、図 25 のルックアップテーブルに入力されるデータが 8 ビットで表される場合であったが、これに限られるものではなく、補間処理等により実質的に補正データを生成することが可能なビット数である限り、ルックアップテーブルに入力されるデータのビット数は任意値としても良い。この場合には、その様な任意のビット数 k (k < n) のデータ (n × n 個) を有する LUT と、その出力段側に設けられる補間処理等を行う回路 (補正データとして選択された任意のビット数 k の LUT データを、上記 LUT の入力信号 D i 1 , D p 0 のビット数 n と同じビット数 n を有する補正現画像データ D j 1 に変換する処理回路) とから成る回路が、広義の LUT 保有回路 13 D を成すものみなされる。

30

#### 【0163】

##### (実施の形態 3 の変形例 1)

本変形例は、図 19 に例示した実施の形態 2 の変形例 1 に類似するものであり、その相違点は、図 19 の減算回路 17、補正量制限回路 18 及び加算回路 19 の不存在にあり、その他の構成要素 20 ~ 23 は両変形例において基本的に共通している。その意味で、本変形例においても、基本的に、実施の形態 2 の変形例 1 において構成要素 20 ~ 23 に関して述べた記載を援用する。以下の記載においては、実施の形態 3 において例示した図 23 を援用する。と言うのは、本変形例の核心部が、図 23 中の画像データ補正回路 10 D の構成を修正する点にあるからである。

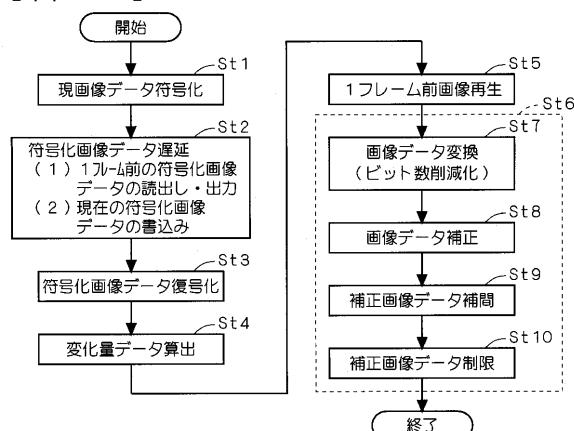

#### 【0164】

図 28 は、本変形例に係る画像データ処理部 3 の動作を示すフローチャートである。ステップ S t 1 からステップ S t 5 迄の各工程における動作は実施の形態 3 において記載した通りであり、その記載を割愛する。本変形例における現画像データ補正工程 S t 6 は、画像データ変換工程 S t 7、画像データ補正工程 S t 8 及び補正画像データ補間工程 S t 9 より成る。以下においては、後述する図 29 を適宜参照することで、本変形例の現画像データ補正工程 S t 6 を詳述する。

40

#### 【0165】

即ち、図 28 の画像データ変換工程 S t 7 においては、現画像データ D i 1 の量子化ビット数を削減する (n ビットから m (m < n) ビットへの削減) と共に、1 フレーム前再生画像データ D p 0 の量子化ビット数をも同時に削減 (n ビットから q (q < n) ビットへ

50

の削減)して、ビット数変換された現画像データD e 1及びビット数変換された1フレーム前再生画像データD e 0を生成する。次の画像データ補正工程S t 8においては、現画像データD e 1及び1フレーム前再生画像データD e 0に基づいて、予め両データD e 1及びD e 0の組合せに対応する補正データが格納されたルックアップテーブルの中から、当該組合せに対応する第1補正画像データD f 1と、当該組合せに隣接する3個の格子点における第2～第4補正画像データD f 2、D f 3、及びD f 4とを抽出して、これらの補正画像データD f 1～D f 4で以って、ビット数変換された現画像データD e 1の補正を行う。次の補正画像データ補間工程S t 9においては、ビット数変換前の現画像データD i 1と1フレーム前再生画像データD p 0とに基づいて、第1～第4補正画像データD f 1、D f 2、D f 3、D f 4の補間演算処理を実行し、得られた補間画像データD h 1を補正現画像データD j 1として出力する。10

#### 【0166】

本変形例に係る画像データ処理部3が有する画像データ補正回路10D1は、図24に示すLUT保有回路13Dに代えて、図29に示す4個の構成要素より成る。即ち、同回路10D1は、第1データ変換回路20、第2データ変換回路21、実質的な画像データ補正回路の動作を担う被削減化LUT保有回路22D及び補間回路23を有する。

#### 【0167】

図29において、第1及び第2データ変換回路20、21は、それぞれ、現画像データD i 1及び1フレーム前再生画像データD p 1の量子化ビット数を、例えば8ビットから3ビットに削減することにより、ビット数変換された現画像データD e 1及びビット数変換された1フレーム前再生画像データD e 0を出力する。同時に、第1及び第2データ変換回路20、21は、それぞれ、現画像データD i 1及び1フレーム前再生画像データD p 0に基づいて行われるビット数変換に際して、第1及び第2補間係数k0、k1を算出する。被削減化LUT保有回路22Dは、ビット数変換された現画像データD e 1及びビット数変換された1フレーム前再生画像データD e 0に基づいて、当該画素に対応する液晶の表示画素部分の透過率が1フレーム期間内に当該現画像の輝度値に対応する透過率となる様に、ビット数変換された現画像データD e 1を補正して、4個の補正画像データD f 1～D f 4を出力する。補間回路23は、ビット数変換の変換結果である第1及び第2補間係数k0、k1を用いて、補正画像データD f 1～D f 4を補間することにより、nビット(例えば8ビット)の補間画像データD h 1を出力する。20

#### 【0168】

補間画像データD h 1は、補正現画像データD j 1として、図23の液晶表示パネル11のドライバ(図示せず)に入力され、同ドライバは補正画像データD h 1に基づいて当該画素に対応するセグメント電極を駆動するための電圧を決定し、当該駆動電圧を対応するセグメント電極に印加する。これにより、液晶表示パネル11は、階調表示動作を行う。

#### 【0169】

図30は、図29の被削減化LUT保有回路22Dが有するルックアップテーブルの構成を模式的に示す図である。この一例では、ビット数変換された現画像データD e 1及びビット数変換された1フレーム前再生画像データD e 0は、共に3ビットデータであり、0～7の範囲内の値をとる。図30に示す様に、当該ルックアップテーブルは、2次元に配列される9×9個のデータを有しており、共に3ビットにビット数変換された、現画像データD e 1及び1フレーム前再生画像データD b 0の両値に対応する補正画像データd t(D e 1, D e 0)を補正画像データD f 1として出力する。更に、ルックアップテーブルは、補正画像データD f 1に隣接する3つの補正画像データd t(D e 1+1, D e 0)、d t(D e 1, D e 0+1)、d t(D e 1+1, D e 0+1)を、それぞれ補正画像データD f 2、D f 3、D f 4として出力する。40

#### 【0170】

補間回路16は、第1及び第2補間係数k1、k0並びに第1～第4補正画像データD f 1～D f 4を用いて、既述した式(1)(但し、式(1)の左辺のD j 5をD h 1に置換すること)で与えられる補間処理を実行することにより、補間された補間画像データD h

10

20

30

40

50

1を算出する。

【0171】

図31は、上記式(1)により表される補間画像データD<sub>h</sub>1の算出方法を模式的に示す図であり、図21に対応している。図31において、s<sub>1</sub>及びs<sub>2</sub>は、第1データ変換回路20により現画像データD<sub>i</sub>1の量子化ビット数を変換する際に用いられる閾値であり、s<sub>3</sub>及びs<sub>4</sub>は、第2データ変換回路21により1フレーム前再生画像データD<sub>p</sub>0の量子化ビット数を変換する際に用いられる閾値である。しかも、閾値s<sub>1</sub>は、ビット数変換された現画像データD<sub>e</sub>1に対応する閾値であり、閾値s<sub>2</sub>は、ビット数変換された現画像データD<sub>e</sub>1よりも1だけ大きい現画像データD<sub>e</sub>1+1に対応する閾値である。又、閾値s<sub>3</sub>は、ビット数変換された1フレーム前再生画像データD<sub>e</sub>0に対応する閾値であり、閾値s<sub>4</sub>は、ビット数変換された1フレーム前再生画像データD<sub>e</sub>0よりも1だけ大きい1フレーム前再生画像データD<sub>e</sub>0+1に対応する閾値である。

【0172】

このとき、第1及び第2補間係数k<sub>1</sub>、k<sub>0</sub>は、それぞれ、式(6)及び式(7)により算出される。

【0173】

【数5】

$$k_1 = (D_i 1 - s_1) / (s_2 - s_1) \quad \dots (6)$$

但し、s<sub>1</sub> < D<sub>i</sub>1 ≤ s<sub>2</sub>

$$k_0 = (D_p 0 - s_3) / (s_4 - s_3) \quad \dots (7)$$

但し、s<sub>3</sub> < D<sub>p</sub>0 ≤ s<sub>4</sub>

【0174】

以上の通り、現画像データD<sub>i</sub>1及び1フレーム前再生画像データD<sub>p</sub>0のビット数を変換する際に算出される第1及び第2補間係数k<sub>0</sub>、k<sub>1</sub>を用いて、ビット数変換されたデータ(D<sub>e</sub>1, D<sub>e</sub>0)、(D<sub>e</sub>1+1, D<sub>e</sub>0)、(D<sub>e</sub>1, D<sub>e</sub>0+1)、及び(D<sub>e</sub>1+1, D<sub>e</sub>0+1)に対応する4つの補正画像データD<sub>f</sub>1、D<sub>f</sub>2、D<sub>f</sub>3、D<sub>f</sub>4を補間演算することで、補間画像データD<sub>h</sub>1を求めている。この補間処理により、ルックアップテーブルの構成を簡素化出来ると共に、第1及び第2データ変換回路20、21における量子化誤差が補間画像データD<sub>h</sub>1に与える影響を低減することが出来る。

【0175】

尚、第1及び第2データ変換回路20、21は、線形量子化以外の非線形量子化によって、入力データのビット数削減を行うことも出来る。例えば、非線形量子化によりビット数を変換する際に、補正画像データの変化(隣接する補正画像データ間の差)に応じて量子化密度を設定する。即ち、補正画像データの変化が大きい領域では量子化密度を相対的に高く設定することにより、ビット数削減に伴う補間画像データD<sub>h</sub>1の誤差をより低減することが出来る。

【0176】

又、第1及び第2データ変換回路20、21によるデータ変換処理後のデータビット数は、3ビットに限られるものではなく、補間回路23によって補間することで実質的に使用可能な補間画像データD<sub>h</sub>1を求め得るビット数であれば、任意のビット数を選択することが出来る。勿論、量子化ビット数の値に応じて、被削減化LUT保有回路22Dにおけるルックアップテーブル内のデータ個数もまた変化する。

【0177】

更に、両データ変換回路20、21によるビット数変換後の各データのビット数m、qが、互いに異なっていても良く、又、いずれか一方のビット数変換を実施しないことも可能である。いずれか一方のビット数変換を実施しない場合には、両データ変換回路20又は21において現画像データD<sub>i</sub>1又は1フレーム前再生画像データD<sub>p</sub>1の量子化ビット数nを削減することにより、ビット数変換された現画像データD<sub>e</sub>1又はビット数変換さ

10

20

30

40

50

れた1フレーム前再生画像データD e 0のいずれか一方が出力される。その次に、ルックアップテーブルへのアクセスにより、ビット数変換された現画像データD e 1と、ビット数変換されていない1フレーム前再生画像データD p 1とに基づいて当該ビット数変換された現画像データD e 1を補正するか、又は、ビット数変換されていない現画像データD i 1及びビット数変換された1フレーム前再生画像データD e 0に基づいて当該現画像データD i 1を補正することにより、補正画像データとこれに隣接する補正画像データが出力される。その後、補間回路23は、現画像データD i 1と1フレーム前再生画像データD p 0とに基づき、ビット数変換の変換結果である補間係数k 1又はk 0を用いて、これらの補正画像データの補間を行うことにより、補間画像データD h 1を生成・出力する。尚、両データ変換回路20, 21によるビット数変換を行った場合には、補正画像データは4個のデータD f 1～D f 4より成るが、両データ変換回路20, 21の何れか一方によるビット数変換を行った場合には、補正画像データは2個のデータより成る(式(1)を参照)。又、両データ変換回路20, 21の何れか一方によるビット数変換を行った場合には、両補間係数k 1, k 0の何れか一方、即ち、現画像データD i 1又は1フレーム前再生画像データD p 1の内のビット数変換を行わなかったデータに対応する補間係数の値は0である。従って、式(1)より、 $k_1 = 0$ のときには、被削減化LUTは少なくとも $2^n \times (2^q + 1)$ 個のデータを有することとなり、逆に $k_0 = 0$ のときには、被削減化LUTは少なくとも $(2^m + 1) \times 2^n$ 個のデータを有することとなる。

10

## 【0178】

尚、補間回路23は、線形補間以外に、高次の関数を用いた補間演算により補間画像データD h 1を算出する様に、構成されても良い。

20

## 【0179】

## (実施の形態3の変形例2)

本変形例は、図22に例示した実施の形態2の変形例2に類似するものであり、その相違点は、図22の減算回路17、補正量制限回路18及び加算回路19の不存在にあり、その他の構成要素20～24は両変形例において基本的に共通している。その意味で、本変形例においても、基本的に、実施の形態2の変形例2において構成要素20～24に関して述べた記載を援用する。以下の記載においては、実施の形態3において例示した図23を援用する。蓋し、本変形例の核心部もまた、図23中の画像データ補正回路10Dの構成を修正する点にあるからである。

30

## 【0180】

図32は、本変形例に係る画像データ処理部3の動作を示すフローチャートである。図32中、ステップS t 1～S t 5、及びステップS t 7～S t 9の各工程における動作は、実施の形態3及びその変形例1において記載したステップと同様であり、そのため、それらのステップの記載をここでは割愛する。本変形例の中核部たる補正画像データ制限工程S t 10においては、以下の所定の場合に、現画像データD i 1及び1フレーム前再生画像データD p 0に基づいて、現画像データD i 1が補正されない様に、又はその補正量が少なくなる様に、補正画像データ補間工程(S t 9)において生成される補間画像データを制限し、これにより得られる制限画像データD g 1を出力する。そして、制限画像データD g 1は、補正現画像データD j 1として、図23の液晶表示パネル11に入力され、同パネル11は制限画像データD g 1に基づいて決定される電圧を当該画素に対応する表示画素用駆動電極に印加することにより、階調表示動作を行う。

40

## 【0181】

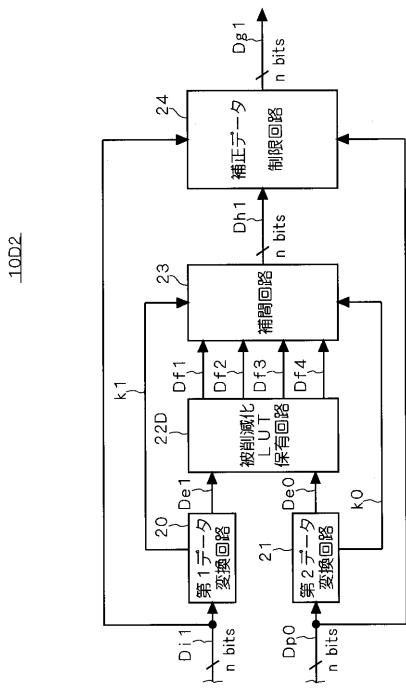

本変形例に係る画像データ補正回路10D2は、図33に示す様に、図29に示す構成要素(第1データ変換回路20、第2データ変換回路21、被削減化LUT保有回路22D及び補間回路23)に加えて、補正データ制限回路24を有する。

## 【0182】

補正データ制限回路24は、現画像データD i 1及び1フレーム前再生画像データD p 0に基づいて、現画像データD i 1と前フレーム再生画像データD p 0とが互いに等しいか否かを判断し、両データD i 1、D p 0が互いに等しいときには、補間画像データD h 1

50

を制限する。即ち、同回路 24 は、補間画像データ D h 1 の代わりに、現画像データ D i 1 自体を補正現画像データ D j 1 として出力する。これにより、現画像データ D i 1 と 1 フレーム前再生画像データ D p 0 とが互いに等しい場合（画像の変化がない場合）に、両データ変換回路 20, 21 によるビット数削減と補間回路 23 による補間演算とに伴う画像データの補正誤差を無くすることが出来る。

#### 【 0 1 8 3 】

現画像データ D i 1 と 1 フレーム前再生画像データ D p 0 との差が少ない場合においても、上記回路 24 は、補間回路 23 が出力する補間画像データ D h 1 の代わりに、現画像データ D i 1 自体を制限画像データ D g 1 として出力するか、あるいは、補正量が少なくなる様に補正画像データ D h 1 を制限することとしても良い。より具体的には、補正データ制限回路 24 が、現画像データ D i 1 と 1 フレーム前再生画像データ D p 0 との差分の絶対値が予め決められた値 S h よりも小さいと判断した場合には、同回路 24 は、以下の式(8)及び式(9)で与えられる演算処理を実行することにより、補間画像データ D h 1 を適切な値に制限することが出来る。

#### 【 0 1 8 4 】

##### 【 数 6 】

$$Dg 1 = Di 1 + m \times (Dh 1 - Di 1) \quad \dots (8)$$

$$m = f(S h - |Di 1 - Dp 0|) \quad \dots (9)$$

但し、 $f(S h - |Di 1 - Dp 0|)$  は、 $S h - |Di 1 - Dp 0|$  における関数である。

10

20

30

#### 【 0 1 8 5 】

この関数については、それが線形関数又は高次関数であっても良く、予め決められた値 S h の境界付近において輝度値が変化する場合に表示画像が不自然になることがない様に当該関数を適宜決定することが出来る。又、予め決められた値 S h についても、両データ変換回路 20, 21 において削減するビット数や補間回路 23 における補間方法等にもその値は依存するけれども、表示画像が不自然になることがない様に、予め適宜に最適な値に当該値 S h を決定することが出来る。

#### 【 0 1 8 6 】

以上の様に、現画像データ D i 1 及び 1 フレーム前再生画像データ D p 0 に基づいて、現画像データ D i 1 の補正を行わないか、又は、補正量が少くなる様に、補正画像データ補間工程 S t 9 において生成される補間画像データを制限して得られる制限画像データ D g 1 を出力することにより、1 フレーム前の画像と現画像との間で画像の変化が殆ど無いか又はその変化が僅少の場合に、両データ変換回路 20, 21 におけるビット数削減と及び補間回路 23 における補間演算とに伴う画像データの補正誤差を無くし、不要な補正による表示画像の劣化を減少させることが出来る。

#### 【 0 1 8 7 】

##### （実施の形態 4 ）

本実施の形態の目的は、現画像に対して圧縮符号化及び復号化を行った上で画像処理を行う液晶表示装置用画像データ処理装置において、圧縮符号化パラメータを適切に設定することにより、液晶の応答速度をより適正に制御可能とすることにある。以下、図面を参照しつつ、本実施の形態の一例を記載する。その際、本実施の形態に係る液晶表示装置用画像データ処理部の構成を記載した後に、核心部たる、F B T C 符号化を用いて圧縮符号化を行う動作について詳述する。

40

#### 【 0 1 8 8 】

図 34 は、本実施の形態に係る液晶表示装置の構成を示すブロック図である。図 34 の液晶表示装置と図 1 に示した液晶表示装置とを比較すると、構成要素 1, 2, 4, 5, 6, 7, 11 は互いに共通する。従って、本実施の形態においても、実施の形態 1 における構成要素 1, 2, 4, 5, 6, 7, 11 に関する記載箇所を基本的に援用する。相違する点

50

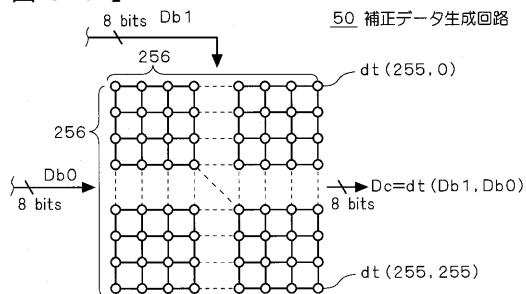

は、本装置が構成要素 50, 100 を有する点である。即ち、本実施の形態に係る液晶表示装置は、入力端子 1、受信回路 2、画像データ処理部 3A、及び液晶表示パネル 11 より構成されており、中核部たる画像データ処理部 3A は、符号化回路 4、メモリ制御回路 5A 及びメモリ 5B を含む遅延回路 5、第 1 及び第 2 復号化回路 6, 7、補正データ生成回路 50、及び補正回路 100 を有する。

#### 【0189】

受信回路 2 は、入力端子 1 を介して受信されるラスター動画像信号を、デジタル形式の現画像データ D<sub>i</sub>1 として、単位時間（例えば 1 クロック）当たりの転送ビット数 N<sub>1</sub> で以って画像データ処理部 3A に出力する。このとき、画像データ処理部 3A が 1 フレーム分の現画像データ D<sub>i</sub>1 を受信するのに必要な時間を受信時間 T<sub>1</sub> と定義する。画像データ処理部 3A は、現画像データ D<sub>i</sub>1 の階調を補正することにより、液晶表示パネル 11 における表示画像の階調変化速度を向上させる。その際、画像データ処理部 3A は、補正された現画像データ D<sub>j</sub>1 を、単位時間当たりの転送ビット数 N<sub>3</sub> で以って液晶表示パネル 11 に出力する。ここで、画像データ処理部 3A が 1 フレーム分の現画像データ D<sub>j</sub>1 を全て出力するのに要する時間を出力時間 T<sub>3</sub> と定義する。特に、画像データ処理部 3A は、第 1 及び第 2 復号化回路 6, 7 による両復号化処理を通じて、圧縮符号化により生じる誤差を打ち消しあって、当該誤差を軽減することが出来ると言う利点を有する。

#### 【0190】

画像データ処理部 3A の遅延回路 5 に含まれるメモリ制御回路 5A は、(i) メモリ 5B に書き込むための圧縮符号化画像データ D<sub>a</sub>1 を一時的に保持するための一時記憶領域と、(ii) メモリ 5B から読み出した、現画像の 1 フレーム前の画像に対応する圧縮符号化画像データを、一時的に保持するための一時記憶領域とを有する。

#### 【0191】

ここで、メモリ制御回路 5A とメモリ 5Bとの間で単位時間当たりに転送されるデータのビット数を、N<sub>2</sub> として表す。従って、転送データビット数 N<sub>2</sub> は、単位時間当たりにメモリ制御回路 5A がメモリ 5B へ出力するデータ量と、単位時間当たりにメモリ制御回路 5A がメモリ 5B から読み出すデータ量との合計になる。

#### 【0192】

又、メモリ制御回路 5A がメモリ 5B に対して 1 フレーム分の圧縮符号化画像データ D<sub>a</sub>1 全てを出力するのに要する時間と、メモリ制御回路 5A がメモリ 5B から 1 フレームに相当する期間だけ遅延された圧縮符号化画像データを 1 フレーム分だけ読み出すのに要する時間とは互いに等しく、両者の時間を T<sub>2</sub> と定義する。

#### 【0193】

あるいは、符号化回路 4 が、メモリ 5B に書き込むための圧縮符号化画像データを一時的に保持するための一時記憶領域を有し、第 2 復号化回路 7 が、メモリ制御回路 5A から出力される 1 フレーム前の圧縮符号化画像データを一時的に保持するための一時記憶領域を有する様に構成しても良い。但し、この場合には、符号化回路 4 がメモリ制御回路 5A を介してメモリ 5B に出力するデータ量と、第 2 復号化回路 7 がメモリ制御回路 5A を介してメモリ 5B から読み出すデータ量との合計が、転送データビット数 N<sub>2</sub> となる。しかも、この場合には、符号化回路 4 がメモリ制御回路 5A を介してメモリ 5B に 1 フレーム分の圧縮符号化画像データ D<sub>a</sub>1 全てを出力するのに要する時間と、第 2 復号化回路 7 がメモリ制御回路 5A を介してメモリ 5B から 1 フレームに相当する期間だけ遅延された圧縮符号化画像データの 1 フレーム分を読み出すのに要する時間とは互いに等しくなり、両者の時間は上記時間 T<sub>2</sub> となる。

#### 【0194】

図 35 は、図 34 に示す画像データ処理部 3A における一連の動作を示すフローチャートであり、既述した図 2 に対応する工程図である。図 35 と図 2 とを比較すると明らかな通り、ステップ S<sub>t</sub>1 - S<sub>t</sub>3 は両実施の形態 4, 1 において共通する工程であり、ステップ S<sub>t</sub>4A, S<sub>t</sub>5A が実施の形態 1 とは相違する。

#### 【0195】

10

20

30

40

50

即ち、現画像データ符号化工程 S t 1 は、符号化回路 4 の動作によって、現画像データ D i 1 を圧縮符号化し、データ容量を圧縮した圧縮符号化画像データ D a 1 を出力する工程である。次の符号化画像データ遅延工程 S t 2 は、メモリ制御回路 5 A 及びメモリ 5 B の動作を利用することによって、( i ) ある画素の現画像に対して 1 フレーム期間だけ前の当該画素の画像を圧縮符号化して成る圧縮符号化画像データ D a 0 を読み出して第 2 復号化回路 7 へ出力すると共に、( i i ) 受信した現画像の圧縮符号化画像データ D a 1 を 1 フレームに相当する期間だけ遅延するために、当該圧縮符号化画像データ D a 1 をメモリ 5 B 内に書込む処理を行う工程である。符号化画像データ復号化工程 S t 3 は、両圧縮符号化画像データ D a 1 , D a 0 を復号化して、復号化された復号化画像データ D b 1 , D b 0 を出力する工程である。

10

## 【 0 1 9 6 】

補正データ生成工程 S t 4 A は、補正データ生成回路 5 0 において、第 1 及び第 2 復号化画像データ D b 1 , D b 0 に基づいて、現画像データ D i 1 を補正するための補正データ D c を生成する工程である。

## 【 0 1 9 7 】

更に、現画像データ補正工程 S t 5 A は、補正回路 1 0 0 において、現画像データ D i 1 を補正データ D c に基づいて補正し、補正された現画像データ D j 1 を液晶表示パネル 1 1 に出力する工程である。

## 【 0 1 9 8 】

そして、各工程 S 1 ~ S t 5 の動作は、現画像データ D i 1 に対して、1 フレーム毎に行われる。以下、画像データ処理部 3 A について詳述する。

## 【 0 1 9 9 】

符号化回路 4 は、現画像データ D i 1 を符号化することにより、そのデータ容量を圧縮した上で、圧縮後の符号化画像データ D a 1 をメモリ制御回路 5 A 及び第 1 復号化回路 6 に送信する。ここで、符号化回路 4 における現画像データ D i 1 の符号化方式としては、例えば、J P E G と言う様な 2 次元離散コサイン変換符号化方式、F B T C 又はG B T C と言う様なブロック符号化方式、J P E G - L S と言う様な予測符号化方式、あるいは、J P E G 2 0 0 0 と言う様なウェーブレット変換方式などを用いることが出来る。要は、上記符号化方式として、任意の静止画用符号化方式を用いることが出来る。又、上記静止画のための符号化方式には、符号化前の画像データと復号化された画像データとが完全に一致する可逆符号化方式、および、両者が一致しない非可逆符号化方式のいずれの方式であっても用いることが出来る。又、画像データによって符号量が変化する可変長符号化方式、及び、符号量が一定である固定長符号化方式の内で何れの方式であっても、その様な方式を用いることが出来る。

30

## 【 0 2 0 0 】

メモリ制御回路 5 A は、符号化回路 4 より送信されて来た圧縮符号化画像データ D a 1 の受信に応じて、( i ) メモリ 5 B の対応するアドレスから、1 フレーム前の当該画素の画像に対応する圧縮符号化画像データ D a 0 を読み出し( この圧縮符号化画像データは現画像から見て 1 フレームに相当する期間だけ遅延された圧縮符号化画像データに相当する )、読み出された圧縮符号化画像データ D a 0 を第 2 復号化回路 7 に送信すると共に、( i i ) 現画像の圧縮符号化画像データ D a 1 をメモリ 5 B に出力して同データ D a 1 をメモリ 5 B の所定のアドレスに格納する。このときの、メモリ制御回路 5 A とメモリ 5 B との間で単位時間当たりに転送されるデータのビット数は上記ビット数 N 2 である。従って、転送データビット数 N 2 は、単位時間当たりにメモリ制御回路 5 A が出力するデータ容量と、単位時間当たりにメモリ 5 B から読み出されるデータ容量との合計となる。例えば、単位時間が 1 フレーム期間である場合には、単位時間当たりにメモリ制御回路 5 A からメモリ 5 B に書き込まれるデータ量と、単位時間当たりにメモリ 5 B からメモリ制御回路 5 A に読み出されるデータ量とは、等しくなる。但し、実際の装置は、データの書き込みとデータの読み出しどとを、同時にあるいは独立して行う様に、構成されているので、局所的な時間内( 例えば 1 クロック内 )では、必ずしも両者のデータ量が一致するとは限らない。

40

50

## 【0201】

又、メモリ制御回路5Aからメモリ5Bに1フレーム分の圧縮符号化画像データD<sub>a</sub>1全てを出力するのに要する時間と、メモリ制御回路5Aがメモリ5Bから1フレーム分の圧縮符号化画像データD<sub>a</sub>0全てを読み出すのに要する時間とは互いに等しく、両者の時間は上記時間T<sub>2</sub>である。

## 【0202】

尚、メモリ5Bは、書き込みと読み出しとを同時に行うことが出来る機能を有するもの、あるいは、書き込みと読み出しとを独立に実行出来る機能を有するものである。

## 【0203】

第1復号化回路6は、圧縮符号化画像データD<sub>a</sub>1を復号化して、第1復号化画像データD<sub>b</sub>1を補正データ生成回路50に送信する。同時に、第2復号化回路7は、メモリ制御回路5Aより送信されて来る圧縮符号化画像データD<sub>a</sub>0を復号化し、その結果得られる第2復号化画像データD<sub>b</sub>0を補正データ生成回路50に送信する。ここで、第1復号化画像データD<sub>b</sub>1は現画像データD<sub>i</sub>1に対応しており、第2復号化画像データD<sub>b</sub>0は、現画像データD<sub>i</sub>1の1フレーム前の画像データに対応している。10

## 【0204】

補正データ生成回路50は、第1復号化画像データD<sub>b</sub>1が与える第1階調数と、1フレーム前の第2復号化画像データD<sub>b</sub>0が与える第2階調数とを、それぞれ対応する（同一座標に位置する）画素毎に比較して、各画素の階調数の変化に対応する補正データD<sub>c</sub>を生成し、同データD<sub>c</sub>を補正回路100に出力する。ここで、補正データD<sub>c</sub>は、画素毎に、その現画像データD<sub>i</sub>1を補正する信号である。即ち、補正データD<sub>c</sub>は、(i)1フレーム前の画像よりも階調数が増加する画素（明るく変化した画素）については（第1階調数 > 第2階調数）、その階調数（現画像データの階調数）をより増加させる第1補正量を与える信号であり、他方、(i)階調数が減少する画素（暗く変化した画素）については（第1階調数 < 第2階調数）、その階調数をより減少させる第2補正量を与える信号である。これに対して、1フレーム内のある画素に関して、現画像とその1フレーム前の画像との間で階調数（明るさ）に変化が無いときには、補正データD<sub>c</sub>は、当該画素における現画像データの階調数の増減を行わない様に指令するレベルを有する信号であり、その結果、当該画素については階調数の補正是行われない。20

## 【0205】

具体例として、補正データ生成回路50は、現画像データD<sub>i</sub>1の階調数を補正する際の補正量を指定する補正データを格納したルックアップテーブル（LUT）により構成される。30

## 【0206】

ここで、図36は、補正データ生成回路50の入出力データを示す図であり、第1及び第2復号化画像データD<sub>b</sub>0,D<sub>b</sub>1が共に8ビット（256階調）の画素データである場合のルックアップテーブルデータを示している。図36の一例においては、補正データ生成回路50は、第1及び第2復号化画像データD<sub>b</sub>1,D<sub>b</sub>0のそれぞれにおける画素データの各階調（0～255）に対応する256×256個の補正データを有する、2次元配列のルックアップテーブルとして構成される。従って、補正データ生成回路50は、両復号化画像データD<sub>b</sub>0,D<sub>b</sub>1の組合せに基づいて、対応する補正データD<sub>c</sub>=d<sub>t</sub>(D<sub>b</sub>1,D<sub>b</sub>0)を出力する。40

## 【0207】

補正データ生成回路50に格納される各補正データd<sub>t</sub>(D<sub>b</sub>1,D<sub>b</sub>0)は、現画像データD<sub>i</sub>1で与えられる各画素データの内で、1フレーム前よりもその階調数が増加する画素については、その階調数をより増加させる様に、逆に減少する画素については、その階調数をより減少させる様に、現画像データD<sub>i</sub>1の階調数を画素毎に補正するための補正量を示すものである。従って、現フレームにおける画像とその1フレーム前における画像との間で階調が変化しない画素については、補正データd<sub>t</sub>(D<sub>b</sub>1,D<sub>b</sub>0)は0となる。50

## 【0208】

補正データ生成回路50は、図34に示す様に、各画素毎の補正データDcを補正回路100に出力する。その結果、補正回路100は、現画像データDi1及び補正データDcに基づいて、現画像データDi1の階調数を画素毎に補正し、補正された現画像データDj1を液晶表示パネル11に出力する。その際、補正現画像データDj1は、当該補正現画像データDj1に基づき液晶表示パネル11が生成する液晶印加電圧により実現される、液晶内の対応表示画素における透過率が、1フレーム期間の経過時に、当該画素の現画像データDi1の第1階調数に相当する第1透過率に到達する様に、決定される。液晶表示パネル11内のドライバ(図示せず)は、補正現画像データDj1に基づいて、対応するセグメント電極を駆動するための電圧を決定し、その駆動電圧を印加することにより、液晶表示パネル11は第1階調数を与える表示動作を行う。10

## 【0209】

尚、メモリ制御回路5Aとメモリ5Bとの間で圧縮符号化画像データを転送するのに要する時間T2が1フレーム分の遅延時間を越えるときには、当該時間T2が、画像データ処理部3Aが1フレーム分の現画像データDi1全てを受信するのに要する時間T1に対して遅れることとなり、他の方法で以ってタイミング調節を行う必要が生ずる。従って、時間T2は、1フレームの遅延期間以内と成る様に設定されなければならない。

## 【0210】

ところで、一般的に、液晶表示において1画素を表示するために必要なデータ容量は、赤色(以下、「R」と言う。)を表示するための8ビット、緑色(以下、「G」と言う。)を表示するための8ビット、及び青色(以下、「B」と言う。)を表示するための8ビットの合計値、即ち24ビットである。又、メモリ制御回路5Aとメモリ5Bとの間でデータを転送するためのバスの幅は、一般に $2^n$ ビットに設定される場合が多く、例えばバス幅は8ビット、16ビット、あるいは32ビットの何れかの大きさである。但し、バス幅がこれらの値に限定されるものではない。20

## 【0211】

ここで、圧縮符号化画像データDa1の第2容量が現画像データDi1の第1容量と等しい場合を考える。この場合、ある1画素の現画像データDi1が受信される時間内に、メモリ制御回路5Aからメモリ5Bに出力されるデータ量は24ビットであり、逆にメモリ制御回路5Aがメモリ5Bから読み出すデータ量も24ビットとなり、両者5A, 5B間で送受信されるデータ量の合計値は48ビットとなる。30

## 【0212】

今、メモリ5Bは書き込みと読み出しとを同時にあるいは独立して行う機能を有するので、若しメモリ制御回路5Aとメモリ5Bとを結ぶバスの幅が48ビット以上の容量を有していないならば、メモリ制御回路5Aとメモリ5Bとの間でデータを転送する時間T2が、1フレーム遅延期間よりも大きくなってしまう。しかし、メモリ制御回路5Aとメモリ5Bとを結ぶバス幅は、最大でも、32ビットである。従って、1画素分の現画像データDi1が受信される時間内に、メモリ制御回路5Aからメモリ5Bに出力されるデータ量と、メモリ制御回路5Aがメモリ5Bから読み出すデータ量との合計(即ち、48ビットのデータ量)を32ビット以下に抑制しない限り、時間T2を1フレーム分の遅延期間内の時間に制御することは出来ない。40

## 【0213】

そこで、符号化回路4は、圧縮符号化画像データDa1のデータ容量(第2容量)が現画像データDi1のデータ容量(第1容量)の $32 / 48 = 2 / 3$ 以下になる様に、現画像データDi1の圧縮符号化を行わなければならない。

## 【0214】

又、圧縮符号化画像データDa1のデータ容量を現画像データDi1の $2 / 3$ 以下、例えば、 $1 / 2$ にすると、1画素分の現画像データDi1が受信される時間内に、メモリ制御回路5Aからメモリ5Bに出力されるデータ及びメモリ制御回路5Aがメモリ5Bより読み出すデータは共に24ビットとなり、 $8 (= 32 - 24)$ ビットの使用されない領域が50

残る。この8ビットの容量を利用して、画像データ以外の情報も、メモリ制御回路5Aからメモリ5Bに出力すると共に、メモリ5Bから読み出すことが出来る。

#### 【0215】

又、メモリ制御回路5Aとメモリ5Bとの間で32ビット単位でデータの読み書きを行う場合、1フレーム期間の内で、1フレーム期間の1/3の時間、両部5A、5B間ににおける読み書きが行われない。この期間を利用して、画像データ以外の情報も、メモリ制御回路5Aからメモリ5Bに出力すると共に、メモリ5Bから読み出すことが出来る。

#### 【0216】

以下では、メモリ制御回路5Aとメモリ5Bとを結ぶバスの幅が32ビットである場合において、圧縮符号化画像データD<sub>a</sub>1の第2容量が現画像データD<sub>i</sub>1の第1容量の1/2以下になる様に、現画像データD<sub>i</sub>1の圧縮符号化を行う場合について記載する。

#### 【0217】