# (19)日本国特許庁(JP) (12) **公開特許 公報**(A) (11)特許出願公開番号

特開2003 - 177422

(P2003 - 177422A)

(43)公開日 平成15年6月27日(2003.6.27)

| (51) Int.CI <sup>7</sup> | 識別記号 | FI                | テーマコード(参考)  |

|--------------------------|------|-------------------|-------------|

| G 0 2 F 1/1368           |      | G 0 2 F 1/1368    | 2 H O 9 2   |

| H 0 1 L 29/786           |      | H 0 1 L 29/78 623 | A 5 F 1 1 0 |

# 審査請求 未請求 請求項の数 20 L (全 4 数)

| (21)出願番号 | 特願2001 - 375402(P2001 - 375402) | (71)出願人 000005821                       |

|----------|---------------------------------|-----------------------------------------|

|          |                                 | 松下電器産業株式会社                              |

| (22)出願日  | 平成13年12月10日(2001.12.10)         | 大阪府門真市大字門真1006番地                        |

|          |                                 | (72)発明者 寺下 俊章                           |

|          |                                 | 大阪府門真市大字門真1006番地 松下電器                   |

|          |                                 | 産業株式会社内                                 |

| (74)代理   |                                 | (74)代理人 110000040                       |

|          |                                 | 特許業務法人池内・佐藤アンドパートナー                     |

|          |                                 | ズ                                       |

|          |                                 | Fターム(参考) 2HO92 GA61 JA24 KA04 MA19 MA27 |

|          |                                 | NA14 NA29                               |

|          |                                 | 5F110 AA22 BB02 BB04 CC01 DD02          |

|          |                                 | GG02 GG13 NN72                          |

|          |                                 |                                         |

# (54)【発明の名称】 薄膜トランジスタとこれを用いた液晶表示装置

# (57)【要約】

【課題】デバイス作製工程中の帯電による素子の破壊を 低減でき、多結晶シリコン薄膜トランジスタアレイの作 製工程でのプロセスダメージによる歩留まりの低下を防 止する。

【解決手段】ガラス基板(11)上に多結晶シリコン薄膜を 活性層に用いた薄膜トランジスタを形成する過程におい て、前記ガラス基板周辺部の薄膜トランジスタ(13)形成 に関与しない金属パターン(12)の少なくとも一部または 全部をフォトリソグラフィによって除去する。液晶表示 装置にも応用でき、少なくとも一方の基板のガラス基板 周辺部の薄膜トランジスタ形成に関与しない金属パター ンの少なくとも一部または全部がフォトリソグラフィに よって除去してもよい。

1

# 【特許請求の範囲】

【請求項1】 ガラス基板上に多結晶シリコン薄膜を活 性層に用いた薄膜トランジスタであって、前記ガラス基 板周辺部の薄膜トランジスタ形成に関与しない金属パタ ーンの少なくとも一部または全部がフォトリソグラフィ によって除去されていることを特徴とする薄膜トランジ スタ。

【請求項2】 2枚の透光性基板間に液晶を挟持してな る液晶表示装置において、少なくとも一方の基板はガラ スであり、前記ガラス基板周辺部の薄膜トランジスタ形 10 パターンに電荷が帯電し、そこから電荷が絶縁膜中へ注 成に関与しない金属パターンの少なくとも一部または全 部がフォトリソグラフィによって除去されていることを 特徴とする液晶表示装置。

### 【発明の詳細な説明】

### [0001]

【発明の属する技術分野】本発明は、薄膜トランジスタ (以下TFTと略す)とこれを用いた液晶表示装置に関 する。

#### [0002]

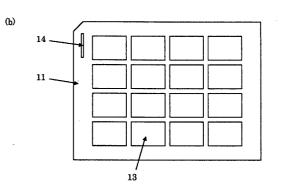

【従来の技術】従来からガラス基板上に薄膜トランジス 20 タを形成する場合、生産効率を向上するために1枚のガ ラス基板から複数の薄膜トランジスタアレイを確保する 薄膜トランジスタアレイの他面取りが採用されている。 図3に従来例として1枚のガラス基板から16面取りの 薄膜トランジスタアレイを製造する場合のガラス基板上 の薄膜トランジスタアレイの配置図を示す。ガラス基板 11に多結晶シリコン薄膜を活性層に用いた薄膜トラン ジスタアレイ12が等間隔に16面配置されており、ガ ラス基板の周辺部には薄膜トランジスタ形成に関与しな いパターン13が形成される。この周辺パターンはシリ 30 周辺部の薄膜トランジスタ形成に関与しない金属パター コンやゲート電極、ソース / ドレイン電極材料成膜後の 露光工程の際にフォトパターンが形成され、エッチング 後そのままパターンとして形成されるが薄膜トランジス 夕形成には全く関与しない。多結晶シリコンを活性層に 用いた相補型金属酸化物半導体(CMOS)構成の薄膜トラン ジスタを形成する際、イオンドーピングやドライエッチ ング、アッシングといったプラズマプロセスにおいて前 記基板周辺部の薄膜トランジスタに関与しない面積の大 きい金属パターンも、薄膜トランジスタ形成に関与する 面積の小さな金属パターンと同様にプラズマに曝される 40 こととなる。なお、14は基板のロットNo.を記すタイ トラーである。

#### [0003]

【発明が解決しようとする課題】多結晶シリコンを活性 層に用いた薄膜トランジスタはその電子移動度が大きく 周辺駆動回路の一部あるいは全てを同一基板上に形成で きるため、高精細・低コストパネルとして開発が盛んで ある。近年では、より加工精度を高めてより高精細パネ ルを実現させるため、またウェットプロセスで使用され る薬液の廃液による環境汚染を低減するため、ドライプ 50 成には全く関与しない。多結晶シリコンを活性層に用い

ロセスへの移行が加速しつつある。しかしながら液晶表 示装置に用いられるガラス基板は絶縁性かつ大面積化が 進んでいるため、プラズマを用いるドライプロセスでは 基板のチャージアップとそれによるデバイスへのダメー ジが課題となる。特に従来例に示した薄膜トランジスタ の製造方法においては、ガラス基板周辺部の薄膜トラン ジスタ形成に関与しない金属パターンの面積が大きいた め、イオンドーピングやドライエッチング、アッシング といったプラズマプロセスにおいて抵抗値の小さな金属 入され、薄膜トランジスタの閾値電圧シフトや最悪の場 合は薄膜トランジスタの破壊を引き起こすといった課題 が生じる。

【0004】本発明は、前記従来の問題を解決するた め、多結晶シリコン薄膜トランジスタアレイの作製工程 でのプロセスダメージによる歩留まりの低下を防止する ことが可能な薄膜トランジスタとこれを用いた液晶表示 装置を提供することを目的とする。

#### [0005]

【課題を解決するための手段】前記目的を達成するた め、本発明の薄膜トランジスタは、ガラス基板上に多結 晶シリコン薄膜を活性層に用いた薄膜トランジスタであ って、前記ガラス基板周辺部の薄膜トランジスタ形成に 関与しない金属パターンの少なくとも一部または全部が フォトリソグラフィによって除去されていることを特徴 とする。

【0006】次に本発明の液晶表示装置は、2枚の透光 性基板間に液晶を挟持してなる液晶表示装置において、 少なくとも一方の基板はガラスであり、前記ガラス基板 ンの少なくとも一部または全部がフォトリソグラフィに よって除去されていることを特徴とする。

#### [0007]

【発明の実施の形態】以下、本発明の実施の形態につい て、図1から図2を用いて説明する。

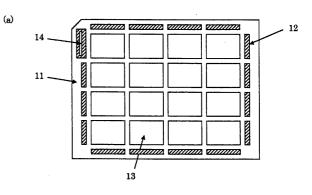

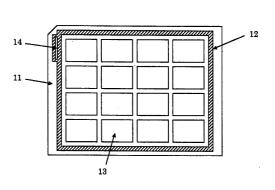

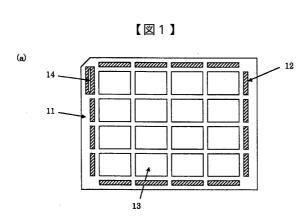

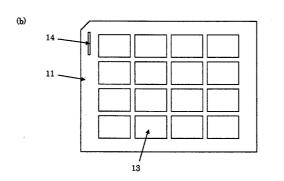

【 0 0 0 8 】 (実施の形態 1 ) 図 1 (a)は本発明の第 1 の実施例を説明する図であり1枚のガラス基板から16 面取りの薄膜トランジスタアレイを製造する場合のガラ ス基板上の薄膜トランジスタアレイの配置図である。ガ ラス基板 1 1 に多結晶シリコン薄膜を活性層に用いた薄 膜トランジスタアレイ12が等間隔に16面配置されて いる。ガラス基板の周辺部には薄膜トランジスタ形成に 関与しないパターン13が形成される。この周辺パター ンはシリコンやゲート電極、ソース / ドレイン電極材料 成膜後の露光工程の際にフォトパターンが形成され、エ ッチング後そのままパターンとして形成されるので、こ れらのパターンを露光する際に周辺金属パターンの一部 にも露光を行い、周辺金属パターンの面積を小さくす る。なお、これらの周辺パターンは薄膜トランジスタ形

たCMOS構成の薄膜トランジスタを形成する際、イオンド ーピングやドライエッチング、アッシングといったプラ ズマプロセスにおいて前記基板周辺部の薄膜トランジス タに関与しない金属パターンも、薄膜トランジスタ形成 に関与する面積の小さな金属パターンと同様にプラズマ に曝されることとなるが、面積が小さいためプラズマエ 程における帯電量も低減し、薄膜トランジスタの破壊を 低減できる。なお、14は基板のロットNo.を記すタイ トラーである。本発明に示したようにアクティブマトリ ックスアレイの製造過程で、ガラス基板周辺部の薄膜ト 10 より、アクティブマトリックスアレイの作製工程での帯 ランジスタ形成に関与しない金属パターンの一部をフォ トリソグラフィ技術によって除去することにより、作製 工程中の帯電による素子の破壊を低減でき、作製歩留ま りが大きく改善できる。

【0009】なお、ここでは薄膜トランジスタ形成に関 与しない金属パターンの一部としたが、図1(b)のよう に薄膜トランジスタ形成に関与しない金属パターンの全 てをフォトリソグラフィ技術によって除去しても同様な 効果が得られる。

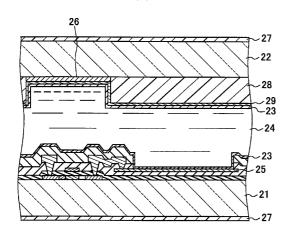

【0010】(実施の形態2)図2は本発明の第2の実2011 ガラス基板 施の形態を説明するための図であり、図1に示した製造 過程で作製したアクティブマトリックスアレイを用いて 作製した液晶表示装置の構成断面図の一例で、画素部を 拡大表示したものである。透光性基板21上に形成した アクティブマトリックスと対向基板22の間に配向膜2 3を介して液晶24が保持されており薄膜トランジスタ をスイッチング素子として画素電極25を駆動して液晶 を充電し画像表示を行っている。本発明の薄膜トランジ スタアレイは従来例の製造方法で作製した薄膜トランジ スタアレイに比較してアレイ作製工程での帯電ダメージ 30 27 偏光板 による薄膜トランジスタの破壊が大幅に低減し製造歩留 まりの良好な液晶表示装置を実現できる。

\*【0011】図2において、26はブラックマトリック ス、27は偏光板、28はカラーフィルター、29は透 明導電層である。

### [0012]

【発明の効果】本発明に示したようにガラス基板上に多 結晶シリコン薄膜を活性層に用いた薄膜トランジスタを 形成する過程において、前記ガラス基板周辺部の薄膜ト ランジスタ形成に関与しない金属パターンの一部または 全部をフォトリソグラフィ技術によって除去することに 電ダメージによる薄膜トランジスタの破壊が大幅に低減 し、製造歩留まりの良好な液晶表示装置が実現できる。

#### 【図面の簡単な説明】

【図1】本発明の薄膜トランジスタアレイの第1の実施 例のガラス基板上の配置を説明する図

【図2】本発明の液晶表示装置の断面校正図の一例図

【図3】従来例の薄膜トランジスタアレイのガラス基板 上の配置を説明する図

#### 【符号の説明】

- 12 基板周辺電極パターン

- 13 薄膜トランジスタアレイ

- 14 タイトラー

- 21 透光性基板(ガラス基板)

- 22 対向基板

- 2 3 配向膜

- 2.4 液晶

- 25 画素電極

- 26 ブラックマトリクス

- 28 カラーフィルター

- 29 透明導電層

【図2】

【図3】

| 专利名称(译)     | 薄膜晶体管和使用该薄膜晶体管的液晶显示装置                                                                                                                                                                                                                                                                |         |            |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|

| 公开(公告)号     | JP2003177422A                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2003-06-27 |  |

| 申请号         | JP2001375402                                                                                                                                                                                                                                                                         | 申请日     | 2001-12-10 |  |

| 申请(专利权)人(译) | 松下电器产业有限公司                                                                                                                                                                                                                                                                           |         |            |  |

| [标]发明人      | 寺下俊章                                                                                                                                                                                                                                                                                 |         |            |  |

| 发明人         | 寺下 俊章                                                                                                                                                                                                                                                                                |         |            |  |

| IPC分类号      | G02F1/1368 H01L29/786                                                                                                                                                                                                                                                                |         |            |  |

| FI分类号       | G02F1/1368 H01L29/78.623.A                                                                                                                                                                                                                                                           |         |            |  |

| F-TERM分类号   | 2H092/GA61 2H092/JA24 2H092/KA04 2H092/MA19 2H092/MA27 2H092/NA14 2H092/NA29 5F110 /AA22 5F110/BB02 5F110/BB04 5F110/CC01 5F110/DD02 5F110/GG02 5F110/GG13 5F110/NN72 2H192/AA24 2H192/BC31 2H192/CB02 2H192/CB34 2H192/EA22 2H192/EA43 2H192/GA31 2H192 /GD71 2H192/HA32 2H192/HA93 |         |            |  |

| 外部链接        | Espacenet                                                                                                                                                                                                                                                                            |         |            |  |

# 摘要(译)

要解决的问题:减少器件制造阶段中元件的静电破坏,并防止由于多晶硅薄膜晶体管阵列的制造阶段中的工艺损坏导致的制造产量降低。 ŽSOLUTION:在形成薄膜晶体管的过程中,其中多晶硅薄膜用作玻璃基板(11)上的有源层,存在于周边部分的金属图案(12)的至少一部分或全部。通过光刻法去除玻璃基板并且不涉及薄膜晶体管(13)的形成。存在于至少一个玻璃基板的周边部分并且不涉及薄膜晶体管的形成的金属图案的至少一部分或全部可以通过光刻法去除,也可以适用于液 □ 品显示装置。Ž