(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5116208号

(P5116208)

(45) 発行日 平成25年1月9日(2013.1.9)

(24) 登録日 平成24年10月26日(2012.10.26)

|                      |                                  |

|----------------------|----------------------------------|

| (51) Int.CI.         | F 1                              |

| G09G 3/36 (2006.01)  | G09G 3/36                        |

| G02F 1/133 (2006.01) | G02F 1/133 505                   |

| G09G 3/20 (2006.01)  | G02F 1/133 535                   |

| G09G 3/34 (2006.01)  | G09G 3/20 611A<br>G09G 3/20 612U |

請求項の数 7 (全 42 頁) 最終頁に続く

(21) 出願番号 特願2004-335269 (P2004-335269)

(22) 出願日 平成16年11月19日 (2004.11.19)

(65) 公開番号 特開2006-145798 (P2006-145798A)

(43) 公開日 平成18年6月8日 (2006.6.8)

審査請求日 平成19年2月23日 (2007.2.23)

(73) 特許権者 502356528

株式会社ジャパンディスプレイイースト

千葉県茂原市早野3300番地

(74) 代理人 110000154

特許業務法人はるか国際特許事務所

(74) 代理人 100075096

弁理士 作田 康夫

(74) 代理人 100100310

弁理士 井上 学

(73) 特許権者 506087819

パナソニック液晶ディスプレイ株式会社

兵庫県姫路市飾磨区姫路日田町1-6

(74) 代理人 110000154

特許業務法人はるか国際特許事務所

最終頁に続く

(54) 【発明の名称】 画像信号表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

一対の基板に挟まれた液晶層を有する液晶表示パネルと、

発光手段を含むバックライトと、

フレームの画像信号に基づいて、前記液晶層を制御するための制御信号である正規化信号と、前記発光手段を制御するための制御信号である正規化係数とを生成する正規化処理回路と、

前記正規化係数が前記フレーム単位の画素構成の表示領域に設定され前記正規化信号がフレーム単位の画素構成の帰線期間に設定されるシリアル信号、または前記正規化係数と前記正規化信号とがフレーム単位の画素構成の表示領域に設定されたシリアル信号を生成する信号成型回路と、

前記信号成型回路が生成したシリアル信号から前記正規化信号と前記正規化係数とを分離する信号分離回路と、

前記分離された正規化信号が変換されたLCD駆動信号を用いて前記液晶表示パネルを駆動するLCD駆動回路と、

前記分離された正規化係数に基づいて前記発光手段を駆動するバックライト駆動回路と、

、

を有することを特徴とする液晶表示装置。

## 【請求項 2】

前記信号成型回路は、前記正規化係数が前記フレーム単位の画素構成の表示領域に設定

10

20

され前記正規化信号がフレーム単位の画素構成の前記表示領域に先立つ帰線期間に設定されるシリアル信号、または前記正規化係数と前記正規化信号とが順にフレーム単位の画素構成の表示領域に設定されたシリアル信号を生成する、

ことを特徴とする請求項1に記載の液晶表示装置。

【請求項3】

前記バックライトにおける、輝度、発光スペクトル、発光色度、発光分布、画面分割数、画面分割形状、変動特性のいずれか又は複数の特性を記憶する手段をさらに有し、

前記正規化処理回路は、前記記憶された特性と前記画像信号とに基づいて前記正規化信号と前記正規化係数とを生成する、

ことを特徴とする請求項1または2に記載の液晶表示装置。

10

【請求項4】

前記液晶層にはそれぞれ光の透過率を制御可能な複数の画素が配置され、

前記バックライトはそれぞれ発光手段により輝度が制御される複数の分割領域を含み、

前記液晶層の前記各画素の透過率と前記発光手段の前記各分割領域の輝度との組合せで表示出力を行い、

所定の条件下における前記表示出力の発光分布特性を検出する手段をさらに備え、

前記正規化処理回路は、前記検出された発光分布特性と前記画像信号とに基づいて前記正規化信号と前記正規化係数とを生成する、

ことを特徴とする請求項1または2に記載の液晶表示装置。

【請求項5】

20

前記発光分布特性は、前記液晶層の各画素の駆動信号と前記発光手段の各分割領域の駆動信号との組合せごとに検出される、

ことを特徴とする請求項4に記載の液晶表示装置。

【請求項6】

一対の基板に挟まれた液晶層を有する液晶表示パネルと、発光手段を含むバックライトと、を含む液晶表示装置を制御する制御部であって、

フレームの画像信号に基づいて、前記液晶層を制御するための制御信号である正規化信号と、前記発光手段を制御するための制御信号である正規化係数とを生成する正規化処理回路と、

前記正規化係数と前記正規化信号とがフレーム単位の画素構成の表示領域に設定されたシリアル信号を送信する信号成型回路と、

30

を備えることを特徴とする制御部。

【請求項7】

前記信号成型回路は、前記正規化係数と前記正規化信号とが順にフレーム単位の画素構成の表示領域に設定されたシリアル信号を送信する、

ことを特徴とする請求項6に記載の制御部。

【発明の詳細な説明】

【技術分野】

【0001】

40

本発明は、液晶表示装置の駆動信号の伝送方法に関する。

【背景技術】

【0002】

近年は液晶パネルとバックライトで構成する表示装置において、バックライトにLED(発光ダイオード)を用いる技術が開発されている。LEDは反射あるいは導光することで、任意形状の面発光体として利用することができ、また発光スペクトルが急峻なため彩度の高い色再現を実現できる。さらに、高速な駆動制御を実現できるため、液晶パネルの表示と共にバックライトの輝度を調整することが可能となる。

【0003】

映像信号と光源の輝度を共に制御する技術としては、特許文献1がある。該文献では、

50

液晶ディスプレイを対象にして、信号振幅制御手段と光源制御手段を備えて平均輝度を維持するように映像信号と光源輝度を制御することでコントラストを改善する装置構成と方法について述べている。

【0004】

そして、入力画像データから、フレーム内の最大、最小、平均値を算出する手段を備え、またフレーム間の信号変化を測定する手段を備えることで、ちらつき等の劣化を抑えることができるとしている。

【0005】

【特許文献1】特許第3430998号公報（特願平11-316725号）

【発明の開示】

10

【発明が解決しようとする課題】

【0006】

特許文献1の従来技術は、画面内の信号の最大値、最小値を測定して、ゲインとオフセットを算出して、入力信号の振幅範囲を補正して表示データとして利用するとともに、液晶ディスプレイのバックライトの輝度を調整することを述べているが、これを実現するには画面内の信号の最大値と最小値の検出を行うことが必要である。この処理手順では画面内の信号を全て入力したあとに測定結果が得られる。しかし、特許文献1の従来技術は、画面内の信号測定と、測定結果を利用した補正処理と、補正結果出力のタイミングが考慮されていない。図面およびその説明文が示す装置構成は、測定を行う画面と、該測定結果を反映する画面は同一とならない。動画は、フレーム毎に画面内の信号が変化するから、特許文献1の従来技術が述べているダイナミックレンジの補正は原理的に成り立たないことになる。

20

【0007】

本願発明の目的は、液晶パネルとバックライトを共に制御する液晶表示装置において、液晶パネルとバックライトをフレーム毎に同期させて表示動作させる、情報の伝送手段を提供することにある。

【課題を解決するための手段】

【0008】

本発明における解決手段は、一対の基板に挟まれた液晶層を有する液晶表示パネルと、輝度を制御可能な光源とを有する液晶表示装置において、フレーム単位の画素構成の表示領域に前記液晶層を制御するための信号を設定し、フレーム単位の画素構成の帰線領域に前記光源を制御するための信号を設定して画像信号を生成する手段を備えることを特徴とする構成をとる。

30

【0009】

また、一対の基板に挟まれた液晶層を有する液晶表示パネルと、輝度を制御可能な光源とを有する液晶表示装置において、フレーム単位の画素構成の表示領域に、前記液晶層を制御するための信号と前記光源を制御するための信号を設定して画像信号を生成する手段を備えることを特徴とする構成をとる。

【0010】

また、前記画像信号を入力する手段と、該入力した信号を前記液晶層を制御するための信号と前記光源を制御するための信号に分離する手段とを有する構成をとる。

40

【0011】

また、前記画像信号をシリアル信号に変換する手段を有する構成をとる。

【0012】

また、前記シリアル信号を前記液晶層を制御するための信号と前記光源を制御するための信号に分離する手段とを有する構成をとる。

【0013】

また、一対の基板に挟まれた液晶層を有する液晶表示パネルと、光源とを有する液晶表示装置において、前記光源における、輝度、発光スペクトル、発光色度、発光分布、画面

50

分割数，画面分割形状，変動特性，外部光源特性のいずれか又は複数の特性を記憶する手段と、前記特性に基づき表示信号の信号処理を行う手段とを備えることを特徴とする構成をとる。

【0014】

また、一対の基板に挟まれ、光の透過率を制御可能な液晶層を有する液晶表示パネルと、複数の分割領域ごとに輝度を制御可能な光源とを有し、前記液晶層の透過率と前記光源の輝度との組合せで表示出力を得る液晶表示装置であって、前記表示出力の発光分布特性を検出する手段を備え、前記液晶層の透過率及び前記光源の輝度を制御するために、検出した前記発光分布特性を用いることを特徴とする構成をとる。

【0015】

また、前記発光分布特性は、前記液晶層の各画素の駆動信号と、前記光源の各分割領域の駆動信号との組合せについて検出されることを特徴とする構成をとる。

【0016】

また、一対の基板に挟まれ、光の透過率を制御可能な液晶層を有する液晶表示パネルと、輝度を制御可能な光源とを有し、前記液晶層はM個の画素ごとに透過率を制御可能であり、前記光源はN個の分割領域ごとに輝度を制御可能であり、前記液晶層の透過率と前記光源の輝度との組合せで得られる表示出力の発光分布特性を検出し、該発光分布特性を用いて、前記M個の画素の透過率制御信号と前記N個の分割領域の輝度制御信号を算出することを特徴とする構成をとる。

【発明の効果】

20

【0017】

本発明によれば、液晶パネルとバックライトの両者のデバイス特性を信号として取り込み、表示する画面を液晶パネルとバックライトの駆動信号として生成し、両者の信号を液晶パネルとバックライトの駆動回路にシリアル伝送して、液晶パネルとバックライトをフレーム毎に同期させて表示動作させることができる。これにより、液晶パネルとバックライトのデバイス特性を組み合わせた表示出力を得ることにより、有効な表示階調数の増加、コントラストの増加、バックライト消費電力の低下、などの効果を得ることが出来る。

【発明を実施するための最良の形態】

【0018】

本発明を実施するための形態を以下に説明する。

30

【実施例1】

【0019】

以下、本発明の基本構成を説明する。

【0020】

(1) 全体構成

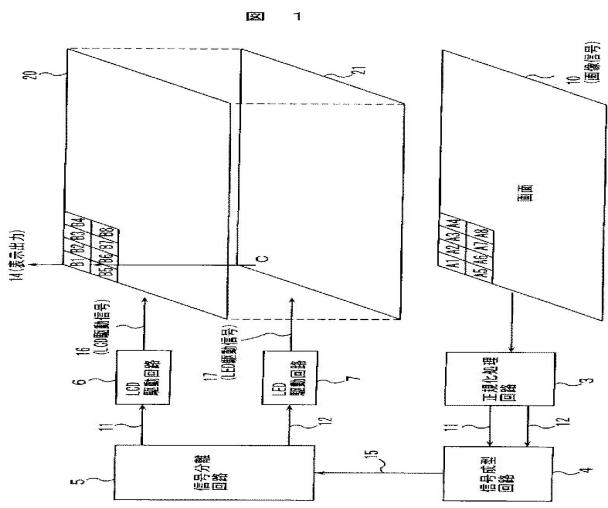

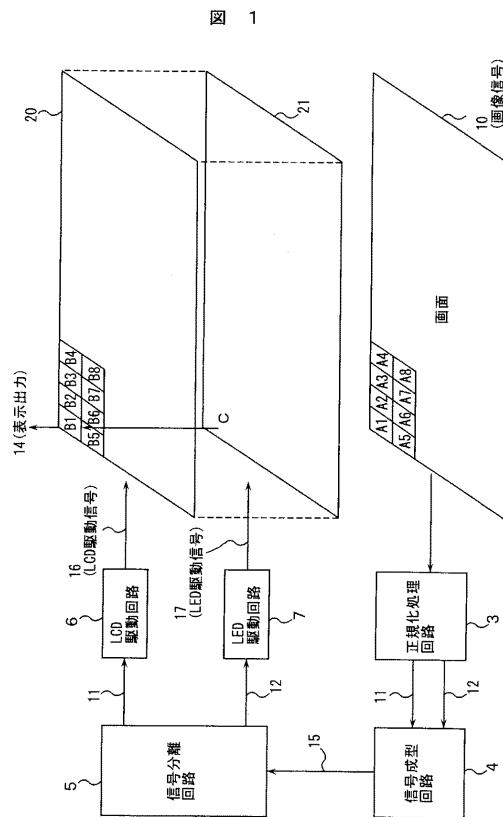

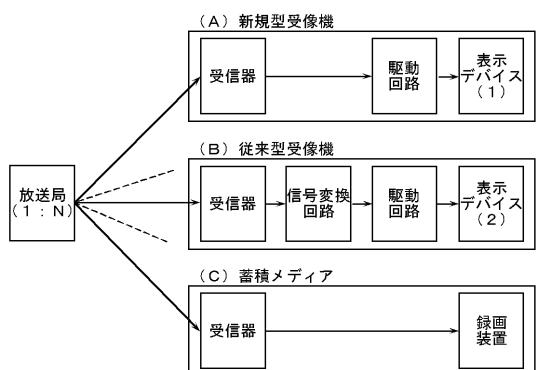

図1に、本発明を実現するための基本構成を示す。

【0021】

本発明の表示装置の構成例としては、液晶パネル20とバックライト21を組み合わせるものである。ここで、液晶パネル20は、複数の画素を平面内に配置して、それぞれが信号レベルに応じて光の透過率を制御する機能を持つ。バックライト21は、前記液晶パネル20の光源であり、冷陰極管、LED(発光ダイオード)等の発光手段があるが、以下の説明ではLEDを利用する場合を説明する。

40

【0022】

本発明は、上記の液晶パネル20とバックライト21の両者を駆動するための2種の信号を備えて、両者をフレーム(画面)単位で同期を取りながら、信号処理、整形(フォーマッティング)，伝送、表示することを特徴とする。なお本発明においては、フレームと画面は同一であり、説明の場面に応じて両者を混在して利用する。

【0023】

駆動信号の一つは液晶パネル20を駆動するためのLCD駆動信号16であり、もう一つはバックライト21を駆動するためのLED駆動信号17である。このように液晶パネ

50

ル20をLCD駆動信号16で、またバックライト21をLED駆動信号17で駆動することで、入力する画像信号10に対応する表示出力14を得る。ここで、LCD駆動信号16は、液晶パネルを構成する各画素に伝達する信号の組み合わせで構成される。また、LED駆動信号の信号形式は、バックライトの発光手段の構成に依存するが、例えばRGB(赤青緑)ごとに全面一括に駆動するならば、RGBそれぞれの3つの信号で構成されることになる。本発明は、バックライト21として、フレーム(画面)単位で駆動制御できる発光手段を利用することで、前記した2種の駆動信号を用いて、同期の取れた表示出力14を得ることを特徴とする。

#### 【0024】

画像信号10は、図中A1,A2等で示すように平面上に配置され画素の集まりで構成される。画像信号10は、画素の信号レベルを表すデジタルデータの集合である。画像信号10は、画素の順番、ピット位置の順番、あるいは色の順番等を、あらかじめ定めておくことで、信号線等を介して伝送できる。画像信号10は、正規化処理回路3を用いて、正規化信号11と正規化係数12に変換する。この信号変換の具体的な内容については後で説明を行うが、正規化信号11はLCD駆動回路6によりLCD駆動信号16に変換され、また、正規化係数12はLED駆動回路7によりLED駆動信号17に変換される関係にあるとするが、両者は2つの駆動信号と言う本発明の特徴においては同一に扱うことができる、以下の説明において両者は混在して利用することがある。正規化信号11とLCD駆動信号16、正規化係数12とLED駆動信号17は、例えばガンマ特性のような表示装置に特有の特性に基づいて、LCD駆動回路6およびLED駆動回路7により変換する関係にあるとする。このように本発明は、正規化信号11と正規化係数12、あるいはLCD駆動信号16とLED駆動信号17について、画質向上の信号処理を行うことを特徴とする。

10

#### 【0025】

液晶パネル20とバックライト21は、上記のようにして生成される2種の駆動信号による組み合わせ動作として、表示出力14を得ることから、2種の駆動信号はフレーム単位の同期が確実に取れていることが不可欠である。このためには、正規化処理回路3から、LCD駆動回路6とLED駆動回路7に伝達される正規化信号11と正規化係数12が、フレーム単位の同期を確実に取ることが不可欠である。このように本発明は、フレーム単位の正規化信号11と正規化係数12を伝送するための、伝送フォーマット、伝送手段を規定することで、機器間の信号接続を確実に実現することを特徴とする。

20

#### 【0026】

ここで、正規化処理回路3とLCD駆動回路6およびLED駆動回路7の間がシリアル伝送路を用いるならば、信号成型回路4を用いて正規化信号11と正規化係数12の2種の信号をシリアル信号15に変換して送信し、受信側では信号分離回路5を用いてシリアル信号15を正規化信号11と正規化係数12の2種の信号に分離することで、2種の信号の両者をフレーム単位の同期を取りながら伝送することを実現する。上記シリアル伝送路は多くの種類とバリエーションがあるのは当然であり、物理的に1本の光ファイバーである場合、1組の導線である場合、あるいは無線電波である場合などを含む。このように本発明は、シリアル伝送路を用いて、フレーム単位の正規化信号11と正規化係数12を伝送するために、信号成型回路4と信号分離回路5を備えることを特徴の一つとする。こうして、正規化信号11と正規化係数12の2種の信号を用いて両者の同期を取りながら表示出力を行うことで、高い画質を実現する。

30

#### 【0027】

尚、図1においてバックライトを領域で分割し、各分割した領域ごとに制御することも可能となる。この場合は、以下の各実施例で示すように輝度制御を工夫する必要がある。

#### 【0028】

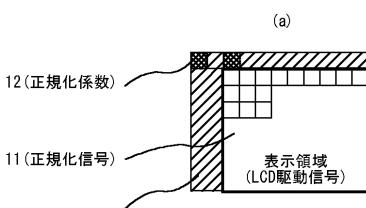

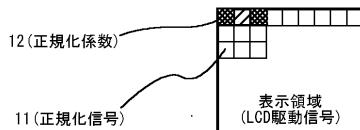

##### (2) 伝送フォーマット

本実施例の伝送フォーマットについて図2を用いて説明する。

#### 【0029】

40

50

図2(a)は、1フレーム内の帰線期間に正規化係数12を配置して、表示領域に正規化信号11を配置する構成を示しており、表示画面に影響を与えることなく、2種の信号を伝送することができる。また、バックライトの分割数に応じて、帰線期間における正規化係数12の個数を設定することになる。これらの設定状況は送信者側と受信者側で確認できている必要があるため、フォーマットの設定状況を、該信号系列中に記述することで受信側に通知する、あるいは伝送に先だって送受双方においてネゴシエーション手順による確認動作を行う、等の手順を利用する。

#### 【0030】

図2(b)は、1フレーム内の表示画面内の1部の画素に正規化係数12を配置して、残る表示領域に正規化信号11を配置する構成を示しており、表示画面内の画素の信号のみを扱うことで、2種の信号を伝送することができる。ここでは、表示領域の特定画素においてバックライト駆動信号を表すようとする。したがって、表示領域において、2種類の駆動信号が混在することになる。例えば、既存のパソコンのようなソフトウェア処理で表示領域の画素信号を設定することができる装置構成においては、正規化信号11、および、正規化係数12の両者をソフトウェアによる数値設定で制御できるメリットがある。

10

#### 【0031】

なお、図面では特定の画素位置に正規化係数12を配置する例を示しているが、これらの画素位置は視覚的に判別しにくいように、すなわち画質に影響を与えるくいように配置することが出来る。例えば、フレーム毎に画素位置を変化させることで時間的に判別を困難にする方法、あるいは信号値を複数画素に分配することで信号振幅的に判別を困難にする方法、あるいは、いわゆる透かし情報として画面内に配置する方法などを利用できる。また併せて、フレーム単位の信号制御を容易にするための補助信号として、例えばフレーム番号、などを付加することもできる。

20

#### 【0032】

本発明は、上記図2(a)および図2(b)に示すように、正規化係数12と正規化信号11の2種の信号のシリアル伝送において、ある画面に関わる正規化係数を、該正規化係数により算出される正規化信号に先立って伝送することを特徴とする。一般に液晶パネルは、入力する画像信号の画素の順序に従って、液晶パネル面上の画素の素子に駆動信号を伝達する。本発明は、該画素の駆動信号の伝達のタイミングに基づいて、バックライトの発光量を制御するための駆動を行う。ここで、あらかじめバックライトの駆動信号として利用する正規化係数を伝達しておくことが、液晶パネルの駆動とバックライトの駆動のタイミングを任意の関係で設定するために効果的である。具体的には、ある画面の画像信号に基づく液晶パネルの画素の駆動の開始時点から、次の画面の駆動に移るまでの、1画面周期内の任意の時点でバックライトの点灯を制御できるようになる。この効果を説明するには、逆の順序で伝送する場合を仮定すればよく、この場合には、バックライトの駆動に利用する正規化係数が入力する時点では、液晶パネルの全ての画素の駆動が終了した段階であることから、液晶パネルの駆動とバックライトの駆動のタイミングの設定の自由度が著しく制限されることになる。液晶素子は、時間的な応答速度がミリセカンドの単位であることから、本発明によれば、上記の液晶パネルの駆動とバックライトの駆動のタイミング設定の自由度を高めることが出来ることにより、表示出力の画質を向上させることに効果がある。

30

#### 【0033】

画像信号の伝送方式としては上記に限らず、例えばビットごとに用意する信号線を用いた伝送が可能であることは言うまでも無い。しかしながら、複数の信号線による伝送路の構成方法は、信号線間の伝送時間のばらつき(スキー)により高速化が困難なこと、無線電波あるいはネットワーク等のシリアル伝送方式と互換が取りにくいこと、などの課題がある。本発明は、正規化係数12と正規化信号11の2種の信号をシリアル伝送する方式を規定しておくことで、機器間の接続を容易に実現できるメリットがある。本発明の画像信号の伝送方式は、色信号の組み合わせに柔軟に対応できる。例えば、RGBの3色信号を伝送する装置構成において、RGB3色信号をそれぞれ独立した三つの色信号に分解

40

50

して、それぞれの色の正規化係数と正規化信号をシリアル伝送するように構成することで、それぞれの色ごとにフレーム単位の同期を取りながら伝送することができる。色の種類を、RGBよりも増加させる場合には色ごとのシリアル伝送線を増加させれば良く、あるいは白黒1種類の色信号を伝送する場合には有効な信号線を1本だけとしてシリアル伝送すれば良く、色数の変化に柔軟に対応できる装置構成を実現することが出来る。

【0034】

あるいは、同期を取るためにには、色信号の種別には関わり無くビットの集合ごとに分割してシリアル伝送することも可能である。例えば、各8ビットRGB色信号、合計24ビットの信号線を、7ビットの集合単位で分割するならば、3本の7ビット信号線と1本の3ビット信号線の合わせて4本となり、それぞれの集合単位をシリアル伝送線で伝送するように構成することも出来る。

10

【0035】

また上記のようなフレーム単位の信号形式は、従来のフレーム単位の画像信号の表現形式と互換性を保つことが出来て、従来の電気的な信号線をそのまま利用できるメリットがある。これは、既存のディスプレイ向けに製造された信号伝送手段を利用して、本発明の新たな画像信号の伝送を実現できるメリットがあり、製造コスト削減とともに、従来方式から本発明の方式への移行を容易に実現できるメリットがある。

【0036】

(3) 正規化係数と正規化信号

ここでは、本実施例の全体図である図1における正規化処理回路3の動作内容と、正規化処理により作られる正規化信号11と正規化係数12について説明する。

20

【0037】

入力する画像信号は、前記したように画素ごとのデジタルデータであり、例えばRGBそれぞれ8ビット、あわせて24ビットで表される。

【0038】

ここで画像信号の正規化処理とは、ある画像領域を単位として、該領域内の最大値を1.0になるように変換することである。

【0039】

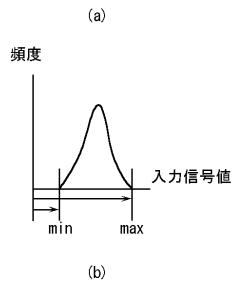

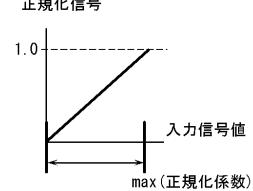

正規化の単位とする画像領域は例えば画素数Nによって設定する。画素数Nの領域において、図3(a)に示す入力信号の大きさの測定結果(ヒストグラム)から最大値maxを求めて、図3(b)に示すように各画素の信号を前記maxで割り算した結果は最大値が1.0となる小数であるが、デジタルデータで表すために任意の係数を掛けて、例えば8ビット2進数に変換して、正規化信号として利用する。また最大値maxは、正規化処理のための係数として、正規化係数として利用する。なおヒストグラムの最小値minは、以下に述べるオフセットとして扱うことが出来る。

30

【0040】

上記の正規化処理は、関係式 $A = F(B, C) + D$ として表記することができる。ここで入力する画像信号をA、1画素単位の正規化信号をB、N画素単位の正規化係数をC、およびオフセットDである。組み合わせ特性Fは、BとCの2項を要素とする線形もしくは非線形の関係を表して、例えば組み合わせ特性Fを掛け算で置き換えるならば、上記の関係式は、 $A = B \times C + D$ となる。

40

【0041】

以下の説明において、画像データ $A = B \times C + D$ 、あるいは画像データ $A = B \times C$ という記述を混在して利用する。

【0042】

上記のヒストグラムにおける最小値minを、強制的に0に設定するならば、D=0において両者は同一であることは明らかである。また表示において、Dは無信号時の表示出力Aを決める値であるため、強制的にD=0に設定することは無信号時に黒表示をすることに相当して、画質的な劣化にはならない。したがって、本発明の特徴を説明するにあたり両者を区別する必要が無い場合には同一に扱うものとする。

50

## 【0043】

例えば  $A = B \times C$  という信号表現の場合に、 $B$  と  $C$  をそれぞれ 8 ビットで表すならば合わせて 16 ビット必要になる。しかし正規化係数  $C$  は、 $N$  画素単位に用意すれば良いことから、画面全体としてのデータ増加量は最大で 2 倍であるが、多くの場合のデータ増加量は比較的に少なく設定できる。例えば  $N$  を 1 画面の画素数とするならば、表示出力できる階調数は  $B$  と  $C$  の組み合わせでありながら、画面全体のデータ量は 1 画面 8 ビットの正規化係数  $B$  と、1 画素 8 ビットの正規化信号  $C$  であるから、データ量の増加は  $8 / N$  ビットで、高い画質の表示出力が可能となる。このようにして得られる正規化信号  $B$  と正規化係数  $C$  は、前記した図 1 に示す表示装置の正規化信号 11 と正規化係数 12 と対応付けることができる。バックライトが画面全体を一括して照明する場合には、 $N$  は画面全体を構成する画素数となる。1 画素単位の正規化信号 11 を、液晶パネル 20 の透過率を制御する LCD 駆動信号 16 として、また、 $N$  画素単位の正規化係数 12 を、バックライト 21 の輝度を制御する LED 駆動信号 17 とすることで、両者の組み合わせにより表示出力 14 を得ることが出来る。10

## 【0044】

上記は、 $N$  が画面全体を示す場合であり、正規化処理の単位と、駆動回路の動作単位を一致させることができる。一方で本発明は、制御部 1 の正規化処理の単位と、表示部 2 の動作単位を異なるように設定することができる。

## 【0045】

また設定する  $N$  の大きさは、バックライトの構成次第で変化する値である。したがって制御部 1 には、正規化の単位を設定する手段を用意することができる。上記を実現するために本発明は、表示出力に先立って、バックライト特性を始めとする表示部 2 の特性を記憶する手段を用意することを特徴とする。20

## 【0046】

## (4) 正規化の単位

正規化処理の単位は、制御部 1 の信号処理において、表示部 2 のバックライト等の構成に依存せずに設定することもできる。

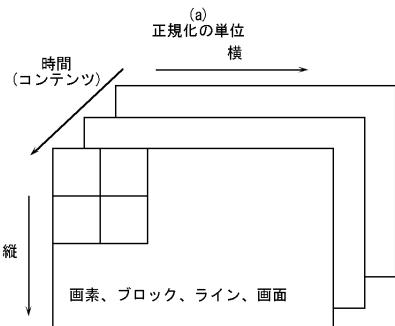

## 【0047】

図 4 (a) に示すように、時間軸方向の番組内容 (コンテンツ)、画面、ブロック、ライン、画素、などを設定することができる。図 4 (b) に、一つの正規化係数と、それにより正規化処理して得られる RGB 色ごとの正規化信号から作られるデータ構造の例を示す。ここで正規化係数は、正規化の単位ごとに設定する。正規化信号は、画像信号と正規化係数を用いて画素ごとに設定する。また 1 画素を RGB 3 色の色信号で表す場合には、各色ごとの正規化係数を設定することも、正規化係数を 3 色共通に設定することもできる。また、両者の信号に加えて、正規化処理の方法とデータ構造を識別するための、付加情報を付け加えることができる。30

## 【0048】

本発明は、正規化処理して得られた正規化信号と正規化係数は、あとから、正規化の単位を変換することができる。例えば、複数画素からなるブロックを正規化処理の単位とする場合に、正規化処理により得られる正規化係数と正規化信号を、より大きな複数ブロックを単位とする正規化係数と正規化信号に変換することができる。例えば二つのブロックを一つに統合する場合には、それぞれのブロックの正規化係数は、それぞれのブロックに含まれる画像信号の最大値であるから、二つのブロックの正規化係数の大きな方の値は、二つのブロックに含まれる画像信号の最大値であり、この最大値を統合ブロックの正規化係数とすることができます。そして、それぞれの画素の信号は、正規化係数と正規化信号を用いて可逆に戻せることから、あらたに設定する正規化係数で再び正規化処理することで、正規化の単位の変換が完了する。40

## 【0049】

同様の手順を用いて、あらかじめ制御部において正規化処理を行った信号を用いて、表示部において表示部特性に基づく正規化信号に変換することができる。したがって、表示50

部の特性が不明である場合においても、あとから正規化の単位を変換しやすいうように比較的に少ない画素数Nを用いて正規化処理を行うことで、表示部の特性への依存を低減することができる。汎用性を高めるための画素数の設定としては、例えば8×8画素の領域などを設定することができて、該画素領域の設定の情報を、例えばヘッダ情報として付加することができる。こうして、得られた正規化信号と正規化係数の汎用性を増すことができる。

#### 【0050】

ところで、上記した数値の正規化表現は、数値の浮動小数点表現と相互に変換することができる。浮動小数点表現は、仮数部と実数部の2種の組み合わせで数値を表す方法であり、有効数字を確保しながら信号振幅範囲を広く取れることが特徴である。一方、正規化表現は、信号振幅範囲の最大最小等の基準値を正規化係数として、正規化の結果を正規化信号として、正規化信号で表される有効数値を0から1の小数点範囲を全て利用することができる。正規化表現がブロック内の最大値で正規化処理していたのに対して、浮動小数点表現は10のべき乗(10進数の場合の桁位置に相当)で正規化処理して、10のべき乗を仮数部、正規化処理後の小数を実数部としていると考えることが出来る。ここで浮動小数点表現における仮数部を、画素ごとではなくて、ブロックごとに設定するならば、両者共に良く似たデータ構造を持ち、若干の信号処理で相互に変換できる。本発明の以下の説明では画像信号の正規化表現を主体にするが、上記のように、浮動小数点表現と正規化表現は置き換えて、両者共に同様の効果を得ることが出来る。

#### 【0051】

例えば、コンピュータグラフィックスのデータ生成においては、HDR(High Dynamic Range)と呼ばれる浮動小数点表現が使われることがある。しかしながら、画像信号の出力段階において固定ビット表現の信号出力手段しか用意されていない場合には、8ビット程度の固定ビット数に変換してからディスプレイに伝送することになる。本発明の実施例の一つは、コンピュータグラフィックスの生成データの表示出力手段として、正規化表現の信号を表示する装置を用意することで、固定ビット数に変換することなく浮動小数点表現あるいは正規化表現のままで伝送して、受信側においてディスプレイ特性に合わせた信号処理を行い、表示することで、画質向上の効果を実現する。ここで画質向上の例としては、ガンマ変換の精度向上、表示データの最大最小値に基づく画面輝度の制御、色変換の精度向上、などを実現できる。上記は、例えばパソコンに備えるグラフィックスボードの機能として実装することができる。そして、グラフィックスボードとディスプレイを接続する信号として、浮動小数点表現あるいは正規化表現の画像信号を用いて、ディスプレイ側で受信した正規化信号と正規化係数について信号処理を行うことで、ディスプレイ特性に合わせ込んだ表示を行うことが出来る。この結果、生成した画像信号を劣化させること無く表示部で利用することができるので、高い画質の表示出力を得られるメリットがある。

#### 【0052】

浮動小数点表現あるいは正規化表現の画像信号は、データ量が増加することが問題となる場合がある。特に、画素数が多く、フレームレートが高くなるほどに画像データが増加して、信号線のデータ伝送レートが上昇することになる。データ量の増加を防止するには、一般に知られているデータ圧縮の手法を利用できることはいうまでも無い。さらに本発明は、浮動小数点表現における仮数部、正規化表現における正規化係数を、複数の画素について共通利用することで、データ量の増加を防止する。これは、画像信号においては、平面方向および時間軸方向において信号相關性が高いことを利用するものである。例えば、画面を複数のブロックに分割して、該ブロック内では、前記の仮数部あるいは正規化係数を単一の数値で表現することで共通利用する。

#### 【0053】

上記の数値表現により、固定ビット数値表現に比較して、データ量の増加を僅かに抑えながら、遙かに広い信号振幅範囲を扱うことが出来るようになり、信号処理の精度向上と、画質向上の効果を得ることが出来る。

#### 【0054】

10

20

30

40

50

ここで、正規化係数と正規化信号の発信を行う装置として制御部1、受信を行う装置として表示部2とするならば、制御部1と表示部2の構成は特に限定するものではなく、以下の例を示す。

【0055】

- 1) 同じ筐体に、制御部と表示部を組み込む

- 2) 制御部の機能はテレビジョン放送局に置き、放送信号として上記信号を含めることで、受信側の表示部を駆動する

- 3) 制御部の機能はパソコン搭載手段で実現して、処理結果を一般の映像信号として伝送することで、表示部を駆動する。

【0056】

上記の画像信号の伝送に先立って、制御部と表示部の能力を相互に確認するためのネゴシエーション手順を用意することが出来ることはいうまでも無い。ネゴシエーション手順は、いわゆるプロトコル階層においては上位に位置して、アプリケーションレベルで実行されるものであり、例えばG3あるいはG4ファクシミリ装置で利用されているような機器能力交渉手順、あるいは、XMLと呼ばれるマーキング言語等を利用して特性表示できることは言うまでも無い。

【0057】

前記したコンピュータグラフィックスの例は、上記3)の構成に該当して、パソコン上のグラフィックスボードを利用して浮動小数点表現あるいは正規化表現の画像信号を生成して、表示部に伝送する。

【実施例2】

【0058】

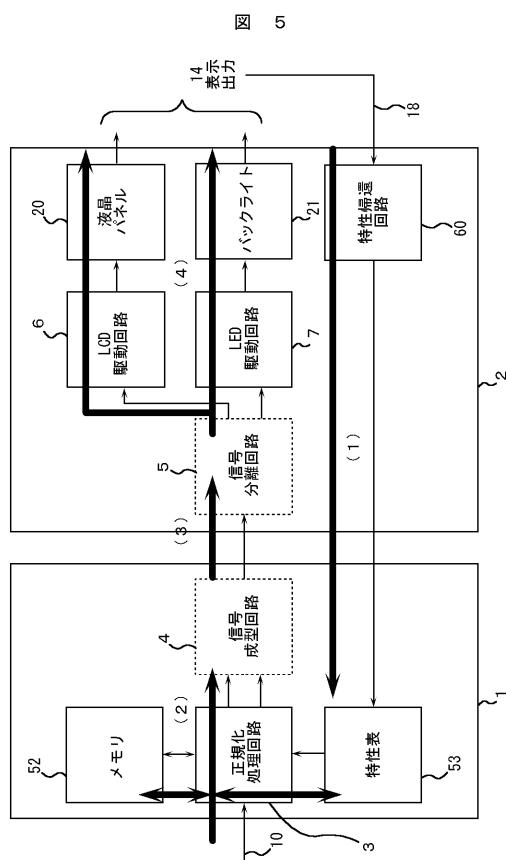

図5は、本発明を構成する制御部1と表示部2を示す図である。ここで、上記構成における主な信号フローを、図中の矢印で示すように、次の4つに分類して説明する。

【0059】

(1) 表示部の特性設定

表示部2が備える特性を、センサ信号18として採取して、特性帰還回路60を用いて制御部1に伝達する。

【0060】

ここで、センサ信号18は、何らかのセンサを用いて採取する変動成分であって良く、あるいは、表示部2が備える静的な特性であっても良い。これらのセンサ信号18の採取、および特性帰還回路60から制御部1への特性伝達は、任意のタイミングで行うことが出来て、例えば工場出荷時、あるいは電源ON時、あるいはキャリブレーション動作時、あるいは一定の時間間隔などとすることができます。こうして採取、伝達した特性データは、特性表53に記憶しておくことで、任意の時間に読み出して利用することができる。

【0061】

(2) 入力画像信号の正規化処理

制御部1は、画像信号10を入力して、表示部2の特性に基づいて正規化処理回路3により、正規化信号11と正規化係数12に変換する。正規化処理回路3は、特性表53から読み出す特性データを利用する。信号処理の手順を実行するためにメモリ52を利用することができる。

【0062】

(3) 正規化処理後の信号伝送

正規化信号11と正規化係数12の2種の信号を、フレームごとに同期をとって伝送するため、信号成型回路4で信号フォーマットにまとめて送信する。本発明は、伝送路の物理的な形態を限定するものではなくて、導線、光ファイバー、あるいは電波等の手段を利用して信号伝送することができる。

【0063】

(4) LCDとLEDの駆動

表示部2は、信号分離回路5を用いて受信信号のフォーマット解析を行いフレームごと

10

20

30

40

50

の正規化信号 11 と正規化係数 12 を分離して、正規化信号 11 は LCD 駆動回路 6 を経由して液晶パネル 20 を駆動して、正規化係数 12 は LED 駆動回路 7 を経由してバックライト 21 を駆動して、両者の組み合わせとして表示出力 14 を出力する。

#### 【0064】

本発明は、上記の 4 つの信号の流れを組み合わせて実現する。信号の流れは、時間的に同時であるもの、あるいは時系列的であるもの、あるいは、非同期であるものなどがあつてよい。

#### 【実施例 3】

#### 【0065】

##### (1) バックライトと表示パネルと正規化処理

10

ここでは表示部のバックライトを構成する発光手段、特に LED に代表される固体発光素子を利用して、平面の発光を行う装置構成について説明する。

#### 【0066】

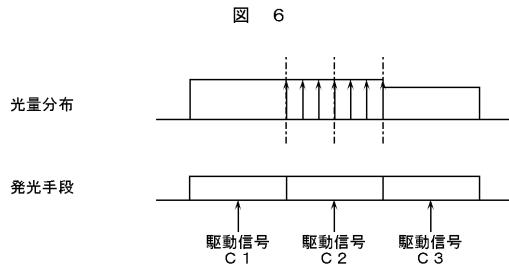

図 6 は、3 個の発光手段の配置構成を断面方向から図示する。簡単のため、個々の発光手段は隙間無く隣接するように並べられ、また個々の発光手段は該当する面内領域で均一な発光量であるとするならば、個々の発光手段に独立に駆動信号を与えることで、ステップ関数の形状の発光分布となる。一般に、個々の発光手段による発光分布の面積は液晶パネルの単一の画素面積よりも大きいことから、バックライトの単一の発光手段は、液晶パネルの複数画素を同時に照射することになる。この画素領域が、前記した正規化処理の単位に相当する。発光手段による発光量が正規化係数に相当して、液晶パネルの画素の透過率が正規化信号に相当する。

20

#### 【0067】

そして、発光手段による発光分布と、液晶パネルの個々の画素の透過率の両者を駆動することで、表示出力を得ることが出来る。

#### 【0068】

ここでバックライトの種別によって、発光手段の構成方法が異なる場合があるが、画面サイズの画面内の分割数、分割領域内の画素数、分割領域の寸法、などの情報を予め用意することで発光手段の特性を示すことができる。発光分布は、面内位置と発光量の対応関係であるので、例えば表形式、あるいは何らかの関数近似により表すことが出来る。また LED 等の発光手段は、代表的な発光波長特性を有するが、個々のチップごとに発光波長のばらつきを有する場合があり、さらに製造技術等の進歩により発光波長の特性が変化する場合がある。発光波長の利用方法により波長特性の表し方が異なって良くて、代表的な波長特性のみが分かれば良い用途では、ピーク波長のみで波長特性を表すことが出来る。これらの発光手段の特性情報は、個々の発光手段に近接した記憶手段に書き込んで置くことで、該記憶手段から情報を読み出して利用することができる。あるいは、例えばインターネット等の通信路を経由して何らかのデータベースを参照することで詳細な特性を入手して、信号処理に利用することも出来る。

30

#### 【0069】

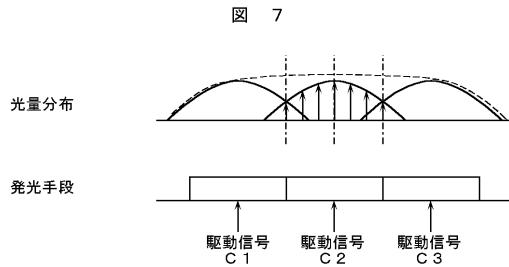

図 7 は、3 個の発光手段を備えるバックライト構成において、発光手段の領域間で発光分布のリーコンプ特性がある場合を、断面方向から図示する。

40

#### 【0070】

一般に、発光手段の分割領域の境界と、液晶パネルの画素の境界を一致させることは、高い組み立て位置精度が必要となり、容易ではない。また液晶パネルとバックライトの面間距離をゼロにすることは困難であるから、両者の空隙において斜め方向の放射光が発生する。上記の事情から、バックライトを構成する発光手段の領域に発光分布のリーコンプが発生することになる。発光分布のリーコンプは、個々の発光手段の制御の独立性を崩すものであるが、発光分布のリーコンプが滑らかで大きいほど領域境界における発光量の変化が緩やかであるから、液晶パネルとバックライトの組み立て位置精度を低く抑えることができるメリットがある。

50

## 【0071】

そこで本発明は、バックライトを複数の発光手段の組み合わせで構成する場合において、分割領域間の発光分布のリークを許容して、信号処理により発光分布のリークを補正することで、組み立てに要求される位置精度を軽減する効果を得る。発光分布のリークを補正するために、まずリークを含めた発光特性を測定して、記憶手段に書き込み、該記憶手段を読み出すことで信号処理に利用できるように構成する。リーク特性は、発光手段とLCDパネルとの組み合わせ、面内位置、等により変化することから、発光手段の単品の特性ではなく、液晶パネルとバックライトとして組み立てた状態で測定することが望ましい。

## 【0072】

10

原理的には、バックライトを構成する全ての発光手段の全ての動作の組み合わせと、液晶パネルの全ての画素位置における発光量を測定することになる。つまり原理的な測定手順は、それぞれの発光手段に駆動信号を供給して、面内に位置する画素に照射される光量を測定することになる。そして該測定結果は、個々の発光手段の駆動信号と、測定画素の位置の組み合わせを条件として、測定値が出力値となる表形式で表されることに成る。

## 【0073】

上記の原理的な測定手順と、測定結果を書き込む表の大きさは、膨大な組み合わせとなることから実用的ではない。

## 【0074】

20

本発明では、個々の発光手段特性の類似性、個々の発光手段、発光分布の対称性、あるいは、発光手段特性の関数近似などの手法により、必要なデータ量を大幅に削減することが可能となる。

## 【0075】

なお説明を省略したが、発光波長を制御するために、例えばRGB3色の発光手段を組み合わせることができるのは言うまでも無く、上記と同等に発光特性を測定することができる。さらにRGB以外の原色を組み合わせて利用することもできる。

## 【0076】

30

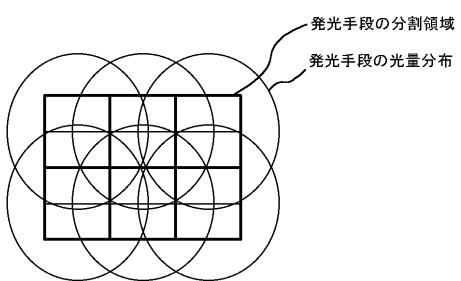

## (2) 発光分布特性

本発明は、光源手段による発光分布特性が大きな役割を持つことから、まず最初に、発光分布特性の採取が不可欠である。発光分布特性の測定手段および測定方法の一例を以下に示す。この測定を行うタイミングとしては、機器の仕様設定の段階、実際に組み立てた段階、工場出荷時、あるいは設置後の任意の段階、等がある。実際には、赤緑青等の光源色の組み合わせで測定を行い結果をまとめるが、以下の説明では簡単のため輝度信号のみとする。

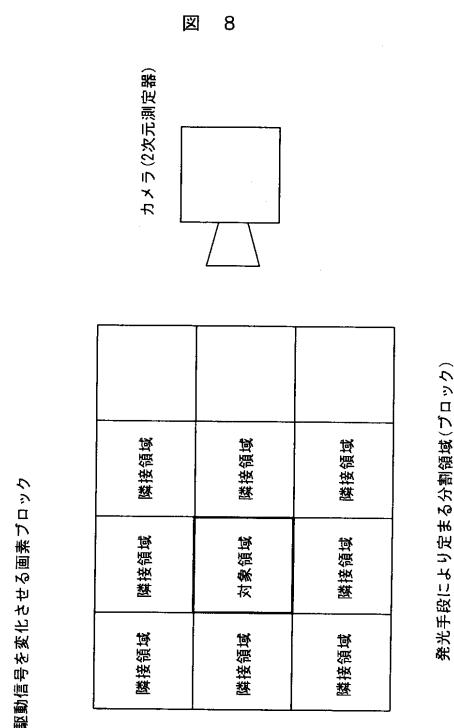

## 【0077】

図8はバックライトと液晶パネルの組み合わせで構成される表示装置の特性測定の装置構成を示している。最も原理的な測定方法は、バックライトと液晶パネルの2つの駆動信号の全ての組み合わせについて、全ての画素位置における表示出力を測定することである。

## 【0078】

40

一方、バックライトを構成する個々の発光手段の特性が同一であると仮定するならば、バックライトの任意の位置における発光量は、個々の発光手段による発光量の積算として算出できることから、単一の発光手段の発光分布のみを測定しておけば良いとすることができる。

## 【0079】

## (3) バックライト特性

バックライトを構成する複数の発光手段の組み合わせにおいて、個々の発光手段の発光分布が同じである場合には、代表的な発光分布特性のみを記憶手段に記憶して、該記憶手段から該画素位置の発光量の読み出しを行い、それぞれの発光手段による発光量を加算することで、該画素位置のバックライトの発光量を算出することが出来る。

50

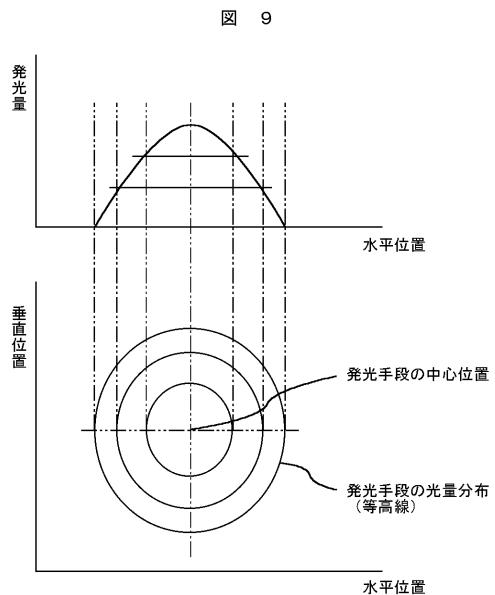

## 【0080】

図9は、発光手段の発光分布を、水平と垂直の2次元の等高線として図示した例を示す。該発光手段を、バックライトとして構成する場合には、隣接する発光手段の位置における発光分布が、リークとなる。上記発光手段の水平垂直の位置を、液晶パネルの画素位置と対応付けて、各位置における発光量を記憶手段に書き込んでおくことにする。これにより、ある画素位置に関わる複数の発光手段の発光量を、前記記憶手段から読み出すことができる。また、複数の発光手段の組み合わせにおいて、個々の発光手段の発光分布が同じである場合には、代表的な発光分布特性のみを記憶手段に記憶して、該記憶手段から該画素位置の発光量の読み出しを行い、それぞれの発光手段による発光量を加算することで、該画素位置のバックライトの発光量を算出することができる。

10

## 【0081】

等高線の高さ、すなわち発光量の大きさは駆動信号の大きさに依存して変化するが、発光分布の形状が相似関係にあるならば、単一の発光分布の特性のみを用意すれば良い。また、等高線の形状が、左右、もしくは上下、もしくは左右上下に対称であるならば、該対称性を利用することで、前期の画素位置と発光量の関係を記憶することができる。例えば左右上下に対称であるならば、4分の1の領域のみの対応関係を記憶すれば良いので、データ量は4分の1となる。

## 【0082】

上記データは、任意のデータ構造で記憶することができる、例えばXML（エクステンデッドマーキングランゲッジ）として知られる記述言語を利用することができる。あるいは、発光手段の発光分布の断面形状、等高線の形状などを、何らかの関数で近似して置き換えることでデータ量を削減することができる。測定値を近似関数で置き換える手法は、例えば重回帰などが従来から知られている。例えば、採取したデータを、三角関数を基底として重回帰分析を行い、三角関数の次数に対応する係数値を算出して記憶する。該計数値を、三角関数の係数値として利用すれば、採取データを近似することができる。

20

## 【0083】

簡単のために、バックライトが16個の発光手段で構成され、それぞれの発光量を制御するための駆動信号を供給するならば、フレームレート60枚/秒として、1秒間に960回（=16個×60フレーム/秒）のデータ書き込みが必要になる。16個のそれぞれの発光手段を独立に制御するためには、それぞれの発光手段に少なくとも2本の駆動信号線を接続することが必要であるから、合計32本（=16個×2本）の信号線を配線することになる。

30

## 【0084】

ここで1回の書き込みデータを、該発光手段の識別コードと発光量制御のための16ビットデータで構成するならば、1秒間14400ビット（=960回×16ビット）となり、データ転送速度は14.4kビット/秒になる。ここで識別コードとは、個々の発光手段を区別するために付加する信号であり、上記例においては高々16個の発光手段を区別できれば良いが、発光手段の製造方法あるいは流通方法との関わりで、必要とするビット数は任意に設定すればよい。発光手段は、送られてくる識別コードから、引き続いて送られてくる発光量制御信号の取捨選択を行うことができる。

40

## 【0085】

本発明は、上記データ転送速度を実現するシリアル伝送線を用いて、バックライトを構成する発光手段に発光量制御のための駆動信号を伝達することを特徴とする。本発明によれば、それぞれの発光手段には、直流電源供給線2本と、シリアル伝送信号線2本を用意すればよく、両者のグランド線を共通にするならば合計3本の信号線を用意すれば、それぞれの発光手段の発光量を制御することができる。ここで、それぞれの発光手段の3本の信号線は、並列配線で接続することができるので、配線を簡略化できる効果がある。さらに、電源供給線を、発光量制御信号の伝達と兼用することも出来て、その場合には2本の信号線で、上記と同様の動作を実現することができる。

## 【0086】

50

また、発光手段の特性データの伝送を、上記のように識別コードとの組み合わせで実行することができる。例えば、外部から識別コードと内容コードを供給して、識別コードで発光手段の区別を行い、内容コードで読み出す特性データを指定して、引き続いて特性データの出力動作を行う。複数の発光手段について、これらの動作を行う信号線を共通に接続しても、確実に区別が出来るため、信号線の配線を簡略化できる効果がある。また発光手段には、何らかのセンサを備えて、該センサにより採取された信号を、上記の特性データの出力動作と同様に、外部へ転送することが出来る。このセンサとしては、該発光手段の発光量を検知する光学的なセンサ、該発光手段の動作温度を検知する温度センサ、該発光手段の動作電流を検知する電流センサ、該発光手段の動作時間を計測する経過時間センサ、などを利用することができる。これらのセンサ信号は、アナログ信号であっても、デジタル信号であっても良い。

10

#### 【0087】

本発明によれば、配線を複雑にすることなく、個々の発光手段の動作状態をセンサ測定することができるために、該測定結果を用いて、精度の高い制御を実現することが出来る。

#### 【0088】

発光量の分布特性は、画素単位の信号値で表すことが出来るほか、複数画素に渡る分布特性を何らかの関数で近似することができる。本発明は関数近似の手法を限定するものではなく、三角関数、べき乗関数、などの組み合わせを利用することが出来る。測定で得られる分布値を関数近似するのは、重回帰などの周知の方法を利用することができる。

20

#### 【0089】

発光分布特性は、面内の2次元における分布値であるから2次元の関数近似を行うことができるが、あるいは面内の対称性がある場合には次元数を削減することができる。例えば、発光手段が正方形の形状であり左右上下に発光分布が対称であるならば、中心点を含む分割領域についての発光分布を関数近似の対象とすれば良い。

#### 【0090】

これらの関数近似は、発光手段の特性として事前に算出して事前に記憶手段に書き込み、用意することができる。

#### 【0091】

記憶手段への書き込みは、専用の書き込み信号線を用意することもできるが、あるいは電源線と共に用する信号伝達を行うことも出来る。

30

#### 【0092】

書き込むタイミングとしては、個々の部品の製造出荷時において該部品と対応付けが可能な記憶手段へ書き込む、部品を組み立て後の製品出荷時において該製品の特性測定結果を該製品と対応付けが可能な記憶手段に書き込む、該製品の動作時においてセンサ等を用いた特性測定結果を帰還して記憶手段に書き込む、等とする。

#### 【実施例4】

#### 【0093】

本発明は、正規化表現による正規化係数と正規化信号の2種の信号を用いた画像信号の伝送、表示出力をを行うことを特徴としているが、新たな表現形式の画像信号を伝送するための、新たな方法と手段を規定することも本発明の特徴である。特に画像信号の伝送は、既存の装置との互換性を保つことも重要な観点であることから、このために本発明は、従来の画像伝送方式から本発明の画像伝送方式へのスムーズな移行も考慮した提案を行うものである。

40

#### 【0094】

##### (1) 回路構成

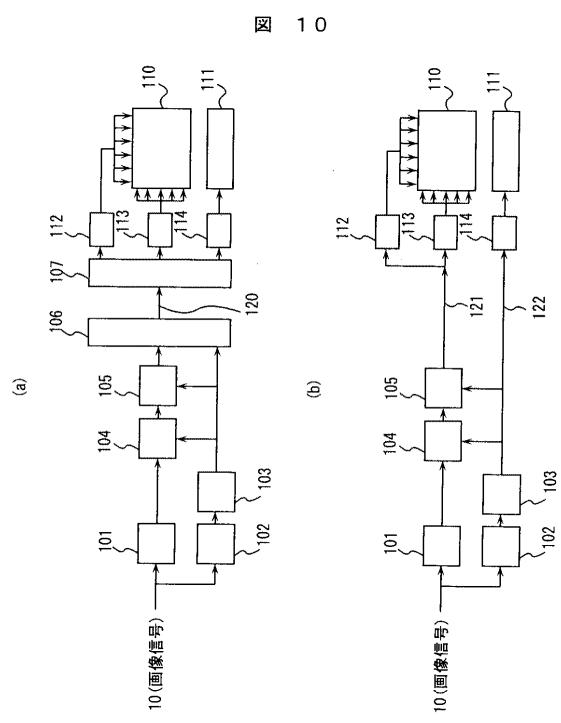

図10は、本発明を実現する回路構成例を示している。図10(A)は制御部から表示部への信号伝送をシリアル伝送する場合の構成であり、図10(B)は制御部から表示部への信号伝送をパラレル伝送する場合の構成を示す。まず両者に共通する全体の動作を説明する。

50

## 【0095】

入力した画像信号10は、フレームメモリ101に書き込むと同時に、信号測定回路102で信号特性の測定を行う。信号特性は、1画面内の画像データにおける、例えば最大最小値、ヒストグラム、色度分布、などとする。1画面の信号特性の測定結果を、同じ画面に対して反映するために、フレームメモリ101は時間合わせのための遅延回路の動作をする。測定結果を、正規化係数設定回路103にて正規化係数を設定をする。フレームメモリ101から読みだした画像信号についてノイズ除去回路104でノイズ成分の除去を行い、次に、正規化回路105で正規化係数で正規化処理を行う。こうして、複数画素の領域単位の正規化係数と、該正規化係数で正規化された画素単位の正規化信号を作成する。

10

## 【0096】

ここで、正規化係数と正規化信号を、信号線120を用いてシリアル伝送する場合には、多重化回路106を用いて、予め定める伝送順序に従いビットストリームに並び替えを行い、さらに伝送順序を再現するための同期信号を加えて、配線基板、筐体内部の電気的あるいは光学的な配線、何らかのネットワーク、無線などの適宜の伝送方式を利用して伝送を行う。該信号線120の受信側では、分離化回路107を用いて、予め定める伝送順序に基づいて、正規化係数と正規化信号を分離する。

## 【0097】

一方、信号線121および122を用いてパラレル伝送の場合には、複数の信号線の時間的なズレ(スキー)などの要因があるために、一般に長い距離の伝送は困難であるが、主に筐体内部の伝送に使うことに限定するならば、前記したシリアル伝送のようなデータ並び替えが不要であるので、簡易な装置構成とすることが出来る。ここで信号線121は正規化信号であり液晶パネルの各画素の透過率制御のための駆動信号として用いて、信号線122は正規化係数でありバックライトの発光輝度を制御する駆動信号として利用する。

20

## 【0098】

次に表示部は、表示パネル110とバックライト111を備えて、両者を独立に駆動するためのドライバを用いて、両者の組み合わせ特性として表示出力を行う。表示パネルは縦軸ドライバ112と横軸ドライバ113でマトリクス駆動を行い、該駆動のタイミングに同期してバックライトドライバ114を駆動して、両者の駆動結果として画面の表示を行うように構成する。バックライト111は、画面全体あるいは画面の一部を照明するために用いられて、正規化係数を用いて制御する。表示パネルの各画素の透過率を、正規化信号を用いて制御する。こうして、バックライトの光量と、表示パネルの透過率との組み合わせた結果が表示出力となる。

30

## 【0099】

## (2) L V D S 回路構成例

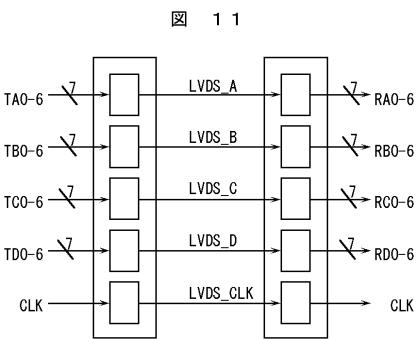

図11は、シリアル伝送としてL V D S方式による回路構成の具体例を示す。L V D Sは、Low Voltage Differential Signalの略であり、高速な信号伝送に有効な方式として知られており、送信受信のためのL S Iが市販されている。これを利用する回路構成を説明する。

40

## 【0100】

制御部1と表示部2を接続する信号インターフェースの形態には、ビット信号に対応する信号線を用意することで複数の信号線をパラレルに配線する場合と、複数のビット信号を单一の信号線で伝送するシリアル配線する場合がある。

## 【0101】

まず制御部と表示デバイスが同一筐体に組み込まれる場合には、両者の物理的な距離が短いことから、信号線の距離は短く抑えることができるとともに、比較的に多数種類の信号線をパラレルに配線することができる。また独自の仕様で配線できる。

## 【0102】

一方制御部と表示デバイスが別の筐体に組み込まれる場合は、両者の装置を接続する信

50

号線の条件は大きく変動することが予想され、条件変動に関わらず確実にデータ伝送を実現するための装置構成が必要になってくる。条件変動の一つに伝送時間のバラツキがあり、仮にパラレル伝送を行う場合にはビットごとのスキュー（遅延ばらつき）が発生することになる。このスキューの影響を排除するためには、単一の信号線を用いたシリアル伝送が有効である。

#### 【0103】

一般にLVDS方式を実現するLSIは、7ビット幅の信号線を基本単位としてシリアル伝送するように構成されている。これは、液晶表示デバイスの表現可能な階調数が6ビット（64階調）であった時期において、制御線1ビットを加えた7ビット幅が標準仕様であった経緯があるためである。7ビット幅の入力信号を7個の時系列の1ビット信号に変換して一対の信号線を利用したシリアル伝送を行い、受信側では1ビット信号を7個まとめてから7ビット幅の信号にパラレル変換して、出力する。

#### 【0104】

ここで、RGB各8ビット合計24ビットを伝送するには、7ビット幅を基本単位とする信号線を4本束ねた28ビット（ $28 = 7 \times 4$ ）を用意すれば十分であり、4本の信号線が余ることになる。本発明は、上記のように7ビット幅の信号線を単位として正規化信号を伝送すると共に、7ビット幅の余り信号線を利用して正規化係数を伝送することを特徴とする。

#### 【0105】

ここで伝送する画像データAを $B \times C$ として、正規化信号Bは画素単位と8ビット、正規化係数Cは画面単位の8ビットとする。そしてRGB3色については、正規化係数は画面単位に8ビット×3色 = 24ビット、正規化信号は画素単位に8ビット×3色 = 24ビットとなる。ここで正規化信号はパラレル伝送であり、正規化係数は余り信号線を利用したシリアル伝送とする。正規化係数のシリアル伝送のデータフォーマット、タイミング等は、この信号インターフェースが装置内部に閉じている場合には任意設定することができるから、限定するものではない。

#### 【0106】

受信側において正規化係数と正規化信号の組み合わせで画像データを確定するために、正規化信号受信に先立って正規化係数を受信するならば、正規化信号受信後の遅滞無く正規化係数を即座に反映させることができる。これを、画面表示のタイミングと、データ伝送のタイミングを工夫することで実現する。画面表示のフレームあるいはフィールドの隙間時間となるタイミングにおいて、次に表示する画面の正規化係数を伝送し、該伝送後に該画面の正規化信号を伝送する。受信側においては、画面の正規化係数を一時記憶して、引き続いて受信する正規化信号と組み合わせて表示のために利用することで、同一画面についての正規化係数と正規化信号を同期させることができる。仮に受信の順番が逆であって、同様に両者を同期させるためには、正規化信号を画面単位で一時記憶させなければならないことは明らかである。上記数値データを利用して一時記憶のためのメモリ容量を比較するならば、画面サイズをVGA（ $640 \times 480$ 画素）とすれば、画面当たりの正規化係数は前記から3バイト（24ビット）、一方正規化信号は $24 \text{ビット} \times 640 \times 480 = 921600$ バイト、となる。このように正規化係数と正規化信号のデータ量は前者が小さいことから、上記のデータ伝送の順番付けは、メモリ容量削減に大きな効果がある。

#### 【0107】

上記では正規化係数をシリアル伝送としたが、余り信号線が複数ある場合には、これらの複数の信号線を利用できる。例えば余り信号線のうち1ビットのみを利用するならばシリアルのみの伝送形式になり、2ビットを利用する場合にはパラレルとシリアルの混在伝送形式となる。この伝送形式の設定は任意であり、いずれの設定であっても受信側では正規化係数を再構成することができる。こうして、7ビットのパラレル／シリアル変換機能を持つデータ伝送手段を利用できることは、従来型のデータ伝送手段と互換性を維持しながら、本発明の特徴を実現できる効果がある。

#### 【0108】

10

20

30

40

50

上記のデータ伝送は、別の信号線として伝送するクロックあるいは同期信号により伝送タイミングを確定することが出来る。また、動作手順のリセット、あるいは特性状態へのセットを指定する制御線を別途用意して、上記データ伝送と組み合わせて動作することも出来る。

【0109】

これにより、既存のデータ伝送装置を利用することで価格、開発コスト、および信頼性のメリットがある。正規化係数と正規化信号を画面単位で同期して伝送することが出来る。

【0110】

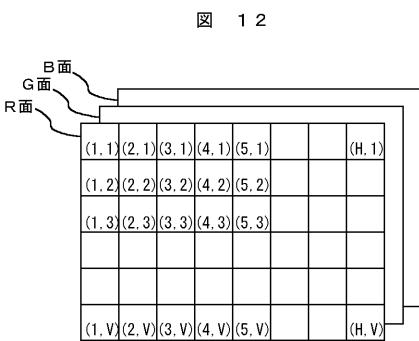

(3) 画素順序

10

図12に画面と画素の位置関係の一例を示す。RGB3色各8ビットの色信号の組み合わせで各画素の信号を表すものとする。縦横方向に画素を並べて配置することで画面を構成している。この画面構成のバリエーションは多数あり、色信号の選択、色信号ごとの画素の大きさとビット数、画面内の画素数、などを任意に設定することができる。

【0111】

この画面をデジタルデータで表現したものを画像データと呼ぶことにする。画像データを、伝送蓄積するには順序付けをしたデータフォーマットが必要になる。例えば左上を始点、右下を終点として、ラインごとに、各画素のRGB信号を、上位ビットから順番に並べることで、いわゆるビットストリームを構成することができる。こうして作られるビットストリームは、順番付けのルールに基づいて、再び画面内の画素の配置を復元することが出来る。

20

【0112】

ところで画像データの表示手段は、このようなビットストリームを入力して、画素位置に対応したRGB信号を表示のための駆動信号として利用する。基本的には全ての画素を表示するが、画面周辺に位置する画素については表示できないことがあることを許容することがある。例えば従来型のCRTにおいては、電子ビームの偏向で画面内の画素位置を設定しているが、偏向の大きさに変動がある場合や、あるいは外部磁気の影響などで、画面周辺が欠けることがあった。このような状況においても、画面中央部を重視する場合においては、画質劣化とは認識されないことが多い。

30

【0113】

本発明は上記状況を利用して、該周辺部に位置する画素の信号を、制御のための信号に置き換えることにする。例えば図面記載の画素位置(1, 1)にあるRGB信号を、直接の表示の目的としない信号に置き換えることで、置き換えた信号を制御信号として利用する。該制御信号の利用方法を、送信側と受信側の双方が予め設定しておくことで、表示手段による表示には使われないことから画質劣化を導くことは無い。また、該画素のRGB信号は欠落することになるが、例えば隣接する画素位置(1, 2)あるいは(2, 1)のRGB信号を表示のために利用することで、画像データが本来的に持っている相関性により画質はほぼ維持することができる。

【0114】

上記は単一の画素位置の信号の置き換えを説明したが、複数画素位置を利用してもよい。また、RGB信号の置き換えではなくて、既存のRGB信号に、制御信号を重畠するように変調をかけることもできる。

40

【0115】

本発明は上記構成により用意する制御信号により、画像データの正規化係数を設定する。そして、残る画素位置のRGB信号に正規化信号を設定する。

【0116】

これにより、正規化係数と正規化信号を、従来型のデータフォーマットで伝送蓄積できる。これは、画像データの生成、伝送、蓄積などにおいて、従来型のデータフォーマットに基づく手段を利用できることになるメリットがある。例えば1画面分の画像データを蓄積するフレームメモリにおいて、RGB色信号を入力してフレームメモリに書き込むとと

50

もに、該画像データの信号特性を測定して、該測定結果に基づいて正規化係数を算出し、該算出した正規化係数を画素位置(1, 1)のRGB信号に見たてて出力して、次にフレームメモリの画素位置(2, 1)から順次に読み出すRGB色信号を、前記正規化係数で正規化処理を行い、得られた正規化信号を引き続いて出力する。これにより、該画面が持つ画素数と同じ個数の信号を画像データと同じデータフォーマットで出力することができる。そして受信側装置では、正規化係数と正規化信号を分離する手段を備えることで、両者を利用した表示のための駆動制御を行う。受信装置は、該データフォーマットにおける画素位置(1, 1)の信号を一時的か記憶手段に書き込み、正規化係数として利用する。また引き続いて受信する信号を正規化信号として利用する。あるいは受信データをデータフォーマットに基づいてフレームメモリに蓄積して、該フレームメモリをメモリアドレスを用いて参照することで正規化係数と正規化信号を分離して利用することができる。ここで、バックライトと透過型液晶パネルを備える表示手段においては、該受信した正規化係数をバックライトの駆動信号として、また該受信した正規化信号を液晶パネルの駆動信号として利用する。このように、バックライトと透過型液晶パネルの二つの駆動手段を備えることで、表示出力する画像は両者の組み合わせ特性となる。両者の入出力特性がリニアであると仮定するならば、バックライトの発光量と、液晶の透過濃度の掛け算が表示出力となる。

#### 【0117】

これにより、従来型の画像データフォーマットを利用しながら、ダイナミックレンジの広い表示ができる。暗い場面においては、バックライトの発光量を低く抑えることができて、電力削減の効果がある。また暗い場面においてバックライトの発光量を低く抑えることで、液晶の濃度設定に依存しない、本来の暗さを表示できる効果がある。

#### 【0118】

上記は画面を構成する信号を用いて正規化係数と正規化信号を伝送する手段を示した。さらに、画面を構成しない信号として、帰線期間にある信号を利用することができる。帰線期間において正規化係数を伝送して、引き続く画面データにおいて正規化信号を伝送することで、1画面の表示に必要となる信号を伝送することができる。受信側においては、帰線期間にある正規化係数を一時的に蓄積することで、引き続いて受信する正規化信号に、正規化係数を反映させるための信号処理を行うことができる。例えば、液晶パネルとLEDバックライトを組み合わせる表示装置においては、上記正規化係数をバックライトの駆動に用いて、上記正規化信号を液晶パネルの駆動に用いることで、両者の組み合わせとして画面を表示出力することができる。

#### 【0119】

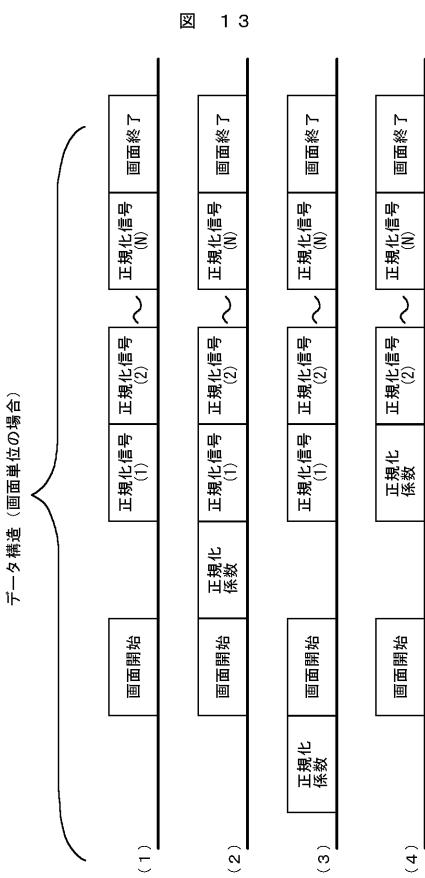

##### (4) データフォーマット

画面単位の正規化係数と、該正規化係数で正規化した正規化信号は、データフォーマットを定めて伝送、あるいは蓄積することができる。伝送する場合には、信号線の形式、伝送順序、タイミングなどの設定を行い、送信側と受信側とで共通の約束に基づいて動作することが不可欠となる。これらの約束の設定方法は、階層的な構造を持たせたり、あるいは言語的な文法構造を持たせたりすることで、破綻の無いように設定することができる。

#### 【0120】

図13は、シリアル伝送路を経由して、画面単位の正規化係数と、該正規化係数で正規化した正規化信号を伝送するデータフォーマットの例を示している。画像データは、静止画あるいは動画においても同期信号を付加することで1画面の開始と終了を表示することができる。同期信号は垂直同期信号、水平同期信号などとして定義できる。

#### 【0121】

正規化の単位としては、画素、ライン、ブロック、画面、複数画面、などを利用できて、これらの種別を識別情報として設定することで、該情報を受信する装置において種別を判断することが出来る。これらの識別情報は幾つかを組み合わせることも出来る。該識別情報に基づく正規化係数、そして正規化係数で正規化を行った正規化信号を順次に伝送す

る。正規化信号を画素単位に設定する場合には、画面を構成する画素位置と伝送順序を予め確定することで、順次の画素データとして伝送する。こうして、送信側と受信側で破綻の無いデータ伝送を実現する。また上記の正規化係数は、垂直帰還あるいは水平帰還に相当する信号に内蔵することもできる。

【0122】

表示のための画像データであっても、含まれる全ての情報が表示されないことがある。C R T のようにアナログ的な走査を行う表示デバイスにおいては、画像データの上下左右の端部が表示可能範囲を外れることがある。このように画像データの端部に位置する画素の信号を、該位置の画素を前記正規化係数で置き換えることにより、データフォーマットを変更することなく新たな制御信号を付加することが出来る。該信号は、仮に表示のために使われたとしても目立たないように信号を設定することができて、例えば無彩色に近い信号値とすることができる。

【0123】

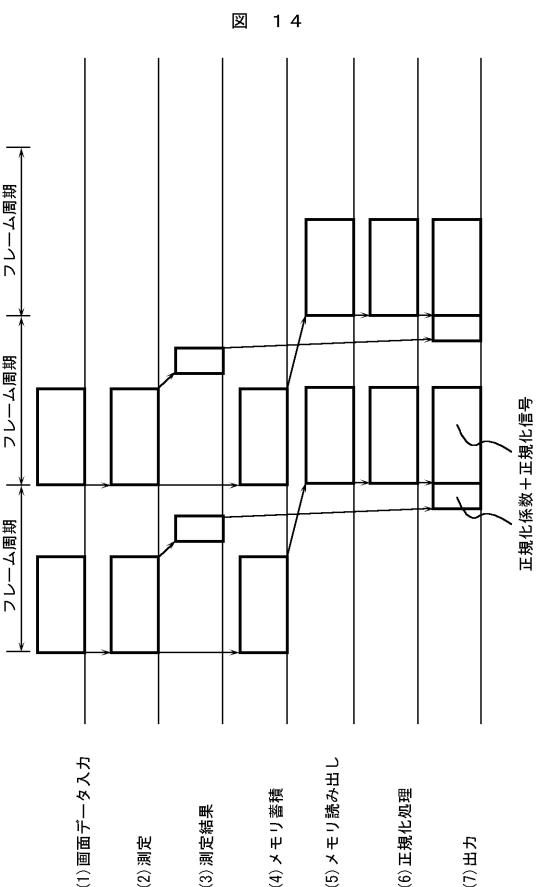

(5) 信号タイミング

図14に、動画像の表示手順を示す。

【0124】

ここでは、動画像が1画面1フレームで入力して、該画像データから正規化係数と正規化信号を算出、出力するタイミングを示している。このために、まず(1)画面データの入力を行う。画面データの大きさ(画素数)、フレーム周期、データフォーマット、色信号の種類等は任意である。(2)入力する画像データの信号測定は、画像データの入力と同時に進行。測定する信号の種類、例えば最大最小値、ヒストグラム、などの任意である。(3)測定結果は1画面データの入力後に得られることになる。(4)該測定結果を用いて該入力した画像データの信号処理を行うために、入力した画像データはメモリ蓄積をする。(5)メモリ蓄積した画像データは、適宜のタイミングで順次に読み出しながら、前記測定結果を用いて信号処理を行う。例えば正規化処理であれば、画面内の最大最小値を測定してから、該画面データの正規化処理を行う。(6)該画面の測定結果と信号処理結果を合わせて出力を行う。例えば正規化処理であれば、正規化係数と正規化信号の組み合わせとする。

【0125】

メモリ蓄積とメモリ読み出しのリードライトの時間的な余裕を作るためには、メモリのデータバス幅を広く取ることが有効である。

【0126】

画像データ出力をシリアル伝送形式とする場合には、正規化係数を正規化信号に先立つて出力する。これは例えば、正規化係数が1画面を単位として設定する信号であるならば、1画面の正規化信号に共通となる正規化係数を先立つて出力する。これにより受信側において、正規化係数に引き続いて入力する正規化信号を即座に利用して、画像データを確定することができる。

【0127】

これが逆に、正規化信号が正規化係数に先立つて出力するならば、受信側において正規化信号を1画面分蓄積した後に始めて正規化係数との関係が確定することになる。このため画面メモリが不可欠となると共に、画像データ確定するタイミングがフレーム周期遅れることになる。

【実施例5】

【0128】

駆動信号の算出

本発明の特徴である、正規化表現による正規化係数と正規化信号の2種の信号を用いた画像信号の伝送、表示出力を行うための、該正規化表現による画像信号の算出方法と手段について説明する。ここで、正規化表現による正規化係数と正規化信号の2種の信号は、表示部を構成する表示デバイスの特性に依存して作成することが基本的な方法である。したがって、まず、表示デバイスを構成する、バックライトの光量分布特性について説明し

10

20

30

40

50

て、本発明を実現するため正規化処理の内容について説明する。

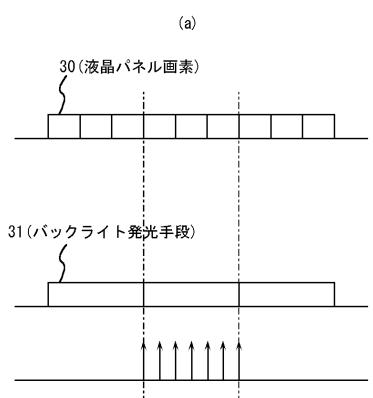

【0129】

(1) 発光分布の補正

図15は、液晶パネルの画素30とバックライトの発光手段31の配置の断面と、あわせて発光手段の発光分布を示している。図16(A)は、発光手段31の発光分布がステップ関数状である場合を示しており、該発光分布の領域内に位置する画素30の表示出力は、該発光分布の大きさ、すなわちステップ関数の高さに、各画素30の透過率を掛け合わせた結果となる。図16(B)は、発光手段31の光量分布が、中央部で大きく周辺部で低くなるような分布特性である場合を示しており、隣接する発光手段間で発光分布がリークする特徴を持つ。ある画素位置の表示出力は、該画素位置の複数の発光手段の発光分布の影響を受けることになる。

10

【0130】

本発明は、複数個の発光手段の面積方向の光量分布特性が隣接する発光手段間でリークすることを許容して、信号補正手段を備えることを特徴とする。これにより、発光手段31の発光分布の境界と、液晶パネルの画素30の境界の位置に誤差があっても、位置の誤差に伴う発光量の変化は比較的小ないことから、表示出力への影響は少なくて済む。このようにリークを許容することで、表示パネルと発光手段の組み合わせは、簡易な位置合わせで良くなることからコスト低減の効果がある。上記リーク特性は、表示パネルの透過率を制御する信号を補正することで、画質劣化を防止する。こうして、積極的に発光分布にリーク特性を持たせることで、表示パネルと発光手段の位置関係の条件緩和を実現することで、コスト低減の効果を実現することができる。

20

【0131】

説明のために、一次元に並ぶM個の画素について、画素位置 $x$ における画像信号A( $x$ )、透過率B( $x$ )、バックライト発光量C( $x$ )とする。ある画素位置 $x$ において、 $A = B \times C$ が成り立つと仮定する。この仮定は、ガンマ特性と呼ばれる非線形特性、透過率のオフセット成分、などの要因がある場合には正確ではないが、各信号の関係を簡易にモデルする目的で利用する。ここで、バックライトを構成する発光手段の発光分布は複数画素の領域に渡り、また隣接する発光手段間でリークがあるものとしたときに、画像信号Aに相当する表示出力を得るために、最小の発光量Cを設定して、該発光量Cの条件で透過率B(0 B 1)を求めるを行う。

30

【0132】

まず表示に先立つ準備段階として、バックライトを構成する複数の発光手段の発光特性を測定する。測定結果は、各発光手段の駆動信号の組み合わせと、画面内のある画素位置における各発光手段からもたらされる発光量の関係としてまとめる。これは、実際に利用するバックライトの表面を、輝度計もしくは分光放射計等を用いて測定することで求められる。ここで、ある画素位置 $x$ において、発光量Cを得るために各発光手段の駆動信号の設定は、複数の発光手段の発光分布の組み合わせとなるために、複数の駆動信号の組み合わせが存在する。本発明では、下記の手順により、上記の複数の駆動信号の組み合わせの中から、一つを選択する。

- (1) 初期設定として、各発光手段の光量分布特性の測定値を用意する。

40

- (2) 入力画像信号の大きさAと位置 $x$ の設定を変化させる繰り返しループ((2)~(9))の開始。

- (3) 各発光手段の駆動信号の組み合わせを変化させる繰り返しループ((3)~(7))の開始。

- (4) 各発光手段の駆動信号に対応する、画素位置 $x$ の発光量Cを算出する。

- (5)  $A < C$ の条件を満たす場合に、全発光手段の消費エネルギーを算出する。

- (6) 消費エネルギーの最小値更新ならば駆動信号設定値を一時保管し、それ以外は次に進む。

- (7) ループ戻る(3)(駆動信号)。

- (8) 一時保管した駆動信号設定値をテーブル蓄積。

- (9) ループ戻る(2)(大きさと位置)。

50

ここで、バックライトを構成する複数の発光手段が、それぞれ全く同じ発光特性である場合には、代表となる単一の発光手段の測定結果を、複数の発光手段の発光特性として利用することができる。この場合には、ある画素位置における発光量は、上記の代表とする発光手段の発光分布特性から、位置をずらした複数の測定結果を読み出して、該複数の発光手段の発光量の加算として算出することができる。また、あるいは、発光手段の発光分布が、何らかの関数で近似出来るならば、上記の代表とする発光手段の発光分布特性と同様に、各発光手段の発光分布特性として利用することができる。いずれの場合でも、各発光手段の全ての駆動信号の組み合わせに対応する、画素位置  $x$  における発光量  $C$  が求まることになる。

## 【0133】

10

次に、実際に入力する画像信号  $A$  を表示するために必要となる、発光手段の駆動信号の算出手順を示す。ここで、画素ごとに発光手段が用意される場合には、画素ごとに  $A = B \times C$ 、および  $0 \leq B \leq 1$  の関係から、 $A < C$  の関係を満たす発光手段の駆動信号を算出すればよいが、ここでは発光手段の発光分布が複数の画素領域に渡るとすることから、複数の画素領域において  $A < C$  の条件を満たすことが必要となる。また、一般に、画像信号は走査順序に入力することから、上記の条件を満たす発光手段の駆動信号の算出も、該画像信号の走査順序にしたがって実行できることが望ましい。本発明は、以下の手順で、画像信号を走査しながら実行する。

(1) 画素領域内の画像信号  $A$  を順次に入力する。

(2) 入力した画像信号  $A$  の位置と大きさから、最小エネルギーの条件を満たす各発光手段の駆動信号の組み合わせを、前記作成した対応表から求める。

20

(3) 該画素について新たに求めた発光手段の駆動信号が、入力済みの画素に関する設定済みの駆動信号よりも大きければ、駆動信号の値を置き換える。

(4) 次の画像信号  $A$  に移り、上記手順(1)から繰り返す。

(5) 発光手段の駆動信号を、メモリ蓄積する。

## 【0134】

こうして、画像信号  $A$  を表示出力するに必要な発光手段の駆動信号の算出を行い、その結果をメモリ蓄積することができる。次に、画像信号  $A$  を表示出力するに必要な液晶パネルの画素ごとの透過率  $B$  ( $0 \leq B \leq 1$ ) の算出を行う。このために、画像信号  $A$  を再び走査順序で入力するとともに、該入力する画像信号  $A$  の位置に対応する発光手段の発光量  $C$  を、メモリ蓄積した駆動信号から求めて用意する。画素単位の透過率  $B$  を求めるには、 $A = B \times C$  が成り立つと仮定するならば、既に  $A$  と  $C$  が求まっているので  $B = A / C$  で算出することができる。あるいは、ガンマ特性などの諸要因があり、上記関係式が成り立たない場合には  $A$  と  $B$  と  $C$  の組み合わせの関係をあらかじめ測定しておき、対応表にまとめることで、 $A$  と  $C$  から  $B$  を求めるように構成できる。また、これらの信号の組み合わせ特性が関数近似できる場合には、対応表を利用せずに、関数近似を利用する計算手順により、信号  $B$  を算出することができる。さらに、対応表の大きさを削減するための工夫を取り入れることは言うまでも無い。

30

## 【0135】

上記のように全体の手順は、

40

(1) 発光手段の駆動信号の組み合わせの算出。

(2) 画像信号を表示出力するための発光手段の駆動信号の算出。

(3) 画像信号を表示出力するため透過率の算出。

の 3 段階に整理できて、(1) は事前準備であり、実時間の信号処理が(2)と(3)であり、画面内の画像信号を(2)と(3)で 2 回スキャンすることでバックライトと液晶パネルの駆動信号の算出を実現できる。すなわち、最初のスキャンで各発光手段の駆動信号を算出して、2 回目で各画素の透過率を算出する。入力する画像信号は最初のスキャンにおいては全て保持しなければならないが、2 回目のスキャンの信号処理後において不要となる。したがって、画像信号の入出力が同じ走査順序である場合には、画像信号の 1 面のメモリを用意して、画像信号の入力段階で 1 回目のスキャン動作してからメモリ書き込みを行い、画像

50

信号の出力段階においてメモリ読出しをして2回目のスキャン動作をすることで、上記手順を実行できる。

【0136】

また、発光手段の駆動信号をメモリ蓄積を行うが、画素領域ごとに一つの駆動信号であるために、データ量は画像信号に比べて小さくて良い。

【0137】

上記手順と手段は、カラー画像の表示出力においても同様に適用できることは言うまでも無くて、発光手段の各色信号ごとに駆動信号を算出して、その結果に基づいて画素ごとの透過率を算出することができる。

【0138】

こうして本発明は、画像信号を表示するために必要な発光手段の駆動信号を、最小エネルギーと簡易高速な処理手順の観点から、算出することができる効果がある。

【0139】

(2) 駆動信号の算出

図16は、バックライトを構成する発光手段の面積方向(2次元)の分割領域と、該発光手段による発光分布を示しており、隣接する発光手段間で発光分布が重なり合う2次元のリーク特性を示している。それぞれの発光手段の分割領域は、液晶パネルの複数の画素領域に対応しており、発光手段の発光量と各画素の透過率の組み合わせで表示出力が得られる。画素の配列で作られる2次元画像は、スキャン順序にしたがった1次元の画素並びを複数組み合わせとして扱うことが出来る。バックライトを構成する発光手段の配置による分割領域の形状として(1)ストライプ(2)正方ブロック(3)ランダムブロック、などがあり、さらに2次元のリーク特性を考慮しなければならない。

【0140】

2次元特性を考慮する場合も、駆動信号の算出手順は、前記した1次元の場合と同様であり、まず準備段階として、ある画素位置 $x$ における、これらのバックライトの発光手段駆動信号の算出手順を、エネルギー最小の条件を考慮して用意する。

【0141】

次に画像信号の入力に従い、次の2パス手順を実行する。

(1)入力画像信号Aの位置と大きさに対応する複数の発光手段の駆動信号の算出手順を画面全体に渡り行うことで、画面全体として必要とする発光手段の駆動信号を算出する。

(2)入力画像信号Aの位置における発光量Cから $A = B \times C$ を満たすような画素の透過率Bを算出する手順を画面全体に渡り行う。

【0142】

上記手順を実行するには、入力する画像信号を蓄積するメモリと、手順(1)で算出する駆動信号を蓄積するメモリを用意しておく。手順(2)で算出する透過率、すなわち液晶用パネルの駆動信号は、1画面分のデータが揃うまでメモリ蓄積して待機することができるが、算出順序に従って順次に出力することもできる。

【0143】

こうして算出した発光手段の発光量および画素の透過率は、それぞれ言い換えれば正規化係数と正規化信号のことであり、両者を同時に利用するために、フレーム単位に整形して出力することで、表示部において表示出力を行うことができる。

【0144】

上記の手順は、例えばバックライトがRGB(赤青緑)で構成されている場合にも同様に適用できる。入力する画像信号がRGBの3種類に増えていたとしても、個々の色の画像信号について発光手段の駆動信号と画素の透過率を設定していくことで実現できる。さらに、バックライトがRGBWのように3色より多い色数であっても、同じ手順を利用できる。

【0145】

回路構成

図17(a)に、1画面を順次走査する入力画像信号520の画素単位に、該画素の表

10

20

30

40

50

示出力を得るために必要な各画素ブロックの発光量から、正規化係数を算出する回路構成を示す。ここで画素ブロックとは、バックライトを構成する発光手段の分割領域に対応する液晶パネルの画素の集まりであり、したがって画素ブロックは発光手段の配置と形状に依存するものであり、製品仕様作成時あるいは工場出荷時には確定する。

【0146】

また、正規化係数と正規化信号は、実際の駆動信号に換算するならば、正規化係数がバックライトを構成する発光手段の駆動信号であり、正規化信号は液晶パネルの画素の透過率とする。

【0147】

全体の動作をタイミング回路501が発生するクロックにより制御するが、図中ではアドレス発生回路502へのクロック供給を示している。 10

【0148】

アドレス発生回路502は、入力画像信号520と同期しながら、画面と画素の位置関係をアドレス信号として生成し、フレームメモリ503、画素ブロックテーブル504に供給する。入力回路510は入力画像信号520を取り込み、信号処理のため掛け算回路511、およびフレームメモリ503へ出力する。画素ブロックテーブル504は、入力画素が属する画素ブロックの識別番号と、入力画素が属する画素ブロックおよび隣接する画素ブロックの発光分布が該画素位置において寄与する比率を、あらかじめ蓄積しておく。画素ブロックテーブル504を読み出すためのアドレス信号は、上記のようにアドレス発生回路502から供給を受けるほか、該アドレスにおける入力画像信号の大きさをアドレス信号として利用することが出来る。 20

【0149】

掛け算回路511は、入力画像信号520と、画素ブロックテーブル504から読み出す該画素位置における各画素ブロックの発光分布の寄与比率とを、各画素ブロックごとに掛け合わせることで、該入力画像信号520に相当する出力を得るために必要な各ブロックの制御信号を得る。この各ブロックの制御信号は、以降の手順において入力画像信号520を正規化するために利用することから、正規化係数と呼ぶことにする。比較回路512は、前記掛け算回路511の出力である正規化係数と、正規化係数メモリ505にあらかじめ記憶されている正規化係数と比較をして、より大きな値を選択するように動作する。そして選択された正規化係数を、再び、正規化係数メモリ505に書き込む。この動作を1画面に渡り行うことで、画素ブロックごとの正規化係数が正規化係数メモリ505に用意できる。 30

【0150】

バックライトを構成する発光手段は、機種ごとに異なる発光分布を持つことが予想される。各種の機種に柔軟に対応するために、画素ブロックテーブル504に、あらかじめ測定した発光分布特性に基づいて、発光分布の寄与比率を蓄積する構成を示している。該テーブル内容が、各画素ブロックに共通であるならば、テーブル内容を共有して利用することが出来る。また、発光分布が何らかの関数近似が出来る場合には関数発生装置に置き換えることで、テーブル容量を削減する効果を実現できる。

【0151】

次に図17(b)を用いて、正規化係数メモリ505と、フレームメモリ503に蓄積した信号を用いて、各画素の正規化信号を算出する回路構成を示す。 40

【0152】

全体の動作をタイミング回路501が発生するクロックにより制御するが、図中ではアドレス発生回路502へのクロック供給を示している。

【0153】

アドレス発生回路502は、画面と画素の位置関係をアドレス信号として生成し、フレームメモリ503、画素ブロックテーブル504に供給する。入力回路510は入力画像信号520を取り込み、信号処理のため掛け算回路511、およびフレームメモリ503へ出力する。画素ブロックテーブル504は、入力画素が属する画素ブロックの識別番号 50

と、入力画素が属する画素ブロックおよび隣接する画素ブロックの発光分布が該画素位置において寄与する比率を、あらかじめ蓄積しておく。

#### 【0154】

画素ブロックテーブル504を読み出すためのアドレス信号は、上記のようにアドレス発生回路502から供給を受けるほか、該アドレスにおける入力画像信号の大きさをアドレス信号として利用することが出来る。そして、画素ブロックテーブル504から読み出す該画素位置における各画素ブロックの発光分布の寄与比率と、正規化信号メモリ505から読み出す各画素ブロックの発光量を、掛け算回路513を用いて掛け合わせ、さらに加算回路514で合計することで、該画素位置における発光量すなわち正規化係数を算出する。そして、該正規化係数を用いて、フレームメモリ503に蓄積しておいた入力画像信号を割り算することで、正規化信号を算出する。この正規化信号は、該画素位置における発光量を制御するための透過率に相当する値である。これらの信号の関係を整理するならば、入力画像信号をA、該画素位置における正規化信号をB、該画素位置における正規化係数をCとして、 $A = F(B, C)$ となる。ここでBは表示パネルの画素単位の透過率を制御する信号であり、Cは発光手段による該画素位置における発光量であり、FはBとCの組み合わせ特性であり例えば掛け算 $A = B \times C$ を表す。

#### 【0155】

さらに必要に応じてガンマ特性を設定する回路手段を組み合わせることができる。

#### 【0156】

##### (3) ノイズ除去

画像信号には、本来の目的からは外れたノイズが混入することがある。ノイズを除去するためには、隣接画素間の相関性の低い画素の除去、信号振幅の上端あるいは下端の画素の除去、発生頻度の少ない色の画素の除去、周波数成分によるフィルタリング、等の方法を利用できる。そして、僅かな頻度で発生する無意味なノイズの影響を除去して、全体としての画像表示出力における画質向上の実現を図るものである。

#### 【0157】

##### (a) 画素間の相関性

ノイズ発生が偶発的な要因であるならば、該ノイズの信号値を持つ画素は孤立して分布することになる。本来の信号が、画像のなかの構造的な特徴を示すとするならば、画素の分布において相違が見られることになる。このような場合には、隣接画素間で信号レベルが大きく変化する孤立画素を除いて、信号の最大値と最小値の測定を行い、正規化を行うことで、ノイズの影響を軽減することが出来る。ここでノイズ除去の判定条件として定数Eを利用する。

#### 【0158】

##### (b) ヒストグラム

信号値と出現頻度を関係付けるヒストグラムにおいて、信号の最大値あるいは最小値にある画素は、本来の信号とは異なる要因により信号振幅が振れている可能性がある。したがって、ヒストグラムの上端および下端近くに位置する画素を取り除き、信号の最大値と最小値の測定を行い、正規化を行うことで、ノイズの影響を軽減することが出来る。ここでノイズ除去の判定条件として定数Eを利用する。

#### 【0159】

##### (c) 色度図

色度図は、色の分布を示すための表示方法であり、色信号を組み合わせた特性を示す。さらに色度と輝度を組み合わせた色立体を示すことが出来る。色信号は、色度分布あるいは色立体の内部座標に位置する。一方、色信号が色度分布あるいは色立体の外部あるいは周辺部に位置する場合、つまり彩度が高い画素、輝度が高い画素、輝度が低い画素、などは、ノイズの影響が予想される。そこで、色度図あるいは色立体の周辺画素を除いて、信号の最大値と最小値の測定を行い、正規化を行うことで、ノイズの影響を軽減することが出来る。ここでノイズ除去の判定条件として定数Eを利用する。

#### 【0160】

10

20

30

40

50

## (d) 周波数特性

一般にノイズは、時間軸方向の信号振幅において孤立した特性を持つことから、高い周波数成分を持つ。あるいは、何らかの周波数分布を持つノイズが重畠する場合がある。ノイズが、周波数特性で特徴づけが出来る場合には、該特徴の周波数成分を除去することでノイズを削除することが出来る。例えばJ P E GあるいはM P E Gのような画像圧縮技術は、D C T（離散コサイン変換）と呼ばれる周波数成分への変換手順を利用していることから、該D C T変換結果を利用して、ノイズ除去を実行することも出来る。

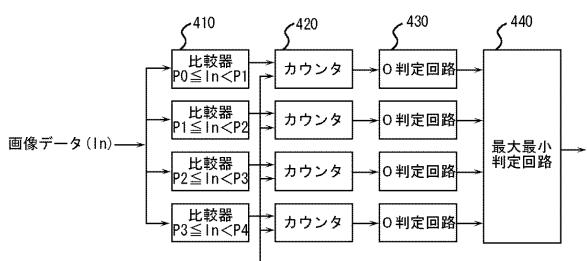

## 【0161】

例えば上記(b)のヒストグラムの利用は、画像データ全体の信号特性を表す指標として利用できることから、最大値と最小値と言うパラメータに変換することなく、そのまま画像信号の附加情報として、画像信号と一緒に伝送、蓄積することもできる。このような目的のために、ヒストグラムの測定手段の構成例を図18に示す。

10

## 【0162】

リセット信号で区切られる画像データ(I n)の系列から、最大最小値を算出する。入力画像データI nと比較判定値Pを比較判別するための比較器410と、該比較結果によりカウントアップするカウンタ420を複数セット用意して、画素の入力タイミングと同期してカウンタのカウントアップを繰り返し、画面あるいはライン等の測定の単位に同期してリセットを行うことで、測定単位ごとのヒストグラムを得ることができる。ここで、信号値ごとにカウンタを用意するのは回路規模的に複雑になる場合には、前記の比較器410の比較値Pを調整することで、例えば信号値が8ごと、あるいは16ごと、のように範囲設定を行うことで、カウンタの個数を削減できる。こうして測定されたヒストグラムは、最大最小値のような特徴量へ変換するには、カウンタ420のカウント値が0以上であるか否かを0判定回路430で判定する。上図に記載した4個のカウンタ値の該判定結果の0と1は4ビットパターンで表されて、最大最小判定回路440に予め用意した該4ビットパターン判定表を用いることで最大最小値を算出することができる。ここで0判定回路430において、0よりも大きな値を判定用に設定するならば、例えばノイズ等の要因で発生する低いカウント値を除去することができる。

20

## 【0163】

あるいは一時情報としてそのまま伝送、蓄積をして利用することができる。例えば画像データをフレームメモリ430に一時記憶しておき、測定結果として得られたヒストグラムあるいは最大最小値のような特徴量と、該測定対象とした画像データを、多重化回路440にて予め定めたデータフォーマットに変換して出力する。

30

## 【0164】

また測定手段として、アドレス線とデータ線を持つメモリを用意して、信号値をメモリアドレスとして利用することで、メモリデータを読み出し、読み出した内容に1を加算し、加算結果を同じメモリアドレスの書き戻し、画面あるいはライン等の測定の単位に同期してメモリクリアを行うことで、測定単位ごとのヒストグラムを得ることができる。ここで、メモリデータの読み出しと、修正と、書き込みの動作は、メモリのリードモディファイドライトと呼ばれる動作モードを利用することで、高速に動作させることができる。

40

## 【0165】

上記手段で測定したヒストグラムの利用方法としては、前記したように最大最小値のような特徴量へ変換するほかに、信号値と出現頻度をパターンとして見なすことができる。

## 【0166】

上記手段で測定する信号は、R G B 3色を対象にするほかに、Y U Vのような輝度と色差信号を対照にすることも出来る。色度を表すx y(スモールx y)、あるいはL a b、などに変換することで、色分布に関するヒストグラムを測定することもできる。いずれの場合も、上記の測定手段に、色信号の変換手段を付加することで実現できる。

## 【0167】

## (4) L E D バックライト

液晶ディスプレイの複数の構成要素としてバックライトと液晶素子に着目して、正規化

50

係数を用いてバックライトを制御して、正規化信号を用いて液晶素子の透過率を制御する装置構成を示す。特に、バックライトとして、RGB 3 色を独立に表示するLED（発光ダイオード）を用いる場合の構成と効果を示す。

【0168】

ここで説明する液晶ディスプレイ装置は、前記の正規化係数と正規化信号を入力する信号インターフェースを備える。物理的なインターフェース仕様は、いわゆるDVI（デジタルビデオインターフェース）と呼ばれる汎用方式を利用する。これに限定するものではないが、インターフェース手段を構成するLSI、ケーブルなどを新規に開発しないでコスト的なメリットを実現する場合の構成例としてDVIを採用する。DVIの信号伝送のタイミングは既存ディスプレイ向けに決まっており、当然ながら本発明を実現する上での正規化係数と正規化信号は定義されていない。本発明は、このような従来型のインターフェースと互換性を維持しながら、上位となる機能を実現する。なお本発明を実現するうえで、従来装置との互換性維持は必須ではなく、独自インターフェースを採用することもできる。

10

【0169】

図19に示す液晶ディスプレイ装置は、何らかの信号処理機能を備える外部装置と接続することを想定しており、液晶ディスプレイ装置の内部における信号処理は不要であるものとする。

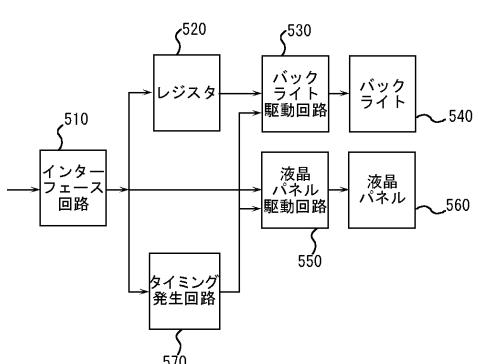

【0170】

垂直帰線期間および水平帰線期間は、本来はCRTの動作原理に基づいて定義されているタイミングであり、液晶ディスプレイには無用であるが、インターフェース仕様の互換性維持のために存在する。したがって、表示装置として本発明の液晶ディスプレイ装置に限定するならば、これらの期間を任意に利用することができる。そこで、本発明では、垂直帰線期間を利用して、画面単位の正規化係数を伝送して、垂直帰線期間に引き続く有効帰線期間において、同一画面の画素単位の正規化信号を伝送する。受信側となる液晶ディスプレイには、正規化係数、正規化信号、同期信号を抽出するインターフェース回路510を備える。そして、正規化係数を一時的に記憶するレジスタ520を用意して、該レジスタに蓄積した正規化係数は、バックライトであるRGB（赤青緑）のLED（発光ダイオード）の駆動回路530の入力信号として、バックライト540を駆動する。また引き続いだ入力する正規化信号は、液晶パネルに配置されている液晶素子の駆動回路550の入力信号として、液晶パネル560を駆動する。液晶素子は、駆動されてから実際に応答するまでの遅延特性があることから、前記LED駆動回路の駆動タイミングは、液晶素子の遅延特性を考慮しながら設定できるように構成する。DVI信号から再生した画面表示の開始と終了および画素クロック等の同期信号から、上記手段の動作手順をタイミング発生回路570にて指示する。なお、仮に液晶ディスプレイ側にフレームメモリ、表示出力のためのクロック発生回路があるならば、上記手段の動作タイミングは液晶ディスプレイの内部で任意に設定することができる。

20

【0171】

バックライトを構成するLEDは比較的に発光スペクトル分布が狭く、従来型のCRT表示と比較するならば、表示色の彩度が高くなる傾向にある。さらにLEDの種類によって発光スペクトル分布が微妙に異なる。このような発光スペクトル分布に依存する色再現の違いを信号処理で補正することが要求される場合においては、この補正処理の結果についての正規化係数と正規化信号が必要になる。ここでは、正規化係数と正規化信号を入力する装置構成を説明しているから、補正処理を外部装置で行い、その結果を入力することになる。外部装置で補正処理を行うためには、ディスプレイに依存する補正のための情報を、補正処理を行う外部装置へ伝えなくてはならない。例えば上記したLEDのスペクトル分布が補正のための情報に相当する。この補正情報は、操作者の手動により設定することもできるが、信号線を用いたネゴシエーションで実現することができる。このネゴシエーションは、機器の電源ON時、あるいは新しい機器構成が行われた時など、正規化係数と正規化信号の伝送に先立って行う。

30

【0172】

40

50

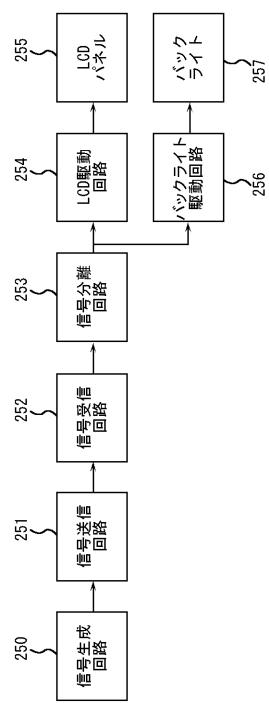

### (5) 信号処理回路の構成例

各画素ブロックの発光手段が、他の画素ブロックに影響を与えない場合には、正規化係数と正規化信号の算出は画素ブロック内の信号特性から算出することが出来る。

#### 【0173】

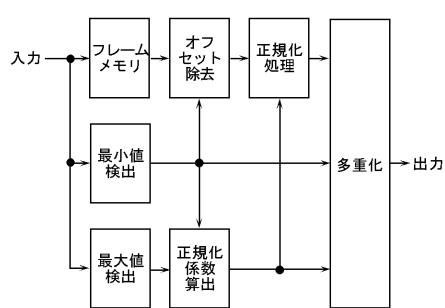

図20に、画像データを入力し、最大最小値に基づく正規化処理を行い、処理結果を多重化したビットストリームに変換して出力する装置構成を示す。

#### 【0174】

入力する画像データを、最小値検出回路330と最大値検出回路340を用いて、画素の信号値を順次に比較しながら最大値と最小値を検出する。ここで、検出回路を画面同期信号でリセットするならば画面単位の最大最小値を検出することができるほか、画面内のブロックあるいはラインごとにリセットすることで、最大最小値の単位を設定することができる。画像データはフレームメモリ320を用いて蓄積および読み出しを行うことで、メモリ容量の制約の範囲内で遅延時間を任意に設定することができる。こうして検出した最大最小値を、検出対象とした画面の画像データの信号処理に利用することができる。

10

#### 【0175】

最大値Max、最小値Minと、正規化処理の結果として得られる $A = B \times C + D$ となるB、C、Dを算出する。このため、最小値検出回路の出力MinをDとして、ゲイン算出回路350は $B = (Max - D) / 255$ 、オフセット除去回路360で $(A - D)$ を算出し、正規化処理回路370を用いて $C = (A - D) / B$ を算出する。そしてB、C、Dを、あらかじめ定めたデータフォーマットにしたがって、単一のビットストリームとして多重化することで、シリアル伝送路を用いて出力する。

20

#### 【0176】

ここで機器組込みの回路であるならば、上記の多重化回路およびシリアル伝送路を用いることなく、B、C、Dの各信号線の同期をとるためのクロックあるいは同期信号に基づいて信号線を直接利用することもできるが、複数種類の信号を高速に伝送する場合には信号間のズレが発生しやすくなる問題があり、シリアル伝送にすることで解決できるメリットがある。

#### 【0177】

画像データの信号特性の測定結果を用いた信号処理を行うためには、入力した画像信号を一時的にメモリ蓄積して、信号処理の順番に従ってメモリ読み出しを行う手順が必要である。信号特性の測定を画面単位で行う場合には、メモリ蓄積とメモリ読み出しは画面単位で動作させて、画像信号入力と信号処理結果の出力を画面単位で同期して動作することができる。入力する画像信号はライン順次であるとして、信号処理結果の正規化信号の出力もライン順次あるとするならば、該メモリの書き込みと読み出しが、1画面分の遅延を持ちながら、同じ画素の順番で動作させることができる。あるいは同じメモリアドレスを兼用することができて、例えばリード・モディファイド・ライトと呼ばれるメモリ動作を利用するならば、順番に従って発生したメモリアドレスを用いて、メモリから画素信号を読み出して正規化処理のために利用して、該メモリアドレスに新たに入力した画素信号を書き込み、これらメモリ読み出しと書き込みを同一のメモリアドレスを用いた一連の動作として完了させることができる。このようなリード・モディファイド・ライトは、メモリ読み出しとメモリ書き込みを別々の動作として実現する場合に比べて高速な動作として実現できる効果がある。

30

#### 【0178】

ここで画面を横8縦6のブロック分割数N=48とするならば、画面の縦方向6分の1を入力するごとに、横方向に並ぶ8分割のブロックの最大値が検出完了することになり、該横方向の8ブロックについては正規化処理を開始できることになる。メモリに蓄積して待機させておく画像信号は、該縦方向6分の1の容量で良いことになる。

40

#### 【0179】

横8縦6のブロック分割して測定した各ブロックの最大値を用いて、異なるブロック分割数Nに対応する測定結果に変換することができる。例えば横1縦6のブロック分割の最

50

大値測定結果に変換するには、横方向に並ぶ 8 個のブロックの最大値測定結果を用いて、再び最大値測定することで実現できる。あるいは画面全体の最大値測定結果に変換するには、横 8 縦 6 の 48 個のブロックの最大値を用いて、再び最大値測定することで、全てのブロックに共通の最大値、すなわち画面全体の最大値を測定することが出来る。

【0180】

このような性質を利用して、回路構成としては最大分割数に相当するブロックを設定して信号特性の測定を行い、実際に利用するブロック分割数  $N$  に応じて測定結果を変換することで、ブロック分割数  $N$  の設定値ごとに測定回路を用意する必要がなくなる。これを実現するには、ブロック分割数  $N$  を設定する手段を用意する。この  $N$  設定手段は、縦横の画素数、画面の分割数、あるいは予め用意したブロック形状の選択、などのブロック形状を設定するための情報として設定することができる。

10

【0181】

入力する画像信号は、上記メモリアクセスと同時に、信号特性の検出を実行することが出来る。信号処理特性としてブロックごとの最大値検出の場合には、画素の属するブロックを、前記メモリアクセス用のアドレスを用いて判定することができる。画面単位にライン順次に入力する画像信号に同期してカウンタをアップすることで、カウント値によって画素位置を特定できる。カウンタは、画面全体で一個とすることもできるが、縦横方向の位置を特定する 2 個で構成することも出来る。いずれの場合にも、入力する画素のカウント値を、ブロック分割位置に相当するカウント値と比較することで、該画素が属するブロックを特定することが出来る。該当するブロックについて最大値検出を行い、正規化係数として利用することが出来る。画素の信号が 8 ビット幅であれば、最大値は 0 から 255 までの値となる。

20

【0182】

検出したブロックごとの正規化係数に基づく正規化処理は、該当するブロック内の画素の信号を正規化係数で割り算を行うことである。ブロック内の最大値をとる画素は、正規化処理により 1.0 となり、それ以外の画素の信号は 1.0 より小さな小数となる。ここで、適宜な係数を掛けて整数の 2 値信号に変換することもでき、例えば 255 を掛けることで 8 ビット幅の 2 値信号として利用できる。

【0183】

このような正規化処理により、入力した画素の 8 ビット信号を、ブロックごとの正規化係数の 8 ビット信号と、画素ごとの正規化信号の 8 ビット信号に変換することになる。

30

【0184】

信号処理結果は、上記の各信号をパラレル出力するように回路構成を作ることも出来る。

【0185】

あるいは適宜なフォーマットに基づくシリアルのビットストリームとして出力することもできる。

【0186】

あるいはパラレルからシリアルに信号変換する回路を外部に用意して利用することも出来る。例えば、パラレルからシリアル変換回路と、LVDS として知られるシリアル伝送インターフェース回路を、両者組み合わせて利用することができる。

40

【0187】

(6) 正規化信号を用いた信号処理

平面方向、時間方向の補間処理をすることで、正規化信号の信号特性を改善することができる。

【0188】

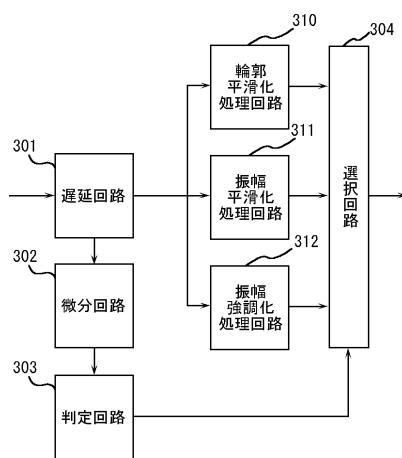

図 21 を用いて、RGB 各 8 ビットの入力信号を、画面単位の正規化係数と正規化信号に変換して、該正規化信号の階調特性を改善するための補間処理を行い、次段へ伝送する信号処理回路の構成を説明する。

【0189】

50

色信号 C ( R G B のいずれかを C とする ) を入力して遅延回路 301 に蓄積する。画面単位の信号処理を行う場合には、遅延回路 301 は少なくとも 1 面分の容量を持つ。また回路動作に余裕を持たせるために、入力信号を一時的に蓄積する複数ラインメモリを備えることができる。

【 0190 】

該入力信号と遅延回路内に蓄積済みの該当位置の信号を参照することで、時間軸方向および平面方向に隣接する複数の画素の信号を参照して、例えば微分回路 302 を用いて信号特性を抽出して、該抽出した信号特性を判定回路 303 を用いて判定して、該判定結果に基づく選択回路 304 を用いて画質向上のための信号処理を選択することができる。例えば一般に隣接する画素の信号は高い相関性を持つことが知られており、この性質を利用することで、輪郭の滑らかさを向上させる輪郭平滑化処理回路 310 , 階調数を増加するような信号補正を行う振幅平滑化回路 311 、あるいはエッジ強調に相当する振幅強調処理回路 312 を、入力信号の信号特性に応じて選択利用することができる。選択回路 304 の出力は、補正済みの正規化係数と正規化信号として出力することができる。

10

【 0191 】

階調数を増加する補正処理の方法として、注目画素および注目画素に隣接する複数画素の信号にフィッティングする関数を利用して、信号値を算出することができる。この結果、注目画素のサンプリング時に欠落した微小信号を、フィッティング関数から推定できるので、滑らかな信号変化を再生することができる。フィッティング関数として簡易なものとして、隣接画素を含む平均化あるいはローパスフィルタと呼ばれる演算を利用できる。例えば、注目画素を中心とする  $3 \times 3$  画素領域を参照して、各画素位置に対応する重み係数を掛けて加算し、画素数で割り算を行う。参照を予定する画素のなかの信号分布に基づいて、適応的に重み係数あるいはフィッティング関数を切り替えることができる。ここで参照する隣接画素は画面内のみならず時間軸方向の隣接画素であってよく、つまり平面と時間の 3 次元空間における信号再生の手法を利用することができる。

20

【 0192 】

このようにして、本発明は正規化表現した画像信号を対象にした信号処理を行うことが出来て、例えば階調数に関わる画質向上を実現することができる。表示部においては、正規化係数と正規化信号の組み合わせで表示出力を行うことから、正規化信号の階調数を増加させることは、入力した画像信号が有する階調数よりも多くの階調数を表示できる効果を実現できる。

30

【 実施例 6 】

【 0193 】

装置構成

本発明の特徴である、正規化表現による正規化係数と正規化信号の 2 種の信号を用いた画像信号の伝送、表示出力を組み込んだ装置構成は、例えばテレビジョン、パソコン、ゲーム機、コンピュータグラフィックス装置、等の製品形態に適用することができる。ここで、着目したいのは、表示出力の画質を高めるメリットと合わせて、画像信号の生成および信号処理段階における画質向上のメリットを実現できることである。例えば、画素あたりの階調数は、一般に 8 から 12 ビット程度で表現できる階調数を利用しているが、本発明によれば正規化係数と正規化信号の 2 種の信号の組み合わせで階調数を表現することと、画像信号の生成および信号処理を行うことで画質向上の効果を実現できることになる。放送においては、このような画質向上を実現するための画像信号の生成および信号処理を、放送局において実現して受像機側に伝送することで、受像機側で必要な信号処理を大幅に増加することなく、表示出力の画質を大幅に高めることができる。

40

【 0194 】

以下に具体的な装置構成における本発明の適用の効果を説明する。

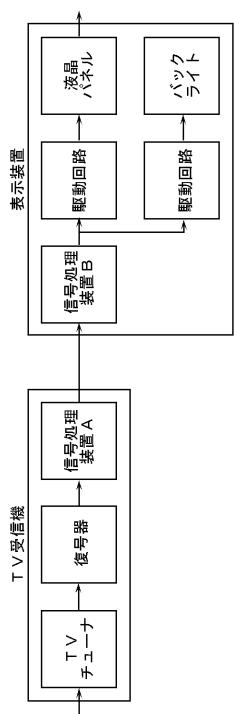

【 0195 】

( 1 ) テレビジョンへの適用

図 22 は、放送局からの放送信号として正規化係数と正規化信号の 2 種類の組み合わせ

50

を伝送する装置形態を示している。ここで、放送を、一つの送信者から不特定の受信者への1対Nデータ伝送と定義する。放送型においては、伝送路は電波、銅線、光ファイバー等を利用してシリアル伝送することが有効である。これは、遠隔地への信号伝送においては、伝送手段による遅延が発生することがあり、複数の信号線を用いるパラレル伝では信号到達のばらつき(スキー)を対策することが複雑になりやすいためである。ところで従来はCRTが唯一の表示デバイスであったことから、CRT表示を前提としてあらかじめ加工した画像データを伝送していた。しかし、様々な原理の表示デバイスが開発されてきたことから上記の前提は崩れかけている。また、受信側において画質向上をするための信号処理を行う場合がある。このように、受像機の装置構成、利用目的、等が多様化するに伴い、放送型で伝送するデータには汎用性が求められる。そこで、正規化表現する単位、すなわちバックライトを構成する発光手段による分割領域を、比較的に小面積に設定することで、受信側で正規化の単位を再構成しやすいうようにすることで、受信機側の装置構成への柔軟な対応を実現することができる。本発明は、伝送する画像信号を、正規化表現のフォーマットとして、放送あるいは通信路を経由してシリアル伝送することを特徴とする。そして、従来の1種類の信号を用いた場合に比べて、高い画質を受像機側で表示出力できるメリットを実現する。

#### 【0196】

また相互通信が可能な場合には、送信側と受信側の機器能力の交渉手順を用意することができて、交渉結果に基づいて伝送する画像信号の作成方法を設定することができる。

#### 【0197】

同図(A)は、放送局から放送信号として正規化係数と正規化信号の組み合わせで伝送して、受像機側では該2種の信号を、2種類の駆動信号に変換して本発明で述べたディスプレイを用いて表示出力を行う装置構成を示している。

#### 【0198】

同図(B)は、放送局から放送信号として正規化係数と正規化信号の組み合わせで伝送して、受像機側では該2種の信号から、従来型の1種の画像信号に変換した後に、駆動信号に変換して、従来型のディスプレイを用いて表示出力を行う装置構成を示している。本発明では、このように従来型のディスプレイで表示出力するための信号変換手段を用意することで、受像機の種類に依存することなく、画像信号を放送することができる。そして、本発明で述べた新規なディスプレイにおいては高い画質を実現して、従来型のディスプレイでは従来程度の画質を実現できる。このように、従来型ディスプレイのためには信号変換手段を用意して互換性を維持しながら、新規な放送信号への移行を容易に実現できることになる。

#### 【0199】

同図(C)は、半導体メモリ、DVD(デジタルバーサタイルディスク)、HD(ハードディスク)等の蓄積手段に、受信した画像信号をいったん録画蓄積する場合の装置構成を示している。画像信号の録画蓄積においても、利用する信号形式を正規化表現することで、画質の向上を実現できる。

#### 【0200】

##### (2) PC装置構成への適用

図23を用いて、

画像データの生成と表示を行うパソコンの装置構成において、本発明の画像データ表現の利用方法と効果について説明する。一般にパソコンと呼ぶ筐体にはCPU、メインメモリ、グラフィックスボード等が組み込まれる。グラフィックスボードには、描画処理をグラフィックスプロセッサ、グラフィックスメモリ、表示出力回路、を備える。そしてパソコン本体に備わるCPU、メインメモリと、グラフィックスボードの組み合わせによる動作を行う。この動作を規定するプログラムは、これらの信号処理装置の能力を発揮するように構成され、高速な描画を行う。グラフィックスプロセッサは、生成、あるいは外部装置から取り込んだ画像データをグラフィックスメモリに描きこみ、適切なタイミングで外部にある表示装置に対して出力を行う。ここで既存のグラフィックスプロセッサは、画像

10

20

30

40

50

データを、各色8ビットのRGB色信号として出力する。グラフィックスメモリに描かれる画面サイズは表示デバイスの表示画素数と一致するように設定される。そして、表示デバイスの動作に同期するように、RGB信号を順次に走査出力していく。

#### 【0201】

表示装置は、表示デバイスと、該表示デバイスを駆動する回路が組み込まれる。表示デバイスは、例えばRGBの3色の表示素子の組み合わせで1画素を形成し、該画素を平面方向に多数配置することで画面を形成し、該画面を時間的に繰り返し書き換えることで表示出力を行う。

#### 【0202】

本発明は、画像データAを、 $A = B \times C + D$ もしくは $A = B \times C$ の形式で生成することを特徴とする。該データ形式の生成方法は任意であるが、例えばプログラムに記述された手順に従いCPU、あるいはグラフィックスボードのグラフィックスプロセッサによる演算結果として得ることができる。 10

#### 【0203】

本発明は、画像データAを、 $A = B \times C + D$ の形式で伝送することを特徴とする。新規なデータであるCとDを伝送するために、信号線あるいはデータフォーマットあるいは伝送タイミングを用意するために、本発明は以下のいずれかの手段を利用することができる。

1) 画面内の特定画素の信号を、置き換える。

2) データフォーマット、あるいは信号線に未定義ビットがある場合には、利用する。 20

3) 伝送タイミングに無為な時間がある場合には、利用する。

装置構成として、パソコンによるテレビ受信と信号処理を行い上記のBとCのデータを出力して、表示部においてはBとCを入力してBとC駆動手段を介してBによる画素の透過率制御とCによるバックライト制御を行う。

#### 【0204】

パソコン内部の動作として、テレビ受信はテレビチューナ等の専用回路を利用して、受信後のデータは画素単位のビットマップデータとして取り扱うことで、他の画像入力あるいは生成により得られる画像信号と区別無く扱えるようになる。1画面の画像データは、画面の縦軸と横軸を座標とした画素データによる配列データとして扱う。色信号の種別はRGB, YUV等の任意として、例えばYUVであるならばYUV間でサンプリングレートを異なるように設定することも良いとする。画像データを対象にする信号測定は容易であり、例えば最大最小、平均、ヒストグラム、色度分布、などを測定結果として得ることが出来る。これにより、テレビ受信画面の各フレームについて、画像データの信号特性の測定結果を得ることが出来て、そして測定結果に基づく信号処理をプログラム制御により行い、例えば最大最小値による正規化処理の結果として正規化係数と正規化信号を算出する。測定結果のデータと測定対象とする画像データは、該プログラムからアクセスするメモリ上に配置する。このメモリは、いわゆるパソコンのメインメモリ、あるいはプロセッサLSI内部メモリ、あるいはいわゆるグラフィックスボード上のメモリであって良い。データの流れは、テレビ受信回路により受信された画像データをメモリに書き込み、プログラム制御するプロセッサによりメモリから読み取る画像データの信号測定を行い、またプログラム制御するプロセッサによりメモリから読み取る画像データの信号処理を行い、信号処理の結果を再びメモリに書き込み、そして外部出力のタイミングに基づいてメモリから画像データを読み出して出力する。 40

#### 【0205】

このように本発明は、外部出力する画像データを正規化係数と正規化信号の組み合わせとすることが特徴である。このための画像信号は、パソコン内部で生成する以外に、上記のようにTVチューナーから入力するテレビジョン信号であってよい。このために、1画面の画像信号を正規化信号と正規化係数で構成して、外部出力する。例えば、入力する画像信号をRGB各色8ビット、各画素24ビットであるならば、該画像信号のデータ構造を維持したまま、正規化信号と正規化係数で置き換えることが出来る。すなわち、従来の 50

R G B 画像信号を出力する出力手段と伝送ケーブルを利用して、新たに本発明の正規化信号と正規化係数を外部出力することができる。

【 0 2 0 6 】

こうして、いわゆるグラフィックスボードを経由して、信号インターフェースの物理的、電気的な特性は従来と同じくしながら、本発明の特徴である正規化係数と正規化信号に分離した画像データの出力を実現できる。

【 0 2 0 7 】

該画像信号を入力する表示デバイス側も同じく、信号インターフェースの物理的、電気的な特性は従来と同じくしながら、本発明の特徴である正規化係数と正規化信号を入力して、表示出力に利用することができる。

10

【 0 2 0 8 】

本発明は、画像信号の設定をネゴシエーションする手段を備えることを特徴とすることができます。ここでネゴシエーションを行う機器をパソコンと表示デバイスとする。定常の動作においては、パソコンから表示デバイスへの一方の伝送が行われる。この定常動作を開始するに先立って、伝送形式に関するネゴシエーションを行う手段を用意する。そして前記した信号 B , C , D の伝送形式を両者間で確実に設定した後にデータ伝送を行うことで、定常動作に移行することができる。ネゴシエーションを行う手段として、例えば U S B ( ユニバーサル シリアル バス ) は、機器接続用の汎用インターフェースとして知られているが、上記のパソコンと表示装置のネゴシエーションのために両者間を配線して利用することが出来る。あるいは操作者が介在して両機器の特性に基づく手動の設定を行うこともネゴシエーションの一種である。

20

【 0 2 0 9 】

( 3 ) P C ソフト構成への適用

画像データの生成と表示を行うパソコンの装置構成において、本発明の画像データ表現の利用方法と効果について説明する。パソコンで信号処理の対象とする画像信号には、外部から入力するテレビ受信画像信号と、自ら生成する画像信号がある。前者は一般的のテレビ受像器と同じ特性の画像信号である。一方後者は、ゲーム画面等のように、OpenGL , DirectX などの画像生成ソフトウェアにより生成するものである。いずれの場合も、画像信号をメモリ蓄積することができ、プログラムによる信号処理の対象とすることが出来る。

30

【 0 2 1 0 】

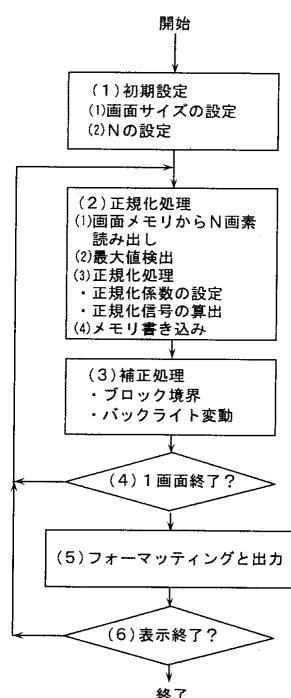

図 2 4 は、正規化処理の手順の一例である。

【 0 2 1 1 】

1 ) まず最初に信号処理のためのパラメータを初期設定する。外部から入力、および外部へ出力する画像信号の形式として、例えば画面サイズ等を設定する。また正規化処理で用いる画素ブロック形状として、例えば画素数 N を設定する。

【 0 2 1 2 】

2 ) 次に、メモリ蓄積した画像信号を対象に正規化処理を行う。具体的には、(1) 画面メモリから N 画素読み出し、(2) 最大値検出、(3) 正規化処理 ( 正規化係数の設定、正規化信号の算出 ) 、(4) メモリ書き込み、といった手順を実行する。これらの手順はプログラムで記述しておき、 C P U ( パソコンのプロセッサ ) あるいは G D P ( グラフィック・ディスプレイ・プロセッサ ) を用いて実行する。

40

【 0 2 1 3 】

3 ) 上記 2 ) で算出した正規化係数と正規化信号を対象にした補正処理を行う。補正の内容は、ブロック境界をリーグするバックライト光量、外部光源による反射光、バックライトの温度依存の輝度変動などがある。これらの変動量は、何らかのセンサで検出した値を用いて補正することが出来る。

【 0 2 1 4 】

4 ) 1 画面に含まれる画素ブロック単位の信号処理が終了したか否かを判定しながら、順次に実行を進めていく。ここでは 1 画面単位の終了判定を行っているが、あるいは 1 画

50

面より小さな画素領域、あるいは複数の画面を、終了判定に用いても良い。

【0215】

5) 正規化処理、および補正処理が完了したならば、正規化係数と正規化信号および他の付加信号を、あらかじめ定めておいたフォーマットに基づいて整形して出力を行う。例えば出力手段として、一般的なグラフィックスボードを経由する場合には、設定できるのは画面データであることから、該画面データのフォーマットを利用して、正規化係数と正規化信号および他の付加信号を書き込んで出力することができる。

【0216】

6) 手順の終了判定を行う。

【0217】

(4) 画像信号生成装置への適用(浮動小数点表現と正規化表現)

10

ここでは、今までの本発明の説明で利用してきた正規化係数と正規化信号の2種の信号を用いた正規化表現を、浮動小数点表現による画像信号で置き換えることを示して、そのメリットを述べる。一般にコンピュータグラフィックス等の技術分野において、信号生成の手順において浮動小数点表現の数値を利用することで、演算途中の有効階調数の欠落を防止する場合がある。本発明は、このように浮動小数点で表された信号を入力して表示装置を駆動することで、表示のダイナミックレンジと有効な階調数を増加することができる。

【0218】

浮動小数点の数値表現を  $A = B \times 10^C$  とするならば、ここで仮数部の  $C$  は 10 進の桁位置を表し、小数部の  $B$  は有効数字を示すが  $C$  の設定に依存して信号範囲は変化する。 $C$  の設定は、必ずしも 10 のべき乗で無くて良く任意の数値で置き換えることもできる。一方、正規化表現は、信号振幅の最大値で「 $10^C$ 」を置き換える表現方法であり、信号振幅の最大値を検出する手順が必要になるものの、有効数字  $B$  を 0 から 1 までの全ての範囲で利用できるようになる。ここで、浮動小数点表現の仮数部を、正規化表現の正規化係数と同値に設定するならば、両者の表現方法は同じになる。すなわち、画像信号の浮動小数点表現と正規化表現は、容易に相互に信号変換することができる。

20

【0219】

上記の浮動小数点表現を行う仮数部と小数部の2種類の信号と、正規化処理により得られる正規化係数と正規化信号の2種類の信号は、データ形式が類似していることから、画像信号の浮動小数点表現と正規化表現は、データ伝送、蓄積等において、同様に扱うことができる。

30

【0220】

また画像信号の浮動小数点表現と正規化表現は、表示装置の駆動においても同様に扱うことが出来る。これは、本発明の表示装置を構成するLCDパネルとバックライトの駆動信号は、正規化信号を用いてLCDパネルを駆動して、正規化係数を用いてバックライトを駆動して、両者の雲合わせとして表示出力が得られることは既に説明した通りである。同様にして、浮動小数点表現の小数部を用いてLCDパネルを駆動して、浮動小数点表現の仮数部を用いてバックライトを駆動して、両者の雲合わせとして表示出力を得ることができる。そして、固定ビット形式で画像信号を入力する場合に比べて、表示のダイナミックレンジと有効な階調数を増加することができるメリットがある。

40

【0221】

なお、画像信号の送信側において、浮動小数点表現から正規化表現の変換を行い、正規化表現の信号を伝達することができて、この場合の装置構成は既に説明した通りである。これらの信号表現形式を設定するために、送信側と受信側で交渉手順を用意することで、両者の機器能力に合わせて、高い画質の表示結果を得るように、装置構成することができる。

【0222】

伝送する画像信号に何らかのデータ圧縮の信号処理を行うことが出来ることは言うまでも無いが、本発明においては、正規化表現における正規化係数と正規化信号の2種類の信

50

号を別々に、あるいは混在させて一括に、圧縮処理を実現することができる。

【0223】

図25に、浮動小数点の数値表現形式の信号を利用する、表示装置の構成例を示す。

【0224】

信号生成回路250は、画素ごとの画像信号を浮動小数点の数値表現形式で生成する。信号送信回路251は、浮動小数点の画像信号をフレーム単位のフォーマットに整形して、出力する。信号受信回路252は浮動小数点の画像信号を受信して、信号分離回路253を用いて小数部と仮数部の2種類の信号に分離する。LCDパネル駆動回路254は、前記の小数部の信号を用いて、LCDパネル255の駆動信号を生成する。バックライト駆動回路256は、前記の仮数部の信号を用いてバックライト257の駆動信号を生成する。そして両者の駆動信号を用いてLCDパネルとバックライトを駆動することで表示出力を得る。このように本発明は、画像信号の浮動小数点の数値表現形式を利用することで、表示のダイナミックレンジと有効な階調数を増加するものである。ここで、浮動小数点の数値表現形式において、画素ごとに小数部と仮数部で構成できるのは当然であるが、あるいは、一般に画像信号は近接する画素において信号相関性が高い性質があることから複数画素について仮数部を共通に利用することができる。仮数部を共通化することで、必要なデータ量を削減できるメリットがある。ここで仮数部を共通化する複数画素の領域は任意であるが、バックライトを構成する発光手段の分割領域に基づいて設定することが出来る。

【0225】

また上記した浮動小数点の画像信号を入力して、適宜の分割領域を単位として、該領域内の信号振幅値を用いて正規化処理を行い、正規化係数と正規化信号に変換することで、LCDパネルとバックライトの駆動信号として利用することができる。ここで分割領域は、バックライトを構成する発光手段の配置構成に依存して設定することができて、バックライトが全面に渡り均一な発光分布である場合には画面を単一の領域と/orすることができ、あるいは、複数のブロックに分割することができる。分割領域を単位として、仮数部あるいは正規化係数の設定を行うことで、データ量を削減することができる。

【0226】

なお画像信号の信号処理において、画像信号に掛けられているガンマ特性を考慮することができて、例えば2画素の平均値を求める手順において、入力信号がガンマ変換されている場合には、あらかじめガンマの逆変換を行ってから平均を算出して、再度ガンマ変換を行うことで出力信号を得ることができる。

【0227】

ところで、コンピュータグラフィックスのデータ生成技術として、画像信号を浮動小数点表現する技術があり、例えばパソコンのグラフィックスボードを構成するGPU(グラフィックスプロセッsingユニット)の内部の演算処理においては画像信号を浮動小数点表現することが行われているが、既存型のディスプレイに出力するために固定ビット数表現に変換後に信号出力する。前記装置構成をパソコンに当てはめれば、パソコンのプロセッサおよびグラフィックスボードが信号生成回路250、グラフィックスボードの出力部が信号受信回路251、そして、本発明の表示装置が、信号分離回路253と、LCDパネル駆動回路254と、LCDパネル255と、バックライト駆動回路256と、バックライト257で構成することができる。ここで、パソコンのプロセッサおよびグラフィックスボードを、例えばゲーム機の信号生成回路等に置き換えることが容易であり、同じく本発明のメリットを実現することができる。

【0228】

本発明は、上記の浮動小数点表現の画像データを直接に、あるいは正規化表現に変換後に表示装置側では該信号を入力して、LCDパネルとバックライトの駆動信号に利用することができる。これにより、従来の固定ビット数表現に比べて、広いダイナミックレンジで表示を実現することができる。

【0229】

10

20

30

40

50

画像信号の出力は、前記の図2を用いて説明した信号フォーマットを利用できる。この場合には、従来型の信号伝送手段を利用して、本発明の新たな信号フォーマットの信号伝送を実現することが出来る。したがって、従来型の信号伝送方式から、本発明の信号伝送方式への移行を、互換性を維持しながら実現することが可能となる。

【0230】

また、本発明は浮動小数点表現した画像信号を対象にした信号処理により、ノイズ除去、階調変換、ガンマ変換、などの信号処理を行うことで、従来の固定ビット型の画像信号による信号処理において発生していたピット精度の課題を発生することなく、高い画質を実現することが出来る。

【図面の簡単な説明】

10

【0231】

【図1】本発明の液晶表示装置の全体図。

【図2】本発明におけるフレームの概念図。

【図3】正規化処理に関する図。

【図4】正規化の単位に関する図。

【図5】本発明の全体構成図。

【図6】発光の分布図(1)。

【図7】発光の分布図(2)。

【図8】分布特性の測定図。

【図9】発光の関数近似の概念図。

20

【図10】画像信号の構成図。

【図11】L V D S の構成図。

【図12】画素順序の構成図。

【図13】フォーマットの概念図。

【図14】タイミングの概念図。

【図15】補正処理図(1)。

【図16】補正処理図(2)。

【図17】回路図。

【図18】ノイズ除去の構成図。

【図19】L E D バックライトの構成図。

30

【図20】正規化処理回路の構成図。

【図21】階調の概念図。

【図22】放送、蓄積の構成図。

【図23】P C セットの構成図。

【図24】P C ソフトの構成図。

【図25】浮動小数の概念図。

【符号の説明】

【0232】

1 ... 制御部、2 ... 表示部、3 ... 正規化処理回路、4 ... 信号成型回路、5 ... 信号分離回路、6 ... L C D 駆動回路、7 ... L E D 駆動回路、10 ... 画像信号、11 ... 正規化信号、12 ... 正規化係数、13 ... 同期信号、14 ... 表示出力、15 ... シリアル信号、16 ... L C D 駆動信号、17 ... L E D 駆動信号、18 ... センサ信号、20 ... 液晶パネル、21 ... バックライト、30 ... 液晶パネルの画素、31 ... バックライトの発光手段、101 ... フレームメモリ、102 ... 信号測定回路、103 ... 正規化係数設定回路、104 ... ノイズ除去回路、105 ... 正規化回路、106 ... 多重化回路、107 ... 分離化回路、110 ... 表示パネル、111 ... バックライト、112 ... 縦軸ドライバ、113 ... 横軸ドライバ、114 ... バックライトドライバ、120, 121, 122 ... 信号線。

40

【図1】

【図2】

図2

(b)

【図3】

図3

(b)

【図4】

図4

(b) データ構造

| 単位                   | データ構造 (例)                                                                                                                           |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| コンテンツ、画面、ブロック、ライン、画素 | 正規化係数<br>n0, n1, n2, n3, n4, n5, n6, n7                                                                                             |

| 画素                   | 正規化信号 R<br>r0, r1, r2, r3, r4, r5, r6, r7<br>正規化信号 G<br>g0, g1, g2, g3, g4, g5, g6, g7<br>正規化信号 B<br>b0, b1, b2, b3, b4, b5, b6, b7 |

【図5】

【図6】

【図7】

【図8】

【図9】

【図 1 0】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

図 15

【図16】

図 16

【図17】

図 17

【図18】

図 18

【図19】

図 19

【図 2 0】

図 2 0

【図 2 1】

図 2 1

【図 2 3】

図 2 3

【図 2 2】

図 2 2

【図 2 4】

図 2 4

【図25】

図 25

---

フロントページの続き

(51)Int.Cl. F I

|        |      |         |

|--------|------|---------|

| G 09 G | 3/20 | 6 2 3 K |

| G 09 G | 3/20 | 6 3 1 U |

| G 09 G | 3/20 | 6 4 2 D |

| G 09 G | 3/20 | 6 4 2 E |

| G 09 G | 3/34 | J       |

(72)発明者 犬塚 達基

茨城県日立市大みか町七丁目1番1号

所内 株式会社 日立製作所 日立研究

(72)発明者 山本 恒典

茨城県日立市大みか町七丁目1番1号

所内 株式会社 日立製作所 日立研究

(72)発明者 紺野 哲豊

茨城県日立市大みか町七丁目1番1号

所内 株式会社 日立製作所 日立研究

(72)発明者 檜山 郁夫

茨城県日立市大みか町七丁目1番1号

所内 株式会社 日立製作所 日立研究

審査官 武田 悟

(56)参考文献 特開2002-99250 (JP, A)

特開2003-255915 (JP, A)

特開2002-366080 (JP, A)

特開2002-258814 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 00 - 3 / 38

G 02 F 1 / 133

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 图像信号显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP5116208B2</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 公开(公告)日 | 2013-01-09 |

| 申请号            | JP2004335269                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 申请日     | 2004-11-19 |

| [标]申请(专利权)人(译) | 株式会社日立制作所                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 日立显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 有限公司日本东显示器<br>松下液晶显示器有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 犬塚達基<br>山本恒典<br>紺野哲豊<br>檜山郁夫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 犬塚 達基<br>山本 恒典<br>紺野 哲豊<br>檜山 郁夫                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20 G09G3/34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| CPC分类号         | G09G3/342 G09G3/2096 G09G3/3426 G09G2320/0261 G09G2320/0646 G09G2360/16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/36 G02F1/133.505 G02F1/133.535 G09G3/20.611.A G09G3/20.612.U G09G3/20.623.K G09G3 /20.631.U G09G3/20.642.D G09G3/20.642.E G09G3/34.J G09G3/20.612.T                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

| F-TERM分类号      | 2H093/NC27 2H093/NC28 2H093/NC29 2H093/NC42 2H093/NC44 2H093/NC50 2H093/NC56 2H093 /NC62 2H093/NC68 2H093/ND03 2H093/ND04 2H093/ND05 2H093/ND06 2H093/ND07 2H093/ND39 2H193/ZD34 2H193/ZG03 2H193/ZG43 2H193/ZH08 2H193/ZH40 2H193/ZH42 5C006/AA11 5C006 /AF13 5C006/AF25 5C006/AF44 5C006/AF45 5C006/AF46 5C006/AF51 5C006/AF52 5C006/AF53 5C006/AF54 5C006/AF61 5C006/AF69 5C006/AF71 5C006/BB29 5C006/BC03 5C006/BC11 5C006 /BF08 5C006/BF14 5C006/BF24 5C006/EA01 5C006/FA01 5C006/FA47 5C006/FA54 5C080/AA10 5C080/BB05 5C080/DD04 5C080/DD26 5C080/DD28 5C080/EE29 5C080/GG12 5C080/JJ02 5C080 /JJ04 5C080/JJ05 5C080/JJ07 |         |            |

| 代理人(译)         | 井上 学                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 审查员(译)         | 武田 悟                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 其他公开文献         | JP2006145798A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |            |

**摘要(译)**

亲切代码：提供一种用于传输信息的装置，该信息用于使液晶面板和背光源对每帧同步地执行显示操作。— 在具有液晶显示面板的液晶显示装置中，所述液晶显示面板具有夹在一对基板和能够控制亮度的光源之间的液晶层，用于控制液晶层的信号设置在具有框架单元的像素结构的显示区域中以及用于在帧基础上设置用于控制像素配置的回扫区域中的光源的信号以生成图像信号的装置。点域1