### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2009-58874 (P2009-58874A)

(43) 公開日 平成21年3月19日(2009.3.19)

| (51) Int.Cl. |        |           | F 1  |        |     | テーマコード (参考) |

|--------------|--------|-----------|------|--------|-----|-------------|

| G02F         | 1/1343 | (2006.01) | GO2F | 1/1343 |     | 2HO91       |

| GO2F         | 1/1335 | (2006.01) | GO2F | 1/1335 | 520 | 2HO92       |

| G09F         | 9/30   | (2006.01) | GO9F | 9/30   | 338 | 5CO94       |

|                       |                                                      | 審査請求     | 未請求 請求項の数 2 OL (全 14 頁)             |  |  |  |  |

|-----------------------|------------------------------------------------------|----------|-------------------------------------|--|--|--|--|

| (21) 出願番号<br>(22) 出願日 | 特願2007-227592 (P2007-227592)<br>平成19年9月3日 (2007.9.3) | (71) 出願人 | 日本ビクター株式会社                          |  |  |  |  |

|                       |                                                      |          | 神奈川県横浜市神奈川区守屋町3丁目12<br>番地           |  |  |  |  |

|                       |                                                      | (74) 代理人 | 100092808                           |  |  |  |  |

|                       |                                                      | (74) 代理人 | 弁理士 羽鳥 亘<br>100140981               |  |  |  |  |

|                       |                                                      | (72) 発明者 | 弁理士 中村 希望<br>川中 博之                  |  |  |  |  |

|                       |                                                      | (12) 光明省 | 神奈川県横浜市神奈川区守屋町3丁目12                 |  |  |  |  |

|                       |                                                      |          | 番地 日本ビクター株式会社内                      |  |  |  |  |

|                       |                                                      | Fターム (参  | 考) 2H091 FA14Y FA34Y FB08 FC02 FC10 |  |  |  |  |

|                       |                                                      |          | FC23 FC26 FD03 FD23 GA02            |  |  |  |  |

|                       |                                                      |          | GA13 LA03                           |  |  |  |  |

|                       |                                                      |          | 最終頁に続く                              |  |  |  |  |

# (54) 【発明の名称】液晶表示素子及び液晶表示素子の製造方法

# (57)【要約】

【課題】画素電極分割部からの光リークを抑制するとと もに開口率の大きい液晶表示素子及び液晶表示素子の製 造方法を提供することを目的とする。

【解決手段】本発明に係る液晶表示素子の製造方法によ れば、画素電極分割部207の幅を絶縁層106cの底 面側から上面側に向かって徐々に狭めることが可能なた め、表示領域に対する画素電極分割部207の占める割 合を減少させ、開口率の大きい高輝度な液晶表示素子6 00を作製することができる。また、液晶表示素子60 0は画素電極分割部207の上面の幅が細いため、画素 電極分割部207からの光リークを大幅に低減すること が可能となり、光リークに起因する悪影響をより抑制す ることができる。

【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

駆動回路部と光反射性を有する画素電極とが一面側に順次設けられた駆動基板と、

前記画素電極と所定の間隙を有して対向配置された光透過性電極を有する光透過性基板と

前記所定の間隙に封入され、前記駆動回路部により前記画素電極毎に駆動される液晶と、 を備え、

前記画素電極は、前記一面に直交する方向に所定の厚さを有すると共に、前記一面に沿って互いに他の間隙を有してマトリクス状に配置され、

前記他の間隙は、前記画素電極の厚さ方向に沿って、前記駆動回路部側から前記液晶側に向かって徐々に狭くなるように構成されてなることを特徴とする液晶表示素子。

#### 【請求項2】

液晶表示素子の製造方法において、

液晶を駆動させる駆動回路部が一面側に形成された基板における前記駆動回路部上に、絶縁層を形成する絶縁層形成工程と、

前記絶縁層形成工程後に、前記絶縁層上に所定形状のレジストパターンを形成して、前記 絶縁層に、前記レジストパターンで覆われた被覆領域と、前記絶縁層が露出した露出領域 とを形成するレジストパターン形成工程と、

前記レジストパターン形成工程後に、前記露出領域の前記絶縁層を、前記被覆領域における前記レジストパターンの外周及びその近傍の領域の前記絶縁層を含んで、所定の深さまでエッチングすることにより、前記被覆領域に、エッチングされた後の前記露出領域における前記絶縁層の表面を底面とし、該底面に沿う方向の幅が前記底面から前記レジストパターンに向かって徐々に小さくなる凸状部を形成する凸状部形成工程と、

前記凸状部形成工程後に、前記レジストパターンを除去するレジストパターン除去工程と

前記レジストパターン除去工程後に、前記凸状部の表面及びその近傍をエッチングして、 前記凸状部の前記幅を小さくするエッチング工程と、

前記エッチング工程後に、前記凸状部及び前記絶縁層の各表面に導電層を形成する導電層 形成工程と、

前記導電層形成工程後に、前記導電層上に、前記凸状部の段差を埋める反射金属層を形成する反射金属層形成工程と、

前記反射金属層形成工程後に、前記凸状部上の前記導電層を除去して、前記凸状部を露出させる凸状部露出工程と、

を有する液晶表示素子の製造方法。

# 【発明の詳細な説明】

# 【技術分野】

#### [00001]

本発明は、液晶表示装置を構成する液晶表示素子及び液晶表示素子の製造方法に関し、特に表示領域に対する画素電極分割部の占める割合が低く開口率が大きい液晶表示素子及び液晶表示素子の製造方法に関するものである。

#### 【背景技術】

# [0002]

従来より、分子配列が一定の秩序を保ちながらその一方で流動性を有し、さらに電界の印加によってその配向が変化する液晶は、表示装置用の材料として各分野の電気電子機器に広く利用されている。

#### [0003]

近年、これら液晶表示装置に関する技術の進歩によって、応答速度等の表示性能の向上、高解像度化、及び大型化が達成され、携帯電話、ノート型パソコン、携帯型オーディオプレーヤ、PDA、デジタルビデオカメラ、デジタルカメラ等の携帯型電気電子機器はもとより、カーステレオ、カーナビゲーションシステム、車載型のテレビモニタ等の車載型

10

20

30

40

電気電子機器、更には、テレビモニタ、パーソナルコンピュータのディスプレイ等の比較的大型な表示装置としても液晶表示装置が利用可能となった。特にテレビモニタの分野に関しては、高画質な映像表示に対応した高解像度、大画面の液晶表示装置が多く商品化されている。また、投射プロジェクタ等のように映像を外部スクリーンなどに表示するための投射型表示装置に関してもこの液晶表示装置を利用したものが商品化されている。

# [0004]

これら液晶表示装置には液晶表示素子を構成する画素の制御方式として、アクティブマトリクス方式とパッシブマトリクス方式とに大別される。アクティブマトリクス方式は画素毎にスイッチング素子を有しており複雑な駆動回路の形成が必要となるが、パッシブマトリクス方式に比べ応答時間が短く、また、画素毎に表示、非表示を高精度に制御可能なため、走査線数の多い高解像度のテレビモニタ等に適している。

[0005]

また、液晶表示装置は、画面表示に必要な光の供給方法から透過型の液晶表示装置と反射型の液晶表示装置とに大別することができる。透過型の液晶表示装置はその裏面側もしくは側面側に設置されたバックライトからの光を透過させて画面表示を行うため、駆動回路等によって遮られる部分の光を画面表示に用いることができず開口率(表示領域全面に対する画素領域の占める割合)が小さいという問題点を有している。

[0006]

これに対して、反射型の液晶表示装置は表示面方向からの光を画素電極により反射して 画面表示を行うため、駆動回路等が光を遮ることがなく、開口率を大きくとることができ る。よって、反射型の液晶表示装置は、より高輝度な画面表示を行うことができる。

[ 0 0 0 7 ]

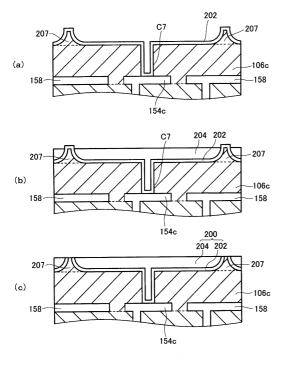

ここで、図6に一般的なアクティブマトリクス方式の反射型液晶表示素子における一つの画素(画素部)の模式的断面図を示す。反射型の液晶表示素子を構成する一つの画素としての画素部400は、液晶表示素子の裏面側に位置する第1の基板としての回路基板部Aと、液晶表示素子の表示側に位置する全ての画素部400に共通の第2の基板としての光透過性基板部Bと、回路基板部Aと光透過性基板部Bとの間隙に封入された液晶層306とを有している。

[0008]

また、回路基板部 A はスイッチング素子部 T r 及び保持容量部 C 等の回路素子が形成された回路素子部 A 1 と、導電層 2 0 2 と反射金属層 2 0 4 とが画素電極分割部 2 0 6 で区切られた画素電極 2 0 0 を有する画素電極部 A 3 と、回路素子部 A 1 と画素電極部 A 3 とを接続するとともに所定の信号等を回路基板部 A に供給する所定の配線電極等を備えた回路配線部 A 2 と、を有している。

[0009]

また、光透過性基板部 B は、全ての画素部 4 0 0 に共通の光透過性電極 3 0 2 と、光透過性電極 3 0 2 を支持する光透過性基板 3 0 0 と、を有している。

[0010]

そして、上記の画素部400が半導体基板100上にマトリクス状に形成されるとともに、個々の画素部400に信号等を供給する信号ラインが形成されることで液晶表示素子が構成される。

[0011]

上記のような液晶表示素子は、前述のように光透過性基板部Bの側から入射した光を画素電極200で反射して画面表示を行うため、駆動回路を構成する回路素子部A1と回路配線部A2が光を遮ることがなく、開口率を大きくとることができる。しかしながら、反射型の液晶表示素子においても、その表示領域には隣接する画素電極200同士を絶縁するための画素電極分割部206が存在しているため、開口率は100%とはならない。例えば、実際の液晶表示素子における画素電極分割部206の幅は0.5μm~1μmあり、仮に画素電極200のピッチを10μmとすると、単純に計算しただけでも開口率は約81%~90%程度となる。そして、高解像度化のために画素電極200のピッチを更に

10

20

30

40

小さくすれば、それだけ表示領域に対して画素電極分割部 2 0 6 の占める割合が増加して 開口率は更に減少する。

# [0012]

表示領域に対する画素電極分割部 2 0 6 の占める割合を低減し、開口率の向上を図るためには画素電極分割部 2 0 6 の幅を狭めることが効果的である。しかしながら、従来のフォトリソグラフィ法とエッチング処理とによる形成手法では、形成される画素電極分割部 2 0 6 の最小幅は 0 . 2 μ m が限界であり、これ以上のファインライン化は技術面及びコストの面から難く、更なる改善が望まれる。

### [0013]

また、この画素電極分割部206では、光源からの光が画素電極分割部206を通して回路基板部A側に侵入する光リークが生じる。この回路基板部A側に侵入した光がスイッチング素子部Trに到達すると光電変換されて光キャリアを生じさせ、スイッチング素子部Trと接続している保持容量部C及び画素電極200へ印加している電圧を低下させる場合がある。一般的な液晶表示素子では液晶層306の劣化を防止するために、液晶層306に対し対称の電圧が印加されるようバイアス電圧をかけて駆動しているが、光キャリアが生じて保持容量部C等の電圧が低下すると、バイアス電圧のバランスが崩れて液晶層306に対して非対称な電圧がかかり、表示画面上におけるフリッカの増大や、焼き付きの発生、更には直流ダメージによる信頼性の低下を引き起こす要因となり好ましいものではない。

# [0014]

このため、通常、回路配線部A2にはリークした光がスイッチング素子部Trに到達することを防止するための遮光電極158が設けられる。しかしながら、リークした一部の光は、図6中の破線矢印で示すように、遮光電極158及びその他の配線電極(図6中では主に中継電極154b、154c)等を繰り返し反射しながら回路配線部A2の絶縁層106a、106b、106cを進行してスイッチング素子部Trに到達する場合があり、この場合でも上記のような悪影響が生じることとなる。そして、このような光リークによる悪影響は液晶表示装置に入射する光量(光密度)にほぼ比例し、特に高輝度の投射型表示装置等では大きな問題となる。

# [0015]

この問題に対して、下記[特許文献1]に開示された液晶表示装置及びその製造方法に関する発明では、画素電極分割部206の底面に反射膜を形成して、画素電極分割部206からの光リークを防止するとともに、画素電極分割部206に照射される光も画面表示に利用可能としている。

# [0016]

【特許文献1】特開2004-326051号公報

# 【発明の開示】

【発明が解決しようとする課題】

### [0017]

しかしながら、[特許文献 1]に開示された発明では、画素電極分割部 2 0 6 からの光リークを防止することは可能であるが、表示領域に対する画素電極分割部 2 0 6 の占める割合は変化せず、開口率が小さいといった問題を解決するものではない。

### [0018]

本発明は、上記事情に鑑みてなされたものであり、画素電極分割部からの光リークを抑制するとともに開口率の大きい液晶表示素子及び液晶表示素子の製造方法を提供することを目的とする。

# 【課題を解決するための手段】

# [0019]

本発明は、

(1)駆動回路部と光反射性を有する画素電極200とが一面側に順次設けられた駆動基板と、

10

20

30

- -

前記画素電極200と所定の間隙を有して対向配置された光透過性電極302を有する光 透過性基板(光透過性基板部B)と、

前記所定の間隙に封入され、前記駆動回路部により前記画素電極200毎に駆動される液 晶(液晶層306)と、

を備え、

前記画素電極200は、前記一面に直交する方向に所定の厚さを有すると共に、前記一面 に沿って互いに他の間隙(画素電極分割部207)を有してマトリクス状に配置され、

前記他の間隙は、前記画素電極200の厚さ方向に沿って、前記駆動回路部側から前記液 晶側に向かって徐々に狭くなるように構成されてなることを特徴とする液晶表示素子60 0を提供することにより、上記課題を解決する。

(2)液晶表示素子の製造方法において、

液晶を駆動させる駆動回路部が一面側に形成された基板における前記駆動回路部上に、絶 縁層106cを形成する絶縁層形成工程と、

前記絶縁層形成工程後に、前記絶縁層106c上に所定形状のレジストパターン(レジス ト層10)を形成して、前記絶縁層106cに、前記レジストパターンで覆われた被覆領 域 と 、 前 記 絶 縁 層 1 0 6 c が 露 出 し た 露 出 領 域 と を 形 成 す る レ ジ ス ト パ タ ー ン 形 成 工 程 と

前記レジストパターン形成工程後に、前記露出領域の前記絶縁層106cを、前記被覆領 域における前記レジストパターンの外周及びその近傍の領域の前記絶縁層106cを含ん で、所定の深さまでエッチングすることにより、前記被覆領域に、エッチングされた後の 前記露出領域における前記絶縁層106cの表面を底面とし、該底面に沿う方向の幅が前 記底面から前記レジストパターンに向かって徐々に小さくなる凸状部207aを形成する 凸状部形成工程と、

前 記 凸 状 部 形 成 工 程 後 に 、 前 記 レ ジ ス ト パ タ ー ン を 除 去 す る レ ジ ス ト パ タ ー ン 除 去 工 程 と

前 記 レ ジ ス ト パ タ ー ン 除 去 工 程 後 に 、 前 記 凸 状 部 2 0 7 a の 表 面 及 び そ の 近 傍 を エ ッ チ ン グして、前記凸状部207aの前記幅を小さくするエッチング工程と、

前記エッチング工程後に、前記凸状部(画素電極分割部207)及び前記絶縁層106c の各表面に導電層202を形成する導電層形成工程と、

前記導電層形成工程後に、前記導電層202上に、前記凸状部の段差を埋める反射金属層 204を形成する反射金属層形成工程と、

前記反射金属層形成工程後に、前記凸状部上の前記導電層202を除去して、前記凸状部 を露出させる凸状部露出工程と、

を有する液晶表示素子の製造方法を提供することにより、上記課題を解決する。

### 【発明の効果】

# [0020]

本発明に係る液晶表示素子及び液晶表示素子の製造方法によれば、

画素電極分割部のファインライン化が可能となり、画素電極分割部からの光リークを抑制 するとともに開口率の大きい液晶表示素子を得ることができる。

【発明を実施するための最良の形態】

# [0021]

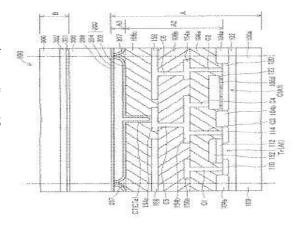

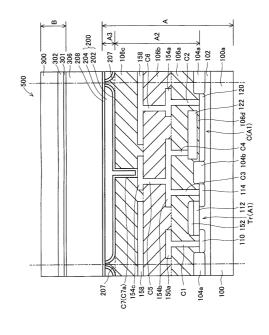

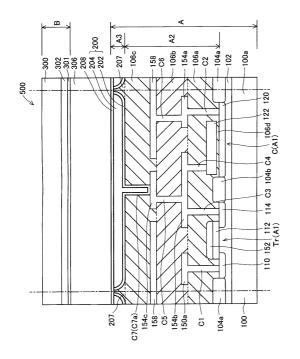

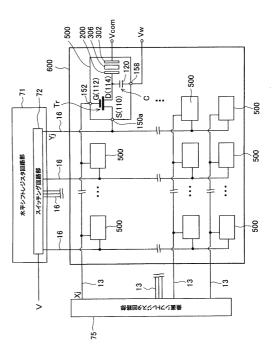

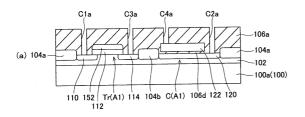

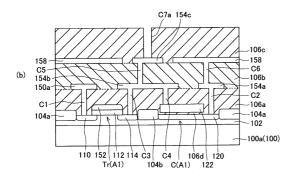

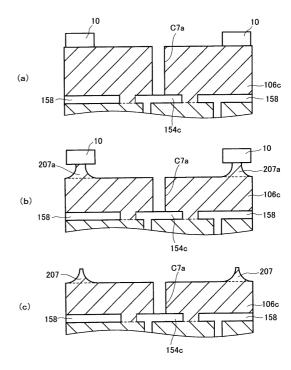

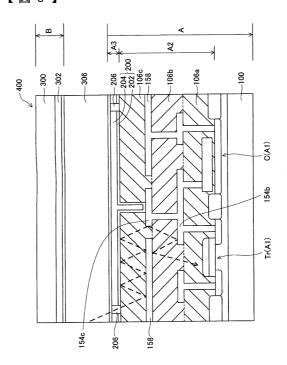

以下、本発明に係る液晶表示素子及び液晶表示素子の製造方法の実施の形態について図 面に基づいて説明する。図1は本発明に係る液晶表示素子を構成する画素部の実施の一形 態 を 説 明 す る た め の 模 式 的 断 面 図 で あ る 。 図 2 は 本 発 明 に 係 る 液 晶 表 示 素 子 の 動 作 の 実 施 例 を 説 明 す る た め の 図 で あ る 。 図 3 は 本 発 明 に 係 る 液 晶 表 示 素 子 の 製 造 方 法 に お い て 、 特 に そ の 回 路 素 子 部 及 び 回 路 配 線 部 の 製 造 方 法 の 実 施 の 一 形 態 を 説 明 す る た め の 模 式 的 断 面 図である。図4、図5は本発明に係る液晶表示素子の製造方法において、特にその画素電 極及び画素電極分割部の製造方法の実施の一形態を説明するための模式的断面図である。 尚、従来技術と同様の部材及び部位に関しては同符号にて示す。

# [0022]

10

20

30

図1に示す画素部500は、後述する反射型の液晶表示素子6000にマトリクス状に配置された複数の画素部500のうちの一つを拡大したものである。尚、本実施の形態で示す画素部500は、特に画素電極200及び画素電極分割部207の形状及びその形成方法に特徴を有するものであり、それ以外の後述するスイッチング素子部Tr、保持容量部Cなどの回路素子部A1の構成、各配線電極、コンタクトホール等の回路配線部A2の構成、及び光透過性基板部B等の構成に関しては、前述した図6に示す従来の反射型液晶表示素子と同じである。また、これら各構成部については、特に図1に限定されるものではない。

# [0023]

図1に示す画素部500は図6と同様に、主として、液晶表示素子600の裏面側(光が入射する側とは反対側)に位置する駆動基板を構成する回路基板部Aと、液晶表示素子600の表示側に位置するとともに全ての画素部500に共通の光透過性基板部Bと、回路基板部Aと光透過性基板部Bとの間隙に封入された液晶層306とで構成される。

# [0024]

画素部500の回路基板部Aは、主として、半導体基板部100aと、半導体基板部100a上の回路素子領域に形成された回路素子としてのスイッチング素子部Tr及び保持容量部Cを有する回路素子部A1と、導電層202と反射金属層204とが画素電極分割部207で区切られた画素電極200を有する画素電極部A3と、回路素子部A1に対し所定の信号及び電力等を供給するとともに回路素子部A1からの出力を画素電極部A3側に伝達する配線電極等を備えた回路配線部A2と、を有している。そして、回路配線部A2により所定の配線がなされた回路素子部A1が画素部500の駆動回路部を構成する。

#### [0025]

回路基板部Aの半導体基板部100aは、ウェル102が回路素子部A1側に形成された全ての画素部500に共通の半導体基板100が、絶縁性を有するフィールド酸化膜104aにより電気的に分離されることで形成される。尚、半導体基板100としてはSi(シリコン)基板が好適である。

### [0026]

回路素子部A1のスイッチング素子部Trは、例えばp型のMOSFET等のスイッチングトランジスタであり、半導体基板部100a上にフィールド酸化膜104bによって保持容量部Cと電気的に絶縁された状態で設けられる。また、スイッチング素子部Trはソース部110、ゲート絶縁膜112、ドレイン部114を有しており、ソース部110は回路配線部A2を構成する絶縁層106aに設けられたコンタクトホールC1を介して絶縁層106a上の配線電極の一つであるソース電極150aに接続される。また、スイッチング素子部Trのゲート絶縁膜112には、後述する走査信号Xjをゲート絶縁膜112に対して出力する配線電極の一つであるゲート電極152が接続される。尚、コンタクトホールC1及び後述するコンタクトホールC2~C6は、その内部にA1(アルミニウム)等の導電性を有する金属が成膜、充填されており、コンタクトホールC1~C6を介して上下配線電極等の電気的接続が可能となる。

# [0027]

保持容量部 C は、ウェル 1 0 2 上に例えばイオン注入によって形成された拡散容量電極 1 2 0 と 拡散容量電極 1 2 0 と対向するように設けられた容量電極 1 2 2 と、これら拡散容量電極 1 2 0 と容量電極 1 2 2 との間に介在する絶縁膜 1 0 6 d と、を有している。そして、保持容量部 C の拡散容量電極 1 2 0 は絶縁層 1 0 6 a に設けられたコンタクトホール C 2 を介して絶縁層 1 0 6 a 上の配線電極の一つである中継電極 1 5 4 a に接続される。さらに、中継電極 1 5 4 a は絶縁層 1 0 6 b に設けられたコンタクトホール C 6 を介して絶縁層 1 0 6 b 上に設けられた遮光電極 1 5 8 に接続される。そして、拡散容量電極 1 2 0 には遮光電極 1 5 8 から、後述するウェル基準電圧 V w が供給される。尚、拡散容量電極 1 2 0 に対してウェル基準電圧 V w 等を印加するための配線電極を、遮光電極 1 5 8 とは別に設けても良い。

# [0028]

10

20

30

また、スイッチング素子部Trのドレイン部114は、絶縁層106aに設けられたコンタクトホールC3を介して絶縁層106a上の配線電極の一つである中継電極154bに接続される。また、保持容量部Cの容量電極122はコンタクトホールC4を介して同じく中継電極154bに接続される。これにより、スイッチング素子部Trのドレイン部114と保持容量部Cの容量電極122とが中継電極154bを介して電気的に接続される。更に、中継電極154bは絶縁層106bに設けられたコンタクトホールC5を介して絶縁層106b上の配線電極の一つである中継電極154cに接続される。そして、中継電極154cは絶縁層106cに設けられたコンタクトホールC7を介して絶縁層106c上の画素電極200に電気的に接続される。これにより、画素電極200は中継電極154c等を介して回路素子部A1を構成するスイッチング素子部Trのドレイン部114及び保持容量部Cの容量電極122とに電気的に接続される。

[0029]

また、絶縁層106b上の絶縁層106cは、隣接する画素電極200同士を電気的に 絶縁するための凸状の画素電極分割部207を有している。画素電極分割部207は、画 素電極200を区切るように絶縁層106cの表面に略格子状に形成され、その幅は画素 電極分割部207によって囲まれた絶縁層106cの表面(底面)側から画素電極分割部 207の液晶層306側の面である上面に向かって徐々に狭くなっている。また、画素電 極分割部207の側面は絶縁層106cの表面と連続した曲面をなしており、よって、画 素電極分割部207の断面形状は、画素電極分割部207の上面と絶縁層106cの表面 とを結ぶ側面が画素電極分割部207の内側に向かって略扇状に湾曲した略台形形状を呈 している。

[0030]

画素電極200は、絶縁層106cの表面、コンタクトホールC7となる後述するスルーホールC7aの内面、及び画素電極分割部207の側面に成膜された導電層202と、導電層202の表面に画素電極分割部207の上面と略同等な位置まで形成された反射金属層204とで主に構成される。そして、導電層202により導電性を付与されたスルーホールC7aはコンタクトホールC7となり、画素電極200と中継電極154cとを電気的に接続する。尚、コンタクトホールC7による導電性を維持しながら、コンタクトホールC7の内面等にタングステンや絶縁部材などを充填して画素電極200の表面を平滑化し、画素部500の反射率の向上を図るようにしても良い。

[0031]

更に、画素電極 2 0 0 の反射面 (表面)には下部配向膜 2 0 8 が成膜され、これらが回路基板部 A の画素電極部 A 3 となる。

[0032]

尚、回路配線部A2の構成には、必要に応じて第2の遮光電極や光吸収層などを適宜設けても良い。また、画素電極分割部207の上面の幅が十分に細く、光リークを問題無いレベルにまで減少させることが可能であれば、遮光電極158は設けずとも良い。

[0033]

上記の回路基板部Aの画素電極 2 0 0 側には、図示しないスペーサが配置され、このスペーサによって画素電極 2 0 0 から所定の間隔を隔てて光透過性基板部Bが配置される。光透過性基板部Bは、主として全ての画素部 5 0 0 に共通の光透過性電極 3 0 2 と、光透過性電極 3 0 2 を支持する例えば透明なガラス板からなる光透過性基板 3 0 0 と、光透過性電極 3 0 2 の画素電極 2 0 0 側の面に形成され回路基板部Aの下部配向膜 2 0 8 と 9 0。異なった配向方向を有する上部配向膜 3 0 1 と、を備えている。

[0034]

更に、光透過性基板部 B の上部配向膜 3 0 1 と回路基板部 A の下部配向膜 2 0 8 との間には液晶層 3 0 6 が封入される。そして、画素電極分割部 2 0 7 及びフィールド酸化膜 1 0 4 a によって区切られた部位が、液晶表示素子 6 0 0 の 1 画素として機能する画素部 5 0 0 となる。

[0035]

10

20

30

次に、液晶表示素子600の動作を図2を用いて簡単に説明する。図2に示す液晶表示素子600は、主として複数の画素部500がマトリクス状に配置されて構成される。尚、図2中において、画素部500は主要部分の等価回路図として示す。画素部500のスイッチング素子部Trのソース部110は、ソース電極150aを介して各列毎に共通の映像信号用配線16に接続される。また、それぞれの映像信号用配線16は水平シフトレジスタ回路部71によってスイッチング制御されるスイッチング回路部72に接続される

# [0036]

スイッチング素子部Trのゲート絶縁膜112は、ゲート電極152を介して各行毎に共通の走査信号用配線13に接続され、それぞれの走査信号用配線13は垂直シフトレジスタ回路部75に接続される。また、画素部500の保持容量部Cを構成する拡散容量電極120には、遮光電極158を介してウェル基準電圧Vwが供給される。また、図示しないが、スイッチング素子部Trには画素電極200に所定の電位を供給するための固定電位が印加されている。尚、スイッチング素子部Trに印加する固定電位は、ウェル基準電圧Vwとしても良いし、別配線によってウェル基準電圧Vwとは異なったものとしても良い。

### [0037]

垂直シフトレジスタ回路部75は映像信号に含まれる水平同期信号に同期して、所定の走査信号 X j を各行の走査信号用配線13に対して順次走査するように繰り返し出力する。また、水平シフトレジスタ回路部71には映像信号ラインVから映像信号が供給され、この映像信号に含まれる画素信号 Y j は、スイッチング回路部72のスイッチングによって映像信号の時系列的な出力タイミングに同期するように、所定の映像信号用配線16に出力される。そして、垂直シフトレジスタ回路部75からの走査信号 X j と水平シフトレジスタ回路部71からの画素信号 Y j とが同時に供給される画素部500では、スイッチング素子部TrがON動作しドレイン部114から画素信号 Y j に応じた電圧が画素電極200に対して印加される。

# [ 0 0 3 8 ]

ここで、画素部 5 0 0 のスイッチング素子部TrがOFFの状態では、液晶層 3 0 6 の液晶分子は上部配向膜 3 0 1 と下部配向膜 2 0 8 とにより、 9 0 ° ねじれた状態に配向している。このような状態では、光透過性基板部 B を透過した外光及び画素電極 2 0 0 からの反射光は液晶層 3 0 6 を透過することが可能で、その結果画素部 5 0 0 は表示状態となる。

#### [0039]

また、画素部500のスイッチング素子部TrがON動作すると、画素電極200にはドレイン部114を介して水平シフトレジスタ回路部71から供給される画素信号Yjに応じた電位が生じる。これにより、画素電極200の電位と光透過性電極302に印加されている電位Vcomと間に電位差が発生し、その電位差に応じて液晶層306の配向状態が変化する。この配向状態の変化によってその領域の光が変調され、画素部500は画素信号Yjに応じた半表示状態もしくは非表示状態となる。そして、これらの動作を画素部500毎に行うことで、液晶表示素子600全体として所定の画像を表示する。

# [0040]

尚、画素電極 2 0 0 に生じた電位は保持容量部 C に電荷のかたちで記憶され、スイッチング素子部 T r が O F F 状態となっても、次の画素信号 Y j が入力するまで画素部 5 0 0 の表示状態は維持される。

#### [0041]

次に、画素部500の製造方法を説明する。初めに、図3を用いて画素部500の回路素子部A1及び回路配線部A2の形成方法を簡単に説明する。

#### [0042]

先ず、図3(a)に示すように、半導体基板100上に回路素子部A1等を形成する。 これらの部位の形成手順としては、先ず、ウェル102が形成された半導体基板100の 10

20

30

40

所定の位置にフィールド酸化膜104a、104bを形成し、これにより画素部500の半導体基板部100aを形成する。次に、半導体基板部100a上の所定の位置に、回路素子としてのソース部110、ゲート絶縁膜112、ドレイン部114を有するスイッチング素子部Trと、保持容量部Cの拡散容量電極120とを、フィールド酸化膜104a、104bによって電気的に絶縁した状態で形成する。その後、スイッチング素子部Trのゲート絶縁膜112にゲート電極152と、拡散容量電極120と対向する位置に絶縁膜106dを介して保持容量部Cの容量電極122とを形成する。これにより、半導体基板部100a上にスイッチング素子部Trと保持容量部Cとを有する回路素子部A1が形成される。尚、回路素子部A1の形成は、CVD(Chemical Vapor Deposition法)法、スパッタリング法、フォトリソグラフィ法、及びエッチング処理などの周知の半導体プロセス技術を用いて順次行う。以上が、回路素子領域形成工程に相当する。

[0043]

次に、これら回路素子部 A 1 上に、回路配線部 A 2 を構成する S i O  $_2$  (二酸化珪素)等の絶縁層 1 0 6 a を C V D 法等により成膜する。次に、絶縁層 1 0 6 a にコンタクトホール C 1 ~ C 4 となるスルーホール C 1 a ~ C 4 a を形成する。スルーホール C 1 a ~ C 4 a の形成は、先ず、絶縁層 1 0 6 a 表面にフォトリソグラフィ法等を用いてスルーホール C 1 a ~ C 4 a に相当する部位に開口部を有するレジスト膜を形成する。次に、エッチングによって開口部から露出した領域の絶縁層 1 0 6 a を除去し、次に絶縁層 1 0 6 a 表面のレジスト膜を除去する。これにより、絶縁層 1 0 6 a にスルーホール C 1 a ~ C 4 a が形成される。

[0044]

次に、図3(b)に示すように、絶縁層106a上に絶縁層106b、106c及び名配線電極等を形成する。これらの形成手順としては、先ず、絶縁層106aの表面及びスルーホールC1a~C4aに、スパッタリング法などを用いてA1などの導電性を有する金属層を形成する。これにより、スルーホールC1a~C4aは金属層で充填され、導生とが多った。次に、フォトリソグラフィ法及びエッケ処理等を用いて金属層の所定の部位を除去し、絶縁層106a上に配線電極として、ソース電極150a、中継電極154a、154bを形成する。次に、絶縁層106a上にSiO2等からなる絶縁層106bをCVD法等により成膜した後、上記の方法と同様にして、コンタクトホールC5、C6、中継電極154c、遮光電極158を順次形成する。以上が、回路配線部形成工程に相当する。次に、絶縁層形成工程として、中継電極154c等が形成された絶縁層106b上に、SiO2等からなる絶縁層106cをCVD法等により成膜する。

[0045]

次に、絶縁層106c上の所定の位置に開口部を有するレジスト膜をフォトリソグラフィ法等を用いて形成する。次に、エッチング処理によって開口部から露出した部分の絶縁層106cを除去し、最後にレジスト膜を除去することにより絶縁層106cにスルーホールC7aを形成する。これにより、回路素子部A1上に回路配線部A2の主要部分が形成される。

[0046]

次に、画素部 5 0 0 の画素電極 2 0 0 及び画素電極分割部 2 0 7 の形成方法を図 4 、図 5 を用いて説明する。尚、図 4 、図 5 においては、画素部 5 0 0 の画素電極 2 0 0 及び画素電極分割部 2 0 7 の形成部及びその周辺のみを拡大して示す。

[0047]

先ず、図4(a)に示すように、絶縁層106cの表面の所定の位置に所定寸法の略格子状のレジスト層10をフォトリソグラフィ法を用いて形成する。尚、レジスト層10の幅は最終的に形成する画素電極分割部207の上面の幅よりも十分に広くて良い。仮に、画素電極分割部207の最終的な上面の幅を0.1 $\mu$ m以下としたい場合でも、レジスト層10の幅は0.4 $\mu$ m~0.6 $\mu$ m程度で構わない。以上が、レジストパターン形成工

10

20

30

40

10

20

30

40

50

程に相当する。

#### [0048]

次に、図4(b)に示すように、反応性イオンエッチングなどの等方性のドライエッチング処理により絶縁層106cの所定の部位を除去する。これにより、レジスト層10から露出した領域の絶縁層106cはレジスト層10の形成面から所定の厚みだけ除去されて凹状となるとともに、レジスト層10に覆われた領域の絶縁層106cは残留して凸状部207aを形成する。このとき、レジスト層10に覆われた領域の絶縁層106cもレジスト層10の辺縁部から除去されるため、凸状部207aの幅は絶縁層106cの凹部底面側からレジスト層10の形成面側に向かって徐々に狭まるとともに、凸状部207aの側面(除去面)は絶縁層106cの表面と連続した曲面となる。即ち、凸状部207aの断面形状はその両側がレジスト層10の辺縁部から略扇形に除去された、略台形形状を呈する。尚、凸状部207aの上面の幅は、レジスト層10が剥離しない0.1μm~0.2μmの範囲とすることが好ましい。以上が凸状部形成工程に相当する。

[0049]

次に、レジストパターン除去工程として、レジスト層10をアッシングなどにより除去する。

### [0050]

次に、図4(c)に示すように、凸状部207aを含む絶縁層106cの表面に対して、垂直方向にアスペクト比の大きな異方性ドライエッチング処理を施す。これにより、凸状部207aは絶縁層106cの底面とともに更に除去されてその上面の幅が更に狭まり、目的とする上面の幅を有する画素電極分割部207となる。以上が、エッチング工程に相当する。この手法によれば、上面の幅が従来手法で形成可能な下限の約0.2μmよりも細い、0.1μm以下の画素電極分割部207を形成することができる。尚、画素電極分割部207の上面の幅は細いほうが液晶表示素子600の開口率を大きくすることができるが、隣接する画素電極200同士の絶縁性の観点から、0.03μm以上が好ましく、特に0.05μm前後が好ましい。

[0051]

次に、図5(a)に示すように、画素電極分割部207を含む絶縁層106cの表面に、TiN(窒化チタン)層、もしくはTi層、あるいはこれらの層を順次積層した層を、導電層202としてスパッタリング法や蒸着法などの周知の成膜手法を用いて形成する。尚、導電層202は中継電極154cと後述する反射金属層204とを電気的に接続するとともに、中継電極154cと反射金属層204との間のマイグレーションを防止するためのものであり、この機能を有する材料であれば特に上記の材料に限定する必要はない。また、絶縁層106cに形成されたスルーホールC7aは、その内面に導電層202が成膜されることで導電性を有するコンタクトホールC7となる。以上が、導電層形成工程に相当する。

[0052]

次に、図5(b)に示すように、導電層202上に反射金属層204を成膜する。このときの反射金属層204の成膜手法としては、半導体基板100の少なくとも絶縁層106c及び導電層202を所定の温度に加熱しながらスパッタリングを行う高温スパッタリング法を用いる。この成膜手法によれば、スパッタリングにより生じた金属粒子は、導電層202表面に到達した際に加熱され、その運動エネルギーが増大することにより流動性が向上する。その結果、金属粒子は画素電極分割部207の突端である上面を避けるようにして、導電層202の形成された絶縁層106cの凹部に、自己整合的かつ選択的に堆積する。即ち、反射金属層204は、画素電極分割部207によって囲まれた絶縁層106cの凹部を充填するように、絶縁層106cの表面から画素電極分割部207の側面に沿って、画素電極分割部207の上面と略同等な位置まで形成される。このとき、導電層202は金属粒子の流動性を更に向上させる効果を有する。

[ 0 0 5 3 ]

反射金属層204の材料としてはA1もしくはA1を主成分とした合金が好ましく、こ

の場合には、スパッタリング時の加熱温度は350~460 とすることが好ましい。 尚、加熱温度がこの範囲よりも低いとA1等の金属粒子の流動性が十分でなく画素電極分 割部207の上面にも反射金属層204が成膜される可能性があり、また加熱温度がこの 範囲よりも高いと回路配線部A2内のA1製の配線電極等が軟化する可能性がある。また 、反射金属層204の材料をA1以外とする場合には、加熱によって回路基板部Aの他の 構成、特に回路配線部A2の各配線電極に軟化などの悪影響が生じないように加熱温度の 設定及び材料の選択を行う必要がある。以上が、反射金属層形成工程に相当する。

### [0054]

次に、図5(c)に示すように、導電層202の材料に対して選択比が高くなるような条件でドライエッチング処理を施し、反射金属層204から露出した導電層202、即ち画素電極分割部207の上面に位置する導電層202を除去する。以上が、凸状部露出工程に相当する。これにより、反射金属層204及び導電層202は画素電極分割部207によって電気的に分割され、この画素電極分割部207によって分割された反射金属層204と導電層202とが、画素部500の画素電極200となる。

### [0055]

上記の画素電極 2 0 0 上には、下部配向膜 2 0 8 が蒸着法等により成膜される。これにより画素電極部 A 3 が形成され、画素部 5 0 0 の回路基板部 A が形成される。

#### [0056]

また、回路基板部Aには、これとは別に作製された全素子共通の光透過性基板部Bが、回路基板部Aの画素電極200と光透過性基板部Bの光透過性電極302とが対向しかつ所定の間隔を取るように配置される。そして、回路基板部A側の下部配向膜208と光透過性基板部B側の上部配向膜301との間隙に液晶層306が封入されることで、液晶表示素子600を構成する1つの画素部500が作製される。

#### [0057]

上記の液晶表示素子の製造方法によれば、画素部500の画素電極分割部207の表示面側に位置する上面の幅を極めて細く形成することができるため、表示領域に対する画素電極分割部207の占める割合を減少させ、開口率の大きい高輝度な液晶表示素子600 を作製することができる。

# [0058]

また、液晶表示素子600は高輝度な画面表示を行うことができることに加え、画素ピッチの微細化に際しても開口率が従来のものに比べさほど低下しないため、高解像度でかつ高輝度な画面表示を行うことができる。

#### [0059]

更に、液晶表示素子600は画素電極分割部207の上面の幅が細いため、画素電極分割部207からの光リークを大幅に低減することが可能となり、表示画面上におけるフリッカの増大や、焼き付きの発生、更には直流ダメージによる信頼性の低下などの悪影響をより抑制することができる。

【図面の簡単な説明】

# [0060]

【図1】本発明に係る液晶表示素子を構成する画素部の実施の一形態を説明するための模式的断面図である。

【 図 2 】 本 発 明 に 係 る 液 晶 表 示 素 子 の 動 作 の 実 施 例 を 説 明 す る た め の 図 で あ る 。

【図3】本発明に係る液晶表示素子の製造方法において、特にその回路素子部及び回路配線部の製造方法の実施の一形態を説明するための模式的断面図である。

【図4】本発明に係る液晶表示素子の製造方法において、特にその画素電極及び画素電極分割部の製造方法の実施の一形態を説明するための模式的断面図である。

【図5】本発明に係る液晶表示素子の製造方法において、特にその画素電極及び画素電極分割部の製造方法の実施の一形態を説明するための模式的断面図である。

【 図 6 】 従 来 の 液 晶 表 示 素 子 を 構 成 す る 画 素 部 を 説 明 す る た め の 模 式 的 断 面 図 で あ る 。

# 【符号の説明】

50

10

20

30

# [0061]

# 【図1】

# 【図2】

【図3】

【図4】

【図5】

【図6】

# フロントページの続き

F ターム(参考) 2H092 GA17 HA05 JA24 JB07 JB54 MA05 MA15 MA18 NA07 NA22 5C094 AA10 AA16 BA03 BA43 CA19 DA13 EA06 EB02 FA10 GB10 HA10

| 专利名称(译)        | 液晶显示装置和液晶显示装置的制造方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|

| 公开(公告)号        | <u>JP2009058874A</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 公开(公告)日 | 2009-03-19 |  |  |  |

| 申请号            | JP2007227592                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 申请日     | 2007-09-03 |  |  |  |

| [标]申请(专利权)人(译) | 日本胜利株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |  |  |  |

| 申请(专利权)人(译)    | 日本有限公司Victor公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |

| [标]发明人         | 川中博之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |  |  |  |

| 发明人            | 川中 博之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |  |  |  |

| IPC分类号         | G02F1/1343 G02F1/1335 G09F9/30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |

| FI分类号          | G02F1/1343 G02F1/1335.520 G09F9/30.338                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |  |  |  |

| F-TERM分类号      | 2H091/FA14Y 2H091/FA34Y 2H091/FB08 2H091/FC02 2H091/FC10 2H091/FC23 2H091/FC26 2H091 /FD03 2H091/FD23 2H091/GA02 2H091/GA13 2H091/LA03 2H092/GA17 2H092/HA05 2H092/JA24 2H092/JB07 2H092/JB54 2H092/MA05 2H092/MA15 2H092/MA18 2H092/NA07 2H092/NA22 5C094 /AA10 5C094/AA16 5C094/BA03 5C094/BA43 5C094/CA19 5C094/DA13 5C094/EA06 5C094/EB02 5C094/FA10 5C094/GB10 5C094/HA10 2H191/FA13Y 2H191/FA31Y 2H191/FB14 2H191/FC02 2H191 /FC10 2H191/GA04 2H191/GA10 2H191/GA19 2H191/LA03 2H191/LA21 2H191/NA43 2H291/FA13Y 2H291/FA31Y 2H291/FB14 2H291/FC02 2H291/FC10 2H291/GA04 2H291/GA10 2H291/GA19 2H291 /LA03 2H291/LA21 2H291/NA43 |         |            |  |  |  |

| 外部链接           | <u>Espacenet</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |  |  |  |

# 摘要(译)

要解决的问题:提供一种抑制从像素电极分割部分漏光并具有高孔径比的液晶显示元件,并提供一种制造液晶显示元件的方法。

ŽSOLUTION:根据本发明的液晶显示元件的制造方法,由于像素电极分割部207的宽度可以从绝缘层106c的下侧到上面侧逐渐变窄,因此占用可以减小像素电极分割部分207相对于显示区域的比例,并且可以制造具有高孔径比和高亮度的液晶显示元件600。由于液晶显示元件600的像素电极分割部分207的上表面较窄,因此可以显着减少来自像素电极分割部分207的光泄漏,并且可以进一步抑制由漏光引起的不利影响。 Ž