## (19) **日本国特許庁(JP)**

# (12) 公開特許公報(A)

(11)特許出願公開番号

特開2008-233703 (P2008-233703A)

(43) 公開日 平成20年10月2日(2008.10.2)

| (51) Int.Cl. |       |                     | F I         |          |          |          | テー    | 73-1 | ・(参え | 琴)   |

|--------------|-------|---------------------|-------------|----------|----------|----------|-------|------|------|------|

| G09G         | 3/36  | (2006.01)           | G09G        | 3/36     |          |          | 2 H ( | 93   |      |      |

| G02F         | 1/133 | (2006.01)           | GO2F        | 1/133    | 550      |          | 5 C C | 006  |      |      |

| G09G         | 3/20  | ( <b>2006</b> . 01) | G09G        | 3/20     | 611A     | 1        | 5 C ( | 080  |      |      |

|              |       |                     | G09G        | 3/20     | 624I     | )        |       |      |      |      |

|              |       |                     | G09G        | 3/20     | 623A     | 1        |       |      |      |      |

|              |       |                     | 審査請求 未      | 請求 請求    | ド項の数<br> | 9 OL     | (全 12 | 2 頁) | 最終真  | 頁に続く |

| (21) 出願番号    |       | 特願2007-75777 (P2    | 007-75777)  | (71) 出願。 | ሊ 30405  | 3854     |       |      |      |      |

| (22) 出願日     |       | 平成19年3月23日(2        | 007. 3. 23) |          | エプ)      | ノンイメー    | -ジング  | デバイ  | ス株式  | 会社   |

|              |       |                     |             |          | 長野り      | 長安曇野市    | 豊科田   | 沢69  | 25   |      |

|              |       |                     |             | (74)代理。  | 人 10010  | 4433     |       |      |      |      |

|              |       |                     |             |          | 弁理:      | t 宮園     | 博一    |      |      |      |

|              |       |                     |             | (72) 発明す | 皆 吉田     | 一輝       |       |      |      |      |

|              |       |                     |             |          | 長野り      | 表安曇野市    | 豊科田   | 沢69  | 25   | エプソ  |

|              |       |                     |             |          |          | メージンク    |       | ス株式  | 会社内  |      |

|              |       |                     |             | F ターム    | (参考) 2F  |          |       | NC03 | NC11 | NC18 |

|              |       |                     |             |          |          | NC24     | NC28  | NC34 | NC35 | NC49 |

|              |       |                     |             |          |          | ND39     |       |      |      |      |

|              |       |                     |             |          | 50       | 006 AC21 | AF42  | AF44 | AF51 | AF53 |

|              |       |                     |             |          |          | AF69     | BC03  | BC16 | BF42 | FA01 |

|              |       |                     |             |          |          | FA47     |       |      |      |      |

|              |       |                     |             |          | 50       | 080 AA10 | BB05  | DD26 | FF11 | JJ02 |

|              |       |                     |             |          |          | JJ04     | JJ05  |      |      |      |

## (54) 【発明の名称】液晶表示装置

## (57)【要約】

【課題】表示部を低消費電力駆動するときの消費電力の 低減をより十分に図ることが可能な液晶表示装置を提供 することである。

【解決手段】この液晶表示装置100は、信号線14および走査線15と、信号線14および走査線15の交差する位置に配置され、画素電極22および画素電極22に対向する共通電極23を含む画素20とを備え、共通電極23は、通常駆動時には交流的に電圧が印加され、低消費電力駆動時には一定電圧(直流的な電圧)が印加される。

【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

信号線および走査線と、

前記信号線および前記走査線の交差する位置に配置され、画素電極および前記画素電極に対向する共通電極を含む画素とを備え、

前記共通電極は、通常駆動時には交流的に電圧が印加され、低消費電力駆動時には一定電圧が印加される、液晶表示装置。

### 【請求項2】

前記通常駆動時に前記共通電極に交流的に電圧を印加するための第1電源部をさらに備え、

10

前記低消費電力駆動時に、前記第1電源部を用いて信号電圧が前記画素電極に印加される、請求項1に記載の液晶表示装置。

### 【請求項3】

前記低消費電力駆動時の前記画素がオン状態のときに前記第1電源部を用いて前記画素電極に印加される信号電圧の絶対値は、前記通常駆動時に前記共通電極に交流的に印加される電圧の絶対値よりも大きくなるように制御されている、請求項2に記載の液晶表示装置。

#### 【請求項4】

信号線および走査線と、

前記信号線および前記走査線の交差する位置に配置され、画素電極および前記画素電極に対向する共通電極を含む画素と、

20

前記通常駆動時に前記共通電極に交流的に電圧を印加するための第1電源部とを備え、前記画素電極は、低消費電力駆動時に、前記第1電源部を用いて信号電圧が印加される、液晶表示装置。

### 【請求項5】

前記低消費電力駆動時に前記画素電極に印加される電圧は、前記画素が水平方向に走査される期間、または、前記画素が1画面分走査される期間ごとに高電圧と低電圧とに切り替えられる、請求項2~5のいずれか1項に記載の液晶表示装置。

### 【請求項6】

前記低消費電力駆動時に前記共通電極に一定電圧を印加するための第2電源部をさらに備え、

30

前記第2電源部の電圧は、前記通常駆動時に用いられる前記第1電源部の前記高電圧と前記低電圧との実質的に中間の電圧になるように設定されている、請求項5に記載の液晶表示装置。

### 【請求項7】

前記低消費電力駆動時に前記共通電極に一定電圧を印加するための第2電源部をさらに備え、

前記低消費電力駆動時の前記画素がオフ状態のときには、前記第2電源部の電圧が、前記画素電極と前記共通電極との両方に印加されるように構成されている、請求項2~6のいずれか1項に記載の液晶表示装置。

40

## 【請求項8】

前記通常駆動時および前記低消費電力駆動時に前記共通電極にそれぞれ印加される前記交流的な電圧および前記一定電圧を切り替えるための共通電極切替回路をさらに備える、請求項1~7のいずれか1項に記載の液晶表示装置。

#### 【請求項9】

前記通常駆動時に前記共通電極に印加される前記交流的な電圧を、前記低消費電力駆動時に前記画素電極に信号電圧として印加するための信号電圧切替回路をさらに備える、請求項2~8のいずれか1項に記載の液晶表示装置。

## 【発明の詳細な説明】

#### 【技術分野】

#### [00001]

本発明は、液晶表示装置に関し、特に、通常駆動および低消費電力駆動を行う液晶表示装置に関する。

## 【背景技術】

### [0002]

従来、液晶表示装置において、消費電力の低減を図るため、表示部の一部分だけを駆動するパーシャル駆動や白および黒のみの色を表示する 2 値表示などの低消費電力駆動を行うことが知られている(たとえば、特許文献 1 参照)。

### [0003]

上記特許文献1に記載の低消費電力駆動を行う液晶表示装置では、表示データに応じた階調数の階調電圧を生成する階調電圧生成回路を有し、その階調電圧生成回路には、階調数と等しい数の階調アンプが含まれている。この液晶表示装置では、低消費電力駆動時において、表示部の表示が変化しない非表示領域の画素が走査される期間には、最高階調電圧を生成する階調アンプまたは最低階調電圧を生成する階調アンプを交互に動作させて画素の共通電極に交流的な電圧を印加するとともに、他の階調電圧を生成する階調アンプは全てオフ状態となる。これにより、非表示領域の画素が走査される期間に動作している階調アンプは1つだけになるので、消費電力の低減を図ることが可能となる。

#### [0004]

【特許文献1】特開2007-17597号公報

### 【発明の開示】

【発明が解決しようとする課題】

#### [0005]

しかしながら、上記特許文献 1 に記載の液晶表示装置では、低消費電力駆動時には、交流的な電圧が共通電極に印加されるため、共通電極に印加される電圧が変化したときには、画素に含まれる補助容量に蓄積された電荷が電流として流れ出してしまうという不都合がある。その結果、再び補助容量に電荷を蓄積する必要があるので、消費電力の低減をより十分に図るのが困難であるという問題点がある。

#### [0006]

この発明は、上記のような課題を解決するためになされたものであり、この発明の1つの目的は、表示部を低消費電力駆動するときの消費電力の低減をより十分に図ることが可能な液晶表示装置を提供することである。

【課題を解決するための手段および発明の効果】

#### [0007]

この発明の第1の局面による液晶表示装置は、信号線および走査線と、信号線および走査線の交差する位置に配置され、画素電極および画素電極に対向する共通電極を含む画素とを備え、共通電極は、通常駆動時には交流的に電圧が印加され、低消費電力駆動時には一定電圧が印加される。

### [0008]

この第1の局面による液晶表示装置では、上記のように、共通電極の電位は、低消費電力駆動時には一定電圧によって駆動されることにより、交流的な電圧によって共通電極が駆動される場合と異なり、画素に含まれる補助容量に蓄積された電荷が電流として流れ出してしまうという不都合が発生するのを抑制することができるので、再び補助容量に電荷を蓄積する必要がない。その結果、消費電力をより十分に低減することができる。

## [0009]

上記第1の局面による液晶表示装置において、好ましくは、通常駆動時に共通電極に交流的に電圧を印加するための第1電源部をさらに備え、低消費電力駆動時に、第1電源部を用いて信号電圧が画素電極に印加される。このように構成すれば、低消費電力駆動時に画素電極に信号電圧を印加するための電源部を別途設ける必要がないので、液晶表示装置の構成を簡略化することができる。

## [0010]

10

20

30

40

この場合、好ましくは、低消費電力駆動時の画素がオン状態のときに第1電源部を用いて画素電極に印加される信号電圧の絶対値は、通常駆動時に共通電極に交流的に印加される電圧の絶対値よりも大きくなるように制御されている。このように構成すれば、低消費電力駆動時において、共通電極に印加される一定電圧と画素電極に印加される電圧との電位差を大きくすることができるので、液晶を完全にオン状態にすることができる。

#### [0011]

この発明の第2の局面による液晶表示装置は、信号線および走査線と、信号線および走査線の交差する位置に配置され、画素電極および画素電極に対向する共通電極を含む画素と、通常駆動時に共通電極に交流的に電圧を印加するための第1電源部とを備え、画素電極は、低消費電力駆動時に、第1電源部を用いて信号電圧が印加される。

[0012]

この第2の局面による液晶表示装置では、上記のように、低消費電力駆動時に、第1電源部を用いて信号電圧が画素電極に印加されることによって、低消費電力駆動時に画素電極に信号電圧を印加するための電源部を別途設ける必要がないので、液晶表示装置の構成を簡略化することができる。

#### [0013]

上記通常駆動時に共通電極に交流的に電圧を印加するための第1電源部を備える液晶表示装置において、好ましくは、低消費電力駆動時に画素電極に印加される電圧は、画素が水平方向に走査される期間、または、画素が1画面分走査される期間ごとに高電圧と低電圧とに切り替えられる。このように構成すれば、低消費電力駆動時に、液晶表示装置に長時間にわたり一定の電圧が印加されることが抑制されるので、残像現象を引き起こす焼き付きを抑えることができる。

[0014]

この場合、好ましくは、低消費電力駆動時に共通電極に一定電圧を印加するための第2電源部をさらに備え、第2電源部の電圧は、通常駆動時に用いられる第1電源部の高電圧と低電圧との実質的に中間の電圧になるように設定されている。このように構成すれば、交流的な電圧が反転しても、一定電圧と交流的な電圧との電位差が同じになるので、一定電圧の電圧を調整しなくても交流的な電圧が反転する前後の画素のオン状態またはオフ状態を維持することができる。

[0015]

上記通常駆動時に共通電極に交流的に電圧を印加するための第1電源部を備える液晶表示装置において、好ましくは、低消費電力駆動時に共通電極に一定電圧を印加するための第2電源部をさらに備え、低消費電力駆動時の画素がオフ状態のときには、第2電源部の電圧が、画素電極と共通電極との両方に印加されるように構成されている。このように構成すれば、容易に、画素電極に印加される電圧と、共通電極に印加される電圧とを、実質的に等しくなるようにすることができる。

[0016]

上記第1の局面および第2の局面による液晶表示装置において、好ましくは、通常駆動時および低消費電力駆動時に共通電極にそれぞれ印加される交流的な電圧および一定電圧を切り替えるための共通電極切替回路をさらに備える。このように構成すれば、容易に、共通電極に印加される電圧を交流的な電圧と一定電圧とに切り替えることができる。

[0017]

上記通常駆動時に共通電極に交流的に電圧を印加するための第1電源部を備える液晶表示装置において、通常駆動時に共通電極に印加される交流的な電圧を、低消費電力駆動時に画素電極に信号電圧として印加するための信号電圧切替回路をさらに備える。このように構成すれば、容易に、通常駆動時に共通電極に印加される交流的な電圧を、低消費電力駆動時に画素電極に信号電圧として印加することができる。

【発明を実施するための最良の形態】

[0018]

以下、本発明の実施形態を図面に基づいて説明する。

10

20

30

50

10

20

30

40

50

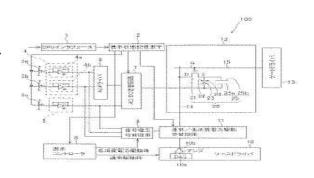

#### [0019]

図1は、本発明の一実施形態による液晶表示装置の全体構成を示したブロック図である。図1を参照して、本発明の一実施形態による液晶表示装置100の構造について説明する。

## [0020]

本実施形態による液晶表示装置100では、図1に示すように、CPUインターフェース1と、表示状態記憶素子2と、可変抵抗3a、3bおよび3cと、AC電源部4と、DC電源部5と、ACドライバ6と、AC/DC切替回路7と、表示コントローラ8と、信号電圧切替回路9と、ソースドライバ10と、通常/低消費電力駆動切替回路11と、表示部12と、ゲートドライバ13とを備えている。なお、AC電源部4は、本発明の「第1電源部」の一例である。また、AC/DC切替回路7は、本発明の「共通電極切替回路」の一例である。また、信号電圧切替回路9は、本発明の「信号電圧切替回路」の一例である。

## [0021]

表示部12に表示される状態は、CPUインターフェース1を介して表示状態記憶素子2に記憶されるように構成されている。また、表示状態記憶素子2は、可変抵抗3a、3bおよび3cと、表示コントローラ8と、AC/DC切替回路7と、通常/低消費電力駆動切替回路11とに接続されている。

#### [0022]

ここで、第1実施形態では、AC電源部4は、オペアンプからなる高電圧電源4aと低電圧電源4bとを有しており、高電圧電源4aと低電圧電源4bとは、それぞれ、可変抵抗3aと可変抵抗3bとに接続されている。これにより、高電圧電源4aと低電圧電源4bとから印加される電圧は、可変抵抗3aおよび3bにより電圧値が変更可能なように構成されている。また、AC電源部4の高電圧電源4aと低電圧電源4bとはACドライバ6に接続されている。このACドライバ6は、AC電源部4の高電圧電源4aと低電圧電源4aと低電圧電源4bとから出力される電圧を選択的に切り替える機能を有する。

#### [ 0 0 2 3 ]

また、第1実施形態では、可変抵抗3cは、DC電源部5に接続されている。これにより、DC電源部5から印加される電圧は、可変抵抗3cにより電圧値が変更可能なように構成されている。なお、DC電源部5は、AC電源部4の高電圧電源4aと低電圧電源4bとの電圧の振幅の中心を調整するための電源としても機能する。また、ACドライバ6と、DC電源部5とは、AC/DC切替回路7に接続されている。このAC/DC切替回路7は、後述する表示部12に含まれる画素20の共通電極23と補助容量25の一方の電極25aとに接続されている。

## [0024]

また、AC電源部4に含まれる高電圧電源4aおよび低電圧電源4bと、DC電源部5とは、信号電圧切替回路9に接続されている。信号電圧切替回路9は、AC電源部4およびDC電源部5から出力される信号電圧を選択的に切り替える機能を有する。

### [0025]

また、表示コントローラ8は、信号電圧切替回路9と、DAC(デジタル アナログコンバータ)10aおよびアンプ10bを含むソースドライバ10に接続されており、低消費電力駆動時には信号電圧切替回路9に接続されるとともに、通常起動時にはソースドライバ10に接続されるように構成されている。

## [0026]

また、信号電圧切替回路 9 と、ソースドライバ 1 0 とは、通常 / 低消費電力駆動切替回路 1 1 に接続されている。通常 / 低消費電力駆動切替回路 1 1 は、通常駆動時には、ソースドライバ 1 0 からの信号を信号線 1 4 に供給するとともに、低消費電力駆動時には、信号電圧切替回路 9 からの信号を信号線 1 4 に供給するように切り替える機能を有する。

#### [0027]

表示部12には、複数の信号線14と、複数の走査線(ゲート線)15とが互いに直交

10

20

30

40

50

するように配置されている。信号線14は、通常駆動/低消費電力データ切替回路11を介してソースドライバ10に接続されているとともに、走査線15は、ゲートドライバ13に接続されている。信号線14と走査線15とが交差する位置には、画素20が配置されている。なお、図1の表示部12には、簡略化のために1画素分の構成のみを示している。各々の画素20は、nチャネルトランジスタ21と、画素電極22と、画素電極22と、画素電極22と、画素電極22と、画素電極22と、画素電極22と、画素電極22と、画素電極22と共通電極23との間に挟持された液晶24と、補助容量25とによって構成されている。そして、nチャネルトランジスタ21のドレイン領域Dは、信号線14に接続されているとともに、ソース領域Sは、画素電極22と補助容量25の他方の電極25 b とに接続されている。また、nチャネルトランジスタ21のゲートGは走査線15に接続されている。

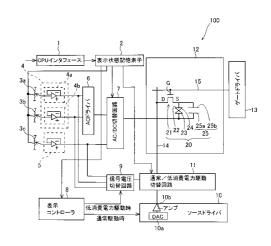

[0028]

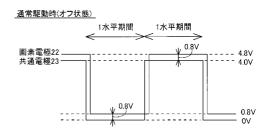

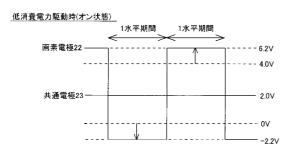

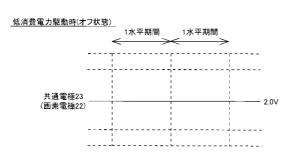

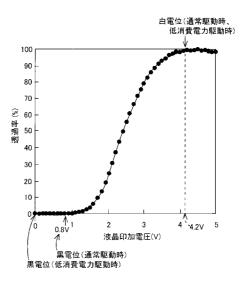

図2~図5は、通常駆動時と低消費電力駆動時における、画素電極と共通電極との電圧を示す図である。図6は、本発明の一実施形態による液晶に印加される電圧と画素の透過率との関係を示す図である。次に、図1~図6を用いて、本実施形態による液晶表示装置100の動作について説明する。

[0029]

(通常駆動時)

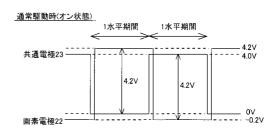

[0030]

次に、図2に示すように、通常駆動時の画素20がオン状態の時には、AC電源部4の高電圧電源4aと低電圧電源4bとから画素20の共通電極23に4.0Vの電圧と0Vの電圧が交流的に交互に印加される。共通電極23に印加される4.0Vおよび0Vの電圧は、表示部12の画素20が水平方向に走査される1水平期間ごとに切り替えられる。また、通常駆動時の画素20がオン状態のときにソースドライバ10から通常/低消費電力駆動切替回路11を介して画素電極22に印加される電圧は、共通電極23に4.0Vの電圧が印加されているときには、-0.2Vの電圧が印加され、0Vの電圧が印加されているときには、-0.2Vの電圧が印加され、0Vの電圧が印加されているときには、4.2Vの電圧が印加される。これにより、画素電極22と共通電極23との電位差は、常に、4.2V(白電位)となり、図6に示すように、画素20の透過率が約100%となる。その結果、画素20がオン状態となる。

[0031]

次に、図3に示すように、通常駆動時の画素20がオフ状態の時には、AC電源部4の高電圧電源4aと低電圧電源4bとから画素20の共通電極23に4.0 Vの電圧と0 Vの電圧が交流的に交互に印加される。共通電極23に印加される4.0 Vおよび0 Vの電圧は、1水平期間ごとに切り替えられる。また、通常駆動時の画素20がオフ状態のときにソースドライバ10から通常/低消費電力駆動切替回路11を介して画素電極22に印加される電圧は、共通電極23に4.0 Vの電圧が印加されているときには、4.8 Vの

電圧が印加され、0 Vの電圧が印加されているときには、0 .8 Vの電圧が印加される。これにより、画素電極22と共通電極23との電位差は、常に、0 .8 V(黒電位)となり、図6に示すように、画素20がオフ状態となる。

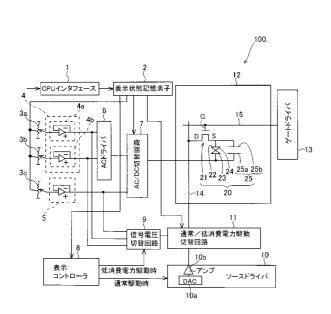

### [0032]

#### (低消費電力駆動時)

低消費電力駆動時には、図1に示すように、表示状態記憶素子2からの信号がAC電源部4およびDC電源部5に供給される。また、表示状態記憶素子2からの信号は、ACノDC切替回路7にも信号が供給される。低消費電力駆動時には、ACノDC切替回路23に加される。また、表示状態記憶素子2のの共通電極23に加される。また、表示状態記憶素子2からの信号は、高号電圧が画素20の共通電極23に加される。また、表示状態記憶素子2からの信号は、信号電圧切替回路9に供給るともでは、低消費電力駆動時において画素20をオン状態にするとともおよびDC電源部5のうち、AC電源部4の高電圧電源4aとは電源4bとで電源4aのうち、AC電源部5が選択される。また、状態記憶素子2からの信号は、通常ノ低消費電力駆動切替回路11に接続される。低消費電圧切替回路9の信号が、信号線14に供給される。

#### [0033]

次に、図4に示すように、低消費電力駆動時の画素20がオン状態の時には、通常駆動時に共通電極23に印加する電源として用いられていたAC電源部4の高電圧電源4aと低電圧電源4bとから画素20の画素電極22に6.2Vの電圧と・2.2Vの電圧は、図1に示す可変抵抗3aおよび3bにより、通常駆動時での4.0Vと0Vとからそれぞれ6.2Vおよび・2.2Vに変更されている。また、画素電極22に印加される6.2Vおよび・2.2Vに変更されている。また、画素電極22に印加される6.2Vおよび・2.2Vの電圧は、1水平期間ごとに切り替えられる。また、共通電極23には、DC電源部5から一定電圧である2.0Vの電圧が印加されている。なお、2.0Vの一定電圧(直流的な電圧)は、通常駆動時におけるAC電源34の高電圧電源4bの電圧との中間の電圧である。画素20の透過率が約100%となる。その結果、画素20がオン状態となる。また、画素20の補助容量25に補助容量25に節積された電荷が流れ出すことが抑制されている。

## [0034]

また、図5に示すように、低消費電力駆動時の画素20がオフ状態の時には、画素電極22および共通電極23の両方にDC電源部5から2.0Vの一定電圧(直流的な電圧)がそれぞれ印加されている。これにより、画素電極22と共通電極23との電位差は、常に、0V(黒電位)となり、図6に示すように、画素20の透過率が約0%となる。その結果、画素20がオフ状態となる。また、画素20がオン状態のときと同様に、画素20の補助容量25にも2.0Vの一定電圧が印加されている。これにより、通常駆動時のように補助容量25に印加される電圧が交流的な電圧である場合と異なり、1水平期間経過後に補助容量25に蓄積された電荷が流れ出すことが抑制されている。

## [0035]

本実施形態では、上記のように、共通電極23の電位は、低消費電力駆動時にはDC電源部5の一定電圧(2.0V)によって駆動されることにより、AC電源部4の交流的な電圧(4.0Vおよび0V)によって共通電極23が駆動される場合と異なり、画素20に含まれる補助容量25に蓄積された電荷が電流として流れ出してしまうという不都合が

10

20

30

40

発生するのを抑制することができるので、再び補助容量 2 5 に電荷を蓄積する必要がない。その結果、消費電力をより十分に低減することができる。

## [0036]

また、本実施形態では、上記のように、通常駆動時に共通電極23に交流的に電圧を印加するためのAC電源部4をさらに備え、低消費電力駆動時の画素20がオン状態のときに、AC電源部4を用いて信号電圧が画素電極22に交流的に印加されるように構成することによって、低消費電力駆動時に画素電極22に交流的に信号電圧を印加するための電源部を別途設ける必要がないので、液晶表示装置100の構成を簡略化することができる

### [0037]

また、本実施形態では、上記のように、低消費電力駆動時の画素 2 0 がオン状態のときに A C 電源部 4 を用いて画素電極 2 2 に交流的に印加される信号電圧(6 . 2 V および - 2 . 2 V )の絶対値は、通常駆動時に共通電極 2 3 に交流的に印加される電圧(4 . 0 V および 0 V )の絶対値よりも大きくなるように制御されていることによって、低消費電力駆動時において、共通電極 2 3 に印加される一定電圧と画素電極 2 2 に印加される交流的な電圧との電位差を大きくすることができるので、液晶 2 4 を完全にオン状態にすることができる。

#### [0038]

また、本実施形態では、上記のように、低消費電力駆動時に画素電極 2 2 に印加される電圧は、画素 2 0 が水平方向に走査される期間、または、画素 2 0 が 1 画面分走査される期間ごとに高電圧電源 4 a の電圧と低電圧電源 4 b の電圧とに切り替えられるように構成することによって、低消費電力駆動時に、液晶表示装置 1 0 0 に長時間にわたり一定の電圧が印加されることが抑制されるので、残像現象を引き起こす焼き付きを抑えることができる。

### [0039]

また、本実施形態では、上記のように、低消費電力駆動時に共通電極23に一定電圧を印加するためのDC電源部5を備え、DC電源部5の電圧は、通常駆動時に用いられるAC電源部4の高電圧電源4aの電圧(4.0V)と低電圧電源4bの電圧(0V)との実質的に中間の電圧(2.0V)になるように設定されていることによって、AC電源部4の交流的な電圧が4.0Vから0V、または、0Vから4.0Vに反転しても、DC電源部5の一定電圧(2.0V)と交流的な電圧との電位差が同じ2.0Vになるので、DC電源部5の電圧を調整しなくても交流的な電圧が反転する前後の画素20のオン状態またはオフ状態を維持することができる。

#### [0040]

また、本実施形態では、上記のように、低消費電力駆動時に共通電極23に一定電圧を印加するためのDC電源部5を備え、低消費電力駆動時の画素20がオフ状態のときには、DC電源部5の電圧が、画素電極22と共通電極23との両方に印加されるように構成されていることによって、容易に、画素電極22に印加される電圧と、共通電極23に印加される電圧とを、実質的に等しくなるようにすることができる。

### [0041]

また、本実施形態では、上記のように、通常駆動時および低消費電力駆動時に共通電極23にそれぞれ印加されるAC電源部4の交流的な電圧およびDC電源部5の一定電圧を切り替えるためのAC/DC切替回路7を備えることによって、容易に、共通電極23に印加される電圧を交流的な電圧と一定電圧とに切り替えることができる。

#### [0042]

また、本実施形態では、上記のように、通常駆動時に共通電極23に印加される交流的な電圧を、低消費電力駆動時に画素電極22に信号電圧として印加するための信号電圧切替回路9を備えることによって、容易に、通常駆動時に共通電極23に印加される交流的な電圧を、低消費電力駆動時に画素電極22に信号電圧として印加することができる。

## [0043]

40

10

20

30

なお、今回開示された実施形態は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態の説明ではなく特許請求の範囲によって示され、さらに特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれる。

## [0044]

たとえば、上記実施形態では、通常駆動時の画素電極および共通電極と、低消費電力駆動時の画素がオン状態のときの画素電極に印加する電圧を1水平期間ごとに変化させる例を示したが、本発明はこれに限らず、表示部の全画素が走査される1フレーム期間ごとに電圧を変化させてもよい。

#### [0045]

また、上記実施形態では、通常駆動時の共通電極に印加される電圧を4.0Vおよび0Vとし、画素電極に印加する電圧を画素がオン状態の時には4.2Vおよび・0.2V、画素がオフ状態の時には4.8Vおよび0.8Vとする例を示したが、本発明はこれに限らず、通常駆動時に画素がオン状態またはオフ状態になるのであれば、共通電極と画素電極とに印加する電圧を他の電圧にしてもよい。

#### [0046]

また、上記実施形態では、低消費電力駆動時の画素がオン状態になるときの共通電極に印加される電圧を2.0 Vとし、画素電極に印加される電圧を6.2 Vと-2.2 Vとする例を示したが、本発明はこれに限らず、共通電極と画素電極との電位差が画素がオン状態になる電位差であれば、共通電極および画素電極に印加する電圧を他の電圧にしてもよい。

#### [0047]

また、上記実施形態では、低消費電力駆動時の画素がオフ状態になるときの共通電極と 画素電極とに印加される電圧を 2 . 0 V とする例を示したが、本発明はこれに限らず、共 通電極と画素電極との電位差が画素がオフ状態になる電位差であれば、共通電極および画 素電極に印加する電圧を他の電圧にしてもよい。

#### [0048]

また、上記実施形態では、低消費電力駆動時に画素電極に印加される高電圧電源と低電圧電源との電圧を、それぞれ、4.0Vから6.2V、および、0Vから-2.2Vに変更する例を示したが、本発明はこれに限らず、共通電極と画素電極の電位差が画素をオン状態にすることができる電位差であれば他の電圧に変更してもよい。

【図面の簡単な説明】

#### [0049]

- 【図1】本発明の一実施形態による液晶表示装置の全体構成を示したブロック図である。

- 【図2】本発明の一実施形態による通常駆動時の画素がオン状態のときの画素電極と共通電極との電圧を示す図である。

- 【図3】本発明の一実施形態による通常駆動時の画素がオフ状態のときの画素電極と共通電極との電圧を示す図である。

- 【図4】本発明の一実施形態による低消費電力駆動時の画素がオン状態のときの画素電極と共通電極との電圧を示す図である。

- 【図 5 】本発明の一実施形態による低消費電力駆動時の画素がオフ状態のときの画素電極と共通電極との電圧を示す図である。

- 【図 6 】本発明の一実施形態による液晶に印加される電圧と画素の透過率との関係を示す図である。

### 【符号の説明】

## [0050]

- 3 a 、 3 b 、 3 c 可变抵抗

- 4 A C 電源部 ( 第 1 電源部 )

- 4 a 高電圧電源

- 4 b 低電圧電源

20

10

30

40

- 5 DC電源部(第2電源部)

- 7 AC/DC切替回路(共通電極切替回路)

- 9 信号電圧切替回路

- 1 4 信号線

- 15 走査線

- 2 2 画素電極

- 23 共通電極

- 2 0 画素

## 【図1】

## 【図3】

## 【図4】

## 【図5】

## 【図6】

# フロントページの続き

(51) Int.Cl.

F I

G 0 9 G 3/20 6 1 2 R G 0 9 G 3/20 6 1 2 A

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                                                                                                                                                            |         |            |  |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|--|--|--|--|

| 公开(公告)号        | <u>JP2008233703A</u>                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2008-10-02 |  |  |  |  |

| 申请号            | JP2007075777                                                                                                                                                                                                                                                                                                                                                      | 申请日     | 2007-03-23 |  |  |  |  |

| [标]申请(专利权)人(译) | 爱普生映像元器件有限公司                                                                                                                                                                                                                                                                                                                                                      |         |            |  |  |  |  |

| 申请(专利权)人(译)    | 爱普生影像设备公司                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |  |

| [标]发明人         | 吉田一輝                                                                                                                                                                                                                                                                                                                                                              |         |            |  |  |  |  |

| 发明人            | 吉田 一輝                                                                                                                                                                                                                                                                                                                                                             |         |            |  |  |  |  |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                                                                                       |         |            |  |  |  |  |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.611.A G09G3/20.624.D G09G3/20.623.A G09G3/20.612.R G09G3/20.612.A                                                                                                                                                                                                                                                                 |         |            |  |  |  |  |

| F-TERM分类号      | 2H093/NA16 2H093/NB07 2H093/NC03 2H093/NC11 2H093/NC18 2H093/NC24 2H093/NC28 2H093 /NC34 2H093/NC35 2H093/NC49 2H093/ND39 5C006/AC21 5C006/AF42 5C006/AF44 5C006/AF51 5C006/AF53 5C006/AF69 5C006/BC03 5C006/BC16 5C006/BF42 5C006/FA01 5C006/FA47 5C080 /AA10 5C080/BB05 5C080/DD26 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080/JJ05 2H193/ZA04 2H193/ZF03 2H193/ZF59 |         |            |  |  |  |  |

| 外部链接           | Espacenet                                                                                                                                                                                                                                                                                                                                                         |         |            |  |  |  |  |

## 摘要(译)

要解决的问题提供一种能够在以低功耗驱动显示部分时充分降低功耗的液晶显示装置。液晶显示装置100包括信号线14和扫描线15,以及公共电极23,公共电极23设置在信号线14和扫描线15彼此交叉并且面对像素电极22和像素电极22的位置处并且像素20.公共电极23在正常驱动期间以AC方式接收电压并且在低功耗驱动期间接收恒定电压(DC电压)。点域1