(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-185819

(P2008-185819A)

(43) 公開日 平成20年8月14日(2008.8.14)

(51) Int.Cl.

G02F 1/1368 (2006.01)

F 1

G02F 1/1368

テーマコード(参考)

2H092

審査請求 未請求 請求項の数 3 O L (全 8 頁)

(21) 出願番号

特願2007-19758 (P2007-19758)

(22) 出願日

平成19年1月30日 (2007.1.30)

(71) 出願人 302020207

東芝松下ディスプレイテクノロジー株式会社

東京都港区港南4-1-8

(74) 代理人 100105809

弁理士 木森 有平

(72) 発明者 松浦 由紀

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

(72) 発明者 多田 正浩

東京都港区港南四丁目1番8号 東芝松下ディスプレイテクノロジー株式会社内

F ターム(参考) 2H092 JA24 JA28 JA37 JA41 JA46

JB22 JB31 JB56 MA27 NA22

NA25

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】 液晶表示装置において、多層配線化による額縁領域の狭小化を実現すると同時に、配線カップリングの形成や LDD 領域のキャリアの誘起を解消可能とする。

【解決手段】 液晶表示パネル 1 の額縁領域に薄膜トランジスタを含む駆動回路が形成されている。配線として、第 1 配線 18 と、第 1 配線 18 上に第 2 層間絶縁膜 19 を介して形成される第 2 配線 20 を有する。薄膜トランジスタと重なる位置に形成される第 2 配線 20 は、薄膜トランジスタのソース領域 13A またはドレイン領域 13B と重なる位置であって、ゲート電極 15 及び低濃度不純物拡散領域 (LDD 領域 13C, 13D) とは重ならない位置に配置されている。あるいは、第 2 配線 20 と薄膜トランジスタのゲート電極 15 間の距離 B が第 1 配線 18 とゲート電極 15 間の距離よりも大とされている。

【選択図】 図 4

**【特許請求の範囲】****【請求項 1】**

液晶表示パネルの額縁領域に薄膜トランジスタを含む駆動回路が形成されてなる液晶表示装置であって、

少なくとも第1配線と、当該第1配線上に層間絶縁膜を介して形成される第2配線を有し、

薄膜トランジスタと重なる位置に形成される第2配線は、前記薄膜トランジスタのソース領域またはドレイン領域と重なる位置であって、ゲート電極及び低濃度不純物拡散領域とは重ならない位置に配置されていることを特徴とする液晶表示装置。

**【請求項 2】**

前記ソース領域またはドレイン領域におけるボロン濃度またはリン濃度が $1 \times 10^{19}$  / cm<sup>3</sup>以上であることを特徴とする請求項1記載の液晶表示装置。

**【請求項 3】**

液晶表示パネルの額縁領域に薄膜トランジスタを含む駆動回路が形成されてなる液晶表示装置であって、

少なくとも第1配線と、当該第1配線上に層間絶縁膜を介して形成される第2配線を有し、

前記第2配線と薄膜トランジスタのゲート電極間の距離が第1配線と前記ゲート電極間の距離よりも大であることを特徴とする液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、額縁領域に駆動回路が形成された液晶表示装置に関するものであり、特に、前記駆動回路が多層配線化された液晶表示装置の改良に関する。

**【背景技術】****【0002】**

アクティブマトリックス型液晶表示素子においては、1画素の液晶を駆動するのに1つの薄膜トランジスタが必要であり、多結晶シリコン（ポリシリコン）をチャンネル層に使用した多結晶薄膜トランジスタをガラス基板上に形成する技術が開発されている。プロセス技術の進歩により、低いプロセス温度でガラス基板上に高性能な多結晶薄膜トランジスタを形成することが可能になっている。

**【0003】**

多結晶シリコン膜を用いた液晶表示パネルの製造においては、前記の通りドライバー回路や電源回路等、駆動回路を構成する薄膜トランジスタを基板上に作り込むことが行われており、例えば外付け集積回路（I C）として設置していた駆動回路についても、液晶表示パネルの額縁領域に作り込むようになってきている。

**【0004】**

この場合、液晶表示パネルの周囲に配線形成等のために必要となる額縁領域の狭小化が大きな課題となる。液晶トランジスタアレイにおいて回路内蔵を行おうとすると、薄膜トランジスタ個数及び配線数が大きくなるため、前記額縁領域の幅を大きくせざるを得ない。従来のように信号線を1層構造の配線で形成した場合、配線を平行にレイアウトするしかなく、配線の占める面積が大きくなり、額縁領域を縮小することは難しい。額縁領域の狭小化を実現するためには、例えば配線を微細化することが考えられるが、配線を微細化すると配線抵抗の増加が問題になるおそれがある。そこで、配線を多層化（2層化）することが検討されている（例えば、特許文献1等を参照）。

**【0005】**

特許文献1には、表示部と額縁部を有するアレイ基板を備え、前記表示部は、複数の配線と、前記配線と接続された複数の薄膜トランジスタとを備え、前記額縁部は、前記薄膜トランジスタを駆動する駆動回路を備え、前記配線は、第1配線材料によって形成された第1配線層と、第1配線層上に形成された第2配線層とを備える画像表示装置が開示され

10

20

30

40

50

ている。特許文献1記載の発明では、配線を第1配線層と第2配線層とから構成するとともに、これら配線層において微細化に適した材料及び低抵抗な材料を役割に応じて使い分けることで、狭額縫化を実現している。

【特許文献1】特開2002-297057号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

前述のような多層配線化は、額縫領域を狭小化する上で有効であるが、薄膜トランジスタの動作の劣化や不安定化の原因となるおそれもある。例えば、多層配線化により薄膜トランジスタ上に第2配線層として信号線を形成した場合、薄膜トランジスタのゲート電極近傍の上部に層間絶縁膜を介して配線が形成されることになり、ゲート電極と前記信号線の間に配線カップリングが形成され、薄膜トランジスタの動作が劣化したり不安定化する。あるいは、低濃度不純物領域（LDD領域）にキャリアが誘起され、やはり薄膜トランジスタの動作が劣化したり不安定化する。

【0007】

本発明は、このような従来の実情に鑑みて提案されたものであり、多層配線化による額縫領域の狭小化を実現すると同時に、配線カップリングの形成やLDD領域のキャリアの誘起を解消可能とし、回路動作が安定で狭額縫化された液晶表示装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

前述の目的を達成するために、本願の第1の発明の液晶表示装置は、液晶表示パネルの額縫領域に薄膜トランジスタを含む駆動回路が形成されてなる液晶表示装置であって、少なくとも第1配線と、当該第1配線上に層間絶縁膜を介して形成される第2配線を有し、薄膜トランジスタと重なる位置に形成される第2配線は、前記薄膜トランジスタのソース領域またはドレイン領域と重なる位置であって、ゲート電極及び低濃度不純物拡散領域とは重ならない位置に配置されていることを特徴とする。

【0009】

第1の発明の液晶表示装置においては、額縫領域に形成される駆動回路を構成する配線が多層配線化されているので、配線引き回しの自由度が高まり、上層配線を下層配線や薄膜トランジスタと重ねて配置することで、駆動回路の設置面積（額縫領域の面積）が大幅に削減される。また、薄膜トランジスタと重なる位置に形成される第2配線にあっては、ゲート電極及び低濃度不純物拡散領域（LDD領域）とは重ならない位置に配置されているので、LDD領域にキャリアが誘起されることもない。したがって、薄膜トランジスタの動作が劣化したり不安定化することはない。

【0010】

一方、本願の第2の発明の液晶表示装置は、液晶表示パネルの額縫領域に薄膜トランジスタを含む駆動回路が形成されてなる液晶表示装置であって、前記駆動回路において、少なくとも第1配線と、当該第1配線上に層間絶縁膜を介して形成される第2配線を有し、前記第2配線と薄膜トランジスタのゲート電極間の距離が第1配線と前記ゲート電極間の距離よりも大であることを特徴とする。

【0011】

第2の発明の液晶表示装置においても、額縫領域に形成される駆動回路を構成する配線が多層配線化されているので、駆動回路の設置面積が大幅に削減されることは先の第1の発明の液晶表示装置と同様である。第2の発明の液晶表示装置では、第2配線と薄膜トランジスタのゲート電極間の距離が第1配線とゲート電極間の距離よりも大とされているので、第2配線とゲート電極間における配線カップリングの形成が抑えられ、これにより薄膜トランジスタの動作の劣化や不安定化が解消される。

【発明の効果】

【0012】

10

20

30

40

50

本発明の液晶表示装置によれば、層配線化による額縁領域の狭小化を実現すると同時に、配線カップリングの形成やLDD領域のキャリアの誘起を解消することが可能であり、回路動作が安定で狭額縁化された液晶表示装置を提供することが可能である。

【発明を実施するための最良の形態】

【0013】

以下、本発明を適用した液晶表示装置の実施形態について、図面を参照して詳細に説明する。

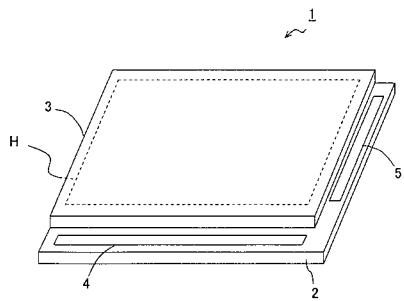

【0014】

液晶表示装置は、図1に示すように、アレイ基板2と対向基板3により構成される液晶表示パネル1を備え、これらアレイ基板2と対向基板3の間の液晶層をアレイ基板2上に形成された薄膜トランジスタ（画素トランジスタ）をスイッチング素子として駆動することで、画像の表示が行われる。

10

【0015】

ここで、表示領域Hにおいては、アレイ基板2に各画素に対応して画素電極がマトリクス状に形成されるとともに、画素電極の行方向に沿って走査線が形成され、列方向に沿って信号線が形成されている。さらに、各走査線と信号線の交差位置に前記画素トランジスタが形成されている。

【0016】

一方、アレイ基板2の周辺領域（液晶表示パネル1の額縁領域）には、アレイ基板2に配列形成される信号線に駆動信号を供給する信号線駆動回路4や、走査線に駆動信号を供給する走査線駆動回路5等の駆動回路が形成されている。これら駆動回路は、複数の薄膜トランジスタと、これら薄膜トランジスタ接続される配線等から構成されている。

20

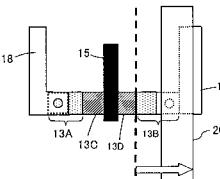

【0017】

図2は、液晶表示パネル1の額縁領域に形成された駆動回路の一部を示す概略断面図である。額縁領域に形成される駆動回路は、複数の薄膜トランジスタを備えているが、これら薄膜トランジスタは、例えばポリシリコンを活性層としてアレイ基板2上に直接形成されている。すなわち、前記薄膜トランジスタは、ガラス基板11上にアンダーコート層12を介して多結晶半導体層（ポリシリコン層）13を形成し、当該多結晶半導体層13を活性層（チャネル層）として利用することにより構成されている。

30

【0018】

ガラス基板11上には、前記の通りアンダーコート層12が形成されるが、これはガラス基板11の表面の傷や穴等を塞いで平坦化すること、ガラス基板11に含まれる不純物の多結晶半導体層13への拡散を防止すること等を目的に形成されている。このアンダーコート層12は、例えばシリコン酸化膜やシリコン窒化膜等を成膜することにより形成されるが、例えば、熱処理により流動化する流動化樹脂からなる平坦化層と、不純物の拡散を防止する被覆層とからなる積層構造とすることも可能である。あるいは、前記ガラス基板11が平坦化に優れ、含まれる不純物も少ない場合には、前記アンダーコート層12を省略することも可能である。

【0019】

前記アンダーコート層12上に形成される多結晶半導体層13は、例えばプラズマCVD法により成膜された非晶質シリコン（a-Si）をアニールした後、レーザ照射等によって多結晶化することにより形成されるものである。この多結晶半導体層13は、エッチングにより島状に素子分離されている。なお、本実施形態の場合、前記多結晶半導体層13はnチャンネル型薄膜トランジスタに対応するものであり、各多結晶半導体層13には、不純物注入によりソース領域13A、及びドレイン領域13Bが形成されており、さらにLDD領域（低濃度不純物拡散領域）13C、13Dが形成されている。

40

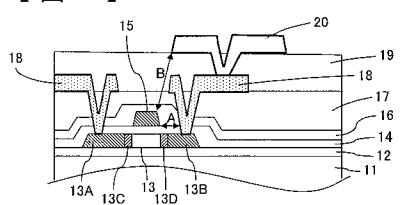

【0020】

前記多結晶半導体層13のチャネル上には、ゲート絶縁膜14を介してゲート電極15が形成され、さらには薄膜トランジスタと他の回路とを結ぶ配線が形成されているが、本実施形態においては、前記配線が多層配線化（2層配線化）されている。具体的には、ゲ

50

ート電極 15 上に第1層間絶縁膜 16 及び平坦化膜 17 を介して第1配線 18 が形成されるとともに、第1配線 18 上に第2層間絶縁膜 19 を介して第2配線 20 が形成されている。そして、これら配線のうち、下層配線である第1配線 18 が第1層間絶縁膜 16 及び平坦化膜 17 に形成したコンタクトホールを介して薄膜トランジスタのソース領域 13A, あるいはドレイン領域 13B と接続されている。第2配線 20 は、第2層間絶縁膜 19 に形成したコンタクトホールを介して第1配線 18 と任意の位置で接続されているが、第1配線 18 と接続されることなく独立に形成されるものであってもよい。

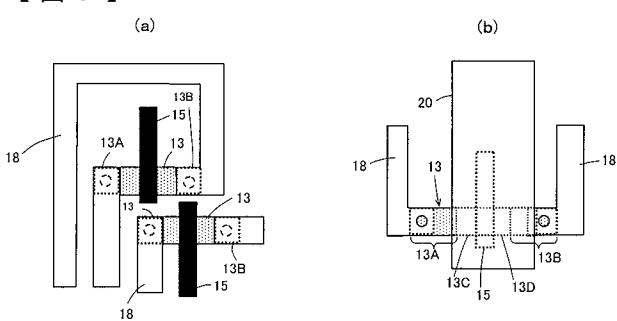

## 【0021】

ここで、前記配線を2層配線化したのは、額縁領域の狭小化のためである。図3(a)に示すように、配線を単層配線(第1配線 18 のみ)とした場合、第1配線 18 同士を交差させることはできず、薄膜トランジスタ上に形成することも難しい。したがって、配線引き回しのためにある程度の面積が必要であり、額縁領域を狭小化することが難しくなる。2層配線化すれば、例えば第1配線 18 と第2配線 20 を交差させることができあり、第2配線 20 を薄膜トランジスタと重なる位置に形成することも可能となるので、配線の自由度が増し、配線引き回しのための面積を大幅に削減することが可能になる。

10

## 【0022】

図3(b)は、2層配線化し、第2配線 20 を薄膜トランジスタのゲート電極 15 や LDD 領域 13C, 13D と重なる位置に形成した状態を示すものである。第2配線 20 を薄膜トランジスタのゲート電極 15 や LDD 領域 13C, 13D と重なる位置に形成することで、配線引き回しに必要な面積が大幅に削減され、額縁領域を狭小化する上で有利である。

20

## 【0023】

ただし、図3(b)に示すように、第2配線 20 が薄膜トランジスタの LDD 領域 13C, 13D と重なる位置に形成されると、LDD 領域にキャリアが誘起され、薄膜トランジスタの特性が劣化したり、動作が不安定になるおそれがある。また、第2配線 20 が薄膜トランジスタのゲート電極 15 と近い位置に形成されていると、第2配線 20 とゲート電極 15 間の配線カップリングにより容量が形成され、やはり薄膜トランジスタの特性が劣化したり、動作が不安定になるおそれがある。

## 【0024】

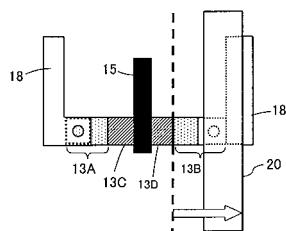

そこで、本実施形態の液晶表示装置においては、先ず第1に、第2配線 20 の形成位置を規制することで、前記 LDD 領域にキャリアが誘起されるのを防止するようにしている(要件1)。具体的には、図4に示すように、第2配線 20 を薄膜トランジスタの LDD 領域 13C, 13D とは重ならない位置(図中、破線よりも外側位置)に形成する。これにより、LDD 領域におけるキャリアの誘起が解消される。

30

## 【0025】

なお、前記第2配線 20 の形成位置の基準となる破線位置(LDD 領域とソース・ドレイン領域との境界)については、不純物濃度  $1 \times 10^{19} / \text{cm}^3$  を境に決めることができる。ソース領域またはドレイン領域における不純物濃度(ボロン濃度またはリン濃度)が  $1 \times 10^{19} / \text{cm}^3$  以上であれば、この上に重ねて第2配線を形成しても、キャリアが誘起されることはない。一方、不純物濃度が  $1 \times 10^{19} / \text{cm}^3$  未満の LDD 領域と重なる位置に第2配線 20 を形成すると、キャリアの誘起が問題になるおそれがある。

40

## 【0026】

前記第2配線 20 は、図4の破線位置よりも外側であれば任意の位置に形成することができるが、薄膜トランジスタから外れる位置に形成したのでは、配線引き回しの面積を削減するという目的を達成することができない。したがって、前記第2配線 20 は、駆動回路を構成する薄膜トランジスタの少なくとも1つにおいて、薄膜トランジスタと重なる位置に形成する必要がある。この場合、第2配線 20 は、不純物濃度が  $1 \times 10^{19} / \text{cm}^3$  未満である LDD 領域 13C, 13D と重ならず、不純物濃度が  $1 \times 10^{19} / \text{cm}^3$  以上のソース領域 13A あるいはドレイン領域 13B と重なる位置に配置すればよい。これにより、配線引き回しの面積を大幅に削減しながら、薄膜トランジスタの特性の劣化や

50

動作の不安定化を防ぐことができる。

【0027】

また、本実施形態においては、第2に、第2配線20と薄膜トランジスタのゲート電極15間の距離を第1配線18と前記ゲート電極15間の距離よりも大とすることで、第2配線20とゲート電極15間の配線カップリングにより容量が形成されるのを防止するようしている（要件2）。

【0028】

すなわち、図2において、ゲート電極15から第1配線18までの距離を距離A、ゲート電極15から第2配線20までの距離を距離Bとしたときに、距離A < 距離Bとなるように設定している。前記距離Bを大きくするためには、例えば第2層間絶縁膜19の厚さを厚くすればよい。これにより、第2配線20とゲート電極15間の配線カップリングの影響を小さくすることができ、薄膜トランジスタの特性の劣化や動作の不安定化を防ぐことができる。

10

【0029】

前述の要件1（第2配線20をLDD領域13C, 13Dと重ならない位置に形成。）と要件2（第2配線20と薄膜トランジスタのゲート電極15間の距離Bを第1配線18と前記ゲート電極15間の距離Aよりも大とする。）は、それぞれ単独に実施してもよいが、これら要件を併せて実施することで、薄膜トランジスタの特性の劣化や動作の不安定化を効果的に防止することができる。

20

【0030】

以上のように、本実施形態の液晶表示装置においては、第2配線20をLDD領域13C, 13Dと重ならない位置に形成しているので、額縁領域を狭小化しながら回路動作を安定化することが可能である。同様に、第2配線20と薄膜トランジスタのゲート電極15間の距離Bを第1配線18と前記ゲート電極15間の距離Aよりも大とすることで、額縁領域を狭小化しながら回路動作を安定化することが可能である。

30

【0031】

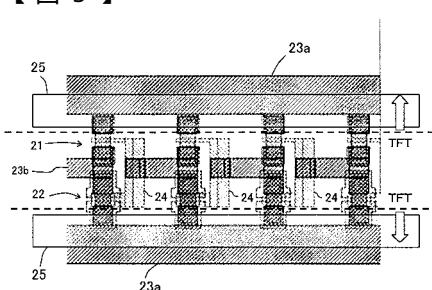

図5は、リングオシレータ回路への適用例を示すものである。リングオシレータ回路は、インバータを奇数個リング状に繋げた回路であり、リングの長さに応じた周波数で発振する。本例の場合、各インバータがn-チャンネルTFT21及びp-チャンネルTFT22により構成されている。第1配線は、電源配線23aや、インバータ間を繋ぐ信号線23b等から構成されている。

30

【0032】

このような構成のリングオシレータ回路において、第1配線のうちの電源配線23aと重ねて第2配線25を形成すれば、配線引き回し面積を大幅に削減することができる。この場合にも、第2配線25は、n-チャンネルTFT21及びp-チャンネルTFT22のLDD領域より外側位置（図中、破線よりも外側位置）に配置形成する。これにより、LDD領域におけるキャリアの誘起を解消することができ、薄膜トランジスタ（n-チャンネルTFT21及びp-チャンネルTFT22）の特性の劣化や動作の不安定化を防ぐことができる。

40

【0033】

また、前記リングオシレータ回路においては、電源配線23aと重ねて第2配線25を形成することに加えて、インバータ間を繋ぐ信号線23b上に第2配線25を形成しないことも重要である。第2配線25を前記信号線23b上に重ねて形成すると、配線カップリングの影響で駆動能力が低下するおそれがある。

【実施例】

【0034】

以下、本発明の具体的な実施例について説明する。

【0035】

（実験1）

本実験例においては、先ず、ガラス基板上にポリシリコン層を膜厚50nmで形成し、

50

ゲート絶縁膜を膜厚 100 nm で全面に成膜した。次いで、その上にゲート配線材料をスパッタにより膜厚 300 nm で成膜した。続いて、リソグラフィ工程によって、レジスト塗布工程、露光工程、現像工程を行い、エッチングのためのレジストマスクを形成し、前記レジストをマスクにドライエッチングでゲート電極を形成した。

## 【0036】

ゲート電極のエッチングの後、ゲート電極をマスクとして不純物のドーピング (N-ドーピング) を行ない、ソース・ドレイン領域及び LDD 領域を形成した。ソース・ドレイン領域における不純物濃度は  $1.3 \times 10^{20} / \text{cm}^3$ 、LDD 領域における不純物濃度は  $5 \times 10^{13} / \text{cm}^3$  とした。

## 【0037】

さらに、第 1 層間絶縁膜を介してソース・ドレイン領域と接続される第 1 配線を形成するとともに、第 1 配線上に第 2 層間絶縁膜を介して第 2 配線を形成した。この第 2 配線の形成位置をゲート電極及び LDD 領域と重なる位置とした場合 (比較例 1) と、LDD 領域の外側に形成した場合 (実施例 1) について、薄膜トランジスタの特性を計測した。計測した特性は、n-チャンネル TFT のしきい値電圧 (V<sub>th</sub>) 及び電界効果移動度である。その結果、比較例 1 ではしきい値電圧が 0.9 V ~ 1.3 V、電界効果移動度が  $130 \text{ cm}^2 \cdot \text{V} / \text{s} \sim 138 \text{ cm}^2 \cdot \text{V} / \text{s}$  と特性のばらつきが見られたが、実施例 1 では、しきい値電圧が 1.1 V \*、電界効果移動度が  $135 \text{ cm}^2 \cdot \text{V} / \text{s}$  であり、特性のばらつきはほとんど見られなかった。

## 【0038】

## (実験 2)

図 5 に示すリングオシレータ回路において、第 2 配線を薄膜トランジスタの LDD 領域上及びインバータ間を繋ぐ信号線上に重ねて形成した場合 (比較例 2) と、第 2 配線を薄膜トランジスタの LDD 領域やインバータ間を繋ぐ信号線とは重ならないように形成した場合 (実施例 2) について、特性の評価を行った。評価は発振周波数について行った。その結果、比較例 2 では 3.2 MHz、実施例 2 では 5.0 MHz であった。第 2 配線を形成しない場合 (リファレンス) の発振周波数は 5.1 MHz であり、実施例 2 において動作速度の劣化が著しく小さいことがわかった。

## 【図面の簡単な説明】

## 【0039】

【図 1】液晶表示パネルの概略構成を示す斜視図である。

【図 2】駆動回路の断面構造の一例を示す概略断面図である。

【図 3】(a) は単層配線の場合の配線引き回し例を示す模式的な平面図であり、(b) は 2 層配線の場合の配線引き回し例を示す模式的な平面図である。

【図 4】第 2 配線の形成位置を示す模式的な平面図である。

【図 5】リングオシレータ回路への適用例を示す概略平面図である。

## 【符号の説明】

## 【0040】

1 液晶表示パネル、2 アレイ基板、3 対向基板、11 ガラス基板、12 アンダーコート層、13 多結晶半導体層、13A ソース領域、13B ドレイン領域、13C、13D LDD 領域、14 ゲート絶縁膜、15 ゲート電極、16 第 1 層間絶縁膜、17 平坦化膜、18 第 1 配線、19 第 2 層間絶縁膜、20 第 2 配線

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

|                |                                                                                                                                                           |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                    |         |            |

| 公开(公告)号        | <a href="#">JP2008185819A</a>                                                                                                                             | 公开(公告)日 | 2008-08-14 |

| 申请号            | JP2007019758                                                                                                                                              | 申请日     | 2007-01-30 |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                                                                                            |         |            |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                                                                                              |         |            |

| [标]发明人         | 松浦由紀<br>多田正浩                                                                                                                                              |         |            |

| 发明人            | 松浦 由紀<br>多田 正浩                                                                                                                                            |         |            |

| IPC分类号         | G02F1/1368                                                                                                                                                |         |            |

| FI分类号          | G02F1/1368                                                                                                                                                |         |            |

| F-TERM分类号      | 2H092/JA24 2H092/JA28 2H092/JA37 2H092/JA41 2H092/JA46 2H092/JB22 2H092/JB31 2H092/JB56 2H092/MA27 2H092/NA22 2H092/NA25 2H192/AA24 2H192/CB02 2H192/FB02 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                 |         |            |

#### 摘要(译)

解决的问题：通过液晶显示装置中的多层布线来实现边框区域的变窄，同时消除在LDD区域中的布线耦合和载流子的感应的形成。在液晶显示面板的边框区域中形成有包括薄膜晶体管的驱动电路。配线包括第一配线18和经由第二层间绝缘膜19形成在第一配线18上的第二配线20。在与薄膜晶体管重叠的位置处形成的第二布线20是与薄膜晶体管的源极区域13A或漏极区域13B重叠的位置，并且不与栅极电极15和低浓度杂质扩散区域( LDD区域13C和13D )重叠。它位于一个位置。替代地，第二布线20与薄膜晶体管的栅电极15之间的距离B被设置为大于第一布线18与栅电极15之间的距离。[选择图]图4