(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-241778

(P2005-241778A)

(43) 公開日 平成17年9月8日(2005.9.8)

(51) Int.Cl.<sup>7</sup>

**G02F** 1/133

**G09G** 3/20

**G09G** 3/36

// **G02F** 1/1343

**G02F** 1/1368

F 1

G02F 1/133 550

G09G 3/20 621A

G09G 3/20 623C

G09G 3/20 660Q

G09G 3/20 670E

テーマコード(参考)

2H092

2H093

5C006

5C080

審査請求 未請求 請求項の数 10 O L (全 16 頁) 最終頁に続く

(21) 出願番号

特願2004-49104 (P2004-49104)

(22) 出願日

平成16年2月25日 (2004.2.25)

(71) 出願人 000004237

日本電気株式会社

東京都港区芝五丁目7番1号

(74) 代理人 100079164

弁理士 高橋 勇

(72) 発明者 佐藤 哲史

東京都港区芝五丁目7番1号 日本電気株式会社内

(72) 発明者 関根 裕之

東京都港区芝五丁目7番1号 日本電気株式会社内

F ターム(参考) 2H092 GA32 JA24 JB02 JB04 JB61

NA04 PA06

2H093 NA16 NA32 NB01 NC34 NC35

NC65 ND01 ND15 ND58 ND60

最終頁に続く

(54) 【発明の名称】 液晶表示装置の駆動方法

## (57) 【要約】

**【課題】** 表示画素領域1の周辺に設けられたダミー画素領域2から発生するリバースツイストドメインによる表示不良を防ぐ。

**【解決手段】** ダミー画素領域2の画素に印加する信号電圧を、表示画素領域1に印加する映像信号電圧の最大値より低くし、かつ隣接するダミー画素領域2と表示画素領域1との間で横方向電界による表示不良が生じない程度の電圧とすることにより、ダミー画素領域2内でのリバースツイストドメインの発生を抑制し、リバースツイストによる表示不良を防ぐ。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

複数の走査線が横方向に平行に配置され、複数の信号線が縦方向に平行に配置され、これらの走査線と信号線との各交点にスイッチ素子、画素電極及び液晶を含む画素が配置された画素領域を有し、

この画素領域が、画像表示に用いられる表示画素領域と、この表示画素領域の周囲に配置され画像表示に用いられないダミー画素領域とによって構成された、液晶表示装置において、

前記表示画素領域の駆動中に、前記ダミー画素領域でリバースツイストドメインが発生する上限電圧値よりも低く、かつ前記表示画素領域と前記ダミー画素領域との境界部に光り漏れが発生する下限電圧値よりも高い最適電圧を、少なくとも一部の前記ダミー画素領域の液晶に印加する、

ことを特徴とする液晶表示装置の駆動方法。

**【請求項 2】**

前記上限電圧値は、前記表示画素領域の液晶に印加する映像信号電圧の最大値よりも低い、

請求項 1 記載の液晶表示装置の駆動方法。

**【請求項 3】**

前記上限電圧値は、前記表示画素領域の液晶に印加する映像信号電圧の最大値よりも、前記スイッチ素子の光リーク電流による一フレーム期間後の電圧低下分だけ低い、

請求項 1 記載の液晶表示装置の駆動方法。

**【請求項 4】**

前記最適電圧は、前記ダミー画素領域の液晶に複数回印加した結果が前記上限電圧値よりも低くかつ前記下限電圧値よりも高くなる、複数の異なる値である、

請求項 1 記載の液晶表示装置の駆動方法。

**【請求項 5】**

$n, m$  が自然数であり、かつ  $n > m$  であるとき、連続する  $n$  回のフレームのうち、

$m$  回の前記最適電圧は、前記表示画素領域の液晶に印加する映像信号電圧の最小値又はこれよりも大きく、

残る  $n - m$  回の前記最適電圧は、前記表示画素領域の液晶に印加する映像信号電圧の最大値又はこれよりも小さい、

請求項 1 記載の液晶表示装置の駆動方法。

**【請求項 6】**

走査線反転駆動法を用い、

前記表示画素領域の左右に配置されたダミー画素領域では、前記最適電圧を前記液晶に印加し、

前記表示画素領域の上下に配置されたダミー画素領域では、前記下限電圧値よりも大きい電圧を前記液晶に印加する、

請求項 1 乃至 5 のいずれかに記載の液晶表示装置の駆動方法。

**【請求項 7】**

走査線反転駆動法を用い、

前記表示画素領域の左右に配置されたダミー画素領域で、前記最適電圧を前記液晶に印加し、

$n, m$  が自然数であり、かつ  $n > m$  であるとき、連続する  $n$  回のフレームのうち、

$m$  回の前記最適電圧は、前記表示画素領域の液晶に印加する映像信号電圧の最小値又はこれよりも大きく、

残る  $n - m$  回の前記最適電圧は、前記表示画素領域の液晶に印加する映像信号電圧の最大値又はこれよりも小さい、

請求項 1 記載の液晶表示装置の駆動方法。

**【請求項 8】**

10

20

30

40

50

信号線反転駆動法を用い、

前記表示画素領域の上下に配置されたダミー画素領域では、前記最適電圧を前記液晶に印加し、

前記表示画素領域の左右に配置されたダミー画素領域では、前記下限電圧値よりも大きい電圧を前記液晶に印加する、

請求項 1 乃至 5 のいずれかに記載の液晶表示装置の駆動方法。

【請求項 9】

信号線反転駆動法を用い、

前記表示画素領域の上下に配置されたダミー画素領域では、前記最適電圧を前記液晶に印加し、

10

$n, m$  が自然数であり、かつ  $n > m$  であるとき、連続する  $n$  回のフレームのうち、

$m$  回の前記最適電圧は、前記表示画素領域の液晶に印加する映像信号電圧の最小値又はこれよりも大きく、

残る  $n - m$  回の前記最適電圧は、前記表示画素領域の液晶に印加する映像信号電圧の最大値又はこれよりも小さい、

請求項 1 記載の液晶表示装置の駆動方法。

【請求項 10】

前記スイッチ素子が薄膜トランジスタである、

請求項 1 乃至 9 のいずれかに記載の液晶表示装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像表示に用いられる表示画素領域と画像表示に用いられないダミー画素領域とを有する液晶表示装置に関し、詳しくはそのダミー画素領域の駆動方法に関する。

【背景技術】

【0002】

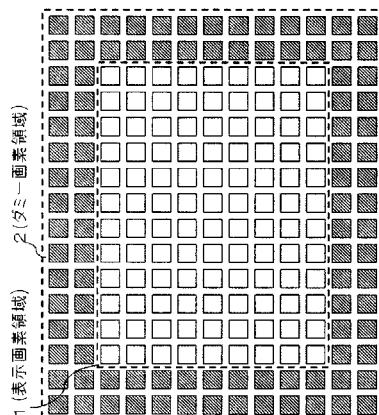

図 8 は、従来の液晶表示装置の駆動方法における画素領域を示す平面図である。以下、この図面に基づき説明する。

【0003】

多数の画素がマトリックス状に配置された表示画素領域 1 全体の液晶印加電圧に対する光学特性を均一にする目的で、表示画素領域 1 の外周に画像表示に直接寄与しないダミー画素領域 2 を設けている。また、その駆動方法において、ダミー画素領域 2 の画素電極に印加する電圧は、表示画素領域 1 の画素電極に印加する映像信号電圧の最大値としている。その理由について、以下に述べる。

【0004】

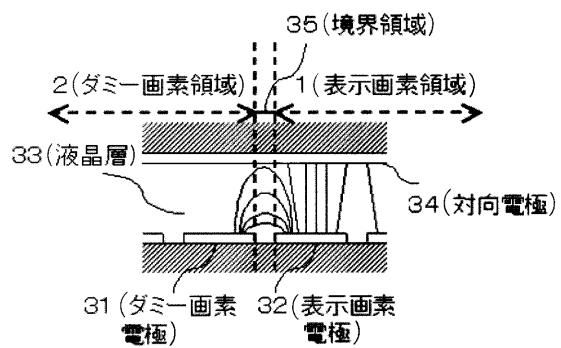

図 9 は、図 8 中の線 X に沿った断面図である。以下、図 9 に基づき説明する。

【0005】

液晶層 33 内に示す線は、対向電極 34 と同じ電圧をダミー画素電極 31 にも印加するとともに、映像信号電圧の最大値を表示画素電極 32 に印加したときの電気力線である。ダミー画素領域 2 と表示画素領域 1 との境界領域 35 の液晶層 33 に横方向電界が生じるため、液晶分子は寝ている状態となる。そのため、境界領域 35 付近の透過率は、表示画素領域 1 の中心側の透過率と異なるため表示画質を悪化させる。より具体的に言えば、液晶に電圧を印加しないときに白を表示するノーマリホワイト方式の場合、表示画素領域 1 の全体に黒を表示させ、かつダミー画素領域 2 に白を表示させる電圧を印加していると、表示画素領域 1 の周囲が光り漏れによって白っぽく見えることになる。

【0006】

この現象を防ぐためには、ダミー画素電極 31 に印加する電圧を映像信号電圧の最大値とすれば良く、その例が特許文献 1 に記載されている。

【0007】

【特許文献 1】特許第 2590992 号公報（第 5 図、第 2 頁右欄第 47 ~ 50 行）

**【発明の開示】****【発明が解決しようとする課題】****【0008】**

しかし、前述の従来技術のように、ダミー画素電極31に印加する電圧を、表示画素電極32に印加する映像信号電圧の最大値とすると、ダミー画素領域2内でリバースツイストドメインが発生し、その影響が表示画像領域1内に及ぶと表示不良が発生する、という問題があった。この表示不良について、ゲート線反転駆動法を例に以下に説明する。

**【0009】**

リバースツイストドメインは、液晶分子が立ち上がった状態から発生するが、液晶分子が強く立ち上がっている状態ほど（すなわち液晶層33に高い電圧が印加されているほど）発生しやすい。

**【0010】**

ダミー画素領域2内のダミー画素は開口部を持たず、画素全体が遮光膜で覆われているため、画素内の薄膜トランジスタ（以下「TFT」という。）の光リーク電流がほとんど発生しない。そのため、ダミー画素領域2内においては、表示画素領域1と同一の電圧を液晶に印加した場合でも、開口部を有する表示画素領域1に比べて、一フレーム期間後も高い電圧を維持しているので、液晶分子がより立ち上がった状態となる。しかも、ダミー画素領域2内には、常に表示画素電極32に印加する最大の電圧が印加され続けているため、液晶分子は常に立ち上がったままの状態となっている。

**【0011】**

そして、ゲート線反転駆動法では画素マトリックスの一行毎に液晶に印加する電圧の極性を変えるため、複数のゲート線が画面の上下方向に平行に並んでいるとすると、画面の上下方向の画素電極間には横方向電界が生じている。横方向電界が生じた領域の液晶分子は、配向異常を起こしやすいので、リバースツイストとなりやすい。このため、ダミー画素領域2内の画面の上下方向の画素間においてリバースツイストドメインが発生すると、周囲の液晶分子にもその影響が及ぶ。このリバースツイストドメインは、表示画素領域1にまで伝播することになる。すなわち、ゲート線反転駆動法の場合、ダミー画素領域2内で発生したリバースツイストドメインが、ゲート線に沿って表示画素領域1に伝播することにより、表示画素領域1では左右から伸びる横筋状の表示不良が発生する。

**【0012】**

そこで、本発明の目的は、ダミー画素領域におけるリバースツイストドメインの発生を防ぐことにより、リバースツイスト起因による表示画素領域での表示不良を解消する、液晶表示装置の駆動方法を提供することにある。

**【課題を解決するための手段】****【0013】**

本発明に係る駆動方法（請求項1）は、複数の走査線が横方向に平行に配置され、複数の信号線が縦方向に平行に配置され、走査線と信号線との各交点にスイッチ素子、画素電極及び液晶を含む画素が配置された画素領域を有する、液晶表示装置に対するものである。そして、この画素領域は、画像表示に用いられる表示画素領域と、表示画素領域の周囲に配置され画像表示に用いられないダミー画素領域とによって構成されている。このとき、表示画素領域の駆動中に、ダミー画素領域でリバースツイストドメインが発生する上限電圧値よりも低く、かつ表示画素領域とダミー画素領域との境界部に光り漏れが発生する下限電圧値よりも高い最適電圧を、少なくとも一部のダミー画素領域の液晶に印加する。

**【0014】**

前述したように、ある従来技術では、ダミー画素領域の液晶に電圧を印加しなかった（すなわちダミー画素電極を対抗電極と同電位にしていた）ので、表示画素領域とダミー画素領域との境界部に光り漏れが発生していた。また、ある従来技術では、表示画素領域の液晶に印加する映像信号電圧の最大値をダミー画素領域の液晶に印加していたので、ダミー画素領域でリバースツイストドメインが発生していた。そこで、本発明では、ダミー画素領域でリバースツイストドメインが発生する上限電圧値と、表示画素領域とダミー画素

10

20

30

40

50

領域との境界部に光り漏れが発生する下限電圧値とを設定し、これらの範囲内の電圧を最適電圧としてダミー画素領域の液晶に印加する。これらの上限電圧値及び下限電圧値は、例えば実験や計算機シミュレーションによって求める。なお、本明細書でいう電圧は絶対値である。

【0015】

請求項2記載の駆動方法は、請求項1記載の駆動方法において、上限電圧値は表示画素領域の液晶に印加する映像信号電圧の最大値よりも低い、というものである。

【0016】

従来技術では、表示画素領域の液晶に印加する映像信号電圧の最大値をダミー画素領域の液晶に印加していたので、ダミー画素領域でリバースツイストドメインが発生していた。そこで、本発明では、表示画素領域の液晶に印加する映像信号電圧の最大値よりも低い電圧を、上限電圧値として設定している。これにより、ダミー画素領域の液晶に印加される電圧は表示画素領域の液晶に印加される電圧よりも低くなるので、ダミー画素領域で発生したリバースツイストドメインが表示画素領域へ伝播することは起こり得ない。もしもダミー画素領域でリバースツイストドメインが発生したならば、表示画素領域でもリバースツイストドメインが発生しているからである。

10

【0017】

請求項3記載の駆動方法は、請求項1記載の駆動方法において、上限電圧値は、表示画素領域の液晶に印加する映像信号電圧の最大値よりも、スイッチ素子の光リーク電流による一フレーム期間後の電圧低下分だけ低い、というものである。

20

【0018】

表示画素領域の液晶に印加された電圧は、一フレーム期間後に再印加されるまで、光リーク電流によって時間とともに徐々に放電され低下する。一方、ダミー画素領域のスイッチ素子は、遮光されているため光リーク電流がほとんど発生しないので、一フレーム期間後の光リーク電流による電圧低下もほとんど発生しない。したがって、ダミー画素領域の液晶は、表示画素領域の液晶と同じ電圧を印加しても、表示画素領域の液晶よりも高電圧が印加されることになる。そこで、本発明では、この電圧低下分を考慮して、表示画素領域の液晶に実際に印加される映像信号電圧の最大値よりも、確実に低くなるように上限電圧値を設定している。

30

【0019】

請求項4記載の駆動方法は、請求項1記載の駆動方法において、最適電圧は、ダミー画素領域の液晶に複数回印加した結果が上限電圧値よりも低くかつ下限電圧値よりも高くなる、複数の異なる値である、というものである。

30

【0020】

最適電圧は、常に上限電圧値及び下限電圧値の範囲内である必要はなく、例えば平均してその範囲内であればよい。

40

【0021】

請求項5記載の駆動方法は、請求項1記載の駆動方法において、 $n, m$ が自然数であり、かつ $n > m$ であるとき、連続する $n$ 回のフレームのうち、 $m$ 回の最適電圧は、表示画素領域の液晶に印加する映像信号電圧の最小値又はこれよりも大きく、残る $n - m$ 回の最適電圧は、表示画素領域の液晶に印加する映像信号電圧の最大値又はこれよりも小さい、というものである。

40

【0022】

最適電圧は、常に上限電圧値及び下限電圧値の範囲内である必要はなく、複数回印加した結果が上限電圧値よりも低くかつ下限電圧値よりも高ければよい。

50

【0023】

請求項6記載の駆動方法は、請求項1～5記載の駆動方法において、走査線反転駆動法を用い、表示画素領域の左右に配置されたダミー画素領域では、最適電圧を液晶に印加し、表示画素領域の上下に配置されたダミー画素領域では、下限電圧値よりも大きい電圧を液晶に印加する、というものである。

## 【0024】

走査線反転駆動法では、ダミー画素領域で発生したリバースツイストドメインが走査線に沿って表示画素領域に伝播する。そのため、表示画素領域の左右に配置されたダミー画素領域でのみ、最適電圧を液晶に印加すればよい。

## 【0025】

請求項7記載の駆動方法は、請求項1記載の駆動方法において、走査線反転駆動法を用い、表示画素領域の左右に配置されたダミー画素領域で、最適電圧を液晶に印加するものである。このとき、 $n, m$ が自然数であり、かつ $n > m$ であるとき、連続する $n$ 回のフレームのうち、 $m$ 回の最適電圧は、表示画素領域の液晶に印加する映像信号電圧の最小値又はこれよりも大きく、残る $n - m$ 回の最適電圧は、表示画素領域の液晶に印加する映像信号電圧の最大値又はこれよりも小さい。

10

## 【0026】

走査線反転駆動法では、ダミー画素領域で発生したリバースツイストドメインが走査線に沿って表示画素領域に伝播する。そのため、表示画素領域の左右に配置されたダミー画素領域でのみ、最適電圧を液晶に印加すればよい。

## 【0027】

請求項8記載の駆動方法は、請求項1～5の駆動方法において、信号線反転駆動法を用い、表示画素領域の上下に配置されたダミー画素領域では、最適電圧を前記液晶に印加し、表示画素領域の左右に配置されたダミー画素領域では、下限電圧値よりも大きい電圧を液晶に印加する、というものである。

20

## 【0028】

信号線反転駆動法では、ダミー画素領域で発生したリバースツイストドメインが信号線に沿って表示画素領域に伝播する。そのため、表示画素領域の上下に配置されたダミー画素領域でのみ、最適電圧を液晶に印加すればよい。

## 【0029】

請求項9記載の駆動方法は、請求項1記載の駆動方法において、信号線反転駆動法を用い、表示画素領域の上下に配置されたダミー画素領域では、最適電圧を液晶に印加するものである。このとき、 $n, m$ が自然数であり、かつ $n > m$ であるとき、連続する $n$ 回のフレームのうち、 $m$ 回の最適電圧は、表示画素領域の液晶に印加する映像信号電圧の最小値又はこれよりも大きく、残る $n - m$ 回の最適電圧は、表示画素領域の液晶に印加する映像信号電圧の最大値又はこれよりも小さい。

30

## 【0030】

信号線反転駆動法では、ダミー画素領域で発生したリバースツイストドメインが信号線に沿って表示画素領域に伝播する。そのため、表示画素領域の上下に配置されたダミー画素領域でのみ、最適電圧を液晶に印加すればよい。

## 【0031】

請求項10記載の駆動方法は、請求項1～9記載の駆動方法において、スイッチ素子がTFTである、というものである。

## 【0032】

TFTは、TFTやMIMなどの他のスイッチ素子に比べて、確実に画素をオン・オフできるので、前述の本発明の効果と相俟って大画面かつ高精細の液晶表示装置を実現できる。

40

## 【0033】

また、本発明は、次のように言い換えることができる。

## 【0034】

本発明の液晶表示装置の駆動方法は、ダミー画素電極に印加する電圧を、表示画素電極に印加する映像信号電圧の最大値より小さくし、かつ、表示画素領域とダミー画素領域との境界部に光り漏れを認識させない電圧とする。なお、ダミー画素電極に印加する電圧は、少なくとも、表示画素電極に最大の映像信号電圧を印加したとき、その電圧から光リレー電流による電圧低下分だけ低い電圧とすることが望ましい。

50

## 【0035】

また、表示画素電極に印加する最大の電圧より低い電圧を印加する別 の方法として、ダミー画素領域の画素電極に印加する電圧を、連続するフレーム内のうちで、ある一部のフレームでは表示画素に印加する映像信号電圧の最小値とし、それ以外のフレームでは前記映像信号電圧の最大値とすることも可能である。

## 【0036】

本発明の作用（効果をもたらす手段の働き）について説明する。ダミー画素領域の画素電極に印加する電圧を、表示画素電極に印加する映像信号電圧の最大値より小さくする。これにより、従来技術に比べて、ダミー画素領域内の液晶分子の立ち上がりを抑制し、リバースツイストドメインの発生を防ぐ。また、ダミー画素電極に印加する電圧を、少なくとも、表示画素電極に最大の映像信号電圧を印加したときの、その電圧から光リーケ電流による電圧低下分だけ低い電圧とすることで、ダミー画素領域内の液晶分子の立ち上がりを表示画素領域内での液晶分子の立ち上がり以下の状態にでき、ダミー画素領域におけるリバースツイストドメインの発生を防ぐ。

## 【0037】

また、ダミー画素電極に印加する電圧を、連続するフレーム内のうちで、ある一部のフレームでは表示画素電極に印加する映像信号電圧の最小値とし、それ以外のフレームでは前記映像信号電圧の最大値とする。これにより、ダミー画素電極に前記映像信号電圧の最大値を印加したフレームで、リバースツイストドメインが発生したとしても、前記映像信号電圧の最小値を印加するフレームで、発生したリバースツイストドメインを消滅させることができる。

## 【0038】

以上のように本発明は、透過型及び反射型の液晶表示装置に適用可能である。また、本発明のスイッチング素子は、ガラス基板上に形成したTFTばかりではなく、シリコン基板に形成したトランジスタ素子でもよい。ガラス基板上に形成したTFTを用いる場合には、透過及び反射表示を行わせることができる。また、シリコン基板に形成したトランジスタ素子を用いる場合には、反射表示を行わせることができる

## 【発明の効果】

## 【0039】

本発明に係る駆動方法によれば、表示画素領域の駆動中に、ダミー画素領域でリバースツイストドメインが発生する上限電圧値よりも低く、かつ表示画素領域とダミー画素領域との境界部に光り漏れが発生する下限電圧値よりも高い最適電圧を、ダミー画素領域の液晶に印加することにより、リバースツイスト起因による表示不良を防ぐことができ、かつ、表示画素領域とダミー画素領域との境界部の光学特性の乱れを防ぐことができるので、液晶表示装置の高画質化を図ることができる。

## 【発明を実施するための最良の形態】

## 【0040】

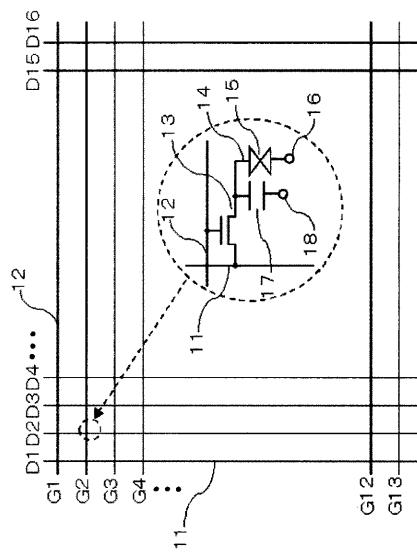

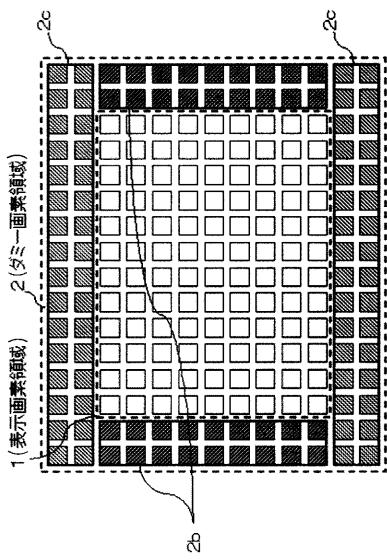

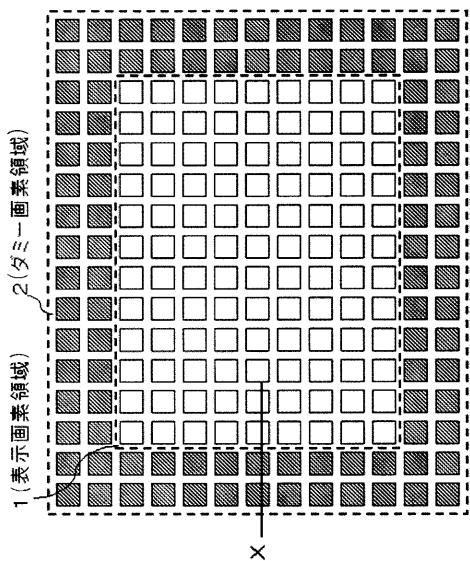

図1は、本発明の第一実施形態における画素領域を示す平面図である。図2は、図1の画素領域を示す等価回路図である。また、特許請求の範囲における「スイッチ素子」、「走査線」及び「信号線」を、それぞれ「TFT」、「ゲート線」及び「データ線」と具体化して言い換える。以下、これらの図面に基づき説明する。

## 【0041】

図示しないが、本実施形態における液晶表示装置は、TFTを用いたアクティブマトリックス型液晶表示装置であり、マトリックス状に複数の画素電極が形成された画素基板と、対向電極が形成された対向基板とが、液晶を介して対向配置された構成となっている。

## 【0042】

図1に示すように、画素領域は、画像表示をするための開口部を持つ画素が配置された表示画素領域1と、開口部を持たない画素が配置されたダミー画素領域2とから構成されている。そして、表示画素領域1の周囲に、ダミー画素領域2が配置される。なお、図1において、ダミー画素領域2は斜線の画素電極群で表す。

## 【0043】

図2に示すように、画素領域は、複数のゲート線12( G1～G13で示す。)が横方向に平行に配置され、複数のデータ線11( D1～D16で示す。)が縦方向に平行に配置される。データ線11とゲート線12の各々の交点付近にはTFT13が設けられ、TFT13のゲート電極はゲート線12と接続され、TFT13のソース電極はデータ線11と接続され、TFT13のドレイン電極は画素電極14と接続されている。画素電極14は、対向電極16との間に液晶容量15を形成するとともに、蓄積容量17に接続されている。蓄積容量17の画素電極14と接続されない側は、蓄積容量線18に接続されている。

## 【0044】

本実施形態での画素は、上記のように構成され、表示画素領域1の画素が開口部を持ちダミー画素領域2の画素が開口部を持たないという点以外、これらの両領域の画素構成は同等である。

## 【0045】

なお、本発明において画素領域の画素数はどのようなものでもよいが、本実施形態では、説明の便宜上、表示画素領域1を縦9画素×横15画素のマトリックスとし、表示画素領域1の周囲のダミー画素領域2として、左右に縦2列ずつ、上下に横2行ずつのダミー画素を配置している。

## 【0046】

次に、本実施形態の動作について説明する。まず、画素電極14への電圧印加動作について図1及び図2を用いて説明する。

## 【0047】

各画素電極14に接続されるTFT13をオンさせる信号をゲート線12に入力すると、オン信号を入力したゲート線12と接続する一行分のTFT13が全て同時にオンする。TFT13のオン時に、表示画像データに基づく映像信号電圧が、データ線11から画素電極14に印加される。印加された映像信号電圧は、TFT13がオフした後も、液晶容量15と蓄積容量17とによって保持される。これらの動作をG1からG13に順次行うことによって、画素領域全体の画素電極14に映像信号電圧が印加され、画素電極14と対向電極16との電圧によって液晶の透過率が変化し、表示画素領域1には文字、画像等が表示され、ダミー画素領域2の液晶も電圧に応じた拳動をする。

## 【0048】

ただし、液晶に直流電圧が長時間にわたって印加され続けると、不純物イオンが画素電極14又は対向電極16に集まるので、液晶に正しい電界を印加できなくなる。この現象を防ぐために、対向電極16に対する画素電極14の電位の極性がフレーム毎に反転するように映像信号電圧を印加する交流駆動が行われる。交流駆動の方法には、画素全部をフレーム毎に極性反転するフレーム反転駆動法と、ゲート線12に沿った画素一行毎に極性反転を行うゲート線反転駆動法と、データ線11に沿った画素一列毎に極性反転を行うデータ線反転駆動法と、縦横に隣接する一画素毎に極性反転を行うドット反転駆動法とがある。本実施形態では、ゲート線反転駆動法を用いている。

## 【0049】

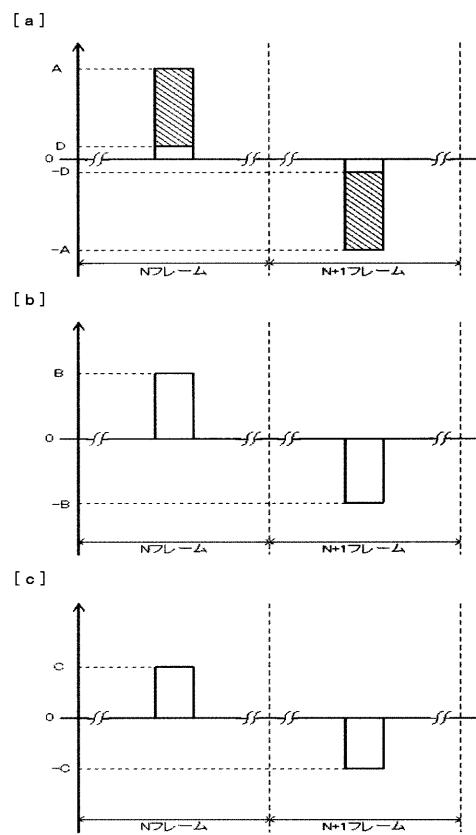

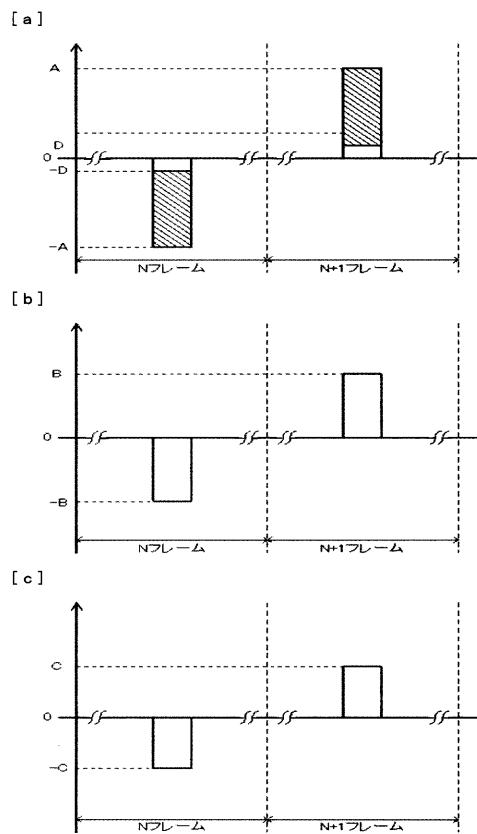

図3は、図1の画素領域の詳細例を示す平面図である。図4及び図5は、本実施形態の動作を示すタイミングチャートである。以下、図2乃至図5を用いて、本実施形態の動作について詳細に説明する。

## 【0050】

図3に示すように、ダミー画素領域2において、表示画素領域1の左右にダミー画素領域2bが配置され、表示画素領域1の上下にダミー画素領域2cが配置されている。

## 【0051】

図4[a]に表示画素領域1の任意の画素電極に印加する映像信号電圧のタイミングチャートを示し、図4[b]にダミー画素領域2bの任意の画素電極に印加する映像信号電圧のタイミングチャートを示し、図4[c]にダミー画素領域2cの任意の画素電極に印

10

20

30

40

50

加する映像信号電圧のタイミングチャートを示す。ここで、図4 [ a ] ~ [ c ] 中の縦軸は電圧であり、0点は対向電極16の電位としている。すなわち、図4の縦軸は、液晶に印加される対向電極16と画素電極14との電圧差及び極性を示している。

#### 【0052】

図4 [ a ] の斜線部は、表示画像に応じて変化する映像信号電圧の範囲を示したものであり、Aは映像信号電圧の最大値を示し、Dはその最小値を示す。また、本実施形態においては、ゲート線反転駆動を用いるため、図4 [ a ] によってタイミングチャートを示した画素の上下に位置する画素のタイミングチャートは、図5 [ a ] となる。

#### 【0053】

図4 [ b ] によると、ダミー画素領域2bの任意の画素電極には電圧Bがフレーム毎に極性を変えて印加される。また、本実施形態においては、ゲート線反転駆動を用いるため、図4 [ b ] によってタイミングチャートを示した画素の上下に位置する画素のタイミングチャートは、図5 [ b ] となる。図3に示す表示画素領域1の左右に配置されたダミー画素領域2bにおいて、リバースツイストドメインが発生するとリバースツイストはゲート線12に沿って伝播するため、表示画素領域1に横筋状の表示不良を発生させる。これを防ぐために、電圧Bは電圧Aよりも小さくしなくてはならない。

#### 【0054】

また、電圧Bが小さすぎると、表示画素領域1とダミー画素領域2bとの境界部に光り漏れを発生させてしまう。したがって、電圧B（最適電圧）は、少なくとも表示画素領域1に映像信号電圧Aを印加したときの光リーケ電流による電圧低下分だけ電圧Aよりも小さく（上限電圧値）、かつ、表示画素領域1の画素全体に映像信号電圧Aが印加されたとき、ダミー画素領域2bとの境界部に光り漏れを認識させない大きさ（下限電圧値）とする。

#### 【0055】

図4 [ c ] によると、ダミー画素領域2cの任意の画素電極には電圧Cがフレーム毎に極性を変えて印加される。また、本実施形態においては、ゲート線反転駆動を用いるため、図4 [ c ] によってタイミングチャートを示した画素の上下に位置する画素のタイミングチャートは、図5 [ c ] となる。図3に示すダミー画素領域2cにおいては、例えリバースツイストドメインが発生しても、リバースツイストはゲート線12に沿って伝播するため、表示画素領域1に及ぶことはない。このため、電圧Cの大きさの上限を決める必要はないが、下限は表示画素領域1の画素全体に映像信号電圧Aが印加されたとき、ダミー画素領域2との境界部に光り漏れを認識させない大きさとする。

#### 【0056】

以上の駆動を行うことにより、ダミー画素領域2bにおけるリバースツイストドメインの発生を防ぐことができ、ゲート線反転駆動時におけるリバースツイスト起因による横筋状の表示不良を防ぐことができ、かつ、表示画素領域1の画素全体に最大の映像信号電圧Aを印加したときにも、ダミー画素領域2との境界部に光り漏れを発生させることのない液晶表示装置を実現できる。

#### 【0057】

換言すると、本実施形態では、ダミー画素領域2の画素に印加する信号電圧を、表示画素領域1に印加する映像信号電圧の最大値より低くし、かつ隣接するダミー画素領域2と表示画素領域1との間で横方向電界による表示不良が生じない程度の電圧とすることにより、ダミー画素領域2内でのリバースツイストドメインの発生を抑制し、リバースツイストによる表示不良を防いでいる。

#### 【0058】

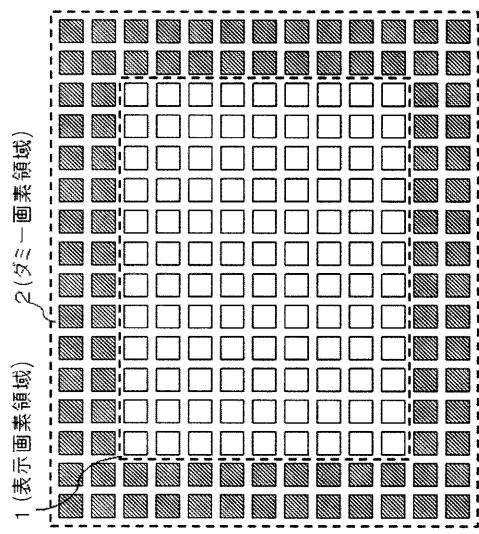

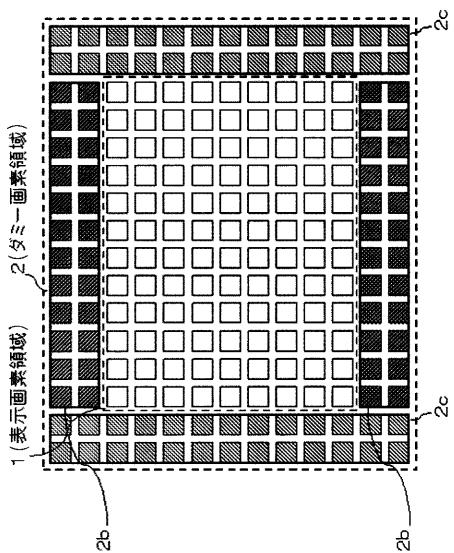

図6は、本発明の第二実施形態における画素領域を示す平面図である。以下、この図面に基づき説明する。ただし、第一実施形態と同じ部分は説明を省略する。

#### 【0059】

本実施形態の液晶表示装置の基本的な構成は、第一実施形態と同じものであるため説明を省く。第一実施形態ではゲート線反転駆動法を用いたが、本発明はゲート線反転駆動法

10

20

30

40

50

に限るものではない。第二実施形態では、データ線反転駆動を用いる。なお、図2によつて説明した画素電極への電圧印加動作については、本実施形態においても同様なので説明を省く。

#### 【0060】

本実施形態においては、図6に示すようにダミー画素領域2において、データ線に沿つて表示画素領域1の上下にダミー画素領域2bが配置され、表示画素領域1の左右にダミー画素領域2cが配置されている。

#### 【0061】

表示画素領域1の任意の画素電極に印加する映像信号電圧のタイミングチャート、ダミー画素領域2bの任意の画素電極に印加する映像信号電圧のタイミングチャート、及び、ダミー画素領域2cの任意の画素電極に印加する映像信号電圧のタイミングチャートは、第一実施形態と同様に、図4[a]～図4[c]によつて示される。ただし、本実施形態においては、データ線反転駆動を用いるため、図4[a]によつてタイミングチャートを示した画素の画面左右方向に位置する画素のタイミングチャートは、図5[a]となり、図4[b]によつてタイミングチャートを示した画素の画面左右方向に位置する画素のタイミングチャートは、図5[b]となり、図4[c]によつてタイミングチャートを示した画素の画面左右方向に位置する画素のタイミングチャートは、図5[c]となる。

#### 【0062】

図6に示す表示画素領域1の上下に配置されたダミー画素領域2bにおいて、リバースツイストドメインが発生するとリバースツイストはデータ線に沿つて伝播するため、表示画素領域に縦筋状の表示不良を発生させる。これを防ぐために、電圧Bは電圧Aよりも小さくしなくてはならない。また、電圧Bが小さすぎると、表示画素領域1とダミー画素領域2との境界部に光り漏れを発生させてしまう。

#### 【0063】

したがつて、電圧B(最適電圧)は、少なくとも表示画素領域1に映像信号電圧Aを印加したときの光リーク電流による電圧低下分だけ電圧Aよりも小さく(上限電圧値)、かつ、表示画素領域1の画素全体に映像信号電圧Aが印加されたとき、ダミー画素領域2との境界部に光り漏れを認識させない大きさ(下限電圧値)とする。

#### 【0064】

また、図6に示すダミー画素領域2cにおいては、例えリバースツイストドメインが発生しても、リバースツイストはデータ線に沿つて伝播するため、表示画素領域1に及ぶことはない。このため、電圧Cの大きさの上限を決める必要はないが、下限は表示画素領域1の画素全体に映像信号電圧Aが印加されたとき、ダミー画素領域2との境界部に光り漏れを認識させない大きさとする。

#### 【0065】

以上の駆動を行うことにより、図6のダミー画素領域2bにおけるリバースツイストドメインの発生を防ぐことができ、データ線反転駆動時におけるリバースツイスト起因による縦筋状の表示不良を防ぐことができ、かつ、表示画素領域1の画素全体に最大の映像信号電圧Aを印加したときにも、ダミー画素領域2との境界部に光り漏れを発生させることのない液晶表示装置を実現できる。

#### 【0066】

次に、本発明の第三実施形態について、図1を用いて説明する。ただし、第一実施形態と同じ部分は説明を省略する。

#### 【0067】

本実施形態の液晶表示装置の基本的な構成は、第一実施形態と同じものであるため説明を省く。第一実施形態ではゲート線反転駆動を用い、第二実施形態ではデータ線反転駆動を用いたが、本実施形態ではドット反転駆動法を用いる。なお、図2によつて説明した画素電極への電圧印加動作については、本実施形態においても同様なので説明を省く。

#### 【0068】

本実施形態において、図1に示すダミー画素領域2の画素電極に印加される映像信号電

10

20

30

40

50

圧は、図1に示す表示画素領域1の画素電極に印加される映像信号電圧の最大値より低くする。図1の表示画素領域1の任意の画素電極に印加する映像信号電圧のタイミングチャートは図4 [a] であり、図1のダミー画素領域2の任意の画素電極に印加する映像信号電圧のタイミングチャートは図4 [b] である。ただし、ドット反転駆動法の場合は、図4 [a] によってタイミングチャートを示した画素の画面上下左右方向に位置する画素のタイミングチャートは、図5 [a] となり、図4 [b] によってタイミングチャートを示した画素の画面上下左右方向に位置する画素のタイミングチャートは、図5 [b] となる。

#### 【0069】

ダミー画素領域2において、リバースツイストドメインの発生を防ぐために、電圧Bは電圧Aよりも小さくしなくてはならない。また、電圧Bが小さすぎると、表示画素領域1とダミー画素領域2との境界部に光り漏れを発生させてしまう。したがって、電圧B（最適電圧）は、少なくとも表示画素領域1に映像信号電圧Aを印加したときの光リーグ電流による電圧低下分だけ電圧Aより小さく（上限電圧値）、かつ、表示画素領域1の画素全体に映像信号電圧Aが印加されたとき、ダミー画素領域2との境界部に光り漏れを認識させない大きさ（下限電圧値）とする。

#### 【0070】

以上の駆動を行うことにより、図1のダミー画素領域2におけるリバースツイストドメインの発生を防ぐことができ、リバースツイスト起因による表示不良を防ぐことができ、かつ、表示画素領域1の画素全体に最大の映像信号電圧Aを印加したときにも、ダミー画素領域2との境界部に光り漏れを発生させることのない液晶表示装置を実現できる。

#### 【0071】

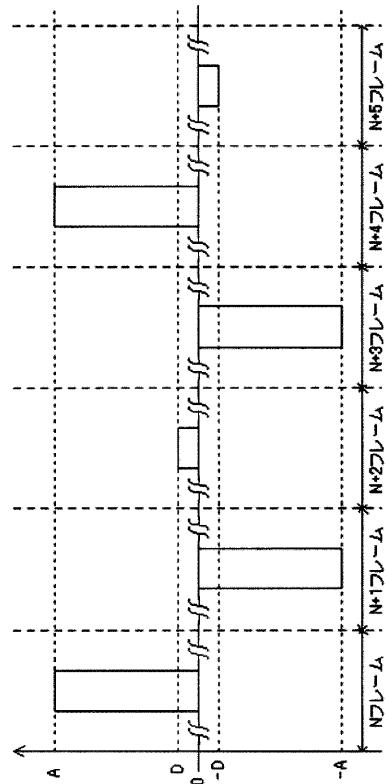

次に、本発明の第四実施形態について、図1及び図7を用いて説明する。

#### 【0072】

本実施形態の液晶表示装置の基本的な構成は、第一実施形態と同じものであるため説明を省く。本実施形態においては、図1に示す表示画素領域1の周囲に配置されたダミー画素領域2の液晶には、連続するn回のフレームの内、m回だけ表示画素領域1の液晶に印加する電圧の最小値を印加し、それ以外のフレームでは、表示画素領域1の液晶に印加する電圧の最大値を印加する。すなわち、n回のフレーム期間以上の時間積分をしたときのダミー画素領域の液晶に印加される実効電圧は、表示画素領域1の液晶に印加する電圧の最大値より小さくなる。

#### 【0073】

図7に、n=3かつm=1としたときのダミー画素領域2の任意の画素電極に印加する映像信号電圧のタイミングチャートを示す。図7の縦軸は電圧であり、0点は対向電極電圧としている。すなわち、図7の縦軸は、液晶に印加される対向電極と画素電極との電圧差と極性を示している。また、図7の電圧Aは、表示画素領域1の液晶に印加する電圧の最大値であり、図7の電圧Dは、表示画素領域1の液晶に印加する電圧の最小値である。

#### 【0074】

本実施形態の駆動方法は、ゲート線反転駆動法を始めとするいかなる交流駆動方法にも適用できる。また、ゲート線反転駆動法においては、本実施形態の駆動方法である連続するn回のフレームの内、m回だけ異なる電圧をダミー画素領域に印加する方法を、図3に示すダミー画素領域2bに適用し、図3のダミー画素領域2cには、連続するn回の全てのフレームにおいて境界部に光り漏れを発生させることのない電圧を印加する駆動方法でもよい。データ線反転駆動においても上記同様に、本実施形態の駆動法を図6に示すダミー画素領域2bに適用し、図6のダミー画素領域2cには、連続するn回の全てのフレームにおいて境界部に光り漏れを発生させることのない電圧を印加する駆動方法でもよい。

#### 【0075】

以上の駆動を行うことで、ダミー画素領域2の液晶に電圧Aが印加されることによって、リバースツイストドメインが発生しても、ダミー画素領域2の液晶に電圧Bが印加されることによって発生したリバースツイストドメインを消すことができる。そのため、例え

10

20

30

40

50

ばゲート線反転駆動を行う際には、ダミー画素領域2で発生したリバースツイストがゲート線に沿って表示画素領域1に伝播する前に、そのリバースツイストドメインを消去することができる。したがって、表示画素領域1内のリバースツイストの発生を防ぐことができ、リバースツイスト起因による表示不良を防ぐことができる。また、表示画素領域1の画素電極に印加する映像信号電圧の最小値とするフレーム数mを減らすことにより、表示画素領域1の画素全体に最大の映像信号電圧Aを印加したときにも、ダミー画素との境界部に光り漏れを発生させることのない液晶表示装置を実現できる。

【0076】

なお、本発明は、言うまでもなく、上記第一乃至第四実施形態に限定されるものではない。また、本発明の利用例として、液晶TV、液晶モニタ、液晶プロジェクタ等が挙げられる。

10

20

30

40

【図面の簡単な説明】

【0077】

【図1】本発明の第一実施形態における画素領域を示す平面図である。

【図2】図1の画素領域を示す等価回路図である。

【図3】図1の画素領域の詳細例を示す平面図である。

【図4】図4[a]は表示画素領域の画素電極に印加する映像信号電圧のタイミングチャートである。図4[b]は第一のダミー画素領域の画素電極に印加する映像信号電圧のタイミングチャートである。図4[c]は第二のダミー画素領域の画素電極に印加する映像信号電圧のタイミングチャートである。

【図5】図5[a]は表示画素領域の他の画素電極に印加する映像信号電圧のタイミングチャートである。図5[b]は第一のダミー画素領域の他の画素電極に印加する映像信号電圧のタイミングチャートである。図5[c]は第二のダミー画素領域の他の画素電極に印加する映像信号電圧のタイミングチャートである。

【図6】本発明の第二実施形態における画素領域を示す平面図である。

【図7】本発明の第四実施形態におけるダミー画素電極に印加する映像信号電圧のタイミングチャートである。

【図8】従来技術における画素領域を示す平面図である。

【図9】図8中の線Xに沿った断面図である。

【符号の説明】

【0078】

1 表示画素領域

2, 2a, 2b ダミー画素領域

11, D1~D16 データ線(信号線)

12, G1~G13 ゲート線(走査線)

13 TFT(スイッチ素子)

14 画素電極

15 液晶容量

16 対向電極

17 蓄積容量

18 蓄積容量線

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

## フロントページの続き

(51)Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

G 0 9 G 3/36

G 0 2 F 1/1343

G 0 2 F 1/1368

F ターム(参考) 5C006 AC21 AF36 AF42 AF59 BB16 BB27 BC11 GA01

5C080 AA10 BB05 DD09 EE32 FF11 JJ01 JJ03 JJ04 JJ06

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)     | 用于驱动液晶显示装置的方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |            |

| 公开(公告)号     | <a href="#">JP2005241778A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2005-09-08 |

| 申请号         | JP2004049104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 申请日     | 2004-02-25 |

| 申请(专利权)人(译) | NEC公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| [标]发明人      | 佐藤哲史<br>閔根裕之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 发明人         | 佐藤 哲史<br>閔根 裕之                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| IPC分类号      | G02F1/1343 G02F1/133 G02F1/1339 G02F1/1368 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号      | G09G3/3648 G09G3/3614 G09G3/3655 G09G2310/0232 G09G2320/0209                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| FI分类号       | G02F1/133.550 G09G3/20.621.A G09G3/20.623.C G09G3/20.660.Q G09G3/20.670.E G09G3/36<br>G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号   | 2H092/GA32 2H092/JA24 2H092/JB02 2H092/JB04 2H092/JB61 2H092/NA04 2H092/PA06 2H093<br>/NA16 2H093/NA32 2H093/NB01 2H093/NC34 2H093/NC35 2H093/NC65 2H093/ND01 2H093/ND15<br>2H093/ND58 2H093/ND60 5C006/AC21 5C006/AF36 5C006/AF42 5C006/AF59 5C006/BB16 5C006<br>/BB27 5C006/BC11 5C006/GA01 5C080/AA10 5C080/BB05 5C080/DD09 5C080/EE32 5C080/FF11<br>5C080/JJ01 5C080/JJ03 5C080/JJ04 5C080/JJ06 2H192/AA24 2H192/DA12 2H192/FA02 2H192<br>/GD61 2H193/ZA04 2H193/ZA08 2H193/ZC02 2H193/ZC04 2H193/ZC07 2H193/ZC13 2H193/ZC16<br>2H193/ZD01 2H193/ZH40 |         |            |

| 代理人(译)      | 高桥 勇                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| 其他公开文献      | JP4419603B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 外部链接        | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

**摘要(译)**

要解决的问题：为了防止由于从设置在显示像素区域1周围的虚拟像素区域2产生的反向扭曲域而导致的显示缺陷。SOLUTION：使施加到虚拟像素区域2的像素的信号电压低于施加到显示像素区域1的视频信号电压的最大值，并且低于相邻的虚拟像素区域2和显示像素区域1之间的视频信号电压的最大值。通过将电压设定为不会发生因横向电场引起的显示不良的程度，可以抑制在虚设像素区域2中产生反向扭曲畴，从而可以防止由于反向扭曲引起的显示不良。[选型图]图1