(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-165273

(P2005-165273A)

(43) 公開日 平成17年6月23日(2005.6.23)

(51) Int.Cl.<sup>7</sup>

**G09G 3/36**

**G02F 1/133**

**G09G 3/20**

**H04N 5/66**

F 1

G09G 3/36

G02F 1/133 505

G09G 3/20 612P

G09G 3/20 621F

G09G 3/20 623B

テーマコード(参考)

2H093

5C006

5C058

5C080

審査請求 未請求 請求項の数 21 O L 外国語出願 (全 24 頁) 最終頁に続く

(21) 出願番号 特願2004-271114 (P2004-271114)

(22) 出願日 平成16年9月17日 (2004.9.17)

(31) 優先権主張番号 60/504060

(32) 優先日 平成15年9月18日 (2003.9.18)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 60/563120

(32) 優先日 平成16年4月15日 (2004.4.15)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 10/909103

(32) 優先日 平成16年7月29日 (2004.7.29)

(33) 優先権主張国 米国(US)

(71) 出願人 502359574

ジェネシス・マイクロチップ・インコーポ

レーテッド

GENESIS MICROCHIP, I

N.C.

アメリカ合衆国 95002 カリフォル

ニア、アルビソ、ゴールド・ストリート

2150

2150 Gold Street, Al

viso, CA 95002 U. S. A

.

(74) 代理人 110000028

特許業務法人明成国際特許事務所

最終頁に続く

(54) 【発明の名称】 LCDパネルの駆動用電子機器の駆動におけるパケット伝送の使用

## (57) 【要約】 (修正有)

【課題】パケットベースの表示方式で、カラムドライバ回路を単純化することにより、デジタル表示プラットフォームを高速化及び高帯域化する。

【解決手段】デジタル表示装置において、選択されたピクセル素子を、カラムドライバに含まれる関連のデータラッ奇によって駆動する、パケットベースの方法が開示される。1ビデオフレーム中の各フレームラインに対し、複数のビデオデータパケットをリンクレートでカラムドライバに直接供給し、ビデオデータパケットに基づいて、適切なビデオデータをライン期間内に複数のデータラッ奇のそれぞれに取り込む。ビデオデータに基づいて、選択されたピクセル素子を駆動する。

【選択図】 図2

Fig. 2

**【特許請求の範囲】****【請求項 1】**

デジタル表示装置において、選択されたピクセル素子を、カラムドライバに含まれる関連のデータラッチによって駆動する、パケットベースの方法であって、

(a) 複数のビデオデータパケットをリンクレートで前記カラムドライバに直接供給する動作と、

(b) ビデオデータパケットに基づいて、適切なビデオデータをライン期間 内に前記複数のデータラッチのそれぞれに取り込む動作と、

(c) 前記ビデオデータに基づいて、選択されたピクセル素子を駆動する動作と、

(d) 1ビデオフレーム中のすべてのフレームラインに対して (a) ~ (c) の動作を繰り返す動作と、を備える方法。 10

**【請求項 2】**

請求項 1 記載の方法であって、さらに、

リンクによって前記デジタル表示装置に連結されたビデオソースにおいて、ビデオ信号を生成する動作と、

前記ビデオ信号に基づいて、パケットベースのビデオストリームを形成する動作と、

前記パケットベースのビデオストリームを、前記リンクレートで前記リンクによって前記デジタル表示装置に伝送する動作と、を備える方法。

**【請求項 3】**

請求項 2 記載の方法であって、

前記デジタル表示装置は、前記リンクに連結された記憶装置であって、前記動作 (a) における供給に先だって、前記ビデオデータパケットの内の選択されたビデオデータパケットを格納するように適切に構成された記憶装置を含む、方法。 20

**【請求項 4】**

請求項 3 記載の方法であって、

前記記憶装置は、1フレームラインに合致する少なくとも一定量のビデオデータパケットを格納するように構成されたラインバッファである、方法。

**【請求項 5】**

請求項 1 記載の方法であって、

前記ビデオデータパケットのそれぞれは、パケットヘッダ及びパケットペイロードを含み、 30

前記パケットヘッダはパケットIDを含み、

前記パケットペイロードは対応するピクセルの駆動に適したビデオデータを含む、方法。 30

**【請求項 6】**

デジタル表示装置であって、

複数のピクセル素子と、

ビデオデータパケットをリンクレートで受信及び配布するように構成されたインターフェースと、

それぞれが、前記インターフェースから配布されたビデオデータパケットを受領し、前記受領されたビデオデータパケットに関するビデオデータを格納し、前記格納されたビデオデータに基づいて前記ピクセル素子の内の選択されたピクセル素子を駆動するように構成された、複数のデータラッチと、を備えるデジタル表示装置。 40

**【請求項 7】**

請求項 6 記載の表示装置であって、

前記複数のデータラッチの内の選択されたデータラッチは、1ビデオフレーム中の1走査ラインに対応するライン期間 内に適切なビデオデータを取り込む、表示装置。

**【請求項 8】**

請求項 7 記載の表示装置であって、

前記ピクセル素子は行と列の形に配列される、表示装置。

50

**【請求項 9】**

請求項 8 記載の表示装置であって、

前記ピクセル素子の列のそれぞれは、表示信号を供給するように構成された 1 つのカラムドライバに関連付けられている、表示装置。

**【請求項 10】**

請求項 9 記載の表示装置であって、

前記カラムドライバのそれぞれは、前記複数のデータラッチの内の一部を含む、表示装置。

**【請求項 11】**

請求項 10 記載の表示装置であって、

前記ビデオデータパケットは、前記リンクレートで前記カラムドライバに直接送られる、表示装置。

**【請求項 12】**

請求項 11 記載の表示装置であって、

走査線の本数に前記ライン期間を乗じた積は、ビデオフレーム期間以下である、表示装置。

**【請求項 13】**

請求項 12 記載の表示装置であって、

前記表示装置は、リンクによってビデオソースに接続され、

前記ビデオソースは、パケットベースのビデオストリームを形成し、前記パケットベースのビデオストリームを前記リンクによって前記リンクレートで前記デジタル表示装置に伝送する、表示装置。

**【請求項 14】**

請求項 13 記載の表示装置であって、

前記デジタル表示装置は、前記リンクに連結された記憶装置であって、前記ビデオデータパケットの内の選択されたビデオデータパケットを格納するように適切に構成された記憶装置を含む、表示装置。

**【請求項 15】**

請求項 14 記載の表示装置であって、

前記記憶装置は、1 フレームラインに合致する少なくとも一定量のビデオデータパケットを格納するように構成されたラインバッファである。表示装置。

**【請求項 16】**

請求項 15 記載の表示装置であって、

前記ビデオデータパケットのそれぞれは、パケットヘッダ及びパケットペイロードを含み、

前記パケットヘッダはパケット ID を含み、

前記パケットペイロードは対応するピクセルの駆動に適したビデオデータを含む、表示装置。

**【請求項 17】**

パケットベースのデジタル表示装置において、選択されたピクセル素子を、カラムドライバに含まれる関連のデータラッチによって駆動するための、コンピュータプログラム製品であって、

複数のビデオデータパケットをリンクレートで前記カラムドライバに直接供給するためのコンピュータコードと、

ビデオデータパケットに基づいて、適切なビデオデータをライン期間 内に前記複数のデータラッチのそれぞれに取り込むためのコンピュータコードと、

前記ビデオデータに基づいて、選択されたピクセル素子を駆動するためのコンピュータコードと、

前記コンピュータコードを格納するためのコンピュータ読み出し可能媒体と、を備えるコンピュータプログラム製品。

10

20

30

40

50

**【請求項 18】**

請求項17記載のコンピュータプログラム製品であって、さらに、リンクによって前記デジタル表示装置に連結されたビデオソースにおいて、ビデオ信号を生成するためのコンピュータコードと、

前記ビデオ信号に基づいて、パケットベースのビデオストリームを形成するためのコンピュータコードと、

前記パケットベースのビデオストリームを、前記リンクレートで前記リンクによって前記デジタル表示装置に伝送するためのコンピュータコードと、を備えるコンピュータプログラム製品。

**【請求項 19】**

請求項18記載のコンピュータプログラム製品であって、

前記デジタル表示装置は、前記リンクに連結された記憶装置であって、前記ビデオデータパケットの内の選択されたビデオデータパケットを格納するように適切に構成された記憶装置を含む、コンピュータプログラム製品。

**【請求項 20】**

請求項19記載のコンピュータプログラム製品であって、

前記記憶装置は、1フレームラインに合致する、少なくとも一定量のビデオデータパケットを格納するように構成されたラインバッファである、コンピュータプログラム製品。

**【請求項 21】**

請求項20記載のコンピュータプログラム製品であって、

前記ビデオデータパケットのそれぞれは、パケットヘッダ及びパケットペイロードを含み、

前記パケットヘッダはパケットIDを含み、

前記パケットペイロードは対応するピクセルを駆動するのに適したビデオデータを含む、コンピュータプログラム製品。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示装置に関する。本発明は、より具体的には、LCDパネルを駆動する駆動用電子機器を使用するための方法及び装置に関する。

**【背景技術】****【0002】**

液晶表示装置(LCD)は、モニタ及びテレビの用途の市場において、ブラウン管(CRT)をベースにしたモニタに取って代わりつつある。これは、一部には、LCDがCRTをベースにした技術と比べていくつかの利点を有するためである。これらの利点には、小型であること(同等のCRTよりも60%小さい)、消費電力が少ないと(50%)、軽量であること(CRTよりも70%軽い)、電磁場が存在しないこと、耐用性に優れることがある。

**【0003】**

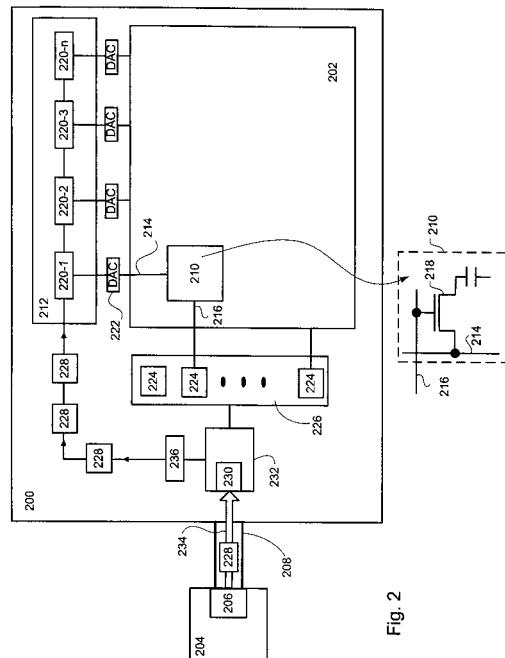

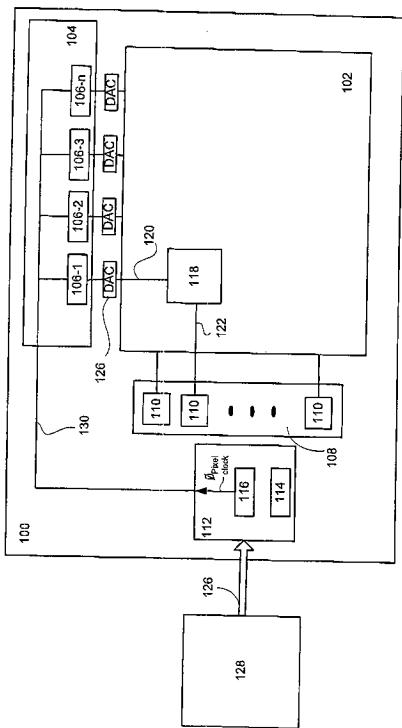

図1は、従来のアクティブマトリックス型液晶表示装置100の一例を示すブロック図である。この液晶表示装置100は、液晶表示パネル102と、画像データの格納に適した複数のデータラッチ106-1~106-nを含むデータ(カラム)ドライバ104と、ゲートドライバ論理回路110を含むゲートドライバ108と、タイミング制御ユニット(TCONとも称される)112と、画像データの格納に適しておりTCON112に含まれた又はTCON112に結合されたメモリ114と、を備える。メモリ114は、ビデオフレーム全体を格納できるフレームメモリの形態を探る場合もあるし、ビデオデータをラインごとに格納できるラインバッファの形態を探る場合もある。いずれの場合も、画像データは、ライン期間と称される期間内に一度に1フレームラインずつラッチ106に伝送され得るようにメモリ114に格納される。図に示されるように、同じくTCON112に含まれた又はTCONに結合されたピクセルクロック発生器116は、リンク

10

20

30

40

50

クロックレートで伝送されたビデオデータを所要のピクセルクロックレートに変換するために使用される。

#### 【0004】

一般に、TCON112は、ビデオ信号（及びほとんどの場合は関連のオーディオ信号）を出力するように適切に構成されたビデオソース128（パソコンやテレビなど）に接続される。動作にあたって、TCON112は、マルチドロップバス130を通して一度に1ピクセルずつビデオデータを送信し、相応してイネーブル化されたデータラッチ106の1つに格納する。例えば、表示パネルが1ラインにつき1024ピクセルを有する場合は、1ラインにつき1024のラッチが存在し（なお、フルカラー表示の場合は、各ピクセルはそれぞれ3つのサブピクセルすなわち赤、青、緑からなるので、合計で $1024 \times 3 = 3072$ のデータラッチが存在する）、それぞれがマルチドロップデータバス130に接続される。TCON112がビデオデータをロードする際には、第1のラッチがラッチイネーブル信号を受信すると共に適切なピクセルデータを格納し、次いで、第2のラッチがラッチイネーブル信号を受信すると共に適切なピクセルデータを格納し、こうして、3072のラッチの全てが一度に1ラッチずつイネーブル化され、適切なピクセルデータを格納し終えるまで、同じことが繰り返される。このように、TCON112は、1フレームラインごとに、ライン期間 内にすべてのピクセルデータを3072のデータラッチのうちの適切なラッチに送信しなければならない。特定の1フレームラインに対応するビデオデータのすべての受信及びラッチが完了すると、そのビデオデータは、表示画像の形成に用いられるLCD配列102に含まれる複数の画像素子118の内の選択された1つを駆動するために用いることが可能になる。10 20

#### 【0005】

したがって、正しいピクセルデータを正しいデータラッチに供給するためには、TCON112は、ハンドシェイクのイネーブル信号を各データラッチ106間に供給し、左端のデータラッチ106-1から右端のデータラッチ106-nに伝搬させることによって、特定の1フレームラインに対応するすべてのビデオデータの格納をライン期間 内に終わらせなければならない。右端のデータラッチ106-nもTCON112によって駆動されなければならないので、ラインごとのピクセル数は、右端の（したがって最も遠い）データラッチ106-nを的確に駆動するためのTCON112の能力によって制限される。大きなマルチドロップバス130に多数（1024のRGB表示の場合は3072）の構成要素が連結された状態は、TCON112にとって、信号の保全性の維持が困難であることを意味する。信号の保全性は表示装置100の正確な動作に不可欠であるので、通常、データレートは低減され、ひいては、表示装置100の解像度を大きく制限する。なぜなら、1フレームラインに対応するデータのすべてが、通常約20マイクロ秒であるライン期間 内に、各データラッチ106に対して伝送されなければならないからである。30

#### 【0006】

この問題の解決方法は、1つには、マルチドロップバス130のサイズを大きくすることであるが、これは、あいにく、バス上のデータ伝送の最適化を困難にするバス容量をも増大させることとなる。他の解決方法（小振幅差動インターフェース信号技術すなわちRSDSなど）は、1本のマルチドロップバスと1ピクセル/クロックとの代わりに複数本のバスと2ピクセル/クロックとを使用する。この解決方法は、TCON112に必要とされる駆動容量を低減させるけれど、TCON駆動回路の複雑度を大幅に増大させる（及びピン数を倍増させる）という不利な結果をもたらす。例えば、24ビットカラーの場合は、RSDSに基づく解決方法は、専用のクロック回線に加えて24本の伝送回線を必要とするので、LCDカラムドライバ104の複雑度を大幅に増大させる。40

#### 【0007】

以上のことから、デジタル表示装置を駆動するための高速で且つ高帯域の方法が求められている。

#### 【発明の開示】

**【 0 0 0 8 】**

液晶表示装置（LCD）などのデジタル表示装置での使用に適した方法、装置、及びシステムとして具体化される表示方式であって、ピクセルレートに無関係であると共に高速で且つ高帯域であるデジタル表示プラットフォームを供給する表示方式が提供される。

**【 0 0 0 9 】**

デジタル表示装置において、選択されたピクセルを、カラムドライバに含まれる関連のデータラッチによって駆動するための、パケットベースの方法が開示される。ビデオフレームの各フレームラインに対し、複数のビデオデータパケットがリンクレートでカラムドライバに直接供給される。次いで、ライン期間 内に、ビデオデータパケットに基づいて、適切なビデオデータが複数のデータラッチのそれぞれに取り込まれる。そして、当該ビデオデータに基づいて、選択されたピクセルが駆動される。

10

**【 0 0 1 0 】**

別の一実施形態では、デジタル表示装置が開示される。このデジタル表示装置は、複数のピクセルと、ビデオデータパケットをリンクレートで受信及び配布するように構成されたインターフェースと、複数のデータラッチと、を備え、各データラッチは、インターフェースから配布されたビデオデータパケットを受信し、受信されたビデオデータパケットに関連するビデオデータを格納し、格納されたビデオデータに基づいて、選択されたピクセルを駆動する。

20

**【 0 0 1 1 】**

さらに別の一実施形態では、パケットベースのデジタル表示装置において、選択されたピクセルを、カラムドライバに含まれる関連のデータラッチによって駆動するための、コンピュータプログラム製品が開示される。このコンピュータプログラム製品は、複数のビデオデータパケットをリンクレートでカラムドライバに直接供給するためのコンピュータコードと、ビデオデータパケットに基づいて、適切なビデオデータをライン期間 内に複数のデータラッチのそれぞれに取り込むためのコンピュータコードと、ビデオデータに基づいて、選択されたピクセルを駆動するためのコンピュータコードと、これらのコンピュータコードを格納するためのコンピュータ読み取り可能媒体と、を備える。

30

**【発明を実施するための最良の形態】****【 0 0 1 2 】**

次に、添付の図面に一例を示された本発明の特定の一実施形態を詳細に説明する。以下では、特定の一実施形態との関連のもとで本発明を説明するが、これは、本発明をその実施形態に限定することを意図しているのではない。反対に、代替形態、変更形態、及び等価形態も、添付の特許請求の範囲に記載された発明の趣旨及び範囲に含まれるものとする。

40

**【 0 0 1 3 】**

LCDパネルなど、従来の構成を有するデジタル表示装置によって画像を表示するためには、タイミングコントローラによって、（1ピクセルクロックのピクセルデータの形態を探る）ビデオデータを最初（通常は左端のデータラッチ）から最後（通常は右端のデータラッチ）まで伝搬させることによって、特定の1フレームラインに対応するビデオデータのすべてをライン期間（通常は約20マイクロ秒）内に格納させなければならない。最後のデータラッチもタイミングコントローラによって駆動されなければならないので、ラインごとのピクセル数は、右端の（したがって最も遠い）データラッチを指定されたライン期間 内に的確に駆動するためのタイミングコントローラの能力によって制限される。表示装置の解像度が増すにつれて（1024のRGB表示の場合は3072のデータラッチ）、タイミングコントローラは、自身に連結されたマルチドロップバスを的確に駆動する能力によって信号の保全性を維持することが次第に困難に且つ不確実になる。信号の保全性は表示装置の正確な動作に不可欠であるので、通常、データレートは低減され、ひいては、表示装置の解像度を大きく制限する。なぜなら、1フレームラインに対応するデータのすべてが、通常約20マイクロ秒であるライン期間 内に、各データラッチに対して伝送されなければならないからである。

50

## 【0014】

この問題の解決方法は、1つには、マルチドロップバスのサイズを大きくすることであるが、これは、あいにく、バス上のデータ伝送の最適化を困難にするバス容量をも増大させることとなる。他の解決方法（小振幅差動インターフェース信号技術すなわちRSDSなど）は、1本のマルチドロップバスと1ピクセル／クロックとの代わりに、複数本のバスと2ピクセル／クロックとを使用する。この解決方法は、タイミングコントローラに必要とされる駆動要件を減少させるけれど、タイミングコントローラ駆動回路の複雑度を大幅に増大させる（及びピン数を倍増させる）という不利な結果をもたらす。例えば、24ビットカラーの場合は、RSDSに基づく解決方法は、専用のクロック回線に加えて24本の伝送回線をデータバスに必要とさせてるので、LCDカラムドライバの複雑度を大幅に増大させる。10

## 【0015】

したがって、液晶表示装置（LCD）などのデジタル表示装置での使用に適した方法、装置、及びシステムとして具体化される、パケットベースの表示方式であって、ピクセルレートをライン期間から切り離した表示方式は、カラムドライバ回路を単純化することによって、高速で且つ高帯域のデジタル表示プラットフォームを提供する。この表示方式は、従来のデジタル表示方式に一般に使用される大きなデータバスを無くすことによって、ポイント・ツー・ポイントの「デイジーチェーン」構成を探ることができる。このような構成では、表示装置の固有水平ライン解像度に一致する数のデータラッチが、互いに直結されている。このように、ビデオデータパケットの転送及び受信は、従来の表示方式で必要とされるようにピクセルデータレートで行われるのではなく、リンクデータレートで行われる。20

## 【0016】

このように、ピクセルクロックの再生成（時間をベースにした回復など）が不要であるため、LCD駆動回路の複雑度を大幅に簡略化することができるうえに、データパケット自身が、これまでデータバス内の個々のデータ線によって供給されていた必要なタイミング及び他の信号を供給するようにエンコードされるので、データバスの大きさを大幅に低減することができる。また、特定の1フレームラインに対応するすべての必要なビデオデータをライン期間内にラッチしなければならない、というのが唯一の制約であるので、ドライバの複雑度やバスの大きさの増大を伴うことなく、表示装置の固有ライン解像度（すなわち水平ピクセルの数）を大幅に増大させることができる。30

## 【0017】

次に、代表的なLCDパネルの観点から本発明を説明する。しかしながら、LCDであれ、プラズマであれ、DLP方式であれ、あらゆるデジタル固定ピクセル表示装置が適しているので、以下の説明においてLCDパネルを用いることは、本発明の範囲及び意図のいずれを限定するものでもない。例えば、2003年12月2日付けで小林によって出願された同時係属出願であって、本明細書に引用によって組み込まれる出願である、米国特許出願第10/726,794号「パケットベースのビデオ表示インターフェース及びその使用方法」に記載されるように、本発明は、任意のパケットベースのビデオ表示インターフェースとの併用に適している。40

## 【0018】

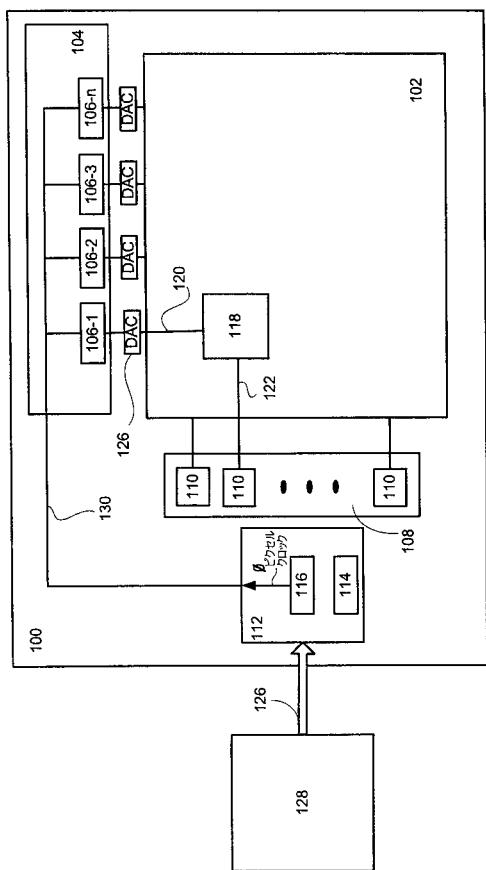

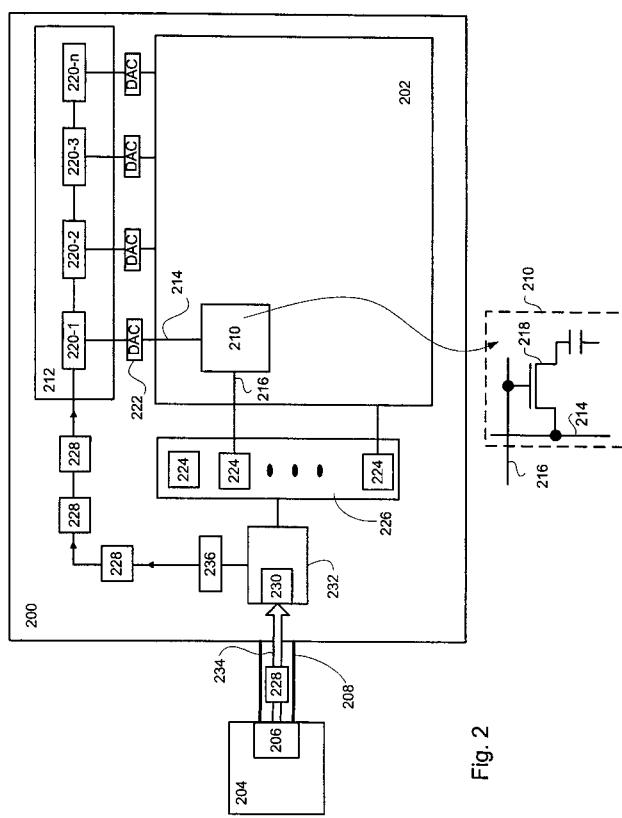

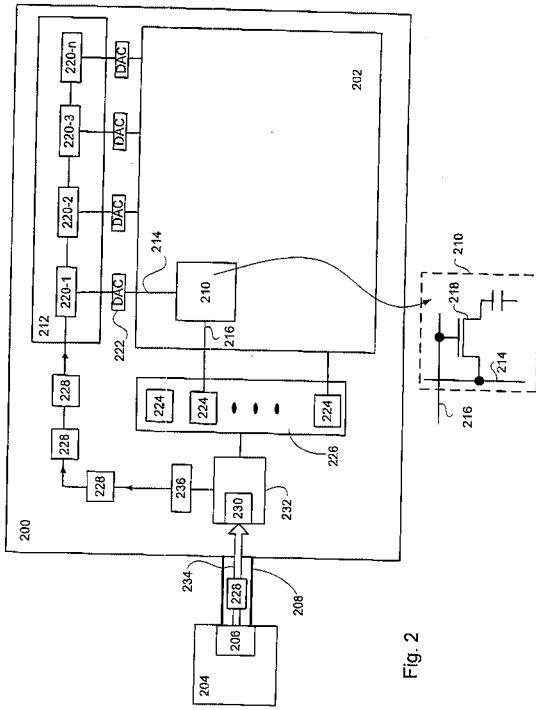

したがって、図2は、本発明の一実施形態にしたがった代表的なデジタル表示システム200を示している。このシステム200は、デジタル表示ユニット202を備え、このデジタル表示ユニット202は、グラフィックスエンジン206を有するビデオソース204にデータリンク208によって結合される。なお、ビデオソース204は、デジタル画像（すなわちスチル若しくはデジタルビデオ）ソース及びアナログ画像（すなわちスチル若しくはアナログビデオ）ソースの一方又は両方を含んでもよい。したがって、ビデオソース204は、複合ビデオ、シリアルデジタル、パラレルデジタル、RGB、コンシューマデジタルビデオのような任意の数およびタイプの周知のフォーマットを有する種々のビデオ信号を供給する。ビデオソース204が、例えばアナログテレビ、スチルカメラ、50

アナログV C R、D V Dプレーヤ、カムコーダ、レーザディスクプレーヤ、テレビチューナ、（衛生D S S又はケーブル信号を伴った）セットトップボックスなど、何らかの形態のアナログビデオソースを含む場合は、ビデオ信号は、アナログビデオ信号であってよい。ビデオソース204は、また、例えばデジタルテレビ（D T V）やデジタルスチルカメラなどのデジタル画像ソースを含んでもよい。デジタルビデオ信号は、S M P T E 274 M - 1995（解像度：1920×1080、プログレッシブ走査またはインターレース走査）やS M P T E 296 M - 1997（解像度：1280×720、プログレッシブ走査）、標準的な480プログレッシブ走査ビデオなど、任意の数およびタイプの周知のデジタルフォーマットを探ってよい。

## 【0019】

10

L C Dパネル202は、複数のデータ線214によってデータドライバ212に接続された行列状の複数の画像素子210（ピクセル）と、複数のゲート線216とを含む。ここで説明される実施形態では、これらの画像素子は、データ線214とゲート線216との間に接続された複数の薄膜トランジスタ（T F T）の形態を探る。動作にあたって、各データラッ奇220は、デジタルデータ信号を、データ線214を通して関連のデジタル／アナログ変換器（D A C）222に出力する。同時に、ゲートドライバ226に含まれる各論理回路224は、所定の走査信号を、水平同期信号と同期したタイミングで順々にゲート線216に出力する。このように、T F T 218は、所定の走査信号がゲート線216に供給されたときにON状態となり、最終的に選択された画像素子210を駆動するためにデータ線214によってD A C 222から供給されたアナログデータ信号を伝送する。

## 【0020】

20

グラフィックスエンジン206がアナログビデオソースを含むとき、またはアナログビデオソースに連結しているとき、グラフィックスエンジン206は、アナログデータをデジタル化してデジタルデータを生成し、次いで、複数のデータパケット228へとパケット化する。ここで説明される実施形態では、各データパケットは、ビデオデータの固有ストリームレートに無関係な、リンクレートL Rと称される伝送速度で、リンク208を通して表示装置202へと伝送される。ただし、リンク208の帯域は、リンク208を通して伝送されるすべてのデータストリームの帯域の合計よりも大きくなければならない。しかしながら、ビデオソースまたは表示装置の種類如何に関わらず、すべてのビデオデータは、リンク208を通して伝送される前に、（必要により）デジタル化され、ほとんどの場合はパケット化される。しかし、場合によっては、パケット化されていない状態でリンク208を通して伝送されてきた任意のビデオデータ及びオーディオデータの一方または両方を、表示ユニット202自身が、表示インターフェース232に含まれる又は表示インターフェースに連結したパケタイザ230を用いてパケット化することによって、表示装置202をあらゆるビデオソースに対して使用可能にすることもある。

30

## 【0021】

40

ここで説明される実施形態では、リンク208の速度すなわちリンクレートは、調整によってリンク条件を補うことのできる複数の論理データチャネル（不図示）を含むように構成することができる。例えば、チャネルあたり2.5 G b p sである場合は、リンク208は、色の階調が18ビット／ピクセルであるS X G A 60 H zをチャネルごとにサポートすることができる。なお、チャネル数の減少は、相互接続の費用を削減だけでなく、携帯機器などの電力依存性の用途にとって重視するべき（と共に望ましい）事柄である消費電力の低減を図ることもできる。しかしながら、チャネル数を4に増やすことによって、リンク208は、60 H zでの色の階調が24ビット／ピクセルであるW Q S X G A（3200×2048の画像解像度）又は60 H zでの色の階調が18ビット／ピクセルであるQ S X G A（2560×2048）を、データ圧縮の必要なしにサポートできるようになる。チャネルあたり1.0 G b p sという最低速度の場合でも、たった2本のチャネル数で、非圧縮H D T V（すなわち、1080 iまたは720 p）データストリームをサポートすることができる。

50

## 【0022】

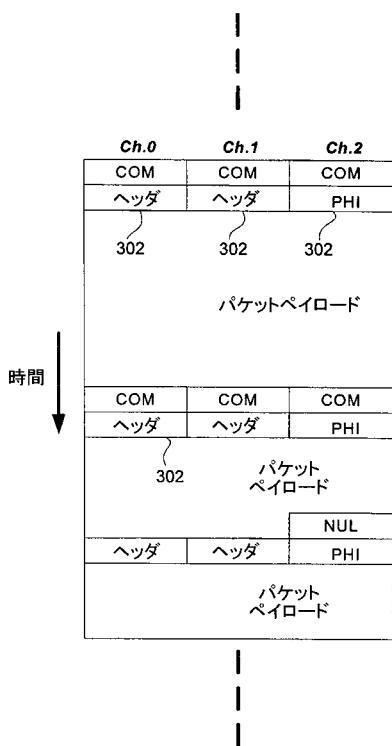

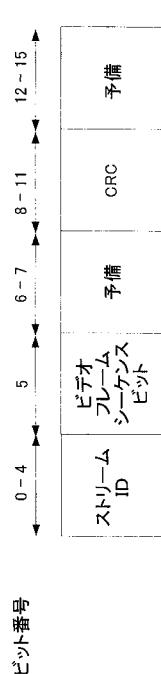

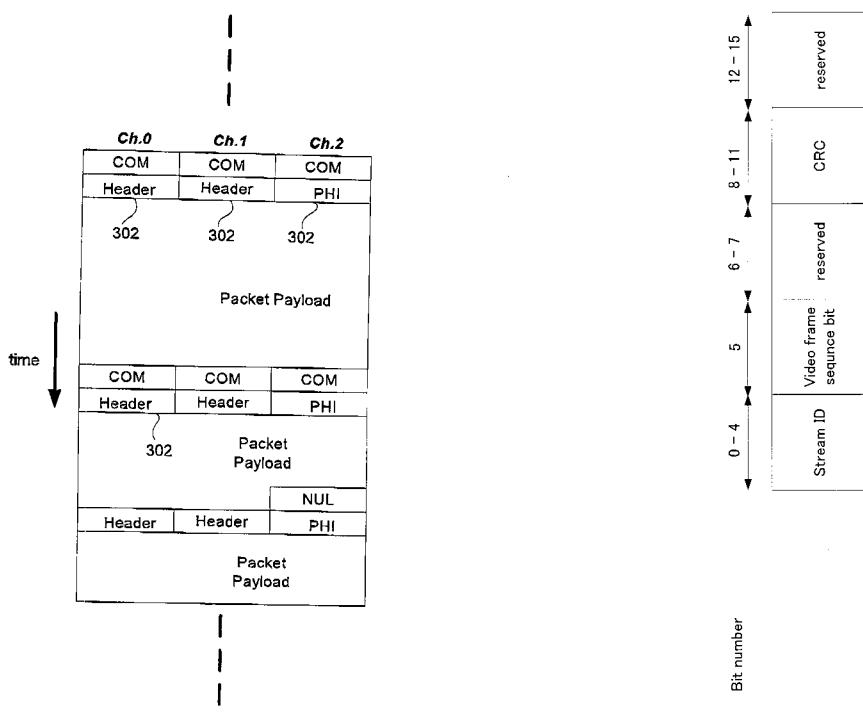

図3Aに示される代表的なデータパケット300は、図3Bに詳細に示された16ビットのデータパケットヘッダ302を含む。データパケットヘッダ302のうち、ビット4～0は、ストリームID(SID)であり、ビット5は、ビデオフレームの境界で「0」から「1」または「1」から「0」に切り替わるフレームカウンタの最下位ビットとして機能するビデオフレームシーケンスであり(非圧縮ビデオストリームの場合にのみ使用される)、ビット7,6は、予備であり、ビット8～10は、先の8ビットのエラーチェックを行う4ビットCRC(CRC)である。

## 【0023】

ビデオデータを伝送するために、ビデオソース204は、表示インターフェース230による受信及び処理を経ることになる複数のデータパケット228を含むデータストリーム234を形成する。ここで説明される実施形態では、データパケット228は、次いで、カラムドライバ212に含まれるデータラッチ220に直接転送される。このとき、データパケット228は、ビデオフレームの特定の1フレームラインnを表示するために使用されるすべてのビデオデータ(ピクセルデータの形態を探る)が、ライン期間内にデータラッチ220に供給されるように転送される。そのため、データドライバ212は、各データラッチ220に適切なピクセルデータが格納された時点で、LCD配列202の中の適切なTFT218を駆動する。

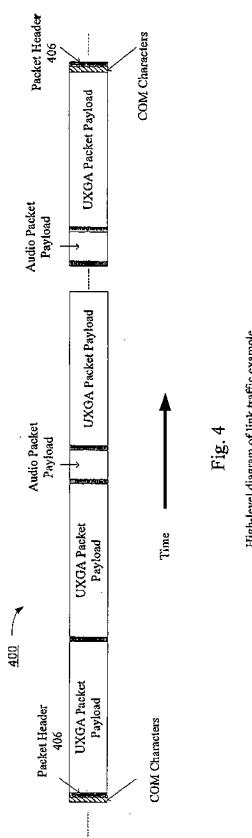

## 【0024】

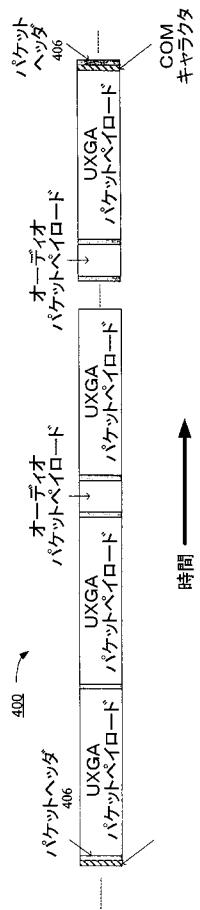

図4は、リンク208によって伝送されるデータストリーム400の詳細図であって、複数のビデオデータパケット402及び複数のオーディオデータパケット404を多重化して得られた1本のデータストリーム400からなる。この例では、ビデオデータパケット402は、オーディオパケット404の形態を探る関連のオーディオ(ストリームID=2)を伴った、UXGAグラフィックスの1280×720ピクセルのビデオ(ストリームID=1)に一致している。この例では、各フレームラインが少なくとも1280ピクセル(または3840サブピクセル)からなるので、ビデオデータの各フレームラインをライン期間内に格納するためには、3840個のデータラッチが必要である。例えば、一実施形態では、データストリーム400が表示インターフェース230によって受信されると、(対応するパケットヘッダ406に定義された)3840個のデータパケットを含む1グループが、フレームメモリ及びラインバッファのいずれの形態を探ることも可能であるメモリ236内に格納される。ただし、厳密なパイプライン方式が望ましい場合は、メモリ236を迂回する或いは全く無くすることも可能である。パイプライン方式では、ビデオソース204は、必要な制御信号を供給することによって、データパケットを適切に構成する。

## 【0025】

メモリ236を含む上記の実施形態に戻り、3840個のデータパケットがすべてきちんとメモリ236に格納され、それらの詳細が明らかにされると、格納されたデータパケットは、次いで、LCDカラムコントローラ212に転送される。1ライン期間内に、適切なビデオデータ(またはオーディオデータ)を適切なデータラッチに格納できるようになるため、データパケット228は、次いで、適切なデータラッチ220へとポイント・ツー・ポイント方式(ディジーチェーン方式とも称される)で転送され、転送先の各データラッチにおいて非パケット化される。ビデオデータは、この時点で既に、対応するDAC222による処理後に表示装置202内の適切な画像素子210を駆動する用意が整っている。このようにすれば、約24本の回線を必要とした従来のLCD駆動方式と異なり、たった2本の回線だけで、適切なビデオデータをデータラッチ220に供給することが可能になる。

## 【0026】

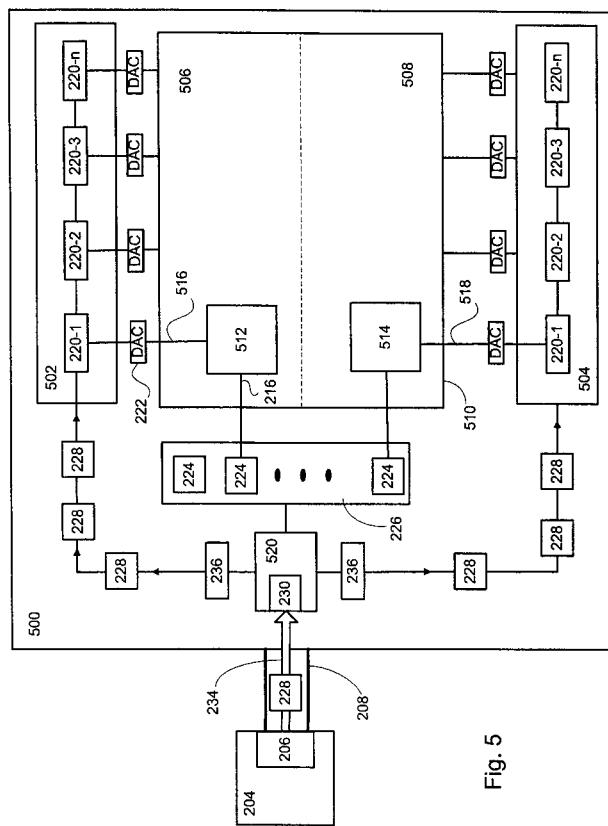

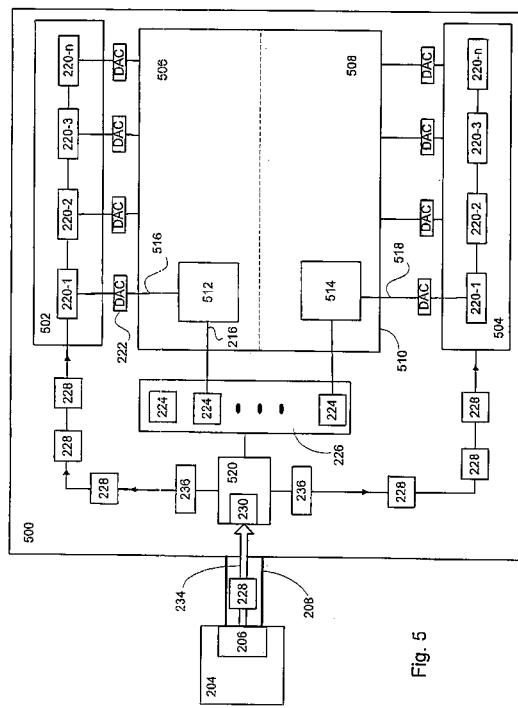

図5は、本発明の一実施形態を示している。デジタル表示装置500は、2つのカラムドライバ502,504を含み、各カラムドライバは、分割された表示装置510の対応部分506,508の中のピクセルを駆動するためにそれぞれ使用される。表示装置510

10

20

30

40

50

0を部分506, 508に分割すると、各カラムドライバ502, 504は、対応する画像素子512, 514（例えば前述のTFT218を含み得る）の駆動に必要な電流が大幅に少なくてすむ。これは、データ線516, 518の長さの短縮に起因する寄生容量が、表示装置510の分割に応じて減少するためである。

【0027】

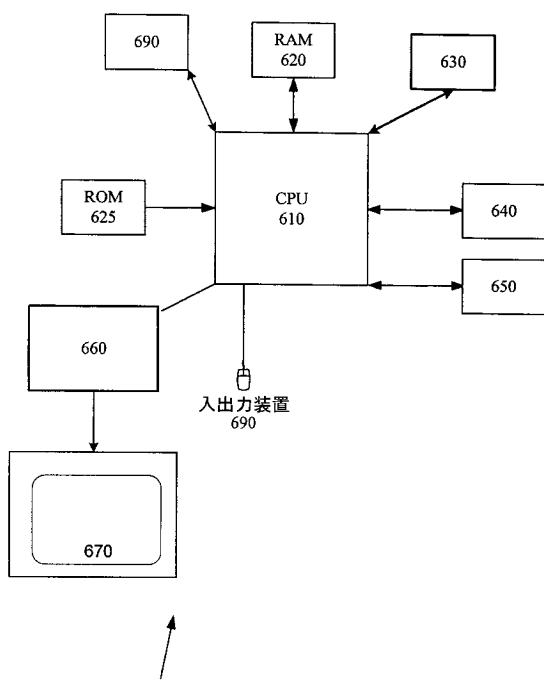

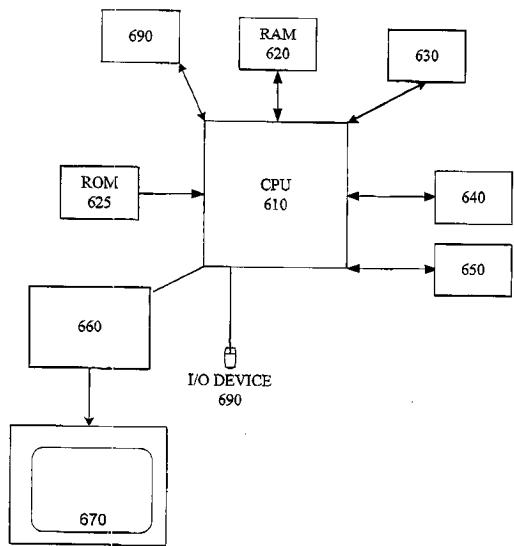

図6は、本発明の具体化に使用できるシステム600を示している。システム600は、本発明の中で具体化できるグラフィックスシステムの一例に過ぎない。システム600は、中央演算処理装置(CPU)610と、ランダムアクセスメモリ(RAM)620と、読み出し専用メモリ(ROM)625と、1つ以上の周辺装置630と、グラフィックスコントローラ660と、一次記憶装置640, 650と、デジタル表示装置670と、を備える。CPU610は、また、1つ以上の入出力装置690にも連結されている。グラフィックスコントローラ660は、画像データ及びそれに対応する参照信号を生成し、両者をデジタル表示装置670に供給する。画像データは、例えば、CPU610または外付けの回路から受領したピクセルデータに基づいて生成することができる。

10

20

【0028】

以上では、本発明の実施形態をいくつか説明したが、本発明は、本発明の範囲及び趣旨から逸脱することなしに、様々な形態で実現することが可能である。上述した実施形態は、例示を目的としたものであって限定を目的としたものではなく、したがって、本発明は、上述の詳細に限定されることはなく、添付した特許請求の範囲及びそれらのあらゆる等価形態の範囲で変更することが可能である。

20

【0029】

以上では、本発明の好ましい実施形態を取り上げて説明したが、そのほかにも、本発明の範囲内で各種の代替形態、置換形態、及び等価形態が可能である。なお、本発明のプロセス及び装置は、多くの方法によって具体化することができる。したがって、本発明は、本発明の真の趣旨及び範囲に含まれる、このようなあらゆる代替形態、置換形態、及び等価形態を含むものと解釈される。

30

【図面の簡単な説明】

【0030】

【図1】従来のアクティブマトリックス型液晶表示装置の一例を示したブロック図である。

【図2】本発明の一実施形態にしたがった代表的なデジタル表示システムの図である。

【図3A】本発明の一実施形態にしたがった代表的なデータパケットの図である。

【図3B】図3Aに示されたデータパケットの詳細な図である。

【図4】本発明の一実施形態にしたがったリンクを通じて伝送されるデータストリームの詳細図である。

【図5】本発明の具体化に使用できるシステムの図である。

【図6】本発明の具体化に使用できるシステムの図である。

【図1】

Fig. 1

従来技術

【図2】

Fig. 2

【図3A】

Fig. 3A

メインリンクのパケット形式

【図3B】

Fig. 3B

【図4】

Fig. 4

リンクトラフィックの詳細例

【図5】

Fig. 5

【図6】

Fig. 6

## フロントページの続き

(51)Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 3 G |

| G 0 9 G | 3/20 | 6 3 1 B |

| G 0 9 G | 3/20 | 6 3 2 F |

| G 0 9 G | 3/20 | 6 3 3 G |

| G 0 9 G | 3/20 | 6 3 3 H |

| H 0 4 N | 5/66 | 1 0 2 B |

(72)発明者 小林 修

アメリカ合衆国 カリフォルニア州 9 4 0 2 4 ロス・アルトス, フォーレン・リーフ・レーン,

1 4 6 4

F ターム(参考) 2H093 NA16 NC12 NC15 NC16 NC22 NC26 NC34 ND34

5C006 AA01 AF03 AF04 AF44 AF45 AF51 AF52 AF53 AF61 AF71

BC11 BC16 BF02 BF03 BF14 BF15 BF16 BF24 EB04 FA13

5C058 AA08 AB02 BA04 BB05 BB12 BB13

5C080 AA05 AA06 AA10 BB05 DD07 DD08 DD28 GG12 JJ02 JJ05

## 【外国語明細書】

## 1. TITLE OF THE INVENTION

USING PACKET TRANSFER FOR DRIVING LCD PANEL DRIVER ELECTRONICS

## 2. DETAILED DESCRIPTION OF THE INVENTION

BACKGROUNDI. Field of the Invention

[0001] The invention relates to display devices. More specifically, the invention describes a method and apparatus for using driving LCD panel drive electronics.

OVERVIEW

[0002] Liquid Crystal Displays (LCDs) have begun to supersede Cathode Ray Tube (CRT) based monitors in the monitor and television applications markets due in part to the fact that LCDs have several advantages compared to CRT based technology. These advantages include smaller size (60% less than comparable CRTs), lower power consumption (50%), lighter weight (70% less than CRT), no electromagnetic fields, and longer service life.

[0003] FIG. 1 is a block diagram showing an example of a conventional active matrix liquid crystal display device 100 that includes a liquid crystal display panel 102, a data (or a column) driver 104 that includes a number of data latches 106-1 through 106-n suitable for storing image data, a gate driver 108 that includes gate driver logic circuits 110, a timing controller unit (also referred to as a TCON) 112, and a memory 114 suitable for storing image data included in or coupled to the TCON 112. In some cases, the memory 114 takes the form of a frame memory capable of storing an entire video frame or in other cases, the memory 114 takes the form of a line buffer capable of storing a single line of video data. In either case, the image data is stored in the memory 114 in such a way as to be available to be transferred to the latches 106 one frame line at a time within a period of time referred to as a line period . As shown, a pixel clock generator unit 116 also included in or coupled to the TCON 112 is used to convert video data delivered at a link clock rate to the required pixel clock rate.

[0004] Typically, the TCON 112 is connected to a video source 128 (such as a personal computer, TV or other such device) suitably arranged to output a video signal (and, in most cases, an associated audio signal). During operation, the TCON 112 sends video data one pixel at a time by way of a multidrop bus 130 to be stored in a correspondingly enabled one of the data latches 106. For example, if the display panel has 1024 pixels per line then there are 1024 latches per line (it should be noted that in the case of a full color display, each pixel is formed of 3 subpixels, Red, Green, and Blue and therefore there are a total of  $1024 \times 3 = 3072$  data latches) each of which is connected to the multidrop data bus 130. When the TCON 112 is loading the video data, a first latch receives a latch enable signal and stores the appropriate pixel data, after which a second latch receives the latch enable signal and stores the appropriate pixel data and so on until all 3072 latches have been enabled and stored the appropriate pixel data one at a time. In this way, for each frame line, the TCON 112 must send the all pixel data to the appropriate one of the 3072 data latches within the line period . Once all the video data for a particular frame line has been received and latched, the video data is then available to drive selected ones of a number of picture elements 118 included in the LCD array 102 used to form the displa

yed image.

[0005] Therefore, in order for the TCON 112 to provide the correct pixel data to the correct data latch, the TCON 112 must provide a handshake enable signal between each data latch 106 that must propagate from the leftmost data latch 106-1 to the rightmost data latch 106-n in such a way that all video data for a particular frame line is stored with the line period . Since even the rightmost data latch 106-n must be driven by the TCON 112, the number of pixels per line is limited by the ability of the TCON 112 to adequately drive the rightmost (and therefore most distant) data latch 106-n. The large number of components (3072 in the case of an 1024 RGB display) coupled to the large multidrop bus 130 presents a severe challenge to the TCON 112 to preserve signal integrity. Since signal integrity is crucial to the proper operation of the display 100, the data rate is typically reduced thereby severely limiting the resolution of the display 100 since all data for a single frame line must be transferred to all data latches 106 within a single line period which is typically about 20 microseconds.

[0006] One approach to solving this problem is to increase the size of the multidrop bus 130 that unfortunately also increases the line capacitance making it difficult to optimize the transmission of the data on the bus. Other approaches (such as reduced swing differential signaling or RSDS) use multiple busses with 2 pixels per clock instead of a single multidrop bus and a single pixel per clock. Although this approach reduces the drive capability required for the TCON 112, it has the unfortunate result of substantially increasing the complexity of the TCON driving circuitry (as well as doubling the number of pins). For example, in the case of 24 bit color, the RSDS approach would require 24 transmission lines in addition to a dedicated clock line greatly increasing the complexity of the LCD column driver 104.

[0007] Therefore a high speed, high bandwidth approach to driving an digital display is needed.

#### SUMMARY OF THE INVENTION

[0008] What is provided is a display architecture embodied as a method, apparatus, and system suitable for implementation with digital displays, such as liquid crystal displays (LCDs), that is independent of pixel rate and provides a high speed, high bandwidth digital display platform.

[0009] In a digital display device, a packet based method of driving selected pixel elements by way of associated data latches included in a column driver is disclosed. For each frame lines in a video frame, a number of video data packets are provided directly to the column driver at a link rate and each of the number of data latches are populated with appropriate video data based upon video data packets within a line period . Selected pixel elements are driven based upon the video data.

[0010] In another embodiment, a digital display device is disclosed that includes a number of pixel elements, an interface arranged to receive and distribute video data packets at a link rate, and a number of data latches each of which are arranged to receive a distributed video data packet from the interface, store video data associated with the received video data packet, and drive selected ones of the pixel elements based upon stored video data.

[0011] In yet another embodiment, computer program product for driving selected pixel elements by way of associated data latches included in a column driver

In a packet based digital display device is disclosed. Computer code for providing a number of video data packets directly to the column driver at a link rate, computer code for populating each of the number of data latches with appropriate video data based upon video data packets within a line period , computer code for driving selected pixel elements based upon the video data, and computer readable medium for storing the computer code

#### DETAILED DESCRIPTION OF SELECTED EMBODIMENTS

[0012] Reference will now be made in detail to a particular embodiment of the invention an example of which is illustrated in the accompanying drawings. While the invention will be described in conjunction with the particular embodiment , it will be understood that it is not intended to limit the invention to the described embodiment. To the contrary, it is intended to cover alternatives, modifications, and equivalents as may be included within the spirit and scope of the invention as defined by the appended claims.

[0013] In order for conventionally configured digital display devices, such as LCD panels, to display images, a timing controller must propagate video data (in the form of pixel data at a pixel clock) from a first (typically a leftmost data latch) to a last (typically a rightmost data latch) in such a way that all video data for a particular frame line is stored with a single line period (usually about 20 microseconds). Since even the last data latch must be driven by the timing controller, the number of pixels per line is limited by the ability of the timing controller to adequately drive the rightmost (and therefore most distant) data latch within the specified line period . As the resolution of a display increases (3072 data latches in the case of a 1024 RGB display), the ability of the timing controller to adequately drive a multidrop bus coupled thereto becomes progressively more difficult and problematic to preserve signal integrity. Since signal integrity is crucial to the proper operation of the display, the data rate is typically reduced thereby severely limiting the resolution of the display since all data for a single frame line must be transferred to all data latches within a single line period which is typically about 20 microseconds .

[0014] One approach to solving this problem is to increase the size of the multidrop bus that unfortunately also has the effect of increasing the line capacitance making it difficult to optimize the transmission of the data on the bus. Other approaches (such as Reduced Swing Differential Signaling, or RSDS) use multiple busses with 2 pixels per clock instead of a single multidrop bus and a single pixel per clock. Although this approach reduces the drive requirements for the timing controller, it has the unfortunate result of substantially increasing the complexity of the timing controller driving circuitry (as well as doubling the number of pins). For example, in the case of 24 bit color, the RSDS approach requires that the data bus have at least 24 transmission lines in addition to a dedicated clock line thereby greatly increasing the complexity of the LCD column driver.

[0015] Accordingly, a packet based display architecture embodied as a method, apparatus, and system suitable for implementation with digital displays, such as liquid crystal displays (LCDs), that decouples the pixel rate from the line period , simplifies the column driver circuitry provides a high speed, high bandwidth digital display platform. The display architecture does away with the large data bus commonly used with conventional digital display architecture in favo

r of a point to point "daisy chain" configuration. In this configuration, a number of data latches consistent with a native horizontal line resolution of the display are directly connected to each other. In this way, the video data packets are transported and received at a link data rate and not as required in conventional display architectures, at the pixel data rate.

[0016] In this way, the complexity of the LCD driver circuitry is greatly simplified since there is no requirement for pixel clock regeneration (such as time based recovery) and the size of the data bus is greatly reduced since the data packets themselves can be encoded to provide necessary timing and other signals heretofore provided by separate data lines in the data bus. In addition, the native line resolution of the display (i.e., the number of horizontal pixels) can be substantially increased without the concomitant increase in driver complexity or bus size since the only constraint is that all necessary video data be latched for a particular frame line within the line period .

[0017] The invention will now be described in terms of a representative LCD panel. However, it should be noted that any digital fixed pixel display, be it LCD, plasma, DLP based, is also suitable and therefore the use of an LCD panel in the following description should not be considered to limit either the scope or the intent of the invention. It should be noted that the invention is also well suited to be used in conjunction with any packet based video display interface such as described in copending U.S. Patent Application Serial No. 10/726,794 entitled "Packet Based Video Display Interface and methods of use thereof" by Kobayashi filed December 3, 2003 and incorporated herein by reference for all purposes.

[0018] Accordingly, Fig. 2 shows an exemplary digital display system 200 in accordance with an embodiment of the invention. The system 200 includes a digital display unit 202 coupled to a video source 204 having a graphics engine 206 by way of a data link 208. It should be noted that the video source 204 can include either or both a digital image (i.e. still or digital video) source and/or an analog image (i.e., still or analog video) source. Accordingly, the video source 204 provides various video signals that can have any number and type of well-known formats, such as composite video, serial digital, parallel digital, RGB, or consumer digital video. The video signal can be an analog video signal provided the source 204 includes some form of an analog video source such as for example, an analog television, still camera, analog VCR, DVD player, camcorder, laser disk player, TV tuner, set top box (with satellite DSS or cable signal) and the like. The source 204 can also include a digital image source such as for example a digital television (DTV), digital still camera, and the like. The digital video signal can be any number and type of well known digital formats such as, SMPTE 274M-1995 (1920 x 1080 resolution, progressive or interlaced scan), SMPTE 296M-1997 (1280 x 720 resolution, progressive scan), as well as standard 480 progressive scan video.

[0019] The LCD panel 202 includes a number of picture elements 210 (pixels) that are arranged in a matrix connected to a data driver 212 by way of a plurality of data lines 214 and a plurality of gate lines 216. In the described embodiment, these picture elements take the form of a plurality of thin film transistors (TFTs) 218 that are connected between the data lines 214 and the gate lines 216. During operation, each of data latch 220 outputs digital data signals to an associated digital to analog converter (DAC) 222 by way of the data lines 214. Concurrently, each of logic circuit 224 included in a gate driver 226 outputs a

predetermined scanning signal to the gate lines 216 in sequence at timings which are in sync with a horizontal synchronizing signal. In this way, the TFTs 218 are turned ON when the predetermined scanning signal is supplied to the gate lines 214 to transmit the analog data signals supplied by the DACs 222 by way of the data lines 214 that ultimately drive selected ones of the picture elements 210.

[0020] When the graphics engine 206 includes or is coupled to an analog video source, the graphics engine 206 digitizes the analog data to form digital data that is then packetized into a number of data packets 228. In the described embodiment, each of the data packets are transmitted to the display 202 by way of the link 208 at a transmission rate referred to as a link rate LR that is independent of the native stream rates of the video data. It should be noted, however, that the bandwidth of the link 208 must be greater than the aggregate bandwidth of all data stream(s) being transmitted over the link 208. Regardless of the type of video source or display, however, all video data are digitized (if necessary) and, in most cases, packetized prior to transmission over the link 208. In some cases, however, using a packetizer 230 included in or coupled to a display interface 232, the display unit 202 itself will packetize any video and/or audio data transmitted over the link 208 in an unpacketized form thereby enabling the use of the display 202 with all video sources.

[0021] In the described embodiment, the speed, or link rate, of the link 208 can be configured to include a number of logical data channels (not shown) that can be adjusted to compensate for link conditions. For example, at 2.5 Gbps per channel, the link 208 can support SXGA 60Hz with a color depth of 18 bits per pixel over a single channel. It should be noted that a reduction in the number of channels reduces not only the cost of interconnect, but also reduces the power consumption which is an important consideration (and desirable) for power sensitive applications such as portable devices and the like. However, by increasing the number of channels to four, the link 208 can support WQSXGA (3200 x 2048 image resolution) with a color depth of 24-bits per pixel at 60Hz. or QSXGA (2560 x 2048) with a color depth of 18-bits per pixel at 60Hz, without data compression. Even at the lowest rate of 1.0 Gbps per channel, only two channels are required to support an uncompressed HDTV (i.e., 1080i or 720p) data stream.

[0022] A representative data packet 300 is shown in Fig. 3A includes a data packet header 302 shown in more detail in Fig. 3B having 16 bits where bits 4-0 are the Stream ID (SID), bit 5 is a video frame sequence bit which acts as the least significant bit of the frame counter which toggles from "0" to "1" or from "1" to "0" at the video frame boundary (used only for uncompressed video stream).

Bits 7 and 6 are reserved whereas bits 8 through 10 are a 4-bit CRC (CRC) that checks errors for the previous eight bits.

[0023] In order to transmit the video data, the video source 204 forms a data stream 234 that includes a number of the data packets 228 which are then received and processed by the display interface 230. In the described embodiment, the data packets 228 are then forwarded to directly to the data latches 220 included in the column driver 212 in such a way that all the video data (in the form of pixel data) used for the display of a particular frame line n of the video frame is provided to the data latches 220 within a line period . Therefore, once each data latch 220 has appropriate pixel data stored therein, the data driver 212 drive appropriate ones of the TFTs 218 in the LCD array 202.

[0024] Fig. 4 shows a high-level diagram of a data stream 400 for transmissio

n over the link 208 formed of a number of video data packets 402 and audio data packets 404 multiplexed into the single data stream 400. In this example the video data packets 402 are consistent with UXGA graphics 1280x720p video (Stream I D = 1) having an associated audio in the form of the audio packets 404 (Stream I D = 2). In this example, each frame line is formed of at least 1280 pixels (or 3840 sub-pixels) therefore requiring 3840 data latches be used to store a single frame line of video data within the line period . For example, in one embodiment, when the data stream 400 is received at the display interface 230, a group of 3840 data packets (as defined by corresponding packet headers 406) are stored in a memory 236 that can be either a frame memory or a line buffer. It should also be noted, however, that the memory 236 can be bypassed or be absent although if a strictly pipelined architecture is desired. In the pipelined architecture, the video source 204 would provide the necessary control signals and configure the data packets appropriately.

[0025] Returning to the described embodiment that includes the memory 236, once all 3840 data packets are properly stored in the memory 236 and accounted for , the stored data packets are then forwarded to the LCD column controller 212. The data packets 228 are then forwarded in a point to point fashion (also referred to as a daisy chain style) to the appropriate ones of the data latches 220 at which point each is depacketized such that the appropriate video data (or audio data) is stored in the appropriate data latch within one line period . At this point, the video data is ready to drive the appropriate ones of the pixel elements 210 located in the display 202 after processing by corresponding DACs 222.

In this way, the number of lines required to provide the appropriate video data to the data latches 220 can be as low as 2 as opposed to approximately 24 in conventional LCD driver architectures.

[0026] FIG. 5 shows an embodiment of the invention whereby a digital display unit 500 includes two column drivers 502 and 504 each of which is used to drive pixels in corresponding portions 506 and 508 of a partitioned display 510. By dividing the display 510 into the portions 506 and 508, each of the column drivers 502 and 504 require substantially less current to drive the corresponding picture elements 512 and 514 (which may include, for example, TFTs 218 described earlier) since the parasitic capacitance due to the reduced length of the data lines 516 and 518 are commensurably reduced.

[0027] FIG. 6 illustrates a system 600 that can be used to implement the invention. The system 600 is only an example of a graphics system in which the present invention can be implemented. System 600 includes central processing unit (CPU) 610, random access memory (RAM) 620, read only memory (ROM) 625, one or more peripherals 630, graphics controller 660, primary storage devices 640 and 650, and digital display unit 670. CPU 610 is also coupled to one or more input/output devices 690. Graphics controller 660 generates image data and corresponding reference signals, and provides both to digital display unit 670. The image data can be generated, for example, based on pixel data received from CPU 610 or from an external circuitry.

[0028] Although only a few embodiments of the present invention have been described, it should be understood that the present invention may be embodied in many other specific forms without departing from the spirit or the scope of the present invention. The present examples are to be considered as illustrative and not restrictive, and the invention is not to be limited to the details given herein, but may be modified within the scope of the appended claims along with thei

r full scope of equivalents.

[0029] While this invention has been described in terms of a preferred embodiment, there are alterations, permutations, and equivalents that fall within the scope of this invention. It should also be noted that there are many alternative ways of implementing both the process and apparatus of the present invention.

It is therefore intended that the invention be interpreted as including all such alterations, permutations, and equivalents as fall within the true spirit and scope of the present invention.

### 3. BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a block diagram showing an example of a conventional active matrix liquid crystal display device.

FIG. 2 shows an exemplary digital display system in accordance with an embodiment of the invention.

FIG. 3A shows a representative data packet in accordance with an embodiment of the invention.

FIG. 3B shows a detailed view of the data packet shown in FIG. 3A.

FIG. 4 shows a high-level diagram of a data stream for transmission over the link in accordance with an embodiment of the invention.

FIG. 5 illustrates a system that can be used to implement the invention.

FIG. 6 illustrates a system 600 that can be used to implement the invention.

1. In a digital display device, a packet based method of driving selected pixel elements by way of associated data latches included in a column driver, comprising:

- (a) providing a number of video data packets directly to the column driver at a link rate;

- (b) populating each of the number of data latches with appropriate video data based upon video data packets within a line period ;

- (c) driving selected pixel elements based upon the video data; and

- (d) repeating (a) - (c) for all frame lines in a video frame.

2. A method as recited in claim 1, further comprising:

generating a video signal at a video source coupled to the digital display device by way of a link;

forming a packet based video stream based upon the video signal; and transmitting the packet based video stream to the digital display device by way of the link at the link rate.

3. A method as recited in claim 2, wherein the digital display device includes a memory device coupled to the link suitably arranged to store selected ones of the video data packets prior to the providing (a).

4. A method as recited in claim 3 wherein the memory device is a line buffer arranged to store at least a quantity of video data packets consistent with a single frame line.

5. A method as recited in claim 1, wherein each of the video data packets includes a packet header and a packet payload, wherein the packet header includes a packet ID and wherein the packet payload includes video data suitable for driving a corresponding pixel.

6. A digital display device, comprising:

a number of pixel elements;

an interface arranged to receive and distribute video data packets at a link rate; and

a number of data latches each of which are arranged to receive a distributed video data packet from the interface, store video data associated with the received video data packet, and drive selected ones of the pixel elements based upon stored video data.

7. A display as recited in claim 6, wherein selected ones of the number of data latches are populated with appropriate video data within a line period corresponding to a scan line in a video frame.

8. A display as recited in claim 7, wherein the pixel elements are arranged in rows and columns.

9. A display as recited in claim 8, wherein each of the columns of pixels are associated with a column driver unit arranged to provide a display signal.

10. A display unit as recited in claim 9, wherein each of the column driver units includes a subset of the number of data latches.

11. A display unit as recited in claim 10, wherein the video data packets are sent directly to the column drivers at the link rate

12. A display unit as recited in claim 11, wherein a number of scan lines times the line period is less than or equal to a video frame period.

13. A display as recited in claim 12, wherein the display is connected by way of a link to a video source wherein the video source forms a packet based video stream and transmits the packet based video stream to the digital display by way of the link at the link rate.

14. A display as recited in claim 13, wherein the digital display device includes a memory device coupled to the link suitably arranged to store selected ones of the video data packets.

15. A display as recited in claim 14 wherein the memory device is a line buffer arranged to store at least a quantity of video data packets consistent with a single frame line.

16. A display as recited in claim 15, wherein each of the video data packets includes a packet header and a packet payload, wherein the packet header includes a packet ID and wherein the packet payload includes video data suitable for driving a corresponding pixel.

17. Computer program product for driving selected pixel elements by way of associated data latches included in a column driver in a packet based digital display device, , comprising:

computer code for providing a number of video data packets directly to the column driver at a link rate; computer code for populating each of the number of data latches with appropriate video data based upon video data packets within a line period ; computer code for driving selected pixel elements based upon the video data; and computer readable medium for storing the computer code.

18. Computer program product as recited in claim 17, further comprising: computer code for generating a video signal at a video source coupled to the digital display device by way of a link; computer code for forming a packet based video stream based upon the video signal; and computer code for transmitting the packet based video stream to the digital display device by way of the link at the link rate.

19. Computer program product as recited in claim 18, wherein the digital display device includes a memory device coupled to the link suitably arranged to store selected ones of the video data packets.

20. Computer program product as recited in claim 19 wherein the memory device is a line buffer arranged to store at least a quantity of video data packets consistent with a single frame line.

21. Computer program product as recited in claim 20, wherein each of the video data packets includes a packet header and a packet payload, wherein the packet header includes a packet ID and wherein the packet payload includes video data suitable for driving a corresponding pixel.

## 1. ABSTRACT

In a digital display device, a packet based method of driving selected pixel elements by way of associated data latches included in a column driver is disclosed. For each frame lines in a video frame, a number of video data packets are provided directly to the column driver at a link rate and each of the number of data latches are populated with appropriate video data based upon video data packets within a line period . Selected pixel elements are driven based upon the video data.

## 2. REPRESENTATIVE DRAWING

Fig. 2

Fig. 1

Prior Art

Fig. 2

Fig. 3A

Main Link Packet Format

**Fig. 4** High-level diagram of link traffic example

Fig. 5

600

Fig. 6

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | <无法获取翻译>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2005165273A5</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 公开(公告)日 | 2007-11-01 |

| 申请号            | JP2004271114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2004-09-17 |

| [标]申请(专利权)人(译) | 创世纪微芯片公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 申请(专利权)人(译)    | Genesis Microchip公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| [标]发明人         | 小林修                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 发明人            | 小林 修                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20 H04N5/66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| CPC分类号         | G09G3/3611 G06F3/14 G09G3/20 G09G3/3666 G09G5/006 G09G2300/0426 G09G2310/0221<br>G09G2310/027 G09G2310/0281 G09G2320/0223 G09G2370/08                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| FI分类号          | G09G3/36 G02F1/133.505 G09G3/20.612.P G09G3/20.621.F G09G3/20.623.B G09G3/20.623.G<br>G09G3/20.631.B G09G3/20.632.F G09G3/20.633.G G09G3/20.633.H H04N5/66.102.B                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NC12 2H093/NC15 2H093/NC16 2H093/NC22 2H093/NC26 2H093/NC34 2H093<br>/ND34 5C006/AA01 5C006/AF03 5C006/AF04 5C006/AF44 5C006/AF45 5C006/AF51 5C006/AF52<br>5C006/AF53 5C006/AF61 5C006/AF71 5C006/BC11 5C006/BC16 5C006/BF02 5C006/BF03 5C006<br>/BF14 5C006/BF15 5C006/BF16 5C006/BF24 5C006/EB04 5C006/FA13 5C058/AA08 5C058/AB02<br>5C058/BA04 5C058/BB05 5C058/BB12 5C058/BB13 5C080/AA05 5C080/AA06 5C080/AA10 5C080<br>/BB05 5C080/DD07 5C080/DD08 5C080/DD28 5C080/GG12 5C080/JJ02 5C080/JJ05 2H193/ZA04<br>2H193/ZF36 |         |            |

| 优先权            | 60/504060 2003-09-18 US<br>60/563120 2004-04-15 US<br>10/909103 2004-07-29 US                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| 其他公开文献         | <a href="#">JP2005165273A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

### 摘要(译)

解决的问题：通过简化基于数据包的显示系统中的列驱动器电路来提高数字显示平台的速度和带宽。公开了一种用于通过包括在列驱动器中的相关联的数据锁存器来驱动数字显示器中的所选像素元素的基于分组的方法。对于一个视频帧中的每一帧线，将多个视频数据包以链接速率直接提供给列驱动器，并基于该视频数据包，在行周期t内将适当的视频数据提供给多个数据锁存器中的每一个。进去 基于视频数据来驱动选择的像素元件。[选择图]图2