特開2003 - 279929

(P2003 - 279929A)

(43)公開日 平成15年10月2日(2003.10.2)

| (51) Int.Cl <sup>7</sup> | 識別記号 | F I           | テ-マコード <sup>8</sup> (参考) |

|--------------------------|------|---------------|--------------------------|

| G 0 2 F 1/133            | 550  | G 0 2 F 1/133 | 550 2 H 0 9 2            |

| 1/1368                   |      | 1/1368        | 2 H 0 9 3                |

| G 0 9 G 3/20             | 621  | G 0 9 G 3/20  | 621 F 5 C 0 0 6          |

|                          | 623  |               | 623 Y 5 C 0 8 0          |

|                          | 624  |               | 624 D                    |

審査請求 未請求 請求項の数 210 L (全 22数) 最終頁に続く

(21)出願番号 特願2002 - 83527(P2002 - 83527)

(22)出願日 平成14年3月25日(2002.3.25)

(71)出願人 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(72)発明者 宮地 弘一

大阪府大阪市阿倍野区長池町22番22号 シ

ヤープ株式会社内(74)代理人 100077931

弁理士 前田 弘 (外3名)

最終頁に続く

(54)【発明の名称】 液晶表示装置の駆動方法及びその液晶表示装置

## (57)【要約】

【課題】 動画を表示するときの応答性に優れる新規な交流駆動方式のアクティブマトリクス型の液晶表示装置の駆動方法を提供する。

【解決手段】 液晶表示装置100は、交流駆動方式のアクティブマトリクス型のものである。補助容量Csの他端の電位から対向電極121の電位を引いた電位差が繰り返し大小変化すると共に、その電位差が画素電極114への電荷の書き込み時と同じときに画素電極114と対向電極121との間に印加される第1の電圧の絶対値が、その電位差が画素電極114への電荷の書き込み時と異なるときに画素電極114と対向電極121との間に印加される第2の電圧の絶対値以下となるように、ソース信号、補助容量Csの他端及び対向電極121のそれぞれの電位を設定する。

## 【特許請求の範囲】

【請求項1】 相互に並行に延びるように設けられゲート信号が順次送られる複数のゲート線と、該複数のゲート線が延びる方向と角度をなす方向に相互に並行に延びるように設けられソース信号が送られる複数のソース線と、該ゲート線と該ソース線との各交差部に対応して設けられてマトリクスを構成し各々がスイッチング素子を有する複数の画素電極と、該複数の画素電極の各々に対応して設けられ該対応した画素電極に一端が接続された複数の補助容量と、を有する素子側基板と、

上記素子側基板に対向するように設けられ対向電極を有する対向側基板と、

上記素子側基板と上記対向側基板との間に狭持されるように設けられ液晶分子を含有してなる液晶層と、を備え、

上記ゲート線より上記スイッチング素子にゲート信号が送られて選択状態となったときに、上記ソース線より該スイッチング素子に対応した画素電極にソース信号が送られることにより該画素電極に電荷が書き込まれて該画素電極と上記対向電極との間に形成される液晶容量及びそれに対応した補助容量に電荷が充電されるように構成された交流駆動方式のアクティブマトリクス型の液晶表示装置の駆動方法であって、

上記補助容量の他端の電位から上記対向電極の電位を引いた電位差が繰り返し大小変化すると共に、該電位差が上記画素電極への電荷の書き込み時と同じときに上記画素電極と上記対向電極との間に印加される第1の電圧の絶対値が、該電位差が該画素電極への電荷の書き込み時と異なるときに該画素電極と該対向電極との間に印加される第2の電圧の絶対値以下となるように、上記ソース信号、上記補助容量の他端及び上記対向電極のそれぞれの電位を設定することを特徴とする液晶表示装置の駆動方法。

【請求項2】 請求項1に記載された液晶表示装置の駆動方法において、

上記補助容量の他端及び上記対向電極のそれぞれの電位を、該補助容量の他端の電位から該対向電極の電位を引いた電位差が、上記画素電極へのプラス極性の電荷の書き込み時に相対的に小となり且つ該画素電極へのマイナス極性の電荷の書き込み時に相対的に大となる波形を構成するように設定することを特徴とする液晶表示装置の駆動方法。

【請求項3】 請求項2に記載された液晶表示装置の駆動方法において、

上記補助容量の他端の電位から上記対向電極の電位を引いた電位差を、上記液晶層の液晶分子が応答不能な周波数のものとすることを特徴とする液晶表示装置の駆動方法。

【請求項4】 請求項3に記載された液晶表示装置の駆動方法において、

\*上記電位差の周波数を、上記液晶表示装置の水平周波数に一致させることを特徴とする液晶表示装置の駆動方法。

【請求項5】 請求項2に記載された液晶表示装置の駆動方法において、

上記電位差の波形の振幅が ( $> 0$ ) となるように上記補助容量の他端及び上記対向電極のそれぞれの電位を設定したとき、上記画素電極へのプラス極性の電荷の書き込み時には上記ソース信号の電位から該対向電極の電位を引いた電位差  $V_s$  を示す下記関係式(1)が満たされる一方、該画素電極へのマイナス極性の電荷の書き込み時には下記関係式(2)が満たされるように該ソース信号の電位を設定することを特徴とする液晶表示装置の駆動方法。

$$【数1】 V_s = \sqrt{V_{LC}^2 - \left( \frac{C_s}{C_{LC} + C_s} \cdot \Delta \right)^2} - \frac{C_s}{C_{LC} + C_s} \cdot \Delta \quad (1)$$

$$【数2】 V_s = -\sqrt{V_{LC}^2 - \left( \frac{C_s}{C_{LC} + C_s} \cdot \Delta \right)^2} + \frac{C_s}{C_{LC} + C_s} \cdot \Delta \quad (2)$$

(ここで、  $C_{LC}$  : 液晶容量、  $V_{LC}$  : 液晶容量  $C_{LC}$  に対応して印加すべき電圧、  $C_s$  : 補助容量)

【請求項6】 請求項5に記載された液晶表示装置の駆動方法において、

上記電位差の波形の振幅  $\Delta$  が下記関係式(3)を満たすように上記補助容量の他端及び上記対向電極のそれぞれの電位を設定することを特徴とする液晶表示装置の駆動方法。

$$【数3】 \Delta = \frac{C_{LC\_min} + C_s}{C_s} \cdot V_{LC\_min} \quad (3)$$

(ここで、  $C_{LC\_min}$  : 液晶容量の最低値、  $V_{LC\_min}$  :  $C_{LC\_min}$  に対応して印加すべき電圧)

【請求項7】 請求項2に記載された液晶表示装置の駆動方法において、

上記スイッチング素子は、上記ゲート線、上記ソース線及び上記画素電極にそれぞれ接続されたドレイン電極、ソース電極及びドレイン電極を有する薄膜トランジスタであり、

上記電位差の波形の振幅が ( $> 0$ ) となるように上記補助容量の他端及び上記対向電極のそれぞれの電位を設定したとき、上記画素電極へのプラス極性の電荷の書き込み時には上記ソース信号の電位から該対向電極の電位を引いた電位差  $V_s$  を示す下記関係式(4)が満たされる一方、該画素電極へのマイナス極性の電荷の書き込み時には下記関係式(5)が満たされるように該ソース信号の電位を設定することを特徴とする液晶表示装置の駆動方法。

【数4】

$$V_s = \sqrt{V_{LC}^2 - \left( \frac{C_s}{C_{total}} \cdot \Delta \right)^2} - \frac{C_s}{C_{total}} \cdot \Delta + \frac{C_{sd}}{C_{total}} (V_{gh} - V_{gl}) \quad (4)$$

【数5】

$$V_s = -\sqrt{V_{LC}^2 - \left( \frac{C_s}{C_{total}} \cdot \Delta \right)^2} + \frac{C_s}{C_{total}} \cdot \Delta + \frac{C_{sd}}{C_{total}} (V_{gh} - V_{gl}) \quad (5)$$

(ここで、 $C_{LC}$ ：液晶容量、 $V_{LC}$ ：液晶容量  $C_{LC}$  に対応して印加すべき電圧、 $C_s$ ：補助容量、 $C_{sd}$ ：ゲート電極とドレイン電極との間の寄生容量、 $C_{total}$ ： $C_{LC} + C_s + C_{sd}$ 、 $V_{gh}$ ：選択時のゲート電極の電位、 $V_{gl}$ ：非選択時のゲート電極の電位)

【請求項8】 請求項7に記載された液晶表示装置の駆

$$\Delta = \frac{C_{LC\_min} + C_s + C_{sd}}{C_s} \cdot V_{LC\_min}$$

(ここで、 $C_{LC\_min}$ ：液晶容量の最低値、 $V_{LC\_min}$ ： $C_{LC\_min}$  に対応して印加すべき電圧)

【請求項9】 請求項1に記載された液晶表示装置の駆動方法において、

上記液晶表示装置は、上記補助容量の他端が接続された補助容量線を有する  $C_s$  - on - Common 型であることを特徴とする液晶表示装置の駆動方法。

【請求項10】 請求項9に記載された液晶表示装置の駆動方法において、

上記液晶表示装置は、ゲート線の延びる方向に配列した補助容量の他端のそれらが同一の補助容量線に接続されている一方、ゲート線の延びる方向に配列したスイッチング素子の相互に隣接したスイッチング素子がそれれ異なるゲート線に接続されており、

同一フレームでの画素電極への電荷の書き込みの際に、ゲート線の延びる方向に配列したスイッチング素子の相互に隣接したスイッチング素子のそれれを異なるゲート線のゲート信号により選択状態とすることにより、ゲート線の延びる方向に相互に隣接した画素電極のそれれに極性の異なる電荷を書き込むことを特徴とする液晶表示装置の駆動方法。

【請求項11】 請求項9に記載された液晶表示装置の制御方法において、

上記液晶表示装置は、ゲート線の延びる方向に配列したスイッチング素子のそれらが同一のゲート線に接続されている一方、ゲート線の延びる方向に配列した補助容量の相互に隣接した補助容量の他端がそれれ異なる補助容量線に接続されており、

同一フレームでの画素電極への電荷の書き込みの際に、ゲート線の延びる方向に配列したスイッチング素子を同一のゲート線のゲート信号により選択状態とすると共に該スイッチング素子に対応して配列した画素電極の相互に隣接した画素電極のそれれに逆相のソース信号を送ることにより、ゲート線の延びる方向に相互に隣接した

駆動方法において、

10 上記電位差の波形の振幅  $\Delta$  が下記関係式(6)を満たすように上記補助容量の他端及び上記対向電極のそれぞれの電位を設定することを特徴とする液晶表示装置の駆動方法。

【数6】

$$(6)$$

画素電極のそれぞれに極性の異なる電荷を書き込むことを特徴とする液晶表示装置の駆動方法。

【請求項12】 請求項11に記載された液晶表示装置の制御方法において、

上記液晶表示装置は、同一フレームでの画素電極への電荷の書き込みの際に極性の同じ電荷が書き込まれる画素電極に対応した補助容量が補助容量線を介して全て繋がれていることを特徴とする液晶表示装置の駆動方法。

【請求項13】 請求項11に記載された液晶表示装置の制御方法において、

上記液晶表示装置は、上記補助容量線が各ゲート線間に設けられていると共に、該各補助容量線に他端が接続された補助容量の一端がそれに対応した画素電極の端部に

30 接続され、且つ該画素電極がゲート線上に該画素電極と該ゲート線との間の容量形成を阻止する絶縁膜を介して設けられていることを特徴とする液晶表示装置の駆動方法。

【請求項14】 請求項1に記載された液晶表示装置の駆動方法において、

上記液晶表示装置は、上記補助容量の他端がそれに対応したゲート線以外のゲート線に接続された  $C_s$  - on - Gate 型であることを特徴とする液晶表示装置の駆動方法。

【請求項15】 相互に並行に延びるように設けられゲート信号が順次送られる複数のゲート線と、該複数のゲート線が延びる方向と角度をなす方向に相互に並行に延びるように設けられソース信号が送られる複数のソース線と、該ゲート線と該ソース線との各交差部に対応して設けられてマトリクスを構成し各々がスイッチング素子を有する複数の画素電極と、該複数の画素電極の各々に対応して設けられ該対応した画素電極に一端が接続された複数の補助容量と、を有する素子側基板と、

上記素子側基板に対向するように設けられ対向電極を有する対向側基板と、

上記素子側基板と上記対向側基板との間に狭持されるように設けられ液晶分子を含有してなる液晶層と、を備え、

上記ゲート線より上記スイッチング素子にゲート信号が送られて選択状態となったときに、上記ソース線より該スイッチング素子に対応した画素電極にソース信号が送られることにより該画素電極に電荷が書き込まれて該画素電極と上記対向電極との間に形成される液晶容量及びそれに対応した補助容量に電荷が充電されるように構成された交流駆動方式のアクティブマトリクス型の液晶表示装置であって、

上記補助容量の他端の電位から上記対向電極の電位を引いた電位差が繰り返し大小変化すると共に、該電位差が上記画素電極への電荷の書き込み時と同じときに上記画素電極と上記対向電極との間に印加される第1の電圧の絶対値が、該電位差が該画素電極への電荷の書き込み時と異なるときに該画素電極と該対向電極との間に印加される第2の電圧の絶対値以下となるように、上記ソース信号、上記補助容量の他端及び上記対向電極のそれぞれの電位が設定されることを特徴とする液晶表示装置。

【請求項16】 請求項15に記載された液晶表示装置において、

上記補助容量の他端が接続された補助容量線を有するC<sub>s</sub>-on-Common型であることを特徴とする液晶表示装置。

【請求項17】 請求項16に記載された液晶表示装置において、

ゲート線の延びる方向に配列した補助容量の他端のそれぞれが同一の補助容量線に接続されている一方、ゲート線の延びる方向に配列したスイッチング素子の相互に隣接したスイッチング素子のそれぞれが異なるゲート線に接続されており、

同一フレームでの画素電極への電荷の書き込みの際に、ゲート線の延びる方向に配列したスイッチング素子の相互に隣接したスイッチング素子のそれぞれが異なるゲート線のゲート信号により選択状態とされることにより、ゲート線の延びる方向に相互に隣接した画素電極のそれぞれに極性の異なる電荷が書き込まれるように構成されていることを特徴とする液晶表示装置。

【請求項18】 請求項16に記載された液晶表示装置において、

ゲート線の延びる方向に配列したスイッチング素子のそれぞれが同一のゲート線に接続されている一方、ゲート線の延びる方向に配列した補助容量の相互に隣接した補助容量の他端のそれぞれが異なる補助容量線に接続されており、

同一フレームでの画素電極への電荷の書き込みの際に、ゲート線の延びる方向に配列したスイッチング素子が同一のゲート線のゲート信号により選択状態とされると共に該スイッチング素子に対応して配列した画素電極の相\*

\*互に隣接した画素電極のそれぞれに逆相のソース信号が送られることにより、ゲート線の延びる方向に相互に隣接した画素電極のそれぞれに極性の異なる電荷が書き込まれるように構成されていることを特徴とする液晶表示装置。

【請求項19】 請求項18に記載された液晶表示装置において、

同一フレームでの画素電極への電荷の書き込みの際に極性の同じ電荷が書き込まれる画素電極に対応した補助容量が補助容量線を介して全て繋がれていることを特徴とする液晶表示装置。

【請求項20】 請求項18に記載された液晶表示装置において、

上記補助容量線が各ゲート線間に設けられていると共に、該各補助容量線に他端が接続された補助容量の一端がそれに対応した画素電極の端部に接続され、且つ該画素電極がゲート線上に該画素電極と該ゲート線との間の容量形成を阻止する絶縁膜を介して設けられていることを特徴とする液晶表示装置。

20 【請求項21】 請求項15に記載された液晶表示装置において、

上記補助容量の他端がそれに対応したゲート線以外のゲート線に接続されたC<sub>s</sub>-on-Gate型であることを特徴とする液晶表示装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、交流駆動方式のアクティブマトリクス型の液晶表示装置の駆動方法及びその液晶表示装置に関する。

【0002】

【従来の技術】近年、スイッチング素子として薄膜トランジスタ(以下「TFT」という)を用いたアクティブマトリクス型の液晶表示装置が広く使用されている。

【0003】かかる液晶表示装置は、TFT基板と対向側基板との一対の基板で液晶層を狭持した構成となっている。TFT基板には、相互に並行して延びる複数のゲート線と、それらのゲート線と直交する方向に相互に並行して延びる複数のソース線とが設けられている。また、ゲート線とソース線との各交差部には、それに対応して画素を構成する画素電極が設けられおり、画素電極が全体としてマトリクスを構成している。さらに、各画素電極に対応してTFTが設けられており、TFTのゲート電極がゲート線に、ソース電極がソース線に、及びドレイン電極が画素電極にそれぞれ接続されている。また、各画素電極に対応してその画素電極に一端が接続された補助容量が設けられており、補助容量は、さらに他端が隣接するゲート線(C<sub>s</sub>-on-Gate型)又は補助容量線(C<sub>s</sub>-on-Common型)に接続されている。一方、対向側基板には、対向共通電極が設けられている。そして、画素電極と対向共通電極との間で液

晶容量を形成し、その液晶容量と補助容量とによって画素容量が構成されている。

【0004】ところで、一般的に、液晶表示装置の応答は遅く、その原因として以下のようなものがある。

【0005】上記のようなTFTをスイッチング素子とする典型的なアクティブマトリクス方式の液晶表示装置は、ゲート線を介してゲート電極にゲート信号が送られることにより画素電極に接続されたTFTが選択状態とされ、その際、ソース線を介してソース電極にソース信号が送られることにより、ソース電極に繋がったドレン電極を介して画素電極に電荷が書き込まれ、そして、それによって画素容量(=液晶容量+補助容量)に所定量の電荷が充電され、液晶層の液晶分子を所望の配向状態にさせて表示を行うようにしたものである。なお、補助容量は、液晶容量に充電された電荷量が保持されるようにする機能を果たす。また、液晶層を直流電圧で駆動するとその寿命が短くなること等のため、ソース電極からのソース信号の送信は、液晶層が交流電圧で駆動されるように充電の度にその極性が反転するように行われる(フレーム反転)。

【0006】このとき、画素容量に充電された電荷量は、理想的には、次にTFTが選択状態となるまで変化しないことが望まれる。ここで、電荷量Q、画素容量C<sub>Pixel</sub>、(=液晶容量C<sub>LC</sub>+補助容量C<sub>s</sub>)、液晶容量に印加される電圧V<sub>LC</sub>、すなわち、ソース信号の電位から対向電極の電位を引いた電位差V<sub>s</sub>とし、対向電極を接地しているとすると下記関係式が成立する、 $Q = C_{Pixel} \cdot V_s$ 一方、例えば、ノーマリーホワイトのTNモードの場合、白表示から黒表示に応答させようすると、液晶分子の誘電率が増加することになる。つまり、C<sub>Pixel</sub>(白) < C<sub>Pixel</sub>(黒)となる。よって、白表示状態において、黒表示状態を示すはずの所定の電圧を画素容量に印加しても、液晶分子の誘電率が増加するために実際に画素容量に印加される電圧が所定の電圧よりも低下してしまい(以下この現象を「電圧変動」という)、黒表示状態になりえないこととなる。但し、何度かこの電圧の印加(充電)を繰り返すといずれ黒表示状態に到達する。従って、この過程のために、液晶分子の応答が見かけ上遅くなる。なお、この電圧変動は、原理上あらゆる階調間応答、すなわち、動画表示において発生し、従って、あらゆる階調間応答が電圧変動により遅くなっているということになる。

【0007】この問題を解決するために、例えば、特開平3-35218公報には、C<sub>s</sub>-on-Gate型のTFT液晶表示装置において、従来2値であったゲート線のゲート信号(TFTのオン状態を得る高電位とオフ状態を得る低電位)にさらに2値を加えて4値とし、新たに加えた2値による変調信号により補助容量との間に電荷のやり取りを発生させ、それによって画素容量に所定の電圧が印加されるようにすることで電圧変動を軽減

し、結果として液晶分子の応答を速めるという容量結合法の技術が開示されている。

【0008】容量結合法では、ゲート線方向に隣接する画素の極性を反転させることができず、フリッカー(ちらつき)が見えやすいという欠点がある。そこで、特開平11-218736号公報には、隣接する画素毎に補助容量を接続するゲート線を前後に振り分けた構造とし、この構造とソース線の延びる方向に隣接する画素の極性が反転するようにするHライン反転駆動とを組み合わせることにより、上下左右に隣接した全ての画素の極性が互いに異なるようにし、それによってフリッカーを軽減する技術が開示されている。

【0009】さらに、特開平4-145490号公報には、C<sub>s</sub>-on-Common型の液晶表示装置での容量結合法について、補助容量線をゲート線毎に独立させて駆動することにより変調信号を液晶容量に重畠させることでC<sub>s</sub>-on-Gate型のものの場合と同様な効果を得ることができることが開示されている。

【0010】

20 【発明が解決しようとする課題】本出願は、動画を表示するときの応答性に優れる新規な交流駆動方式のアクティブマトリクス型の液晶表示装置の駆動方法及びその液晶表示装置を提供することを目的とする。

【0011】

【課題を解決するための手段】本発明は、補助容量の他端の電位から対向電極の電位を引いた電位差が繰り返し大小変化するものとすると共に、その電位差が画素電極への電荷の書き込み時と同じときに画素電極と対向電極との間に印加される第1の電圧の絶対値が、その電位差が画素電極への電荷の書き込み時と異なるときに画素電極と対向電極との間に印加される第2の電圧の絶対値以下となるようにしたものである。

30 【0012】具体的には、本発明は、相互に並行に延びるように設けられゲート信号が順次送られる複数のゲート線と、該複数のゲート線が延びる方向と角度をなす方向に相互に並行に延びるように設けられソース信号が送られる複数のソース線と、該ゲート線と該ソース線との各交差部に対応して設けられてマトリクスを構成し各々がスイッチング素子を有する複数の画素電極と、該複数の画素電極の各々に対応して設けられ該対応した画素電極に一端が接続された複数の補助容量と、を有する素子側基板と、上記素子側基板に対向するように設けられ対向電極を有する対向側基板と、上記素子側基板と上記対向側基板との間に狭持されるように設けられ液晶分子を含有してなる液晶層と、を備え、上記ゲート線より上記スイッチング素子にゲート信号が送られて選択状態となつたときに、上記ソース線より該スイッチング素子に対応した画素電極にソース信号が送られることにより該画素電極に電荷が書き込まれて該画素電極と上記対向電極との間に形成される液晶容量及びそれに対応した補助容

量に電荷が充電されるように構成された交流駆動方式のアクティブマトリクス型の液晶表示装置の駆動方法であって、上記補助容量の他端の電位から上記対向電極の電位を引いた電位差が繰り返し大小変化すると共に、該電位差が上記画素電極への電荷の書き込み時と同じときに上記画素電極と上記対向電極との間に印加される第1の電圧の絶対値が、該電位差が該画素電極への電荷の書き込み時と異なるときに該画素電極と該対向電極との間に印加される第2の電圧の絶対値以下となるように、上記ソース信号、上記補助容量の他端及び上記対向電極のそれぞれの電位を設定することを特徴とする。

【0013】上記のようにすれば、補助容量の他端の電位から対向電極の電位を引いた電位差が繰り返し大小変化し、その電位差が画素電極への電荷の書き込み時と同じときに画素電極と対向電極との間に印加される第1の電圧の絶対値が、その電位差が画素電極への電荷の書き込み時と異なるときに画素電極と対向電極との間に印加される第2の電圧の絶対値以下となるようにしており、例えば、一の階調を表示する場合、液晶容量の変化のない一の階調の静止画を表示するときには、液晶容量に実質的に印加される電圧は、一の階調の液晶容量に対応した第1及び第2の電圧間の所定電圧となる一方、液晶容量の変化のある他の階調から一の階調へと動画を表示するときには、液晶容量に実質的に印加される第1及び第2の電圧間の所定電圧は、液晶容量の変化に伴って第2の電圧が変化するために変化し、最終的に一の階調の静止画を表示するときに液晶容量に実質的に印加される所定電圧へ収束する、すなわち、同一階調を表示する場合でも、静止画を表示するときと動画を表示するときとで液晶容量に実質的に印加される電圧が異なるものとなり、その電圧の差により電荷の移動が促進され、液晶分子の応答を加速させることができるので、表示の階調を変化させて動画を表示するときの応答性を優れたものとすることができる。

【0014】本発明の駆動方法は、上記補助容量の他端及び上記対向電極のそれぞれの電位を、該補助容量の他端の電位から該対向電極の電位を引いた電位差が、上記画素電極へのプラス極性の電荷の書き込み時に相対的に小となり且つ該画素電極へのマイナス極性の電荷の書き込み時に相対的に大となる波形を構成するように設定するものであってもよい。

【0015】典型的なものとしては、例えば、補助容量の他端の電位から対向電極の電位を引いた電位差により矩形波を構成することを挙げることができる。

【0016】この場合、本発明の駆動方法は、上記補助容量の他端の電位から上記対向電極の電位を引いた電位差を、上記液晶層の液晶分子が応答不能な周波数のものとするものであってもよい。

【0017】上記電位差が液晶層の液晶分子が応答可能な周波数のものであると、その電位差の変化による液晶<sup>50</sup>

\*分子の応答によりフリッカーが発生し、表示品位が低いものとなってしまう。しかしながら、上記のようにすれば、上記電位差の変化に対して液晶分子が応答しないので、かかるフリッカーの発生を防止することができる。

【0018】また、本発明の駆動方法は、上記電位差の周波数を、上記液晶表示装置の水平周波数に一致させるようにしてもよい。

【0019】このようにすれば、液晶層の液晶分子が応答不能なほどに充分に周波数が高く、また、駆動回路を簡略化することができる。

【0020】さらに、本発明の駆動方法は、上記電位差の波形の振幅が ( $> 0$ ) となるように上記補助容量の他端及び上記対向電極のそれぞれの電位を設定したとき、上記画素電極へのプラス極性の電荷の書き込み時には上記ソース信号の電位から該対向電極の電位を引いた電位差  $V_s$  を示す下記関係式(1)が満たされる一方、該画素電極へのマイナス極性の電荷の書き込み時には下記関係式(2)が満たされるように該ソース信号の電位を設定するものであってもよい。

【0021】

【数7】

$$V_s = \sqrt{V_{LC}^2 - \left( \frac{C_s}{C_{LC} + C_s} \cdot \Delta \right)^2} - \frac{C_s}{C_{LC} + C_s} \cdot \Delta \quad (1)$$

【0022】

【数8】

$$V_s = -\sqrt{V_{LC}^2 - \left( \frac{C_s}{C_{LC} + C_s} \cdot \Delta \right)^2} + \frac{C_s}{C_{LC} + C_s} \cdot \Delta \quad (2)$$

30 (ここで、  $C_{LC}$  : 液晶容量、  $V_{LC}$  : 液晶容量  $C_{LC}$  に対応して印加すべき電圧、  $C_s$  : 補助容量)

【0023】このようにすれば、本発明の作用がより具体的に営まれることとなる。このような方法は、例えば、スイッチング素子が TFT であって、ゲート電極とドレイン電極との間の寄生容量を無視できるような場合に有効である。なお、ここで、振幅とは、上記波形のピークピーク電圧の半分の値を意味する(以下同じ)。

【0024】この場合、本発明の駆動方法は、上記電位差の波形の振幅が下記関係式(3)を満たすように上記補助容量の他端及び上記対向電極のそれぞれの電位を設定するようにしてもよい。

【0025】

【数9】

$$\Delta = \frac{C_{LC\_min} + C_s}{C_s} \cdot V_{LC\_min} \quad (3)$$

(ここで、  $C_{LC\_min}$  : 液晶容量の最低値、  $V_{LC\_min}$  :  $C_{LC\_min}$  に対応して印加すべき電圧)

【0026】このようにすれば、静止画の表示時と動画の表示時との画素電極と対向電極との間に印加される電圧の差が最大となり、電荷の移動促進効果が最も高く

なるので、液晶分子の応答を最大限に加速させることができる。

【0027】本発明の駆動方法は、上記スイッチング素子が、上記ゲート線、上記ソース線及び上記画素電極にそれぞれ接続されたドレイン電極、ソース電極及びドレイン電極を有するTFTであり、上記電位差の波形の振幅が( $>0$ )となるように上記補助容量の他端及び上記対向電極のそれぞれの電位を設定したとき、上記画\*

$$V_s = \sqrt{V_{LC}^2 - \left( \frac{C_s}{C_{total}} \cdot \Delta \right)^2} - \frac{C_s}{C_{total}} \cdot \Delta + \frac{C_{sd}}{C_{total}} (V_{gh} - V_{gl}) \quad (4)$$

【0029】

$$V_s = -\sqrt{V_{LC}^2 - \left( \frac{C_s}{C_{total}} \cdot \Delta \right)^2} + \frac{C_s}{C_{total}} \cdot \Delta + \frac{C_{sd}}{C_{total}} (V_{gh} - V_{gl}) \quad (5)$$

(ここで、 $C_{LC}$ ：液晶容量、 $V_{LC}$ ：液晶容量 $C_{LC}$ に対応して印加すべき電圧、 $C_s$ ：補助容量、 $C_{gd}$ ：ゲート電極とドレイン電極との間の寄生容量、 $C_{total}$ ： $C_{LC} + C_s + C_{gd}$ 、 $V_{gh}$ ：選択時のゲート電極の電位、 $V_{gl}$ ：非選択時のゲート電極の電位)

【0030】このようにすれば、スイッチング素子がTFTで、ゲート電極とドレイン電極との間の寄生容量を無視できないような場合であっても、本発明の作用がよ

$$\Delta = \frac{C_{LC\_min} + C_s + C_{sd}}{C_s} \cdot V_{LC\_min} \quad (6)$$

(ここで、 $C_{LC\_min}$ ：液晶容量の最低値、 $V_{LC\_min}$ ： $C_{LC\_min}$ に対応して印加すべき電圧)

【0033】このようにすれば、静止画の表示時と動画の表示時との画素電極と対向電極との間に印加される電圧の差が最大となり、電荷の移動促進効果が最も高くなるので、液晶分子の応答を最大限に加速させることができる。

【0034】本発明の駆動方法は、上記補助容量の他端が接続された補助容量線を有する $C_s - on - Comm on$ 型の液晶表示装置のものであってもよい。

【0035】この場合、本発明の駆動方法は、上記液晶表示装置が、ゲート線の延びる方向に配列した補助容量の他端のそれぞれが同一の補助容量線に接続されている一方、ゲート線の延びる方向に配列したスイッチング素子の相互に隣接したスイッチング素子のそれぞれが異なるゲート線に接続されており、同一フレームでの画素電極への電荷の書き込みの際に、ゲート線の延びる方向に配列したスイッチング素子の相互に隣接したスイッチング素子のそれを異なるゲート線のゲート信号により選択状態とすることにより、ゲート線の延びる方向に相互に隣接した画素電極のそれぞれに極性の異なる電荷を書き込むようにしてもよい。

【0036】このようにすれば、ゲート線の延びる方向に相互に隣接した画素電極のそれぞれに極性の異なる電荷が書き込まれるので、その方向でのフリッカーの発生

\*素電極へのプラス極性の電荷の書き込み時には上記ソース信号の電位から該対向電極の電位を引いた電位差 $V_s$ を示す下記関係式(4)が満たされる一方、該画素電極へのマイナス極性の電荷の書き込み時には下記関係式(5)が満たされるように該ソース信号の電位を設定するものであってもよい。

【0028】

【数10】

【数11】

$$V_s = -\sqrt{V_{LC}^2 - \left( \frac{C_s}{C_{total}} \cdot \Delta \right)^2} + \frac{C_s}{C_{total}} \cdot \Delta + \frac{C_{sd}}{C_{total}} (V_{gh} - V_{gl}) \quad (5)$$

り具体的に営まれることとなる。

【0031】この場合、本発明の駆動方法は、上記電位差の波形の振幅 $\Delta$ が下記関係式(6)を満たすように上記補助容量の他端及び上記対向電極のそれぞれの電位を設定するようにしてよい。

【0032】

【数12】

を抑止することができる。また、これに、いわゆるHライン反転駆動を組み合わせるとソース線の延びる方向でのフリッカーの発生をも抑止することができる。

【0037】また、本発明の駆動方法は、上記液晶表示装置が、ゲート線の延びる方向に配列したスイッチング素子のそれぞれが同一のゲート線に接続されている一方、ゲート線の延びる方向に配列した補助容量の相互に隣接した補助容量のそれぞれが異なる補助容量線に接続されており、同一フレームでの画素電極への電荷の書き込みの際に、ゲート線の延びる方向に配列したスイッチング素子を同一のゲート線のゲート信号により選択状態とすると共に該スイッチング素子に対応して配列した画素電極の相互に隣接した画素電極のそれぞれに逆相のソース信号を送ることにより、ゲート線の延びる方向に相互に隣接した画素電極のそれぞれに極性の異なる電荷を書き込むようにしてよい。

【0038】このようにすれば、ゲート線の延びる方向に相互に隣接した画素電極のそれぞれに極性の異なる電荷が書き込まれるので、その方向でのフリッckerの発生を抑止することができる。また、ゲート線の延びる方向に配列したスイッチング素子を同一のゲート線のゲート信号により選択状態とするようにしている、すなわち、それらのスイッチング素子に対応した画素電極に同時に電荷の書き込みを行うようにしているので、ゲート線の延びる方向に配列したスイッチング素子を分類してそれ

ぞれ異なるゲート線のゲート信号により選択状態とする場合に必要となるラインメモリが不要となる。さらに、これに、いわゆるHライン反転駆動を組み合わせるとソース線の延びる方向でのフリッカーの発生をも抑止することができる。

【0039】この場合、本発明の駆動方法は、上記液晶表示装置が、同一フレームでの画素電極への電荷の書き込みの際に極性の同じ電荷が書き込まれる画素電極に対応した補助容量が補助容量線を介して全て繋がれているものであってもよい。

【0040】このようにすれば、補助容量線を2種に分類して結線すればよいので、液晶表示装置として構成の簡略化が図られ、また、その2種の補助容量線のそれぞれの制御だけを行えばよいので、制御が容易である。

【0041】また、本発明の駆動方法は、上記液晶表示装置が、上記補助容量線が各ゲート線間に設けられていると共に、該各補助容量線に他端が接続された補助容量の一端がそれに対応した画素電極の端部に接続され、且つ該画素電極がゲート線上に該画素電極と該ゲート線との間の容量形成を阻止する絶縁膜を介して設けられているものであってもよい。

【0042】このようにすれば、ゲート線上に画素電極が設けられているにもかかわらず、それらの間に容量が形成されるのが阻止されるので、画素電極への正常な電荷の書き込みを行うことができる。

【0043】本発明の駆動方法は、上記補助容量の他端がそれに対応したゲート線以外のゲート線に接続されたC<sub>s</sub>-on-Gate型の液晶表示装置のものであってもよい。

【0044】そして、本発明の駆動方法によって駆動される本発明の液晶表示装置は、相互に並行に延びるよう設けられゲート信号が順次送られる複数のゲート線と、該複数のゲート線が延びる方向と角度をなす方向に相互に並行に延びるように設けられソース信号が送られる複数のソース線と、該ゲート線と該ソース線との各交差部に対応して設けられてマトリクスを構成し各々がスイッチング素子を有する複数の画素電極と、該複数の画素電極の各々に対応して設けられ該対応した画素電極に一端が接続された複数の補助容量と、を有する素子側基板と、上記素子側基板に対向するように設けられ対向電極を有する対向側基板と、上記素子側基板と上記対向側基板との間に狭持されるように設けられ液晶分子を含有してなる液晶層と、を備え、上記ゲート線より上記スイッチング素子にゲート信号が送られて選択状態となつたときに、上記ソース線より該スイッチング素子に対応した画素電極にソース信号が送られることにより該画素電極に電荷が書き込まれて該画素電極と上記対向電極との間に形成される液晶容量及びそれに対応した補助容量に電荷が充電されるように構成された交流駆動方式のアクティブマトリクス型のものであって、上記補助容量の他

(8)

14

端の電位から上記対向電極の電位を引いた電位差が繰り返し大小変化すると共に、該電位差が上記画素電極への電荷の書き込み時と同じときに上記画素電極と上記対向電極との間に印加される第1の電圧の絶対値が、該電位差が該画素電極への電荷の書き込み時と異なるときに該画素電極と該対向電極との間に印加される第2の電圧の絶対値以下となるように、上記ソース信号、上記補助容量の他端及び上記対向電極のそれぞれの電位が設定されることを特徴とする。

10 【0045】本発明の液晶表示装置は、上記補助容量の他端が接続された補助容量線を有するC<sub>s</sub>-on-Common型のものであってもよい。

【0046】この場合、本発明の液晶表示装置は、ゲート線の延びる方向に配列した補助容量の他端のそれぞれが同一の補助容量線に接続されている一方、ゲート線の延びる方向に配列したスイッチング素子の相互に隣接したスイッチング素子のそれぞれが異なるゲート線に接続されており、同一フレームでの画素電極への電荷の書き込みの際に、ゲート線の延びる方向に配列したスイッチング素子の相互に隣接したスイッチング素子のそれぞれが異なるゲート線のゲート信号により選択状態とされることにより、ゲート線の延びる方向に相互に隣接した画素電極のそれぞれに極性の異なる電荷が書き込まれるよう構成されているものであってもよい。

【0047】また、本発明の液晶表示装置は、ゲート線の延びる方向に配列したスイッチング素子のそれぞれが同一のゲート線に接続されている一方、ゲート線の延びる方向に配列した補助容量の相互に隣接した補助容量の他端のそれぞれが異なる補助容量線に接続されており、同一フレームでの画素電極への電荷の書き込みの際に、ゲート線の延びる方向に配列したスイッチング素子が同一のゲート線のゲート信号により選択状態とされると共に該スイッチング素子に対応して配列した画素電極の相互に隣接した画素電極のそれぞれに逆相のソース信号が送られることにより、ゲート線の延びる方向に相互に隣接した画素電極のそれぞれに極性の異なる電荷が書き込まれるよう構成されているものであってもよい。

40 【0048】この場合、本発明の液晶表示装置は、同一フレームでの画素電極への電荷の書き込みの際に極性の同じ電荷が書き込まれる画素電極に対応した補助容量が補助容量線を介して全て繋がれているものであってもよい。

【0049】また、本発明の液晶表示装置は、上記補助容量線が各ゲート線間に設けられていると共に、該各補助容量線に他端が接続された補助容量の一端がそれに対応した画素電極の端部に接続され、且つ該画素電極がゲート線上に該画素電極と該ゲート線との間の容量形成を阻止する絶縁膜を介して設けられているものであってもよい。

【0050】本発明の液晶表示装置は、上記補助容量の

他端がそれに対応したゲート線以外のゲート線に接続された $C_s$ -on-Gate型のものであってもよい。

【0051】

【発明の実施の形態】以下、本発明の実施形態を図面に基づいて詳細に説明する。

【0052】(実施形態1)

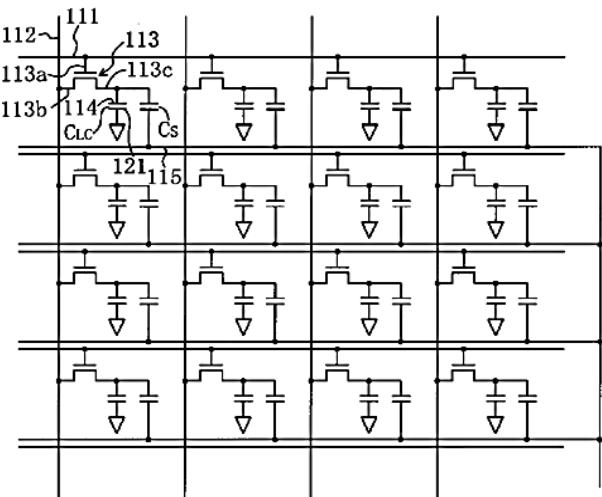

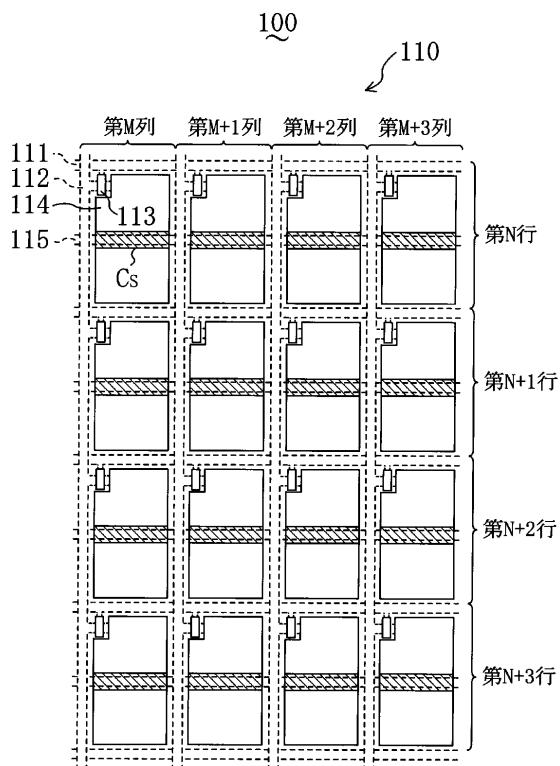

<液晶表示装置の構成>図1及び2は、本発明の実施形態1に係る液晶表示装置100を示す。

【0053】この液晶表示装置100は、TFT基板(素子側基板)110と、TFT基板110に対向して設けられた対向側基板と、それらの両基板で挟持されるように設けられた液晶層と、を備えている。

【0054】TFT基板110には、ガラス製又はプラスチック製の基板本体内側に、相互に並行に延びる複数のゲート線111が設けられ、また、それらのゲート線111と絶縁体を介して層を異にしてゲート線111が延びる方向に直交する方向に相互に並行に延びる複数のソース線112が設けられ、さらに、それらと絶縁体を介して層を異にしてゲート線111とソース線112との各交差部に対応し相互に隣接する一対のゲート線111及び一対のソース線112で囲まれた領域にITO(酸化インジウムと酸化スズとを主成分とする柱状結晶質の酸化物)等の透明電極からなる略矩形の画素電極114が設けられている。複数の画素電極114は、全体としてマトリクスを構成している。各画素電極114は、対応するゲート線111とソース線112との交差部に近い角部にスイッチング素子としてのTFT113を有している。各TFT113は、そのゲート電極111a、ソース電極113b及びドレイン電極113cがそれぞれ対応したゲート線111、ソース線112及び画素電極114に接続されている。また、ゲート線111と同じ層には、各ゲート線111間にゲート線111と並行して延びる補助容量線115が設けられており、画素電極114とこの補助容量線115との間で挟持された絶縁体により、一端が画素電極114に接続され且つ他端が補助容量線115に接続された補助容量 $C_s$ が構成されている。すなわち、この液晶表示装置100は、 $C_s$ -on-Common型のものである。各ゲート線111間に設けられた補助容量線115は、全てが1つに結線されている。なお、基板本体内側の画素電極114上には、他にラビング処理された配向膜が設けられている一方、基板本体外側には、偏光板が設けられている。

【0055】対向側基板には、ガラス製又はプラスチック製の基板本体の内側に、ITO等の透明電極からなる対向共通電極(対向電極)121が設けられている。なお、基板本体内側には、他にカラー表示用のRGBのカラーフィルタ及びラビング処理された配向膜が設けられている一方、基板本体外側には、入射光の状態を制御するための位相差板、偏光板、及び反射防止膜が設けられ

ている。

【0056】液晶層には、誘電性のネマチック液晶等の液晶分子が含まれている。

【0057】このような構成の液晶表示装置100は、スイッチング素子としてTFT113を有する各画素電極114に対応して1つの画素が規定されるアクティブマトリクス型のものであり、ゲート線111よりTFT113にゲート信号が送られて選択状態となったときに、ソース線112よりそのTFT113に対応した画素電極114にソース信号が送られることにより画素電極114に電荷が書き込まれ、そして、画素電極114と対向共通電極121との間に形成される液晶容量 $C_{LC}$ 及び補助容量 $C_s$ 、すなわち、これらの画素容量に電荷が充電されるように構成され、その液晶容量 $C_{LC}$ への充電量を操作して液晶層の液晶分子の配向状態を調整し、それによって光の透過度を制御して表示を行うようにしたものである。

【0058】<液晶表示装置の駆動方法1>この液晶表示装置100の第1の駆動方法について説明する。

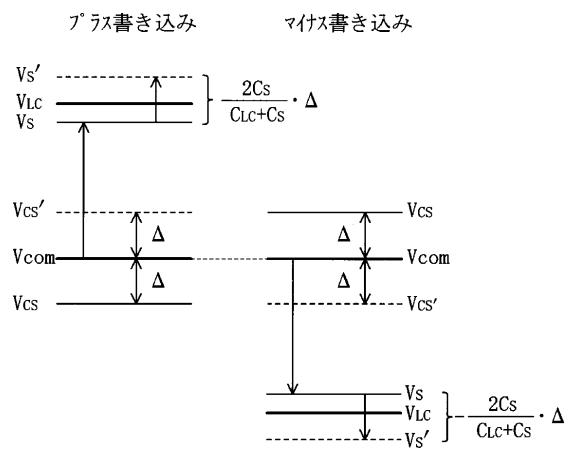

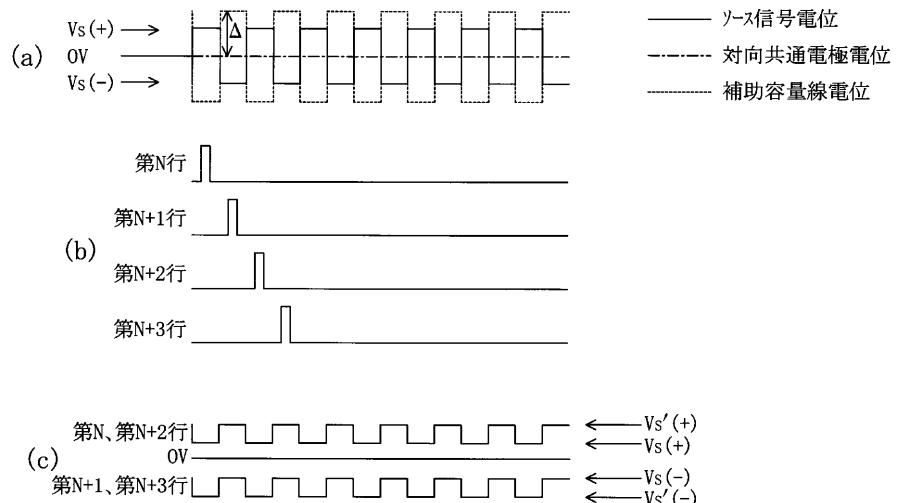

【0059】図3(a)は、ソース線112の電位 $V_s$ 、補助容量線115の電位 $V_{cs}$ 及び対向共通電極121の電位 $V_{com}$ のそれぞれの波形を示す。図3(b)は、第N行～第N+3行の各ゲート線111の電位のそれぞれの波形を示す。図3(c)は、第N行～第N+3行の各行の画素における画素電極114と対向共通電極121との間に印加される電圧のそれぞれの波形を示す。

【0060】第1の駆動方法では、前提として、ゲート電極113aとドレイン電極113cとの間の寄生容量を無視し、対向共通電極121が接地されているものとする。従って、図3(a)に示すように、対向共通電極121の電位 $V_{com}$ は、 $V_{com} = 0V$ (一定)である。

【0061】図3(b)に示すように、第N行～第N+3行のゲート線111にはゲート信号が順次送られる。ゲート信号が送られたとき、その行のTFT113は全てオン状態となって選択状態となり、それによってソース電極113bとドレイン電極113cとが導通される。

【0062】図3(a)に示すように、ソース信号の電位 $V_s$ は交流の矩形波を構成する。TFT113がオン状態となってソース電極113bとドレイン電極113cとが導通された際には、対向共通電極121が接地されていることから、画素電極114と対向共通電極121との間にはソース信号の電位 $V_s$ に等しい信号電圧が印加され、その信号電圧の極性と同じ極性の電荷が画素電極114に書き込まれる。この画素電極114への電荷の書き込みは、フレーム毎に異なる極性の電荷が書き込まれるようにソース信号の制御がなされており、すなわち、液晶表示装置100がいわゆる交流駆動方式とされており、それによって直流電圧が印加されると寿命が

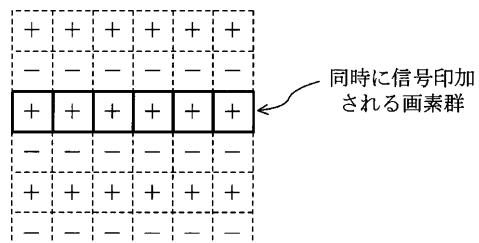

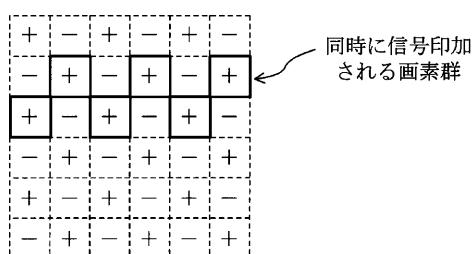

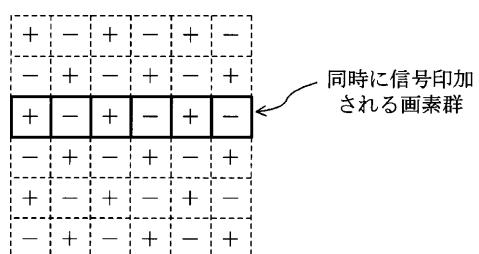

短くなる液晶層の信頼性が高められている。また、例えば図3(a)及び(b)に示すように、第N行及び第N+2行の選択時にはプラス極性の電荷及び第N+1行及び第N+3行の選択時にはマイナス極性の電荷が各行の画素電極114に書き込まれることとなり、同一フレームでの全ての画素電極114への電荷の書き込み後には、電荷の極性分布は、図4に示すように、ゲート線111の延びる方向に配列した画素電極114には全て同一極性の電荷が書き込まれる一方、ソース線112の延びる方向に配列した画素電極114には極性の異なる電荷が交互に書き込まれたものとなり、これによってソース線112の延びる方向でのフリッカーの発生が抑止されることとなる。すなわち、この液晶表示装置100は、Hライン反転駆動方式のものである。

【0063】図3(a)に示すように、補助容量線115の電位 $V_{cs}$ 、すなわち、補助容量 $C_s$ の他端の電位は、中心電位が0V(対向共通電極121の電位 $V_{com}$ )で且つ振幅が( $>0$ )であるソース信号の電位とは逆相の交流の矩形波を構成する。従って、補助容量線115の電位 $V_{cs}$ から対向共通電極121の電位 $V_{com}$ まで $Q_d = C_{LC}(V_s - 0) + C_s[V_s - (\mp \Delta)]$

【0067】で表される。なお、複合符号の上側は画素電極114へのプラス極性の電荷の書き込みのとき、下側は画素電極114へのマイナス極性の書き込みのときにそれぞれ対応する(以下同じ)。

【0068】一方、画素電極114への電荷の書き込み後、それと異なる状態となったとき、すなわち、補助容量 $C_s$ の他端の電位(補助容量線115の電位 $V_{com}'$ )が $Q_d' = C_{LC}(V_s' - 0) + C_s[V_s' - (\pm \Delta)]$

【0070】で表される。ここで、 $V_s'$ は、補助容量 $C_s$ の他端の電位(補助容量線115の電位 $V_{com}$ )が画素電極114への電荷の書き込み時と異なるものとなったときの画素電極114の電位であり、また、 $V_{cs}'$ は、そのときの補助容量線115の電位 $V_{com}'$ である。

$$V_s' = V_s \pm \frac{2C_s}{C_{LC} + C_s} \cdot \Delta$$

【0073】が導かれる。

【0074】対向共通電極121は接地されているので、 $V_s$ 及び $V_s'$ は、画素電極114と対向共通電極121との間に印加される電圧に等しいと考えることができる。従って、画素電極114にプラス極性又はマイナス極性の電荷が書き込まれた後には、補助容量線115の電位 $V_{com}$ が画素電極114への電荷書き込み時と同じときに(プラス極性の書き込みのときには-、マイナス極性の書き込みのときには+)、画素電極114と対向共通電極121との間に $V_s$ の電圧(第1の電圧)が印加される一方、補助容量線115の電位 $V_{com}$ が画素電極114への電荷書き込み時と異なるときに(プラス極性の書き込みのときには+、マイナス極性の書き込み

\* $V_{com}$ を引いた電位差は、+と-との間を大小変化する交流の矩形波の信号電圧となる。この電位差の信号電圧の周波数は、ソース信号の周波数と同一である、すなわち、液晶表示装置100の水平周波数に一致しているので、これによって制御回路の簡略化を図ることができる。また、かかる周波数は、液晶層の液晶分子が応答不能なものであるので、その電位差の変化に起因するフリッカーの発生を防止することができる。

【0064】画素電極114にある電荷が書き込まれて10から次の電荷が書き込まれるまでの動作について図5を参照しながら説明する。

【0065】画素電極114への電荷の書き込み時及びそれと同じ状態となったとき、すなわち、補助容量 $C_s$ の他端の電位(補助容量線115の電位 $V_{com}$ )が画素電極114への電荷の書き込み時と同じものとなったとき(プラス極性の書き込みのときには-、マイナス極性の書き込みのときには+)、ドレイン電極113cの電荷量 $Q_d$ は次の関係式(7)

【0066】

【数13】

$$(7)$$

画素電極114への電荷の書き込み時と異なるものとなったとき(プラス極性の書き込みのときには+、マイナス極性の書き込みのときには-)、ドレイン電極113cの電荷量 $Q_d'$ は下記関係式(8)

【0069】

【数14】

$$(8)$$

【0071】電荷の漏れがないものとすれば、 $Q_d = Q_d'$ とすることができますので、これより、下記関係式(9)

【0072】

【数15】

$$(9)$$

のときには-、画素電極114と対向共通電極121との間に $V_s'$ (第2の電圧)の電圧が印加される。つまり、画素電極114と対向共通電極121との間に印加される電圧が1水平期間毎に $V_s$ と $V_s'$ とに交互に変化することとなる。

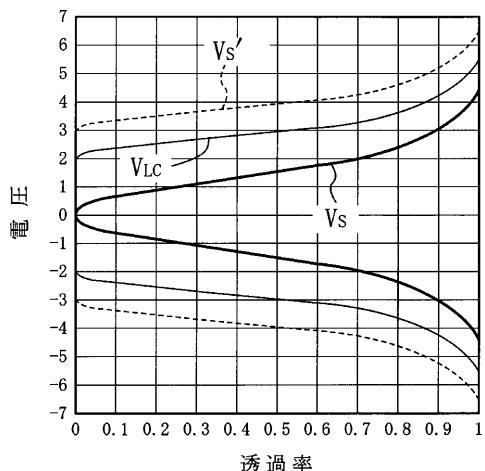

【0075】ここで、図6及び表1に透過率と電圧との関係の一例を示す。透過率が0の場合、 $V_s$ と $V_s'$ とは絶対値が等しく且つ極性が逆となるが、透過率が0よりも高い場合、プラス極性の書き込みでは $V_s < V_s'$ となる一方、マイナス書き込みでは $V_s > V_s'$ となる。従って、第1の電圧である $V_s$ の絶対値が第2の電圧である $V_s'$ の絶対値以下となるということができる。

【表1】

| 透過率   | 液晶+  | Vs+   | Vs'+ | 液晶-   | Vs-   | Vs'-  |

|-------|------|-------|------|-------|-------|-------|

| 0.000 | 1.49 | -1.49 | 1.49 | -1.49 | 1.49  | -1.49 |

| 0.001 | 2.10 | 0.00  | 2.97 | -2.10 | 0.00  | -2.97 |

| 0.004 | 2.16 | 0.13  | 3.05 | -2.16 | -0.13 | -3.05 |

| 0.013 | 2.22 | 0.25  | 3.13 | -2.22 | -0.25 | -3.13 |

| 0.102 | 2.43 | 0.66  | 3.37 | -2.43 | -0.66 | -3.37 |

| 0.208 | 2.58 | 0.93  | 3.53 | -2.58 | -0.93 | -3.53 |

| 0.328 | 2.73 | 1.16  | 3.68 | -2.73 | -1.16 | -3.68 |

| 0.407 | 2.83 | 1.31  | 3.78 | -2.83 | -1.31 | -3.78 |

| 0.516 | 2.98 | 1.53  | 3.93 | -2.98 | -1.53 | -3.93 |

| 0.609 | 3.14 | 1.73  | 4.09 | -3.14 | -1.73 | -4.09 |

| 0.706 | 3.35 | 2.00  | 4.29 | -3.35 | -2.00 | -4.29 |

| 0.806 | 3.67 | 2.38  | 4.61 | -3.67 | -2.38 | -4.61 |

| 0.904 | 4.23 | 3.01  | 5.17 | -4.23 | -3.01 | -5.17 |

| 0.950 | 4.69 | 3.51  | 5.62 | -4.69 | -3.51 | -5.62 |

| 1.000 | 5.49 | 4.37  | 6.42 | -5.49 | -4.37 | -6.42 |

【0076】図3(c)に示すように、第N行及び第N+2行における画素電極114と対向共通電極121との間にはプラス極性のVs及びVs'が交互に印加される一方、第N+1行及び第N+3行における画素電極114と対向共通電極121との間にはマイナス極性のVs及びVs'が交互に印加され、前者にVsが印加されるときと後者にVs'が印加されるときとは一致しており、同様に、前者にVs'が印加されるときと後者にVsが印加されるときも一致している。これは、相互に隣接した\*

$$V_{LC} = \pm \sqrt{\frac{V_s^2 + V_{s'}^2}{2}} \quad (10)$$

【0079】が成立し、これに関係式(9)を代入してVsについて求めると、下記関係式(11)\*

$$V_s = \pm \sqrt{V_{LC}^2 - \left( \frac{C_s}{C_{LC} + C_s} \cdot \Delta \right)^2} \mp \frac{C_s}{C_{LC} + C_s} \cdot \Delta \quad (11)$$

【0081】が導かれる。

【0082】次に、表示の階調を変化させない静止画を表示する場合(液晶容量がC<sub>LC1</sub>のまま維持される場合)と、表示の階調を変化させる動画を表示する場合(液晶容量がC<sub>LC0</sub>からC<sub>LC1</sub>変化する場合)と、について説明する。

【0083】画素電極114への電荷の書き込み時及びそれと同じ状態となったとき、すなわち、補助容量C<sub>s</sub>\*

$$V_{s1} = \pm \sqrt{V_{LC1}^2 - \left( \frac{C_s}{C_{LC1} + C_s} \cdot \Delta \right)^2} \mp \frac{C_s}{C_{LC1} + C_s} \cdot \Delta \quad (12)$$

【0085】に示すものとなる。

【0086】しかしながら、画素電極114への電荷の書き込み後、それと異なる状態となったとき、すなわち、補助容量C<sub>s</sub>の他端の電位(補助容量線115の電位V<sub>cs</sub>)が画素電極114への電荷の書き込み時と異なるものとなったときの画素電極114と対向共通電極121との間に印加される電圧は、それぞれの場合で異なる

$$V_{s11} = V_s \pm \frac{2C_s}{C_{LC1} + C_s} \cdot \Delta \quad (13)$$

【0089】に示すものとなる。

\*画素電極114のそれぞれに極性の異なる電荷が充電されても、すべての補助信号線115が結線されており、どの補助容量C<sub>s</sub>の他端も同一の電位とされることによるものである。

【0077】実際に液晶層に印加される電圧V<sub>LC</sub>は、それらの実効値を考えればよいので、下記関係式(10)

【0078】

【数16】

\*【0080】

【数17】

\*の他端の電位(補助容量線115の電位V<sub>cs</sub>)が画素電極114への電荷の書き込み時と同じものとなったときの画素電極114と対向共通電極121との間に印加される電圧V<sub>s1</sub>は、画素電極114への電荷の書き込み時のソース信号の信号電圧に等しいので、いずれの場合においても、下記関係式(12)

【0084】

【数18】

るものとなる。

【0087】静止画を表示する場合(液晶容量がC<sub>LC1</sub>のまま維持される場合)では、画素電極114と対向共通電極121との間に印加される電圧V<sub>s11</sub>'は、下記関係式(13)

【0088】

【数19】

【0090】一方、動画を表示する場合(液晶容量がC

| 表示             | 黒      | 中間調(50%) | 白     |

|----------------|--------|----------|-------|

| $V_{LC}$       | 1.488  | 3.148    | 5.496 |

| $C_{LC}$       | 1.000  | 1.457    | 1.782 |

| $C_s$          | 1.426  | ←        | ←     |

| $\Delta_{max}$ | 2.532  | ←        | ←     |

| $V_s$          | -1.488 | 1.636    | 4.254 |

| $V_s'$         | 1.488  | 4.140    | 6.505 |

【0111】また、白表示から黒表示、黒表示から中間調表示、黒表示から白表示、中間調表示から黒表示、白表示から中間調表示、及び中間調表示から白表示へのそれぞれの動画表示時の $V_s$ 、 $V_s'$ 、 $V_{LC}$ 及び $V$ を表3及び4示す。これらの値は、関係式(12)、(14)、\*<sup>16</sup>及び<sup>17</sup>算出したものである。

## 【0112】

【表3】

|            | 白→黒    | 黒→中間調 | 黒→白   |

|------------|--------|-------|-------|

| $V_s$      | -1.488 | 1.636 | 4.254 |

| $V_s'$     | 0.762  | 4.612 | 7.230 |

| $V_{LC}$   | 1.182  | 3.460 | 5.932 |

| $\delta V$ | -0.306 | 0.312 | 0.436 |

## 【0113】

## \* \* 【表4】

|            | 中間調→黒  | 白→中間調  | 中間調→白 |

|------------|--------|--------|-------|

| $V_s$      | -1.488 | 1.636  | 4.254 |

| $V_s'$     | 1.016  | 3.887  | 6.759 |

| $V_{LC}$   | 1.274  | 2.982  | 5.647 |

| $\delta V$ | -0.214 | -0.166 | 0.151 |

【0114】表2～4によれば、例えば、黒表示の静止画を表示する場合の $V_{LC} = 1.488$ (V)と白表示から黒表示の動画を表示する場合の $V_{LC} = 1.182$ (V)とが異なり、そのため $V = -0.306$ (V)0となっているのが分かる。補助容量線115の電位 $V_{Cs}$ を変化させなければ、動画を表示する場合も静止画を表示する場合と同じ $V_{LC}$ となるが、この電圧の差があることにより、電荷の移動が促進されることとなる。

## 【0115】同じ液晶表示装置を用い、本発明のように\*

\*補助容量線の電位を変化させた場合と従来のように変化させない場合について、黒表示、中間調表示及び白表示のそれぞれを開始階調として、異なる階調を表示する、すなわち、動画を表示するのに要する応答時間を測定した。補助容量線の電位を変化させた場合の結果を表5に及び変化させなかった場合の結果を表6にそれぞれ示す。

## 【0116】

【表5】

|      |     | 到達階調 |     |    |

|------|-----|------|-----|----|

|      |     | 黒    | 中間調 | 白  |

| 開始階調 | 黒   | /    | 35  | 20 |

|      | 中間調 | 10   | /   | -  |

|      | 白   | 11   | 24  | /  |

単位: ms

## 【0117】

【表6】

|      |     | 到達階調 |     |    |

|------|-----|------|-----|----|

|      |     | 黒    | 中間調 | 白  |

| 開始階調 | 黒   | /    | 22  | 12 |

|      | 中間調 | 7    | /   | -  |

|      | 白   | 8    | 15  | /  |

単位: ms

【0118】表5及び6によれば、いずれの組み合わせの動画を表示する場合も、補助容量線の電位を変化させた場合の方が変化させなかった場合よりも応答時間が短いことが分かる。これは、動画を表示する場合と静止画を表示する場合とで、後者では $V_{LC}$ が同一であるのに対して前者では $V_{LC}$ が異なるために、その電圧の差があることによって電荷の移動が促進されたためであると考えられる。

$$V_s = \pm \sqrt{V_{LC}^2 - \left( \frac{C_s}{C_{total}} \cdot \Delta \right)^2} \mp \frac{C_s}{C_{total}} \cdot \Delta + \frac{C_{gd}}{C_{total}} (V_{gh} - V_{gl}) \quad (20)$$

【0122】で表される。ここで、 $C_{total}$ は $C_{LC} + C_s + C_{gd}$ 、 $V_{gh}$ は選択時のゲート電極113aの電位、 $V_{gl}$ は非選択時のゲート電極113aの電位である。

【0123】また、 $V_s'$ は、 $C_{gd}$ を無視した場合と同

$$V_s' = V_s \pm \frac{2C_s}{C_{LC} + C_s} \cdot \Delta \quad (21)$$

【0125】で表される。

【0126】さらに、液晶容量 $C_{LC}$ に印加される電圧の実効値 $V_{LC}$ も同様に下記関係式(22)

$$V_{LC} = \pm \sqrt{\frac{V_s^2 + V_s'^2}{2}} \quad (22)$$

【0128】で表される。

【0129】そして、液晶分子の応答の加速効果を最大にする $\Delta_{max}$ は、下記関係式(23)

$$\Delta_{max} = \frac{C_{LC\_min} + C_s + C_{gd}}{C_s} \cdot V_{LC\_min} \quad (23)$$

【0131】で表される。

【0132】従って、ゲート電極113aとドレイン電極113cとの間の寄生容量を無視し得ないような場合には、以上の式に基づいてソース信号、補助容量線115(補助容量 $C_s$ の他端)及び対向共通電極121のそれぞれの電位を設定することで、動画を表示するときの良好な応答性を得ることができる。

【0133】<液晶表示装置の駆動方法2>この液晶表示装置100の第2の駆動方法について説明する。

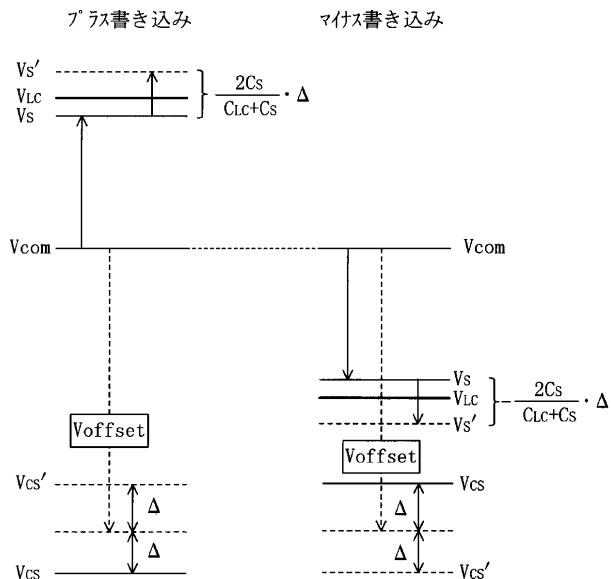

【0134】第2の駆動方法では、図7に示すように、補助容量線115の電位 $V_{cs}$ ( $V_{cs}'$ )の中心が接地された対向共通電極121の電位 $V_{com}$ から $V_{offset}$ だけ低くオフセットされている。その他の駆動方法は第1の駆動方法と同一である。

【0135】この場合、補助容量線115の電位 $V_{cs}$ が

\*【0119】次に、ゲート電極113aとドレイン電極113cとの間の寄生容量 $C_{gd}$ を考慮した場合について説明する。

【0120】この場合について、 $C_{gd}$ を無視した場合と同様の理論展開を行うと、ソース信号の電位 $V_s$ は下記関係式(20)

【0121】

【数26】

\*様に下記関係式(21)

【0124】

【数27】

【0127】

【数28】

20

【0130】

【数29】

(23)

オフセットされているものの駆動態様1と同一の作用が営まれ、同一の効果を得ることができる。

【0136】<液晶表示装置の駆動方法3>この液晶表示装置100の第3の駆動方法について説明する。

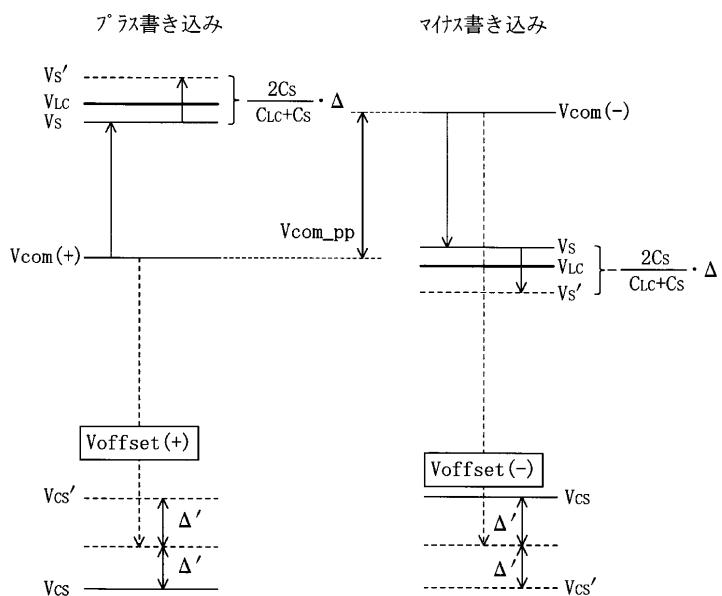

【0137】第3の駆動方法では、図8に示すように、対向共通電極121の電位 $V_{com}$ は、プラス極性の書き込みのときには $V_{com}(+)$ となる一方、マイナス極性の書き込みのときには $V_{com}(-)$ 、すなわち、ピークピーク電圧 $V_{com\_pp}$ で大小変化する矩形波を構成する。また、補助容量線115の電位 $V_{cs}$ は、中心電位が $V_{com}(+)$ から $V_{offset}(+)$ だけ且つ $V_{com}(-)$ から $V_{offset}(-)$ だけ低くオフセットされた電位で且つ振幅が $(+ > 0)$ であるソース信号の電位とは逆相の交流の矩形波を構成する。これにより、補助容量線115の電位 $V_{cs}$ から対向共通電極121の電位 $V_{com}$ を

40

引いた電位差は、 $= ' - V_{com\_pp} / 2$  とすると、ピーカーピーク電圧が 2 で大小変化する矩形波の信号電圧となる。

【0138】この場合でも、駆動態様 1 と同一の作用が営まれ、同一の効果を得ることができる。

【0139】(実施形態 2)

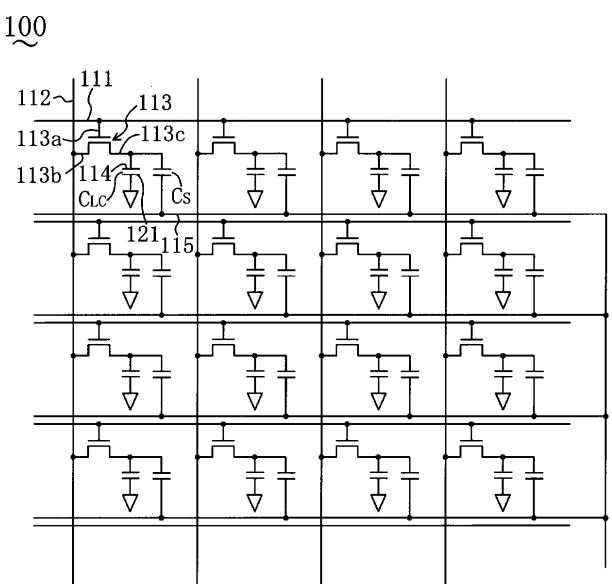

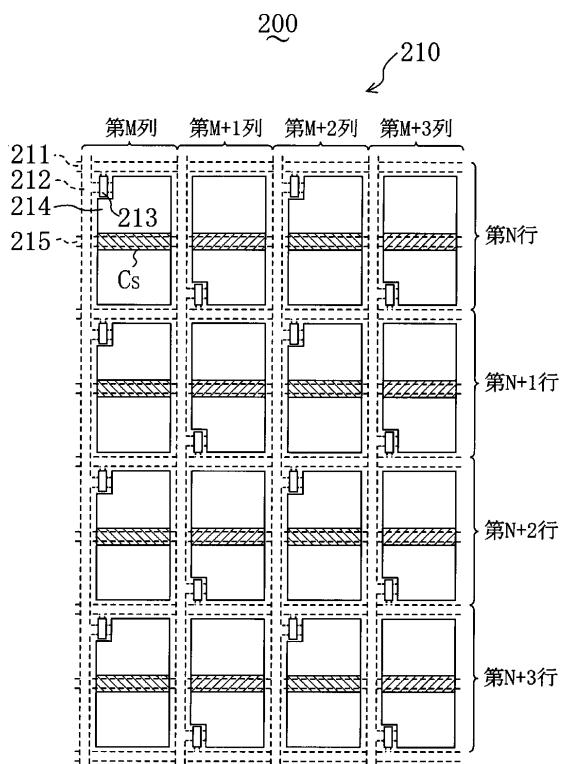

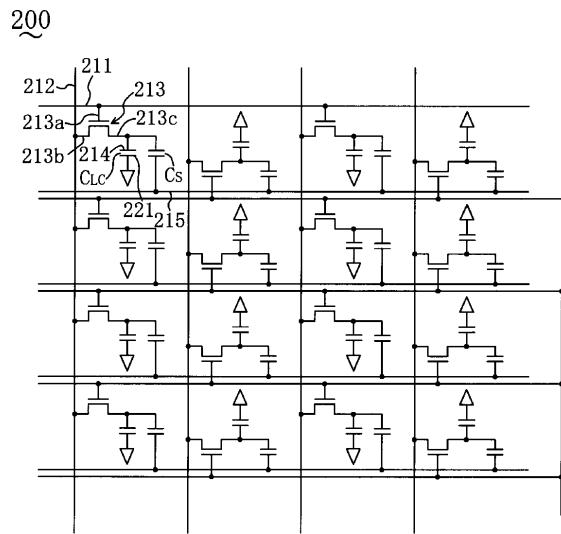

<液晶表示装置の構成> 図 9 及び 10 は、本発明の実施形態 2 に係る液晶表示装置 200 を示す。

【0140】この液晶表示装置 200 では、例えば図 8 及び 9 に示すように、第 N 行・第 M 列の画素電極 214 が TFT213 を介してその画素電極 214 に対応した第 N 行のゲート線 211 に接続されている一方、第 N 行・第 M + 1 列の画素電極 214 が TFT213 を介してその画素電極 214 に対応していない次の行の第 N + 1 行のゲート線 211 に接続されている。つまり、第 M 列、第 M + 2 列、…の画素電極 214 がそれに対応したゲート線 211 に接続されており、第 M + 1 列、第 M + 3 列、…の画素電極 214 がそれに対応していない次の行のゲート線 211 に接続されている。その結果、ゲート線 211 の延びる方向に配列した画素電極 214 は、対応したゲート線 211 に接続されたものと対応していない次の行のゲート線 211 に接続されたものとが交互に並んだものとなっている。

【0141】その他の構成は、実施形態 1 と同一である。

【0142】<液晶表示装置の駆動方法> この液晶表示装置 200 を実施形態 1 と同様に交流駆動すると共に H ライン反転駆動すると、例えば、第 N + 2 行のゲート線 211 にゲート信号が送られたとき、第 M 列、第 M + 2 列、…では、第 N + 2 行の TFT213 が選択状態となつて画素電極 214 に電荷が書き込まれ、第 M + 1 列、第 M + 3 列、…では、第 N + 1 行の TFT213 が選択状態となつて画素電極 214 に電荷が書き込まれることとなる。なお、第 N + 2 行の第 M + 1 列、第 M + 3 列、…のデータはラインメモリに保持される。そして、このとき、画素電極 214 にプラス極性の電荷が書き込まれたものとすると、次に、第 N + 3 行のゲート線 211 にゲート信号が送られたとき、第 M 列、第 M + 2 列、…では、第 N + 3 行の TFT213 が選択状態となつて画素電極 214 にマイナス極性の電荷が書き込まれ、第 M + 1 列、第 M + 3 列、…では、第 N + 2 行の TFT213 が選択状態となつて画素電極 214 にマイナス極性の電荷が書き込まれることとなる。つまり、ゲート線 211 の延びる方向に配列した TFT213 の相互に隣接した TFT213 のそれぞれが異なるゲート線 211 のゲート信号により選択状態とすることにより、ゲート線 211 の延びる方向に相互に隣接した画素電極 214 のそれぞれに極性の異なる電荷が書き込まれることとなる。しかも、これに H ライン反転駆動が組み合わされて、同一フレームでの画素電極 214 への電荷の書き込

み後には、図 11 に示すように、電荷の極性分布は、ゲート線 211 及びソース線 212 のそれぞれの延びる方向に相互に隣接した画素電極 214 のそれぞれに異なる極性の電荷が書き込まれたものとなり、これによってゲート線 211 及びソース線 212 のそれぞれの延びる方向でのフリッカーの発生が抑止されることとなる。

【0143】また、同時に行われる画素電極 214 への電荷の書き込みは同じ極性の書き込みであり、また、補助容量線 215 は全てが繋がれているので、実施形態 1 と同一の補助容量線 215 の電位  $V_{cs}$  の制御がされることにより、動画を表示するときの良好な応答性を得ることができる。

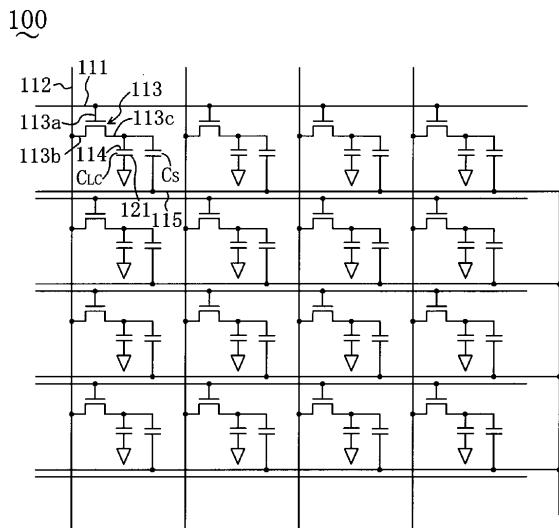

【0144】(実施形態 3)

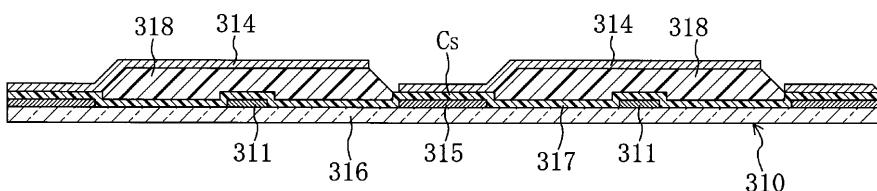

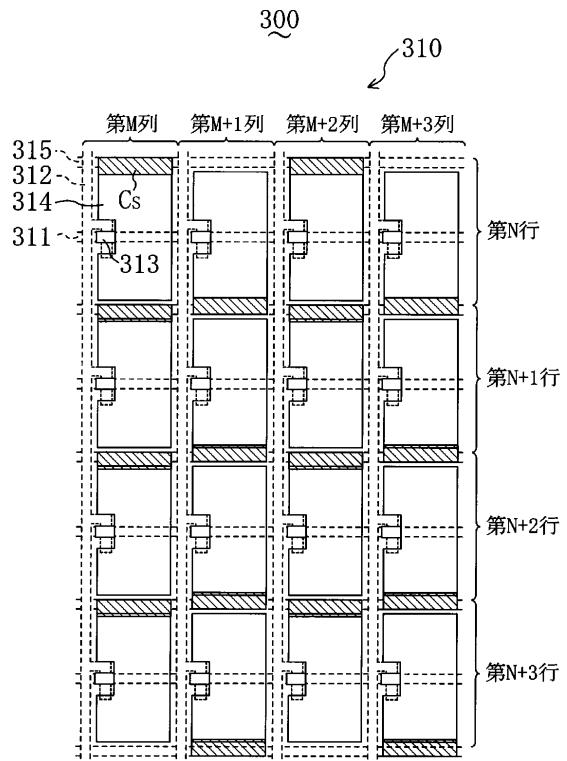

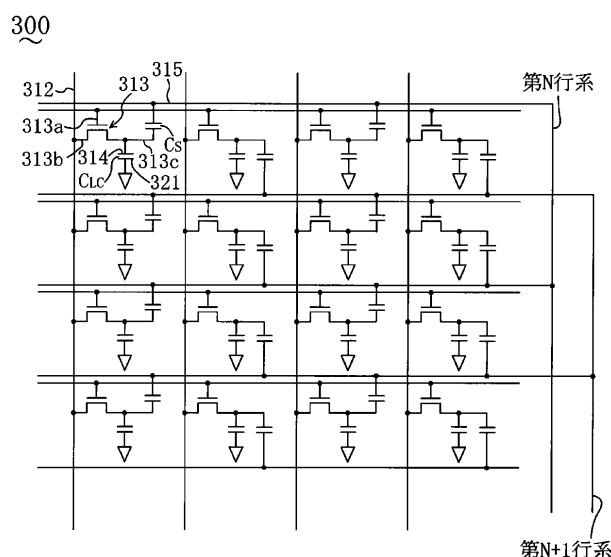

<液晶表示装置の構成> 図 12 及び 13 は、本発明の実施形態 3 に係る液晶表示装置 300 を示す。

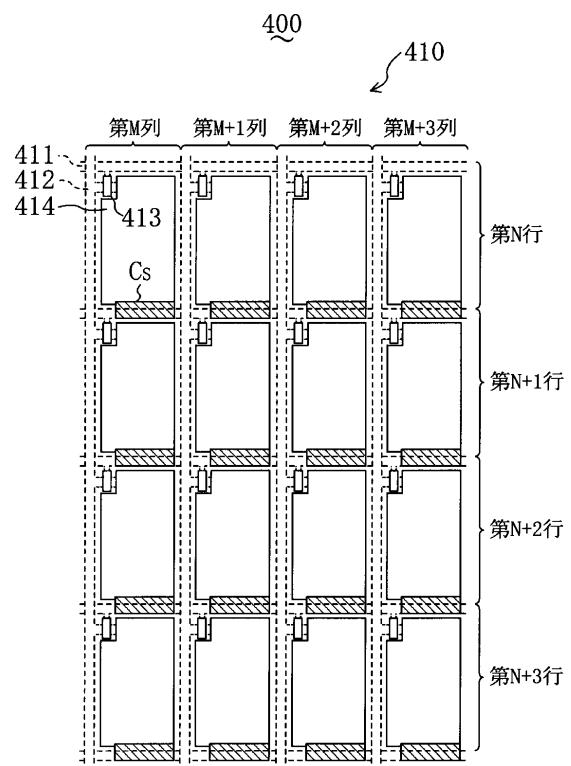

【0145】この液晶表示装置 300 では、相互に隣接する一対の補助容量線 315 及び一対のソース線 312 で囲まれる領域に画素電極 314 が設けられている。各画素電極 314 は、一方の長辺側端中央にスイッチング素子としての TFT313 を有している。そして、例えば図 12 及び 13 に示すように、第 N 行・第 M 列の画素電極 314 の短辺側端部がその画素電極 314 に対応した第 N 行の補助容量線 315 の上に設けられ、図 14 に示すように、それらの間のゲート絶縁膜 317 で補助容量  $C_s$  を形成している一方、第 N 行・第 M + 1 列の画素電極 314 の短辺側端部がその画素電極 314 に対応していない次の行の第 N + 1 行の補助容量線 315 の上に設けられて補助容量  $C_s$  を形成している。つまり、第 M 列、第 M + 2 列、…の画素電極 314 がそれに対応した補助容量線 315 との間で補助容量  $C_s$  を形成しており、第 M + 1 列、第 M + 3 列、…の画素電極 314 がそれに対応していない次の行の補助容量線 315 との間で補助容量  $C_s$  を形成している。その結果、ゲート線 311 の延びる方向に配列した画素電極 314 は、対応した補助容量線 315 との間で補助容量  $C_s$  を形成するものと対応していない次の行の補助容量線 315 との間で補助容量  $C_s$  を形成するものとが交互に並んだものとなっている。また、第 N 行、第 N + 2 行、…の補助容量線 315 が結線されていると共に、第 N + 1 行、第 N + 3 行、…の補助容量線 315 が結線されている。つまり、補助容量線 315 が第 N 行系と第 N + 1 行系の 2 群に分かれている。さらに、画素電極 314 は基板本体 316 上のそれに対応したゲート線 311 の上に設けられているが、それらの間に低誘電率の透明樹脂膜（例えば、比誘電率 = 3、厚さ 3  $\mu m$ ）318 が介設されており、これによって画素電極 314 とゲート線 311 との間に容量が形成されるのが阻止され、画素電極 314 への正常な電荷の書き込みを行うことができる。

【0146】その他の構成は、実施形態 1 と同一である。

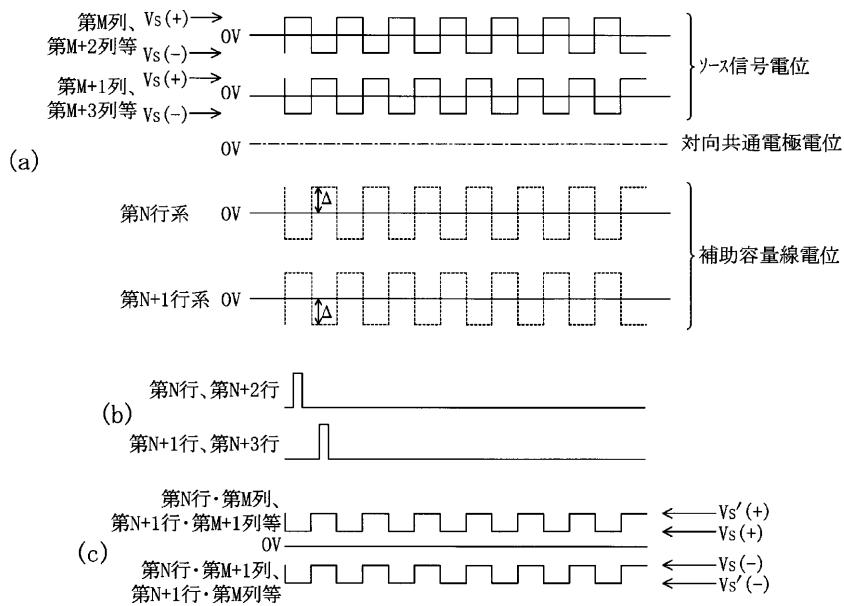

【0147】<液晶表示装置の駆動方法>図15(a)は、ソース線312の電位、補助容量線315の電位 $V_{cs}$ 及び対向共通電極321の電位 $V_{com}$ のそれぞれの波形を示す。図15(b)は、第N行～第N+1行の各ゲート線311の電位のそれぞれの波形を示す。図15(c)は、画素電極314と対向共通電極321との間に印加される電圧の波形を示す。

【0148】この駆動方法では、実施形態1と同様に交流駆動すると共にHライン反転駆動するものではあるが、図15(a)に示すように、第M列、第M+2列、...に送られるソース信号と、それと同時に第M+1列、第M+3列、...に送られるソース信号とが逆相となっている。従って、例えば図15(a)及び(b)に示すように、第N行のゲート線311にゲート信号が送られたとき、第M列、第M+2列、...の画素電極314にはプラス極性の電荷が書き込まれ、第M+1列、第M+3列、...の画素電極314にはマイナス極性の電荷が書き込まれることとなる。そして、次に、第N+1行のゲート線311にゲート信号が送られたとき、第M列、第M+2列、...の画素電極314にはマイナス極性の電荷が書き込まれ、第M+1列、第M+3列、...の画素電極314にはプラス極性の電荷が書き込まれることとなる。つまり、ゲート線311の延びる方向に配列したTFT313が同一のゲート線311のゲート信号により選択状態とされると共にそのTFT313に対応して配列した画素電極314の相互に隣接した画素電極314のそれぞれに逆相のソース信号を送ることにより、ゲート線311の延びる方向に相互に隣接した画素電極314のそれぞれに極性の異なる電荷が書き込まれることとなる。しかも、これにHライン反転駆動が組み合わされて、同一フレームでの画素電極314への電荷の書き込み後には、図16に示すように、電荷の極性分布は、ゲート線311及びソース線312のそれぞれの延びる方向に相互に隣接した画素電極314のそれぞれに異なる極性の電荷が書き込まれたものとなり、これによってゲート線311及びソース線312のそれぞれの延びる方向でのフリッカーの発生が抑止されることとなる。また、ゲート線311の延びる方向に配列したTFT313を同一のゲート線311のゲート信号により選択状態とするようにしている、すなわち、それらのTFT313に対応した画素電極314に同時に電荷の書き込みを行うようにしているので、ゲート線311の延びる方向に配列したTFT313を分類してそれぞれ異なるゲート線311のゲート信号により選択状態とする場合に必要となるラインメモリが不要である。

【0149】上記した液晶表示装置300の構成より、同一フレームでの画素電極314への電荷の書き込みの際に極性の同じ電荷が書き込まれる画素電極314に対応した補助容量 $C_s$ の他端が接続された補助容量線315同士が結線されているということができる。また、補

\*助容量線315の電位 $V_{cs}$ 、すなわち、補助容量 $C_s$ の他端の電位は、図15(a)に示すような矩形波を構成し、対向共通電極321が接地されているので、補助容量線315の電位 $V_{cs}$ から対向共通電極321の電位 $V_{com}$ を引いた電位差は、補助容量線315の電位 $V_{cs}$ に等しい振幅である交流の矩形波の信号電圧となる。そして、各画素においては、画素電極314に送られるソース信号とその交流の電位差とが逆相となる。従って、例えば図15(c)に示すように、プラス極性の電荷が書き込まれた第N行・第M列、第N+1行・第M+1列等における画素電極314と対向共通電極321との間にはプラス極性の電圧 $V_s$ 及び $V_s'$ が交互に印加され、マイナス極性の電荷が書き込まれた第N行・第M+1列、第N+1行・第M列等における画素電極314と対向共通電極321との間にはマイナス極性の電圧 $V_s$ 及び $V_s'$ が交互に印加されることとなり、各画素毎に見れば、実施形態1及び2と同様の補助容量 $C_s$ の他端の電位の制御がされることにより、動画を表示するときの良好な応答性を得ることができる。

【0150】(実施形態4)

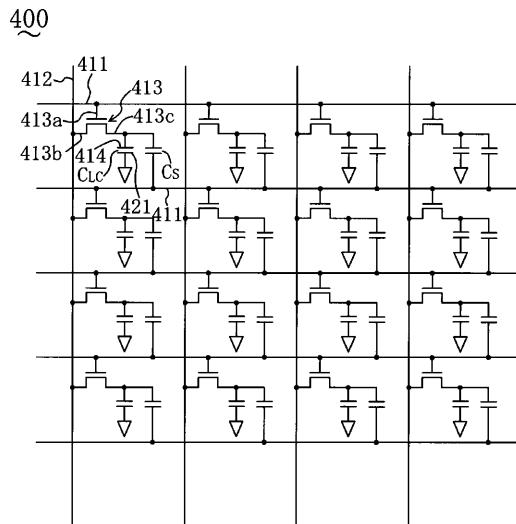

<液晶表示装置の構成>図17及び18は、本発明の実施形態4に係る液晶表示装置400を示す。

【0151】この液晶表示装置400では、例えば図16及び17に示すように、第N行の画素電極414の短辺部が第N+1行のゲート線411の上に設けられていることにより、それらの間に補助容量 $C_s$ が形成されており、独立した補助容量線が設けられていない。すなわち、この液晶表示装置400は、 $C_s$ -on-Gate型のものである。

【0152】その他の構成は、実施形態1と同一である。

【0153】<液晶表示装置の駆動方法>以上の液晶表示装置400は、図7及び8における補助容量線の電位を、画素電極414に電荷が書き込まれる行の次行のゲート線411の電位に読み替え、オフセット電圧を調整してゲート線411の電位を非選択電位(例えば、典型的には-15~-5V)に調整することにより実施形態1と同様の駆動を行うことができ、それによって動画を表示するときの良好な応答性を得ることができる。

【0154】

【発明の効果】以上説明したように、本発明によれば、同一階調を表示する場合でも、静止画を表示するときと動画を表示するときとで液晶容量に実質的に印加される電圧が異なるものとなり、その電圧の差により液晶分子の応答を加速させることができるので、表示の階調を変化させて動画を表示したときの応答性を優れたものとすことができる。

【図面の簡単な説明】

【図1】実施形態1に係る液晶表示装置のTFT基板の正面図である。

【図2】実施形態1に係る液晶表示装置の等価回路図である。

【図3】(a)は、ソース線の電位、補助容量線の電位及び対向共通電極の電位のそれぞれの波形を示す図であり、(b)は、第N行～第N+3行の各ゲート線の電位のそれぞれの波形を示す図であり、(c)は、第N行～第N+3行の各行の画素における画素電極と対向共通電極との間に印加される電圧の波形を示す図である。

【図4】実施形態1の1フレームの画素電極への電荷の書き込み後の電荷の極性の分布を示す説明図である。

【図5】実施形態1に係る液晶表示装置の第1の駆動方法の説明図である。

【図6】透過率と電圧との関係を示すグラフである。

【図7】実施形態1に係る液晶表示装置の第2の駆動方法の説明図である。

【図8】実施形態1に係る液晶表示装置の第3の駆動方法の説明図である。

【図9】実施形態2に係る液晶表示装置のTFT基板の正面図である。

【図10】実施形態2に係る液晶表示装置の等価回路図である。

【図11】実施形態2の1フレームの画素電極への電荷の書き込み後の電荷の極性の分布を示す説明図である。

【図12】実施形態3に係る液晶表示装置のTFT基板の正面図である。

【図13】実施形態3に係る液晶表示装置の等価回路図である。

【図14】実施形態3に係る液晶表示装置のTFT基板の部分断面図である。

【図15】(a)は、ソース線の電位、補助容量線の電位及び対向共通電極の電位のそれぞれの波形を示す図で\*

\*あり、(b)は、第N行～第N+1行の各ゲート線の電位のそれぞれの波形を示す図であり、(c)は、画素電極と対向共通電極との間に印加される電圧の波形を示す図である。

【図16】実施形態3の1フレームの画素電極への電荷の書き込み後の電荷の極性の分布を示す説明図である。

【図17】実施形態3に係る液晶表示装置のTFT基板の正面図である。

【図18】実施形態3に係る液晶表示装置の等価回路図である。

#### 【符号の説明】

100, 200, 300, 400 液晶表示装置

110, 210, 310, 410 TFT基板(素子側基板)

111, 211, 311, 411 ゲート線

112, 212, 312, 412 ソース線

113, 213, 313, 413 TFT(スイッチング素子)

113a, 213a, 313a, 413a ゲート電極

113b, 213b, 313b, 413b ソース電極

113c, 213c, 313c, 413c ドレイン電極

114, 214, 314, 414 画素電極

115, 215, 315, 415 補助容量線

121, 221, 321, 421 対向共通電極(対向電極)

316 基板本体

317 ゲート絶縁膜

318 透明樹脂膜

30  $C_{LC}$  液晶容量

$C_s$  補助容量

【図2】

【図4】

【図1】

### 【図5】

【図3】

【図11】

〔図16〕

【図6】

【図7】

【図8】

【図9】

【図14】

【図10】

【図12】

【図13】

【図17】

【図15】

【図18】

F ターム(参考) 2H092 JA24 JA37 JA41 JB69 NA05

PA01 PA02 PA08 PA10 PA11

PA12 QA07

2H093 NA16 NC34 ND06 ND10 ND32

NE01 NF05

5C006 AA01 AA16 AC24 AC27 BB16

BC06 FA14 FA23 FA56 GA02

5C080 AA10 BB05 CC03 DD06 DD08

EE19 EE29 FF11 JJ02 JJ04

JJ05 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 驱动液晶显示装置的方法及其液晶显示装置                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| 公开(公告)号        | <a href="#">JP2003279929A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 公开(公告)日 | 2003-10-02 |

| 申请号            | JP2002083527                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 申请日     | 2002-03-25 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| [标]发明人         | 宫地弘一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 发明人            | 宫地 弘一                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

| IPC分类号         | G02F1/1368 G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| CPC分类号         | G09G3/3648 G09G3/3614 G09G3/3655 G09G2300/0876 G09G2320/0252 G09G2320/0261                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| FI分类号          | G02F1/133.550 G02F1/1368 G09G3/20.621.F G09G3/20.623.Y G09G3/20.624.D G09G3/36 G02F1/133.570                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| F-TERM分类号      | 2H092/JA24 2H092/JA37 2H092/JA41 2H092/JB69 2H092/NA05 2H092/PA01 2H092/PA02 2H092/PA08 2H092/PA10 2H092/PA11 2H092/PA12 2H092/QA07 2H093/NA16 2H093/NC34 2H093/ND06 2H093/ND10 2H093/ND32 2H093/NE01 2H093/NF05 5C006/AA01 5C006/AA16 5C006/AC24 5C006/AC27 5C006/BB16 5C006/BC06 5C006/FA14 5C006/FA23 5C006/FA56 5C006/GA02 5C080/AA10 5C080/BB05 5C080/CC03 5C080/DD06 5C080/DD08 5C080/EE19 5C080/EE29 5C080/FF11 5C080/JJ02 5C080/JJ04 5C080/JJ05 5C080/JJ06 2H092/PA06 2H093/NC18 2H093/NC35 2H192/AA24 2H192/AA42 2H192/CC04 2H192/CC26 2H192/DA02 2H192/DA12 2H192/GD61 2H193/ZA04 2H193/ZA07 2H193/ZA08 2H193/ZB14 2H193/ZC04 2H193/ZC13 2H193/ZC36 2H193/ZF59 2H193/ZP01 2H193/ZQ06 |         |            |

| 其他公开文献         | JP3924485B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

### 摘要(译)

解决的问题：提供一种新颖的AC驱动型有源矩阵型液晶显示装置的驱动方法，该方法在显示运动图像时响应性极好。液晶显示装置100是交流驱动方式的有源矩阵方式。从辅助电容C小号另一端的电势减去对电极121的电势获得的电势差反复变化，并且同时电势差与电荷写入像素电极114，像素电极114和对电极的电势差相同。当施加在像素电极114和第二电极121之间的第一电压的绝对值不同于当电荷被写入像素电极114中时施加的第一电压的绝对值时，施加在像素电极114和对电极121之间的第二电压。将源信号的电位，辅助电容C的另一端 小号 和对电极121的电位设定为等于或小于电压的绝对值。