(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3744818号

(P3744818)

(45) 発行日 平成18年2月15日(2006.2.15)

(24) 登録日 平成17年12月2日(2005.12.2)

(51) Int.CI.

F 1

|             |              |                  |             |              |             |

|-------------|--------------|------------------|-------------|--------------|-------------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/36</b>  |             |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | <b>G02F</b> | <b>1/133</b> | <b>550</b>  |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | <b>G09G</b> | <b>3/20</b>  | <b>611A</b> |

|             |              |                  | <b>G09G</b> | <b>3/20</b>  | <b>621E</b> |

請求項の数 10 (全 30 頁)

(21) 出願番号

特願2001-155193 (P2001-155193)

(22) 出願日

平成13年5月24日 (2001.5.24)

(65) 公開番号

特開2002-351412 (P2002-351412A)

(43) 公開日

平成14年12月6日 (2002.12.6)

審査請求日

平成16年1月15日 (2004.1.15)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100090387

弁理士 布施 行夫

(74) 代理人 100090398

弁理士 大渕 美千栄

(72) 発明者 森田 晶

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 西島 篤宏

最終頁に続く

(54) 【発明の名称】信号駆動回路、表示装置、及び電気光学装置

## (57) 【特許請求の範囲】

## 【請求項 1】

互いに交差する複数の走査ライン及び複数の信号ラインにより特定される画素を有する電気光学装置の信号ラインを、画像データに基づいて駆動する信号駆動回路であって、

水平走査周期で、画像データをラッチするラインラッチと、

順次供給される前記画像データをシフトして一水平走査単位の画像データを前記ラインラッチに供給するシフトレジスタと、

所与のシフト方向切り替え信号に基づいて、前記シフトレジスタのシフト方向を切り替える手段と、

前記ラインラッチにラッチされた画像データに基づいて、信号ラインごとに駆動電圧を生成する駆動電圧生成手段と、

前記駆動電圧生成手段によって生成された駆動電圧に基づいて、各信号ラインを駆動する信号ライン駆動手段と、

所与の複数の信号ラインごとに分割されたブロックを単位として、画像データに基づく信号ラインへの出力可否を示すパーシャル表示データを保持するパーシャル表示データ保持手段と、

前記所与のシフト方向の切り替え信号に基づいて、前記パーシャル表示データ保持手段に保持されたブロック単位のパーシャル表示データの並びを逆に入れ替えるデータ入れ替え手段と、

を含み、

10

20

前記信号ライン駆動手段は、

前記データ入れ替え手段から供給されたパーシャル表示データに基づいて、前記プロック単位に信号ラインの駆動電圧の出力制御を行うことを特徴とする信号駆動回路。

#### 【請求項 2】

互いに交差する複数の走査ライン及び複数の信号ラインにより特定される画素を有する電気光学装置の信号ラインを、画像データに基づいて駆動する信号駆動回路であって、

水平走査周期で、画像データをラッチするラインラッチと、

前記ラインラッチにラッチされた画像データに基づいて、信号ラインごとに駆動電圧を生成する駆動電圧生成手段と、

前記駆動電圧生成手段によって生成された駆動電圧に基づいて、各信号ラインを駆動する信号ライン駆動手段と、

所与の複数の信号ラインごとに分割されたプロックを単位として、画像データに基づく信号ラインへの出力可否を示すパーシャル表示データを保持するパーシャル表示データ保持手段と、

を含み、

前記信号ライン駆動手段は、

前記駆動電圧生成手段によって生成された駆動電圧をインピーダンス変換し、各信号ラインに出力するインピーダンス変換手段と、

前記信号ラインに所与の非表示レベル電圧を生成する非表示レベル電圧供給手段と、

を含み、

各信号ラインは、前記パーシャル表示データに基づいて、プロック単位で、前記インピーダンス変換手段又は前記非表示レベル電圧供給手段のうちいずれか一方により駆動されることを特徴とする信号駆動回路。

#### 【請求項 3】

請求項 2において、

前記インピーダンス変換手段は、

前記パーシャル表示データにより出力がオンに指定されたプロックの信号ラインに対し、前記駆動電圧をインピーダンス変換して出力し、

前記パーシャル表示データにより出力がオフに指定されたプロックの信号ラインを、ハイインピーダンス状態にし、

前記非表示レベル電圧供給手段は、

前記パーシャル表示データにより出力がオンに指定されたプロックの信号ラインを、ハイインピーダンス状態にし、

前記パーシャル表示データにより出力がオフに指定されたプロックの信号ラインに対し、所与の非表示レベル電圧を供給することを特徴とする信号駆動回路。

#### 【請求項 4】

請求項 1乃至 3のいずれかにおいて、

前記駆動電圧生成手段は、

前記パーシャル表示データにより出力がオフに指定されたプロックの信号ラインを駆動するための駆動電圧の生成動作を停止することを特徴とする信号駆動回路。

#### 【請求項 5】

請求項 2乃至 4のいずれかにおいて、

前記電気光学装置は、画素に対応して、前記走査ラインと前記信号ラインに接続されたスイッチング手段を介して設けられた画素電極を有し、

前記非表示レベルの電圧は、

前記画素電極の印加電圧と、前記画素電極と電気光学素子を介して設けられた対向電極との電圧差を、所与の閾値より小さくする電圧であることを特徴とする信号駆動回路。

#### 【請求項 6】

請求項 2乃至 4のいずれかにおいて、

前記電気光学装置は、画素に対応して、前記走査ラインと前記信号ラインに接続された

10

20

30

40

50

スイッチング手段を介して設けられた画素電極を有し、

前記非表示レベルの電圧は、

前記画素電極と電気光学素子を介して設けられた対向電極と同等の電圧であることを特徴とする信号駆動回路。

**【請求項 7】**

請求項 2 乃至 4 のいずれかにおいて、

前記非表示レベルの電圧は、

前記画像データに基づいて生成可能な階調電圧の最大値又は最小値のいずれか一方であることを特徴とする信号駆動回路。

**【請求項 8】**

10

請求項 1 乃至 7 のいずれかにおいて、

前記ブロック単位は、8 ピクセル単位であることを特徴とする信号駆動回路。

**【請求項 9】**

互いに交差する複数の走査ライン及び複数の信号ラインにより特定される画素を有する表示パネルと、

前記走査ラインを走査駆動する走査駆動回路と、

画像データに基づいて、前記信号ラインを駆動する請求項 1 乃至 8 いずれか記載の信号駆動回路と、

を含むことを特徴とする表示装置。

**【請求項 10】**

20

互いに交差する複数の走査ライン及び複数の信号ラインにより特定される画素と、

前記走査ラインを走査駆動する走査駆動回路と、

画像データに基づいて、前記信号ラインを駆動する請求項 1 乃至 8 いずれか記載の信号駆動回路と、

を含むことを特徴とする電気光学装置。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、信号駆動回路、これを用いた表示装置、電気光学装置及び信号駆動方法に関する。30

30

**【0002】**

**【背景技術及び発明が解決しようとする課題】**

例えば携帯電話機のような電子機器の表示部には、液晶パネルが用いられており、電子機器の低消費電力化や小型軽量化等が図られている。この液晶パネルについては、近年の携帯電話機の普及によって情報性の高い静止画や動画が配信されるようになると、その高画質化が要求されるようになっている。

**【0003】**

40

電子機器の表示部の高画質化を実現する液晶パネルとして、薄膜トランジスタ (Thin Film Transistor: 以下、TFTと略す。) 液晶を用いたアクティブマトリクス型液晶パネルが知られている。TFT 液晶を用いたアクティブマトリクス型液晶パネルは、ダイナミック駆動による STN (SuperTwisted Nematic) 液晶を用いた単純マトリクス型液晶パネルに比べて、高速応答、高コントラストを実現し、動画等の表示に適している。

**【0004】**

しかしながら、TFT 液晶を用いたアクティブマトリクス型液晶パネルは、消費電力が大きく、携帯電話機のようなバッテリ駆動が行われる携帯型の電子機器の表示部として採用することが困難とされている。

**【0005】**

本発明は以上のような技術的課題に鑑みてなされたものであり、その目的とするところは、高画質化と低消費電力化とを両立させ、アクティブマトリクス型液晶パネルに好適な信号駆動回路、これを用いた表示装置、及び電気光学装置を提供することにある。

50

**【0006】****【課題を解決するための手段】**

上記課題を解決するために本発明は、互いに交差する複数の走査ライン及び複数の信号ラインにより特定される画素を有する電気光学装置の信号ラインを、画像データに基づいて駆動する信号駆動回路であって、水平走査周期で、画像データをラッチするラインラッチと、前記ラインラッチにラッチされた画像データに基づいて、信号ラインごとに駆動電圧を生成する駆動電圧生成手段と、前記駆動電圧生成手段によって生成された駆動電圧に基づいて、各信号ラインを駆動する信号ライン駆動手段と、所与の複数の信号ラインごとに分割されたブロックを単位として、画像データに基づく信号ラインへの出力可否を示すパーシャル表示データを保持するパーシャル表示データ保持手段とを含み、前記信号ライン駆動手段は、前記パーシャル表示データに基づいて、前記ブロック単位に信号ラインの駆動電圧の出力制御を行うことを特徴とする。

10

**【0007】**

ここで、電気光学装置としては、例えば互いに交差する複数の走査ライン及び複数の信号ラインと、前記走査ラインと前記信号ラインに接続されたスイッチング手段と、前記スイッチング手段に接続された画素電極とを有するように構成しても良い。

**【0008】**

また、ブロック単位に分割される信号ラインは、互いに隣接した複数の信号ラインであっても良いし、任意に選択された複数の信号ラインであっても良い。

**【0009】**

信号ラインの駆動電圧の出力制御とは、例えば画像データに基づいて生成された駆動電圧で信号ラインを駆動するか否かや、当該駆動電圧に代えて所与の電圧で信号ラインを駆動することを制御することをいう。

20

**【0010】**

本発明によれば、電気光学装置の信号ラインを、画像データに基づいて駆動する信号駆動回路に、所与の複数の信号ラインごとに分割されたブロックを単位として、画像データに基づく信号ラインへの出力可否を示すパーシャル表示データを保持するパーシャル表示データ保持手段を備えさせるとともに、このブロック単位に指定されたパーシャル表示データに基づいて、ブロック単位に信号ラインに供給する駆動電圧の出力制御を行うようにしたので、任意に設定可能なパーシャル表示制御を行うことができるようになる。これにより、非表示エリアの信号駆動による電力消費を削減することができる。

30

**【0011】**

また本発明は、順次供給される前記画像データをシフトして一水平走査単位の画像データを前記ラインラッチに供給するシフトレジスタと、所与のシフト方向切り替え信号に基づいて、前記シフトレジスタのシフト方向を切り替える手段と、前記所与のシフト方向の切り替え信号に基づいて、前記パーシャル表示データ保持手段に保持されたブロック単位のパーシャル表示データの並びを逆に入れ替えるデータ入れ替え手段とを含み、前記信号ライン駆動手段は、前記データ入れ替え手段から供給されたパーシャル表示データに基づいて、前記ブロック単位に信号ラインの駆動電圧の出力制御を行うことを特徴とする。

**【0012】**

40

ここで、シフト方向とは、例えば所与の単位で順次入力される画像データを、一水平走査単位でラインラッチにラッチする際に、当該入力される画像データを順次取り込むシフトレジスタにおけるシフト方向をいう。

**【0013】**

本発明においては、実装状態に応じてシフト方向を切り替えて画像データを入力するためのシフト方向の切り替え信号を用いて、ブロックごとに画像データに基づく信号ラインの駆動を行うか否かを示すパーシャル表示データの並び順を逆に入れ替えるようにした。これにより、ユーザは、実装状態に応じたデータの並びを意識することなく、画像データを本発明に係る信号駆動回路に供給するだけでよいので、ユーザの使い勝手が向上して開発工数の削減に貢献することができる。

50

**【0014】**

また本発明は、前記信号ライン駆動手段は、前記駆動電圧生成手段によって生成された駆動電圧をインピーダンス変換し、各信号ラインに出力するインピーダンス変換手段と、前記信号ラインに所与の非表示レベル電圧を供給する非表示レベル電圧供給手段とを含み、各信号ラインは、前記パーシャル表示データに基づいて、ブロック単位で、前記インピーダンス変換手段又は前記非表示レベル電圧供給手段のうちいずれか一方により駆動されることを特徴とする。

**【0015】**

本発明によれば、パーシャル表示データに設定された内容に基づいて、ブロック単位で、インピーダンス変換手段による画像データに基づく信号ラインの駆動、若しくは非表示レベル電圧供給手段による信号ラインへの所与の非表示レベル電圧の供給のいずれかを行うようにしたので、非表示エリアを所与のノーマリ色に設定することができる。これにより、上述した効果に加えて、パーシャル表示制御により設定される表示エリアを際立たせることができる。

**【0016】**

また本発明は、前記インピーダンス変換手段は、前記パーシャル表示データにより出力がオンに指定されたブロックの信号ラインに対し、前記駆動電圧をインピーダンス変換して出力し、前記パーシャル表示データにより出力がオフに指定されたブロックの信号ラインを、ハイインピーダンス状態にし、前記非表示レベル電圧供給手段は、前記パーシャル表示データにより出力がオンに指定されたブロックの信号ラインを、ハイインピーダンス状態にし、前記パーシャル表示データにより出力がオフに指定されたブロックの信号ラインに対し、所与の非表示レベル電圧を供給することを特徴とする。

**【0017】**

また本発明は、前記駆動電圧生成手段は、前記パーシャル表示データにより出力がオフに指定されたブロックの信号ラインを駆動するための駆動電圧の生成動作を停止することを特徴とする。

**【0018】**

本発明によれば、パーシャル表示データに基づいて、ブロック単位に、非表示エリアに設定されたブロックの駆動電圧生成手段を制御することができるので、非表示エリアに設定されたブロックの電力消費を効果的に抑えることができ、パーシャル表示制御による低消費化をより一層促進することができる。

**【0019】**

また本発明は、前記電気光学装置は、画素に対応して、前記走査ラインと前記信号ラインに接続されたスイッチング手段を介して設けられた画素電極を有し、前記非表示レベルの電圧は、前記画素電極の印加電圧と、前記画素電極と電気光学素子を介して設けられた対向電極との電圧差を、所与の閾値より小さくする電圧であることを特徴とする。

**【0020】**

本発明によれば、走査ラインと信号ラインに接続されたスイッチング手段を介して設けられた画素電極の印加電圧と、この画素電極と電気光学素子を介して設けられた対向電極との電圧差を、所与の閾値より小さくするような非表示レベル電圧を設定するようにしたので、少なくとも電気光学装置の画素の透過率が変化しない範囲で非表示エリアを設定することができ、非表示レベル電圧の精度に依存することなくパーシャル表示制御の簡素化を図ることができる。

**【0021】**

また本発明は、前記電気光学装置は、画素に対応して、前記走査ラインと前記信号ラインに接続されたスイッチング手段を介して設けられた画素電極を有し、前記非表示レベルの電圧は、前記画素電極と電気光学素子を介して設けられた対向電極と同等の電圧であることを特徴とする。

**【0022】**

本発明によれば、画素電極と、これに対向する対向電極との電圧差がほぼ0になるように

10

20

30

40

50

非表示レベル電圧を設定するようにしたので、パーシャル表示制御の簡素化を図ると共に、非表示エリアの表示色を一定させ、表示エリアを際立たせるような画像表示が可能となる。

【0023】

また本発明は、前記非表示レベルの電圧は、前記画像データに基づいて生成可能な階調電圧の最大値及び最小値のいずれか一方であることを特徴とする。

【0024】

本発明によれば、非表示レベルの電圧として、駆動電圧生成手段で生成可能な階調電圧の両端の電圧のいずれかを一方を供給するようにしたので、ユーザは任意に非表示エリアのノーマリ色を指定することができ、ユーザにとっての使い勝手を向上させることができる

10。

【0025】

また本発明は、前記ブロック単位は、8ピクセル単位であることを特徴とする。

【0026】

本発明によれば、キャラクタ文字単位で表示エリアと非表示エリアの設定が可能となり、パーシャル表示制御の簡素化と、効果的なパーシャル表示による画像を提供することができる。

【0027】

また本発明に係る表示装置は、互いに交差する複数の走査ライン及び複数の信号ラインにより特定される画素を有する表示パネルと、前記走査ラインを走査駆動する走査駆動回路と、画像データに基づいて、前記信号ラインを駆動する上記いずれか記載の信号駆動回路とを含むことを特徴とする。

20

【0028】

本発明によれば、パーシャル表示制御による低消費電力化を実現する表示装置を提供することができ、例えばアクティブマトリクス型液晶パネルを適用することで、高画質なパーシャル表示をも実現することができる。

【0029】

また本発明に係る電気光学装置は、互いに交差する複数の走査ライン及び複数の信号ラインにより特定される画素と、前記走査ラインを走査駆動する走査駆動回路と、画像データに基づいて、前記信号ラインを駆動する上記いずれか記載の信号駆動回路とを含むことを特徴とする。

30

【0030】

本発明によれば、パーシャル表示制御による低消費電力化を実現する電気光学装置を提供することができ、例えばアクティブマトリクス型液晶パネルに適用することで、高画質なパーシャル表示をも実現することができる。

【0031】

また本発明は、水平走査周期で、画像データをラッチするラインラッチと、前記ラインラッチにラッチされた画像データに基づいて、信号ラインごとに駆動電圧を生成する駆動電圧生成手段と、前記駆動電圧生成手段によって生成された駆動電圧に基づいて、各信号ラインを駆動する信号ライン駆動手段とを有し、互いに交差する複数の走査ライン及び複数の信号ラインとにより特定される画素を有する電気光学装置の信号ラインを駆動する信号駆動回路の信号駆動方法であって、所与の複数の信号ラインごとに分割されたブロックを単位に画像データに基づく信号ラインへの出力可否を示すパーシャル表示データに基づいて、ブロック単位に前記信号ライン駆動手段の信号ラインへの駆動電圧の出力制御を行うことを特徴とする。

40

【0032】

本発明によれば、ブロック単位にパーシャル表示を制御することができるので、制御回路の簡素化と、低消費電力化とを図ることができ、例えばアクティブマトリクス型液晶パネルに適用することで、高画質なパーシャル表示をも実現することができる。

【0033】

10

20

30

40

50

**【発明の実施の形態】**

以下、本発明の好適な実施の形態について図面を用いて詳細に説明する。

**【0034】**

1. 表示装置

1.1 表示装置の構成

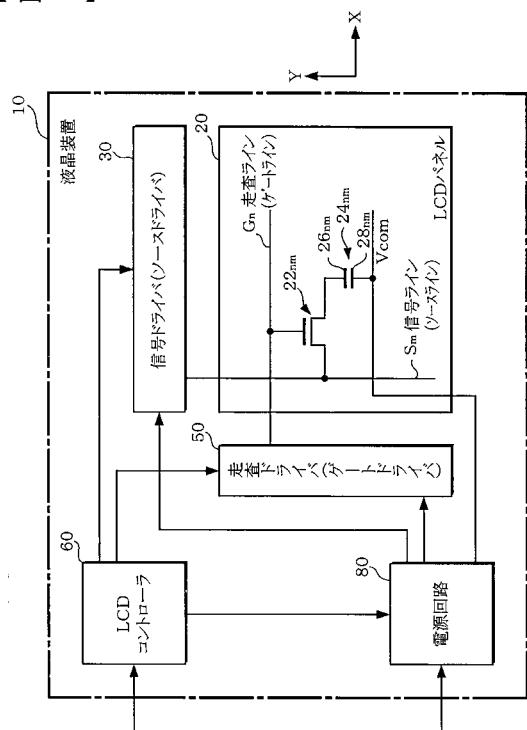

図1に、本実施形態における信号駆動回路（信号ドライバ）を適用した表示装置の構成の概要を示す。

**【0035】**

表示装置としての液晶装置10は、液晶ディスプレイ（Liquid Crystal Display：以下、LCDと略す。）パネル20、信号ドライバ（信号駆動回路）（狭義には、ソースドライバ）30、走査ドライバ（走査駆動回路）（狭義には、ゲートドライバ）50、LCDコントローラ60、電源回路80を含む。

**【0036】**

LCDパネル（広義には、電気光学装置）20は、例えばガラス基板上に形成される。このガラス基板上には、Y方向に複数配列されそれぞれX方向に伸びる走査ライン（狭義には、ゲートライン）G<sub>1</sub>～G<sub>N</sub>（Nは、2以上の自然数）と、X方向に複数配列されそれぞれY方向に伸びる信号ライン（狭義には、ソースライン）信号ラインS<sub>1</sub>～S<sub>M</sub>（Mは、2以上の自然数）とが配置されている。また、走査ラインG<sub>n</sub>（1≤n≤N、nは自然数）と信号ラインS<sub>m</sub>（1≤m≤M、mは自然数）との交差点に対応して、TFT22<sub>n,m</sub>（広義には、スイッチング手段）が設けられている。

**【0037】**

TFT22<sub>n,m</sub>のゲート電極は、走査ラインG<sub>n</sub>に接続されている。TFT22<sub>n,m</sub>のソース電極は、信号ラインS<sub>m</sub>に接続されている。TFT22<sub>n,m</sub>のドレイン電極は、液晶容量（広義には、液晶素子又は電気光学素子）24<sub>n,m</sub>の画素電極26<sub>n,m</sub>に接続されている。

**【0038】**

液晶容量24<sub>n,m</sub>においては、画素電極26<sub>n,m</sub>に対向する対向電極28<sub>n,m</sub>との間に液晶が封入されて形成され、これら電極間の印加電圧に応じて画素（液晶）の透過率が変化するようになっている。

**【0039】**

対向電極28<sub>n,m</sub>には、電源回路80により生成された対向電極電圧V<sub>c o m</sub>が供給されている。

**【0040】**

信号ドライバ30は、一水平走査単位の画像データ（狭義には、階調データ）に基づいて、LCDパネル20の信号ラインS<sub>1</sub>～S<sub>M</sub>を駆動する。

**【0041】**

走査ドライバ50は、一垂直走査期間内に、水平同期信号に同期して、LCDパネル20の走査ラインG<sub>1</sub>～G<sub>N</sub>を順次走査駆動する。

**【0042】**

LCDコントローラ60は、図示しない中央処理装置（Central Processing Unit：以下、CPUと略す。）等のホストにより設定された内容に従って、信号ドライバ30、走査ドライバ50及び電源回路80を制御する。より具体的には、LCDコントローラ60は、信号ドライバ30及び走査ドライバ50に対して、例えば動作モードの設定や内部で生成した垂直同期信号や水平同期信号の供給を行い、電源回路80に対しては対向電極電圧V<sub>c o m</sub>の極性反転タイミングの供給を行う。

**【0043】**

電源回路80は、外部から供給される基準電圧に基づいて、LCDパネル20の液晶駆動に必要な電圧レベルや、対向電極電圧V<sub>c o m</sub>を生成する。このような各種電圧レベルは、信号ドライバ30、走査ドライバ50及びLCDパネル20に供給される。また、対向電極電圧V<sub>c o m</sub>は、LCDパネル20のTFTの画素電極に対向して設けられた対向電極に供給される。

10

20

30

40

50

**【0044】**

このような構成の液晶装置10は、LCDコントローラ60の制御の下、外部から供給される画像データに基づいて、信号ドライバ30、走査ドライバ50及び電源回路80が協調してLCDパネル20を表示駆動する。

**【0045】**

なお、図1では、液晶装置10にLCDコントローラ60を含めて構成するようにしているが、LCDコントローラ60を液晶装置10の外部に設けて構成するようにしても良い。或いは、LCDコントローラ60と共にホストを液晶装置10に含めるように構成することも可能である。

**【0046】**

10

## (信号ドライバ)

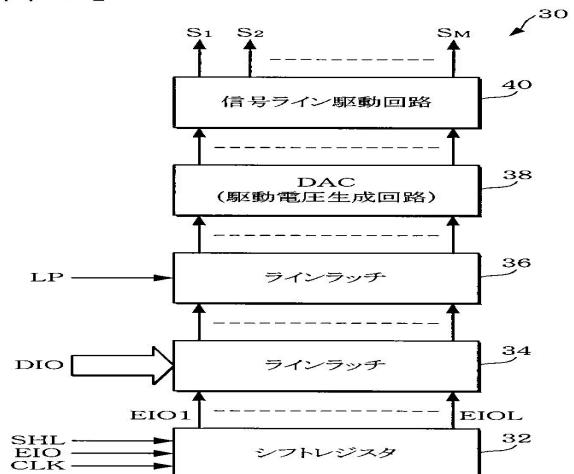

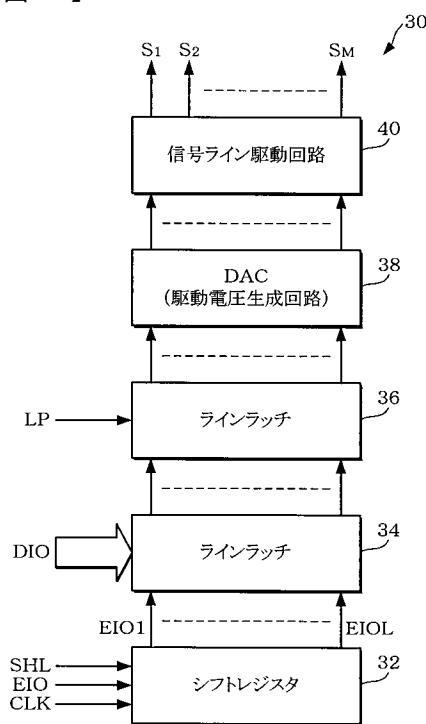

図2に、図1に示した信号ドライバの構成の概要を示す。

**【0047】**

信号ドライバ30は、シフトレジスタ32、ラインラッチ34、36、ディジタル・アナログ変換回路(広義には、駆動電圧生成回路)38、信号ライン駆動回路40を含む。

**【0048】**

シフトレジスタ32は、複数のフリップフロップを有しており、これらフリップフロップが順次接続される。このシフトレジスタ32は、クロック信号CLKに同期してイネーブル入出力信号EIOを保持すると、順次クロック信号CLKに同期して隣接するフリップフロップにイネーブル入出力信号EIOをシフトする。

20

**【0049】**

また、このシフトレジスタ32には、シフト方向切り替え信号SHLが供給される。シフトレジスタ32は、このシフト方向切り替え信号SHLにより、画像データ(DIO)のシフト方向と、イネーブル入出力信号EIOの入出力方向が切り替えられる。したがって、このシフト方向切り替え信号SHLによりシフト方向を切り替えることによって、信号ドライバ30の実装状態により信号ドライバ30に対して画像データを供給するLCDコントローラ60の位置が異なった場合であっても、その配線の引き回しによって実装面積が拡大することなく、柔軟な実装を可能にすることができます。

**【0050】**

30

ラインラッチ34は、LCDコントローラ60から例えば18ビット(6ビット(階調データ)×3(RGB各色))単位で画像データ(DIO)が入力される。ラインラッチ34は、この画像データ(DIO)を、シフトレジスタ32の各フリップフロップで順次シフトされたイネーブル入出力信号EIOに同期してラッチする。

**【0051】**

ラインラッチ36は、LCDコントローラ60から供給される水平同期信号LPに同期して、ラインラッチ34でラッチされた一水平走査単位の画像データをラッチする。

**【0052】**

DAC38は、信号ラインごとに、画像データに基づいてアナログ化された駆動電圧を生成する。

**【0053】**

40

信号ライン駆動回路40は、DAC38によって生成された駆動電圧に基づいて、信号ラインを駆動する。

**【0054】**

このような信号ドライバ30は、LCDコントローラ60から順次入力される所与の単位(例えば18ビット単位)の画像データを順次取り込み、水平同期信号LPに同期して一水平走査単位の画像データをラインラッチ36で一旦保持する。そして、この画像データに基づいて、各信号ラインを駆動する。この結果、LCDパネル20の TFT のソース電極には、画像データに基づく駆動電圧が供給される。

**【0055】**

## (走査ドライバ)

50

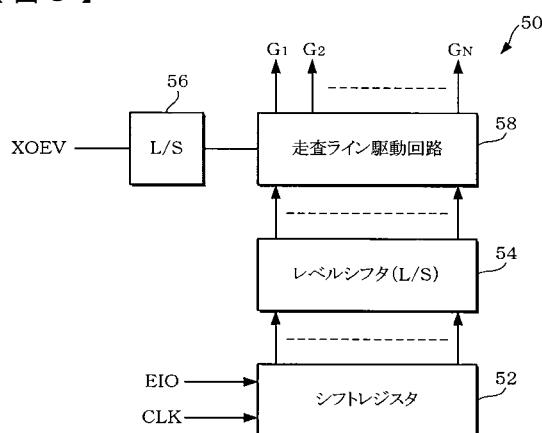

図3に、図1に示した走査ドライバの構成の概要を示す。

【0056】

走査ドライバ50は、シフトレジスタ52、レベルシフタ(Level Shifter:以下、L/Sと略す。)54、56、走査ライン駆動回路58を含む。

【0057】

シフトレジスタ52は、各走査ラインに対応して設けられたフリップフロップが順次接続される。このシフトレジスタ52は、クロック信号CLKに同期してイネーブル入出力信号EIOをフリップフロップに保持すると、順次クロック信号CLKに同期して隣接するフリップフロップにイネーブル入出力信号EIOをシフトする。ここで入力されるイネーブル入出力信号EIOは、LCDコントローラ60から供給される垂直同期信号である。 10

【0058】

L/S54は、LCDパネル20の液晶材と TFTのトランジスタ能力とに応じた電圧レベルにシフトする。この電圧レベルとしては、例えば20V~50Vの高い電圧レベルが必要とされるため、他のロジック回路部とは異なる高耐圧プロセスが用いられる。

【0059】

走査ライン駆動回路58は、L/S54によってシフトされた駆動電圧に基づいて、CMOS駆動を行う。また、この走査ドライバ50は、L/S56を有しており、LCDコントローラ60から供給される出力イネーブル信号XOEVの電圧シフトが行われる。走査ライン駆動回路58は、L/S56によってシフトされた出力イネーブル信号XOEVにより、オンオフ制御が行われる。 20

【0060】

このような走査ドライバ50は、垂直同期信号として入力されたイネーブル入出力信号EIOが、クロック信号CLKに同期してシフトレジスタ52の各フリップフロップに順次シフトされる。シフトレジスタ52の各フリップフロップは、各走査ラインに対応して設けられているため、各フリップフロップに保持された垂直同期信号のパルスにより、走査ラインが逐一的に順次選択される。選択された走査ラインは、L/S54によってシフトされた電圧レベルで、走査ライン駆動回路58により駆動される。これにより、LCDパネル20のTFTのゲート電極には、一垂直走査周期で所与の走査駆動電圧が供給されることになる。このとき、LCDパネル20のTFTのドレイン電極は、ソース電極に接続される信号ラインの電位に対応して、ほぼ同等の電位となる。 30

【0061】

(LCDコントローラ)

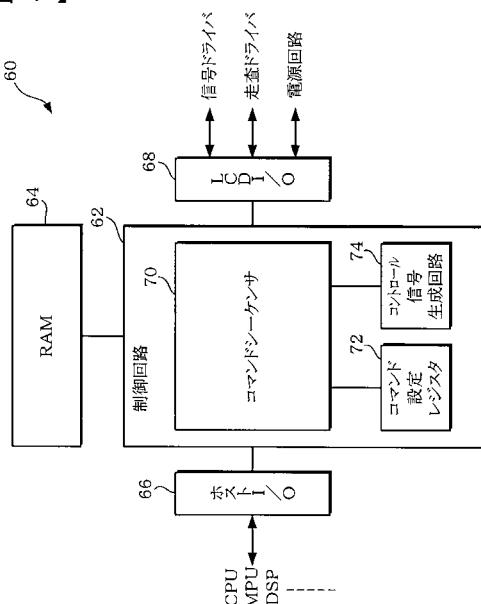

図4に、図1に示したLCDコントローラの構成の概要を示す。

【0062】

LCDコントローラ60は、制御回路62、ランダムアクセスメモリ(Random Access Memory:以下、RAMと略す。)(広義には、記憶手段)64、ホスト入出力回路(I/O)66、LCD入出力回路68を含む。さらに、制御回路62は、コマンドシーケンサ70、コマンド設定レジスタ72、コントロール信号生成回路74を含む。

【0063】

制御回路62は、ホストによって設定された内容にしたがい、信号ドライバ30、走査ドライバ50及び電源回路80の各種動作モード設定や同期制御等を行う。より具体的には、コマンドシーケンサ70が、ホストからの指示に従って、コマンド設定レジスタ72で設定された内容に基づいて、コントロール信号生成回路74で同期タイミングを生成したり、信号ドライバ等に対して所与の動作モードを設定したりする。 40

【0064】

RAM64は、画像表示を行うためのフレームバッファとしての機能を有するとともに、制御回路62の作業領域にもなる。

【0065】

このLCDコントローラ60は、ホストI/O66を介して、画像データや、信号ドライバ30及び走査ドライバ50を制御するためのコマンドデータが供給される。ホストI/ 50

O 6 6 には、図示しない C P U や、ディジタル信号処理装置 (Digital Signal Processor : D S P ) 或いはマイクロプロセッサユニット (Micro Processor Unit : M P U ) が接続される。

#### 【 0 0 6 6 】

L C D コントローラ 6 0 は、画像データとして図示しない C P U より静止画データが供給されたり、D S P 或いはM P U より動画データが供給される。また、L C D コントローラ 6 0 は、コマンドデータとして図示しない C P U より、信号ドライバ 3 0 又は走査ドライバ 5 0 を制御するためのレジスタの内容や、各種動作モードを設定するためのデータが供給される。

#### 【 0 0 6 7 】

画像データとコマンドデータは、それぞれ別個のデータバスを介してデータを供給するようにも良いし、データバスを共用化しても良い。この場合、例えばコマンド (Command : C M D ) 端子に入力された信号レベルによって、データバス上のデータが、画像データか、或いはコマンドデータかを識別できるようにすることで、画像データとコマンドデータとの共用化を容易に図ることができ、実装面積の縮小化が可能になる。

#### 【 0 0 6 8 】

L C D コントローラ 6 0 は、画像データが供給された場合、この画像データをフレームバッファとしての R A M 6 4 に保持する。一方、コマンドデータが供給された場合、L C D コントローラ 6 0 は、コマンド設定レジスタ 7 2 若しくは R A M 6 4 に保持する。

#### 【 0 0 6 9 】

コマンドシーケンサ 7 0 は、コマンド設定レジスタ 7 2 に設定された内容にしたがって、コントロール信号生成回路 7 4 により各種タイミング信号を生成させる。また、コマンドシーケンサ 7 0 は、コマンド設定レジスタ 7 2 に設定された内容にしたがって、L C D 入出力回路 6 8 を介して、信号ドライバ 3 0 、走査ドライバ 5 0 若しくは電源回路 8 0 のモード設定を行う。

#### 【 0 0 7 0 】

また、コマンドシーケンサ 7 0 は、コントロール信号生成回路 7 4 で生成された表示タイミングにより、R A M 6 4 に記憶された画像データから所与の形式の画像データを生成し、L C D 入出力回路 6 8 を介して、信号ドライバ 3 0 に供給するようになっている。

#### 【 0 0 7 1 】

1 . 2 反転駆動方式

ところで、液晶を表示駆動する場合、液晶の耐久性や、コントラストの観点から、周期的に液晶容量に蓄積される電荷を放電する必要がある。そのため、上述した液晶装置 1 0 では、交流化駆動によって、所与の周期で液晶に印加される電圧の極性を反転させることが行われる。この交流化駆動方式としては、例えばフレーム反転駆動方式や、ライン反転駆動方式がある。

#### 【 0 0 7 2 】

フレーム反転駆動方式は、フレームごとに液晶容量に印加される電圧の極性を反転する方式である。一方、ライン反転駆動方式は、ラインごとに液晶容量に印加される電圧の極性を反転する方式である。なお、ライン反転駆動方式の場合も、各ラインに着目すれば、フレーム周期で液晶容量に印加される電圧の極性も反転される。

#### 【 0 0 7 3 】

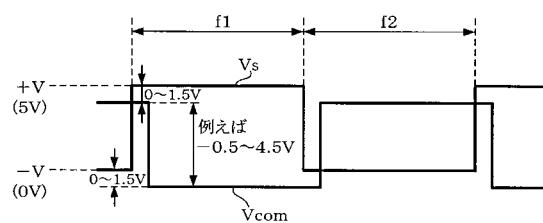

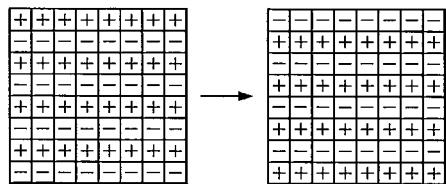

図 5 (A) 、(B) に、フレーム反転駆動方式の動作を説明するための図を示す。図 5 (A) は、フレーム反転駆動方式による信号ラインの駆動電圧及び対向電極電圧 V c o m の波形を模式的に示したものである。図 5 (B) は、フレーム反転駆動方式を行った場合に、フレームごとに、各画素に対応した液晶容量に印加される電圧の極性を模式的に示したものである。

#### 【 0 0 7 4 】

フレーム反転駆動方式では、図 5 (A) に示すように信号ラインに印加される駆動電圧の極性が 1 フレーム周期ごとに反転されている。すなわち、信号ラインに接続される T F T

10

20

30

40

50

のソース電極に供給される電圧  $V_s$  は、フレーム f 1 では正極性「+V」、後続のフレーム f 2 では負極性の「-V」となる。一方、TFT のドレイン電極に接続される画素電極に対向する対向電極に供給される対向電極電圧  $V_{com}$  も、信号ラインの駆動電圧の極性反転周期に同期して反転される。

#### 【0075】

液晶容量には、画素電極と対向電極との電圧の差が印加されるため、図 5 (B) に示すようにフレーム f 1 では正極性、フレーム 2 では負極性の電圧がそれぞれ印加されることになる。

#### 【0076】

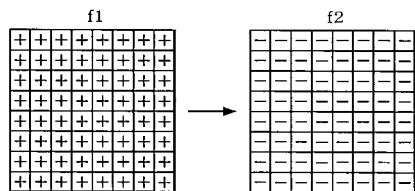

図 6 (A)、(B) に、ライン反転駆動方式の動作を説明するための図を示す。

10

#### 【0077】

図 6 (A) は、ライン反転駆動方式による信号ラインの駆動電圧及び対向電極電圧  $V_{com}$  の波形を模式的に示したものである。図 6 (B) は、ライン反転駆動方式を行った場合に、フレームごとに、各画素に対応した液晶容量に印加される電圧の極性を模式的に示したものである。

#### 【0078】

ライン反転駆動方式では、図 6 (A) に示すように信号ラインに印加される駆動電圧の極性が、各水平走査周期 (1H) ごとに、かつ 1 フレーム周期ごとに反転されている。すなわち、信号ラインに接続される TFT のソース電極に供給される電圧  $V_s$  は、フレーム f 1 の 1H では正極性「+V」、2H では負極性の「-V」となる。なお、当該電圧  $V_s$  は、フレーム f 2 の 1H では負極性「-V」、2H では正極性の「+V」となる。

20

#### 【0079】

一方、TFT のドレイン電極に接続される画素電極に対向する対向電極に供給される対向電極電圧  $V_{com}$  も、信号ラインの駆動電圧の極性反転周期に同期して反転される。

#### 【0080】

液晶容量には、画素電極と対向電極との電圧の差が印加されるため、走査ラインごとに極性を反転することで、図 6 (B) に示すようにフレーム周期で、各ラインごとに極性が反転する電圧がそれぞれ印加されることになる。

#### 【0081】

一般的に、フレーム反転駆動方式に比べてライン反転駆動方式のほうが、変化の周期が 1 ライン周期となるため、画質の向上に貢献できるものの、消費電力が大きくなる。

30

#### 【0082】

##### 1.3 液晶駆動波形

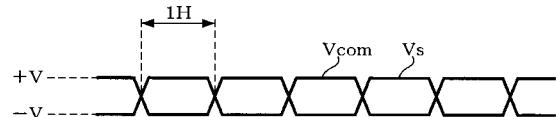

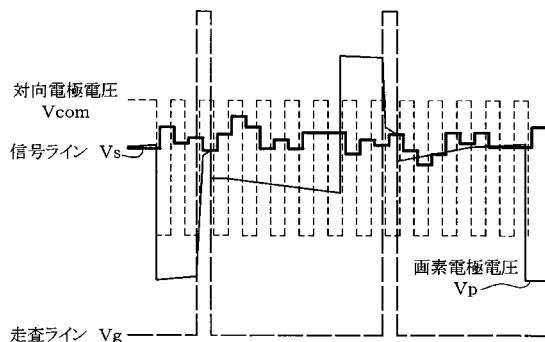

図 7 に、上述した構成の液晶装置 10 の LCD パネル 20 の駆動波形の一例を示す。ここでは、ライン反転駆動方式により駆動する場合を示している。

#### 【0083】

上述したように、液晶装置 10 では、LCD コントローラ 60 によって生成された表示タイミングに従って、信号ドライバ 30、走査ドライバ 50 及び電源回路 80 が制御される。LCD コントローラ 60 は、信号ドライバ 30 に対しては一水平走査単位の画像データを順次転送するとともに、内部で生成した水平同期信号や反転駆動タイミングを示す極性反転信号 POL を供給する。また、LCD コントローラ 60 は、走査ドライバ 50 に対しては、内部で生成した垂直同期信号を供給する。さらに、LCD コントローラ 60 は、電源回路 80 に対して対向電極電圧極性反転信号  $V_{COM}$  を供給する。

40

#### 【0084】

これにより、信号ドライバ 30 は、水平同期信号に同期して、一水平走査単位の画像データに基づいて信号ラインの駆動を行う。走査ドライバ 50 は、垂直同期信号をトリガとして、LCD パネル 20 にマトリックス状に配置された TFT のゲート電極に接続される走査ラインを、順次駆動電圧  $V_g$  で走査駆動する。電源回路 80 は、内部で生成した対向電極電圧  $V_{com}$  を、対向電極電圧極性反転信号  $V_{COM}$  に同期して極性反転を行いながら、LCD パネル 20 の各対向電極に供給する。

50

## 【0085】

液晶容量には、TFTのドレイン電極に接続される画素電極と対向電極の電圧 $V_{com}$ との電圧に応じた電荷が充電される。したがって、液晶容量に蓄積された電荷によって保持された画素電極電圧 $V_p$ が、所与の閾値 $V_{CL}$ を越えると画像表示が可能となる。画素電極電圧 $V_p$ が所与の閾値 $V_{CL}$ を越えると、その電圧レベルに応じて画素の透過率が変化し、階調表現が可能となる。

## 【0086】

## 2. 信号ドライバ

## 2.1 ブロック単位の出力制御

本実施形態における信号ドライバ30は、所与の複数の信号ラインごとに分割されたブロックを単位として、画像データに基づく信号駆動を行って、パーシャル表示を実現することができるようになっている。そのため信号ドライバ30は、パーシャル表示選択レジスタを有しており、ブロック単位で各ブロックの出力可否を示すパーシャル表示データを保持するようになっている。パーシャル表示データにより出力がオンに設定されたブロックは、当該ブロックの信号ラインに対して画像データに基づく信号駆動を行う表示エリアとして設定されることになる。一方、パーシャル表示データにより表示がオフに設定されたブロックは、当該ブロックの信号ラインに対して所与の非表示レベル電圧が供給される非表示エリアとして設定されることになる。

10

## 【0087】

本実施形態では、このブロックを8ピクセル単位としている。ここで、1ピクセルは、RGB信号の3ビットからなる。したがって、信号ドライバ30は、計24出力（例えば、 $S_1 \sim S_{24}$ ）を1ブロックとしている。これにより、LCDパネル20の表示エリアをキャラクタ文字（1バイト）単位で設定することができるので、携帯電話機のようなキャラクタ文字の表示を行う電子機器において、効率的な表示エリアの設定及びその画像表示が可能となる。

20

## 【0088】

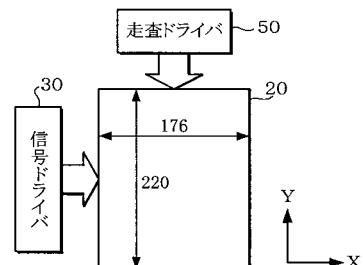

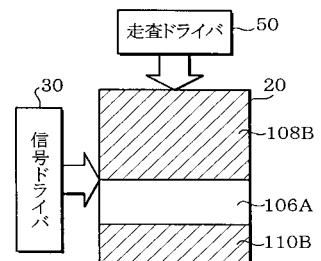

図8(A)、(B)、(C)に、このような本実施形態における信号ドライバにより実現したパーシャル表示の一例を模式的に示す。

## 【0089】

例えば、図8(A)に示すようにLCDパネル20に対して、Y方向に複数の信号ラインが配列されるように信号ドライバ30を配置し、X方向に複数の走査ラインが配列されるように走査ドライバ50を配置した場合、図8(B)に示すようにブロック単位で非表示エリア100Bを設定する。こうすることで、表示エリア102A、104Aに対応するブロックの信号ラインのみを画像データに基づいて駆動すればよい。

30

## 【0090】

或いは、図8(C)に示すようにブロック単位で表示エリア106Aを設定することで、非表示エリア108B、110Bに対応するブロックの信号ラインを画像データに基づいて駆動する必要がなくなる。また、図8(B)、(C)において、複数の非表示エリア若しくは表示エリアを設定するようにしても良い。

## 【0091】

40

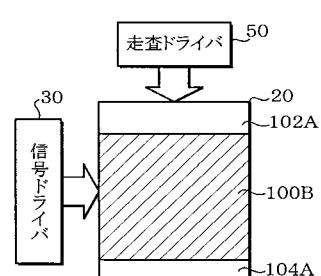

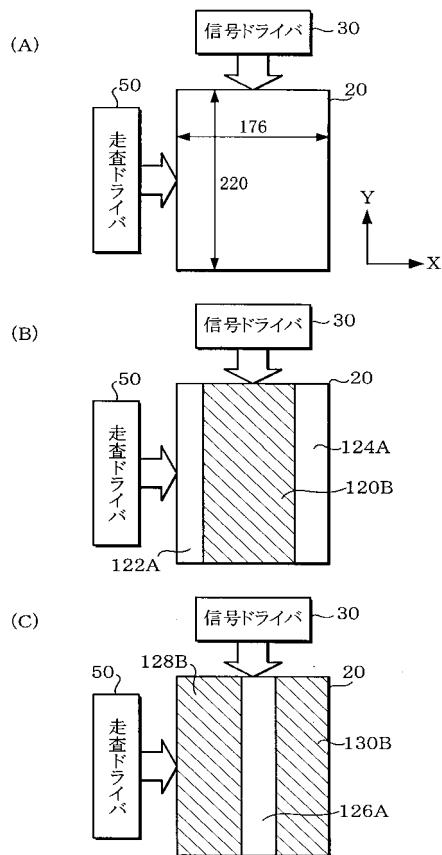

図9(A)、(B)、(C)に、本実施形態による信号ドライバにより実現したパーシャル表示の他の例を模式的に示す。

## 【0092】

この場合、図9(A)に示すようにLCDパネル20に対して、X方向に複数の信号ラインが配列されるように信号ドライバ30を配置し、Y方向に複数の走査ラインが配列されるように走査ドライバ50を配置すると、図9(B)に示すようにブロック単位で非表示エリア120Bを設定することで、表示エリア122A、124Aに対応するブロックの信号ラインのみを画像データに基づいて駆動すればよい。

## 【0093】

或いは、図9(C)に示すようにブロック単位で表示エリア126Aを設定することで、

50

非表示エリア 128B、130B に対応するブロックの信号ラインを画像データに基づいて駆動する必要がない。なお、図 9 (B)、(C)において、複数の非表示エリア若しくは表示エリアを設定するようにしても良い。

#### 【0094】

また、各表示エリアは、例えば静止画表示エリアと動画表示エリアとを区切るようにしても良い。こうすることで、ユーザにとって見やすい画面を提供することができるとともに、低消費電力化を図ることが可能となる。

#### 【0095】

本実施形態における信号ドライバ 30において、信号ライン駆動回路 40 はブロック単位に制御され、ブロックの信号ラインをボルテージフォロワ接続されたオペアンプ、若しくは非表示レベル電圧供給回路により駆動する。10

#### 【0096】

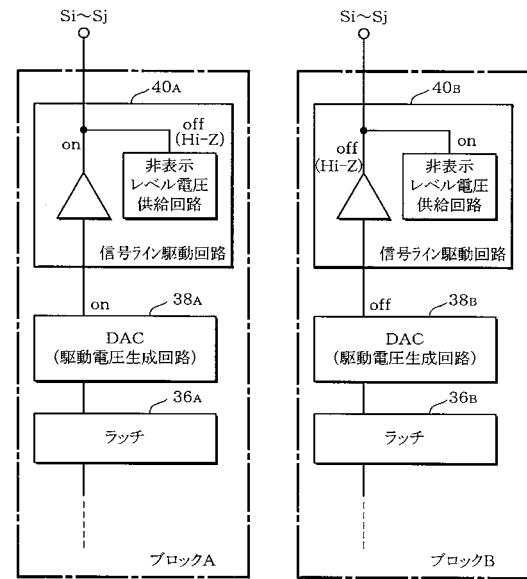

図 10 (A)、(B) に、本実施形態における信号ライン駆動回路の制御内容を模式的に示す。

#### 【0097】

パーシャル表示データにより出力がオンに設定された表示エリアに対応するブロックの信号ラインを画像データに基づいて駆動する場合、図 10 (A) に示すように、D A C 38<sub>A</sub> により駆動電圧を生成させ、信号ライン駆動回路 40<sub>A</sub> においてボルテージフォロワ接続されたオペアンプによりインピーダンス変換を行って、当該ブロックに割り当てられた 1 又は複数の信号ラインを駆動する。この際、信号ライン駆動回路 40<sub>A</sub> の非表示レベル電圧供給回路は、その出力がハイインピーダンス制御される。20

#### 【0098】

一方、パーシャル表示データにより出力がオフに設定された非表示エリアに対応するブロックの信号ラインについては、図 10 (B) に示すように、D A C 38<sub>B</sub> による駆動電圧の生成制御を停止させるとともに、信号ライン駆動回路 40<sub>B</sub> においてボルテージフォロワ接続されたオペアンプの出力をハイインピーダンス制御する。そして、信号ライン駆動回路 40<sub>B</sub> の非表示レベル電圧供給回路により生成した非表示レベル電圧で、当該ブロックに割り当てられた 1 又は複数の信号ラインを駆動する。この非表示レベル電圧は、TFT に接続される液晶容量に印加される電圧を、少なくとも画素の透過率が変化して表示可能となる所与の閾値  $V_{CL}$  より小さくするような電圧レベルに設定される。30

#### 【0099】

これにより、上述した画像表現による効果に加えて、オペアンプの定常的な電流消費を削減することができるので、従来から問題となっていた TFT 液晶を用いたアクティブマトリクス型液晶パネルの消費電力を低減し、バッテリ駆動の携帯型の電子機器への搭載が可能となる。

#### 【0100】

##### 2.2 シフト方向に応じたブロックの入れ替え

本実施形態における信号ドライバ 30 は、図 8 (A) ~ (C)、図 9 (A) ~ (C) に示したように、実装対象となる電子機器に応じて、LCD パネル 20 に対して配置される位置が異なる場合がある。40

#### 【0101】

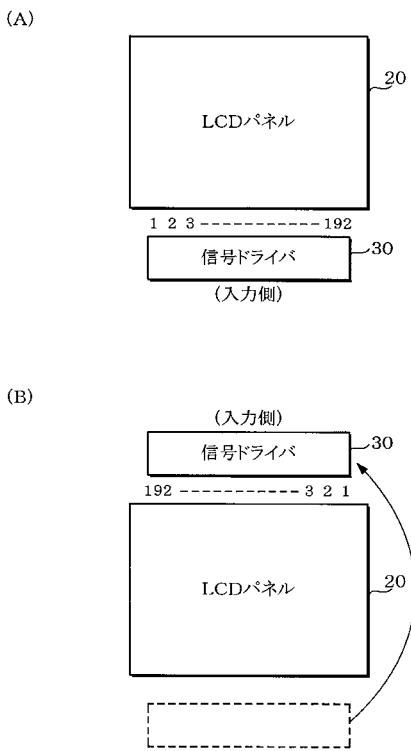

図 11 (A)、(B) に、LCD パネル 20 に対して異なる位置に実装される信号ドライバ 30 を模式的に示す。

#### 【0102】

すなわち、図 11 (A) に示す場合では、LCD パネル 20 に対して下側に信号ドライバ 30 が配置されている。一方、図 11 (B) に示す場合では、LCD パネル 20 に対して上側に信号ドライバ 30 が配置されている。

#### 【0103】

信号ドライバ 30 の信号ライン駆動出力側は、固定されているため、図 11 (A) に示すように LCD パネル 20 に対して下側に信号ドライバ 30 が配置されたときの駆動側の順

番が、図11(B)に示すようにLCDパネル20に対して上側に配置されたとき駆動側の順番と逆になる。したがって、実装状態によって信号ドライバ30への配線の引き回しのため実装面積が増大してしまう。このため、シフト方向入れ替え信号SHLによって、画像データのシフト方向を切り替えるようにしている。

#### 【0104】

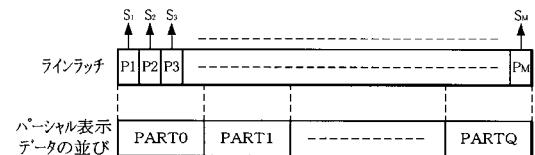

図12(A)、(B)、(C)に、ラインラッチに保持された画像データと、ブロックの対応関係を模式的に示す。

#### 【0105】

例えば図11(A)に示す位置に信号ドライバ30が配置された場合、シフト方向切り替え信号SHLを「H」にすることで、図12(A)に示すように、シフトレジスタで順次保持されてラインラッチ36でラッチされた一水平走査単位の画像データが、信号ラインS<sub>1</sub>～S<sub>M</sub>に対応して、画像データP1～PMの並びの順番になるものとする。

10

#### 【0106】

これに対して図11(B)に示す位置に信号ドライバ30が配置された場合、シフト方向切り替え信号SHLを「L」にすることで、図12(B)に示すように、図12(A)と同じ並びの順番でLCDコントローラ60から供給される画像データに対して、ラインラッチ36には、信号ラインS<sub>1</sub>～S<sub>M</sub>に対応して、画像データPM、…、P3、P2、P1の並びの順番で保持される。

#### 【0107】

ところが、ユーザにとっては、図12(A)、(B)に示すように、複数の信号ラインを分割したブロックの並びの順番は変わらない。したがって、ブロック単位に、上述した画像データを制御する場合、ユーザもシフト方向に応じてブロックの順番の並びが変更することを認識して画像表示制御を行わなければならなくなる。

20

#### 【0108】

そこで、本実施形態では、ユーザがシフト方向によって入れ替わるブロックの並びの順番を気にすることなく、上述したブロック単位のパーシャル表示制御を可能にするため、図12(C)に示すように、これらブロック単位で指定されるパーシャル表示データについてもシフト方向に応じて切り替えるようにしている。すなわち、本実施形態における信号ドライバ30は、シフト方向を切り替えた場合に上述したパーシャル表示選択レジスタに記憶されたパーシャル表示データの順番を逆に入れ替えることができるブロックデータ入れ替え回路を含む。

30

#### 【0109】

これにより、表示エリア及び非表示エリアが設定されたブロックと、実際のパネルの駆動回路との対応関係を維持し、信号ドライバ30の実装状態に依存することなく、ブロック単位のパーシャル表示切替を実現させることができる。

#### 【0110】

以下では、このような本実施形態における信号ドライバ30の具体的な構成例について説明する。

#### 【0111】

3. 本実施形態における信号ドライバの構成の具体例

40

##### 3.1 信号ドライバの構成（ブロック単位）

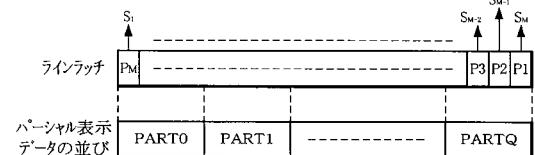

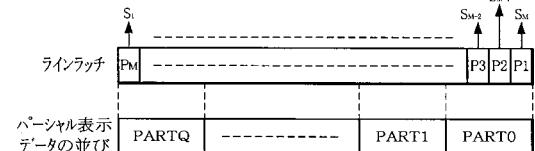

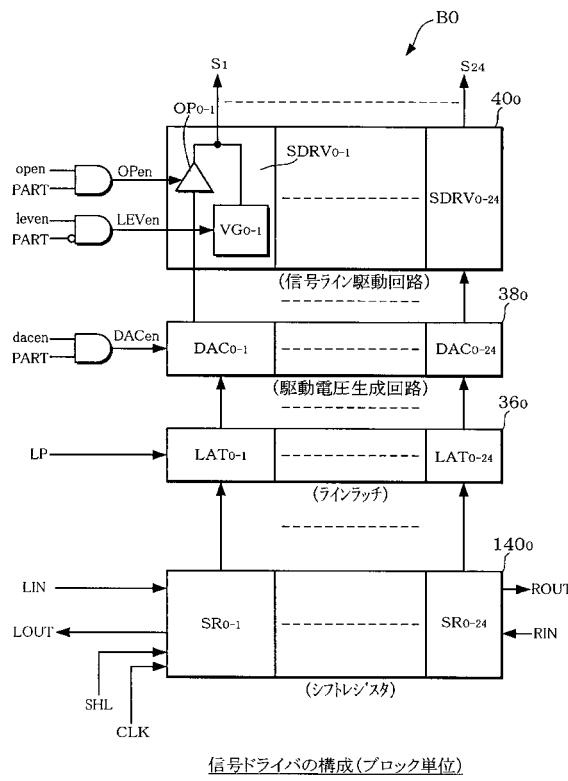

図13に、本実施形態における信号ドライバ30において制御されるブロック単位の構成の概要を示す。

#### 【0112】

本実施形態における信号ドライバ30は、288本の信号ライン出力(S<sub>1</sub>～S<sub>288</sub>)を有しているものとする。

#### 【0113】

すなわち、本実施形態における信号ドライバ30は、24出力端子単位(S<sub>1</sub>～S<sub>24</sub>、S<sub>25</sub>～S<sub>48</sub>、…、S<sub>265</sub>～S<sub>288</sub>)に、図13に示す構成を備えており、計12ブロック(B0～B11)を有している。以下では、図13は、ブロックB0を示すものとして説

50

明するが、他のブロック B 1 ~ B 11 についても同様である。

**【 0 1 1 4 】**

信号ドライバ 30 のブロック B 0 は、信号ライン  $S_1 \sim S_{24}$  の各信号ラインに対応して、シフトレジスタ 140<sub>0</sub>、ラインラッチ 36<sub>0</sub>、駆動電圧生成回路 38<sub>0</sub>、信号ライン駆動回路 40<sub>0</sub> を含む。ここで、シフトレジスタ 140<sub>0</sub> は、図 2 に示すシフトレジスタ 32 及びラインラッチ 34 の機能を有する。

**【 0 1 1 5 】**

シフトレジスタ 140<sub>0</sub> は、各信号ラインに対応して  $S R_{0-1} \sim S R_{0-24}$  を含む。ラインラッチ 36<sub>0</sub> は、各信号ラインに対応して  $L A T_{0-1} \sim L A T_{0-24}$  を含む。駆動電圧生成回路 38<sub>0</sub> は、各信号ラインに対応して  $D A C_{0-1} \sim D A C_{0-24}$  を含む。信号ライン駆動回路 40<sub>0</sub> は、各信号ラインに対応して  $S D R V_{0-1} \sim S D R V_{0-24}$  を含む。10

**【 0 1 1 6 】**

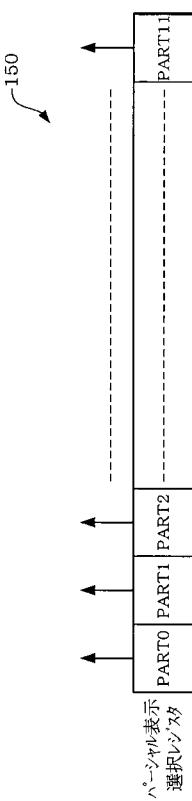

### 3.2 パーシャル表示選択レジスタ

上述したように、本実施形態における信号ドライバ 30 は、ブロック単位に出力制御される。そのため、本実施形態における信号ドライバ 30 は、図 14 に示すようにパーシャル表示選択レジスタ 150 を有している。このパーシャル表示選択レジスタ 150 は、LCD コントローラ 60 によって設定される。LCD コントローラ 60 は、ホスト (CPU) からの制御によって、所与のタイミングで信号ドライバ 30 のパーシャル表示選択レジスタ 150 の内容を更新することができるようになっており、その都度最適なパーシャル表示を実現することができる。20

**【 0 1 1 7 】**

パーシャル表示選択レジスタ 150 は、ブロック B 0 ~ B 11 に対応して、各ブロックの信号ラインを画像データに基づいて信号駆動するか否かを示すパーシャル表示データ PART0 ~ PART11 を含む。本実施形態では、パーシャル表示データ PART0 ~ PART11 のうち、出力がオンであることを示す「1」に設定されたブロックを表示エリア、出力がオフであることを示す「0」に設定されたブロックを非表示エリアとして、表示制御を行う。

**【 0 1 1 8 】**

上述したように、信号ドライバ 30 の実装状態に応じて、ユーザにブロックの順番を気にさせる必要なく、ブロック単位のパーシャル表示を実現させるために、パーシャル表示データをブロック単位で切り替える必要がある。30

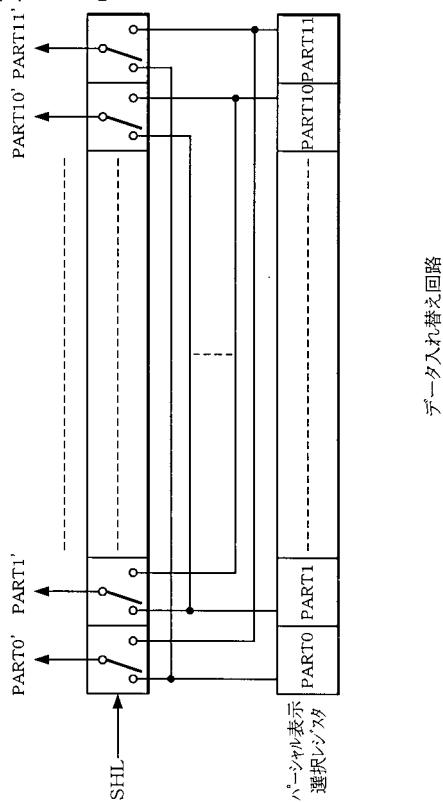

**【 0 1 1 9 】**

そこで、本実施形態では、以下に示すブロックデータ入れ替え回路により、パーシャル表示選択レジスタのブロックの並び順を、シフト方向に応じて切り替えるようになっている。。

**【 0 1 2 0 】**

図 15 に、ブロックデータ入れ替え回路の構成の一例を示す。

**【 0 1 2 1 】**

上述したように、信号ドライバ 30 の実装状態に応じて、ユーザにブロックの順番を気にさせる必要なく、ブロック単位のパーシャル表示を実現させるために、パーシャル表示データをブロック単位で切り替える必要がある。40

**【 0 1 2 2 】**

このブロックデータ入れ替え回路は、パーシャル表示データ選択レジスタに設定されたパーシャル表示データ PART0 ~ PART11 の並びをシフト方向切り替え信号 SHL に応じて切り替える。より具体的には、ブロックデータ入れ替え回路は、シフト方向切り替え信号 SHL に応じて、パーシャル表示データ PART0 及び PART11 のいずれか一方を PART0' として選択出力する。同様に、シフト方向切り替え信号 SHL に応じて、パーシャル表示データ PART1 及び PART10 のいずれか一方を PART1' 、パーシャル表示データ PART2 及び PART9 のいずれか一方を PART2' 、 . . . 、パーシャル表示データ PART11 及び PART0 のいずれか一方を PART11' とし50

て、それぞれ選択出力する。

**【0123】**

このようにシフト方向に応じてブロック単位の並び順が切り替えられたパーシャル表示データ P A R T 0' ~ P A R T 11' は、シフト方向に応じて P A R T 0、P A R T 1、・・・、P A R T 11、又は P A R T 11、P A R T 10、・・・、P A R T 0 のいずれかのデータとして、それぞれ対応する各ブロック B 0 ~ B 11 に供給される。各ブロック B 0 ~ B 11 は、パーシャル表示データ P A R T 0' ~ P A R T 11' に基づいてパーシャル表示制御を行う。

**【0124】**

ブロック B 0 は、パーシャル表示データ P A R T 0' に基づいてパーシャル表示制御が行 10 われる。

**【0125】**

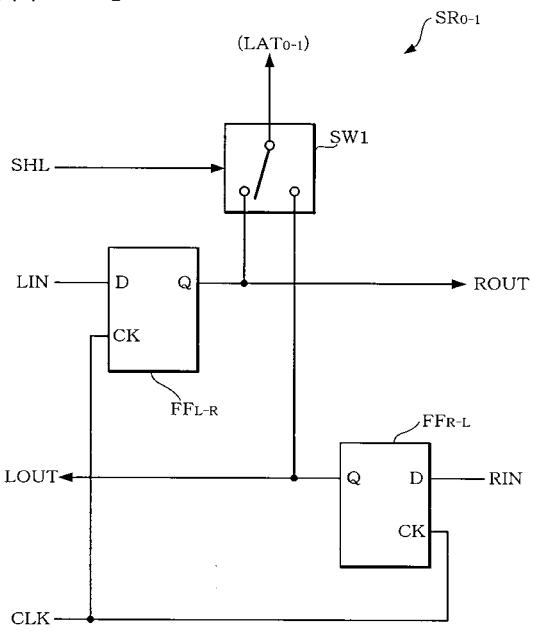

3.3 シフトレジスタ

ブロック B 0 のシフトレジスタ 140<sub>0</sub> は、クロック信号 C L K に同期して、隣接するブロックのシフトレジスタからシフトされた画像データを順次各 S R においてシフトする。また、シフトレジスタ 140<sub>0</sub> は、シフト方向切り替え信号 S H L に応じて、左方向データ入力信号 L I N 若しくは右方向データ入力信号 R I N として隣接するブロックのシフトレジスタから入力された画像データを順次シフトする。なお、ブロック B 0 の L I N 及び L O U T、ブロック B 1 1 の R I N 及び R O U T は、シフト切り替え信号 S H L によって入出力方向が切り替えられる。

20

**【0126】**

図 16 に、S R<sub>0-1</sub> の構成の一例を示す。

**【0127】**

ここでは、S R<sub>0-1</sub> の構成について示すが、他の S R<sub>0-2</sub> ~ S R<sub>0-24</sub> についても同様に構成することができる。

**【0128】**

S R<sub>0-1</sub> は、F F<sub>L-R</sub>、F F<sub>R-L</sub>、S W 1 を含む。

**【0129】**

F F<sub>L-R</sub> は、例えば D 端子に入力される左方向データ入力信号 L I N を、C K 端子に入力されるクロック信号の立ち上がりエッジに同期してラッチし、Q 端子から右方向データ出力信号 R O U T として、S R<sub>0-2</sub> の D 端子に対して左方向データ入力信号 L I N を供給する。

30

**【0130】**

F F<sub>R-L</sub> は、例えば D 端子に入力される右方向データ入力信号 R I N を、C K 端子に入力されるクロック信号の立ち上がりエッジに同期してラッチし、Q 端子から左方向データ出力信号 L O U T を出力する。

**【0131】**

F F<sub>L-R</sub> の Q 端子から出力される右方向データ出力信号 R O U T と、F F<sub>R-L</sub> の Q 端子から出力される左方向出力信号 L O U T とは、S W 1 にも供給される。S W 1 は、シフト方向切り替え信号 S H L に応じて、右方向データ出力信号 R O U T と、F F<sub>R-L</sub> の Q 端子から出力される左方向出力信号 L O U T のうち、いずれか一方を選択して、ラインラッチ 36<sub>0</sub> の L A T<sub>0-1</sub> に供給する。

40

**【0132】**

このようにして、シフトレジスタ 140<sub>0</sub> の各 S R<sub>0-1</sub> ~ S R<sub>0-24</sub> に保持された画像データは、水平同期信号 L P に同期してそれぞれラインラッチ 36<sub>0</sub> の各 L A T<sub>0-1</sub> ~ L A T<sub>0-24</sub> にラッチされる。

**【0133】**

3.4 ラインラッチ

ラインラッチ L A T<sub>0-1</sub> にラッチされた信号 ライン S<sub>1</sub> に対応する画像データは、駆動電圧生成回路の D A C<sub>0-1</sub> に供給される。D A C<sub>0-1</sub> は、D A C イネーブル信号 D A C e n が論

50

理レベル「H」のときに、 $L A T_{0..1}$ から供給された例えば6ビットの階調データ（画像データ）に基づいて、64レベルの階調電圧を発生する。

【0134】

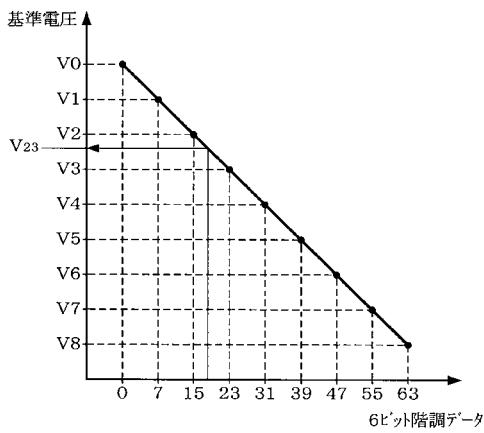

### 3.5 駆動電圧生成回路

図17に、 $D A C_{0..1}$ によって生成される階調電圧を説明するための図を示す。

【0135】

$D A C_{0..1}$ は、電源回路80から例えば $V_0 \sim V_8$ の各レベルの基準電圧が供給されている。 $D A C_{0..1}$ は、 $D A C$ イネーブル信号 $D A C_{e n}$ が論理レベル「H」になると、各信号ラインの画像データとしての6ビットの階調データのうち例えば上位3ビットから $V_0 \sim V_8$ によって分割された電圧範囲のうちの1つを選択する。ここで、例えば基準電圧 $V_{10}$ と $V_3$ との間を選択すると、6ビットの階調データのうち例えば下位3ビットによって特定される $V_2$ と $V_3$ の間の8レベルのうちいずれか1つである $V_{23}$ を選択する。

【0136】

このように、信号ライン $S_1$ に対応する $D A C_{0..1}$ に選択された駆動電圧は、信号ライン駆動回路40<sub>0</sub>の $S D R V_{0..1}$ に供給される。同様に、他の信号ライン $S_2 \sim S_{24}$ についても、駆動電圧の供給が行われる。

【0137】

本実施形態では、 $D A C$ イネーブル信号 $D A C_{e n}$ が、信号ドライバ30の図示しない制御回路で生成された $D A C$ 制御信号 $d a c_{e n}$ と、パーシャル表示選択レジスタのブロックB0のパーシャル表示の可否を示すパーシャル表示データPART(PART0')との論理積により生成される。すなわち、パーシャル表示エリアとして設定された場合にのみ $D A C$ 動作を行う一方、パーシャル非表示エリアとして設定された場合、 $D A C$ 動作を停止してラダー抵抗に流れる電流消費を削減する。

【0138】

なお、この $D A C$ イネーブル信号 $D A C_{e n}$ は、他の信号ライン $S_2 \sim S_{24}$ に対応する $D A C_{0..2} \sim D A C_{0..24}$ にも同様に供給され、ブロック単位で $D A C$ の動作制御が行われる。

【0139】

### 3.6 信号駆動回路

信号ライン駆動回路40<sub>0</sub>の $S D R V_{0..1}$ は、インピーダンス変換手段としてのボルテージフォロワ接続されたオペアンプOP<sub>0..1</sub>と、パーシャル非表示レベル電圧供給回路 $V G_{0..1}$ を含む。

【0140】

#### 3.6.1 オペアンプ

ボルテージフォロワ接続されたオペアンプOP<sub>0..1</sub>は、その出力端子が負帰還され、オペアンプの入力インピーダンスも極めて大きくなり、入力電流はほとんど流れなくなる。そして、オペアンプイネーブル信号OP<sub>e n</sub>が論理レベル「H」のときに、 $D A C_{0..1}$ によって生成された駆動電圧をインピーダンス変換して、信号ライン $S_1$ を駆動する。これにより、信号ライン $S_1$ の出力負荷に依存することなく、信号駆動を行うことができる。

【0141】

本実施形態では、オペアンプイネーブル信号OP<sub>e n</sub>が、信号ドライバ30の図示しない制御回路で生成されたオペアンプ制御信号openと、パーシャル表示選択レジスタのブロックB0のパーシャル表示の可否を示すパーシャル表示データPART(PART0')との論理積により生成される。すなわち、パーシャル表示エリアとして設定された場合にのみインピーダンス変換して信号ラインの駆動を行う一方、パーシャル非表示エリアとして設定された場合、オペアンプ動作を停止して電流源を停止して電流消費を削減する。

【0142】

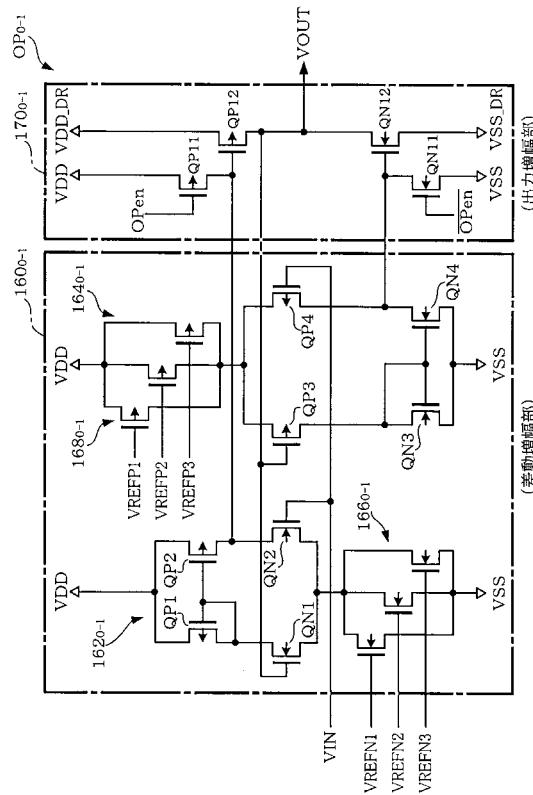

図18に、ボルテージフォロワ接続されたオペアンプOP<sub>0..1</sub>の構成の一例を示す。

【0143】

このオペアンプOP<sub>0..1</sub>は、差動増幅部160<sub>0..1</sub>と、出力増幅部170<sub>0..1</sub>とを含む。こ

のオペアンプ O P<sub>0.1</sub>は、オペアンプイネーブル信号 O P e n にしたがって、D A C<sub>0.1</sub>から供給された入力電圧 V I N をインピーダンス変換して、出力電圧 V O U T を出力する。

【 0 1 4 4 】

差動増幅部 1 6 0<sub>0.1</sub>は、第 1 及び第 2 の差動増幅回路 1 6 2<sub>0.1</sub>、1 6 4<sub>0.1</sub>を含む。

【 0 1 4 5 】

第 1 の差動増幅回路 1 6 2<sub>0.1</sub>は、p 型トランジスタ Q P 1、Q P 2 と、n 型トランジスタ Q N 1、Q N 2 を少なくとも含む。

【 0 1 4 6 】

第 1 の差動増幅回路 1 6 2<sub>0.1</sub>において、p 型トランジスタ Q P 1、Q P 2 のソース端子は、電源電圧レベル V D D に接続されている。また、p 型トランジスタ Q P 1、Q P 2 のゲート端子は互いに接続され、これらゲート端子はさらに p 型トランジスタ Q P 1 のドレイン端子に接続されてカレントミラー構造となっている。p 型トランジスタ Q P 1 のドレイン端子は、n 型トランジスタ Q N 1 のドレイン端子に接続される。p 型トランジスタ Q P 2 のドレイン端子は、n 型トランジスタ Q N 2 のドレイン端子に接続される。

10

【 0 1 4 7 】

n 型トランジスタ Q N 1 のゲート端子には、出力電圧 V O U T が供給され、負帰還されている。n 型トランジスタ Q N 2 のゲート端子には、入力電圧 V I N が供給されている。

【 0 1 4 8 】

n 型トランジスタ Q N 1、Q N 2 のソース端子は、基準電圧選択信号 V R E F N 1 ~ V R E F N 3 のいずれかが論理レベル「H」になることで形成される電流源 1 6 6<sub>0.1</sub>を介して、接地レベル V S S に接続される。

20

【 0 1 4 9 】

第 2 の差動増幅回路 1 6 4<sub>0.1</sub>は、p 型トランジスタ Q P 3、Q P 4 と、n 型トランジスタ Q N 3、Q N 4 を少なくとも含む。

【 0 1 5 0 】

第 2 の差動増幅回路 1 6 4<sub>0.1</sub>において、n 型トランジスタ Q N 3、Q N 4 のソース端子は、接地レベル V S S に接続されている。また、n 型トランジスタ Q N 3、Q N 4 のゲート端子は互いに接続され、これらゲート端子はさらに n 型トランジスタ Q N 3 のドレイン端子に接続されてカレントミラー構造となっている。n 型トランジスタ Q N 3 のドレイン端子は、p 型トランジスタ Q P 3 のドレイン端子に接続される。n 型トランジスタ Q N 4 のドレイン端子は、p 型トランジスタ Q P 4 のドレイン端子に接続される。

30

【 0 1 5 1 】

p 型トランジスタ Q P 3 のゲート端子には、出力電圧 V O U T が供給され、負帰還されている。p 型トランジスタ Q P 4 のゲート端子には、入力電圧 V I N が供給されている。

【 0 1 5 2 】

p 型トランジスタ Q P 3、Q P 4 のソース端子は、基準電圧選択信号 V R E F P 1 ~ V R E F P 3 のいずれかが論理レベル「L」になることで形成される電流源 1 6 8<sub>0.1</sub>を介して、電源電圧レベル V D D に接続される。

【 0 1 5 3 】

また、出力増幅部 1 7 0<sub>0.1</sub>は、p 型トランジスタ Q P 1 1、Q P 1 2、n 型トランジスタ Q N 1 1、Q N 1 2 を含む。

40

【 0 1 5 4 】

出力増幅部 1 7 0<sub>0.1</sub>において、p 型トランジスタ Q P 1 1 のソース端子には電源電圧レベル V D D が接続され、ゲート端子にはオペアンプイネーブル信号 O P e n が供給される。また、p 型トランジスタ Q P 1 1 のドレイン端子は、p 型トランジスタ Q P 2 のドレイン端子と、p 型トランジスタ Q P 1 2 のゲート端子に接続される。

【 0 1 5 5 】

p 型トランジスタ Q P 1 2 のソース端子は、駆動電圧レベル V D D \_ D R V に接続され、ドレイン端子から出力電圧 V O U T が出力される。

【 0 1 5 6 】

また、n型トランジスタQN11のソース端子に接地レベルVSSが接続され、ゲート端子にオペアンプイネーブル信号OPenの反転信号が供給される。また、n型トランジスタQN11のドレイン端子は、n型トランジスタQN4のドレイン端子と、n型トランジスタNp12のゲート端子に接続される。

#### 【0157】

n型トランジスタQN12のソース端子は駆動接地レベルVSS\_DRVに接続され、ドレイン端子から出力電圧VOUTが出力される。

#### 【0158】

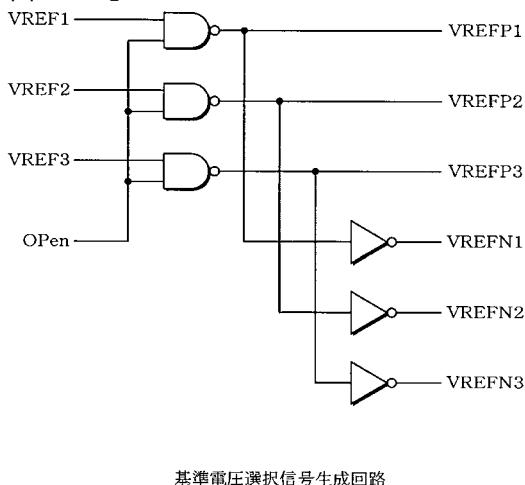

図19に、第1及び第2の差動増幅回路162<sub>0.1</sub>、164<sub>0.1</sub>に供給される基準電圧選択信号生成回路の構成の概要を示す。

10

#### 【0159】

本実施形態では、基準電圧選択信号VREF1～VREF3により、出力負荷に応じた最適な電流駆動能力を有する電流源を形成することができるようになっている。そのため、基準電圧選択信号生成回路は、基準電圧選択信号VREF1～VREF3により、p型トランジスタ用の基準電圧選択信号VREFP1～VREFP3と、n型トランジスタ用の基準電圧選択信号VREFN1～VREFN3を生成する。

#### 【0160】

この際、オペアンプイネーブル信号OPenの論理レベルが「H」のときにのみ、基準電圧選択信号VREF1～VREF3の状態に応じて、p型トランジスタ用の基準電圧選択信号VREFP1～VREFP3と、n型トランジスタ用の基準電圧選択信号VREFN1～VREFN3により、電流源166<sub>0.1</sub>、168<sub>0.1</sub>を制御する。一方、オペアンプイネーブル信号OPenの論理レベルが「L」のときには、基準電圧選択信号VREF1～VREF3をマスクする。そのため、電流源166<sub>0.1</sub>、168<sub>0.1</sub>は、電流源に流れる電流がなくなり、差動増幅動作を停止する。

20

#### 【0161】

次に、このような構成のボルテージフォロワ接続されたオペアンプOP<sub>0.1</sub>の動作の概要を説明する。

#### 【0162】

オペアンプイネーブル信号OPenの論理レベルが「H」の場合、出力電圧VOUTが入力電圧VINより低いとき、第1の差動増幅回路162<sub>0.1</sub>において、n型トランジスタQN2のドレイン端子が低くなっている、p型トランジスタQp12を介して出力電圧VOUTの電位を高める。

30

#### 【0163】

これに対して、出力電圧VOUTが入力電圧VINより高い場合、第2の差動増幅回路164<sub>0.1</sub>において、p型トランジスタQp4のドレイン端子の電位が高くなっている、n型トランジスタQN12を介して出力電圧VOUTの電位を低くする。

#### 【0164】

一方、オペアンプイネーブル信号OPenの論理レベルが「L」の場合、図19に示したように基準電圧選択信号VREF1～VREF3がマスクされるため、電流源166<sub>0.1</sub>、168<sub>0.1</sub>の各トランジスタはオフとなるとともに、p型トランジスタQp11のドレイン端子が電源電圧レベルVDDに接続され、n型トランジスタQN11のドレイン端子が接地レベルVSSに接続される。したがって、出力電圧VOUTはハイインピーダンス状態となる。この場合、本来出力電圧VOUTが供給される信号ラインには、後述するパーシャル非表示レベル電圧供給回路VG<sub>0.1</sub>により生成された所与のパーシャル非表示レベル電圧が供給されることになる。

40

#### 【0165】

### 3.6.2 非表示レベル電圧供給回路

図13において、パーシャル非表示レベル電圧供給回路VG<sub>0.1</sub>は、非表示レベル電圧供給イネーブル信号LEVEnが論理レベル「H」の場合に、上述したパーシャル表示選択レジスタにおいて非表示エリア（出力がオフ）に設定されたとき、信号ラインに供給する

50

所与の非表示レベル電圧  $V_{PART-LEVEL}$  を生成する。

【0166】

ここで、非表示レベル電圧  $V_{PART-LEVEL}$  は、画素の透過率が変化する所与の閾値  $V_{CL}$  と、この画素電極に対向する対向電極の対向電極電圧  $V_{COM}$  に対して、次の(1)式の関係を有する。

【0167】

$$|V_{PART-LEVEL} - V_{COM}| < V_{CL} \quad \dots (1)$$

【0168】

すなわち、非表示レベル電圧  $V_{PART-LEVEL}$  は、駆動対象の信号ラインに接続された TFT のドレイン電極に接続される画素電極に印加された場合、液晶容量の印加電圧が、所与の閾値  $V_{CL}$  を越えないような電圧レベルとなっている。

10

【0169】

なお、この非表示レベル電圧  $V_{PART-LEVEL}$  は、電圧レベルの生成及び制御の容易さから、対向電極電圧  $V_{COM}$  と同等の電圧レベルであることが望ましい。したがって、本実施形態では、対向電極電圧  $V_{COM}$  と同等の電圧レベルを供給する。この場合、LCDパネル 20 の非表示エリアには、液晶がオフのときの色が表示される。

【0170】

また、本実施形態における非表示レベル電圧供給回路  $V_{G_{0..1}}$  は、階調レベル電圧の両端の電圧レベル  $V_0$  若しくは  $V_8$  のいずれかを非表示レベル電圧  $V_{PART-LEVEL}$  として選択出力するができるようになっている。ここで、階調電圧レベルの両端の電圧レベル  $V_0$  若しくは  $V_8$  は、反転駆動方式によりフレームごとに交互に出力するための電圧レベルである。本実施形態では、ユーザによって指定された選択信号  $SEL$  により、非表示レベル電圧  $V_{PART-LEVEL}$  として、上述した対向電極電圧  $V_{COM}$  か、階調レベル電圧の両端の電圧レベル  $V_0$  若しくは  $V_8$  かを選択できるようになる。これにより、ユーザは、非表示エリアの色の選択の自由度を高めることができる。

20

【0171】

本実施形態では、非表示レベル電圧供給イネーブル信号  $LEN$  が、信号ドライバ 30 の図示しない制御回路で生成された非表示レベル電圧供給回路制御信号  $len$  と、パーシャル表示選択レジスタのブロック  $B_0$  のパーシャル表示の可否を示すパーシャル表示データ  $PART (PART')$  の反転との論理積により生成される。すなわち、非表示エリア（出力がオフ）として設定された場合にのみ所与の非表示レベル電圧を信号ラインに駆動し、表示エリア（出力がオン）として設定された場合、非表示レベル電圧供給回路  $V_{G_{0..1}}$  はハイインピーダンス状態となって信号ラインの駆動を行わない。

30

【0172】

なお、このオペアンプイネーブル信号  $OPE$  及び非表示レベル電圧供給イネーブル信号  $LEN$  は、他の信号ライン  $S_2 \sim S_{24}$  に対応する  $SDRV_{0..2} \sim SDRV_{0..24}$  にも同様に供給され、ブロック単位で信号ラインの駆動制御が行われる。

30

【0173】

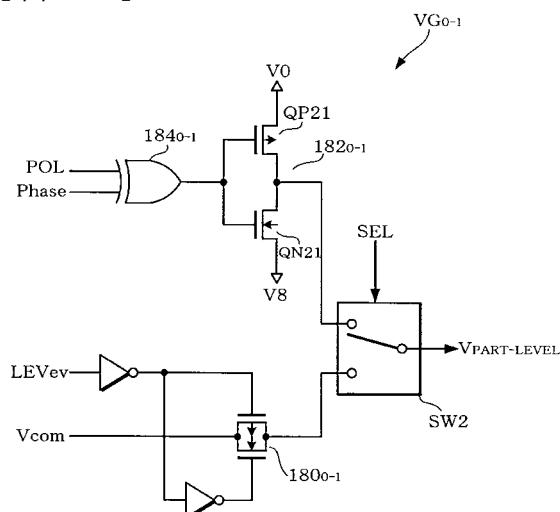

図 20 に、本実施形態における非表示レベル電圧供給回路  $V_{G_{0..1}}$  の構成の一例を示す。

【0174】

40

非表示レベル電圧供給回路  $V_{G_{0..1}}$  は、非表示レベル電圧供給イネーブル信号  $LEN$  により対向電極電圧と同等の電圧  $V_{COM}$  を出力するためのトランジスタ回路  $T180_{0..1}$ 、インバータ回路  $I182_{0..1}$  と、スイッチ回路  $SW2$  を含む。

【0175】

インバータ回路  $I182_{0..1}$  は、互いにドレイン端子が接続された  $n$  型トランジスタ  $QN2_1$  及び  $p$  型トランジスタ  $QP2_1$  を含む。 $n$  型トランジスタ  $QN2_1$  のソース端子には、電圧レベル  $V_8$  が接続される。 $p$  型トランジスタ  $QP2_1$  のソース端子には、電圧レベル  $V_0$  が接続される。 $n$  型トランジスタ  $QN2_1$  のゲート端子及び  $p$  型トランジスタ  $QP2_1$  のゲート端子は、 $XOR$  回路  $I184_{0..1}$  が接続される。 $XOR$  回路  $I184_{0..1}$  は、極性反転のタイミングを示す極性反転信号  $POL$  と、現在の位相を示す  $Phase$  との排他的論理

50

理和が演算される。

**【0176】**

このようなインバータ回路 $182_{0..1}$ は、極性反転信号POLのタイミングにしたがって、現在の位相を示すPhaseの論理レベルが反転し、電圧レベルV0若しくはV8のいずれかがスイッチ回路SW2に供給される。

**【0177】**

スイッチ回路SW2は、選択信号SELによって、トランスマスター回路 $180_{0..1}$ の出力、インバータ回路 $182_{0..1}$ の出力、又はハイインピーダンス状態のいずれか1つを非表示レベル電圧 $V_{PART-LEVEL}$ として出力する。

**【0178】**

3.7 動作例

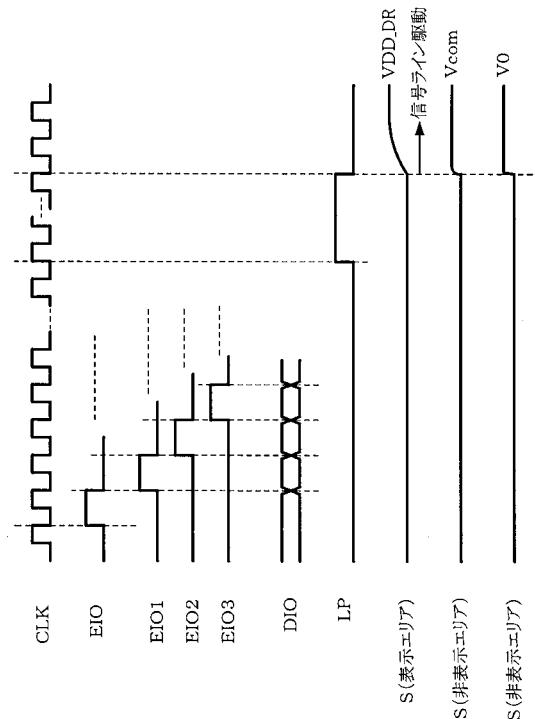

図21に、本実施形態における信号ドライバ30の動作の一例を示す。

**【0179】**

シフトレジスタは、クロック信号CLKに同期して、イネーブル入出力信号EIOがシフトされて、EIO1～EIOL（Lは、2以上の自然数）を生成する。そして、各EIO1～EIOLに同期してラインラッチに、画像データ（DIO）が順次ラッチされる。

**【0180】**

ラインラッチ36は、水平同期信号LPの立ち上がりに同期して、一水平走査単位の画像データをラッチし、その立ち下がりからDAC38及び信号ライン駆動回路40により信号ラインの駆動を行う。

**【0181】**

本実施形態では、上述したようにブロック単位で画像データに基づいて信号ラインの駆動を行うか否かを選択できるようになっており、これにより表示エリア及び非表示エリアの設定が可能となる。表示エリアに設定されたブロックの信号ラインについては、階調データに基づいて生成された駆動電圧に基づいて信号ラインが駆動される。非表示エリアに設定されたブロックの信号ラインについては、対向電極電圧 $V_{com}$ 若しくは、階調電圧レベルの両端の電圧のうちの一方が選択出力される。

**【0182】**

このような本実施系形態における信号ドライバを用いることにより、携帯電話機のようなバッテリ駆動が行われる携帯型の電子機器の表示部として、高コントラストを有する高画質化と、パーシャル表示による低消費電力化とを両立させることができるようになる。

**【0183】**

なお、本発明は上述した実施の形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形実施が可能である。例えば、上述したLCDパネルの駆動に適用されるものに限らず、エレクトロルミネッセンス、プラズマディスプレイ装置にも適用可能である。

**【0184】**

また、本実施形態では、隣接する24出力を1ブロックとして分割するものとして説明したが、これに限定されるものではない。24出力以下であっても良い、24出力以上であっても良い。また、隣接する複数の信号ラインごとに分割する必要もなく、所与の信号ライン間隔で選択した複数の信号ラインを1ブロックとして扱うようにしても良い。

**【0185】**

さらにまた、本実施形態における信号ドライバは、ライン反転駆動方式に限らず、フレーム反転駆動方式にも適用することができる。

**【0186】**

また、本実施形態では、表示装置に、LCDパネル、走査ドライバ及び信号ドライバを含むように構成したが、これに限定されるものではない。例えば、LCDパネルに、走査ドライバ及び信号ドライバを含んで構成するようにしても良い。

**【0187】**

さらに、本実施形態では、TFT液晶を用いたアクティブラチクス型液晶パネルを例に説明したが、これに限定されるものではない。

10

20

30

40

50

**【図面の簡単な説明】**

【図 1】本実施形態における信号駆動回路（信号ドライバ）を適用した表示装置の構成の概要を示すブロック図である。

【図 2】図 1 に示した信号ドライバの構成の概要を示すブロック図である。

【図 3】図 1 に示した走査ドライバの構成の概要を示すブロック図である。

【図 4】図 1 に示した L C D コントローラの構成の概要を示すブロック図である。

【図 5】図 5 ( A ) は、フレーム反転駆動方式による信号ラインの駆動電圧及び対向電極電圧  $V_{com}$  の波形を模式的に示す模式図である。図 5 ( B ) は、フレーム反転駆動方式を行った場合に、フレームごとに、各画素に対応した液晶容量に印加される電圧の極性を模式的に示す模式図である。

【図 6】図 6 ( A ) は、ライン反転駆動方式による信号ラインの駆動電圧及び対向電極電圧  $V_{com}$  の波形を模式的に示す模式図である。図 6 ( B ) は、ライン反転駆動方式を行った場合に、フレームごとに、各画素に対応した液晶容量に印加される電圧の極性を模式的に示す模式図である。

【図 7】液晶装置の L C D パネルの駆動波形の一例を示す説明図である。

【図 8】図 8 ( A )、( B )、( C ) は、本実施形態における信号ドライバにより実現したパーシャル表示の一例を模式的に示す説明図である。

【図 9】図 9 ( A )、( B )、( C ) は、本実施形態における信号ドライバにより実現したパーシャル表示の他の例を模式的に示す説明図である。

【図 10】図 10 ( A )、( B ) は、本実施形態における信号ライン駆動回路の制御内容を模式的に示す説明図である。

【図 11】図 11 ( A )、( B ) は、L C D パネルに対して異なる位置に実装される信号ドライバを模式的に示す説明図である。

【図 12】図 12 ( A )、( B )、( C ) は、ラインラッチに保持された画像データと、ブロックの対応関係を模式的に示す説明図である。

【図 13】本実施形態における信号ドライバにおいて制御されるブロック単位の構成の概要を示す構成図である。

【図 14】本実施形態における信号ドライバが有するパーシャル表示選択レジスタを示す説明図である。

【図 15】本実施形態におけるブロックデータ入れ替え回路の構成の一例を示す構成図である。

【図 16】本実施形態におけるシフトレジスタを構成する S R の構成の一例を示す構成図である。

【図 17】本実施形態における D A C によって生成される階調電圧を説明するための説明図である。

【図 18】本実施形態におけるボルテージフォロワ接続されたオペアンプ O P の構成の一例を示す回路構成図である。

【図 19】本実施形態におけるボルテージフォロワ接続されたオペアンプ O P の第 1 及び第 2 の差動增幅回路に供給される基準電圧選択信号生成回路の構成の一例を示す回路構成図である。

【図 20】本実施形態における非表示レベル電圧供給回路の構成の一例を示す構成図である。

【図 21】本実施形態における信号ドライバの動作波形の一例を示すタイミング図である。

**【符号の説明】**

1 0 液晶装置（表示装置）

2 0 L C D パネル（電気光学装置）

2 2<sub>n m</sub> T F T

2 4<sub>n m</sub> 液晶容量

2 6<sub>n m</sub> 画素電極

10

20

30

40

50

|                                        |                   |    |

|----------------------------------------|-------------------|----|

| 2 8 n <sub>m</sub>                     | 対向電極              |    |

| 3 0                                    | 信号ドライバ            |    |

| 3 2、5 2、1 4 0、1 4 0 <sub>0</sub>       | シフトレジスタ           |    |

| 3 4、3 6、3 6 <sub>0</sub>               | ラインラッチ            |    |

| 3 8、3 8 <sub>0</sub>                   | 駆動電圧生成回路 (D A C)  |    |

| 4 0、4 0 <sub>0</sub>                   | 信号ライン駆動回路         |    |

| 5 0                                    | 走査ドライバ            |    |

| 5 4、5 6                                | L / S             |    |

| 5 8                                    | 走査ライン駆動回路         |    |

| 6 0                                    | L C D コントローラ      | 10 |

| 6 2                                    | 制御回路              |    |

| 6 4                                    | R A M             |    |

| 6 6                                    | ホストI / O          |    |

| 6 8                                    | L C D I / O       |    |

| 7 0                                    | コマンドシーケンサ         |    |

| 7 2                                    | コマンド設定レジスタ        |    |

| 7 4                                    | コントロール信号生成回路      |    |

| 8 0                                    | 電源回路              |    |

| 1 0 0 B、1 0 8 B、1 2 0 B、1 2 8 B        | 非表示エリア            |    |

| 1 0 2 A、1 0 6 A、1 2 2 A、1 2 6 A        | 表示エリア             | 20 |

| 1 5 0                                  | パーシャル表示選択レジスタ     |    |

| 1 6 0 <sub>0</sub>                     | 差動増幅部             |    |

| 1 6 2 <sub>0</sub>                     | 第1の差動増幅回路         |    |

| 1 6 4 <sub>0</sub>                     | 第2の差動増幅回路         |    |

| 1 6 6 <sub>0</sub> 、1 6 8 <sub>0</sub> | 電流源               |    |

| 1 7 0 <sub>0</sub>                     | 出力増幅部             |    |

| 1 8 0 <sub>0</sub>                     | トランスマスファーレ回路      |    |

| 1 8 2 <sub>0</sub>                     | インバータ回路           |    |

| 1 8 4 <sub>0</sub>                     | X O R回路           |    |

| C L K                                  | クロック信号            | 30 |

| D A C e n                              | D A C イネーブル信号     |    |

| d a c e n                              | D A C 制御信号        |    |

| E I O                                  | イネーブル入出力信号        |    |

| L E V e n                              | 非表示レベル電圧供給イネーブル信号 |    |

| l e v e n                              | 非表示レベル電圧供給回路制御信号  |    |

| L P                                    | 水平同期信号            |    |

| O P e n                                | オペアンプイネーブル信号      |    |

| o p e n                                | オペアンプ制御信号         |    |

| P O L                                  | 極性反転信号            |    |

| S H L                                  | シフト方向切り替え信号       | 40 |

| X O E V                                | 出力イネーブル信号         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

(A)

(B)

【図6】

(A)

(B)

【図7】

【図8】

(A)

(B)

(C)

【図9】

【図10】

(A) パーシャル表示データがオンに設定されたブロック

(B) パーシャル表示データがオフに設定されたブロック

【図11】

【図12】

(A) SHL='H'

(B) SHL='L'

データ入れ替えなし(C) SHL='L'

データ入れ替えあり

【図13】

【図14】

【図15】

【図16】

【図17】

【 図 1 8 】

【 図 19 】

【 図 2 0 】

【図 2 1】

---

フロントページの続き

(56)参考文献 国際公開第97/022036 (WO, A1)

特開2000-181414 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00- 3/38

G02F 1/133 505-580

|                |                                                                                                                                                                                                                                                                                                          |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 信号驱动电路，显示装置和电光装置                                                                                                                                                                                                                                                                                         |         |            |

| 公开(公告)号        | <a href="#">JP3744818B2</a>                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2006-02-15 |

| 申请号            | JP2001155193                                                                                                                                                                                                                                                                                             | 申请日     | 2001-05-24 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                                                                                                                                                                                                                |         |            |

| 申请(专利权)人(译)    | 精工爱普生公司                                                                                                                                                                                                                                                                                                  |         |            |

| 当前申请(专利权)人(译)  | 精工爱普生公司                                                                                                                                                                                                                                                                                                  |         |            |

| [标]发明人         | 森田晶                                                                                                                                                                                                                                                                                                      |         |            |

| 发明人            | 森田晶                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G09G3/36 G02F1/133 G09G3/20                                                                                                                                                                                                                                                                              |         |            |

| CPC分类号         | G09G3/3688 G09G3/3614 G09G3/3648 G09G3/3666 G09G3/3677 G09G3/3696 G09G2310/0232<br>G09G2310/027 G09G2310/0283 G09G2310/0289 G09G2310/0291 G09G2310/0297 G09G2310/04<br>G09G2330/021 G09G2340/0414 G09G2340/0421 G09G2340/0471 G09G2340/0478                                                              |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G09G3/20.611.A G09G3/20.621.E                                                                                                                                                                                                                                                     |         |            |

| F-TERM分类号      | 2H093/NA31 2H093/NA41 2H093/NC11 2H093/NC22 2H093/NC26 2H093/NC28 2H093/NC34 2H093<br>/ND39 2H093/ND60 2H093/NF13 2H193/ZA04 2H193/ZQ09 5C006/AC24 5C006/BB14 5C006/BB16<br>5C006/BF05 5C006/FA47 5C080/AA10 5C080/BB06 5C080/DD26 5C080/FF11 5C080/JJ01 5C080<br>/JJ02 5C080/JJ03 5C080/JJ04 5C080/KK07 |         |            |

| 代理人(译)         | 井上一                                                                                                                                                                                                                                                                                                      |         |            |

| 其他公开文献         | <a href="#">JP2002351412A</a>                                                                                                                                                                                                                                                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                |         |            |

## 摘要(译)

要解决的问题：为有源矩阵型液晶面板提供信号驱动电路，使高图像质量与低功耗兼容，显示装置，电光装置和使用信号驱动的信号驱动方法。解决方案：该信号驱动器（信号驱动电路）包括移位寄存器140，该移位寄存器140通过使用为每个多个信号线分配的块作为单元，根据块的信号线的图像数据，线锁存器连续移位图36中所示的图像数据与水平同步信号LP同步地锁存，驱动电压产生电路38基于图像数据和信号线驱动电路40产生驱动电压，并且在驱动器中，基于部分显示数据PART控制部分显示以块为单位指定。基于图像数据驱动设置在显示区域中的块的信号线。此外，在非显示区域中设置的每个块的信号线由在非显示电平电压提供电路中产生的给定非显示电平电压驱动。

【図2】