(19)日本国特許庁 (JP)

(12) 公開特許公報 (A) (11)特許出願公開番号

特開2003-188183

(P2003-188183A)

(43)公開日 平成15年7月4日(2003.7.4)

| (51) Int.CI <sup>7</sup> | 識別記号 | F I            | テ-マコード (参考) |

|--------------------------|------|----------------|-------------|

| H 0 1 L 21/336           |      | G 0 2 F 1/1368 | 2 H 0 9 2   |

| G 0 2 F 1/1368           |      | G 0 9 F 9/00   | 5 C 0 9 4   |

| G 0 9 F 9/00             | 342  | 9/30           | 5 F 0 4 8   |

|                          |      | 338            | 5 F 1 1 0   |

| 9/30                     |      | 9/35           | 5 G 4 3 5   |

| 9/35                     |      | H 0 1 L 27/08  |             |

|                          |      | 331 E          |             |

|                          |      |                |             |

審査請求 未請求 請求項の数 70 L (全 38数) 最終頁に続く

(21)出願番号 特願2001-388306(P2001-388306)

(71)出願人 302036002

富士通ディスプレイテクノロジーズ株式会

社

神奈川県川崎市中原区上小田中4丁目1番1号

土井 誠児

神奈川県川崎市中原区上小田中4丁目1番1号

富士通株式会社内

(72)発明者 堀田 和重

神奈川県川崎市中原区上小田中4丁目1番1号

富士通株式会社内

(74)代理人 100108187

弁理士 横山 淳一

(22)出願日 平成13年12月20日(2001.12.20)

最終頁に続く

(54)【発明の名称】薄膜トランジスタ装置、その製造方法及び液晶表示装置

(57)【要約】

【課題】 ゲート絶縁膜の膜厚が異なるTFTを同一基板上に有し、耐圧の劣化を防止し、動作層のエッジ部での寄生TFTの動作を抑制することができる薄膜トランジスタ装置を、さらなる微細化を図りつつ作成することが可能な薄膜トランジスタ装置の製造方法を提供することを目的とする。

【解決手段】 第1の島状半導体膜24aを被覆する第1の絶縁膜25上にネガティブフォトレジスト膜26を形成する工程と、透明基板21の裏面側からネガティブフォトレジスト膜26を露光し、現像して第1の島状半導体膜24aの周縁から内側の表面に開口部を有するレジストマスクを形成する工程と、レジストマスクの開口部内の第1の絶縁膜25をエッチングする工程と、第1の絶縁膜25を被覆する第2の絶縁膜と、その上の導電体膜を形成する工程と、導電体膜をパターニングし、第1のゲート電極と第2のゲート電極とを形成する工程とを有する。

## 【特許請求の範囲】

【請求項1】 透明基板の表面に第1及び第2の島状半導体膜を形成する工程と、

前記第1及び第2の島状半導体膜を被覆する第1の絶縁膜を形成する工程と、

前記第1の絶縁膜上にネガティブフォトレジスト膜を形成する工程と、

前記第1の島状半導体膜の全域を遮光するマスクを介して前記ネガティブフォトレジスト膜を露光する工程と、前記透明基板の裏面側から前記ネガティブフォトレジスト膜を露光する工程と、

前記ネガティブフォトレジスト膜を現像して前記第1の島状半導体膜の周縁から内側の表面に開口部を有するレジストマスクを形成する工程と、

前記レジストマスクの開口部内の前記第1の絶縁膜をエッチングする工程と、

前記レジストマスクを除去する工程と、

前記透明基板の表面側全面に第2の絶縁膜を形成し、さらにその上に導電体膜を形成する工程と、

前記第1の島状半導体膜上方の導電体膜上に第1のマスクパターンを形成し、前記第2の島状半導体膜上方の導電体膜上に第2のマスクパターンを形成する工程と、前記第1のマスクパターンをマスクとして前記導電体膜をエッチングして第1のゲート電極を形成し、前記第2のマスクパターンをマスクとして前記導電体膜をエッチングして第2のゲート電極を形成する工程とを有することを特徴とする薄膜トランジスタ装置の製造方法。

【請求項2】 基板上に第1及び第2の島状半導体膜を形成する工程と、

前記第1及び第2の島状半導体膜を被覆する半導体膜を形成し、さらに該半導体膜上に絶縁膜を形成する工程と、

前記絶縁膜を選択的にエッチングして前記第2の島状半導体膜上方に前記絶縁膜のパターンを形成する工程と、前記絶縁膜のパターンの下部及びその他の部分の半導体膜を酸化して、前記第1の島状半導体膜上に前記半導体膜を酸化してなる絶縁膜からなる第1のゲート絶縁膜を形成し、前記第2の島状半導体膜上に前記半導体膜を酸化してなる絶縁膜と前記絶縁膜のパターンとからなる第2のゲート絶縁膜を形成する工程と、

前記第1のゲート絶縁膜上に第1のゲート電極を形成し、前記第2のゲート絶縁膜上に第2のゲート電極を形成する工程とを有することを特徴とする薄膜トランジスタ装置の製造方法。

【請求項3】 基板上に第1の半導体膜を形成する工程と、

前記第1の半導体膜上に第1の絶縁膜と第2の半導体膜と第2の絶縁膜とをこの順に形成する工程と、

前記第2の絶縁膜を選択的にエッチングして前記第2の絶縁膜のパターンを形成する工程と、

10

前記第2の半導体膜を選択的にエッチングして、前記第2の絶縁膜のパターンを含まない島状の第2の半導体膜と、前記第2の絶縁膜のパターンを含む島状の第2の半導体膜とを形成する工程と、

前記第2の絶縁膜のパターンの下部及びその他の部分の島状の第2の半導体膜を酸化するとともに、前記島状の第2の半導体膜で覆われていない領域の第1の半導体膜を前記第1の絶縁膜を介して酸化し、前記第2の絶縁膜のパターンを含まない島状の第2の半導体膜で覆われていた領域に前記第1の半導体膜からなる第1の島状半導体膜を形成し、前記第2の絶縁膜のパターンを含む島状の第2の半導体膜で覆われていた領域に前記第1の半導体膜からなる第2の島状半導体膜を形成するとともに、前記第1の島状半導体膜上に前記第2の半導体膜を酸化してなる絶縁膜と前記第1の絶縁膜とからなる第1のゲート絶縁膜を形成し、前記第2の島状半導体膜上に前記第2の絶縁膜のパターンと前記第2の半導体膜を酸化してなる絶縁膜と前記第1の絶縁膜とからなる第2のゲート絶縁膜を形成する工程と、

前記第1のゲート絶縁膜上に第1のゲート電極を形成し、前記第2のゲート絶縁膜上に第2のゲート電極を形成する工程とを有することを特徴とする薄膜トランジスタ装置の製造方法。

【請求項4】 チャネル領域を挟んで形成された一対のソース／ドレイン領域を有する第1の島状半導体膜と、前記第1の島状半導体膜の前記チャネル領域上に形成された第1の絶縁膜からなる第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1の導電体膜からなる第1のゲート電極とにより構成された第1の薄膜トランジスタと、

チャネル領域を挟んで形成された一対のソース／ドレイン領域を有する第2の島状半導体膜と、前記第2の島状半導体膜の前記チャネル領域上に形成された前記第1の絶縁膜及び第2の絶縁膜からなる第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2の導電体膜からなる第2のゲート電極とにより構成された第2の薄膜トランジスタとを同一の基板上に有し、

前記第1の薄膜トランジスタは前記第1の島状半導体膜の両側部のエッジの上方で、かつ前記第1のゲート電極上に前記第2の絶縁膜を介して前記第2の導電体膜からなる電界緩和電極を有し、前記第2の薄膜トランジスタは前記第2のゲート電極下で、かつ前記第2の島状半導体膜の両側部のエッジの上に前記第1の絶縁膜を介して前記第1の導電体膜からなる電界緩和電極を有することを特徴とする薄膜トランジスタ装置。

【請求項5】 基板上に第1及び第2の島状半導体膜を形成する工程と、

前記第1及び第2の島状半導体膜を被覆する第1の絶縁膜を形成する工程と、

50 全面に第1の導電体膜を形成し、さらに前記第1の導電

体膜を選択的にエッティングして前記第1の島状半導体膜の上方の第1の絶縁膜上に第1のゲート電極を形成する工程と、

全面に第2の絶縁膜と第2の導電体膜をこの順に形成する工程と、

前記第2の導電体膜の上にマスクパターンを形成し、該マスクパターンをマスクとして前記第2の導電体膜をサイドエッティングして前記マスクパターンよりも幅が狭い第2のゲート電極を形成する工程と、

前記マスクパターンをマスクとして前記第2の絶縁膜を異方性エッティングし、

さらに前記第1のゲート電極及び前記マスクパターンをマスクとして前記第1の絶縁膜を異方性エッティングして、前記第1のゲート電極下に前記第1の絶縁膜からなる第1のゲート絶縁膜を形成するとともに、前記第2のゲート電極下に前記第1及び第2の絶縁膜からなる第2のゲート絶縁膜を形成する工程と、

前記マスクパターンを除去する工程と、

前記第1のゲート電極をマスクとして前記第1の島状半導体膜に不純物をイオン注入して前記第1のゲート電極の両側に高濃度不純物領域を形成し、前記第2のゲート電極及び前記第2のゲート絶縁膜をマスクとして前記第2の島状半導体膜に不純物をイオン注入して、前記第2のゲート電極の両側に一対の高濃度不純物領域を形成する工程と、

前記第2のゲート電極をマスクとし、かつ前記第2のゲート電極の周辺部の第2のゲート絶縁膜を透過する条件で前記第2の島状半導体膜に不純物をイオン注入して、前記第2のゲート電極の両側で前記第2のゲート絶縁膜下に一対の低濃度不純物領域を形成する工程とを有することを特徴とする薄膜トランジスタ装置の製造方法。

【請求項6】 基板上に形成された第1の薄膜トランジスタと、第2の薄膜トランジスタと、前記第2の薄膜トランジスタのソース／ドレイン領域と接続された画素電極と、前記画素電極と交差する蓄積容量バスラインとを有し、

前記第1の薄膜トランジスタは、

チャネル領域を挟んで形成された一対のソース／ドレン領域を有する第1の島状半導体膜と、

前記第1の島状半導体膜の前記チャネル領域上に形成された第1の絶縁膜からなる第1のゲート絶縁膜と、

前記第1のゲート絶縁膜上に形成された第1の導電体膜からなる第1のゲート電極とにより構成され、

前記第2の薄膜トランジスタは、

チャネル領域を挟んで形成された一対のソース／ドレン領域を有し、そのうち何れか一が前記画素電極と接続した第2の島状半導体膜と、

前記第2の島状半導体膜の前記チャネル領域上に形成された前記第1の絶縁膜及び第2の絶縁膜からなる第2のゲート絶縁膜と、

\*前記第2のゲート絶縁膜上に形成された第2の導電体膜からなる第2のゲート電極とにより構成され、前記蓄積容量バスラインは、

前記第1の導電体膜により構成され、その一部領域で、前記蓄積容量バスライン上に前記第2の絶縁膜と前記画素電極と接続された第2の導電体膜とがこの順に積層されてなることを特徴とする液晶表示装置。

【請求項7】 基板上に形成された第1の薄膜トランジスタと、第2の薄膜トランジスタと、前記第2の薄膜トランジスタのソース／ドレイン領域と接続された画素電極と、前記画素電極と交差する蓄積容量バスラインとを有し、

前記第1の薄膜トランジスタは、チャネル領域を挟んで形成された一対のソース／ドレン領域を有する第1の島状半導体膜と、

前記第1の島状半導体膜の前記チャネル領域上に形成された第1の絶縁膜からなる第1のゲート絶縁膜と、

前記第1のゲート絶縁膜上に形成された第1の導電体膜からなる第1のゲート電極とにより構成され、

前記第2の薄膜トランジスタは、チャネル領域を挟んで形成された一対のソース／ドレン領域を有し、そのうち何れか一が前記画素電極と接続した第2の島状半導体膜と、

前記第2の島状半導体膜の前記チャネル領域上に形成された前記第1の絶縁膜及び第2の絶縁膜からなる第2のゲート絶縁膜と、

前記第2のゲート絶縁膜上に形成された第2の導電体膜からなる第2のゲート電極とにより構成され、

前記蓄積容量バスラインは、

前記第1の導電体膜により構成され、その一部領域で、前記蓄積容量バスラインをゲート電極とし、前記画素電極と接続されたソース／ドレン領域を有する第3の島状半導体膜と、前記第1の絶縁膜からなるゲート絶縁膜とを有する第3の薄膜トランジスタを備えていることを特徴とする液晶表示装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】 本発明は、薄膜トランジスタ装置、その製造方法及び液晶表示装置に関し、より詳しくは、液晶表示装置その他の絶縁性基板上に形成される薄膜トランジスタ装置、その製造方法及び液晶表示装置に関する。

【0002】

【従来の技術】 液晶表示装置は、軽量かつ薄型で、低消費電力であることなどの特徴を有し、携帯端末やビデオカメラのファインダ、ノートパソコンなど幅広い分野に応用されている。特に、コンピュータ用ディスプレイなど高品質かつ高精細な表示を得る用途に、薄膜トランジスタ（以下、TFTと称する。）をスイッチング素子とするアクティブラトリックス液晶表示装置が多用されてい

る。

【0003】アクティブマトリクス液晶表示装置においては、その駆動能力の高さからポリシリコン膜を動作層とするTFT(以下、pSi-TFTと称する。)が用いられている。近年、ポリシリコンの成膜技術の進歩に伴い、低コスト化、高機能化を目的として、表示領域内の薄膜トランジスタ(以下、画素TFTと称する。)と、表示領域外の周辺回路部のTFTとを同一の基板上に形成する検討が行われている。

【0004】画素TFTは液晶駆動に用いるためゲートやドレインに高電圧を印加する必要があり、ゲート電圧やドレイン電圧に対して高耐圧であることが要求される。一方、周辺回路部のTFTは低消費電力で高速な動作が可能なことが要求される。

【0005】これを実現するため、特開平10-170953号公報等には、ゲート絶縁膜を厚くした画素TFTと、ゲート絶縁膜を薄くした周辺回路部のTFTとを同一の基板上に設けた例が提案されている。

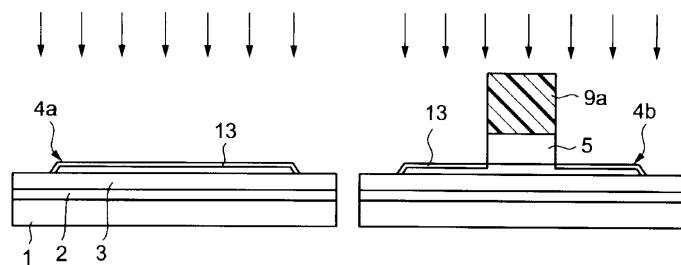

【0006】図29に、同一基板上に形成された画素TFTと周辺回路部のTFTとで、ゲート絶縁膜の膜厚が異なる液晶表示装置の断面構造を示す。なお、周辺回路部のTFTでも高電圧のかかるものがあり、画素TFTと同じ構造が採られる。

【0007】上記の液晶表示装置の製造方法においては、ポリシリコン膜からなる島状半導体膜4a、4b上にシリコン酸化膜からなるゲート絶縁膜を形成する際に、多層の絶縁膜を順次形成し、かつ不要な絶縁膜をエッチングすることにより、厚膜部と薄膜部で絶縁膜の積層数を変えて膜厚の調整を行っている。

【0008】具体的には、基板全面に第1の絶縁膜を成膜した後、エッチングにより厚膜部のTFTの形成領域に第1の絶縁膜5を残し、他の領域では除去する。

【0009】次いで、全面に第2の絶縁膜と金属膜とをこの順に成膜したのち、金属膜をパターニングして薄膜部のTFTの形成領域において、第2の絶縁膜6a上に第1のゲート電極7aを形成し、厚膜部のTFTの形成領域において第1の絶縁膜5と第2の絶縁膜6bとの積層構造上に第2のゲート電極7bを形成する。これにより、薄膜部のTFTの形成領域において、第1のゲート電極7aの下に第2の絶縁膜6aの単層構造からなる第1のゲート絶縁膜を形成し、厚膜部のTFTの形成領域において第2のゲート電極7bの下に第1及び第2の絶縁膜5、6bの2層構造からなる第2のゲート絶縁膜を形成する。

【0010】また、厚膜部のTFTは、一般的に、ホットキャリアによるオン特性の劣化を抑制し、かつオフ電流を低減するために、図33に示すように、ゲート電極75下のチャネル領域4beと高濃度不純物領域4b a、4b bとの隣接領域に低濃度不純物領域4bc、4bdが設けられたLDD(Lightly Doped Drain)構造

を有している。上から見たとき、チャネル領域4beと低濃度不純物領域4bc、4bdとの境界は、ゲート電極75のエッジのほぼ真下に位置している。なお、低濃度不純物領域4bc、4bdに対応する領域を不純物を導入しないオフセット領域とすることもある。

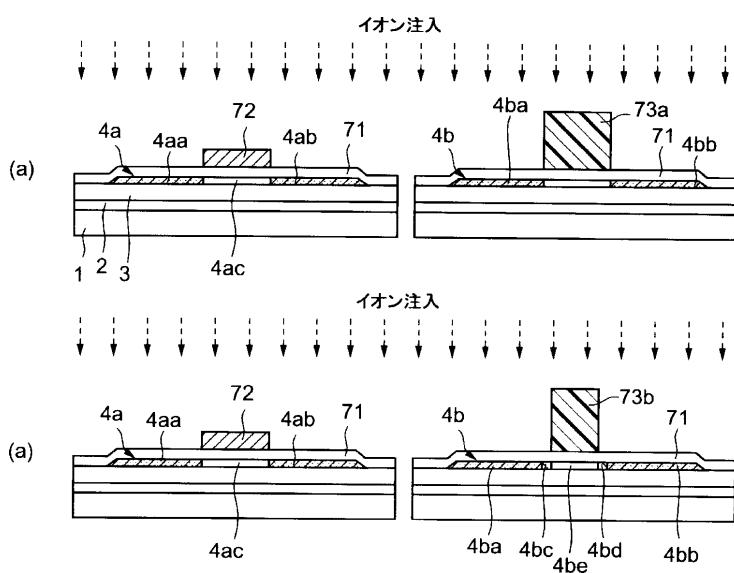

【0011】薄膜部において通常のTFTを形成し、かつ厚膜部においてLDD構造を有するTFTを形成するため、図34(a)に示すように、まず、薄膜部のTFTの形成領域において第1の絶縁膜71上に第1のゲート電極72を形成した後、厚膜部のTFTの形成領域においてゲート電極の形成領域よりも片側でLDD領域分だけ幅が広いレジストマスク73aで覆う。次いで、第1のゲート電極72とレジストマスク73aをマスクとしてイオン注入し、第1のゲート電極72の両側の島状半導体膜4a内に高濃度不純物領域4aa、4abを形成するとともに、レジストマスク73aの両側の島状半導体膜4b内に高濃度不純物領域4ba、4bbを形成する。

【0012】次いで、レジストマスク73aを除去した後、図34(b)に示すように、厚膜部のTFTの形成領域において、レジストマスク73aが形成されていた領域よりも狭い領域に新たなレジストマスク73bを形成する。続いて、レジストマスク73bに基づいてイオン注入して、レジストマスク73bのエッジから高濃度不純物領域4ba、4bbのエッジの間の領域に低濃度不純物領域4bc、4bdを形成する。なお、低濃度不純物領域4bc、4bdに挟まれた領域がチャネル領域4beとなる。

【0013】次に、第1のゲート電極72とレジストマスク73bをマスクとして第1の絶縁膜71をエッチングして、図33に示すように、第1のゲート電極72下に第1のゲート絶縁膜71aを形成し、レジストマスク73bの下に第1の絶縁膜71bを残す。次いで、レジストマスク73bを除去した後、全面に第2の絶縁膜と金属膜を形成する。

【0014】次いで、金属膜をパターニングして、図33に示すように、厚膜部のTFTの形成領域においてチャネル領域4beの上方に第2のゲート電極75を形成し、続いて、第2のゲート電極75をマスクとして第2の絶縁膜をエッチングして第2の絶縁膜74aを残す。これにより、第2のゲート電極75の下に第1及び第2の絶縁膜71b、74aからなる2層構造の第2のゲート絶縁膜が形成される。

【0015】以降、通常の工程を経て、図33に示す薄膜トランジスタ装置を作成することができる。なお、図33中、符号76は第1の層間絶縁膜、76a乃至76dはコンタクトホール、77a乃至77dはソース/ドレイン電極、78は第2の層間絶縁膜である。

【0016】

【発明が解決しようとする課題】しかしながら、図29

に示す従来の製造方法では、図30に示すように、ドライエッティング法で第1の絶縁膜5をエッティングする場合、特に薄膜部のTFTの形成領域の島状半導体膜4aの表面、特にチャネル領域の表面がエッティングガスのプラズマに曝されるため、島状半導体膜4aの表面にダメージ層13が生じ、薄膜部のTFTの特性が厚膜部のTFTの特性に比べて劣化してしまうという問題があった。

【0017】一方、図31(a)に示すように、フッ酸等を用いたウエットエッティング法で第1の絶縁膜5をエッティングする場合、島状半導体膜4a、4bの下層の下地シリコン酸化膜3とのエッティング選択比をとることが困難であるので、オーバエッティング時に下地のシリコン酸化膜3もエッティングされてしまう。このため、島状半導体膜4a、4bのエッジ部下のシリコン酸化膜3に「えぐれ14」が生じる。

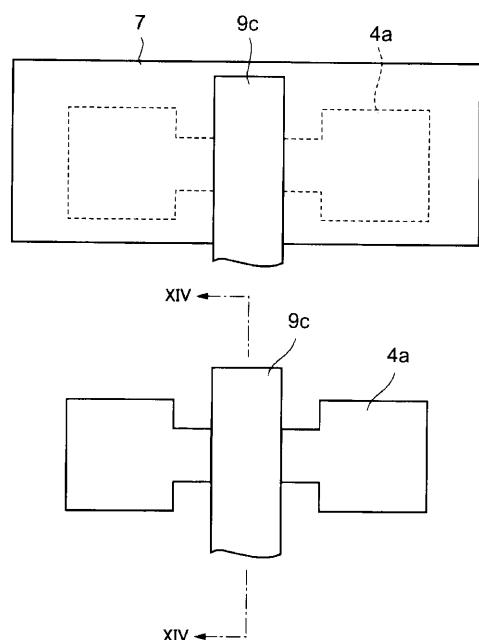

【0018】このため、図31(b)に示すように、その後第2の絶縁膜6及びゲート電極となる金属膜7を形成し、図32(a)、(b)に示すように、レジストマスク9cによりパターニングしてゲート電極7aを形成すると、薄膜部のTFTのゲート絶縁膜は第2の絶縁膜6aのみで薄いため、島状半導体膜4aのエッジ部のえぐれ部分で第2の絶縁膜6aにクラックが発生しやすくなる。従って、薄膜部のTFTのゲート耐圧が極端に劣化してしまうという問題があった。

【0019】さらに、島状半導体膜4aのエッジ部にえぐれが生じなくても、島状半導体膜4aのエッジ部はエッティングによりテーパがついて先端が鋭角になっているため、特に薄膜部のTFTにおいては、ゲート電圧を印加すると電界の集中が生じ、所謂寄生TFTが正規よりも早く動作してしまうという問題があった。

【0020】また、これらを防ぐため、薄膜部のTFTの島状半導体膜4aのエッジ部のみを被覆する構造では、一般的に基板1上面からのマスク露光により形成するため、マスク精度や位置合わせ精度のマージンを確保する点から、島状半導体膜4a、4bの幅を大きくする必要があり、TFTの微細化に限界が生じてしまう。

【0021】また、図34(a)、(b)に示す従来の製造方法では、LDD構造を形成する際、微細化の進展に伴い、高濃度不純物領域4ba、4bbと低濃度不純物領域4bc、4bdとゲート電極75とを相互の配置を保ったまま形成することが困難になってきており、微細化の妨げとなっている。

【0022】また、図33に示すゲート絶縁膜を構成する多層の絶縁膜71b、74aをそれぞれ別々の工程でエッティングしているため、手間がかかり、工程の簡略化が望まれている。

【0023】本発明は、上記従来例の問題点に鑑みて創作されたものであり、ゲート絶縁膜の膜厚が異なるTFTを同一基板上に有し、厚膜部のTFTをLDD構造と

する薄膜トランジスタ装置であって、特性や耐圧の劣化を防止し、動作層のエッジ部での寄生TFTの動作を抑制することができる薄膜トランジスタ装置と、工程の簡略化を図り、かつさらなる微細化を図りつつそのような薄膜トランジスタ装置を形成することが可能な薄膜トランジスタ装置の製造方法と、薄膜トランジスタ装置を用いた液晶表示装置を提供することを目的とする。

#### 【0024】

【課題を解決するための手段】本願請求項1に記載の薄膜トランジスタ装置の製造方法は、透明基板の表面に第1及び第2の島状半導体膜を形成する工程と、前記第1及び第2の島状半導体膜を被覆する第1の絶縁膜を形成する工程と、前記第1の絶縁膜上にネガティブフォトレジスト膜を形成する工程と、前記第1の島状半導体膜の全域を遮光するマスクを介して前記ネガティブフォトレジスト膜を露光する工程と、前記透明基板の裏面側から前記ネガティブフォトレジスト膜を露光する工程と、前記ネガティブフォトレジスト膜を現像して前記第1の島状半導体膜の周縁から内側の表面に開口部を有するレジストパターンを形成する工程と、前記レジストパターンの開口部内の前記第1の絶縁膜をエッティングする工程と、前記レジストパターンを除去する工程と、前記透明基板の表面側全面に第2の絶縁膜を形成し、さらにその上に導電体膜を形成する工程と、前記第1の島状半導体膜上方の導電体膜上に第1のマスクパターンを形成し、前記第2の島状半導体膜上方の導電体膜上に第2のマスクパターンを形成する工程と、前記第1のマスクパターンをマスクとして前記導電体膜をエッティングして第1のゲート電極を形成し、前記第2のマスクパターンをマスクとして前記導電体膜をエッティングして第2のゲート電極を形成する工程とを有することを特徴とする。

【0025】本発明においては、薄い膜厚の第1のゲート絶縁膜を有する薄膜トランジスタの形成領域において、第1のゲート絶縁膜を形成する前に、第1の絶縁膜で第1の島状半導体膜の周縁部を覆っている。従って、第1の絶縁膜上に第1のゲート絶縁膜となる第2の絶縁膜と第1のゲート電極となる導電体膜とを積層すると、第1のゲート電極下の第1の島状半導体膜の周縁部は第2の絶縁膜のほかに第1の絶縁膜で覆われる。このため、第1の島状半導体膜の周縁部でゲート電圧印加時の電界集中を緩和して寄生薄膜トランジスタが動作するのを防止することができる。

【0026】また、薄い膜厚の第1のゲート絶縁膜を有する薄膜トランジスタの形成領域において、第1の島状半導体膜の上方のネガティブフォトレジスト膜の未露光領域に対して、第1の島状半導体膜をマスクとして透明基板の裏面から露光光を照射しているので、第1の島状半導体膜の周縁から光が回折する範囲で自己整合的にその未露光領域が露光される。このため、極めて精度よく第1の島状半導体膜の周縁部を第1の絶縁膜で覆うこと

ができるので、第1の島状半導体膜のチャネル幅方向の寸法マージンを最小にすることができる、従って薄膜トランジスタの微細化が可能である。

【0027】本願請求項2記載の薄膜トランジスタ装置の製造方法は、基板上に第1及び第2の島状半導体膜を形成する工程と、前記第1及び第2の島状半導体膜を被覆する半導体膜を形成し、さらに該半導体膜上に絶縁膜を形成する工程と、前記第2の島状半導体膜上方の前記絶縁膜を選択的にエッチングして前記絶縁膜のパターンを形成する工程と、前記絶縁膜のパターンの下部及びその他の部分の半導体膜を酸化して、前記第1の島状半導体膜上に前記半導体膜を酸化してなる絶縁膜からなる第1のゲート絶縁膜を形成し、前記第2の島状半導体膜上に前記半導体膜を酸化してなる絶縁膜と前記絶縁膜のパターンとからなる第2のゲート絶縁膜を形成する工程と、前記第1のゲート絶縁膜上に第1のゲート電極を形成し、前記第2のゲート絶縁膜上に第2のゲート電極を形成する工程とを有することを特徴とする。

【0028】本発明によれば、半導体膜上の絶縁膜をエッチングして第2のゲート絶縁膜の一部となる絶縁膜を形成するときに、下地の半導体膜により第1の島状半導体膜が保護されるため、第1の島状半導体膜のチャネル領域が絶縁膜のエッチングガスのプラズマに曝されない。このため、薄い膜厚の第1のゲート絶縁膜を有する薄膜トランジスタの特性が劣化するのを防止して、厚い膜厚の第2のゲート絶縁膜を有する薄膜トランジスタ及び薄い膜厚の第1のゲート絶縁膜を有する薄膜トランジスタともに良好な特性を確保することができる。

【0029】また、第1及び第2の島状半導体膜の下地の基板も半導体膜により保護されているため、基板表面に絶縁膜が形成されている場合、第1及び第2の島状半導体膜の端部で基板表面の絶縁膜がエッチングされることによる「えぐれ」も生じない。

【0030】さらに、半導体膜上の絶縁膜をエッチングして第2のゲート絶縁膜の一部となる絶縁膜を形成するときに、絶縁膜のエッチャントに対して半導体膜はエッチング耐性を有するため膜減りしない。この実施の形態では、半導体膜を酸化して第1のゲート絶縁膜を形成しているため、第1のゲート絶縁膜の膜厚を精度よく、かつ容易に制御することが可能である。

【0031】本願請求項3記載の薄膜トランジスタ装置の製造方法は、基板上に第1の半導体膜を形成する工程と、前記第1の半導体膜上に第1の絶縁膜と第2の半導体膜と第2の絶縁膜とをこの順に形成する工程と、前記第2の絶縁膜を選択的にエッチングして前記第2の絶縁膜のパターンを形成する工程と、前記第2の半導体膜を選択的にエッチングして、前記第2の絶縁膜のパターンを含まない島状の第2の半導体膜と、前記第2の絶縁膜のパターンを含む島状の第2の半導体膜とを形成する工程と、前記第2の絶縁膜のパターンの下部及びその他の

部分の島状の第2の半導体膜を酸化するとともに、前記島状の第2の半導体膜で覆われていない領域の第1の半導体膜を前記第1の絶縁膜を介して酸化し、前記第2の絶縁膜のパターンを含まない島状の第2の半導体膜で覆われていた領域に前記第1の半導体膜からなる第1の島状半導体膜を形成し、前記第2の絶縁膜のパターンを含む島状の第2の半導体膜で覆われていた領域に前記第1の半導体膜からなる第2の島状半導体膜を形成するとともに、前記第1の島状半導体膜上に前記第2の半導体膜を酸化してなる絶縁膜と前記第1の絶縁膜とからなる第1のゲート絶縁膜を形成し、前記第2の島状半導体膜上に前記第2の絶縁膜のパターンと前記第2の半導体膜を酸化してなる絶縁膜と前記第1の絶縁膜とからなる第2のゲート絶縁膜を形成する工程と、前記第1のゲート絶縁膜上に第1のゲート電極を形成し、前記第2のゲート絶縁膜上に第2のゲート電極を形成する工程とを有することを特徴とする。

【0032】本発明によれば、第2の半導体膜上の第2の絶縁膜をエッチングして第2のゲート絶縁膜の一部となる絶縁膜を形成するときに、下地の第2の半導体膜により第1の島状半導体膜が保護されるため、第1の島状半導体膜のチャネル領域が第2の絶縁膜のエッチングガスのプラズマに曝されない。このため、薄い膜厚の第1のゲート絶縁膜を有する薄膜トランジスタの特性が劣化するのを防止して、厚い膜厚の第2のゲート絶縁膜を有する薄膜トランジスタ及び薄い膜厚の第1のゲート絶縁膜を有する薄膜トランジスタともに良好な特性を確保することができる。

【0033】また、第2のゲート絶縁膜のうち厚い絶縁膜となる、第2の半導体膜上の第2の絶縁膜をエッチングした後に、第2の半導体膜を酸化するとともに、第2の半導体膜下の第1の半導体膜を選択的に酸化して第1及び第2の島状半導体膜を形成している。このように、下地の基板表面は絶縁膜のエッチングガス等に曝されないため、第1及び第2の島状半導体膜の端部で所謂「えぐれ」を生じない。

【0034】さらに、第2の絶縁膜をエッチングして第2のゲート絶縁膜の一部となる絶縁膜を形成するときに、第2の絶縁膜のエッチャントに対して第2の半導体膜はエッチャント耐性を有するため膜減りしない。この実施の形態では、第2の半導体膜を酸化してなる絶縁膜と第1の絶縁膜とにより第1のゲート絶縁膜を形成しているため、第1のゲート絶縁膜の膜厚を精度よく、かつ容易に制御することが可能である。

【0035】本願請求項4記載の薄膜トランジスタ装置は、チャネル領域を挟んで形成された一対のソース／ドレイン領域を有する第1の島状半導体膜と、前記第1の島状半導体膜の前記チャネル領域上に形成された第1の絶縁膜からなる第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1の導電体膜からなる第1の

ゲート電極とにより構成された第1の薄膜トランジスタと、チャネル領域を挟んで形成された一対のソース／ドレイン領域を有する第2の島状半導体膜と、前記第2の島状半導体膜の前記チャネル領域上に形成された前記第1の絶縁膜及び第2の絶縁膜からなる第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2の導電体膜からなる第2のゲート電極とにより構成された第2の薄膜トランジスタとを同一の基板上に有し、前記第1の薄膜トランジスタは前記第1の島状半導体膜の両側部のエッジの上方で、かつ前記第1のゲート電極上に前記第2の絶縁膜を介して前記第2の導電体膜からなる電界緩和電極を有し、前記第2の薄膜トランジスタは前記第2のゲート電極下で、かつ前記第2の島状半導体膜の両側部のエッジの上に前記第1の絶縁膜を介して前記第1の導電体膜からなる電界緩和電極を有することを特徴とする。

【0036】本発明によれば、第1の薄膜トランジスタにおいては、第1の島状半導体膜の両側部のエッジの上方で、かつ第1のゲート電極上に、第2の絶縁膜を介して電界緩和電極を有している。従って、この部分の寄生容量は、第1の島状半導体膜と第1の絶縁膜と第1のゲート電極とで形成される容量に対して、第1のゲート電極と第2の絶縁膜と電界緩和電極とで形成される静電容量分だけ大きくなる。このため、薄膜トランジスタのゲートを交流で駆動する場合、第1の島状半導体膜の両側部のエッジ部分にかかるゲート電位は遅く立ち上がる。従って、第1の島状半導体膜の両側部のエッジ部の寄生トランジスタが動作するのを抑制することができる。

【0037】また、第2の薄膜トランジスタにおいては、第2のゲート電極下で、かつ第2の島状半導体膜の両側部のエッジの上に第1の絶縁膜を介して電界緩和電極を有している。従って、電界緩和電極の電位を第2の島状半導体膜の両側部のエッジ部のチャネルが導通しない電位に設定しておくことで、第2の島状半導体膜の両側部のエッジ部のチャネルが導通するのを抑制し、また、第2のゲート電極からの電界の影響をシールドして、寄生トランジスタがオンするのを抑制することができる。

【0038】本願請求項5記載の薄膜トランジスタ装置の製造方法は、基板上に第1及び第2の島状半導体膜を形成する工程と、前記第1及び第2の島状半導体膜を被覆する第1の絶縁膜を形成する工程と、全面に第1の導電体膜を形成し、さらに前記第1の導電体膜を選択的にエッティングして前記第1の島状半導体膜の上方の第1の絶縁膜上に第1のゲート電極を形成する工程と、全面に第2の絶縁膜と第2の導電体膜をこの順に形成する工程と、前記第2の導電体膜の上にマスクパターンを形成し、該マスクパターンをマスクとして前記第2の導電体膜をサイドエッティングして前記マスクパターンよりも幅が狭い第2のゲート電極を形成する工程と、前記マスク

10 パターンをマスクとして前記第2の絶縁膜を異方性エッティングし、さらに前記第1のゲート電極及び前記マスクパターンをマスクとして前記第1の絶縁膜を異方性エッティングして、前記第1のゲート電極下に前記第1の絶縁膜からなる第1のゲート絶縁膜を形成するとともに、前記第2のゲート電極下に前記第1及び第2の絶縁膜からなる第2のゲート絶縁膜を形成する工程と、前記マスクパターンを除去する工程と、前記第1のゲート電極をマスクとして前記第1の島状半導体膜に不純物をイオン注入して前記第1のゲート電極の両側に高濃度不純物領域を形成し、前記第2のゲート電極及び前記第2のゲート絶縁膜をマスクとして前記第2の島状半導体膜に不純物をイオン注入して、前記第2のゲート電極の両側に一対の高濃度不純物領域を形成する工程と、前記第2のゲート電極をマスクとし、かつ前記第2のゲート電極の周辺部の第2のゲート絶縁膜を透過する条件で前記第2の島状半導体膜に不純物をイオン注入して、前記第2のゲート電極の両側で前記第2のゲート絶縁膜下に一対の低濃度不純物領域を形成する工程とを有することを特徴とする。

【0039】本発明によれば、マスクパターンに基づき、第2の導電体膜をサイドエッティングして、マスクパターンよりも幅が狭い第2のゲート電極を形成し、さらに、同じマスクパターンに基づき、第1及び第2の絶縁膜を異方性エッティングして第2のゲート電極よりも幅が広い第2のゲート絶縁膜を形成している。そして、第2のゲート電極及び第2のゲート絶縁膜を透過しないような条件でイオン注入して高濃度不純物領域を形成し、さらに第2のゲート電極を透過せず、かつ第2のゲート絶縁膜を透過するような条件でイオン注入して、第2の島状半導体膜に低濃度不純物領域を形成している。これにより、第2のゲート電極下のチャネル領域を挟んでチャネル領域の近くから低濃度不純物領域と高濃度不純物領域とが第2の島状半導体膜に形成される。

【0040】従って、サイドエッティングの幅がLDD領域として必要な幅となるように調整することにより、露光用マスクを増やさずに、ゲート電極やゲート絶縁膜を利用して自己整合的にLDD構造を形成することができる。

【0041】また、膜厚の異なる第1及び第2のゲート絶縁膜を一度のエッティングにより形成することができる。この場合、第1及び第2の島状半導体膜のチャネル領域はお互いにエッティングガスのプラズマに曝されないので、第1及び第2の島状半導体膜のチャネル領域表面にダメージ層が発生するのを防止することができる。

【0042】本願請求項6記載の液晶表示装置は、基板上に形成された第1の薄膜トランジスタと、第2の薄膜トランジスタと、前記第2の薄膜トランジスタのソース／ドレイン領域と接続された画素電極と、前記画素電極

と交差する蓄積容量バスラインとを有し、前記第1の薄膜トランジスタは、チャネル領域を挟んで形成された一対のソース／ドレイン領域を有する第1の島状半導体膜と、前記第1の島状半導体膜の前記チャネル領域上に形成された第1の絶縁膜からなる第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1の導電体膜からなる第1のゲート電極とにより構成され、前記第2の薄膜トランジスタは、チャネル領域を挟んで形成された一対のソース／ドレイン領域を有し、そのうち何れか一が前記画素電極と接続した第2の島状半導体膜と、前記第2の島状半導体膜の前記チャネル領域上に形成された前記第1の絶縁膜及び第2の絶縁膜からなる第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2の導電体膜からなる第2のゲート電極とにより構成され、前記蓄積容量バスラインは、前記第1の導電体膜により構成され、その一部領域で、前記蓄積容量バスライン上に前記第2の絶縁膜と前記画素電極と接続された第2の導電体膜とがこの順に積層されてなることを特徴とする。

【0043】本発明によれば、第1の薄膜トランジスタの第1のゲート電極と同じ材料の表示部の蓄積容量バスラインを有し、蓄積容量バスライン上に第2の絶縁膜と画素電極と接続された第2の導電体膜とがこの順に積層されてなる。言い換えれば、蓄積容量バスラインを一方の電極とし、第2のゲート絶縁膜のうち第2の絶縁膜と同じ材料の絶縁膜を容量絶縁膜とし、第2のゲート電極と同じ材料の第2の導電体膜を他方の電極とする容量素子が形成される。

【0044】これにより、ゲート絶縁膜は通常薄く形成されるので、ITO膜を他方の電極とし、層間絶縁膜を容量絶縁膜とする容量素子よりも、単位面積当たり高い容量値の容量素子を得ることができる。これにより、蓄積容量を形成するために必要な蓄積容量バスラインの面積、即ち遮光領域を減らすことができるので、開口率を向上させることができる。

【0045】本願請求項7記載の液晶表示装置は、基板上に形成された第1の薄膜トランジスタと、第2の薄膜トランジスタと、前記第2の薄膜トランジスタのソース／ドレイン領域と接続された画素電極と、前記画素電極と交差する蓄積容量バスラインとを有し、前記第1の薄膜トランジスタは、チャネル領域を挟んで形成された一対のソース／ドレイン領域を有する第1の島状半導体膜と、前記第1の島状半導体膜の前記チャネル領域上に形成された第1の絶縁膜からなる第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1の導電体膜からなる第1のゲート電極とにより構成され、前記第2の薄膜トランジスタは、チャネル領域を挟んで形成された一対のソース／ドレイン領域を有し、そのうち何れか一が前記画素電極と接続した第2の島状半導体膜と、前記第2の島状半導体膜の前記チャネル領域上に形成され

た前記第1の絶縁膜及び第2の絶縁膜からなる第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2の導電体膜からなる第2のゲート電極とにより構成され、前記蓄積容量バスラインは、前記第1の導電体膜により構成され、その一部領域で、前記蓄積容量バスラインをゲート電極とし、前記画素電極と接続されたソース／ドレイン領域を有する第3の島状半導体膜と、前記第1の絶縁膜からなるゲート絶縁膜とを有する第3の薄膜トランジスタを備えていることを特徴とする。

【0046】本発明によれば、蓄積容量バスラインは、第1のゲート電極と同じ材料である第1の導電体膜により構成され、その一部領域で、蓄積容量バスラインをゲート電極とし、画素電極と接続されたソース／ドレイン領域を有する第3の島状半導体膜と、第2のゲート絶縁膜のうち第1の絶縁膜と同じ材料の絶縁膜からなるゲート絶縁膜とを有している。

【0047】言い換えれば、これらは薄膜トランジスタを構成している。チャネルが常に導通するようなゲート電圧をゲート電極に印加することにより、第3の島状半導体膜は低抵抗の電極となり得る。従って、蓄積容量バスラインを一方の電極とし、第1の絶縁膜を容量絶縁膜とし、第3の島状半導体膜を他方の電極とする蓄積容量素子が形成される。

【0048】これにより、ゲート絶縁膜は通常薄く形成されるので、ITO膜を他方の電極とし、層間絶縁膜を容量絶縁膜とする蓄積容量素子よりも、単位面積当たり高い容量値の蓄積容量素子を得ることができる。これにより、蓄積容量を形成するために必要な蓄積容量バスラインの面積、即ち遮光領域を減らすことができるので、開口率を向上させることができる。

【0049】

【発明の実施の形態】以下、本発明の実施の形態について図面を参照して説明する。

【0050】(第1の実施の形態)

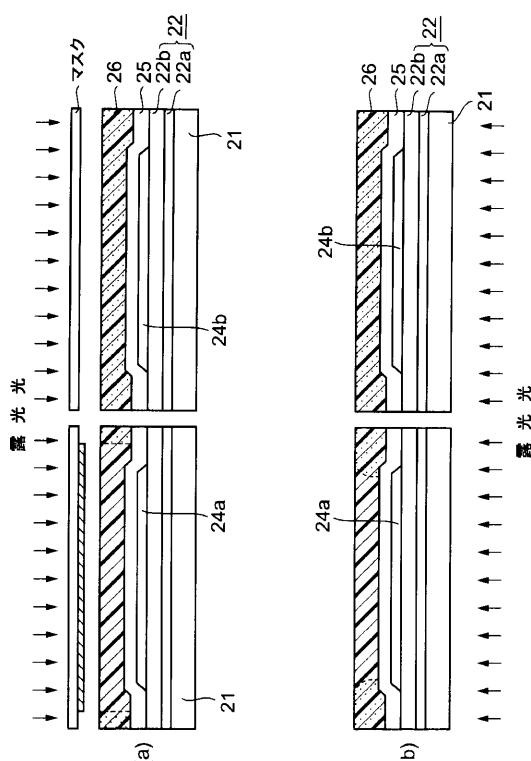

(薄膜トランジスタ装置の構造)図1は、本発明の第1の実施の形態である薄膜トランジスタ装置(透過型液晶表示装置)の構成を示すブロック図である。図2は表示部の一画素の構成を示す平面図である。但し、以下の例ではXGA(1024×768ピクセル)モードの液晶表示装置について説明する。1個のピクセルはR(赤色)、G(緑色)、及びB(青色)の3個の画素により構成される。

【0051】この実施の形態の液晶表示装置は、制御回路101、データドライバ102、ゲートドライバ103及び表示部104により構成されている。この液晶表示装置には、コンピュータ等の外部装置(図示せず)から表示信号RGB、水平同期信号Hsync及び垂直同期信号Vsync等の信号が供給され、電源(図示せず)から高電圧VH(18V)、低電圧VL(3.3V又は5V)及び接地電位Vgndが供給される。

【0052】表示部104には、水平方向に3072(1024×RGB)個、垂直方向に768個の画素が配列されている。各画素は、nチャネル型のTFT(以下、n型TFTと称する。特に断らない限りTFTの記載はn型TFTのことをいう。)105と、このTFT105のソース電極に接続された表示セル(液晶セル)106及び蓄積容量107により構成されている。

【0053】表示セル106は、TFT105のソース電極と接続された画素電極110を一方の電極とし、CF基板上の電極(図示しない)を他方の電極とする一对の電極と、それらの電極間の液晶(図示しない)により構成される。

【0054】また、表示部104には、垂直方向に延びる3072本のデータバスライン108と、水平方向に延びる768本のゲートバスライン109と、同じく水平方向に延びる蓄積容量バスライン111とが設けられている。水平方向に並ぶ画素の各TFT105のゲート電極は同一のゲートバスライン109に接続され、垂直方向に並ぶ各画素のTFT105のドレイン電極は同一のデータバスライン108に接続されている。また、蓄積容量バスライン111は画素電極110と交差するように形成され、蓄積容量107の一対の電極のうち一方の電極となる。蓄積容量107は画素電極110と蓄積容量バスライン111を一对の電極とし、一对の電極間に挟まれた層間絶縁膜を容量絶縁膜とする。

【0055】制御回路101は、水平同期信号Hsync及び垂直同期信号Vsyncを入力し、1水平同期期間の開始時にアクティブになるデータスタート信号DSIと、1水平期間を一定の間隔に分割するデータクロックDCLKと、1垂直同期期間の開始時にアクティブになるゲートスタート信号GSIと、1垂直同期期間を一定の間隔に分割するゲートクロックGCLKとを出力する。この制御回路101は、低電圧VLで駆動するn型TFT及びpチャネル型のTFT(p型TFT)により構成されている。

【0056】データドライバ102は、シフトレジスタ102a、レベルシフタ102b及びアナログスイッチ102cにより構成されている。

【0057】シフトレジスタ102aは、3072個の出力端子を有している。このシフトレジスタ102aはデータスタート信号DSIにより初期化され、データクロックDCLKに同期したタイミングで各出力端子から順番に低電圧(3.3V又は5V)のアクティブ信号を出力する。このシフトレジスタ102aは低電圧VLで駆動するn型TFT及びp型TFTにより構成されている。

【0058】レベルシフタ102bは、3072個の入力端子と3072個の出力端子を備えている。そして、シフトレジスタ102aから出力された低電圧のアクティブ信号を、高電圧(18V)に変換して出力する。このレベルシフタ102bは、低電圧VLで駆動するn型TFT及びp型TFTと、高電圧VHで駆動するn型T

FET及びp型TFTにより構成されている。

【0059】アナログスイッチ102cも3072個の入力端子と3072個の出力端子とを有している。アナログスイッチ102cの各出力端子は、それぞれ対応するデータバスライン108に接続されている。アナログスイッチ102cは、レベルシフタ102bからアクティブ信号を入力すると、アクティブ信号を入力した入力端子に対応する出力端子に表示信号RGB(R信号、G信号及びB信号の何れか1つ)を出力する。このアナログスイッチ102cは、高電圧VHで駆動するn型TFT及びp型TFTにより構成されている。

【0060】すなわち、データドライバ102は、1水平期間内にデータクロックDCLKに同期したタイミングで、表示部104の3072本のデータバスライン108にR信号、G信号及びB信号を順番に出力する。

【0061】ゲートドライバ103は、シフトレジスタ103a、レベルシフタ103b及び出力バッファ103cにより構成されている。

【0062】シフトレジスタ103aは、768個の出力端子を有している。このシフトレジスタ103aはゲートスタート信号により初期化され、ゲートクロックGCLKに同期したタイミングで各出力端子から順番に低電圧(3.3V又は5V)の走査信号を出力する。このシフトレジスタ103aは、低電圧VLで駆動するn型TFT及びp型TFTにより構成されている。

【0063】レベルシフタ103bは、768個の入力端子と768個の出力端子とを有している。出力バッファ103cの各出力端子は、それぞれ対応するゲートバスライン109に接続されている。出力バッファ103cは、レベルシフタ103bから入力された走査信号を、入力端子に対応する出力端子を介してゲートバスライン109に供給する。この出力バッファ103cは、高電圧VHで駆動するn型TFT及びp型TFTにより構成されている。

【0064】すなわち、ゲートドライバ103からは、1垂直同期期間内にゲートクロックGCLKに同期したタイミングで、表示部104の768本のゲートバスライン109に走査信号を順番に供給する。

【0065】表示部104のTFT105は、ゲートバスライン109に走査信号が供給されるとオンとなる。このとき、データバスライン108に表示信号RGB(R信号、G信号及びB信号の何れか1つ)が供給されると、表示セル106及び蓄積容量107に表示信号RGBが書き込まれる。表示セル106では、書き込まれた表示信号RGBにより液晶分子の傾きが変化し、その結果表示セル106の光透過率が変化する。各画素毎に表示セル106の光透過率を制御することによって、所望の画像が表示される。

【0066】以下の実施の形態では、表示部104内に設けられたTFTを画素TFTという。また、データド

ライバ102及びゲートドライバ103内のTFTのうち高電圧(18V)で駆動するTFTを、高電圧駆動用TFTという。さらに、制御回路101、データドライバ102及びゲートドライバ103内のTFTのうち低電圧(3.3V又は5V)で駆動するTFTを、低電圧駆動用TFTという。

【0067】(液晶表示装置に用いられた薄膜トランジスタの構造)以下に、上記3種類のTFTの構造について説明する。ここで、高電圧駆動用TFTは画素TFTとほぼ同じ構造を有するので、それらを代表して画素TFTについて説明し、高電圧駆動用TFTはその説明を省略する。また、p型TFTはn型TFTとほぼ同じ構造を有するので、その説明を省略する。

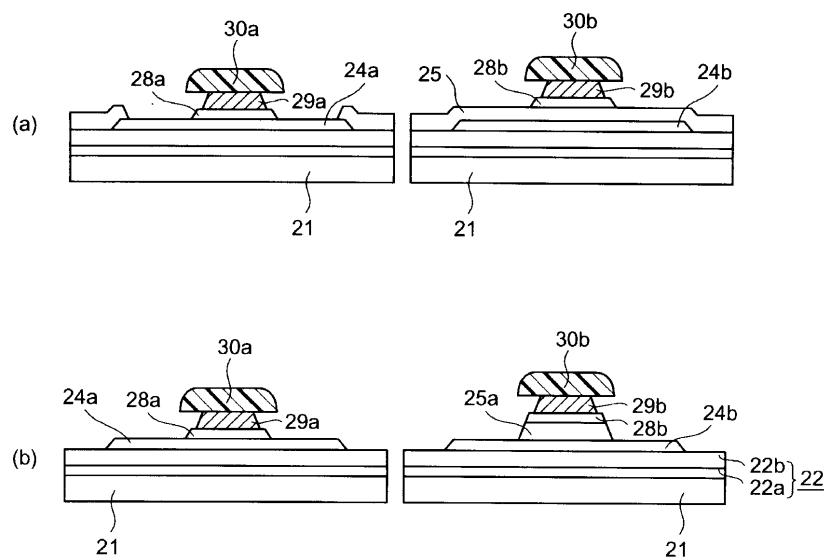

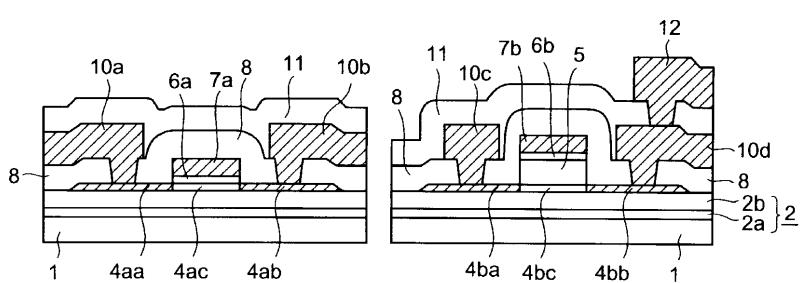

【0068】図10(b)の左の図は低電圧駆動用TFTの構造を示す断面図である。同じく右の図は画素TFTの構造を示す断面図であり、図2のI-I線に沿う断面を示す。

【0069】まず、低電圧駆動用TFTにおいては、図10(b)の左の図に示すように、ガラス基板21上にシリコン窒化膜22aとシリコン酸化膜22bの積層構造からなる下地絶縁膜22が形成されている。この下地絶縁膜22の上にTFTの動作層となるポリシリコン膜からなる第1の島状半導体膜24aが形成されている。この第1の島状半導体膜24aには、TFTのソース/ドレインである一対の高濃度不純物領域(オーミックコンタクト領域)24aa、24abがチャネル領域24acを挟んで形成されている。

【0070】下地絶縁膜22及び第1の島状半導体膜24aの上には、厚さが30nmのシリコン酸化膜(SiO<sub>2</sub>膜)28aからなるゲート絶縁膜が形成されている。また、このシリコン酸化膜28aの上には、ゲート電極29aが形成されている。低電圧駆動用TFTでは、高濃度不純物領域24aa、24abのチャネル領域側のエッジが、いずれもゲート電極29aのエッジのほぼ真下に位置している。

【0071】シリコン酸化膜28a及びゲート電極29aの上には、厚さが90nmのシリコン酸化膜31と厚さが350nmのシリコン窒化膜(SiN膜)32とが積層されている。シリコン窒化膜32の上には電極(ソース電極及びドレイン電極)34a、34bが形成されている。これらの電極34a、34bは、シリコン窒化膜32の上面から高濃度不純物領域24aa、24abに通じるコンタクトホール33a、33b内に埋め込まれた金属により、高濃度不純物領域24aa、24abに電気的に接続されている。

【0072】以上のように、低電圧駆動用TFTは、ゲート絶縁膜が厚さ30nmのシリコン酸化膜28aのみで構成されており、さらにLDD領域が設けられていないので、低電圧での高速動作が可能である。また、不純物領域24aa、24abがゲート電極29aに対し、

自己整合的に形成できるので、素子の微細化が容易である。なお、この低電圧駆動用TFTにはLDD領域が設けられていないが、低電圧駆動するのでホットエレクトロンが少なく、ホットエレクトロンに起因するオン特性の劣化とオフ電流の増大が回避される。

【0073】次に、画素TFTにおいては、図10(b)の右側の図に示すように、ガラス基板21の上には上記したと同じ積層構造の下地絶縁膜22が形成されている。この下地絶縁膜22上には、TFTの動作層となるポリシリコン膜からなる第2の島状半導体膜24bが形成されている。第2の島状半導体膜24bにTFTのソース/ドレインである一対のn型高濃度不純物領域(オーミックコンタクト領域)24ba、24bbがチャネル領域24beを挟んで形成されている。また、これらのn型高濃度不純物領域24ba、24bbのチャネル領域24be側の端部には、n型低濃度不純物領域であるLDD領域24bc、24bdが形成されている。

【0074】下地絶縁膜22及び第2の島状半導体膜24bの上には、厚さが90nmのシリコン酸化膜25aと厚さが30nmのシリコン酸化膜28bとを積層してなるゲート絶縁膜が形成されている。そして、シリコン酸化膜28bの上にはゲート電極29bが形成されている。ゲート電極29bはゲートバスライン109と一体的に形成されている。また、ゲート電極29bと同じ材料で蓄積容量バスライン111が形成されている。

【0075】この画素TFTでは、上から見たときに、ゲート電極29bの両側のエッジのほぼ真下に、LDD領域24bc、24bdのチャネル領域側エッジが配置されている。画素TFTでは、表示信号として正及び負の信号が与えられるので、ソース側及びドレイン側の両方にLDD領域24bc、24bdを設けないと、ホットエレクトロンによるトランジスタ特性の劣化が発生する。

【0076】ゲート電極29bの露出した表面を被覆するようにシリコン酸化膜31と厚さ350nmのシリコン窒化膜32が形成されている。シリコン窒化膜32の上には電極(ソース/ドレイン電極)34c、34dが形成されている。これらの電極34c、34dは、シリコン窒化膜32の上面から高濃度不純物領域24ba、24bbに通じるコンタクトホール33c、33d内に埋め込まれた金属により、高濃度不純物領域24ba、24bbに電気的に接続されている。一対のソース/ドレイン電極34c、34dのうちドレイン側のソース/ドレイン電極34cはデータバスライン108と一体的に形成されている。

【0077】以上のように、これらの画素TFTによれば、ゲート絶縁膜が120nmと厚いシリコン酸化膜(シリコン酸化膜25a+シリコン酸化膜28b)で形成されているので、耐圧が高く、高電圧で駆動させるこ

とができる。

【0078】なお、説明を省略した高電圧駆動用TFTにおいて、画素TFTと異なるところは高電圧のかかるドレイン側にのみLDD領域を有している点である。また、説明を省略した周辺回路の高電圧駆動用p型TFTではLDD領域は設けられていない。これは、p型TFTの場合は、キャリアが正孔であるので、ホットキャリアの発生がほとんどなく、LDD領域を設けなくてもトランジスタ特性に支障がないからである。

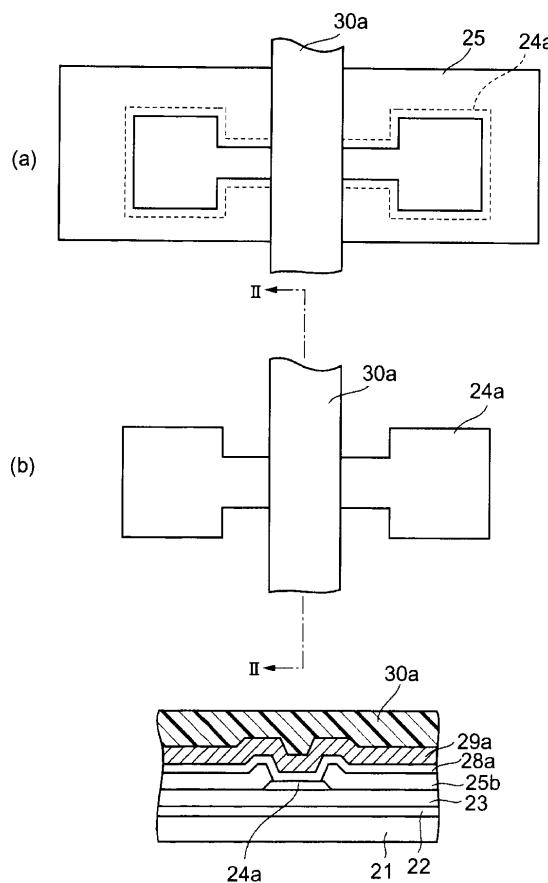

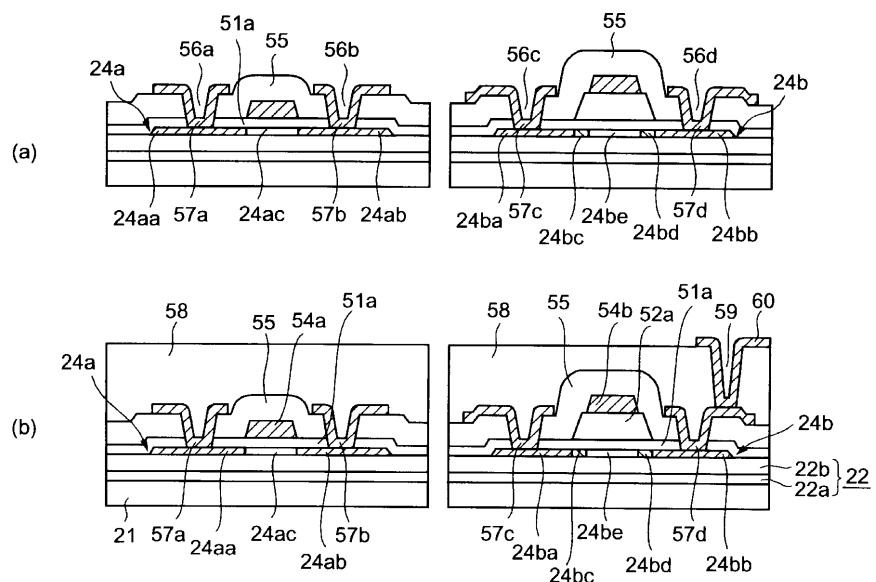

【0079】(薄膜トランジスタ装置の製造方法)次に、本実施の形態の薄膜トランジスタ装置の製造方法について、図3乃至図12を参照して説明する。なお、これらの図のうち図3乃至10において、左の図が低電圧駆動用TFTの形成領域における断面図であり、右の図は画素TFTの形成領域における断面図である。また、図11(a)は低電圧駆動用TFTの製造工程途中の図8(a)における平面図、同図(b)は同じく図8(b)における平面図及びII-II線に沿う断面図である。図12(a)は画素TFTの製造工程途中の図8(a)における平面図、同図(b)は同じく図8(b)における平面図及びIII-III線に沿う断面図である。

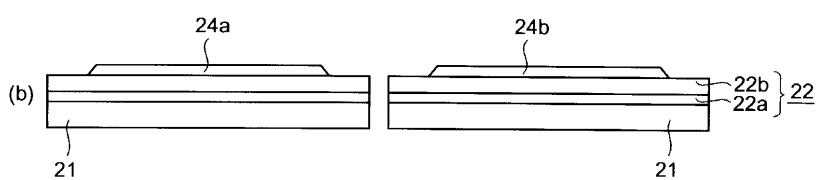

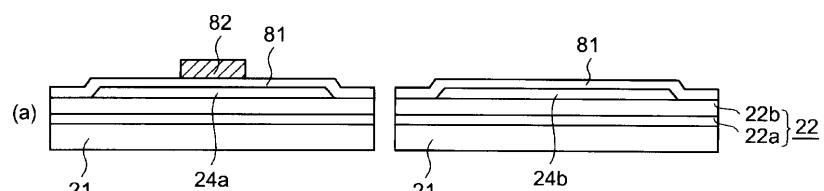

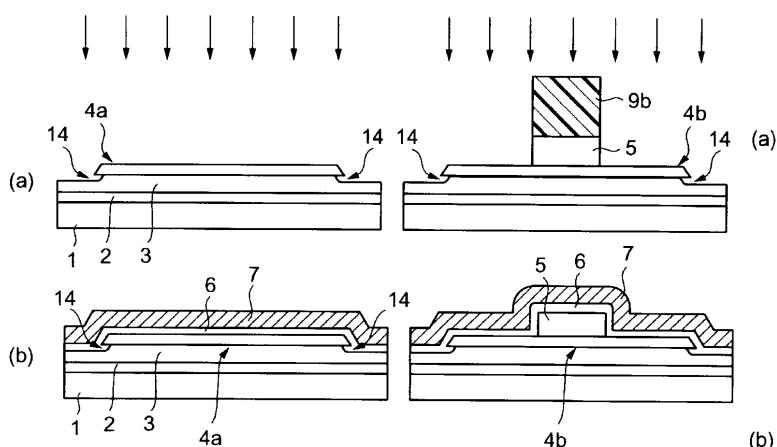

【0080】まず、図3(a)に示すように、プラズマCVD法により、ガラス基板21の上に、下地絶縁膜としてシリコン塗化膜22aを約50nm、シリコン酸化膜22bを200nmの厚さに形成する。続いて、シリコン酸化膜22bの上にアモルファスシリコン膜24を約50nmの厚さで形成する。

【0081】次に、アモルファスシリコン膜24中の水素を低減するために、450の温度でアニールする。そして、アモルファスシリコン膜24にエキシマレーザを照射して、アモルファスシリコン膜24をポリシリコン膜に変化させる。

【0082】次に、ポリシリコン膜の上にフォトレジストを塗布し、選択露光及び現像工程を経て、所定のレジストマスク(図示せず)を形成する。そして、このレジストマスクに基づき、ポリシリコン膜をドライエッティングし、図3(b)に示すように、所定の領域のみにポリシリコン膜からなる第1及び第2の島状半導体膜24a、24bを残す。その後、レジストマスクを除去する。

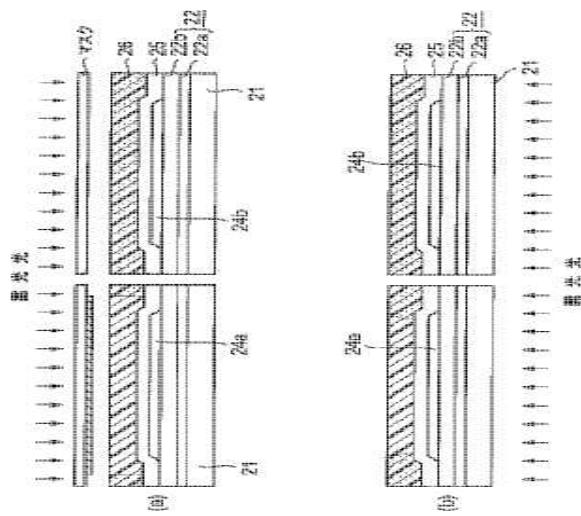

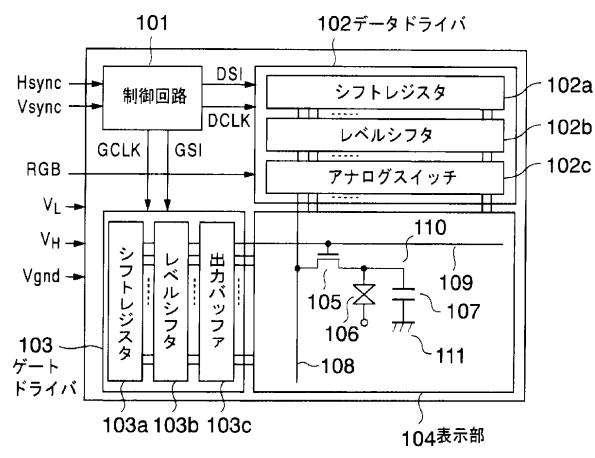

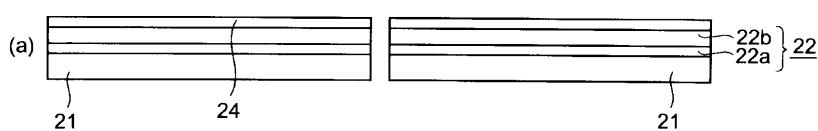

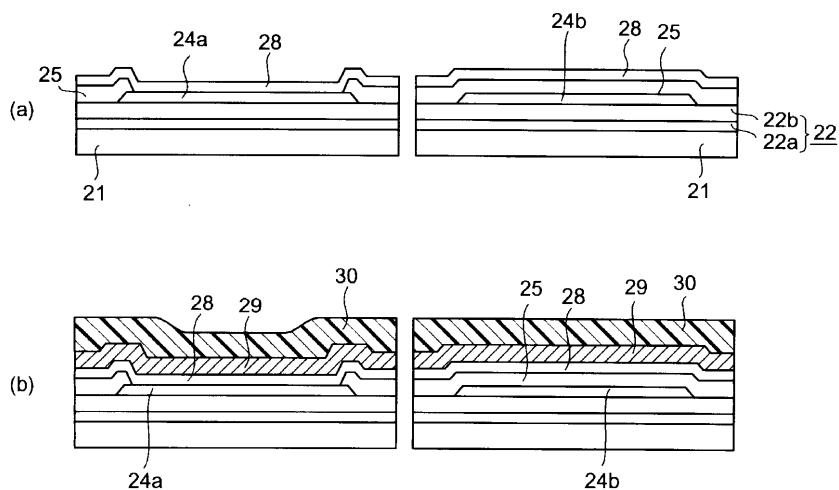

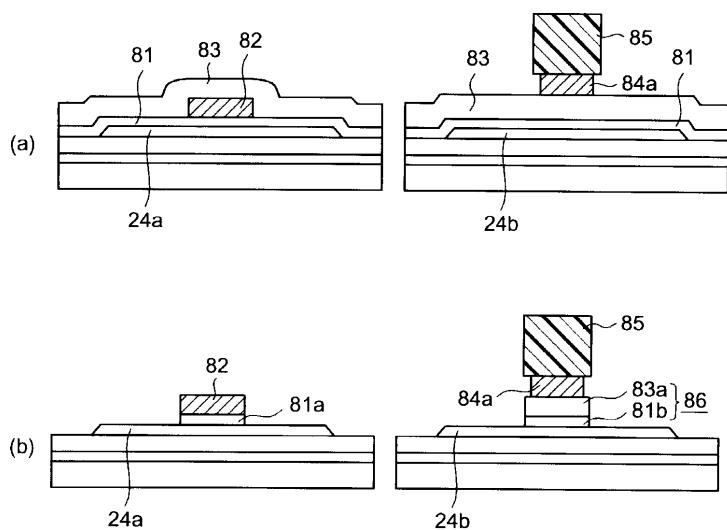

【0083】次に、図4(a)に示すように、プラズマCVD法により、ガラス基板21の上側全面に第1のシリコン酸化膜(第1の絶縁膜)25を90nmの厚さに成膜する。続いて、塗布法により第1のシリコン酸化膜25の上にネガティブフォトレジスト膜26を形成する。次いで、低電圧駆動用TFTの形成領域の第1の島状半導体膜24a全体を遮光するようなマスクを用いて、ネガティブフォトレジスト膜26を露光する。これにより、低電圧駆動用TFTの形成領域の第1の島状半導体膜24a上方であって、第1の島状半導体膜24a

の形成領域よりも広い範囲でネガティブフォトレジスト膜26の未露光領域が残る。

【0084】次に、図4(b)に示すように、背面からガラス基板21を介してネガティブフォトレジスト膜26を露光する。このとき、露光光は第1の島状半導体膜24aにより遮光されるが、周縁部での光の回折により、第1の島状半導体膜24aの周縁よりも内側の一定の範囲までネガティブフォトレジスト膜26が露光される。

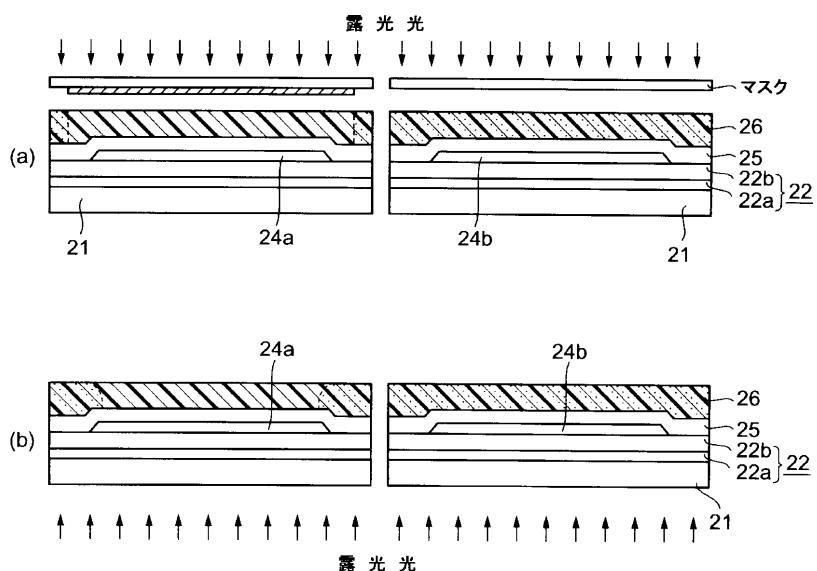

10 【0085】次に、図5(a)に示すように、ネガティブフォトレジスト膜26を現像する。これにより、ネガティブフォトレジスト膜26には第1の島状半導体膜24aの周縁よりも内側の領域に開口部26aが形成される。

【0086】次に、図5(b)に示すように、現像により形成されたレジストマスク26の開口部26aを通して第1のシリコン酸化膜25をドライエッティングする。これにより、第1の島状半導体膜24aの周縁よりも内側の領域に第1のシリコン酸化膜25の開口部25aが形成される。即ち、第1のシリコン酸化膜25は第1の島状半導体膜24aの周縁部を覆うように残る。その後、ネガティブフォトレジスト膜26を除去する。

【0087】次に、図6(a)に示すように、プラズマCVD法により、ガラス基板21の上側全面に第2のシリコン酸化膜(第2の絶縁膜)28を30nmの厚さに形成する。

【0088】次に、図6(b)に示すように、第2のシリコン酸化膜28の上にAl-Nd(アルミニウム-ネオジム: Nd含有量は2at.%、導電体膜)膜29を約300nmの厚さに形成する。続いて、Al-Nd膜29の上にフォトレジスト膜30を形成する。

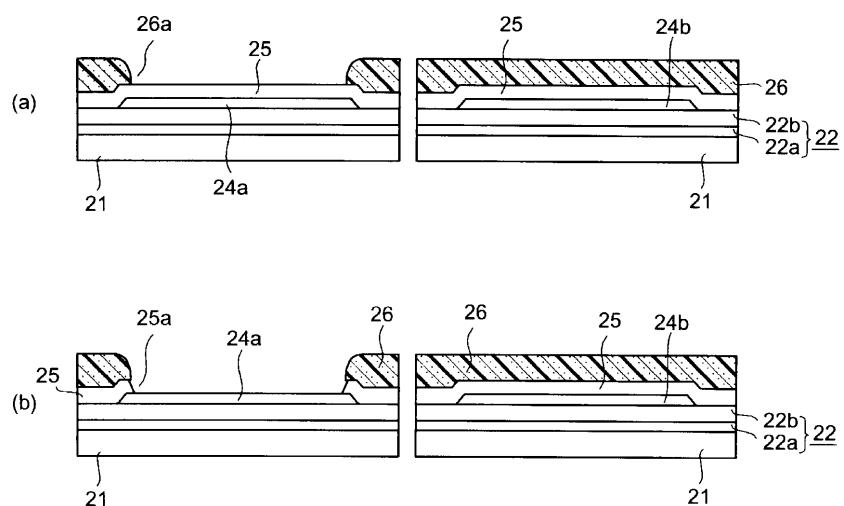

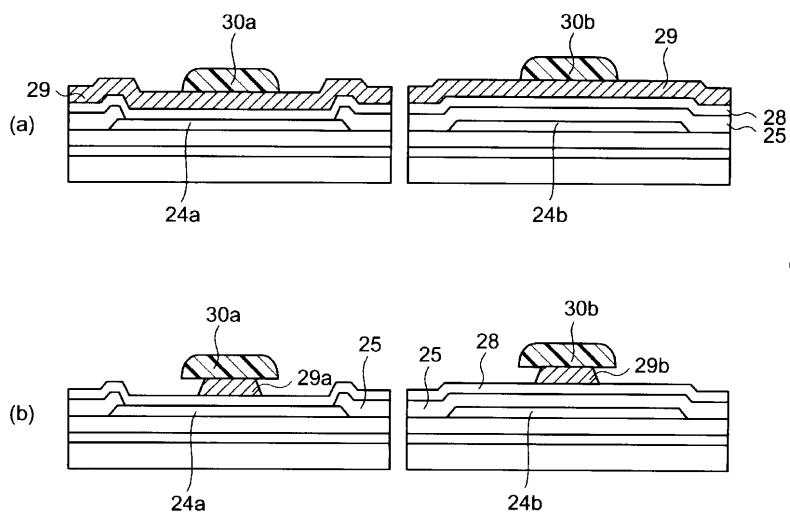

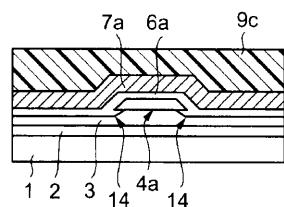

【0089】次に、フォトレジスト膜30を選択露光し、現像して、図7(a)に示すように、各TFTのゲート電極を形成すべき領域にレジストマスク30a、30bを形成する。次いで、図7(b)に示すように、レジストマスク30a、30bに基づき、Al-Nd膜29をエッティングして、低電圧駆動用TFTのゲート電極29aと、画素TFTのゲート電極29bとを形成する。

40 【0090】次に、図8(a)に示すように、レジストマスク30a、30bに基づき、第2のシリコン酸化膜28を異方性エッティングする。このとき、低電圧駆動用TFTの形成領域を上から見た場合、図11(a)に示すようになっている。また、画素TFTの形成領域を上から見た場合、図12(a)に示すようになっている。

【0091】続いて、図8(b)に示すように、ガラス基板21上方に残る、かつレジストマスク30a、30bで覆われていないシリコン酸化膜25をエッティングにより除去する。このとき、低電圧駆動用TFTの形成領域において、第1の島状半導体膜24aの周縁部をゲー

ト電極29aが横切る領域では、図11(b)に示すように、ゲート電極29aの下に第1の島状半導体膜24aを覆ってシリコン酸化膜25b、28aが残る。また、画素TFTの形成領域においても、第2の島状半導体膜24bの周縁部をゲート電極29bが横切る領域では、図12(b)に示すように、ゲート電極29bの下に第2の島状半導体膜24bを覆ってシリコン酸化膜25a、28bが残る。なお、高電圧駆動用TFTの形成領域においても同様にゲート電極の下に島状半導体膜を覆って厚いシリコン酸化膜と薄いシリコン酸化膜がともに残る。

【0092】その後、レジストマスク30a、30bを除去する。

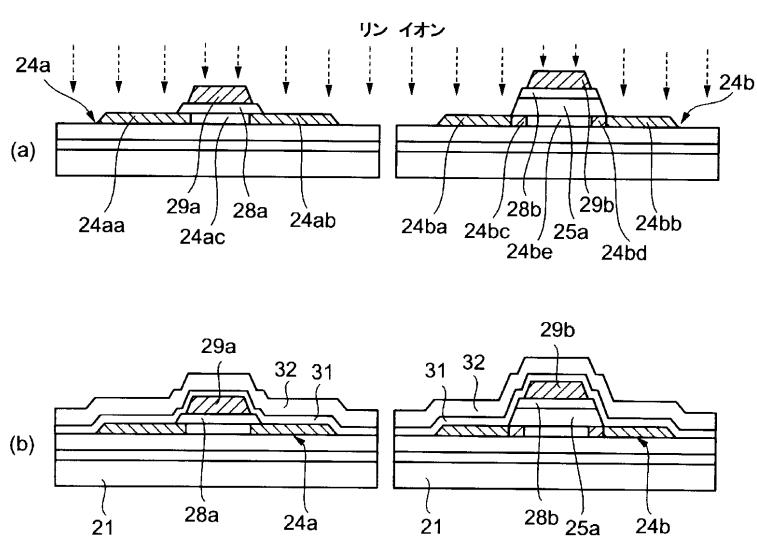

【0093】次に、図9(a)に示すように、ゲート電極29a、29b及びゲート絶縁膜28b及び25bを透過せずに、ゲート絶縁膜28aを透過するような条件、例えば、加速電圧が25keV、注入量が $7 \times 10^{14} \text{ cm}^{-2}$ の条件で第1及び第2の島状半導体膜24a、24bにリン(P)をイオン注入する。これにより、低電圧駆動用TFTの形成領域のゲート電極29aに覆われていない領域の第1の島状半導体膜24aに高濃度不純物領域(ソース/ドレイン領域)24aa、24abが形成される。また、画素TFTの形成領域のゲート電極29b及びゲート絶縁膜28b及び25bに覆われていない領域の第2の島状半導体膜24bに高濃度不純物領域(ソース/ドレイン領域)24ba、24bbが形成される。このとき、高電圧駆動用TFTの形成領域の島状半導体膜にも高濃度不純物領域(ソース/ドレイン領域)が形成される。

【0094】次に、ゲート電極29a、29bを透過せず、ゲート絶縁膜28b及び25bを透過するような加速電圧の条件、例えば加速電圧が70keVで、低ドーズ量、例えば $2 \times 10^{13} \text{ cm}^{-2}$ の条件でリンをイオン注入して、画素TFTの形成領域のゲート電極29bエッジとゲート絶縁膜28b及び25bエッジとの間に、低濃度不純物領域(低濃度ソース/ドレイン領域)24bc、24bdを形成する。このとき、高電圧駆動用TFTの形成領域の島状半導体膜にもドレイン側に低濃度不純物領域であるLDD領域が形成される。なお、低電圧駆動用TFTの形成領域では、注入イオンは加速電圧が高いため、第1の島状半導体膜24aを透過し、このため、第1の島状半導体膜24a中には不純物が導入されない。

【0095】次に、図9(b)に示すように、プラズマCVD法により、ガラス基板21の上側全面にシリコン酸化膜31を90nmの厚さで形成し、さらにその上にシリコン窒化膜32を350nmの厚さで形成する。

【0096】次に、図10(a)に示すように、低電圧駆動用TFTの形成領域において、高濃度不純物領域24aa、24ab上のシリコン窒化膜32とシリコン酸

化膜31を貫通するコンタクトホール33a、33bを形成するとともに、画素TFTの形成領域において、高濃度不純物領域24ba、24bb上のシリコン窒化膜32とシリコン酸化膜31を貫通するコンタクトホール33c、33dを形成する。

【0097】次に、図10(b)に示すように、スパッタ法により、ガラス基板21の上側全面に、Ti膜を100nm、Al膜を200nm、Ti膜を50nmの厚さに順次堆積し、これらの金属膜でコンタクトホール33a、33b、33c、33dを埋め込むとともにシリコン窒化膜32上に金属の積層膜を形成する。その後、フォトリソグラフィによりレジストマスク(不図示)を形成し、続いて、このレジストマスクを基に金属膜をドライエッティングする。このようにして、低電圧駆動用TFTの高濃度不純物領域24aa、24abと接触したソース/ドレイン電極34a、34bを形成し、同時に、画素TFTの高濃度不純物領域24ba、24bbと接触したソース/ドレイン電極34c、34dを形成する。

【0098】なお、液晶表示装置の表示部104では、ソース/ドレイン電極34a乃至34dの形成と同時に、データバスライン108を形成する。また、制御回路101、データドライバ102及びゲートドライバ103の形成領域では、ソース/ドレイン電極34a乃至34dの形成と同時に、所定の配線パターンを形成する。続いて、感光性樹脂を塗布して厚さが3.0μmの樹脂膜35を形成する。

【0099】以上のようにして、薄膜トランジスタ装置が完成する。液晶表示装置を作成するため、引き続き以下の工程を行う。

【0100】次に、樹脂膜35の所定領域に、配線パターンを介してソース/ドレイン電極34dに繋がるビアホールを形成する。その後、スパッタ法により、ガラス基板21の上側全面に厚さが70nmのITO(indium-tin oxide: インジウム酸化スズ)膜を成膜した後、通常のフォトリソグラフィ工程によりITO膜をパターニングして、画素TFTのソース側不純物領域に電気的に接続した画素電極36を形成する。その後、ガラス基板21の上側全面に、液晶分子の初期状態(電圧無印加時)の配向方向を決める配向膜(図示せず)を形成する。

【0101】このようにして、液晶表示装置のTFT基板が完成する。

【0102】液晶表示装置の対向基板は、公知の方法で作成する。すなわち、ガラス基板上に、例えばCr(クロム)により、画素間の領域を遮光するタメのブラックマトリクスを形成する。また、ガラス基板上に赤色、緑色及び青色のカラーフィルタを形成し、各画素毎に赤色、緑色及び青色の何れか1色のカラーフィルタを配置する。その後、ガラス基板の上側全面にITO膜からな

る透明電極を形成し、透明電極の上に配向膜を形成する。

【0103】このようにして製造されたTFT基板と対向基板とを貼り合わせ、両者の間に液晶を封入して液晶パネルとする。この液晶パネルの両面に偏光板を配置し、裏面側にバックライトを配置すると、液晶表示装置が完成する。

【0104】以上のように、本発明の第1の実施の形態によれば、図5(b)に示すように、低電圧駆動用TFTの形成領域において、ゲート絶縁膜28を形成する前に、第1の島状半導体膜24aの周縁部を高電圧駆動用TFTの厚いゲート絶縁膜の一部となる厚いシリコン酸化膜25で覆っている。従って、厚いシリコン酸化膜25上にゲート絶縁膜となるシリコン酸化膜28とゲート電極となる金属膜29とを積層し、図8(b)に示すように、第1の島状半導体膜24aと交差する帯状のレジストマスク30aに基づき、ゲート電極29a及びゲート絶縁膜28aをエッティングにより形成すると、図11(b)に示すように、ゲート電極29a下の第1の島状半導体膜24aの周縁部はシリコン酸化膜28aのほかに厚いシリコン酸化膜25bで覆われる。このため、第1の島状半導体膜24aの周縁部でゲート電圧印加時の電界集中を緩和して寄生TFTが動作するのを防止することができる。

【0105】また、図4(a)、(b)に示すように、低電圧駆動用TFTの形成領域において、第1の島状半導体膜24aの上方のネガティブフォトレジスト膜26の未露光領域に対して、第1の島状半導体膜24aをマスクとしてガラス基板21の裏面から露光光を照射しているので、第1の島状半導体膜24aの周縁から光が回折する範囲で自己整合的にその未露光領域が露光される。このため、極めて精度よく第1の島状半導体膜24aの周縁部をシリコン酸化膜25で覆うことができるので、第1の島状半導体膜24aのチャネル幅方向の寸法マージンを最小にすることができる、従ってTFTの微細化が可能である。

【0106】(第2の実施の形態) 次に、本発明の第2の実施の形態について図面を参照して説明する。

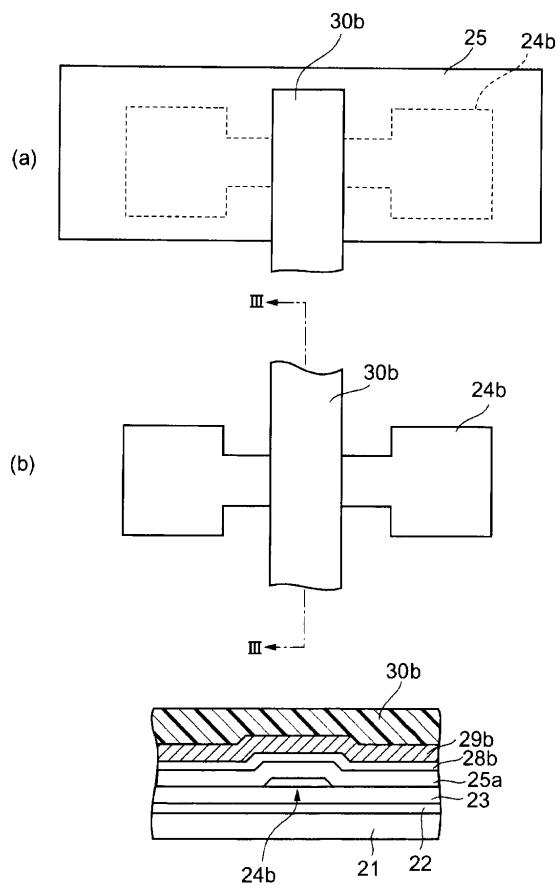

【0107】(液晶表示装置に用いられた薄膜トランジスタ装置の構造) 以下に、第2の実施の形態である、液晶表示装置に用いられた薄膜トランジスタ装置の構造について、図16(b)を参照して説明する。ここで、高電圧駆動用TFTは画素TFTとほぼ同じ構造を有するので、それらを代表して画素TFTについて説明し、高電圧駆動用TFTはその説明を省略する。また、p型TFTはn型TFTとほぼ同じ構造を有するので、その説明を省略する。

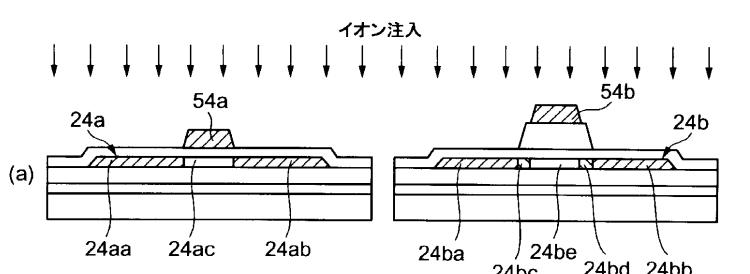

【0108】図16(b)の左の図はnチャネル型の低電圧駆動用TFTの構造を示す断面図であり、同じく右の図はnチャネル型の画素TFTの構造を示す断面図で

ある。

【0109】まず、低電圧駆動用TFTにおいては、図16(b)の左の図に示すように、ガラス基板21上に厚さが50nmのシリコン窒化膜22aと厚さが200nmのシリコン酸化膜22bとの積層構造からなる下地絶縁膜22が形成されている。この下地絶縁膜22の上にTFTの動作層となる厚さが40nmのポリシリコン膜からなる第1の島状半導体膜24aが形成されている。この第1の島状半導体膜24aには、TFTのソース/ドレインである一対の高濃度不純物領域(オーミックコンタクト領域)24aa、24abがチャネル領域24acを挟んで形成されている。

【0110】下地絶縁膜22及び第1の島状半導体膜24aの上には、厚さが約30nmのシリコン酸化膜からなる第1のゲート絶縁膜51aが形成されている。このシリコン酸化膜51aはアモルファスシリコン膜を酸化して形成されている。

【0111】また、この第1のゲート絶縁膜51aの上には、第1のゲート電極54aが形成されている。高濃度不純物領域24aa、24abのチャネル領域側のエッジが、いずれもゲート電極54aのエッジのほぼ真下に位置している。

【0112】第1のゲート絶縁膜51a及び第1のゲート電極54aの上には、厚さが370nmのシリコン窒化膜(第1の層間絶縁膜)55が形成されている。シリコン窒化膜55の上には一対のソース/ドレイン電極57a、57bが形成されている。これらのソース/ドレイン電極57a、57bは、シリコン窒化膜55の上面から高濃度不純物領域24aa、24abに通じるコンタクトホール56a、56b内に埋め込まれた金属により、高濃度不純物領域24aa、24abに電気的に接続されている。

【0113】以上のように、低電圧駆動用TFTは、第1のゲート絶縁膜51aが厚さ約30nmのシリコン酸化膜のみで構成されており、さらにLDD領域が設けられていないので、低電圧での高速動作が可能である。また、高濃度不純物領域24aa、24abが第1のゲート電極54aに対し、自己整合的に形成できるので、素子の微細化が容易である。なお、この低電圧駆動用TFTにはLDD領域が設けられていないが、低電圧駆動するのでホットエレクトロンが少なく、ホットエレクトロンに起因するオン特性の劣化とオフ電流の増大が回避される。

【0114】次に、画素TFTにおいては、図16(b)の右側の図に示すように、ガラス基板21の上には上記したと同じ積層構造の下地絶縁膜22が形成されている。この下地絶縁膜22上には、TFTの動作層となる第2の島状半導体膜24bが形成されている。第2の島状半導体膜24bにTFTのソース/ドレインのオーミックコンタクト領域である一対のn型の高濃度不純物

物領域24b a、24b bがチャネル領域24b eを挟んで形成されている。また、これらの高濃度不純物領域24b a、24b bのチャネル領域24b e側の端部には、それぞれn型の低濃度不純物領域(LDD領域)24b c、24b dが形成されている。

【0115】下地絶縁膜22及び第2の島状半導体膜24bの上には、厚さが約10nmのシリコン酸化膜51aと厚さが100nmのシリコン酸化膜52aが積層して形成されている。そして、シリコン酸化膜52aの上には第2のゲート電極54bが形成されている。第2のゲート電極54b下のシリコン酸化膜51aとシリコン酸化膜52aとで構成された絶縁膜の積層構造が第2のゲート絶縁膜となる。

【0116】この画素TFTでは、上から見たときに、第2のゲート電極54bの両側のエッジのほぼ真下に、LDD領域24b c、24b dのチャネル領域側エッジが配置されている。画素TFTでは、表示信号として正及び負の信号が与えられるので、ソース側及びドレイン側の両方にLDD領域24b c、24b dを設けないと、ホットエレクトロンによるトランジスタ特性の劣化が発生する。

【0117】第2のゲート電極54b及びシリコン酸化膜51aの上には厚さ370nmのシリコン窒化膜55が形成されている。シリコン窒化膜55の上には一对のソース/ドレイン電極57c、57dが形成されている。これらのソース/ドレイン電極57c、57dはコンタクトホール56c、56dを通して高濃度不純物領域24b a、24b bと接触している。

【0118】以上のように、上記画素TFTによれば、第2のゲート絶縁膜が110nmと厚いシリコン酸化膜(シリコン酸化膜51a+シリコン酸化膜52a)で形成されているので、耐圧が高く、高電圧で駆動させることができる。

【0119】なお、説明を省略した高電圧駆動用TFTにおいて、画素TFTと異なるところは高電圧のかかるドレイン側にのみLDD領域を有している点である。また、説明を省略した周辺回路の高電圧駆動用p型TFTではLDD領域は設けられていない。これは、p型TFTの場合は、キャリアが正孔であるので、ホットキャリアの発生がほとんどなく、LDD領域を設けなくてもトランジスタ特性に支障がないからである。

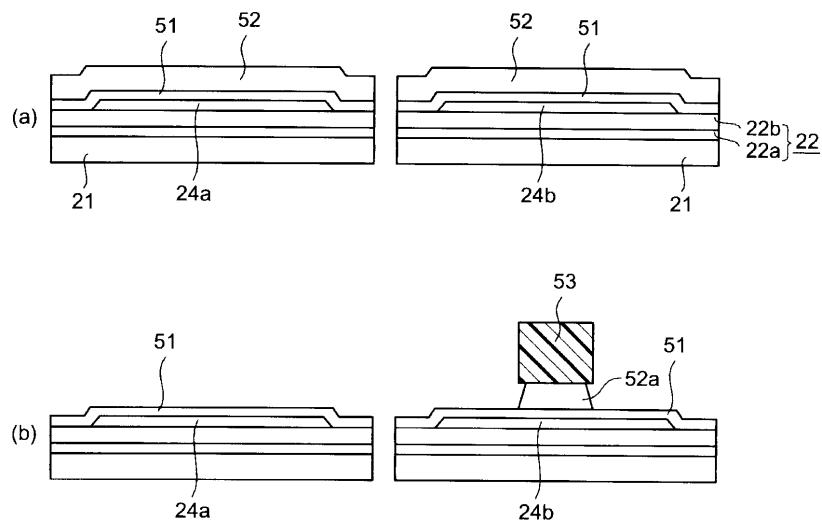

【0120】(液晶表示装置に用いられた薄膜トランジスタの製造方法)次に、本実施の形態の液晶表示装置に用いられた薄膜トランジスタ装置の製造方法について、図13乃至図16を参照して説明する。なお、これらの図において、左の図が低電圧駆動用TFTの形成領域における断面図であり、右の図は画素TFTの形成領域における断面図である。

【0121】まず、図13(a)に示すように、プラズマCVD法により、ガラス基板21の上に、下地絶縁膜50

としてシリコン窒化膜22aを約50nmの厚さで、シリコン酸化膜22bを200nmの厚さでこの順に形成する。続いて、シリコン酸化膜22bの上にアモルファスシリコン膜を約40nmの厚さで形成する。

【0122】次に、アモルファスシリコン膜中の水素を低減するために、450℃の温度でアニールする。そして、アモルファスシリコン膜にエキシマレーザを照射して、アモルファスシリコン膜をポリシリコン膜に変化させる。

【0123】次に、ポリシリコン膜の上にフォトレジストを塗布し、露光及び現像工程を経て、所定のレジストマスク(図示せず)を形成する。そして、このレジストマスクに基づき、ポリシリコン膜をドライエッティングし、所定の領域のみにポリシリコン膜からなる第1の島状半導体膜24a及び第2の島状半導体膜24bを残す。その後、レジストマスクを除去する。

【0124】次に、プラズマCVD法により、ガラス基板21の上側全面にアモルファスシリコン膜51を10nmの厚さに成膜し、さらにシリコン酸化膜(絶縁膜)52を100nmの厚さに成膜する。

【0125】続いて、塗布法によりシリコン酸化膜52の上にフォトレジスト膜を形成した後、露光及び現像工程を経て、図13(b)に示すように、画素TFTの形成領域にレジストマスク53を形成する。

【0126】次いで、レジストマスク53に基づいてシリコン酸化膜52を希フッ酸によりウエットエッティングする。このとき、希フッ酸に対してエッティング耐性のある、シリコン酸化膜52下のアモルファスシリコン膜51をエッティングのストップとする。これにより、レジストマスク53の下にシリコン酸化膜のパターン(絶縁膜のパターン)52aを形成する。その後、レジストマスク53を除去する。

【0127】次に、図14(a)に示すように、高圧酸化法によりシリコン酸化膜のパターン52aの下部を含む全体のアモルファスシリコン膜51を酸化して、シリコン酸化膜(半導体膜を酸化してなる絶縁膜)51aを形成する。高圧酸化は、例えば圧力2MPaに調整された水蒸気雰囲気中、温度550℃、酸化時間1時間の条件で行う。なお、高圧酸化法の代わりによく知られた熱酸化法、或いはプラズマ酸化法などの方法を用いることが可能である。

【0128】これにより、第1の島状半導体膜24a上にシリコン酸化膜51aからなる第1のゲート絶縁膜が形成され、第2の島状半導体膜24b上にシリコン酸化膜51aとシリコン酸化膜のパターン52aとからなる第2のゲート絶縁膜が形成される。

【0129】次に、図14(b)に示すように、スパッタ法により、Al-Nd膜を厚さ300nmで成膜した後、図示しないレジストマスクに基づいてAl-Nd膜をエッティングし、低電圧駆動用TFTの形成領域におい

て第1のゲート絶縁膜51a上に第1のゲート電極54aを形成し、画素TFTの形成領域において、第2のゲート絶縁膜51a及び52a上に第2のゲート電極54bを形成する。このとき、第2のゲート電極54bは第2のゲート絶縁膜52aの上面の面積よりも小さい面積で、かつ第2のゲート絶縁膜52aの上面の周縁よりも内側に形成する。その後、レジストマスクを除去する。

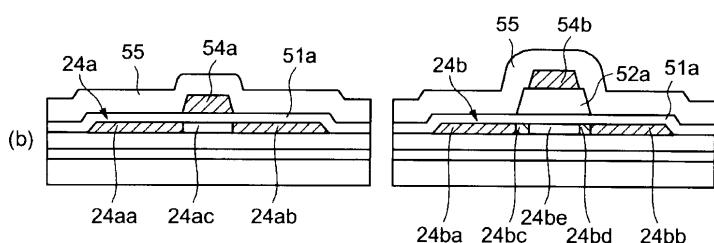

【0130】次に、図15(a)に示すように、第1のゲート電極54aをマスクとして第1の島状半導体膜24a内に高濃度のリンをイオン注入する。同時に、第2のゲート電極54b及び第2のゲート絶縁膜51a及び52aをマスクとして第2の島状半導体膜24b内に高濃度のリンをイオン注入する。このとき、イオン注入の条件を、例えば、加速電圧が25keV、注入量が $7 \times 10^{14} \text{ cm}^{-2}$ とする。これにより、第1のゲート電極54aの両側の第1の島状半導体膜24aにn型の高濃度不純物領域24a a、24a bが形成され、第2のゲート絶縁膜51a及び52aの両側の第2の島状半導体膜24b内にn型の高濃度不純物領域24b a、24b bが形成される。

【0131】続いて、第1及び第2のゲート電極を透過せず、かつ第1及び第2の島状半導体膜24a、24bを透過し、第2のゲート絶縁膜51a及び52aを透過する条件で第2の島状半導体膜24b内に低濃度のリンをイオン注入する。イオン注入の条件を、例えば、加速電圧が70keVで、低いドーズ量 $2 \times 10^{13} \text{ cm}^{-2}$ とする。これにより、第2のゲート電極54bのエッジと高濃度不純物領域24b a、24b bのエッジの間の第2の島状半導体膜24b内にn型の低濃度不純物領域(LDD領域)24b c、24b dが形成される。

【0132】次に、図15(b)に示すように、プラズマCVD法により、ガラス基板21表面の全面にシリコン窒化膜55を厚さ370nmで成膜する。

【0133】次に、図16(a)に示すように、図示しないレジストマスクに基づき、シリコン窒化膜(第1の層間絶縁膜)55をSF<sub>6</sub>ガスによりドライエッティングし、第1の島状半導体膜24aの高濃度不純物領域24a a、24a b上のシリコン窒化膜55を貫通するコンタクトホール56a、56bを形成する。同時に、第2の島状半導体膜24bの高濃度不純物領域24b a、24b b上のシリコン窒化膜55を貫通するコンタクトホール56c、56dを形成する。その後、レジストマスクを除去する。

【0134】次いで、図16(b)に示すように、スパッタ法により、ガラス基板21の上側全面に、Ti膜を50nm、Al膜を100nm、Ti膜を50nmの厚さに順次堆積し、これらの金属膜でコンタクトホール56a、56b、56c、56dを埋め込むとともにシリコン窒化膜55上に金属の積層膜を形成する。その後、フォトリソグラフィによりレジストマスク(不図示)を

形成し、続いて、このレジストマスクに基づいて、金属膜をドライエッティングする。これにより、低電圧駆動用TFTの高濃度不純物領域(ソース/ドレイン領域)24a a、24a bと接触したソース/ドレイン電極57a、57bを形成する。同時に、画素TFTの高濃度不純物領域(ソース/ドレイン領域)24b a、24b bと接触したソース/ドレイン電極57c、57dを形成する。

【0135】なお、ソース/ドレイン電極57a乃至57dの形成と同時に、表示部104ではデータバスライン108を形成し、制御回路101、データドライバ102及びゲートドライバ103の形成領域では、所定の配線パターンを形成する。

【0136】次に、感光性樹脂を塗布して厚さが3.0μmの樹脂膜(第2の層間絶縁膜)58を形成する。以上のようにして、薄膜トランジスタ装置が完成する。引き続き、液晶表示装置を作成するため、以下の工程を行う。

【0137】次に、この樹脂膜58のソース/ドレイン電極57d上にビアホール59を形成する。その後、スパッタ法により、ガラス基板21の上側全面に厚さが70nmのITO膜を成膜した後、通常のフォトリソグラフィ工程によりITO膜をパターニングして、画素TFTのソース側不純物領域に接触する画素電極60を形成する。その後、ガラス基板21の上側全面に、液晶分子の初期状態(電圧無印加時)の配向方向を決める配向膜(図示せず)を形成する。

【0138】このようにして、液晶表示装置のTFT基板が完成する。

【0139】液晶表示装置の対向基板は、公知の方法で作成する。すなわち、ガラス基板上に、例えばCr(クロム)により、画素間の領域を遮光するためのブラックマトリクスを形成する。また、ガラス基板上に赤色、緑色及び青色のカラーフィルタを形成し、各画素毎に赤色、緑色及び青色の何れか1色のカラーフィルタを配置する。その後、ガラス基板の上側全面にITO膜からなる透明電極を形成し、透明電極の上に配向膜を形成する。

【0140】このようにして製造されたTFT基板と対向基板とを貼り合わせ、両者の間に液晶を封入して液晶パネルとする。この液晶パネルの両面に偏光板を配置し、裏面側にバックライトを配置すると、液晶表示装置が完成する。

【0141】以上のように、第2の実施の形態によれば、図13(b)に示すように、シリコン酸化膜52をエッティングして第2のゲート絶縁膜の一部となる絶縁膜を形成するときに、下地のアモルファシリコン膜51により第1の島状半導体膜24aが保護されるため、第1の島状半導体膜24aのチャネル領域がシリコン酸化膜52のエッティングガスのプラズマに曝されない。この

ため、低電圧駆動用TFTで代表される薄膜部のTFTの特性が劣化するのを防止して、画素TFTで代表される厚膜部のTFT及び薄膜部のTFTともに良好な特性を確保することができる。

【0142】また、第1及び第2の島状半導体膜24a、24bの下地のシリコン酸化膜22bもアモルファスシリコン膜51により保護されているため、第1及び第2の島状半導体膜24a、24bの端部でシリコン酸化膜22bがエッティングされることによる「えぐれ」も生じない。

【0143】さらに、シリコン酸化膜52をエッティングして第2のゲート絶縁膜の一部となる絶縁膜を形成するときに、シリコン酸化膜52のエッチャントに対してアモルファスシリコン膜51はエッティング耐性を有するため膜減りしない。この実施の形態では、アモルファスシリコン膜51を酸化して第1のゲート絶縁膜51aを形成しているため、第1のゲート絶縁膜51aの膜厚を精度よく、かつ容易に制御することが可能である。

【0144】なお、上記の実施の形態においては、第1及び第2の島状半導体膜24a、24bの上に直接アモルファスシリコン膜51を形成しているが、第1及び第2の島状半導体膜24a、24bを被覆するシリコン酸化膜を形成し、その上にアモルファスシリコン膜51とシリコン酸化膜52とを形成してもよい。これにより、上記の効果のほかに、アモルファスシリコン膜51を酸化して第1のゲート絶縁膜を形成するときに、第1のゲート絶縁膜の膜厚の制御がさらに容易になる。この場合、第1のゲート絶縁膜の膜厚は第1の島状半導体膜24aを被覆するシリコン酸化膜と、アモルファスシリコン膜を酸化してなるシリコン酸化膜51aとで構成され、第2のゲート絶縁膜は第2の島状半導体膜24bを被覆するシリコン酸化膜と、アモルファスシリコン膜を酸化してなるシリコン酸化膜51aと、シリコン酸化膜52aとで構成されることになる。

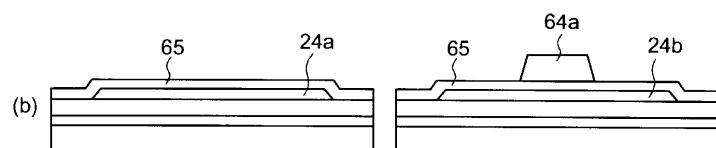

【0145】(薄膜トランジスタ装置の他の製造方法)図17乃至図18はこの発明の第2の実施の形態である薄膜トランジスタ装置の他の製造方法について説明する断面図である。

【0146】図17(a)に示すように、第1の実施の形態と同様に、ガラス基板21上に膜厚50nmのシリコン窒化膜22aと膜厚200nmのシリコン酸化膜22bと膜厚40nmのアモルファスシリコン膜を形成した後、アモルファスシリコン膜にエキシマレーザを照射してアモルファスシリコン膜をポリシリコン膜(第1の半導体膜)24に変換する。

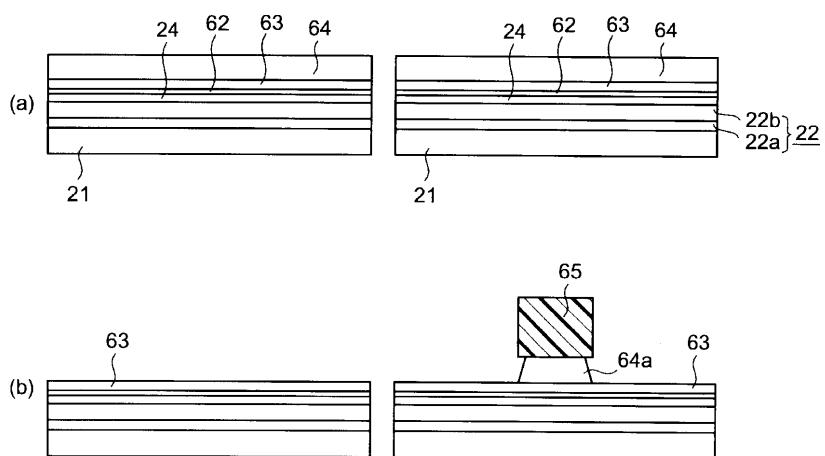

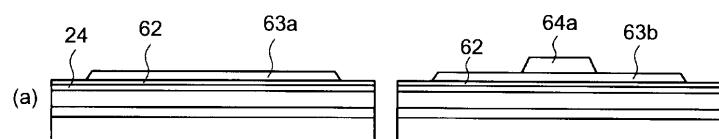

【0147】次いで、プラズマCVD法により、膜厚10nmの第1のシリコン酸化膜(第1の絶縁膜)62と、膜厚10nmのアモルファスシリコン膜(第2の半導体膜)63と、膜厚100nmの第2のシリコン酸化膜(第2の絶縁膜)64とを成膜する。

【0148】次に、図17(b)に示すように、画素TFTの形成領域にレジストマスク65を形成した後、レジストマスク65に基づき、希フッ酸によりシリコン酸化膜64をエッティングし、第2のシリコン酸化膜のパターン(第2の絶縁膜のパターン)64aを形成する。その後レジストマスク65を除去する。

【0149】次いで、図18(a)に示すように、図示しない新たなレジストマスクを形成した後、新たなレジストマスクに基づき、フッ素を含むエッティングガスを用いてアモルファスシリコン膜63をドライエッティングして、第1の島状のアモルファスシリコン膜(第2の絶縁膜のパターンを含まない島状の第2の半導体膜)63aと第2の島状のアモルファスシリコン膜(第2の絶縁膜のパターンを含む島状の第2の半導体膜)63bを形成する。その後、レジストマスクを除去する。

【0150】次に、例えば、高圧酸化法により、第1の島状のアモルファスシリコン膜63a、及び第2のシリコン酸化膜のパターン64aの下部及びその他の部分の第2の島状のアモルファスシリコン膜63bを酸化する。同時に、第1の島状のアモルファスシリコン膜63aで覆われていなかった領域のポリシリコン膜24と、第2の島状のアモルファスシリコン膜63bで覆われていなかった領域のポリシリコン膜24とを第1のシリコン酸化膜62を介して酸化する。これにより、図18(b)に示すように、第1の島状のアモルファスシリコン膜63aで覆われていた領域にポリシリコン膜からなる第1の島状半導体膜24aを形成し、第2の島状のアモルファスシリコン膜63bで覆われていた領域にポリシリコン膜からなる第2の島状半導体膜24bを形成する。従って、第1の島状半導体膜24a上に、第1のシリコン酸化膜62及び第1の島状のアモルファスシリコン膜63aを酸化してなる絶縁膜で構成される第1のゲート絶縁膜65を形成する。同時に、第2の島状半導体膜24b上に、第1のシリコン酸化膜62及び第2の島状のアモルファスシリコン膜63bを酸化してなる絶縁膜で構成される絶縁膜65と、第2のシリコン酸化膜のパターン64aとからなる第2のゲート絶縁膜を形成する。

【0151】以降、図14(b)乃至図15(b)の工程と同様な工程を経て、薄膜トランジスタ装置を作成し、さらに、第1及び別の第2の実施の形態で説明した液晶表示装置の製造方法における通常の工程を経て液晶表示装置を作成する。

【0152】以上のように、第2の実施の形態である他の薄膜トランジスタ装置の製造方法によれば、図17(b)に示すように、シリコン酸化膜64をエッティングして第2のゲート絶縁膜の一部となる絶縁膜64aを形成するときに、下地のアモルファスシリコン膜63により第1の島状半導体膜24aが保護されるため、第1の島状半導体膜24aのチャネル領域がシリコン酸化膜6

4のエッティングガスのプラズマに曝されない。このため、薄膜部のTFTの特性が劣化するのを防止して、厚膜部のTFT及び薄膜部のTFTとともに良好な特性を確保することができる。

【0153】また、図18(b)に示すように、第2のゲート絶縁膜のうち厚い絶縁膜となる、アモルファスシリコン膜63上のシリコン酸化膜64をエッティングした後に、アモルファスシリコン膜63下のポリシリコン膜24を選択的に酸化して第1及び第2の島状半導体膜24a、24bを形成している。このように、下地のシリコン酸化膜22bはエッティングガス等に曝されない。このため、第1及び第2の島状半導体膜24a、24bの端部で下地のシリコン酸化膜22bがエッティングされることによる「えぐれ」を生じない。

【0154】さらに、シリコン酸化膜64をエッティングして第2のゲート絶縁膜の一部となる絶縁膜を形成するときに、シリコン酸化膜64のエッチャントに対してアモルファスシリコン膜63はエッティング耐性を有するため膜減りしない。この実施の形態では、アモルファスシリコン膜63を酸化してなる絶縁膜63aと第1のシリコン酸化膜62とにより第1のゲート絶縁膜を形成しているため、第1のゲート絶縁膜の膜厚を精度よく、かつ容易に制御することが可能である。

【0155】(第3の実施の形態)次に、本発明の第3の実施の形態の薄膜トランジスタ装置の構造について図面を参照して説明する。

【0156】第3の実施の形態の薄膜トランジスタ装置は、n型TFT及びp型TFTのうち少なくとも何れか一の薄いゲート絶縁膜を有するTFT(以下、薄膜部のTFTと称する。)と、n型TFT及びp型TFTのうち少なくとも何れか一の厚いゲート絶縁膜を有するTFT(厚膜部のTFTと称する。)とを同一基板上に搭載している。以下に、薄膜部のn型TFT及び厚膜部のn型TFTの構造を説明する。

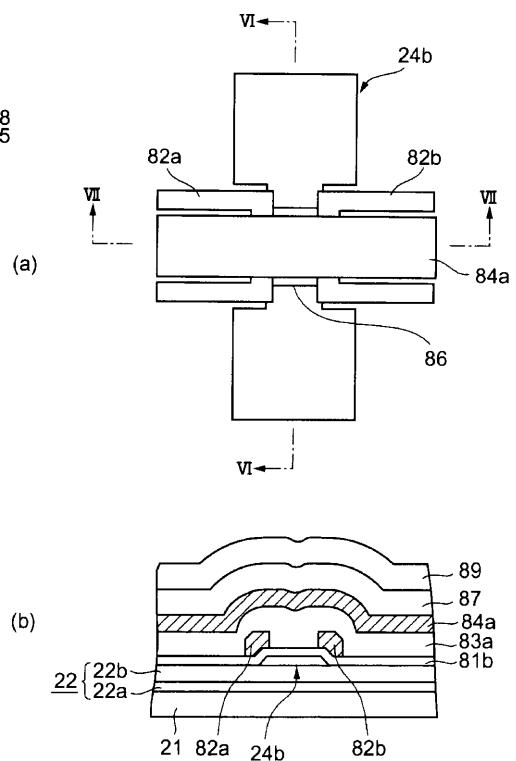

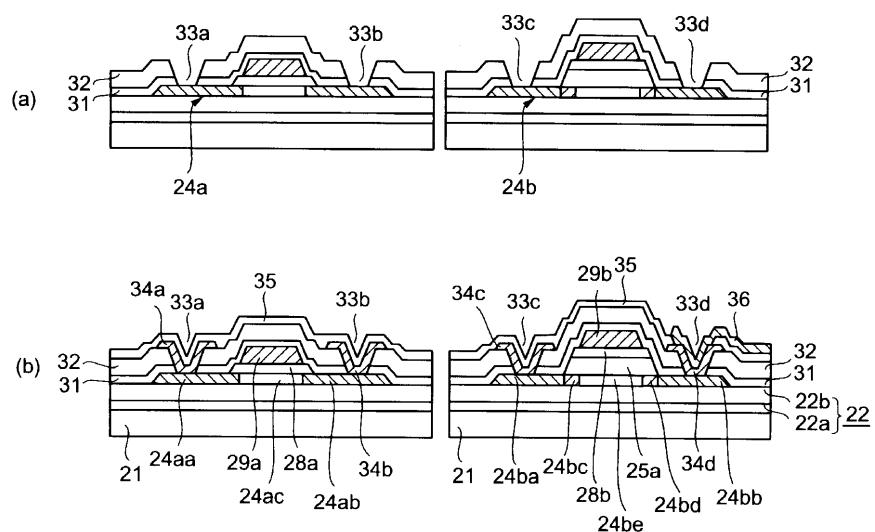

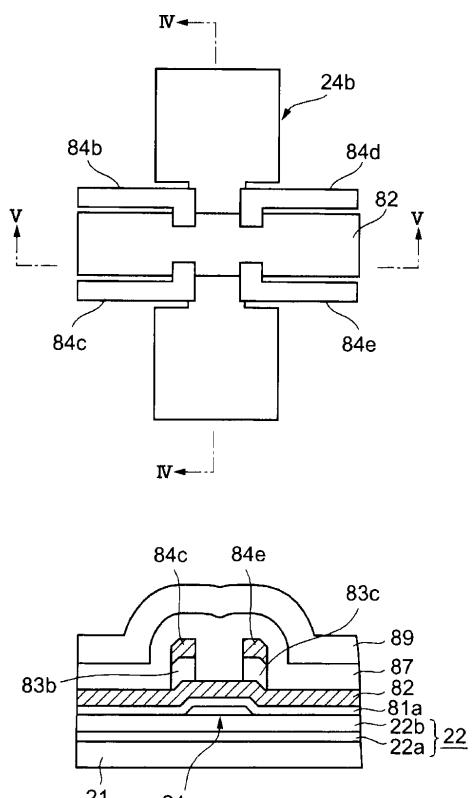

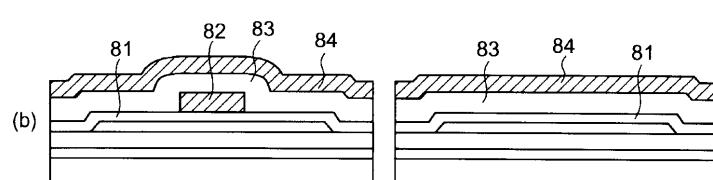

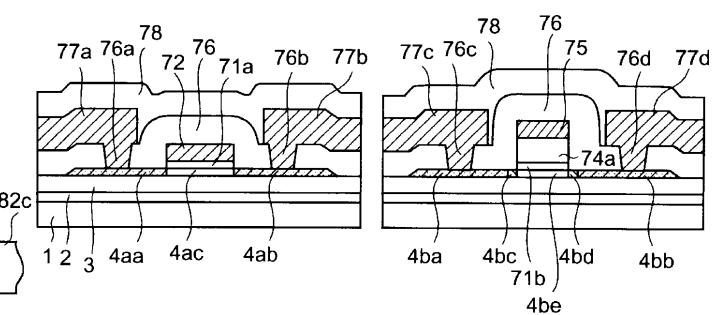

【0157】図23(a)は薄膜部のTFTの上から見た平面図であり、図21(b)の左の図は図23(a)のIV-IV線に沿う断面図である。また、図23(b)は、図23(a)のV-V線に沿う断面図である。

【0158】薄膜部のTFT(第1の薄膜トランジスタ)は、図23(a)、図21(b)の左の図に示すように、チャネル領域24a cを挟んで一対のn型のソース/ドレイン領域24a a、24a bが形成された膜厚約50nmのポリシリコン膜からなる第1の島状半導体膜24aと、第1の島状半導体膜24aのチャネル領域24a c上に形成された膜厚30nmの第1のシリコン酸化膜(第1の絶縁膜)からなる第1のゲート絶縁膜81aと、第1のゲート絶縁膜81a上に形成された膜厚300nmの第1のA1-Nd膜(第1の導電体膜)からなる第1のゲート電極82とを有する。

【0159】また、第1の島状半導体膜24aと第1の

ゲート電極82とを覆う膜厚400nmのシリコン窒化膜からなる第1の層間絶縁膜87と、第1の層間絶縁膜87に形成されたコンタクトホール87a、87bと、コンタクトホール87a、87bを通してソース/ドレイン領域24a a、24a bとそれぞれ接続された全膜厚200nmのTi膜/A1膜/Ti膜の3層の金属膜からなるソース/ドレイン電極88a、88bと、ソース/ドレイン電極88a、88bを覆う膜厚400nmのシリコン窒化膜からなる第2の層間絶縁膜89とを有する。

【0160】さらに、薄膜ゲートTFTは、図23(a)、(b)に示すように、第1の島状半導体膜24aの両側部のエッジの上方で、かつ第1のゲート電極82上に、第2のシリコン酸化膜(第2の絶縁膜)83bを介して膜厚300nmの第2のA1-Nd膜(第2の導電体膜)からなる電界緩和電極84c乃至84fを有している。

【0161】次に、厚膜部のTFTについて説明する。図24(a)は厚膜部のTFTの上から見た平面図であり、図21(b)の右の図は図24(a)のVI-VI線に沿う断面図であり、図24(b)は、図24(a)のVI-I-VI線に沿う断面図である。

【0162】厚膜部のTFT(第2の薄膜トランジスタ)は、図24(a)、図21(b)の右の図に示すように、チャネル領域24b eを挟んで一対のn型のソース/ドレイン領域24b a、24b bが形成された膜厚約50nmのポリシリコン膜からなる第2の島状半導体膜24bと、第2の島状半導体膜24bのチャネル領域24b e上に形成された膜厚30nmの第1のシリコン酸化膜81a及び膜厚70nmの第2のシリコン酸化膜83bからなる第2のゲート絶縁膜と、第2のゲート絶縁膜上に形成された膜厚300nmの第2のA1-Nd膜(第2の導電体膜)からなる第2のゲート電極84aとを有する。

【0163】さらに、厚膜部のTFT(第2の薄膜トランジスタ)は、第2の島状半導体膜24bと第2のゲート電極84aとを覆うシリコン窒化膜(第1の層間絶縁膜)87と、シリコン窒化膜87に形成されたコンタクトホール87c、87dを通してソース/ドレイン電極88c、88dと、ソース/ドレイン電極88c、88dを覆うシリコン酸化膜(第2の層間絶縁膜)89とを有する。

【0164】また、厚膜部のTFTは、図24(a)、(b)に示すように、第2のゲート電極84a下で、かつ第2の島状半導体膜24bの側部のエッジの上に第1のシリコン酸化膜81bを介して第1のA1-Nd膜からなる電界緩和電極82b、82cを有している。

【0165】以上のように、本発明の第3の実施の形態の薄膜トランジスタ装置によれば、薄膜部のTFTにお

いては、第1の島状半導体膜24aの両側部のエッジの上方で、かつ第1のゲート電極82上に、第2のシリコン酸化膜83bを介して電界緩和電極84c乃至84fを有している。従って、この部分の寄生容量は、第1の島状半導体膜24aと第1のシリコン酸化膜81aと第1のゲート電極82とで形成される容量に対して、第1のゲート電極82と電界緩和電極84c乃至84fとで形成される静電容量分だけ大きくなる。このため、TFTのゲートを交流で駆動する場合、第1の島状半導体膜24aの両側部のエッジ部分にかかるゲート電位の変化は遅くなる。従って、第1の島状半導体膜24aの両側部のエッジ部の寄生トランジスタが動作するのを抑制することができる。

【0166】また、厚膜部のTFTにおいては、第2のゲート電極84a下で、かつ第2の島状半導体膜24bの両側部のエッジの上に第1のシリコン酸化膜81bを介して電界緩和電極82b、82cを有している。従って、電界緩和電極82b、82cの電位を第2の島状半導体膜24bの両側部のエッジ部のチャネルが導通しない電位に設定しておくことで、第2の島状半導体膜24bの両側部のエッジ部のチャネルが導通するのを抑制し、また、第2のゲート電極84aからの電界の影響をシールドして、寄生トランジスタがオンするのを抑制することができる。

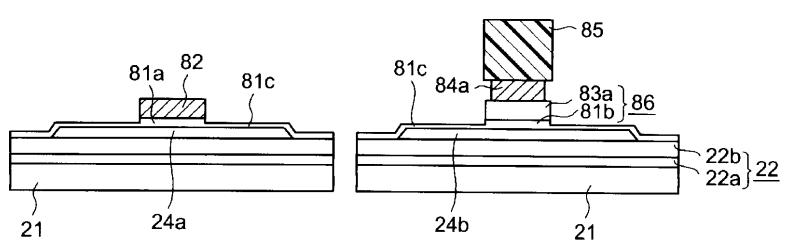

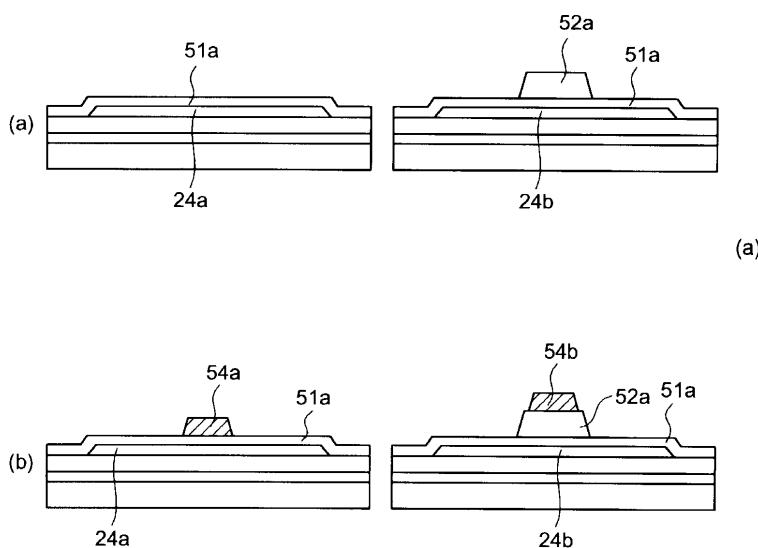

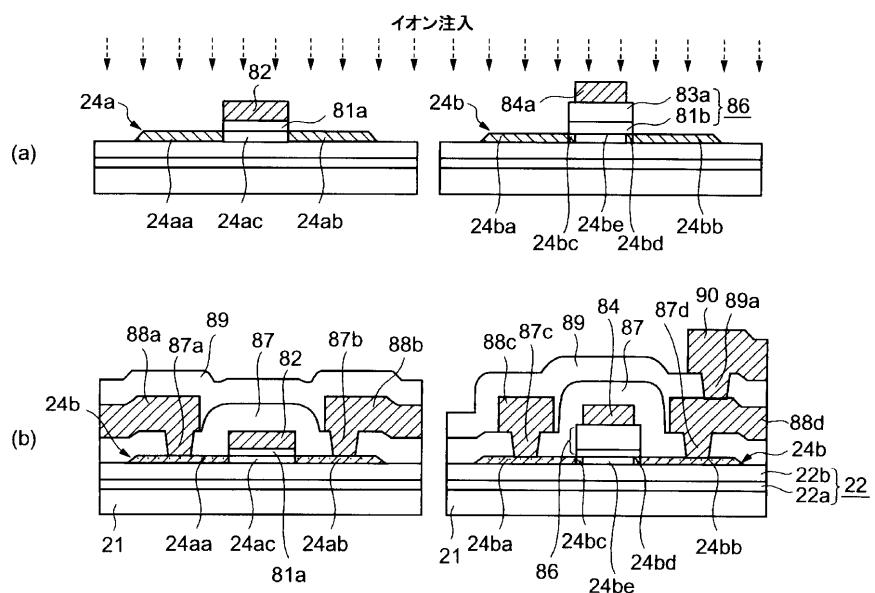

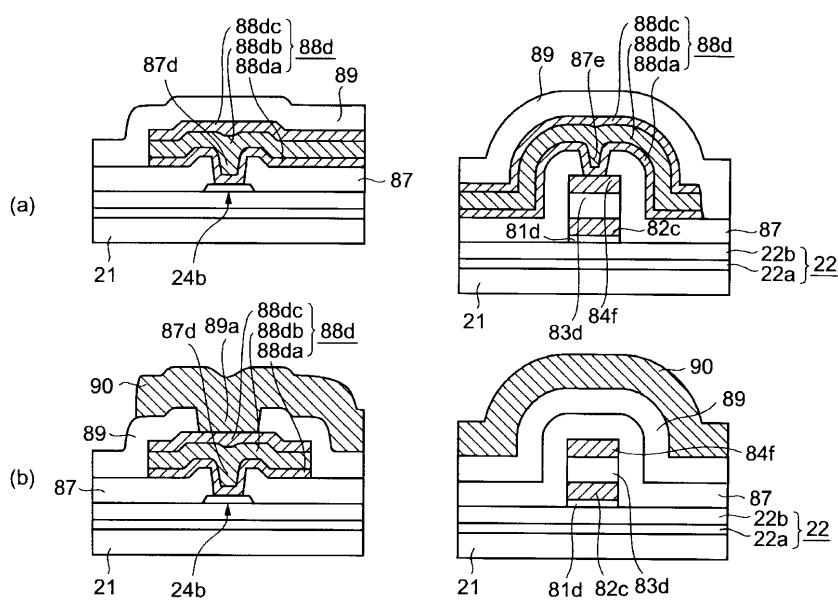

【0167】次に、第3の実施の形態の薄膜トランジスタ装置の製造方法について図19乃至図21を参照して説明する。

【0168】図19(a)に示すように、ガラス基板21上に膜厚50nmのシリコン窒化膜22aと膜厚250nmのシリコン酸化膜22bとを順次積層して基板を作成する。なお、場合により、シリコン窒化膜22aを省略してもよい。

【0169】その後、基板上に膜厚50nmのアモルファシリコン膜を形成した後、温度400で加熱して水素出しを行う。次いで、エキシマレーザを用いてエネルギー300mJ/cm<sup>2</sup>の条件でアモルファシリコン膜をアニールし、ポリシリコン膜に変換する。続いて、ポリシリコン膜をパターニングして第1及び第2の島状半導体膜24a、24bを形成する。

【0170】次に、第1及び第2の島状半導体膜24a、24bを被覆する膜厚30nmの第1のシリコン酸化膜(第1の絶縁膜)81をCVD法により形成した後、全面に膜厚300nmの第1のA1-Nd膜(第1の導電体膜)をPVD法により形成する。さらに、燐酸と酢酸を含む溶液により図示しないレジストマスクを基に第1のA1-Nd膜を選択的にエッティングして第1の島状半導体膜24aの上方の第1のシリコン酸化膜81上に第1のゲート電極82を形成する。

【0171】このとき、厚膜部のTFTの第2のゲート電極84aと交差する領域で、かつ第2の島状半導体膜50

24bの両側部のエッジの上に、第1のシリコン酸化膜81を介して、図24(a)、(b)に示す第1のA1-Nd膜からなる電界緩和電極82b、82cを形成する。

【0172】次いで、薄膜部のTFTの形成領域を図示しないレジストマスクで覆った後、フッ酸を含む溶液でシリコン酸化膜をライトエッティングする。その後、レジストマスクを除去する。なお、薄膜部のTFTのゲート絶縁膜81の材料をシリコン窒化膜とし、第1のゲート電極82の材料をクロム(Cr)とした場合、これらの材料はフッ酸を含む溶液に対してエッティング耐性があるため、薄膜部のTFTの形成領域をレジストマスクで保護しなくてもよい。

【0173】次に、図19(b)に示すように、全面に膜厚70nmの第2のシリコン酸化膜(第2の絶縁膜)83をCVD法により形成し、続いて膜厚300nmの第2のA1-Nd膜(第2の導電体膜)84をPVD法により形成する。

【0174】次に、図20(a)に示すように、第2のA1-Nd膜84の上にレジストマスク(マスクパターン)85を形成し、レジストマスク85に基づき、燐酸と酢酸を含む溶液で第2のA1-Nd膜84をウエットエッティングしてレジストマスク85で覆われていない領域の第2のA1-Nd膜84を除去し、さらにレジストマスク85下の第2のA1-Nd膜84をサイドエッティングしてレジストマスク85よりも片側でLDD領域分だけ幅を狭くした第2のゲート電極84aを形成する。

【0175】このとき、第1の島状半導体膜24aの両側部のエッジの上方で、かつ第1のゲート電極24a上に、第2のシリコン酸化膜83b、83cを介して図23(a)、(b)に示す第2のA1-Nd膜からなる電界緩和電極84c乃至84fを形成する。

【0176】次に、図20(b)に示すように、同じレジストマスク85に基づき、CHF<sub>3</sub>を含むエッティングガスを用いて第2のシリコン酸化膜83を異方性エッティングし、さらに第1のゲート電極82及びレジストマスク85に基づき、第1のシリコン酸化膜81を異方性エッティングして、第1のゲート電極82下に第1のシリコン酸化膜81aからなる第1のゲート絶縁膜を形成する。また、同時に、第2のゲート電極84a下に第1及び第2のシリコン酸化膜81b、83aからなる第2のゲート絶縁膜86を形成する。

【0177】なお、このとき、図22に示すように、島状半導体膜24a、24b上及びその他の領域に第1のシリコン酸化膜81cを膜厚10nm程度残すようにしてもよい。

【0178】その後、レジストマスク85を除去する。

【0179】次に、図21(a)に示すように、第1のゲート電極82をマスクとして第1の島状半導体膜24aにリン(不純物)を高濃度でイオン注入して第1のゲ

ート電極8 2の両側に高濃度不純物領域2 4 a a、2 4 a bを形成する。同時に、第2のゲート電極8 4 a及び第2のゲート絶縁膜8 3 a、8 1 bをマスクとして第2の島状半導体膜2 4 bにリン(不純物)を高濃度でイオン注入して、第2のゲート電極8 4 aの両側に一对の高濃度不純物領域2 4 b a、2 4 b bを形成する。このとき、イオン注入条件を、例えば、加速電圧10 kV、ドーズ量 $1 \times 10^{15} / \text{cm}^2$ とする。

【0180】次いで、第2のゲート電極8 4 aをマスクとし、かつ第2のゲート電極8 4 aの周辺部の第2のゲート絶縁膜8 3 a、8 1 bを透過する条件で第2の島状半導体膜2 4 bにリン(不純物)を低濃度でイオン注入して、第2のゲート電極8 4 aの両側で第2のゲート絶縁膜8 3 a、8 1 b下にLDD領域である一对の低濃度不純物領域2 4 b c、2 4 b dを形成する。このとき、イオン注入条件を、例えば、加速電圧100 kV、ドーズ量 $1 \times 10^{14} / \text{cm}^2$ とする。

【0181】なお、pチャネル型TFTが混在している場合、リンのイオン注入ではpチャネル型TFTの動作層をマスクせずにイオン注入し、その前でも後でもよいが、ボロンを高濃度に、例えば加速電圧10 kV、ドーズ量 $1 \times 10^{16} / \text{cm}^2$ の条件でイオン注入することで、リンの濃度を補償してp型化する。

【0182】次いで、温度400でアニールすることにより、第1及び第2の島状半導体膜2 4 a、2 4 b内の水素出しを行う。次いで、250 mJ /  $\text{cm}^2$ の条件で、レーザ照射してアニールし、第1及び第2の島状半導体膜2 4 a、2 4 b内のリンを活性化する。

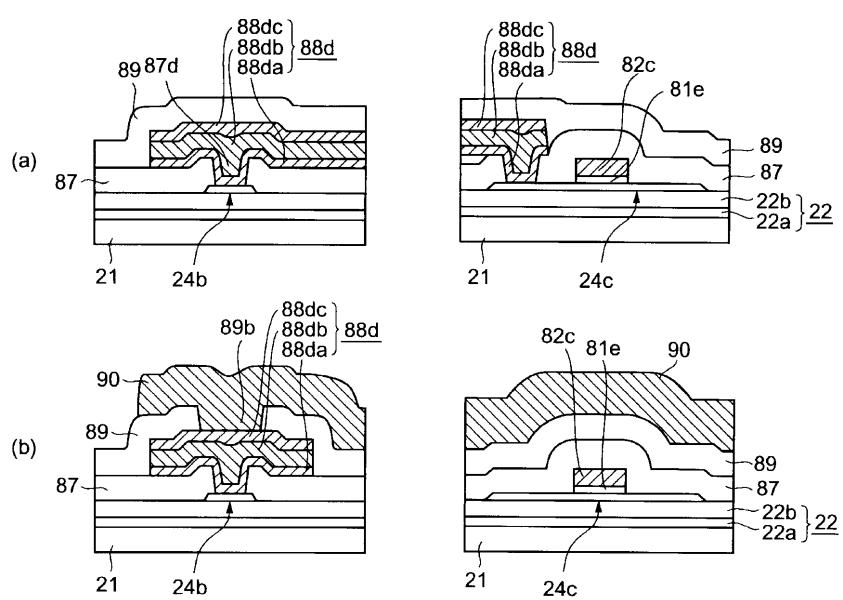

【0183】次に、図21(b)に示すように、CVD法により、シリコン窒化膜(第1の層間絶縁膜)8 7を厚さ400 nmで成膜する。続いて、第1のシリコン窒化膜8 7をパターニングし、薄膜部のTFTの形成領域の高濃度不純物領域2 4 a a、2 4 a b上にコンタクトホール8 7 a、8 7 bを形成する。同時に厚膜部のTFTの形成領域の高濃度不純物領域2 4 b a、2 4 b b上にコンタクトホール8 7 c、8 7 dを形成する。

【0184】次に、PVD法により、Ti膜/A1膜/Ti膜の3層の金属膜を全膜厚200 nmで成膜した後、パターニングしてコンタクトホール8 7 a、8 7 bを通して高濃度不純物領域2 4 a a、2 4 a bと接触するソース/ドレイン電極8 8 a、8 8 bを形成する。同時に、コンタクトホール8 7 c、8 7 dを通して高濃度不純物領域2 4 b a、2 4 b bと接触するソース/ドレイン電極8 8 c、8 8 dを形成する。

【0185】次に、CVD法により、ソース/ドレイン電極8 8 a乃至8 8 dを被覆するシリコン窒化膜(第2の層間絶縁膜)8 9を膜厚400 nmで成膜する。これにより、薄膜トランジスタ装置が完成する。

【0186】液晶表示装置のTFT基板及び液晶表示装置を作成する場合、図21(b)の右の図に示すよう

に、ソース/ドレイン電極8 8 d上のシリコン窒化膜8 9にピアホール8 9 aを形成する。続いて、ITO膜を成膜した後、ITO膜をパターニングし、ピアホール8 9 aを介してソース/ドレイン電極8 8 dと接触する画素電極9 0を形成する。その後、第1及び第2の実施の形態で説明した製造方法に従う。

【0187】以上のように、本発明の第3の実施の形態の薄膜トランジスタ装置の製造方法においては、図20(a)に示すように、レジストマスク8 5に基づき、A1-Nd膜をサイドエッチングして、レジストマスク8 5のエッジから片側でLDD領域分だけ小さい第2のゲート電極8 4 aを形成し、さらに、レジストマスク8 5に基づき、シリコン酸化膜8 3、8 1を異方性エッチングして第2のゲート電極8 4 aよりも片側でLDD領域分だけ大きい第2のゲート絶縁膜8 6を形成している。そして、図21(a)に示すように、イオン注入の際に第2のゲート絶縁膜8 6を透過しないような条件で高ドーズ量のイオン注入を行い、さらに第2のゲート絶縁膜8 6を透過するような条件で低ドーズ量のイオン注入を行うことにより、第2の島状半導体膜2 4 bにLDD構造を形成している。

【0188】このように、露光用マスクを増やさずに、ゲート電極8 4 aやゲート絶縁膜8 6を利用して自己整合的にLDD構造を形成することができる。

【0189】また、図20(a)、(b)に示すように、膜厚の異なるゲート絶縁膜8 1 a、8 6を一度のエッチングにより形成することができるので、工程の簡略化を図ることができる。この場合、島状半導体膜2 4 a、2 4 bのチャネル領域はお互いにエッチングガスのプラズマに曝されないので、島状半導体膜2 4 a、2 4 bのチャネル領域表面にダメージ層が発生するのを防止することができる。

【0190】(第4の実施の形態)次に、本発明の第4の実施の形態の薄膜トランジスタ装置を搭載した液晶表示装置の構造について図面を参照して説明する。

【0191】その液晶表示装置においては、第1の実施の形態で既に説明したように、同一の基板上に薄膜部のTFT(第1の薄膜トランジスタ)と、厚膜部のTFT(第2の薄膜トランジスタ)とが形成されている。薄膜部のTFTは周辺回路部で用いられ、厚膜部のTFTは表示部で用いられる。また、周辺回路部でも高電圧を扱うバッファ部では、厚膜部のTFT類似のTFTが用いられる。

【0192】この第4の実施の形態では、表示部の構造、特に蓄積容量バスラインに付属する蓄積容量素子の構造に特徴があるので、それを中心に説明する。

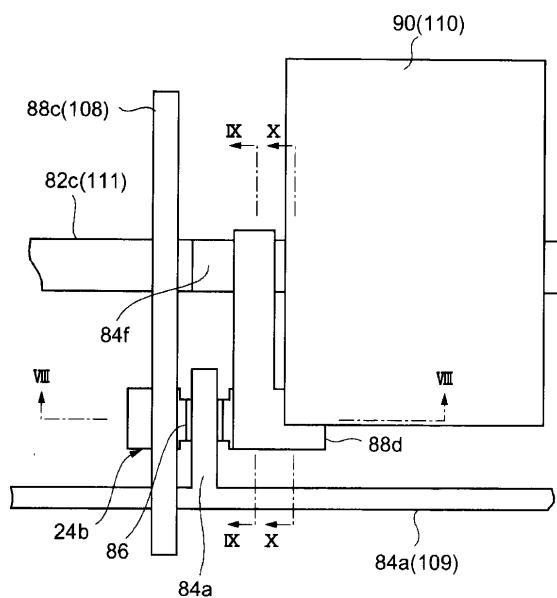

【0193】図25は、本発明の第4の実施の形態の液晶表示装置の表示部の一画素を上から見た構造を示す平面図である。図25のIIIV-IIIV線に沿う断面図はTFTの断面であり、図21(b)の右の図に示す。図26

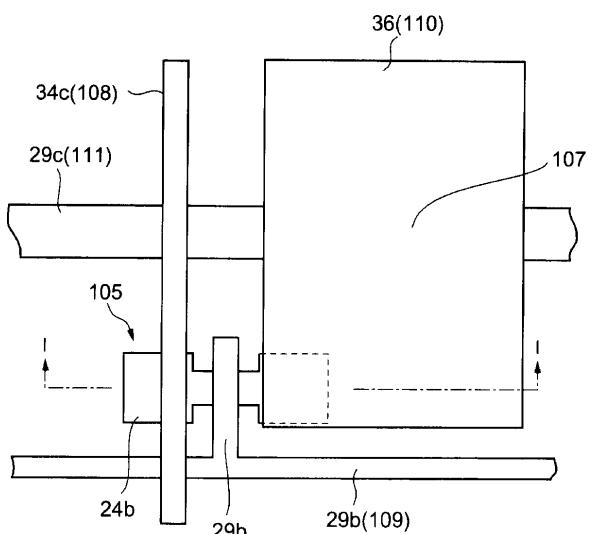

(a) は図25のIX-IX線に沿う断面図、同図(b) は図25のX-X線に沿う断面図である。

【0194】図25に示すように、画素電極90(90)が厚膜部のTFTのソース/ドレイン電極88dを介してソース/ドレイン領域24b<sub>a</sub>と接続され、画素電極90と交差するように蓄積容量バスライン111(82c)が設けられている。蓄積容量バスライン82cは薄膜部のTFTの第1のゲート電極82と同じ材料で形成されており、厚膜部のTFTのソース/ドレイン電極88dと接続されている。

【0195】データバスライン108はソース/ドレイン電極88cと同じ材料で形成されており、厚膜部のTFTのもう一方のソース/ドレイン領域24b<sub>a</sub>と接続されている。また、ゲートバスライン109は厚膜部のTFTの第2のゲート電極84aと同じ材料で形成され、かつその第2のゲート電極84aと繋がっている。

【0196】厚膜部のTFTは、図21(b)の右の図に示すように、チャネル領域24b<sub>e</sub>を挟んで形成された一対のソース/ドレイン領域24b<sub>a</sub>、24b<sub>b</sub>を有し、そのうち何れか一が画素電極90と接続した第2の島状半導体膜24bと、第2の島状半導体膜24bのチャネル領域24b<sub>e</sub>上に形成された第1及び第2のシリコン酸化膜81b、83aからなる第2のゲート絶縁膜86と、第2のゲート絶縁膜86上に形成された第2のA1-Nd膜からなる第2のゲート電極84aにより構成されている。

【0197】蓄積容量バスライン82cは、図26(a)、(b)のそれぞれ右の図に示すように、第1のA1-Nd膜により構成され、その一部領域で、蓄積容量バスライン82c上に第2のシリコン酸化膜83dと第2のA1-Nd膜84fとがこの順に積層されてなる。また、図26(a)に示すように、第2のA1-Nd膜84fは厚膜部のTFTのソース/ドレイン電極88dと接続され、さらに、図26(b)の左の図に示すように、ソース/ドレイン電極88dを介して画素電極90と接続されている。なお、ソース/ドレイン電極88dはTi膜88d<sub>a</sub>/A1膜88d<sub>b</sub>/Ti膜88d<sub>c</sub>の3層構造となっている。図中、図21(b)と同じ符号で示すものは図21(b)と同じものを示すので、その説明を省略する。

【0198】なお、薄膜部のTFTは、図21(b)の左の図と同じ構造を有するので、説明を省略する。

【0199】以上のように、本発明の第4の実施の形態の液晶表示装置によれば、薄膜部のTFTの第1のゲート電極82と同じ材料により表示部の蓄積容量バスライン108を形成している。また、蓄積容量バスライン108を一方の電極とし、第2のゲート絶縁膜86のうち第2の絶縁膜83aと同じ材料で容量絶縁膜83dを形成し、第2のゲート電極84aと同じ材料で他方の電極84fを形成した容量素子を有している。

【0200】これにより、ゲート絶縁膜は通常薄く形成されるので、ITO膜を他方の電極とし、層間絶縁膜を容量絶縁膜とする容量素子よりも、単位面積当たり高い容量値の容量素子を得ることができる。従って、蓄積容量を形成するために必要な蓄積容量バスライン108の面積、即ち遮光領域を減らすことができるので、開口率を向上させることができる。

【0201】この液晶表示装置に用いる薄膜トランジスタ装置の作成は、第3の実施の形態の薄膜トランジスタ装置の製造方法を適用する。この場合、蓄積容量バスライン82c等は、以下のように、TFTのゲート電極等の形成工程と共に形成される。

【0202】蓄積容量バスライン82cは、第1のゲート電極82を形成するときに同時に第1のA1-Nd膜で形成する。また、厚膜部のTFTの第2のゲート絶縁膜86を形成するため第2のシリコン酸化膜83をエッティングするときに、蓄積容量バスライン82a上に第2のシリコン酸化膜83dを残す。第2のシリコン酸化膜83d上の第2のA1-Nd膜84fは第2のゲート電極84aを形成するときに同時にパターニングして形成する。また、ゲート電極84aの形成と同時にゲートバスライン109を形成し、ソース/ドレイン電極88a乃至88dの形成と同時にデータバスライン108を形成する。

【0203】その後、第3の実施の形態で説明したシリコン窒化膜89を形成する工程に続いて、シリコン窒化膜89をパターニングし、ソース/ドレイン電極88d上にピアホール89aを形成する。次に、PVD法により、膜厚100nmのITO膜を形成した後、パターニングして画素電極90を形成する。

【0204】次いで、ガラス基板21の上側全面に、液晶分子の初期状態(電圧無印加時)の配向方向を決める配向膜(図示せず)を形成する。

【0205】このようにして、液晶表示装置のTFT基板が完成する。

【0206】液晶表示装置の対向基板は、公知の方法で作成する。すなわち、ガラス基板上に、例えばCr(クロム)により、画素間の領域を遮光するためのブラックマトリクスを形成する。また、ガラス基板上に赤色、緑色及び青色のカラーフィルタを形成し、各画素毎に赤色、緑色及び青色の何れか1色のカラーフィルタを配置する。その後、ガラス基板の上側全面にITO膜からなる透明電極を形成し、透明電極の上に配向膜を形成する。

【0207】このようにして製造されたTFT基板と対向基板とを貼り合わせ、両者の間に液晶を封入して液晶パネルとする。この液晶パネルの両面に偏光板を配置し、裏面側にバックライトを配置すると、液晶表示装置が完成する。

【0208】(第5の実施の形態) 次に、本発明の第5

の実施の形態の薄膜トランジスタ装置を搭載した液晶表示装置の構造について図面を参照して説明する。

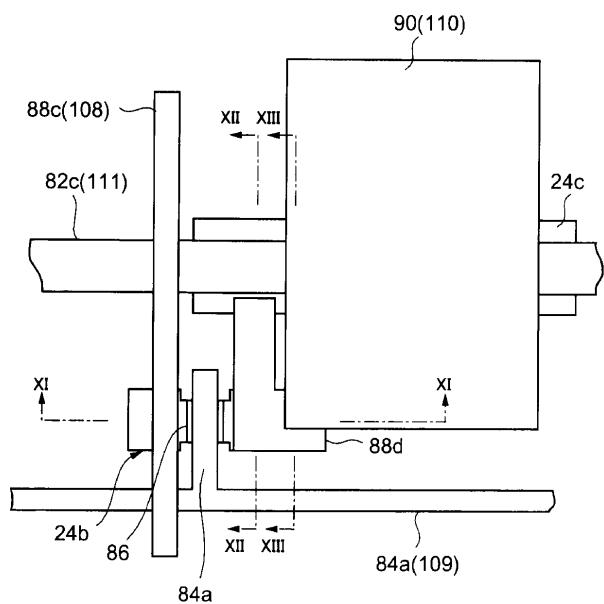

【0209】第5の実施の形態の液晶表示装置は、第4の実施の形態の液晶表示装置と同様に、基板上に形成された薄膜部のTFTと、厚膜部のTFTと、厚膜部のTFTのソース／ドレイン領域と接続された画素電極110(90)及びデータバスライン108(88c)と、厚膜部のTFTのゲート電極と接続されたゲートバスライン109(84a)と、画素電極90と交差する蓄積容量バスライン111(82c)とを有する。

【0210】第4の実施の形態と異なるところは、表示部、特に蓄積容量バスライン82cに付属する蓄積容量素子の構造である。

【0211】図27は本発明の第5の実施の形態である液晶表示装置の表示部の一画素を上から見た構造を示す平面図である。図27のXI-XI線に沿う断面図はTFTの断面であり、図21(b)の右の図に示す。図28(a)は図27のXII-XII線に沿う断面図であり、図28(b)は図27のXIII-XIII線に沿う断面図である。

【0212】表示部の構成要素のうち、薄膜部のTFT及び厚膜部のTFTは、第4の実施の形態と同じ構造なので、その詳細な説明を省略する。

【0213】蓄積容量バスライン82c(111)は、図28(a)、(b)に示すように、薄膜部のTFTの第1のゲート電極82と同じ材料である第1のA1-Nd膜(第1の導電体膜)により構成され、その一部領域で、蓄積容量バスライン82cを一方の電極とする蓄積容量素子を備えている。その蓄積容量素子は蓄積容量バスライン82cからなる一方の電極と、薄膜部のTFTの第1のゲート絶縁膜81aと同じ材料である第1のシリコン酸化膜81eからなる容量絶縁膜と、第1及び第2の島状半導体膜24a、24bと同じ材料である第3の島状半導体膜24cからなる他方の電極とにより構成される。蓄積容量バスライン82cの両側の第3の島状半導体膜24cに一対のp型不純物領域が形成されている。一対のp型不純物領域のうち何れか一は画素電極90と接続されている。言い換えれば、蓄積容量バスライン82cを第3のゲート電極とし、第1のシリコン酸化膜81eを第3のゲート絶縁膜とし、第3の島状半導体膜24cを動作層とし、一対のp型不純物領域をソース／ドレイン領域とする、pチャネル型の第3の薄膜トランジスタと同じ構造となっている。

【0214】ここで、pチャネル型の第3の薄膜トランジスタを用いているのは、以下の理由による。即ち、画素TFTをnチャネル型とするとオン電流が高く、画素の蓄積電荷量を増やしやすい。また、画素TFTをnチャネル型とし、寄生TFTの影響を防止するために、図24のような構造を用いた場合、画素TFTの電界緩和電極82a、82bへの印加電圧を負にすることが好ましい。さらに、画素TFTの電界緩和電極82a、82b

と蓄積容量素子のゲート電極(蓄積容量バスライン)82cとを同電位とすることで電源を減らすことができる。以上より、蓄積容量素子のゲート電極(蓄積容量バスライン)82cには負の電位がかかるので、第3の薄膜トランジスタをpチャネル型とすることで、常にチャネルが導通している状態を保持することができる、即ち電極として用いることができるからである。

【0215】次に、第5の実施の形態の液晶表示装置の製造方法について説明する。そのうち、薄膜トランジスタ装置の作成は、第3の実施の形態の薄膜トランジスタ装置の製造方法を適用する。この場合、蓄積容量バスライン82c等は、以下のように、TFTのゲート電極等の形成工程と共に形成される。

【0216】第3の島状半導体膜24cは、第1及び第2の島状半導体膜24a、24bを形成するときに、同時にパターニングして形成する。第1のシリコン酸化膜81eからなるゲート絶縁膜は、第1のシリコン酸化膜81をパターニングして第1のゲート絶縁膜81aと、第2のゲート絶縁膜86の一部を形成するときに同時にパターニングして形成する。蓄積容量バスライン82cは第1のA1-Nd膜をパターニングして第1のゲート電極82を形成するときに同時にパターニングして形成する。

【0217】その後、第3の実施の形態で説明したシリコン窒化膜89を形成する工程に続いて、シリコン窒化膜89をパターニングし、ソース／ドレイン電極88d上にピアホール89aを形成する。次に、PVD法により、膜厚100nmのITO膜を形成した後、パターニングして画素電極90を形成する。

【0218】次いで、ガラス基板21の上側全面に、液晶分子の初期状態(電圧無印加時)の配向方向を決める配向膜(図示せず)を形成する。

【0219】このようにして、液晶表示装置のTFT基板が完成する。

【0220】液晶表示装置の対向基板は、公知の方法で作成する。すなわち、ガラス基板上に、例えばCr(クロム)により、画素間の領域を遮光するタメのブラックマトリクスを形成する。また、ガラス基板上に赤色、緑色及び青色のカラーフィルタを形成し、各画素毎に赤色、緑色及び青色の何れか1色のカラーフィルタを配置する。その後、ガラス基板の上側全面にITO膜からなる透明電極を形成し、透明電極の上に配向膜を形成する。

【0221】このようにして製造されたTFT基板と対向基板とを貼り合わせ、両者の間に液晶を封入して液晶パネルとする。この液晶パネルの両面に偏光板を配置し、裏面側にパックライトを配置すると、液晶表示装置が完成する。

【0222】以上のように、本発明の第5の実施の形態においては、薄膜部のTFTの第1のゲート電極82cと

同じ材料である蓄積容量バスライン108を一方の電極とし、第2のゲート絶縁膜86のうち第1の絶縁膜81bと同じ材料で容量絶縁膜81eを形成し、第1及び第2の島状半導体膜24a、24bと同じ材料で他方の電極24cを形成した蓄積容量素子を有している。

【0223】これにより、ゲート絶縁膜は通常薄く形成されるので、ITO膜を他方の電極とし、層間絶縁膜を容量絶縁膜とする蓄積容量素子よりも、単位面積当たり高い容量値の蓄積容量素子を得ることができる。これにより、蓄積容量を形成するために必要な蓄積容量バスライン108の面積、即ち遮光領域を減らすことができる10ので、開口率を向上させることができる。

【0224】また、画素TFTを図24の電界緩和電極82a、82bを備えたような構造としても、蓄積容量素子のゲート電極82cと電界緩和電極82a、82bに一つの蓄積容量バスライン82cから電圧を供給することができる。従って、蓄積容量素子のゲート電極82c及び電界緩和電極82a、82bへの電圧供給のための余分な配線を増やす必要がないので、開口率の低下を防止することができる。

【0225】以上、実施の形態によりこの発明を具体的に説明したが、この発明は上記実施の形態に具体的に示した例に限られるものではなく、この発明の要旨を逸脱しない範囲の上記実施の形態の変更はこの発明の範囲に含まれる。

【0226】例えば、上記では薄膜トランジスタ装置を液晶表示装置に応用しているが、有機EL表示装置に適用することも可能である。

【0227】また、基板として、ガラス基板上にシリコン窒化膜及びシリコン酸化膜を積層した透明な基板を用いているが、裏面から露光光を照射する工程を有する製造方法を適用している場合を除き、不透明な基板を用いることもできる。

【0228】(付記1) 透明基板の表面に第1及び第2の島状半導体膜を形成する工程と、前記第1及び第2の島状半導体膜を被覆する第1の絶縁膜を形成する工程と、前記第1の絶縁膜上にネガティブフォトレジスト膜を形成する工程と、前記第1の島状半導体膜の全域を遮光するマスクを介して前記ネガティブフォトレジスト膜を露光する工程と、前記透明基板の裏面側から前記ネガティブフォトレジスト膜を露光する工程と、前記ネガティブフォトレジスト膜を現像して前記第1の島状半導体膜の周縁から内側の表面に開口部を有するレジストパターンを形成する工程と、前記レジストパターンの開口部内の前記第1の絶縁膜をエッチングする工程と、前記レジストパターンを除去する工程と、前記透明基板の表面側全面に第2の絶縁膜を形成し、さらにその上に導電体膜を形成する工程と、前記第1の島状半導体膜上方の導電体膜上に第1のマスクパターンを形成し、前記第2の島状半導体膜上方の導電体膜上に第2のマスクパターン50

を形成する工程と、前記第1のマスクパターンをマスクとして前記導電体膜をエッチングして第1のゲート電極を形成し、前記第2のマスクパターンをマスクとして前記導電体膜をエッチングして第2のゲート電極を形成する工程とを有することを特徴とする薄膜トランジスタ装置の製造方法。

【0229】(付記2) 前記透明基板の裏面側から前記ネガティブフォトレジスト膜を露光する工程において、前記露光に用いる光はg線、h線、i線、エキシマレーザ又はUV光であることを特徴とする付記1記載の薄膜トランジスタ装置の製造方法。

【0230】(付記3) 基板上に第1及び第2の島状半導体膜を形成する工程と、前記第1及び第2の島状半導体膜を被覆する半導体膜を形成し、さらに該半導体膜上に絶縁膜を形成する工程と、前記第2の島状半導体膜上方の前記絶縁膜を選択的にエッチングして前記絶縁膜のパターンを形成する工程と、前記絶縁膜のパターンの下部及びその他の部分の半導体膜を酸化して、前記第1の島状半導体膜上に前記半導体膜を酸化してなる絶縁膜からなる第1のゲート絶縁膜を形成し、前記第2の島状半導体膜上に前記半導体膜を酸化してなる絶縁膜と前記絶縁膜のパターンとからなる第2のゲート絶縁膜を形成する工程と、前記第1のゲート絶縁膜上に第1のゲート電極を形成し、前記第2のゲート絶縁膜上に第2のゲート電極を形成する工程とを有することを特徴とする薄膜トランジスタ装置の製造方法。

【0231】(付記4) 前記第1及び第2の島状半導体膜はポリシリコン膜であり、前記半導体膜はアモルファスシリコン膜であることを特徴とする付記3記載の薄膜トランジスタ装置の製造方法。

【0232】(付記5) 前記第2の島状半導体膜上方の前記絶縁膜を選択的にエッチングして前記絶縁膜のパターンを形成する工程において、前記絶縁膜をエッチングする際に前記半導体膜をエッチングのストップとすることを特徴とする付記3記載の薄膜トランジスタ装置の製造方法。

【0233】(付記6) 前記半導体膜を形成する前に、前記第1及び第2の島状半導体膜を被覆する絶縁膜を形成する工程を有し、前記第1のゲート絶縁膜は前記第1の島状半導体膜を被覆する絶縁膜と前記半導体膜を酸化してなる絶縁膜とからなり、前記第2のゲート絶縁膜は前記第2の島状半導体膜を被覆する絶縁膜と前記半導体膜を酸化してなる絶縁膜と前記絶縁膜のパターンとからなることを特徴とする付記3記載の薄膜トランジスタ装置の製造方法。

【0234】(付記7) 基板上に第1の半導体膜を形成する工程と、前記第1の半導体膜上に第1の絶縁膜と第2の半導体膜と第2の絶縁膜とをこの順に形成する工程と、前記第2の絶縁膜を選択的にエッチングして前記第2の絶縁膜のパターンを形成する工程と、前記第2の

半導体膜を選択的にエッティングして、前記第2の絶縁膜のパターンを含まない島状の第2の半導体膜と、前記第2の絶縁膜のパターンを含む島状の第2の半導体膜とを形成する工程と、前記第2の絶縁膜のパターンの下部及びその他の部分の島状の第2の半導体膜を酸化するとともに、前記島状の第2の半導体膜を前記第1の絶縁膜を介して酸化し、前記第2の絶縁膜のパターンを含まない島状の第2の半導体膜で覆われていた領域の第1の半導体膜を前記第1の絶縁膜を介して酸化し、前記島状の第2の半導体膜で覆われていた領域に前記第1の半導体膜からなる第1の島状半導体膜を形成し、前記第2の絶縁膜のパターンを含む島状の第2の半導体膜で覆われていた領域に前記第1の半導体膜からなる第2の島状半導体膜を形成するとともに、前記第1の島状半導体膜上に前記第2の半導体膜を酸化してなる絶縁膜と前記第1の絶縁膜とからなる第1のゲート絶縁膜を形成し、前記第2の島状半導体膜上に前記第2の絶縁膜のパターンと前記第2の半導体膜を酸化してなる絶縁膜と前記第1の絶縁膜とからなる第2のゲート絶縁膜を形成する工程と、前記第1のゲート絶縁膜上に第1のゲート電極を形成し、前記第2のゲート絶縁膜上に第2のゲート電極を形成する工程とを有することを特徴とする薄膜トランジスタ装置の製造方法。

【0235】(付記8) 前記第1の半導体膜はポリシリコン膜であり、第2の半導体膜はアモルファスシリコン膜であることを特徴とする付記7記載の薄膜トランジスタ装置の製造方法。

【0236】(付記9) 前記第2の絶縁膜を選択的にエッティングして前記第2の絶縁膜のパターンを形成する工程において、前記第2の絶縁膜をエッティングする際に前記第2の半導体膜をエッティングのストップとすることを特徴とする付記7記載の薄膜トランジスタ装置の製造方法。

【0237】(付記10) 前記第2の半導体膜を選択的にエッティングして、前記第2の絶縁膜のパターンを含まない島状の第2の半導体膜と、前記第2の絶縁膜のパターンを含む島状の第2の半導体膜とを形成する工程において、前記第2の半導体膜を選択的にエッティングする際に前記第1の絶縁膜をエッティングのストップとすることを特徴とする付記7記載の薄膜トランジスタ装置の製造方法。

【0238】(付記11) チャネル領域を挟んで形成された一対のソース／ドレイン領域を有する第1の島状半導体膜と、前記第1の島状半導体膜の前記チャネル領域上に形成された第1の絶縁膜からなる第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1の導電体膜からなる第1のゲート電極とにより構成された第1の薄膜トランジスタと、チャネル領域を挟んで形成された一対のソース／ドレイン領域を有する第2の島状半導体膜と、前記第2の島状半導体膜の前記チャネル領域上に形成された前記第1の絶縁膜及び第2の絶縁膜か

10

20

30

40

50

らなる第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2の導電体膜からなる第2のゲート電極とにより構成された第2の薄膜トランジスタとを同一の基板上に有し、前記第1の薄膜トランジスタは前記第1の島状半導体膜の側部のエッジの上方で、かつ第1のゲート電極上に前記第2の絶縁膜を介して前記第2の導電体膜からなる電界緩和電極を有し、前記第2の薄膜トランジスタは前記第2のゲート電極下で、かつ前記第2の島状半導体膜の側部のエッジの上に前記第1の絶縁膜を介して前記第1の導電体膜からなる電界緩和電極を有することを特徴とする薄膜トランジスタ装置。

【0239】(付記12) 基板上に第1及び第2の島状半導体膜を形成する工程と、前記第1及び第2の島状半導体膜を被覆する第1の絶縁膜を形成する工程と、全面に第1の導電体膜を形成し、さらに前記第1の導電体膜を選択的にエッティングして前記第1の島状半導体膜の上方の第1の絶縁膜上に第1のゲート電極を形成する工程と、全面に第2の絶縁膜と第2の導電体膜をこの順に形成する工程と、前記第2の導電体膜の上にマスクパターンを形成し、該マスクパターンをマスクとして前記第2の導電体膜をサイドエッティングして前記マスクパターンよりも幅が狭い第2のゲート電極を形成する工程と、前記マスクパターンをマスクとして前記第2の絶縁膜を異方性エッティングし、さらに前記第1のゲート電極及び前記マスクパターンをマスクとして前記第1の絶縁膜を異方性エッティングして、前記第1のゲート電極下に前記第1の絶縁膜からなる第1のゲート絶縁膜を形成するとともに、前記第2のゲート電極下に前記第1及び第2の絶縁膜からなる第2のゲート絶縁膜を形成する工程と、前記マスクパターンを除去する工程と、前記第1のゲート電極をマスクとして前記第1の島状半導体膜に不純物をイオン注入して前記第1のゲート電極の両側に高濃度不純物領域を形成し、前記第2のゲート電極及び前記第2のゲート絶縁膜をマスクとして前記第2の島状半導体膜に不純物をイオン注入して、前記第2のゲート電極の両側に一対の高濃度不純物領域を形成する工程と、前記第2のゲート電極をマスクとし、かつ前記第2のゲート電極の周辺部の第2のゲート絶縁膜を透過する条件で前記第2の島状半導体膜に不純物をイオン注入して、前記第2のゲート電極の両側で前記第2のゲート絶縁膜下に一対の低濃度不純物領域を形成する工程とを有することを特徴とする薄膜トランジスタ装置の製造方法。

【0240】(付記13) 前記マスクパターンをマスクとして前記第2の絶縁膜を異方性エッティングし、さらに前記第1のゲート電極及び前記マスクパターンをマスクとして前記第1の絶縁膜を異方性エッティングする工程において、前記第1及び第2の島状半導体膜が前記第1の絶縁膜で被覆されるように、前記第1の絶縁膜を残すことを特徴とする付記12記載の薄膜トランジスタ装置の製造方法。

【0241】(付記14) 全面に第1の導電体膜を形成し、さらに前記第1の導電体膜を選択的にエッティングして前記第1の島状半導体膜の上方の第1の絶縁膜上に第1のゲート電極を形成する工程において、第2のゲート電極を形成すべき領域で、かつ前記第2の島状半導体膜の両側部のエッジの上に前記第1の絶縁膜を介して前記第1の導電体膜からなる電界緩和電極を形成することを特徴とする付記12記載の薄膜トランジスタ装置の製造方法。

【0242】(付記15) 前記第2の導電体膜の上にマスクパターンを形成し、該マスクパターンをマスクとして前記第2の導電体膜をサイドエッティングして前記マスクパターンよりも幅が狭い第2のゲート電極を形成する工程において、前記第1の島状半導体膜の両側部のエッジの上方で、かつ前記第1のゲート電極上に前記第2の絶縁膜を介して前記第2の導電体膜からなる電界緩和電極を形成することを特徴とする付記12記載の薄膜トランジスタ装置の製造方法。

【0243】(付記16) 基板上に形成された第1の薄膜トランジスタと、第2の薄膜トランジスタと、前記第2の薄膜トランジスタのソース／ドレイン領域と接続された画素電極と、前記画素電極と交差する蓄積容量バスラインとを有し、前記第1の薄膜トランジスタは、チャネル領域を挟んで形成された一対のソース／ドレイン領域を有する第1の島状半導体膜と、前記第1の島状半導体膜の前記チャネル領域上に形成された第1の絶縁膜からなる第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された第1の導電体膜からなる第1のゲート電極とにより構成され、前記第2の薄膜トランジスタは、チャネル領域を挟んで形成された一対のソース／ドレイン領域を有し、そのうち何れか一が前記画素電極と接続した第2の島状半導体膜と、前記第2の島状半導体膜の前記チャネル領域上に形成された前記第1の絶縁膜及び第2の絶縁膜からなる第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2の導電体膜からなる第2のゲート電極とにより構成され、前記蓄積容量バスラインは、前記第1の導電体膜により構成され、その一部領域で、前記蓄積容量バスライン上に前記第2の絶縁膜と前記画素電極と接続された第2の導電体膜とがこの順に積層されることを特徴とする液晶表示装置。

【0244】(付記17) 基板上に形成された第1の薄膜トランジスタと、第2の薄膜トランジスタと、前記第2の薄膜トランジスタのソース／ドレイン領域と接続された画素電極と、前記画素電極と交差する蓄積容量バスラインとを有し、前記第1の薄膜トランジスタは、チャネル領域を挟んで形成された一対のソース／ドレイン領域を有する第1の島状半導体膜と、前記第1の島状半導体膜の前記チャネル領域上に形成された第1の絶縁膜からなる第1のゲート絶縁膜と、前記第1のゲート絶縁膜

膜上に形成された第1の導電体膜からなる第1のゲート電極とにより構成され、前記第2の薄膜トランジスタは、チャネル領域を挟んで形成された一対のソース／ドレイン領域を有し、そのうち何れか一が前記画素電極と接続した第2の島状半導体膜と、前記第2の島状半導体膜の前記チャネル領域上に形成された前記第1の絶縁膜及び第2の絶縁膜からなる第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2の導電体膜からなる第2のゲート電極とにより構成され、前記蓄積容量バスラインは、前記第1の導電体膜により構成され、その一部領域で、前記蓄積容量バスラインをゲート電極とし、前記画素電極と接続されたソース／ドレイン領域を有する第3の島状半導体膜と、前記第1の絶縁膜からなるゲート絶縁膜とを有する第3の薄膜トランジスタを備えていることを特徴とする液晶表示装置。

【0245】(付記18) 前記第1及び第2の薄膜トランジスタはnチャネル型であり、前記第3の薄膜トランジスタはpチャネル型であることを特徴とする付記17記載の液晶表示装置。

【0246】(付記19) 前記第1、第2及び第3の島状半導体膜は同一の半導体膜からなることを特徴とする付記17記載の液晶表示装置。

【0247】

【発明の効果】以上説明したように、本発明によれば、薄い膜厚の第1のゲート絶縁膜を有する薄膜トランジスタの形成領域において、第1のゲート絶縁膜を形成する前に、厚い膜厚の第2のゲート絶縁膜を有する薄膜トランジスタのゲート絶縁膜の一部となる第1の絶縁膜で第1の島状半導体膜の周縁部を覆っているため、ゲート部を作成したときに第1のゲート電極下の第1の島状半導体膜の周縁部は第2の絶縁膜のほかに第1の絶縁膜で覆われる。このため、第1の島状半導体膜の周縁部でゲート電圧印加時の電界集中を緩和して寄生薄膜トランジスタが動作するのを防止することができる。

【0248】また、第1の島状半導体膜の周縁部を覆う第1の絶縁膜をパターニングする際に、第1の島状半導体膜をマスクとして透明基板の裏面から露光光を照射しているため、自己整合的に極めて精度よく第1の島状半導体膜の周縁部を第1の絶縁膜で覆うことができる。これにより、第1の島状半導体膜のチャネル幅方向の寸法マージンを最小にすることができる、従って薄膜トランジスタの微細化が可能である。

【0249】また、本発明によれば、絶縁膜をエッティングして第2のゲート絶縁膜の一部となる絶縁膜を形成するときに、下地の半導体膜等によりエッティングガス等から第1の島状半導体膜が保護されるため、厚い膜厚の第2のゲート絶縁膜を有する薄膜トランジスタ及び薄い膜厚の第1のゲート絶縁膜を有する薄膜トランジスタともに良好な特性を確保することができる。

【0250】また、第1及び第2の島状半導体膜の下地

の基板も半導体膜等により保護されているため、基板表面に絶縁膜が形成されている場合、第1及び第2の島状半導体膜の端部で基板表面の絶縁膜がエッティングされることによる「えぐれ」も生じない。

【0251】さらに、半導体膜を酸化してゲート絶縁膜を形成しているため、ゲート絶縁膜の膜厚を精度よく、かつ容易に制御することが可能である。

【0252】さらに、本発明によれば、第1の薄膜トランジスタにおいては、第1の島状半導体膜の両側部のエッジの上方で、かつ第1のゲート電極上に、第2の絶縁膜を介して電界緩和電極を有している。従って、第1の島状半導体膜の両側部のエッジ部分にかかるゲート電位の立ち上がりを遅らせることにより、第1の島状半導体膜の両側部のエッジ部の寄生トランジスタが動作するのを抑制することができる。また、第2の薄膜トランジスタにおいては、第2のゲート電極下で、かつ第2の島状半導体膜の両側部のエッジの上に第1の絶縁膜を介して電界緩和電極を有しているので、第2の島状半導体膜の両側部のエッジ部のチャネルが導通するのを抑制し、また、第2のゲート電極からの電界の影響をシールドして、寄生トランジスタがオンするのを抑制することができる。

【0253】また、本発明によれば、サイドエッティングによりマスクパターンよりも幅が狭い第2のゲート電極を形成し、さらに、同じマスクパターンに基づき、異方性エッティングにより第2のゲート電極よりも幅が広い第2のゲート絶縁膜を形成している。そして、第2のゲート電極と第2のゲート絶縁膜をマスクとしてイオン注入することにより、高濃度不純物領域を形成し、さらに低濃度不純物領域を形成している。これにより、露光用マスクを増やすずに、ゲート電極やゲート絶縁膜を利用して自己整合的にLDD構造を形成することができる。

【0254】また、膜厚の異なる第1及び第2のゲート絶縁膜を一度のエッティングにより形成することができるので、工程の簡略化を図ることができる。

【0255】さらに、本発明によれば、蓄積容量バスラインを一方の電極とし、第2のゲート絶縁膜のうち第2の絶縁膜と同じ材料の絶縁膜を容量絶縁膜とし、第2のゲート電極と同じ材料の第2の導電体膜を他方の電極とする蓄積容量素子を備えている。また、蓄積容量バスラインを一方の電極とし、第1の絶縁膜を容量絶縁膜とし、第3の島状半導体膜を他方の電極とする蓄積容量素子を備えている。

【0256】ゲート絶縁膜は通常薄く形成されるので、ITO膜を他方の電極とし、層間絶縁膜を容量絶縁膜とする蓄積容量素子よりも、単位面積当たり高い容量値の蓄積容量素子を得ることができる。これにより、蓄積容量を形成するために必要な蓄積容量バスラインの面積、即ち遮光領域を減らすことができるので、開口率を向上させることができる。

#### 【図面の簡単な説明】

【図1】本発明の第1の実施の形態の薄膜トランジスタ装置（透過型液晶表示装置）の構成を示すブロック図である。

【図2】本発明の第1の実施の形態の薄膜トランジスタ装置を示す平面図である。

【図3】(a)、(b)は本発明の第1の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その1）である。

【図4】(a)、(b)は本発明の第1の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その2）である。

【図5】(a)、(b)は本発明の第1の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その3）である。

【図6】(a)、(b)は本発明の第1の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その4）である。

【図7】(a)、(b)は本発明の第1の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その5）である。

【図8】(a)、(b)は本発明の第1の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その6）である。

【図9】(a)、(b)は本発明の第1の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その7）である。

【図10】(a)、(b)は本発明の第1の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その8）である。

【図11】(a)は、本発明の第1の実施の形態の薄膜トランジスタ装置の製造方法の途中工程を示す平面図であり、(b)の上の図は同じく薄膜トランジスタ装置の製造方法の他の途中工程を示す平面図であり、下の図はII-II線に沿う断面図である。

【図12】(a)は、本発明の第1の実施の形態の薄膜トランジスタ装置の製造方法の途中工程を示す平面図であり、(b)の上の図は同じく薄膜トランジスタ装置の製造方法の他の途中工程を示す平面図であり、下の図はIII-III線に沿う断面図である。

【図13】(a)、(b)は本発明の第2の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その1）である。

【図14】(a)、(b)は本発明の第2の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その2）である。

【図15】(a)、(b)は本発明の第2の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その3）である。

【図16】(a)、(b)は本発明の第2の実施の形態

の薄膜トランジスタ装置の製造方法を示す断面図（その4）である。

【図17】（a）、（b）は本発明の第2の実施の形態の薄膜トランジスタ装置の他の製造方法を示す断面図（その1）である。

【図18】（a）、（b）は本発明の第2の実施の形態の薄膜トランジスタ装置の他の製造方法を示す断面図（その2）である。

【図19】（a）、（b）は本発明の第3の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その1）である。

【図20】（a）、（b）は本発明の第3の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その2）である。

【図21】（a）、（b）は本発明の第3の実施の形態の薄膜トランジスタ装置の製造方法を示す断面図（その3）である。

【図22】本発明の第3の実施の形態の薄膜トランジスタ装置の他の製造方法を示す断面図である。

【図23】（a）は、本発明の第3の実施の形態の薄膜トランジスタ装置を示す平面図であり、（b）は同図（a）のIV-IV線に沿う断面図である。

【図24】（a）は、本発明の第3の実施の形態の薄膜トランジスタ装置を示す平面図であり、（b）は同図（a）のVI-VI線に沿う断面図である。

【図25】本発明の第4の実施の形態の薄膜トランジスタ装置を備えた液晶表示装置を示す平面図である。

【図26】（a）は、同じく図25のIX-IX線に沿う断面図であり、（b）は同じく図25のX-X線に沿う断面図である。

【図27】本発明の第5の実施の形態の薄膜トランジスタ装置を備えた液晶表示装置を示す平面図である。

【図28】（a）は、同じく図27のXII-XII線に沿う断面図であり、（b）は同じく図27のXIII-XIII線に沿う断面図である。

【図29】従来例の薄膜トランジスタ装置を示す断面図である。

【図30】従来例の薄膜トランジスタ装置の製造方法における問題点を示す断面図である。

【図31】（a）、（b）は、従来例の薄膜トランジスタ装置の製造方法における他の問題点を示す断面図である。

【図32】（a）は、従来例の薄膜トランジスタ装置の製造方法の途中工程を示す平面図であり、（b）の上の図は同じく薄膜トランジスタ装置の製造方法の他の途中工程を示す平面図であり、下の図はXIV-XIV線に沿う断面図である。

【図33】従来例の他の薄膜トランジスタ装置を示す断面図である。

【図34】（a）、（b）は、従来例の他の薄膜トラン

ジスタ装置の製造方法における問題点を示す断面図である。

【符号の説明】

- 2 1 ガラス基板、

- 2 2 下地絶縁膜、

- 2 2 a、3 2 シリコン窒化膜、

- 2 2 b、3 1 シリコン酸化膜、

- 2 4 ポリシリコン膜（第1の半導体膜）、

- 2 4 a 第1の島状半導体膜、

- 2 4 a a、2 4 a b、2 4 b a、2 4 b b 高濃度不純物領域（オーミックコンタクト領域、ソース／ドレイン領域）、

- 2 4 a c、2 4 b e チャネル領域、

- 2 4 b 第2の島状半導体膜、

- 2 4 b c、2 4 b d 低濃度不純物領域（LDD領域、低濃度ソース／ドレイン領域）、

- 2 5、6 2、8 1、8 1 b 第1のシリコン酸化膜（第1の絶縁膜）、

- 2 5 a 2 8 a、2 8 b ゲート絶縁膜、

- 2 6 ネガティブフォトレジスト膜、

- 2 8、6 4、8 3、8 3 a、8 3 b、8 3 c 第2のシリコン酸化膜（第2の絶縁膜）、

- 2 9 A 1 - N d 膜（導電体膜）、

- 2 9 a、5 4 a、8 2 第1のゲート電極、

- 2 9 b、5 4 b 第2のゲート電極、

- 3 0 a レジストマスク（第1のマスクパターン）、

- 3 0 b レジストマスク（第2のマスクパターン）、

- 3 4 a乃至3 4 d ソース／ドレイン電極、

- 3 6、9 0、1 1 0 画素電極、

- 30 5 1 アモルファスシリコン膜（半導体膜）、

- 5 1 a シリコン酸化膜（半導体膜を酸化してなる絶縁膜、第1のゲート絶縁膜）、

- 5 2 シリコン酸化膜（絶縁膜）、

- 5 2 a シリコン酸化膜のパターン（絶縁膜のパターン）、

- 5 5、8 7 シリコン窒化膜（第1の層間絶縁膜）、

- 5 8 樹脂膜（第2の層間絶縁膜）、

- 6 3 アモルファスシリコン膜（第2の半導体膜）、

- 6 3 a 第1の島状のアモルファスシリコン膜（第2の絶縁膜のパターンを含まない第2の半導体膜）、

- 6 3 b 第2の島状のアモルファスシリコン膜（第2の絶縁膜のパターンを含む第2の半導体膜）、

- 6 4 a 第2のシリコン酸化膜のパターン（第2の絶縁膜のパターン）、

- 8 1 a 第1のシリコン酸化膜（第1のゲート絶縁膜）、

- 8 2 a、8 2 b、8 4 b乃至8 4 e 電界緩和電極、

- 8 2 c、1 1 1 蓄積容量バスライン、

- 8 3 d 容量絶縁膜、

- 8 4 第2のA 1 - N d 膜（第2の導電体膜）、

- 8 4 a 第2のゲート電極(ゲートバスライン)、

8 4 f 電極、

8 5 レジストマスク(マスクパターン)、

8 6 第2のゲート絶縁膜、

8 8 c、108 ソース/ドレイン電極(データバスラ\*)

- \*イン)、

8 8 d ソース/ドレイン電極、

8 9 シリコン窒化膜(第2の層間絶縁膜)、

109 ゲートバスライン。

【図1】

【図2】

【図3】

【図4】

【図5】

【図17】

【図6】

【図7】

【図24】

【図9】

【図8】

【図10】

【図22】

【図11】

【図12】

【図13】

【図14】

【図23】

【図15】

【図29】

【図16】

【図18】

【図19】

【図20】

### 【図2-1】

### 【図30】

【図25】

【図33】

【図26】

【図27】

【図28】

【図31】

【図32】

【図34】

## フロントページの続き

| (51) Int.Cl. <sup>7</sup> | 識別記号                               | F I           | テ-マ-コ-ド <sup>®</sup> (参考)                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H 0 1 L 21/8238           |                                    | H 0 1 L 29/78 | 6 1 7 S                                                                                                                                                                                                                                                                                                                                                                                            |

| 27/08                     | 3 3 1                              |               | 6 2 7 C                                                                                                                                                                                                                                                                                                                                                                                            |

| 27/092                    |                                    |               | 6 1 3 A                                                                                                                                                                                                                                                                                                                                                                                            |

| 29/786                    |                                    |               | 6 1 2 B                                                                                                                                                                                                                                                                                                                                                                                            |

|                           |                                    |               | 6 1 6 A                                                                                                                                                                                                                                                                                                                                                                                            |

|                           |                                    |               | 6 1 7 N                                                                                                                                                                                                                                                                                                                                                                                            |

|                           |                                    |               | 6 1 3 Z                                                                                                                                                                                                                                                                                                                                                                                            |

|                           |                                    | 27/08         | 3 2 1 D                                                                                                                                                                                                                                                                                                                                                                                            |

| (72)発明者 堀田 和重             | 神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内 | F ターム(参考)     | 2H092 GA59 HA04 JA25 JA33 JA35<br>JA36 JA47 JB57 JB69 KA04<br>KA05 KA12 KA16 KA17 KB04<br>MA05 MA08 MA16 MA17 MA30<br>MA42 NA21 NA23                                                                                                                                                                                                                                                               |

| (72)発明者 平野 琢也             | 神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内 |               | 5C094 AA05 AA42 AA43 BA03 BA43<br>CA19 DA15 EA04 EA07 GB10<br>HA08                                                                                                                                                                                                                                                                                                                                 |

| (72)発明者 梁井 健一             | 神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内 |               | 5F048 AA05 AA07 AB10 AC04 BA16<br>BB16 BC06 BC16 BG05<br>5F110 AA12 AA16 AA26 BB02 BB04<br>CC02 DD02 DD13 DD14 DD17<br>EE04 EE06 EE24 EE29 EE44<br>FF02 FF03 FF09 FF12 FF22<br>FF23 FF25 FF30 FF35 GG02<br>GG13 GG25 HJ01 HJ04 HJ13<br>HJ23 HL03 HL04 HL07 HL12<br>HL23 HM15 NN03 NN04 NN23<br>NN24 NN27 NN35 NN36 NN73<br>NN78 PP03 PP35 QQ11 QQ12<br>5G435 AA01 AA17 BB12 CC09 KK05<br>KK09 LL07 |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 薄膜晶体管器件，其制造方法和液晶显示器件                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">JP2003188183A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 公开(公告)日 | 2003-07-04 |

| 申请号            | JP2001388306                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 申请日     | 2001-12-20 |

| [标]申请(专利权)人(译) | 富士通显示技术股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 富士通显示器科技公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |