(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4544251号

(P4544251)

(45) 発行日 平成22年9月15日(2010.9.15)

(24) 登録日 平成22年7月9日(2010.7.9)

(51) Int.CI.

F 1

G02F 1/1343 (2006.01)

G02F 1/1368 (2006.01)G02F 1/1343

G02F 1/1368

請求項の数 12 (全 21 頁)

(21) 出願番号 特願2007-46534 (P2007-46534)

(22) 出願日 平成19年2月27日 (2007.2.27)

(65) 公開番号 特開2008-209686 (P2008-209686A)

(43) 公開日 平成20年9月11日 (2008.9.11)

審査請求日 平成20年3月17日 (2008.3.17)

前置審査

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100098785

弁理士 藤島 洋一郎

(72) 発明者 田中 大直

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 野口 幸治

東京都港区港南1丁目7番1号 ソニー株式会社内

(72) 発明者 金谷 康弘

東京都港区港南1丁目7番1号 ソニー株式会社内

最終頁に続く

(54) 【発明の名称】 液晶表示素子および表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1基板と第2基板との間に挟持された液晶層を備え、当該液晶層に対して電界を印加する共通電極と画素電極とを前記第1基板側に有し、

前記第1基板上にマトリクス状に配置された複数の走査線および複数の信号線と、

前記走査線および前記信号線の交差部に配置された駆動素子と、

前記駆動素子を覆う状態で、前記第1基板上に設けられた第1絶縁膜と、

前記第1絶縁膜上に配置された共通電極と、

前記共通電極を覆う状態で、前記第1絶縁膜上に配置された第2絶縁膜と、

画素領域内に配置され、前記第2絶縁膜および前記第1絶縁膜に設けられたコンタクトホールを介して前記駆動素子と接続された複数のスリットを有する前記画素電極とを備え、

前記共通電極は、前記第1絶縁膜上の前記コンタクトホールの形成領域を除く画素領域と、前記駆動素子のゲート電極を含む前記走査線と、前記信号線とを覆う状態で配置され、

前記画素電極の複数のスリットは、前記信号線と平行に設けられ、

前記画素電極は、当該画素電極の前記信号線側の端部と当該信号線に最も近い位置のスリットとの間の電極部の幅が、他のスリット間の電極部の幅よりも狭くなるように構成されている

液晶表示素子。

10

## 【請求項 2】

前記共通電極は、前記第1絶縁膜上の前記コンタクトホールの形成領域を除く隣接する画素間を含む領域に設けられている

請求項1記載の液晶表示素子。

## 【請求項 3】

前記共通電極は、前記第1絶縁膜上の前記コンタクトホールの形成領域を除く表示領域の全域に設けられている

請求項1記載の液晶表示素子。

## 【請求項 4】

前記第1絶縁膜は、SOG膜または有機絶縁膜で形成されている

10

請求項1記載の液晶表示素子。

## 【請求項 5】

前記第2絶縁膜は、無機絶縁膜で形成されている

請求項4記載の液晶表示素子。

## 【請求項 6】

前記共通電極は、当該共通電極よりも抵抗値の低い材質からなる共通電位線と接続されており、

前記共通電位線は、前記信号線または前記走査線と平面視的に重なる状態で配置されている

請求項1記載の液晶表示素子。

20

## 【請求項 7】

第1基板と第2基板との間に挟持された液晶層を備え、当該液晶層に対して電界を印加する共通電極と画素電極とを前記第1基板側に有する液晶表示素子を有しており、この液晶表示素子によって変調された光を用いて映像表示を行う表示装置であって、

前記第1基板上にマトリクス状に配置された複数の走査線および複数の信号線と、

前記走査線および前記信号線の交差部に配置された駆動素子と、

前記駆動素子を覆う状態で、前記第1基板上に設けられた第1絶縁膜と、

前記第1絶縁膜上に配置された共通電極と、

前記共通電極を覆う状態で、前記第1絶縁膜上に配置された第2絶縁膜と、

画素領域内の前記第2絶縁膜上に配置され、前記第2絶縁膜および前記第1絶縁膜に設けられたコンタクトホールを介して前記駆動素子と接続された複数のスリットを有する前記画素電極とを備え、

前記共通電極は、前記第1絶縁膜上の前記コンタクトホールの形成領域を除く画素領域と、前記駆動素子のゲート電極を含む前記走査線と、前記信号線とを覆う状態で配置され、

前記画素電極の複数のスリットは、前記信号線と平行に設けられ、

前記画素電極は、当該画素電極の前記信号線側の端部と当該信号線に最も近い位置のスリットとの間の電極部の幅が、他のスリット間の電極部の幅よりも狭くなるように構成されている

表示装置。

40

## 【請求項 8】

前記共通電極は、前記第1絶縁膜上の前記コンタクトホールの形成領域を除く隣接する画素間を含む領域に設けられている

請求項7記載の表示装置。

## 【請求項 9】

前記共通電極は、前記第1絶縁膜上の前記コンタクトホールの形成領域を除く表示領域の全域に設けられている

請求項7記載の表示装置。

## 【請求項 10】

前記第1絶縁膜は、SOG膜または有機絶縁膜で形成されている

50

請求項 7 記載の表示装置。

【請求項 1 1】

前記第 2 絶縁膜は、無機絶縁膜で形成されている

請求項 1 0 記載の表示装置。

【請求項 1 2】

前記共通電極は、当該共通電極よりも抵抗値の低い材質からなる共通電位線と接続されており、

前記共通電位線は、前記信号線または前記走査線と平面視的に重なる状態で配置されている

請求項 7 記載の表示装置。

10

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、液晶表示素子および表示装置に関し、特には、フリンジフィールドスイッチング (Fringe field switching ( F F S ) ) モード (別名; In Plane Switching ( I P S ) - P r o モード) の液晶表示素子およびこれを備えた表示装置に関する。

【背景技術】

【0 0 0 2】

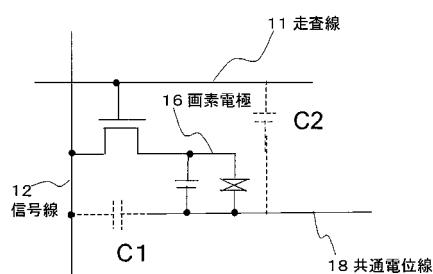

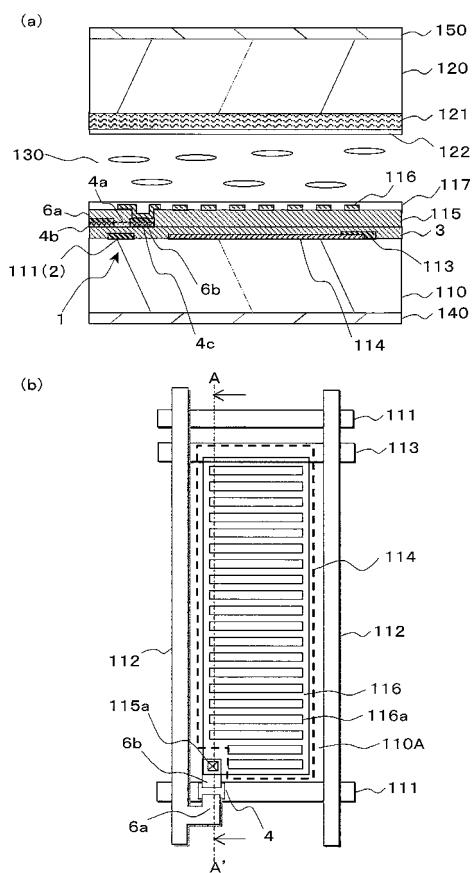

F F S モードの液晶表示装置は、液晶層に対して基板面に略平行な横電界を印加する共通電極と画素電極とが同一基板側に設けられており、この横電界によって液晶素子を駆動して画像表示を行う。ここで、従来の F F S モードの液晶表示装置について、図 1 4 を用いて説明する。ここで、図 1 4 ( a ) の平面図は、図 1 4 ( b ) の A - A ' 断面図を示している。

20

【0 0 0 3】

この図に示す液晶表示装置は、透過型の液晶表示装置であり、液晶表示装置は、第 1 基板 1 1 0 と、この第 1 基板 1 1 0 の素子形成面側に対向配置された第 2 基板 1 2 0 と、これらの第 1 基板 1 1 0 と第 2 基板 1 2 0 との間に狭持された液晶層 1 3 0 とからなる液晶パネルを備えている。また、この液晶パネルにおいて、第 1 基板 1 1 0 および第 2 基板 1 2 0 の外側面には、偏光板 1 4 0 , 1 5 0 が密着状態で設けられており、第 1 基板 1 1 0 側の偏光板 1 4 0 のさらに外側には、透過表示を行うための光源となるバックライト ( 図示省略 ) が設けられている。

30

【0 0 0 4】

このうち第 1 基板 1 1 0 は、ガラス基板のような透明基板からなり、その液晶層 1 3 0 に向かう面上には、マトリクス状に配置された複数の走査線 1 1 1 および複数の信号線 1 1 2 を備えている。また、この走査線 1 1 1 と信号線 1 1 2 の各交差部には、各画素を駆動するための薄膜トランジスタ (Thin Film Transistor ( T F T ) ) 1 からなる駆動素子が設けられており、上記走査線 1 1 1 と信号線 1 1 2 で囲まれた領域が画素領域 1 1 0 A となる。

【0 0 0 5】

また、走査線 1 1 1 と隣接する画素の走査線 1 1 1 との間には、隣接する画素の走査線 1 1 1 側に、走査線 1 1 1 と平行に共通電位線 1 1 3 が設けられている。そして、同一面上の画素領域 1 1 0 A において、T F T 1 の形成領域を除く領域には、上記共通電位線 1 1 3 と一端側が重なる状態で、共通電極 1 1 4 が設けられている。この共通電極 1 1 4 は、走査線 1 1 1 と同一面で設けられるため、走査線 1 1 1 によりその配置が制限される。

40

【0 0 0 6】

また、上記 T F T 1 のゲート電極 2 は、上記走査線 1 1 1 の一部で構成されており、上記走査線 1 1 1 、共通電位線 1 1 3 、共通電極 1 1 4 を覆う状態で、第 1 基板 1 1 0 上には、ゲート絶縁膜 3 が設けられている。さらに、ゲート電極 2 を覆うゲート絶縁膜 3 上には、半導体層 4 がパターン形成されている。

【0 0 0 7】

50

上記半導体層4は、ゲート電極2の直上をチャネル層4aとし、その両側にn型不純物を含むソース領域4bとドレイン領域4cが設けられている。上記ソース領域4b上には、ソース領域4bと接続する状態でソース電極6aが配置され、このソース電極6aは上記信号線112と接続されている。また、ドレイン領域4c上には、ドレイン領域4cと接続する状態でドレイン電極6bが配置されている。以上のようにTFT1が構成される。

#### 【0008】

また、上記TFT1を覆う状態で、ゲート絶縁膜3上には、層間絶縁膜115が設けられている。この層間絶縁膜115には、TFT1のドレイン電極6bに達する状態のコンタクトホール115aが設けられており、層間絶縁膜115上には、このコンタクトホール115aを介してTFT1に接続された複数のスリット116aを有する画素電極116が設けられている。このスリット116aは、走査線111と平行に設けられている。また、上記画素電極116を覆う状態で、層間絶縁膜115上には、配向膜117が配置されている。

#### 【0009】

そして、スリット116aを挟んで設けられた画素電極116の電極部の端部と上記共通電極114との間に電界が生じることで、基板面に略平行な横電界が上記液晶層130に対して印加される。

#### 【0010】

一方、第2基板120はガラス基板のような透明基板からなり、この第2基板120の液晶層130に向かう面には、R(赤)、G(緑)、B(青)各色のカラーフィルタ121と配向膜122がこの順に設けられている。

#### 【0011】

しかし、上述したような構成の液晶表示装置では、第1基板110の同一面上に走査線111と共に共通電極114とが配置されるため、走査線111により共通電極114の形成領域が制限される。よって、開口率が低く、透過率が低いという問題がある。

#### 【0012】

そこで、上記図を用いて説明した液晶表示装置の構成において、スリット116aを有する画素電極116をゲート絶縁膜3上に配置し、共通電極114を層間絶縁膜115上に配置した液晶表示装置の例が報告されている(例えば、特許文献1参照)。

#### 【0013】

また、上記図を用いて説明した液晶表示装置の構成において、ゲート絶縁膜3上に共通電極114を配置した例も報告されている(例えば、特許文献2、3参照)。

【特許文献1】特許第3742837号公報

【特許文献2】特許第3740514号公報

【特許文献3】特許第3742836号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0014】

しかし、特許文献1に記載された液晶表示装置では、共通電極114の配置制限はないものの、スリット116aを有する画素電極116が液晶層130側に配置されていないため、基板面に平行な電界がかかり難く、液晶層130を制御することが出来ず、液晶表示自体が難しい。

#### 【0015】

また、特許文献2、3に記載された液晶表示装置では、信号線112により共通電極114の配置が制限されてしまい、開口率を広く取ることが難しい。

#### 【0016】

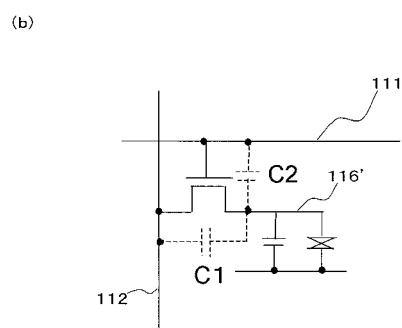

そこで、開口率を向上させるために、図15(a)の平面図に示すように、信号線112側が共通電極114よりも一回り大きくなるように形成した画素電極116'を信号線112と重なる状態で配置することも考えられるが、図15(b)の回路図に示すように

10

20

30

40

50

、信号線 112 と画素電極 116' との間に寄生容量 C1、C2 が発生してしまい、縦クローストークの原因となってしまっていた。

【0017】

そこで、本発明は、寄生容量を抑制した状態で開口率を向上させることが可能な液晶表示素子およびこれを備えた表示装置を提供することを目的とする。

【課題を解決するための手段】

【0018】

本発明の液晶表示素子は、第1基板と第2基板との間に挟持された液晶層を備え、当該液晶層に対して電界を印加する共通電極と画素電極とを前記第1基板側に有し、第1基板上にマトリクス状に配置された複数の走査線および複数の信号線と、走査線および信号線の交差部に配置された駆動素子と、駆動素子を覆う状態で、第1基板上に設けられた第1絶縁膜と、第1絶縁膜上に配置された共通電極と、共通電極を覆う状態で、第1絶縁膜上に配置された第2絶縁膜と、画素領域内に配置され、前記第2絶縁膜および前記第1絶縁膜に設けられたコンタクトホールを介して前記駆動素子と接続された複数のスリットを有する画素電極とを備え、共通電極は、第1絶縁膜上のコンタクトホールの形成領域を除く画素領域と、駆動素子のゲート電極を含む走査線と、信号線とを覆う状態で配置され、画素電極の複数のスリットは、信号線と平行に設けられ、画素電極は、当該画素電極の信号線側の端部と当該信号線に最も近い位置のスリットとの間の電極部の幅が、他のスリット間の電極部の幅よりも狭くなるように構成されていることを特徴としている。

【0019】

本発明の表示装置は、第1基板と第2基板との間に挟持された液晶層を備え、当該液晶層に対して電界を印加する共通電極と画素電極とを第1基板側に有する液晶表示素子を有しており、この液晶表示素子によって変調された光を用いて映像表示を行う表示装置において、第1基板上にマトリクス状に配置された複数の走査線および複数の信号線と、走査線および信号線の交差部に配置された駆動素子と、駆動素子を覆う状態で、第1基板上に設けられた第1絶縁膜と、第1絶縁膜上に配置された共通電極と、共通電極を覆う状態で、第1絶縁膜上に配置された第2絶縁膜と、画素領域内の前記第2絶縁膜上に配置され、前記第2絶縁膜および前記第1絶縁膜に設けられたコンタクトホールを介して前記駆動素子と接続された複数のスリットを有する画素電極とを備え、共通電極は、第1絶縁膜上のコンタクトホールの形成領域を除く画素領域と、駆動素子のゲート電極を含む走査線と、信号線とを覆う状態で配置され、画素電極の複数のスリットは、信号線と平行に設けられ、画素電極は、当該画素電極の信号線側の端部と当該信号線に最も近い位置のスリットとの間の電極部の幅が、他のスリット間の電極部の幅よりも狭くなるように構成されていることを特徴としている。

【0020】

このような液晶表示素子および表示装置によれば、信号線および走査線を覆う第1絶縁膜上に、上記コンタクトホールの形成領域を除く画素領域だけでなく、走査線および信号線の少なくとも一方を覆う状態で、上記共通電極が配置されることから、有効画素領域が増大し、開口率を向上させることができるとなる。また、共通電極が走査線および信号線の少なくとも一方を覆う状態で配置されることで、走査線と画素電極の間または信号線と画素電極の間の寄生容量が抑制される。

【発明の効果】

【0021】

以上説明したように、本発明の液晶表示素子および表示装置によれば、開口率を向上させることができるとため、光透過率が向上し、液晶表示装置のコントラストを向上させることができる。また、走査線と画素電極の間または信号線と画素電極の間の寄生容量を抑制されることで、画素内の信号ノイズを防止することができるため、保持された画素電位が安定し、縦、横クローストークが発生しないことから、液晶表示装置の高画質化が図れる。

【0022】

10

20

30

40

50

また、本実施形態の液晶表示素子およびこれを備えた表示装置は、例えばトランジスタからなる駆動素子に対して、信号線、走査線、画素電極からの電界で半導体層にバックチャンネルを発生させないため、寄生バックチャンネルによる不安定な動作が防止される。

【発明を実施するための最良の形態】

【0023】

以下、本発明の実施の形態について詳細に説明する。

【0024】

(第1実施形態)

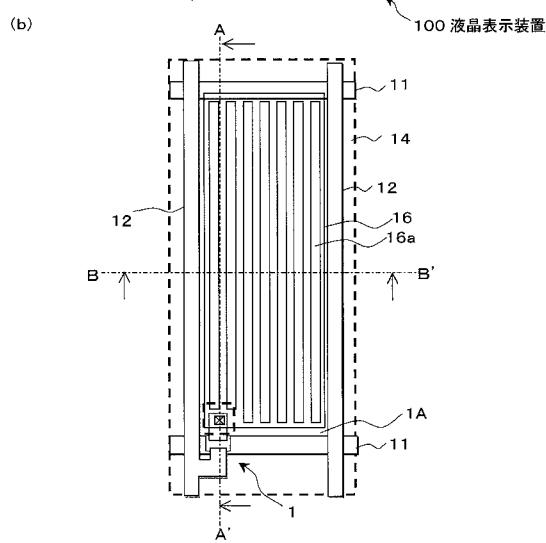

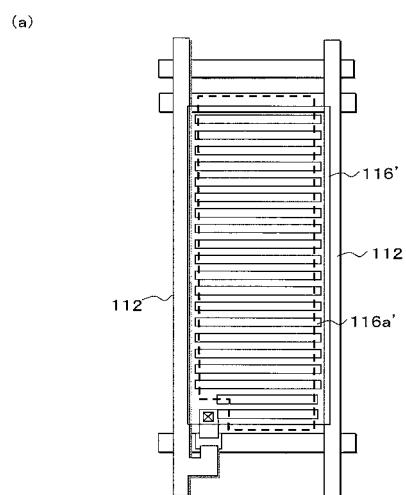

図1(a)は、FFSモードの透過型の液晶表示装置の断面図であり、図1(b)は平面図である。なお、図1(a)は図1(b)のA-A'断面を示す。

10

【0025】

すなわち液晶表示装置100は、第1基板10と、この第1基板10の素子形成面側に対向配置された第2基板20と、これらの第1基板10と第2基板20との間に狭持された液晶層30とからなる液晶パネルを備えている。ここでは、液晶層30が、ネマチック液晶で構成されていることとする。またこの液晶パネルにおいて、第1基板10および第2基板20の外側面には、偏光板40, 50が接着剤(図示省略)を介して密着状態で設けられている。これらの偏光板40, 50は、クロスニコル状態で設けられていることとする。また、第1基板10側の偏光板40のさらに外側には、透過表示を行うための光源となるバックライト(図示省略)が設けられている。

【0026】

20

上記構成のうち、第1基板10を除く構成は一般的な構成であり、例えば表示側基板となる第2基板20はガラス基板のような透明基板からなり、この第2基板20の液晶層30に向かう面には、R(赤)、G(緑)、B(青)各色のカラーフィルタ21と配向膜22とがこの順に設けられている。

【0027】

一方、背面側基板となる第1基板10については、本発明に特徴的な構成を有するため、以下に詳細に説明する。

【0028】

上記第1基板10は、ガラス基板のような透明基板からなり、その液晶層30に向かう面上には、マトリクス状に配置された複数の走査線11および複数の信号線12を備えている。走査線11および信号線12の構成材料としては、アルミニウム(A1)、モリブデン(Mo)、クロム(Cr)、タングステン(W)、チタン(Ti)、鉛(Pb)、またはこれらの複合層/etc, Ti / A1もしくは金属化合物層(MoS<sub>2</sub>, Al<sub>2</sub>Si)が用いられ、ここでは、例えばどちらもアルミニウム(A1)で構成されることとする。ただし、走査線11と信号線12は異なる材料で構成されてもよい。

30

【0029】

また、この走査線11と信号線12の各交差部には、各画素を駆動するための例えばボトムゲート型のTFT1からなる駆動素子が設けられており、上記走査線11と信号線12で囲まれた領域が画素領域1Aとなる。ここで、この画素領域1Aは、例えば信号線12側を長辺、走査線11側を短辺とする平面視矩形状であることとする。

40

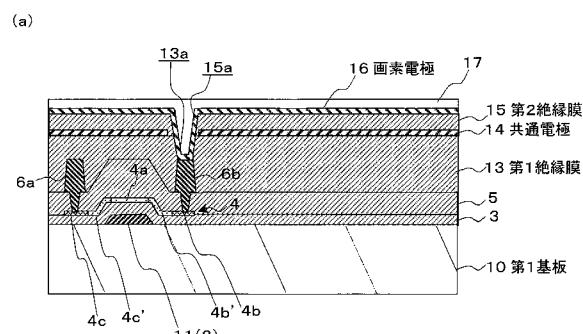

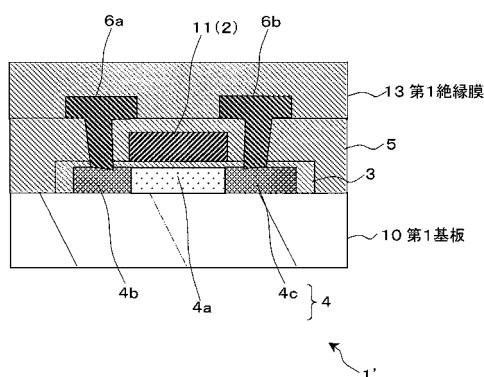

【0030】

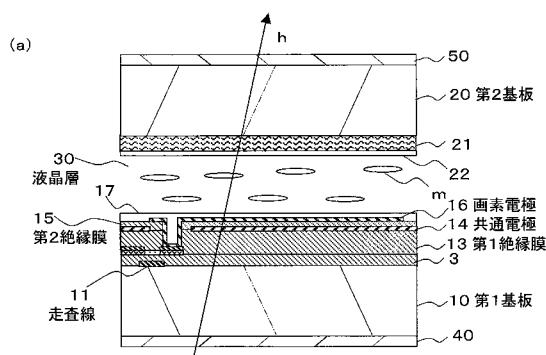

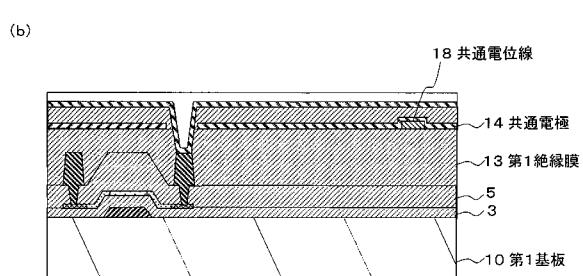

ここで、図2(a)のA-A'断面の要部拡大図に示すように、走査線11の一部で上記TFT1のゲート電極2が構成されており、上記ゲート電極2を含む走査線11を覆う状態で、上記第1基板10上に、ゲート絶縁膜3が設けられている。また、ゲート電極2を覆うゲート絶縁膜3上には、半導体層4がパターン形成されている。

【0031】

ここで、半導体層4は、例えばアモルファスシリコン(a-Si)、ポリシリコン(Poly-Si)または単結晶シリコンで構成されており、ゲート電極2の直上をチャネル層4aとし、その両側に例えばn型不純物を含むソース領域4bとドレイン領域4cが設けられている。また、チャネル層4aとソース・ドレイン領域4b, 4cとの間には、ソ

50

ース・ドレイン領域 4 b、4 c よりも不純物濃度の低い L D D 領域 4 b'、4 c' がそれぞれ設けられている。

#### 【 0 0 3 2 】

また、上記半導体層 4 を覆う状態で、ゲート絶縁膜 3 上には、絶縁層 5 が設けられており、この絶縁層 5 に上記ソース・ドレイン領域 4 b、4 c に達する状態で設けられたコンタクトホールを介して、上記ソース・ドレイン領域 4 b、4 c にソース電極 6 a とドレイン電極 6 b が接続されている。なお、このソース電極 6 a は上記信号線 1 2 と同一層で接続されている。

#### 【 0 0 3 3 】

そして、上記ソース・ドレイン電極 6 a、6 b を覆う状態で、絶縁層 5 上に、第 1 絶縁膜 1 3 が設けられている。ここで、この第 1 絶縁膜 1 3 は、後工程で、第 1 絶縁膜 1 3 上に形成する第 2 絶縁膜を 200 ~ 400 程度の高温で成膜するため、耐熱性を有するだけでなく、その上層に共通電極を形成することから平坦性を有することが好ましい。また、寄生容量を抑制するため、比誘電率が低く、透過率が高く、膜応力が低い膜であることが好ましい。このような特性を有する第 1 絶縁膜 1 3 としては、例えば S O G (Spin On Glass) 膜が特に好適に用いられる。ここで、第 1 絶縁膜 1 3 の膜厚は、走査線 1 1、信号線 1 2、後工程で第 1 絶縁膜 1 3 上に形成する共通電極の負荷容量に大きく影響し、膜厚が厚いほど負荷容量は低減される。このため、第 1 絶縁膜 1 3 の膜厚は、液晶表示素子の駆動特性の許容範囲内で、例えば 0.5 μm ~ 4.0 μm 程度の膜厚で形成されることが好ましい。

#### 【 0 0 3 4 】

なお、第 1 絶縁膜 1 3 としては、上記 S O G 膜の他に、化学的気相成長 (Chemical Vap or Deposition (CVD)) 法により成膜された酸化シリコン (SiO<sub>2</sub>) や窒化シリコン (SiN) 等の無機絶縁膜を用いてもよく、有機絶縁膜を用いてもよい。ただし、第 1 絶縁膜 1 3 としては、CVD 法により成膜した無機絶縁膜を用いるよりも有機絶縁膜を用いた方が、平坦性を有し、比誘電率が低く、塗布法により容易に成膜できるため、好ましい。有機絶縁膜としては、非感光性樹脂と感光性樹脂とが用いられ、非感光性樹脂としては、例えばアクリル樹脂、ポリエステル、塩化ビニル、ポリカーボネート、ポリプロピレン、ポリエチレン、トリアセテート、ポリイミド等、感光性樹脂としては、例えばアクリル樹脂、ポリイミド、住友ベークライト社製スミレジンエクセル C R C - 8 3 0 0 等が挙げられる。ここで、有機絶縁膜材料の物性を表 1 に示す。

10

20

30

【表1】

|                                      | ポリエスチル<br>PET | 塩ビ<br>PVC | ポリカーボネート<br>PC | ポリプロピレン<br>PP | ポリエチレン<br>PE | トリアセテート<br>TAC | ポリイミド<br>(非感光性)<br>PI(文献)<br>東レ・デュポン | ポリイミド<br>(非感光性)<br>住友ベーク | CRC-8300<br>住友ベーク |

|--------------------------------------|---------------|-----------|----------------|---------------|--------------|----------------|--------------------------------------|--------------------------|-------------------|

| 厚さ(μm)                               | 25            | 25        | 25             | 25            | 25           | 25             | 25                                   | 25                       | 12 12             |

| 密度(g/cm <sup>2</sup> )               | 1.40          | 1.40      | 1.20           | 0.91          | 0.92         | 1.30           | 1.43                                 | —                        | —                 |

| 引張強さ(Mpa)                            | 176           | 98        | 98             | 186           | 20           | 118            | 274                                  | 140~350                  | 120 120           |

| 伸び率(%)                               | 120           | 50        | 140            | 110           | 400          | 30             | 9                                    | 57~150                   | 42 65             |

| 端裂抵抗(Kg)                             | 23            | 8         | 10             | 15            | 2            | 3              | 17                                   | —                        | —                 |

| 透湿度(g/m <sup>2</sup> ・24hr)          | 21            | 35        | 60             | 8             | 20           | 700            | 4                                    | —                        | 150 300           |

| 酸素透過率<br>(cc/m <sup>2</sup> ・hr・atm) | 3             | 6         | 300            | 100           | 250          | 110            | 9.3                                  | —                        | —                 |

| 吸水率(%)                               | 0.3           | 0.05      | 0.2            | 0.01          | 0.02         | 4.4            | 1.3                                  | 1.0~2.9                  | 1.9 0.3           |

| 熱膨張係数(ppm/°C)                        | 90            | 118       | 70             | 110           | 170          | —              | 54                                   | 16~60                    | 43 47             |

| 湿度膨張係数<br>(ppm/%RH)                  | —             | —         | —              | —             | —            | —              | —                                    | 16~24                    | —                 |

| 絶縁破壊電圧(KV/mm)                        | 130           | 80        | 1200           | 120           | 80           | 60             | 140                                  | 60~400                   | 260 260           |

| 体積抵抗率(Ω・cm)                          | 1.0E+17       | 1.0E+15   | 1.0E+17        | 1.0E+16       | 1.0E+17      | 1.0E+15        | 1.0E+17                              | 1.0E+15                  | 3.5E+16 1.0E+16   |

| 誘電率                                  | 3.2           | 3.0       | 3.0            | 2.1           | 2.3          | 3.5            | 3.3                                  | —                        | 3.5 2.9           |

| 誘電正接                                 | 0.002         | 0.01      | 0.002          | 0.003         | 0.0005       | 0.02           | 0.001                                | —                        | —                 |

| 融点(°C)                               | 258           | 180       | 240            | 170           | 135          | 290            | —                                    | —                        | —                 |

| 脆化温度                                 | -70           | -45       | -100           | -40           | -60          | —              | —                                    | —                        | —                 |

| 使用可能温度                               | -70~150       | -20~80    | -100~130       | -50~120       | -50~75       | ~120           | —                                    | —                        | —                 |

【0035】

そして、本発明の特徴的な構成として、後述する画素電極と上記TFT1とを接続するためのコンタクトホールの形成領域を除く画素領域1Aと、上記走査線11上および上記信号線12上の少なくとも一方とを覆う状態で、上記第1絶縁膜13上に共通電極14が設けられている。これにより、上記走査線11上および上記信号線12上の少なくとも一方が共通電極14で覆われる分、有効画素領域が増大し、開口率を向上させることが可能となる。この共通電極14は、例えばITO(Indium Tin Oxide)、IZO(Indium Zinc Oxide)等の透明電極膜で形成される。

#### 【0036】

ここでは、上記コンタクトホールの形成領域を除く表示領域の全域に共通電極14が設けられることとする。この場合には、表示領域外でVcom端子に接続された金属配線から共通電極14に電位が供給されるため、さらに開口率を向上させることが可能となる。ここで、コンタクトホールと共通電極14とは、後述するように、コンタクトホール内に配置される画素電極と共通電極とがショートしない程度に離間していればよい。

10

#### 【0037】

なお、本実施形態では、表示領域外でVcom端子に接続された金属配線から共通電極14に電位が供給されることとしたが、図2(b)に示すように、共通電極14と接続する状態で、第1絶縁膜13上に、共通電極14よりも抵抗値の低い材料からなる複数の共通電位線18が、走査線11と平行に配置されていてもよい。この共通電位線18は、例えばAl、Mo、Ti、Pb、W、Cr、またはこれらの複合層(etc, Ti / Al)、もしくは金属化合物層(MoS<sub>2</sub>, AlSi)で形成される。ここでは、共通電位線18が例えば走査線11および信号線12と同じAlで構成されることとするが、上記走査線11、信号線12と共通電位線18が異なる材料で構成されていてもよい。

20

#### 【0038】

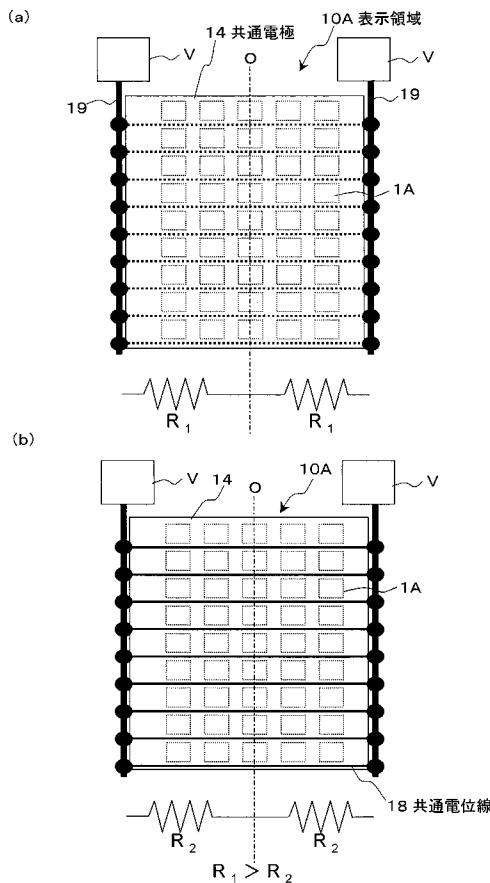

ここで、図3に共通電位線が配置されていない場合(a)と共通電位線が配置された場合(b)について、抵抗値の違いを比較するための模式図を示す。なお、ここでは、Vcom端子Vに接続された金属配線19が、画素領域1Aを配列してなる表示領域10Aの両側に表示領域10Aを挟んで並設され、これらの金属配線19からコンタクトホールを除く表示領域10Aの全域に設けられた共通電極14に電位が供給されることとする。これにより、2本の金属配線19から表示領域10Aの中心部Oに向けて電位が供給される。

30

#### 【0039】

ここで、図3(a)に示すように、共通電位線が配置されておらず、表示領域10A外に配置された金属配線19からITOからなる共通電極14に直接電位が供給される場合には、ITOの抵抗が10~200 / であるため、表示領域10Aの端部から中心部Oまでの共通電極14の抵抗R<sub>1</sub>が大きくなってしまい。このため、表示領域10Aの端部から中心部Oまでの供給電位に時間的なずれが生じ、液晶パネルの表示領域10Aにおける場所による輝度差が生じてしまう。これに対し、図3(b)に示すように、複数の共通電位線18を画素列毎に配置すると、共通電位線18を構成する金属材料は、例えばAlが0.05 / 、Moが0.5 / と、共通電極14を構成するITOよりも抵抗が低いため、表示領域10Aの端部から中心部Oまでの共通電極14の抵抗R<sub>2</sub>は、上記R<sub>1</sub>よりも小さくなる。これにより、表示領域10Aの端部から中心部Oまでの供給電位の時間的なずれが防止され、表示領域10Aの場所による輝度差を改善することが可能となる。

40

#### 【0040】

また、この共通電位線18を、走査線11または信号線12と重なる状態で配置することで、開口率に影響を与えずに共通電位線18を配置することができるため、好ましい。

#### 【0041】

なお、ここでは、2本の金属配線19が表示領域10Aの両側に配置された例について説明したが、1本の金属配線19が表示領域10Aの片側のみに配置されてもよい。ただし、2本の金属配線19が表示領域10Aの両側に配置された方が、表示領域10Aの端

50

部から中心部までの共通電極 14 の抵抗を低くすることができるため、好ましい。

【0042】

また、ここでは、共通電位線 18 を第 1 絶縁膜 13 と共通電極 14 との間に配置したが、共通電位線 18 は、共通電極 14 と接続すればよく、絶縁層 5 上、ゲート絶縁膜 3 上、第 1 基板 10 上のいずれに配置してもよい。

【0043】

ここで、再び図 2 (a) に示すように、共通電極 14 上には、例えば CVD 法により成膜された  $\text{SiO}_2$ 、 $\text{SiN}$  等の無機絶縁膜からなる第 2 絶縁膜 15 が設けられている。この第 2 絶縁膜 15 を CVD 法により成膜された無機絶縁膜として、焼き付き防止や歩留まり向上等の利点がある。なお、第 2 絶縁膜 15 としては、上記以外にも、SOG、有機絶縁膜を用いることが可能である。有機絶縁膜としては、第 1 絶縁膜 13 で例示した材料と同一のものを用いることができる。

10

【0044】

ここで、第 1 絶縁膜 13 と第 2 絶縁膜 15 の組み合わせを、表 2 に示す。

【表 2】

|      | 第 1 絶縁膜   | 第 2 絶縁膜   |

|------|-----------|-----------|

| 方式 1 | SOG       | CVD-無機絶縁膜 |

| 方式 2 | 有機絶縁膜     | CVD-無機絶縁膜 |

| 方式 3 | CVD-無機絶縁膜 | CVD-無機絶縁膜 |

| 方式 4 | SOG       | SOG       |

| 方式 5 | 有機絶縁膜     | SOG       |

| 方式 6 | CVD-無機絶縁膜 | SOG       |

| 方式 7 | SOG       | 有機絶縁膜     |

| 方式 8 | 有機絶縁膜     | 有機絶縁膜     |

| 方式 9 | CVD-無機絶縁膜 | 有機絶縁膜     |

20

30

【0045】

この表に示すように、第 1 絶縁膜 13 と第 2 絶縁膜 15 としては、様々な組み合わせが考えられるが、上述したように、第 1 絶縁膜 13 としては、SOG、有機絶縁膜、また、第 2 絶縁膜 15 としては、CVD 法により成膜された無機絶縁膜（表中、CVD-無機絶縁膜）を用いた方式 1、2 の組み合わせが好ましい。

40

【0046】

上記第 2 絶縁膜 15 および第 1 絶縁膜 13 には、上記ドレイン電極 6b に達するコンタクトホール 15a、13a が連通する状態で、すなわち平面視的に重なる状態で設けられている。そして、このコンタクトホール 15a、13a を介して上記ドレイン電極 6b と接続された状態で、上記第 2 絶縁膜 15 上に、画素電極 16 が設けられている。

【0047】

ここで、上記コンタクトホール 15a、13a は平面視的に重なる状態で配置されるため、同一のエッチングマスクを用いた一度のエッチングにより形成することができる。また、コンタクトホール 15a、13a が平面視的に重ならない場合についても本発明は適用可能であるが、重なる方が開口率を広くとることができるとため、好ましい。

【0048】

50

また、画素電極 16 を覆う状態で、第2絶縁膜 15 上には、配向膜 17 が配置されている。ここで、図 1 (b) に示すように、この画素電極 16 は複数のスリット 16a を有しており、このスリット 16a は、信号線 12 と平行に設けられている。

#### 【0049】

上記画素電極 16 の複数のスリット 16a が信号線 12 と平行に配置されることで、背景技術で図 14 を用いて説明したように、複数のスリットが走査線 11 と平行に配置される場合と比較して、有効画素領域が増大する。これは、上記スリットが走査線 11 と平行である場合には、信号線 12 に近いスリットの短辺側は、この短辺を構成する電極部により液晶分子 m の配向が阻害されるため有効画素領域とならないが、上記スリット 16a が信号線 12 と平行に配置されることで、画素電極 16 の信号線 12 の端部側まで有効画素領域とすることができます。また、この場合でも画素電極 16 のスリット 16a の短辺側は有効画素領域とはならないが、この部分を走査線 11 と重ねることで、開口率を広くとることが可能となるため、好ましい。

#### 【0050】

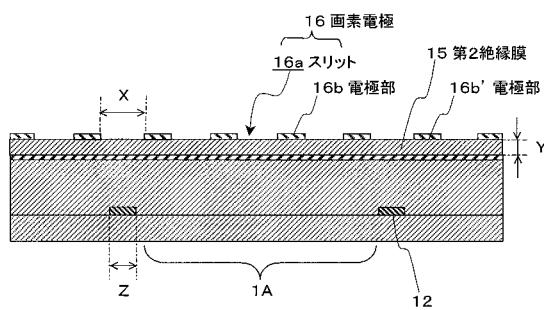

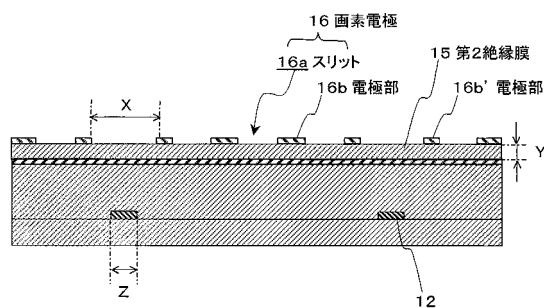

ここで、図 1 (b) の B - B' 断面である図 4 に示すように、各画素を駆動させるための駆動電圧は、画素電極 16 の中央部のスリット 16a の幅と、スリット 16a 間の電極部 16b の幅と第2絶縁膜 15 の膜厚とで規定され、隣接する画素の画素電極 16 間の間隔 X は、近すぎると隣接する画素からの光漏れが生じるため、所定の間隔以上離して配置する方が好ましい。そこで、画素電極 16 の信号線 12 側の端部と信号線 12 に最も近い位置のスリット 16a との間の電極部 16b' の幅を、この電極部 16b' 以外の電極部 16b と異なる幅に調整することで、隣接する画素の画素電極 16 間の間隔 X を制御する。

#### 【0051】

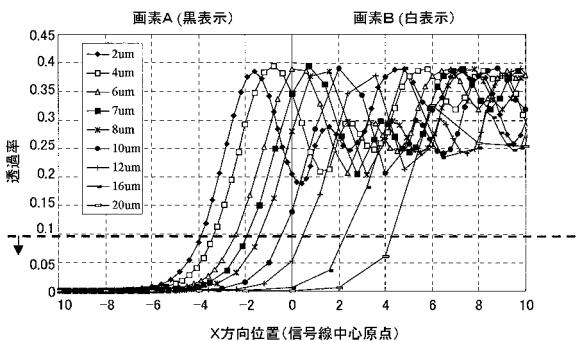

ここで、図 5 に、隣接する黒表示状態の画素 A と白表示状態の画素 B の画素電極 16 間の間隔 X を、2、4、6、7、8、10、12、16、20  $\mu\text{m}$  と変えた場合に、画素 B から画素 A への光漏れを、縦軸を透過率として測定したグラフを示す。このグラフに示すように、隣接画素の画素電極 16 間の間隔 X が小さくなるほど、光漏れが発生することが確認された。ここで、A 1 からなる信号線 12 は、遮光体として機能するため、信号線 12 の線幅 Z を大きくすることで、光漏れを防ぐことが可能となる。

#### 【0052】

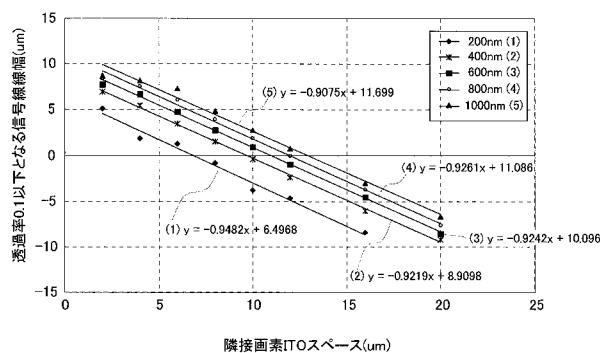

そこで、光漏れが視認されない程度の黒表示画素 A での透過率 0.1 以下をクライティアとし、隣接画素の画素電極 16 間の間隔 X を横軸にとり、第2絶縁膜 15 の膜厚 Y を 200、400、600、800、1000 nm とした場合に、黒表示画素 A の透過率が 0.1 以下となる信号線 12 の線幅 Z をシミュレーションしたグラフを図 6 に示す。このグラフに示すように、上記信号線幅 Z (y) は、画素電極 16 間の間隔 X (x) を変数とした一次関数で示され、傾きは第2絶縁膜 15 の膜厚によらず、ほぼ一定であることが確認された。また、y 切片は第2絶縁膜 15 の膜厚依存性があり、第2絶縁膜 15 の膜厚が厚いほど、遮光体となる信号線の線幅を広くとる必要があることが確認された。

#### 【0053】

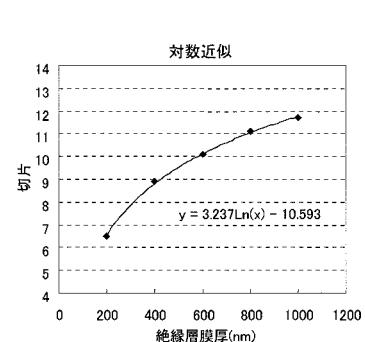

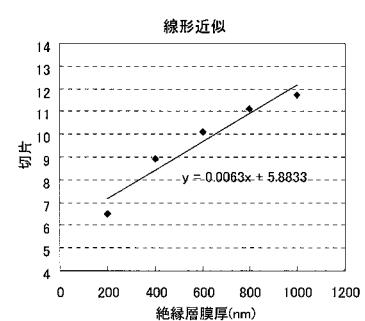

そこで、傾きは第2絶縁膜 15 の膜厚 Y を変えた場合の 5 つの式の平均値とし、切片については近似式を用いて式を一般化した。ここで、図 7 (a) は対数近似、図 7 (b) は線形近似のグラフを示す。

#### 【0054】

そして、上記式から必要な信号線 12 の線幅 Z は、対数近似を用いた場合は下記数式 (1) で表され、線形近似を用いた場合には下記数式 (2) で表される。

#### 【数 1】

$$Z \geq -0.92558X + 3.237 \ln(Y) - 10.593 \quad \cdots \text{数式(1)}$$

## 【数2】

$$Z \geq -0.92558X + 0.0063Y + 5.8833 \quad \cdots \text{式(2)}$$

## 【0055】

上記の2式のどちらかが成り立つように隣接画素の画素電極間の間隔X、第2層間絶縁膜の膜厚Y、遮光物の線幅Zを設定する。特に精度の高い対数近似の式(1)により、各値を設定すると、光漏れを確実に抑制することが可能となる。

## 【0056】

ただし、本実施形態においては、信号線12が遮光体を兼ねており、信号線12の線幅Zおよび第2絶縁膜15の膜厚Yは液晶表示素子の設計上で規定される。ただし、線幅Zが小さい方が、開口率が高くなるため、Zを最低値とし、隣接画素の画素電極間の間隔Xを上記式(1)または式(2)を満たすように設定する。そして、図8に示すように、信号線12に最も近い画素電極16の電極部16b'の幅を他の電極部16bの幅よりも狭くすることで、隣接画素の画素電極間の間隔Xを調整する。

## 【0057】

なお、本実施形態では、信号線12が遮光体として機能することとしたが、信号線12の下層に、どの電極とも電気的に接続されていない遮光体を配置してもよい。

## 【0058】

次に、上記液晶表示装置100の動作について、再び図1を用いて説明する。無電界時においては、液晶層30中の液晶分子mが位相差を生じないように配向されるため、偏光板40を通過したバックライトの光hが、偏光板40に対してクロスニコル状態で配置された偏光板50で吸収され、黒表示となる。

## 【0059】

一方、電界印加時においては、液晶層30を透過することで $\pi/2$ の位相差を生じるように液晶分子mが配向する。これにより、偏光板40を通過したバックライトの光hが、液晶層30を透過することで、 $\pi/2$ の位相差を生じて $90^\circ$ 回転した直線偏光となるため、偏光板50を透過し、白表示となる。

## 【0060】

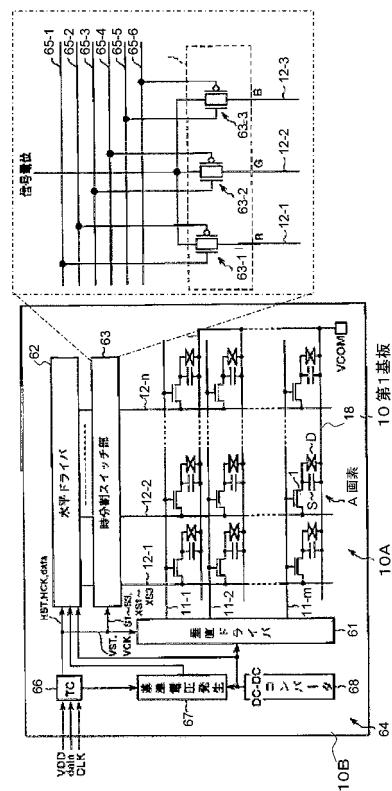

次いで、この液晶表示装置100の回路図を図9に示す。この液晶表示装置100の第1基板10上には、表示領域10Aとその周辺領域10Bとが設定されている。ただし、この場合の回路図は図3(a)、(b)を用いて説明したように、電位を供給する金属配線19が表示領域10A外の一方の周辺領域10Bのみに配置された場合の回路図である。

## 【0061】

上記表示領域10Aは、複数の走査線11と複数の信号線12とがマトリクス状に配線されており、それぞれの交差部に対応して1つの画素Aが設けられた画素アレイ部として構成されている。

## 【0062】

また、上記周辺領域10Bには、表示領域10Aの各画素Aを行単位で順次選択する垂直ドライバ61、行単位で選択された各画素Aに画素信号を書き込む水平ドライバ62、時分割駆動のための時分割スイッチ部63および垂直、水平ドライバ61, 62や時分割スイッチ部63をコントロールする制御系64が実装された構成となっている。

## 【0063】

画素Aの各々は、ゲート電極が走査線11-1~11-mに接続され、ソース電極6aが信号線12-1~12-nに接続されたTFT1と、このTFT1のドレイン電極6bに画素電極16が接続された表示素子Dと、TFT1のドレイン電極6bに一方の電極が接続された補助容量Sとから構成されている。かかる構成の画素Aの各々において、表示素子Dの共通電極は、補助容量Sの他方の電極と共に共通電位線18に接続されている。共通電位線18には、所定の直流電圧もしくは水平同期信号と同期した矩形電圧が共通電位電圧V

10

20

30

40

50

COMとして与えられる。

【0064】

ここで、この液晶表示装置100は、時分割駆動法により駆動される。時分割駆動法とは、表示領域10Aの互いに隣り合う複数本の信号線12を1単位（ブロック）として分割し、この1分割ブロック内の複数本の信号線12に与える信号電圧を時系列で水平ドライバ62の各出力端子から出力する一方、複数本の信号線12を1単位として時分割スイッチ部63を設け、この時分割スイッチ部63によって水平ドライバ62から出力される時系列の信号電圧を時分割でサンプリングして複数本の信号ラインに順次与える駆動方法である。

【0065】

上記時分割スイッチ部63は、水平ドライバ62から出力される時系列の信号電圧を時分割でサンプリングするアナログスイッチ（トランスマッシュョンスイッチ）によって構成されている。この時分割スイッチ部63の具体的な構成例を示す。なお、この時分割スイッチ部63は、水平ドライバ62の各出力に対して1個ずつ設けられるものである。また、ここでは、R（赤）、G（緑）、B（青）に対応して3時分割駆動を行う場合を例にとつて示している。

【0066】

この時分割スイッチ部63は、PchMOSトランジスタおよびNchMOSトランジスタが並列に接続されてなるCMOS構成のアナログスイッチ63-1, 63-2, 63-3によって構成されている。なお、本例では、アナログスイッチ63-1, 63-2, 63-3として、CMOS構成のものを用いるとしたが、PMOSあるいはNMOS構成のものを用いることも可能である。

【0067】

この時分割スイッチ部63において、3個のアナログスイッチ63-1, 63-2, 63-3の各入力端が共通に接続され、各出力端が3本の信号ライン12-1, 12-2, 12-3の各一端にそれぞれ接続されている。そして、これらアナログスイッチ63-1, 63-2, 63-3の各入力端には、水平ドライバ62から時系列で出力される信号電位が与えられる。

【0068】

ここで、本発明における共通電極14をアナログスイッチ63-1, 63-2, 63-3の上部にも配置することにより、ボトムゲート構造のTFT1により形成されたアナログスイッチ63-1, 63-2, 63-3は、近傍のゲート選択信号、隣接の信号線12-1, 12-2, 12-3各々からの寄生容量による電位変動の影響を削除することができる。なお、これは、アナログスイッチ63-1, 63-2, 63-3がトップゲート構造で形成された場合に關しても同様な効果をもつのは明らかである。

【0069】

また、1個のアナログスイッチにつき2本ずつ、合計6本の制御ライン65-1～65-6が配線されている。そして、アナログスイッチ63-1の2つ制御入力端（即ち、CMOSトランジスタの各ゲート）が制御ライン65-1, 65-2に、アナログスイッチ63-2の2つ制御入力端が制御ライン65-3, 65-4に、アナログスイッチ63-3の2つ制御入端が制御ライン65-5, 65-6にそれぞれ接続されている。

【0070】

6本の制御ライン65-1～65-6に対して、3個のアナログスイッチ63-1, 63-2, 63-3を順に選択するためのゲート選択信号S1～S3, XS1～XS3が、後述するタイミングコントローラ（TC）66から与えられる。ただし、ゲート選択信号XS1～XS3は、ゲート選択信号S1～S3の反転信号である。

【0071】

ゲート選択信号S1～S3, XS1～XS3は、水平ドライバ62から出力される時系列の信号電位に同期して、3個のアナログスイッチ63-1, 63-2, 63-3を順次オンさせる。これにより、アナログスイッチ63-1, 63-2, 63-3は、水平ドライバ62から出力される時系列の信号電位を、1H期間に3時分割でサンプリングしつつ、対応する信

10

20

30

40

50

号ライン 1 2 -1 , 1 2 -2 , 1 2 -3 にそれぞれ供給する。

【 0 0 7 2 】

垂直ドライバ 6 1 、水平ドライバ 6 2 および時分割スイッチ部 6 3 を制御する制御系 6 4 は、タイミングコントローラ ( T C ) 6 6 、基準電圧発生源 6 7 および D C - D C コンバータ 6 8 などを有し、これら回路が上記第 1 基板の周辺領域 1 0 B 上に垂直ドライバ 6 1 、水平ドライバ 6 2 および時分割スイッチ部 6 3 と共に実装された構成となっている。

【 0 0 7 3 】

この制御系 6 4 において、タイミングコントローラ 6 6 には、例えば、外部の電源部 ( 図示せず ) から電源電圧 V D D が、外部の C P U ( 図示省略 ) からデジタル画像データ data が、外部のクロック発生器 ( 図示省略 ) からクロック C L K がそれぞれ T C P ( 図示省略 ) を通して入力される。

【 0 0 7 4 】

ここで、本実施形態の液晶表示装置の各画素 A の回路図を図 1 0 に示すと、共通電極 1 4 がコンタクトホール形成領域を除く表示領域 1 0 A の全域に設けられることで、信号線 1 2 と画素電極 1 6 との間および走査線 1 1 と画素電極 1 6 との間に発生する寄生容量 C 1 、 C 2 が共通電極 1 4 に結合し、画素電位への影響が抑制される。

【 0 0 7 5 】

このような液晶表示素子およびこれを備えた表示装置によれば、上記共通電極 1 4 が、第 1 絶縁膜 1 3 上に、コンタクトホール 1 3 a 、 1 5 a の形成領域を除く画素領域 1 A だけでなく、走査線 1 1 および信号線 1 2 の少なくとも一方を覆う状態で配置されることから、有効画素領域を増大させることができることが可能となり、開口率を向上させることができることが可能となる。したがって、光透過率が向上し、コントラストを向上させることができる。

【 0 0 7 6 】

また、共通電極 1 4 が走査線 1 1 および信号線 1 2 の少なくとも一方を覆う状態で配置されることで、信号線 1 2 と画素電極 1 6 の間または走査線 1 1 と画素電極 1 6 の間の寄生容量が抑制される。特に、本実施形態の液晶表示装置によれば、コンタクトホール 1 3 a 、 1 5 a の形成領域以外の表示領域 1 0 A の全域が共通電極 1 4 で覆われている。これにより、画素内の信号ノイズを確実に防止することができるため、保持された画素電位が安定し、縦、横クローストロークが発生しないことから、液晶表示装置の高画質化が図れる。

【 0 0 7 7 】

また、本実施形態の液晶表示素子およびこれを備えた表示装置は、 a - S i 、 p o l y - S i 、または crystal - S i を半導体層 4 として使用するボトムゲート型の T F T 1 に對して、信号線 1 1 、走査線 1 2 、画素電極 1 6 からの電界で半導体層にバックチャンネルを発生させないため、寄生バックチャンネルによる不安定な動作がない。これは、トップゲート T F T に関しても同様な効果をもつのは明らかである。

【 0 0 7 8 】

なお、 T F T 1 がトップゲート型のトランジスタである場合には、図 1 1 に示すように、第 1 基板 1 0 上に、 a - S i 、 P o l y - S i または c r y s t a l - S i からなる半導体層 4 がパターン形成され、この半導体層 4 上にゲート絶縁膜 3 を介して一部がゲート電極 2 として機能する一方向に延設された走査線 1 1 がパターン形成される。この場合には、ゲート電極 2 をマスクとして n 型不純物がイオン注入されるため、ゲート電極 2 直下の半導体層 4 がチャネル層 4 a となり、その両側の半導体層 4 がソース領域 4 b とドレイン領域 4 c になる。また、 ゲート電極 2 およびゲート絶縁膜 3 上には、絶縁層 5 が設けられており、絶縁層 5 に設けられたコンタクトホール 5 a 、 5 b を介して、ソース・ドレイン領域 4 b 、 4 c とソース・ドレイン電極 6 a 、 6 b が接続される。そして、ソース・ドレイン電極 6 a 、 6 b を覆う状態で第 1 絶縁膜 1 3 が設けられている。

【 0 0 7 9 】

( 变形例 1 )

なお、上述した第 1 実施形態では、画素電極 1 6 が矩形状であり、矩形状のスリット 1

10

20

30

40

50

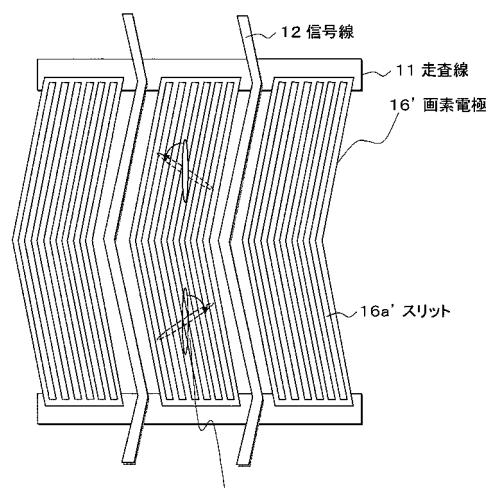

6 a が設けられた例について説明したが、図 1 2 の平面図に示すように、画素電極 1 6 ' が平面視的にその長手方向の中央部で曲折した形状、すなわち「くの字状（V字状）」に曲折した形状のマルチドメイン構造であってもよい。この場合には、画素電極 1 6 ' のスリット 1 6 a ' も画素電極 1 6 ' の外形状に合わせて「くの字状（V字状）」に開口される。画素領域 1 A 内で、電界方向が異なる 2 つの領域が存在するため、液晶分子 m の配向方向 2 方向となり、視野角特性を大幅に改善することができる。この場合には、信号線 1 2 も上記画素電極 1 6 ' の曲折に合わせてジグザグ状に配置される。

#### 【 0 0 8 0 】

ここで、「くの字状（V字状）」に開口されるスリット 1 6 a ' は、上述した電界方向が異なる 2 つの領域において、電界印加時の上記液晶分子 m の長軸の配向方向を 90° とした場合に、上記液晶分子 m の長軸に対するスリット 1 6 a ' の長手方向の角度の範囲が 45° 以上 90° 未満、好ましくは 65° 以上 89° 以下となるようにする。

#### 【 0 0 8 1 】

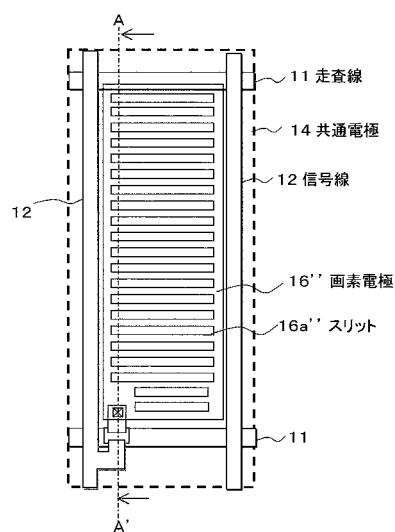

##### （変形例 2 ）

また、図 1 3 の平面図に示すように、画素電極 1 6 " の複数のスリット 1 6 a " は、走査線 1 1 と略平行に配置されていてもよい。ここで、略平行とは、走査線 1 1 に対して 0° から 45° 程度までの傾きを有することを指す。この場合であっても、共通電極 1 4 がコンタクトホール 1 3 a 、 1 5 a の形成領域を除く表示領域 1 0 A の全域に配置されることで、開口率が向上し、信号線 1 2 と画素電極 1 6 " 、走査線 1 1 と画素電極 1 6 " の寄生容量が抑制される。ただし、開口率は、第 1 実施形態で説明したように、画素電極 1 6 のスリット 1 6 a を信号線 1 2 と平行に配置した方が、広くなるため、好ましい。

#### 【 0 0 8 2 】

このような液晶表示装置であっても、開口率が広くなることで、光透過率が向上し、コントラストを向上させることができる。また、走査線と画素電極の間または信号線と画素電極の間の寄生容量が抑制されることで、画素内の信号ノイズを防止することができるため、保持された画素電位が安定し、縦、横クローストークが発生しないことから、液晶表示装置の高画質化が図れる。

#### 【 0 0 8 3 】

なお、この変形例 2 の構成においても、図 2 ( b ) を用いて説明したように、上記共通電極 1 4 と接続される共通電位線を配置してもよく、上記変形例 1 で説明したマルチドメイン構造を適用してもよい。

#### 【 0 0 8 4 】

なお、上記実施形態および変形例では、透過型の液晶表示装置の例をとり説明したが、本発明はこれに限定されることなく、反射型または反射領域と透過領域を有する半透過型の FFS モードの液晶表示装置であっても、適用可能である。

#### 【 実施例 】

#### 【 0 0 8 5 】

さらに、本発明の具体的な実施例について説明する。

#### 【 0 0 8 6 】

##### （実施例 1 ）

上記第 1 実施形態で図 1 を用いて説明した構成と同様に、第 1 絶縁膜 1 3 上のコンタクトホールの形成領域以外の表示領域の全域に、共通電極 1 4 を配置し、画素電極 1 6 の複数のスリットを信号線 1 2 と平行に配置した液晶表示装置を製造した。

#### 【 0 0 8 7 】

##### （実施例 2 ）

また、上記変形例 2 で図 1 3 を用いて説明した構成と同様に、第 1 絶縁膜 1 3 上のコンタクトホールの形成領域以外の表示領域の全域に、共通電極 1 4 を配置し、画素電極 1 6 " の複数のスリット 1 6 a " を走査線 1 1 と平行に配置した液晶表示装置を製造した。

#### 【 0 0 8 8 】

##### （比較例 1 ）

10

20

30

40

50

一方、上記実施例1、2に対する比較例として、背景技術で図14を用いて説明した構成と同様に、共通電極114を第1基板110上のTFT1の形成領域を除く画素領域に配置し、画素電極116の複数のスリット116aを走査線111と平行に配置した液晶表示装置を製造した。

【0089】

そして、上記実施例1、2および比較例1の液晶表示装置について、開口率および相対透過率を比較した。相対透過率は入射光を100%とした場合の取り出し光の割合であり、開口率に比例する値である。その結果を表3に示す。

【表3】

10

|      | 開口率 (%) | 相対透過率 (%) |

|------|---------|-----------|

| 実施例1 | 132     | 7.0       |

| 実施例2 | 120     | 6.4       |

| 比較例1 | 100     | 5.3       |

【0090】

上記表に示すように、比較例1の液晶表示装置と比較して、実施例1、2の液晶表示装置の開口率は高くなり、比較例1の開口率を100%とした場合の開口率は、実施例1で132%、実施例2で120%を示すことが確認された。また、比較例1の相対透過率が5.3%であるのに対し、実施例1の相対透過率は7.0%、実施例2の相対透過率は6.4%であり、開口率の増加にともない、相対透過率も高くなることが確認された。

20

【図面の簡単な説明】

【0091】

【図1】本発明の実施形態に係る液晶表示装置の構成を示す断面図(a)および平面図(b)である。

【図2】本発明の実施形態に係る液晶表示装置の第1基板のA-A'断面の要部拡大図である。

30

【図3】本発明の実施形態に係る液晶表示装置の共通電位線が配置されていない場合(a)と配置されている場合(b)の模式図である。

【図4】本発明の実施形態に係る液晶表示装置の第1基板のB-B'断面の要部拡大図である(その1)。

【図5】本発明の実施形態に係る隣接画素の画素電極の間隔を変化させた場合の光漏れを示すグラフである。

【図6】本発明の実施形態に係る隣接画素の画素電極の間隔を変化させた場合の信号線の線幅と、第2絶縁膜の膜厚の関係を示すグラフである。

【図7】本発明の実施形態に係る第2絶縁膜の膜厚を変化させた場合の信号線幅を画素電極間の間隔を変数として1次関数で表した場合のy切片に関する対数近似のグラフ(a)と線形近似のグラフ(b)である。

40

【図8】本発明の実施形態に係る液晶表示装置の第1基板のB-B'断面の要部拡大図である(その2)。

【図9】本発明の実施形態に係る回路図である。

【図10】本発明の実施形態に係る1画素内の回路図である。

【図11】本発明の実施形態に係る別のトランジスタを示す構成図である。

【図12】本発明の実施形態の変形例1の平面図である。

【図13】本発明の実施形態の変形例2の平面図である。

【図14】従来の液晶表示装置の構成を説明するための断面図(a)および平面図(b)である。

50

【図15】従来の液晶表示装置の課題を示す平面図および回路図である。

【符号の説明】

【0092】

100...液晶表示装置、10...第1基板、13...第1絶縁膜、14...共通電極、15...第2絶縁膜、16, 16'...画素電極、16a, 16a'...スリット、16b, 16b'...電極部、20...第2基板、30...液晶層

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

(b)

【図8】

【図9】

【 义 1 0 】

【図 1 2】

### 【図 1 1】

【図13】

【図14】

【図15】

---

フロントページの続き

(72)発明者 中嶋 大貴

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 野津 大輔

東京都港区港南1丁目7番1号 ソニー株式会社内

(72)発明者 猪野 益充

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 廣田 かおり

(56)参考文献 特開2001-235765(JP,A)

特開2007-018015(JP,A)

特開2006-317516(JP,A)

特開2006-227661(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 02 F 1 / 1343

G 02 F 1 / 1368

|                |                                                                                                                                                                                                                                                                                                                                                      |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置和显示装置                                                                                                                                                                                                                                                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">JP4544251B2</a>                                                                                                                                                                                                                                                                                                                          | 公开(公告)日 | 2010-09-15 |

| 申请号            | JP2007046534                                                                                                                                                                                                                                                                                                                                         | 申请日     | 2007-02-27 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                                                                                                                                                                                                                                                                 |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                                                                                                                                                                                                                                                                                 |         |            |

| [标]发明人         | 田中大直<br>野口幸治<br>金谷康弘<br>中嶋大貴<br>野津大輔<br>猪野益充                                                                                                                                                                                                                                                                                                         |         |            |

| 发明人            | 田中 大直<br>野口 幸治<br>金谷 康弘<br>中嶋 大貴<br>野津 大輔<br>猪野 益充                                                                                                                                                                                                                                                                                                   |         |            |

| IPC分类号         | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                |         |            |

| CPC分类号         | G02F1/136213 G02F1/134363 G02F2201/40                                                                                                                                                                                                                                                                                                                |         |            |

| FI分类号          | G02F1/1343 G02F1/1368                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 2H092/GA14 2H092/GA15 2H092/GA29 2H092/JA26 2H092/JA46 2H092/JB05 2H092/JB06 2H092/KB22 2H092/KB25 2H092/NA07 2H092/NA19 2H092/NA23 2H092/PA08 2H092/QA06 2H192/AA24 2H192/BB13 2H192/BB81 2H192/BC32 2H192/CB02 2H192/CB05 2H192/CC04 2H192/CC55 2H192/DA12 2H192/DA52 2H192/DA73 2H192/DA74 2H192/EA04 2H192/EA17 2H192/EA67 2H192/GA03 2H192/JA33 |         |            |

| 其他公开文献         | JP2008209686A                                                                                                                                                                                                                                                                                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                            |         |            |

## 摘要(译)

提供一种能够在抑制寄生电容的状态下提高开口率的液晶显示元件和显示装置。在第一基板上以矩阵排列的多条扫描线和多条信号线，在扫描线和信号线的交叉处布置的TFT，以及覆盖TFT的TFT在覆盖设置在第一基板10上的第一绝缘膜13的状态下，在第一绝缘膜13上设置在第一绝缘膜13上的公共电极14和公共电极14的第二绝缘膜15被设置在像素区域1A中的第二绝缘膜15，这是通过在第二绝缘膜15中的接触孔和第一绝缘膜连接到所述TFT1多个13具有狭缝16a中，共用电极14，其覆盖像素区域10A除了接触孔在第一绝缘膜13形成区域，和扫描线11中的至少一个和信号线12的像素电极16的状态液晶显示元件和显示装置按此顺序排列。

## 点域1