(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-233869

(P2008-233869A)

(43) 公開日 平成20年10月2日(2008.10.2)

(51) Int.Cl.

G02F 1/1345 (2006.01)

G02F 1/1368 (2006.01)

F 1

G02F 1/1345

G02F 1/1368

テーマコード(参考)

2 H 0 9 2

審査請求 有 請求項の数 16 O L (全 30 頁)

(21) 出願番号 特願2007-341171 (P2007-341171)

(22) 出願日 平成19年12月28日 (2007.12.28)

(31) 優先権主張番号 10-2007-0026070

(32) 優先日 平成19年3月16日 (2007.3.16)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 10-2007-0030323

(32) 優先日 平成19年3月28日 (2007.3.28)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 10-2007-0030332

(32) 優先日 平成19年3月28日 (2007.3.28)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 10-2007-0030333

(32) 優先日 平成19年3月28日 (2007.3.28)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル, ヨンドゥンパーク, ヨ

イドードン 20

(74) 代理人 100110423

弁理士 曾我 道治

(74) 代理人 100084010

弁理士 古川 秀利

(74) 代理人 100094695

弁理士 鈴木 憲七

(74) 代理人 100111648

弁理士 梶並 順

(74) 代理人 100147566

弁理士 上田 俊一

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】コントロールP C Bを簡素化した液晶表示装置を提供する。

【解決手段】液晶表示装置は、第1及び第2データライン群、該第1及び第2データライン群と交差する複数のゲートライン、及びマトリクス状に配置された複数の液晶セルを含む液晶表示パネル30と、前記第1データライン群にデータを供給する第1データI Cに接続された第1ソースP C B 41 Aと、前記第2データライン群にデータを供給する第2データI Cに接続された第2ソースP C B 41 Bと、シングルポートを介して前記第1及び第2データI Cにビデオデータを出力するとともに、前記シングルポートを介して前記第1及び第2データI Cを制御するためのタイミング制御信号を出力するタイミングコントローラー31とを備える。

【選択図】図13

**【特許請求の範囲】****【請求項 1】**

第1及び第2データライン群、該第1及び第2データライン群と交差する複数のゲートライン、及びマトリクス状に配置された複数の液晶セルを含む液晶表示パネルと、

前記第1データライン群にデータを供給する第1データI Cに接続された第1ソースP C Bと、

前記第2データライン群にデータを供給する第2データI Cに接続された第2ソースP C Bと、

シングルポートを介して前記第1及び第2データI Cにビデオデータを出力するとともに、前記シングルポートを介して前記第1及び第2データI Cを制御するためのタイミング制御信号を出力するタイミングコントローラーと

を備えることを特徴とする液晶表示装置。

**【請求項 2】**

前記タイミングコントローラーのシングルポートを前記第1及び第2ソースP C Bのうち、少なくともいずれか1つに接続して、前記タイミングコントローラーからのビデオデータとタイミング制御信号とを前記第1及び第2ソースP C Bのうち、少なくともいずれか1つに送信する第1接続ケーブルを備えることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 3】**

前記タイミングコントローラーのシングルポートを前記第1ソースP C Bに接続して、前記タイミングコントローラーからのビデオデータとタイミング制御信号とを前記第1ソースP C Bに送信する第1接続ケーブルと、

前記タイミングコントローラーのシングルポートを前記第2ソースP C Bに接続して、前記タイミングコントローラーからのビデオデータとタイミング制御信号とを前記第2ソースP C Bに送信する第2接続ケーブルと

を備えることを特徴とする請求項1に記載の液晶表示装置。

**【請求項 4】**

前記タイミングコントローラーが実装され、前記タイミングコントローラーのシングルポートを前記第1及び第2接続ケーブルに接続して、前記タイミングコントローラーからのデータとタイミング制御信号とを前記第1及び第2接続ケーブルに送信する接続配線が形成されたコントロールP C Bをさらに備えることを特徴とする請求項3に記載の液晶表示装置。

**【請求項 5】**

前記接続配線と前記第1及び第2接続ケーブルは、前記第1データI Cのうちのいずれか1つと第2データI Cのうちのいずれか1つとの間でキャリー信号を送信することを特徴とする請求項4に記載の液晶表示装置。

**【請求項 6】**

前記第1接続ケーブルは、前記タイミングコントローラーのシングルポートを前記第1及び第2ソースP C Bに接続して、前記タイミングコントローラーからのビデオデータとタイミング制御信号とを前記第1及び第2ソースP C Bに送信することを特徴とする請求項2に記載の液晶表示装置。

**【請求項 7】**

前記第1接続ケーブルは、前記第1データI Cのうちのいずれか1つと第2データI Cのうちのいずれか1つとの間でキャリー信号を送信することを特徴とする請求項6に記載の液晶表示装置。

**【請求項 8】**

前記第1接続ケーブルは、前記タイミングコントローラーのシングルポートを前記第1及び第2ソースP C Bのうちのいずれか1つにのみ接続して、前記タイミングコントローラーからのビデオデータとタイミング制御信号を前記第1及び第2ソースP C Bのうちのいずれか1つに送信し、

10

20

30

40

50

前記液晶表示パネルは、前記第1ソースP C Bを前記第2ソースP C Bに接続するL O G配線を備え、前記L O G配線は、前記第1及び第2ソースP C Bのうちのいずれか1つからのビデオデータ、タイミング制御信号及び駆動電圧を他のソースP C Bに送信することを特徴とする請求項2に記載の液晶表示装置。

【請求項9】

前記L O G配線は、前記第1データI Cのうちのいずれか1つと前記第2データI Cのうちのいずれか1つとの間でキャリー信号を送信することを特徴とする請求項6に記載の液晶表示装置。

【請求項10】

外部ソースから入力データを受けるインターフェース回路、前記インターフェース回路からの入力データに基づいて、前記タイミングコントローラーにデジタルビデオデータとタイミング信号を供給するグラフィック処理回路と、

前記液晶表示パネルを駆動するための駆動電圧を発生する電圧源を含むシステムボードと

をさらに備えることを特徴とする請求項1に記載の液晶表示装置。

【請求項11】

前記システムボードは、前記タイミングコントローラーに前記タイミング制御信号の波形選択情報を供給するメモリをさらに備えることを特徴とする請求項10に記載の液晶表示装置。

【請求項12】

前記第1データI Cは、前記駆動電圧を分圧して、ガンマ補償電圧を発生する抵抗列と、

前記抵抗列に並列接続した補償抵抗と

を備えることを特徴とする請求項8に記載の液晶表示装置。

【請求項13】

前記第1データI Cが実装され、第1ダミー配線が形成される第1C O Fと、

前記第2データI Cが実装され、第2ダミー配線が形成される第2C O Fと

を備え、

前記第1ダミー配線は、前記第1ソースP C Bを前記L O G配線の一方に接続して、前記第1ソースP C Bからのビデオデータ、タイミング制御信号及び駆動電圧を前記L O G配線に送信し、前記第2ダミー配線は、前記第2ソースP C Bを前記L O G配線の他方に接続して、前記第2ソースP C Bからのビデオデータ、タイミング制御信号及び駆動電圧を前記L O G配線に送信し、

前記ダミー配線のうち、前記駆動電圧が送信されるダミー配線の線幅が、前記タイミング制御信号が送信されるダミー配線の線幅より広く、前記L O G配線のうち、前記駆動電圧が送信されるダミー配線に接続されたL O G配線の線幅が、前記タイミング制御信号が送信されるダミー配線に接続されたL O G配線の線幅より広いことを特徴とする請求項8に記載の液晶表示装置。

【請求項14】

前記第1データI Cの信号入力端子に接続された第1抵抗と、

前記第2データI Cの信号入力端子に接続された第2抵抗と

をさらに備え、

前記抵抗の抵抗値をR<sub>T A</sub>とするとき、その抵抗値は、

【数1】

$$R_{TA} = \frac{R_{TB}(R_{EQ} + R_{LOG})}{R_{EQ}}$$

であり、ここで、R<sub>T B</sub>は、前記第2ソースP C Bに接続された前記データI Cの信号入力端子に接続された抵抗、R<sub>E Q</sub>は、前記接続部の抵抗、R<sub>L O G</sub>は、前記L O G配線の抵抗をそれぞれ意味することを特徴とする請求項8に記載の液晶表示装置。

10

20

30

40

50

## 【請求項 15】

第1及び第2データライン群、前記第1及び第2データライン群と交差する複数のゲートライン、及びマトリクス状に配置された複数の液晶セルを含む液晶表示パネルと、

前記第1データライン群にデータを供給する第1データI Cに接続された第1ソースP C Bと、

前記第2データライン群にデータを供給する第2データI Cに接続された第2ソースP C Bと、

シングルポートを介して前記第1及び第2データI Cにビデオデータを出力するとともに、前記シングルポートを介して前記第1及び第2データI Cを制御するためのタイミング制御信号を出力するタイミングコントローラーと

を備え、

前記タイミングコントローラーは、第1周波数で入力データを受けて前記第1周波数より高い第2周波数で前記ビデオデータを出力することを特徴とする液晶表示装置。

## 【請求項 16】

前記タイミングコントローラーは、

前記第1周波数で入力される入力データを奇数の画素データと偶数の画素データとに分離し、該分離されたデータを前記第1周波数の1/2周波数で出力する2ポート拡張部と、

前記2ポート拡張部からのデータを変調して、前記シングルポートを介して出力されるデータのスイング幅を減らし、前記第1周波数と対比して2倍高い前記第2周波数で前記変調されたデータを出力するデータ変調部と

を備えることを特徴とする請求項15に記載の液晶表示装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、液晶表示装置に関し、特に、コントロールプリント回路ボード( Printed Circuit Board : 以下、P C Bと略す)を簡素化した液晶表示装置に関する。

## 【背景技術】

## 【0002】

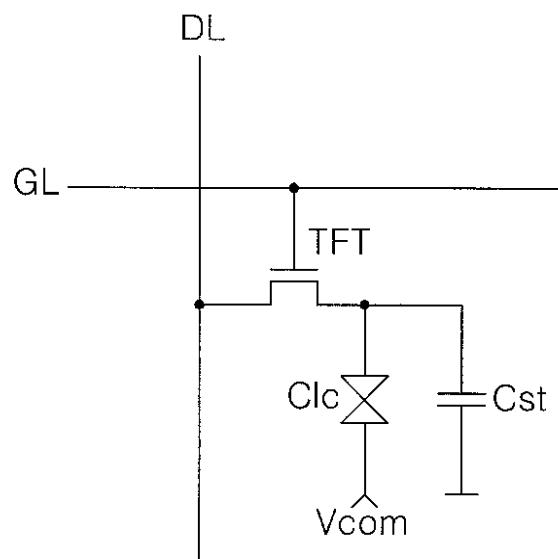

液晶表示装置は、ビデオ信号に応じて液晶セルの光透過率を調節して画像を表示する。アクティブマトリクスタイプの液晶表示装置は、図1のように、液晶セルC1cごとに形成された薄膜トランジスタ(Thin Film Transistor : 以下、TFTと略す)を用いて液晶セルに供給されるデータ電圧をスイッチングしてデータを能動的に制御するので、動画の表示品質を高めることができる。図1において、図面符号「Cst」は、液晶セルC1cに充電されたデータ電圧を維持するためのストレージキャパシタ、「DL」は、データ電圧が供給されるデータライン、「GL」は、スキャン電圧が供給されるゲートラインをそれぞれ意味する。

## 【0003】

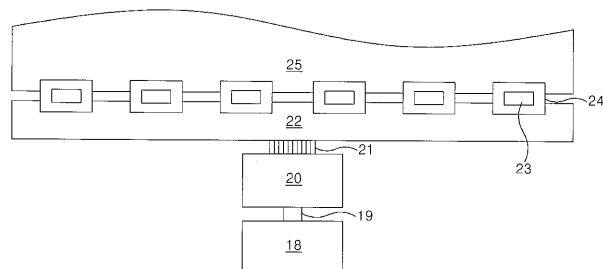

液晶表示装置は、最近のテレビやモニターが大画面化しつつ、小型とともに、中大型モデルの開発が進められている。このような液晶表示装置は、図2のように、コントロールP C B20、ソースP C B22、ソースP C B22とコントロールP C B20との間に接続されたケーブル21、ソースP C B22と液晶表示パネル25との間に接続された複数のソースCOF(Chip on film)を備える。

## 【0004】

ソースCOF24は、ソースP C B22と液晶表示パネル25とのデータパッドに電気的に接続される。このソースCOF24には、データ集積回路(Integrated Circuit ; 以下、「I C」と略す)23が実装される。

## 【0005】

ソースP C B22には、コントロールP C B20からのデジタルビデオデータとタイミ

10

20

30

40

50

ング制御信号を送信するための信号配線が形成される。

【0006】

コントロールPCB20には、制御回路とデータ送信回路などが実装される。このコントロールPCB20は、ソースPCB22のデータICにデータを供給し、データICの動作を制御するためのタイミング制御信号を、ケーブル21を介してソースPCB22に供給する。

【0007】

図2のような液晶表示装置において、液晶表示パネル25が大きくなれば、それに伴ってデータラインとソースCOF24が多くなり、その結果、ソースPCB22も大きくなる。この場合に、ソースPCB22とソースCOF24との整列が難しくなる。ソースPCB22が大きくなれば、従来のSMT(Surface Mount Technology)装置のような自動化実装装置は、相対的に小さな大きさのソースPCB22を基準に設計されたため、大きなソースPCB22を扱うことができない。コントロールPCB20は、液晶表示装置が大型化するほど、メモリ等の回路素子が多くなり、出力ピンの数が増加するという問題点がある。

10

【0008】

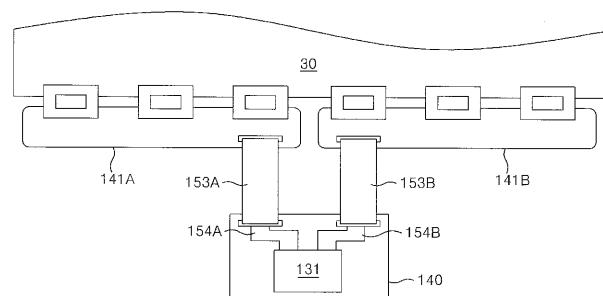

一方、図3のように、ソースPCBを分離し、タイミングコントローラー131の出力ポートをソースPCBの分割数分だけ複数に分割する方法も考慮できるが、この場合には、タイミングコントローラー131とコントロールPCB140とが大きくならざるをえない。

20

【0009】

以下、これを詳細に説明する。

【0010】

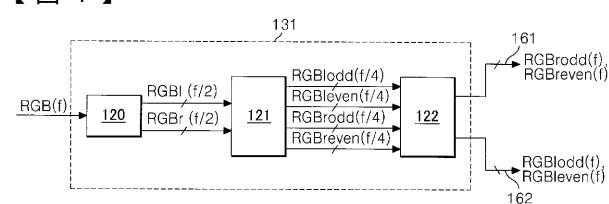

タイミングコントローラー131の出力ポートが2つに分離されると仮定するとき、タイミングコントローラー131は、図4のように左/右データ分離部120、2ポート拡張部121及びデータ変調部122を備える。

30

【0011】

左/右データ分離部120は、フレームメモリを用いて入力周波数(f)で入力される入力デジタルビデオデータRGBを、左側データRGB1と右側データRGBrとに分離する。左/右データ分離部120から出力されるデータRGB1、RGBrは、入力周波数の1/2周波数(f/2)で2ポート拡張部121に供給される。このような左/右データ分離部120によってタイミングコントローラー131の出力ポートを分離すれば、タイミングコントローラー131の大きさが大きくならざるをえない。

30

【0012】

2ポート拡張部121は、左/右データ分離部120から1/2周波数(f/2)で入力される左/右のデータRGB1、RGBrを奇数の画素データRGB1odd、RGBroddと偶数の画素データRGB1even、RGBrevenとに分離して、分離したそれぞれのデータを1/4周波数(f/4)でデータ変調部122に供給する。

【0013】

データ変調部122は、mini-LVDS方式でデータを変調する場合に、4倍速のmini-LVDSクロックに応じて2ポート拡張部121からのデータRGB1odd、RGBrodd、RGB1even、RGBrevenの周波数を高めて、入力周波数と同じ周波数(f)で左側データRGB1odd、RGB1evenと右側データRGBrodd、RGBrevenとを、分離された2個の出力ポート161、162を介して分割出力する。左側データRGB1odd、RGB1evenと右側データRGBrodd、RGBrevenのそれぞれは、3対の奇数の画素データ、3対の偶数の画素データ及び1対のminiクロックを含むので、タイミングコントローラー131の出力ピンの数が多くなるをえない。左側データRGB1odd、RGB1evenは、タイミングコントローラー131の第1出力ポート161と第1接続配線153Aとを経由して第1ソースPCB141Aに送信され、右側データRGBrodd、RGBrevenは、

40

50

タイミングコントローラー 131 の第 2 出力ポート 162 と第 2 接続配線 153B とを経由して第 2 ソース PCB 141B に送信される。

#### 【0014】

結果的に、図 3 のように、ソース PCB を 2 つに分離するとしても、タイミングコントローラー 131 とその出力ピン数を減らすのが難しく、コントロール PCB 140 の大きさを小さくすることが難しい。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0015】

本発明は、上述の問題点に鑑みてなされたもので、その目的は、ソース PCB を分割し、コントロール PCB の大きさと出力ピン数を減らすようにした液晶表示装置を提供することにある。

10

#### 【課題を解決するための手段】

#### 【0016】

上記の目的を達成すべく、本発明の実施の形態に係る液晶表示装置は、第 1 及び第 2 データライン群、該第 1 及び第 2 データライン群と交差する複数のゲートライン、及びマトリクス状に配置された複数の液晶セルを含む液晶表示パネルと、前記第 1 データライン群にデータを供給する第 1 データ I C に接続された第 1 ソース PCB と、前記第 2 データライン群にデータを供給する第 2 データ I C に接続された第 2 ソース PCB と、シングルポートを介して前記第 1 及び第 2 データ I C にビデオデータを出力するとともに、前記シングルポートを介して前記第 1 及び第 2 データ I C を制御するためのタイミング制御信号を出力するタイミングコントローラーとを備える。

20

#### 【0017】

本発明の他の実施の形態に係る液晶表示装置は、第 1 及び第 2 データライン群、前記第 1 及び第 2 データライン群と交差する複数のゲートライン、及びマトリクス状に配置された複数の液晶セルを含む液晶表示パネルと、前記第 1 データライン群にデータを供給する第 1 データ I C に接続された第 1 ソース PCB と、前記第 2 データライン群にデータを供給する第 2 データ I C に接続された第 2 ソース PCB と、シングルポートを介して前記第 1 及び第 2 データ I C にビデオデータを出力するとともに、前記シングルポートを介して前記第 1 及び第 2 データ I C を制御するためのタイミング制御信号を出力するタイミングコントローラーとを備え、前記タイミングコントローラーは、第 1 周波数で入力データを受けて前記第 1 周波数より高い第 2 周波数で前記ビデオデータを出力する。

30

#### 【発明の効果】

#### 【0018】

本発明に係る液晶表示装置によれば、ソース PCB を分割しタイミングコントローラーの出力ポートをシングル出力ポートで構成することで、コントロール PCB の大きさと出力ピン数を減らすことができる。また、本発明に係る液晶表示装置によれば、液晶表示パネルに形成された L O G 配線を用いて 1 つの F F C を除去することによって、ソース PCB とコントロール PCB との接続構造を単純化でき、かつ部品数を減らすことができる。

40

#### 【0019】

また、本発明に係る液晶表示装置によれば、F F C を介して直接コントロール PCB から駆動信号を供給される第 1 ソース PCB のデータ I C 内に各々補償抵抗を並列に接続することによって、L O G 配線を介して駆動信号を供給される第 2 ソース PCB と前記第 1 ソース PCB との間のガンマ補償電圧の偏差をなくすことができる。

#### 【0020】

なお、本発明に係る液晶表示装置によれば、ソース C O F 又はソース T C P に形成されて、駆動電圧を送信するダミー配線の線幅を、データタイミング制御信号を送信する他のダミー配線の線幅より広く形成している。その結果、L O G 配線抵抗による電圧降下分を最小にして、第 1 ソース PCB と第 2 ソース PCB との間のガンマ補償電圧の偏差をなくすことができる。

50

## 【発明を実施するための最良の形態】

## 【0021】

以下、図5～図35を参照して、本発明の好ましい実施の形態について説明する。

## 【0022】

まず、図5～図16は、本発明の第1の実施の形態に係る液晶表示装置を示す。

## 【0023】

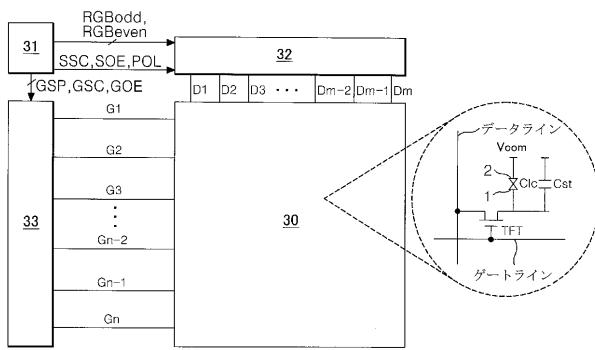

図5に示すように、本発明の実施の形態に係る液晶表示装置は、液晶表示パネル30、タイミングコントローラー31、データ駆動回路32、及びゲート駆動回路33を備える。

## 【0024】

液晶表示パネル30において、2枚のガラス基板の間には液晶層が形成される。この液晶表示パネル30は、m個のデータラインD1～Dmと、n個のゲートラインG1～Gnとが交差構造によりマトリクス状に配置されたm×n個の液晶セルC1cを含む。

## 【0025】

液晶表示パネル30の下部ガラス基板には、データラインD1～Dm、ゲートラインG1～Gn、TFT、TFTに接続された液晶セルC1cの画素電極1、及びストレージキャパシタCstなどが形成される。この液晶表示パネル30の下部ガラス基板には、後述のソースCOFの間でデータ、データタイミング制御信号、駆動電圧などを送信するLOG(Lines On Glass)配線が形成される。

## 【0026】

液晶表示パネル30の上部ガラス基板上には、ブラックマトリクス、カラーフィルター及び共通電極2が形成される。共通電極2は、TN(Twisted Nematic)モードとVA(Vertical Alignment)モードのような垂直電界駆動方式により上部ガラス基板上に形成され、IPS(In Plane Switching)モードとFFS(Fringe Field Switching)モードのような水平電界駆動方式により画素電極1と共に下部ガラス基板上に形成される。液晶表示パネル30の上部ガラス基板と下部ガラス基板上には、光軸が直交する偏光板が付着され、液晶と接する内面に液晶のプレチルト角を設定するための配向膜が形成される。

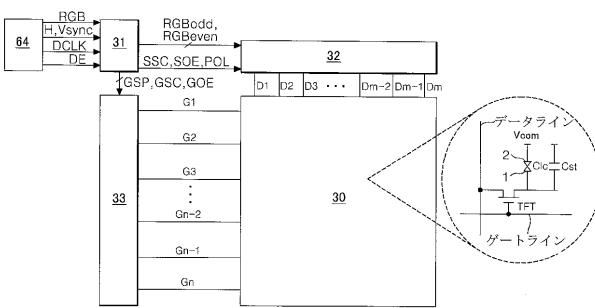

## 【0027】

タイミングコントローラー31は、垂直/水平同期信号、データタイミング信号、クロック信号などのタイミング信号を受信して、データ駆動回路32とゲート駆動回路33との動作タイミングを制御するためのタイミング制御信号を発生する。タイミングコントローラー31は、図6のように、グラフィック処理回路64からタイミング信号とデジタルビデオデータRGBとを受信することができる。グラフィック処理回路64は、システムボードに実装されて、液晶表示パネル30の解像度に合うように入力データの解像度を変換してタイミングコントローラー31に供給する。

## 【0028】

タイミングコントローラー31により生成されるタイミング制御信号は、ゲートスタートパルス(Gate Start Pulse)GSP、ゲートシフトクロック信号(Gate Shift Clock)GSC、ゲート出力イネーブル信号(Gate Output Enable)GOEなどのゲートタイミング制御信号を含む。ゲートスタートパルスGSPは、1画面が表示される1垂直期間のうち、スキャンが始まるスタート水平ラインを指示する。ゲートシフトクロック信号GSCは、ゲート駆動回路内のシフトレジスタに入力されてゲートスタートパルスGSPを順次シフトさせるためのタイミング制御信号であって、TFTのオン期間に対応するパルス幅で発生する。ゲート出力信号GOEは、ゲート駆動回路33の出力を指示する。また、タイミングコントローラー31により生成されるタイミング制御信号は、ソースサンプリングクロック(Source Sampling Clock)SSC、ソース出力イネーブル信号(Source Output Enable)SOE、極性制御信号(Polarity)POLなどを含むデータタイミング制御信号を含む。ソースサンプリングクロックSSCは、立ち上がり又は

10

20

30

40

50

立下リエッジに基づいて、データ駆動回路32内でデータのラッチ動作を指示する。ソース出力イネーブル信号S0Eは、データ駆動回路32の出力を指示する。極性制御信号POLは、液晶表示パネル30の液晶セルC1cに供給されるデータ電圧の極性を指示する。また、タイミングコントローラー31は、デジタルビデオデータを奇数の画素データRGBoddと偶数の画素データRGBevenとに分離し、そのデータをデータ駆動回路32に供給する。

【0029】

データの送信経路上において、EMIとデータ電圧のスイング幅を減らすために、タイミングコントローラー31は、データをmini-LVDS(low-voltage differential signaling)方式又はRSDS(Reduced Swing Differential Signaling)方式で変調して、データ駆動回路32に供給する。

10

【0030】

データ駆動回路32は、タイミングコントローラー31の制御下にデジタルビデオデータRGBodd、RGBevenをラッチする。そして、データ駆動回路32は、デジタルビデオデータを極性制御信号POLに応じて、アナログ正極性/負極性ガンマ補償電圧に変換して、正極性/負極性アナログデータ電圧を発生し、そのデータ電圧をデータラインD1~Dmに供給する。

【0031】

ゲート駆動回路33は、シフトレジスタ、シフトレジスタの出力信号を液晶セルのTFT駆動に適したスイング幅に変換するためのレベルシフタ、及びレベルシフタとゲートラインG1~Gnとの間に接続する出力バッファをそれぞれ含む複数のゲートICで構成される。このゲート駆動回路33は、ゲートパルス(又はスキャンパルス)を順次出力する。このようなゲート駆動回路33のICは、COF又はTCPに実装されて、ACF(anicotropic conductive film)を介して液晶表示パネル30の下部ガラス基板に形成されたゲートパッドに接続される。また、ゲート駆動回路33は、ゲートインパネル(Gate In Panel)工程を用いて、画素アレイに形成されたデータラインD1~Dm、ゲートラインG1~Gn及びTFTとともに、液晶表示パネル30の下部ガラス基板上に直接形成することができる。また、ゲート駆動回路33のICは、チップオングラス(Chip On Glass)方式により、液晶表示パネル30の下部ガラス基板上に直接接着することもできる。

20

30

【0032】

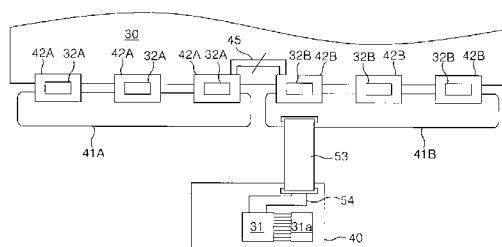

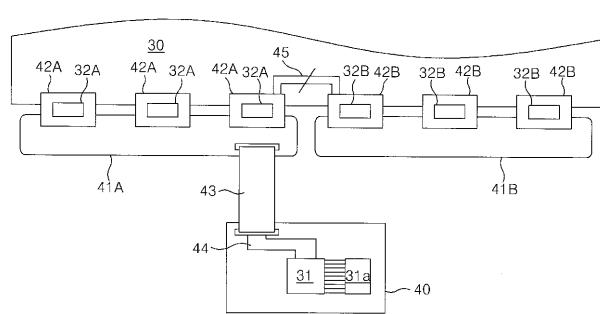

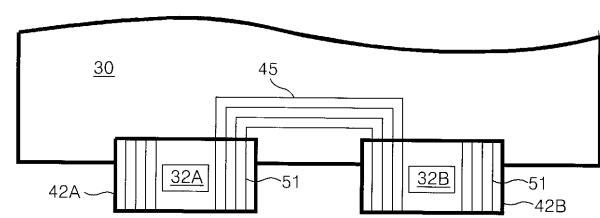

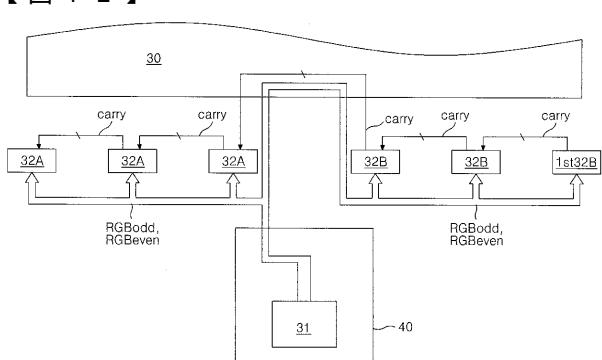

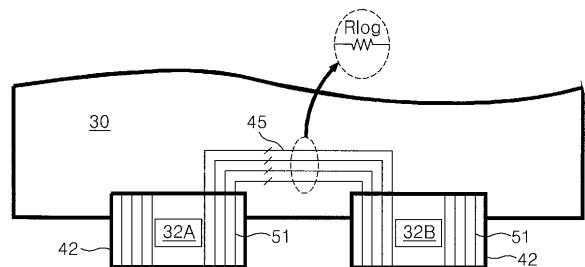

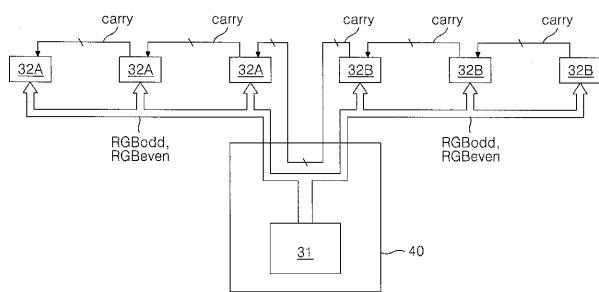

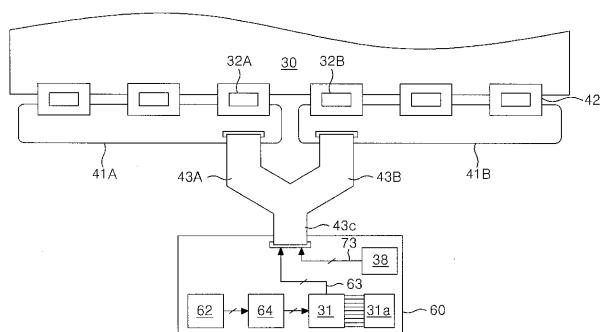

図7は、図5に示す液晶表示パネル30、データ駆動回路32及びタイミングコントローラー31の組み立て状態を示す図である。図8は、ソースCOFに形成されたダミー配線と液晶表示パネル30の基板上に形成されたLOG配線とを示す図である。

【0033】

図7及び図8に示すように、データ駆動回路32は、複数のデータIC32A、32Bを含む。

【0034】

複数のデータIC32A、32Bは、ソースCOF42A、42Bにそれぞれ実装される。ソースCOF42A、42Bの代わりにソースTCP(Tape Carrier Package)を適用することもできる。ソースCOF42A、42Bは、2つに分割された第1及び第2ソースPCB41A、41Bに分けられて接続される。表示画面の右半部に形成されたデータラインにデータを供給するためのソースCOF42Aは、第1ソースPCB41Aに接続され、表示画面の左半部に形成されたデータラインにデータを供給するためのソースCOF42Bは、第2ソースPCB41Bに接続される。ソースCOF42A、42Bの入力端子は、ソースPCB41A、41Bの出力端子に電気的に接続され、ソースCOF42A、42Bの出力端子は、ACFを介して液晶表示パネル30の下部ガラス基板に形成されたデータパッドに電気的に接続される。データパッドは、データリンク配線を経由してデータラインD1~Dmに接続される。

40

50

## 【0035】

ソースCOF42A、42Bには、図8のように、ダミー配線51が形成される。ダミー配線51には、隣接したソースCOF42A、42Bに送信されるデジタルビデオデータRGBo d d、RGBe v e nと、データタイミング制御信号、キャリー信号が供給され、また、高電位電源電圧VDD、低電位電源電圧VSS、及びガンマ基準電圧(Gamma reference voltages)などの駆動電圧が供給される。第1ソースPCB41Aに接続されたソースCOF42Aのうち、第2ソースPCB41Bに隣接するソースCOF42Aのダミー配線51と、第2ソースPCB41Bに接続されたソースCOF42Bのうち、第1ソースPCB41Aに隣接するソースCOF42Bのダミー配線51は、液晶表示パネル30の下部ガラス基板に形成されたLOG配線45を経由して電気的に接続される。10

## 【0036】

第1及び第2ソースPCB41A、41Bには、デジタルビデオデータRGBo d d、RGBe v e nが送信されるバス配線、データタイミング制御信号が送信されるバス配線、駆動電圧が送信されるバス配線が形成される。

## 【0037】

第1ソースPCB41Aの入力端子は、FFC(Flexibl e Flat Cabl e)43を経由してコントロールPCB40上に形成された接続配線44に電気的に接続される。第2ソースPCB41Bは、コントロールPCB40に接続されない。分割されたソースPCB41A、41Bは、LOG配線45とソースCOF42A、42Bとを経由して電気的に接続される。したがって、第1ソースPCB41Aは、コントロールPCB40に形成された接続配線44を経由して、コントロールPCB40のシングル出力ポートからデジタルビデオデータRGBo d d、RGBe v e n、データタイミング信号及び駆動電圧を供給され、第2ソースPCB41Bは、LOG配線45とソースCOF42A、42Bを経由して、第1ソースPCB41AからデジタルビデオデータRGBo d d、RGBe v e n、キャリー信号、データタイミング信号及び駆動電圧を供給される。20

## 【0038】

コントロールPCB40には、タイミングコントローラー31、EEPROM31a、液晶表示パネル30の駆動電圧を発生するための直流-直流変換器(DC-DC Converter)などの回路と共に、接続配線44が形成される。直流-直流変換器から生成される駆動電圧は、ゲートハイ電圧VGH、ゲートロー電圧VGL、共通電圧Vcom、高電位電源電圧VDD、低電位電源電圧VSS、高電位電源電圧VDDと低電位電源電圧VSSとの間で分圧される複数のガンマ基準電圧(Gamma reference voltages)などを含む。ガンマ基準電圧は、デジタルビデオデータRGBo d d、RGBe v e nのビット数で表現可能な階調数分だけデータIC32a内で各階調に該当するアナログガンマ補償電圧に細分化される。ゲートハイ電圧VGH、ゲートロー電圧VGLは、スキャンパルスのスイング電圧である。EEPROM31aは、タイミングコントローラー31から生成されるタイミング制御信号に対する波形オプション情報が複数のモード別に格納されて、ユーザからの命令に応じて該当モードで波形情報をタイミングコントローラー31に供給する。タイミングコントローラー31は、EEPROM31aからの波形オプション情報に応じて、各々のモードで互いに異なる形態でタイミング制御信号を生成する。30

## 【0039】

コントロールPCB40に形成された接続配線44を介して、図9に示すタイミングコントローラー31のシングル出力ポート63は、FFC43に接続される。シングル出力ポート63は、データ、駆動電圧及びタイミング制御信号が出力される複数の出力ピンを含む。接続配線44を介してタイミングコントローラー31から生成されたデジタルビデオデータRGBo d d、RGBe v e n及びタイミング制御信号と、直流-直流変換器から生成された駆動電圧が、FFC43に伝達される。40

## 【0040】

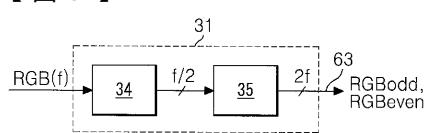

図9は、タイミングコントローラー31内のデータ処理部分を示す図である。

【0041】

図9に示すように、タイミングコントローラー31は、2ポート拡張部34とデータ変調部35を備える。

【0042】

2ポート拡張部34は、システムのメインボードから所定の入力周波数( $f$ )で入力されるデジタルビデオデータRGBを、奇数の画素データRGBooddと偶数の画素データRGBevenとに分離して、そのデータRGBoodd、RGBevenを1/2周波数( $f/2$ )でデータ変調部35に供給する。ここで、周波数を1/2に減らす理由は、EMI(Electromagnetic Interference)を減らすためである。2ポート拡張部34から出力されるデータRGBoodd、RGBevenのスイング幅は、TTL(transistor-to-transistor)レベルである3.3V程度で比較的高い。

10

【0043】

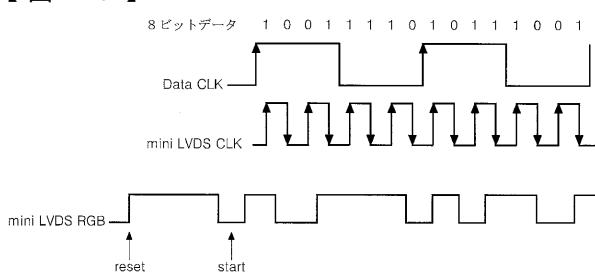

データ変調部35は、mini-LVDS方式でデータを変調して、2ポート拡張部34からのデータRGBoodd、RGBevenのスイング幅を300mV~600mV程度に下げ、mini-LVDSクロックに応じてデータの周波数を2倍( $2f$ )に上げる。データ変調部35から出力される信号は、3対の奇数の画素データRGBoodd、3対の偶数の画素データRGBeven及び1対のminiクロックminicLKを含む。各信号対は、図10及び図11のように、正極性信号Pと負極性信号Nを含む。一方、データ変調部35は、RSDS方式によりデータを変調することもできる。

20

【0044】

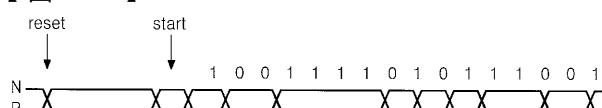

図10及び図11は、データ変調部35から出力されるデータの一例を示すものであって、mini-LVDS方式で変調されたデータの一例である。

【0045】

図10において、DataCLKは、システムのメインボードから生成されるデータクロックであり、mini-LVDSCLKは、データ変調部35から生成されてデータと共に送信されるクロックである。そして、mini-LVDSRGBは、リセット波形を含んでデータ変調部35により変調された正極性データ波形Pである。

30

【0046】

データ変調部35は、正極性データ信号Pの逆位相となる負極性データ信号Nも生成し、各々正極性信号Pと負極性信号Nを含む6対のデータと1対のmini-LVDSクロックを発生する。図12のように、第1番目のデータをサンプリングする第1データIC1st32Bは、リセット波形に続いて発生するスタートパルスstartをデータサンプリングスタート時点と認識して、スタートパルスstartに続いて供給されるデータをサンプリングし始める。したがって、タイミングコントローラー31は、別途の配線を介してソーススタートパルス(Source Start Pulse:SSP)を発生しない。

【0047】

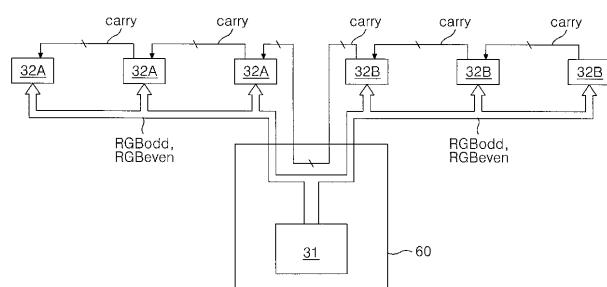

図12は、タイミングコントローラー31とデータIC32A、32Bとの間の信号送信経路を示す。

40

【0048】

図7、図9及び図12に示すように、タイミングコントローラー31によりmini-LVDS方式又はRSDS方式により変調されたデジタルビデオデータのうち、右側データRGBoodd、RGBevenは、タイミングコントローラー31のシングル出力ポート63、接続配線44、及びFFC43を経由して第1ソースPCB41Aに接続されたデータIC32Aに送信される。右側データRGBoodd、RGBevenは、液晶表示パネル30の右半部の画面に表示されるデータである。また、図7、図9及び図12に示すように、タイミングコントローラー31によりmini-LVDS方式又はRSDS方式で変調された左側データRGBoodd、RGBevenは、タイミングコントローラー

50

31のシングル出力ポート63、接続配線44、第1ソースP C B 4 1 A、ソースC O F 4 2 Aのダミー配線51、及び液晶表示パネル30のL O G配線45を経由して、第2ソースP C B 4 1 Bに接続されたデータI C 3 2 Bに送信される。左側データR G B o d d 、R G B e v e nは、液晶表示パネル30の左半部の画面に表示されるデータである。

【0049】

タイミングコントローラー31から発生するデータタイミング制御信号は、データと共にタイミングコントローラー31のシングル出力ポート63、接続配線44、及びF F C 4 3を経由して、第1ソースP C B 4 1 Aに接続されたデータI C 3 2 Aに送信される。また、データタイミング制御信号は、タイミングコントローラー31のシングル出力ポート63、接続配線44、第1ソースP C B 4 1 A、ソースC O F 4 2 のダミー配線51、及び液晶表示パネル30のL O G配線45を経由して、第2ソースP C B 4 1 Bに接続されたデータI C 3 2 Bに送信される。

10

【0050】

第1番目のデータをサンプリングする最左側の第1データI C 3 2 Bは、図10及び図11においてスタートパルス以後のデータを自身の出力チャネル数分だけサンプリングした後に、その次のデータのサンプリングタイミングを指示するキャリー信号c a r r yを発生して、隣接したデータI C 3 2 Bに供給する。同様に、キャリー信号c a r r yは、隣接したデータI C 3 2 A、3 2 Bに順次伝達される。第1及び第2ソースP C B 4 1 A、4 1 Bの間で、キャリー信号c a r r yは、液晶表示パネル30に形成されたL O G配線45を介して送信される。一方、データI C 3 2 Aのデータサンプリング方向は、反対に調整されうる。この場合、第1及び第2ソースP C B 4 1 A、4 1 Bの間でキャリー信号c a r r yは、反対方向に送信される。

20

【0051】

コントロールP C B 4 0に実装された直流-直流変換器から発生する駆動電圧は、直流-直流変換器の出力端子、接続配線44及びF F C 4 3を経由して第1ソースP C B 4 1 Aに接続されたデータI C 3 2 Aに送信される。また、駆動電圧は、直流-直流変換器の出力端子、接続配線44、第1ソースP C B 4 1 A、ソースC O F 4 2 Aのダミー配線51、及び液晶表示パネル30のL O G配線45を経由して、第2ソースP C B 4 1 Bに接続されたデータI C 3 2 Bに送信される。

30

【0052】

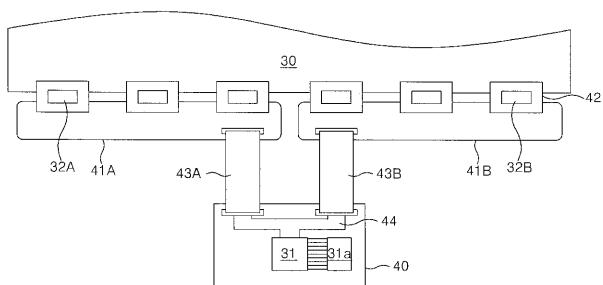

図13は、本発明の第1の実施の形態に係る液晶表示装置の他の構造を示す。

【0053】

図13に示すように、第2ソースP C B 4 1 Bは、F F C 5 3を経由してコントロールP C B 4 0上に形成された接続配線54に電気的に接続される。第1ソースP C B 4 1 Aとそれに接続されたデータC O F 4 2 Aは、コントロールP C B 4 0には接続されず、接続配線54、F F C 5 3、第2ソースP C B 4 1 B、L O G配線45を経由して、データタイミング制御信号、キャリー信号、及び駆動電圧を供給される。

【0054】

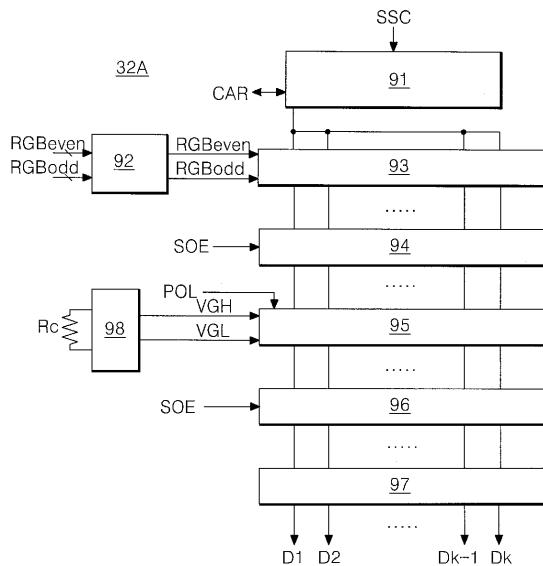

図14及び図15は、データI C 3 2 A、3 2 Bを詳細に示す回路図である。

40

【0055】

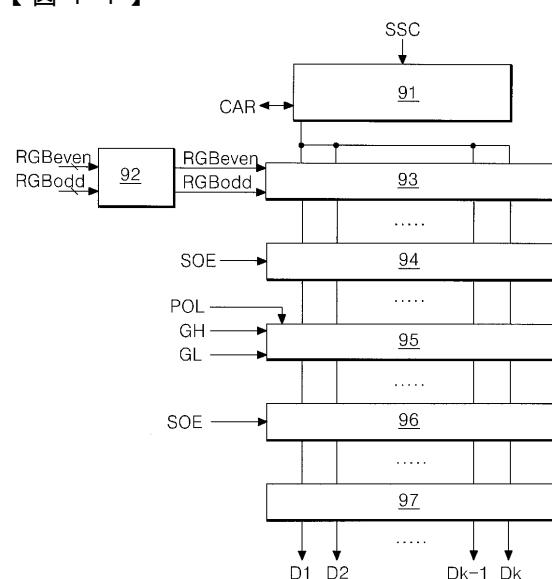

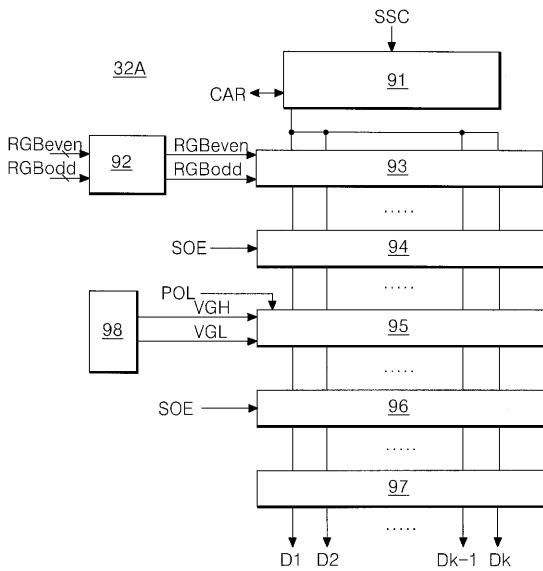

図14及び図15に示すように、データI C 3 2 A、3 2 Bのそれぞれは、シフトレジスタ91、データ復元部92、第1ラッチアレイ93、第2ラッチアレイ94、デジタル/アナログ変換器（以下、「D A C」と略す）95、チャージシェア回路（C h a r g e S h a r e C i r c u i t ）96及び出力回路97を含む。

【0056】

データ復元部92は、タイミングコントローラー31により分離された奇数の画素データR G B o d d と偶数の画素データR G B e v e nとを一時格納し、タイミングコントローラー31の変調方式に対応する復調方式で、変調されたデータを復元する。例えば、データ復元部92は、図11のように正極性データがハイ論理であるときに「1」を発生し、正極性データがロー論理であるときに「0」を発生してデータを復元する。そして、デ

50

データ復元部 92 は、復元されたデータ R G B o d d 、 R G B e v e n を、第 1 ラッチアレイ 93 に供給する。

【 0 0 5 7 】

シフトレジスタ 91 は、ソースサンプリングクロック S S C に応じてサンプリング信号をシフトさせる。また、シフトレジスタ 91 は、第 1 ラッチアレイ 93 のラッチ数を超過するデータが供給されるとき、キャリー信号 C a r r y を発生する。第 1 番目のデータをサンプリングする第 1 データ I C 1 s t 3 2 B のシフトレジスタ 91 は、図 11 のように、データバスを介してリセット信号 r e s e t とスタートパルス s t a r t に続いて供給されるデータを、第 1 番目にサンプリングするデータと判断する。

【 0 0 5 8 】

第 1 ラッチアレイ 93 は、シフトレジスタ 91 から順次入力されるサンプリング信号に応答して、データ復元部 92 からのデジタルビデオデータ R G B e v e n 、 R G B o d d をサンプリングし、そのデータ R G B e v e n 、 R G B o d d を 1 水平ライン分ずつラッチした後、 1 水平ライン分のデータを同時に出力する。

【 0 0 5 9 】

第 2 ラッチアレイ 94 は、第 1 ラッチアレイ 93 から入力される 1 水平ライン分のデータをラッチした後、ソース出力イネーブル信号 S O E のロー論理期間の間に、他のデータ I C 3 2 A の第 2 ラッチアレイ 94 と同時にラッチされたデジタルビデオデータ R G B e v e n 、 R G B o d d を出力する。

【 0 0 6 0 】

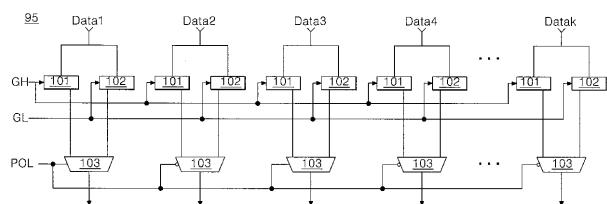

D A C 95 は、図 15 のように、正極性ガンマ補償電圧 G H が供給される P - デコーダ ( P D E C ) 101 、負極性ガンマ補償電圧 G L が供給される N - デコーダ ( N D E C ) 102 、極性制御信号 P O L に応答して P - デコーダ 101 の出力と N - デコーダ 102 の出力を選択するマルチプレクサ 103 を含む。 P - デコーダ 101 は、第 2 ラッチアレイ 94 から入力されるデジタルビデオデータ R G B e v e n 、 R G B o d d をデコードして、そのデータの階調値に該当する正極性ガンマ補償電圧 G H を出力し、 N - デコーダ 102 は、第 2 ラッチアレイ 94 から入力されるデジタルビデオデータ R G B e v e n 、 R G B o d d をデコードして、そのデータの階調値に該当する負極性ガンマ補償電圧 G L を出力する。マルチプレクサ 103 は、極性制御信号 P O L に応答して正極性のガンマ補償電圧と負極性のガンマ補償電圧を選択する。

【 0 0 6 1 】

チャージシェア回路 96 は、ソース出力イネーブル信号 S O E のハイ論理期間の間に、隣接したデータ出力チャネルを短絡 ( s h o r t ) させて、隣接したデータ電圧の平均値をチャージシェア電圧として出力するか、またはソース出力イネーブル信号 S O E のハイ論理期間の間に、データ出力チャネルに共通電圧 V c o m を供給して、正極性データ電圧と負極性データ電圧の急激な変化を減らす。

【 0 0 6 2 】

出力回路 97 は、バッファを含んでおり、データライン D 1 ~ D k に供給されるアナログデータ電圧の信号減衰を最小化する。

【 0 0 6 3 】

図 16 は、図 7 に示すタイミングコントローラー 31 、第 1 ソース P C B 4 1 A に接続されたデータ I C 3 2 A と、第 2 ソース P C B 4 1 B に接続されたデータ I C 3 2 B と、その間の抵抗 R s 、 R D I V 、 R E Q 、 R L O G 、 R T A 、 R T B を等価的に示す。

【 0 0 6 4 】

タイミングコントローラー 31 から出力されるデータとクロック信号のそれぞれは、正極性信号 P と負極性信号 N を含む。このタイミングコントローラー 31 の正極性信号出力端子には、抵抗 R s が接続され、タイミングコントローラー 31 の負極性信号出力端子には、抵抗 R s が接続される。また、タイミングコントローラー 31 の正極性信号出力端子と負極性信号出力端子との間に抵抗 R D I V が接続される。データ I C 3 2 A 、 3 2 B のそれぞれの正極性信号入力端子と負極性信号入力端子との間には、抵抗 R T A 、 R T B が

10

20

30

40

50

接続される。このような抵抗  $R_S$ 、 $R_{D_{IV}}$ 、 $R_{T_A}$ 、 $R_{T_B}$  は、正極性信号  $P$  と負極性信号  $N$  の位相を同期させ、その電圧を  $300\text{mV} \sim 600\text{mV}$  程度に調整する。「 $R_{EQ}$ 」は、直列抵抗  $R_S$  と第1ソース PCB 41A に接続されたデータ I C 32A との間の信号送信配線と、直列抵抗  $R_S$  と LOG 配線 45 との間の信号送信配線を等価的に示した抵抗であって、コントロール PCB 40 に形成された接続配線 44 と FFC 43 の抵抗を含む。

## 【0065】

図 16 から分かるように、第2ソース PCB 41B に接続されたデータ I C 32B に供給されるデータ、キャリー、及び駆動電圧は、LOG 配線 45 の抵抗  $R_{LOG}$  によって電圧降下する。したがって、第1ソース PCB 41A に接続されたデータ I C 32A に供給される信号に比べて、第2ソース PCB 41B に接続されたデータ I C 32B に供給される信号の電圧が低くなる。

## 【0066】

LOG 抵抗を補償するために、本発明の第1の実施の形態に係る液晶表示装置は、LOG 抵抗の影響を受けないデータ I C 32A の正極性信号入力端子と負極性信号入力端子との間に接続された抵抗  $R_{T_A}$ 、 $R_{T_B}$  の抵抗値を、下記のように決定する。

## 【0067】

LOG 抵抗に影響を受けないデータ I C 32A に供給される  $\text{mini-LVDS}$  信号の電圧  $V_{swing_A}$  は、下式(1)のとおりである。

## 【0068】

## 【数1】

$$V_{swing_A} = \frac{(R_{D_{IV}/2})}{(R_{D_{IV}/2} + R_{DRIVER} + R_S)} \cdot \frac{(R_{T_B}/2)}{(R_{T_B/2}) + R_{EQ}} \cdot V_{cco} \quad (1)$$

## 【0069】

LOG 抵抗に影響を受けるデータ I C 32B に供給される  $\text{mini-LVDS}$  信号の電圧  $V_{swing_B}$  は、下式(2)のとおりである。

## 【0070】

## 【数2】

$$V_{swing_B} = \frac{(R_{D_{IV}/2})}{(R_{D_{IV}/2} + R_{DRIVER} + R_S)} \cdot \frac{(R_{T_A}/2)}{(R_{T_A/2}) + R_{EQ} + R_{LOG}} \cdot V_{cco} \quad (2)$$

## 【0071】

上式(1)及び(2)において、 $R_{D_{R_{IV}}}$  は、タイミングコントローラー 31 内の内部抵抗であり、 $V_{cco}$  は、タイミングコントローラー 31 の出力段に内蔵されたデータ送信バッファの駆動電圧である。

## 【0072】

このデータ I C 32A、32B の  $\text{mini-LVDS}$  信号入力の偏差を補正するためには、下式(3)のように、LOG 抵抗の影響を受けない  $\text{mini-LVDS}$  信号入力電圧と、LOG 抵抗の影響を受ける  $\text{mini-LVDS}$  信号入力電圧とが同じでなければならない。

## 【0073】

## 【数3】

$$V_{swing_A} = V_{swing_B}$$

$$= \frac{R_{T_B}}{R_{T_B} + 2R_{EQ}} = \frac{R_{T_A}}{R_{T_A} + 2R_{EQ} + 2R_{LOG}} \quad (3)$$

## 【0074】

10

20

30

40

50

したがって、第1ソースP C B 4 1 Aに接続されたデータI C 3 2 Aの正極性信号入力端子と負極性信号入力端子との間に接続された抵抗R<sub>TA</sub>は、下式(4)のような抵抗値で決定される。

【0075】

【数4】

$$R_{TA} = \frac{R_{TB}(R_{EQ} + R_{LOG})}{R_{EQ}} \quad (4)$$

【0076】

本発明の第2の実施の形態に係る液晶表示装置は、コントロールP C Bに形成された、いくつかの構成要素を除去する代わりに、その構成要素をシステムボード内に集積する。以下において、本発明の第1の実施の形態において説明済みの構成要素については、同じ図面符号を付し、それについての詳細な説明を省略する。

10

【0077】

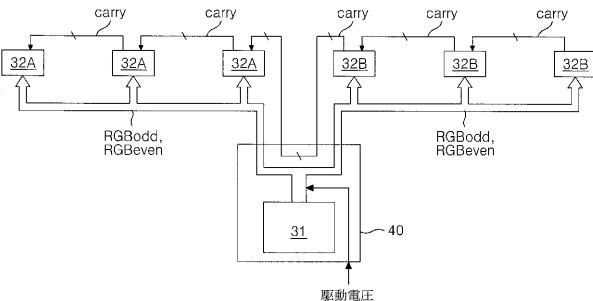

次に、図17～図21を用いて、本発明の第2の実施の形態に係る液晶表示装置を説明する。

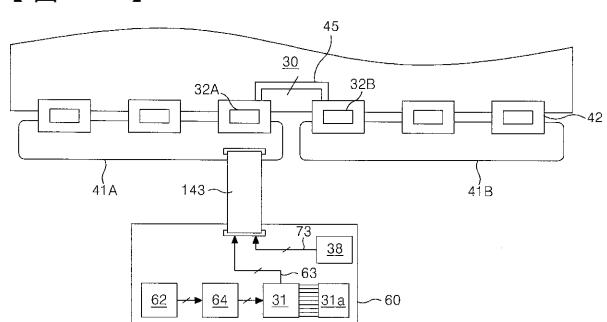

図17は、本発明の第2の実施の形態に係る液晶表示パネル30、データ駆動回路32、タイミングコントローラー31及びグラフィック処理回路64の組み立て状態を示す。

20

【0078】

図17に示すように、システムボード60は、外部機器から入力される多様な属性の映像データを供給するためのインターフェース回路62、インターフェース回路62からの映像データを液晶表示パネル30に合うように変換するグラフィック処理回路64、及び液晶表示パネル30の駆動に必要な駆動電圧を発生する直流-直流変換器(DC-DC C onverter)38を備える。

20

【0079】

インターフェース回路62は、DVD、CD及びHDDなどの格納媒体、TV受信回路などからの多様な属性の映像データをグラフィック処理回路64に供給する。

20

【0080】

グラフィック処理回路64は、アナログ-デジタル変換部64a、スケーラー部64b、イメージ処理部64cなどを含んで、インターフェース回路62からの映像データを液晶表示パネル30に合うように変換するとともに、インターフェース回路62からの映像データを用いて、液晶表示パネル30の解像度に合うタイミング信号を生成する。グラフィック処理回路64は、変換されたデジタル映像データ及び生成されたタイミング信号を、ワイヤーケーブル68を介してタイミングコントローラー31に供給する。

30

【0081】

アナログ-デジタル変換部64aは、インターフェース回路62を介して供給されるアナログ映像データをデジタルビデオデータに変換する。

30

【0082】

スケーラー部64bは、インターフェース回路62からのデジタルビデオデータの解像度を液晶表示パネル30の解像度に合うように変換する。また、スケーラー部64bは、液晶表示パネル30の応答特性及びコントラスト比のうち、少なくともいずれか1つを調整するために、予め設定された所定の補償値でインターフェース回路62からのデジタルビデオデータを変調することもできる。このために、スケーラー部64bは、液晶表示パネル30の応答特性を向上させるための第1変調部と、液晶表示パネル30のコントラスト比を強調させるための第2変調部のうち、少なくともいずれか1つを備えることができる。

40

【0083】

第1変調部は、図18のように、前回フレームデータと現在フレームデータとを比較し、その比較結果に応じるデータの変化を判断して、その判断結果に対応する第1補償値をメモリから読んで、その第1補償値でデジタルビデオデータを変調することによって、平板表示パネルの応答特性を向上させる。液晶表示装置において主に用いられているTNモ

50

ード (Twisted Nematic mode) の液晶応答速度は、液晶材料の物性とセルギャップなどにより変わるが、通常、立ち上がりタイムが 20 ms ~ 80 ms の範囲であり、立下りタイムが 20 ms ~ 30 ms の範囲である。このような液晶の応答速度は、1 フレーム期間 (NTSC: 16.67 ms) より長い。このため、液晶セルに充電される電圧が、所望の電圧に到達する前に、次のフレームに進んでしまうため、動画において画面が薄暗くなるモーションバーリング (Motion Burring) 現象が現れる。すなわち、液晶の応答速度に起因して、あるレベルから他のレベルにデータが変わると、それに対応する表示輝度が所望の目標輝度に到達できない。第 1 変調部は、デジタルビデオデータを前回フレームと現在フレームとの間で比較し、その比較結果に応じて、予め設定された第 1 補償値を選択し、選択された補償値でデジタルビデオデータを変調して、液晶表示パネルに供給される電圧の絶対値を VD から MV<sub>D</sub> に大きくする。そのために、第 1 変調部は、図 19 のように、2 つのフレームメモリ 111、112 とルックアップテーブル 113 を含む。

10

#### 【0084】

第 1 及び第 2 フレームメモリ 111、112 は、デジタルビデオデータ R<sub>i</sub> G<sub>i</sub> B<sub>i</sub> をフレーム単位に交互に格納し、該格納されたデータを交互に出力して、ルックアップテーブル 113 に前回フレームデータ、すなわち、n-1 番目のフレームデータ F<sub>n-1</sub> を供給する。

20

#### 【0085】

ルックアップテーブル 113 は、予め設定された第 1 補償値を含んでメモリに格納されている。このルックアップテーブル 113 は、n 番目のフレームデータ F<sub>n</sub> と第 1 及び第 2 フレームメモリ 111、112 から入力される n-1 番目のフレームデータ F<sub>n-1</sub> を比較し、その比較結果に対応する第 1 補償値を変調されたデジタルビデオデータ ODC (RGB) として出力する。

20

#### 【0086】

換言すれば、第 1 変調部は、予め決定された第 1 補償値に応じて、同じピクセルでそのピクセルデータ値が前回フレーム F<sub>n-1</sub> より現在フレーム F<sub>n</sub> が、より大きくなれば、現在フレーム F<sub>n</sub> より大きい値でデジタルビデオデータを変調し、前回フレーム F<sub>n-1</sub> より現在フレーム F<sub>n</sub> が、より小さくなれば、現在フレーム F<sub>n</sub> より小さな値でデジタルビデオデータを変調する。そして、第 1 変調部は、同じピクセルでそのピクセルデータ値が前回フレーム F<sub>n-1</sub> と現在フレーム F<sub>n</sub> とで同一であれば、現在フレーム F<sub>n</sub> と同じ値でデジタルビデオデータを変調、すなわち、現在フレーム F<sub>n</sub> のデータをそのまま出力する。

30

#### 【0087】

このような第 1 変調部は、本願出願人により既出願された韓国特許出願第 10-2001-0032364 号、第 10-2001-0057119 号、第 10-2001-0054123 号、第 10-2001-0054124 号、第 10-2001-0054125 号、第 10-2001-0054127 号、第 10-2001-0054128 号、第 10-2001-0054327 号、第 10-2001-0054889 号、第 10-2001-0056235 号、第 10-2001-0078449 号、第 10-2002-0046858 号、第 10-2002-0074366 号等に開示された変調方式を用いて、液晶の応答特性を速くすることができる。

40

#### 【0088】

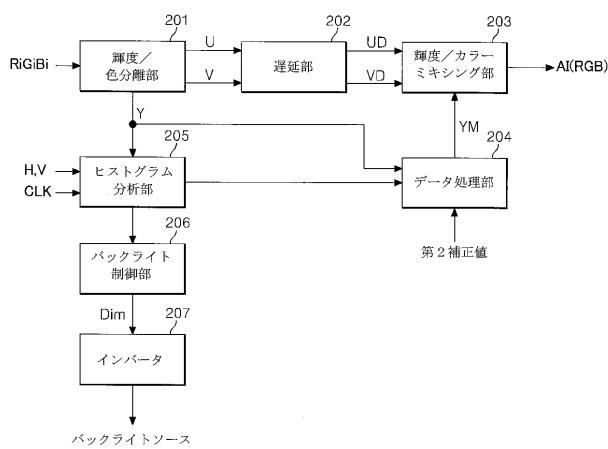

第 2 変調部は、図 20 のように、1 フレーム映像のデジタルビデオデータ R<sub>i</sub> G<sub>i</sub> B<sub>i</sub> に対して輝度を分析し、その輝度分析結果に応じてメモリに格納された第 2 補償値でデジタルビデオデータ R<sub>i</sub> G<sub>i</sub> B<sub>i</sub> を変調して、明るい映像部分に表示されるデジタルビデオデータ R<sub>i</sub> G<sub>i</sub> B<sub>i</sub> の輝度値を高め、その一方で、相対的に暗い映像部分に表示されるデジタルビデオデータ R<sub>i</sub> G<sub>i</sub> B<sub>i</sub> の輝度値を下げる。第 2 補償値は、各階調区間の輝度及びコントラストを強調するための多様な形態のデータストレッチングカーブの出力階調に対応する値で決定される。ここで、第 2 変調部は、1 画面の階調分布において、デジタル

50

ビデオデータ R i G i B i が集中する階調区間で傾きが大きく、相対的にデジタルビデオデータ R i G i B i の分布が小さな階調区間で傾きが小さなデータストレッチングカーブの第 2 補償値で、デジタルビデオデータ R i G i B i を変調する。これと同時に、第 2 変調部は、輝度分析結果に応じて、明るい映像部分に光を照射するバックライト光源の明るさを上げ、その一方で、相対的に暗い部分に光を照射するバックライト光源の明るさを下げるよう 10 に液晶表示装置のバックライトユニット輝度を制御する。結果的に、第 2 変調部は、映像分析の結果に応じてデジタルビデオデータ R i G i B i の輝度を変調すると同時に、バックライト輝度を制御して表示映像の輝度及びコントラストを増加させて、動画においてダイナミックコントラスト比 (Dynamic contrast ratio) を大きくする。このために、第 2 変調部は、図 20 のように、輝度 / 色分離部 201、遅延部 202、輝度 / カラーミキシング部 203、データ処理部 204、ヒストグラム分析部 205、及びバックライト制御部 206 を備える。

【0089】

輝度 / 色分離部 201 は、デジタルビデオデータ R i G i B i を輝度成分 Y と色差成分 U、V とに分離する。

【0090】

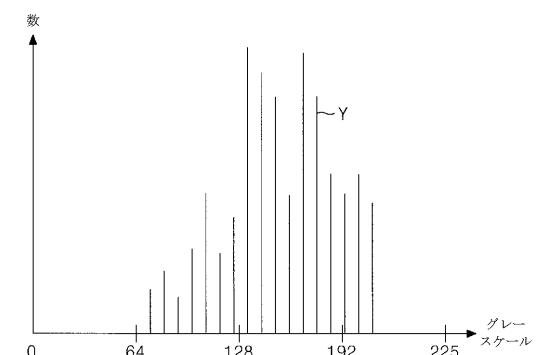

ヒストグラム分析部 205 は、輝度 / 色分離部 201 により分離された輝度成分 Y を受けて、輝度成分 Y を階調別累積分布関数に分類、すなわち、図 21 のようなヒストグラムに分類する。また、ヒストグラム分析部 205 は、水平及び垂直同期信号 H、V とクロック信号 C L K とを用いて、デジタルビデオデータ R i G i B i の表示位置を判断する。 20

データ処理部 204 は、ヒストグラム分析部 205 から入力されるヒストグラム分析結果とメモリから入力される第 2 補償値とを用いて、入力映像の輝度成分 Y を選択的に変調して、コントラスト比が選択的に強調された輝度成分 Y M を出力する。

【0091】

遅延部 202 は、データ処理部 204 で変調された輝度成分 Y M が生成されるまで、色差成分 U、V を遅延させて、輝度 / カラーミキシング部 203 に入力される変調された輝度成分 Y M と色差成分 U D、V D とを同期させる。

【0092】

輝度 / カラーミキシング部 203 は、変調された輝度成分 Y M と遅延された色差成分 U D、V D とを用いて、変調デジタルビデオデータ A I (RGB) を算出する。 30

【0093】

バックライト制御部 206 は、ヒストグラム分析部 205 から入力されるヒストグラム分析結果と、デジタルビデオデータ R i G i B i のそれぞれの表示位置判定結果とに基づいて調光制御信号 D i m を異なるように発生して、データ処理部 204 によりコントラスト比が強調されたデータ A I (RGB) の表示面に光を照射するバックライト光源の輝度を調整する。

【0094】

インバータ 207 は、調光制御信号 D i m に応じてバックライト光源の各々に供給される駆動交流電源のデューティー比（又は点灯及び消灯比）を異なるように制御して、表示映像の輝度に応じてバックライト輝度を異なるように制御する。 40

【0095】

このような第 2 変調部は、本願出願人により既出願された韓国特許出願第 10-2003-0099334 号、第 10-2004-0030334 号、第 10-2003-0041127 号、第 10-2004-0078112 号、第 10-2003-0099330 号、第 10-2004-0115740 号、第 10-2004-0049637 号、第 10-2003-0040127 号、第 10-2003-0081171 号、第 10-2004-0030335 号、第 10-2004-0049305 号、第 10-2003-0081174 号、第 10-2003-0081175 号、第 10-2003-0081172 号、第 10-2003-0080177 号、第 10-2003-0081173 号、第 10-2004-0030336 号等に開示された変調方式を用いて、液晶表示パネ 50

ル30のコントラスト比を上げることができる。

【0096】

図17において、イメージ処理部64cは、解像度の変換による画質の低下を、信号補間法により補償することによって、入力映像のイメージを処理する。また、イメージ処理部64cは、液晶表示パネル30の解像度に合う垂直/水平同期信号H.V sync、データイネーブル信号DE及びクロック信号DCLKを生成する。

【0097】

直流-直流変換器38は、液晶表示パネル30において必要とされる駆動電圧を発生する。直流-直流変換器38から発生する駆動電圧は、ゲートハイ電圧VGH、ゲートロー電圧VGL、共通電圧Vcom、高電位電源電圧VDD、低電位電源電圧VSS、高電位電源電圧VDDと低電位電源電圧VSSとの間で分圧される複数のガンマ基準電圧などを含む。ガンマ基準電圧は、デジタルビデオデータRGBroad、RGBevenのビット数で表現可能な階調数分だけデータIIC32A、32B内で各階調に該当するアナログガンマ補償電圧に細分化される。ゲートハイ電圧VGH、ゲートロー電圧VGLは、スキャンパルスのスイング電圧である。このような駆動電圧は、ケーブル68を経由してコントロールPCB40上の信号配線46に供給される。

10

【0098】

システムボード40上に実装された直流-直流変換器38から発生された駆動電圧は、直流-直流変換器の出力端子、ケーブル68、信号配線46、1ポート接続配線44及びFFC43を経由して、第1ソースPCB41Aに接続された第1データIIC32Aに送信される。また、駆動電圧は、直流-直流変換器の出力端子、ワイヤーケーブル、信号配線46、第1ソースPCB41A、ソースCOF42のダミー配線48、及び液晶表示パネル30のLOG配線45を経由して、第2ソースPCB41Bに接続された第2データIIC32Bに送信される。

20

【0099】

このように、本発明の第2の実施の形態に係る液晶表示装置は、従来のコントロールPCBにより行なわれた一部機能、すなわち、液晶表示パネル30の応答特性及びコントラスト比のうち、少なくともいずれか1つを調整するために、所定の補償値でデジタル映像データを変調する機能と液晶表示パネル30の駆動に必要な駆動電圧を発生する回路をシステムボード60に実装する。したがって、本発明の第2の実施の形態に係る液晶表示装置は、コントロールPCB40の大きさを大幅に減少させることができる。

30

【0100】

上述のように、本発明の第2の実施の形態に係る液晶表示装置は、ソースPCBを分割し、コントロールPCBの一部機能をシステムボードに統合させ、かつタイミングコントローラーの出力ポートをシングル出力ポートで構成してコントロールPCBの大きさと出力ピン数を減らすことによって、工程時間の縮小、製造費用の低減及び液晶表示装置の薄型化を可能にする。

30

【0101】

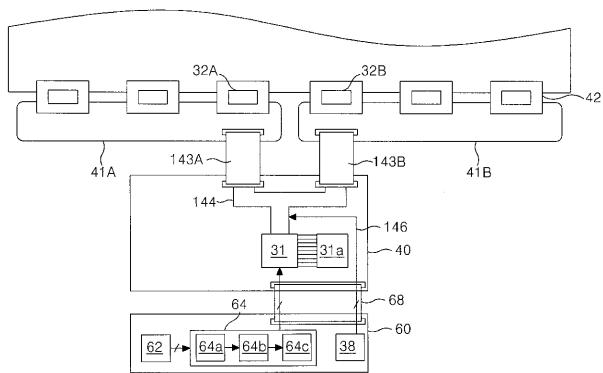

次に、図22を用いて、本発明の第3の実施の形態に係る液晶表示装置を説明する。

本発明の第3の実施の形態に係る液晶表示装置は、従来の技術においてコントロールPCB上に実装されたすべての構成要素をシステムボード60内に集積する。

40

【0102】

図22に示すように、システムボード60上には、タイミングコントローラー31、EEPROM31a、液晶表示パネル30の駆動電圧を発生するための直流-直流変換器38などの回路が含まれている。また、システムボード60は、外部機器から入力される多様な属性の映像データを供給するためのインターフェース回路62を含む。また、システムボード60上には、アナログデータをデジタルデータに変換し、液晶表示パネル30の解像度に合うように入力データの解像度を変換するためのスケーラーと、信号補間(Signal Interpolation)とイメージ処理のためのイメージ処理回路などを含むグラフィック処理回路64が実装される。このように、本発明の第3の実施の形態に

50

係る液晶表示装置は、従来の技術においてコントロールP C B上に実装されたタイミングコントローラー、E E P R O M、及び直流-直流変換器などを、システムボード60上に実装して、既存のコントロールP C Bとシステムボードとを1つのボードに統合する。したがって、本発明の第3の実施の形態に係る液晶表示装置は、既存のコントロールP C Bとシステムボードとを接続したワイヤーケーブルを除去できるので、製造費用の低減、工程時間の減少及び液晶表示装置の薄型化を可能にする。

【0103】

図22において、FFC143は、システムボード40と第1ソースP C B41Aとを電気的に接続する。このFFC143は、タイミングコントローラー31から生成されたデジタルビデオデータR G B o d d、R G B e v e n及びタイミング制御信号と、直流-直流変換器38から生成された駆動電圧を、第1ソースP C B41AのデータI C32Aに伝達する。

10

【0104】

次に、図23～図26を用いて、本発明の第4の実施の形態に係る液晶表示装置を説明する。

【0105】

以下、本発明の第4の実施の形態に係る液晶表示装置の構成のうち、前述の実施の形態と実質的に同じ構成については、同じ図面符号を付し、それについての詳細な説明は省略する。

20

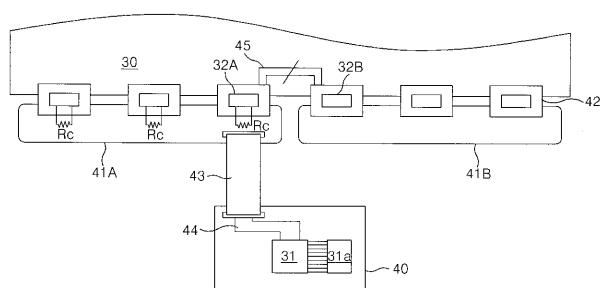

【0106】

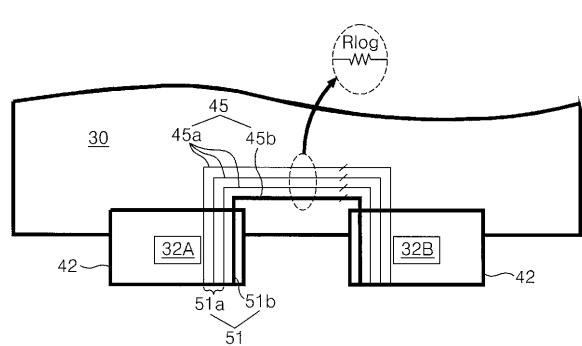

図23は、本発明の第4の実施の形態に係る液晶表示装置において、タイミングコントローラーとデータI Cとの接続構造を詳細に示す図である。図24は、ソースC O Fに形成されたダミー配線と液晶表示パネル30の基板上に形成されたL O G配線とを示す図である。

20

【0107】

図23及び図24に示すように、L O G配線45は、大きなライン抵抗を有し、そのライン抵抗の合計を「R l o g」とすれば、第2ソースP C B41Bから供給される駆動電圧は、L O G抵抗R l o gにより電圧降下して、第1ソースP C B41Aから供給される信号電圧に比べて小さくなる。したがって、第1ソースP C B41Aに接続されたソースC O F42のそれぞれに実装された第1データI C32Aには、第2データI C32Bに供給される信号電圧の電圧降下分だけ第1ソースP C B41Aから供給される駆動電圧を下げるために、補償抵抗R cが接続される。この補償抵抗R cにより、データI C32Aに供給される電圧とデータI C32Bに供給される駆動電圧とが同様になる。

30

【0108】

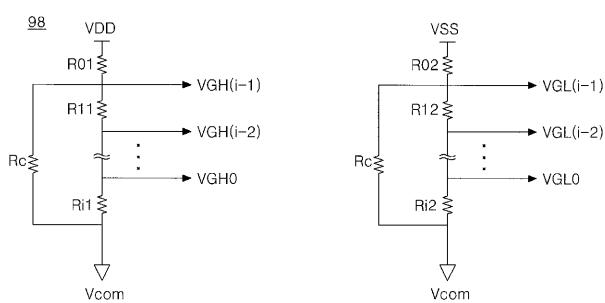

図25及び図26は、第1データI C32Aを詳細に示す回路図である。

【0109】

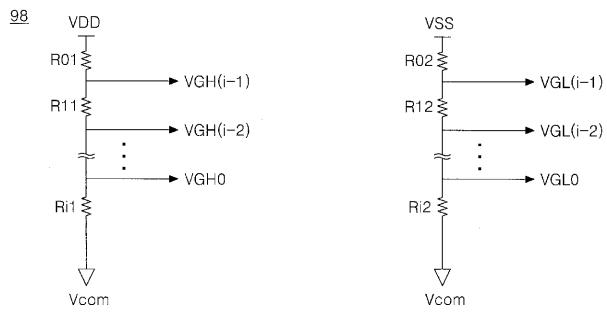

図25及び図26に示すように、第1データI C32Aのそれぞれは、シフトレジスタ91、データ復元部92、第1ラッチアレイ93、第2ラッチアレイ94、D A C95、チャージシェア回路96、出力回路97及びガンマ補償電圧発生部98を含む。

40

【0110】

ガンマ補償電圧発生部98は、図26のように、共通電圧V c o mを間に隔てて高電位電源電圧V D Dと低電位電源電圧V S Sとの間で分圧される複数のガンマ基準電圧をデジタルビデオデータR G B o d d、R G B e v e nのビット数で表現可能な階調数(i)の分だけ、さらに細分化して、各階調に該当する正極性ガンマ補償電圧V G H 0～V G H(i-1)と負極性ガンマ補償電圧V G L 0～V G L(i-1)を発生する。このために、ガンマ補償電圧発生部98は、高電位電源電圧V D Dと低電位電源電圧V S Sとの間に互いに直列に接続された複数の分圧用抵抗R 0 1～R i 1、R 0 2～R i 2を含む抵抗ストリング(S t r i n g)を備える。抵抗ストリングに並列に接続された補償抵抗R cは、正極性ガンマ補償電圧V G H 0～V G H(i-1)と負極性ガンマ補償電圧V G L 0～V G L(i-1)の大きさを下げる機能を果たす。この補償抵抗R cは、第1ソースP C B

50

41Aに接続された第1データIC32Aのそれぞれの抵抗ストリングに並列に接続される。この補償抵抗Rcの大きさは、図5のLOG配線45の等価抵抗R<sub>10g</sub>による電圧降下分を考慮して、第1ソースPCB41Aに接続された第1データIC32Aのそれから発生するガンマ補償電圧の大きさと、第2ソースPCB41Bに接続された第2データIC32Bのそれから発生するガンマ補償電圧の大きさが、互いに同一階調のデータにおいて同じになるように設定されなければならない。

【0111】

一方、第2データIC32Bは、ガンマ補償電圧発生部98を除外すれば、第1データIC32Aと実質的に同じ構成を有する。図面には示していないが、第2データIC32Bのガンマ補償電圧発生部は、分圧用抵抗ストリングで構成され、抵抗ストリングに並列に接続された補償抵抗を必要としない。

10

【0112】

次に、図27～図29を用いて、本発明の第5の実施の形態に係る液晶表示装置を説明する。

図27は、本発明の第5の実施の形態に係る液晶表示装置を示す。この実施の形態5において、前述した実施の形態と同じ構成要素については、同じ図面符号を付し、それについての詳細な説明を省略する。

【0113】

図27に示すように、ソースCOF42は、第1及び第2ソースPCB41A、41Bに分けて接続される。ソースCOF42には、データタイミング制御信号と駆動電圧を送信するダミー配線51が形成される。ダミー配線51は、デジタルビデオデータRGBodd、RGBevenとキャリー信号を含むデータタイミング制御信号を送信する第1ダミー配線51aと、高電位電源電圧VDD、低電位電源電圧VSS、及びガンマ基準電圧(Gamma reference voltages)などの駆動電圧を送信する第2ダミー配線51bとに分けられる。

20

【0114】

本発明の第5の実施の形態では、駆動電圧を送信する第2ダミー配線51bの線幅を、データタイミング制御信号を送信する第1ダミー配線51aの線幅より広くする。また、第2ダミー配線51bと電気的に接続される第2LOG配線45bの線幅も、第1ダミー配線51aと電気的に接続される第1LOG配線45aの線幅より広くする。抵抗の大きさは、長さに比例し、単位面積に反比例するので、第2ダミー配線51bの線幅を広くするとき、それだけLOGライン抵抗R<sub>10g</sub>による電圧降下量が減少する。第1ダミー配線51aは、デジタルビデオデータRGBodd、RGBevenとキャリー信号とを含むデータタイミング制御信号を送信するので、第1LOG配線45aのライン抵抗に影響を受けない。

30

【0115】

図28及び図29は、図27に示す第1データIC32Aを詳細に示す回路図である。

【0116】

図28及び図29に示すように、第1データIC32Aのそれぞれは、シフトレジスタ91、データ復元部92、第1ラッチアレイ93、第2ラッチアレイ94、DAC95、チャージシェア回路96、出力回路97及びガンマ補償電圧発生部98を含む。

40

【0117】

ガンマ補償電圧発生部98は、共通電圧Vcomを隔てて高電位電源電圧VDDと低電位電源電圧VSSとの間で分圧される複数のガンマ基準電圧をデジタルビデオデータRGBodd、RGBevenのビット数で表現可能な階調数(i)の分だけ、さらに細分化して、各階調に該当する正極性ガンマ補償電圧VGH0～VGH(i-1)と負極性ガンマ補償電圧VGL0～VGL(i-1)とを発生する。このために、ガンマ補償電圧発生部98は、高電位電源電圧VDDと低電位電源電圧VSSとの間で互いに直列に接続された複数の分圧用抵抗R01～Ri1、R02～Ri2を含む抵抗ストリング(String)を備える。一方、図示していないが、第2データIC32Bは、第1データIC32

50

A と実質的に同じ構成を有する。

【0118】

次に、図30、図31を用いて、本発明の第6の実施の形態に係る液晶表示装置を説明する。

図30は、本発明の第6の実施の形態に係る液晶表示装置において、液晶表示パネル30、データ駆動回路32及びタイミングコントローラー31の組み立て状態を示す図である。

【0119】

図30に示すように、データ駆動回路32は、複数のデータIC32A、32Bを含む。複数のデータIC32A、32Bは、ソースCOF42にそれぞれ実装される。ソースCOF42は、2つに分割された第1及び第2ソースPCB41A、41Bに分けられて接続される。ソースCOF42の入力端子は、第1及び第2ソースPCB41A、41Bの出力端子に電気的に接続され、第1及び第2ソースCOF42の出力端子は、ACFを介して液晶表示パネル30の下部ガラス基板に形成されたデータパッドに電気的に接続される。第1及び第2ソースPCB41A、41Bには、デジタルビデオデータRGBroad、RGBevenが送信されるバス配線、データタイミング制御信号が送信されるバス配線、及び駆動電圧が送信されるバス配線が形成される。

10

【0120】

第1ソースPCB41Aの入力端子は、第1FFC43Aを経由してコントロールPCB40上に形成された2ポート接続配線44に接続される。第2ソースPCB41Bの入力端子は、第2FFC43Bを経由してコントロールPCB40上に形成された2ポート接続配線44に接続される。

20

【0121】

コントロールPCB40には、タイミングコントローラー31、EEPROM31a、液晶表示パネル30の駆動電圧を発生するための直流-直流変換器などの回路と共に、2ポート接続配線44が形成される。直流-直流変換器から生成される駆動電圧は、ゲートハイ電圧VGH、ゲートロー電圧VGL、共通電圧Vcom、高電位電源電圧VDD、低電位電源電圧VSS、高電位電源電圧VDDと低電位電源電圧VSSとの間で分圧される複数のガンマ基準電圧などを含む。ガンマ基準電圧は、デジタルビデオデータRGBroad、RGBevenのビット数で表現可能な階調数の分だけ、データIC32A内で分圧されて、各階調に該当するアナログガンマ補償電圧に細分化される。ゲートハイ電圧VGH、ゲートロー電圧VGLは、スキャンパルスのスイング電圧である。EEPROM31aは、タイミングコントローラー31から生成されるタイミング制御信号に対する波形オプション情報が複数のモード別に格納されて、ユーザからの命令に応じて該当モードで波形情報をタイミングコントローラー31に供給する。タイミングコントローラー31は、EEPROM31aからの波形オプション情報に応じて、各々のモードで互いに異なる形態でタイミング制御信号を生成する。

30

【0122】

コントロールPCB40に形成された2ポート接続配線44は、「Y」字状にパターニングされて、図9に示すタイミングコントローラー31のシングル出力ポート63を第1及び第2FFC43A、43Bに接続する。この2ポート接続配線44を介してタイミングコントローラー31から生成されたデジタルビデオデータRGBroad、RGBeven及びタイミング制御信号と、直流-直流変換器から生成された駆動電圧が、第1及び第2FFC43A、43Bに供給される。

40

【0123】

図31は、タイミングコントローラー31とデータIC32A、32Bとの間の信号送信経路を示す。

【0124】

図31に示すように、タイミングコントローラー31によりminim-LVDS方式又はRS-DS方式で変調されたデジタルビデオデータのうち、左側データRGBroad、R

50

GBevenは、タイミングコントローラー31のシングル出力ポート63、2ポート接続配線44、及び第1FFC43Aを経由して、第1ソースPCB41Aに接続された第1データIC32Aに送信される。左側データRGBoodd、RGBevenは、液晶表示パネル30の左半部の画面に表示されるデータである。タイミングコントローラー31によりmini-LVDS方式又はRSDS方式で変調された右側データRGBoodd、RGBevenは、タイミングコントローラー31のシングル出力ポート63、2ポート接続配線44、及び第2FFC43Bを経由して、第2ソースPCB41Bに接続された第2データIC32Bに送信される。右側データRGBoodd、RGBevenは、液晶表示パネル30の右半部の画面に表示されるデータである。

## 【0125】

第1番目のデータをサンプリングする最右側の第1データIC32Bは、図10及び図11においてスタートパルス以後のデータを自身の出力チャネル数分だけサンプリングした後に、その次のデータのサンプリングタイミングを指示するキャリー信号Carryを発生して、隣接した第2データIC32Bに供給する。同様に、キャリー信号Carryは、隣接したデータIC32A、32Bに順次伝達される。第1及び第2ソースPCB41A、41Bの間でキャリー信号Carryは、第2FFC43B、コントロールPCB40上に形成された2ポート接続配線44及び第1FFC43Aを経由して送信される。一方、データIC32A、32Bのデータサンプリング方向は、反対に調整されうる。この場合、第1及び第2ソースPCB41A、41Bの間でキャリー信号Carryは、第1FFC43A、2ポート接続配線44及び第2FFC43Bを経由して、反対方向に送信される。

10

20

## 【0126】

コントロールPCB40上に実装された直流-直流変換器から発生する駆動電圧は、2ポート接続配線44、第1FFC43A及び第2FFC43Bを経由して、すべてのデータIC32A、32Bに同時に供給される。

## 【0127】

次に、図32、図33を用いて、本発明の第7の実施の形態に係る液晶表示装置を説明する。

図32は、本発明の第7の実施の形態に係る液晶表示パネル30、データ駆動回路32及びタイミングコントローラー31の組み立て状態を示す。

30

## 【0128】

図32に示すように、データ駆動回路32は、複数の第1及び第2データIC32A、32Bを含む。

## 【0129】

複数のデータIC32A、32Bは、ソースCOF42にそれぞれ実装される。ソースCOF42の代わりにソースTCP(Tape Carrier Package)を適用することもできる。ソースCOF42は、2つに分割された第1及び第2ソースPCB41A、41Bに分けられて接続される。ソースCOF42の入力端子は、第1及び第2ソースPCB41A、41Bの出力端子に電気的に接続され、ソースCOF42の出力端子は、ACFを介して液晶表示パネル30の下部ガラス基板に形成されたデータパッドに電気的に接続される。第1及び第2ソースPCB41A、41Bには、デジタルビデオデータRGBoodd、RGBevenが送信されるバス配線、キャリー信号を含むデータタイミング制御信号が送信されるバス配線、及び駆動電圧が送信されるバス配線が形成される。

40

## 【0130】

第1ソースPCB41Aの入力端子は、Y型FFC(Flexible Flat Cabil)の第1出力段43AとY型FFCの共通入力段43Cを経由して、システムボード60と電気的に接続される。第2ソースPCB41Bの入力端子は、Y型FFCの第2出力段43BとY型FFCの共通入力段43Cとを経由して、システムボード60と電気的に接続される。

50

## 【0131】

システムボード60上には、タイミングコントローラー31、EEPROM31a、液晶表示パネル30の駆動電圧を発生するための直流-直流変換器38などの回路が含まれている。また、システムボード40上には、インターフェース回路62とグラフィック処理回路64とが実装される。このように、本発明の第7の実施の形態に係る液晶表示装置は、従来の技術においてコントロールPCB上に実装されたタイミングコントローラー、EEPROM、及び直流-直流変換器などをシステムボード60上に実装して、従来のコントロールPCBとシステムボードとを1つのボードに統合する。

## 【0132】

システムボード60と第1及び第2ソースPCB41A、41Bとを電気的に接続するFFCは、Y字状を有する。このY型FFCの共通入力段43Cを経由してタイミングコントローラー31から生成されたデジタルビデオデータRGBroad、RGBeven及びタイミング制御信号と、直流-直流変換器38から生成された駆動電圧が第1及び第2ソースPCB41A、41BのデータIC32A、32Bに伝達される。

10

## 【0133】

図33は、本発明の第7の実施の形態に係る液晶表示装置において、タイミングコントローラー31とデータIC32a、32bとの間の信号送信経路を示す。

## 【0134】

図33に示すように、タイミングコントローラー31によりmini-LVDS方式又はRS-422方式で変調されたデジタルビデオデータのうち、右側データRGBroad、RGBevenは、タイミングコントローラー31のシングル出力ポート63、Y型FFCの共通入力段43C、及びY型FFCの一方の出力段43Aを経由して、第1ソースPCB41Aに接続された第1データIC32Aに送信される。右側データRGBroad、RGBevenは、液晶表示パネル30の右半部の画面に表示されるデータである。タイミングコントローラー31によりmini-LVDS方式又はRS-422方式で変調された左側データRGBroad、RGBevenは、タイミングコントローラー31のシングル出力ポート63、Y型FFCの共通入力段43C、及びY型FFCの他側出力段43Bを経由して、第2ソースPCB41Bに接続された第2データIC32Bに送信される。左側データRGBroad、RGBevenは、液晶表示パネル30の左半部の画面に表示されるデータである。

20

## 【0135】

タイミングコントローラー31から発生するデータタイミング制御信号は、データと共にタイミングコントローラー31のシングル出力ポート63、Y型FFCの共通入力段43C、及びY型FFCの一方の出力段43Aを経由して、第1ソースPCB41Aに接続された第1データIC32Aに送信される。また、データタイミング制御信号は、タイミングコントローラー31のシングル出力ポート63、Y型FFCの共通入力段43C、及びY型FFCの他側出力段43Bを経由して、第2ソースPCB41Bに接続された第2データIC32Bに送信される。

30

## 【0136】

第1番目のデータをサンプリングする最右側のデータIC32Bは、スタートパルス以後のデータを自身の出力チャネル数分だけサンプリングした後に、その次のデータのサンプリングタイミングを指示するキャリー信号Carryを発生して、右側に直に隣接するデータIC32Bに供給する。同様に、キャリー信号Carryは、隣接したデータIC32A、32Bに順次伝達される。第1及び第2ソースPCB41A、41Bの間でキャリー信号Carryは、Y型FFCの他側43B、Y型FFCの一側43Aを経由して送信される。データIC32A、32Bのデータサンプリング方向は、反対に調整されうる。この場合、第1及び第2ソースPCB41A、41Bの間でキャリー信号Carryは、反対方向に送信される。

40

## 【0137】

システムボード60上に実装された直流-直流変換器38から発生される駆動電圧は、

50

直流 - 直流変換器の出力端子 73、Y型 FCC の共通入力段 43C、及び Y型 FCC の一侧出力段 43A を経由して、第 1 ソース PCB 41A に接続された第 1 データ I C 32A に送信される。また、駆動電圧は、直流 - 直流変換器の出力端子 73、Y型 FCC の共通入力段 43C、及び Y型 FCC の他側出力段 43B を経由して、第 2 ソース PCB 41B に接続された第 2 データ I C 32B に送信される。

#### 【0138】

次に、図 34、図 35 を用いて、本発明の第 8 の実施の形態に係る液晶表示装置を説明する。

図 34 は、本発明の第 8 の実施の形態に係る液晶表示装置において、液晶表示パネル 30、データ駆動回路 32、タイミングコントローラー 31 及びグラフィック処理回路 64 の組み立て状態を示す。図 35 は、図 32 に示す液晶表示装置の信号の送信経路を示す。

#### 【0139】

図 34 及び図 35 に示すように、コントロール PCB 40 には、タイミングコントローラー 31、EEPROM 31a と共に、2 ポート接続配線 144 が形成される。EEPROM 31a は、タイミングコントローラー 31 から生成されるタイミング制御信号に対する波形オプション情報が複数のモード別に格納されて、ユーザからの命令に応じて該当モードで波形情報をタイミングコントローラー 31 に供給する。タイミングコントローラー 31 は、EEPROM 31a からの波形オプション情報に応じて、各々のモードで互いに異なる形態でタイミング制御信号を生成する。

#### 【0140】

システムボード 60 上には、外部機器から入力される多様な属性の映像データを供給されるためのインターフェース回路 62、インターフェース回路 62 からの映像データを液晶表示パネル 30 に合うように変調するグラフィック処理回路 64、及び液晶表示パネル 30 の駆動に必要な駆動電圧を発生する直流 - 直流変換器 38 などが形成される。

#### 【0141】

上述のように、本発明の液晶表示装置は、ソース PCB を分割しタイミングコントローラーの出力ポートをシングル出力ポートで構成して、コントロール PCB の大きさと出力ピン数を減らすことができる。また、本発明の実施の形態に係る液晶表示装置は、液晶表示パネルに形成された LOG 配線を用いて 1 つの FCC を除去することによって、ソース PCB とコントロール PCB との接続構造を単純化でき、かつ部品数を減らすことができる。

#### 【0142】

また、本発明の液晶表示装置は、FCC を介して直接コントロール PCB から駆動信号を供給される第 1 ソース PCB のデータ I C 内に各々補償抵抗を並列に接続することによって、LOG 配線を介して駆動信号が供給される第 2 ソース PCB と前記第 1 ソース PCB との間のガンマ補償電圧の偏差をなくすことができる。

#### 【0143】

また、本発明の液晶表示装置は、ソース COF 又はソース TCP に形成されて、駆動電圧を送信するダミー配線の線幅を、データタイミング制御信号を送信する他のダミー配線の線幅より広く形成する。その結果、LOG 配線抵抗による電圧降下分を最小にして、第 1 ソース PCB と第 2 ソース PCB との間のガンマ補償電圧の偏差をなくすことができる。

#### 【図面の簡単な説明】

#### 【0144】

【図 1】液晶表示装置の液晶セルを示す回路図である。

【図 2】シングルソース PCB を有する液晶表示装置を示す図である。

【図 3】タイミングコントローラーの出力ポートをデュアル出力ポートで構成し、その出力ポートに接続されたデュアルソース PCB を示す図である。

【図 4】タイミングコントローラーの出力ポートをデュアル出力ポートで構成し、その出力ポートに接続されたデュアルソース PCB を示す図である。

10

20

30

40

50

【図 5】本発明に係る液晶表示装置を示すブロック図である。

【図 6】本発明に係る液晶表示装置を示すブロック図である。

【図 7】図 5 に示すタイミングコントローラーとデータ I C との接続構造を詳細に示す図である。

【図 8】ソース C O F に形成されたダミー配線と液晶表示パネルの基板上に形成された L O G 配線を示す平面図である。

【図 9】図 5 ~ 図 7 に示すタイミングコントローラーのデータ処理部を詳細に示すブロック図である。

【図 10】図 9 に示すデータ変調部の出力信号の一例を示す波形図である。

【図 11】図 9 に示すデータ変調部の出力信号の一例を示す波形図である。

【図 12】図 7 に示すタイミングコントローラーとデータ I C との間の信号の送信経路を示す図である。

【図 13】本発明の第 1 の実施の形態に係る液晶表示装置の他の接続構造を示すブロック図である。

【図 14】図 7 に示すデータ I C を詳細に示すブロック図である。

【図 15】図 14 に示す D A C を詳細に示す回路図である。

【図 16】図 7 に示すタイミングコントローラー、第 1 ソース P C B に接続されたデータ I C 、第 2 ソース P C B に接続されたデータ I C とその間の抵抗を等価的に示す回路図である。

【図 17】本発明の第 2 の実施の形態に係る液晶表示装置を示す図である。

【図 18】図 17 に示すデータ変調部により変調されるデータ電圧の例を示す図である。

【図 19】図 17 に示すデータ変調部の第 1 の実施の形態を示すブロック図である。

【図 20】図 17 に示すデータ変調部の第 2 の実施の形態を示すブロック図である。

【図 21】図 20 に示すヒストグラム分析部のヒストグラム分析結果の一例を示す図である。

【図 22】本発明の第 3 の実施の形態に係る液晶表示装置を示す図である。

【図 23】本発明の第 4 の実施の形態に係る液晶表示装置を示す図である。

【図 24】本発明の第 4 の実施の形態に係る液晶表示装置において L O G 配線の抵抗を示す図である。

【図 25】第 1 データ I C を詳細に示すブロック図である。

【図 26】図 25 に示すガンマ補償電圧発生部を詳細に示す回路図である。

【図 27】本発明の第 5 の実施の形態に係る液晶表示装置を示す図である。

【図 28】第 1 データ I C を詳細に示すブロック図である。

【図 29】図 28 に示すガンマ補償電圧発生部を詳細に示す回路図である。

【図 30】本発明の第 6 の実施の形態に係る液晶表示装置を示す図である。

【図 31】図 30 に示す液晶表示装置の信号の送信経路を示す図である。

【図 32】本発明の第 7 の実施の形態に係る液晶表示装置を示す図である。

【図 33】図 32 に示す液晶表示装置の信号の送信経路を示す図である。

【図 34】本発明の第 8 の実施の形態に係る液晶表示装置を示す図である。

【図 35】図 34 に示す液晶表示装置の信号の送信経路を示す図である。

【符号の説明】

【0 1 4 5】

3 0 液晶表示パネル、3 1 タイミングコントローラー、3 2 データ駆動回路、3 3 ゲート駆動回路、3 4 ポート拡張部、3 5 データ変調部、3 6 グラフィック処理回路、3 8 直流 - 直流変換器、4 0 システムボード、4 1 A 第 1 ソース P C B 、4 1 B 第 2 ソース P C B 、4 2 A 、4 2 B ソース C O F 、6 0 システムボード、6 2 インタフェース回路、6 4 グラフィック処理回路、6 4 a アナログ - デジタル変換部、6 4 b スケーラー部、6 4 c イメージ処理部、9 1 シフトレジスタ、9 2 データ復元部、9 3 、9 4 ラッチアレイ、9 6 チャージシェア回路、9 7 出力回路、9 8 ガンマ補償電圧発生部、1 0 1 、1 0 2 デコーダ、1 0 3 マルチプレクサ、

10

20

30

40

50

111 フレームメモリ、113 ルックアップテーブル、201 色分離部、202

遅延部、203 カラーミキシング部、204 データ処理部、205 ヒストグラム分析部、206 バックライト制御部、207 インバータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

データライン

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図 2 9】

【図 3 1】

【図 3 0】

【図 3 2】

【図 3 3】

【図 3 5】

【図 3 4】

---

フロントページの続き

(31) 優先権主張番号 10-2007-0030454

(32) 優先日 平成19年3月28日(2007.3.28)

(33) 優先権主張国 韓国(KR)

(31) 優先権主張番号 10-2007-0046113

(32) 優先日 平成19年5月11日(2007.5.11)

(33) 優先権主張国 韓国(KR)

(31) 優先権主張番号 10-2007-0046126

(32) 優先日 平成19年5月11日(2007.5.11)

(33) 優先権主張国 韓国(KR)

(72) 発明者 ホンソン・ソン

大韓民国、キョンブク、クミ-シ、クピョン-ドン 474-7、ブヨン・アパートメント 80

3-706

(72) 発明者 ウンギ・ミン

大韓民国、テグ、ブク-グ、トンチョン-ドン 891、トンフワゴールデンヴィル 103-1

205

(72) 発明者 ビヨンジン・チェ

大韓民国、キョンブク、クミ-シ、トリヤン-ドン 224、トリヤンヒューマンシア 403-

303

(72) 発明者 ドンファン・チャ

大韓民国、キョンブク、クミ-シ、チンピョン-ドン 98ビー、イネイジュゴン・アパートメン

ト 202-1509

(72) 発明者 ソヨク・チャン

大韓民国、テグ、ブク-グ、トンチョン-ドン、ヨンナムセカンドタウン 103-902

F ターム(参考) 2H092 GA32 GA40 GA51 GA55 JA24 KA03 NA25 NA27 PA06

|                |                                                                                                                                                                                                                       |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶表示装置                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2008233869A</a>                                                                                                                                                                                         | 公开(公告)日 | 2008-10-02 |

| 申请号            | JP2007341171                                                                                                                                                                                                          | 申请日     | 2007-12-28 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | Eruji显示有限公司                                                                                                                                                                                                           |         |            |

| [标]发明人         | ホンソンソン<br>ウンギミン<br>ビヨンジンチエ<br>ドンフンチャ<br>ソヨクチャン                                                                                                                                                                        |         |            |

| 发明人            | ホンソン・ソン<br>ウンギ・ミン<br>ビヨンジン・チエ<br>ドンフン・チャ<br>ソヨク・チャン                                                                                                                                                                   |         |            |

| IPC分类号         | G02F1/1345 G02F1/1368                                                                                                                                                                                                 |         |            |

| CPC分类号         | G09G3/3648 G09G3/3406 G09G3/3611 G09G3/3688 G09G2300/0426 G09G2310/027 G09G2310/0281 G09G2320/0252 G09G2320/0646 G09G2330/06 G09G2340/16 G09G2360/16 G09G2370/08                                                      |         |            |

| F1分类号          | G02F1/1345 G02F1/1368 G02F1/133.520 G02F1/133.550                                                                                                                                                                     |         |            |

| F-TERM分类号      | 2H092/GA32 2H092/GA40 2H092/GA51 2H092/GA55 2H092/JA24 2H092/KA03 2H092/NA25 2H092/NA27 2H092/PA06 2H192/AA24 2H192/DA91 2H192/FA54 2H192/FB46 2H192/FB52 2H192/FB71 2H193/ZA04 2H193/ZF42 2H193/ZF51 2H193/ZF52      |         |            |

| 代理人(译)         | 英年古河<br>Kajinami秩序<br>上田俊一                                                                                                                                                                                            |         |            |

| 优先权            | 1020070026070 2007-03-16 KR<br>1020070030323 2007-03-28 KR<br>1020070030332 2007-03-28 KR<br>1020070030333 2007-03-28 KR<br>1020070030454 2007-03-28 KR<br>1020070046113 2007-05-11 KR<br>1020070046126 2007-05-11 KR |         |            |

| 其他公开文献         | JP4750780B2                                                                                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                             |         |            |

**摘要(译)**

要解决的问题：提供一种简化了控制PCB的液晶显示装置。 ŹSOLUTION：液晶显示装置包括：液晶显示面板30，包括第一和第二组数据线，与第一和第二组数据线交叉的多条栅极线，以及排列成矩阵的多个液晶单元;第一源PCB 41A，耦合到第一数据IC，以向第一组数据线提供数据;第二源PCB 41B，耦合到第二数据IC，以向第二组数据线提供数据;定时控制器31通过单个端口将视频数据输出到第一和第二数据IC，并通过单个端口输出用于控制第一和第二数据IC的定时控制信号。 Ź