(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-128092

(P2007-128092A)

(43) 公開日 平成19年5月24日(2007.5.24)

(51) Int.C1.

G02F 1/1362 (2006.01)

F 1

G02F 1/1362

テーマコード(参考)

2 H 0 9 2

審査請求 未請求 請求項の数 13 O L (全 22 頁)

(21) 出願番号 特願2006-299548 (P2006-299548)

(22) 出願日 平成18年11月2日 (2006.11.2)

(31) 優先権主張番号 10-2005-0104176

(32) 優先日 平成17年11月2日 (2005.11.2)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞416

(74) 代理人 100072349

弁理士 八田 幹雄

(74) 代理人 100110995

弁理士 奈良 泰男

(74) 代理人 100114649

弁理士 宇谷 勝幸

(74) 代理人 100129126

弁理士 藤田 健

(74) 代理人 100130971

弁理士 都築 正則

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】画面の染みの発生を防止した液晶表示装置を提供する。

【解決手段】本発明による液晶表示装置は、基板と、前記基板上に形成され、複数の画素を有する第1(PXr1)及び第2画素行(PXr2)と、前記基板上を行方向に伸び、前記第1画素行と接続される第1ゲート線と、前記基板上を行方向に伸び、前記第1画素行と接続され、前記第1ゲート線と隣接する第2ゲート線と、前記基板上を行方向に伸び、前記第2画素行と接続され、前記第2ゲート線と隣接する第3ゲート線と、前記基板上を行方向に伸び、前記第2画素行と接続され、前記第3ゲート線と隣接する第4ゲート線と、前記基板上に列方向に伸び、二つの画素列ごとに一つずつ配置される複数のデータ線と、前記第1及び第4ゲート線と接続され、前記第1及び第4ゲート線にゲート信号を印加する第1ゲート駆動部(400L)と、前記第2及び第3ゲート線と接続され、前記第2及び第3ゲート線にゲート信号を印加する第2ゲート駆動部(400R)とを有する。

【選択図】図3A

**【特許請求の範囲】****【請求項 1】**

基板と、

前記基板上に形成され、複数の画素を有する第1及び第2画素行と、

前記基板上を行方向に伸び、前記第1画素行と接続される第1ゲート線と、

前記基板上を行方向に伸び、前記第1画素行と接続され、前記第1ゲート線と隣接する第2ゲート線と、

前記基板上を行方向に伸び、前記第2画素行と接続され、前記第2ゲート線と隣接する第3ゲート線と、

前記基板上を行方向に伸び、前記第2画素行と接続され、前記第3ゲート線と隣接する第4ゲート線と、

前記基板上を列方向に伸び、二つの画素列ごとに一つずつ配置される複数のデータ線と、

前記第1及び第4ゲート線と接続され、前記第1及び第4ゲート線にゲート信号を印加する第1ゲート駆動部と、

前記第2及び第3ゲート線と接続され、前記第2及び第3ゲート線にゲート信号を印加する第2ゲート駆動部と、

を有する液晶表示装置。

**【請求項 2】**

前記第1及び第2ゲート線は前記第1画素行を間に挟んで上下に配置され、

前記第3及び第4ゲート線は前記第2画素行を間に挟んで上下に配置されることを特徴とする請求項1記載の液晶表示装置。

**【請求項 3】**

前記第1及び第2ゲート駆動部は前記基板上に集積されることを特徴とする請求項1記載の液晶表示装置。

**【請求項 4】**

前記第1ゲート駆動部と第2ゲート駆動部は、前記行方向に対して互いに反対側に位置することを特徴とする請求項1記載の液晶表示装置。

**【請求項 5】**

基板と、

前記基板上に形成され、複数の画素を有する複数の第1及び第2画素行と、

前記基板上を行方向に伸び、前記第1画素行と接続され、互いに前記第1画素行を挟んで隣接する第1上部ゲート線及び第1下部ゲート線からなる複数の第1ゲート線群と、

前記基板上を行方向に伸び、前記第2画素行と接続され、互いに前記第2画素行を挟んで隣接する第2上部ゲート線及び第2下部ゲート線からなる複数の第2ゲート線群と、

前記基板上に列方向に伸びて、二つの画素列ごとに一つずつ配置されている複数のデータ線と、

前記第1上部ゲート線及び前記第2下部ゲート線と接続されている第1ゲート駆動部と、

前記第1下部ゲート線及び前記第2上部ゲート線と接続されている第2ゲート駆動部と、

を有することを特徴とする液晶表示装置。

**【請求項 6】**

前記第1及び第2ゲート駆動部は前記基板上に集積されることを特徴とする請求項5記載の液晶表示装置。

**【請求項 7】**

前記第1ゲート駆動部と第2ゲート駆動部は、前記行方向に対して互いに反対側に位置することを特徴とする請求項5記載の液晶表示装置。

**【請求項 8】**

前記第1ゲート線群が一定数を単位として繰り返して配置され、次いで、前記第2ゲー

10

20

30

40

50

ト線群が一定数を単位として繰り返して配置されることを特徴とする請求項 5 記載の液晶表示装置。

【請求項 9】

前記第 1 ゲート線群と前記第 2 ゲート線群が交互に隣接することを特徴とする請求項 5 に記載の液晶表示装置。

【請求項 10】

前記データ線のうちの隣接した二つのデータ線の間に行方向に隣接して配列されている二つの画素は同一のデータ線に接続されることを特徴とする請求項 5 記載の液晶表示装置。

【請求項 11】

列方向に隣接した二つの画素は互いに異なるデータ線に接続されることを特徴とする請求項 5 記載の液晶表示装置。

【請求項 12】

前記二つのデータ線の間に行方向に隣接して配列されている二つの画素にデータ信号を供給する各スイッチング素子は、一方が前記第 1 上部ゲート線及び前記第 2 上部ゲート線に、他方が前記第 1 下部ゲート線及び前記第 2 下部ゲート線に各々接続されることを特徴とする請求項 11 記載の液晶表示装置。

【請求項 13】

前記データ線のうちの隣接した二つのデータ線の間に行方向に隣接して配列される二つの画素からなる単位画素対は、前記単位画素対を構成する二つの画素にそれぞれデータ信号を供給する各スイッチング素子の位置は同一であることを特徴とする請求項 5 記載の液晶表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は液晶表示装置に関するものである。

【背景技術】

【0002】

液晶表示装置は現在最も広く使用されている平板表示装置のうちの一つであって、画素電極と共に通電極といった電場生成用電極が形成されている二枚の表示板と、その間に入っている液晶層を有する。液晶表示装置は電場生成用電極に電圧を印加して液晶層に電場を生成し、これを通じて液晶層の液晶分子の配向を決めて、入射光の偏光を制御することによって映像を表示する。

【0003】

液晶表示装置はまた、各画素電極に接続されているスイッチング素子及びスイッチング素子を制御して画素電極に電圧を印加するためのゲート線とデータ線など複数の信号線を有する。ゲート線はゲート駆動回路が生成したゲート信号を伝達し、データ線はデータ駆動回路が生成したデータ電圧を伝達し、スイッチング素子はゲート信号によってデータ電圧を画素電極に伝達する。

【0004】

このようなゲート駆動回路及びデータ駆動回路は、複数の集積回路チップの形態で表示板に直接装着されたり、可撓性回路膜などに装着されて表示板に実装されたりするが、このような集積回路チップは液晶表示装置の製造費用における高い比率を占める。特に、データ駆動集積回路チップの場合、ゲート駆動回路チップに比べてその価格が非常に高いため、高解像度、大面積液晶表示装置の場合にはその個数を減らす必要がある。ゲート駆動回路の場合、ゲート線、データ線及びスイッチング素子と共に表示板に集積することによってその価格を減らすことができるが、データ駆動回路はその構造がやや複雑であるため、表示板に集積することが難しく、そのため、さらにその個数を減らす必要性が高い。

【0005】

一方、画素には信号線の重畠による寄生容量が存在するため、データ電圧が印加された

10

20

30

40

50

後、ゲートオン電圧がゲートオフ電圧になる瞬間に寄生容量によってキックバック電圧 (kickback voltage) が発生する。そのため、データ電圧が多少減少し、次いで、ゲートオン電圧がゲートオフ電圧に変わる瞬間にキックバック電圧によってさらに一度データ電圧が減少する。その結果、正極性と負極性の画素電圧に差が生じて、フリッカー (flicker) を誘発する一方、画面に染みが生じることもある。

【発明の開示】

【発明が解決しようとする課題】

【0006】

本発明が目的とする技術的課題は、画面の染みが発生することを防止することにある。

【課題を解決するための手段】

【0007】

本発明の液晶表示装置は、基板と、前記基板上に形成され、複数の画素を有する第1及び第2画素行と、前記基板上を行方向に伸び、前記第1画素行と接続されている第1ゲート線と、前記基板上を行方向に伸び、前記第1画素行と接続され、前記第1ゲート線と隣接する第2ゲート線と、前記基板上を行方向に伸び、前記第2画素行と接続され、前記第2ゲート線と隣接する第3ゲート線と、前記基板上を行方向に伸び、前記第2画素行と接続され、前記第3ゲート線と隣接する第4ゲート線と、前記基板上を列方向に伸び、二つの画素列ごとに一つずつ配置される複数のデータ線と、前記第1及び第4ゲート線と接続され、前記第1及び第4ゲート線にゲート信号を印加する第1ゲート駆動部と、前記第2及び第3ゲート線と接続され、前記第2及び第3ゲート線にゲート信号を印加する第2ゲート駆動部とを有する。

【0008】

前記第1及び第2ゲート線は、前記第1画素行を間に挟んで上下に配置され、前記第3及び第4ゲート線は前記第2画素行を間に挟んで上下に配置されてもよい。

【0009】

前記第1及び第2ゲート駆動部は前記基板上に集積されてもよい。

【0010】

前記第1ゲート駆動部と第2ゲート駆動部は、前記行方向に対して互いに反対側に位置することができる。

【0011】

本発明の他の実施形態による液晶表示装置は、基板と、前記基板上に形成され、複数の画素を有する複数の第1及び第2画素行と、前記基板上を行方向に伸び、前記第1画素行と接続され、互いに前記第1画素行を挟んで隣接する第1上部ゲート線及び第1下部ゲート線からなる複数の第1ゲート線群と、前記基板上を行方向に伸び、前記第2画素行と接続され、互いに前記第2画素行を挟んで隣接する第2上部ゲート線及び第2下部ゲート線からなる複数の第2ゲート線群と、前記基板上に列方向に伸びて、二つの画素列ごとに一つずつ配置されている複数のデータ線と、前記第1上部ゲート線及び前記第2下部ゲート線と接続されている第1ゲート駆動部と、前記第1下部ゲート線及び前記第2上部ゲート線と接続されている第2ゲート駆動部とを有することができる。

【0012】

前記第1及び第2ゲート駆動部は前記基板上に集積されてもよい。

【0013】

前記第1ゲート駆動部と第2ゲート駆動部は、前記行方向に対して互いに反対側に位置することができる。

【0014】

前記第1ゲート線群が一定数を単位として繰り返して配置され、次いで、前記第2ゲート線群が一定数を単位として繰り返して配置されてもよい。

【0015】

前記第1ゲート線群と前記第2ゲート線群が交互に隣接してもよい。

【0016】

10

20

30

40

50

前記データ線のうちの隣接した二つのデータ線の間に行方向に隣接して配列されている二つの画素は同一のデータ線に接続されてもよい。

【0017】

列方向に隣接した二つの画素は互いに異なるデータ線に接続されてもよい。

【0018】

前記二つのデータ線の間に行方向に隣接して配列されている二つの画素にデータ信号を供給する各スイッチング素子は、一方が前記第1上部ゲート線及び前記第2上部ゲート線に、他方が前記前記第1下部ゲート線及び前記第2下部ゲート線に各々接続されてもよい。

【0019】

前記データ線のうちの隣接した二つのデータ線の間に行方向に隣接して配列される二つの画素からなる単位画素対は、前記単位画素対を構成する二つの画素にそれぞれデータ信号を供給する各スイッチング素子の位置は同一であり得る。

【発明の効果】

【0020】

本発明により、各画素の輝度差による画面の染みが発生することを防止できる。

【発明を実施するための最良の形態】

【0021】

次に、本発明に係る液晶表示装置を実施するための最良の形態を、図面を参照しながら説明する。

【0022】

図面においては、多様な層及び領域を明確に表現するために厚さを拡大して表示している。明細書全体にわたって類似の部分に対しては同一の図面符号を付けた。層、膜、領域、板などの部分が他の部分の“上”にあるとする時、これは他の部分の“直上”にある場合だけでなく、その中間に他の部分がある場合も含む。反対に、ある部分が他の部分の“直上”にあるとする時には、中間に他の部分がないことを意味する。

【0023】

まず、図1、図2、図3Aを参照して、本発明の一実施形態による液晶表示装置について説明する。

【0024】

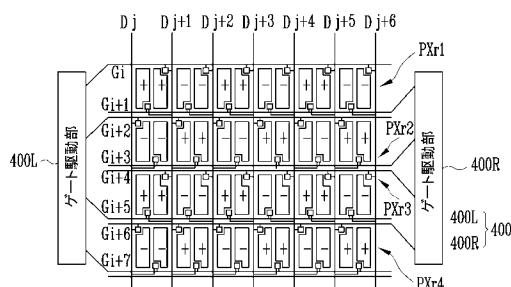

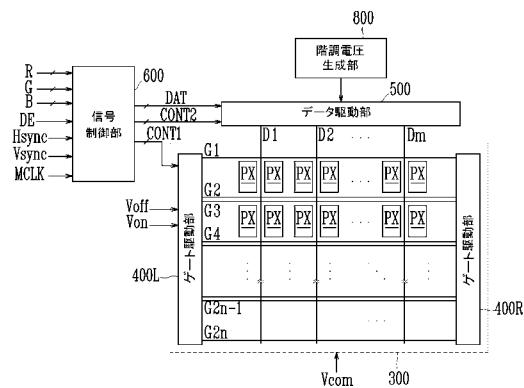

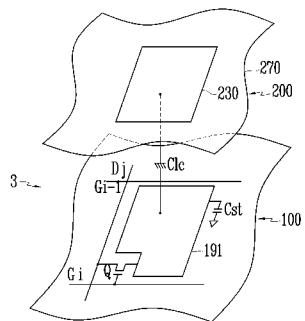

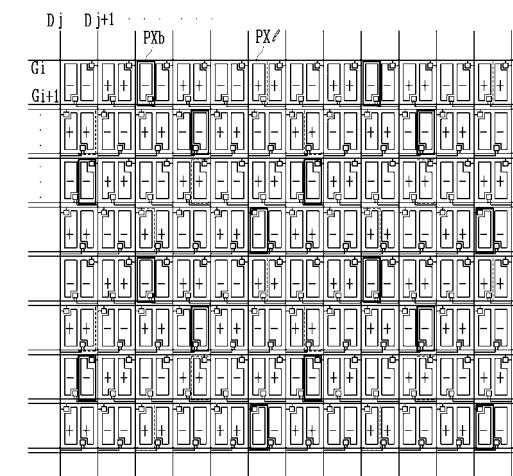

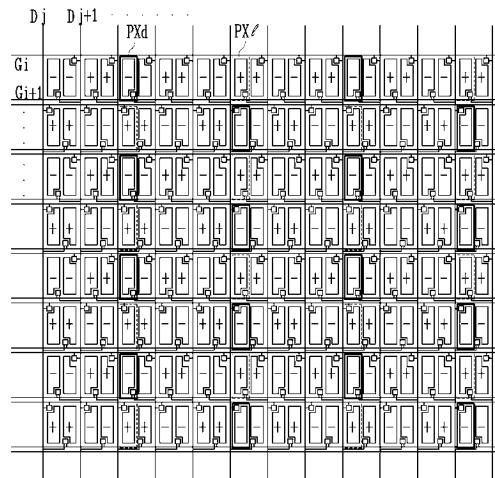

図1は本発明の一実施形態による液晶表示装置のブロック図であり、図2は本発明の一実施形態による液晶表示装置の一つの画素に対する等価回路図であり、図3Aは本発明の一実施形態による液晶表示装置の画素及び信号線の空間的な配列を説明する図面である。

【0025】

図1及び図2を参照すれば、本発明の一実施形態による液晶表示装置は、液晶表示板組立体300と、これに接続された一対のゲート駆動部400R、400Lと、データ駆動部500と、データ駆動部500に接続された階調電圧生成部800と、これらを制御する信号制御部600とを有する。

【0026】

液晶表示板組立体300は等価回路で見る時、複数の信号線G<sub>1</sub> - G<sub>2n</sub>、D<sub>1</sub> - D<sub>m</sub>と、これに接続されてほぼ行列形態に配列された複数の画素P Xを有する。一方、図2に示した構造で見たときは、液晶表示板組立体300は互いに対向する下部及び上部表示板100、200と、その間に入っている液晶層3を有する。

【0027】

信号線はゲート信号（“走査信号”とも言う）を伝達する複数のゲート線G<sub>1</sub> - G<sub>2n</sub>と、データ信号を伝達する複数のデータ線D<sub>1</sub> - D<sub>m</sub>を有する。ゲート線G<sub>1</sub> - G<sub>2n</sub>はほぼ行方向に伸びて互いにほとんど平行であり、データ線D<sub>1</sub> - D<sub>m</sub>はほぼ列方向に伸びて互いにほぼ平行である。

【0028】

各画素P Xは信号線に接続されたスイッチング素子Qと、これに接続された液晶キャバ

10

20

30

40

50

シタ (liquid crystal capacitor) C<sub>1c</sub> 及びストレージキャパシタ (storage capacitor) C<sub>st</sub> を有する。ストレージキャパシタ C<sub>st</sub> は必要に応じて省略してもよい。

#### 【0029】

スイッチング素子 Q は下部表示板 100 に備えられている薄膜トランジスタなどの三端子素子であって、その制御端子はゲート線 G<sub>i</sub> と接続され、入力端子はデータ線 D<sub>j</sub> と接続され、出力端子は液晶キャパシタ C<sub>1c</sub> 及びストレージキャパシタ C<sub>st</sub> と接続されている。

#### 【0030】

液晶キャパシタ C<sub>1c</sub> は下部表示板 100 の画素電極 191 と上部表示板 200 の共通電極 270 を二つの端子とし、二つの電極 191、270 の間の液晶層 3 は誘電体として機能する。画素電極 191 はスイッチング素子 Q と接続され、共通電極 270 は上部表示板 200 の全面に形成されて共通電圧 V<sub>com</sub> の印加を受ける。図 2 とは異なり、共通電極 270 が下部表示板 100 に備えられる場合もあり、この時には二つの電極 191、270 のうちの少なくとも一つが線状または棒状に作られることができる。

#### 【0031】

液晶キャパシタ C<sub>1c</sub> の補助的な役割を果たすストレージキャパシタ C<sub>st</sub> は、下部表示板 100 に備えられた別個の信号線（図示せず）と画素電極 191 が絶縁体を挟んで重なることによって構成され、この別個の信号線には共通電圧 V<sub>com</sub> などの決められた電圧が印加される。ただし、ストレージキャパシタ C<sub>st</sub> は画素電極 191 が絶縁体を挟んで直上の前段ゲート線と重なって構成されることもできる。

#### 【0032】

図 3A に示したように、一対のゲート線 (G<sub>i</sub> 及び G<sub>i+1</sub>、G<sub>i+2</sub> 及び G<sub>i+3</sub> ...) は一つの行の画素電極 191 の上下に配置されている。また、データ線 D<sub>1</sub> - D<sub>m</sub> は二つの列の画素電極 191 の間に一つずつ配置されている。つまり、一対の画素列の間に一つのデータ線が配置されている。以下、隣接する二つのデータ線の間に配置される二つの画素を単位画素対と言う。

#### 【0033】

次に、これらゲート線 G<sub>1</sub> - G<sub>2n</sub> 及びデータ線 D<sub>1</sub> - D<sub>m</sub> と画素電極 191 間の接続をより詳しく説明する。

#### 【0034】

画素電極 191 の上側と下側に接続された複数対のゲート線 G<sub>1</sub> - G<sub>2n</sub> は各画素電極 191 の上側または下側に配置されたスイッチング素子 Q を通じて当該画素電極 191 に接続される。

#### 【0035】

つまり、奇数番目画素行 P X r 1、P X r 3 において、一つのデータ線 D<sub>1</sub> - D<sub>m</sub> を中心に左側に位置したスイッチング素子 Q は上側に位置したゲート線 G<sub>i</sub>、G<sub>i+4</sub> に接続されており、一つのデータ線 D<sub>1</sub> - D<sub>m</sub> を中心に右側に位置したスイッチング素子 Q は下側に位置したゲート線 G<sub>i+1</sub>、G<sub>i+5</sub> に接続されている。一方、偶数番目画素行 P X r 2、P X r 4 に位置した上側ゲート線 G<sub>i+2</sub>、G<sub>i+6</sub> 及び下側ゲート線 G<sub>i+3</sub>、G<sub>i+7</sub> とスイッチング素子 Q との接続は奇数番目画素行と反対である。つまり、一つのデータ線 D<sub>1</sub> - D<sub>m</sub> を中心に右側に位置するスイッチング素子 Q は上側に位置したゲート線 G<sub>i+2</sub>、G<sub>i+6</sub> に接続されており、一つのデータ線 D<sub>1</sub> - D<sub>m</sub> を中心に左側に位置するスイッチング素子 Q は下側に位置したゲート線 G<sub>i+3</sub>、G<sub>i+7</sub> に接続されている。

#### 【0036】

奇数番目画素行 P X r 1、P X r 3 において、データ線 D<sub>1</sub> - D<sub>m</sub> を中心に左側に位置した画素電極 191 はスイッチング素子 Q を通じて直接隣接したデータ線に接続されており、データ線 D<sub>1</sub> - D<sub>m</sub> を中心に右側に位置した画素電極 191 はスイッチング素子 Q を通じて、直接隣接したデータ線ではなく、二番目に近い距離で隣接したデータ線 D<sub>1</sub> - D<sub>m</sub> に接続されている。偶数番目画素行 P X r 2、P X r 4 において、データ線 D<sub>1</sub> - D<sub>m</sub>

10

20

30

40

50

を中心にして左側に位置した画素電極 191 はスイッチング素子 Q を通じて、直接隣接したデータ線ではなく、二番目に近い距離で隣接したデータ線に接続されており、データ線  $D_1 - D_m$  を中心に右側に位置した画素電極 191 はスイッチング素子 Q を通じて直接隣接したデータ線に接続されている。

【0037】

また、図 3A に示した配置でスイッチング素子 Q の位置は毎画素行ごとに変わる。つまり、奇数番目画素行  $P X r 1, P X r 3$  に位置した画素対のうちのデータ線  $D_1 - D_m$  の左側に位置した画素  $P X$  には右側上端部にスイッチング素子 Q が形成されており、データ線  $D_1 - D_m$  の右側に位置した画素には右側下端部にスイッチング素子 Q が形成されている。

【0038】

一方、偶数番目画素行  $P X r 2, P X r 4$  に位置した画素のスイッチング素子 Q の形成位置は隣接した画素行の形成位置と正反対である。つまり、偶数番目行に位置した画素対のうちのデータ線  $D_1 - D_m$  の左側に位置した画素には左側下端部にスイッチング素子 Q が形成されており、データ線  $D_1 - D_m$  の右側に位置した画素には左側上端部にスイッチング素子 Q が形成されている。

【0039】

このようにスイッチング素子 Q の位置を毎画素行  $P X r 1 - 4$  ごとに変える理由は、各画素に形成されたスイッチング素子 Q とデータ線  $D_1 - D_m$  の接続長さを可能な限り短くするためである。

【0040】

図 3A に示した画素電極 191 とデータ線  $D_1 - D_m$  の接続について整理すると、各画素行において、単位画素対のスイッチング素子 Q は同一なデータ線に接続されている。つまり、奇数番目画素行で単位画素対のスイッチング素子 Q は右側に位置したデータ線に接続されており、偶数番目画素行で単位画素対のスイッチング素子 Q は左側に位置したデータ線に接続されている。

【0041】

図 3A に示した配置は単に一つの例に過ぎず、奇数番目行と偶数番目行の画素電極 191 とデータ線  $D_1 - D_m$  及びゲート線  $G_1 - G_{2n}$  の接続は互いに変わることがあり、また、他の接続関係を有することもある。

【0042】

一方、色表示を実現する方式としては、各画素  $P X$  が基本色のうちの一つを固有に表示する（空間分割）ものと、各画素  $P X$  が時間によって交互に基本色を表示する（時間分割）ものがある。そして、これら基本色の空間的、時間的合計によって所望する色相が認識される。基本色の例としては、赤色、緑色、青色などの三原色がある。図 2 は空間分割の一例で、各画素  $P X$  が画素電極 191 に対応する上部表示板 200 の領域に基本色のうちの一つを示す色フィルター 230 を備えることを示している。図 2 と異なり、色フィルター 230 は下部表示板 100 の画素電極 191 の上または下に形成してもよい。

【0043】

液晶表示板組立体 300 の外側には、光を偏光させる少なくとも一つの偏光子（図示せず）が実装されている。

【0044】

図 1 を参照すると、階調電圧生成部 800 は画素  $P X$  の透過率と関係する二対の階調電圧集合（または基準階調電圧集合）を生成する。二対のうちの一対は共通電圧  $V_{com}$  に対して正の値を有し、他の一対は負の値を有する。

【0045】

ゲート駆動部は各々液晶表示板 300 の右側と左側に配置される第 1 及び第 2 ゲート駆動部 400L, 400R から成る。ゲート駆動部 400L, 400R は液晶表示板組立体 300 のゲート線  $G_1 - G_{2n}$  と接続されて、ゲートオン電圧  $V_{on}$  とゲートオフ電圧  $V_{off}$  の組み合わせからなるゲート信号をゲート線  $G_1 - G_{2n}$  に印加する。

## 【0046】

次に、図3Aによって、ゲート駆動部400L、400R部とゲート線G<sub>1</sub>-G<sub>2n</sub>の接続関係を詳細に説明する。

## 【0047】

第1画素行PXR1で上側に位置するゲート線G<sub>i</sub>は第1ゲート駆動部400Lと接続されており、下側に位置するゲート線G<sub>i+1</sub>は第2ゲート駆動部400Rと接続されている。第2画素行PXR2のゲート線G<sub>i+2</sub>、G<sub>i+3</sub>と第1及び第2ゲート駆動部400L、400Rの接続関係は第1画素行PXR1と同一である。

## 【0048】

一方、第3及び第4番目画素行PXR3、PXR4のゲート線G<sub>i+4</sub>、G<sub>i+5</sub>、G<sub>i+6</sub>、G<sub>i+7</sub>とゲート駆動部400L、400Rの接続関係は第1及び第2画素行PXR1、PXR2と反対である。つまり、第3/第4番目画素行PXR3、PXR4で上側に位置するゲート線G<sub>i+4</sub>/G<sub>i+6</sub>は第2ゲート駆動部400Rと接続されており、下側に位置するゲート線G<sub>i+5</sub>/G<sub>i+7</sub>は第2ゲート駆動部400Lと接続されている。

## 【0049】

以下、図3Aに示されているように第1及び第2番目画素行PXR1、PXR2及びゲート駆動部400L、400Rのような接続関係を第1群画素行とし、第3及び第4番目画素行PXR3、PXR4及びゲート駆動部400L、400Rのような接続関係を第2群画素行とする。図3Aの液晶表示板は第1群画素行が二回繰り返され、次いで、第2群画素行が二回繰り返される形態を取る。図3Aに図示してはいないが、このような規則は第5番目以下の画素行でも繰り返される。

## 【0050】

一方、図3Aでは第1群画素行及び第2群画素行が各々二回ずつ繰り返されたが、本発明はこれに限定されず、第1群画素行及び第2群画素行が各々三回ずつ、四回ずつ…反復できる。つまり、ゲート線全体の個数が2n(n=1、2、3、4….)とする時、第1群画素行は最大n回連続して繰り返されて、次いで、第2群画素行が最大n回繰り返される形態を取ってもよい。

## 【0051】

ゲート駆動部400L、400Rは信号線G<sub>1</sub>-G<sub>2n</sub>、D<sub>1</sub>-D<sub>m</sub>及び薄膜トランジスタスイッチング素子Qなどと共に液晶表示板組立体300に集積されている。ゲート駆動部400L、400Rはまた、集積回路チップの形態で組立体300上に直接装着されてもよく、可撓性印刷回路膜(図示せず)上に装着されてTCP(tape carrier package)の形態で液晶表示板組立体300に実装されてもよく、別途の印刷回路基板(図示せず)上に実装されてもよい。

## 【0052】

データ駆動部500は液晶表示板組立体300のデータ線D<sub>1</sub>-D<sub>m</sub>に接続されており、階調電圧生成部800からの階調電圧を選択して、これをデータ信号としてデータ線D<sub>1</sub>-D<sub>m</sub>に印加する。しかし、階調電圧生成部800が全ての階調に対する電圧を全て提供するのではなく、決められた数の基準階調電圧のみを提供する場合に、データ駆動部500は基準階調電圧を分圧して全階調に対する階調電圧を生成し、この中でデータ信号を選択する。

## 【0053】

信号制御部600はゲート駆動部400R、400L及びデータ駆動部500を制御する。

## 【0054】

このような駆動装置500、600、800の各々は、少なくとも一つの集積回路チップの形態で液晶表示板組立体300上に直接装着されたり、可撓性印刷回路膜(図示せず)上に装着されてTCPの形態で液晶表示板組立体300に付着されたり、別途の印刷回路基板(図示せず)上に装着されてもよい。これとは異なり、これら駆動装置500、600、800は信号線G<sub>1</sub>-G<sub>2n</sub>、D<sub>1</sub>-D<sub>m</sub>及び薄膜トランジスタスイッチング素子Q

10

20

30

40

50

などと共に液晶表示板組立体 300 に集積されてもよい。また、駆動装置 400、500、600、800 は単一チップに集積されてもよく、この場合、これらのうちの少なくとも一つまたはこれらを構成する少なくとも一つの回路素子が単一チップに集積されずに、その外側にあってもよい。

【0055】

次に、このような液晶表示装置の動作について詳細に説明する。

【0056】

信号制御部 600 は外部のグラフィック制御器（図示せず）から入力映像信号 R、G、B 及び、その表示を制御する入力制御信号を受信する。入力制御信号の例としては垂直同期信号 V sync と水平同期信号 H sync、メインクロック MCLK、データインターブル信号 DE などがある。

【0057】

信号制御部 600 は入力映像信号 R、G、B と入力制御信号に基づいて入力映像信号 R、G、B を液晶表示板組立体 300 の動作条件に合わせて適切に処理して、ゲート制御信号 CONT1 及びデータ制御信号 CONT2 などを生成した後、ゲート制御信号 CONT1 をゲート駆動部 400 に出力して、データ制御信号 CONT2 と処理した映像信号 DAT をデータ駆動部 500 に出力する。

【0058】

ゲート制御信号 CONT1 は走査開始を指示する走査開始信号 STV と、ゲートオン電圧 Von の出力周期を制御する少なくとも一つのクロック信号を有する。ゲート制御信号 CONT1 はまた、ゲートオン電圧 Von の持続時間を限定する出力イネーブル信号 ODE をさらに有することができる。

【0059】

データ制御信号 CONT2 は一つの行もしくは複数の行を構成する画素 PX に対する映像データの伝送開始を知らせる水平同期開始信号 STH と、データ線 D<sub>1</sub> - D<sub>m</sub> にデータ信号を印加することを命令するロード信号 LOAD 及びデータクロック信号 HCLK を有する。データ制御信号 CONT2 は、また、共通電圧 Vcom に対するデータ信号の電圧極性（以下、“共通電圧に対するデータ信号の電圧極性”を略して“データ信号の極性”と言う）を反転させる反転信号 RVS をさらに有することができる。

【0060】

データ駆動部 500 は、信号制御部 600 からのデータ制御信号 CONT2 によって、一つの行もしくは複数の行を構成する画素 PX に対するデジタル映像信号 DAT を受信し、各デジタル映像信号 DAT に対応する階調電圧を選択することによって、デジタル映像信号 DAT をアナログデータ信号に変換した後、これを当該データ線 D<sub>1</sub> - D<sub>m</sub> に印加する。

【0061】

ゲート駆動部 400L、400R は信号制御部 600 からのゲート制御信号 CONT1 によってゲートオン電圧 Von をゲート線 G<sub>1</sub> - G<sub>2n</sub> に印加して、このゲート線 G<sub>1</sub> - G<sub>2n</sub> に接続されたスイッチング素子 Q を導通させる。その結果、データ線 D<sub>1</sub> - D<sub>m</sub> に印加されたデータ信号は導通したスイッチング素子 Q を通じて当該画素 PX に印加される。

【0062】

画素 PX に印加されたデータ信号の電圧と共通電圧 Vcom の差は液晶キャパシタ C<sub>1c</sub> の充電電圧、つまり、画素電圧となる。液晶分子は画素電圧の大きさによってその配列を変化させ、それにより液晶層 3 を通過する光の偏光が変化する。このような偏光の変化は表示板組立体 300 に実装された偏光子による光の透過率変化で示される。

【0063】

1 水平周期（“1H”とも言って、水平同期信号 H sync 及びデータインターブル信号 DE の一周期と同一である）を単位として、このような過程を繰り返すことによって全てのゲート線 G<sub>1</sub> - G<sub>2n</sub> に対して順次にゲートオン電圧 Von を印加して、全ての画素 PX にデータ信号を印加して一つのフレームの映像を表示する。

10

20

30

40

50

## 【0064】

一つのフレームが終われば、次のフレームが始まり、各画素  $P_X$  に印加されるデータ信号の極性が直前フレームにおける極性と反対になるようにデータ駆動部 500 に印加される反転信号  $RVS$  の状態が制御される（“フレーム反転”）。この時、一つのフレーム内においても、反転信号  $RVS$  の特性によって一つのデータ線を通じて流れるデータ信号の極性を変えたり（例：行反転、点反転）、一つの画素行に印加されるデータ信号の極性を互いに変えたりすることがある（例：列反転、点反転）。

## 【0065】

以下では、図 3A～図 3C を参照して、本発明の一実施形態による液晶表示装置の駆動状態についてさらに詳細に説明する。

10

## 【0066】

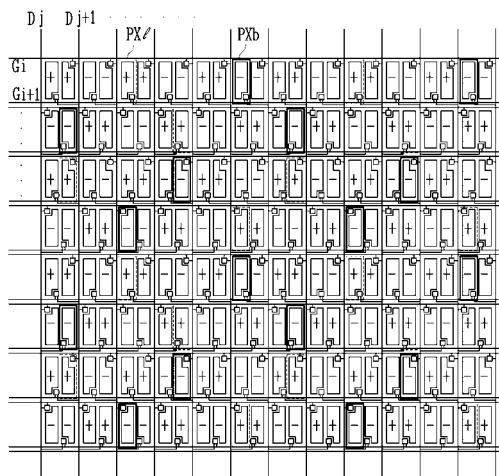

図 3B 及び図 3C は、図 3A の液晶表示装置が動作する状態を示す図面であり、互いに反転した状態を示す。

## 【0067】

図 3B 及び図 3C の表示装置は、図 3A に示したように、ゲート駆動部 400L、400R とゲート線  $G_1 - G_{2n}$  の接続関係が 4 行の規則単位で配置されている。

20

## 【0068】

信号制御部 600 から入力されるゲート制御信号  $CONT_1$  により制御されるゲート駆動部 400L、400R によって、一つの単位画素対と接続される一対のゲート線うちの一つのゲート線にゲートオン電圧  $V_{on}$  が印加されると、このゲート線に接続されたスイッチング素子  $Q$  が導通する。次いで、前記一対のゲート線のうちの他の一つのゲート線にもゲートオン電圧  $V_{on}$  が印加されて、このゲート線に接続されたスイッチング素子  $Q$  が導通する。その結果、データ線  $D_1 - D_m$  に印加されたデータ信号が導通したスイッチング素子  $Q$  を通じて当該画素  $P_X$  に印加される。

20

## 【0069】

ここで、ゲート線  $G_1 - G_{2n}$  と画素電極 191 間の寄生容量によってゲートオン電圧が下降し、ゲートオフ電圧になる瞬間にデータ電圧を多少減少させる 1 次キックバック電圧  $V_{kb}$  が発生する。次いで、次のゲートオン電圧が下降してゲートオフ電圧になる瞬間に 2 次キックバック電圧  $V_{kb}$  が発生する。2 次キックバック電圧  $V_{kb}$  が発生する画素電極 191 の中で負極性（-）から正極性（+）に反転する画素電極 191 は、画素電極電圧が共通電圧  $V_{com}$  に近い方向にシフトして画素  $P_X$  が正常より明るくなる。また、2 次キックバック電圧が発生する画素電極 191 の中で正極性（+）から負極性（-）に反転する画素電極 191 は、画素電極電圧が共通電圧  $V_{com}$  から遠い方向にシフトして画素  $P_X$  が正常より暗くなる。

30

## 【0070】

図 3B において点線で表示したボックスは 2 次キックバック電圧が発生する画素の中で負極性（-）から正極性（+）に反転して正常より明るくなる画素  $P_X 1$  であり、実線で表示したボックスは 2 次キックバック電圧が発生する画素の中で正極性（+）から負極性（-）に反転して正常より暗くなる画素  $P_X d$  である。フレームが反転すると、図 3B の表示は図 3C のように変わる。つまり、図 3B で明るくなった画素  $P_X 1$  は図 3C では暗くなり、図 3B で暗くなった画素  $P_X d$  は図 3C で明るくなる。つまり、フレームが繰り返されながら、図 3A の液晶表示装置は図 3B 及び図 3C の形態を繰り返す。

40

## 【0071】

もし、表示板で正常より明るくなる画素  $P_X 1$  及び暗くなる画素  $P_X d$  が各々行方向に連続して現れる場合には、輝度の異なる縦線の染みが認められる。また、フレームごとに反転するとしても頭を振ったり、視野を動かしたりして見ると、縦線が移動する形態で縦線の染みが認められる。しかし、本実施形態による表示装置は、図 3B 及び図 3C のように、画素が正常より明るくなったり正常より暗くなったりするといった輝度の差が出る画素  $P_X 1$ 、 $P_X d$  が表示板内において適切に混合されて表示される。したがって、横方向や縦方向に表示染みが発生しない。

50

## 【0072】

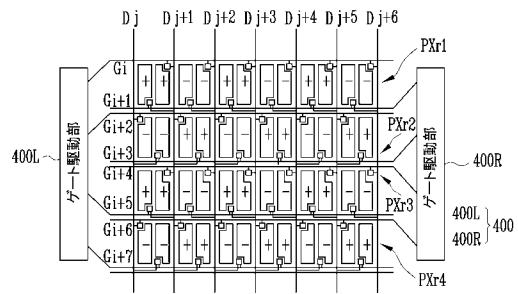

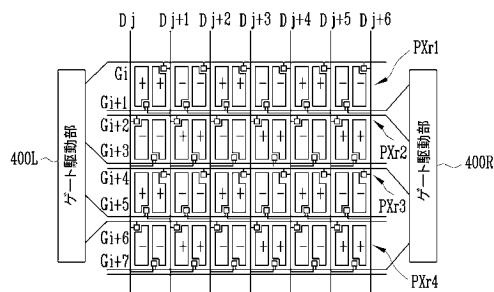

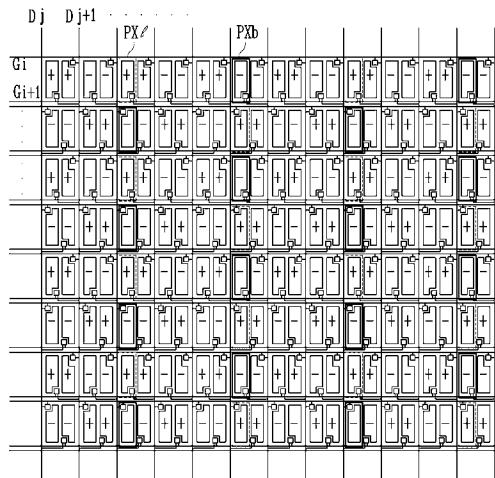

次に、図4により本発明の他の実施形態による液晶表示装置について詳細に説明する。

## 【0073】

図4は本発明の他の実施形態による液晶表示装置の画素及び信号線の空間的な配列を示す図面である。

## 【0074】

図4の液晶表示装置もまた、一対のゲート線( $G_i$ 及び $G_{i+1}$ 、 $G_{i+2}$ 及び $G_{i+3}$ ...)が一つの行の画素電極191の上下に配置されている。また、データ線 $D_1$ - $D_m$ は二つの列の画素電極191の間に一つずつ配置されている。画素電極191の上側と下側に接続された複数対のゲート線は各画素電極191の上側または下側に配置されたスイッチング素子Qを通じて当該画素電極191に接続される。つまり、奇数番目画素行 $P_{Xr1}$ 、 $P_{Xr3}$ において、一つのデータ線 $D_1$ - $D_m$ を中心に左側に位置したスイッチング素子Qは上側に位置したゲート線 $G_i$ 、 $G_{i+4}$ に接続され、一つのデータ線 $D_1$ - $D_m$ を中心に右側に位置したスイッチング素子Qは下側に位置したゲート線 $G_{i+1}$ 、 $G_{i+5}$ に接続される。一方、偶数番目画素行 $P_{Xr2}$ 、 $P_{Xr4}$ に位置した上側ゲート線 $G_{i+2}$ 、 $G_{i+6}$ 及び下側ゲート線 $G_{i+3}$ 、 $G_{i+7}$ とスイッチング素子Qとの接続は奇数番目画素行と反対である。奇数番目画素行の画素電極191の中でデータ線 $D_1$ - $D_m$ を中心に左側に位置した画素電極191はスイッチング素子Qを通じて直接隣接したデータ線 $D_1$ - $D_m$ に接続され、データ線 $D_1$ - $D_m$ を中心に右側に位置した画素電極191はスイッチング素子Qを通じて、直接隣接したデータ線ではなく、二番目に近い距離で隣接したデータ線 $D_1$ - $D_m$ に接続される。偶数番目画素行の画素電極191の中でデータ線 $D_1$ - $D_m$ を中心に左側に位置した画素電極191はスイッチング素子Qを通じて、直接隣接したデータ線ではなく、二番目に近い距離で隣接するデータ線に接続され、データ線 $D_1$ - $D_m$ を中心に右側に位置した画素電極191はスイッチング素子Qを通じて直接隣接したデータ線に接続される。各画素行において、単位画素対のスイッチング素子Qは同一なデータ線に接続される。

## 【0075】

しかし、図4の液晶表示装置は図3Aの液晶表示装置とは異なり、一つの画素行で上側に位置するゲート線が第1ゲート駆動部400Lと接続され、下側に位置するゲート線が第2ゲート駆動部400Rと接続される第1群画素行と、一つの画素行で上側に位置するゲート線が第2ゲート駆動部400Rと接続され、下側に位置するゲート線が第1ゲート駆動部400Lと接続される第2群画素行が隣接して配置される。そして、前記第2群画素行の下には他の第2群画素行が隣接し、次いで、第1群または第2群画素行の中で異なる種類の画素行が二つずつ繰り返されて配置される。

## 【0076】

図4では最も上の画素行に第1群画素行が配置されたが、第2群画素行が最も上に配置されて、表示板全体で第1群及び第2群画素行の位置が変わってもよい。また、図4において、第1群及び第2群画素行それぞれの繰り返される個数は2個で示したが、これに限定されず、ゲート線の総数以内でさらに多くの個数の第1群及び第2群画素行が各々繰り返されてもよい。

## 【0077】

その他に、図3Aに示した液晶表示装置の多くの特徴が図4に示した液晶表示装置にも適用できる。

## 【0078】

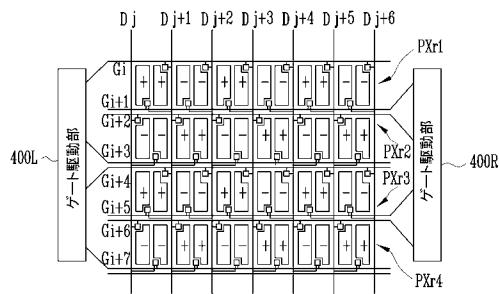

次に、図5A乃至図5Cを参照して、本発明の他の実施形態による液晶表示装置について説明する。

## 【0079】

図5Aは本発明のさらに別の実施形態による液晶表示装置の画素及び信号線の空間的な配列を示す図面であり、図5B及び図5Cは図5Aの液晶表示装置が駆動される様子を示す図面である。

10

20

30

40

50

## 【0080】

図5A～図5Cの液晶表示装置もまた、一対のゲート線( $G_i$ 及び $G_{i+1}$ 、 $G_{i+2}$ 及び $G_{i+3}$ ...)が一つの行の画素電極191の上下に配置される。また、データ線 $D_1-D_m$ は二つの列の画素電極191の間に一つずつ配置される。画素電極191の上側と下側に接続された複数対のゲート線は、各画素電極191の上側または下側に配置されたスイッチング素子Qを通じて当該画素電極191に接続される。つまり、奇数番目画素行 $P X r 1$ 、 $P X r 3$ において、一つのデータ線 $D_1-D_m$ を中心に左側に位置したスイッチング素子Qは上側に位置したゲート線 $G_i$ 、 $G_{i+4}$ に接続され、一つのデータ線 $D_1-D_m$ を中心に右側に位置したスイッチング素子Qは下側に位置したゲート線 $G_{i+1}$ 、 $G_{i+5}$ に接続される。一方、偶数番目画素行 $P X r 2$ 、 $P X r 4$ に位置した上側ゲート線 $G_{i+2}$ 、 $G_{i+6}$ 及び下側ゲート線 $G_{i+3}$ 、 $G_{i+7}$ とスイッチング素子Qとの接続は奇数番目画素行と反対である。奇数番目画素行の画素電極191の中でデータ線 $D_1-D_m$ を中心に左側に位置した画素電極191はスイッチング素子Qを通じて直接隣接したデータ線 $D_1-D_m$ に接続され、データ線 $D_1-D_m$ を中心に右側に位置した画素電極191はスイッチング素子Qを通じて、直接隣接したデータ線ではなく、二番目に近い距離で隣接するデータ線 $D_1-D_m$ に接続される。偶数番目画素行の画素電極191の中でデータ線 $D_1-D_m$ を中心に左側に位置した画素電極191はスイッチング素子Qを通じて、直接隣接したデータ線ではなく、二番目に近い距離で隣接するデータ線に接続され、データ線 $D_1-D_m$ を中心に右側に位置した画素電極191はスイッチング素子Qを通じて直接隣接したデータ線に接続される。各画素行において、単位画素対のスイッチング素子Qは同一のデータ線に接続される。

## 【0081】

しかし、図5Aの液晶表示装置は、図3Aまたは図4の液晶表示装置とは異なり、一つの画素行で上側に位置するゲート線が第1ゲート駆動部400Lと接続され、下側に位置するゲート線が第2ゲート駆動部400Rと接続される第1群画素行と、一つの画素行で上側に位置するゲート線が第2ゲート駆動部400Rと接続され、下側に位置するゲート線が第1ゲート駆動部400Lと接続される第2群画素行が全て交互に隣接するように配置される。

## 【0082】

図5B及び図5Cを参照すれば、点線で表示したボックスは2次キックバック電圧が発生する画素の中で負極性(-)から正極性(+)に反転して正常より明るくなる画素 $P X 1$ であり、実線で表示したボックスは2次キックバック電圧が発生する画素の中で正極性(+)から負極性(-)に反転して正常より暗くなる画素 $P X b$ である。図5Bで正常より明るくなる画素 $P X 1$ 及び暗くなる画素 $P X b$ は一つの列で互いに隣接して繰り返される。フレームが反転する場合、図5Bの表示は図5Cのように変わる。つまり、図5Bで明るくなった画素は図5Cでは暗くなり、図5Bで暗くなった画素は図5Cで明るくなる。つまり、フレームが繰り返されながら、図5Aの液晶表示装置は図5B及び図5Cの形態を繰り返す。このように、異なる輝度の画素が一つの画素列で隣接して配置されるので、輝度の差が適切に相殺して表示装置の縦及び横染みが発生することが防止できる。

その他に、図3Aに示した液晶表示装置の多くの特徴が図5Aに示した液晶表示装置にも適用できる。

## 【0083】

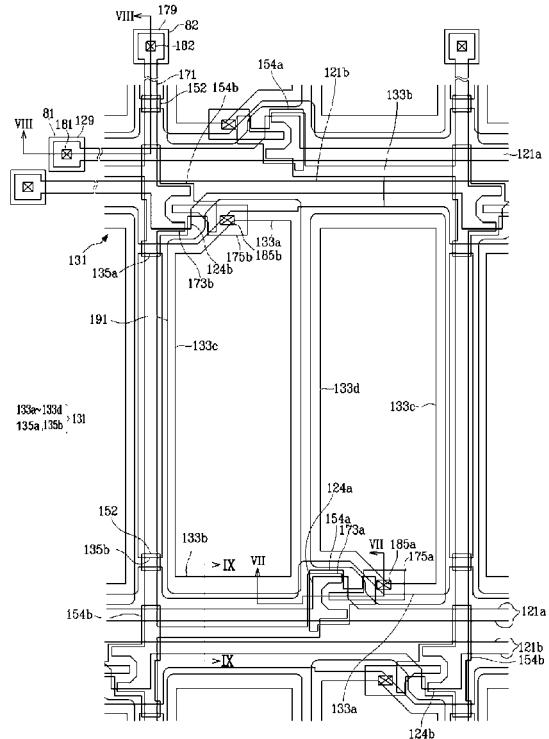

以下、本発明による液晶表示装置の一例について図6乃至図9を参照して詳細に説明する。

## 【0084】

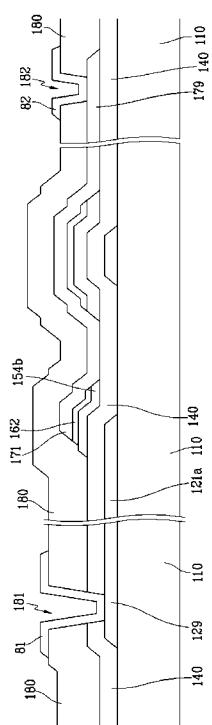

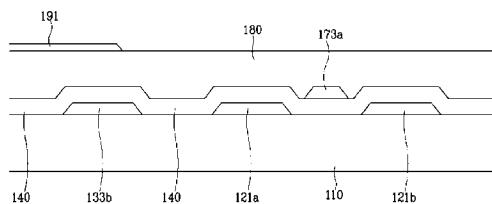

図6は本発明の一実施形態による液晶表示装置の配置図であり、図7乃至図9は各々図6の液晶表示装置をVII-VII、VIII-VIII及びIV-IV線に沿って切削した断面図である。

## 【0085】

図6乃至図9に示す通り、本発明の一実施形態による液晶表示板組立体は、下部表示板

10

20

30

40

50

(薄膜トランジスタ表示板) 100と、上部表示板(共通電極表示板) 200と、これら二つの表示板100、200の間に入っている液晶層3とを有する。

【0086】

まず、上部表示板100について詳細に説明する。

【0087】

透明なガラスまたはプラスチックなどで作られた絶縁基板110上に複数対の第1及び第2ゲート線121a、121bと複数の維持電極線131を含む複数のゲート導電体が形成される。

【0088】

第1及び第2ゲート線121a、121bはゲート信号を伝達し、主に横方向に伸びて、各々画素電極の上側及び下側に位置する。 10

【0089】

第1ゲート線121aは下に突出した複数の第1ゲート電極124aと他の層またはゲート駆動部400L、400Rとの接続のための広い端部129aを有する。第2ゲート線121bは上に突出した複数の第2ゲート電極124bと他の層またはゲート駆動部400との接続のための広い端部129bを有する。ゲート駆動部400が基板110上に集積されている場合、ゲート線121a、121bが伸びてこれと直接接続できる。

【0090】

維持電極線131は共通電圧Vcomなど、所定の電圧の印加を受けるが、ゲート線121a、121bとは絶縁されている。各維持電極線131は互いに接続されて、一対の長方形をなす複数の維持電極133a、133b、133c、133d集合と一対の維持電極接続部135a、135bを有する。 20

【0091】

一つの維持電極群133a-133dは、主に横方向に伸びた第1維持電極133a及び第2維持電極133bを一対ずつ有し、主に縦方向に伸びた一対の第3維持電極133cと、その間に位置して縦方向に伸びた第4維持電極133dを有する。第4維持電極133dを中心に左右両側に第1乃至第3維持電極133a-133cが一つずつ配置されて第4維持電極133dを共有する長方形をなして、この二つの長方形は第4維持電極133d中央を中心に180回転対称関係を有する。

【0092】

維持電極接続部135は隣接した二つの維持電極133a-133d集合の隣接した維持電極133cを接続し、維持電極133aはゲート電極124付近で屈曲している。しかし、維持電極133a、133bをはじめとした維持電極線131の模様及び配置は多様な形態に変更することができる。 30

【0093】

ゲート導電体121a、121b、維持電極線131はアルミニウム(A1)やアルミニウム合金などのアルミニウム系金属、銀や銀合金などの銀系金属、銅や銅合金など銅系金属、モリブデンやモリブデン合金などのモリブデン系金属、クロム、タンタル及びチタニウムなどからなることができる。しかし、これらは物理的性質の異なる二つの導電膜(図示せず)を有する多重膜構造であってもよい。このうちの一つの導電膜は、信号遅延や電圧降下を減らすことができるよう比抵抗(resistivity)の低い金属、例えば、アルミニウム系金属、銀系金属、銅系金属などで作られる。これとは異なり、他の導電膜は他の物質、特にITO(酸化インジウムスズ)及びIZO(酸化インジウム亜鉛)との物理的、化学的、電気的接触特性に優れた物質、例えば、モリブデン系金属、クロム、タンタル、チタニウムなどで作られる。このような組み合わせの良い例としては、クロム下部膜とアルミニウム(合金)上部膜及びアルミニウム(合金)下部膜とモリブデン(合金)上部膜がある。しかし、ゲート導電体121a、121b、維持電極線131はこの他にも多様な金属または導電体で作ることができる。 40

【0094】

ゲート導電体121a、121b、維持電極線131の側面は基板110面に対して傾

50

いており、その傾斜角は約30°乃至約80°であるのが好ましい。

【0095】

ゲート導電体121a、121b、維持電極線131上には窒化シリコン(SiNx)または酸化シリコン(SiOx)などで作られたゲート絶縁膜140が形成される。

【0096】

ゲート絶縁膜140上には水素化非晶質シリコン(非晶質シリコンは略してa-Siとも言う)または多結晶シリコンなどで作られた複数の島状半導体152、154a、154bが形成される。半導体154a、154bは各々ゲート電極124a、124b上に位置して、これらを覆っており半導体154aは伸びて隣接するゲート線121a及び維持電極接続部135aを覆う。また、半導体152は維持電極接続部135bを覆っている。

【0097】

第1第2半導体154a、154b上には複数の島状抵抗性接触部材163a、165aが形成される。抵抗性接触部材163a、165aはリンなどのn型不純物が高濃度でドーピングされているn+水素化非晶質シリコンなどの物質や、シリサイド(silicide)によって形成されることができる。抵抗性接触部材163a、165aは対をなして半導体154a上に配置され、半導体154b上にも抵抗性接触部材(図示せず)と他の島状抵抗性接触部材(図示せず)が対をなして配置される。

【0098】

半導体154a、154bと抵抗性接触部材163b、165bの側面もまた、基板10面に対して傾いて、傾斜角は30乃至80程度である。

【0099】

抵抗性接触部材163b、165b及びゲート絶縁膜140上には複数のデータ線171と複数対の第1及び第2ドレイン電極175a、175bを含むデータ導電体が形成される。

【0100】

データ線171はデータ信号を伝達して、主に縦方向に伸びてゲート線121a、121b及び維持電極線131と交差する。各データ線171は第1及び第2ゲート電極124a、124bに向かって各々伸びてC字型で屈曲した複数対の第1及び第2ソース電極173a、173bと他の層またはデータ駆動部500との接続のために面積の広い端部179を有する。

【0101】

第1及び第2ドレイン電極175a、175bは互いに絶縁され、データ線171とも絶縁される。

【0102】

第1/第2ドレイン電極175a/175bは第1/第2ゲート電極124a/124bを中心に第1/第2ソース電極173a/173bと対向する。

【0103】

第1及び第2ドレイン電極175a、175bは棒状の一側端部と他側端の拡張部177a、177bを有する。拡張部177a、177bは維持電極137a、137bと各々重なる。各ドレイン電極175a、175bの棒状端部はソース電極137a、137bで一部囲まれている。

【0104】

第1/第2ゲート電極124a/124b、第1/第2ソース電極173a/173b及び第1/第2ドレイン電極175a/175bは第1/第2半導体154a/154bと共に第1/第2薄膜トランジスタ(TFT)を構成し、第1/第2薄膜トランジスタのチャンネルは第1/第2ソース電極173a/173bと第1/第2ドレイン電極175a/175bの間の第1/第2半導体154a/154bに形成される。

【0105】

データ導電体171、175a、175bはモリブデン、クロム、タンタル及びチタニ

ウムなど耐火性金属またはこれらの合金から形成されるのが好ましく、耐火性金属膜（図示せず）と低抵抗導電膜（図示せず）を有する多重膜構造であってもよい。多重膜構造の例としては、クロムまたはモリブデン（合金）下部膜とアルミニウム（合金）上部膜の二重膜、モリブデン（合金）下部膜とアルミニウム（合金）中間膜とモリブデン（合金）上部膜の三重膜がある。しかし、データ導電体171、175a、175bはその他にも多様な金属または導電体からなることができる。

【0106】

データ導電体171、175a、175bもまた、その側面が基板110面に対して30°乃至80°程度の傾斜角で傾くことが好ましい。

【0107】

抵抗性接触部材163b、165bは、その下の半導体154a、154bとその上のデータ導電体171、175a、175bの間にのみ存在し、これらの間の接触抵抗を低くする。半導体154a、154bにはソース電極173a、173bとドレイン電極175a、175bの間をはじめとして、データ導電体171、175a、175bで覆われずに露出された部分を有する。

【0108】

データ導電体であるデータ線171、ドレイン電極175a、175b及び露出された半導体154a、154b部分上には保護膜180が形成されている。保護膜180は無機絶縁物または有機絶縁物などで作られ、表面が平坦であってもよい。有機絶縁物は4.0以下の誘電定数を有するのが好ましく、感光性を有してもよい。しかし、保護膜180は有機膜の優れた絶縁特性を生かしながら、露出された半導体154a、154b部分に悪影響を与えないように、下部無機膜と上部有機膜の二重膜構造を有することができる。

【0109】

保護膜180にはデータ線171の端部179を露出する複数の接触孔182と第1及び第2ドレイン電極175a、175bの拡張部177a、177bを露出する複数対の接触孔185a、185bが形成される。保護膜180とゲート絶縁膜140にはゲート線121a、121bの端部129a、129bを各々露出する複数の接触孔181a、181bが形成される。

【0110】

保護膜180上には複数の画素電極191及び複数の接触補助部材81a、81b、82が形成される。これらはITOまたはIZOなどの透明な導電物質やアルミニウム、銀、クロムまたはその合金などの反射性金属からなることができる。

【0111】

画素電極191は接触孔185を通じてドレイン電極175a、175bと物理的、電気的に接続されており、ドレイン電極175a、175bからデータ電圧の印加を受ける。データ電圧が印加された画素電極191は共通電圧の印加を受ける他の表示板200の共通電極270と共に電場を生成することによって二つの電極191、270の間の液晶層3の液晶分子の方向を決める。このように決められた液晶分子の方向によって液晶層3を通過する光の偏光が変わる。画素電極191と共通電極270はキャパシタ（以下、“液晶キャパシタ”と言う）を構成して、薄膜トランジスタが遮断された後にも印加された電圧を維持する。

【0112】

画素電極191は維持電極133a-dをはじめとした維持電極線131と重なり、画素電極191及び、これと電気的に接続されたドレイン電極175a、175bが維持電極線131と重なって構成するキャパシタを“ストレージキャパシタ”とし、ストレージキャパシタは液晶キャパシタの電圧維持能力を強化する。

【0113】

画素電極191はドレイン電極175a、175bの拡張された端部と維持電極133aを覆って、維持電極133b、133c、133dとは一部重なって画素電極191の境界線が維持電極133b、133c、133d上に位置する。このようにゲート線12

10

20

30

40

50

1a、121bと画素電極190の境界線との間に維持電極133bが形成されており、画素電極191とゲート線121aとの間の寄生容量による画素電極191の電圧変動が減少する。

【0114】

接触補助部材81a、81b、82は、各々接触孔181a、181b、182を通じてゲート線121a、121bの端部129a、129b及びデータ線171の端部179と接続される。接触補助部材81a、81b、82はゲート線121a、121bの端部129a、129b及びデータ線171の端部179と外部装置との接着性を補完して、これらを保護する。

【0115】

次に、上部表示板200について説明する。

【0116】

透明なガラスまたはプラスチックなどで作られた絶縁基板210上に遮光部材220が形成される。遮光部材220は画素電極191の屈曲辺に対応する屈曲部(図示せず)と薄膜トランジスタに対応する四角形部分(図示せず)を有することができ、画素電極191の間の光漏れを防止して画素電極191と対向する開口領域を定義する。

【0117】

基板210及び遮光部材220上にはまた、複数の色フィルター230が形成される。色フィルター230は遮光部材220で囲まれた領域内にほぼ存在し、画素電極191列に沿って長く伸びることができる。各色フィルター230は赤色、緑色及び青色の三原色など、基本色のうちの一つを表示することができる。

【0118】

色フィルター230及び遮光部材220上には蓋膜250が形成されている。蓋膜250は(有機)絶縁物で作られてもよく、色フィルター230が露出されることを防止して平坦面を提供する。蓋膜250は省略してもよい。

【0119】

蓋膜250上には共通電極270が形成されている。

【0120】

表示板100、200の内側には配向膜11、21が形成されており、これらは垂直配向膜であってもよい。

【0121】

表示板100、200の外側には偏光板12、22が備えられている。

【0122】

液晶表示装置は偏光板12、22、位相遅延膜、表示板100、200及び液晶層3に光を供給する照明部(図示せず)を有することができる。

【0123】

液晶層3は負の誘電率異方性を有し、液晶層3の液晶分子は電場のない状態でその長軸が二つの表示板の表面に対して垂直をなすように配向されている。

【0124】

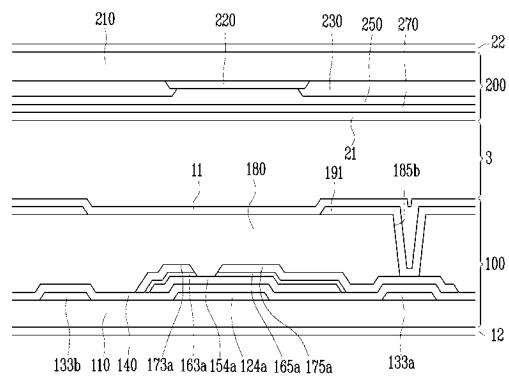

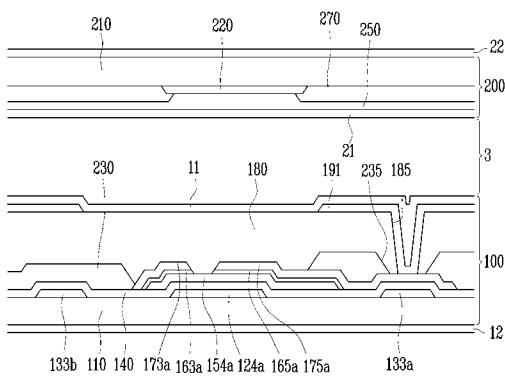

次に、図10と前述した図6、図8及び図9を参照して、本発明の他の実施形態による液晶表示装置について詳細に説明する。

【0125】

図10は本発明の他の実施形態による液晶表示装置の断面図である。

【0126】

図10に示すように、本実施形態による液晶表示板組立体も互いに対向する下部表示板と上部表示板、これら二つの表示板の間に入っている液晶層を有する。

【0127】

本実施形態による液晶表示板組立体の層状構造はほとんど図6及び図9に示した液晶表示板組立体の層状構造と同一である。

【0128】

10

20

30

40

50

下部表示板 100 の構造においては、絶縁基板 110 上に複数対の第 1 及び第 2 ゲート線 121a、121b と複数の維持電極線（図示せず）を有する複数のゲート導電体が形成される。各ゲート線 121a、121b はゲート電極 124a と端部（図示せず）を有し、各維持電極線 131（図示せず）は維持電極 133a、133b を有する。ゲート導電体 121a、121b 上にはゲート絶縁膜 140 が形成される。ゲート絶縁膜 140 上には複数の半導体 154a が形成され、その上には複数の抵抗性接触部材 163a、165b が形成される。抵抗性接触部材 163a、165b 及びゲート絶縁膜 140 上には複数のデータ線（図示せず）と複数の第 1 及び第 2 ドレイン電極 175a を有するデータ導電体が形成される。データ線は複数のソース電極 173a と端部（図示せず）を有し、ドレイン電極 175a は広い端部（図示せず）を有する。データ導電体 175a 及び露出された半導体 154a 部分上には保護膜 180 が形成され、保護膜 180 及びゲート絶縁膜には複数の接触孔 185 が形成される。保護膜 180 上には複数の画素電極 191 と複数の接触補助部材（図示せず）が形成される。画素電極 191、接触補助部材及び保護膜 180 上には配向膜 11 が形成される。

10

## 【0129】

上部表示板 200 の構造においては、絶縁基板 210 上に遮光部材 220、蓋膜 250、共通電極 270、そして配向膜 21 が形成される。

## 【0130】

しかし、図 10 の液晶表示装置は、図 6 乃至図 9 に示した液晶表示板組立体とは異なり、本実施形態による液晶表示装置では共通電極表示板 200 に色フィルター 230 がなく、その代わり薄膜トランジスタ表示板 100 の保護膜 180 下に複数の色フィルター 230 が形成されている。

20

## 【0131】

色フィルター 230 は画素電極 191 列に沿って帯状で縦に長く伸びており、隣接する二つの色フィルター 230 がデータ線の上部で重なっている。互いに重なっている色フィルター 230 は有機膜からなっていて画素電極 191 とデータ線との間を絶縁する。したがって、絶縁膜 180 を有機膜で形成しなくても、画素電極 191 とデータ線 171 が重なる部分で寄生容量が発生することを防止する。また、画素電極 191 の間の光漏れを防止する遮光部材の役割を果たすことができる。この場合、共通電極表示板 200 上の遮光部材 220 が省略できるので、工程が簡素化する。

30

## 【0132】

色フィルター 230 には接触孔 185 が通過する貫通孔 235 が形成されており、貫通孔 235 は接触孔 185 より大きい。ゲート線 121 の端部 129 及びデータ線の端部が位置した周辺領域には色フィルター 230 が存在しない。

## 【0133】

色フィルター 230 の下にも保護膜（図示せず）を置くことができる。

## 【0134】

その他に、図 6 乃至図 9 に示した液晶表示装置の多くの特徴が図 10 に示した液晶表示装置にも適用できる。

40

## 【0135】

以上、本発明の好ましい実施形態について詳細に説明した。しかし、本発明の技術的範囲は上記の実施例には限定されない。特許請求の範囲で定義されている本発明の基本概念を利用した当業者による多様な変形及び改良もまた、本発明の技術的範囲に属すると解されるべきである。

## 【図面の簡単な説明】

## 【0136】

【図 1】本発明の実施形態による液晶表示装置を示すブロック図である。

【図 2】本発明の実施形態による液晶表示装置の等価回路図である。

【図 3A】本発明の実施形態による液晶表示装置の画素及び信号線の空間的な配列を示す図面である。

50

【図3B】図3Aに示した液晶表示装置が動作した状態を示す図面である。

【図3C】図3Aに示した液晶表示装置が動作した状態を示す図面である。

【図4】本発明の実施形態による液晶表示装置の画素及び信号線の空間的な配列を示す図面である。

【図5A】本発明の実施形態による液晶表示装置の画素及び信号線の空間的な配列を示す図面である。

【図5B】図5Aに示した液晶表示装置が動作した状態を示す図面である。

【図5C】図5Aに示した液晶表示装置が動作した状態を示す図面である。

【図6】本発明の実施形態による液晶表示装置を示す配置図である。

【図7】図6の液晶表示装置をVII-VIIに沿って切断した断面図である。 10

【図8】図6の液晶表示装置をVII-I-VII及に沿って切断した断面図である。

【図9】図6の液晶表示装置をIX-IX線に沿って切断した断面図である。

【図10】本発明の実施形態による液晶表示装置を示す断面図である。

【符号の説明】

【0137】

|                         |             |    |

|-------------------------|-------------|----|

| 3                       | 液晶層、        |    |

| 11、21                   | 配向膜、        |    |

| 12、21、22                | 偏光板、        |    |

| 81、82                   | 接触補助部材、     |    |

| 100                     | 下部表示板、      | 20 |

| 110、210                 | 絶縁基板、       |    |

| 121a、121b               | ゲート線、       |    |

| 124a、124b               | ゲート電極、      |    |

| 131                     | 維持電極線、      |    |

| 133a-d                  | 維持電極、       |    |

| 140                     | ゲート絶縁膜、     |    |

| 154a、154b               | 半導体、        |    |

| 162、163a、163a、165a、165b | 抵抗性接触部材、    |    |

| 171                     | データ線、       |    |

| 173a、173b               | ソース電極、      | 30 |

| 175a、175b               | ドレイン電極、     |    |

| 179                     | データ線の端部、    |    |

| 180                     | 保護膜、        |    |

| 181、182、185a、185b       | 接触孔、        |    |

| 191                     | 画素電極、       |    |

| 200                     | 上部表示板、      |    |

| 210                     | 絶縁基板、       |    |

| 220                     | 遮光部材、       |    |

| 230                     | 色フィルター、     |    |

| 235                     | 色フィルターの貫通孔、 | 40 |

| 250                     | 蓋膜、         |    |

| 270                     | 共通電極、       |    |

| 300                     | 液晶表示板組立体、   |    |

| 400L、400R               | ゲート駆動部、     |    |

| 500                     | データ駆動部、     |    |

| 600                     | 信号制御部、      |    |

| 800                     | 階調電圧生成部。    |    |

【図1】

【図2】

【図3 A】

【図3 B】

【 図 4 】

【図5A】

【図5C】

【 図 5 B 】

【 四 6 】

【図7】

〔 四 8 〕

【 図 9 】

【 図 1 0 】

---

フロントページの続き

(74)代理人 100134348

弁理士 長谷川 俊弘

(72)発明者 金 聖 萬

大韓民国ソウル特別市松坡区新川洞 チャンミアパート30棟508号

(72)発明者 李 奉 俊

大韓民国ソウル特別市鐘路区昭格洞37番地地下階

(72)発明者 姜 信 宅

大韓民国京畿道龍仁市上 けん 洞 スンウォンサンテビル230棟1801号

F ターム(参考) 2H092 GA11 JA34 JA37 JA41 JB22 JB31 NA25 PA01 PA06 PA08

PA10 PA11

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | <无法获取翻译>                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">JP2007128092A5</a>                                                                                                                                                                                                                                                                                                                                                                                                                                        | 公开(公告)日 | 2009-12-17 |

| 申请号            | JP2006299548                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 申请日     | 2006-11-02 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |            |

| [标]发明人         | 金聖萬<br>李奉俊<br>姜信宅                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |            |

| 发明人            | 金 聖 萬<br>李 奉 俊<br>姜 信 宅                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| IPC分类号         | G02F1/1362                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| CPC分类号         | G09G3/3659 G02F1/134336 G02F1/136286 G09G3/3614 G09G3/3677 G09G2300/0426 G09G2310 /0218 G09G2320/0219 G09G2320/0247                                                                                                                                                                                                                                                                                                                                                   |         |            |

| FI分类号          | G02F1/1362                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |            |

| F-TERM分类号      | 2H092/GA11 2H092/JA34 2H092/JA37 2H092/JA41 2H092/JB22 2H092/JB31 2H092/NA25 2H092 /PA01 2H092/PA06 2H092/PA08 2H092/PA10 2H092/PA11 2H189/CA35 2H189/FA81 2H189/JA10 2H189/LA01 2H189/LA03 2H189/LA06 2H189/LA08 2H189/LA09 2H189/LA10 2H192/AA24 2H192 /AA43 2H192/BC31 2H192/CB05 2H192/CB14 2H192/CB45 2H192/CC12 2H192/CC24 2H192/CC52 2H192/CC62 2H192/CC72 2H192/DA12 2H192/DA73 2H192/EA22 2H192/EA43 2H192/FA44 2H192 /FA65 2H192/FB03 2H192/FB27 2H192/GD61 |         |            |

| 代理人(译)         | 宇谷 胜幸<br>藤田 健                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |            |

| 优先权            | 1020050104176 2005-11-02 KR                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

| 其他公开文献         | JP2007128092A<br>JP5441301B2                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |            |

**摘要(译)**

要解决的问题：提供一种防止在屏幕上出现斑点的液晶显示装置。根据本发明的液晶显示装置包括：基板，形成在基板上，第一，具有多个像素和 (PXR) 和第二像素行 (PXr2)，在行方向上延伸的上基板连接到第一像素行的第一栅极线，沿基板上的行方向延伸并连接到第一像素行并且与第一栅极线相邻的第二栅极线，第三栅极线，连接到第二像素行并且与第二栅极线相邻，第三栅极线在基板上沿行方向延伸并连接到第二像素行，3和邻近于栅极线的第四栅极线，在延伸在基板上的列方向，多条数据线设置在一个接一个对每个两个像素列，分别连接到第一和第四栅极线用于施加栅极信号到所述第一和第四栅极线和 (400 L)，对所述第二和第三栅极线连接，前第一栅极驱动器第二栅极驱动器将栅极信号施加到第二和第三栅极线和 (400R)。点域3A