(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-12872

(P2004-12872A)

(43) 公開日 平成16年1月15日(2004.1.15)

(51) Int.Cl.<sup>7</sup>**G09G 3/36**

**G02F 1/133**

**G09G 3/20**

F 1

G09G 3/36

G02F 1/133 550

G02F 1/133 570

G09G 3/20 612F

G09G 3/20 622M

テーマコード(参考)

2H093

5C006

5C080

審査請求 未請求 請求項の数 7 O L (全 17 頁) 最終頁に続く

(21) 出願番号

特願2002-167109(P2002-167109)

(22) 出願日

平成14年6月7日(2002.6.7)

(71) 出願人

302062931

NECエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人

100109313

弁理士 机 昌彦

(74) 代理人

100085268

弁理士 河合 信明

(74) 代理人

100111637

弁理士 谷澤 靖久

(72) 発明者

能勢 崇

東京都港区芝五丁目7番1号

日本電気株式会社内

F ターム(参考) 2H093 NA16 NA45 NA47 NC22 NC34

NC49 ND01 ND60

最終頁に続く

(54) 【発明の名称】表示装置及びその駆動方法

## (57) 【要約】

【課題】液晶表示装置のようなホールド型表示装置においては、1フレーム期間中に黒画像を挿入することで動画ボケを解消する方法が開発されているが、信号線駆動回路部は依然として画素列すべての画素データを保持して信号線駆動回路から出力する形式であり、駆動回路部を縮小して表示装置のコンパクト化に対応できる構成とはなっていなかった。

【解決手段】異なる行の2つの画素に同時に画素データ及び黒データを書き込み、この動作を同一行の画素に対して2回に分けて行って一行の画素全部にデータを書き込む。この動作をすべての画素行に対して1フレーム期間内で行えば、従来の信号線駆動回路と比べて、データラッチ回路には従来の画素データの半分のデータのみを保持すれば良く、チップサイズを約半分に縮小でき、表示装置の占有面積が小さくなる。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

行列状に並ぶ画素を有する表示装置の駆動方法において、

前記画素の画素行のうち少なくとも1つの画素行に画像データを書き込む期間を第1走査期間と第2走査期間に分け、

前記第1走査期間において、任意の画素行の内で所定の画素列に位置する画素に画像データを書き込むと共に、前記任意の画素行と異なる画素行の内で前記所定の画素列以外に位置する画素に黒色データを書き込み、

前記第2走査期間は、前記第1走査期間において画像データを書き込んだ画素行の内で画像データを書き込んだ画素以外の画素に画像データを書き込むと共に、前記第1走査期間において黒色データを書き込んだ画素行の内で黒色データを書き込んだ画素以外の画素に黒色データを書き込むことを特徴とする表示装置の駆動方法。10

**【請求項 2】**

前記第1走査期間と前記第2走査期間において、黒色データが書き込まれる画素行が異なる画素行である請求項1記載の表示装置の駆動方法。

**【請求項 3】**

行列状に並ぶ画素を有する表示装置において、前記画素の1画素行の内で所定の画素を選択する第1の走査線と、前記1画素行の内のその他の画素を選択する第2の走査線と、前記画素の画素行毎に設けるこれら第1と第2の走査線を順次選択的に駆動する走査線駆動回路と、前記第1の走査線により選択される画素に画像データ又は黒色に応じた電圧を供給する第1の信号線と、前記第2の走査線により選択される画素に画像データ又は黒色に応じた電圧を供給する第2の信号線と、前記第1と第2の信号線を駆動する信号線駆動回路とを有し、前記走査線駆動回路は、前記第1の走査線と当該走査線とは別の画素行を選択する第2の走査線を同時に駆動し、前記信号線駆動回路は、画像データに応じた電圧又は黒色に応じた電圧のいずれか一方を前記第1の信号線に出力すると共に、他方を第2の信号線に出力することで、画像データに応じた電圧と黒色に応じた電圧をそれぞれ異なる画素行の画素に同時に書き込むことを特徴とする表示装置。20

**【請求項 4】**

前記第1の走査線により選択される画素と、前記第2の走査線により選択される画素が、それぞれ隣接する複数の画素からなる画素列毎に配置されることを特徴とする請求項3に記載の表示装置。30

**【請求項 5】**

前記第1の走査線により選択される画素と、前記第2の走査線により選択される画素が同数であるよう前記第1の信号線と前記第2の信号線が、それぞれ前記信号線の本数の半分の本数とすることを特徴とする請求項3に記載の表示装置。

**【請求項 6】**

前記信号線駆動回路が、前記信号線本数の半分のシフト段数を持ち、順次入力される画像データをシフトしながら格納するシフトレジスタ回路と、前記シフトレジスタ回路の各段の出力である前記信号線本数の半分の画像データを一度にラッチして格納するラッチ回路と、前記ラッチ回路に格納された前記信号線本数の半分の画像データを表示装置の特性に合わせて階調電圧に変換するD/Aコンバータと、前記D/Aコンバータから出力される前記信号線本数の半分の画像データに応じた電圧を所定の前記信号線へ出力すると共に、前記黒色に応じた電圧を前記所定の信号線以外の信号線へ出力する出力バッファとから構成されることを特徴とする請求項3乃至請求項5の何れかに記載の表示装置。40

**【請求項 7】**

前記信号線駆動回路が、前記画像データに応じた電圧と前記黒色に応じた電圧を選択して前記信号線へ出力するマルチプレクサを有することを特徴とする請求項6に記載の表示装置。

**【発明の詳細な説明】****【0001】**

**【発明の属する技術分野】**

本発明は、表示装置、特に、液晶表示装置の残像現象を解決する表示装置の駆動回路に関するものである。

**【0002】****【従来の技術】**

近年、液晶表示装置 (Liquid Crystal Display : 以下、LCDと称する) は大型化、高精細化が進み、表示される画像もパソコンコンピュータやワードプロセッサ等に用いられる液晶表示装置のように主として静止画像を扱うものから、TV等として用いられる液晶表示装置のように動画像を扱う分野にも普及しつつある。LCDは、CRT (Cathod Ray Tube) を備えるTVに比べて薄型であり、場所をさほど占有せずに設置することができるため、今後一般家庭への普及率が高くなるものと考えられる。また、かかる液晶表示装置においては、液晶の劣化を防ぐため、いわゆる交流駆動を行い、液晶に対して直流成分の電圧が長時間印加されないように制御するのが一般的である。交流駆動を行う方法の一例として、共通電極に印加する電圧を一定にし、画素電極に正極性と負極性の信号電圧を交互に印加する方法がある。

**【0003】**

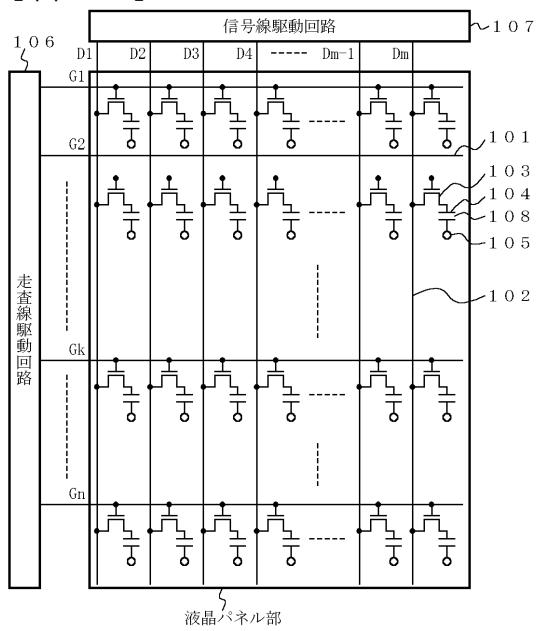

図13は、従来の液晶パネルのアクティブマトリクス基板の構成例を示す図である。このアクティブマトリクス基板上には、n (nは自然数) 本の走査線101とm本 (mは自然数) の信号線102が格子状に配置され、走査線101と信号線102の各交差部付近に非線形素子 (スイッチング素子) であるTFT (Thin Film Transistor or) 103が設けられている。

TFT 103のゲート電極は走査線101に接続され、ソース電極は信号線102に接続され、ドレイン電極は画素電極104にそれぞれ接続される。画素電極104は、アクティブマトリクス基板と対向して配置される対向基板上の共通電極105と液晶 (図示省略) を挟んで画素容量108を構成する。

**【0004】**

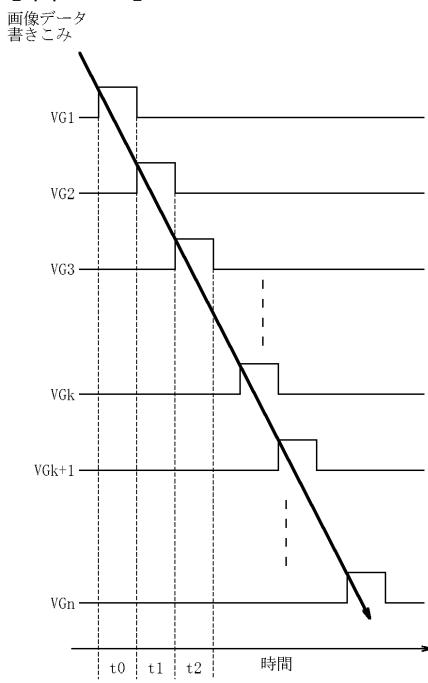

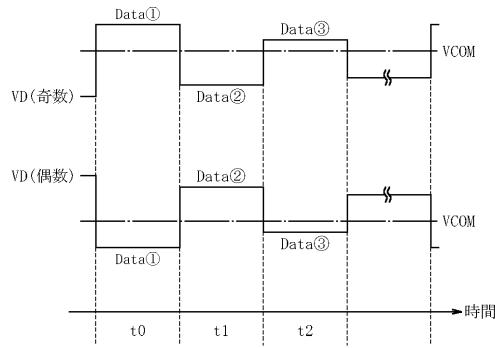

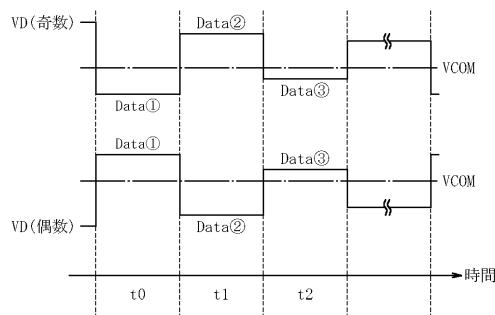

上記走査線101及び信号線102は、走査走線駆動回路106及び信号線駆動回路107にそれぞれ接続されている。走査線駆動回路106は図14に示すように、n本の走査線101に対して高電位を順次駆動して、各走査線101に接続されたTFTをオン状態とする。走査走線駆動回路106が走査されている状態において、図15に示すように信号線駆動回路107が画像データに応じた階調電圧VDをm本の信号線の何れかに出力することにより、オン状態となっているTFT 103を介して階調電圧が画素電極104に供給される。この階調電圧は、一定の電位に設定された共通電極105と画素電極104との間の電位差となり、この電位差により発生する電界によって液晶を透過する光の透過量が制御されて表示が行われる (図15のData 1 ~ 3は、1~3行目の画素データを表す)。このようにして、図16に示すように液晶表示パネル部が駆動される。

**【0005】**

この液晶表示パネル部において動画像の表示を行った場合、現状では残像現象等の画質劣化を引き起こすという問題が生じる。

**【0006】**

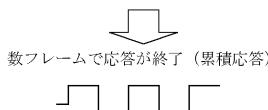

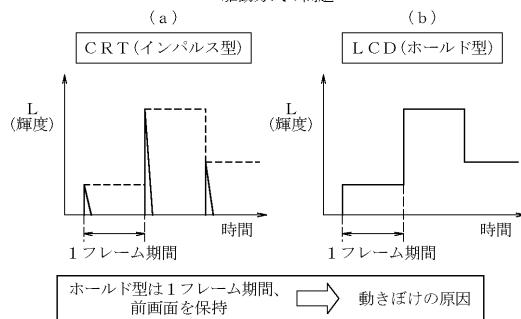

図17は、液晶の応答速度によりもたらされる輝度の応答特性を示したものである。液晶材料の応答速度が遅いため、階調変化が起きると1フレーム期間では階調変化に追随できず、数フレーム期間を要する形で累積応答する。これが残像現象の一因と考えられている。この問題を解決する策として様々な高速応答の液晶材料等の研究が進められている。

**【0007】**

しかしながら、上記の残像現象等の問題は、液晶の応答速度だけに原因があるのでなく、LCDの表示方法に起因するという報告がNHK放送技術研究所等からなされている (例えば、1999年電子情報通信学会総合大会、SC-8-1、pp. 207-208等を参照されたい)。以下、LCDの表示方法の問題について、CRTの駆動方法とLCDの駆動方法とを比較して説明する。

**【 0 0 0 8 】**

液晶表示装置は、図14、15に示すような線順次駆動方式であり、表示画像を1フレーム期間保持するホールド型表示装置である。表示画像を1フレーム期間保持するため、表示画像と人間の目の動きとの間にズレが発生し動きボケが生じる。

**【 0 0 0 9 】**

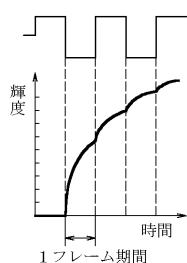

図18は、ある画素についてCRTとLCDの表示光の時間応答の比較結果を示す図であり、(a)はCRTの時間応答を示す図であって、(b)はLCDの時間応答を示す図である。

**【 0 0 1 0 】**

図18(a)に示すように、CRTは、電子ビームが管面の蛍光体に当った時点から数ミリ秒の間だけ光を発する、いわばインパルス型表示装置であるのに対し、図18(b)に示すLCDは、画素へのデータの書き込みが終わった時から次の書き込みに至るまで1フレーム期間に渡って表示光保持するいわゆるホールド型表示装置である。

**【 0 0 1 1 】**

かかる特性を有するCRT及びLCDで動画像を表示する場合、図18(a)に示されたように、インパルス型表示装置であるCRTは時間に対応した位置に表示対象物が瞬間に表示されるのに対し、ホールド型表示装置であるLCDでは、新たに書き込みを行う直前まで1フレーム前の画像が残ることになり、動きボケとなって見える原因となる。

**【 0 0 1 2 】**

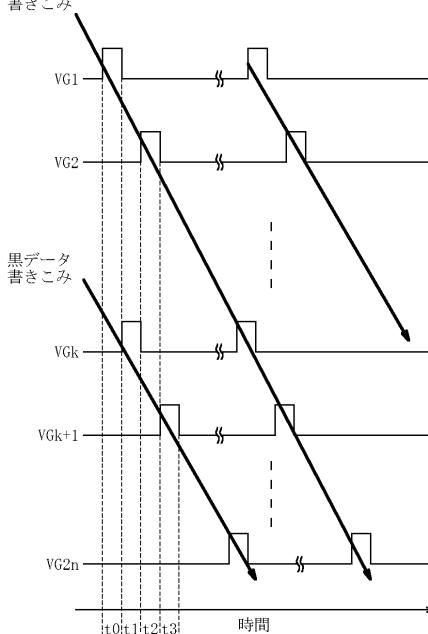

この動きボケを解消するため、高速応答の液晶パネルの開発と共に、動画表示用の駆動方法が特開平2000-122596号公報等により検討されている。このホールド型表示装置特有の動きボケを解消するために、図13の液晶パネルのアクティブマトリクス基板に対して図19、図20に示す駆動方法が用いられる。

**【 0 0 1 3 】**

図19、20に示される駆動方法は、1フレーム期間中に黒画像を挿入することで、目をリセットし動画ボケを解消する方法である。

**【 0 0 1 4 】**

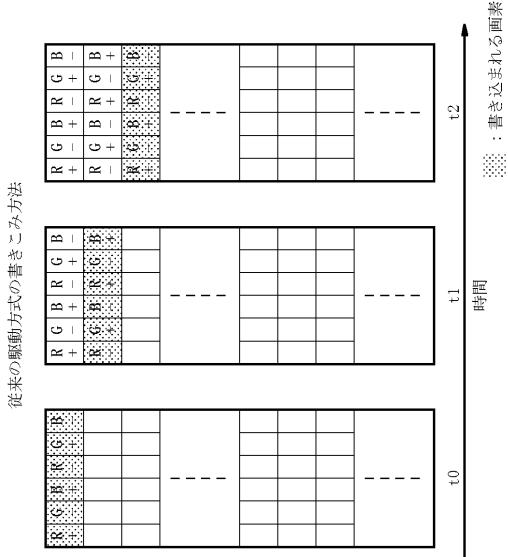

図19、20のような駆動方法を用いることで、図21に示すように或る画素行の全画素に同時に画像データを書き込むのとは別に、当該画素行と複数行離れた画素行の全画素に同時に黒表示の電圧を印加して、残像現象を抑えようとするものである。

**【 0 0 1 5 】**

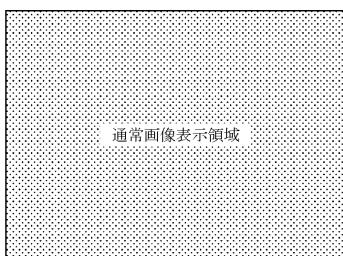

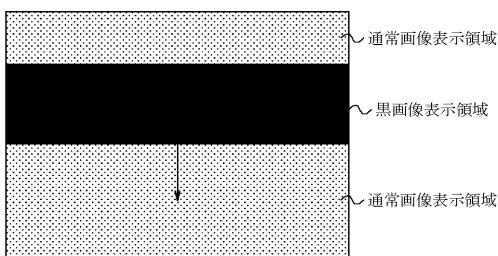

図22に図14、15で駆動した場合の表示イメージを、図23に図19、20で駆動した場合の表示イメージをそれぞれ示す。図23では、黒画面表示領域がスキャンされることで目がリセットされ、動画ボケが解消される。

**【 0 0 1 6 】****【発明が解決しようとする課題】**

しかしながら、上記のような信号線駆動方式を用いて動画ボケが解消されたとしても、液晶表示装置のコスト削減が強く求められている昨今の状況において、信号線駆動回路の液晶表示装置のコストに占める割合は依然として従来と同様に高いままであり、動画ボケを解消するのと併せて信号線駆動回路のチップサイズを縮小することが重要な課題となっている。

**【 0 0 1 7 】**

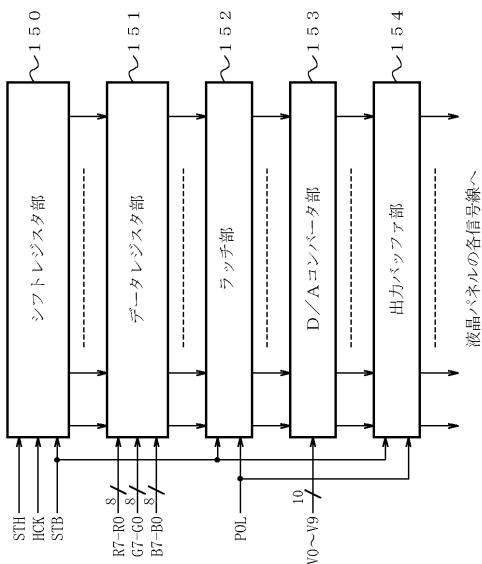

図24に従来の信号線駆動回路の構成を示す。図24に示されるように、信号線駆動回路は、シフトレジスタ部150、データレジスタ部151、ラッチ部152、D/Aコンバータ部153、出力バッファ部154から構成されている。各データバス(R0~R7、G0~G7、B0~B7)から画像データが入力され、データレジスタ部151を介して、ラッチ部152に信号線分の画像データ(m画素分の画像データ)が格納される。格納された信号線分の画像データは、D/Aコンバータ部153で液晶パネルの透過率特性に合わせた電圧に変換され、出力バッファ154から出力される。

**【 0 0 1 8 】**

10

20

30

40

50

なお、S T H はスタートパルス信号、H C K は水平方向クロック信号、S T B は出力タイミングパルス信号、P O L は出力極性反転信号、V 0 ~ V 9 は基準階調電圧である。

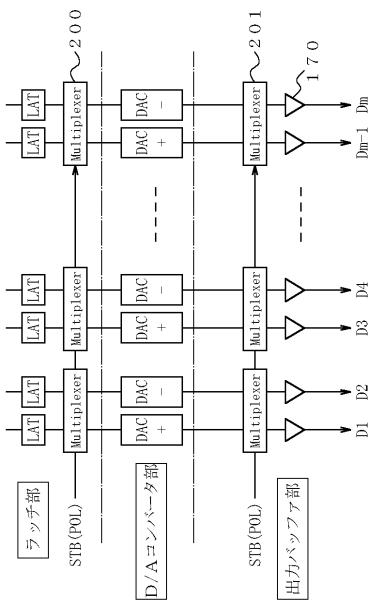

#### 【0019】

図25に信号線駆動回路の出力部構成の詳細を示す。信号線に正極性と負極性の信号電圧を交互に印加するため、D / A コンバータ部には画像データに応じて正極性の階調電圧を出力するD A C + と画像データに応じて負極性の階調電圧を出力するD A C - が配置されており、ラッチ部及出力バッファ部にあるマルチプレクサ200と201をS T B 信号(又はP O L 信号)により切替えることで交流駆動を実現している。

#### 【0020】

例えは、D 1への画像データは、図25の1番左のL A T に格納された後、マルチプレクサ200でD A C + 又はD A C - を介して、マルチプレクサ201により選択され、出力アンプ170を通ってD 1へ出力される。なお、1番左のL A T に格納された画像データがD 2に出力されることはない。

#### 【0021】

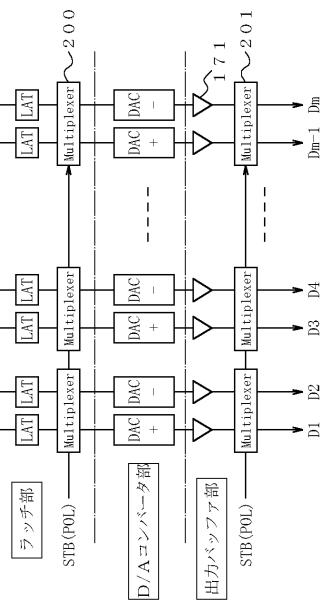

また、従来の信号線駆動回路の出力部構成は、図26に示す構成の場合もある。

#### 【0022】

以上説明したように、従来の信号線駆動回路は信号線分の画像データ(m画素分の画像データ)を保持した後に各信号線へ同時に出力する構成となっているため、信号線への出力数によってチップサイズはほぼ決まっている。

#### 【0023】

図19～図21に示すような技術においても信号線駆動回路部は依然として、信号線分の画像データを保持した後に各信号線へ同時に出力する形式であり、信号線駆動回路を縮小する構成とはなっていない。

#### 【0024】

本発明の目的は、動画ボケを解消すると共に、信号線駆動回路部のチップサイズを縮小することを可能とする表示装置の駆動方法及びそれを用いた表示装置の駆動回路を提供することにある。

#### 【0025】

##### 【課題を解決するための手段】

本発明の表示装置の駆動方法は、行列状に並ぶ画素を有する表示装置の駆動方法において

、前記画素の画素行のうち少なくとも1つの画素行に画像データを書き込む期間を第1走査期間と第2走査期間に分け、

前記第1走査期間において、任意の画素行の内で所定の画素列に位置する画素に画像データを書き込むと共に、前記任意の画素行と異なる画素行の内で前記所定の画素列以外に位置する画素に黒色データを書き込み、

前記第2走査期間は、前記第1走査期間において画像データを書き込んだ画素行の内で画像データを書き込んだ画素以外の画素に画像データを書き込むと共に、前記第1走査期間において黒色データを書き込んだ画素行の内で黒色データを書き込んだ画素以外の画素に黒色データを書き込むことを特徴とする。

#### 【0026】

上記本発明の表示装置の駆動方法は、前記第1走査期間と前記第2走査期間において、黒色データが書き込まれる画素行が異なる画素行である。

#### 【0027】

本発明の表示装置は、行列状に並ぶ画素を有する表示装置において、前記画素の1画素行の内で所定の画素を選択する第1の走査線と、前記1画素行の内のその他の画素を選択する第2の走査線と、前記画素の画素行毎に設けるこれら第1と第2の走査線を順次選択的に駆動する走査線駆動回路と、前記第1の走査線により選択される画素に画像データ又は黒色に応じた電圧を供給する第1の信号線と、前記第2の走査線により選択される画素に画像データ又は黒色に応じた電圧を供給する第2の信号線と、前記第1と第2の信号線を

10

20

30

40

50

駆動する信号線駆動回路とを有し、前記走査線駆動回路は、前記第1の走査線と当該走査線とは別の画素行を選択する第2の走査線を同時に駆動し、前記信号線駆動回路は、画像データに応じた電圧又は黒色に応じた電圧のいずれか一方を前記第1の信号線に出力すると共に、他方を第2の信号線に出力することで、画像データに応じた電圧と黒色に応じた電圧をそれぞれ異なる画素行の画素に同時に書き込むことを特徴とする。本発明の表示装置は、次のような適用形態を有する。

#### 【0028】

上記本発明の表示装置は、前記第1の走査線により選択される画素と、前記第2の走査線により選択される画素が、それぞれ隣接する複数の画素からなる画素列毎に配置されることを特徴とする。10

#### 【0029】

上記本発明の表示装置は、前記第1の走査線により選択される画素と、前記第2の走査線により選択される画素が同数であるように前記第1の信号線と前記第2の信号線が、それぞれ前記信号線の本数の半分の本数とすることを特徴とする。

#### 【0030】

上記本発明の表示装置は、前記信号線駆動回路が、前記信号線本数の半分のシフト段数を持ち、順次入力される画像データをシフトしながら格納するシフトレジスタ回路と、前記シフトレジスタ回路の各段の出力である前記信号線本数の半分の画像データを一度にラッチして格納するラッチ回路と、前記ラッチ回路に格納された前記信号線本数の半分の画像データを表示装置の特性に合わせて階調電圧に変換するD/Aコンバータと、前記D/Aコンバータから出力される前記信号線本数の半分の画像データに応じた電圧を所定の前記信号線へ出力すると共に、前記黒色に応じた電圧を前記所定の信号線以外の信号線へ出力する出力バッファとから構成されることを特徴とし、さらに、前記信号線駆動回路が、前記画像データに応じた電圧と前記黒色に応じた電圧を選択して前記信号線へ出力するマルチプレクサを有することを特徴とする。20

#### 【0031】

#### 【発明の実施の形態】

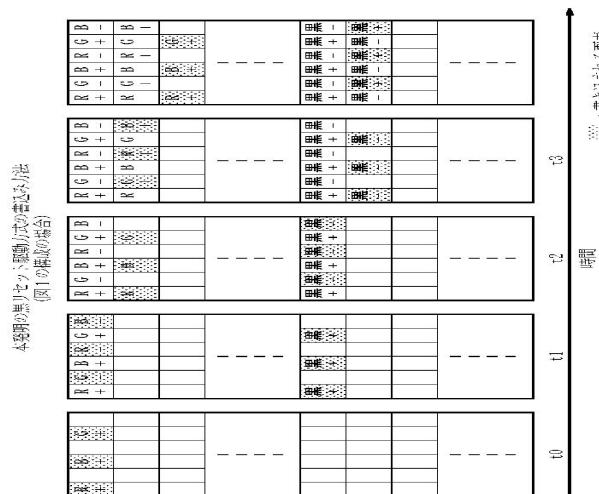

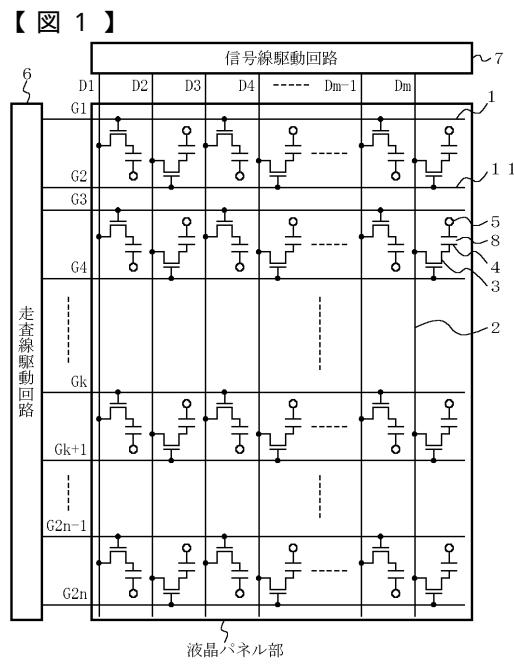

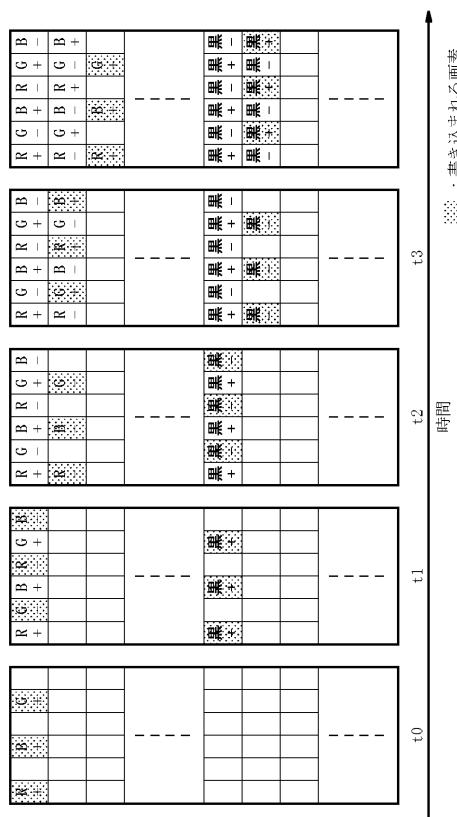

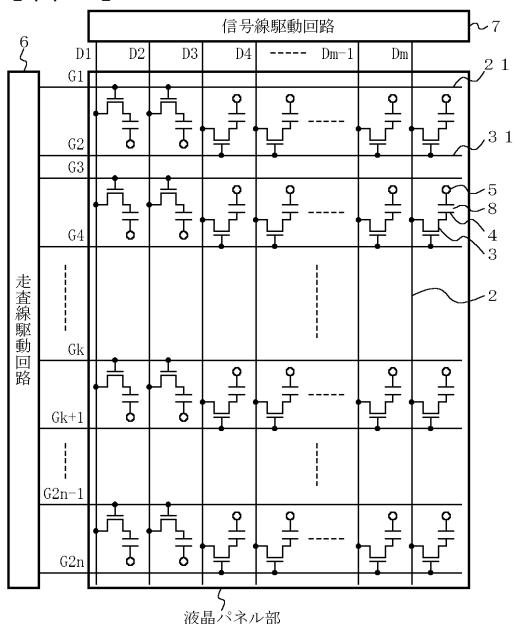

図1～図4に、本発明の表示装置の概略構成及び駆動方法を示す。

#### 【0032】

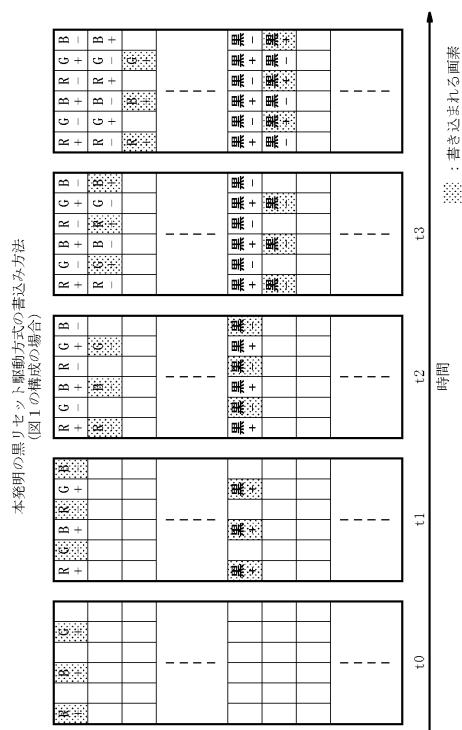

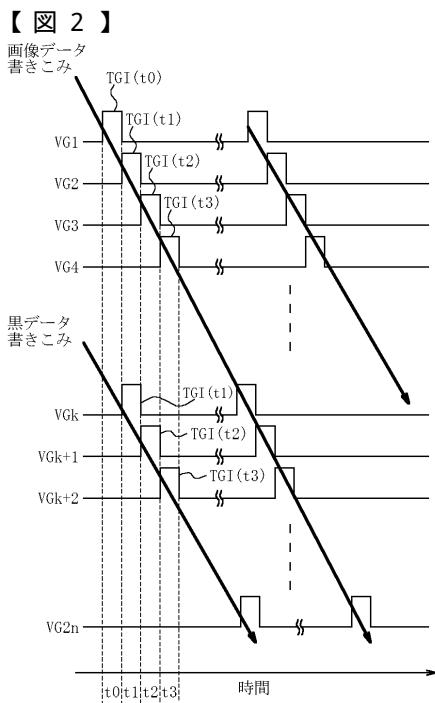

図1に示すように、走査線方向の各画素は、1画素毎に異なった2本の走査線1、11にTFT3のゲート電極が接続されている。各走査線は、図2に示すように、1フレーム期間に画像データ書き込み用パルスTGIと黒データ書き込み用パルスTGBの選択期間を持ち、それぞれ線順次駆動される。30

#### 【0033】

また、信号線駆動回路からは、図3に示すように信号線2毎に画像データData(図3のData1～3は、1～3行目の画素データを表す)と黒データBLが出力され、それぞれの信号線2は出力毎に画像データと黒データを交互に出力する。画像データは画像データ書き込み用パルスTGIにより選択される画素に書き込まれ、黒データは黒データ書き込み用パルスTGBにより選択される画素に書き込まれる。

#### 【0034】

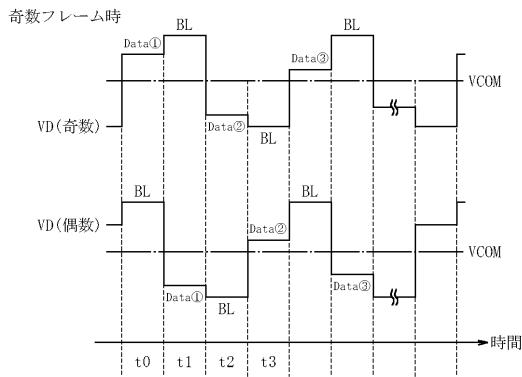

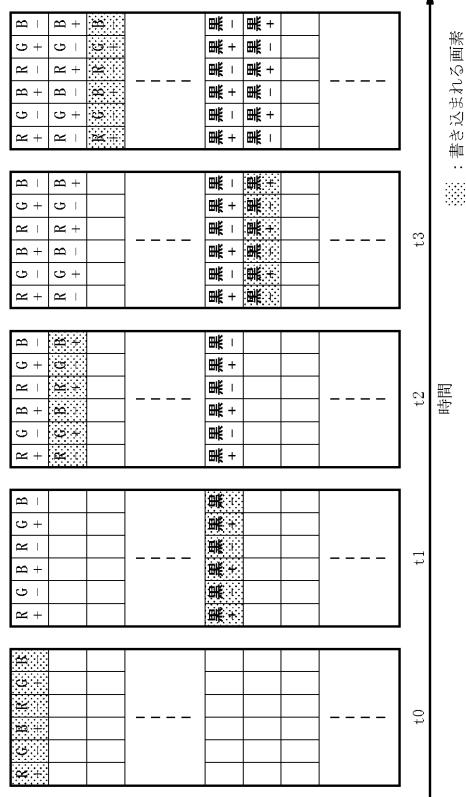

図4は、液晶パネル上の1フレーム期間内での画素データ書き込みと黒データ書き込みの様子を示す模式図である。40

#### 【0035】

図2に示すように、まず、時間t0において走査線VG(1)にTGI(t0)が印加されると、図4のように1画素行目の左側の画素に画素データが表示される。

#### 【0036】

次に、時間t1において、走査線VG(2)にTGI(t1)、走査線VG(k)にTGB(t1)がそれぞれ印加される( $2 < k < n - 1$ 、kは奇数)と、図4のように、1画素行目の右側の画素に画素データが表示され、同時に、 $(k + 1) / 2$ 画素行目の左側の画素に黒データが表示される。50

**【 0 0 3 7 】**

次に、時間  $t_2$ において、走査線  $VG(3)$ に  $TGI(t_2)$ 、走査線  $VG(k+1)$ に  $TGB(t_2)$ がそれぞれ印加されると、図4のように、2画素行目)の奇数番目の画素に画素データが表示され、同時に、 $(k+1)/2$ 画素行目の偶数番目の画素に黒データが表示される。

**【 0 0 3 8 】**

次に、時間  $t_3$ において、走査線  $VG(4)$ に  $TGI(t_3)$ 、走査線  $VG(k+2)$ に  $TGB(t_3)$ がそれぞれ印加されると、図4のように、2画素行目の偶数番目の画素に画素データが表示され、同時に、 $(k+3)/2$ 画素行目の奇数番目の画素に黒データが表示される。

10

**【 0 0 3 9 】**

以上の動作を順次繰り返す。図1の回路構成及び図2、図3の駆動方法を用いることにより、動画ボケを解消する従来の駆動方法(図19～図21)と同等の表示イメージ(図23(b))が実現される。

**【 0 0 4 0 】**

図1の液晶パネルの回路構成は、図5に示すように、走査方向の各画素を、2画素毎に異なった2本の走査線  $2_1$ 、 $3_1$ に接続する構成としても良い。

**【 0 0 4 1 】**

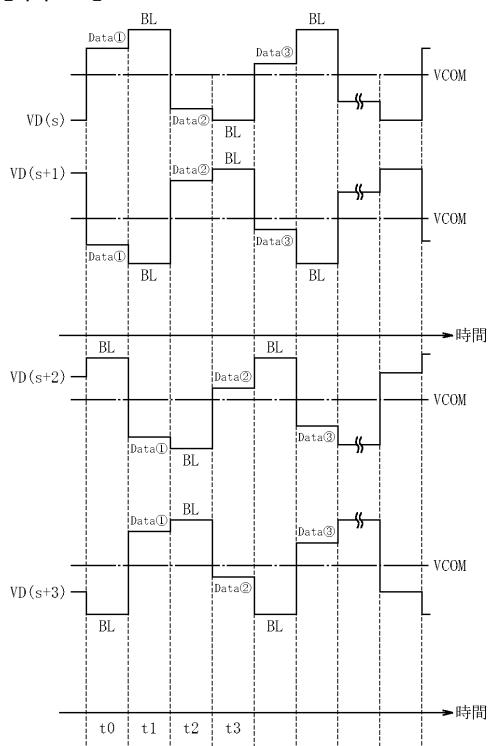

図5の構成とする場合は、信号線駆動回路から図6に示すように、信号線2を2本毎に画像データData(図6のData1～3は、1～3行目の画素データを表す)と黒データBLが出力され、それぞれの信号線2は出力毎に画像データと黒データを交互に出力する。(なお、図6の各信号線電圧:  $VD(s \sim s+3)$ はフレーム毎に反転する。 $s$ は自然数。)

20

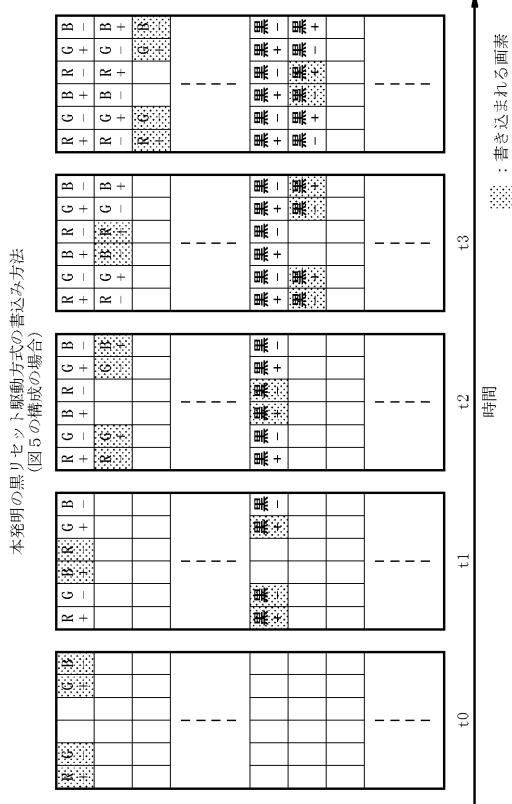

図7は、図5に示す構成における液晶パネル上の1フレーム期間内での画素データ書き込みと黒データ書き込みの様子を示す模式図である。

**【 0 0 4 2 】**

本発明の構成にすることによって、信号線駆動回路からは、信号線本数の半分( $m/2$ 本)に画素データに応じた階調電圧が出力され、残りの半分の信号線に黒データに応じた電圧が同時に出力される。

30

**【 0 0 4 3 】**

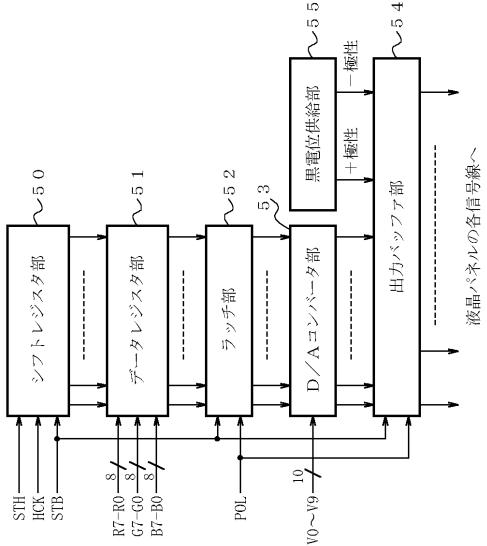

図8は、本発明に使用される信号線駆動回路の概略構成図である。本発明の信号線駆動回路は、図24に示す従来の信号線駆動回路と比較して、黒電位供給部55が付加されている。

**【 0 0 4 4 】**

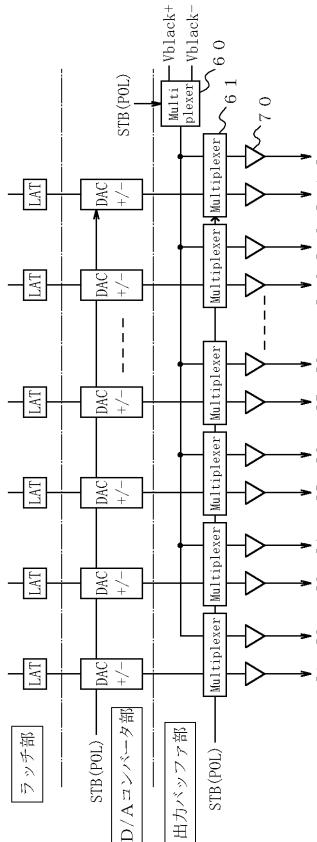

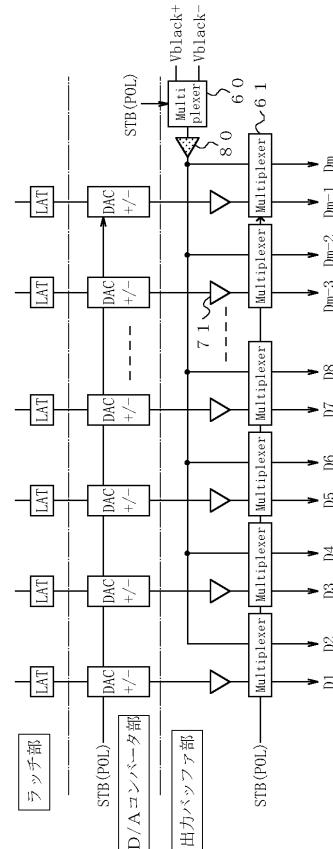

図9に信号線駆動回路の出力部構成の詳細を示す。なお、図9は、液晶パネル部が図1に示す構成の場合に使用される。図9に示すように画像データを格納するラッチ回路(LAT)は、従来の信号線駆動回路(図25)と比較して半分となっている。また、図1に示す構成では、画像データを出力する信号線への極性は同極性であるので(図4)、画像データに応じた正極性の階調電圧と負極性の階調電圧をSTB信号により切替えて出力するDAC+/−が用いられている。出力バッファ部のマルチプレクサ61は、DAC+/−より出力される画像データに応じた正極性の階調電圧又は、負極性の階調電圧と、マルチプレクサ60により選択された正極性の黒画像の電圧  $V_{b1ack+}$  又は負極性の黒画像の電圧  $V_{b1ack-}$  を、2本の信号線に対してそれぞれ選択し、出力する。なお、LATに格納される画像データは、奇数番目の信号線への画像データと、偶数番目の信号線への画像データとが信号線への出力毎に入れられる。図9に示す出力部構成とすることで図3に示す出力波形を実現している。

40

**【 0 0 4 5 】**

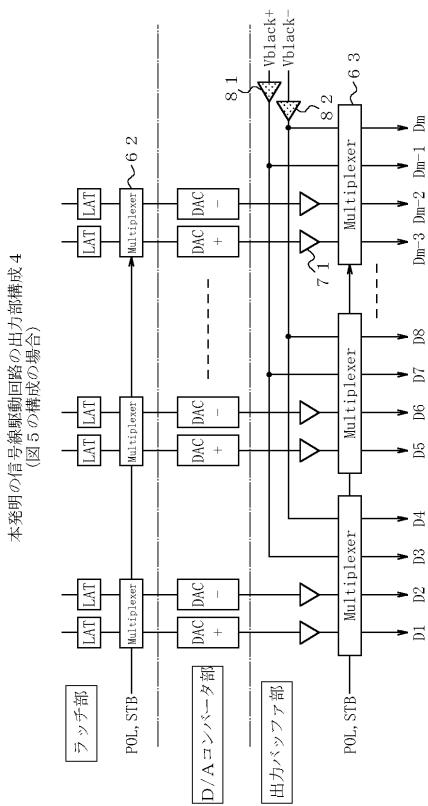

また、本発明の信号線駆動回路は、図10に示されるような回路構成としても良い。黒電位用出力アンプ80は  $V_{b1ack+}$  又は  $V_{b1ank-}$  のみの出力なため、ダイナミックレンジを必要としないアンプを使用することが可能となる。

50

**【 0 0 4 6 】**

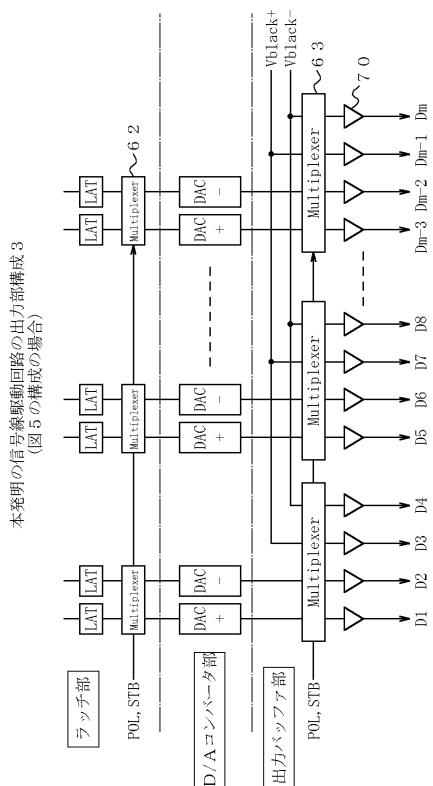

液晶パネル部が図5に示す構成の場合は、信号線駆動回路の出力部構成を図11に示すように構成する。図25に示す従来の信号線駆動回路との違いは、出力バッファ部のマルチプレクサ63が4本の信号線に対して、DAC+より出力される画像データに応じた正極性の階調電圧、DAC-より出力される画像データに応じた負極性の階調電圧、正極性の黒画像の電圧Vb1ack+、負極性の黒画像の電圧Vb1ack-をそれぞれ選択し、出力することである。また、LAT、マルチプレクサ62、DAC+、DAC-は、それぞれ従来の信号線駆動回路の半分となる。

**【 0 0 4 7 】**

図5に示すような液晶パネルの場合、LATに格納される画像データは、マルチプレクサ63により選択される4本の信号線中の左2本、又は右2本が信号線への出力毎に入れられる。LATに格納される画像データは、マルチプレクサ62によりDAC+又はDAC-を介して、マルチプレクサ63に入力され、所定の信号線へ選択が行われると共に、所定の信号線以外には正極性の黒画像の電位Vb1ack+と負極性の黒画像の電位Vb1ack-が出力されることで、図6に示す出力となる。また、本発明の信号線駆動回路は、図12に示されるような回路構成としても良い。黒電位用出力アンプ81と黒電位用出力アンプ82は、それぞれVb1ack+、Vb1ank-のみの出力なため、ダイナミックレンジを必要としないアンプを使用することが可能となる。

**【 0 0 4 8 】**

本発明の回路構成を適用することにより、従来の信号線駆動回路（図25参照）と比べて、ラッチ回路（LAT）には従来の画素データの半分のデータのみを保持すれば良いことになり、ラッチ回路以外にも図8に示す信号線駆動回路部を構成するシフトレジスタ部50、データレジスタ部51、D/Aコンバータ部53のチップサイズを約半分に縮小でき、表示装置として大幅に占有面積を小さくすることができる。

**【 0 0 4 9 】**

以上のように、本発明の表示装置では、動画表示時の動画ボケを防止できると共に、信号線駆動回路のチップサイズを大幅に縮小することが可能となり、表示装置のコンパクト化が必要とされる技術分野において大いにその効果を発揮することができる。

**【 0 0 5 0 】****【 発明の効果 】**

以上のように、本発明の表示装置及びその駆動方法によれば、行列状に並ぶ画素を有する表示装置において、画素の1画素行の内で所定の画素を選択する第1の走査線と、他の画素を選択する第2の走査線と、画素行毎に設けるこれら第1と第2の走査線を順次選択的に駆動する走査線駆動回路と、第1の走査線により選択される画素に画像データ又は黒色に応じた電圧を供給する第1の信号線と、第2の走査線により選択される画素に画像データ又は黒色に応じた電圧を供給する第2の信号線と、第1と第2の信号線を駆動する信号線駆動回路とを有し、走査線駆動回路は、第1の走査線と当該走査線とは別の画素行を選択する第2の走査線を同時に駆動し、信号線駆動回路は、出力タイミングパルス信号に応じて第1と第2の信号線に画像データに応じた電圧と黒色に応じた電圧を交互に出力することで、画像データに応じた電圧と黒色に応じた電圧をそれぞれ異なる画素行の画素に同時に供給する。従って、従来の信号線駆動回路と比べて、ラッチ回路（LAT）には従来の画素データの半分のデータのみを保持すれば良いことになり、ラッチ回路以外にも信号線駆動回路部を構成するシフトレジスタ部、データレジスタ部、D/Aコンバータ部のチップサイズを約半分に縮小でき、表示装置として大幅に占有面積を小さくすることができる。

**【 0 0 5 1 】**

以上のように、本発明の表示装置では、動画表示時の動画ボケを防止できると共に、信号線駆動回路のチップサイズを大幅に縮小することが可能となる。

**【 図面の簡単な説明 】**

【図1】本発明の実施形態の表示装置の概略回路構成である。

10

20

30

40

50

【図2】本発明の実施形態の表示装置における走査線の駆動方法を示すタイミングチャート図である。

【図3】本発明の実施形態の表示装置における信号線の駆動方法を示すタイミングチャート図である。

【図4】本発明における液晶パネル上の1フレーム期間内での画素データ書き込みと黒データ書き込みの様子を示す模式図である。

【図5】本発明の実施形態の表示装置の他の形態の概略回路構成である。

【図6】図5に示す本発明の実施形態における信号線の駆動方法を示すタイミングチャート図である。

【図7】図5に示す本発明の実施形態における液晶パネル上の1フレーム期間内での画素データ書き込みと黒データ書き込みの様子を示す模式図である。 10

【図8】本発明の実施形態の表示装置に用いられる信号線駆動回路部を構成する回路ブロックである。

【図9】図1に示す本発明の実施形態の表示装置に用いられる出力部近傍の信号線駆動回路図である。

【図10】図1に示す本発明の実施形態の表示装置に用いられる出力部近傍の別の形態の信号線駆動回路図である。

【図11】図5に示す本発明の実施形態の表示装置に用いられる出力部近傍の信号線駆動回路図である。

【図12】図5に示す本発明の実施形態の表示装置に用いられる出力部近傍の別の形態の信号線駆動回路図である。 20

【図13】従来の液晶パネルのアクティブマトリクス基板の概略回路構成である。

【図14】従来の表示装置における走査線の駆動方法を示すタイミングチャート図である。

【図15】従来の表示装置における信号線の駆動方法を示すタイミングチャート図である。

【図16】従来の方法による画素データ書き込みの様子を示す模式図である。

【図17】液晶の応答速度によりもたらされる表示装置の輝度の応答特性を示したものである。

【図18】ある画素についてCRTとLCDの表示光の時間応答の比較結果を示す図である。 30

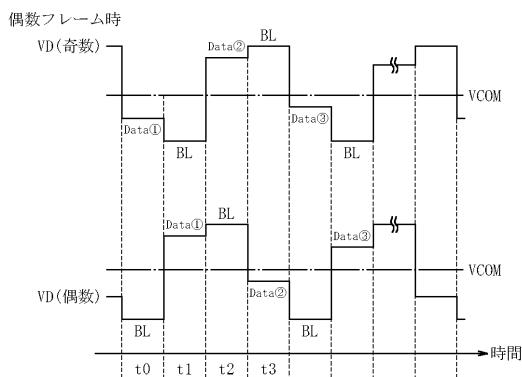

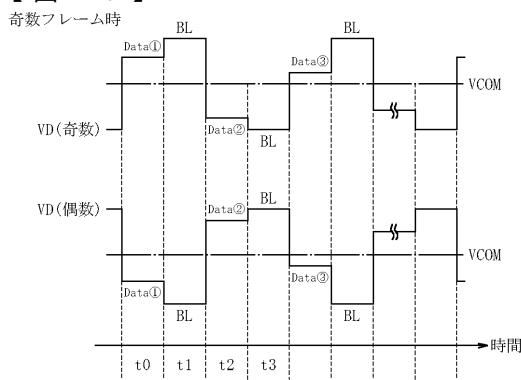

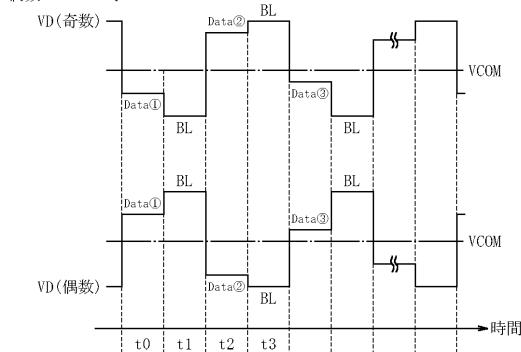

【図19】ホールド型表示装置特有の動きボケを解消するために用いられる表示装置の駆動方法における走査線のタイミングチャート図である。

【図20】ホールド型表示装置特有の動きボケを解消するために用いられる表示装置の駆動方法における信号線のタイミングチャート図である。

【図21】ホールド型表示装置特有の動きボケを解消する駆動方法による画素データ書き込みと黒データ書き込みの様子を示す模式図である。

【図22】図14、15に示される従来の駆動方法での表示イメージである。

【図23】図19、20に示されるホールド型表示装置特有の動きボケを解消する駆動方法での表示イメージである。 40

【図24】従来の表示装置に用いられる信号線駆動回路部を構成する回路ブロックである。

【図25】従来の表示装置に用いられる出力部近傍の信号線駆動回路図である。

【図26】従来の表示装置に用いられる出力部近傍の別の形態の信号線駆動回路図である。

#### 【符号の説明】

1、111、211、311、101 走査線

2、102 信号線

3、103 薄膜トランジスタ(TFT)

4、104 画素電極

- 5、105 共通電極

6、106 走査線駆動回路

7、107 信号線駆動回路

8、108 画素容量

50、150 シフトレジスタ部

51、151 データレジスタ部

52、152 ラッチ部

53、153 D/Aコンバータ部

54、154 出力バッファ部

55 黒電位供給部

60、61、200、201 2対1マルチプレクサ

63 4対1マルチプレクサ

70、71、170、171 出力アンプ

80、81、82 黒電位用出力アンプ

10

【図3】

【図4】

【図5】

【図6】

sは自然数( $s < m$ )

【図7】

【図8】

:書き込まれる画素

【図9】

本発明の信号線駆動回路の出力部構成1

(図1の構成の場合)

【図10】

本発明の信号線駆動回路の出力部構成2

(図1の構成の場合)

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

奇数フレーム時

偶数フレーム時

【図16】

【図17】

LCDにおける動画表示の問題点(1)

1フレーム期間より液晶応答が遅い

(TN液晶: 数+m s)

数フレームで応答が終了(累積応答)

【図18】

LCDにおける動画表示の問題点(2)

駆動方式の問題

【図19】

画像データ書き込み

【 図 20 】

偶数フレーム時

【 図 2 1 】

【 図 2 2 】

図14、図15に示される駆動方法での表示イメージ

【 図 2 3 】

図19、図20に示される駆動方法での表示イメージ

【 図 2 4 】

【図 2 5】

従来の信号線駆動回路の出力部構成 1

【図 2 6】

従来の信号線駆動回路の出力部構成 2

## フロントページの続き

(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 3 E |

| G 0 9 G | 3/20 | 6 2 3 F |

| G 0 9 G | 3/20 | 6 2 3 G |

| G 0 9 G | 3/20 | 6 2 3 H |

| G 0 9 G | 3/20 | 6 2 3 W |

| G 0 9 G | 3/20 | 6 2 3 Y |

| G 0 9 G | 3/20 | 6 4 1 C |

| G 0 9 G | 3/20 | 6 4 1 R |

F ターム(参考) 5C006 AA01 AA16 AC21 AC27 AC28 AF44 AF45 AF46 AF51 AF53

AF71 AF83 BB16 BC03 BC06 BC12 BC20 BF03 BF04 BF43

EB05 FA29 FA41

5C080 AA10 BB05 DD03 DD25 EE19 EE29 FF11 GG07 GG08 JJ02

JJ03 JJ04 JJ06

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |            |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置及其驱动方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">JP2004012872A</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 公开(公告)日 | 2004-01-15 |

| 申请号            | JP2002167109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 申请日     | 2002-06-07 |

| [标]申请(专利权)人(译) | NEC电子股份有限公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | NEC电子公司                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |            |

| [标]发明人         | 能勢崇                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |            |

| 发明人            | 能勢 崇                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |            |

| IPC分类号         | G02F1/133 G09G3/20 G09G3/36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| CPC分类号         | G09G3/3685 G09G3/3614 G09G3/3648 G09G2300/0823 G09G2310/0297 G09G2320/0257 G09G2320/0261                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |            |

| FI分类号          | G09G3/36 G02F1/133.550 G02F1/133.570 G09G3/20.612.F G09G3/20.622.M G09G3/20.623.E G09G3/20.623.F G09G3/20.623.G G09G3/20.623.H G09G3/20.623.W G09G3/20.623.Y G09G3/20.641.C G09G3/20.641.R                                                                                                                                                                                                                                                                                                                                |         |            |

| F-TERM分类号      | 2H093/NA16 2H093/NA45 2H093/NA47 2H093/NC22 2H093/NC34 2H093/NC49 2H093/ND01 2H093/ND60 5C006/AA01 5C006/AA16 5C006/AC21 5C006/AC27 5C006/AC28 5C006/AF44 5C006/AF45 5C006/AF46 5C006/AF51 5C006/AF53 5C006/AF71 5C006/AF83 5C006/BB16 5C006/BC03 5C006/BC06 5C006/BC12 5C006/BC20 5C006/BF03 5C006/BF04 5C006/BF43 5C006/EB05 5C006/FA29 5C006/FA41 5C080/AA10 5C080/BB05 5C080/DD03 5C080/DD25 5C080/EE19 5C080/EE29 5C080/FF11 5C080/GG07 5C080/GG08 5C080/JJ02 5C080/JJ03 5C080/JJ04 5C080/JJ06 2H193/ZA04 2H193/ZC26 |         |            |

| 代理人(译)         | 台正彦<br>谷泽恭久                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |            |

### 摘要(译)

要解决的问题：为了解决以下问题：已经开发了一种用于在一个帧周期期间插入黑色图像来消除运动图像模糊的方法，用于诸如液晶显示装置的保持型显示装置，信号线驱动电路部分仍保持所有像素列的像素数据并从信号线驱动电路输出像素数据，并且不构成成为通过减小驱动电路部分来应对紧凑的显示装置。解决方案：像素数据和黑色数据同时写入不同列的两个像素中，通过对同一列的像素执行两次此操作，数据被写入一列的所有像素中。通过在一个帧周期期间对所有像素列执行这样的操作，与传统信号线驱动电路相比，只有一半的传统像素数据必须保持在数据锁存电路中。因此，芯片尺寸可以减小到大约一半并且显示装置的占用面积减小。